Issue 43 Summer 2002

THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

## **Cover Story**

Xilinx CEO Wim Roelandts Reveals How to Survive a Recession and Gain Market Leadership

## ANALYSIS

**Total Cost Management**

**TECHNOLOGY**

How to Build Efficient FIR Filters

Xyron Inc. Makes RTOS Breakthrough

PERSPECTIVE

Using DSP in Real-Time Video Processing

NEWS

IBM ASICs Incorporate Xilinx Technology

Virtex-II Pro – New Products, Reduced Pricing

VIRTER

SPARTAN

GLOBAL SERVICES

PARTNERS

Carlis Collins editor@xilinx.com 408-879-4519

Tom Durkin

Jane Bratun Brendan Bridgford

LeRov Miller

Ryan Wilson

Scott Blair

Dan Teie

tom.durkin@xilinx.com 530-271-0899

EDITOR IN CHIEF

MANAGING EDITOR

CONTRIBUTING EDITORS

DESIGN & ILLUSTRATION

XCell journal

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780 ©2002 Xilinx Inc. All rights reserved.

Xcell is published quarterly. XILINX, the Xilinx logo, CoolRunner, Spartan, and Virtex are registered trademarks of Xilinx Inc. Alliance Series, Xilinx Foundation Series, AllianceCORE, Foundation, IRL, LogiCORE, Selectl/O, WebPACK, WebPOWERED, WebFITTER, VPro, XPERTS, XtremeDSP, CORE Generator, Rocket I/O, Fast Zero Power, SelectRAM, IP-Immersion, System ACE, ChipScope, and all XC-prefix products are trademarks, and The Programmable Logic Company is a service mark of Xilinx Inc. Other brand or product names are trademarks or registered trademarks of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts on lability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby.

## We Did It Again — Only Better This Time

ast year, Xilinx debuted at #14 on the *FORTUNE* 100 Best Companies to Work For<sup>TM</sup> annual list. This year, we broke into the Top 10 with a ranking of #6 – the only Silicon Valley/San Francisco Bay Area company to make the Top 10.

To help determine the new rankings, *FORTUNE* weighed how companies reacted to the economic downturn of 2001. Although revenue at Xilinx declined by 50 percent over the course of 2001, the company decided employee layoffs would come only as a last resort. As a result of significant cost-cutting measures – including tiered salary cuts for everyone except the lowest paid employees – Xilinx managed to avoid layoffs, continued to bring remarkable new products to market, and became larger than all other public programmable logic companies combined.

We believe the FORTUNE magazine ranking reflects the strong values we hold at Xilinx:

- Customer focus

- Respect

- Excellence

- Accountability

- Teamwork

- Integrity

- Very open communication

- Enjoying our work.

"MANY XILINX EMPLOYEES HAVE TOLD ME HOW PROUD THEY ARE TO RECEIVE THIS RECOGNITION. IT SPEAKS AS MUCH ABOUT THE GREAT CULTURE WE HAVE CREATED AT XILINX AS IS DOES ABOUT THE QUALITY OF PEOPLE WHO WORK HERE."

- WIM ROELANDTS, CEO, XILINX INC.

These CREATIVE values are a vital part of our culture, and they make a positive difference for our employees and our customers. Our values make Xilinx a great company to work for – and a great company to work with. Our technology, our service, and our customer satisfaction continue to lead the industry. We are always seeking new ways to make a real difference in our world. And, though technology drives our business, we've built our success on the strong partnerships we've created with our customers, our suppliers, and other technology leaders in our industry.

To learn more about the *FORTUNE* magazine's top 100 companies to work for, go to: *www.fortune.com/lists/bestcompanies/*.

Tom Durkin

Tom Durkin Managing Editor

## Cover Story Pc

## Page 4

## How to Survive a Recession and Gain Market Leadership

"I said from the beginning that we wanted to emerge from the recession a greater company — and I think we have achieved that."

## **Perspective**

## When Total Cost Management Counts, Xilinx PLDs Pay Off

CoolRunner-II CPLDs, Spartan-IIE FPGAs, and Virtex-II EasyPath Platform FPGAs can give you total system cost solutions superior to those of traditional ASICs.

Page 24

Page 8

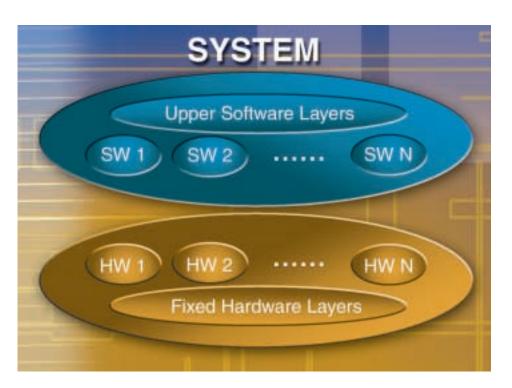

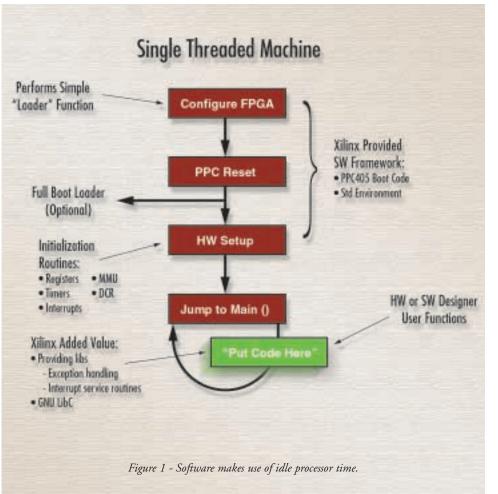

## Exploring Hardware/Software Co-Design with Virtex-II Pro FPGAs

To explore the possibilities of hardware/software co-design, the Xilinx Design Services team created a reference design for a real-time operating system for telecommunications.

## Technology Focus Page 42

## Customize Virtual Private Networks with Spartan-IIE FPGA Solutions

Spartan-IIE FPGA solutions can help you to customize your virtual private network for highest performance, greatest security, and lowest cost.

## Page 55

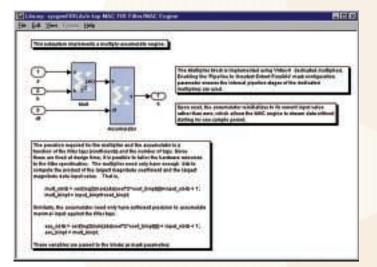

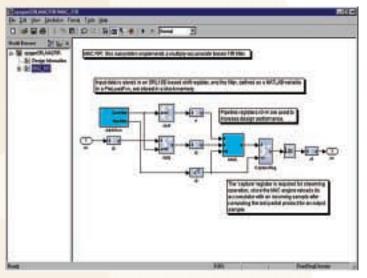

## How to Build an Efficient FIR Filter Using System Generator

Xilinx System Generator 2.2 software enables high-level modeling and implementation of DSP systems in Xilinx Platform FPGAs to outperform traditional DSP processors.

## New Products Page 62

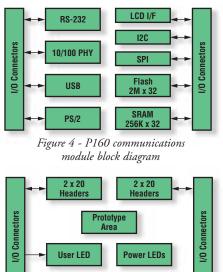

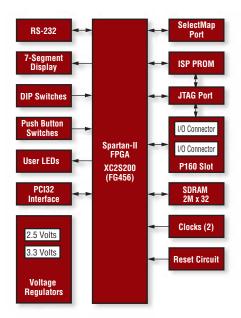

## Develop MicroBlaze Applications with Three Flexible Hardware Evaluation Platforms

MicroBlaze Development Kits from Memec Design demonstrate the versatility of the MicroBlaze soft processor core in a variety of Xilinx FPGAs.

Page 74

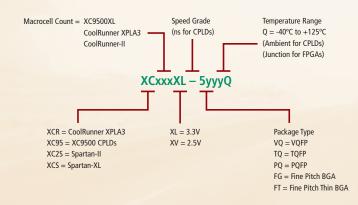

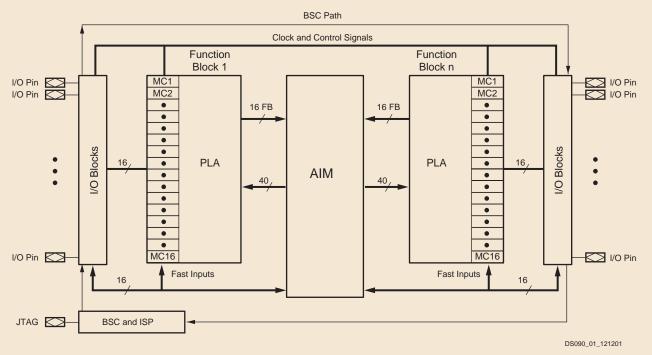

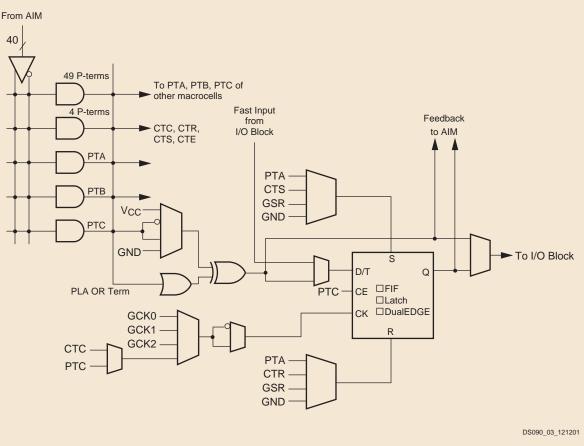

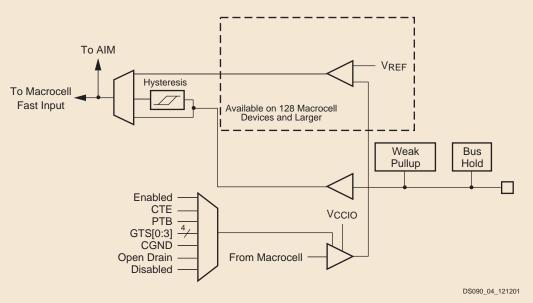

## CoolRunner-II Data Sheet

RealDigital CPLDs consume only microwatts of power, yet provide very high performance — take a look at what's "under the hood."

## Contents Sum

## Summer 2002

| How to Survive a Recession and Gain Market Leadership   | 4   |

|---------------------------------------------------------|-----|

| IBM ASICs Incorporate Xilinx Technology                 | 7   |

| Total Cost Management                                   | 8   |

| New Virtex-II Pro Devices — Lower Cost                  | .12 |

| Virtex-II FPGAs Deliver Advanced Data Security          |     |

| CoolRunner-II CPLDs Go All Digital                      |     |

| If Disaster Strikes, Xilinx Is Prepared                 | .21 |

| Xilinx Software Improves Your Productivity              | .22 |

| Hardware/Software Co-Design with Virtex-II Pro FPGAs    | .24 |

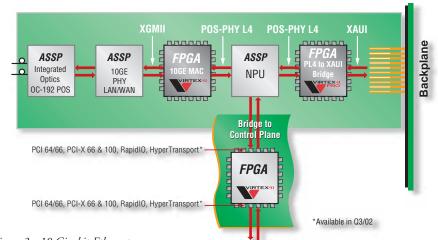

| Virtex-II Pro Platform FPGA Drives Convergence          | .27 |

| Xilinx Offers End-to-End Solutions                      | .30 |

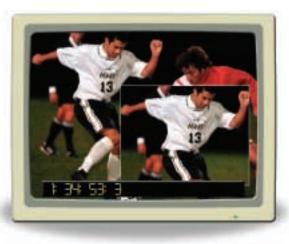

| FPGAs — Enabling DSP in Real-Time Video Processing      | .32 |

| FPGAs Provide Flexibility in Digital TV Development     | .36 |

| Xilinx Technology Can Disable Stolen Cell Phones        | .39 |

| Customize Virtual Private Networks                      | .42 |

| Build Secure and Robust Wireless Communications         | .44 |

| Leading Technologies for Wired Home Networking          | .48 |

| You Can Take It With You: On the Road with Xilinx       | .52 |

| Build an Efficient FIR Filter Using System Generator    | .55 |

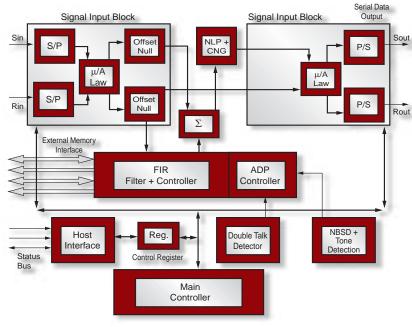

| Xilinx Software Tools to Reduce Line Echoes             | .58 |

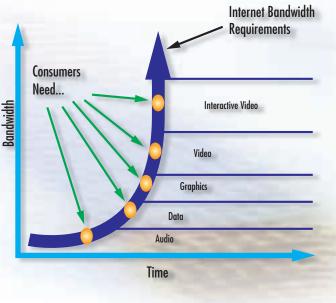

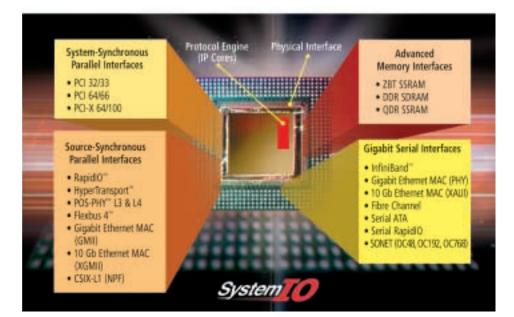

| SystemIO Solution Expands with Bandwidth Demands        | .59 |

| Develop MicroBlaze Applications                         | .62 |

| Xyron Semiconductor's RTOS Breakthrough                 | .64 |

| Power Supply Solutions for Virtex-II Pro Platform FPGAs | .66 |

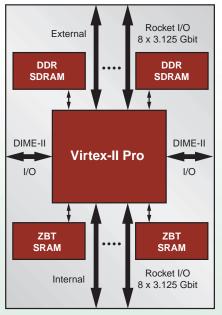

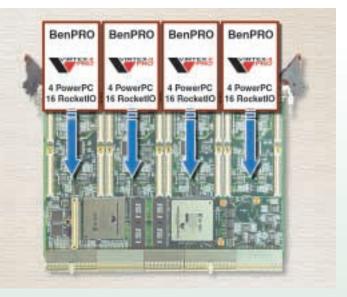

| Nallatech's DIME-II Architecture Goes Pro               | .68 |

| Platform FPGAs Take on ASIC SOCs                        | .70 |

| CoolRunner-II Data Sheet                                | .74 |

| Reference Pages                                         | .86 |

Subscribe to the Xilinx Xcell Journal at: www.xilinx.com/forms/literature.htm.

Visit Xcell Online for the latest news and information, as soon as it arrives at: www.xilinx.com/publications/xcellonline/.

## How to Survive a Recession and Gain Market Leadership

"I said from the beginning that we wanted to emerge from the recession a greater company — and I think we have achieved that."

VIRTEX-II PRO

SPARTAN-I

COOLRUNNER-II

SYSTEM GENERATOR

BPACK

rs

DESIGN SERVICES

EMPLOYEES

## by Wim Roelandts CEO, Xilinx, Inc.

Last year was a very difficult year for the semiconductor industry. In fact, it was the worst recession

ever in the history of semiconductors. In 1985, the industry decreased in a yearover-year basis by 17% to 18%. In 2001, the decline was 32% to 33% – almost twice as bad as 1985.

Nevertheless, I believe that it's in the recessions that the good companies distance themselves from the not so good companies. Even though our business was very weak, we gained market share during this recession in quite a dramatic way. Last quarter, for the first time in our history, we became larger than all the other public programmable logic device companies combined.

From a strategic point of view, we want to win through product leadership. That means we have to have the best products – always from the customer's point of view – which means the highest densities, the fastest performance, and the software and service to support them.

When you are an industry that is new and that is still changing very rapidly, you have to continue to innovate. You have to continue to bring new products into the market.

Despite the recession, the last part of 2001 and the early part of 2002 was one of our most productive periods for new product introductions. In about five months' time, we introduced a new family in every one of our product categories – Spartan<sup>TM</sup>, CoolRunner<sup>TM</sup>, and Virtex<sup>TM</sup>. Each, in its own way, is unique in its capabilities. In fact, two of these new products – the CoolRunner-II RealDigital CPLD and the Virtex-II Pro<sup>TM</sup> Platform FPGA – have no competition. Literally, there are no comparable products on the market that can compete directly with them.

## **Total Solutions**

I'm very excited about the programmable logic industry. It's an industry that's still in the early phases, but over time, it will become the dominant way to implement integrated circuit designs.

The inherent flexibility of programmable logic allows you to gain time to market, to introduce new products very quickly, and to upgrade your product, even after the sale, through field-upgradeable technology.

We're not just focusing on the chips, however. Our chips must also have the software, the intellectual property cores, the training, and the support to deliver total solutions to our customers.

And we have to continue to be innovative in all these areas of IC technology. My whole belief is that Xilinx must excel in a continuous push to innovation – throughout the company, be it in chip design, software development, or marketing. Innovation is absolutely critical – especially in times of recession.

## No Layoffs - Not Just a Nice Thing to Do

This recession has put a tremendous strain on the industry. When I saw this decline coming, I concluded that it would be best for us if we could avoid layoffs – even though the economic consequences would be very difficult. I wanted to avoid layoffs, because once you start layoffs, people get worried – and if people are worried, they cannot innovate.

Innovation means that you have to take risks that some things are not going to work, and therefore, if you are worried about your job, the mantra becomes, "Don't rock the boat. Don't push yourself or make yourself too visible" – which is totally opposite from what we want to see happening.

If people are worried about their jobs, clearly, they're not going to be as productive. Layoffs affect not only the people who get laid off. Very often the people who are still there go through trauma, because they see their friends disappear – and they always have this fear: "Maybe next time it will be me." Whenever you lay off employees, some of the accumulated knowledge of the company - its "intellectual capital" - is going to walk out the door. Especially in the high-tech industry, the value of the company is in the heads of its engineers and support staff. At Xilinx, 70% or 80 % of our employees are highly educated people working in engineering and marketing and supply-chain management. They are all experts and specialists in their own way - and that's why it's so important to keep these people happy at Xilinx. Once people like that leave, that intellectual capital goes out the door with them, and that's a lot of value for a cutting-edge company to lose.

Several compelling studies have proved that if you go back two years later, the companies that laid off employees are generally in worse shape than companies that didn't. Layoffs have a very profound impact on the morale and the trust between management and employees. Furthermore, a lot of know-how has left the company. And it takes a long time to get it back.

For these reasons, and more, I decided to try to avoid layoffs.

## Pay Cuts – An Innovative Approach

The reality of economics is that when business drops, you have to bring your labor costs in line. With layoffs not being an option, the way we cut our labor costs was by a very innovative program where we had a tiered salary reduction that was proportional to the size of each worker's salary. The lowest paid people had no reductions, and the highest paid people had the biggest reductions (myself included).

In implementing this policy, we discovered that we should give people some choices and make sure they get something in return. People had the choice to either take the salary reduction or to take vacation time – or take stock options. Stock options aren't money, but it is compensation for the work people put in. We can't ask the employees to sacrifice unless we can compensate them for the extra flexibility we're asking from them.

The tiered salary reduction was extremely well received in the company. The vast majority – and I'm talking about close to 100% of the employees – felt this was the right thing to do.

People even volunteered for the plan, which was important in Europe, because in Europe, companies cannot mandate salary reductions. It must be done on a voluntary basis. If people hadn't volunteered, we could not have done it, but pretty much all of our European employees volunteered for the salary reduction, because they felt solidarity with the company.

With an acceptance of fair pay cuts and a promise of no layoffs, our employees felt safe to continue to risk and innovate. They have kept their attention full-time on their jobs. The net result has been that we have been able to maintain our aggressive schedule of new product rollouts – and this in a period when our business was off by 50% in three quarters.

Moreover, we were not only able to remain in the black from a profit point of view, but during all this period, we were also able to remain cash-flow positive for the company.

## The Importance of Being "Fabless"

One of the reasons we could afford to stay in the black is because Xilinx is a "fabless" semiconductor company. We don't own fabs [fabrication plants]. We don't have this big problem of having a fab that we need to keep busy. For us, if business goes down, we just buy fewer wafers.

The same thing is true for our sales force. We don't have a Xilinx sales force. We work through distribution and sales reps, which again means that our sales costs are by and large variable. Sales people get paid a commission. If they don't sell, there's no commission.

These two factors helped us tremendously in remaining in the black and remaining cash-flow positive, because a lot of our expenses go up and down with the business climate.

The good news is that we reached our lowest quarter in September of 2001.

Since then, business has been starting to improve. We were able to eliminate salary reductions early in 2002, and as of this moment, all salary reductions have been eliminated. The company continues to do very well from both a new product generation point of view, as well as a business point of view.

## Innovation - Not Just for Engineers

Innovation is not just the engineering department. Even in the way we manage the company, we are very innovative – and it really has paid off for us. Morale is very high, and the attrition rate is extremely low. People have kept their attention on their jobs of designing great new products and marketing them and supporting them.

In general, I think Xilinx is very much an admired company in our industry. I think we are perceived as a leader in our industry – not just from a product point of view or a financial point of new, but also from a management point of view.

I want to stress, however, that all of this is possible because we are a fabless company. If we had our own fabs, I don't know if we could have done this.

Nevertheless, as a fabless company, our business model lends itself very well to go though these economic cycles that are infamous in the semiconductor industry. This last recession was the worst, but it also served to prove that our business model is a very, very solid model that allows us to go through these ups and downs without too much hurt.

## Conclusion

In high technology, things change very, very rapidly. And companies often get in trouble because they don't change quickly enough. One of the reasons they don't change quickly is that the people who see the change happen don't act on it, and the people who can act on it don't even know the change is happening.

Therefore, what we are creating at Xilinx is an environment where everybody says: "Hey, if it changes, let's change with it. Let's anticipate change. Let's make the change happen ourselves. Let's be in charge of the change – not the victim of the change."

It is this kind of thinking that got us through the recession, and now that we are emerging from the recession, there is a tremendous sense of pride in the company. People are saying: "Hey, this is unique. We have done something that very few other companies have done. Even companies that didn't lay people off didn't do it the way we did."

There is absolutely no doubt in my mind that there is a much, much higher spirit of belonging, of community within the Xilinx people than there was before. When you go through a tough time together, it creates solid bonds.

And it shows that, indeed, if you can manage a company during a recession in a correct way, you can really differentiate yourself from the competition. You can gain market share and emerge a stronger company with a creative, dedicated – and intact – workforce at the end of recession.  $\Sigma$

## IBM ASICs Will Incorporate New ASICs from IBM will contain Xilinx programmable logic technology.

by Xilinx Staff

IBM and Xilinx recently signed an agreement that could help you shave hundreds of thousands of dollars off the cost of creating custom chips. Under the agreement, IBM has licensed FPGA technology from Xilinx for integration into IBM's recently announced Cu-08 application-specific integrated circuits (ASICs). Cu-08 will support circuits as small as 90 nanometers – less than 1/1,000th the width of a human hair.

This news underscores our joint commitment to a technology relationship aimed at bringing innovative and flexible new "hybrid" chips to market, combining the best attributes of standard ASIC and flexible FPGA technology for use in communications, storage, and consumer applications.

Engineers working on complex chip designs have been clamoring for ways to achieve high levels of integration, yet still have the ability to change "on the fly" late in the design cycle. By combining FPGAs (circuits that can be configured to perform a wide variety of digital electronic circuit functions) with standard ASICs, you get the flexibility of the FPGA, with the density, performance, and overall cost advantages of an ASIC – all on one chip.

"Savings here could be dramatic," said Michel Mayer, general manager, IBM Microelectronics Division. "When an ASIC takes on more function, you can reduce cost by eliminating one, two, or even more separate chips. With this technology, customers would be able to tweak designs and integrate new changes immediately, eliminating the need to restart a whole new design cycle, bringing tremendous time-to-market advantages."

Mayer said changes that force an additional chip prototype can easily cost hundreds of thousands of extra dollars and can stretch design cycles out for several additional months. "This approach is expected to change the landscape entirely," he said.

Cu-08, with as many as eight layers of copper wiring separated by an advanced low-k insulation, will support up to 72 million gates for high-complexity IC solutions. As many as 400,000 ASIC gates may be dedicated to one or more of the FPGA cores on the ASIC.

"We've improved upon our delivery of programmable hardware by allowing reconfiguration using the same chip. Flexibility is the beauty of combining ASIC and FPGA technology," said Wim Roelandts, president and CEO of Xilinx. "Our latest agreement with IBM is a natural extension of and a significant milestone in our existing relationship that allows us to address new opportunities in the high-end ASIC market."

Even after this new custom chip is built into a product, you can add to its functionality, simply, easily, and effectively. A good example would be in the communication industry, where various protocol and interface specifications are constantly evolving. Cell phones, printers, set top boxes, and other consumer electronic products also are well suited for this new approach.

IBM is the number one ASIC manufacturer worldwide. Xilinx is the number one PLD manufacturer worldwide, with more than 15 years experience in FPGA design tools.

IBM and Xilinx already have a productive business relationship. IBM supplies embedded PowerPC<sup>™</sup> processors for Xilinx Virtex-II Pro<sup>™</sup> FPGAs. In March of this year, Xilinx signed a high-volume, multi-million dollar manufacturing agreement with IBM to manufacture these FPGAs using IBM's advanced 130 nanometer and 90 nanometer copperbased chip-making technology.

The new FPGA cores for the Cu-80 ASICS are now in development. They are expected to be available from IBM, embedded in an ASIC, in early 2004, following IBM's full release of its standard-setting Cu-08 technology. **X**

**Perspective**

## When Total Cost Management Counts, Xilinx PLDs Pay Off

CoolRunner-II CPLDs, Spartan-IIE FPGAs, and Virtex-II EasyPath Platform FPGAs can give you total system cost solutions superior to those of traditional ASICs.

by Eric Thacker Manager, Product Solutions Marketing Xilinx, Inc. *eric.thacker@xilinx.com*

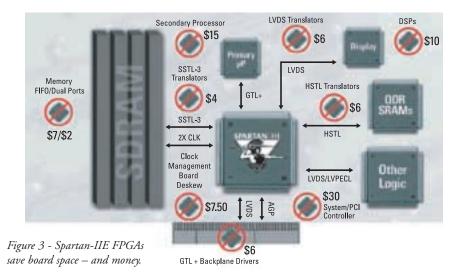

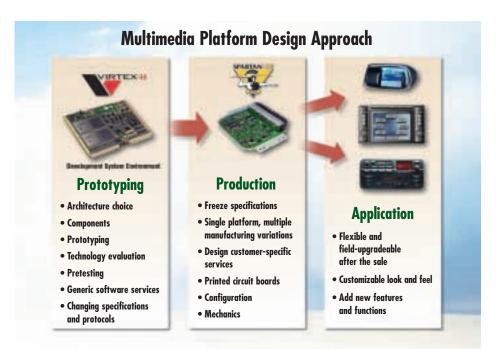

Rapidly changing markets and new technologies are subverting traditional system design paradigms. Historically, in electronic systems development, the standard design procedure was to prototype a system using programmable logic devices (PLDs), and then redesign the system using ASICs as soon as possible for cost reduction. The idea was to leverage the flexibility and development time advantage of programmable logic until the design stabilized and then to convert the design to a lower-unitcost ASIC to reduce overall system cost. In the past, programmable logic was lower density, lower performance, and more limited in capabilities. When systems followed traditional product life cycle behavior, the PLD-to-ASIC design strategy worked quite well. In fact, in some market segments, characterized by relatively mature technologies, established standards, and a stable competitive environment, this strategy is still optimal today.

In dynamic, rapidly changing markets, however, this strategy becomes questionable. For many advanced electronic products – such as plasma televisions, home networking hardware, and digital audio/video equipment – the market is anything but stable. Baseline standards for advanced products are ever-changing, features demanded by customers shift constantly, new technological capabilities are continually being introduced, and competitors are always trying to gain a better market position – resulting in many short-lived products.

These volatile market pressures give a significant competitive advantage to flexible and first-to-market products. In these markets, ASICs – with their long lead times, high initial costs, high minimum order quantities, higher risks, and inflexibility – are not a compelling solution.

Therefore, many designers are tapping into programmable logic's benefits of instant reprogrammability, short lead times, greatly improved performance, expanded densities, and overall flexibility. Indeed, today's programmable logic devices offer many of the same features found in ASICs. Clock management, embedded processors, high-performance DSP, advanced interfacing, and a plethora of intellectual property (IP) cores all make today's PLDs strong candidates for a system's core logic.

With their emphasis on cost-optimization, the CoolRunner<sup>TM</sup>-II CPLDs, Spartan<sup>TM</sup>-IIE FPGAs, and Virtex-II EasyPath<sup>TM</sup> Solutions families from Xilinx bring these advanced benefits to your high volume applications.

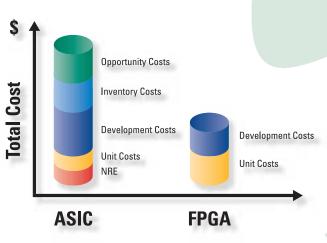

Figure 1 - Cost comparison of ASICs and FPGAs

## **Total Cost Solution**

In the past, the primary motivation in converting a PLD design to one based on an ASIC was unit cost. ASICs, in general, are available at lower unit cost than PLDs. But looking at unit costs alone could actually lead to an overall higher cost solution. That is because unit costs are only one of the factors that contribute to total system cost. Total system costs can be broken down into three broad categories – design and development, production, and life cycle.

### Design and Development

Design costs are primarily worker-hour and non-recurring engineering (NRE) costs. PLD designs require fewer worker hours, because design/debug changes can be made instantly, hardware and software can be developed concurrently, test vector generation is unnecessary, and product lead times are practically zero compared to ASICs. PLDs have no NRE costs, which can be a very important consideration as production volumes per design revision are much lower in rapidly evolving markets. In many cases, Xilinx offers free PLD design tools, thus increasing the PLD cost advantage.

There are also lost opportunity costs associated with ASICs. Systems using ASICS lose market penetration due to long development times. Furthermore, the inflexibility of ASICbased systems prevents upgrading products to meet changing market needs. Overall, PLD design cost advantages alone can often outweigh any ASIC unit cost advantage.

## Production

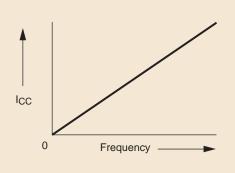

Unit cost is the most obvious cost in this category. ASICs usually do hold the unit cost advantage over PLDs, but this cost differential is shrinking.

Today's PLDs have aggressively driven down both die size and package costs to provide a persuasive ASIC alternative. The advanced system capabilities of modern PLDs allow

designers to integrate discrete component functions into the PLD – reducing board and total component costs.

Finally, unlike an inflexible ASIC, one line of PLDs can be inventoried to supply multiple applications. You can reprogram and redeploy PLDs as needed. Combined with much lower minimum order quantities, PLDs reduce inventory costs, as well as the risk of obsolescence, further offsetting PLDs' unit cost disadvantage. See Figure 1.

## Life Cycle

Life cycle costs are probably the least considered costs when designing an electronic system, but they can have a significant impact on the total return from a given design. Using PLDs instead of ASICs means practically no risk of obsolete inventory, because

standard-product PLDs can be redeployed to different applications as needed. Unlike ASICs, PLDs do not have to be scrapped if a specific product is cancelled.

In addition, because PLDs can be reprogrammed, it is possible to upgrade products in the field simply by downloading a new hardware configuration file to the PLD. Bug fixes and feature upgrades can be performed remotely without changing any hardware.

As illustrated in the discussion of these three cost categories, we must look beyond unit cost when deciding on logic solutions based on cost. In many applications, the unit cost savings of ASICs are more than offset by the lower risks, design, production, and life cycle costs of PLDs.

### **Xilinx Solutions for Total Cost Management**

Xilinx has taken the lead among PLD suppliers in providing low risk, low cost, high performance logic solutions for today's rapidly changing and highly competitive markets.

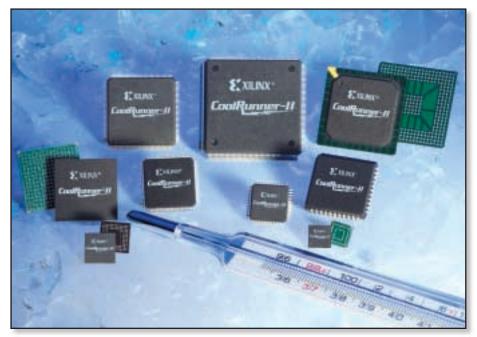

## Low Power, Low Density: CoolRunner-II CPLDs

CoolRunner-II RealDigital CPLDs combine high performance, ultra low power, low cost, and integration of specialized capabilities to bring you a new class of programmable logic devices. The versatility and low cost of CoolRunner-II CPLDs allow them to serve a multitude of logic, interface, and control functions. See Figure 2.

Figure 2 - CoolRunner-II CPLDs deliver high performance at low cost.

The 0.18-micron CoolRunner-II family utilizes second-generation Fast Zero Power<sup>™</sup> technology for low power, high performance operation. These RealDigital CPLDs feature an all-digital core that eliminates power-hungry analog sense amplifiers. The CPLDs also offer increased capabilities, higher performance, and lower cost – with no performance penalty.

Available in densities from 32 to 512 macrocells, the CoolRunner-II family provides performance over 330 MHz, with standby power consumption of less than 100  $\mu$ A. CoolRunner-II devices also deliver advanced system features that enable the integration of costly discrete system functions into a single reprogrammable device. This integration results in lower costs, further power reduction, increased reliability, faster time to market, and smaller designs. These system features include superior I/Os, advanced clocking features, and four levels of design security.

The in-system reprogrammable nature of CoolRunner-II CPLDs allows designers to change designs on the fly, correct designs, and test out alternate designs without changing any hardware. This saves significant engineering change orders (ECOs) and NRE charges compared to ASIC solutions.

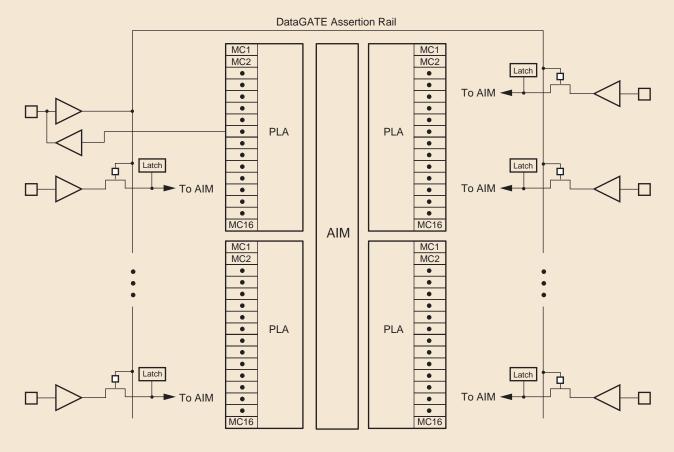

The CoolRunner-II CPLDs' advanced I/O interface capabilities include DataGATE, a programmable on/off switch for power management; advanced interfaces such as HSTL, and SSTL; and Schmitt trigger inputs for input signal conditioning. All of these features reduce the need for external components, reducing part costs and board space.

To further reduce system costs and the need for additional components, the CoolRunner-II family provides a unique feature called CoolCLOCK. CoolCLOCK is a combination of a clock doubler and clock divider. The incoming clock is divided by two and then doubled at the output to maintain the same performance, while reducing the internal power consumption.

To increase your cost management advantage, Xilinx provides a free Internetbased ISE WebPACK<sup>TM</sup> design tool suite and a free WebFITTER<sup>TM</sup> design fitting tool to give you a complete, pushbutton design solution.

The combination of advanced interfacing, integrated system features, and free design tools makes CoolRunner-II CPLDs a compelling choice for logic functions in cost-sensitive applications. For more information, visit *www.xilinx.com/coolrunner2*.

## Moderate Density, System Integration: Spartan-IIE FPGAs

Cutting-edge consumer electronics markets demand products that provide performance and flexibility in a cost-optimized format for home networking equipment, home theater systems, and other high-end personal electronic devices. These consumer products must accommodate rapidly evolving standards, shifting demand patterns, highly fluid competitive positioning, and the continuous introduction of new capabilities. Logic requirements for these designs include moderate density, advanced system features, predesigned and verified IP blocks, and highquality design tools. Spartan-IIE FPGAs meet all of these requirements and more.

Xilinx designed its next-generation Spartan-IIE consumer FPGA with total cost management in mind. Spartan-IIE FPGAs range in density from 50,000 system gates to 300,000 system gates. To reduce FPGA component costs, Spartan-IIE FPGAs are produced by the industry's most advanced foundry process on 300 mm wafers. This process lowers die cost and enables advanced, low-cost packaging.

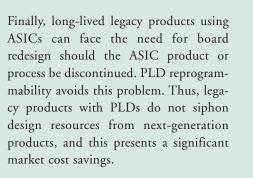

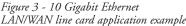

To reduce board cost and improve system performance, Spartan-IIE FPGAs have a number of built-in advanced system features that allow you to eliminate costly discrete translators and commodity chips from your boards, as shown in Figure 3.

Advanced interfacing – including LVDS, LVPECL, HSTL, and SSTL – remove the need for specialized interface components on the board. Furthermore, Spartan-IIE FPGAs offer four delay-locked loops (DLLs) for advanced clock management. Spartan-IIE FPGAs also contain both parameterizable block RAM (single or dual port) and distributed RAM (scalable and adjacent to logic). All these features can speed the design process, provide design flexibility, reduce design worker hours, deliver very high levels of performance, and accelerate time to market.

As consumer products increase their digital capabilities, digital signal processing (DSP) capability has become a critical performance factor. The Xilinx XtremeDSP<sup>TM</sup> initiative enables nearly one billion DSP multiplyand-accumulates (MACs) per second per dollar of performance in Spartan-IIE devices – delivering advanced DSP without the need for specialized board components.

Xilinx offers more than 200 Spartan-family IP cores to speed logic design and reduce engineering resources needed to complete the system. These IP cores are also optimized for die area, which may permit the use of smaller density Spartan-IIE parts, resulting in further cost savings.

Additionally, the free ISE WebPACK software provides the industry's most advanced design tool platform to support the entire Spartan series.

Die and packaging, advanced system features, extensive IP offerings, enhanced flexibility – all these Spartan-IIE cost control features give you the performance, features, and time to market advantage necessary to compete in today's rapidly evolving electronics markets. For more information, visit *www.xilinx.com/spartan*.

## High Performance, High Density: Virtex-II EasyPath FPGAs

The Virtex-II<sup>TM</sup> FPGA is the first embodiment of the Platform FPGA concept. Virtex-II devices deliver SystemIO interfaces to bridge emerging standards, XtremeDSP performance up to 100X conventional DSP solutions, multi-gigabit transceivers, and Empower! embedded processor technology. Together with the industry's most advanced design tools, Virtex-II Platform FPGAs offer a feature set that is unparalleled in the industry.

Virtex-II EasyPath FPGAs bring the unprecedented capabilities of the Virtex-II family to cost-sensitive applications by reducing the cost of high-density FPGA designs. Virtex-II EasyPath Solutions use the exact same FPGA silicon as the Virtex-II FPGA family, but Virtex-II EasyPath Solutions make use of a specialized testing program to verify the FPGAs for a specific customer application, resulting in higher yields and significantly lower costs.

Virtex-II EasyPath solutions provide an FPGA volume conversion strategy with no risk, no investment of customer engineering resources, and the fastest conversion time of any competing high-volume strategy for high-density FPGA designs. The main benefits of Virtex-II EasyPath solutions are:

• Lower unit costs: Customers can expect a 30-90% price reduction compared to standard FPGAs.

- Lower up-front costs: These costs can be as low as 30% of the NRE costs of an ASIC or gate array.

- No added engineering resources: Unlike other FPGA conversion strategies, Virtex-II EasyPath FPGAs require no additional engineering resources or tools. Customers are not required to contribute any resources for conversion, verification, qualification, or board redesign.

- No risk: Virtex-II EasyPath Solutions have none of the performance, timing, functionality, or architecture match risks of alternative FPGA conversion strategies, because the conversion FPGA fabric is the same as the standard Virtex-II FPGA.

- Minimal lead times: With Virtex-II EasyPath FPGAs, initial orders are filled within six weeks and restocking orders are filled within days of being placed. Compare that to lead times of multiple months for both initial and follow-on orders for alternative conversion strategies.

Because Virtex-II EasyPath FPGAs are tested for a specific design configuration, testing throughput and yields are significantly higher, thus driving down the unit costs of the FPGA, as shown in Figure 4. You can initially design your system using standard Virtex-II FPGAs. Once the design has stabilized, you can use Virtex-II EasyPath Solutions to convert to a lower-cost platform with none of the risk, lower NRE costs, and none of the additional engineering resources required by conversion to ASICs. For more information, visit *www.xilinx.com/virtex2*.

## Conclusion

From low density, ultra low power CoolRunner-II CPLDs to mid-range, low cost Spartan-IIE FPGAs to high density Virtex-II EasyPath Platform FPGA Solutions, Xilinx presents a portfolio of products that can play a critical role in your total cost management of system design. These advantages include:

- Cost-optimized silicon and packaging to minimize unit costs

- Advanced system features to reduce costs through system integration

- Reprogrammability to streamline design and debug

- No-cost system upgrade capabilities

- Reduced risk of obsolete inventory

- An extensive IP library to improve design efficiency and reduce system components

- Free design tools that maximize design efficiency.

Together, Xilinx CPLDs and FPGAs give you a cost-optimized solution for managing system costs while maximizing system performance, functionality, and flexibility. **X**

Figure 4 - Virtex-II EasyPath Solutions are design-specific and cost-effective.

## New Virtex-II Pro Devices — Increased Capability, Lower Cost

Now you get programmable system features at programmable logic prices. by Anil Telikepalli, Marketing Manager

Virtex Solutions, Worldwide Marketing Xilinx, Inc. anil.telikepalli@xilinx.com

In a significant move, Xilinx recently expanded the Virtex-II Pro<sup>™</sup> Platform FPGA family two ways:

- Five new devices offering increased capability

- Lower cost versions for the entire family in a new reduced-speed series.

With this, the new Virtex-II Pro family expands to ten devices, and sets industry records in every conceivable category, providing the advanced system-level features and high performance you need, at remarkably low prices.

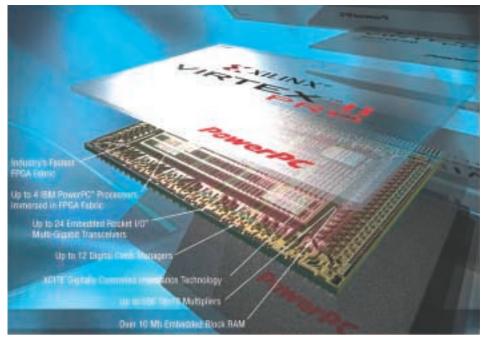

The new Virtex-II Pro FPGA solution, illustrated in Figure 1, provides everything you need, on a single, reprogrammable device, including:

- The world's highest logic and memory density

- The world's highest I/O capacity

- The world's fastest DSP capability

- The world's fastest multi-gigabit serial I/O connectivity

- The world's most flexible parallel I/O connectivity

- The world's only embedded processing FPGA solution using IBM® PowerPC<sup>TM</sup> processor cores.

Figure 1 - Virtex-II Pro Platform FPGA

Your demands, both for increased capability as well as lower cost versions of our Virtex-II Pro devices, were made clear at our Programmable World 2002 event. And now, we can deliver the performance and the pricing you need due to the success of our initial devices and development tools, as well as advances in our process technology which includes 300-mm wafers.

These new, lower cost devices not only deliver tremendous cost savings over comparable competing programmable device offerings, but they also bring Virtex-II Pro capabilities within the reach of a much wider range of applications. With the Virtex-II Pro family you now get multiple IBM PowerPC processors and multi-gigabit serial transceivers at about the same cost as our Virtex-II<sup>TM</sup> FPGAs (which don't offer these features), effectively providing programmable system features at programmable logic prices.

## The Highest Performance and the Lowest Cost

The new Virtex-II Pro XC2VP125 FPGA, shown in Table 1, is the world's highest capacity, highest performance, and highest capability programmable logic device, delivering unique system performance such as one trillion MACs/sec DSP performance and 120 Gb/s aggregate payload bandwidth. There is no programmable device in the world that competes with it in features, performance, or cost. With such unparalleled leadership advantage, the Virtex-II Pro Platform FPGAs put you on a platform of success, closer to your design goals. age, digital broadcast, networking, and wireless networking. For example, in networking, as you move from the core of the network to the edge, the line rate and processing speed of the equipment decreases while the need for intelligent processing increases. In addition, price pressure increases, because the edge equipment is more price sensitive than the core equipment. This analogy can be applied to almost any application and market segment. Xilinx is providing -5 devices specifically to address such price-sensitive applications that benefit from system features that include embedded processors and multi-gigabit transceivers.

## Virtex-II Pro FPGA Architecture Review

The Virtex-II Pro family, shipping since February of this year, is the world's first 130 nm, 9-layer copper, FPGA family and the first and only one to offer integrated IBM PowerPC microprocessor technology and 3.125 Gb/s serial transceivers. Its architecture is built upon the award-winning Virtex-II FPGA fabric, which already has thousands of satisfied users.

"THE VIRTEX BRAND HAS BEEN THE NUMBER ONE CHOICE OF DESIGNERS WORLDWIDE, BASED ON ITS INDUSTRY-LEADING CAPACITY, PERFORMANCE, CAPABILITIES, AND COST-EFFECTIVENESS. IN EACH GENERATION OF FAMILIES, OUR MISSION IS TO DELIVER SIGNIFICANTLY ENHANCED FUNCTIONALITY WHILE DRIVING DOWN PRICES. WE CONTINUE THIS STRATEGY IN THE VIRTEX-II PRO FAMILY BY INCLUDING STATE-OF-THE-ART MULTI-GIGABIT SERIAL TRANS-CEIVERS AND HIGH-PERFORMANCE POWERPC RISC CPUS, IN THE STANDARD FEATURE SET, AT NO CHARGE. THUS, WE ENABLE THE CREATION OF NEXT-GENERATION SYSTEMS DESIGNS AT PREVIOUSLY UNATTAINABLE PRICE POINTS."

ERICH GOETTING — VICE PRESIDENT AND GENERAL MANAGER OF THE XILINX ADVANCED PRODUCTS DIVISION

## Expanding the Market and Target Applications

The new -5 speed grade delivers costeffective 2Gb/s transceiver performance, with over 266 MHz embedded PowerPC processor performance. In comparison, our fastest devices (-7 speed grade) provide up to 3.125 Gb/s transceiver performance, with over 300 MHz embedded PowerPC processor performance. The -5 speed grade is therefore ideal for medium to high-speed applications including storWith 10 devices, multiple packages, and multiple speed grades to choose from, the Virtex-II Pro FPGAs give you the right features and performance to meet your specific needs. The family, as shown in Table 1, includes:

- Immersed IBM PowerPC processors (0 to 4)

- Integrated 3.125 Gb/s Rocket I/O<sup>TM</sup> transceivers (0 to 24)

- The award-winning Virtex-II FPGA fabric.

## IBM PowerPC Processors

Each immersed IBM PowerPC processor runs at up to 300+ MHz and 420+ Dhrystone MIPS providing high-performance embedded processing. The PowerPC processor is supported by the IBM CoreConnect<sup>TM</sup> bus technology. A complete set of embedded software tools are available to help you quickly develop and debug your PowerPC designs – through an OEM agreement, Xilinx provides software tools from Wind River Systems, customized for Virtex-II Pro FPGAs.

"WITH THE IMMERSION OF POWERPC CORES, XILINX HAS DEVELOPED THE OPTIMAL PLATFORM TO IMPLE-MENT OUR STORAGE NETWORK DESIGNS. VIRTEX-II PRO DEVICES PROVIDE THE CRITICAL ELEMENTS OF SYSTEM-LEVEL DESIGN, INCLUDING HIGH-SPEED SERIAL 1/O, MAKING IT AN IDEAL COMBINATION FOR OUR NEXT GENERATION PRODUCTS. MOREOVER, THE UNIQUE ARCHITECTURAL SYNTHESIS DESIGN ENVIRONMENT ALLOWS US TO MAKE HARDWARE AND SOFTWARE TRADEOFFS THROUGHOUT THE DESIGN CYCLE."

## SANDY HELTON — EXECUTIVE VP AND CTO, SAN VALLEY

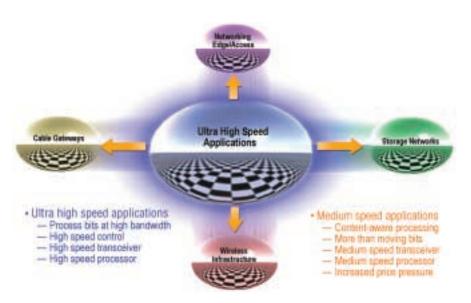

Figure 2 - Expanding the market from ultra-high speed to medium-high speed applications

## Rocket I/O Multi-gigabit Transceivers

The Rocket I/O<sup>TM</sup> multi-gigabit transceivers (MGTs) are based on the Mindspeed SkyRail<sup>TM</sup> CMOS technology. Each transceiver runs at rates ranging from 622 Mb/s to 3.125 Gb/s, and includes the entire transceiver support circuitry. Each Rocket I/O transceiver consists of both a digital Physical Coding Sublayer (PCS), as well as an analog Physical Media Attachment (PMA), to provide an integrated SerDes (serializer/deserializer) function.

## Award-winning Virtex-II Fabric

The Virtex-II FPGA fabric provides features for high-performance system design

| Device                          | XC2VP2 | XC2VP4 | XC2VP7 | XC2VP20 | XC2VP30 | XC2VP40 | XC2VP50 | XC2VP70 | XC2VP100 | XC2VP125 |

|---------------------------------|--------|--------|--------|---------|---------|---------|---------|---------|----------|----------|

| Logic Cells                     | 3,168  | 6,768  | 11,088 | 20,880  | 30,816  | 43,632  | 53,136  | 74,448  | 99,216   | 125,136  |

| Block RAM (Kbits)               | 216    | 504    | 792    | 1,584   | 2,448   | 3,456   | 4,176   | 5,904   | 7,992    | 10,008   |

| 18x18 Multipliers               | 12     | 28     | 44     | 88      | 136     | 192     | 232     | 328     | 444      | 556      |

| Digital Clock Management Blocks | 4      | 4      | 4      | 8       | 8       | 8       | 8       | 8       | 12       | 12       |

| Configuration Memory (Mbits)    | 1.31   | 3.01   | 4.49   | 8.21    | 11.36   | 15.56   | 19.02   | 25.6    | 33.65    | 42.78    |

| IBM PowerPC Processors          | 0      | 1      | 1      | 2       | 2       | 2       | 2       | 2       | 2        | 4        |

| Multi-Gigabit Transceivers      | 4      | 4      | 8      | 8       | 8       | 12*     | 16*     | 20      | 20*      | 24*      |

| Max Available User I/O          | 204    | 348    | 396    | 564     | 692     | 804     | 852     | 996     | 1164     | 1200     |

| Package                         |        |        |        |         |         |         |         |         |          |          |

| FG256                           | 140    | 140    |        |         |         |         |         |         |          |          |

| FG456                           | 156    | 248    | 248    |         |         |         |         |         |          |          |

| FF672                           | 204    | 348    | 396    |         |         |         |         |         |          |          |

| FF896                           |        |        | 396    | 556     | 556     |         |         |         |          |          |

| FF1152                          |        |        |        | 564     | 692     | 692     | 692     |         |          |          |

| FF1148*                         |        |        |        |         |         | 804     | 812     |         |          |          |

| FF1517                          |        |        |        |         |         | 804     | 852     | 964     |          |          |

| FF1704                          |        |        |        |         |         |         |         | 996     | 1040     | 1040     |

| FF1696*                         |        |        |        |         |         |         |         |         | 1164     | 1200     |

Table 1- Virtex-II Pro Platform FPGAs Power of Choice (new -5 devices shown in red)

\*Note: FF1148 and FF1696 packages support higher user I/O and zero Rocket I/O multi-gigabit transceivers that has made it a platform of choice for users. These features include:

- High-performance logic with a wide choice of densities

- Embedded block RAM

- XtremeDSP embedded hardware multiply circuitry

- Advanced digital clock management circuitry

- XCITE technology for digitally controlled impedance matching on I/Os

- Bitstream encryption technology for design protection

- Flexible Select I/O<sup>TM</sup>-Ultra technology for supporting over 20 single-ended and differential I/O signaling standards.

## Conclusion

The expanded Virtex-II Pro family provides a broad choice of 10 devices in scalable features and speed grades. It marks leadership in every facet, providing more capability than any other competing programmable logic device. In addition, the new pricing delivers programmable system features at programmable logic prices, making embedded PowerPC processors and multi-gigabit transceivers standard features in high-performance programmable devices. For more information on Virtex-II Pro Platform FPGAs and design resources, go to *www.xilinx.com/virtex2pro.* **X**

# How to Use Virtex-II FPGAs to Deliver Gigabit Advanced Data Security with Helion Encryption Cores

Virtex-II Platform FPGAs enabled Helion Technology Ltd. not only to deliver on time but to exceed the client's requirements.

by Simon Cocking Design Consultant Helion Technology Limited simon@heliontech.com

As secure communication data rates increase, software implementations of the key data encryption algorithms present a major system bottleneck. To make matters worse, standard off-the-shelf CPUs and DSPs have failed to keep pace with the computational demands of data encryption algorithms. Besides, CPUs and DSPs just have too many other tasks to perform.

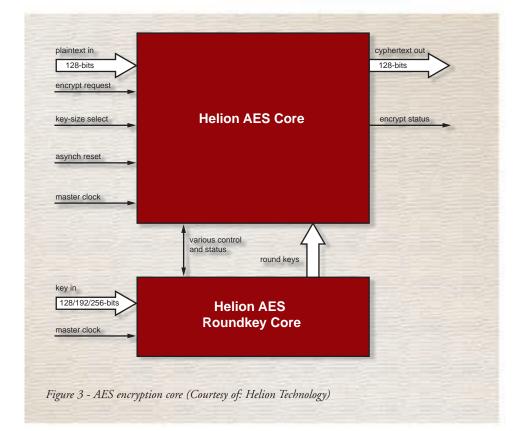

The magnitude of the software performance gap for high-speed data encryption is illustrated by the benchmark results shown in Table 1. These figures are for implementations of the new 128-bit Advanced Encryption Standard (AES) algorithm running on standard CPU and DSP architectures – as compared to how a Virtex<sup>TM</sup>-II Platform FPGA solution based on a Fast AES core from Helion Technology Ltd. can provide the multi-gigabit encryption data throughput required by high-speed interconnect technologies.

## The Design Brief

Last year, we at Helion were asked by one of our clients to provide a flexible, high performance FPGA-based data security engine to handle encryption of Internet Protocol (IP) packet-based data for their next-generation network security products. Even though their product was based on a high-performance dual 64-bit MIPS network processor, benchmarking had shown a software encryption solution to be somewhat short of achieving the minimum 600 Mbps throughput our client required.

The system requirement was for a PCIbased engine that could accommodate multiple encryption algorithms: AES and a proprietary algorithm for legacy purposes. The solution had to be low cost, capable of supporting gigabit data rates, and flexible enough to allow for future algorithm changes.

After evaluating the available options, the only solution that met all of the requirements was a PCI card containing the one million-gate Virtex-II XC2V1000 Platform FPGA. The device incorporated a Xilinx LogiCORE<sup>TM</sup> 32-bit/66-MHz PCI core and Helion-designed encryption cores.

## Why Use a Virtex-II FPGA?

From our many years of design experience with leading edge technology, we were well aware of the potential pitfalls, such as inadequate design tool support and unavailable parts. Fortunately, Virtex-II Platform FPGAs use the same EDA toolset as earlier technologies, and the XC2V1000 device was already in production. The reasons for choosing the XC2V1000 instead of the more established Virtex-E family were compelling:

- Costs The Virtex-II XC2V1000 cost less than half the nearest equivalent Virtex-E(-8) device.

- Performance Benchmarking with the Helion AES core showed the Virtex-II(-4) FPGA to be 30% faster than the nearest equivalent Virtex-E(-8) device.

- Bigger and wider block RAM We found 32-bit wide data buffers were more efficiently implemented in Virtex-II block RAM. For example, a 512x32 buffer required only a single Virtex-II block RAM rather than four in Virtex-E technology.

- Enhanced CLBs The MUXF7 and MUXF8 primitives allowed up to four slices to be combined for fast implementations of any logic function up to eight inputs wide. This led to fewer logic levels and faster critical paths for the very wide logic functions typical of encryption algorithms.

- Digital Clock Manager (DCM) True clock frequency synthesis allowed the encryption data clock to be tuned to closely match worst-case PAR (placeand-route) timing, optimizing encryption throughput.

- Easier Design Implementation The raw speed of Virtex-II devices meant no PAR guide file was required for the LogiCORE 66-MHz PCI bus logic.

## **Encryption Engine Overview**

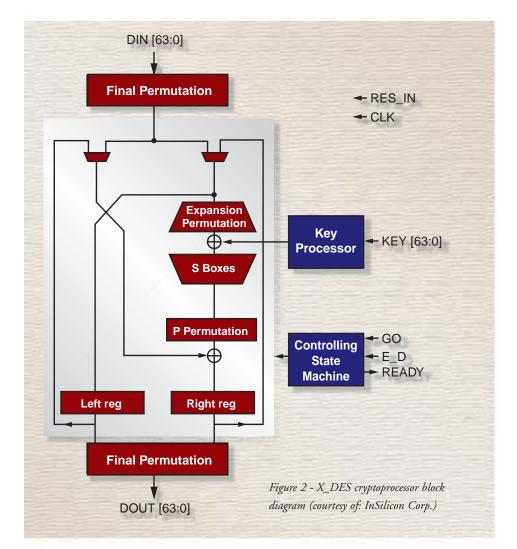

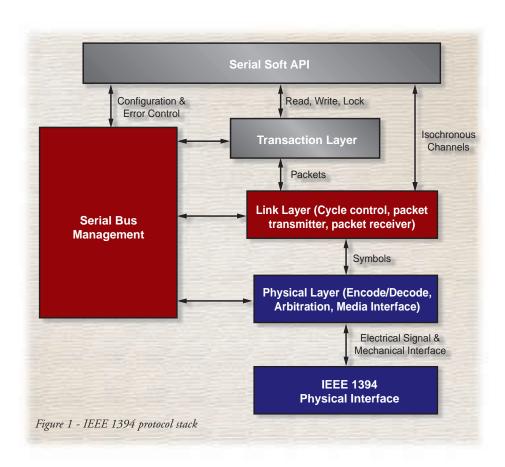

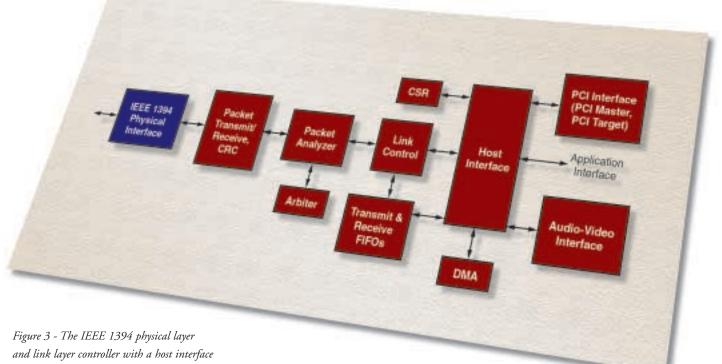

A block diagram of the encryption engine is shown in Figure 1. The only external interface is the LogiCORE 32-bit/66-MHz PCI bus.

All encryption key information and data to be encrypted (plaintext) are stored in PCI system memory and transferred into the FPGA by the direct memory access (DMA) controller. This configuration allows the encryption keys to be easily changed by software – an important security feature.

The DMA read-and-write buffers use block RAM to support the long PCI burst read-and-write transfers needed to achieve optimum performance. Checksum calculation and buffering is also provided for the encrypted data (ciphertext) to off-load this task from the system software, which reads the checksum(s) at the end of each DMA transfer.

The main data path between the DMA buffers is through the encryption cores. The Helion 128-bit fast AES encryption core had already been developed, so it was simply a case of dropping it into the design. However, it was still necessary to develop a high-performance core for the proprietary algorithm.

## **Encryption Engine Operation**

While the encryption engine is inactive (no DMA encrypt transfer in progress), the PCI interface defaults to "target" mode and waits for the system CPU to initiate a DMA transfer. Once a DMA operation is requested, the PCI interface is switched to "master" mode, and the DMA controller initiates the required bus transfers.

Upon completion, the encryption engine asserts the PCI interrupt request and returns the interface to "target" mode so that the system CPU can read the checksums and/or start the next transfer.

| Solution                              | Clock (MHz) | Encryption Data Rate | Comments                                                            |  |  |  |

|---------------------------------------|-------------|----------------------|---------------------------------------------------------------------|--|--|--|

| TMS320C62XX 32-bit<br>fixed-point DSP | 200         | 112 Mbps             |                                                                     |  |  |  |

| MIPS-based 64-bit<br>RISC processor   | 250         | 392 Mbps             | Assumes fully primed cache and<br>CPU fully dedicated to encryption |  |  |  |

| Pentium III                           | 1,000       | 464 Mbps             | Assumes fully primed cache and<br>CPU fully dedicated to encryption |  |  |  |

| Helion Fast AES Core                  | 132         | 1536 Mbps            | Virtex-II XC2V1000-4 target                                         |  |  |  |

Table 1 - Typical achievable data rates for 128-bit Advanced Encryption Standard solutions

Because the plaintext data stream written into PCI system memory can be fragmented into multiple IP packets, the system software is responsible for creating a control data structure that details the size, location, and number of fragments, as well as the encryption type to use. This structure is transferred from memory into a block RAM in the DMA controller at the start of each encrypt transfer.

The encryption engine can then read in all plaintext fragments, encrypt them using the selected algorithm, and reassemble the ciphertext fragments in memory. In the process of writing ciphertext back to memory, a checksum is calculated for each encrypted fragment, and this value is added to a total checksum of all fragments. These checksums are stored in a small distributed RAM in the FPGA, and then read back by the system CPU at the end of each transfer.

## **Encryption Engine Performance**

Our client was delighted to learn that not only was the final encryption engine design delivered on time, but that it also exceeded the required data throughput for both encryption algorithms by a significant margin.

The proprietary algorithm core is clocked at 66 MHz to achieve a raw encryption throughput of 990 Mbps. The AES core is clocked at 132 MHz to yield a raw encryption throughput of 1.536 Gbps.

However, these raw throughput figures are degraded somewhat in the final system due to bus arbitration overhead in the PCI bridge. In fact, the data throughput of the Helion fast AES core is so high that the maximum available bandwidth on the 32bit/66-MHz PCI bus acts as a ceiling on its performance. Frequent changing of the encryption keys will also lead to a reduction in overall data encryption throughput due to the increased transfer load on the PCI bus.

## Conclusion

The encryption engine project we've described is a great example of how a combination of third-party intellectual property cores and Virtex-II Platform FPGA technology can yield flexible, high-performance security products in record time.

A large reduction in the effort required to implement such a design relies on the ready availability of intellectual property like the Xilinx LogiCORE PCI products and the range of advanced encryption cores we have developed at Helion. Design blocks like these enable a single engineer to attack a million-gate design and achieve results in a matter of weeks. Future plans for our encryption engine include the use of a higher bandwidth bus interface, such as HyperTransport<sup>TM</sup> technology in place of PCI. We also plan the addition of multiple AES cores to provide a full-duplex (encrypt and decrypt), higher performance solution.

The Helion encryption cores allow for even higher throughput: Eight similar Fast AES cores in a larger Virtex-II Platform FPGA could provide encryption at rates in excess of 12 Gbps. This is fast enough to support emerging high-speed interconnect standards, such as OC-192, 10 Gigabit Ethernet, POS-PHY L4, and RapidIO<sup>TM</sup> Phy.

For more detailed information on Helion and our products and services, please visit the Helion website at *www.heliontech.com.*  $\Sigma$

CPLD

## CooRunner-II CPLDs Go All Digital

Xilinx CoolRunner-II RealDigital CPLDs consume less power and offer reprogrammable flexibility with unprecedented design security — without a price premium.

by Steve Prokosch CPLD Product Marketing Xilinx, Inc. steve.prokosch@xilinx.com

When Xilinx asked design engineers what they expected from the new generation of complex programmable logic devices (CPLDs), their responses showed they pretty much wanted it all:

- Advantages derived from state-of-the-art fabrication processes

- More industry standard I/O features

- System security

- Lower power operation

- Higher performance.

Designers required the next generation of CPLDs to increase performance of battery-powered devices. And, they stipulated that the next generation of CPLDs must improve performance without power penalties – and with the features and functions that would meet the expectations of today's discriminating designers and cost-conscious consumers.

In response to the high expectations of top design engineers, Xilinx has created the CoolRunner<sup>TM</sup>-II RealDigital CPLD. The CoolRunner-II CPLD architecture introduces, for the first time, the advantage of both high performance and low power operation. The CoolRunner-II RealDigital CPLD reprogrammable logic solution just may be the defining element of a new era of CPLD-based applications – small form factor, high performance, power sensitive products that are feature rich and protected by multiple levels of security.

## **CoolRunner-II RealDigital CPLDs**

Evolutions of the XPLA (extended programmable logic array) CPLD architecture have led to this ultra low power, ultra high speed, reprogrammable CMOS logic that offers significant improvements over earlier generations. (See sidebar "The Evolution of Low-Power CPLDs.") These capabilities are aiding in dramatic device size reductions and performance increases that are enhancing the look and feel of both handheld and high performance products.

The CoolRunner-II RealDigital CPLD delivers on several design fronts: low power, high performance, design flexibility, and security. Today, designers can choose high performance devices that do not require extra power for speed.

## Process Technology

The CoolRunner-II family of CPLDs has benefited from the leading edge of Xilinx FPGA (field programmable gate array) process technology. The original CoolRunner CPLD architecture began on a 0.5-micron process and then migrated to 0.35 micron.

Today, the CoolRunner-II CPLD family is manufactured using a 0.18-micron process technology – the same as the high-end Xilinx Virtex<sup>TM</sup>-II FPGAs. With this ultra high density process technology, and scalable CMOS architecture, it is now possible to lower power consumption even further than before.

## Multiple I/O Features

To facilitate its use in multiple system architectures, various input/output (I/O) standards have been incorporated in the CoolRunner-II interface. These include:

- LVTTL

- LVCMOS 33, 25, 18

- SSTL2-1, SSTL3-1

- HSTL-1

- 1.5V I/O.

High-speed transceiver logic (HSTL) I/O standards are common in high-speed memory interfaces. Stub-series terminated logic

Figure 1 - Xilinx CoolRunner-II CPLD product family

(SSTL) is associated with circuit designs where buses must be isolated from relatively large stubs. With these added I/O standards, CoolRunner-II CPLDs can easily adapt to a variety of interfaces that other low power processors might not be able to handle. This makes CoolRunner-II CPLDs a great system integration solution for microprocessor-based applications.

## 100% Digital Core

CoolRunner-II RealDigital CPLDs do not use traditional sense amplifier technology – and that means the historical tradeoff between speed and power has been eliminated. RealDigital technology has enabled Xilinx to offer the industry's lowest power consumption and highest performance on a single device with no price premium.

## Low Power Enhancements

Learning that designers of portable products wanted even lower power than CoolRunner XPLA3 CPLDs, Xilinx added architectural features to accommodate tight power budgets. Even with FZP (Fast Zero Power<sup>TM</sup>) technology and voltage reduction, we still had to add two new architectural features to lower overall power consumption in designs for power sensitive applications. Those features are DataGATE and CoolCLOCK. DataGATE makes it possible to reduce power consumption by reducing unnecessary toggling of inputs when they are not in use. A prime example of this would be a bus interface. These input signals would become active only when information is passed to the CPLD. This eliminates the unnecessary switching from high to low/low to high. As bus interfaces grow, so will the power demand from needless switching of input signals.

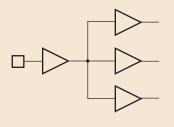

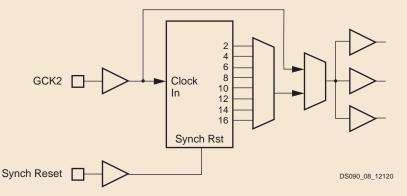

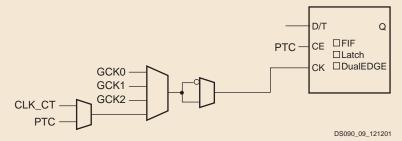

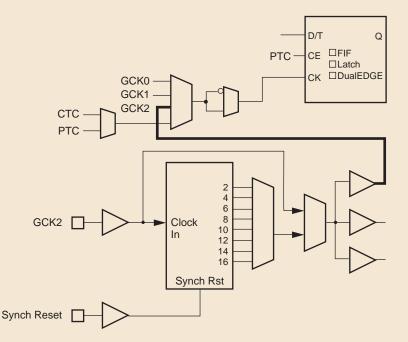

CoolCLOCK, another CoolRunner-II low power enhancement, is implemented by dividing, then doubling, a clock signal. Using Global Clock 2 (GCK2) clock input and dividing by 2, then doubling the clock at the macrocell, performance can be maintained while lowering power consumption. The CoolCLOCK method is easily synthesized and is available on 128 macrocell and larger devices.

## Schmitt Trigger

When communicating with CPLD design engineers, we discovered they were looking for an easy method to interface to noisy analog components. Thus, CoolRunner-II CPLDs incorporate Schmitt trigger inputs, which are helpful by delaying the switching time on slow rising or falling signals. Schmitt trigger inputs also help eliminate false switching due to noise spikes. The possibility also exists to form a simple oscillator circuit from these inputs. You must exercise care to assure reliability, but it can save component costs on simple circuit designs.

## Security

The loss of intellectual property is always a concern for electronic equipment manufacturers. With CoolRunner-II RealDigital CPLDs, security was enhanced to eliminate the possibility of code theft. The security bits are scattered and affect different modes of operation. If any tampering of the security chain is detected, the device automatically locks down and is erased. Even if the device is de-capped, buried interconnects make it almost impossible to trace security connections without destroying the device. Security details cannot be discussed even under non-disclosure agreements, thus ensuring ultimate protection.

## User-Defined Grounds

As voltage levels decrease, noise and ground bounce become larger factors in signal integrity. Now, a few hundred millivolts is the difference between on and off, versus a few volts in legacy devices. We had to take extra care in design and layout to shorten signal paths and minimize potential interference.

Differential signaling (SSTL and HSTL) serves as a good method to reduce noise and increase signal integrity – with the provision that extra pins are available for differential I/O and reference voltage sources.

To simplify the elimination of noise and ground bounce, CoolRunner-II CPLDs also employ software-definable ground pins. These programmable ground pins are an ideal way to reduce noise and ground bounce effects. By using neighboring I/Os as ground pins, CoolRunner-II devices can tolerate a larger amount of potential signal noise.

### Voltage Translator Clearinghouse

Due to the availability of various specialty electronic devices, it may be necessary to interface with multiple component voltage levels. With CoolRunner-II RealDigital CPLDs, I/O banking is an easy way to eliminate voltage level translators. "Banking" is the ability to separate function blocks within the CPLD so that these blocks can operate independently at different voltage levels.

For instance, one function block could be I/O compatible with 3.3V devices, and another function block could interface with 1.8V devices. This saves board space and eases voltage level design issues.

### Conclusion

From process technology to a 100% digital core to added power reduction features,

CoolRunner-II RealDigital devices mark the beginning of a new era for CPLD applications. Many system design concerns – including speed, power, I/O interfaces, clock management, and security – have been consolidated into one reprogrammable logic solution: CoolRunner-II RealDigital CPLDS from Xilinx.

For more information, please visit www. xilinx.com > Products > CPLDs > Introducing CoolRunner-II RealDigital CPLDs, or www.xilinx.com/xlnx/xil\_prodcat\_product.jsp? title=coolrunner2\_page. **X**

## A Short History of Low Power CPLDs

The first reprogrammable logic devices have their roots in bipolar PROM (programmable read-only memory) technology, with added logic capacity and features. The first company to generate customer interest was Signetics, with their introduction of the 82S100 FPLA (field programmable logic array).

Monolithic Memories Inc. attempted to be a second source supplier to the 82S100, but failed due to a process technology mismatch. They instead developed the now famous PAL (programmable array logic). This development by MMI led to aggressive process technology shrinks and increased speeds as logic designers pushed for faster state machine operation.

Philips Semiconductors purchased Signetics, and in 1977, acquired a second source license for the PAL from MMI. Philips continued to work on different architectural enhancements and migrated to a BiCMOS (bipolar CMOS) process. When the first 22V10 PAL from AMD hit the market, it was a greater success than anyone anticipated. From this beginning, devices matured into what are now known as CPLDs. Xilinx entered the CPLD market in the early 1990s by acquiring Plus Logic and introduced the 7200 family of CPLDs.

CMOS CPLD products use power for speed improvements by partially turning on (biasing) transistors and by using sense amp technology. In the past, this was an easy way to promote devices and claim a speed advantage. The by-product, however, was heat.

In 1994, Philips Semiconductors made the move to CMOS CPLDs. With this decision, CPLDs broke away from their BiCMOS PROM roots and entered into the scalable process technology arena. These products reflected innovative approaches in circuit design with an awareness of power consumption by removing the old bipolar style sense amplifier from the circuitry.

Xilinx purchased the CoolRunner line of CPLDs from Philips Semiconductors in 1999 to penetrate the low power CPLD market segment. Today, ultra high density CMOS processes (0.18 micron) make possible reduced size and lower power consumption, which directly reduces heat dissipation.

Consumers' demands for smaller, faster, cheaper, better products are the driving forces in today's competitive markets – and the state-of-the-art CoolRunner-II RealDigital CPLDs meet these demands.

## If Disaster Strikes, Xilinx Is Prepared

War, natural disasters, terrorism, economic ruin, and other catastrophes can't be prevented, but their effects can be attenuated. Xilinx has in place a Business Continuity Program designed to minimize the impact on your business.

## Business Continuity

by Alicia Tripp Manager, Business Continuity Program Xilinx, Inc. alicia.tripp@xilinx.com

Our customers depend on us – and you expect us to provide reliable product and consistent service, even in the event of a disaster or interruption to our business. For these reasons and for the benefit of our stakeholders, we incorporated the Business Continuity Program (BCP) into the Xilinx culture in June 2000. The BCP is a corporation-wide initiative that is supported by our Board of Directors and throughout our employee population.

We began the program by conducting a business impact analysis (BIA) and a threat and risk assessment (TRA) to determine the critical business processes within the company. In addition, the BIA and TRA provided an understanding of the impact of the loss of one or more of the critical functions. Once the analyses were completed, more than 80 departmental recovery plans were developed. The recovery plans are the road maps that will allow us to continue providing products and services to our customers during a major disruption. Incident management teams (IMTs) are one of the most vital parts of the Business Continuity Program. We have located IMTs strategically throughout the Xilinx enterprise. Each team consists of members of functional business units within the company such as Human Resources, Legal, Purchasing, Security, Facilities, Risk Management, Accounting, and Safety. The IMTs are responsible for handling the event, from the time of a disaster through recovery and restoration activities. The purpose of the IMTs is to protect the health and safety of our employees, to guide the company through a crisis, and to provide a structured organization for overseeing the response. These teams will convene during a major business interruption to assess the situation and determine if a disaster should be declared and whether or not to launch departmental recovery plans.

Incident management teams convened four times in less than 48 hours after the September 11, 2001, terrorist attacks to make plans to assist our employees. We were able to have counselors on site, and travel representatives helped employees traveling on business to schedule return flights home.

The Business Continuity Program has been successfully integrated into our business culture – in large part, because of the toplevel support from executive management. From the very beginning, our executive staff has been onboard to make sure the program goals and objectives are achieved.

The BCP includes an executive awareness and ongoing plan development that helps our executive officers to continue to be involved and ready to respond. This executive awareness plan will allow Xilinx to prop-

> erly manage any incident from the time a disaster is declared through recovery and restoration activities.

Recovery plans and IMTs are exercised on a regular basis. By developing and actively maintaining the Business Continuity Program, we

are prepared to limit the effect a long-term business interruption might have on Xilinx – and to mitigate the impact on our customers.

Please contact your local sales representative for additional information.  $\Sigma$

## Even as Designs Grow More Complex, Xilinx Software Improves Your Productivity

Xilinx Integrated Software Environment (ISE) design tools promise to manage design complexity and, at the same time, ensure your logic design flow is easy to use.

by Lee Hansen Product Marketing Manager Xilinx, Inc. Iee.hansen@xilinx.com

Your Xilinx programmable logic device offers you more capabilities than ever before, and coming releases of the ISE design tools will help you to handle the pressure that comes from using these complex new features. Come along for a glimpse into the future of ISE.

## **ISE Delivers a Wealth of Device Features**

The most compelling pressure on the logic design flow comes from the added complexity of new capabilities and tool features. Embedded systems, increased clock speeds, verification of high-density designs, new device capabilities, high-speed I/O, a variety of IP (intellectual property) sources, and design reuse – all of these logic trends force more requirements into the design flow.

In 2001, the Virtex<sup>™</sup>-II FPGA introduced a revolution in clock capabilities with Digital Clock Manager (DCM), and this year, the Virtex-II Pro<sup>™</sup> Platform FPGA broke new ground by delivering 3.125-gigabit serial I/O transceivers and embedded IBM PowerPC<sup>™</sup> microprocessors. As the demand for more device features continues to grow, engineers must learn all the programming attributes for these new features – and the learning curve escalates with the introduction of each new device feature.

To ease the learning curve, Xilinx ISE 5.1i will offer designers even more interactive architecture and design assistance. In addition to quick and easy dialogs, wizards will automatically step you through configuring advanced device features and inserting those configurations directly into your HDL source code. Upcoming releases of ISE will soften your learning curve, helping to speed design completion.

## **ISE Enables IP Capture and Design Reuse**

As design sizes grow, source management and methods to improve source code productivity must keep pace. In a multi-million-gate design, source code can come from multiple resources, including purchased IP, developed code, and "design reuse" – modules of HDL developed and proved in a prior design.

In upcoming releases of ISE, it will be possible to capture proven IP modules at the floorplan level. This captured IP will not be just a module of code, but it will also have attached relative placement and floorplanning area information that will help speed implementation in later uses.

As time-to-market pressures increase, design change impacts late in the design cycle will become an even larger design challenge. Enhancements to ISE will confine late-cycle design changes to only that portion of the design that is required to change. The remainder of the design will be left intact, thus speeding overall design completion. This technology is enabled by new floorplanning capabilities along HDL hierarchy boundaries that make it easier to define areas of logic.

## High-Speed Design Will Push Innovation

High-speed design pressures will continue to push more innovation into logic design and into the board design flow.

Timing analysis and timing constraints have – until now – lived under two different analysis domains, separated at the FPGA pin. The logic designer has looked to the specification and timing requirements to define design closure, while the board designer has picked up the signal at the logic pin and attempted to lay out and analyze the effects that the PCB trace will have on that signal.

Now, however, the line between logic designer and board designer functions will begin to blur as timing constraint languages become more uniform across the logic tools and among the logic-level and board-level tools. Trace analysis packages also will increasingly use more complex pin models provided by the logic tools, but these complex analyses will also become much faster, dumping slower general analog simulation in favor of specialized transmission line trace simulations.

## A Higher Level of Abstraction Is Coming

While high-level languages (HLLs) have been explored in logic and systems design, the pain of existing logic design methodologies hasn't been great enough to force a high-level language or associated methodology into common use.

Verilog and VHDL have served the logic design space well for the last two decades,