-SPECIAL SECTION: DESIGNING FOR PC SYSTEMS

# THS IS A BIGTINE GAL.

Time is finally on your side. Our new **GAL2ORA10-15**, with ten individually programmable clocks and a 15ns propagation delay, offers the world's fastest performance. A combination that delivers the ultimate in design flexibility and speed, all in a 24-pin E<sup>2</sup>CMOS<sup>®</sup> GAL device.

For example, design engineers can independently clock, reset and preset each of ten output logic macrocells. These individually programmable clocks enable asynchronous designs, taking your system performance to even higher levels.

If your design is ready for the big time, call **1-800-FASTGAL**, and ask for dept. 203. We'll send you free samples and a databook describing our entire line of high speed E<sup>2</sup>CMOS GAL devices. Fast.

5555 Northeast Moore Court • Hillsboro, Oregon 97124

Leader in E<sup>2</sup>CMOS PLDs."

Copyright © 1990, Lattice Semiconductor Corporation. GAL and E<sup>2</sup>CMOS are registered trademarks of Lattice Semiconductor Corporation. CIRCLE 151 FOR LITERATURE

# We've put CMOS on display.

If you're looking for the right LED display solution, take a look at HP. We've got a full line of low-power, easy-to-use alphanumeric CMOS displays.

All featuring an integrated on-board CMOS IC. And all designed to provide you with a better way to meet your display requirements.

Take our eight-character 5 x 7 smart alphanumeric display, for example. It's the industry's only customizable display. With up to 16 user-definable characters and the capability to generate foreign characters, special symbols and logos.

Or choose from four-character 5 x 7 CMOS displays in all four LED colors.

Smart 16-segment displays with built-in RAM, ASCII decoder and LED drive circuitry. Which also come in a drop-in 5 x 7 dot-matrix upgrade.

And single-character red hexadecimal displays with a 4 x 7 dot-matrix display. Best of all, they're from HP. So you're always assured of HP's commitment to excellence in service, support and reliability.

For a free brochure describing our full line of CMOS display solutions, call **1-800-752-0900 ext. 233H.** And see how easy it is to shine.

There is a better way.

CG08902

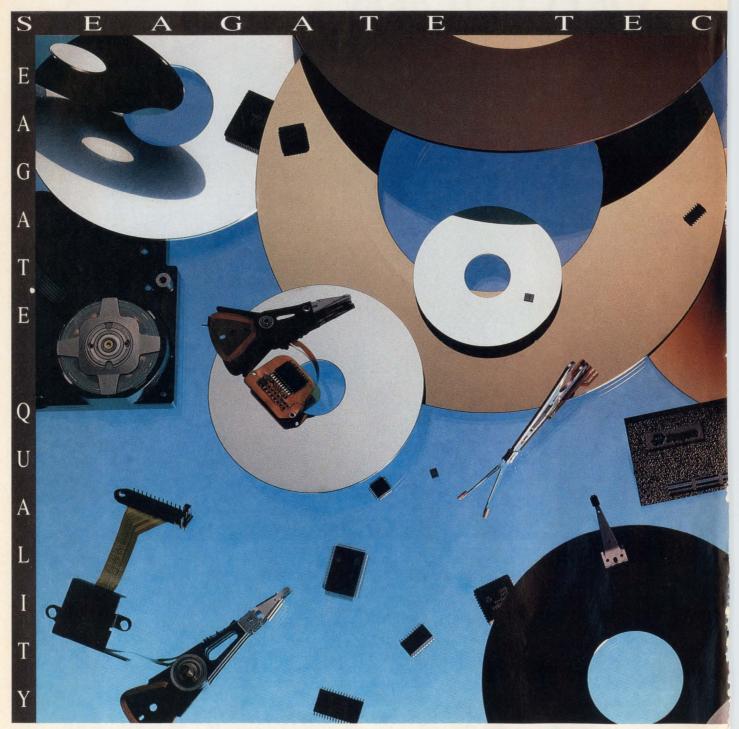

# Extraordinary disc drives require extraordinary parts.

Seagate and the Seagate logo are registered trademarks of Seagate Technology, Inc. © 1991, Seagate Technology, Inc. Today's disc drives are smaller in size and larger in capacity than ever before due to advances in component technology. By

designing and manufacturing most of the components ourselves — a concept called vertical integration — we can control the technology, cost, availability and quality of these critical parts.

Technically speaking, no one builds more advanced thin-film discs and recording heads than Seagate. These core technologies help us put 3 gigabytes of storage in a box the size of a toaster. And because we design our own components, we can bring our new products to market faster.

Of course, a key consideration in building our own parts is the cost. By controlling

> the manufacturing process down to the component level, we can have a significant impact on the cost of our finished products. The

end-result is a better value for the customer without sacrificing quality or performance.

In terms of availability, it's important to know that Seagate shipped over 7 million disc drives last year alone. With volumes like these, building our own components helps us avoid the parts shortages that often plague other disc drive manufacturers.

Most importantly, vertical integration allows us to maximize the quality of every component we produce. With the industry's most advanced equipment and testing techniques, we consistently turn out components and finished products that are beyond reproach.

Obviously, it takes an extraordinary capital investment to pursue this strategy. But the disc drive companies who control their critical component production will be better able to control their own destinies, as well as those of their customers.

For more information on our complete line of high-performance disc storage products, contact your authorized Seagate distributor. Or call Seagate at 800-468-DISC, or 408-438-6550.

Seagate Seagate

The first name in disc drives CIRCLE 146 MARCH 14, 1991 VOL. 39, NO. 5

### ELECTRONIC DESIGN

| - Alterna                   |                                                                                                                                                                                                |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             |                                                                                                                                                                                                |

| N                           |                                                                                                                                                                                                |

|                             |                                                                                                                                                                                                |

|                             |                                                                                                                                                                                                |

| X                           |                                                                                                                                                                                                |

|                             |                                                                                                                                                                                                |

| - Miles                     |                                                                                                                                                                                                |

|                             |                                                                                                                                                                                                |

|                             |                                                                                                                                                                                                |

|                             |                                                                                                                                                                                                |

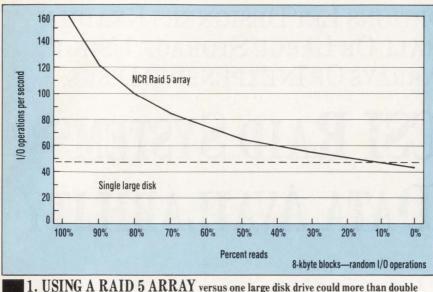

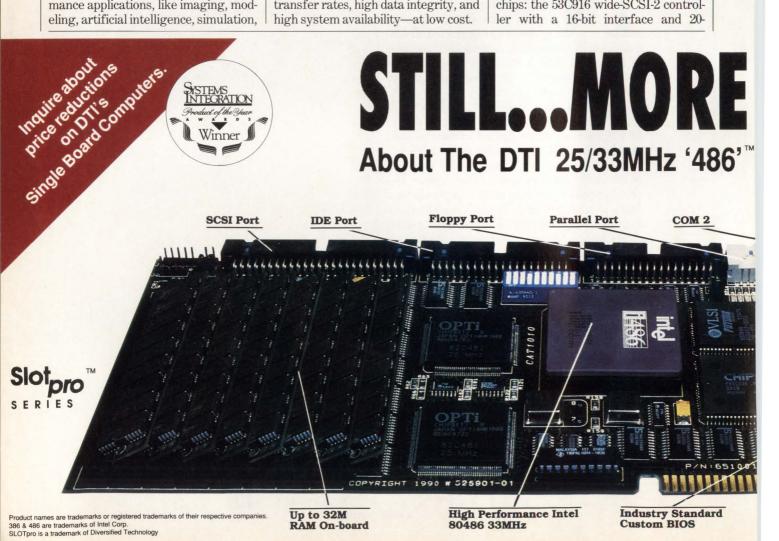

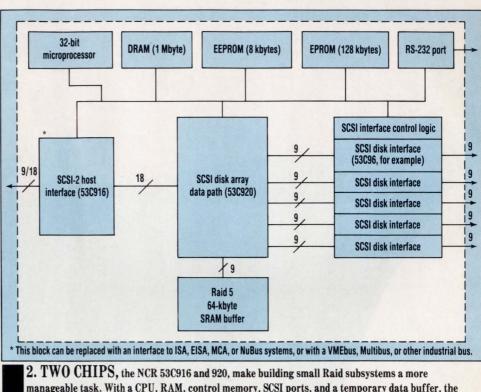

| COVER<br>FEATURE            | <b>35 BUILD SCSI RAID SYSTEMS TO BOOST DATA AVAILABILITY</b><br>Two chip-set options let designers readily implement small or large storage<br>using redundant arrays of inexpensive disks.    |

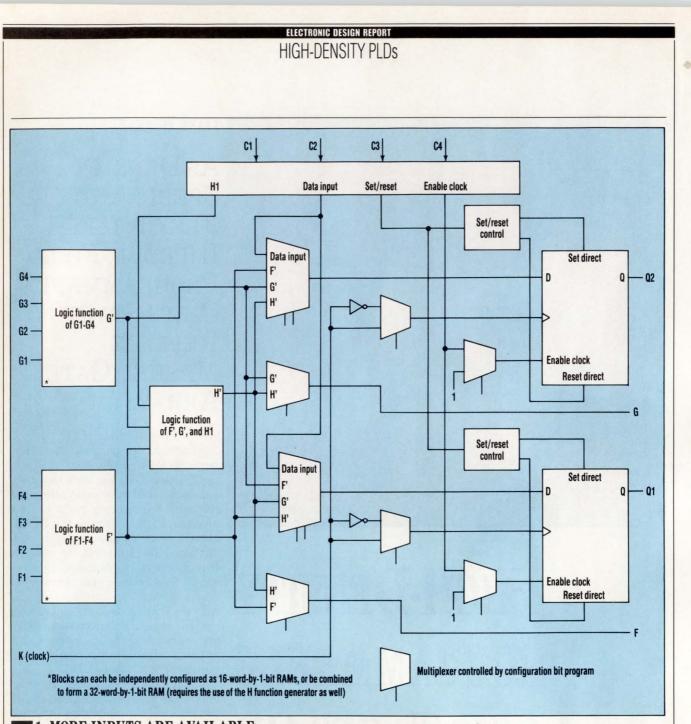

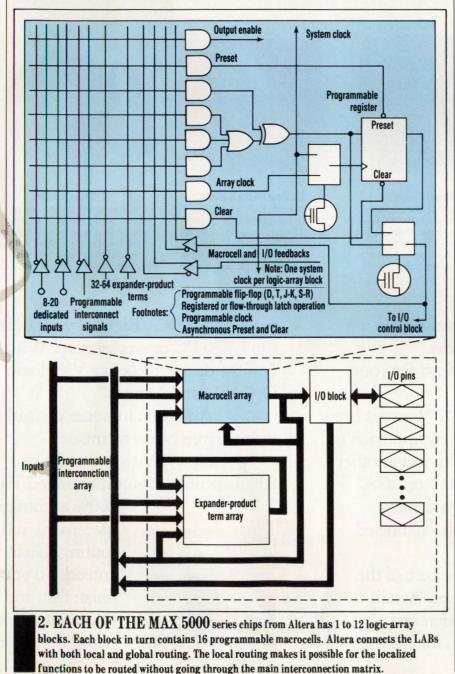

| ELECTRONIC<br>Design Report | 45 HIGH-DENSITY PROGRAMMABLE LOGIC TAKES ON GATE ARRAYS<br>As density, speed, and flexibility improve, field-programmable chips start to<br>replace masked gate arrays.                        |

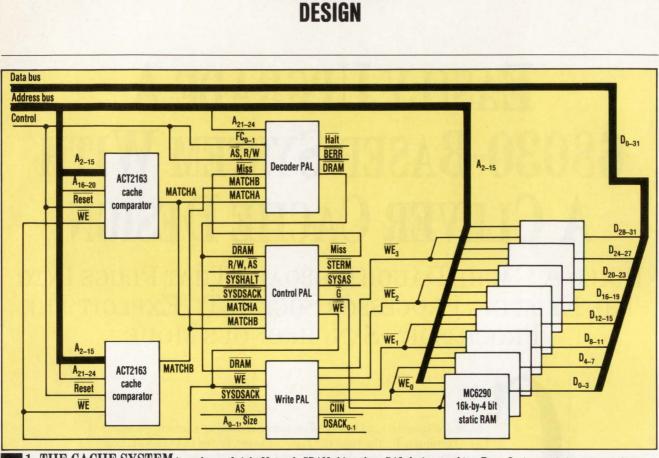

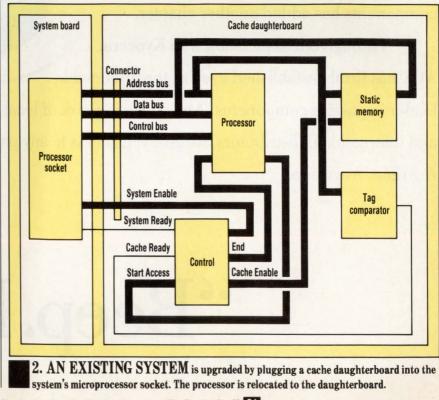

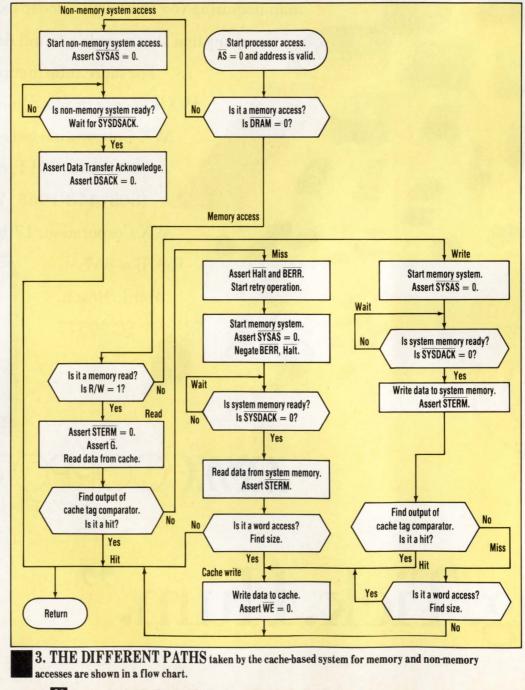

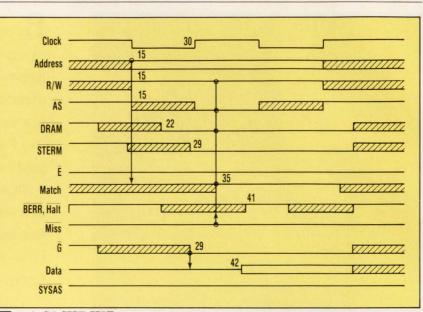

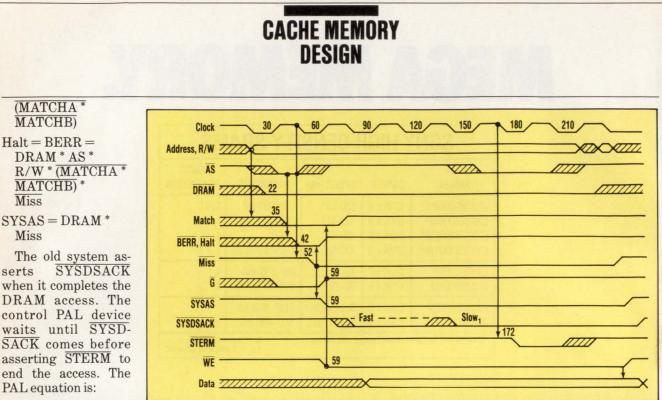

| DESIGN<br>Applications      | <b>59 UPGRADE A 68030-BASED SYSTEM WITH A CLEVER CACHE DESIGN</b><br>Build a cache daughterboard that plugs into the existing processor socket to<br>exploit the processor's synchronous mode. |

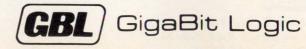

| PRODUCT<br>INNOVATIONS      | 101 REPEATER INTERFACE IC TAKES ON ETHERNET MEDIA<br>Robust executive and control functions simplify network-management tasks<br>for future Ethernet LANs.                                     |

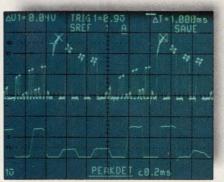

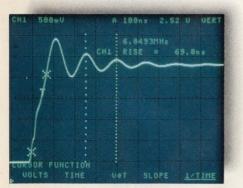

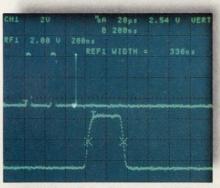

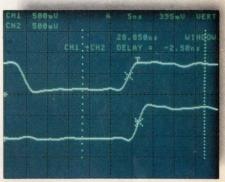

|                             | 105 SCOPES OFFER DIGITAL POWER IN A COZY SETTING<br>A pair of digital storage oscilloscopes try to make designers forsake the<br>comfort of their familiar analog instruments.                 |

|                             | 4 E L E C T R O N I C D E S I G N                                                                                                                                                              |

**4** E L E C T R O N I C D E S I G N MARCH 14, 1991

#### **14 EDITORIAL**

#### **18 TECHNOLOGY BRIEFING**

Improve power factor or lose Europe

#### **23 TECHNOLOGY NEWSLETTER**

• Software tackles RF designs up to 3 GHz

• Technology database aids system designers

• Software deal aims for common environment

• IBM strengthens its support for ISDN

• Service group judges system performance

• Graphical software does EMI modeling

• Box connects up to 16 hardware emulators

• Largest biCMOS arrays pack 150,000 gates

#### **29 TECHNOLOGY ADVANCES**

• U.S.-Japan developments enhance DRAM performance and packaging

Certificate of Merit Winner, 1988 Jesse H. Neal Editorial Achievement Awards

#### PC DESIGN SPECIAL EDITORIAL SECTION

69 PC Design Newsletter

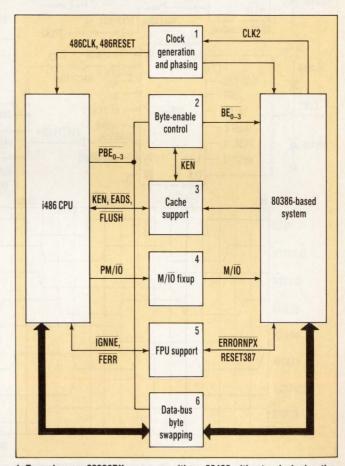

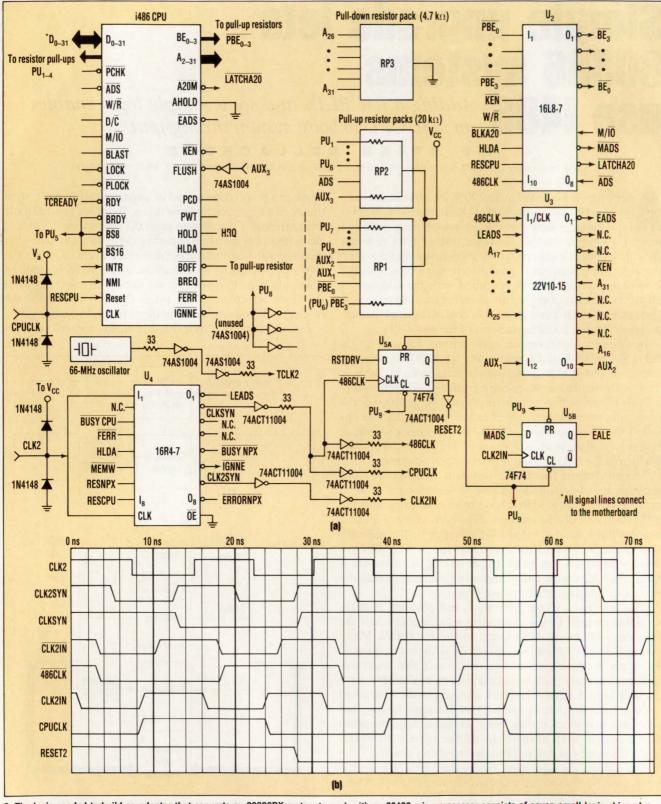

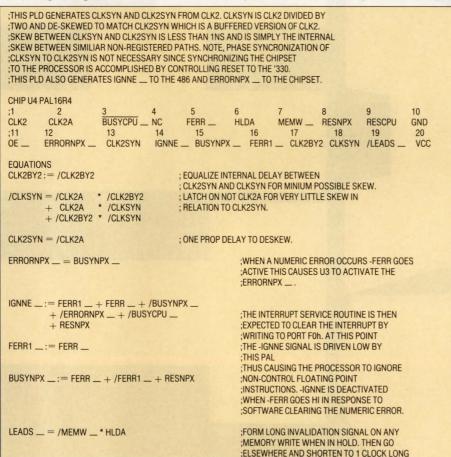

**71 PC Design Editorial Feature** Simple upgrade lets 80386 systems use i486

81 PC Design Products

#### **85 IDEAS FOR DESIGN**

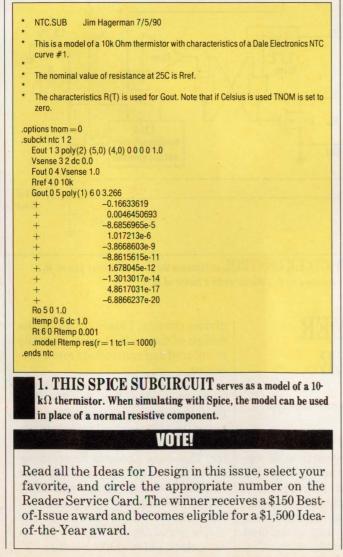

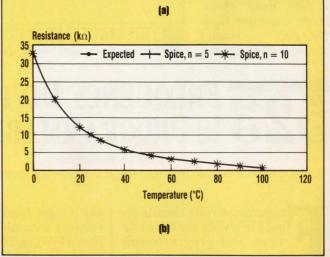

• Model thermistor with Spice

• Increase dc-dc converter power

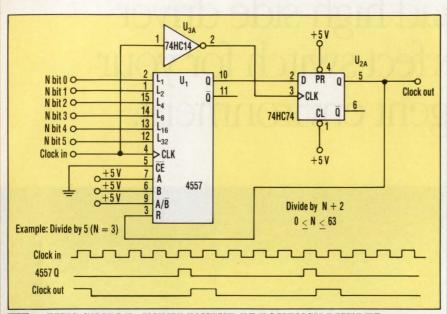

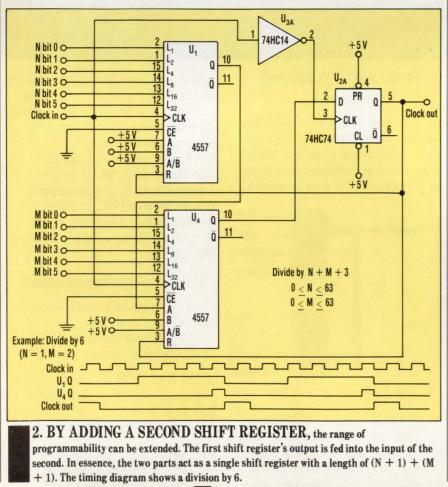

• Frequency divider is programmable

#### **91 QUICK LOOK**

• Perspectives on Time-to-Market: Creating project models

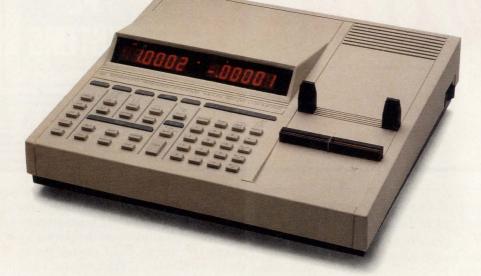

• Universal frequency counter-timer teams up with Windows 3.0

• Free software to help you find out if you qualify for a small-business loan

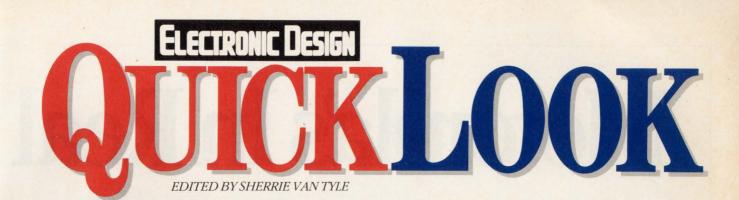

• Demand for RISC chips propels market for 32-bit microprocessors

• What engineering investors need to know about futures funds

#### **97 PEASE PORRIDGE**

What's all this statistical stuff, anyhow?

#### **NEW PRODUCTS**

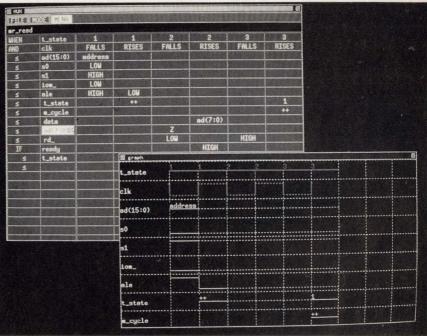

**109 Computer-Aided Engineering** Spreadsheet-like VHDL tool alleviates programming hassles

117 Communications

**118 Instruments**

#### **127 INDEX OF ADVERTISERS**

#### **129 READER SERVICE CARD**

**COMING NEXT ISSUE**

• Special Report: Fax modem chips

• Design Team Issues: Architectural models are key to system-level design

• First details on new workstation graphics ICs

• PIPS: Power, Packaging, Interconnections, Switches & Relays

• Suppress EMI/RFI from the ground up

• How to recognize a good conductor crimp

• Manufacturer listing for interconnections

Special products section

• PLUS: Ideas for Design Pease Porridge Technology Advances

ELECTRONIC DESIGN (USPS 172-080; ISSN 0013-4872) is published semi monthly by Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543. Paid rates for a one year subscription are as follows: 875 U.S., 8140 Canada, \$220 International. Second-class postage paid at Cleveland, OH, and additional mailing offices. Editorial and advertising addresses: ELECTRONIC DESIGN, 611 Route #46 West, Hasbrouck Heights, NJ 07604. Telephone (201) 393-6060. Facsimile (201) 393-0204.

Printed in U.S.A. Title registered in U.S. Patent Office. Copyright® 1991 by Penton Publishing Inc. All rights reserved. The contents of this publication may not be reproduced in whole or in part without the consent of the copyright owner.

Without the consent of the copyright owner. Permission is granted to users registered with the Copyright Clearance Center Inc. (CCC) to photocopy any article, with the exception of those for which separate copyright ownership is indicated on the first page of the article, provided that a base fee of \$1 per copy of the article plus \$.50 per page is paid directly to the CCC, 27 Congress St., Salem, MA 01970 (Code No. 0013-4872/91 \$1.00 + .50). Copying done for other than personal or internal reference use without the express permission of Penton Publishing, Inc. is prohibited. Requests for special permission or bulk orders should be addressed to the editor.

For subscriber change of address and subscription inquiries, call (216) 696-7000. POSTMASTER: Please send change of address

POSTMASTER: Please send change of address to ELECTRONIC DESIGN, Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543.

Cover: Tony Vitolo

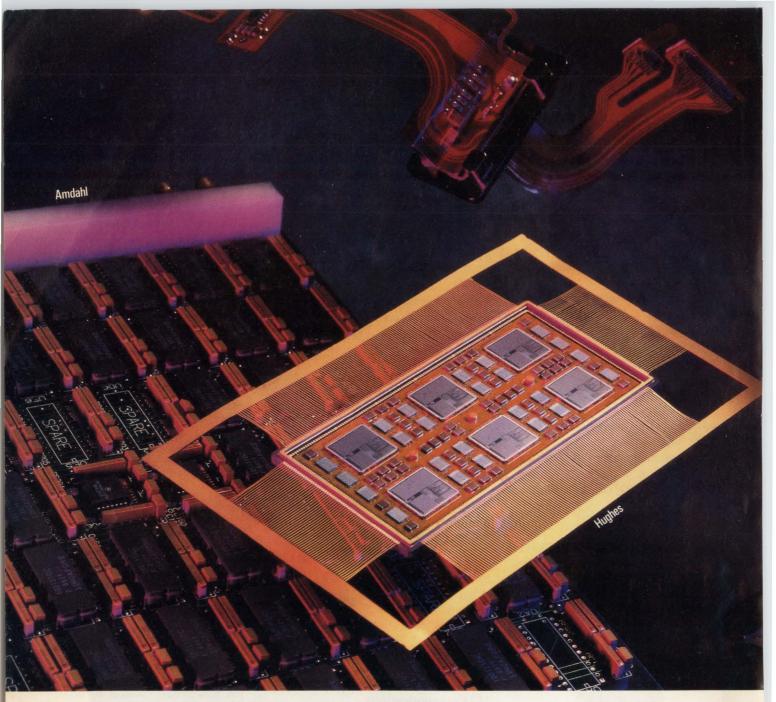

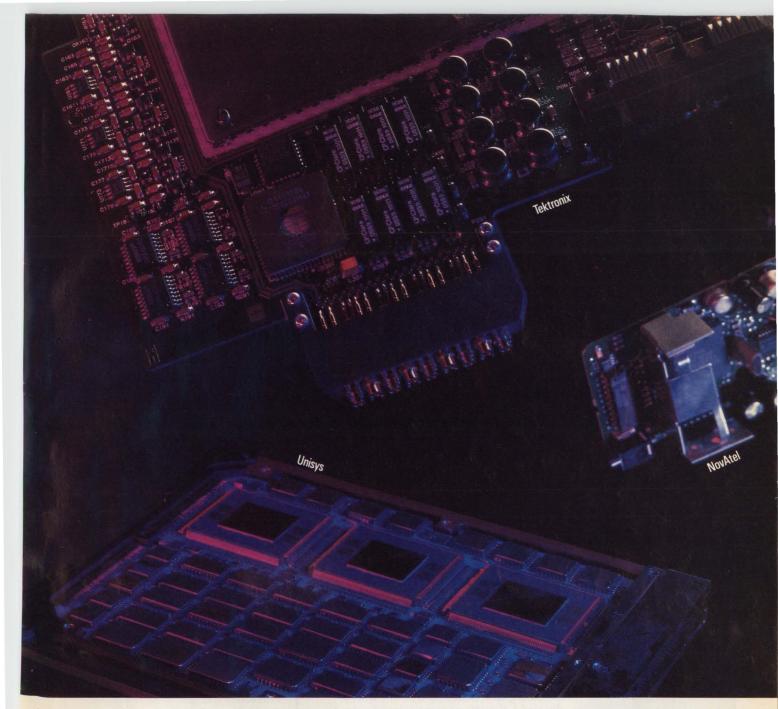

### THE LEADERS IN PCB DE WE SUPPLY

You're looking at some truly outstanding examples of advanced systems technology. PCB, hybrid, MCM. From some of the most prominent players in the electronics industry.

In each case, Mentor Graphics design tools helped leverage these complex board technologies into successful products:

A ten-layer ECL board from Amdahl with 1257 components and 1659 nets,

each with a length or impedance constraint.

A board from Tektronix combining very high-speed digital and low-noise analog circuitry.

A PCB from NovAtel using chip-onboard (COB) technology for dramatic space savings.

A flexible circuit board from a major hard disk manufacturer with complex curved geometries. A multi-chip module (MCM) from Hughes with 82 devices and 3300 interconnects on a 96x45 mm (3.8" x1.8") silicon substrate.

A Mil-Std multi-layer ceramic module from Unisys that packs 57 chips and 2834 pins into a 6''x6'' space less than .6'' thick.

Each of these designs required superior engineering combined with superb tool technology. Precisely the kind of partnership

### SIGN SUPPLY THE TALENT. THE TOOLS.

you get with Mentor Graphics, the leader in design automation. We offer tools that span the entire bandwidth of electronics systems technology, from PCB to hybrid to MCM.

Our Advanced Dynamic Editor, which brings new dimensions of productivity to manual routing operations. Our highperformance autorouter. And our special support for high-speed circuitry. But tools are only half the story. Mentor Graphics Consulting and Support Services round out our partnership with you and help ensure your success. The best in customer and engineering support. Integration services that smooth the transition of our tools into your environment. Plus the Mentor Graphics Falcon Framework™ can bind all your design automation tools into a productive whole, regardless of their source. So for more information, phone 1-800-547-3000 or 1-503-685-8000 (Dept. 102). If you've got the talent, we've got the tools.

ANCOT'S SCSI instruments are powerful, easier to use, and cost less. Proven in use worldwide, Ancot's portable equipment travels from bench to field and back again without ever slowing down. They are time and labor saving instruments, for design, manufacturing, repairing, and inspection applications.

120

Call today for product data sheets, demo disc, or to make arrangements for a free evaluation unit in your facility.

5] 322-5322 fax: (415) 322-0455 115 Constitution Drive Menlo Park, CA 94025

CIRCLE 132

#### ELECTRONIC DESIGN

Editor-in-Chief: Stephen E. Scrupski

Executive Editor: Roger Allan

Managing Editor: Bob Milne

Senior Editors: Frank Goodenough, Milt Leonard, John Novellino

#### **Technology Editors:**

Analog & Power: Frank Goodenough Communications & Industrial: Milt Leonard (San Jose) Components & Packaging: David Maliniak Computer-Aided Engineering: Lisa Maliniak Computer Systems: Richard Nass Semiconductors: Dave Bursky (San Jose) Test & Measurement: John Novellino

News Editor: Sherrie Van Tyle

New Products Editor: Susan Nordyk

#### **Field Bureaus:**

West Coast Executive Editor: Dave Bursky (San Jose) Boston: Lawrence Curran Dallas: Jon Campbell Frankfurt: John Gosch London: Peter Fletcher

Chief Copy Editor: Roger Engelke, Jr.

**Contributing Editors:** Ron Kmetovicz, Robert A. Pease

**Editorial Production Manager:** Lisa Iarkowski

Editorial Support Supervisor: Mary James

Editorial Assistant: Ann Kunzweiler

Editorial Secretary: Bradie Guerrero

Editorial Offices: (201) 393-6272

Advertising Production: (201) 393-6093 or FAX (201) 393-0410

**Production Manager:** Michael McCabe *Production Assistants:* Donna Marie Bright, Lucrezia Hlavaty, Eileen Slavinsky

Circulation Manager: Robert Clark

Promotion Manager: Clifford Meth

Reprints: Helen Ryan 1-800-835-7746

Group Art Director: Peter K. Jeziorski

**Computer Systems Administrator:** Anne Gilio Turtoro

Published by Penton Publishing Vice President-Editorial: Perry Pascarella Group Editorial Director: Leland Teschler

Publisher: Paul C. Mazzacano

CIRCLE 100 BELECTRONICDESIGN MARCH 14, 1991

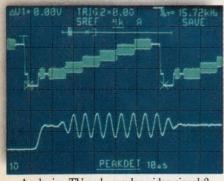

#### IS IT C<sup>#</sup>, JENNY'S FIRST WORD, OR A TURBINE ABOUT TO EXPLODE?

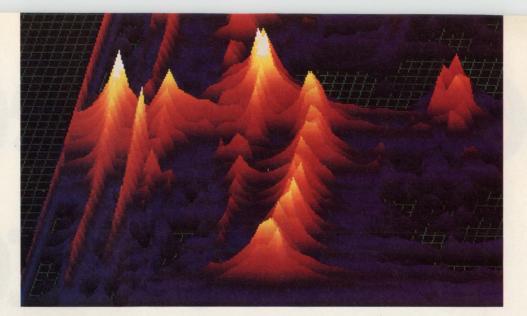

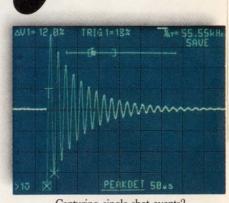

MacDSP can acquire, analyze and display signals so quickly you can actually see the harmonic variations of a flute as it plays, recognize speech, or spot dangerous signals before it's too late.

With an advanced 50 MHz floating-point digital signal processor and modular data acquisition on a single card, MacDSP's design bypasses CPU traffic jams and lets the Macintosh do what it does best: graphics.

MacDSP hardware can be configured with a variety of processor speeds to meet your specs and budget, memory capacities large enough for speech analysis or image processing, and acquisition options to handle anything from robotic control to electronic music to ultrasonic vibration.

MacDSP Signal Analysis software turns your Macintosh into a signal processing instrument with real-time displays which surpass ordinary oscilloscopes and spectrum analyzers. We offer an array processing library of common DSP and mathematical functions to speed up your existing programs, and AT&T's optimized C compiler for more advanced applications.

Contact us for a free demo disk. Spectral Innovations, Inc., 4633 Old Ironsides Dr., Ste.450, Santa Clara, CA 95054. Phone: (408) 727-1314. FAX: (408) 727-1423.

# Because Speed We'll Stop

#### MACH

Fastest High Density CMOS PLDs At 15ns

PALCE16V8H-10

Fast Universal CMOS PLD Family At 10ns

PAL16L8-5

Fast Bipolar PLD Family At 5ns

# Is Everything, At Nothing.

20N5

15NS 10NS 5 NS PAL16L8-4 **Fastest TTL Bipolar PLD** At 4.5ns

#### Whatever kind of PLD you need, the fastest comes from AMD.

We'd love it if all our work amounted to "zero." As in zero delay. And we're not far off.

Not surprising—because AMD invented the PAL<sup>®</sup> device. That's why we know programmables better. And offer you the most choices of the best devices.

Say you want speed, but can't sacrifice density. Don't. Use our new MACH™ products (Macro Array CMOS High-density) that give you up to 3600 gates and 15ns performance. They're two to three times faster than the competition and cost 40% less.

For more speed, along with low power consumption, try our new 10- and 15-nanosecond CMOS PLDs. Use our 16V8-10s and 20V8-10s anywhere you'd use a GAL® device. Or choose the everpopular AMD-invented 22V10, at 15ns.

Faster still are our seventh generation bipolar PAL devices. Complete families of 16L8-5s, 20L8-5s, and the 22V10-10s. And for real speed freaks, we're now shipping a 4.5ns bipolar PAL device—the world's fastest TTL programmable logic.

Along with all this speed, we're providing equally fast delivery. In quantity. In fact, we deliver more programmable logic devices than all our competitors combined.

For details, call AMD now at **1-800-222-9323**. And let nothing stand between you and your need for speed.

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088 © 1991 Advanced Micro Devices. Inc. MACH is a trademark and PAL is a registered trademark of Advanced Micro Devices. GAL is a registered trademark of Lattice Semiconductor.

CIRCLE 135

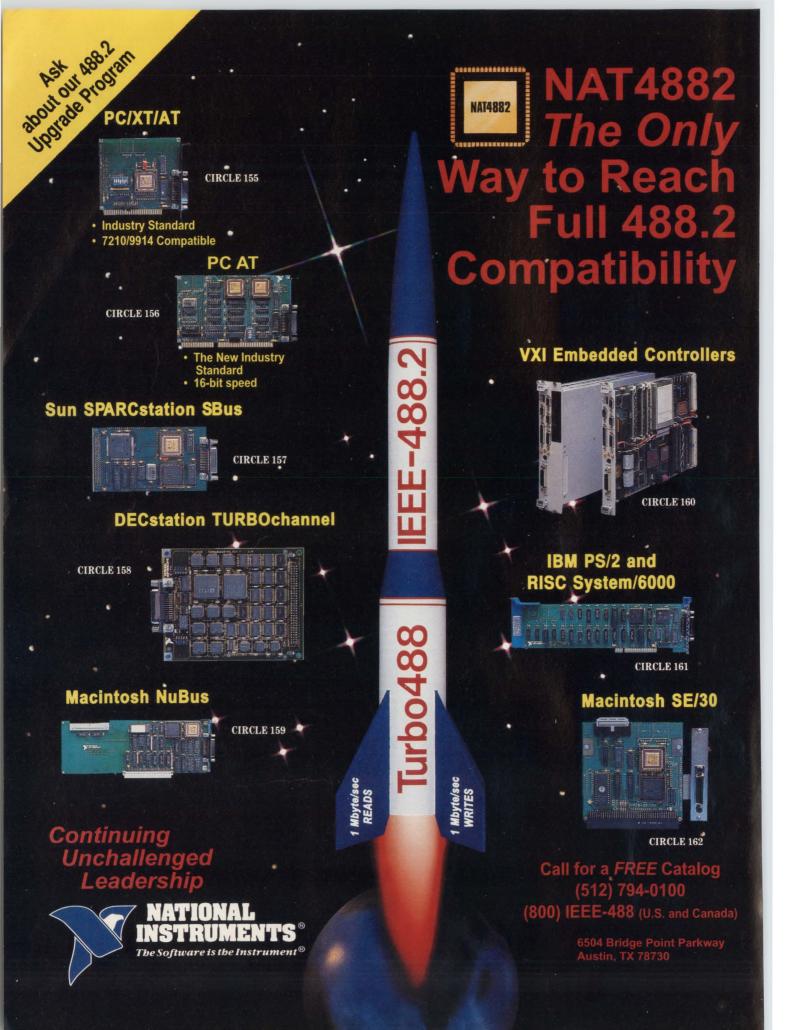

### The IBM RISC System/ The power you've been seeking

It's a never-ending quest for power seekers. You're always looking for ways to run your favorite applications faster. Well, search no more. The RISC System/6000<sup>~</sup> family of POWERstations and POWERservers gives you power that soars as high as 23 MFLOPS and 56 MIPS.

|                     | MFLOPS | MIPS | SPECmark™ |

|---------------------|--------|------|-----------|

| POWERstation 320    | 7.4    | 29.5 | 22.4      |

| DECstation 5000-200 | 3.7    | 24.2 | 18.5      |

When it comes to porting, your ship has come in. Of course, all the speed in the world wouldn't mean much without the applications you need. So the RISC System/6000 family already has more than 2,000 of the most popular technical and commercial applications up, running and running fast. And if you think you know a good thing when you see it, so do software vendors. That's why you'll also be seeing more and more applications coming on board the RISC System/6000 platform all the time. And if you like to build your own solutions, there's a full arsenal of enablers and relational data bases from leading vendors, as well as CASE tools and a host of popular programming languages.

A smorgasbord of solutions. Applications already announced include the IBM engineering design packages CADAM, CAEDS, CBDS,

MFLOPS are the results of the double-precision, all FORTRAN Linpack test 100x100 array suite. The Dhrystone Version 1.1 test results are used to compute RISC System/6000 Integer MIPS value where 1,757 Dhrystones/second is 1 MIPS (Vax 11/780). SPECmark is a geometric mean of ten benchmark tests. All performance data are based on published benchmark information.

IBM is a registered trademark, and RISC System/6000 and CAEDS are trademarks of International Business Machines Corporation. SPECmark is a trademark of Standard Performance Evaluation Corporation. UNIX is a registered trademark of UNIX System Laboratories. Inc: CADAM is a trademark of CADAM INC: CATIA is a trademark of Dasault Systemes. CBDS is a trademark of Bell Northern Research Corporation. DECstation is a trademark of Digital Equipment Corporation. ACAR THE HORRIBLE Character(s) @ 1990 (International Business, Inc: @IABAM Is a trademark of Digital Equipment Corporation. HACAR THE HORRIBLE Character(s) @ 1990 (International Business, Inc: @IABAM Is a trademark of Digital Equipment Corporation. HORRIBLE Character(s) @ 1990 (International Business, Inc: @IABAM Is a trademark of Digital Equipment Corporation. HORRIBLE Character(s) @ 1990 (International Business, Inc: @IABAM Is a trademark of Digital Equipment Corporation. HORRIBLE Character(s) @ 1990 (International Business, Inc) @ 1990 (International Business) @ 1990 (International Busi

### 6000 family. for all your applications.

CATIA<sup>™</sup> and AES. Also available are a broad spectrum of solutions from vendors like Valid Logic, MacNeal Schwendler, Swanson Analysis, SAS Institute, SPSS, Wavefront, Alias, Polygen, **Cadence**, Fluid Dynamics International, Western Atlas, ECL Petro and creare.X. Scientific and technical applications are available in areas like physics, structural analysis, chemistry, securities trading, mathematics, earth resources, operations research, visualization, graphics, technical publishing and more. There's also accounting software like FourGen and support for leading UNIX<sup>®</sup>-based office automation packages. And there are key industry applications for businesses in medical groups, retail stores, newspapers, pharmacies and many more.

#### Command enormous processing clout.

The RISC System/6000 family is built to boost the performance of the software power seekers use most. It's got the best floating point processor in the business for numerically intensive applications, plus a new superscalar processor

and incredible 3D graphics capabilities. To find out more, call your IBM marketing representative or IBM Business Partner. For literature, call 1 800 IBM-6676, ext. 990.

#### For the Power Seeker.

**CIRCLE 94**

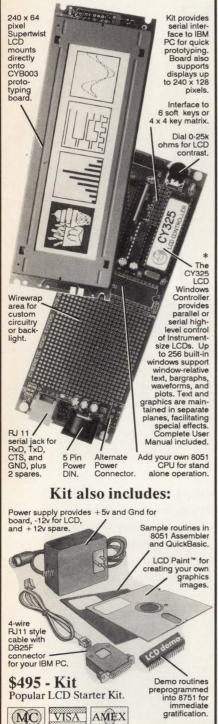

#### LCD Proto Kit

Everything you need to start your LCD application .... create complex screens in just a few hours!

(\$595 pre-assembled & tested)

The CY325 40-pin CMOS LCD Controller IC is available from stock @ \$75/singles, \$20/1000s (Surface mount also avail in qty.)

CyberneticMicroSystems Box 3000 • San Gregorio CA 94074 Tel: 415-726-3000 • Fax: 415-726-3003

**CIRCLE 121**

#### EDITORIAL

#### THE ELECTRONIC ROLE IN WAR

p to now, we've hesitated to mention the Persian Gulf War in this column because of a time lag between the time this column must be written to meet our deadline and the time it appears on readers' desks. In this intervening period, rapidly changing events may render our comments, when they appear in print, inappropriate, or worse, insensitive to a negative turn of events in the war. However, while writing this column, the situation seems close to being resolved, with little doubt about the outcome. In the hope that peace will soon arrive, and within the bounds of the caveat cited above, we offer a comment on the technological aspects of the episode.

The prime-time TV showcase for the U.S. arsenal of sophisticated, electronically controlled weapons will be etched in our memories. For those who have built careers on designing electronic equipment to solve a customer's problem, there should be little surprise about their performance. After all, these devices, properly designed, simply follow the laws of physics, just as much as a bomb falling from a plane follows the basic physical law of gravity. But even knowing this, we still marvel at just how well those systems work, combining optics, radar, computer, and propulsion technologies.

Having proven the performance of this breed of intelligent weapons, what's next for the defense electronics industry? These weapons, with their demonstrated effectiveness, could undoubtedly be improved by incorporating the latest technology. We certainly hope that this is the last time they're used, but that should not stop us from improving the accuracy and reliability of the next generation, just in case we need them again.

While we're at it, let's also hope that the Department of Defense and defense-industry management will institute corresponding improvements in program administration to cut waste and inefficiency. This may not be easy to do, but it's as important as the swiftness and accuracy of the weapons themselves.

dien &

Stephen E. Scrupski Editor-in-Chief

14 E L E C T R O N I C D E S I G N MARCH 14, 1991

## PRECISION TTL-CONTROLLED ATTENU/ATO

Now...precision TTL-controlled attenuators accurate over 10 to 1000MHz and -55 to +100°C. Four models are available in the new TOAT-series, each with 3 discrete attenuators switchable to provide 7 discrete and accurate attenuation levels (see chart). Cascade all four models for up to 64.5dB control in 0.5dB steps. Custom values available on request. The 50-ohm TOAT-series performs with 6µsec switching speed

up to 35dB 10 to 1000MHz

| TOAT-R512<br>Accuracy<br>(dB) (+/-dB) |      | TOAT-<br>Accur<br>(dB) |     | -dB) TOAT-3610<br>Accuracy<br>(dB) (+/-c |     | TOAT-51020<br>Accuracy<br>(dB) (+/ |     |

|---------------------------------------|------|------------------------|-----|------------------------------------------|-----|------------------------------------|-----|

| 0.5                                   | 0.12 | 1.0                    | 0.2 | 3.0<br>6.0                               | 0.3 | 5.0<br>10.0                        | 0.3 |

| 1.5                                   | 0.32 | 3.0                    | 0.4 | 9.0                                      | 0.6 | 15.0                               | 0.6 |

| 2.0                                   | 0.2  | 4.0                    | 0.3 | 10.0                                     | 0.3 | 20.0                               | 0.4 |

| 2.5                                   | 0.32 | 5.0                    | 0.5 | 13.0                                     | 0.6 | 25.0                               | 0.7 |

| 3.0                                   | 0.4  | 6.0                    | 0.5 | 16.0                                     | 0.6 | 30.0                               | 0.7 |

| 3.5                                   | 0.52 | 7.0                    | 0.7 | 19.0                                     | 0.9 | 35.0                               | 1.0 |

bold faced values are individual elements in the units

**CIRCLE 148**

WE ACCEPT AMERICAN EXPRESS

present designs and plan future systems.

and can handle power levels up to 0dBm. Units are housed in a rugged hermetically-sealed TO-8 package to withstand the shock, vibration, and temperature stresses of MIL-STD-883. Connector versions are available. Take advantage of the \$59.95 (1-9 qty) price breakthrough to stimulate new applications as you implement

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 Domestic and International Telexes: 6852844 or 620156

rcu

| TOAT-<br>Accur<br>(dB) |     | TOAT-51020<br>Accuracy<br>(dB) (+/-dB) |     |  |  |

|------------------------|-----|----------------------------------------|-----|--|--|

| 3.0                    | 0.3 | 5.0                                    | 0.3 |  |  |

| 6.0                    | 0.3 | 10.0                                   | 0.3 |  |  |

| 9.0                    | 0.6 | 15.0                                   | 0.6 |  |  |

| 10.0                   | 0.3 | 20.0                                   | 0.4 |  |  |

| 100                    | 00  | 05.0                                   | 07  |  |  |

finding new ways ...

setting higher standards

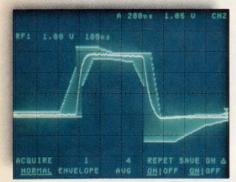

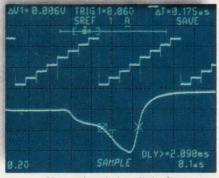

# What's

Analyzing TV and complex video signals?

Testing telecommunications signals?

Uncovering elusive glitches?

Finding aberrations buried within a signal?

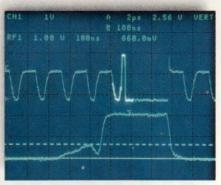

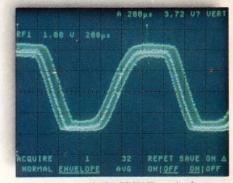

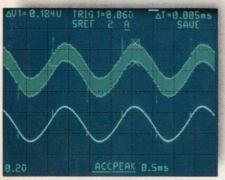

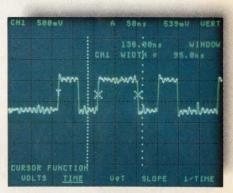

You can't depend on banner specs alone to solve problems like these. Whether you're trying to measure waveform parameters or analyze long data streams, identify infrequent events or track down glitches as narrow as 2 ns — there's all the difference between the depth of Tek troubleshooting and the trade-offs in other DSOs that compromise your results.

Spec for spec, feature for feature, no other company offers the credentials Tek does to

Capturing single-shot events?

Automatic PASS/FAIL testing?

effectively match DSO performance to your application needs. Whatever your criteria, you'll find a perfect solution in our line of problem-solving portable DSOs, from 10 to 500 MS/s.

Select the features to support your application. Tek DSOs offer a diverse set of capabilities including peak detect to uncover elusive glitches. Fast update rate for live signal display. Combined analog/digital operation for real-time verification of your

# r problem?

Characterizing signal noise?

Capturing and analyzing long data streams?

Performing complex measurements automatically?

Expanding glitches for close analysis?

Measuring timing relationship between signals?

Windowing in on signal details?

signal. Or Save on Delta to automatically verify that all parts of your signal fall within prescribed limits. Best of all, Tek's line of 100 MS/s digitizing scopes start at just \$3995.

To find out which Tek scope is right for you, contact your Tek representative, return the card or call Tek direct. We can answer your questions and show you a scope that doesn't just look good on paper. It makes your toughest troubleshooting challenges routine.

#### TECHNOLOGY BRIEFING

#### **IMPROVE POWER FACTOR OR LOSE EUROPE**

uilding power-factor correction into switching power supplies has become a fact of life for a number of reasons. For one, it alleviates the problems caused in electrical-distribution networks when the supplies' filter capacitors draw current in short pulses. It also keeps current out of the neutral line in balanced-load systems.

But for those who keep an eye on such things, as all power-supply manufacturers must (and as users should), power-factor correction can also keep products from running afoul of some prickly regulatory require-

from running afoul of some prickly regulatory requirements. One requirement, which now exists only in an COMPONENTS & PACKAGING

advisory capacity in Europe, may, upon its widespread adoption, fundamentally change the way power-supply makers and users look at the need for power-factor correction.

Though intended originally for household electronic equipment at power levels above 200 W, the requirement in question, IEC 555-2, allows a maximum third-harmonic current of 2.3 A with decreasing limits for higher-order harmonics. These limits will become even more stringent when a new revision (77A) is accepted. In this proposal, the standard applies to all equipment with line currents up to 16 A—there's no minimum. It also gives a relative as well as a reduced absolute limit for each current harmonic. The third-harmonic limit will now be set at 3.6 mA/W or 1.08 A absolute, with similarly decreasing limits for the higher orders.

The implications of the specification are already becoming clear. It's anticipated that these limits will be enforced extensively in Europe within the next year or two. Austria has begun invoking the standard and Germany is preparing to do so. Moreover, it's likely that the United States will soon begin to take these limits seriously. The effect of enforcement is to effectively ban the sale of any equipment that does not comply. Major systems manufacturers, who must be looking at least two years ahead in terms of their component specifications, should pay attention. If they want to get their products into the European marketplace, they'll be compelled to specify higher power factors and lower harmonic-current levels in their next-generation power supplies. The alternative, which is to specify a compliant and a non-compliant supply, is likely to be too costly for most OEMs.

There are some caveats to power-factor correction, though. For one, it makes the supply's design more complex. According to Lou Pechi, director of marketing at Power-One Inc., Camarillo, Calif., power-factor correction can increase design difficulty by up to a magnitude. When the power-supply business began emphasizing switching supplies instead of linear designs, much of the business went from captive to non-captive. Many power-supply consumers tried to design their own switchers in-house, but it required specialized design skills that were in short supply. Instead, many users bought switchers from OEM vendors. The same trend is likely to continue with the new generation of power-factor-corrected supplies.

On the one hand, Pechi agrees that enforcing the IEC 555-2 specification, on a virtual worldwide basis, is inevitable. But on the other, he noted, the IEC 555-2 specification doesn't demand a 0.99 power factor in all cases. For a 2000-W supply, in which harmonics will likely exceed the specification, the upper limits of correction are a necessity. As output levels decrease, however, the level of correction can fall as well. At 750 W, a 0.8 power factor is adequate. And at 500 W, users can probably live with a power factor of 0.6, which is the power factor of a regular power supply. Below 250 W, its not needed at all, because the harmonic content isn't there. The bottom line is that before specifying a power-factor-corrected supply for a given application, users have to dust off their Fourier textbooks and determine if it's needed at all.

#### The best address for Siemens Semiconductors:

A Wien Tel. (0222) 71711-5661 (AUS) Melbourne, Vic. 3121 Tel. (03) 4 20 71 **(B)** Bruxelles Tel. (02) 536-2111 (BR) São Paulo-SP Tel. (011) 833-221 (CDN) Mississauga L5T 1P2 Tel. (416) 564-1995 **CH** Zürich Tel. (01) 495-3111 D Berlin 10 Tel. (030) 3993-0 Düsseldorf 1 Tel. (0211) 399-0 Frankfurt 1 Tel. (069) 797-0 Hamburg 1 Tel. (040) 2889-0 Hannover 81 Tel. (0511) 877-0 München 80 Tel. (089) 9221-4391/4138 Nürnberg 1 Tel. (0911) 654-0 Stuttgart 1 Tel (0711) 2076-0 **DK** Ballerup Tel. (44) 774477 E Madrid Tel. (01) 5554062 (F) Paris Tel. (1) 4922-3810 **(GB)** Sunbury on Thames Tel. (0932) 75261 **GR** Amaroussio/Athen Tel. (01) 6864-111 (HK) Hongkong Tel. 5-8330222 (1) Milano Tel. (02) 6766-4241 (IND) Bombay 400018 Tel. 4938786 (IRL) Dublin Tel. (01) 30 28 55 J Tokyo 100 Tel. (03) 201-2401 (N) Oslo 5 Fel. (02) 633000 NL Den Haag Tel. (070) 3333333 P Alfragide Tel. (01) 4183311 (RA) Buenos Aires Tel. (01) 300411 (RC) Taipei Tel. (02) 5234700 (ROC) Seoul Tel. (02) 275-6111 (s) Kista Tel. (08) 7033500 (SF) Helsinki Tel. (9) 051051 (SEP) Singapore 0513 Tel. 7760044 (TR) Istanbul Tel. (01) 1510900 (USA) Iselin Tel. (201) 906-4300 (Discrete) Santa Clara Tel. (408) 980-4500 (ICs) Cupertino rel. (408) 725-7910 (Opto) (ZA) Johannesburg Tel. (011) 407-4111

18 E L E C T R O N I C D E S I MARCH 14, 1991

IGN

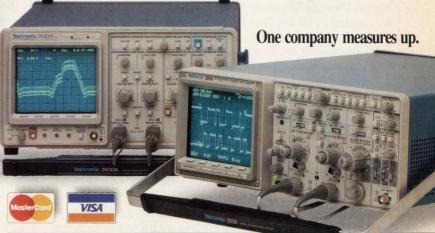

#### Switchcraft as witchcraft.

If the issue is digital switching and conferencing, the solution is utmost flexibility in capability, capacity and unsurpassed economy. Switchcraft is wanted as witchcraft.

Siemens Semiconductors offers the most economical answer to any conceivable application in the field: Our complete family of switching network devices satisfies even the most rigorous switching demands.

Take our MTSC (Memory Time Switch CMOS) PEB 2045 with a switching capability of 512 incoming PCM channels to 256 outgoing PCM channels. It has the perfect size to build very economical medium sized switches. The design of a non-blocking switch for 512 PCM channels is possible with a simple parallel configuration of a second MTSC. If you need a non-blocking switch for up to 256 channels, we offer a smaller version of the MTSC, the MTSS (Memory Time Switch Small) PEB 2046. And the MTSL (Memory Time Switch Large) PEB 2047, the largest in our family, is capable of switching 1024 PCM channels in a single device.

Siemens also supplies the best solution for conferencing. Our MUSAC (Multipoint Switching and Conferencing Unit) PEB 2245 performs the complete switching functions of the MTSC, and offers a signal processor for handling up to 64 conferencing channels in any combination. The input and output channels can also be attenuated individually to achieve best transmission quality.

CIRCLE 152

Pin compatible devices as well as wideband switching capabilities allows simplicity in hardware and software design. To allow for more flexibility, the PCM data rate can be 2, 4 or 8 MBit/s – configurable also for mixed use. No matter what size you need, is it not time to switch over? For details, call (800) 456-9229, or write Siemens Components, Inc., 2191 Laurelwood Road, Santa Clara, CA 95054-1514. Ask for literature package M12A005.

Siemens Practical Solutions By Design

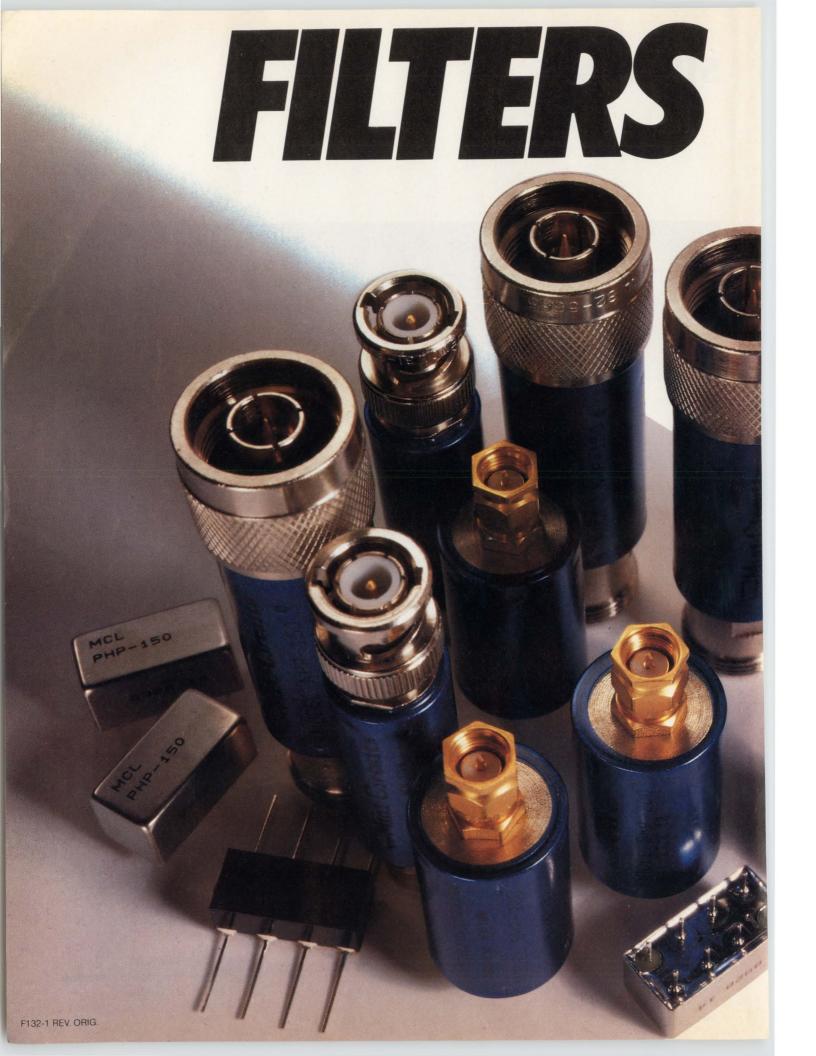

# dc to 3GHz from \$1145

#### lowpass, highpass, bandpass, narrowband IF

- less than 1dB insertion loss

greater than 40dB stopband rejection

- 5-section, 30dB/octave rolloff VSWR less than 1.7 (typ) meets MIL-STD-202 tests

- rugged hermetically-sealed pin models

BNC, Type N; SMA available

- surface-mount over 100 off-the-shelf models immediate delivery

| low | pass | dc  | to  | 1200    | WHz  |

|-----|------|-----|-----|---------|------|

|     |      | PAS | SBA | ND, MHZ | fco, |

| LON | W PASS |  |

|-----|--------|--|

|     |        |  |

frequency

|              | PASSBAND, MHz<br>(loss <1dB) | fco, MHz<br>(loss 3db) | (loss>2 | OP BAND, I<br>20dB) (loss | MHz<br>s>40dB) | pass-        | stop-        | PRICE         |

|--------------|------------------------------|------------------------|---------|---------------------------|----------------|--------------|--------------|---------------|

| MODEL<br>NO. | Min.                         | Nom.                   | Max.    | Max.                      | Min.           | band<br>typ. | band<br>typ. | Qty.<br>(1-9) |

| PLP-10.7     | DC-11                        | 14                     | 19      | 24                        | 200            | 1.7          | 18           | 11.45         |

| PLP-21.4     | DC-22                        | 24.5                   | 32      | 41                        | 200            | 1.7          | 18           | 11.45         |

| PLP-30       | DC-32                        | 35                     | 47      | 61                        | 200            | 1.7          | 18           | 11.45         |

| PLP-50       | DC-48                        | 55                     | 70      | 90                        | 200            | 1.7          | 18           | 11.45         |

| PLP-70       | DC-60                        | 67                     | 90      | 117                       | 300            | 1.7          | 18           | 11.45         |

| PLP-100      | DC-98                        | 108                    | 146     | 189                       | 400            | 1.7          | 18           | 11.45         |

| PLP-150      | DC-140                       | 155                    | 210     | 300                       | 600            | 1.7          | 18           | 11.45         |

| PLP-200      | DC-190                       | 210                    | 290     | 390                       | 800            | 1.7          | 18           | 11.45         |

| PLP-250      | DC-225                       | 250                    | 320     | 400                       | 1200           | 1.7          | 18           | 11.45         |

| PLP-300      | DC-270                       | 297                    | 410     | 550                       | 1200           | 1.7          | 18           | 11.45         |

| PLP-450      | DC-400                       | 440                    | 580     | 750                       | 1800           | 1.7          | 18           | 11.45         |

| PLP-550      | DC-520                       | 570                    | 750     | 920                       | 2000           | 1.7          | 18           | 11.45         |

| PLP-600      | DC-580                       | 640                    | 840     | 1120                      | 2000           | 1.7          | 18           | 11.45         |

| PLP-750      | DC-700                       | 770                    | 1000    | 1300                      | 2000           | 1.7          | 18           | 11.45         |

| PLP-800      | DC-720                       | 800                    | 1080    | 1400                      | 2000           | 1.7          | 18           | 11.45         |

| PLP-850      | DC-780                       | 850                    | 1100    | 1400                      | 2000           | 1.7          | 18           | 11.45         |

| PLP-1000     | DC-900                       | 990                    | 1340    | 1750                      | 2000           | 1.7          | 18           | 11.45         |

| PLP-1200     | DC-1000                      | 1200                   | 1620    | 2100                      | 2500           | 1.7          | 18           | 11.45         |

#### high pass dc to 2500MHz

| MODEL<br>NO. |      | ND, MHz<br><1dB)<br>Min. | fco, MHz<br>(loss 3db)<br>Nom. | STOP BA<br>(loss>20dB)<br>Min. | ND, MHz<br>(loss>40dB)<br>Min. | VS<br>pass-<br>band<br>typ. | WR<br>stop-<br>band<br>typ. | PRICE<br>\$<br>Qty.<br>(1-9) |

|--------------|------|--------------------------|--------------------------------|--------------------------------|--------------------------------|-----------------------------|-----------------------------|------------------------------|

| PHP-50       | 41   | 200                      | 37                             | 26                             | 20                             | 1.5                         | 17                          | 14.95                        |

| PHP-100      | 90   | 400                      | 82                             | 55                             | 40                             | 1.5                         | 17                          | 14.95                        |

| PHP-150      | 133  | 600                      | 120                            | 95                             | 70                             | 1.8                         | 17                          | 14.95                        |

| PHP-175      | 160  | 800                      | 140                            | 105                            | 70                             | 1.5                         | 17                          | 14.95                        |

| PHP-200      | 185  | 800                      | 164                            | 116                            | 90                             | 1.6                         | 17                          | 14.95                        |

| PHP-250      | 225  | 1200                     | 205                            | 150                            | 100                            | 1.3                         | 17                          | 14.95                        |

| PHP-300      | 290  | 1200                     | 245                            | 190                            | 145                            | 1.7                         | 17                          | 14.95                        |

| PHP-400      | 395  | 1600                     | 360                            | 290                            | 210                            | 1.7                         | 17                          | 14.95                        |

| PHP-500      | 500  | 1600                     | 454                            | 365                            | 280                            | 1.9                         | 17                          | 14.95                        |

| PHP-600      | 600  | 1600                     | 545                            | 440                            | 350                            | 2.0                         | 17                          | 14.95                        |

| PHP-700      | 700  | 1800                     | 640                            | 520                            | 400                            | 1.6                         | 17                          | 14.95                        |

| PHP-800      | 780  | 2000                     | 710                            | 570                            | 445                            | 2.1                         | 17                          | 14.95                        |

| PHP-900      | 910  | 2100                     | 820                            | 660                            | 520                            | 1.8                         | 17                          | 14.95                        |

| PHP-1000     | 1000 | 2200                     | 900                            | 720                            | 550                            | 1.9                         | 17                          | 14.95                        |

#### bandpass 20 to 70MHz

|                                                            | CENTER<br>FREQ.                    |                                  | ND, MHz<br><1dB)                 | (loss >                            |                                       | AND, MHz<br>(loss > 2                  |                                        | VSWR<br>1.3:1 typ.                                       | PRICE                                                       |

|------------------------------------------------------------|------------------------------------|----------------------------------|----------------------------------|------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|

| MODEL<br>NO.                                               | MHz<br>F0                          | Max.<br>F1                       | Min.<br>F2                       | Min.<br>F3                         | Max.<br>F4                            | Min.<br>F5                             | Max.<br>F6                             | total band<br>MHz                                        | Qty.<br>(1-9)                                               |

| PIF-21.4<br>PIF-30<br>PIF-40<br>PIF-50<br>PIF-60<br>PIF-70 | 21.4<br>30<br>42<br>50<br>60<br>70 | 18<br>25<br>35<br>41<br>50<br>58 | 25<br>35<br>49<br>58<br>70<br>82 | 4.9<br>7<br>10<br>11.5<br>14<br>16 | 85<br>120<br>168<br>200<br>240<br>280 | 1.3<br>1.9<br>2.6<br>3.1<br>3.8<br>4.4 | 150<br>210<br>300<br>350<br>400<br>490 | DC-220<br>DC-330<br>DC-400<br>DC-440<br>DC-500<br>DC-550 | 14.95<br>14.95<br>14.95<br>14.95<br>14.95<br>14.95<br>14.95 |

#### narrowband IF

| MODEL                                              | CENTER<br>FREQ.<br>MHz               | PASS BAND, MHz<br>I.L. 1.5dB max.                            | STOP BA                       |                            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | BAND, MHz<br>>35dB                                    | PASS-<br>BAND<br>VSWR                  | PRICE<br>\$<br>Qty.                                |

|----------------------------------------------------|--------------------------------------|--------------------------------------------------------------|-------------------------------|----------------------------|---------------------------------------|-------------------------------------------------------|----------------------------------------|----------------------------------------------------|

| NO.                                                | FO                                   | F1-F2                                                        | F5                            | F6                         | F7                                    | F8-F9                                                 | Max.                                   | (1-9)                                              |

| PBP-10.7<br>PBP-21.4<br>PBP-30<br>PBP-60<br>PBP-70 | 10.7<br>21.4<br>30.0<br>60.0<br>70.0 | 9.5-11.5<br>19.2-23.6<br>27.0-33.0<br>55.0-67.0<br>63.0-77.0 | 7.5<br>15.5<br>22<br>44<br>51 | 15<br>29<br>40<br>79<br>94 | 0.6<br>3.0<br>3.2<br>4.6<br>6         | 50-1000<br>80-1000<br>99-1000<br>190-1000<br>193-1000 | 1.7<br>1.7<br>1.7<br>1.7<br>1.7<br>1.7 | 18.95<br>18.95<br>18.95<br>18.95<br>18.95<br>18.95 |

#### Mini-Circuits

**CIRCLE 154**

P.O. BOX 350166, Brooklyn, New York 11235-0003 (718) 934-4500 FAX (718) 332-4661 TELEX 6852844 or 620156 WE ACCEPT AMERICAN EXPRESS

HIGH PASS

NARROWBAND IF

#### TECHNOLOGY NEWSLETTER

SOFTWARE TACKLES RF By combining a harmonic-balance simulator and advanced graphics capabilities, a software package for RF engineers promises to drastically trim circuit DESIGNS UP TO 3 GHZ development time. The simulator portion, from EEsof Inc., Westlake Village, Calif., lets designers analyze, tune, and optimize many linear and nonlinear RF circuits operating at frequencies of 3 GHz and below. As with lower-frequency software, such as Spice, the jOMEGA harmonic-balance program offers frequency- and time-domain simulation to analyze and optimize waveform characteristics. It also provides frequency response for such circuits as amplifiers, mixers, and oscillators, as well as for interface and signal-distribution networks. The harmonic-balance algorithms work with a full range of RF models (lossy and dispersive transmission lines, for example) developed for frequency-domain simulators. Nonlinear tuning and optimization capabilities quickly find the best conditions for amplifier outputs, mixer-conversion losses, and oscillator output-spectral purity. Other features include schematic entry, multi-window simulation controls, engineering documentation, and an optional module for RF board-design layout and floor planning. With that option, users can view circuit layout while simulating a design. Circuit parasitics and potential layout problems can thus be eliminated earlier in the design stage. The jOMEGA software runs on popular OS/ 2 and Unix platforms. It's starting price is \$24,500. Contact Thomas Reeder, (818) 991-7530. DB

TECHNOLOGY DATABASE The first in a series of technology databases helps system designers approach their job from an international, market, and application-driven per-AIDS SYSTEM DESIGNERS spective. The Integrated Circuit Technology Database from Cypress Information Resources, Los Gatos, Calif., quickly gives designers about 100,000 IC offerings of over 350 IC companies for 500-plus applications. The application-structured database provides product selection and analysis with functional operation, electrical specifications, and product features for various VLSI chips. For example, a designer can enter in an application, such as data compression, and immediately retrieve a diverse selection of ICs. Or research and development, market, and vendor information, such as agreements, customer base, facilities, and sales could be examined. Addresses, fax numbers, and 800 numbers are listed for each company as well. The IC Technology Database, which costs \$295, includes diskettes, a printed version of "The IC Product & Market Guide," and an instruction manual. For more information, call (408) 354-4887. LM

SOFTWARE DEAL AIMS FOR Hewlett-Packard Co., Palo Alto, Calif., and Sun Microsystems Inc., Moun-tain View, Calif., have inked a joint software development agreement to COMMON ENVIRONMENT remove many application-interoperability barriers on different Unix workstation platforms. As a result, users will be able to seamlessly integrate data objects—text, graphics, and a spreadsheet block, for example-from systems made by different vendors on one or more networks. HP and Sun are targeting a common software environment to be made available through licensing. Initially, they've jointly defined an object-management specification—the object-management facility—and just proposed it as a common standard to the Object Management Group, a 108-member organization. The proposed standard employs object-management technology from HP and distributed computing technologies from both companies. In the next stage, both firms will work with standards bodies to promote interoperability of the HP network computing system and Sun's open network computing standards at the working protocol level. The ultimate objective is a common distributed application environment for Unix and other operating systems. Sunsoft Inc., Sun's new software subsidiary, will do the development work with HP. Contact Robert Frankenberg of HP at (408) 447-0905 and Edward Zander of SunSoft at (415) 336-6543. DB

IBM STRENGTHENS ITS Following up on its 7820 terminal adapter for the Integrated Services Digital Network (ISDN), IBM Corp., White Plains, N.Y., deepened its ISDN market SUPPORT FOR ISDN involvement with several additional products and services for its PS/2 workstations. The company's new ISDN Interface Coprocessor/2 Model 2 adapter card attaches to the ISDN Basic Rate Interface. The card, teamed with supporting IBM software, transmits full-duplex data at 64 kbits/s over each of the two information (B) channels, controlled by the 16-kbit/s control (D) channel. This processing speed is over six times faster than 9600-bit/s modems currently used with PS/2s. Up to four cards can be installed in a PS/2 workstation for ISDN connection to similarly equipped IBM systems using either the 7820 terminal adapter or the new 3174 ISDN Basic Rate Interface adapter. Four ports on the 3174 support up to eight

> ELECTRONIC DESIGN23 MARCH 14, 1991

# How to ge customs with

#### Custom IC Solutions

Need a custom IC? You'll bypass the usual red tape by working with an experienced custom IC partner like Silicon Systems.

Our 20 years of experience developing ICs for mass storage, communications and automotive applications means we can move quickly from your inspiration to a working custom prototype in no time.

And speed your custom IC into volume production. In our MSICs <sup>™</sup> (Mixed-Signal Integrated Circuits) world we combine high-performance analog and digital circuitry on a single chip and allow you to take full advantage of our state-of-the-art design systems. From there we will optimize the performance and integration of your design in CMOS, Bipolar or BiCMOS

# et through out any delays.

Enough said? Move to the front of the line and discuss your custom design requirements with a Silicon Systems representative. Or call us for literature package CUST-1.

> Circle 111 for Product Info Circle 112 for Career Info

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680 Ph 1-800-624-8999, ext.151 Fax (714) 669-8814 European Hdq. U.K. Ph (44) 79-881-2331 Fax (44) 79-881-2117

#### TECHNOLOGY NEWSLETTER

remote PS/2 ISDN workstations with no contention. Through dial-up connections, workstations equipped with these products will be able to access IBM applications and systems on the company's Information Network. Initially, network connections will be available in Boulder, Chicago, Dallas, Houston, Philadelphia, St. Louis, and Tampa. *ML*

SERVICE GROUP JUDGES SYSTEM PERFORMANCE A service called Performance Design and Debug (PDD) is now available to designers of complex electronic and computer-based systems. Typical users of PDD, from CAE Plus Inc., Austin, Texas, are electrical and computer engineers who evaluate system performance prior to implementing a new design or debugging performance problems in existing systems. CAE Plus uses validated and parameterized architectural models along with client-supplied data to identify performance attributes and bottlenecks. PDD features customized architectural models, model validation, analysis of simulation results, and architecture design recommendations. For more information, call (512) 338-0165. LM

**GRAPHICAL SOFTWARE DOES EMI MODELING** A new graphical spreadsheet accelerates modeling-data analysis by providing a visual approach to modeling EMI and posing "what-if" considerations. The graphical EMI modeling software (Gems), developed by Atkinson Engious sources, victims, and coupling paths that make up the overall EMI situation. Every interconnection and interrelation between the sources, victims, and coupling paths can then be visualized. Graphics window displays supply amplitude vs. frequency plots for input, model, and output for any cell in the spreadsheet. With the spreadsheet concept, each cell (item model) can be a simple model that's tied with other cells to form more complex models. Libraries of standard or configurable models can be created and stored for future reuse. Some examples of models include a crosstalk cell that calculates the amount of crosstalk from a culprit to a victim, while a source model figures the signal amplitudes and frequencies generated at a specific source. As each cell is added to the spreadsheet, the software checks the cell type to ensure that the input and output characteristics and units match the connecting cells. The Gems package runs on PC systems under Microsoft Windows 3.0 and sells for \$2950, with a package of 10 cell models adding another \$950. Contact Kenn Atkinson, (703) 347-5716. DB

**BOX CONNECTS UP TO 16** HARDWARE EMULATORS Today, engineers need multiple hardware emulators that validate ASIC designs in excess of 50,000 gates. Quickturn Systems Inc., Mountain View, Calif., recently introduced the RPM Interconnect Box (RIB) to ease the task of emulator interconnection. The RIB can function either as a connector and breadboard accessory to help interconnect up to 16 of the company's RPM emulators or as a breadboarding platform to assemble prototype systems and to interconnect to an RPM emulator. It can also connect emulated designs with target systems. As a breadboarding platform, the RIB lends a convenient target-system prototyping area for connection to an RPM emulator before the actual target system is available. Microprocessors, peripherals, RAM, and user-defined analog and digital circuits can be mounted on the RIB. The RIB is available now for \$2950. For more information, call (415) 967-3300. LM

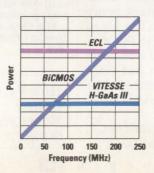

LARGEST BICMOS ARRAYS PACK 150,000 GATES is the largest in a family of seven from Texas Instruments Inc., Dallas. The abundant levels of interconnection allow array utilization to approach 75% in most applications. The sea-of-gates architecture is akin to the one reported at several previous conferences, with just a few minor adjustments. Compilers are available to custom-define memory blocks, data paths, and other functions. Unloaded gate delays are typically about 150 ps, while on-chip RAM blocks achieve 3-ns access times. TI will allow large customers to define a user-specific version that has RAM, ROM, or data-path sections prediffused into base silicon. Core logic on the biCMOS arrays (without the I/O buffers) consumes only about 10% more power than logic on a pure-CMOS array. From 80 to 320 signal pins are available, depending on the array. Package pin counts range from 100 to 240 leads when housing an array in a metal quad-sided flat package, and up to 409 pins for a pin-grid-array package. Contact Tom Sprunger at (214) 997-3156. DB

> 26 E L E C T R O N I C D E S I G N MARCH 14, 1991

### A NEW CONCEPT DC-DC CONVERTER MILIVARY GRADE

| Designed and Built for Reliability                                                                                                           |                              |                              |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|

| Rugged:<br>—Low Internal Temperatures<br>—Low Component Count<br>—Withstands 5000g<br>—Welded Hermetic Package<br>—Remote Shutdown and Sense |                              |                              |

| 28V to 5V, Single Output                                                                                                                     |                              | $\times$                     |

| Full Output Power for<br>$T_c = -55^{\circ}$ to 125 $^{\circ}$ (No Derating)                                                                 |                              |                              |

| Wide Continuous Supply Range                                                                                                                 |                              | 50                           |

| High Power Density 20W/in <sup>3</sup>                                                                                                       | emperat                      | 40                           |

| 000000                                                                                                                                       | unde (°C)                    | VIN (V)                      |

|                                                                                                                                              | APEX IS12                    | The Competition              |

| 000000                                                                                                                                       | Applications                 |                              |

|                                                                                                                                              | 28 volt 704D Designs         | Parallel Redundant Operation |

|                                                                                                                                              | Digital Circuit Power Supply | High Current, Low Voltage    |

| PATENT PENDING                                                                                                                               | Isolated Instrumentation     | Analog Circuits              |

|                                                                                                                                              |                              | ;/                           |

| APEXREL                                                                                                                                      | <b>JABILITY BY D</b>         | ESIGN                        |

To Place An Order Call 602-742-8601

For Applications Assistance Call **1-800-421-1865**

APEX MICROTECHNOLOGY CORPORATION

To receive your copy of our High Performance Amplifier Handbook please call toll free **1-800-448-1025**

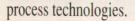

### The programmable display system: Design applications for land, sea or air.

Vivisun Series 2000, now the leading programmable display pushbutton system, interfaces the operator with the host computer. The user-friendly LED dot-matrix displays can display any graphics or alpha-numerics and are available in green, red or amber. They can efficiently guide the operator through any complex sequence with no errors and no wasted time.

They also simplify operator training as well as control panel design. One Vivisun Series 2000

programmable display system can do the work of 50 or more dedicated switches. In short, Vivisun Series 2000 gives the design engineer more control over the design.

Contact us today.

MENU

Vivisun Series 2000 programmable displays. The intelligent communications system.

# VIVISUN 2000

HYDRIC

#### TECHNOLOGY ADVANCES

#### U.S.-JAPAN DEVELOPMENTS ENHANCE DRAM PERFORMANCE AND PACKAGING

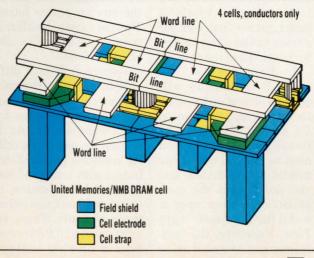

pair of joint U.S. and Japanese developments promise to improve dynamic-RAM density and performance, as well as revolutionize the way chip design is approached. In one development, a new field-shield-capacitor cell structure improves the densities and speeds of DRAMs, and simplifies their structures. In another development, a packaging technique called lead-on-chip with center bond (LOCCB) allows DRAM designers to put more silicon in the same package size. It also minimizes on-chip noise and improves DRAM lead electrical uniformity.

As dynamic RAMs increase in density, fabricating their storage cells gets more and more complex. with designers being forced to either stack lavers above the substrate or create trench structures in the substrate. A novel coaxial memory cell, created inside a trench, now promises to simplify the fabrication processes compared to other trench or stacked structures previously described by other companies. The cell was developed jointly by a small U.S.-based design consulting firm, United Memories Ltd., Colorado Springs, Colo., and NMB Semiconductor Ltd., Chiba, Japan.

Designers at United Memories in 1988 took a field-shield coaxial capacitor structure and implemented DRAM storage cells that provide sufficient capacitance for use in 4-, 16-, and possibly 64-Mbit-generation DRAMs. First prototypes of the structures for a 4-Mbit chip yield access times of 50 ns with a chip that fits in a 300-mil DIP.

The field-shield structure incorporates a polysilicon field-shield layer in the isolation or field-oxide region of the memory cell (see the United Memories/NMB figure). By holding the field-shield region over the p-well implants in the substrate at ground potential, n-channel parasitic devices can be shut off. The field-shield sections over n-well regions are kept at the supply level to shut off p-channel parasitic field devices.

Because the gates of both parasitic transistor types are actively held off, the devices' threshold voltages can be set for about 2 V. Standard devices made with local-oxide-isolation schemes require a 10-V isolation capability, which means larger spacings between devices. The lower voltage enables the fieldshield devices to be closer because isolation distances don't have to be as large. The field shield also precludes a field implant, simplifying the manufacturing flow.

Although the memory cell might be loosely classified as a "stacked-intrench" type structure, the field shield goes into the trench before the cell electrode. That shields the cell electrode and reduces cell leakage. The combined structure is known as a buried-electrode shieldedtrench (Best) cell.

Only two masking steps are required to build the Best capacitor, compared with the three to five masks typically needed for stacked capacitors. Moreover, only two etch steps are needed (one is a trenchformation etch). By comparison, a stacked-capacitor structure requires three to five etch steps (but no trench etch).

Because the field shield goes into the trench before the cell electrode and is separated from the substrate by a grown oxide, the trench's sidewalls and bottom serve as isolation areas. Consequently,

ELECTRONIC DESIGN 29 MARCH 14, 1991

there's no need to dope the sidewalls of the trench, as might be required in a typical trench process.

The counter-electrode of the DRAM cell capacitor serves as the field shield. This shield encloses the cell's capacitor electrode. preventing any cell-to-cell or cell-to-substrate coupling. That reduces any pattern sensitivity of the memory array. Furthermore, because the cell's capacitor electrode is shielded from the substrate by the field shield, trenches can be located adjacent to the wordline transistor without affecting the wordline-transistor characteristics.

A high resistivity p-type substrate and shallow p well help fabricate n-channel transistors with lowbody effects and low source/drain-to-substrate capacitance.

The low-body effect lets more of the charge reach the memory cell during a write operation. That eliminates the need to boost or bootstrap the wordline, simplifying memory circuit design and reducing chip operating power.

One key issue during coaxial-cell fabrication is the need for a highly selective polysilicon etching process, so that the polysilicon can be removed without affecting the oxide layer. An etch ratio of about 15:1 is needed, and that ratio can be achieved on a repeatable basis with today's processing equipment.

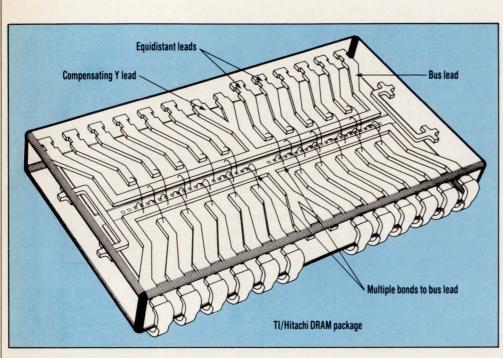

In a related area of DRAM development, wideranging implications can be seen with the recent packaging innovations from Texas Instruments, Dallas, and Hitachi America Ltd., Brisbane, Calif., in

#### TECHNOLOGY ADVANCES

their forthcoming 16-Mbit DRAM. The new package involves bond pads running in parallel rows down the chip's center rather than around its edges. The chip is then wire-bonded to a leadframe that extends over the top of the chip.

For a 16-Mbit DRAM, the effect is to create a very stable ground with multiple bonds to the chip. But the leadframe technique carries great promise for future memories, plus other technologies involving large die and high speeds, such as ASICs and linear ICs. It also may change the way designers approach chip design and layout: Traditional approaches, with bond pads around the chip's perimeter and a third layer of metal for grounds, may be passe.

According to Ken Pope, manager of product marketing for Hitachi America, the LOCCB packaging technology will shine brightest when it's applied to memory devices handling such wide words as by-16 and by-18 parts. The multiple outputs required by such chips can benefit greatly from the stable ground offered by the LOCCB technique.

In addition, the technique allows bond pads to be placed where it's most convenient for the design's sake and not for bonding machines. It also saves the complexity and expense of a third or fourth layer of metal to achieve the highest possible speed. In a high-speed static RAM, for example, a block of memory cells that's perhaps 512kbits deep can have its own I/O bonding pad right in its midst, rather than routing a trace to the other side or to the middle of the chip.

In Pope's view, the LOCCB technique will soon be picked up by other technologies. "It's ideal for devices like ASICs or linear parts, where you need to get I/O out of the middle of the device, and you don't want the complexity of another layer of metal for the speed," says Pope. Moreover, the leadframes can be tooled using

**30 E L E C T R O N I C** MARCH 14, 1991

standard CAD tools for ICs with irregular structures.

The packaging technique is the first result to be disclosed from the total 16-Mbit DRAM development project the two companies launched in December, 1988. The memory's plastic SOJ package houses chips as large as 330 by 660 mils, conforms to JEDEC standards of 400 by 725 mils, and has dualpower (V<sub>CC</sub>) and ground (V<sub>SS</sub>) pins. The lead-on-chip package also offers a very area-efficient chip design by minimizing the size of the on-chip power buses. The package's leadframe routes power above the chip's surface.

Voltage drops and difficult-to-manage thermal and mechanical stresses are foremost concerns for both companies. As it stands, the package exhibits low-noise power distribution with a drop of less than 0.2 V, resistance of less than 10 m $\Omega$ , and inductance of 6 nH. These results mean a 10-fold reduction in on-chip voltage

DESIGN

spikes compared with conventional plastic SOJ packages, which have  $20\text{-m}\Omega$  resistances and 10-to-20-nH inductances in the on-chip power buses.

At the heart of the LOCCB design is its balanced-capacitance leadframe that maintains uniform input-pin capacitance. All internal leads are equidistant from each other. A passive Y lead in the middle of the leadframe, and on either side, minimizes differences in pin-to-pin capacitance (see the TI/Hitachi figure).

Two metal bus lines run parallel above the full length of the chip. One links the dual V<sub>SS</sub> pins located at the ends of the package, while the other links the corner dual  $V_{CC}$ pins on the other side of the chip. As a result, multiple bonds exist from the power and ground pins to the circuit. With dual pins for each bus, resistance is slashed to under  $10 \text{ m}\Omega$ , effective inductance to about 6nH, and electrical noise to less than 0.2 V.

Later iterations of the 16-Mbit DRAM will involve smaller die, and the leadframe will shrink accordingly. But rather than going to fewer pins, which would take the part out of JEDEC standards, the developers may widen some traces to improve speed as they work toward wideword memories. Another advantage of the LOCCB technique is that because the bond pads aren't on the chip's periphery, designers gain some space on the die for circuitry. That means more than one generation of die could be squeezed into a same-size package.

DAVE BURSKY and DAVID MALINIAK

## **Count On IDT**

#### The R3001 RISController™: The Embedded Processing Solution

The R3001 is the first derivative of the R3000 processor designed specifically for embedded control applications. Compared to the Intel 960 and AMD 29K processors, the R3001 is the most cost-effective solution for these applications—we have the data to prove it! Call and ask for KIT CODE 0091A to get an R3001 Performance Comparison Report.

#### BiCEMOS<sup>™</sup> ECL SRAMs: Technology for the '90s

Design the fastest systems with IDT's BiCEMOS ECL family. At 7ns, the IDT10494 is the fastest BiCMOS 64K ECL SRAM in production. 256K and synchronous self-timed SRAMs are also available in 10K/100K/101K configurations. Call and ask for KIT CODE 0091B to get a copy of the BiCEMOS ECL Product Information booklet.

#### FCT-T Logic: Fastest Speed/ Lowest Ground Bounce

DT's FCT-T Logic Family is the fastest logic family available and has the lowest ground bounce—up to 40% less than previous FCT devices! The FCT-T family provides direct TTL logic compatibility and is available in FCT, FCT-AT, and FCT-CT speeds. Call today for **KIT CODE 0091C** and get a copy of the **High-Speed CMOS Logic Design Guide**.

#### The SyncFIFO<sup>™</sup> Family: Double Your FIFO Performance

SyncFIFOs offer leading-edge performance that is 50% faster than other FIFOs. The synchronous architecture is easy to implement and reduces chip count 9-to-1. SyncFIFOs have 18-bit buses and are ideal for 32bit systems. Ask for **KIT CODE** 0091D to get AN-60: Designing with the IDT SyncFIFO<sup>™</sup>.

#### IDT Subsystem Modules: Building Blocks for the '90s

DT offers a complete line of board-level subsystem products, including cache memory, shared-port memory, writable control store, RISC CPU, high integration modules, and custom designs for specific applications. Call today for **KIT CODE 0091E** and receive technical data and *a free IDT puzzle*!

#### 12ns Cache Tag SRAMs: Wait No Longer

RISController, BiCEMOS, and SyncFIFO are trademarks of Integrated Device Technology. In The IDT logo is a registered trademark of Integrated Device Technology, Inc.

Contact us today to receive data sheets and other design information on IDT's products.

(800) 345-7015 FAX: 408-492-8454

3236 Scott Boulevard, P.O. Box 58015, Santa Clara, CA 95052-8015

When cost-effective performance counts

Integrated Device Technology, Inc.

# Making

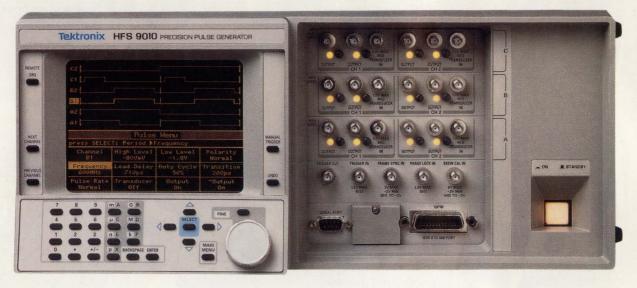

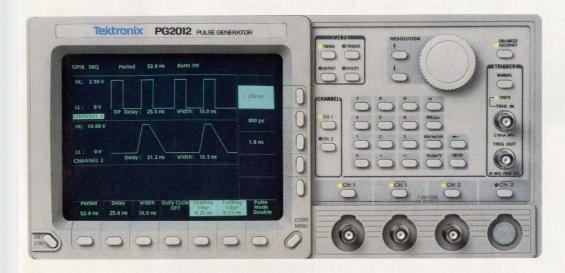

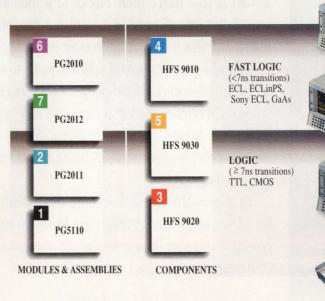

You're looking at the biggest news in signal sources in years: two new families of pulse generators from Tektronix.

You can already see one reason why Tek's new pulse generators are stirring up so much interest: their what-yousee-is-what-you-get user interface vastly simplifies your life.

Now you can stop piecing the big picture together from one-line LEDs, blinking error lights and trial-anderror iteration. Tek's new scope-like display lets you set up and modify a whole set of parameters at once, with a true representation of your pulses and instant, visual feedback.

You name your application and logic technology: Tek has a signal source to match. For the first time, you can choose channel capacities from one to *six* channels, or rep rates from 50 MHz to a remarkable 600 MHz. Choose tools designed for logic, fast logic, or *mixed* technologies. Vary transition times from 200 ps to 10 ms. Test complex timing relationships with ease.

Add to all this our popular pulse generator plug-ins from Tek TM500/

# Waves.

5000 modular instrumentation, and you can see why we're making waves!

Easier to use, more precise and more expandable, Tek's new pulse generators are doing for signal sources what DSOs have done for measurements.

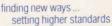

Contact your Tek sales office for a demonstration, or call for more information.