1 1621 1921 1921 192

the first of the death of the de

APRIL 2, 1992

QUICHION

FOR ENGINEERS AND ENGINEERING MANAGERS--WORLDWIDE

# MULTIMEDIA CHIP SET HANDLES ANA PROTOCOL

A PENTON PUBLICATION U.S. \$10.00

#### SPECIAL REPU HIGH-SPEED STATIC RAMS

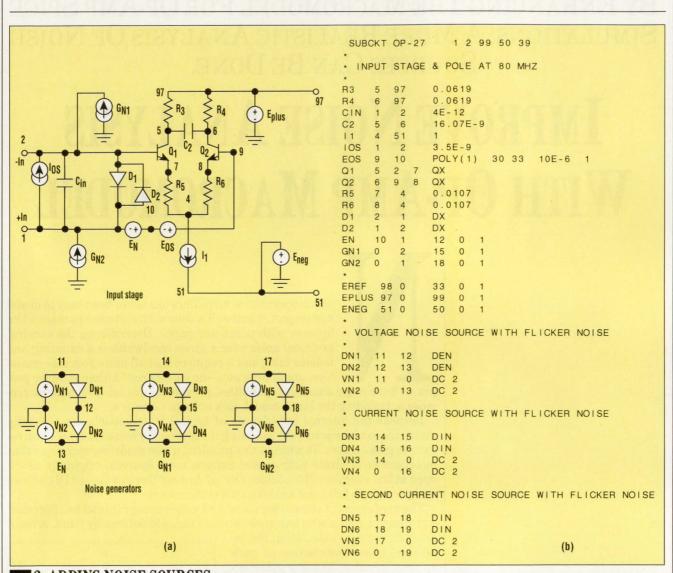

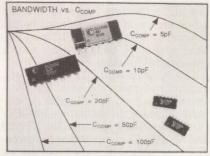

MODELING OP-AMP NOISE WITH SPICE

IC DACS HOLD PROGRAMMABLE COMPARATORS

### Our GAL22V10-7 is Super Fast.

At 7.5ns, Lattice provides the world's fastest field-programmable 22V10. Based on our high-performance  $E^2CMOS^{\mbox{\tiny $\mathbb{R}$}}$  technology, the **GAL22V10-7** combines 111 MHz  $F_{max}$  with extremely low power consumption. It even supports industry standard loads and pinouts. What's more, it's 100% tested to guarantee perfect programming yields, less board rework and fewer system failures.

For free samples and a GAL<sup>®</sup> Data Book, call **1-800-FASTGAL** and ask for information packet 107.

Leader in E<sup>2</sup>CMOS PLDs.

Lattice Semiconductor Corp. 5555 Northeast Moore Court Hillsboro, Oregon 97124

Copyright  ${\rm (III)}$  1992, Lattice Semiconductor Corporation.  ${\rm E}^2 CMOS$  and GAL are registered trademarks of Lattice Semiconductor Corporation.

### HP's 50 MBd Plastic Fiber-Optic Data Links. Anything else would be twisted.

Our new data links are so fast and cost-effective, it would be crazy to stick with twisted pair.

Sure, optical fiber is immune to noise, but who can afford it? With HP's new high-speed plastic fiber links, the answer is anyone.

That's because our new links rely on plastic optical fiber cable which keeps costs way below glass fiber, while offering far greater voltage isolation and noise immunity than twisted pair wire.

#### A quick turn for the best.

With data rates soaring to 50 MBd, HP's plastic fiber links offer the fastest solution for designing computer, telecommunications, or industrial applications. So you can avoid bottlenecks, and design in data multiplexing.

#### Perfectly flexible.

You can choose interlocking horizontal or vertical mounts for greater mechanical design flexibility. The analog in/out provides the electrical design flexibility you need to meet your cost and performance goals.

#### The whole ball of wax.

What's more, as the largest optoelectronic supplier in the U.S., HP offers you the industry's most complete package of products and support services. To find out more about HP's 50 MBd Plastic Fiber-Optic Data Links, call **1 (800) 752-0900, ext. 2948** in the U.S.\* You'd be crazy not to.

There is a better way.

\*In Europe, FAX to: (49) 7031-14-1750.

# Soon, Eight Ho Computing Will

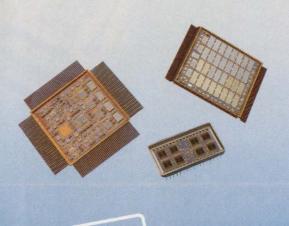

(actual size)

#### AMD Introduces The World's First 386 Microprocessor With 3-Volt Technology.

Two standard dry-cell batteries. There's really nothing special about them. Aside from the fact that they can run a powerful, portable 386 computer for a full eight hours. Provided, of course, that portable is built around a low-voltage Am386<sup>™</sup> microprocessor.

Thanks to the low-voltage Am386 microprocessors, laptop, palmtop and notebook computer designs will become smaller, lighter,

THE PARAMETERS IN THE PARAMETERS INTERS INTERS

The 25MHz DXLV and the 25MHz SXLV are available in PQFP packaging.

and more powerful than ever before. With battery life of up to eight hours or more. That's a full day's worth of 386 performance—the per-

901 Thompson Place, PO. Box 3453, Sunnyvale, CA 94088 @ 1991 Advanced Micro Devices, Inc. "We're Not Your Competition" is a service mark and Am 386 is a trademark of Advanced Micro Devices. Inc

# urs Of Portable Look Like This.

formance you need to run sophisticated applications like Windows™3.0.

And rest assured, the low-voltage Am386 microprocessors are proven compatible and comply fully with JEDEC standards for low-power, 3-volt computing. We can even supply you with the 3-volt EPROMs your systems will need. Other 3-volt system logic is also readily available.

For more information on the low-voltage

Am386 microprocessors call AMD today at **1-800-222-9323**. You'll never look at dry-cell batteries the same way again.

All brand or product names mentioned are trademarks or registered trademarks of their respective holders. DURACELL is a registered trademark of Duracell International. Inc.

CIRCLE 80 FOR U.S. RESPONSE

CIRCLE 81 FOR RESPONSE OUTSIDE THE U.S.

#### **14 EDITORIAL**

#### **18 TECHNOLOGY BRIEFING**

TAB positions itself for growth

#### **23 TECHNOLOGY NEWSLETTER**

• High-speed 3.3-V logic operates down to 1.2 V

• 64-bit RISC CPU IC to spearhead workstations

• Holland hosts analog-circuit workshop

- PC buyers get lifetime warranties, discounts

- Mixed-signal arrays hold 12-GHz npns

- Gyroscope-based PC pointer goes wireless

- RAMBUS-DRAM socket looms on the horizon

- Transceiver targets wireless networks

#### **33 TECHNOLOGY ADVANCES**

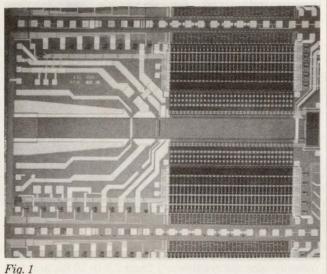

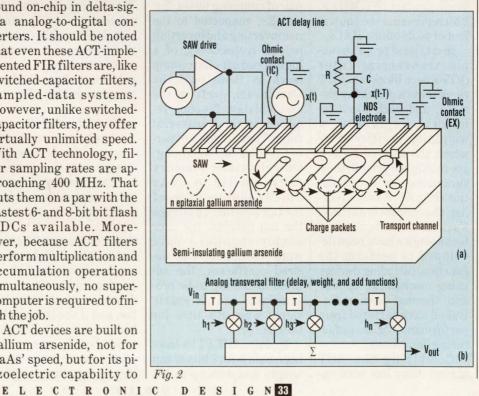

• SAW, ACT technologies combine to produce 50 billion multiply-accumulate/second ICs

• MCM conference stresses systemlevel design

#### **83 IDEAS FOR DESIGN**

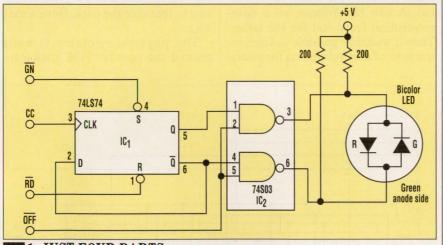

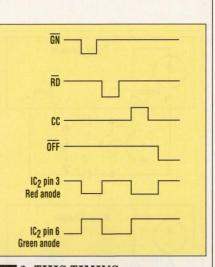

• Get three colors from a bicolor LED

- Precisely check low resistances

- Transfer data from a DMM to a PC

Jesse H. Neal Editorial Achievement Awards: 1967 First Place Award 1968 First Place Award 1972 Certificate of Merit 1975 Two Certificates of Merit 1976 Certificate of Merit 1980 Certificate of Merit 1980 Certificate of Merit 1989 Certificate of Merit 1989 Certificate of Merit

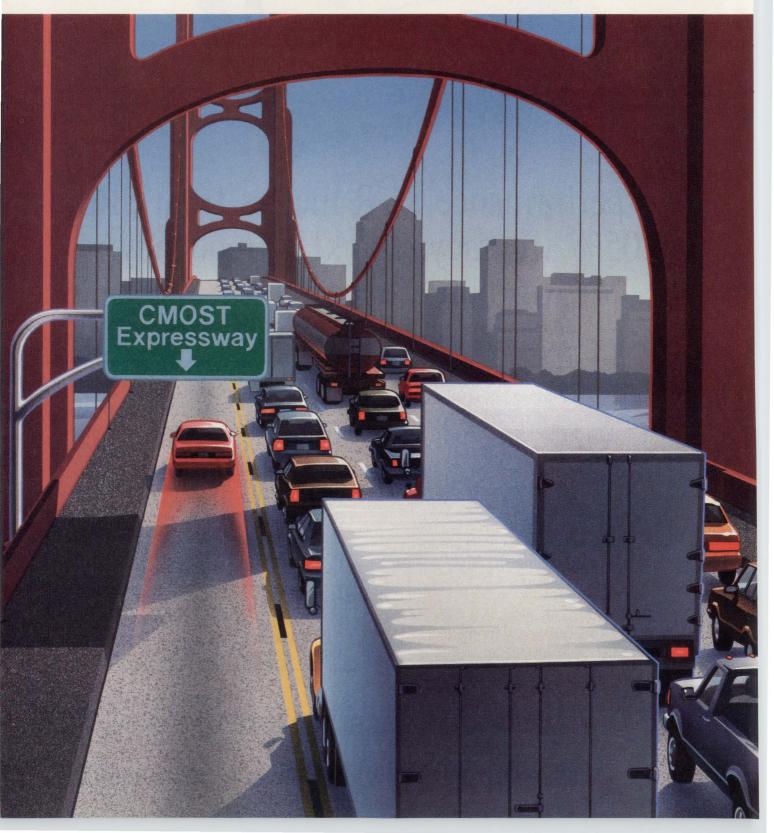

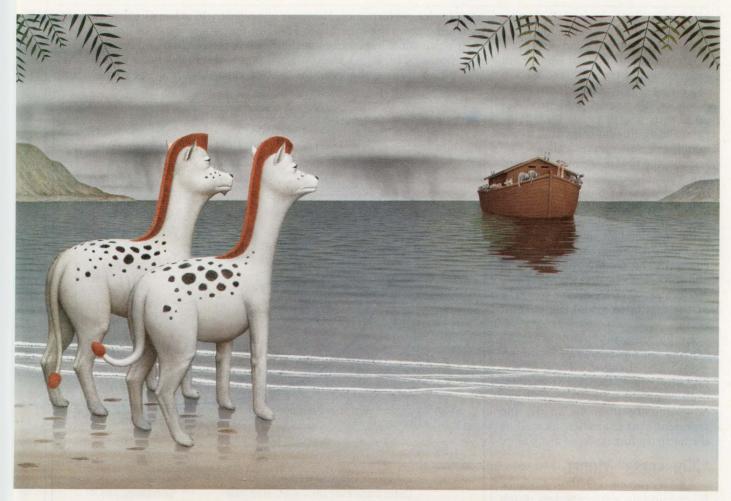

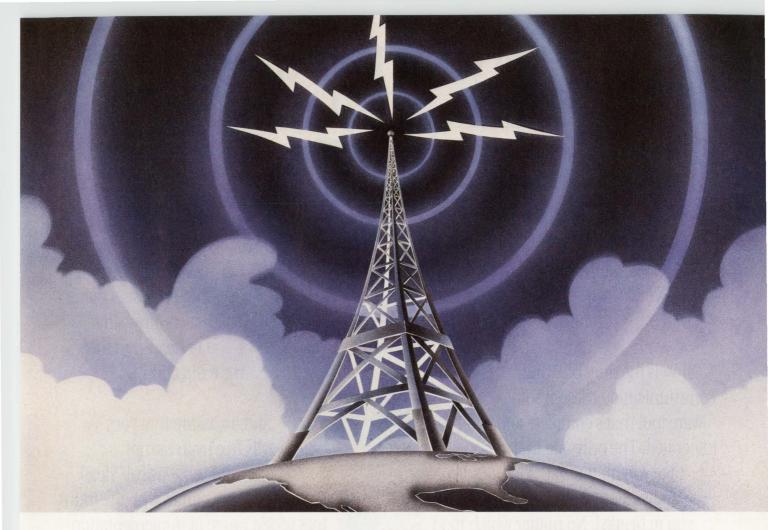

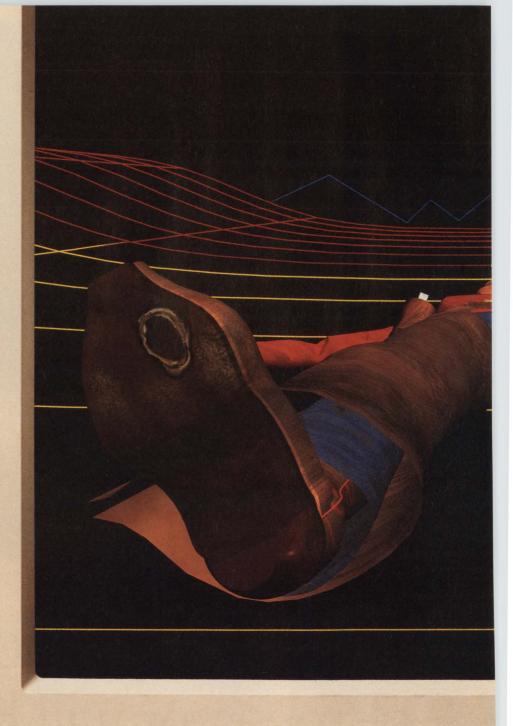

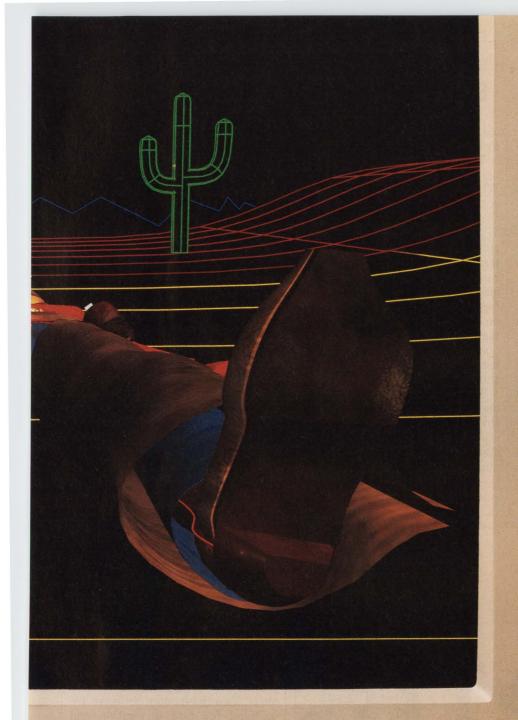

Cover Illustration: Robert G. Alcorn

#### **89 QUICK LOOK**

- First annual concurrent engineering award at Test & Design Expo

- First-of-a-kind products: Will AT&T's picture phone hit a grand slam?

- Engineering investors and mutual funds

- Which technical books are the most popular in Silicon Valley?

**95 PEASE PORRIDGE** What's all this calculator stuff, anyhow?

#### **NEW PRODUCTS**

114 Digital ICs

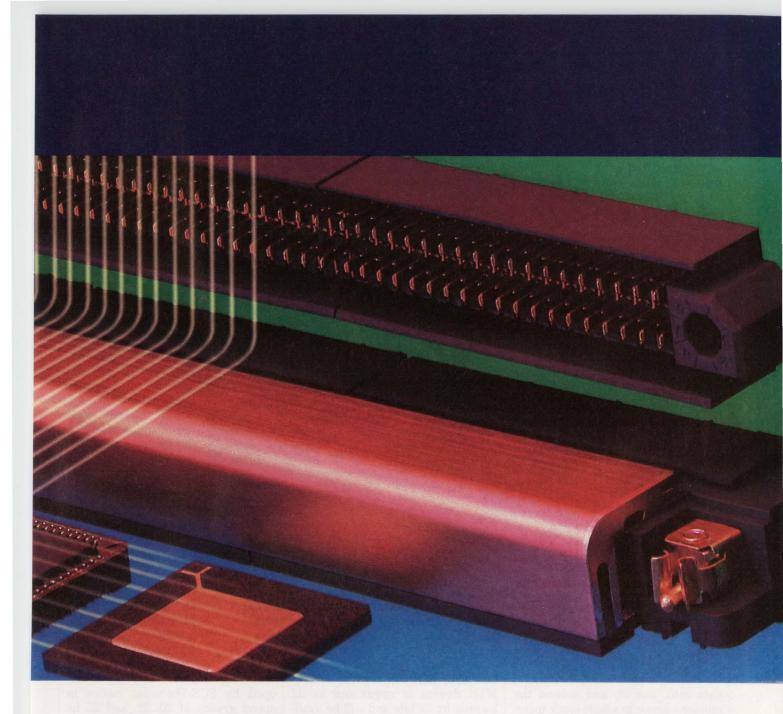

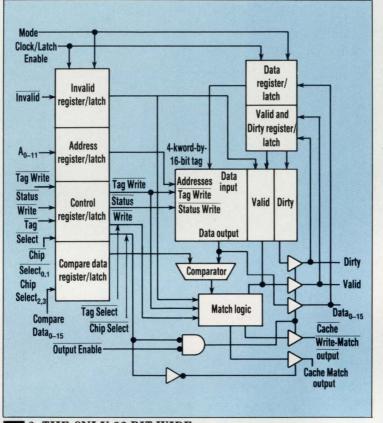

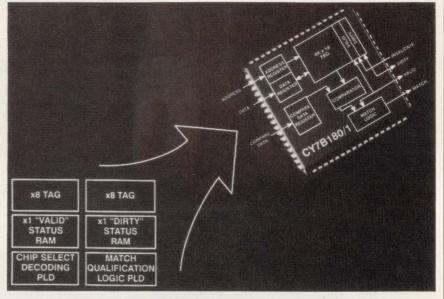

Highly integrated cache-tag RAMs perform matches in 12 ns

119 Analog

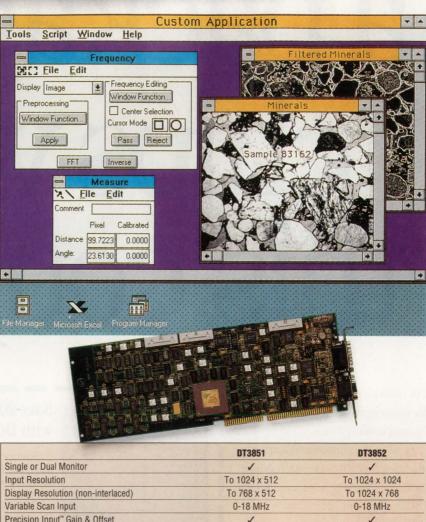

**121 Instruments**

123 Packaging & Production

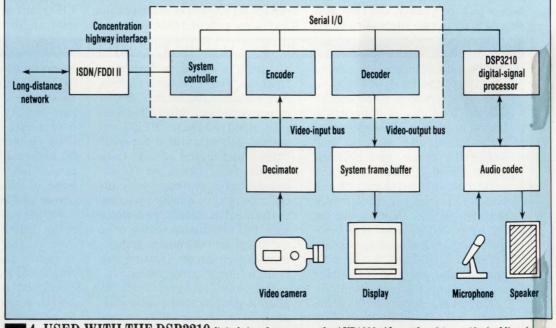

124 Communications Development kit simplifies multimedia design effort

126 Power

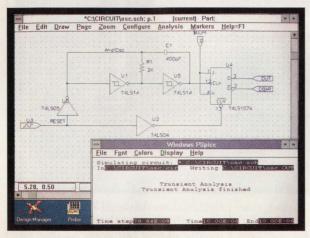

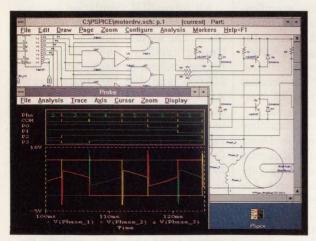

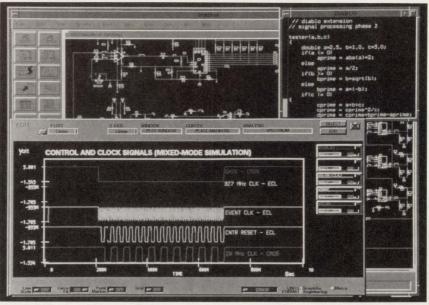

128 Computer-Aided Engineering Analog behavioral modeling, VHDL support embellish broad EDA software line

#### **135 INDEX OF ADVERTISERS**

#### **137 READER SERVICE CARD**

#### **COMING NEXT ISSUE**

• Special Report: Digital audio's impact on high-resolution DACs

• How to extend voltage-reference options with op amps

- First details on a switching-regulator IC for laptop PCs

- Special Section: Designing PC systems

• Evaluating the communications performance of next-generation boards

• Implementing new graphics standards for local buses

• Review of new products for personal computers

• A new family of high-performance CMOS op amps

• PLUS: Ideas for Design Pease Porridge Technology Advances Quick Look

ELECTRONIC DESIGN (USPS 172-080; ISSN 0013-4872) is published semi monthly except for 3 issues in May and 3 issues in November by Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543. Paid rates for a one year subscription are as follows: 895 U.S., 8175 Canada, 8255 International. Second-class postage paid at Cleveland, OH, and additional mailing offices. Editorial and advertising addresses: ELECTRONIC DESIGN, 611 Route #46 West, Hasbrouck Heights, NJ 07604. Telephone (201) 393-6060. Facsimile (201) 393-0204.

Printed in U.S.A. Title registered in U.S. Patent Office. Copyright © 1992 by Penton Publishing Inc. All rights reserved. The contents of this publication may not be reproduced in whole or in part without the consent of the copyright owner.

tion may not be reproduced in whole or in part without the consent of the copyright owner. Permission is granted to users registered with the Copyright Clearance Center Inc. (CCC) to photocopy any article, with the exception of those for which separate copyright ownership is indicated on the first page of the article, provided that a base fee of \$1 per copy of the article plus \$.50 per page is paid directly to the CCC, 27 Congress St., Salem, MA 01970 (Code No. 0013-4872/92 \$1.00 + .50). (Can. GST # R126431964) Copying done for other than personal or internal reference use without the express permission of Penton Publishing, Inc. is prohibited. Requests for special permission or bulk orders should be addressed to the editor.

For subscriber change of address and subscription inquiries, call (216) 696-7000. POSTMASTER: Please send change of address

POSTMASTER: Please send change of address to ELECTRONIC DESIGN, Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543.

ELECTRONIC DESIGN APRIL 2, 1992

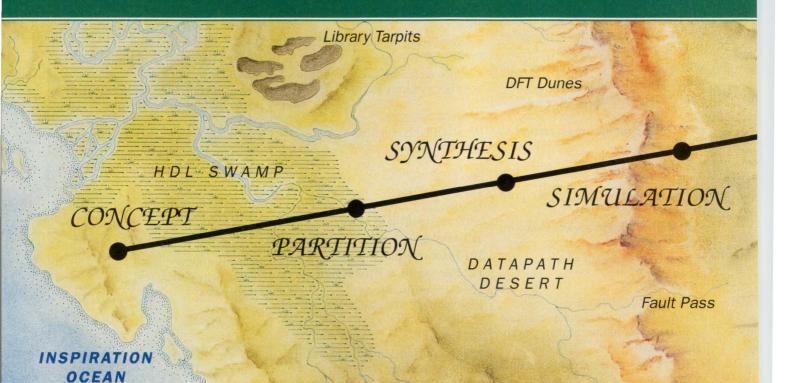

### NAVIGATE THE PERILS OF TOP-DOWN DESIGN.

No one ever said

the road to top-down ASIC design was easy. Along the

way, there are all sorts of obstacles that can get you off track – and into trouble. More than one designer has gotten bogged down in the swamp of HDL programming, lost in the

datapath desert, or tangled up in the timing jungle. And that's not even the half of it. To navigate the journey from first concept to first silicon, you need a few things. Like a reliable map. A guide who's already been down the road to top-down

design. And the right tools to keep you on the path through the ASIC wilderness.

COMPASS<sup>®</sup>

Design Automation gives you all that and more. Front end to back, our tools integrate every aspect of ASIC product development. A truly integrated top-down ASIC solution that's already been tested in

Spice Peak

thousands of successful designs.

Our Navigator<sup>™</sup> Series provides an integrated graphical design specification and synthesis environment that guides you past the swamp of HDL programming.

It generates behavioral VHDL and analyzes your partitioning to match your system requirements - up front. It synthesizes manufacturing and diagnostic test structures.

And it provides you with sophisticated floorplanning software and interactive place-and-route tools.

The result is more predictable performance, greater design control, and the ability to compare structural and behavioral models. All of

CIRCLE 94 FOR U.S. RESPONSE

which translates into faster time to market, lower production costs and a quality product. Also ask us about our library

support for: • VLSI Technology

- Fujitsu

- LSI Logic

- Motorola

- NCR

- SMOS • Toshiba

- Xilinx

Call us now at 800-433-4880, and let COMPASS be your guide.

COM Design Automation

1865 Lundy Avenue San Jose, CA 95131 ©1992 COMPASS Design Automation, Inc. COMPASS and the COMPASS logo are registered trademarks of COMPASS Design Automation, Inc. Navigator is a trademark of COMPASS Design Automation, Inc.

CIRCLE OF DO

Clock-tree Forest

SILICON

AS FEATUR

IDEA - / CICC - I DAC - Ju

SYST

SEA

VERIFICATION

POST

ROUTE CRATER

LAYOUT

River

Routability

EDIF Falls

Critical Path

Creek

NETLIST

FLOORPLAN

TIMING JUNGLE

Test Plateau

CANYON

Marketing Communications Manager: Clifford Meth

Reprints: Helen Ryan 1-800-835-7746

Group Art Director: Peter K. Jeziorski

Published by Penton Publishing Vice President-Editorial: Perry Pascarella

PONSE OUTSIDE THE U.S. Publisher: Paul C. Mazzacano

BELECTRONIC DESIGN

APRIL 2, 1992

1

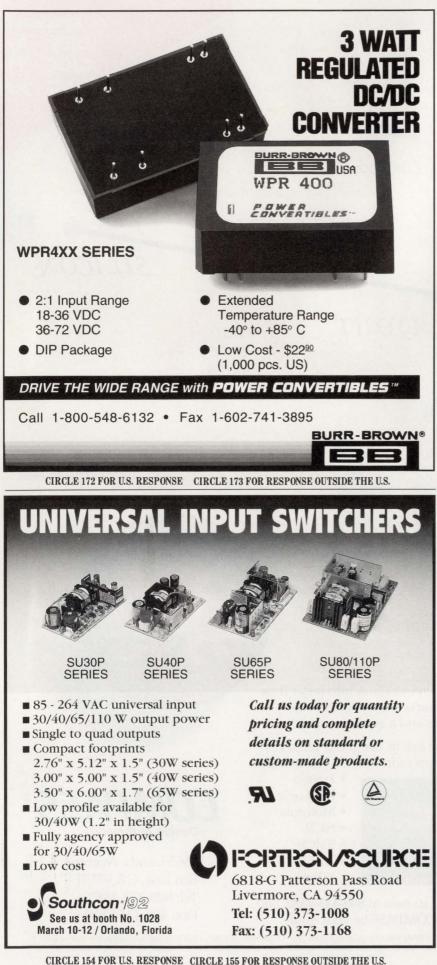

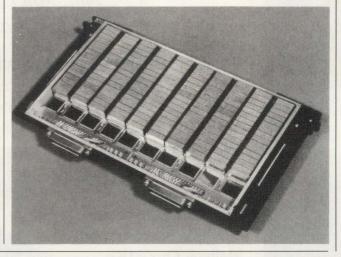

# Synchronous SRAMs

REDUCED BOARD SPACE

#### EASE OF DESIGN

# Make your next move on time

You're ready to make your next strategic design move. So make it on time with Micron Synchronous SRAMs.

Micron Synchronous SRAMs reduce the logic required with commodity SRAM solutions — simplifying your system designs and greatly reducing propagation delays. Plus you'll speed-up cycle times, reduce power consumption and decrease board space more than the commodity-plus-logic solution. All in one move.

We've also made your move to synchronous easier by offering on-board data latches, dual chip enables and a variety of different packages including PQFP. So whether you design high-performance systems, cache subsystems, DSP or systems requiring wide SRAMs, make the smart move and call Micron at 208-368-3900. And see why the time is right to move to synchronous.

Micron. Technology that works for you.

| Memory<br>Configuration | Part<br>Number | Access<br>Time       | Output Enable<br>Access Time | Package                 |

|-------------------------|----------------|----------------------|------------------------------|-------------------------|

| 16K x 16                | MT58C1616**    | 13,15,17,<br>20,25ns | 5,6,7,8,10ns                 | 52-pin PLCC<br>and PQFP |

| 16K x 18                | MT58C1618**    | 13,15,17,<br>20,25ns | 5,6,7,8,10ns                 | 52-pin PLCC<br>and PQFP |

| 128K x 9                | MT58C1289      | 16.6,20ns            | *                            | 32-pin SOJ              |

\* Output Enable is a synchronous signal on the 128K x

\*\*\*\*\*\*\*\*\*\*\*\*\*

2805 E. Columbia Rd., Boise, ID 83706 (208) 368-3900

Customer Comment Lines: U.S. 800-932-4992; Intl: 01-208-368-3410

CIRCLE 170 FOR U.S. RESPONSE © 1991 Micron Technology, Inc. CIRCLE 171 FOR RESPONSE OUTSIDE THE U.S.

# Very Special Be#1 In EPROMs.

AMD EPROMs today are what other mere mortal EPROMs can only aspire to be: high density, of course. But also high speed. Able to store massive amounts of information, with lightning fast access times. All in our superior CMOS technology.

EPROMs have always been our strength—thanks to our unparalleled performance, selection, reliability, and quality.

That's why we sell more EPROMs than any other vendor.\* Period. And we're ready to do the same for years to come. While other vendors have abandoned EPROMs, we're still committed to making the fastest, highest density EPROMs.

In fact, we've got the most advanced EPROM wafer fab, assembly and test facilities in the world. Which produce the most reliable, highest quality EPROMs available. In everything from surface mount plastic to mil spec compliant packages.

So make yourself a hero. The instant you know your EPROM requirements, get them fast. Get them dense. Get them in volume. And get them right away.

Call AMD at **1-800-222-9323** for more information. Or call your local sales office to place an order.

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088 © 1991 Advanced Micro Devices, Inc. All brand or product names mentioned are trademarks or registered trademarks of their respective holders. \*Dataouest, March 1991, based on 1990 data

# While you've been pushing the limits of digital devices,

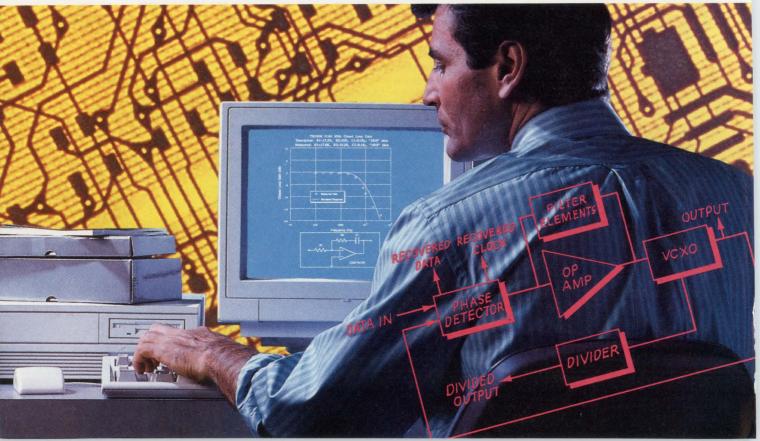

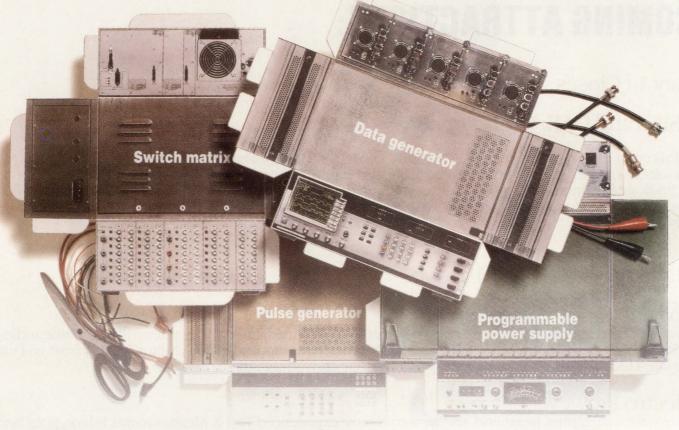

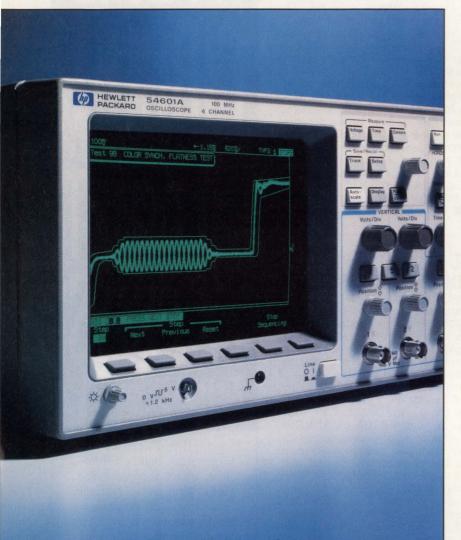

HP's specially designed per-pin architecture makes high-performance testing an economic reality.

The HP 83000 Model F660 Digital Test System uses specially designed multi-chip modules to give you the performance you need to fully characterize designs on anything from GaAs to CMOS. With 50 ps accuracy. Speeds to 660 MHz. And up to 1024 chan-

The HP 83000 Digital Test System for both engineering and production applications. nels with true tester-per-pin architecture.

CAE links, automatic test functions, and software tools make test set up fast and characterization thorough. And there's one PMU for every 16 channels, for faster dc testing and greater throughput.

Yet, the HP 83000's highly integrated, modular electronics bring you all this performance at a cost that's less than tradi-

## we've been pushing the limits of testing.

© 1992 Hewlett-Packard Co. TMBID136/ED

tional ATE systems. And since they make the footprint smaller and upgrading easier, cost of ownership is lower, too. In fact, every technical aspect of the HP 83000 system was designed with the best combination of performance and cost efficiency in mind.

So, if you're pushing the performance of digital devices, call 1-800-452-4844\*. Ask for Ext. 2898, and we'll send you infor-

mation that explains how the HP 83000 lets you test them to their limits.

There is a better way.

\* In Canada call 1-800-387-3867, Dept. 432.

#### EDITORIAL

# LON<sup>TM</sup> or LINC<sup>TM</sup> ?

Now that engineers have investigated LON technology, many are coming back to the original LINC (the CY233 Local Intelligent Network Controller), or are discovering the CY233 chip for the first time.

With CY233s, one IBM-PC COM port can address up to 2048 TTL I/O lines. Try this with LON!

- The CY233 instruction set and features are fully documented. Try getting this info for LON.

- The CY233 does <u>not</u> require a \$17,995.00 development system! You can start for \$17.95 plus any RS232 port computer.

- No CY233 royalties or licenses required. Be sure to check out LON terms and conditions.

- Learn 7 LON levels or 1 easy LINC level.

- Easy CY233 interface to 8051 and similar microcontrollers.

- The CY233 is in stock now.

Discouraged by \$17,995.00 to start using LON? If you need a network, but LON is overkill, **try these introductory offers!** Get started with the CYB233 prototyping kit with an onboard CY233 and wirewrap area, ready to assemble, for only \$179.95, or try our introductory chip offer of 2 CY233s for only \$17.95 each.

#### Call 415-726-3000 today or Fax 415-726-3003 for info. Say LON sent you, and get these

great introductory prices! Credit Cards OK!

The CMOS CY233 operates at speeds up to 57,600 baud and is available from stock in a 40-pin DIP. (44-pin PLCC or Quad Flat Pak available in 1000s.)

#### **Cybernetic Micro Systems**

PO Box 3000 San Gregorio CA 94074 Tel: 415-726-3000 Fax: 415-726-3003

LON is a trademark of Echelon Corp. CY233-Linc is a trademark of Cybernetic Micro Sys. Limit one of each introductory offer per customer.

CIRCLE 150 FOR U.S. RESPONSE CIRCLE 151 FOR RESPONSE OUTSIDE THE U.S.

## **BLAME IT ON...THE MOON?**

as anyone ever considered the possibility that holes in the ozone layer are exposing us not only to more intense ultraviolet radiation from the sun, but also to more intense illumination from the full moon? How else can anyone explain the recent rash of lunacies that we see all around us?

Case in point no. 1: The average salary of major-league baseball players now is about one million dollars per year. However, ballplayers aren't alone in that income bracket. They're in a class with many executives of in-the-red corporations, whose boards of directors seem to be much less demanding of performance excellence than baseball managers. For one group, only teammates and fans get hurt when the manager makes a bad decision, while the other has thousands of other people's jobs riding on his or her decisions.

Case in point no. 2: In a New York Times article about the shrinking number of jobs for physicists in the U.S., IEEE president-elect Merrill W. Buckley draws fire for his remarks on the immigration of foreign engineers in times of high unemployment. This view is disputed by a professor of physics who says, "Without the foreign physicists who came to the United States during this century, American science would have been in a sorry state." That may have been true earlier in this century. But today, the knowledge and talent of many trained American engineers and physicists are wasted in menial technical jobs, if they have jobs at all. Companies, for whatever reason, no longer invest in research and development as they once did, surrendering the future for shortterm budget gains today. And still, universities beat the drums for more students, with claims of a looming shortage of engineers and scientists.

Case in point no. 3: The House of Representatives turns out to be a club for rubber-check writers. According to our Constitution, the House is the source of any bill that raises revenue, and now it becomes clear why the federal government always operates under a deficit. And these people are the same ones who waited until the middle of the night, when bill-paying, hard-working citizens (those who still had their jobs) were sleeping, to vote themselves a raise. Once again, Walt Kelly's Pogo is proven right: "We have met the enemy and he is us."

Case in point no. 4: Politicians continue to jump aboard the trade protectionist bandwagon, instead of coming up with programs that would help U.S. manufacturers compete in today's and tomorrow's global marketplace. That's the best way to assure that voters will have jobs in the future. International competition is going to intensify in the coming years, and only the quality producers – and their workers' jobs – will

survive.

Needless to say, we'd better plug that ozone layer in a hurry.

Editor-in-Chief

# SPJESTERS PARAMETERS SPJESTERS SPJES

### 10 to 3000MHz from \$3995

Now, high-speed, high-isolation switches with with built-in drivers, tough enough to pass stringent MIL-STD-202 tests. There's no longer any need to hassle with the complexities of designing a TTL driver interface and then adding yet another component to your subsystem...it's already included in a rugged, low-cost, compact assembly. Available in the popular hermetically-sealed TO-8 package or a small EMI-shielded metal connectorized

case, these tiny PIN-diode reflective switches, complete with driver, can operate over a 10 to 3000MHz span with a fast  $2\mu$ sec switching speed.

Despite their small size, these units offer isolation as high as 40dB(typ), insertion loss of only 1.1dB(typ), and a 1dB compression point of +27dBm over most of the frequency range. All models are TTL-compatible and operate from a dc supply voltage of 4.5 to 5.5 V with 1.8mA quiescent current. Switch to Mini-Circuits for highest quality innovative products... and leave the driving to us.

> finding new ways ... setting higher standards Mini-Circuits A Division of Scientific Components Corporation P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 Domestic and International Telexes: 6852844 or 620156 WE ACCEPT AMERICAN EXPRESS

#### SPECIFICATIONS

|                          | ZFSW                       | -230<br>-230DR | ZFSW                       | -425<br>-425DR |

|--------------------------|----------------------------|----------------|----------------------------|----------------|

| Freq. Range(MHz)         | 10-300                     | 00             | 10-250                     | 00             |

| Insert. Loss (dB)        | typ.                       | max.           | typ.                       | max.           |

| 10-100MHz                | 1.3                        | 1.9            | 1.3                        | 1.7            |

| 100-1500MHz              | 1.1                        | 1.9            | 1.1                        | 1.7            |

| 1500-3000MHz             | 1.8                        | 2.7            | 1.8                        | 2.5            |

| Isolation(dB)            | typ.                       | min.           | typ.                       | min.           |

| 10-100MHz                | 60                         | 40             | 60                         | 40             |

| 100-1500MHz              | 40                         | <b>28</b>      | 40                         | 30             |

| 1500-3000MHz             | 35                         | 22             | 35                         | 22             |

| 1dB Compression(dBm)     | typ.                       | min.           | typ.                       | min.           |

| 10-100MHz                | 17                         | 6              | 17                         | 6              |

| 100-1500MHz              | 27                         | 19             | 27                         | 19             |

| 1500-3000MHz             | 30                         | 28             | 30                         | 28             |

| VSWR(ON)                 | typ.                       | max.           | typ.                       | max.           |

|                          | 1.3                        | 1.6            | 1.3                        | 1.6            |

| Switching Time (µsec)    | typ.                       | max.           | typ.                       | max.           |

| (from 50% TTL to 90% RF) | 2.0                        | 4.0            | 2.0                        | 4.0            |

| Oper. Temp.(°C)          | -55 to                     | +100           | -55 to                     | +100           |

| Stor. Temp.(°C)          | -55 to                     | +100           | -55 to                     | +100           |

| Price (10-24)<br>(1-9)   | \$39.95<br><b>\$89.9</b> 5 |                | \$59.95<br><b>\$109.</b> 9 |                |

TOSIM 220

TOCINI ADD

CIRCLE 122 FOR U.S. RESPONSE CIRCLE 123 FOR RESPONSE OUTSIDE THE U.S.

F126 REV. A

# When is designing with DSPs stool? When you lack the sup

# like sitting on a two-legged port only TMS320 provides.

trong, solid support is essential to your design success with digital signal processing. That's why we at Texas Instruments have developed the support for our TMS320 DSP family as carefully and extensively as the family itself.

World-class development tools Choose any DSP in our five-generation

family, and you will find that the development environment is the same as that for general-purpose microprocessors. Included in the comprehensive lineup are advanced high-level-language

ANSI-compatible C compilers, HLL C-sourcelevel debuggers, scan-based emulators,

a multitasking DSP operating system and a low-cost evaluation module for benchmarking.

#### Tap into plenty of help

Our technical hot line connects you with TMS320 specialists who can answer your questions, provide more information or discuss

a fine design point. We also maintain an on-line bulletinboard service.

Hands-on workshops are a convenient

opportunity for familiarizing yourself with the TMS320 family and development environment. More than 2,000 pages of applications notes and DSP code are available. In addition, there are over 100 third parties and consultants supporting the TMS320 family. And our university program

includes more than 100 university labs. When it comes to DSP support, no one in the industry gives you as

strong a third leg as we do.

#### The right DSP at the right price

The other two legs — performance and price — are just as strong.

Our industry-standard TMS320 family contains more than 30 members, including the super-performance parallelprocessing TMS320C40. Prices start as low as \$3 for 16-bit devices and \$25 for 32-bit devices. That makes it easier and faster than ever before for you to closely match a DSP to your price/ performance needs.

When only a custom device will do, our unique customizable digital signal processing capability (cDSP can adapt our general-purpose DSPs to your needs.

To experience our strong support, call 1-800-336-5236, ext. 3536 We'll send you our interactive disk "Designing with DSPs is Easy" so you can experience the TMS320 Programmer's Interface. In addition, you'll receive information on our broad TMS320 family, our world-class support and customizable capability (cDSP).

08-12041

### PICO High Voltage DC-DC Converters

### .4"Htx.5"x.5" up to 1000VDC

#### **Series AV**

- 56 Standard Models

- 100VDC to 1000VDC Output

- Ultra-miniature Size and Weight (4 grams) 0.1 Cubic Inch Volume

- 4 Standard Input Voltages 5, 12, 24 and 28 Volts DC

- No Heat Sink or Electrical Derating Required

- Standard Operating Temp. –25°C to +70°C, Ambient

- Input/Output Isolation

#### **Options Available for Military Applications**

- Optional Operating Temp. –55°C to +85°C, Ambient

- Screening available per MIL-STD-883

- Stabilization Bake

- Temperature Cycle

- Hi-Temp, Full Power Burn-In, 160 Hours –125°C typical case temp.

CIRCLE 136 FOR U.S. RESPONSE CIRCLE 137 FOR RESPONSE OUTSIDE THE U.S.

### TAB POSITIONS ITSELF FOR GROWTH

**TECHNOLOGY BRIEFING**

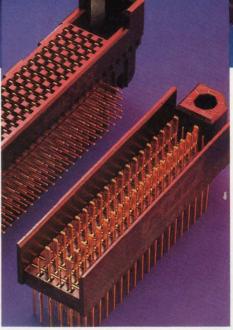

ape-automated bonding (TAB) is making inroads as an enabling technology for future generations of multichip modules (ELECTRONIC DESIGN, Jan. 9, p. 83). But despite its wide acceptance in Japan and growth in the U.S. and Europe, the technology does have its critics. At the recent Fourth International TAB Symposium, San Jose, Calif., a new direction was described for TAB that sidesteps many of its pitfalls and may offer an avenue for substantial growth as a mainstream packaging technology.

In developing a technique called demountable TAB (DTAB), researchers at Hewlett-Packard's Circuit Technology R&D Center, Palo Alto, Calif., sought to

DAVID MALINIAK COMPONENTS & PACKAGING

overcome the limitations that TAB's critics have decried for years. These include the technology's high entry cost, the expense of applying gold bumps to chips, and the need for ever-finer pitches for pc-board traces. The loudest complaints concern the difficulties TAB poses for rework and repair. But by perfecting a proprietary bumpless inner-lead-bond process, HP eliminated the bumping of chips. More importantly, the package's separable outer-lead pressure contacts make for easy removal from the board after mounting. This creates unlimited rework, not to mention ease of diagnostics and field service at the chip level. The 284-lead package uses area-array connection directly to through-hole vias on the pc board, eliminating the need for fine-pitch traces.

The package plugs into precise alignment holes in the pc board. The board is backed by a spring stiffener and the package is secured by screws. Compressed elastomer is used to apply force to the outer leads. In performance tests at 65 MHz and 125 MHz, the DTAB package equalled or exceeded the thermal and electrical performance of any single-chip VLSI package. The package also withstood aggressive environmental testing. As a result, HP envisions DTAB as potentially spurring the proliferation of high-performance TAB technology.

Researchers are also investigating other ways of getting around gold bumping of die for TAB attachment. A report from IBM Corp.'s Endicott, N.Y. facility describes a process called solder-attach tape technology, in which the inner leads aren't bonded by thermocompressing gold bumps on the chip. Instead, the heat necessary to form the bond is transferred to a tin-lead solder bump on the chip and gold-plated TAB leads by convection from hot gas applied through a nozzle over the bond site. The leads are pressed into the preheated solder by the nozzle, which applies the hot gas. A cool-gas cycle then solidifies the joint.

The advantages of this technique, which borrows from IBM's established flipchip methodology, is that bonds can be formed over active circuitry. This means that array footprints can be packaged. Earlier TAB methodologies were limited to perimeter connections. The shorter line lengths will reduce capacitive loading and other parasitic effects. Hence, devices will be faster.

Some MCM developers have discovered that module testing requires a multiphased approach to hardware test, and that TAB technology provides for easier assembly than wire bonding. In addition, it's easier to sort for good die when they're mounted in TAB carriers. The experiences reported by the Tactical Systems Division of Rockwell International Corp., Anaheim, Calif., show that MCM developers have a better handle on the complexity of module assembly and verification than ever before.

Rockwell's approach to designing its dual-1750A processor module for a highspeed missile-interceptor program may well point the way for future MCM developers. The company attributes its first-pass success to months of up-front work at the system level, which included an effort to reduce design complexity.

Thus, as TAB developers and end-users explore ways to expand the technology's applicability, TAB inches closer and closer to the mainstream of packaging technology.

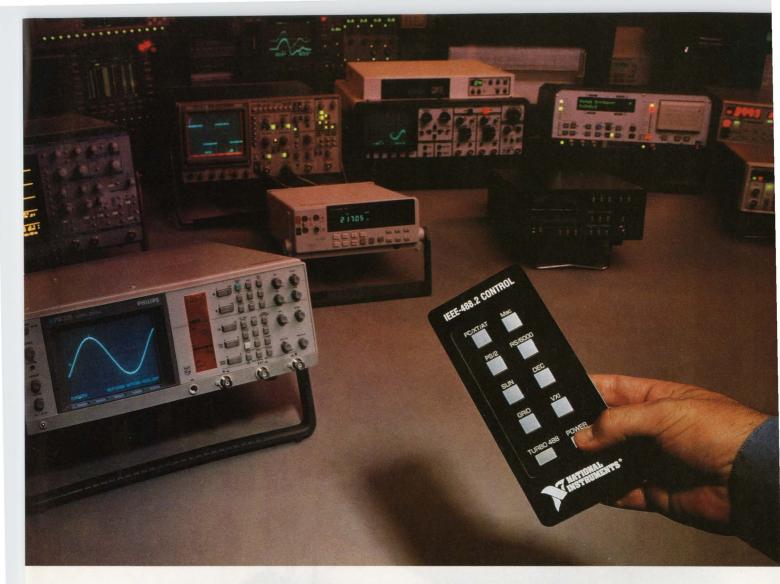

# **ULTIMATE CONTROL**

#### No one can give you control of your GPIB test system like National Instruments can.

#### PERFORMANCE

The NAT4882<sup>™</sup> chip makes our GPIB controller boards completely IEEE-488.2 compatible. When the NAT4882 is teamed with the Turbo488<sup>®</sup> performance chip, you get the 488 transfer rate of 1 Mbites (see for both read

maximum IEEE-488 transfer rate of 1 Mbytes/sec for both read and write operations.

Use our industry-standard NI-488<sup>®</sup> software to control your GPIB instruments and give your test programs maximum throughput, regardless of your choice of personal computers or workstations.

#### COMPATIBILITY

The NAT4882 controller chip is also compatible with the controller chips of the past, so you get the best of both worlds – complete compatibility with your existing applications and the ability to meet your future requirements.

And when your controller needs change, NI-488 programs are compatible across many different platforms and operating systems – without modification.

#### **UPGRADE PROGRAM**

Existing PC, PS/2, and Macintosh customers can upgrade to the benefits of IEEE-488.2 and increased performance through a special upgrade program.

#### **TRAINING**

Learn even more ways to improve your test system by taking our hands-on, IEEE-488 training course.

For more information on how you can have the ultimate GPIB control, call: (512) 794-0100 or (800) IEEE 488 (Toll-free U.S. and Canada)

6504 Bridge Point Parkway Austin, TX 78730-5039

See Us At ATE And Instrumentation Booth #108

AUSTRALIA (03) 879 9422 • DENMARK (45) 76 73 22 • FRANCE (1) 48 65 33 70 • GERMANY (089) 714 5093 • ITALY (02) 4830 1892 JAPAN (03) 3788 1921 • NETHERLANDS (01720) 45761 • NORWAY (03) 846 866 • SPAIN (908) 604 304 • SWITZERLAND (056) 45 58 80 • U.K. (0635) 523 545

JAPAN (03) 3788 1921 • NETHERLANDS (01720) 45761 • NORWAY (03) 846 866 • SPAIN (908) 604 304 • SWITZERLAND (056) 45 58 80 • U.K. (0635) 523 545 Product names listed are trademarks of their respective manufacturers. Company names listed are trademarks or trade names of their respective companies. © Copyright 1991 National Instruments Corporation. All rights reserved.

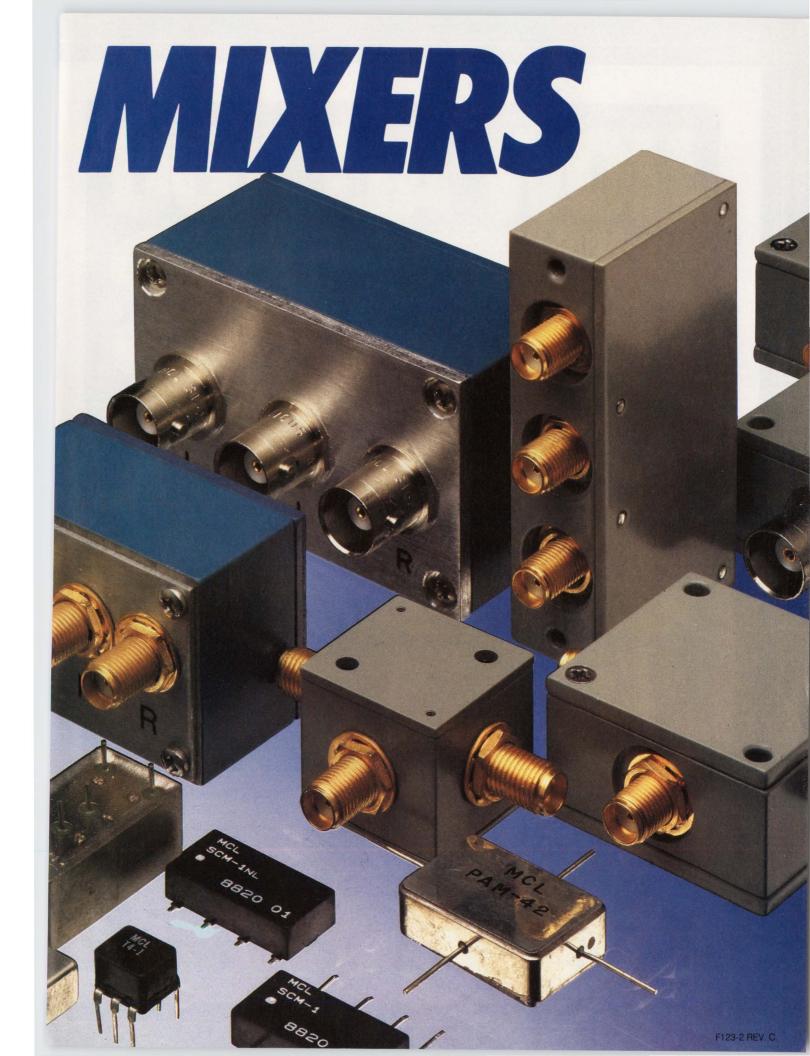

# Over 50 off-the-shelf models ...

Having difficulty locating RF or pulse transformers with low droop, fast risetime or a particular impedance ratio over a specific frequency range?...Mini-Circuits offers a solution.

Choose impedance ratios from 1:1 to 36:1, connector or pin versions (plastic or metal case built to meet MIL-T-21038 and MIL-T-55831 requirements\*). Ultra-wideband response achieves low droop and fast risetime for pulse applications. Ratings up to 1000M ohms insulation resistance and up to 1000V dielectric voltage. For wide dynamic range applications involving up to 100 mA DC primary current, use the T-H series. Coaxial connector models are offered with 50 and 75 ohm bent lead version style X 65 impedance; BNC standard; request other types. Available for immediate delivery with one-year guarantee.

or

Call or write for 68-page catalog or see our catalog in EEM, or Microwaves Product Data Directory. \*units are not QPL listed

case styles T, TH, case W 38, X 65 bent lead version, KK81 bent lead version TMO, case A 11, † case B 13 FT, FTB, case H 16 NEW TC SURFACE MOUNT MODELS from 1MHz to 1500 MHz

MCL NO.

TMO2-1 TMO2.5-6 TMO2.5-6T

TMO3-1T TMO4-1

TM04-2

TMO4-6

TM05-11

TMO9-TMO16-1 NSN

TMO

| NSN GUI   | NSN              |  |

|-----------|------------------|--|

| FTB1-1-75 | 5950-01-132-8034 |  |

|           |                  |  |

| FTB1-6    | 5950-01-225-8773 |  |

| T1-1      | 5950-10-128-3745 |  |

| T1-1T     | 5950-01-153-0668 |  |

| T2-1      | 5950-01-106-1218 |  |

| T3-1T     | 5950-01-153-0298 |  |

| T4-1      | 5950-01-024-7626 |  |

| T9-1      | 5950-01-105-8153 |  |

| T16-1     | 5950-01-094-7439 |  |

| TMO1-1    | 5950-01-178-2612 |  |

T, TH, TT

T, TH, TT

TO

T, TH, TT bent lead version style KK81

# FORMERS 3KHz-800MHz from \$325

|    |                                     |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                        | FREQUENCY<br>MHz                                                                                                                                                                                                 | 11                                                                                                                                                                                                               | SERTION L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PRICE \$                                                                                                             |

|----|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|    | case style number see opposite page | MODEL<br>NO.                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                        | IVII IL                                                                                                                                                                                                          | 3dB<br>MHz                                                                                                                                                                                                       | 2dB<br>MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1dB<br>MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Qty.<br>(1-9)                                                                                                        |

| Ā* | PRI SEC                             | T T1-1T<br>T1-6T<br>T2-1T<br>T2.5-6T<br>T3-1T<br>T4-1<br>T4-1<br>T6-6T<br>TH T4-1H<br>TMO TM01-1T<br>TM02-1T<br>TM02-1T<br>TM03-1T<br>TM03-1T                                                                           | 1<br>2<br>25<br>3<br>4<br>4<br>5<br>8<br>13<br>16<br>4<br>1<br>2<br>2<br>5<br>3<br>4<br>5<br>13                                                                                                                                                                        | 05-200<br>003-300<br>07-200<br>01-100<br>05-250<br>2-350<br>02-250<br>0-2-50<br>0-2-250<br>0-3-300<br>03-140<br>03-75<br>10-350<br>05-200<br>0.7-200<br>0.7-200<br>0.1-100<br>0.5-250<br>2-350<br>3-300<br>3-120 | 0.05-200<br>003-300<br>0.7-200<br>0.1-100<br>0.5-200<br>2-350<br>0.2-250<br>0.3-300<br>0.3-140<br>0.3-120<br>0.3-75<br>10-350<br>0.5-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.5-250<br>2-350<br>3-300<br>3-3120 | .08-150<br>.01-150<br>.02-50<br>.1-100<br>.02-50<br>.1-200<br>.35-300<br>.05-150<br>.6-200<br>.06-30<br>.15-300<br>.08-150<br>.1-100<br>.02-50<br>.1-200<br>.35-300<br>.6-200<br>.7-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} .2 - 80 \\ .02 - 50 \\ .5 - 50 \\ .5 - 70 \\ .5 - 70 \\ .2 - 100 \\ .1 - 100 \\ .5 - 100 \\ .5 - 20 \\ .1 - 20 \\ .2 - 200 \\ .2 - 80 \\ .5 - 50 \\ .5 - 50 \\ .5 - 50 \\ .5 - 70 \\ .5 - 70 \\ .5 - 100 \\ .5 - 100 \\ .5 - 100 \\ .5 - 20 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.45<br>6.95<br>4.95<br>4.95<br>3.25<br>4.45<br>7.95<br>5.65<br>5.95<br>7.95<br>8.45<br>8.45<br>8.45<br>8.45<br>8.45 |

| B* | PRI OF SEC                          | TT TT1-6<br>TT1.5-1<br>TT2.5-6<br>TT4-1<br>TT4-1A<br>TT25-1<br>TTMO25-11<br>TTMO25-11<br>TTMO4-1A                                                                                                                       | 1<br>1.5<br>2.5<br>3<br>4<br>25<br>25<br>1<br>4                                                                                                                                                                                                                        | .004-500<br>.075-500<br>.01-50<br>.05-200<br>.02-30<br>.02-30<br>.005-100<br>0.1-300                                                                                                                             | .004-500<br>.075-500<br>.01-50<br>.2-50<br>0.1-300<br>.02-30<br>.005-100<br>0.1-300                                                                                                                              | .02-200<br>.2-100<br>.025-25<br>.2-50<br>0.2-250<br>.05-20<br>.05-20<br>.01-75<br>0.2-250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .1-50<br>1-50<br>.05-10<br>1-30<br>0.3-180<br>.1-10<br>.05-40<br>0.3-180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6.95<br>5.95<br>6.45<br>5.95<br>6.95<br>9.95<br>11.95<br>11.45<br>13.95                                              |

| C  | PR SEC                              | T T1-1<br>T1.18-3<br>T1-6<br>T1.5-1<br>T1.5-6<br>T2.5-6<br>T4-6<br>T9-1<br>T16-1<br>T0 T0-75<br>TH T1-1H<br>T9-1H<br>T16-H<br>TMO TM01-02<br>TMO TM01-02<br>TM01-1<br>TM02.5-6<br>TM04-6<br>TM09-1<br>TM09-1<br>TM016-1 | 1<br>1.18<br>1<br>1.5<br>2.5<br>4<br>9<br>16<br>36<br>1<br>1<br>9<br>16<br>1<br>1.5<br>2.5<br>4<br>9<br>16<br>36<br>1<br>1<br>1.5<br>2.5<br>4<br>9<br>16<br>36<br>1<br>1<br>1.5<br>2.5<br>4<br>9<br>16<br>36<br>1<br>1<br>1.5<br>1.5<br>1.5<br>1.5<br>1.5<br>1.5<br>1. | .15-400<br>0.01-250<br>0.1-150<br>.1-300<br>.02-100<br>.02-200<br>.03-200<br>.15-200<br>.3-120<br>.03-20<br>.10-500<br>8-300<br>2-90<br>7-85<br>1-800<br>.15-400<br>.15-400<br>.15-200<br>.3-120                 | .15-400<br>0.01-250<br>0.1-150<br>.1-300<br>.02-100<br>.02-100<br>.03-100<br>.03-200<br>.3-120<br>.3-120<br>.3-200<br>.15-200<br>.3-200<br>.1-85<br>1-800<br>.1-300<br>.01-100<br>.02-200<br>.3-200<br>.3-120    | $\begin{array}{c} .35-200\\ 0.02-200\\ .02-100\\ .2-150\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02-50\\ .02$ | $\begin{array}{c} 2-50\\ 0.03-50\\ .05-50\\ .5-80\\ .05-20\\ .1-25\\ .05-20\\ .1-100\\ 2-40\\ 5-20\\ .1-5\\ 40-250\\ 25-100\\ 6-50\\ 15-40\\ -\\ -\\ 2-50\\ .5-8\\ .05-20\\ .1-100\\ 5-50\\ .5-80\\ .5-100\\ .5-80\\ .5-80\\ .5-100\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\ .5-80\\$ | 3.25<br>5.65<br>5.65<br>4.45<br>5.66<br>4.45<br>4.45<br>4.45<br>4.4                                                  |

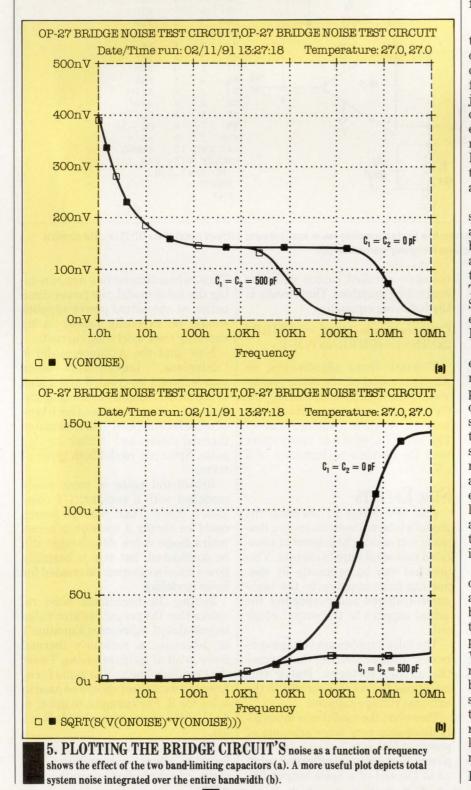

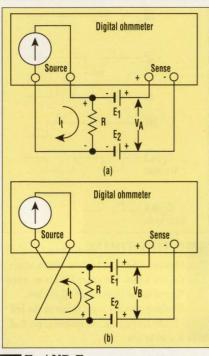

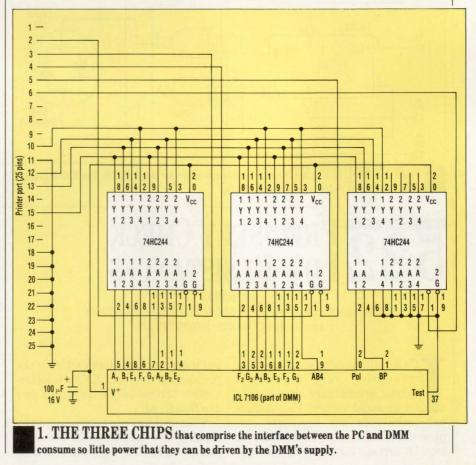

| D  | PRI SEC                             | T T2-1<br>T3-1<br>T4-2<br>T8-1<br>T14-1<br>TMO<br>TMO2-1<br>TMO3-1<br>TMO8-1<br>TMO8-1<br>TMO14-1<br>FT FT1.22-1<br>FT1.5-1                                                                                             | 2<br>3<br>4<br>14<br>2<br>3<br>4<br>8<br>14<br>1.22<br>1.5                                                                                                                                                                                                             | .050-600<br>.5-800<br>.2-600<br>.15-250<br>.2-150<br>.050-600<br>.5-800<br>.2-600<br>.2-600<br>.2-500<br>.2-150<br>.005-100<br>.1-400                                                                            | 050-600<br>.5-800<br>.2-600<br>.15-250<br>.2-150<br>.050-600<br>.2-600<br>.2-600<br>.15-250<br>.2-150<br>.005-100<br>.1-400                                                                                      | 1-400<br>2-400<br>.5-500<br>.5-200<br>.5-100<br>1-400<br>2-400<br>.5-500<br>.25-200<br>.5-100<br>.01-50<br>5-200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .5-200<br><br>2-250<br>2-100<br>2-50<br>.5-200<br><br>2-250<br>2-100<br>2-50<br>.05-25<br>1-100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.95<br>4.45<br>3.95<br>4.95<br>7.95<br>8.45<br>7.95<br>8.45<br>7.95<br>8.45<br>35.95<br>35.95                       |