An American Federation of Information Processing Societies Publication

Volume 20

# COMPUTERS - KEY TO TOTAL SYSTEMS CONTROL

Proceedings of the Eastern Joint Computer Conference Washington, D.C., December 12-14, 1961 © Copyright 1961 by

#### American Federation of Information Processing Societies

## PRIOR CONFERENCE PROCEEDINGS

| Number | Conference | Location      | Date                    |

|--------|------------|---------------|-------------------------|

| 1      | Eastern    | Philadelphia  | Dec. 10-12, 1951        |

| 2      | Eastern    | New York City | Dec. 10-12, 1952        |

| 3      | Western    | Los Angeles   | Dec. 4-6, 1953          |

| 4      | Eastern    | Washington    | Dec. 8-10, 1953         |

| 5      | Western    | Los Angeles   | Feb. 11-12, 1954        |

| 6      | Eastern    | Philadelphia  | Dec. 8-10, 1954         |

| 7      | Western    | Los Angeles   | Mar. 1-3, 1955          |

| 8      | Eastern    | Boston        | Nov. 7-9, 1955          |

| 9      | Western    | San Francisco | Feb. 7-9, 1956          |

| 10     | Eastern    | New York City | Dec. 10-12, 1956        |

| 11     | Western    | Los Angeles   | Feb. 26-28, 1957        |

| 12     | Eastern    | Washington    | Dec. 9-13, 1957         |

| 13     | Western    | Los Angeles   | May 6-8, 1958           |

| 14     | Eastern    | Philadelphia  | Dec. 3-5, 1958          |

| 15     | Western    | San Francisco | Mar. 3-5, 1959          |

| 16     | Eastern    | Boston        | Dec. 1-3, 1959          |

| 17     | Western    | San Francisco | May 3-5, 1960           |

| 18     | Eastern    | New York      | Dec. 13-15, 1960        |

| 19     | Western    | Los Angeles   | May 9 <b>-</b> 11, 1961 |

Manufactured in the United States of America by McGregor & Werner, Inc., Washington 12, D.C.

\_

## PREFACE

On behalf of the Board of Governors of the American Federation of Information Processing Societies, it is my pleasure to welcome you to this conference, the first to be sponsored by the Federation rather than the National Joint Computer Committee. In May of this year, the AFIPS was created by the American Institute of Electrical Engineers, the Association for Computing Machinery, and the Institute of Radio Engineers, to be the unified national voice for the information processing and computer profession in the United States. Since then, there has been an orderly transfer of business from the NJCC to the AFIPS. As a society of societies, the AFIPS differs from the NJCC in that it can accept into membership other professional societies which are interested in information processing, and it is expected that it will grow significantly.

As stated in our constitution, the goals of AFIPS "shall be the advancement and diffusion of knowledge of the information processing sciences. . .for literary and scientific purposes. . .To this end, it is part of the purposes of the Federation. . .to serve the public by making available to journals, newspapers, and other channels of public information reliable communications as to information processing and its progress; to cooperate with local, national, and international organizations or agencies on matters pertaining to information processing; to serve as representative of the United States of America in international organizations with like interests; to promote unity and effectiveness of effort among all those who are devoting themselves to information processing by research, by application of its principles, by teaching or by study; and to foster the relations of the sciences of information processing to other sciences and to the arts and industries."

Some of these items we are well started on—others we will inaugurate soon. We represent the United States to the International Federation of Information Processing Societies and contribute financially to IFIPS in behalf of this country. We have assumed sponsorship and financial responsibility of the Joint Computer Conferences. We have accepted applications for membership from other societies. We have made our existence known to other professional societies. We are an active and growing organization acting to promote the interchange of information among information processing specialists through sponsorship of greater cooperative efforts between their professional societies. The American Federation of Information Processing Societies promises to be an instrument of tremendous utility to American technology in the exciting and dynamic years ahead.

> Willis H. Ware Chairman, Board of Governors American Federation of Information Processing Societies

## FOREWORD

Early in the infancy of what is still a very young discipline, it was recognized that segmentation was taking place among those working in the computer sciences. Many new computing societies or specialized extensions of existing organizations sprang up, accentuating the divergence by specialization to the detriment of the industry.

It was with this thought in mind that the leaders of the Association for Computing Machinery, the Professional Group on Electronic Computers of the Institute of Radio Engineers, and the Committee on Computing Devices of the American Institute of Electrical Engineers established the Joint Computer Committee. The sole function of this Committee was to sponsor the Joint Computer Conferences, designed to provide a forum by which members of the three sponsoring societies, as well as all those interested in the computing field, could assemble and explore through the medium of technical papers, personal conversations, and technical exhibits the latest developments of interest to all.

The phenomenal growth of the field resulted in the contribution of an increasing number of excellent contributed papers. When confronted with the need to complete the conferences in a reasonable period of time, such as the traditional three days, organizers tended to resort, more and more as the years went by, to parallel technical sessions. The result has frequently been sessions whose subject matter and audience to a large extent paralleled the interests and membership of the various sponsoring societies. From this point of view the Joint Computer Conferences have not served their desired purposes, but have become a general extension of the individual meetings of the various societies.

Although tempted to expand the size of the conference by the many excellent papers contributed, either through greater duration or the establishment of parallel sessions, the Committee for the 1961 Eastern Joint Computer Conference has attempted to return to first principles, eliminate parallel sessions, and maintain the generally accepted three day length of the conference. The Committee has assembled a program which is believed to be of interest to most people in the computer field, regardless of whether their orientation is in programming, engineering, management, or other areas. The theme of this conference, "Computers— Key to Total Systems Control," lends itself particularly to this aim by its generality and its importance.

Eliminating parallel sessions and adhering to a unified technical program is particularly appropriate, too, by virtue of the fact that this 1961 Eastern Joint Computer Conference is the first conference under the sponsorship of the American Federation of Information Processing Societies. Whereas the Joint Computer Committee by its very organization was limited to the original three sponsoring societies, the charter of AFIPS provides specifically for the enlargement of its member organizations to include such other organizations interested in affiliation, whether they have a major interest in the computing field or simply peripheral interests in these activities. Although this may be looked upon as somewhat of a noble experiment, the Committee believes that as more and more organizations become affiliated with AFIPS, the growth of multiple sessions that would result would lessen cross-fertilization—and, incidentally, tax the supply of public rooms in most hotels.

Another innovation pioneered at this meeting is the publication of these <u>Proceedings</u> in a permanent, hardbound form. It is the belief of the Committee that this form enhances the lasting value of the <u>Proceedings</u> to the registrants. It was an added attraction to the solicitation of worthwhile contributions to the technical sessions. Through arrangements with the publisher, the hardbound trade edition will provide wider distribution of these <u>Proceedings</u> far beyond the capabilities of the individual sponsoring societies. Acknowledgment is made to Mr. Robert Teitler of The Macmillan Company for his suggestions, encouragement, and solicitude in the preparation and publication of these <u>Proceedings</u>. His activities have been of considerable assistance and material benefit to the Committee.

Members of the Committee who have primary responsibility in different areas are listed elsewhere in these <u>Proceedings</u>. Space does not permit naming the many individuals who have assisted the various committee chairmen in their functions. Their creativity, diligence and attention to detail are responsible for the many arrangements necessary in preparing for a conference of this magnitude.

> Jack Moshman General Chairman

## AMERICAN FEDERATION OF INFORMATION PROCESSING SOCIETIES (AFIPS)

AFIPS P. O. Box 1196 Santa Monica, Calif.

General Chairman

Dr. Willis H. Ware The RAND Corporation 1700 Main Street Santa Monica, Calif.

#### Secretary

Miss Margaret R. Fox National Bureau of Standards Data Processing Systems Division Washington 25, D. C.

#### **Executive Committee**

Mr. R. A. Imm (AIEE) Dr. H. D. Huskey (ACM) Dr. A. A. Cohen (IRE) Dr. W. H. Ware, Chairman

#### **IRE Directors**

Dr. Werner Buchholz IBM Corporation South Road Laboratory Poughkeepsie, New York

Dr. Arnold A. Cohen Remington Rand Univac Univac Park St. Paul 16, Minnesota

Mr. Frank E. Heart Lincoln Laboratory, Rm. B-283 P. O. Box 73 Lexington 73, Mass.

Mr. Harry T. Larson Aeronutronic Div. of Ford Motor Co. P. O. Box 486 Newport Beach, Calif.

#### **AIEE Directors**

Mr. R. A. Imm IBM Corporation Dept. 550, Bldg. 604 Rochester, Minnesota

Mr. F. S. Gardner American Inst. of Elec. Engrs. 33 West 39th Street New York 18, N. Y.

Mr. Claude A. R. Kagan Western Electric Co. Engineering Research Center P. O. Box 900 Princeton, New Jersey

Dr. Morris Rubinoff 517 Anthwyn Road Merion Station, Pennsylvania

#### ACM Directors

Mr. Walter Carlson Engineering Dept. E. I. duPont de Nemours & Co. Louviers Bldg. Wilmington 98, Delaware

Dr. Bruce Gilchrist IBM Corporation 590 Madison Ave. New York 22, N. Y. Dr. Harry D. Huskey Dept. of Mathematics 441 Corey Hall University of California Berkeley 4, California

Mr. J. D. Madden System Development Corp. 2500 Colorado Ave. Santa Monica, Calif.

## 1961 EASTERN JOINT COMPUTER CONFERENCE COMMITTEE

.

| General Chairman | Dr. Jack Moshman,<br>C-E-I-R, INC.                                          |

|------------------|-----------------------------------------------------------------------------|

| Vice Chairman    | William L. Witzel,<br>Computer Concepts, Inc.                               |

| Secretary        | Herbert R. Koller,<br>U. S. Patent Office                                   |

| Finance          | Solomon Rosenthal, Chairman<br>Headquarters, U. S. Air Force                |

| Public Relations | Isaac Seligsohn, Chairman<br>IBM Federal Systems Division                   |

| Proceedings      | Paul W. Howerton, Chairman<br>Central Intelligence Agency                   |

|                  | Terence G. Jackson, Jr.,<br>Stanford Research Institute                     |

| Program          | Bruce G. Oldfield, Chairman<br>IBM Federal Systems Division                 |

|                  | George G. Heller, Assistant to the Chairman<br>IBM Federal Systems Division |

|                  | Samuel N. Alexander,<br>National Bureau of Standards                        |

|                  | Herbert S. Bright,<br>Philco Corporation, Computer Division                 |

|                  | Saul I. Gass,<br>IBM Federal Systems Division                               |

|                  | Herbert R. Koller,<br>U. S. Patent Office                                   |

|                  | Charles A. Phillips,<br>Department of Defense                               |

|                  | Solomon Rosenthal,<br>Headquarters, U. S. Air Force                         |

|                  | Howard E. Tompkins,<br>National Institutes of Health                        |

| Hotel Arrangements              | Henry S. Forrest, Chairman<br>Control Data Corporation           |

|---------------------------------|------------------------------------------------------------------|

|                                 | John W. Lacey,<br>Control Data Corporation                       |

|                                 | Clifford J. Leahy,<br>Thompson Ramo-Wooldridge                   |

| Women's Activities              | Ethel C. Marden, Chairman<br>National Bureau of Standards        |

|                                 | Eleanor Alexander<br>Jeanne Beiman<br>Iby Heller<br>Sarah Newman |

| Printing and Mailing            | Mike Healy, Chairman<br>System Development Corporation           |

| Registration                    | John T. Harris, Chairman<br>Remington Rand Univac                |

|                                 | W. B. Larson,<br>Aeronutronic Div. of Ford Motor Co.             |

|                                 | Jack A. Neal,<br>C-E-I-R, INC.                                   |

|                                 | E. R. Quady,<br>Remington Rand Univac                            |

| Exhibits                        | Charles A. Phillips, Chairman<br>Department of Defense           |

|                                 | W. Howard Gammon,<br>Department of Defense                       |

|                                 | L. David Whitelock,<br>Department of the Navy                    |

| Exhibits Manager                | John L. Whitlock Associates                                      |

| Public Relations<br>Consultants | Stavisky & Associates                                            |

.

### LIST OF REVIEWERS

The Program Committee would like to express its deep appreciation to those listed below for their conscientious, thoughtful reviewing of the abstracts and summaries of the 242 papers submitted. Their unfailing efforts contributed significantly toward the selection of this year's EJCC program.

- Mr. R. J. Arms, National Bureau of Standards

- Mrs. Dorothy P. Armstrong, Bureau of the Census

- Mr. James V. Batley, IBM Corp.

- Mr. Wayne D. Bartlett, General Electric Co. Mr. Noel D. Belnap, Jr., System Develop-

- ment Corp.

- Mr. Martin A. Belsky, IBM Corp.

- Mr. William Blodgett, Electronic Associates, Inc.

- Mr. Robert Bosak, System Development Corp.

- Mr. L. E. Brown, Aeronutronic

- Dr. Edward A. Brown, IBM Corp.

- Mr. James H. Burrows, Mitre Corp.

- Mr. Robert Courtney, IBM Corp.

- Mr. Robert P. Crago, IBM Corp.

- Mr. Charles F. Crichton, C-E-I-R, INC.

- Mr. J. A. Cunningham, National Bureau of Standards

- Dr. Ruth M. Davis, David Taylor Model Basin

- Mr. Arthur A. Ernst, National Bureau of Standards

- Mr. James M. Farrar, Jr., IBM Corp.

- Mr. Romeo R. Favreau, Electronic Associates. Inc.

- Mr. Howard R. Fletcher, Bureau of Census

- Miss Margaret R. Fox, National Bureau of Standards

- Mr. R. F. Garrard, General Electric Company

- Mr. Lewey O. Gilstrap, Jr., Adaptronics, Inc.

- Mr. Seymour Ginsburg, System Development Corp.

- Mr. Ezra Glazer, National Bureau of Standards

- Mr. Geoffrey Gordon, IBM Corp.

- Dr. Saul Gorn, University of Pennsylvania

- Mr. Sidney Greenwald, Rabinow Engineering Company

- Dr. Jerome J. Hahn, NIH

- Mr. George M. Heller, Bureau of the Census

- Mr. Thomas N. Hibbard, System Development Corp.

- Mr. James Hill, Rabinow Engineering Company

- Mr. E. W. Hogue, National Bureau of Standards

- Mrs. Francis E. Holberton, David Taylor Model Basin

- Dr. Grace M. Hopper, Sperry Rand Corp.

- Mr. Richard A. Hornseth, Bureau of Census

- Mr. Paul W. Howerton, CIA

- Dr. Morton A. Hyman, IBM Corp.

- Mr. Graham Jones, IBM Corp.

- Mr. Horace Joseph, National Bureau of Standards

- Mr. R. A. Kirsch, National Bureau of Standards

- Mr. F. H. Kranz, IBM Corp.

- Mr. M. R. Lackner, System Development Corp.

- Mr. Chuck H. Lee, Bureau of the Census

- Mr. Richard Lee, National Science Foundation

- Dr. Herbert W. Leibowitz, IBM Corp.

- Mr. Harry Loberman, National Bureau of Standards

- Mr. J. D. Madden, System Development Corp.

- Mrs. Ethel Marden, National Bureau of Standards

Dr. H. L. Mason, National Bureau of Standards

- Mr. Phil W. Metzger, IBM Corp.

- Mr. Robert J. Miles, IBM Corp.

- Dr. A. H. Mitchell, IBM Corp.

Mrs. Betty S. Mitchell, Bureau of the Census Miss Elsa Moser, IBM Corp.

- Mr. Ralph Mullendore, Bureau of the Census Mr. Simon Newman, Consultant

- Mr. James P. Nigro, National Bureau of Standards

- Mr. G. W. Petrie, IBM Corp.

- Mr. J. L. Pike, National Bureau of Standards

- Dr. W. T. Putney, IBM Corp.

- Mr. Jack Rabinow, Rabinow Engineering Company

- Mr. George M. Reitwiesner, National Bureau of Standards

- Mr. Stanley B. Rosen, General Electric Company

- Mr. David Rosenblatt, National Bureau of Standards

- Mr. Arthur I. Rubin, Electronic Associates, Inc.

- Mr. Bruce Rupp, IBM Corp.

- Dr. Lindy Saline, General Electric Company

- Mr. Isaac Seligsohn, IBM Corp.

- Dr. Norman Shapiro, NIH

- Mr. Jack E. Sherman, Lockheed

- Mr. William Shooman, System Development Corp.

- Mr. Robert A. Sibley, Jr., IBM Corp.

- Miss Mary Elizabeth Stevens, National Bureau of Standards

- Mr. Robert F. Stevens, IBM Corp.

- Mr. Frank Stockmal, System Development Corp.

- Mr. Jack A. Strong, C-E-I-R, INC.

- Dr. J. H. Turnock, IBM Corp.

- Mr. Walter D. Urban, National Bureau of Standards

- Mr. Richard Van Horn, Rand Corp.

- Mr. Kenneth Webb, IBM Corp.

- Mr. Joseph H. Wegstein, National Bureau of Standards

- Mr. Tom J. Welch, IBM Corp.

- Mr. W. W. Youden, National Bureau of Standards

- Charles W. Adams Associates, Incorporated, Bedford, Massachusetts

- Aeronutronic Division of Ford Motor Company, Newport Beach, California

- American Data Machines, Incorporated, Hicksville, Long Island, New York

- American Systems, Incorporated, Hawthorne, California

- American Telephone & Telegraph Company -Long Lines Department, New York, N. Y.

- AMP, Incorporated Magnetics Division, Harrisburg, Pennsylvania

- Ampex Computer Products Company, Culver City, California

- ANelex Corporation, Boston, Massachusetts

- Applied Dynamics, Incorporated, Ann Arbor, Michigan

- Audio Devices, Incorporated, New York, N.Y.

- Auerbach Corporation, Philadelphia, Pennsylvania

- Autonetics Industrial Products Division of North American Aviation, Incorporated, Los Angeles, California

- Bendix Computer Division The Bendix Corporation, Los Angeles, California

- Boonshaft and Fuchs, Incorporated, Hatboro, Pennsylvania

- Bryant Computer Products Division of Ex-Cell-O Corporation, Walled Lake, Michigan

- The Bureau of National Affairs, Incorporated, Washington, D. C.

- Burroughs Corporation, Detroit, Michigan

- Business Automation, Elmhurst, Illinois

- California Computer Products, Incorporated, Downey, California

- C-E-I-R, INC., Arlington, Virginia

- C. P. Clare & Company, Chicago, Illinois

- Clary Corporation, San Gabriel, California

- Comcor, Incorporated, Denver, Colorado

- Computer Control Company, Incorporated, Framingham, Massachusetts

- Computer Systems, Incorporated, Monmouth Junction, New Jersey

- Computron, Incorporated, Waltham, Massachusetts

- Consolidated Electrodynamics Corporation, Pasadena, California

- Control Data Corporation, Minneapolis, Minnesota

- Dashew Business Machines, Incorporated, Los Angeles, California

- Data Display, Incorporated, St. Paul, Minnesota

- Datamation Division F. D. Thompson Publications, Incorporated, New York, N. Y.

- Datapulse, Incorporated, Inglewood, California

- DI/AN Controls, Incorporated, Boston, Massachusetts

- Digital Equipment Corporation, Maynard, Massachusetts

- Digitronics Corporation, New York, N. Y.

- Elco Corporation, Philadelphia, Pennsylvania

- Electronic Associates, Incorporated, Long Branch, New Jersey

- Electronic Memories, Incorporated, Los Angeles, California

- Engineered Electronics Company, Santa Ana, California

- Fabri-Tek, Incorporated, Amery, Wisconsin

- Fairchild Semiconductor Corporation, Mountain View, California

- Ferranti Electric, Incorporated, Plainview, Long Island, New York

- GPS Instrument Company, Incorporated, Newton, Massachusetts

- General Dynamics/Electronics Information Technology Division, San Diego, California

- General Electric Company Defense Systems Department, Washington, D. C.

- General Kinetics, Incorporated, Arlington, Virginia

- The Gerber Scientific Instrument Company Hartford, Connecticut

- Harvey-Wells Electronics, Incorporated, Natick, Massachusetts

- Idaho Maryland Industries, Incorporated, Studio City, California

- Indiana General Corporation, Valparaiso, Indiana

- Industry Reports, Incorporated, Washington, D. C.

- IBM Corporation, New York, New York

- Invac Corporation, Natick, Massachusetts

- Laboratory For Electronics, Incorporated, Computer Products Division, Boston, Massachusetts

- Litton Systems, Incorporated, Beverly Hills, California

- Micro Switch Division of Minneapolis-Honeywell Regulator Company, Freeport, Illinois

- Midwestern Instruments, Incorporated, Tulsa, Oklahoma

- Minneapolis-Honeywell Regulator Company, EDP Division, Wellesley Hills, Massachusetts

- Mnemotron Corporation, Pearl River, New York

- Monroe Calculating Machine Company, Incorporated, Orange, New Jersey

- The National Cash Register Company, Dayton, Ohio

- Omnitronics, Incorporated, Philadelphia, Pennsylvania

- Packard Bell Computer Corporation, Los Angeles, California

- Philco Corporation G & I Group, Philadelphia, Pennsylvania

- Photocircuits Corporation, Glen Cove, New York

- Potter Instrument Company, Incorporated, Plainview, Long Island, New York

- Radio Corporation of America EDP Division, Camden, New Jersey

- Radio Corporation of America Semiconductor & Materials Division, Somerville, New Jersey

- Reeves Soundcraft Corporation, Danbury, Connecticut

- Remington Rand Univac Division Sperry Rand Corporation, New York, New York

- Rese Engineering, Incorporated, Philadelphia, Pennsylvania

- Rotron Manufacturing Company, Incorporated, Woodstock, New York

- Royal McBee Corporation, New York, New York

- Soroban Engineering, Incorporated, Melbourne, Florida

- Sprague Electric Company, North Adams, Massachusetts

- Sylvania Electronic Systems, Waltham, Massachusetts

- Tally Register Corporation, Seattle, Washington

- Tech Serv, Incorporated, College Park, Maryland

- Telltype Corporation, Skokie, Illinois

- Telex, Incorporated Data Systems Division, Saint Paul, Minnesota

- Texas Instruments, Incorporated, Dallas, Texas

Underwood Corporation, New York, New York

- Uptime Corporation, Broomfield, Colorado Wang Laboratories, Incorporated, Natick,

- Massachusetts

- Washington Aluminum Company, Incorporated, Baltimore, Maryland

- John Wiley & Sons, Incorporated, New York, New York

The above list was compiled as of the time this book went to press.

· · · ·

,

## TABLE OF CONTENTS

ı

Page

| Multilevel Programming For a Real-Time System                                                                | 1   |

|--------------------------------------------------------------------------------------------------------------|-----|

| DODDAC - An Integrated System for Data Processing, Interrogation, and Display<br>W. F. Bauer and W. L. Frank | 17  |

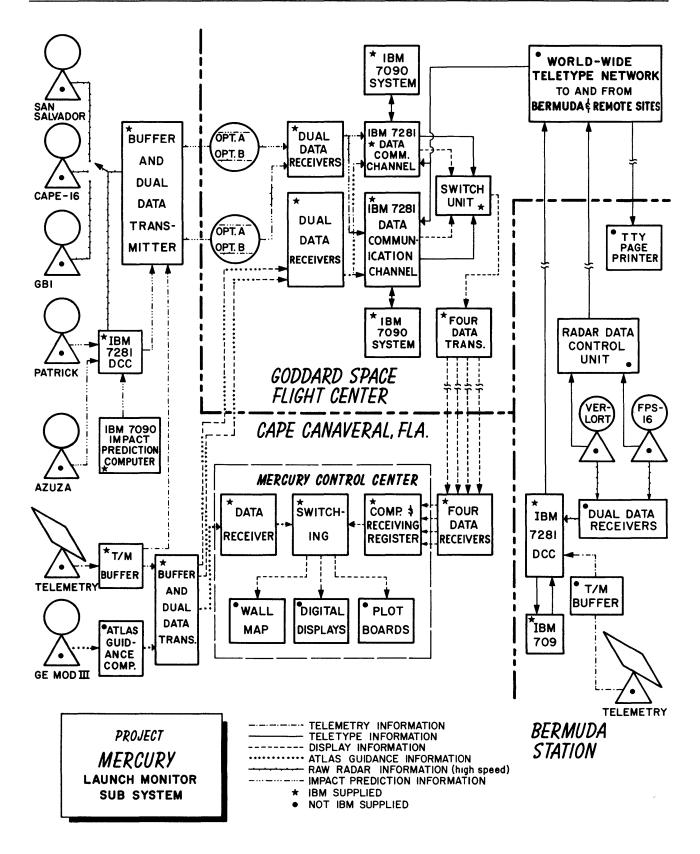

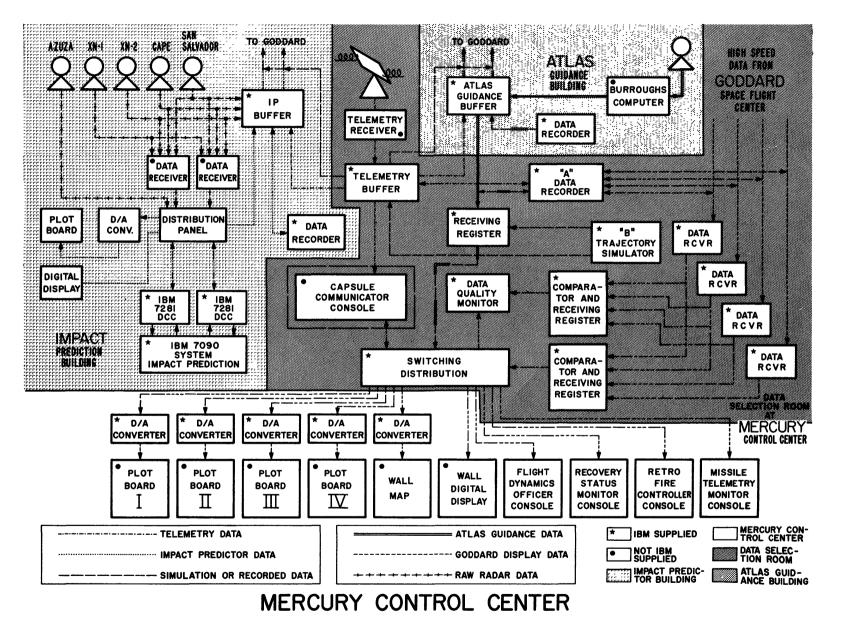

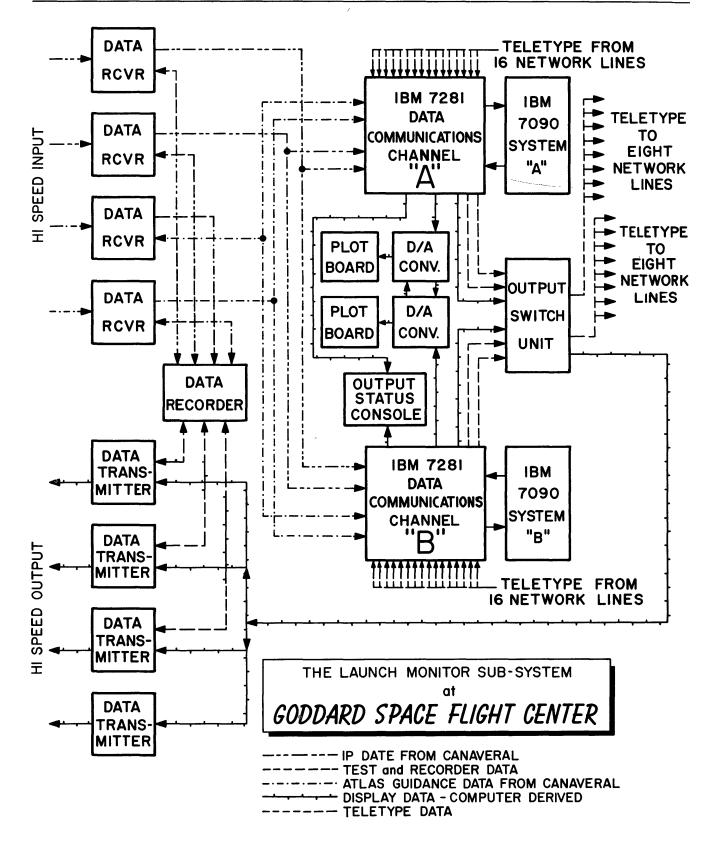

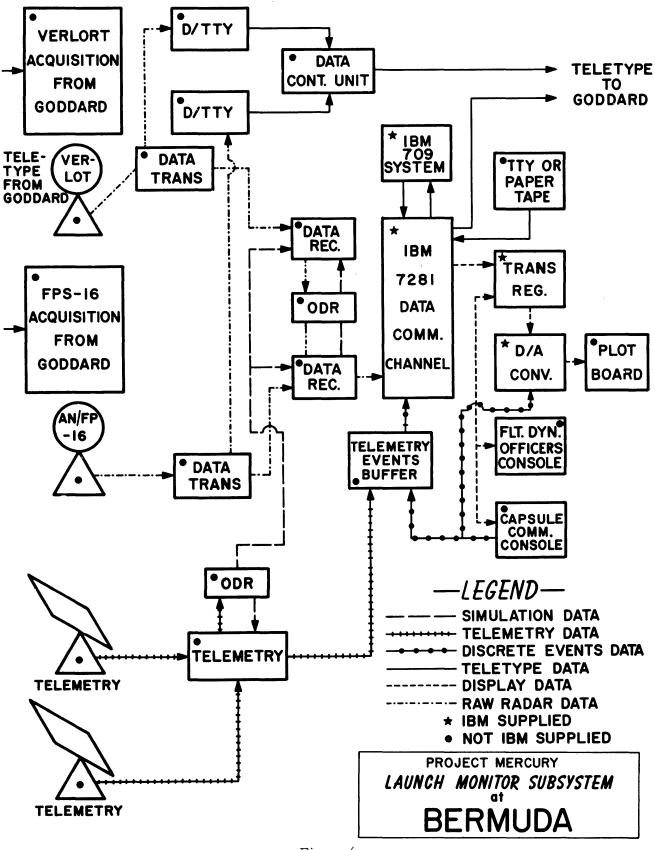

| Project Mercury Real-Time Computational and Data-Flow System                                                 | 33  |

| A Simulation Model for Data System Analysis                                                                  | 79  |

| A General Purpose Systems Simulation Program                                                                 | 87  |

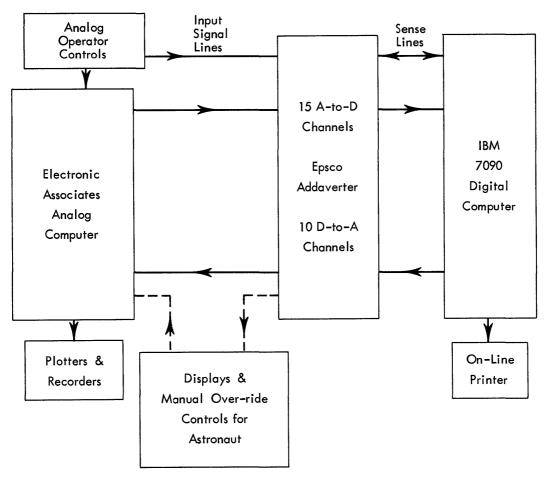

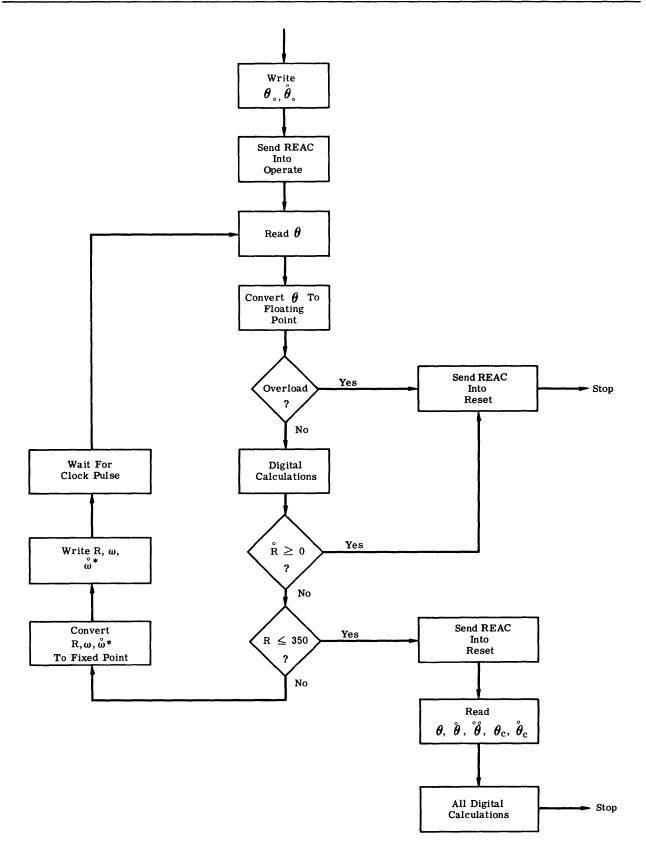

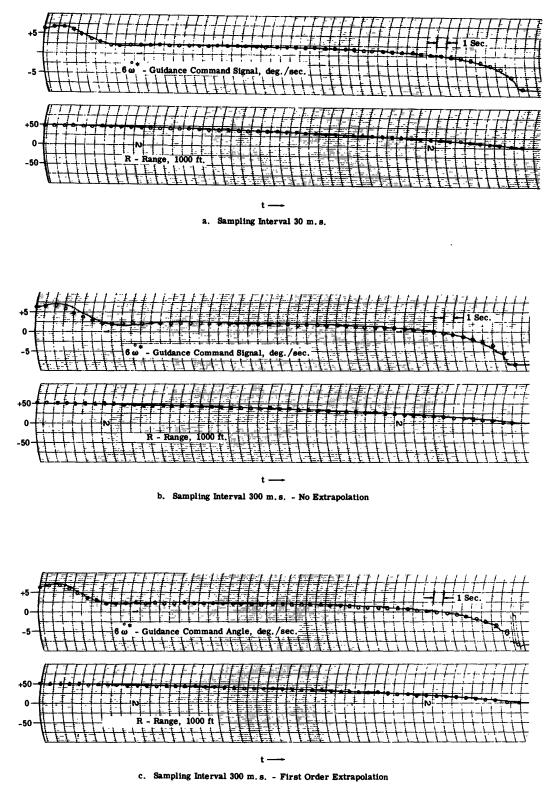

| Use of a Combined Analog - Digital System for Re-entry Vehicle Flight Simulation Dr. Allan Wilson            | 105 |

| Combined Analog - Digital Simulation Arthur J. Burns and Richard E. Kopp                                     | 114 |

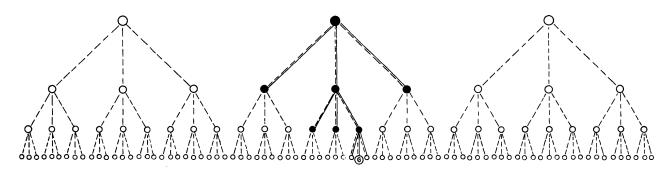

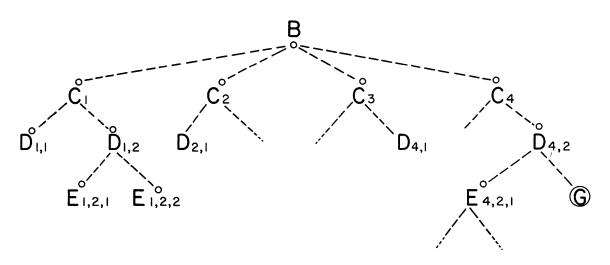

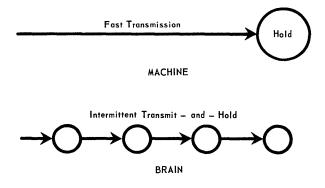

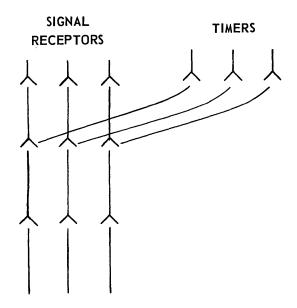

| CONTRANS - (Conceptual Thought, Random-Net Simulation) David Malin                                           | 124 |

| Digital to Voice Conversion                                                                                  | 135 |

| Card Random Access Memory (CRAM): Functions and Use                                                          | 147 |

| The Logic Design of the FC-4100 Data Processing System                                                       | 158 |

| A Versatile Man-Machine Communication Console<br>R. Green, P. Lazovick, J. Trost and A. W. Reickord          | 166 |

| Dataview, A General Purpose Data Display System                                                              | 174 |

| A Computer for Direct Execution of Algorithmic Languages                                                     | 184 |

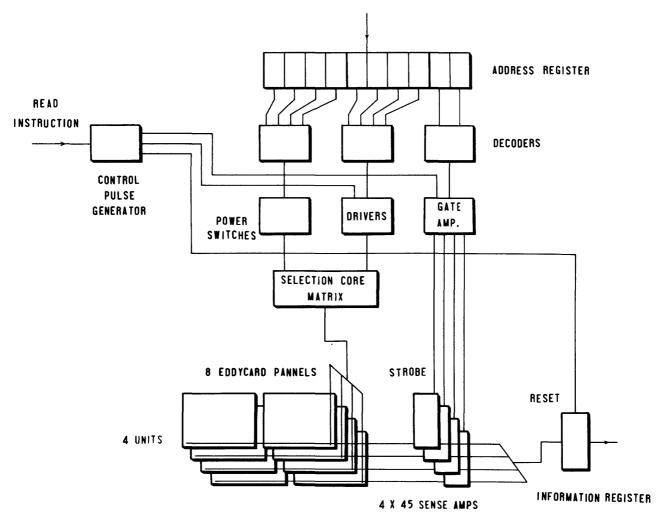

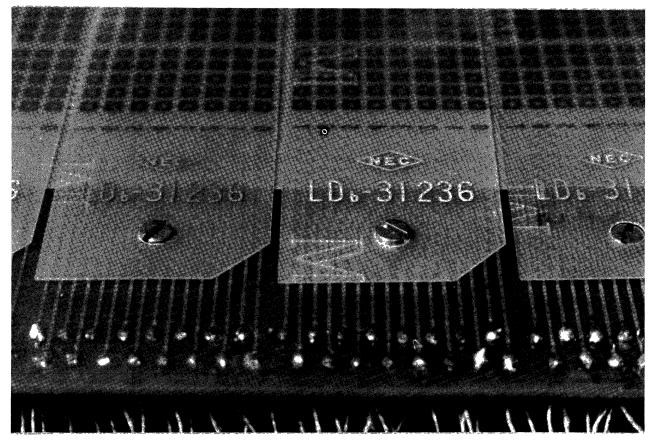

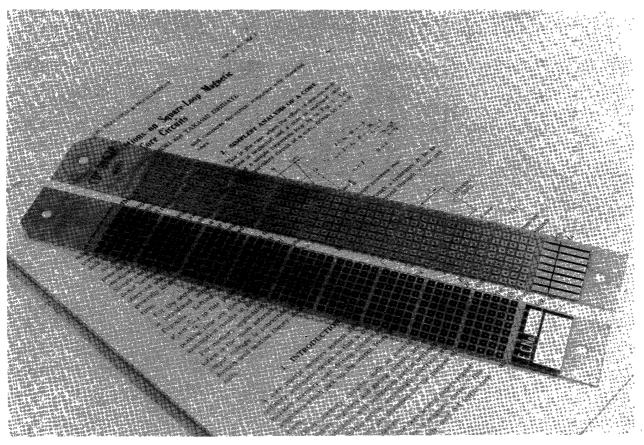

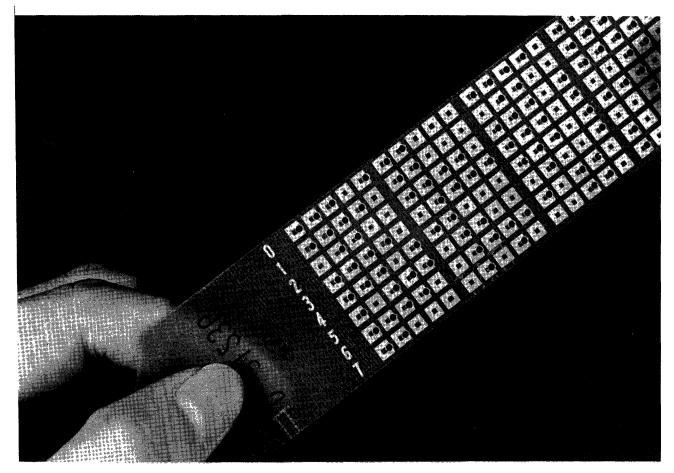

| Eddycard Memory—A Semi-Permanent Storage                                                                     | 194 |

| Digital Data Transmission: The User's View                                                                   | 209 |

| Tele-processing Systems                                                                                      | 213 |

| Communications for Computer Applications                                                                     | 219 |

| The Saturn Automatic Checkout System                                                                         | 232 |

### Page

| Information Handling in the Defense Communications Control Complex<br>T. J. Heckelman and R. H. Lazinski | 241 |

|----------------------------------------------------------------------------------------------------------|-----|

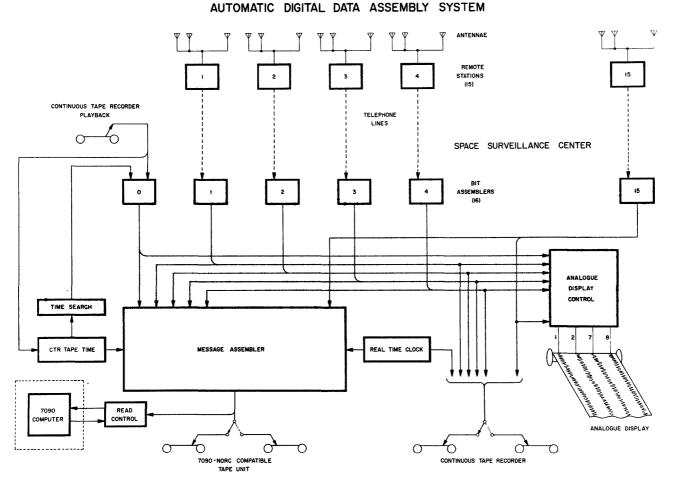

| An Automatic Digital Data Assembly System for Space Surveillance                                         | 257 |

| Four Advanced Computers - Key to Air Force Digital Data Communications System                            | 264 |

| R. J. Segal and H. P. Guerber                                                                            |     |

| The Atlas Supervisor                                                                                     | 279 |

| T. Kilburn, R. B. Payne, and D. J. Howarth                                                               |     |

| A Syntax Directed Generator                                                                              | 295 |

| S. Warshall                                                                                              |     |

| An Automated Technique for Conducting A Total System Study                                               | 306 |

| A. O. Ridgway                                                                                            |     |

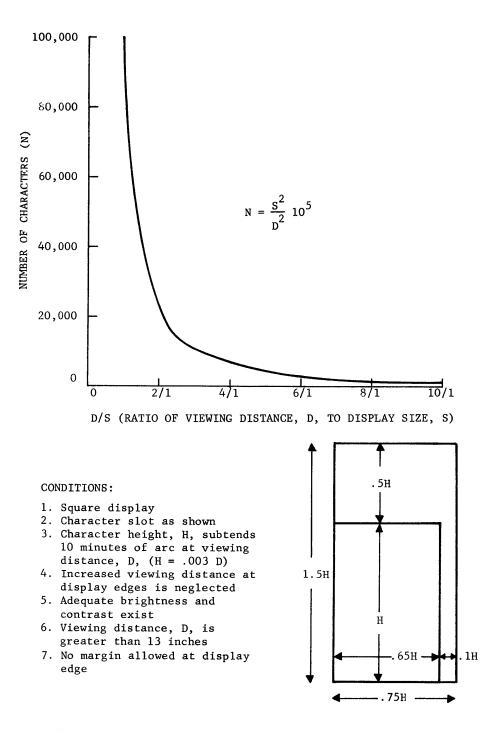

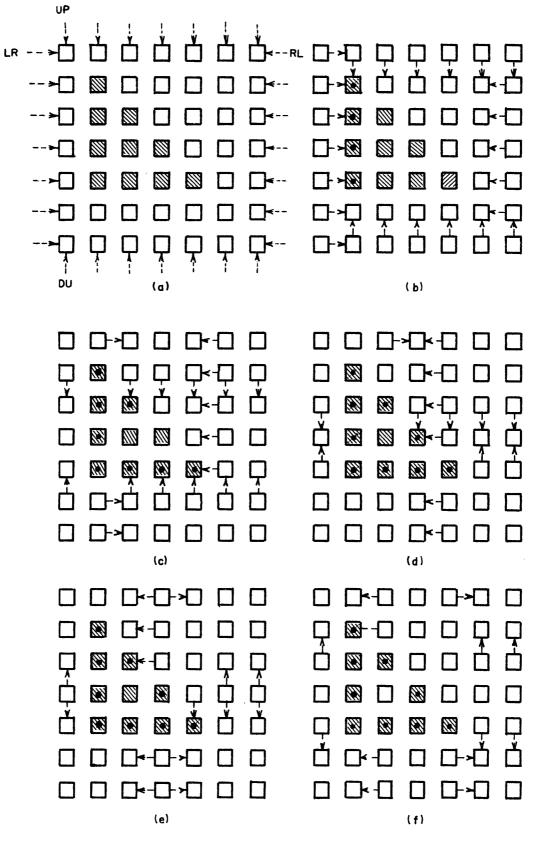

| Display System Design Considerations                                                                     | 323 |

| R. T. Loewe and P. Horowitz                                                                              |     |

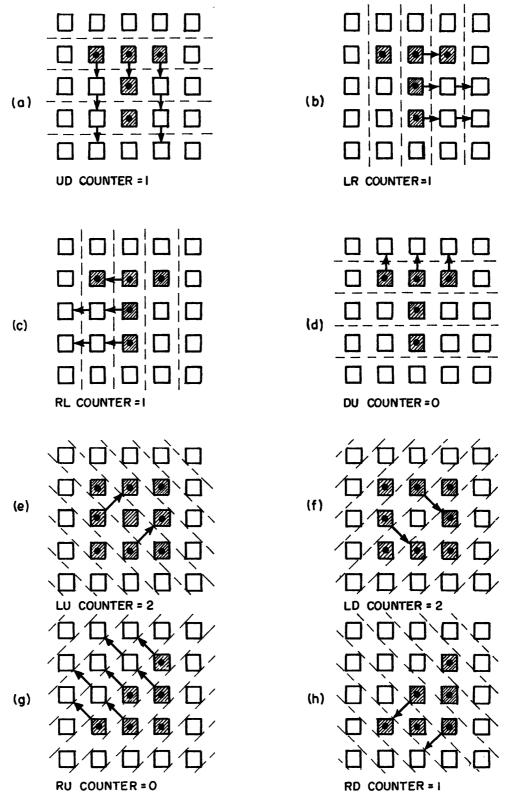

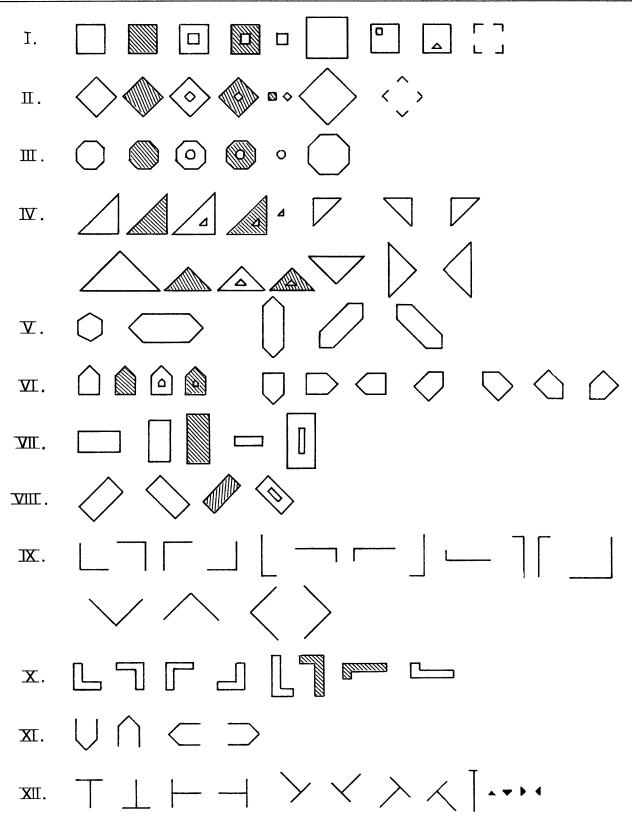

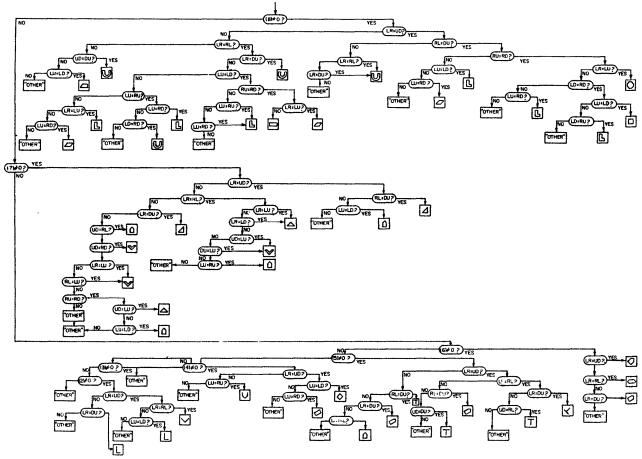

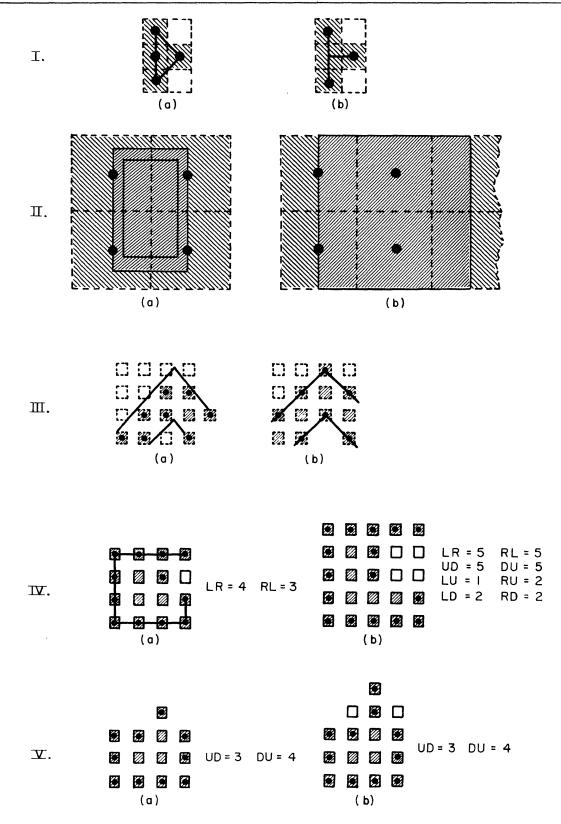

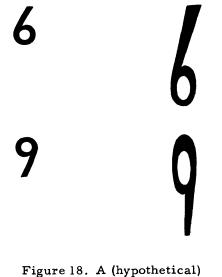

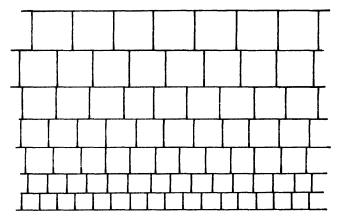

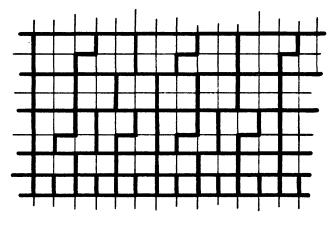

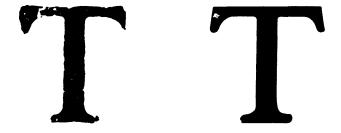

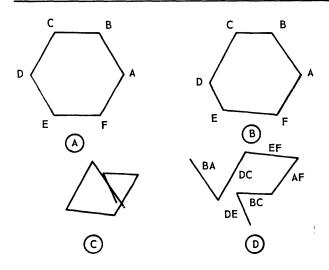

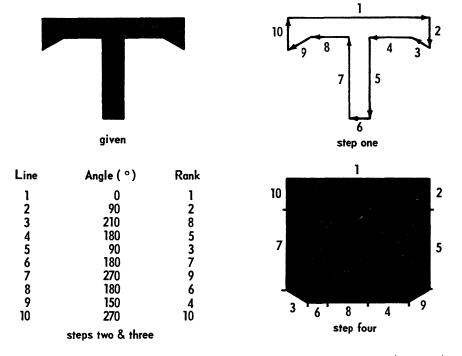

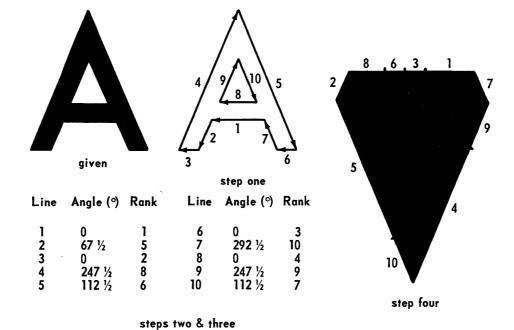

| Abstract Shaper Recognition by Machine                                                                   | 332 |

| M. E. Stevens                                                                                            |     |

| Chrysler Optical Processing Scanner                                                                      | 352 |

| D. N. Buell                                                                                              |     |

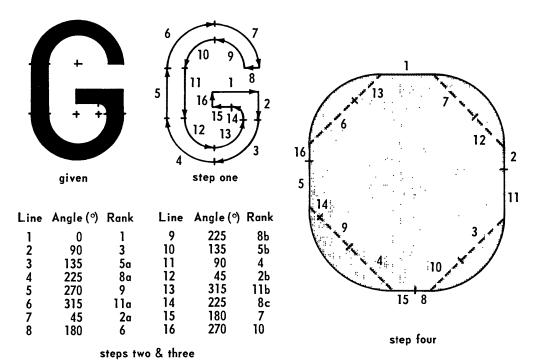

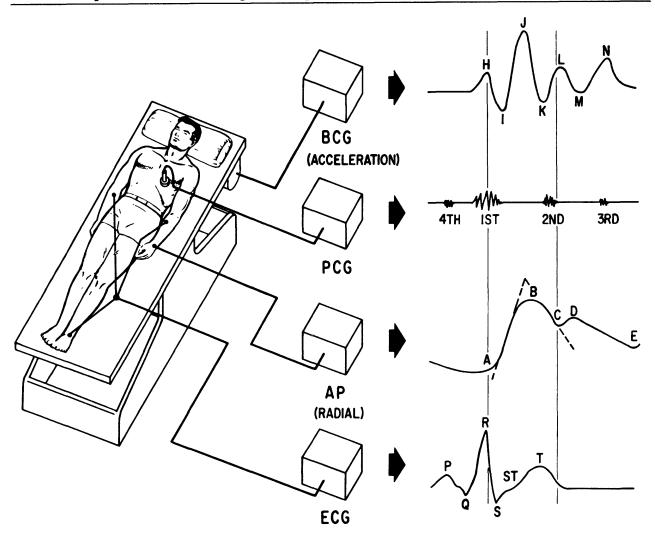

| Techniques for the Use of the Digital Computer as an Aid in the Diagnosis of                             |     |

| Heart Disease                                                                                            | 371 |

| C. A. Steinberg, W. E. Tolles, A. H. Freiman, C. A. Caceres, and S. Abraham                              |     |

|                                                                                                          |     |

7

## MULTI-LEVEL PROGRAMMING FOR A REAL-TIME SYSTEM

A. B. Shafritz Auerbach Corporation Philadelphia, Pa. A. E. Miller Auerbach Corporation Philadelphia, Pa. K. Rose Auerbach Corporation Philadelphia, Pa.

#### Introduction

Recent computer literature has given considerable attention to the problem of matching high-speed data processing equipment with low-speed input-output equipment. The solution most often presented is the use of multiple input-output processing equipment, allowing for an increased computation load that keeps the central processing unit active. While input-output equipment is operating on one part of the program, the processor is not waiting, but working on some other part. If the benefits of such a configuration are to be realized most fully, an efficient multiprogram system must be designed.

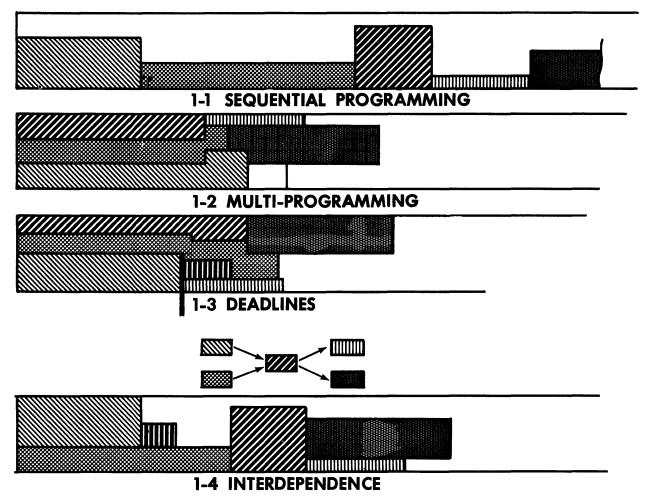

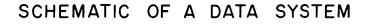

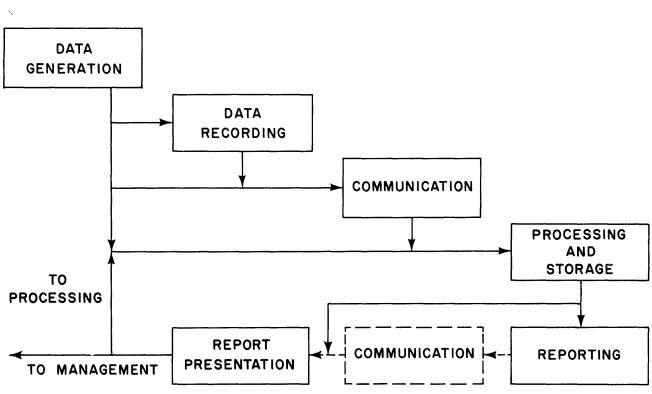

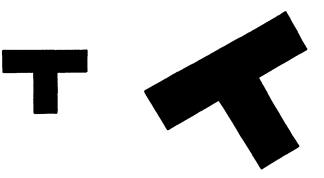

The efficiency that can be attained by multi-programming is suggested in Figure 1. The individual programs occupy only a fraction of a computer's capability, as indicated by the heights of the rectangles in the diagram. The assumption is that the central processing unit remains idle much of the time waiting for input data or access to output equipment in use. If the programs are carried out one after another, the total time (represented by lengths) is excessive (Figure 1-1, Sequential Programming).

One way to shorten this time is to give the computer some number of tasks to work on at once, and let the computer divide its time equally among them (Figure 1-2, Multi-Programming). Such a mixing technique might provide for the possibility of one task's not requiring its full fraction, and for use of this additional time by one of the other programs. When any program is finished, another is begun, so that the computer is kept busy as long as work is available. Under certain circumstances, this lack of idle time may be an adequate criterion of efficiency.

Real-time problems introduce a feature that is easy to recognize, but may be quite difficult to mechanize. If one or more programs have deadlines to meet, they might be given a greater share of the computer's time without reducing the overall efficiency (Figure 1-3, Deadlines). A collection of deadlines for many programs might easily prove incompatible, and call for compromises that take into account the severity of the penalty for transgressing each.

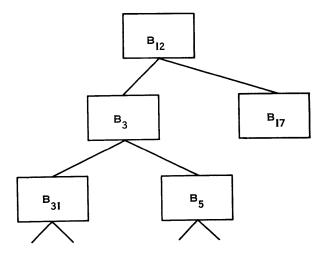

Another complication in multi-programming is that of interdependence of programs (Figure 1-4), Interdependence). In many important applications, the units to be scheduled are not independent programs, but parts of one major program. Any one of them may require the completion of others before it can begin. This program, in turn, may be a prerequisite for still others, in which case the efficient approach might be to carry it out promptly rather than have it share the computer's attention with other tasks.

When a multi-programming task involves both deadlines and interdependence, it becomes a challenge to the programmer. The modern computer features permitting the

Figure 1. A Problem in Programming.

use of efficient multi-programming techniques do not, by themselves, solve all the problems. It is our concern in this paper to consider a programming technique which makes use of different levels of processing to take full advantage of the multi-programming capabilities of these computers. This technique has been used to varying extents on several projects by our programming staff. It is best described by tracing the development of a multi-level programming task through a particular problem. However, we will try as we go along to abstract the general features of the problem that make such an approach desirable.

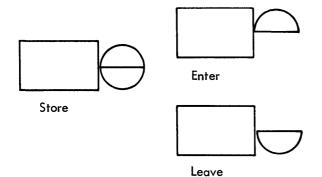

#### Elements of a Store-And-Forward Communication System

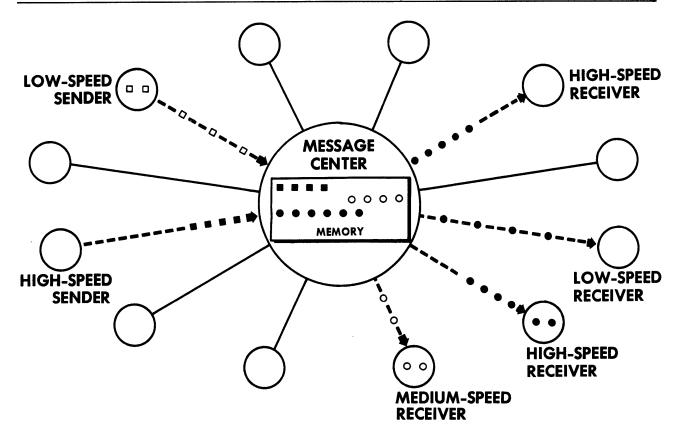

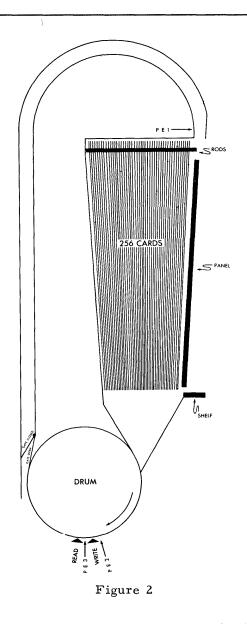

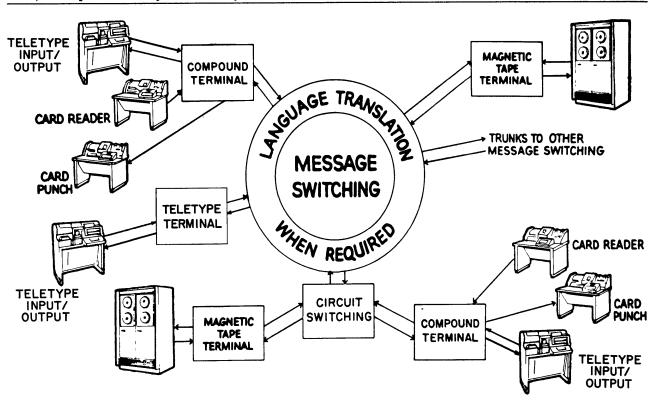

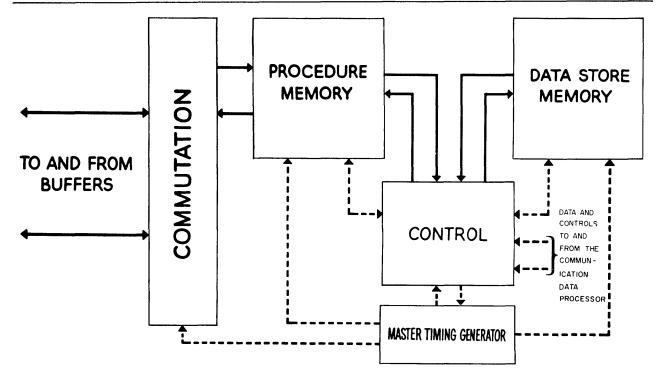

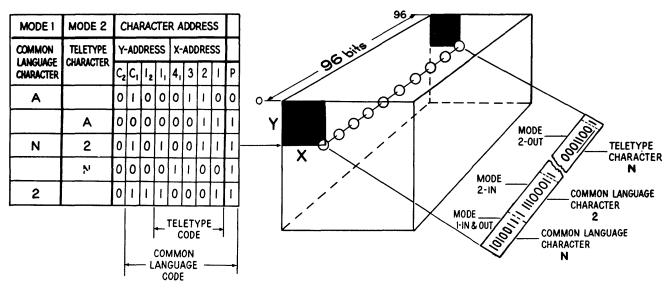

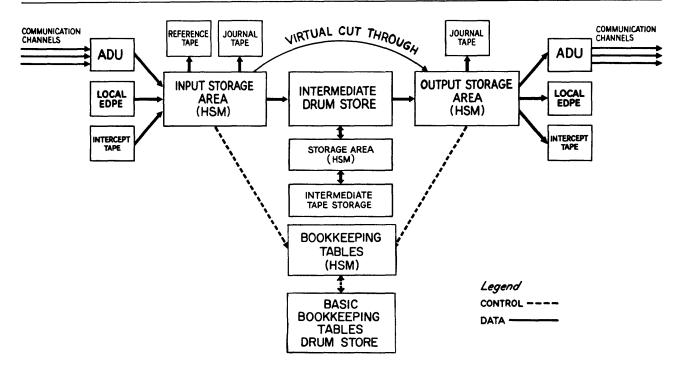

The task at hand is to program a highspeed data processor to operate a Store-And-Forward Communication System. As Figure 2

shows, the Communication System is made up of a message switching center connected by two-way channels to a number of subscriber terminals. Messages from these subscribers are sent to the center, at will, to be transmitted to addresses at the earliest opportunity. One message may require transmission to several destinations. The memory at the center stores a message as it is received. The entire message is then retained in memory until the last transmission has been completed. Each transmission of a given message can be at a different time, and at any of a number of specified speeds. In the course of transmitting copies of a message, the computer may be called upon to translate the message from one code and format to another. The system calls for first-in first-out service, with complications that necessitate extensive processing.

Multi-Level Programming for a Real-Time System / 3

Figure 2. Store-and-Forward Communication System.

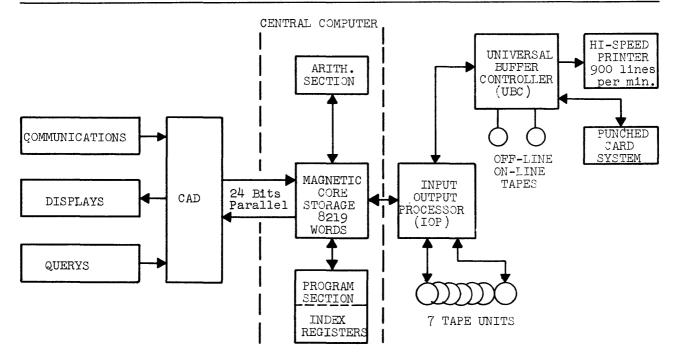

#### **Equipment Configuration**

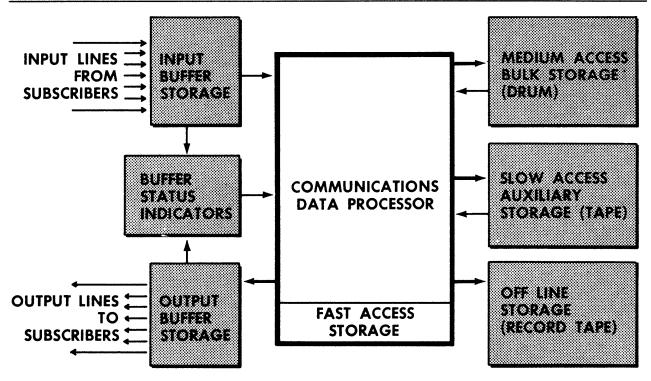

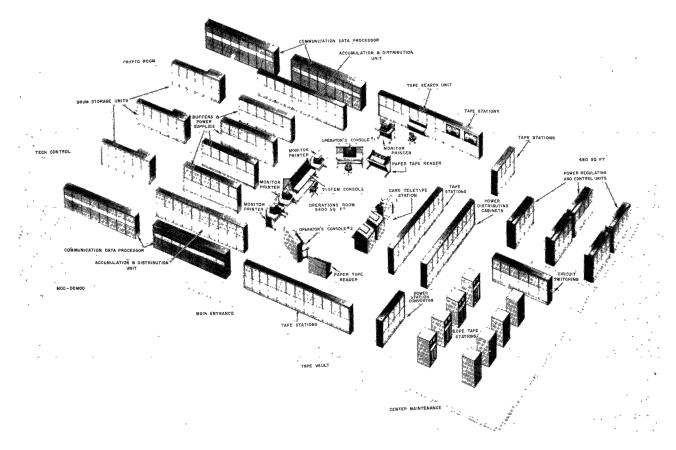

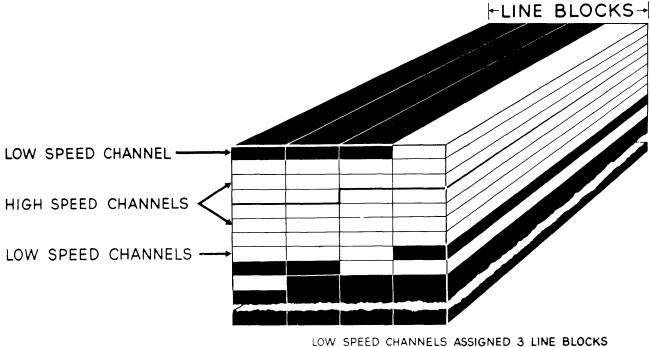

Figure 3 shows a possible arrangement of the main equipment in the message switching center. Input buffer storage, in the form of a coincident-current memory (or a highspeed drum), is provided to receive the successive characters of each incoming message and collect them into message sections. Logically, a separate buffer is associated with each input line, the size of the buffer depending on the speed of the line. In this system it is assumed that each buffer is capable of holding at least a few seconds of traffic. The communications processor is responsible for servicing each buffer often enough so that the buffer never becomes full. If this responsibility is met, the total transmission rate is limited only by the line capacities, and the processor service is effectively continuous. If the processor under certain peak traffic conditions cannot get around to a buffer fast enough, the penalty paid is a momentary forced traffic slowdown that holds up the subscriber.

The output is similarly buffered, with the computer unloading message sections to be transmitted at the receiver's speed. The computer's responsibility is to keep output buffers from "running dry" as long as there are messages for the associated lines. The buffer status indicators, controlled by the two sets of buffers, indicate to the processor the contents of each portion of the buffers.

The processor has its own high-speed, random-access memory, and for the purposes of this paper the entire operational program and associated bookkeeping tables are assumed to be stored therein. The processor also operates several other devices that provide bulk storage with a more limited access. A set of drums constitutes the main message store. (This function might be accomplished with discs or other media, but it will be convenient to use "drum" as a short name for bulk storage in the remainder of this paper.) Magnetic tapes back up the drum with auxiliary storage space to handle heavy message backlogs which might occur at peak periods, or when one or more receiving

Figure 3. Message Switching Center.

stations are closed down. One tape unit is used for "off-line storage" that is not retrieved in the normal on-line operation. This is the record tape, on which a copy of every message section received is written, with enough other data to give a complete record of the traffic through the system.

The drums, tapes, buffers, and buffer status indicators are all treated as asynchronous peripheral devices by the processor. The processor gives them instructions to transfer information into or out of its high-speed memory, and then goes about its own business while the peripheral devices are operating. Several peripheral devices may operate simultaneously, along with the processor's central processing unit. It is the coordination of these asynchronous operations, together with the interweaving of the processing, that constitutes the problem under consideration. It is assumed that the processor has the ability to interrupt the main program upon the termination of an inputoutput operation. Such a capability is available, to varying degrees of sophistication, in most of the latest large-scale computers.

#### Interrupt Feature

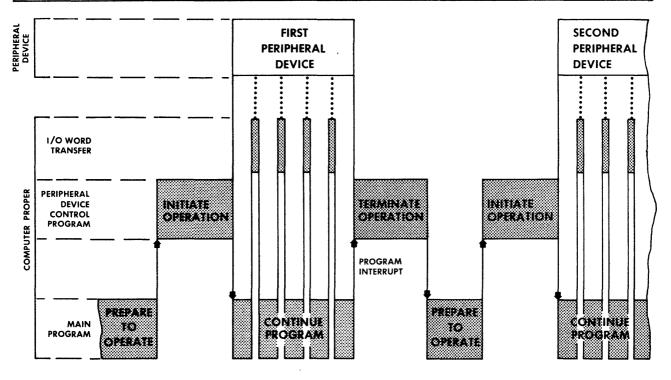

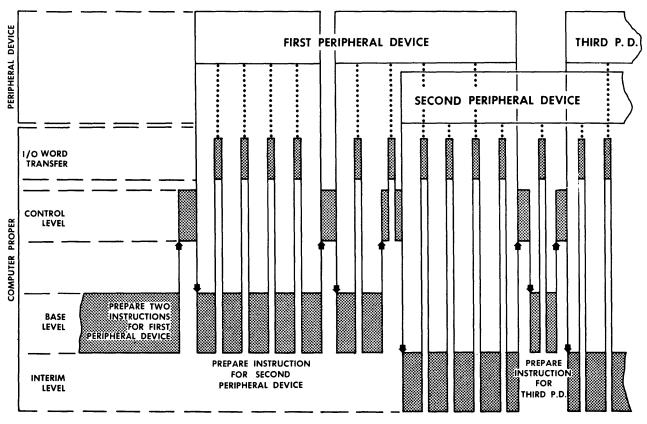

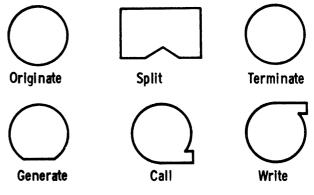

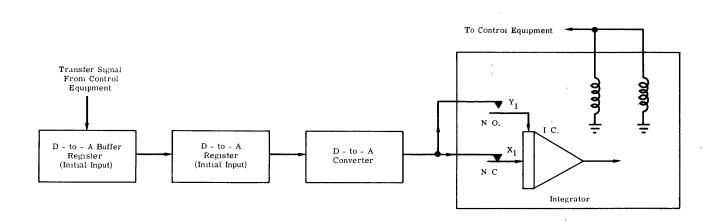

Figure 4 illustrates the use of the interrupt feature and also suggests the concept of

different programming levels. In the example presented, the main program performs data processing or logical operations in preparation for the operation of the first peripheral device, and then transfers control to the program level labeled "peripheral device control" to initiate the operation of the device. After the initiation, the main program continues with other tasks. During the operation of the peripheral device, brief periods of main frame time may be lost when words are transferred between the computer memory and the peripheral device. At the termination of the peripheral device operation, an interrupt transfers the program back to the peripheral device control level to perform any procedure associated with the termination of the operation (such as error checks or the storing of the contents of certain registers). Following the termination process, it is determined that a second peripheral device should be operated, and a similar sequence of actions is carried out for the second peripheral device operation. The concept of processing levels is developed more fully in the latter part of this paper.

#### **Computation Cycle**

In this, as in most real-time systems, there are a number of basic functions that

Figure 4. Interrupt System.

must be executed periodically. Ideally, each function should be carried out at its own best frequency. But to assign the lengths of periods independently would greatly complicate program control as well as entail the risk of irregular computer loading. At one time many functions might be demanding computer time simultaneously, while at another time the computer might be forced to remain idle for some period when all operations were out of phase. This could occur even under heavy traffic loads, and reduce the effective throughput of the system.

The compromise that is usually made is to establish a computation cycle, with a frequency that is close to that of as many of the basic functions as possible. Those that require more frequent execution may be done more than once in a cycle, and those whose periods should be longer may be programmed to occur in one cycle and then skip one or several cycles. If there are enough of these unusual periods, a complex of interrelated cycles may be employed.

Our cycle is concerned with two types of processing; one associated with input and the other with output. Briefly, the input processing consists of transferring message sections from the input buffer storage (and perhaps from tape) to the computer high-speed memory, storing the message sections on the drums and record tape, and performing associated bookkeeping operations. Conversely, the output processing consists of retrieving message sections from the drums, processing these, and writing them into output buffer storage and perhaps onto tapes.

#### **Batch Size**

It is important to estimate the size of the character batch, both in and out, to be handled in a cycle. The capacity of the inputoutput buffers does not in itself fix the cycle. It is true that every buffer should be serviced within the number of seconds for which it can hold traffic, but to serve all at once would call for an excessively large capacity in high-speed memory. At the other extreme. a small internal memory would tax the peripheral devices and the computer proper. For the drums, increasing the batch size helps the latency problem; for tapes, larger records may be written, cutting down on the start-stop wastage; and for the computer, fewer tests, setups, and general bookkeeping operations have to be performed.

In seeking the optimum batch size, the programmer must examine the system requirements, and in so doing he becomes

confronted with the complication of "worstcase" design. The concept of an "average" traffic flow for the system would be meaningless. The message switching center must operate efficiently at "peak" loading, and must therefore be over-designed for average traffic conditions. The design should be such that correct operation can be maintained under the worst conditions that are within the realm of possibility. The processor must not break down even if all inputs lines attempt to send messages at their maximum rates simultaneously. It is not economical, however, to base the whole design on such remote possibilities. Statistics should be gleaned on the overall picture of traffic flow, to provide a description of a "reasonable worst-case." This should be chosen as a level that will be exceeded so seldom or so

briefly that some inconvenience can be tolerated when this occurs.

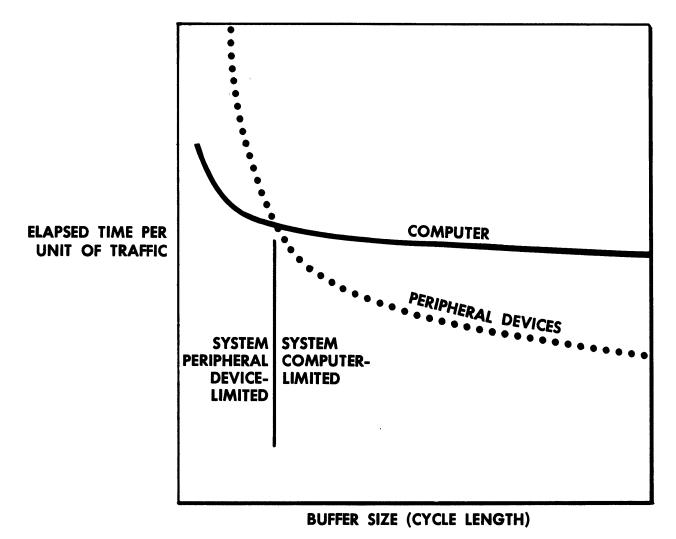

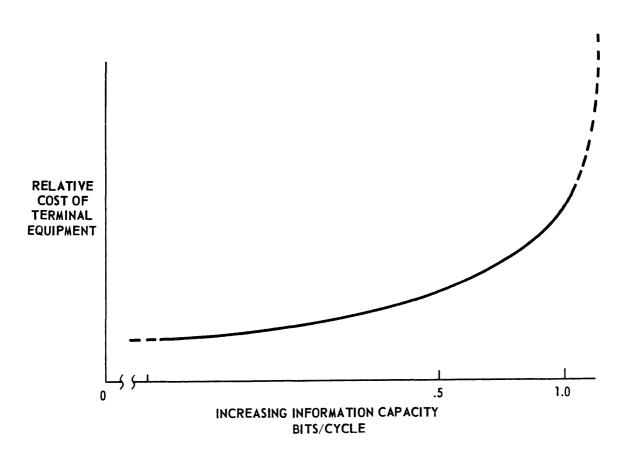

From the "reasonable worst-case" conditions, it should be estimated how much processing time is required for each character going through the system. This is divided into two categories, peripheraldevice time and computer time, and both are functions of batch size. Figure 5 shows these functions very much oversimplified. They are not necessarily monotonic nor even continuous: they depend on the equipment complex, techniques used, and many other factors. A batch size somewhere near where the two curves cross will produce an efficient and economical cycle. It is assumed that the equipment complex is well-suited to do the job at hand, and the batch size so chosen will afford an adequate excess capacity.

Figure 5. Cycle Length Determination.

#### Tasks to be Performed

With a size chosen for the batch, the actual work of programming begins. A list is made of all the tasks that are normally performed in an input-output cycle. It is helpful to have estimates of the time they will require, and this involves three parts: the computer time to prepare the data, the time for the peripheral device to operate, and the computer time to terminate the task. These time estimates need not be well defined; the programmer will want to know general orders of magnitude, or in some cases just comparisons, such as that a tape operation will not take as long as a drum operation.

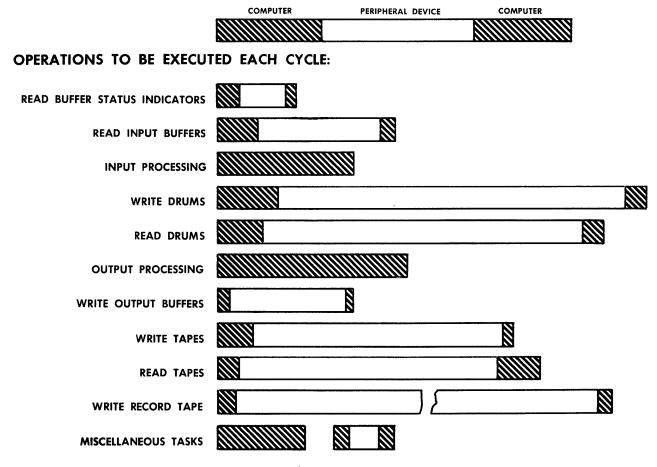

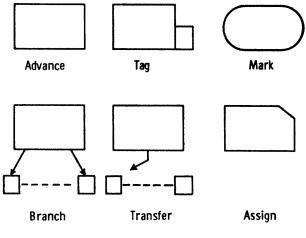

The tasks for this program, as shown in Figure 6, are 11 per cycle (not necessarily in order) as follows:

- 1. <u>Read Buffer Status Indicators (B.S.I.)</u> to determine the contents of each input and output buffer.

- 2. <u>Read Input Buffers</u>. The computer portion of this task includes examination of the results of Read B.S.I. to select the input buffers to be serviced.

- 3. Input Processing. This operates on the message sections transferred by (2) and involves the updating of tables in the system that indicate when messages arrived, what their destinations are, and the like. It is set apart from the processing required to prepare to write drum.

- 4. Write Drum. This task is kept to a minimum of what must be done between the time the data arrives in high-speed memory and the time the drum write order begins. While the writing occurs, the information remains in high-speed memory and can still be accessed, although it must not be changed while the asynchronous writing is under way. Any processing that can meet the requirements is made a part of input processing rather than a part of the write drum operation.

- 5. <u>Read Drum</u>. This task calls for decisions of what to read, based on buffer status information associated with the output buffers. And again, any of this processing that can be, is relegated to output processing.

- 6. Output Processing. This involves selection of new messages for output lines, minor message format changes,

and bookkeeping procedures. It includes any operation on output data that is not directly associated with the operation of a peripheral device.

- 7. Write Output Buffers. This does not itself involve much computer processing; the other tasks preceding it complete most of the decisions on what to write.

- 8. Write Tapes.

- Read Tapes. These two tasks are normal and may occur in any cycle, but will probably not go on so regularly as

through (7). Part of the terminal processing required after reading tapes is the decision what to do with the data read. As tape is used in this system, messages from tape may go (via the computer memory) to the drum or onto another tape.

- 10. Write Record Tape. This is the longest peripheral operation in our system: the recording of every piece of an incoming message with additional data to identify sources. (From cycle to cycle, the pieces of a message maybecome separated on record tape.) While writing on record tape is being done, other tasks using the same data can be performed; thus this task may go on throughout the cycle.

- 11. Miscellaneous Tasks. This list of 11 tasks is greatly oversimplified, omitting even many regular tasks actually required in a message system. Tasks (1) through (10) can be thought of as including all those operations that must be totally carried out each cycle. "Miscellaneous tasks" can be thought of as those functions taken out of the main stream and made to extend over a number of cycles to regulate the cycle length. An example of such a function is message translation on a characterby-character basis. This can be a time-consuming process, but it will be required for relatively few messages. When it is necessary, it may delay the individual message involved, but others in the batch should be processed promptly. For this reason, message translation is not made a part of output processing. Miscellaneous tasks would also include non-periodic operations performed by the computer on request, or tasks such as recording of statistics,

which might be hourly or daily rather than once per cycle. Miscellaneous tasks may involve operating peripheral devices, possible even some that are not included in normal operations.

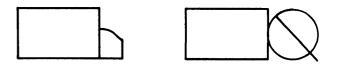

#### Interrelationship Between Tasks

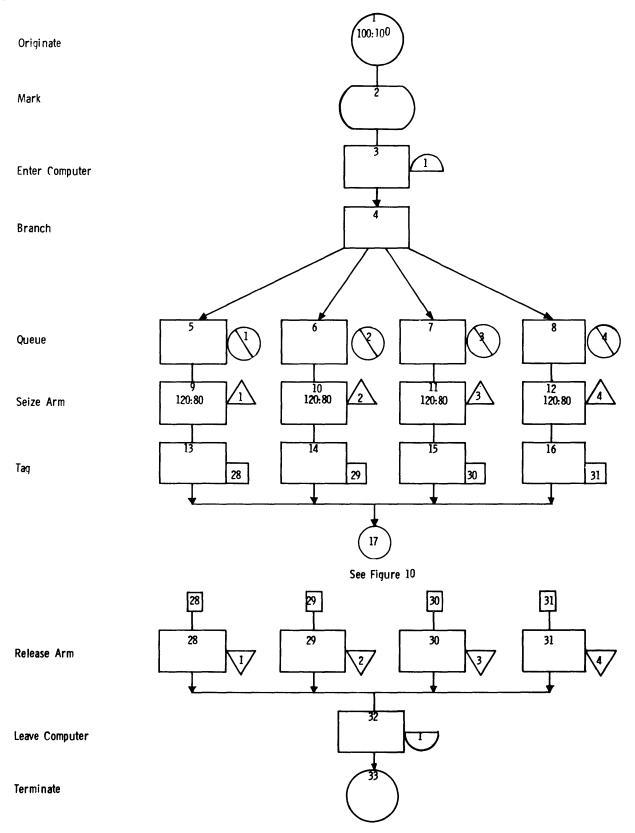

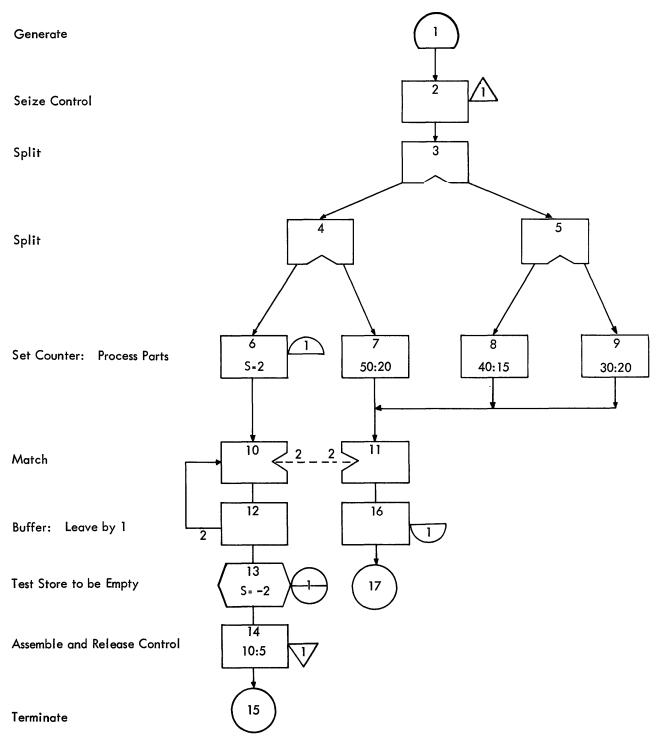

In a fixed inflexible program, these tasks might be arranged in arbitrary order to constitute the program. In multi-level programming, the order of their execution can vary from one cycle to the next. But general limits must be established. For this purpose, it is required to determine which tasks are prerequisite to each other. Each task must wait until the completion of others, either in the same cycle or in the previous one, as shown in Figure 7. The eight input-output functions are the present concern; the three processing functions are treated later.

The reading of buffer status indicators (B.S.I.) must take place after the write output buffer operation in order that the indications be up to date. In general, prerequisites of a

write order are the tasks that provide data to be written. A read order must wait until the completion of the write orders that clear out what was previously read. It should be noted that this program assigns a fixed buffer space to each input device; data are rearranged (if required) within an input buffer area and transferred from there to the output divices by means of the write instructions.

The establishment of prerequisites leads to a re-ordering of the list of tasks into a cycle. The sequencing may involve some "cut-and-try" work, but can be guided by a few well-defined principles:

- 1. Two operations with the same prerequisites (e.g., read drums, read tapes) should be in juxtaposition in the program. The one that serves as a prerequisite for the greater number of subsequent operations should be first.

- 2. When the prerequisites for one operation are a subset of those for another, the former should precede the latter (as write output buffers, write tapes).

Figure 6. List of Tasks.

| TASK                                      | PREREQUISITES                                                  |

|-------------------------------------------|----------------------------------------------------------------|

| READ BUFFER<br>STATUS INDICATORS (B.S.I.) | WRITE OUTPUT BUFFERS                                           |

| READ DRUMS                                | WRITE TAPES, WRITE DRUMS, READ B.S.I.                          |

| READ TAPES                                | WRITE TAPES, WRITE DRUMS, READ B.S.I.                          |

| READ INPUT BUFFERS                        | WRITE TAPES, WRITE DRUMS, READ B.S.I.<br>AND WRITE RECORD TAPE |

| WRITE RECORD TAPE                         | READ INPUT BUFFERS                                             |

| WRITE OUTPUT BUFFERS                      | READ DRUMS                                                     |

| WRITE TAPES                               | READ DRUMS, READ TAPES                                         |

| WRITE DRUMS                               | READ DRUMS, READ TAPES, READ INPUT BUFFERS                     |

Figure 7. Ordering by Prerequisites.

3. The circularity of the cycle should be kept in mind, and its "beginning" left flexible. In this list, Read B.S.I. is an obvious beginning, being prerequisite (by transitivity) to all other operations. But Read B.S.I. does not necessarily have to wait for the end of the previous cycle. In other words, one cycle can begin before another has ended.

In the problem under consideration, the cycle determined according to these principles divides itself into a read portion and a write portion. The central processor "inhales" information from all input sources, and after proper processing, it "exhales" into all output destinations. This gives the opportunity for information to be transferred from any peripheral device to any other during one cycle. The "read" and "write" portions of the cycle are not to be confused with system input and output. From the viewpoint of the central processor, all other parts of the system are external. Reading an input message from its buffer is the same as reading a message from the drum when that message is on its way <u>out</u> of the system. The input and output sub-cycles are fairly simple when considered separately.

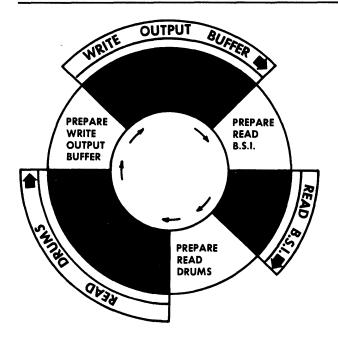

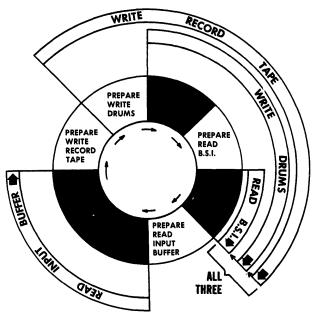

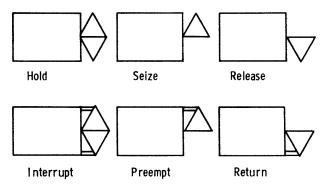

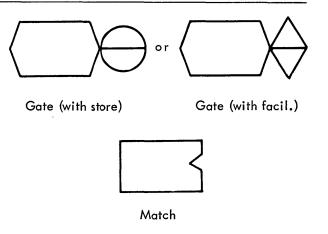

#### Output Sub-Cycle

As Figure 8 shows, the output operation has three parts that are mutually prerequisite and thus determine a cycle. Each of the three parts is done by a peripheral device. When each operation is finished, a program interrupt occurs, and the computer prepares for the next step. For simplicity in this and following diagrams, some steps of the program have been removed. The computer operations required for termination of any peripheral device operation are assumed to take place as soon as an interrupt occurs. Then the preparation for the next step begins. This is shown in one block on the inner ring, which represents operation of the computer proper. The cycle is expedited by keeping these intra-peripheral operations to a minimum.

Figure 8. Output Sub-Cycle.

It should be noted that the cycle (clockwise direction) is <u>not</u> fixed as to time. It proceeds as fast as the peripheral devices will allow, and may vary greatly in length. This is based on the simplified assumption that there is ample time to carry out all the required processing tasks during the peripheral device operations.

The black areas on Figure 8 represents time that the computer can spend on all its other functions. Some of these operations are scheduled into a larger cycle, as shown on subsequent figures. Others occur at variable times in the cycle, according to the time the processor has to work on them.

#### Input Sub-Cycle

Figure 9 shows the somewhat more complex input sub-cycle. Again, each interrupt is followed by termination operations and then the preparations indicated on the diagram. The prerequisities for reading the input buffer include the completion of three operations; write record tape, write drums, and read B.S.I. Generally these operations will not finish at the same time. The last of the three termination interrupts to occur initiates reading of the input buffers. When the previous operations are completed (whichever two they may be) the computer may perform the required terminal operations individually, but it will not go on to prepare

Figure 9. Input Sub-Cycle

read input buffer until all three are performed.

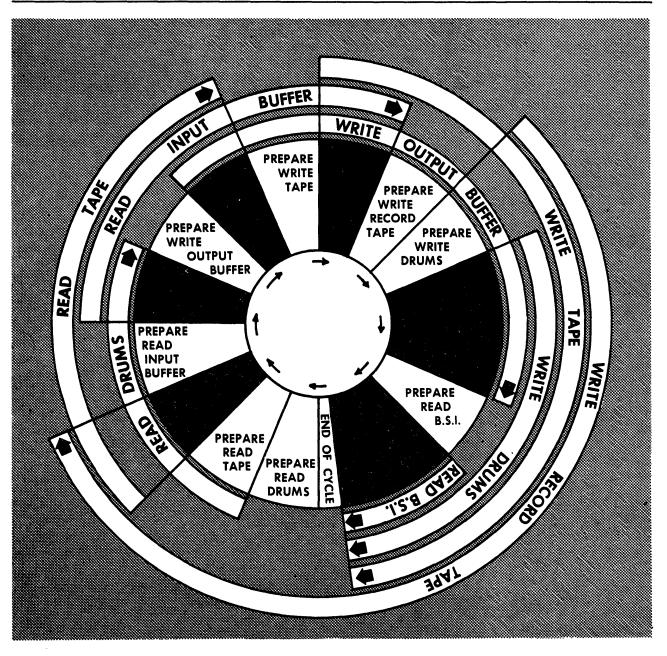

#### Input-Output Cycle

In Figure 10 the input and output functions are shown merged into one cycle. The computer steps required for one sub-cycle occupy some of the empty intervals in the other. There are still spaces left for input processing, output processing, and any other operations that use the computer but not peripheral devices. These are not scheduled at fixed times in the cycle, but executed as time permits, as will be explained later.

The time required by each peripheral device is so variable that these empty spaces may change size or even be eliminated. If a peripheral device operation is short or nonexistent, the interrupt will be early and the computer will not have to wait for it. There may even be a line-up of interrupts waiting for attention. The machine and program are designed to handle such situations.

Figure 10 has features added beyond the combination of the previous figures. The tape operations and preparations are shown, and an end of cycle checkpoint is included just prior to the read drums operation. The latter is a necessary safety feature in our variable cycle. It affords an interlock to insure that all the input processing, output processing, and scheduled miscellaneous

Figure 10. Input-Output Cycle.

processing have been carried out during the cycle. If the end of cycle routine finds that further processing remains to be carried out, the cycle is accordingly extended.

The end of cycle routine serves another purpose. If it finds that the cycle has been completed in an extra short time, it extends the cycle, permitting the program to do further miscellaneous tasks in the cycle rather then have the computer "spin its wheels" sampling buffers too frequently.

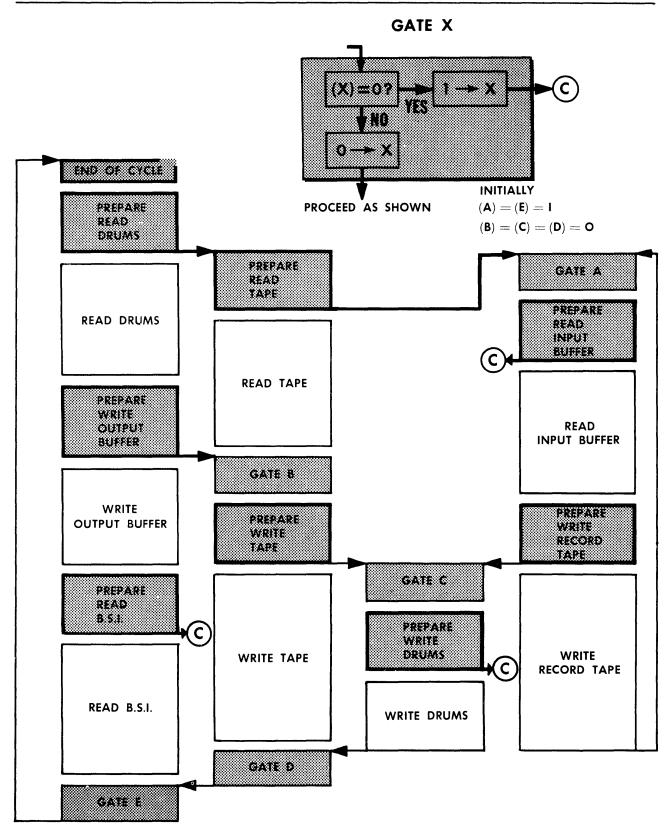

#### **Program Implementation**

It is only fair to point out that Figure 10 is not one of the steps in setting up the multilevel program, but rather an advance view of the result. The same steps are shown in Figure 11 as a flow chart that describes the cycle less graphically but more simply.

A program interrupt at the completion of a peripheral device operation generally leads directly to the initiation of some other

Figure 11. Input-Output Cycle Flow Chart.

peripheral device operation. The one completed is generally the last prerequisite for the other. Other prerequisites are implied by the sequencing of the parts.

One of the problems in this type of programming is to find ways to represent on diagrams the peripheral and computer operations. They are interconnected by initiations and interrupts, but operate asynchronously and do not lend themselves to representation with time as a fixed coordinate. Figure 11 uses some conventions to meet this problem. When the operation of a peripheral device begins, the computer goes on with some other task (shaded blocks). At such branch points, therefore, both branches must be taken. The computer and the device operate at the same time. When the peripheral device has finished its job, it initiates a new part of the program by the interrupt mechanism. This interrupt may sometimes not occur immediately, but it is most convenient to indicate it as the next step after the peripheral operation.

Figure 11 has five places where two branches meet, called gates. Each of these is a program step associated with a program control flip-flop. When either of the entrances indicated brings the computer to that spot, the flip-flop is examined to see if the other step has already occurred. If not, the state of the flip-flop is changed, and the Control Program determines the next function to be carried out. When the second of the two entrances occurs, the program proceeds as shown. Initially, the gates are set up in the same pattern that they reach at the end of each cycle when all jobs have been done.

When a cycle begins, the three read operations are promptly begun, and the computer goes to the Control Program, as indicated by the circled C. While the read operations are going on, the computer works on its other tasks, as will be described more fully later. As soon as the read input buffer operation is finished, the computer initiates the write record tape sequence, whether other reads are completed or not. Similarly, when the read drums operation is finished, the write output buffer operation is begun. When both drums and tapes have been read, the write tape sequence begins, and when all three read operations are over, the write drums operation is started.

Of the write operations, the write output buffer operation should be finished first. As soon as it is over, the indicators are read in preparation for the next cycle, which begins when all write operations are finished. The write record tape sequence may extend into the next cycle. However, it will not delay any of the read operations except the one for which it is prerequisite.

The length of this cycle, and even the sequence of events in it, depends on how long the peripheral operation takes. If the write tape sequence is long, other operations that do not depend on it are dispatched as soon as possible. Any of seven sets of operations may determine how long the cycle actually lasts. These can be seen by tracing through the diagram. The cycle length is the longest of the following seven combination (along with associated computer processing):

- 1. Read Drums, Write Output Buffer, Read B.S.I.

- 2. Read Drums, Write Tape

- 3. Read Drums, Write Drums

- 4. Read Tape, Write Tape

- 5. Read Tape, Write Drums

- 6. Read Input Buffer, Write Drums

- 7. Write Record Tape (portion remaining from previous cycle), Read Input Buffer, Write Drums.

Checking against the list of prerequisites will show that the cycle could not possibly be shorter than any of these sequences. Thus, the program does succeed in optimizing cycle length.

#### Non-Peripheral Operations

Both the cycle diagram and the flow chart (Figures 10 and 11) are concerned primarily with peripheral device operations, as the scheduling of these operations is the most critical part of the program under consideration. It is also important to incorporate efficiently the other operations, such as input and output processing, that must be performed during every cycle. On the cycle diagram, blank spaces in the computer ring indicate when these operations are carried out. On the flow chart, entrances to these portions of the program are indicated by a circled C. This represents transfer to a specific part of the control program, which takes place at three times in the program, and also any time one of the gates is found "closed."

Upon transfer to this location, the processor examines a list of tasks, arranged according to their prerequisites like the peripheral device operations already considered. The first item on the list is advance preparation of peripheral device orders. This preparation is done in advance whenever possible, in order to expedite later parts of the program. When all that is possible has been done (or immediately if no such operations were ready to be done), the program continues to the next time. It goes on through input and output processing, and any other tasks that need to be performed once per cycle, doing as much of each one as is possible at the time.

All of these operations are subject to interruption when a peripheral device completes one of its tasks. After an interruption, the steps to terminate the peripheral operation will be dispatched. Then the task that was interrupted will be finished, and finally the processor will go back to the beginning of the list again. If any advance preparations, or other operations previously passed by, have become possible as a result of the operation just completed, they will be done next. The list is arranged in preferential order, with the tasks that are prerequisites for other operations considered first.

If the program reaches the end of cycle indication with some tasks on this list not yet done, the next cycle will be held up until they have been completed. This situation will not generally occur unless requirements for processor time exceed those for peripheral devices. Normally, the program will catch up on these operations frequently during the cycle, and have time to go into other operations of lower priority.

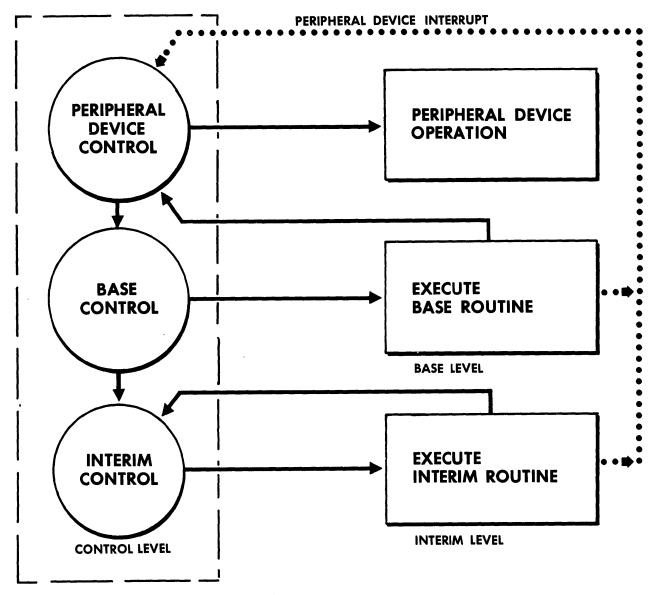

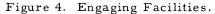

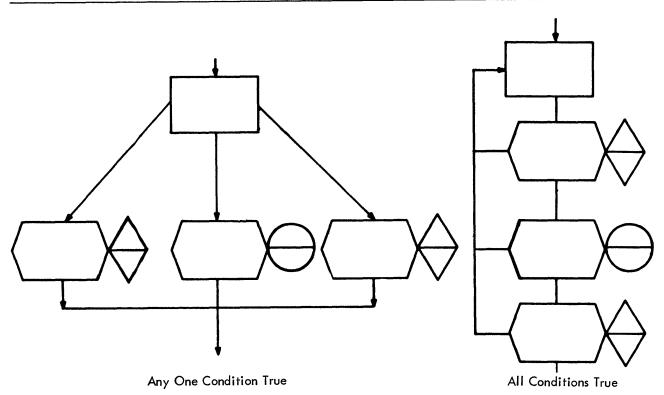

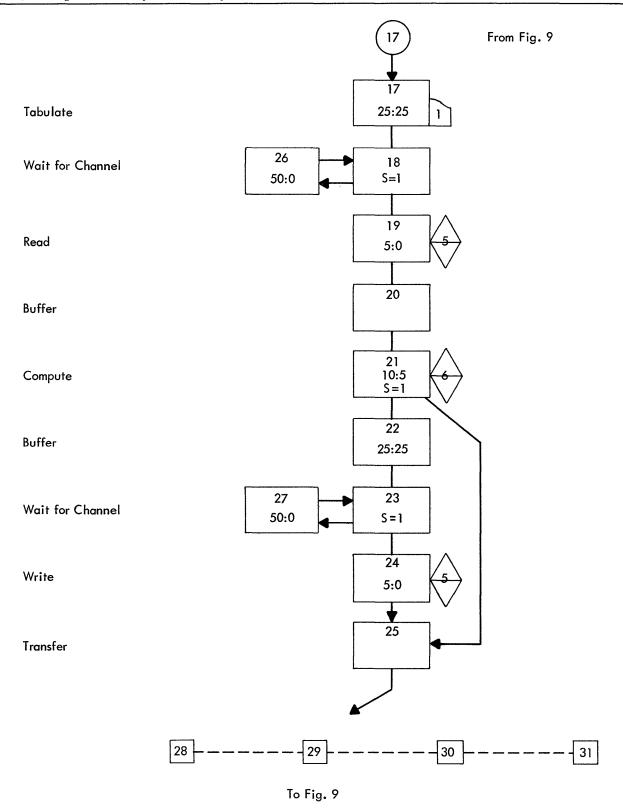

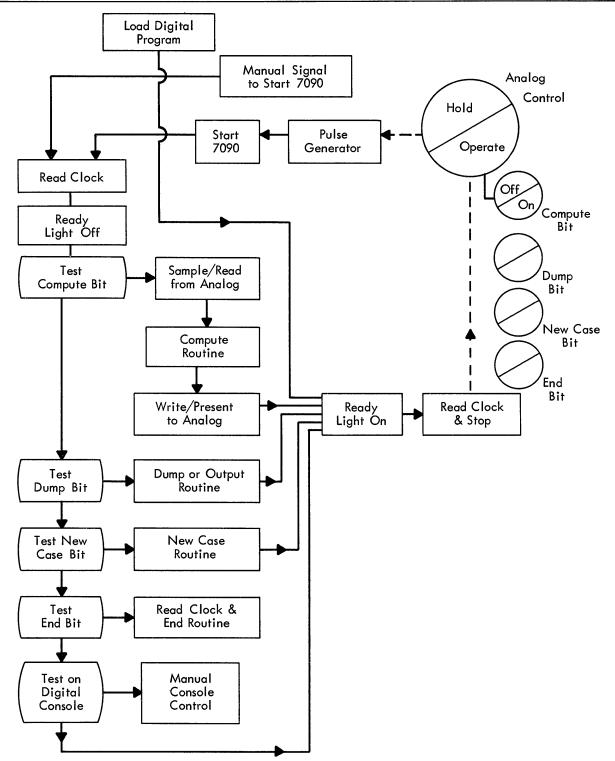

#### Base Level

We have seen the relationship between peripheral device control operation and processor operation. The former constitutes one of the levels of the multi-level program. Processor operations are divided into two levels, one of which has already been considered. The operations that must be done in each cycle, including the preparations for peripheral operations, constitute the base level of the program. It is related to the peripheral device control level as shown in Figure 12. Base routines are carried out successively under base control. They usually lead to peripheral device operations, and after initiating a peripheral device operation the computer returns to base control to determine what routine should be worked on next.

#### Interim Level

A third level, the interim level consists of miscellaneous tasks that need not be synchronous with the input-output cycle. The program reverts to the interim level whenever base control finds no routines ready to be performed. Interim control examines a list like that of base control, with tasks arranged in preferential order. The program goes through the list, performing any tasks for which the required data are available. Performance of possible tasks continues through the list until a peripheral device interrupt leads the program back to base level. If the peripheral device operation opens up new possibilities at the base level, the processing will not necessarily return to interim level for some time. When it does so, the task that was interrupted is finished, and the list is examined again from the beginning.

While a cycle may be held up if all base routines have not been performed, interim routines are allowed to extend over several cycles. When the computer is heavily loaded, this could result in long waiting for tasks at the end of the list examined by interim control. Even though they are not critical, these tasks must not be delayed indefinitely. To insure against this, the interim program differs from the base in one respect: each task is assigned a quota (either predetermined or program controlled) representing the amount that should be done in one cycle. The control program moves on to each task when the quotas are completed for the previous ones, rather than when the entire tasks have been completed.

If the end of the cycle finds tasks that have not received their quota of processor time, the cycle will be held up as for base operations. If, on the other hand, the quotas are all completed before the cycle is over, the interim control program may start through the list again, giving "second helpings," possibly smaller than the original quotas.

The last item on the list of interim tasks is error-checking routines. These can go on indefinitely, so that the processor will never be at a loss for something to do, even if it remains in the interim level for long periods of time. This of course, will not occur unless all the higher level tasks have been taken care of.

The base and interim levels are interruptible by peripheral devices. The control

Figure 12. Program Sequencing.

program, which includes not only peripheral device initiation and termination but control routines for the other two levels, is not interruptible.

#### Multi-Level Sequencing

Figure 13 reviews the realtionship among the levels by showing a typical segment of the program in time sequence. A base routine prepares two instructions for a peripheral device, and then transfers to the control level. This level includes not only the initiation of the first peripheral operation, but the base control decision as to what routine will be worked on next. The transfer to the actual execution of this routine is shown as a shift to the base level.

The second base routine starts to prepare an operation for another device (these could be read drum and read tape in this program). When the first device finishes its first order, it needs the computer's attention very briefly to start its second order, and accordingly interrupts the base routine. When the brief control routine to start the second order is over, the base control makes the decision to return to the interrupted routine, and it is taken up from the point of interruption.

After the second peripheral device has been given its job, the control program examines the base list, and, finding nothing to

Figure 13. The Multi-Level Program.

be done, goes to interim control. From there, the program reverts to interim processing, to continue a task previously interrupted, or take up a new one from the list. The completion of the second order by the first peripheral device interrupts the interim program, but the processor does not return to it immediately after the control routine. This operation was the last prerequisite for a third peripheral device (possible the write output buffer). A new base routine that could not be done before is possible now. After it and the follow-up peripheral device order are done, the program goes back to the interim level. Here too there may be a new task possible that could not be done before.

This system of control, interim, and base programming, insures that there will not be delays unless traffic necessitates them. If the computer is ever idle (continuously performing error detection routines), it is because it has finished all its other tasks. Furthermore, peripheral devices are operating to bring it more work to do as soon as possible. Similarly, if peripheral devices are ever delayed, it is because the computer has been constantly busy and yet has not completed the tasks required of it.

#### Conclusions

Multi-level programming adjusts itself in each cycle to the traffic conditions. When the system is computer-limited, the computer works full time to meet the situation, holding up peripheral devices as necessary. When peripheral devices require more time than the central processor, their operations are optimally sequenced. Meanwhile, the processor keeps its own operations caught up, and whenever it is forced to wait for peripheral devices, it busies itself with low priority tasks or error checking.

This type of programming succeeds in keeping the processor and associated devices busy whenever possible, which is one criterion for judging the efficiency of multiprogramming. This system goes further, and makes a highly flexible choice of what tasks various devices will perform first. It anticipates deadlines by giving first precedence to operations on which others depend, and thereby avoids alternating periods when equipment is very busy and idle under the same conditions. Thus, while it represents a considerable programming effort initially, it pays off in truly efficient real-time operation.

## DODDAC - AN INTEGRATED SYSTEM FOR DATA PROCESSING, INTERROGATION, AND DISPLAY

Walter F. Bauer and Werner L. Frank Thompson Ramo Wooldridge Inc. Canoga Park, California

#### ABSTRACT

With the DASA Department of Defense Damage Assessment Center a significant advance has been achieved in the establishment of a large-scale military data handling system which operates under real-time constraints. Although characteristics and requirements of this system are similar to those of Command/Control systems now in development, the integration of man to this configuration is of paramount concern. The DODDAC demands swift man and system interaction to elicit the information upon which decisions are based.

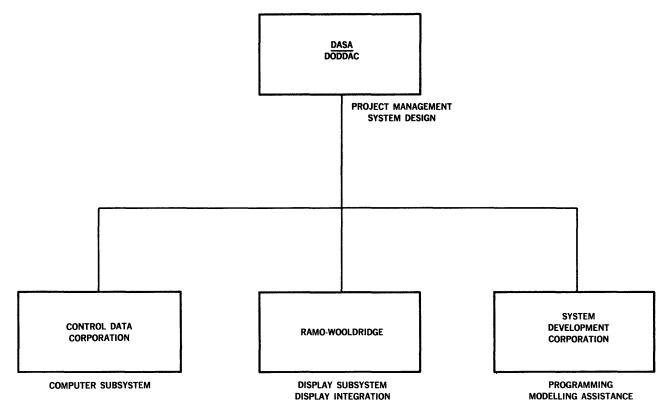

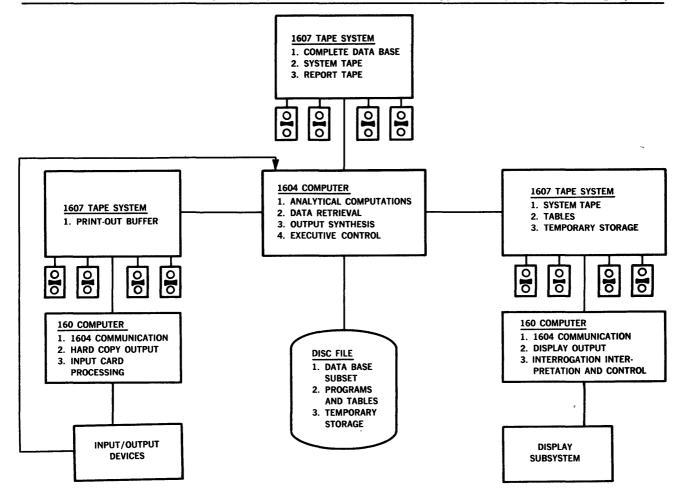

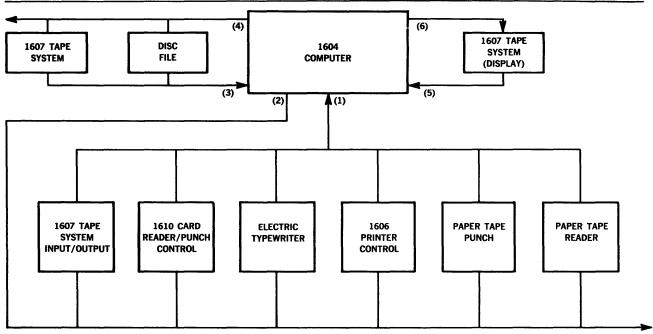

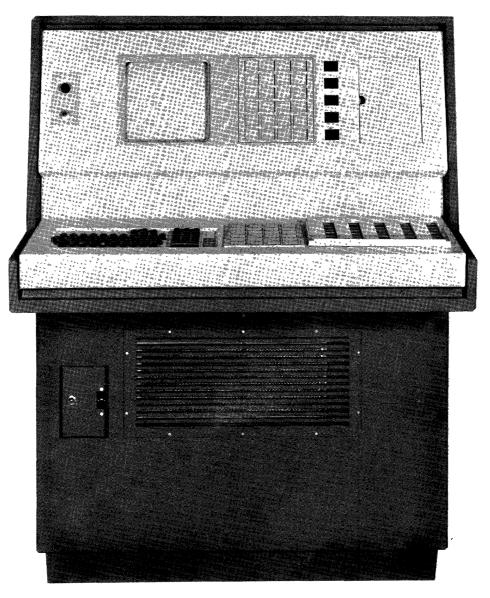

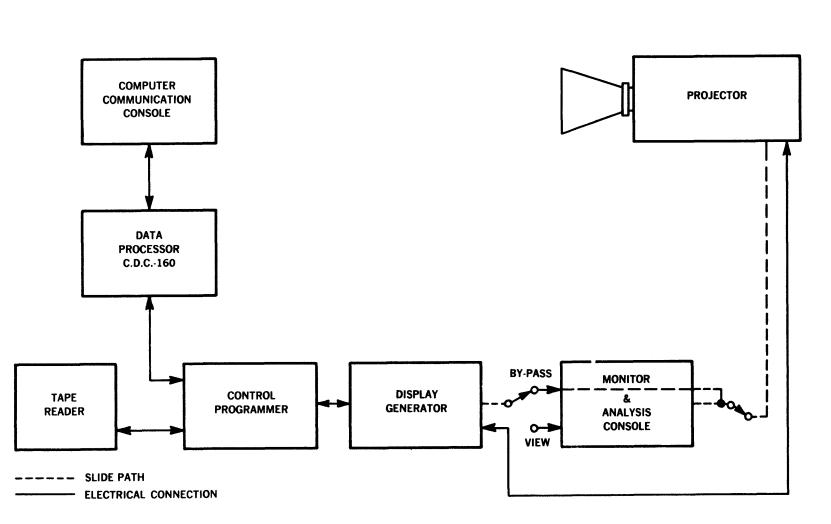

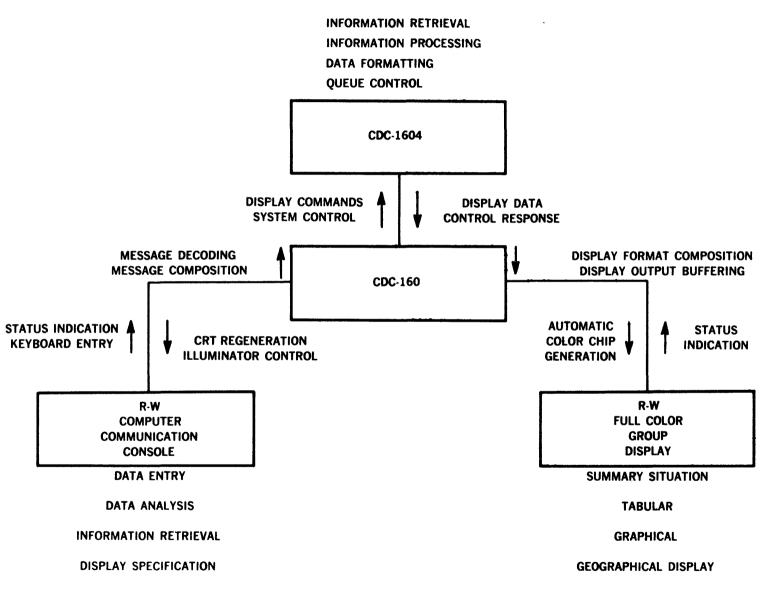

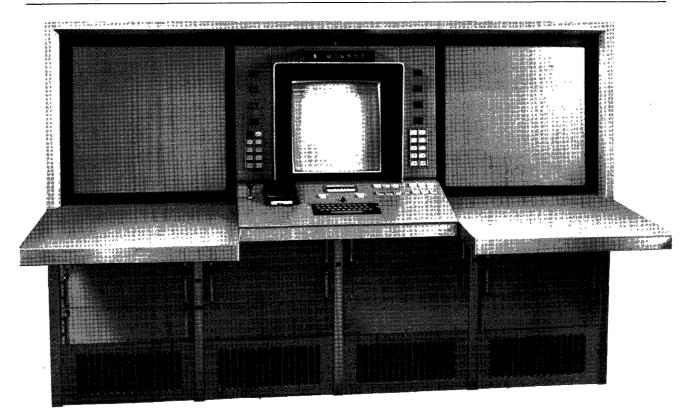

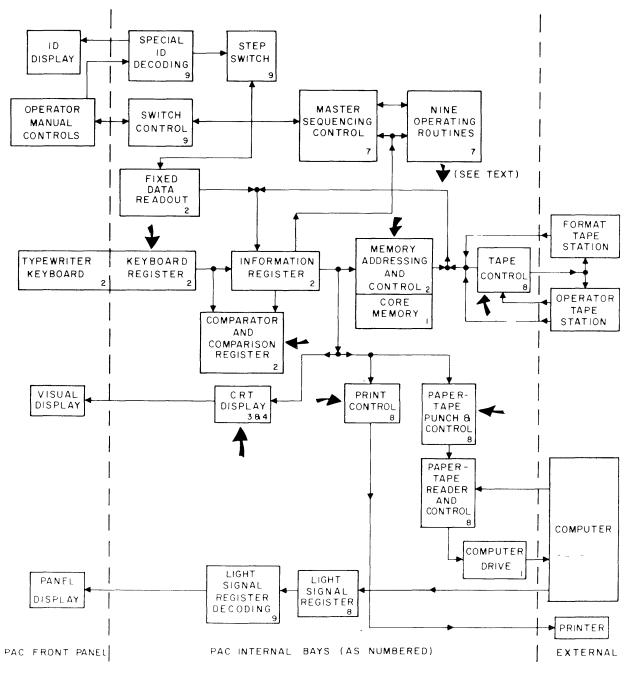

The system consists of a Control Data Corporation 1604 Satellite System and communication and display devices manufactured by Thompson Ramo Wooldridge Inc. The latter includes a Computer Communication Console and an on-line group display.

#### Introduction

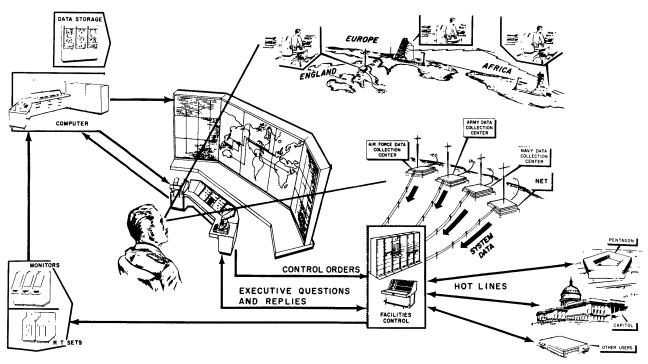

The need for a damage assessment center that could rapidly handle and process extremely complex military data led to the expansion of the Defense Atomic Support Agency to include the Department of Defense Damage Assessment Center (DODDAC). Under the Deputy Chief of Staff, Damage Assessment Systems of DASA, DODDAC now provides damage assessment support to elements of the Department of Defense and the Joint Chiefs of Staff. It provides comprehensive information affecting peacetime and wartime decisions with rapidity after particular queries are received. Because of the great amount of data handled, the complexity of the processing, the comprehensiveness and the facility of output, and the fast system responses required for both man and machine, the design and implementation of the data system are especially challenging. In delivering this performance, DODDAC represents a significant advance in large scale data handling systems.

The characteristics and requirements of this system have many features common to the general class of military Command/ Control systems now in development. They require, for example: large capacity random data storage devices, parallel processing of data, continual operation with near absolute reliability, real-time response, and servicing of queues formed by continual data entry and consumer requests for output.

Of paramount concern was the integration of man to the configuration, i.e., providing him with adequate tools by which he interacts with the data and the processing. In this respect especially, the design represents one of the more advanced real-time systems incorporating on-line interrogation and display.

The DODDAC system design and project management was provided by the DASA. The

design was implemented by a Control Data Corporation Satellite System, a Ramo-Wooldridge Interrogation and Display System, and by programming and modelling accomplished by the System Development Corporation. This paper presents the technical aspects of the data processing and display systems, following a discussion of the mission, functions, and requirements of DODDAC.

#### Mission

DASA is a joint services organization with broad military responsibilities in the atomic energy field. DASA, formerly the Armed Forces Special Weapons Project, succeeded the Manhattan Project of World War II. As part of its responsibilities, DASA has for some years been performing computational studies of weapons effects, hazards, and vulnerabilities related to atomic warfare, exercised earlier by the DASA Deputy Chief of Staff for Weapons Effects and Tests and now, insofar as applications to real target systems, by the Deputy Chief of Staff for Damage Assessment Systems. Under the latter, DODDAC was established by a Department of Defense directive. On March 4, 1960, the Chief, Defense Atomic Support Agency, was designated as Executive Director of the DODDAC.

Should war occur, DASA (DODDAC) will support the Joint Chiefs of Staff and other designated military and government groups in assessing nuclear damage sustained by the armed forces and resources of the United States, its allies, and the enemy, supplementing its peacetime responsibility for appraisals of attack hazards and vulnerabilities.

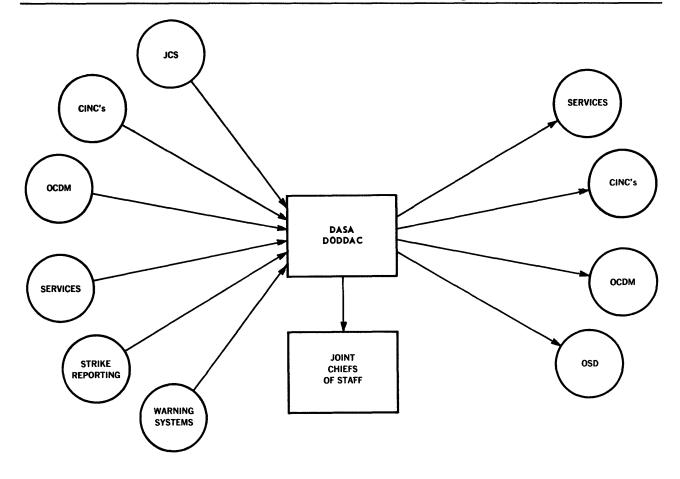

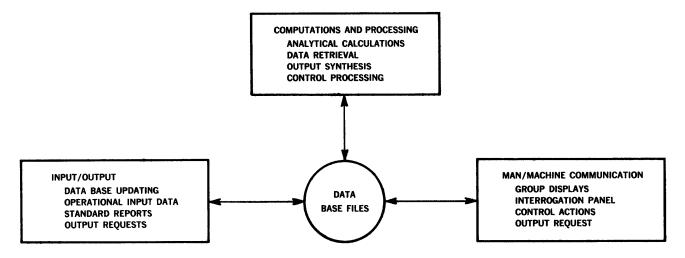

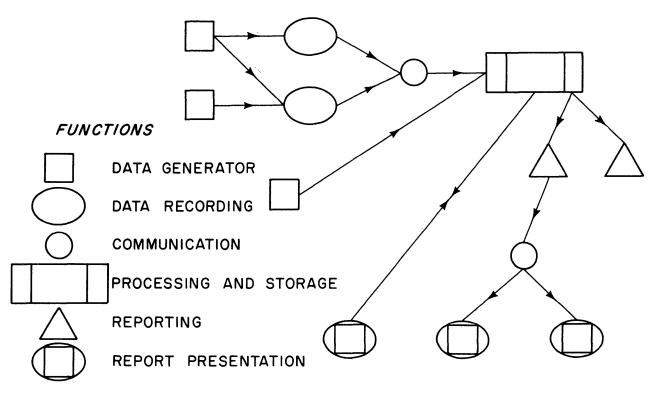

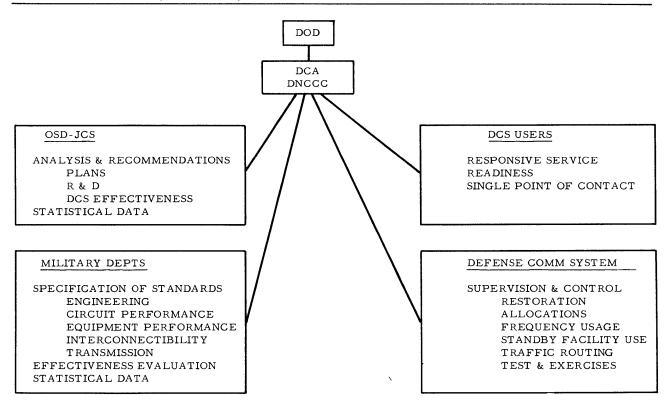

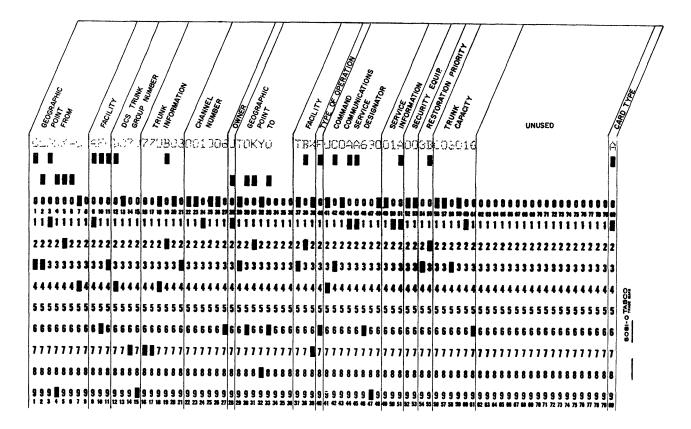

Figure 1 depicts schematically the mission of DASA DODDAC by presenting the overall data flow through the system. Data comes into the DODDAC from the indicated agencies in three categories: target data, system parameters, and attack information. Target data is a comprehensive description of forces and resources, system parameters include certain data on weapon effects, and attack information is that volatile data related to a specific and unpredictable pattern of events during post attack phases.

The sources and users of data shown in Figure 1 is not an exhaustive list but a representative one. The principal user, as indicated, is the Joint Chiefs of Staff.

#### **Functions and Requirements**

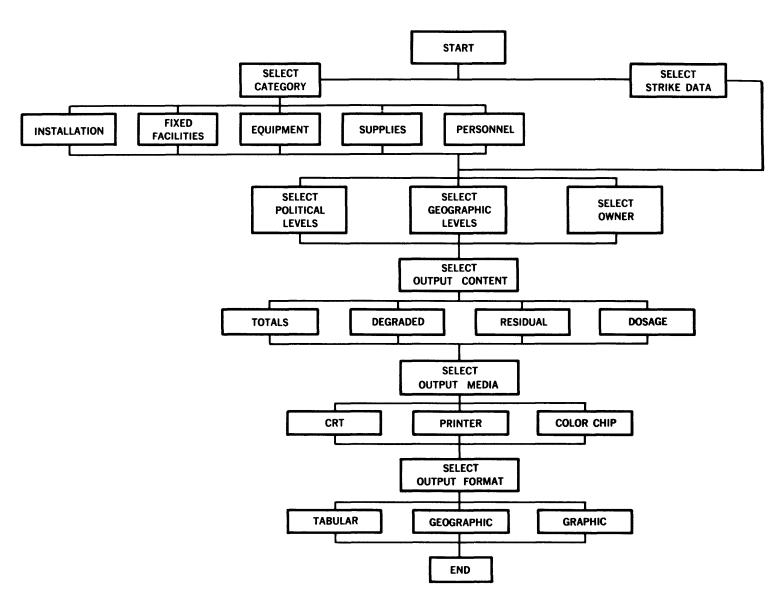

A general statement of the functions of the DODDAC is as follows: perform hazard and vulnerability studies on a continuing basis, keep an up-to-date file of military forces and resources information, and in the event of hostilities, accept information quickly, process it rapidly, and provide display products suitable for top level command use.

The DASA-DODDAC has also been given the responsibility to support the war gaming activity of the Joint Chiefs of Staff. In this capacity the DODDAC works with the Joint War Games Control Group from which guidance is given leading to the development of gaming models, computer programs implementing the models, output designs and presentation methods.

More specifically, the imposing list of requirements is as follows:

- 1. Provide a data base of information necessary for damage assessment processing which can in the near future grow to 100 million characters.

- 2. Provide a means to up-date the data base on a day-to-day basis.

- 3. Design and implement a data handling system for handling these large amounts of data accurately and expeditiously.

- 4. Allow for the data transmission to DODDAC over hardened, secure, and reliable communication facilities, and devise and arrange for sources of information appropriate to the damage assessment process.

- 5. Accept attack data as real-time inputs and allow for their direct input to the computer system.

- 6. Develop damage assessment models which represent the delicate balance between comprehensiveness or realism, and speed.

- 7. Provide a technique for man/machine communications, allowing quick access to nearly all data in the files.

- 8. Provide a system for the automatic generation and presentation of high quality output products of fast response which are suitable for group viewing by top command personnel.

There is a special challenge in the last two requirements for there are few, if any, data processing systems in existence today which provide all flexible and all-purpose interrogation and display system required.

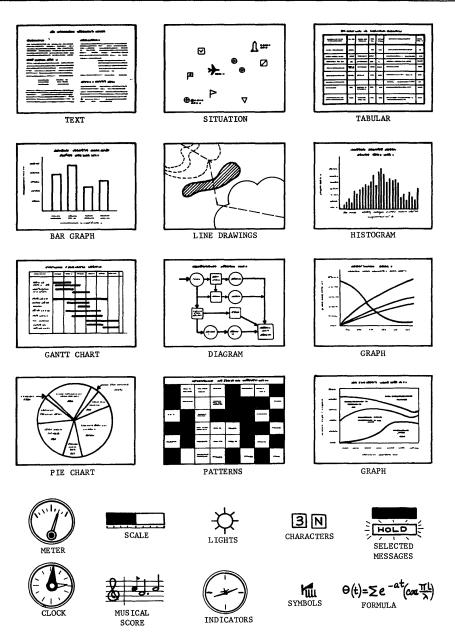

Figure 1. DASA -- DODDAC Mission - Overall Data Flow

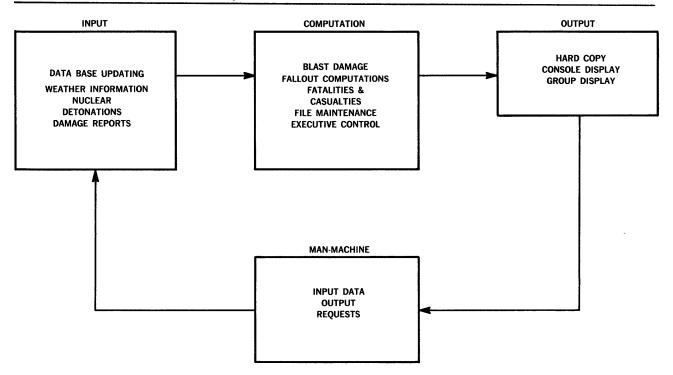

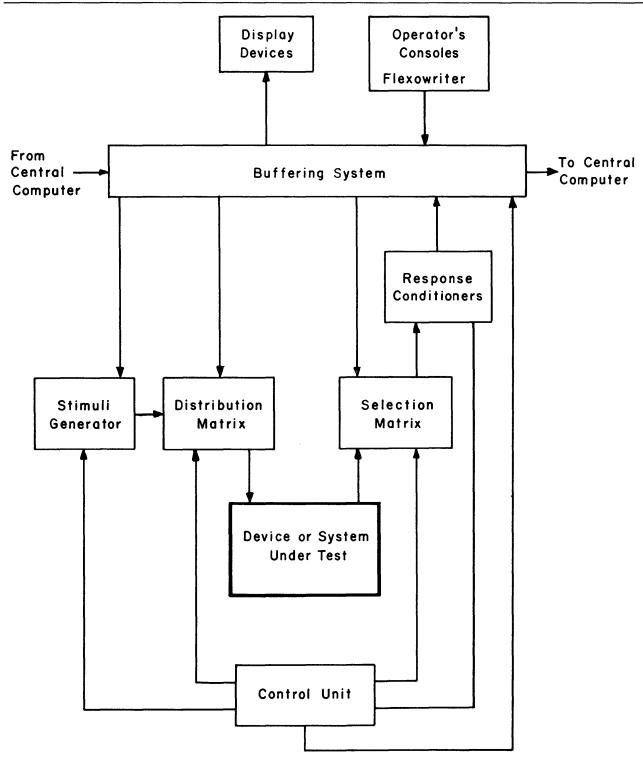

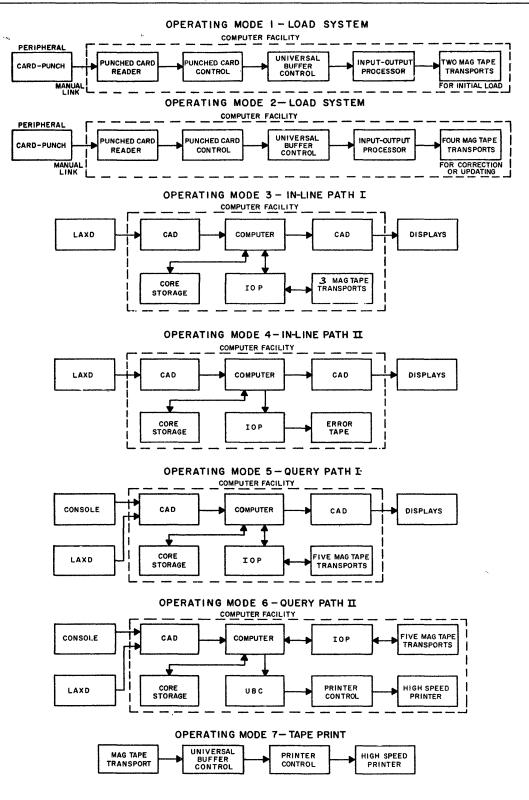

Figure 2 shows the functions to be performed by the data system. The input data, as shown, can come in through many sources: voice communications, teletype data links, specialized communication systems, and standard digital data links. The system must allow for automatic entry of data as well as manual type entry. The computations must allow for various kinds of damage assessment processes. For the various models, there must be a number of modes of operation which allow various trade-offs between comprehensiveness of the model and the speed with which results must be obtained. Standard output in terms of hard copy must be available. In addition, individual or console type displays are necessary for the individual analysis of file data.

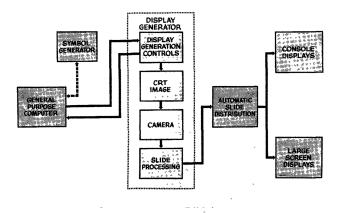

A last requirement for output is a display for group viewing. Man/machine facilities for the input of data and for calling for requests, complete the required capabilities of the system.

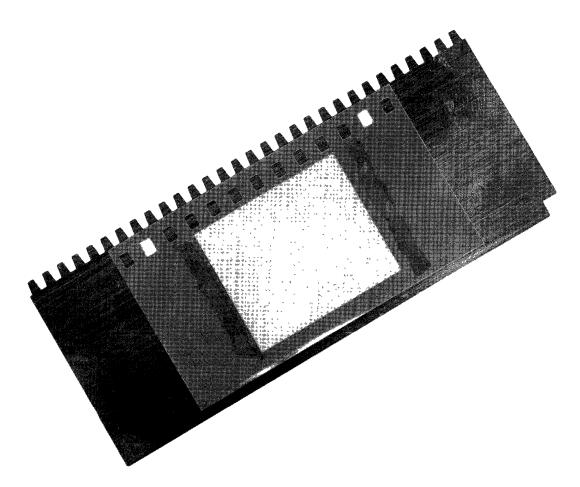

Of special concern is the system for group display. In order to have the quality and comprehensibility of the group display required for command use, it was deemed necessary to have a full color display system. It was desired that this display system allow for the placing of symbols on maps and charts in full color, with no dilution of the color of the superimposed symbols. Finally, because of large amounts of information to be placed on the slides for group viewing and the fast response times necessary for their preparation, it was necessary to have completely automatic operation. This automatic operation must allow for the input of information directly from the computer, the automatic preparation of the slides, and the transportation of the slides to a projector for viewing as required.

#### Implementation Philosophy

In the fall of 1960 the first steps were taken toward the eventual operational DODDAC. In order to accelerate the establishment of the

Figure 2. Data System Functions

necessary capability, an implementation philosophy was adopted which saw the following three activities in parallel development:

- 1. A semi-automatic manual system providing an immediate and basic capability.

- 2. A Developmental Center containing a simplex of equipments with which to study and test the operational DODDAC environment and requirements. This functional unit also represents a level of sophistication that fulfills many of the requirements set forth by the Department of Defense.

- 3. Develop a design of future systems, based on a better understanding of the problems and experience gained in operating the first two systems.

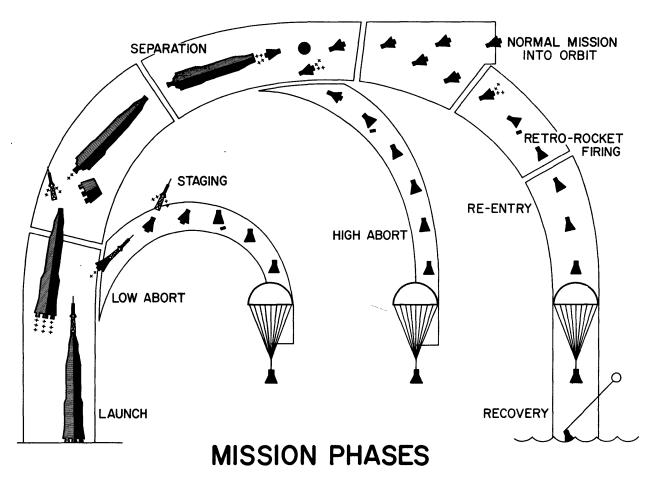

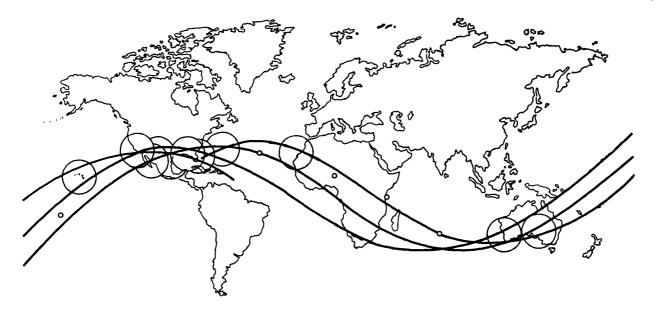

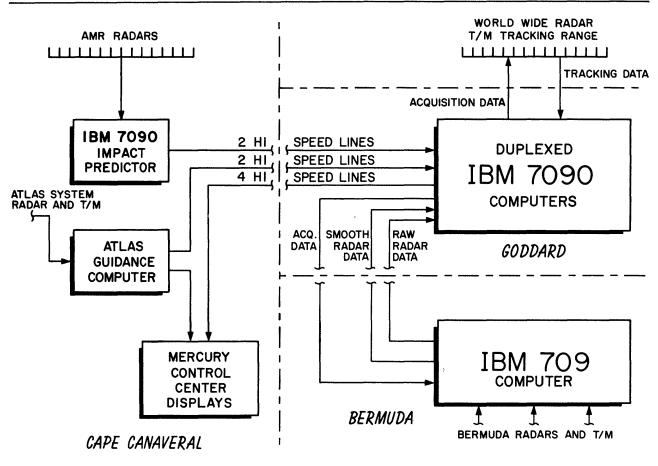

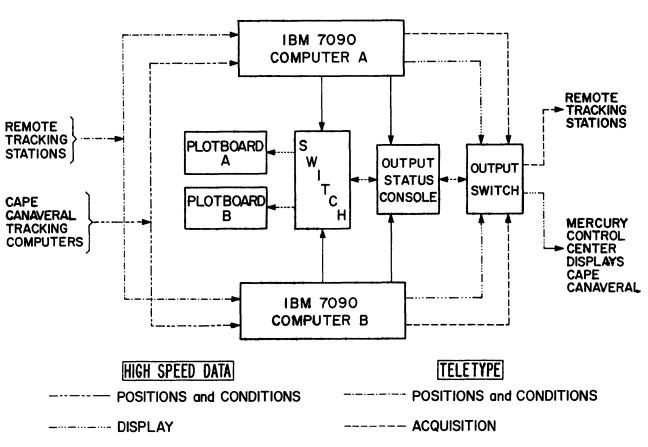

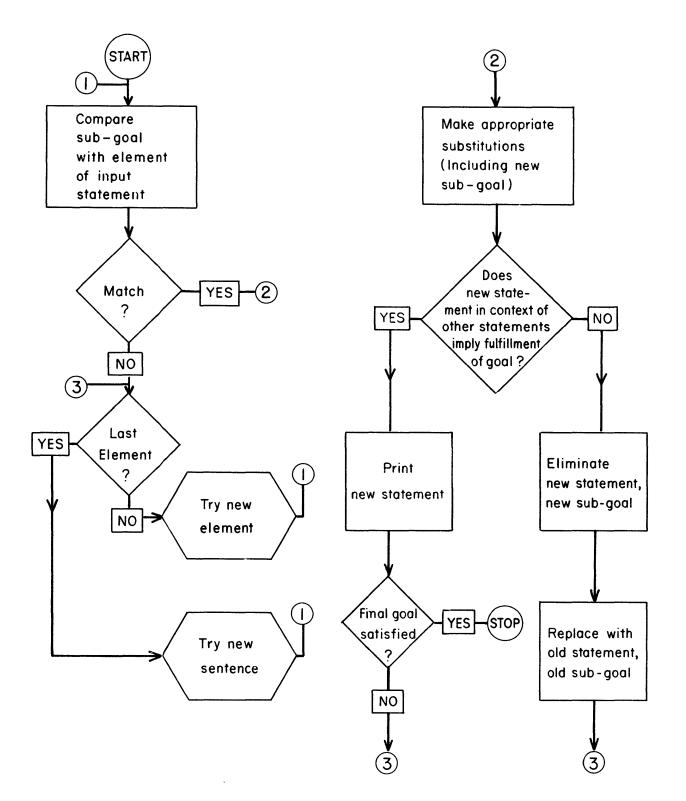

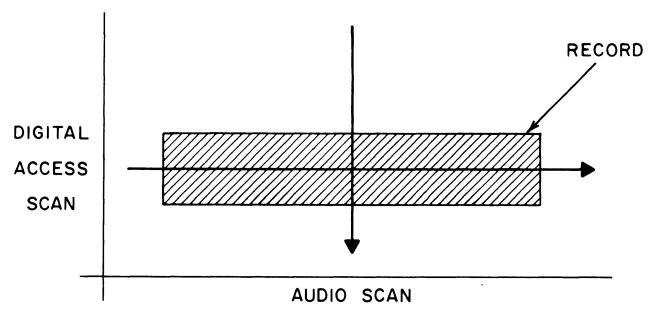

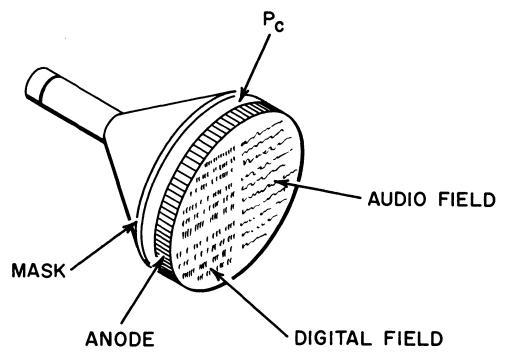

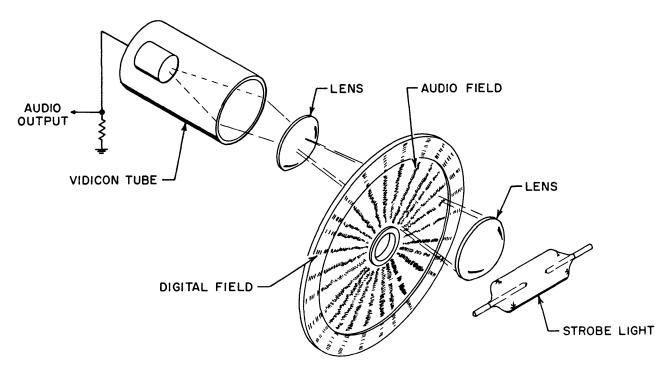

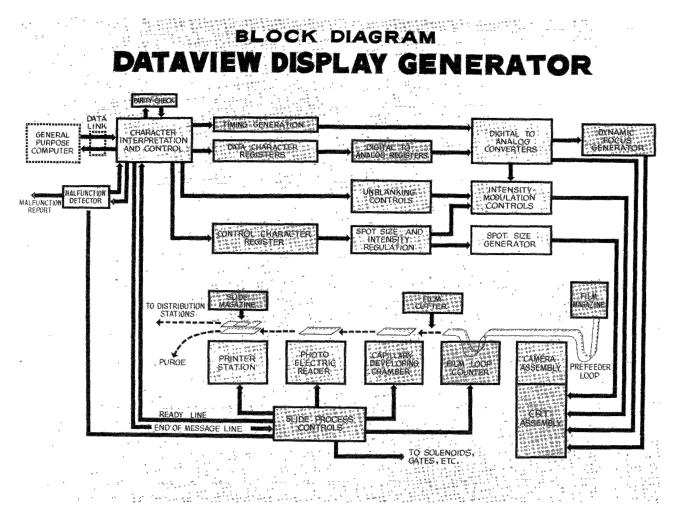

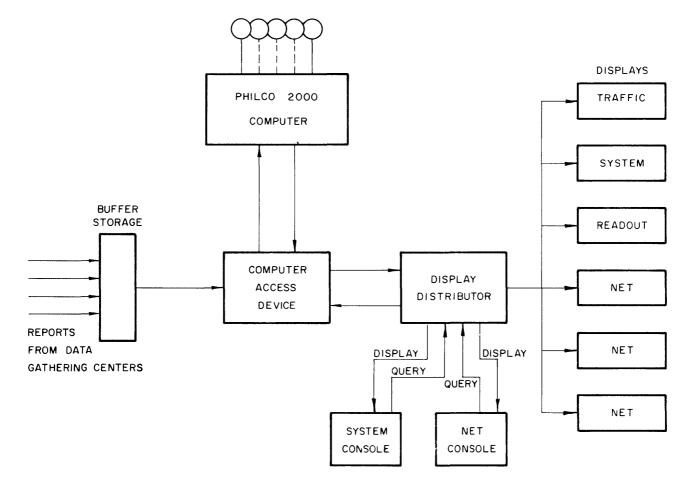

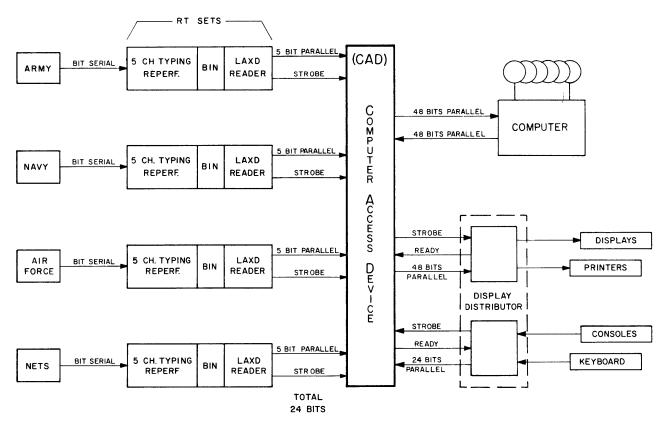

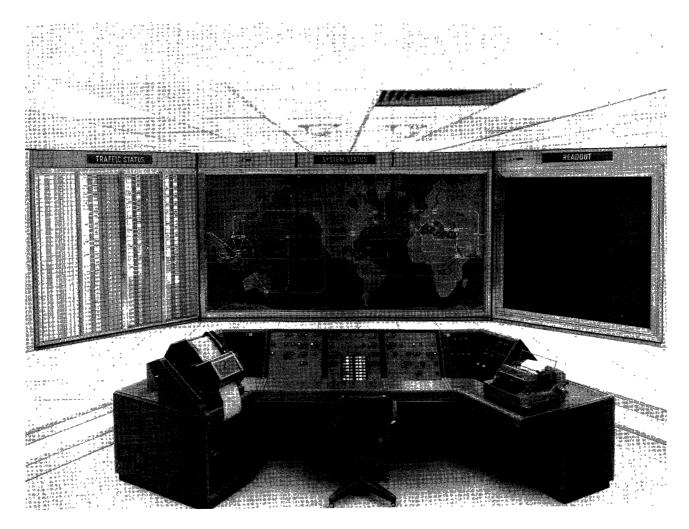

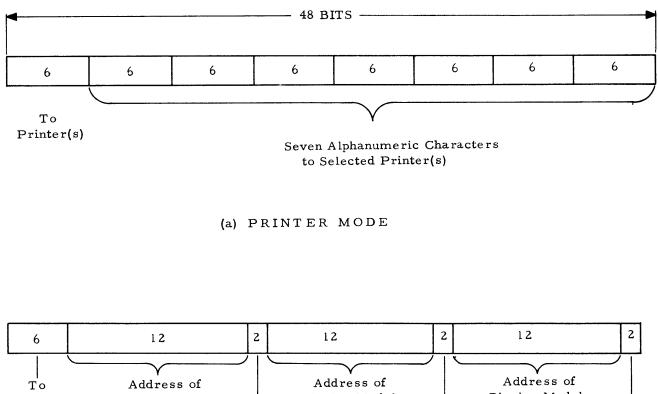

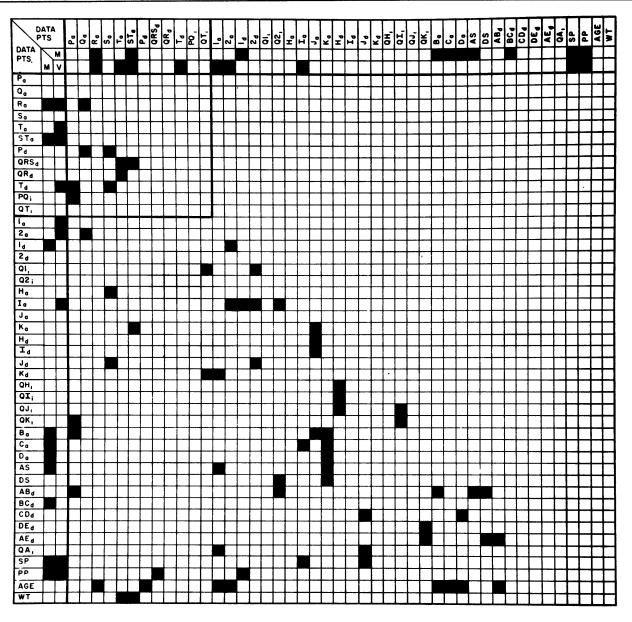

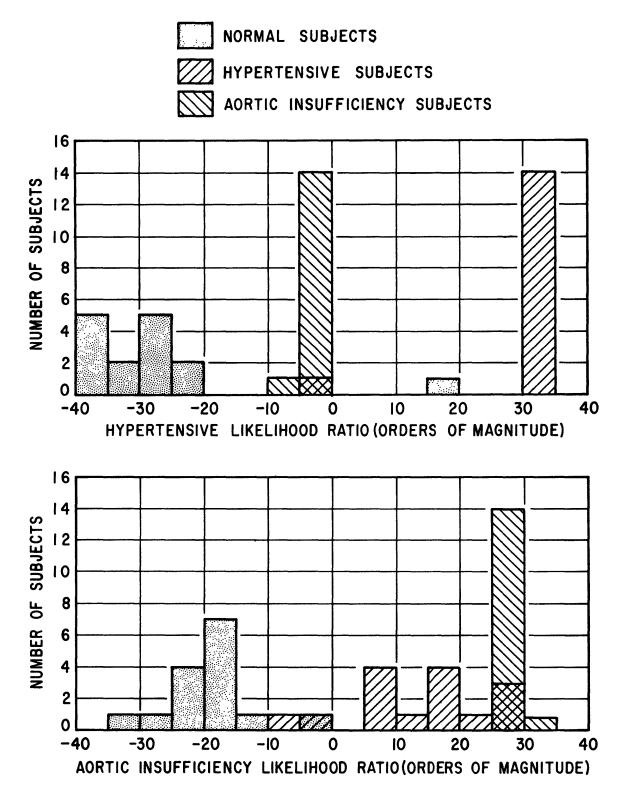

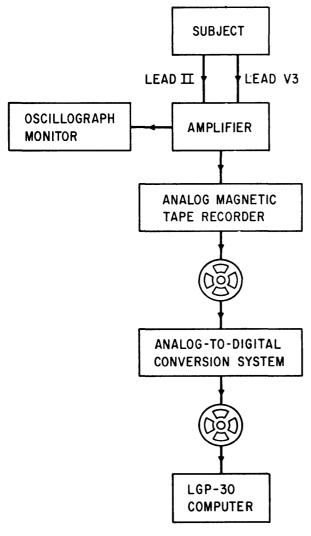

This plan allowed an early basic capability while recognizing that significant technology must evolve gradually in areas of computers, programming, and displays, with the passage of many months. It was recognized that starting immediately toward a full blown operational system would have been costly and inefficient; the plan allowed the maximum contribution to damage assessment required by national defense consistent with reasonable expenditures.