# **AFIPS** CONFERENCE PROCEEDINGS

HOWARD LEE MORGAN Editor and Program Chairman

> RUSSELL K. BROWN Conference Chairman

# **1982** NATIONAL COMPUTER CONFERENCE

AFIPS PRESS 1815 NORTH LYNN STREET ARLINGTON, VIRGINIA 22209

June 7–10, 1982 Houston, Texas The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1982 National Computer Conference or the American Federation of Information Processing Societies, Inc.

Library of Congress Catalog Card Number 80–649583 ISSN 0095-6880 ISBN 0-88283-035-X AFIPS PRESS 1815 North Lynn Street Arlington, Virginia 22209

© 1982 by AFIPS Press. Copying is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) reference to the AFIPS Proceedings and notice of copyright are included on the first page. The title and abstract may be used without further permission in computer-based and other information-service systems. Permission to republish other excerpts should be obtained from AFIPS Press.

Printed in the United States of America

## Preface

#### RUSSELL K. BROWN 1982 NCC Chairman

The purpose of the National Computer Conference is to provide an atmosphere in which designers, suppliers, users, managers, educators, and representatives of government and society at large can meet and interact. Discussions of new technical developments, as well as national and international issues and challenges facing the information processing community, are encouraged.

This year's discussions and developments are contained, for the most part, in this anniversary Volume 51 of the Proceedings of the National Computer Conference, completing its first decade as the world's premier computer exposition.

The decision to chair a National Computer Conference may well be one of the more major choices one makes in even a complicated lifetime. Certainly, this choice was compounded by the change in site from New York to Houston, made only thirteen months prior to the Conference date. Perhaps a few words on that move are in order.

In spring 1981 the NCC Committee and Board were faced with a dilemma of some magnitude. The Conference exhibits had grown so large that plans to house them in New York became unrealistic. To have held NCC '82 there would have dictated a requirement to cut back the number of companies exhibiting, the maximum exhibit size, or both. After much arranging by the AFIPS staff, a plan was presented to use New York to its absolute limits. To do this, we would have had to split the show across the convention facility, some number of hotel ballrooms, and a covered pier on the East River. Even then, booth size would have had to be cut and the rather spectacular island concept with which you are familiar in our exhibit areas would have been affected severely.

As a long-time Houstonian, I was well aware of the potential abilities of my city to handle an NCC. In a very short time, we were able to arrange the use of the Astrohall and Arena, reserve 12,000 hotel rooms, and make other arrangements necessary to effect the move.

Naturally there were a few rough edges. Because of the timing, we had to spread out our hotels much more than will be the case when we return for NCC '84. But we feel that, given less than half the normal preparatory time accorded

most Conference Steering Committees, you will see few shortcuts or shortcomings.

What you *will* see is a display of 650 companies filling 3,200 booth units for a new NCC record. You will be exposed to a high-quality program, high-quality Professional Development Seminars, four major invited addresses, a special Pioneer Day program, and numerous other attractions that we feel will make this a noteworthy week. It is the intention of the CSC to give you, the attending registrant, all the positive values of a move to our city and make any negatives as invisible as possible.

An example of this is the expenditure of nearly \$200,000 for busing to assist you in the various round trips between your hotel and the Conference.

If I may return to our program, possibly I can elicit in you a feeling of satisfaction to match the pride I feel. The program is made permanent by the archival record of the Proceedings. Here we capture for posterity the most current reports on recent achievements and new applications, on advances at the frontiers of computer science and technology.

Dr. Howard Morgan of the Wharton School was buffeted in mid-preparation of this program and these Proceedings by the move. Through all the personnel shuffling and turmoil, he managed to steer a straight course toward a superior presentation.

Howard recognized, early on, that the registrant has only three days, on the average, to assimilate all aspects of an NCC. His first decision was to direct that, with a superior Professional Development Program together with ten football fields of exhibits, the program as defined in the past be intensely screened for shortcomings. His Committee introduced a much finer mesh in their screen than has ever been used before. The number of papers and sessions are down slightly from what you have seen in previous NCCs, but we are confident that their value to you will be high. We will be surprised if you depart early from any of our sessions.

Volunteers, for a Conference of this magnitude, number in the hundreds. They are members of the NCC Sponsoring Societies and the other AFIPS Constituent Societies. To these groups and their participating members I would like to give my heartiest thanks, particularly in view of the truncated schedules on which we were all operating.

To the NCC Board and Committee, who well knew the danger to NCC '82 if plans were not well organized, my thanks for your confidence and support.

To the AFIPS Headquarters Staff and all the members of

our CSC, thank you for your dedication, time, and effort. You have contributed to an ongoing tradition of excellence.

To my wife, who only once asked, "Why?" but a hundred times asked, "How can I help?" you know my thoughts.

And finally, to the nine NCC Chairmen of the past, thank you for your assistance, guidance, and inventiveness. Much of what you created is embodied here.

## Introduction

HOWARD LEE MORGAN 1982 NCC Program Chairman

"Advancing Professionalism" is the theme for the 1982 National Computer Conference. It is our belief that these Proceedings represent a contribution to the professionalism of you who are reading them or those who attended the conference. The computing field now incorporates many types of professionals: designers, analysts, programmers, managers, and users of office and personal computing systems. Parts of our program are aimed specifically at each of these types of users. More important, we hope that people will integrate and broaden their knowledge with the help of the wide spectrum of sessions, panels, and papers presented, which cover all major aspects of the computing field as we know it today.

With this theme as the base, the NCC '82 program has been structured into eight major areas. These include the following:

- 1. Hardware and computer architecture: providing more power and newer structures than those that have been traditional for hardware designers.

- 2. Software engineering: techniques to aid in the building of correctly working and properly engineered software.

- 3. Personal computing: included this year for the first time in the main NCC program and undergoing explosive growth in both business and home use.

- The social and organizational implications of computing: this area indicates how totally computers now impinge on our daily lives.

- Office Systems: this area addresses the concerns of those involved in the growing office automation environment.

- Decision support and management issues: to aid those whose job it is to manage computing or to provide services directly to top executives.

- Language and database processing: two key applications systems tools.

- 8. Finally, the applications of computing themselves.

As a special feature, the history of computing and Pioneer Day focus on FORTRAN and its early development. We are fortunate to have several key papers in these Proceedings.

We have reduced the number of sessions this year to 86, as opposed to the 105 to 120 of previous years. This has had the favorable effect of permitting us to select and work with higher average quality levels, but some worthwhile paper and session proposals were not able to be included in the conference. We are sure that the panels and paper sessions in the program provide detailed, high-quality presentations in their specific areas. These Proceedings are organized according to the areas of interest, as noted in the conference program. The conference program contains a page number key to these specific papers, for easy reference by attendants. Because space is limited, summaries of the panel discussions are not printed in these Proceedings; but they are available in the conference guide.

The plan and organization of the 1982 NCC program required the concerted, dedicated, and extreme efforts of many individuals: the Program Committee members; the session organizers and leaders; the panelists, presenters, and authors of technical papers; and the referees, who helped us select the papers to be presented in these Proceedings. In addition, the entire NCC committee structure and the staff organizations at AFIPS have played an important role in the smooth operation of the conference. The committee assistants, Françoise Aubert-Santelli and Susan O'Leary, performed far beyond the call of duty. I wish to extend my sincere thanks to all of these individuals and most especially to our Program Committee. It is through their efforts that the NCC '82 program and these Proceedings have come alive. It is our sincere hope that your attendance at the program will prove a fruitful and enjoyable activity to those of you who were fortunate enough to come and that these 1982 NCC Proceedings will join their predecessors as a useful reference for many years.

.

.

## **CONTENTS**

| Preface                                                                                                                          | iii |

|----------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction<br>Howard Lee Morgan                                                                                                | v   |

| HARDWARE/COMPUTER ARCHITECTURE                                                                                                   |     |

| Firmware quality assurance                                                                                                       | 3   |

| The 5.25-inch fixed/removable disk drive<br>Don Minami                                                                           | 11  |

| Practical CMOS microprocessor systems<br>Bill Huston                                                                             | 19  |

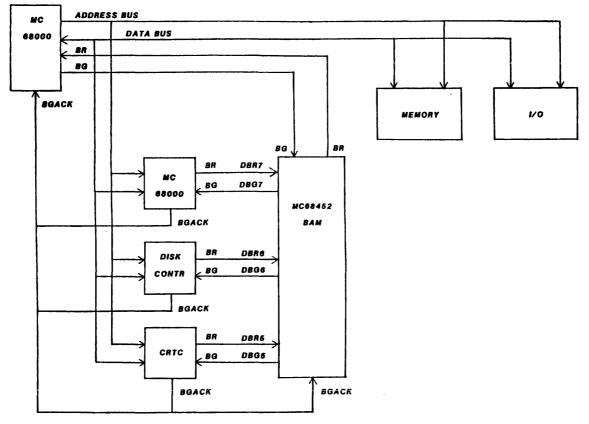

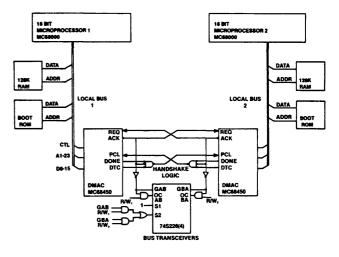

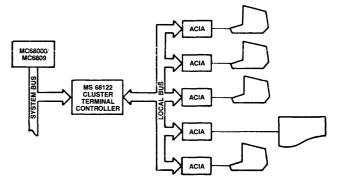

| The MC68000 family and distributed processing John F. Stockton                                                                   | 29  |

| Using operational standards to enhance system performance<br>David R. Vincent                                                    | 37  |

| Distributed processing with the Z8000 family<br>Richard Mateosian and Janak Pathak                                               | 53  |

| Distributed processing with iAPX 186 microprocessor systems<br>Tony Zingale                                                      | 59  |

| High-performance, high-capacity single-chip microcomputers<br>Ed Peatrowsky                                                      | 67  |

| Expanded single-chip principles in practical applications                                                                        | 73  |

| Making the most of VLSI in microcomputers<br>Jerry L. Corbin                                                                     | 81  |

| Single-chip microcomputers can be easy to programBill Huston                                                                     | 85  |

| Speak software and carry a strip chip<br>Michael Shapiro                                                                         | 95  |

| A distributed operating system for a powerful system with dynamic architecture<br>Steven I. Kartashev and Svetlana P. Kartashev  | 103 |

| Software testing techniques for universal building blocks of multimicrosystems                                                   | 117 |

| A methodology for the development of special-purpose function architectures<br>Raymond A. Liuzzi and P. Bruce Berra              | 125 |

| Applications of SIMD computers in signal processing            Laxmi N. Bhuyan and Dharma P. Agrawal                             | 135 |

| A list-processing-oriented data flow machine architecture<br>Makoto Amamiya, Ryuzo Hasegawa, Osamu Nakamura, and Hirohide Mikami | 143 |

| Lookahead networds                                                                                                                       | 153 |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

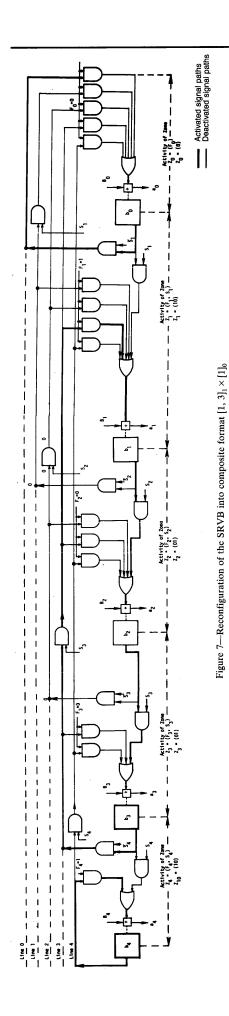

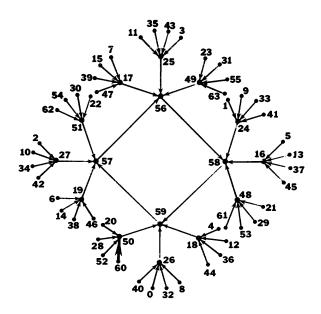

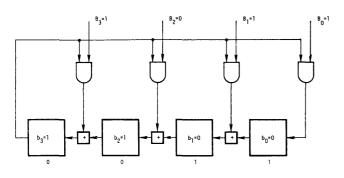

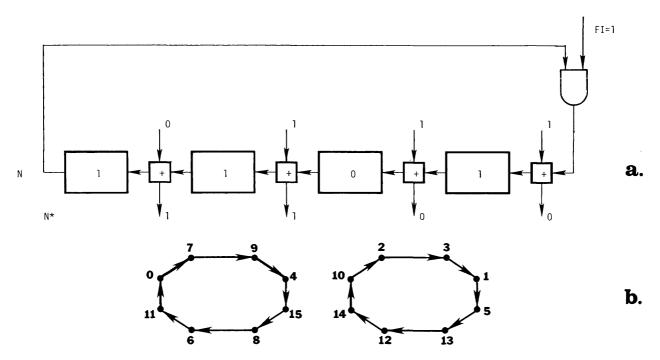

| Reconfigurable multicomputer networks for very fast real-time applications<br>Carl Davis, Svetlana P. Kartashev, and Steven I. Kartashev | 167 |

| MPP: a supersystem for satellite image processing<br>Kenneth E. Batcher                                                                  | 185 |

| Optimal design of a distributed supersystem<br>David F. Palmer, James P. Ignizio, and Catherine M. Murphy                                | 193 |

| Distributed processing with the NS16000 family Leslie Kohn                                                                               | 199 |

| SOFTWARE ENGINEERING                                                                                                                     |     |

| Exploiting parallelism for the performance enhancement of non-numeric applications                                                       | 207 |

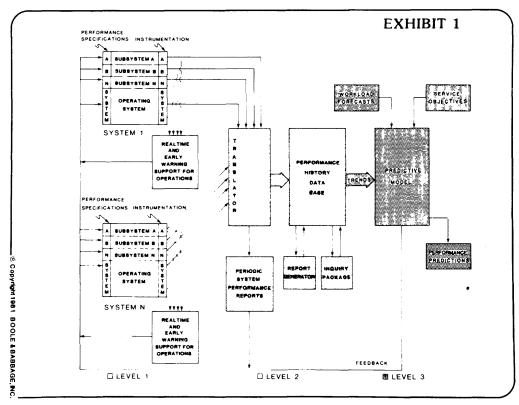

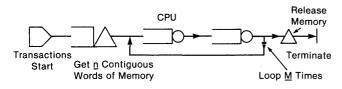

| Performance engineering of software systems: a case study<br>C. U. Smith and J. C. Browne                                                | 217 |

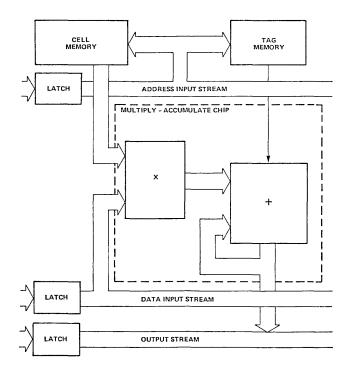

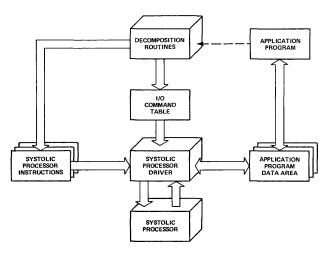

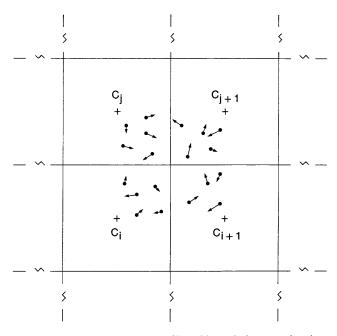

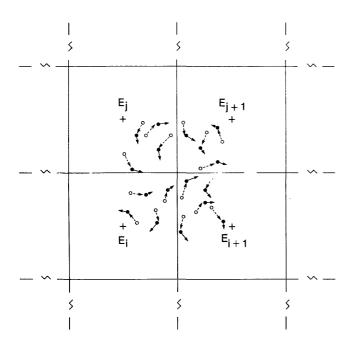

| A systolic processor for signal processing<br>G. A. Frank, E. M. Greenawalt, and A. V. Kulkarni                                          | 225 |

| Parallel-processing a large scientific problem                                                                                           | 233 |

| Design of software for distributed/multiprocessor systems                                                                                | 239 |

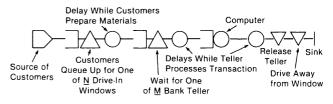

| The use of performance models in systematic design<br>K. M. Chandy, J. Misra, R. Berry, and D. Neuse                                     | 251 |

| Performance modeling in the design process                                                                                               | 257 |

| MEDOC: A methodology for designing and evaluating large-scale real-time systems                                                          | 263 |

| The research queueing package: Past, present, and future<br>Charles H. Sauer, Edward A. MacNair, and James F. Kurose                     | 273 |

| Audience identification for end user documentation<br>Janis G. Raymond                                                                   | 281 |

| Computer-aided documentation                                                                                                             | 287 |

| The development of software engineers: a view from a user                                                                                | 293 |

| An industrial software engineering methodology supported by an automated environment                                                     | 301 |

| An approach to the definition and implementation of a software development environment                                                   | 309 |

| A JOVIAL programming support environment                                                                                                 | 319 |

| The impact of Ada on software engineering<br>Kenneth L. Bowles                                                                           | 327 |

| The importance of Ada programming support environments<br>Thomas A. Standish                                                             | 333 |

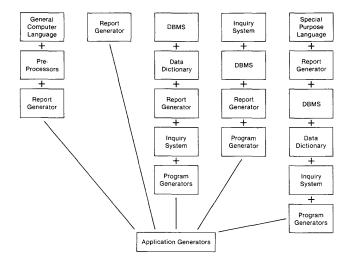

| Challenges and requirements for new application generators<br>Alfonso F. Cardenas and William P. Grafton                                 | 341 |

| Program generators and their effect on programmer productivity<br>Richard L. Roth                                                                | 351 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Application generators at IBM Aaron M. Goodman                                                                                                   | 359 |

| Application generators: a case study<br>James H. Waldrop                                                                                         | 363 |

| Requirements definition and its interface to the SARA design methodology for computer-based systems<br>James W. Winchester and Gerald Estrin     | 369 |

| The role of requirements analysis in the system life cycle<br>Yuzo Yamamoto, Richard V. Morris, Christopher Hartsough, and E. David Callender    | 381 |

| Application generators: an introduction<br>Jerrold M. Grochow                                                                                    | 389 |

| Software product quality assurance<br>John R. Ryan                                                                                               | 393 |

| A quality assurance program for software maintenance                                                                                             | 399 |

| The independent role: verification and validation, and compliance testing<br>Barbara J. Taute                                                    | 409 |

| Quality assurance in a large commercial data processing installation<br>C. W. Lybrook                                                            | 415 |

| PERSONAL COMPUTING                                                                                                                               |     |

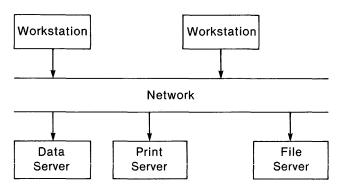

| Data server design issues<br>Fred Maryanski                                                                                                      | 429 |

| SOCIAL AND ORGANIZATIONAL IMPLICATIONS                                                                                                           |     |

| Acceptance criteria for computer security                                                                                                        | 441 |

| Private sector needs for trusted/secure computer systems                                                                                         | 449 |

| Impacts of information system vulnerabilities on society<br>Lance J. Hoffman                                                                     | 461 |

| Uniform help facilities for a cooperative user interface<br>Philip J. Hayes                                                                      | 469 |

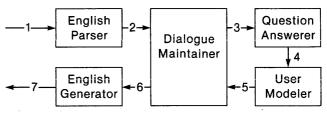

| Natural-language help in the Consul system                                                                                                       | 475 |

| Programs as data for their help systems<br>Elaine A. Rich                                                                                        | 481 |

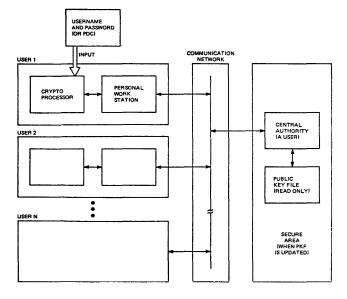

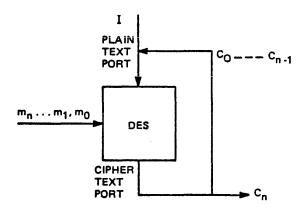

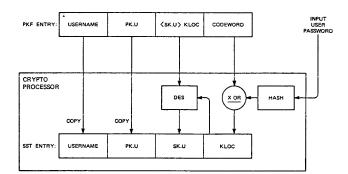

| The implementation of a cryptography-based secure office system<br>Christian Mueller-Schloer and Neal R. Wagner                                  | 487 |

| Criteria for a standard command language based on data abstraction<br>David Beech                                                                | 493 |

| Integration of bottom-up and top-down contextual knowledge in text error correction<br>Sargur N. Srihari, Jonathan J. Hull, and Ramesh Choudhari | 501 |

| Dialogue: Providing total terminal independence<br>David Vaskevitch                                                                              | 509 |

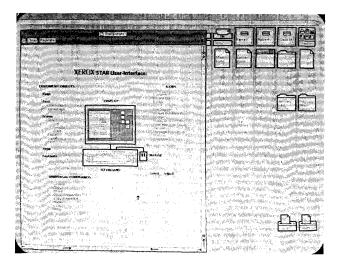

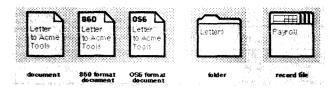

| The Star user interface: an overview<br>David Canfield Smith, Charles Irby, Ralph Kimball, and Eric Harslem                                      | 515 |

|                                                                                                                                                  |     |

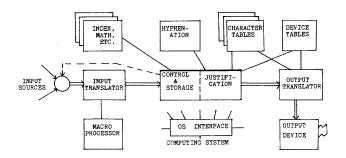

| MFS: a modular text formatting system<br>James D. Mooney                                                                                                                                              | 529 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| MANAGEMENT ISSUES/DECISION SCIENCE SUPPORT SYSTEMS                                                                                                                                                    |     |

| Complex business systems: a strategy for success                                                                                                                                                      | 539 |

| The role of the user at Standard Oil Company (Indiana) in the development of large-scale business systems<br>James E. Jackson                                                                         | 549 |

| The role of data center personnel in the development of a large-scale business system                                                                                                                 | 555 |

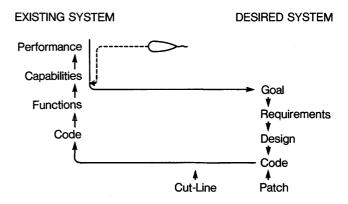

| What life? What cycle?    Nicholas Zvegintzov                                                                                                                                                         | 561 |

| LANGUAGE AND DATABASE PROCESSING                                                                                                                                                                      |     |

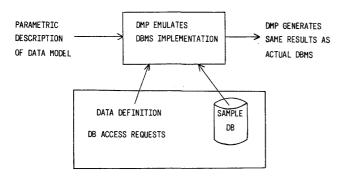

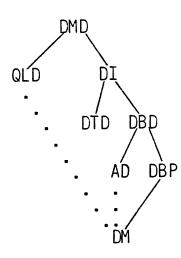

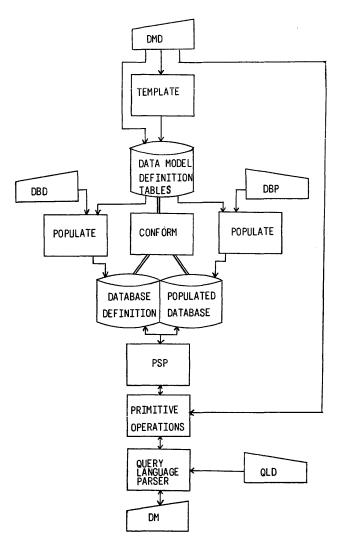

| Data model processing<br>Matthew B. Koll, W. Terry Hardgrave, and Sandra B. Salazar                                                                                                                   | 571 |

| Automatic database system conversion: schema revision, data translation,                                                                                                                              |     |

| and source-to-source program transformation<br>Ben Shneiderman and Glenn Thomas                                                                                                                       | 579 |

| Fair timestamp allocation in distributed systems         Said K. Rahimi and William R. Franta                                                                                                         | 589 |

| Data abstraction for Pascal programmers<br>Viswanathan Santhanam and John R. Potochnik                                                                                                                | 595 |

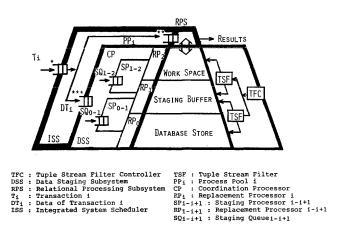

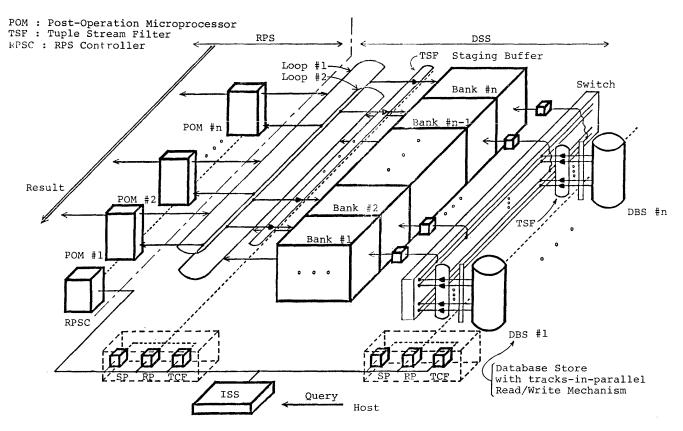

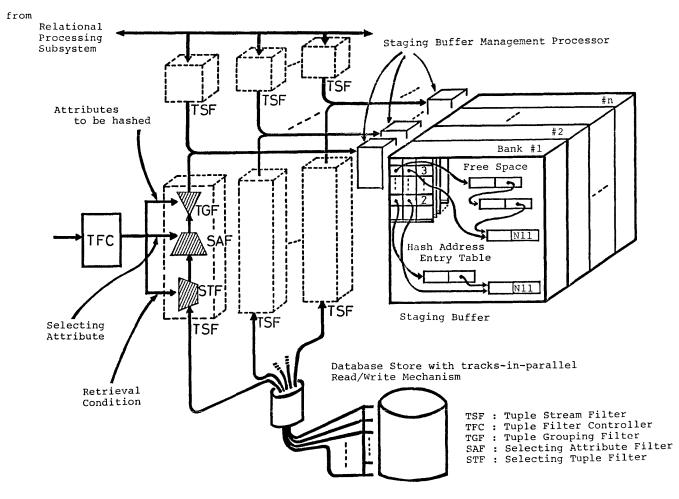

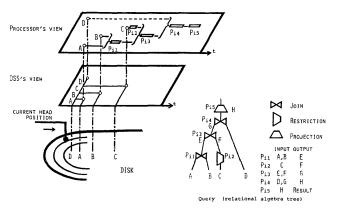

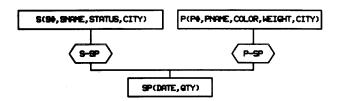

| SPIRIT-III: an advanced relational database machine introducing a novel data-staging architecture<br>with Tuple Stream Filters to preprocess relational algebra<br>Noriyuki Kamibayashi and Kazuo Seo | 605 |

| Data language requirements of database machines<br>Dawei Luo, Daozhong Xia, and S. Bing Yao                                                                                                           | 617 |

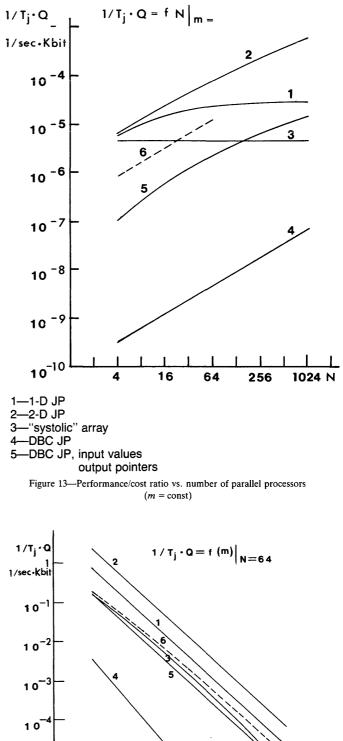

| Performance analysis of database join processors<br>Fu Tong and S. Bing Yao                                                                                                                           | 627 |

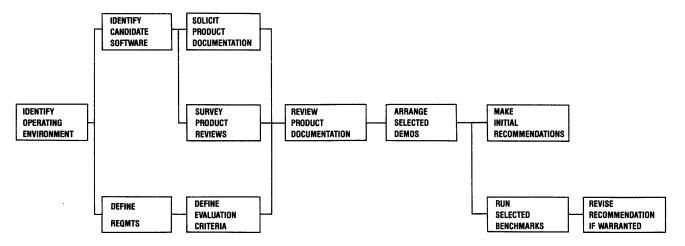

| Evaluating database management systems<br>Edward Davidson                                                                                                                                             | 639 |

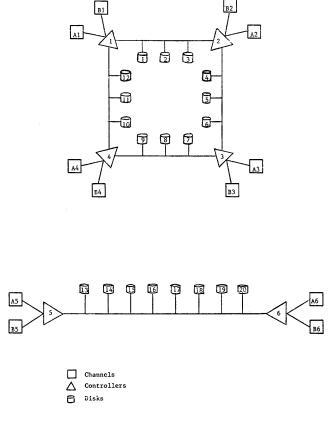

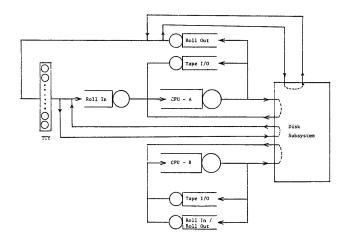

| Performance study of a dual CDC Cyber 170/750 system<br>M. Seetha Lakshmi and Tom W. Keller                                                                                                           | 649 |

| Computational lexicology: A research program<br>Robert A. Amsler                                                                                                                                      | 657 |

| Use of Webster's Seventh Collegiate Dictionary to construct a master hyphenation list                                                                                                                 | 665 |

| Models, languages, and heuristics for distributed computing<br>Robert E. Filman and Daniel P. Friedman                                                                                                | 671 |

| Weakest environment of communicating processes                                                                                                                                                        | 679 |

| Adaptive structuring of distributed databases                                                                                                                                                         | 691 |

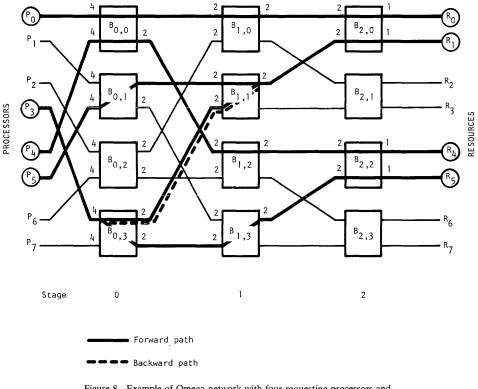

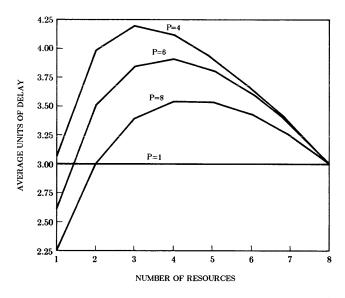

| Distributed scheduling of resources on interconnection networks<br>Benjamin W. Wah and Anthony Hicks                                                                                                  | 697 |

| APPLICATIONS OF COMPUTING                                                                                                                                                                             |     |

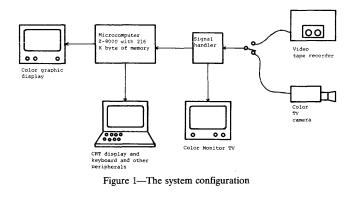

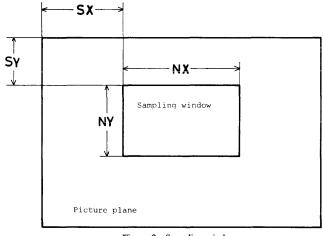

| A microcomputer system for color video picture processing                                                                                                                                             | 713 |

•

| The importance and futility of device independence in computer graphics                                                                                | 719 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

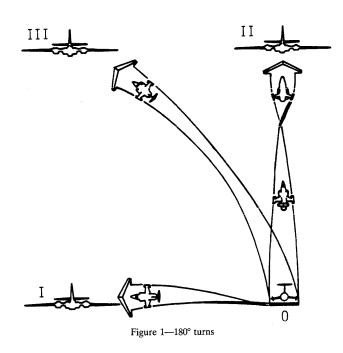

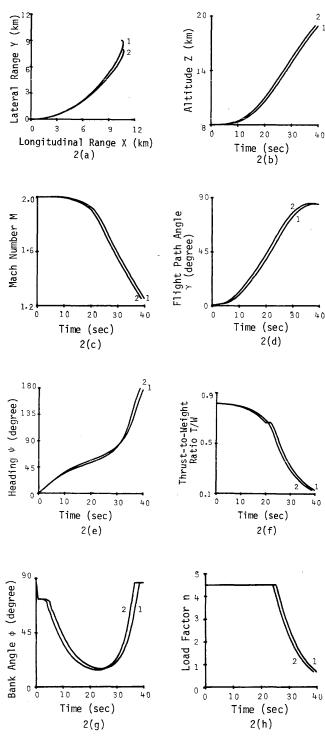

| Optimal three-dimensional flight control of a supersonic fighter<br>Ching-Fang Lin and Khai Li Hsu                                                     | 727 |

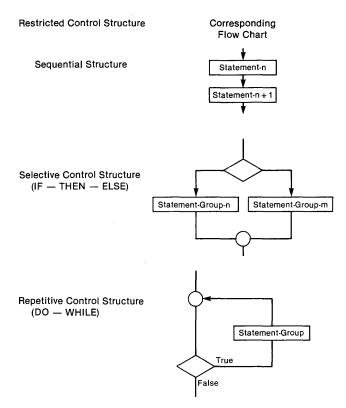

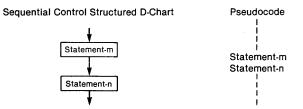

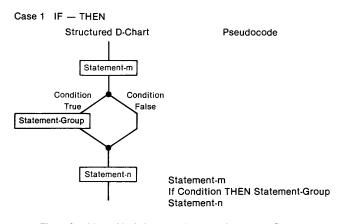

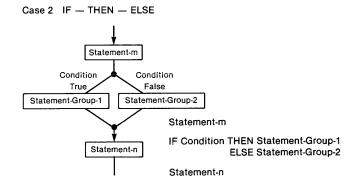

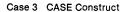

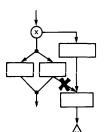

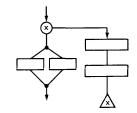

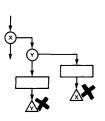

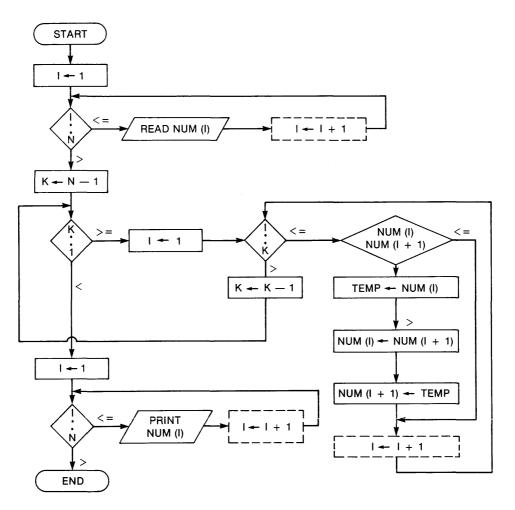

| Structured D-chart: A diagrammatic methodology in structured programming<br>C. Jinshong Hwang                                                          | 735 |

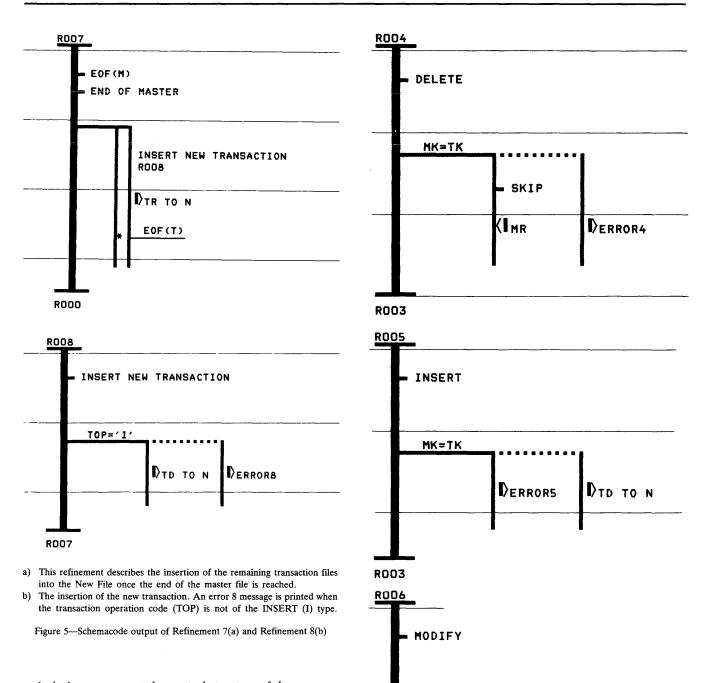

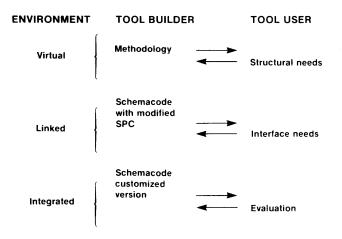

| Planning for software tool implementation: experience with Schemacode<br>Pierre N. Robillard and Réjean Plamondon                                      | 749 |

| Distributed processing of problem-solving applications for farmers<br>Robert Gammill and Lynn Thorp                                                    | 759 |

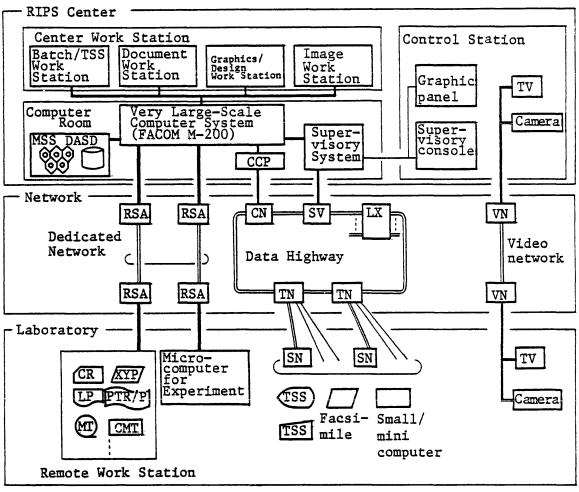

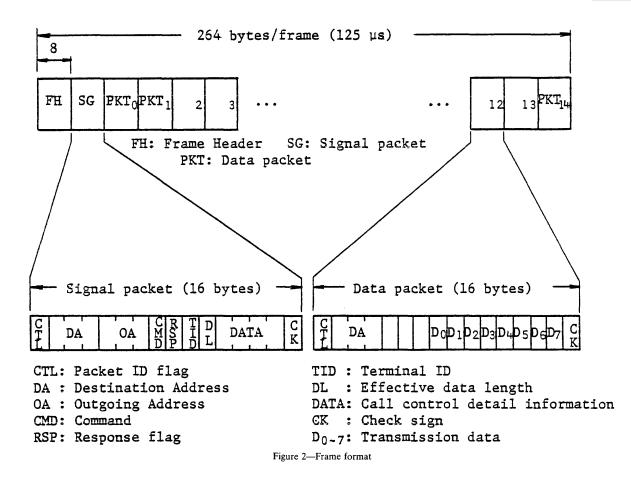

| RIPS net: The impact of an optical communication network                                                                                               | 767 |

| A coherent scheme to support location-independent references in internetwork environment<br>Ray Cheng and J. W. S. Liu                                 | 775 |

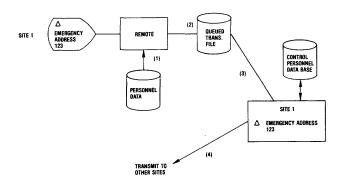

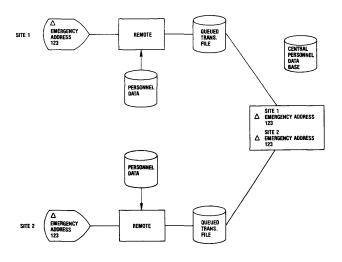

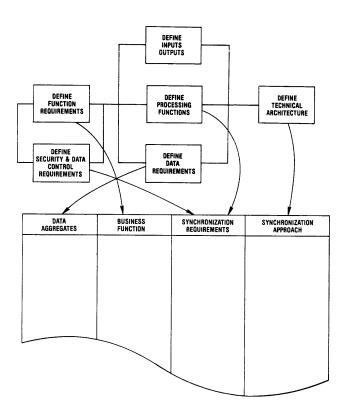

| Issues and methods for practical distributed data processing applications—IIssues and methods for practical distributed data processing applications—I | 785 |

| Issues and methods for practical distributed data processing applications—IIII                                                                         | 793 |

| PIONEER DAY                                                                                                                                            |     |

| A technological review of the FORTRAN I compiler<br>F. E. Allen                                                                                        | 805 |

| Computing prior to FORTRAN<br>R. W. Bemer                                                                                                              | 811 |

| History of FORTRAN standardization                                                                                                                     | 817 |

| DYSTAL: Nonnumeric applications of FORTRANJames M. Sakoda                                                                                              | 825 |

HARDWARE/COMPUTER ARCHITECTURE

.

### Firmware quality assurance

by HELMUT K. BERG and PRAKASH RAO

Honeywell Corporate Computer Sciences Center Bloomington, Minnesota and BRUCE D. SHRIVER University of Southwestern Louisiana Lafayette, Louisiana

#### ABSTRACT

The paper reviews problems, solutions, and trends in the area of firmware quality assurance. Firmware quality assurance is considered to be the certification of the fact that a firmware system meets its requirements with respect to functional correctness as well as performance, operational, and implementational properties. The emphasis of the paper is on formal correctness proofs, firmware testing, and the automatic synthesis of microcode and associated hardware structures. Firmware specifications, high-level microprogramming languages, and automated support tools are discussed as they relate to these areas. The impact of advances and trends in very large-scale integration (VLSI) on the techniques and tools for firmware quality assurance is reviewed. The observation is made that valuable results have been obtained in the areas of firmware correctness proofs and firmware testing. However, further improvements are needed to cope with the complexity of VLSI. An alternative that may overcome the limitations of these two approaches is automated synthesis of firmware and hardware and design for testability.

#### A. INTRODUCTION

For products of any kind, assurance needs to be gained that they meet their product requirements before they are dedicated to serve their intended purpose. This need applies to end-user or consumer products as well as to the individual components to be integrated into such products. The product requirements may be stated in a variety of forms, including assessments of market needs, functional product specifications, and specifications of nonfunctional product attributes. The form of these requirement statements changes as the development of a product proceeds from the marketing product definition through the product design and implementation to the use and maintenance of the product. This process is referred to as the product life cycle, and it comprises various stages in each of which the ability of the product to meet its requirements is established. These certification steps may be summarized under the term quality assurance.

Ideally, firmware is developed and deployed in a life cycle that includes the following steps. The development begins with a step called requirements engineering. Given the purpose of the system, this step identifies the functional requirements and attributes of the system. Nonprocedural design formalizes these requirements and attributes in the form of functional and property specifications. The procedural design uses the specifications to produce "blueprints" for the implementation. The implementation step embodies the blueprints in system modules and microprograms. The integration step combines and tests the modules and microprograms so that the assemblage results in an operational firmware system. In the installation step, the firmware system is integrated into the overall system and submitted to operation. Maintenance is concerned with corrections and extensions to the operational firmware.

Every step in the firmware life cycle is associated with an appropriate validation step. For example, it needs to be demonstrated that the requirements and attributes conform to the statement of the purpose. The correspondence between requirements and specifications needs to be demonstrated. Obviously, it should be verified that each step in the development process was conducted correctly.

The quality of the firmware refers not only to the functional correctness of the integrated microprograms, but also to the performance, operational, and implementational properties of the system. Among the properties of a firmware system, we may find execution time, object microprogram size, reliability, robustness, and viability. Hence, *firmware quality assurance* may be defined as the certification of the fact that a firmware system meets its requirements in an optimal way. In this definition, optimality is not assumed to be an absolute measure. In fact, the optimization of some of the firmware

properties listed above has been shown to be NP-hard.<sup>1</sup> Furthermore, absolute functional correctness cannot be established by testing, and formal correctness proof methods, which theoretically have the ability to demonstrate the absence of errors, have generally not reached the point of being rigorously applicable in firmware development environments.<sup>2</sup>

The need for firmware quality assurance has been discussed widely in the literature. The necessity for the verification of functional correctness<sup>9</sup> stems from two intrinsic characteristics of firmware:

- microprograms control all native hardware resources. Thus, microprogram errors result in an erroneous virtual machine, and

- microprograms very often reside in read-only storage media. Thus, modifications and error corrections can be both difficult and costly.

The need for the optimization of execution speed and object microprogram size<sup>3</sup> is dictated by the desire to

- realize faster and functionally more powerful machines, with available technology, and

- obtain the extensive benefits of high-level microprogramming languages in the firmware development process.

The need for firmware quality assurance is intensified by technological advances, most importantly by very-large-scale integration (VLSI).<sup>4</sup> Hardware performing specialized functions is being replaced by regular arrays of logic and memory. The functionality of the firmware is changing from conventional instruction set emulators to more extensive and powerful instruction sets, diagnostic programs, interpreters for highlevel languages, and operating system functions. In addition, the integration of microprogrammed control schemes into VLSI places more stringent requirements on tools and techniques for firmware quality assurance, which cannot be met by traditional microprogramming aids.

In summary, the major concerns in firmware quality assurance are

- the specification of functions and properties of firmware systems,

- the realization of correct and optimal microcode, together with appropriate hardware structures, and

- automated tools that aid the designer in exploring alternative designs and in keeping track of design and implementation details.

It is not possible in this paper to treat entire methodologies and engineering environments for firmware development and 6

quality assurance. We restrict our attention to areas of formal firmware correctness proofs, firmware testing, and the automatic synthesis of microcode and associated hardware structures. Firmware specifications, high-level microprogramming languages, and automated support tools are discussed only as they relate to these areas.

#### **B. VERIFICATION OF FIRMWARE**

Firmware verification through formal correctness proofs is an area of firmware engineering that received considerable attention over the last decade.<sup>6</sup> Although several approaches to firmware correctness proofs have been developed and demonstrated, problems remain at all levels. Among these problems are the development of appropriate theoretical foundations, the definition of design disciplines that support correctness proofs, tool support for correctness proofs, and the education of users regarding formal techniques. Despite these problems and the controversies surrounding formal correctness proofs in general,<sup>7</sup> some workers report that no matter how expensive it is to find errors by firmware verification it is still a magnitude cheaper than finding errors when a product is shipped.<sup>8,9</sup> This section reviews firmware verification by summarizing some efforts in the area, discussing their contribution to quality assurance, and indicating possibilities and limitations in their use.

#### **B.1** Approaches to Firmware Verification

Approaches to firmware verification generally draw from results obtained in software verification.<sup>10</sup> Given the current state of the art, correctness proof processes are inherently complex, and cannot be fully automated. Human interaction with verification systems is required to suggest proof goals, to partition proofs, and to interpret results obtained from the proof system to direct the continuation of the proof process.

The STRUM system<sup>11</sup> is an advanced verification system that is based on Floyd's inductive assertion technique<sup>12</sup> and uses a Pascal-like high-level microprogramming language. The automated proof process is integrated into the translation process.

Another successfully applied verification system is the IBM Microprogram Certification System (MCS).<sup>13</sup> This system is based on Milner's technique of the simulation between programs<sup>21</sup> and the symbolic execution of programs.<sup>22</sup> A similar approach is being pursued at the Information Science Institute of the University of Southern California.<sup>23</sup> The MCS approach considers both the description of the host system on which the microcode is to run and of the target system that is being emulated by the microcode. The verification system accepts the host microcode and its specification, including proof commands, to establish the equivalence of both firmware definitions by symbolic execution and the proof of simulation relations.

A third approach that has received considerable attention is the microprogramming language schema S<sup>\*</sup>.<sup>24</sup> This approach defines an axiomatic basis for microprogramming similar to Hoare's axiomatic definition of programming languages.<sup>25</sup> The axiomatic basis is a set of schemas that define the semantics of a Pascal-like microprogramming language. These schemas constitute the axioms and inference rules of a deductive system in which formal correctness proofs can be carried out using the defined logical inferences. For each particular machine, the schematic semantic definitions can be instantiated to capture the machine-dependencies influencing the execution of the firmware on that machine. Thus, after the instantiation, the microprogrammer works with a machine-dependent, but high-level, axiomatic proof system.

For a survey of other approaches to firmware verification, the reader is referred to Davidson and Shriver (1980).<sup>6</sup>

#### **B.2** Status of Firmware Verification

Successful application of firmware correctness proofs has established firmware verification as a viable approach to firmware quality assurance. Two major observations need to be made, however. First, correctness proofs are complex in nature; thus the verification process needs to be incorporated into an overall firmware engineering discipline that is supportive of correctness proofs; additionally, the proof process itself needs to be supported by automated tools. Second, quality assurance is not restricted to the functional correctness of firmware, but is also concerned with execution time and memory efficiency of the executable code as well as with the reliability of firmware systems in general. Thus, verification approaches need to be developed based on high-level microprogramming languages that facilitate abstract representations of firmware systems and allow code optimization. It is imperative that the user be able to understand what the system is supposed to do.

The systems described above partially satisfy these requirements. The STRUM system has been applied to the development of the emulator for the Hewlett-Packard HP-2115.11 Besides the verification of the microcode written in the highlevel language, the resulting code could be optimized to match an independently generated, hand-optimized version of the same microcode. The success of the microcode verification system used for the Fault-Tolerant Spaceborne Computer (FTSC) is partially due to the guiding principle of that project.<sup>23</sup> It concentrates on the practical side of the verification problem, solving the theoretical problems as they arise. Emphasis is placed on ways of making the user understand what the system is doing and writing the microcode with the subsequent verification in mind. The FTSC project is explicitly seeking an approach to a disciplined firmware design and development process. Additionally, software engineering approaches can be enhanced further for the production of more reliable microcode. For example, techniques such as code inspections, walk-throughs, or step-wise refinement may be integrated into the firmware engineering discipline.

In summary, languages and quality assurance techniques are needed that help the microprogrammer with machine dependent problems such as microparallelism, microcode optimization, and the variability in computer micro-architectures, on the one hand, and support abstract representations of firmware systems, on the other hand. Progress made toward these seemingly conflicting goals is best reflected by high-level microprogramming languages such as MPL,<sup>26</sup> STRUM,<sup>11</sup> EMPL,<sup>27</sup> VMPL,<sup>28</sup> and S<sup>\*</sup>.<sup>24</sup> Most of these languages effectively attack the problem of code optimization,<sup>3</sup> but problems remain in the area of verification.

#### B.3 Summary

Limitations in firmware verification techniques result from several fundamental weaknesses of the proposed approaches. The weaknesses include the inadequate specification of the timing characteristics of the control flow in semantic definitions of microinstructions. Furthermore, the deductive systems (i.e., the set of available logical inferences) for carrying out firmware correctness proofs are not related closely enough to the characteristics of the underlying hardware. These weaknesses limit the practicality of firmware correctness proofs even for moderately sized microprograms. The inclusion of parallelism, synchronization, and microinstruction execution subcycles will considerably increase the complexity of the correctness proof. Powerful interactive capabilities may mitigate this deficiency of verification systems. Correctness proof techniques need to acquire conceptual foundations that bridge the gap between high-level machineindependent firmware representations and specific microprogram running environments, in order to cope with the firmware complexity anticipated for VLSI.

Several approaches to the solution of this problem have been proposed. These approaches require that the firmware quality assurance process be carried out in a high-levellanguage environment in which mappings to machine specific environments can be automated. The approaches include axiomatization of the running environment,<sup>24,30</sup> explicit descriptions of the microprogram running environment,<sup>23,31</sup> and machine virtualization.<sup>28,32</sup> Although most of these approaches still need to be demonstrated for problems of the scope anticipated for VLSI, it is certain that they will be viable alternatives to firmware verification only if they are supported by sophisticated tools that automate design, coding and verification.

#### C. TESTING OF FIRMWARE

Firmware testing is the assurance of firmware functionality for a specified set of input values. By definition, then, firmware testing does not necessarily assure functional correctness for all legitimate input values and is not as strong an argument about the correctness of microprograms as that provided by formal correctness proofs. Under the restriction imposed by the absence of sufficiently versatile verification methods, firmware testing is one of the alternatives available for assuring the quality of firmware.<sup>5,2</sup>

Firmware testing has traditionally been viewed as an extension to the testing of software.<sup>2</sup> With the impact of VLSI, it is no longer possible to separate the functionality of the underlying hardware from the microprograms that control it.<sup>4</sup> The increasing degree of integration of microprograms with their hardware environment also requires a unified approach to the design of the firmware and its supporting hardware. This design approach, called "design for testability,"<sup>33</sup> incorporates the important concept of testability directly into the synthesis procedure and thereby enhances the assurance of firmware system quality. The discussion of design for testability is deferred to the next section.

#### C.1 Firmware Testing

Microprogram testing has been addressed by Berg.<sup>2</sup> Formal techniques of firmware testing and test data selection have been specified. Three levels of microprogram testing have been identified. These are

- Tests at the microprogram level that consider complete microprograms by either analyzing their code or investigating the machine states resulting from their execution.

- Tests at the microinstruction level that consider single microinstructions by either analyzing the assignment of micro-operations to them or investigating the machine states resulting from their execution.

- Tests at the micro-operation level that consider individual micro-operations by monitoring their execution.

An error detected at the microprogram level may be caused by any number of faulty microinstructions or micro-operations in the microprogram. The manifestation of such errors is defined by the identification of a set of faulty microinstructions and micro-operations. To identify faulty microinstructions or micro-operations in an erroneous microprogram, tests at the microinstruction level may be necessary. An error detected at the microinstruction level is located if the set of faulty micro-operations in the microinstruction can be identified.

The selection of tests and test data for firmware testing at each of these three levels is based on the methods described by Goodenough and Gerhart.<sup>5</sup> The basis for correct function is the program specification. The method distinguishes between test data and test predicates.

#### C.2 Hardware Testing

Hardware testing has traditionally been viewed in isolation, despite increasing trends towards the implementation of systems as microprogrammed control structures. With the integration of hardware and firmware in VLSI a major problem is the diminishing observability and controllability of the hardware due to pin limitations. Hardware testing will therefore entirely devolve on the micro-operations that it supports. As a consequence, hardware must be tested at the register transfer level, where a description of the system is specified in terms of the hardware resources and their interconnection. This requirement necessitates that the degree of encoding of microinstructions be restricted to keep testability as an objective during the design process.

A significant step toward the testing of hardware through the microprogramming level and the implementation of serviceability features was taken during the design of the IBM System/360 as reported in Carter et al. (1964).<sup>14</sup>

Hardware test strategies for microprogrammed units use a partitioning of the unit into an operative part and a control part.<sup>18</sup> The operative part consists of the hardware resources

and the control part of the algorithms for their operation and sequencing. A methodology for generating an internal microprogram to test a microprogrammed unit is described by Ciaramella.<sup>19</sup> The dynamic testing of control units has been reported by Robach and Saucier.<sup>38</sup>

Identification of the control and operative parts of the system is performed from a behavioral description of the system hardware function. This description can be given using a highlevel design language such as a register-transfer language (RTL) or a multiple-level design language such as LALSD-Language for Automated Logic and System Design<sup>16</sup>—or SIMPL (Simple Identity Microprogramming Language).<sup>17</sup> Techniques for generating tests from such behavioral descriptions are mentioned by Su and Hsieh<sup>20</sup> and Levendel and Menon.<sup>15</sup> The area of behavioral-level testing of digital systems is still in a period of evolution. This problem is further complicated by the fact that hardware access is limited to the microprogramming level. Techniques for the development of hardware support functions needed for firmware system quality assurance still need to be formalized. The evolution of abstract fault models at the behavioral level will be of great assistance in the development of test-generation algorithms for testing microprogrammed units. Developments in this direction have been started in the area of microprocessor testing.37

#### C.3 Summary

The problem of firmware testing can be divided into two subtasks: the testing of microprograms and the testing of the underlying hardware. The problem of microprogram testing is addressed by borrowing concepts from software testing. Approaches to hardware testing using a high-level description of the hardware resources and their interconnection is still in its infancy. This problem will be increasingly aggravated as more and more firmware systems are implemeted in VLSI.

## D. AUTOMATED SYNTHESIS AND DESIGN FOR TESTABILITY

In this section, we take a look at the future growth of firmware and microprogrammed systems and highlight issues of testability that arise owing to the increased complexity and the reduced access to the hardware as dictated by the restricted pin count.

#### D.1 Characteristics of the Design Environment

The future of microprogramming will be greatly affected by the characteristics of VLSI design. With the cost advantage and support of design tools for fast turnaround, single-chip designs in VLSI will become increasingly common. Complex structures such as parallel architectures will be designed routinely using sophisticated design aids for hardware and microcode.<sup>4</sup> Trends in the development of high level microprogramming languages as described in Section B contribute to this development. The microprogram verification problem has therefore been brought closer to a solution in terms of facilities for looking at analogs in the software field. The migration of microprogrammed control units of very high complexity into VLSI brings in all the problems that VLSI designers of digital systems have been facing. The increase in complexity, the choice of design styles, architectures, and implementation technologies provide a design environment in which a number of tradeoffs have to be made between several objectives. The most important of these objectives are

- to minimize cost by minimizing silicon area and pin count,

- to maximize performance in terms of speed,

- to increase chip functionality by providing more powerful instructions,

- to increase chip fault tolerance,

- to provide an enhanced user interface,

- to achieve reasonably fast design turnaround time and minimize design costs, and

- to minimize power consumption.

Usually, a tradeoff is made between economy of silicon area and performance, fault tolerance, ease of use, and design turnaround time. This often implies that fault tolerance has to be traded off for real estate on silicon. Thus, there is a need for building fault tolerance into the design itself and to minimize the overhead that caused the tradeoff for real estate. Specific design rules that aid the testability of VLSI must be developed.

With the increase in complexity and with the design problem constrained to be an optimization of multiple objectives, designers of the future will have no other alternative but to employ automated tools. To be viable, these tools must aid in the design of the microcode as well as in the synthesis of the hardware implementing the design specification. The need for quality assurance, therefore, dictates the requirement that these tools have testability as an objective.

Research in microprogram design aids has been classified into three classes:<sup>4</sup>

- microcode verification

- microcode generation from a high level language

- synthesis of microcode and microcontroller hardware from high-level specifications.

These research areas have been dealt with in the literature.  $^{11,34,35,36}$

#### D.2 Testability and Automated Hardware/Firmware Synthesis

Automated synthesis has been attempted with varying degrees of success. The MIMOLA system<sup>36</sup> provides interaction between user and system. It generates microcode based on the input of user-declared data paths and hardware resources. Hardware measures are provided to aid in monitoring the efficiency of the design and to identify critical paths. The designer interactively varies hardware restrictions to satisfy the performance and cost requirements. There is no design for testability built into the generation procedure for microcode. The microcode generated has a degree of encoding restricted to function-select lines and multiplexers.

The problem of providing adequate testability may be addressed at two levels by

- incorporating design for testability at the structural or implementation level of description when the logic is being committed; or by

- incorporating design for testability techniques at the behavioral or specification level.

Traditional methods of design for testability have taken the first approach. At the implementation level, additional hardware is provided to enable the input of test patterns and the breaking of feed-back loops. The latter reduces the testing problem to the more tractable task of testing combinatorial circuits. An extensive survey of design for testability methods of this type is reported in the literature.<sup>33</sup> In this approach, design rules are formulated with design edicts laid down to ensure that access for testability is provided.

The incorporation of design for testability at the behavioral or specification level is relatively new and results of a substantial nature are yet to be reported. In this approach, testability is incorporated into the synthesis procedure as an objective. The design of the micro-operation and microinstruction structures and the generation of microprograms is conducted with the testability of the registers and functional units in mind. Inaccessible registers are not permitted and the length limitation on the longest checking sequence needed to test functionality in functional blocks and registers is one of the constraints in the synthesis procedure.

#### D.3 Summary

We conclude that there is a future trend toward single-chip implementation of firmware systems bringing with it the use of automated-synthesis tools and microprogram-design aids. There is a need to build testability into the synthesis procedure at a high level in the design process. There is considerable need for further research in this area. Until substantial results have been obtained designers will continue to use the conventional techniques of utilizing additional hardware overhead to provide adequate testability.

#### REFERENCES

- Robertson, E. L.: "Microcode Bit Optimization Is NP-Hard", SIGMICRO Newsletter, Vol. 8, 1977, pp. 40–43.

- Berg, H. K. "Firmware Testing and Test Data Selection", Proceedings of the 1981 National Computer Conference, Vol. 50 AFIPS Press, Arlington, Va., 1981, pp. 75–80.

- Landskov, D.; S. Davidson, B. Shriver, P. W. Mallett. "Local Microcode Compaction Techniques," *Computing Surveys*, Vol. 12, No. 3, 1980, pp. 261–294.

- Parker, A. C., W. T. Wilner. "Microprogramming—The Challenge of VLSI," Proceedings of the 1981 National Computer Conference, Vol. 50, AFIPS Press, Arlington, Va., 1981, pp. 63–68.

- Goodenough, J. B., S. L. Gerhart. "Toward a Theory of Test Data Selection" *IEEE Transactions on Software Engineering*, Vol. 1, No. 2, 1975, pp. 20–37.

- Davidson, S., B. D. Shriver. "Firmware Engineering: An Extensive Update," in *Firmware, Microprogramming and Restructurable Hardware*. North-Holland Publ. Co., New York, 1980, pp. 1–40.

- DeMillo, R. A., R. J. Lipton, and A. J. Perlis. "Social Processes and Proofs of Theorems and Programs," *Communications of the ACM*, Vol. 22, No. 5., 1979, pp. 271–280.

- Husson, S. S. (panel chairman). "Microcode Verification—Summary of the Panel Discussion," in *Firmware, Microprogramming and Restructurable Hardware*, North-Holland Publ. Col., New York, 1980, pp. 105.

- Carter, W. C., "Microcode Verification," Presentation in the Session on Microprogramming—The Challenge of the 1980's, 1981 National Computer Conference, Chicago, II.

- Berg, H. K., W. E. Boebert, W. R. Franta, and T. G. Moher. Formal Methods of Program Verification and Specification, Prentice-Hall, Englewood Cliffs, N.J., 1982.

- Patterson, D. A. "STRUM: Structured Microprogramming System for Correct Firmware," *IEEE Transactions on Computers*, Vol. 25, No. 10, 1976, pp. 974–986.

- Floyd, R. W. "Assigning Meaning to Programs," *Proceedings of Symposia* in Applied Mathematics, American Mathematical Society, Vol. 19, 1967, pp. 19–32.

- Joyner, W. H., W. C. Carter, and G. B. Leeman. "Automated Proofs of Microprogram Correctness," *SIGMICRO Newsletter*, Vol. 7, No. 3, 1976, pp. 51–55.

- Carter, W. C., H. C. Montgomery, R. J. Preiss, and H. J. Reinheimer. "Design of Serviceability Feature for the IBM System/360," *IBM Journal*, 1964, pp. 115–126.

- Levendel, Y. H., and P. R. Menon. "Test Generation Algorithm for Nonprocedural Hardware Description Languages", *IEEE FTCS-11*, 1981, pp. 200–105.

- Su, S. Y. H., and C. L. Huang. "A Multi-Level Hardware Design Language LALSD II and its Translator," Proceedings of the 1981 International Symposium on CHDL's and Their Application, 1981.

- Tsuchiya, M., and L. V. Ramamoorthy. "Design of a Multi-Level Microprogrammable Computer and a High-Level Microprogramming Language," University of Texas at Austin, Tech. Report 135, 1972.

- Hill, F. J., and B. Hueg. "SCIRTISS: A Search System for Sequential Circuit Test Sequences," *IEEE Transactions on Computers*, Vol. C-26, No. 5, 1977, pp. 490–502.

- Ciaramella, A. "Testing of Microprogrammed Units," *IEEE FTCS-9*, 1979, pp. 161–163.

- Su, S. Y. M., and Yu-I Hsieh. "Testing Functional Faults in Digital Systems Described by Register Transfer Language," *1981 IEEE Test Conference*, 1981, pp. 433–439.

- Milner, R. "An Algebraic Definition of Simulation between Programs," Proceedings of the 2nd International Joint Conference on Artificial Intelligence, 1971, pp. 481–489.

- Darringer, J. A., and J. C. King, "Application of Symbolic Execution to Program Testing," *Computer*, Vol. 11, No. 4, 1978, pp. 51-60.

- Crocker, S. D., L. Marcus, and D. van-Mierop. "The ISI Microcode Verification System," *Firmware, Microprogramming and Restructurable Hard*ware, North-Holland Publ. Co., New York, 1980, pp. 89–103.

- Dasgupta, S. "Some Implications of Programming Methodology for Microprogramming Language Design," *Firmware, Microprogramming and Restructurable Hardware*, North-Holland Publ. Co., New York, 1980, pp. 243–252.

- Hoare, C. A. R. "An Axiomatic Basis for Computer Programming," Communications of the ACM, Vol. 12, No. 10, 1969, pp. 576–583.

- Eckhouse, R. H. "A High Level Microprogramming Language (MPL)," *Proceedings of the 1971 Spring Joint Computer Conference*, AFIPS Press, Arlington Virginia, 1971.

- Dewitt, D. J. "Extensibility—A New Approach for Designing Machine Independent Microprogramming Languages," *SIGMICRO Newsletter*, Vol. 7, No. 3, 1976, pp. 33–41.

- Malik, K., and T. G. Lewis. "Design Objectives for High-Level Microprogramming Languages," *SIGMICRO Newsletter*, Vol. 9, No. 4, 1978, pp. 154–160.

- Carter, W. C.; W. H. Joyner, and D. Brand. "Microprogram Verification Considered Necessary," *Proceedings of the 1978 National Computer Conference*, AFIPS Press, Arlington, Virginia, 1978, pp. 657–664.

- Berg, H. K., and W. R. Franta. "Firmware Engineering: Critical Remarks and a Proposed Strategy," *Firmware, Microprogramming and Restructurable Hardware*, North-Holland Publ. Co., New York, 1980, pp. 41–64.

- Richter, L. "High-Level Language Extensions for Micro-Code Generation and Verification," *Firmware, Microprogramming and Restructurable Hardware*, North-Holland Publ. Co., New York, 1980, pp. 233–242.

- Davidson, S., and B. D. Shriver. "MARBLE: A High Level Machine Independent Language for Microprogramming," *Firmware, Microprogramming and Restructurable Hardware*, North-Holland Publ. Co., New York, 1980, pp. 253–266.

- Williams, T. W. and K. P. Parker. "Design for Testability—A Survey," IEEE Transactions on Computers Vol. C-31, No. 1, 1982, pp. 2–15.

- Marwedel, P. "A Retargetable Microcode Generation System for a High-Level Microprogramming Language," *SIGMICRO Newsletter*, Vol. 12, No. 4, 1981, pp. 115–123.

- Van Mierop, D., S. Crocker, and L. Marcus. "Verification of the FTSC Microprogram," SIGMICRO Newsletter, Vol. 9, No. 4, 1978, pp. 118.

- Zimmermann, G. "The MIMOLA Design System: A Computer Aided Digital Processor Design Method" Proceedings of the 16th Design Automation Conference, 1979, pp. 53-58.

- Thatte, S. M. and J. A. Abraham. "Test Generation for Microprocessors," *IEEE Transactions on Computers*, Vol. C-29 (1980), pp. 429–441.

- Robach, C., and G. Saucier. "Dynamic Testing of Control Units," *IEEE Trans. on Computers*, Vol. C-27, July 1978, pp. 617–623.

## The 5.25-inch fixed/removable disk drive

by DON M. MINAMI DMA Systems Corporation Santa Barbara, California

#### ABSTRACT

The fixed/removable 5.25-inch Winchester drive provides combined computer peripheral support functions, such as mass storage, input/output, and backup. The 13.5-MByte total capacity (6.75 MBytes fixed/6.75 MBytes removable) is packaged in a unit about the size of a shoebox.

Reliability has been the major factor in determining the design parameters of the fixed/removable drive. Not only has Winchester reliability been enhanced, but preventive maintenance has been eliminated.

#### INTRODUCTION

Reliable mass storage at a relatively low cost is the driving force behind the trend toward increased use of Winchester disk technology for small computer systems. Although the conventional Winchester drive offers high reliability due to its nonremovable media, it requires some form of data file backup. One solution is to use a tape drive for backup; this allows adequate backup storage capacity, but it is too slow and not form-factored for many small computer systems. Another solution is to use a flexible disk drive, but it does not provide sufficient mass-storage capacity without resorting to multiple diskettes.

A better solution is a Winchester disk drive for both fixed and removable media in a single unit that provides mass storage, input/output, and backup. The 5.25-inch Micro-Magnum 5/5 (see Figure 1) from DMA Systems is the first such drive

Figure 1-Micro-magnum 5/5

with a fixed disk and a removable disk cartridge built to the proposed ANSI standard. The Micro-Magnum 5/5 offers significant reliability and performance advantages which include the following:

- 1. No preventive maintenance or head alignment required

- 2. Heads retracted from the media surface, thus preventing damage

- 3. The necessity of external backup devices and their controllers is eliminated

- 4. Reduced space and power requirements

- 5. Faster backup time because of a higher disk transfer rate

- 6. Reduced component count

- 7. Reduced overall system cost

The origin of the Micro-Magnum 5/5 and the product design specifications were derived from a market survey. This survey included inputs from system manufacturers, system integrators, component suppliers, and computer industry consultants. The result of this survey was a product specification which emphasized reliability in terms of product life, data integrity, data interchange, and freedom from preventive maintenance.

#### GENERAL SPECIFICATIONS

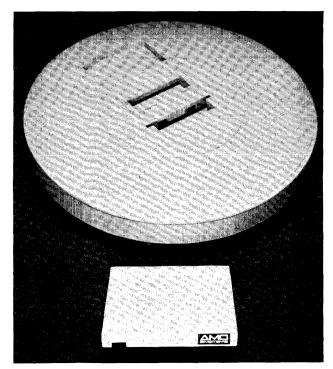

The Micro-Magnum 5/5 is designed with 6.75 MBytes (5.0 formatted) fixed and 6.75 MBytes (5.0 formatted) removable. The drive uses an ANSI-proposed 5.25-inch removable disk cartridge (see Figure 2) with 5.0 MBytes of formatted data. The front panel face is 3.25 inches high by 5.75 inches wide, which is typical of 5.25-inch Winchester drives.

The 5 MBytes per disk formats 306 tracks with 33 sectors

Figure 2—Micro-magnum cartridge compared to the traditional 14-inch disk cartridge

(one spare sector) and 256-byte sectors on each surface. The recording density is 8600 fci using MFM encoding, and the track density is 450 tpi.

#### TRACK FOLLOWING

Accurate and repeatable positioning of the read/write heads is a necessity in the fixed/removable drive in order to maintain data interchangeability. The primary complication is the removable cartridge being used as a means for data interchange and transportability.

The drive, in conjunction with the disk cartridge, must allow for mistracking errors, cartridge registration errors, temperature gradients, spindle runout, and head-track width tolerances. This mechanical error budget requires a trackfollowing system which will compensate for these variations. The elimination of precise head alignment is also as important; the market survey indicated that any such field maintenance procedures would not be tolerated.

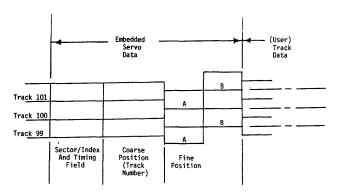

To overcome the errors due to thermal expansion, the problems of cartridge interchange, and the elimination of field maintenance, embedded servo positioning was selected for the Micro-Magnum 5/5. Embedded servo data (see Figure 3) is prerecorded during the manufacturing of the drive and the cartridge, and it is contained in the 26 bytes at the start of each sector. The embedded servo format has been submitted to ANSI for standardization. (A copy of the proposed servo format can be obtained by contacting DMA Systems or ANSI.)

Figure 3-Embedded servo data

Embedded servo positioning is a two-step process. First, course positioning allows the proper track to be located; second, the fine positioning locates the read/write over the center of the desired track. As the desired track is being sought, the course-positioning process is activated. The course-positioning process uses a Gray code for each track number and is prerecorded as part of a 26-byte servo format. As the desired track is approached, within half a track, fine positioning takes over. Prerecorded signal segments A and B (see Figure 3) define the fine-positioning servo bursts. The edges of A and B are along the centerline of the tracks, so that a head centered exactly on a track will read equal amplitudes

from both segments. If the head is off-center, one amplitude will read higher and the other, lower. The difference is detected and used as an error signal to drive a linear motor positioner to seek a zero error to maintain the proper track centerline position.

#### LINEAR MOTOR

The linear motor, in conjunction with the embedded servo track-following system, provides not only fast access time (40 msec average) but also reliability. Figure 4 shows the Micro-Magnum 5/5 linear motor positioner assembly.

Figure 4-Carriage head and linear motor

The reliability features of the linear motor positioner are the following:

- 1. The heads are allowed to be fully retracted off the disk surface and latched into position inside the drive.

- 2. Contamination control is improved due to the smaller cartridge and drive-door openings.

- 3. Head gaps move in a radial line, giving the best possible tolerance for cartridge interchange.

- 4. The structural resonance is better controlled.

- 5. Manufacturing of the head-carriage assembly is simplified.

#### HEAD-MEDIA CONTACT

Two problems can result from head-media contact; the head and/or the media surface can be damaged. Therefore, optimal data reliability can only be obtained by making it impossible for the head to ever make contact with the media. In the Micro-Magnum drive, the heads are never allowed to make contact with the disk. This is achieved by a patented head design (see Figure 5) which allows a Winchester air bearing to be loaded dynamically onto a spinning disk. (Forty-thousand load/unloads have been successfully completed with no damage to head or media.) The heads are also retracted completely off the media when the drive is shut down.

Reliability is significantly enhanced using a dynamic load/ unload head design. Avoided are reliability compromises that exist with typical Winchester drives, which allow heads to

Figure 5-DMA systems composite head assembly

start/stop on the media. Eliminated problems are the following:

- 1. The heads wringing onto the media

- 2. The heads landing on top of contaminants even after a purge cycle

- 3. Heads and/or media being damaged during transit, during shipment, or when the system is transported from one desk top to another

#### CONTAMINATION CONTROL

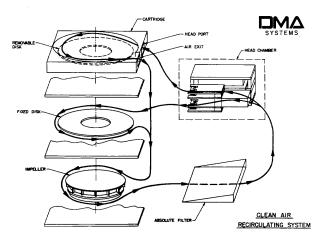

In typical office environments, contaminants such as smoke and dust can cause severe damage to the heads and media. Contamination control is therefore a very important reliability consideration. Figure 6 shows the Micro-Magnum's highcapacity closed-loop air system.

Figure 6-Closed-loop air filtration

The closed-loop air filtration system is designed so that an impeller generates sufficient system air flow to move a volume of air through the recirculating filter once per second. (The filter has a design life of five years, with no filter change required in a normal office environment.) During a purge cycle, this allows efficient removal of contaminants that may have been introduced during the cartridge insertion.

The Micro-Magnum 5/5 drive, as well as the cartridge, have self-sealing doors to preclude contaminants from entering their respective compartments. The drive has a door that seals the head port opening and keeps contaminants from entering the drive's clean air compartment. It is not necessary to take any precautionary measures to assure that the cartridge insertion door is secured and closed. The cartridge also has a door that closes the head opening and a clamp that secures the hub against the cartridge to prevent contaminants from entering the cartridge. Because the drive compartment is sealed and not accessible, the total volume of contamination that can enter the clean-air system is limited to the cartridge at the time of insertion.

#### ELECTRONIC SYSTEM

The electronic packaging of the Micro-Magnum 5/5 was no minor task, considering all the electronic functions that had to be housed in a 3.25-inch by 5.75-inch by 10.50-inch volume. Complicating the design was the necessary circuitry for the embedded servo and voice-coil positioner.

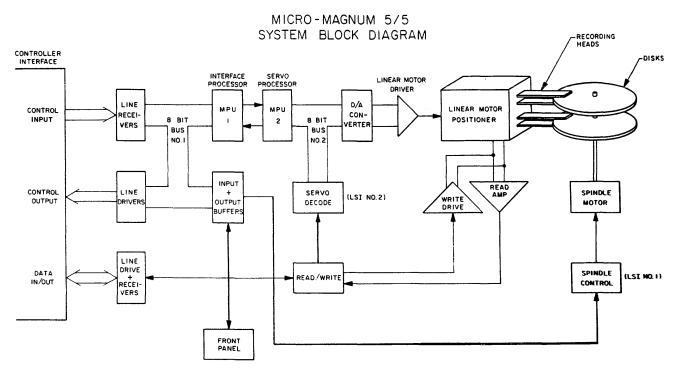

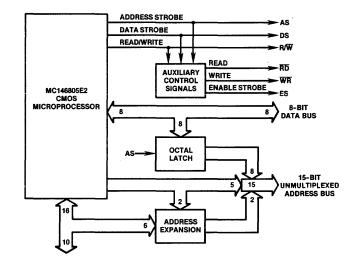

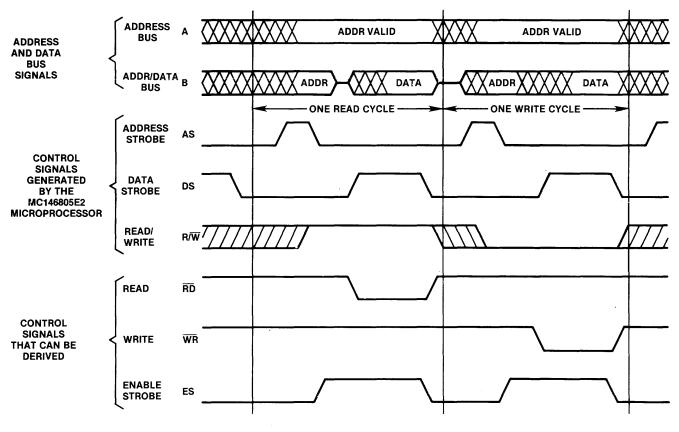

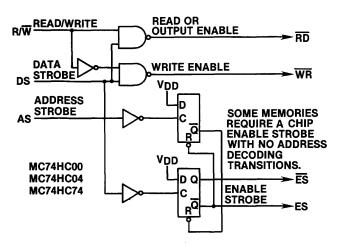

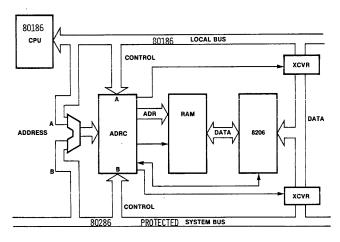

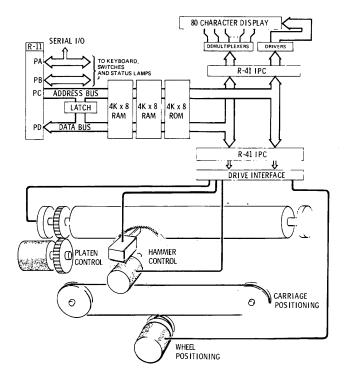

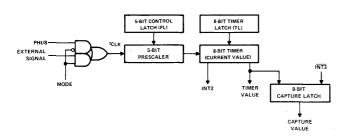

The Micro-Magnum's electronic block diagram is shown in Figure 7. A dual-microprocessor system was employed to conserve space and partition functions in order to make firmware design simpler. MPU1 is dedicated to the interface and status functions that include all controller input and output lines, front panel functions, safety checks, and fault algorithms. MPU2 receives embedded servo information from the servo decode circuit (LSI2). This serves the basic servo functions, such as track follow, seek, re-zero, load, and retracking of the heads.

To achieve the required packing density, two CMOS gate array custom IC's were developed. LSI1, a 200-gate array, is used to control spindle servo. LSI2, a 500-gate array, is used to perform decoding of digital information in the embedded servo fields.

An all-important electronic function is the control of the write operation to prevent overwriting the embedded servo fields. Overwriting the embedded servo field could result in the loss of removable and/or fixed data. The Micro-Magnum 5/5 drive, therefore, has a series of hardware and software safety checks that are performed before a write operation is allowed. Hardware functions are gated directly to the write current enable function of the head read/write chip. Also, all the following conditions must be true simultaneously before the logic circuits allow write current to be enabled:

- 1. Spindle speed must be within 0.1%.

- 2. Heads and head circuits must be in a safe condition; i.e., no shorts or opens, only one head selected, MFM data being received.

- 3. All power supplied must be in tolerance.

- 4. Power must be safe, spindle must be on, write gate signals must be enabled on the interface, and the drive must be selected.

Figure 7-System block diagram

- 5. The previous embedded servo field must be decoded properly, including a correct sector/index field and clock-shift check code.

- 6. Servo system must indicate that the head is within the "on track" limits as determined from the fine position information.

- 7. A redundant spindle-speed check circuit must indicate that the spindle is within the allowed 0.5% of normal.

- 8. The write protect switch for the disk to be written must not be activated.

#### REDUNDANCY

There is always a possibility that data errors can occur during system operation. Therefore, the disk drive must have the capability to provide data redundancy and error correction in a manner that is transparent to the user. This can be achieved by providing spare sectors and alternate tracks on the disk, as well as data formats that allow the controller or host computer to provide user-transparent correction techniques.

In the Micro-Magnum 5/5, one spare sector per track and five spare tracks per surface are provided to replace those found to be defective. This allows 4.5% media redundancy for the accommodation of defects. The defect-tolerant system is further enhanced by provisions for CRC (cyclic redundancy checking) and ECC (error-correction coding) in the data formats.

Error-correcting technology serves to verify header and data field accuracy, plus providing the capability for correction of errors. Most errors can be corrected by the combination of CRC and ECC techniques, and no data will be lost. This is accomplished by using an intelligent controller or the host computer in conjunction with the CRC and ECC formats of the Micro-Magnum system.

Defective track correction can be handled in two ways by the intelligent controller of host computer. These are:

- 1. After a seek to a defective track has been completed, the Bad Track Flag in the first sector tells the controller that an alternate track has been assigned. The data field information is then read and a new seek is issued to the assigned alternate.

- 2. Alternatively, the alternate track catalog can be read and stored by the controller upon the initial spindle-up sequence after a cartridge is installed. If a seek to a bad track occurs, the controller automatically issues a seek to the assigned alternate track. The same algorithm can be implemented by the host computer.

"Hard" errors can usually be corrected to protect data, using the error-correction techniques. If a defect cannot be error-corrected, it should be mapped into the defective sector category and spared out by the appropriate method. If the sector is spared while it is still a correctable defect, no data will be lost.

When a new defect is spared and an alternate track is required, the alternate-track catalog must be updated along with the data field information on the bad track.

#### DATA TRANSPORTABILITY/ INTERCHANGEABILITY

Use of a removable cartridge using embedded servo permits a reliable mass-storage system that is transportable and interchangeable with other similar systems. The disk cartridge has been accepted as a proposed ANSI standard for the mechanical configuration of the removable cartridge; this allows the mechanical standard to be used in all similar systems. However, no standard has yet been established for the data formats on the 5.25-inch fixed/removable Winchester drive. With the hope that a standard can be established that provides data file compatibility, the following information on the data formats for the Micro-Magnum 5/5 is presented.

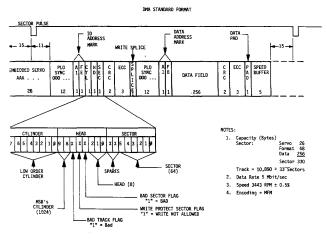

Using MFM (modified frequency modulation) encoding, the disk is organized into tracks of 10,890 bytes each of unformatted capacity. Each track is divided into 33 sectors of 330 bytes each. When formatted, each sector contains 256 bytes of data, 48 bytes of format information, and 26 bytes of embedded servo information. Figure 8 shows the organization of each sector. It is detailed below:

- Embedded Servo Field—Track and sector location information is embedded in 26 bytes.

- PLO (Phrase-Locked Oscillator) Sync—Consists of 12 bytes of 000's transmitted for data separator synchronization.

- 3. *ID and Data Address Marks*—a 1-byte address mark, made unique by omitting the clock transition between bits 4 and 5, precedes both the ID and Data Addresses. The 1-byte, FE (hex), identifies the ID Address Mark; and the 1-byte, F8 (hex), identifies the Data Address Mark.

- 4. Write Splice—This byte is provided between the ID field and Data field PLO Sync to turn on the write current if data is to be recorded in the Data field.

- 5. *Data Pad*—To guarantee data integrity, a 1-byte pad is provided between the final ECC field and the speed buffer area.

- 6. Speed Buffer—A 5-byte buffer at the end of the sector accommodates spindle-speed variations up to  $\pm 0.75\%$ .