DENNIS J. FRAILEY Editor and Program Chairman

> RUSSELL K. BROWN Conference Chairman

# **AFIPS** CONFERENCE PROCEEDINGS

# **1984** NATIONAL COMPUTER CONFERENCE

AFIPS PRESS 1899 PRESTON WHITE DRIVE RESTON, VIRGINIA 22091

July 9–12, 1984 Las Vegas, Nevada The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1984 National Computer Conference or the American Federation of Information Processing Societies, Inc.

Library of Congress Catalog Card Number 80-649583 ISSN 0095-6880 ISBN 0-88283-043-0

> AFIPS PRESS 1899 Preston White Drive Reston, Virginia 22091

© 1984 by AFIPS Press. Copying is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) reference to the AFIPS 1984 National Computer Conference Proceedings and notice of copyright are included on the first page. The title and abstract may be used without further permission in computer-based and other information service systems. Permission to republish other excerpts should be obtained from AFIPS Press.

Registered names and trademarks, etc., used in this publication, even without specific indication thereof, are not to be considered unprotected by law.

Printed in the United States of America

### Preface

RUSSELL K. BROWN 1984 NCC Chairman

The purpose of the National Computer Conference is to provide an atmosphere in which designers, suppliers, users, managers, educators, and representatives of government and society at large can meet and interact. Discussions of new technical developments, as well as national and international issues and challenges facing the information processing community, are encouraged.

This year's discussions and developments are included, for the most part, in this anniversary Volume 53 of the *Proceedings* of the National Computer Conference, completing 12 years as the world's premier computer exposition.

The decision to chair a second National Computer Conference may well be one of the more major choices one makes in even a complicated lifetime. Certainly this choice was compounded by the change in site from Houston to Las Vegas, made only 15 months before the Conference date. Perhaps a few words on that move are in order.

In Fall 1982 the NCC Committee and Board were again faced with a dilemma of great magnitude. After the move of the 1982 NCC from New York to Houston—because of space (3,200 booth units) and facility considerations—and the plan to use Houston in 1984, the plan for 1984 was also scrapped because of the same considerations. With a need to expand yet another 600 booth units, only Las Vegas and Chicago could house the show. And since Chicago is the site of NCC '85, the decision seemed obvious.

Compounding the decision, however, was the fact all NCCs of the past were presented in a major population center. Over the past four years, local and nearby interest added as much as 50,000 to the total attendance. It was obvious that a total nationalization of the NCC, with massive publicity, would be needed to turn out crowds approaching those of recent years. This week, we hope, you will be able to observe our success.

A major show in Las Vegas in July presents its own special challenges. Thirty thousand hotel rooms guarantee close-in housing for those attending. And certainly no one can fault Las Vegas' ability to entertain its guests. In addition, you will see *no* shortcuts or shortcomings in the presentation of this NCC.

What you will see is a display of 650 companies filling 3,800 booth units for a new NCC record. You will be exposed to a high-quality program, high-quality Professional Development Seminars, a major keynote address, a special Pioneer Day program, and numerous other attractions that we feel will make this a noteworthy week. It is the intention of the CSC to give attending registrants all the positive values of moving to a new city and to make any negatives as invisible as possible.

An example of this is the largest busing expenditure in Las Vegas history for the various round trips between hotels and the Conference during the warm summer days.

If I may return to our program, I may be able to elicit in you a feeling of satisfaction to match the pride I feel. The program is made permanent by the archival record of the *Proceedings*. Here we capture for posterity the most current reports on recent achievements and new applications, on advances at the frontiers of computer science and technology.

Dr. Dennis Frailey of the Texas Instruments corporation was buffeted in midpreparation of this program and these *Proceedings* by the move. Through all the personnel shuffling and turmoil, he managed to steer a straight course toward a superior presentation.

Dennis recognized, early on, that the registrant has only three days, on the average, to assimilate all aspects of an NCC. His first decision was to direct that with a superior Professional Development Program and 12 football fields of exhibits—the program as defined in the past be intensely screened for shortcomings. His Committee introduced a much finer mesh in their screen than has ever been used before. The number of papers and sessions are down slightly from what you have seen in previous NCCs, but we are confident that their value to you will be high.

Volunteers, for a conference of this magnitude, number in the hundreds. They are members of the NCC Sponsoring Societies and the other AFIPS Constituent Societies. To these groups and their participating members I would like to give my heartiest thanks, particularly in view of the truncated schedules on which we were all operating.

To the Las Vegas Convention Bureau, which greatly eased our move into a new city, my thanks for the myriad arrangements and assistance you provided.

To the NCC Board and Committee, who well knew the danger to NCC '84 if plans were not well organized, my thanks for your confidence and support.

To the AFIPS Headquarters Staff and all the members of our CSC, thank you for your dedication, time, and effort you have contributed to an ongoing tradition of excellence.

To my wife, who in 1981 asked, "Why?" in 1982 asked, "How can I help?" and in 1983 said, "Let me be a part of this," you know my thoughts.

And finally, to ten of the previous NCC Chairmen, thank you for your assistance, guidance, and inventiveness. Much of what you created is embodied here.

### Introduction

DENNIS J. FRAILEY 1984 NCC Program Chairman

1984! Orwell's year is here! Have events happened as Orwell predicted in 1984? Have computers become the tool of those who would suppress our individual freedoms? These were the obvious questions when the program committee first sat down in fall 1982 to develop a theme for the 1984 NCC. Each of us reread Orwell's classic. We discussed ideas for a conference theme that would truly represent the current state of computing. And we were struck by a simple fact: computers are being used today in many ways that were totally unexpected. The choreographer whose computer provides a breakthrough in explaining his ideas to dancers; the businessman whose spread sheet program turned his company around financially; the physically handicapped whose voice-activated personal computers give them control over their environment—these and others whose uses of computers were only recently the stuff of science fiction serve to point out what is really important and unique about computing today—creative use of computers by individuals.

The availability of computers to individuals has evolved from timeshared mainframe systems to minicomputers to personal computers. Each step has provided a significant increase in availability and power through dramatic cost reduction. Data communication technology has kept pace in recent years, enabling a truly worldwide system of information exchange to be developed. What is important about this technology, and indeed what is anti-Orwellian about it, is that control is migrating away from the center—toward the individual. This is what's different about computers today. This is what promises to continue the computer revolution. And this creative use by individuals—in the office, the factory, and the home—is the theme that ties together the diverse topics addressed by the NCC program.

The program consists of over 90 sessions, presented over a four-day period. Ten topic areas or tracks represent the committee's way of dividing a broad set of subjects into manageable components. In addition to a wide range of sessions on such topics as hardware and architecture, software, management, automation of office and factory, databases, data communications, personal computers and societal issues, we've augmented the program in the areas of artificial intelligence and computer graphics and entertainment—areas where those attending recent NCCs have shown particularly high interest. We've also oriented the focus toward the questions we believe are uppermost in the minds of NCC attendees: "What's new?" and "How will it affect me?"

Although this *Proceedings* volume contains more than 80 papers, they represent less than a third of the total NCC program. Panel discussions occupy more than half of the program, and some of the sessions include presentations on topics too recent to meet the publication deadline for the *Proceedings*, such as the very latest microprocessors and networks. The *Proceedings* are organized by track, and each section begins with an overview of the whole track—panel sessions as well as papers. For those attending, this serves as a guide to the program as a whole. For those unable to attend, it serves to give the flavor of the program and helps to put the papers into perspective. Because of the frequent overlap of topics, readers are likely to find sessions and papers of interest in several of the tracks.

The 1984 NCC program is the combined effort of almost 1,000 people, most of whom are unpaid volunteers. This includes 12 program committee members; more than 90 session organizers and chairs; almost 300 presenters, panelists, and authors of technical papers; and nearly 500 referees who helped us select the technical papers. (There were also several hundred people whose high-quality papers and session proposals could not be accommodated.) In addition, recognition must go to at least a dozen AFIPS staff members; the program committee staff, headed by Jean Presnell; and the spouses and employers of all of the above, whose forbearance and assistance made their contributions possible. All of us sincerely hope that each person attending NCC will find the program stimulating, helpful, and educational.

| Preface                                                                                                                                                             | iii |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction<br>Dennis J. Frailey                                                                                                                                   | v   |

| THE AUTOMATED OFFICE<br>Michael Alsup                                                                                                                               |     |

| Implementing a large office automation system—how to make it work<br>Jack Golden and Stuart Bell                                                                    | 3   |

| COMPUTER HARDWARE AND ARCHITECTURES<br>Fayé Briggs                                                                                                                  |     |

| A multiaccess bus arbitration scheme for VLSI-densed distributed systems<br>Jie-Yong Juang and Benjamin W. Wah                                                      | 13  |

| DMERT—An operating system for telecommunications systems<br>S. F. Ho, C. J. Richardson, and W. C. Schwartz                                                          | 23  |

| Global concurrency control mechanisms for a local network consisting of systems without concurrency control                                                         |     |

| capability                                                                                                                                                          | 31  |

| Synapse tightly coupled multiprocessors: A new approach to solve old problems                                                                                       | 41  |

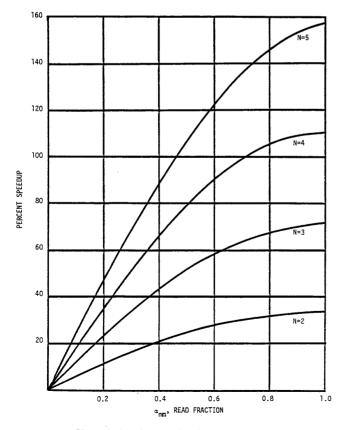

| Throughput of multiprocessors with replicated shared memories                                                                                                       | 51  |

| The DCS—A new approach to multisystem data-sharing<br>Akira Sekino, Keizo Moritani, Teruaki Masai, Toshiaki Tasaki, and Kazuo Goto                                  | 59  |

| Reduced-instruction set multi-microcomputer system<br>Lewis Foti, David English, Richard P. Hopkins, David J. Kinniment, Philip C. Treleaven, and<br>Wang Long Wang | 69  |

| System considerations in the NS32032 design<br>Richard Mateosian                                                                                                    | 77  |

| An inside look at the Z80,000 CPU: Zilog's new 32-bit microprocessor<br>Anil Patel                                                                                  | 83  |

| An interleaved array-processing architecture<br>J. R. Jump, J. D. Wise, and D. T. Harper III                                                                        | 93  |

| Compatible software and hardware implementations permitted by IEEE standard for binary floating-point arithmetic                                                    | 101 |

| Goals and tradeoffs in the design of the MC68881 floating point coprocessor                                                                                         | 107 |

| An extended-precision operand computer for integer factoring<br>Jeffrey W. Smith and Samuel S. Wagstaff, Jr.                                                        | 115 |

| New microprocessor-based computer architectures<br>Omri Serlin                                                                                                      | 123 |

| How smart the computer: Status and future on building its brain<br>David J. Elliott                                                                                 | 131 |

| IDAS—An integrated design automation system<br>Stephen Y. H. Su                                                                                                     | 143 |

### CONTENTS

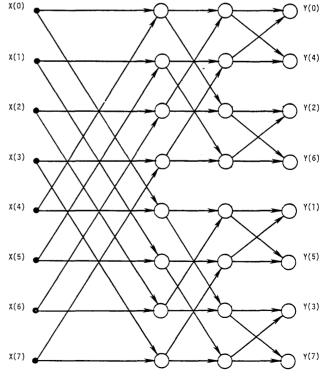

| A versatile VLSI fast Fourier transform processor<br>Kuang-cheng Ting and Chuan-lin Wu                                                 | 151 |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Design diversity: An approach to fault tolerance of design faults                                                                      | 163 |

| Tradeoffs in system level diagnosis of multiprocessor systems         A. Kavianpour and A. D. Friedman                                 | 173 |

| SOFTWARE<br>A. Winsor Brown                                                                                                            |     |

| Maintenance as a function of design<br>James R. McKee                                                                                  | 187 |

| Maintaining user satisfaction with performance of an online system                                                                     | 195 |

| Redocumentation: Addressing the maintenance legacy                                                                                     | 203 |

| System information database: An automated maintenance aidLinda Brice and John Connell                                                  | 209 |

| COBOL-80: The new structured language<br>Jerome Garfunkel                                                                              | 217 |

| Is COBOL-8X cost effective?                                                                                                            | 223 |

| Technology transfer in the maintenance environment<br>Florence J. Bell                                                                 | 229 |

| Two perceptions of software maintenance performed by an on-site contractor                                                             | 235 |

| Prolonging the life of softwareJohn Connell and Linda Brice                                                                            | 243 |

| Software maintenance in fourth-generation language environments<br>Paul C. Tinnirello                                                  | 251 |

| Specification and implementations of interactive information systems                                                                   | 259 |

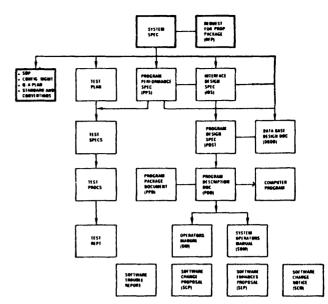

| Software management issues for new systems designs<br>Robert E. Loesh, Donald J. Reifer, and Steven M. Jacobs                          | 267 |

| Results of modern software engineering principles applied to small and large projects<br>Peter R. H. McConnell and Wolfgang B. Strigel | 273 |

| A portable Modula-2 operating system: SAM2S                                                                                            | 283 |

| Giving away the data processing store, or Does the data processing department as we know it today have a future?                       | 293 |

| Lois Zells<br>Are methodologies and system design techniques independent of one another?                                               | 303 |

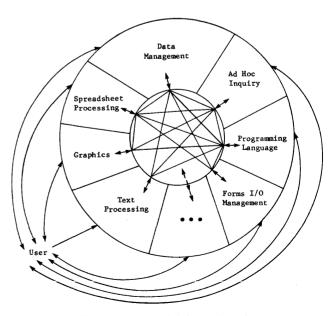

| Denis A. Connor Aspects of integrated software.                                                                                        | 311 |

| Clyde W. Holsapple and Andrew B. Whinston                                                                                              | 311 |

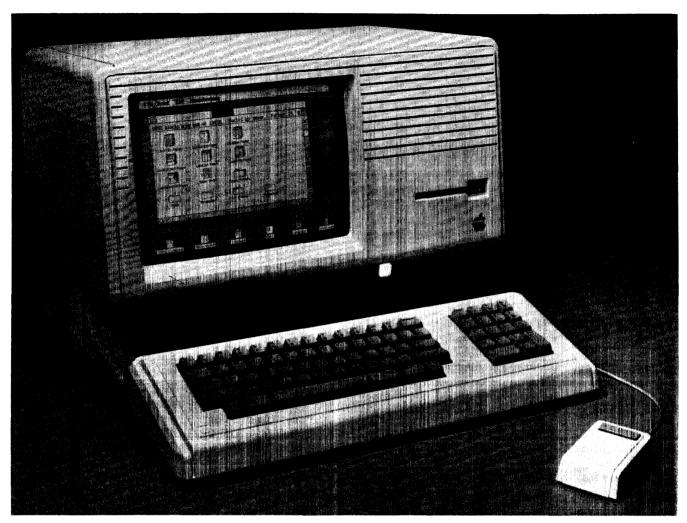

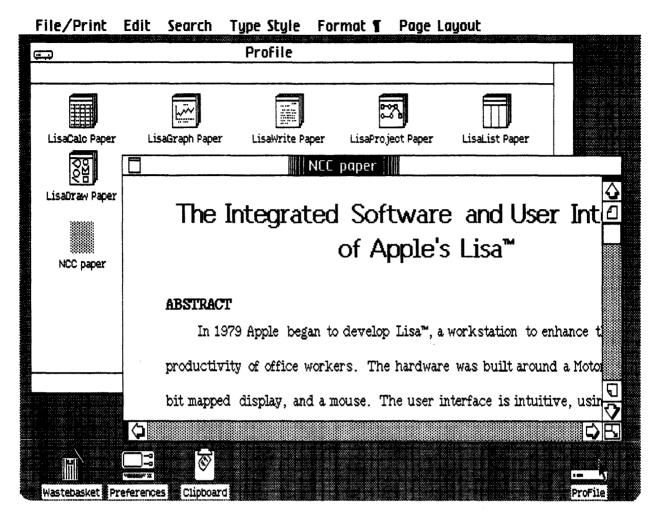

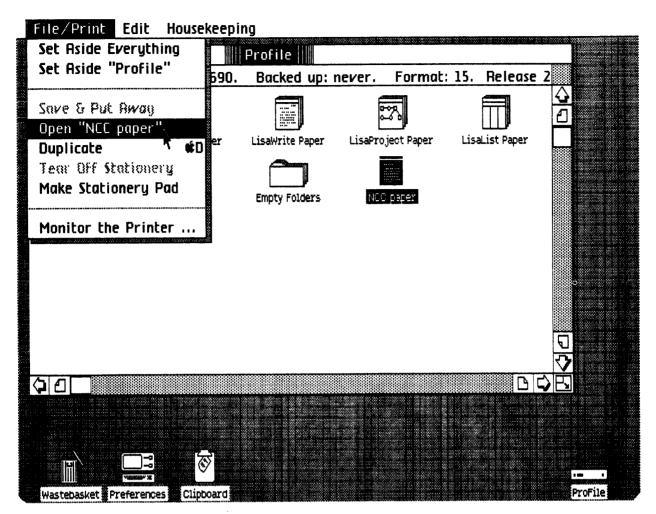

| The integrated software and user interface of Apple's Lisa<br>Edward W. Birss                                                          | 319 |

| FlowGuide—A programmer's work station<br>Phil J. Grouse                                                                                | 329 |

| Information resource planning and management methodologies                                                 | 337 |

|------------------------------------------------------------------------------------------------------------|-----|

| IRP/IRM methodologies<br>Michael R. Wood                                                                   | 343 |

| Simulation as an aid to software transferability<br>Aaron H. Konstam and Ronald G. Reinhard                | 349 |

| Software manufacturing techniques and maintenance                                                          | 357 |

| A prototyping environment for real-time graphics<br>Nola Donato, Robert Rocchetti, and Janet Tom           | 367 |

| A publisher's view of writing successful software<br>Gary Swanson                                          | 375 |

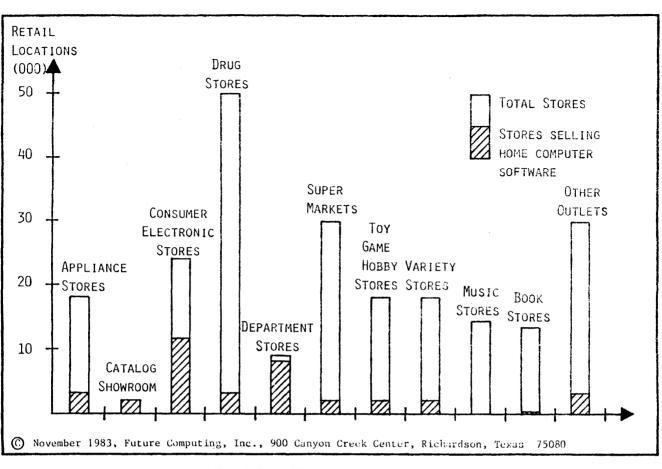

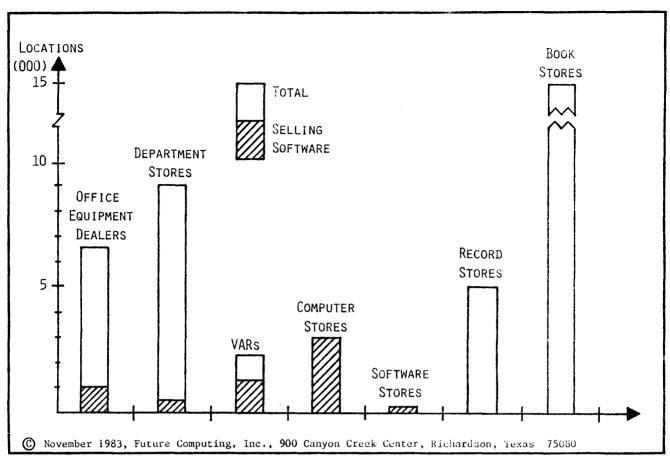

| Versatile packaging: Software for all retail environments<br>Elwin E. Lages                                | 381 |

| Commercial and military software documentation: Different steps to a common goal                           | 389 |

| One person's perception of military documentation<br>Don Mather                                            | 395 |

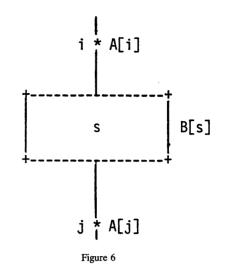

| Simple dynamic assertions for interactive program validation                                               | 405 |

| A tool-based approach for software testing and validation<br>J. C. Huang, Peter Valdes, and Raymond T. Yeh | 411 |

| Guidance for test selection based on the cost of errors<br>David A. Gustafson                              | 423 |

| COMPUTER GRAPHICS—COMING OF AGE<br>Alan Paller                                                             |     |

| PERSONAL COMPUTERS<br>Jean Yates                                                                           |     |

| Will notebook computers revolutionize computer usage?<br>David H. Ahl                                      | 435 |

| EDUCATIONAL AND SOCIETAL ISSUES<br>Alfred Riccomi                                                          |     |

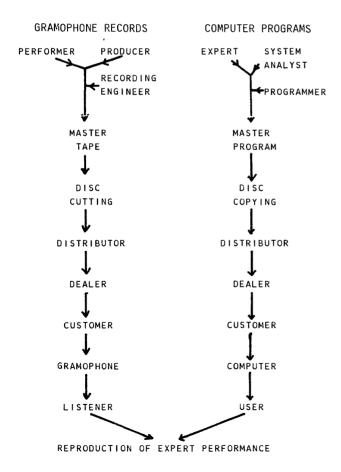

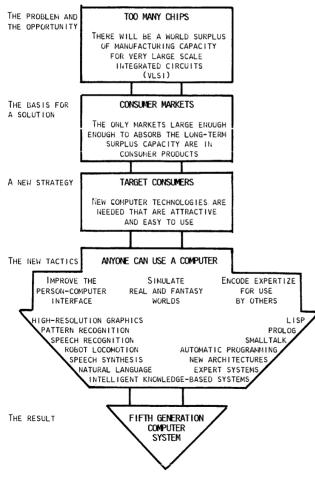

| Fifth-generation computing as the next stage of a new medium<br>Mildred L. G. Shaw and Brian R. Gaines     | 445 |

| A framework for the fifth generation<br>Brian R. Gaines                                                    | 453 |

| Computers and the future of human creativity<br>Michael Conrad and M. A. Rahimi                            | 461 |

| A national computer policy: Forging the final synergy of computers and society<br>Ben G. Matley            | 469 |

| INFORMATION PROCESSING MANAGEMENT<br>Eugene Smith                                                          |     |

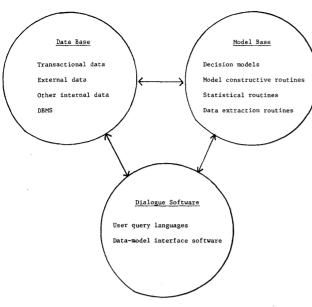

| Decision support in a distributed environment<br>Daniel T. Lee                                             | 477 |

| Issues in the design of expert systems for management                                                      | 489 |

| An investigation of task team structure and its impact on productivity<br>Kathy Brittain White                                                    | 497 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Incentive compensation for information systems departments                                                                                        | 505 |

| Gaining competitive advantage, or how to succeed as the vice-president of information systems<br>M. Victor Janulaitis                             | 513 |

| DATABASE MANAGEMENT<br>Darrell Ward                                                                                                               |     |

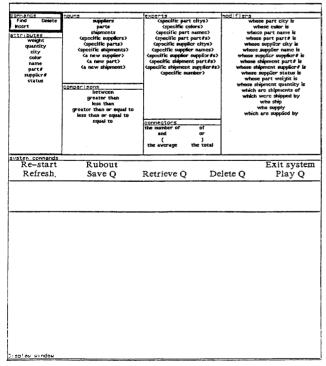

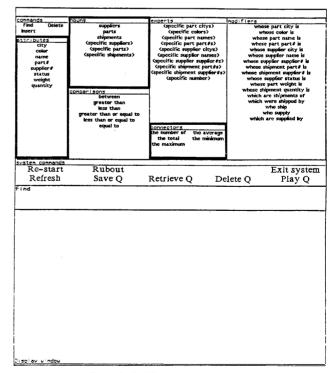

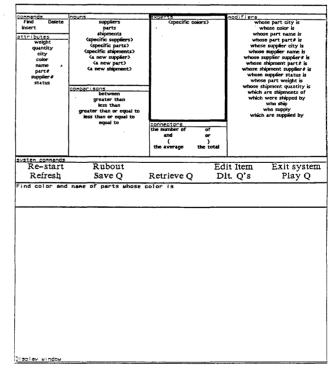

| An interface for novice and infrequent database management system users<br>James A. Larson and Jennifer B. Wallick                                | 523 |

| REQUEST: A testbed relational database management system for instructional and research purposes<br>Bogdan Czejdo and Marek Rusinkiewicz          | 531 |

| Sibyl: A relational database system with remote-access capabilities<br>Manfred Ruschitzka, Andrew Choi, and John L. Clevenger                     | 537 |

| Functions of the database workbench                                                                                                               | 547 |

| Fourth-generation languages (4GLs) and personal computers                                                                                         | 555 |

| SALVO—A fourth-generation language for personal computers                                                                                         | 561 |

| Uniform organization of inverted files                                                                                                            | 567 |

| A generalized method for maintaining views                                                                                                        | 587 |

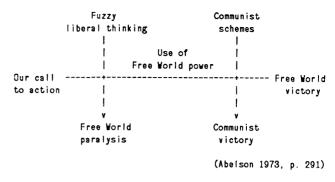

| The representation of debate as a basis for information storage and retrieval<br>David Lowe                                                       | 595 |

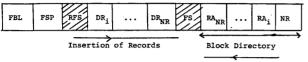

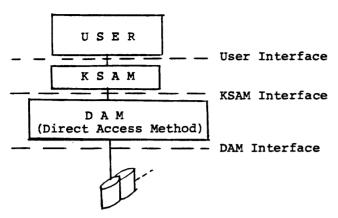

| KSAM: a B <sup>+</sup> -tree-based keyed sequential-access method                                                                                 | 605 |

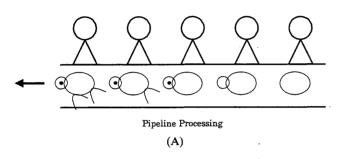

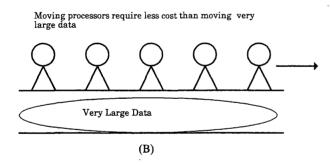

| A database machine based on the data distribution approach                                                                                        | 613 |

| ARTIFICIAL INTELLIGENCE<br>James R. Miller                                                                                                        |     |

| Menu-based natural language understanding                                                                                                         | 629 |

| An analysis of scripts generated in writing between users and computer consultants                                                                | 637 |

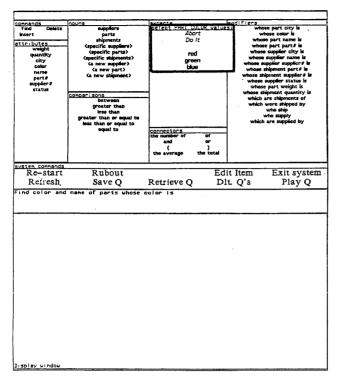

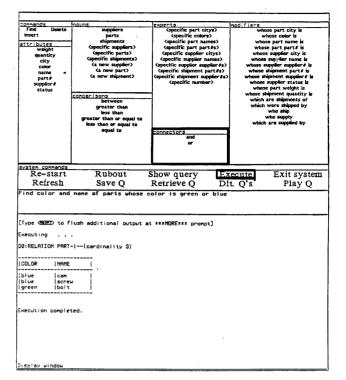

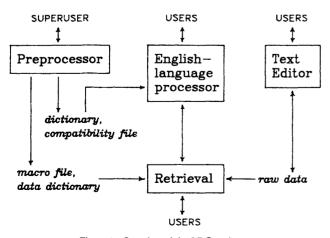

| Transportable English-language processing for office environments<br>Bruce W. Ballard, John C. Lusth, and Nancy L. Tinkham                        | 643 |

| Really arguing with your computer in natural language                                                                                             | 651 |

| Introducing VIPS: A voice-interactive processing system for document management                                                                   | 661 |

| An expert system for drafting legal documents<br>James Sprowl, Periyasamy Balasubramanian, Taizoon Chinwalla, Martha Evens, and Henriette Klawans | 667 |

|                                                                                                                                                   |     |

### COMPUTER COMMUNICATIONS Neal Laurance

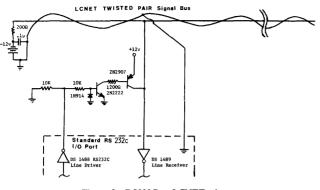

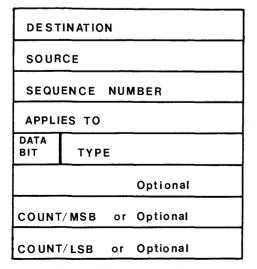

| LCNET: Ethernet concepts + ubiquitous RS232C ports = Low Cost NETwork<br>Jay B. Jordan and Victor P. Holmes                            | 677 |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

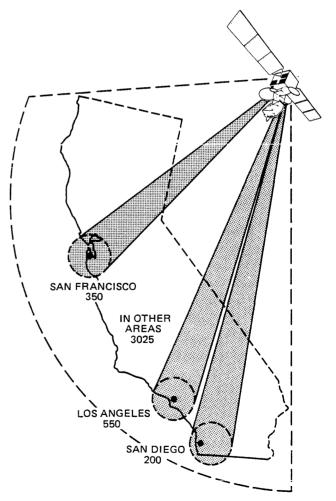

| Direct work station to remote computer communications via satellite                                                                    | 685 |

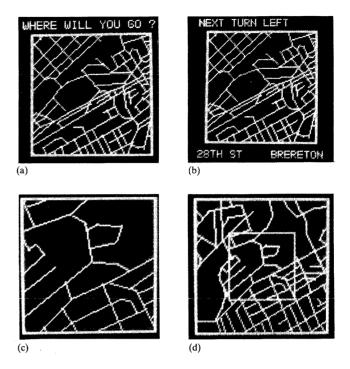

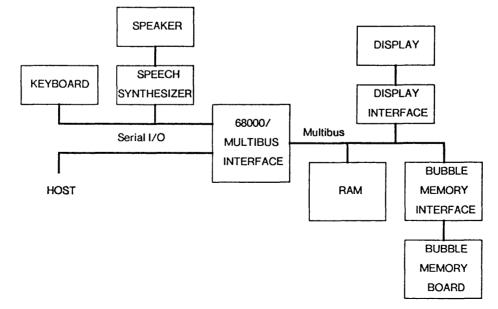

| CARGuide—On-board computer for automobile route guidance<br>M. Sugie, O. Menzilcioglu, and H. T. Kung                                  | 695 |

| Telecommunications and business strategy: The basic variables for design<br>Eric K. Clemons, Peter G. W. Keen, and Steven O. Kimbrough | 707 |

### The automated office

Michael Alsup, Track Chair

The Office Automation track at this year's NCC includes 12 sessions rich with ideas and information. The contributions that office systems can make to productivity and managerial effectiveness are reviewed from functional, technical, strategic, and end-user perspectives; and the depth and breadth of office automation is presented by a number of industry experts.

The current state of the art in office automation is outlined in the first session, entitled "Office Automation: State of the Art." Noted consultants summarize current trends in the marketplace and analyze vendor offerings.

The key to the implementation of successful office systems is to identify user requirements and select equipment that satisfies those requirements. Two sessions outline approaches that have been successful in the definition of user requirements. In "Analyzing Managers'/Professionals' needs for OA," a consultant will discuss how to evaluate user requirements for office systems, and representatives from two organizations that have recently evaluated these requirements and implemented advanced office systems will share their experiences. In a second session, "Office Automation in Large Organizations," two organizations that have implemented very large and integrated office systems summarize their experiences and outline their successes and failures. Organizations that are considering their requirements for office automation have a valuable opportunity in these sessions to learn from others who have pioneered in this area.

As microcomputers and word processors have become more powerful, additional attention is being focused on design and functionality in office systems. Vendors are integrating the delivery of a number of functions and application systems into a single work station with powerful communications capabilities and a standard user interface to all applications. Four sessions explore the changing role of work stations in the office. "Design and Functionality in Office Systems" examines how the user aspects of office systems are evolving. A consultant summarizes the trends and likely market direction and evaluates several well-known products. A second session, "Management Work Stations and Integrated Information Systems," examines three new work stations that include powerful capabilities for data, voice, and video; and it evaluates the issues involved in the successful implementation of these systems. "The Micro-Mainframe Connection" explores benefits and pitfalls in the connection of microcomputers and mainframe computers from software, communications, and end-user points of view. Finally, the role and potential of voice in office systems will be explored in "Voice Technology in the Office." These sessions are especially useful to organizations considering the role and fast-evolving capabilities of work stations in their organizations.

The strategic and managerial implications of office automation are explored in two sessions. "Strategic Systems Planning: Art, Science, or Nonsense?" explores whether it is possible to develop a strategic plan for office automation in the face of rapid and profound technological change. "Office Automation Selection Criteria: A Q&A Session" explores and defines appropriate selection criteria for office automation systems from a management point of view.

Communications networks are becoming the nervous systems of large organizations. Three office automation sessions examine the impact of developments in communication technology for the office environment. The advantages and disadvantages of three different approaches for integrating office systems equipment are presented in "Integration Alternatives and Strategies." Representatives of a well-known mainframe vendor, a PBX vendor, and a local area network vendor outline the short- and longer-term advantages of their systems architectures in the office.

One of the principal advantages of a local area network is the attachment of devices whose capabilities are shared among the work stations on the network. These devices include intelligent copiers, electronic file cabinets, communications gateways, and mainframe computers. "Shared Network Resources" summarizes the advantages and capabilities of these resources, and two leading vendors summarize their offerings.

Electronic mail is an important and practical way to improve productivity and reduce costs. It can be broadly defined as the transmission of messages by electronic means. "Electronic Mail: Current Developments" summarizes the alternatives available in electronic mail, and three vendors with leading-edge products summarize their offerings.

## Implementing a large office automation system—how to make it work

by JACK GOLDEN and STUART BELL The MITRE Corporation McLean, Virginia

### ABSTRACT

This paper discusses the implementation of a large office automation system to be used by nondata processing as well as data processing staff, i.e., the knowledge worker. At its completion the system will encompass more than 1,000 terminals (one terminal per office). The paper covers the nature of the basic system, IBM's Professional Office System (PROFS), what it does, how it functions, the extent of use, and how to encourage potential users to use it. The paper reviews training procedures from one-on-one to higher ratios and the reasoning behind them, and goes over in detail the nature of the "innovation" curve. Also reviewed are the computer performance and the Local Area Network (broadband with Sytek bus interface units). We currently serve more than 500 users with around 300 terminals already distributed.

### INTRODUCTION

We discuss here the implementation of a large office automation (OA) system and how we made it work. By and large, we're talking about one terminal per office, or a total of 1,000 terminals, covering nine buildings within a two-mile radius.

Our discussion will go over the nature of the corporation, a nonprofit organization that does business primarily with the federal government. We will review our office automation architecture and design goals, our implementation strategy in terms of our basic system, the pilot group used in developing the system, and how we controlled additions to the group.

And most importantly, we'll cover what actually happened in terms of acceptance of OA concepts by the pilot group, communications problems, and wide-implementation problems.

#### Corporation Background

The MITRE Corporation is a not-for-profit systems engineering company chartered in the public interest. MITRE was established in 1958 to assist the Air Force, but today assists most federal civilian agencies, as well as other DoD agencies in the areas of command and control systems, information systems, as well as the energy/environmental area. The major product of the corporation is information, utilizing the media of reports, specifications, memos, briefings, etc. paper in general.

We cover here office automation activities supporting the 1,500 or so staff at the Washington center. We will allude to other systems used throughout the rest of the corporation and how we interface with them. Additionally, we wish to stress the implementation problems and solutions, not the specific hardware or software components of the system.

### OA at MITRE

MITRE entered the office automation area in 1972 when we developed a centralized word processing support facility with an administration support center. During this period we had two shifts (eight operators each shift, working six days per week at its high point). In 1976 we migrated to the decentralized word processing concept (approximately 40 word processing terminals off cluster controllers). From 1976 until 1980, word processing and computer useage was growing at a rapid rate.

In 1981, the Corporate management decided it was time to develop an integrated plan for the spread of information services to our professionals, secretaries, and administrative staff. An internal study group, consisting of four senior managers, was chartered to review the computer and telecommunication support needs of the company. The committee's work was completed in the fall of 1981 with corporate management's acceptance of a "target system," a four-phase implementation plan, and authorization and funding for the plan's first two phases.

The system was designed to account for the heterogeneous user population in terms of data processing skills, typing skills, the nature of work being performed, and the level of each person in the company. The design encompassed hundreds of terminals and tens of computers with multiple vendors making up the system.

The target system networked computer resources, allowing the users to share data, programs, and special-purpose peripherals. We also strongly wanted to have a local area network that would support video in terms of both security (e.g., badge readers from remote buildings) and instructional TV (e.g., the lunch-time seminars).

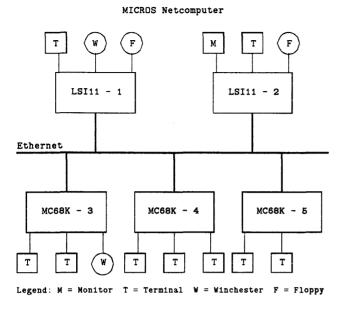

Based on the 1981 recommendations of the committee, our 1983 architecture evolved to a fully connected system. We are basically utilizing a Sytek LocalNet 20 bus interface unit in our broadband data distribution system. We now have connectivity and information transfer among all of our major segments, internally in the Washington Center and with the outside world.

#### Implementing a Large-Scale OA System

We would now like to discuss how our implementation strategy obtained a workable office automation system.

There are four major components that make the system work:

- the computer system

- the local area network

- user acceptance

- applications software

Our implementation strategy was as follows. In late 1981 we evaluated the available software options in the office automation area. Our primary concern, beyond the normal OA functions, was that the software reside on our IBM mainframe. The Professional Office System (PROFS) was chosen because of cost, maturity of the product, breadth of applications, and relative ease of use. 1982 was spent debugging, customizing, testing the product, and implementing a prototype system. By mid-1983 we were ready for corporate-wide implementation.

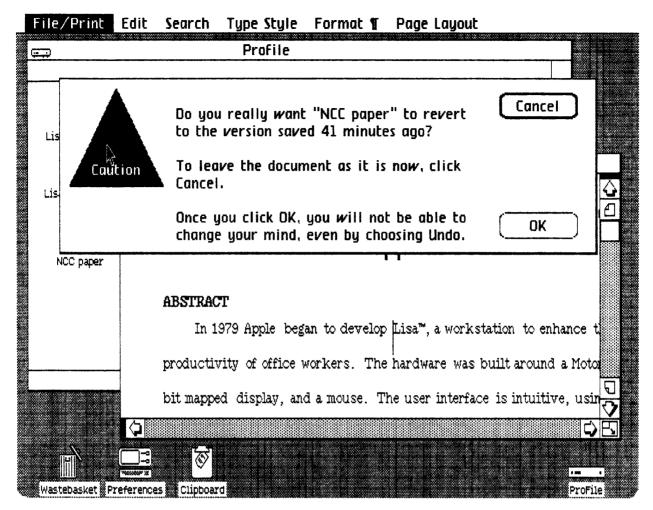

PROFS is a menu-driven system; that is, the capabilities are

accessed through menus (or lists). There are three main menus and numerous submenus. The display terminal's Program Function Keys (PF Keys) are used to move between menus and to invoke specific functions. The system was customized over time to offer the various user segments different levels of information. These included (what we deemed important) management needs, and staff needs.

As was stated, the PROFs architecture allows for the ready access of information not provided by the basic software. The basic software offers general OA tools such as electronic mail, calendar functions, electronic filing/retrieving, reminder functions, and document preparation.

From March to August 1983 we undertook several studies. These included a system evaluation, communication options between buildings (statistical multiplexing, microwave option, etc.), a definition of our FY84 configuration, a definition of an adequate support structure, a finalized training mechanism, and, of course, a study of the role of the personal computer in our environment.

Starting in August 1983 and extending to August 1984, we have been installing an additional 180 terminals (which translates to an additional 270 or so users to the system). This is Phase 1 of across-the-company implementation. FY85 will be an additional 180 terminals, and so on until there will be one terminal per office.

#### The Local Area Network

For our local area network we used a broadband CATV system utilizing Sytek LocalNet 20 system. LocalNet is a packet-switched local area data communications network providing communication functions and standard broadband CATV coaxial cables. The properties of a broadband system permit LocalNet to construct independent subnetworksterminal channels. Each of those subnetworks provides data communications for hundreds of users. In the summer of 1982, we initiated a limited test of the system within one building to ensure functional compatibility of all components. In 1983 we extended the network to cover our five remote buildings, all within a two-mile radius. Our problems arose when we could not physically connect the buildings with a cable. We experimented with a host of alternatives; these included telephone lines at 9,600 bits per second, microwave transmission at a very high effective data rate, laser transmission, and the use of statistical multiplexors. We are currently utilizing all of these for one reason or another.

The LocalNet medium provides the high band with 300 to 400 MHZ proven reliability and multidrop capability required for growing data communications requirements. Analog video or voice applications can share the same cable using dedicated frequency channels. A single channel can accommodate approximately 100 simultaneous virtual circuits.

### Getting The System "Used"

We would now like to discuss how one goes about generating productive use of the system. Nothing is more important than having senior management commitment; however, 100% commitment is really not needed to have successful implementation. Management should not be negative. Once this commitment is in place, the road to success can then be followed.

Aside from the typical notes and messages on any office automation system, it is important to have tools on the system that would be helpful to the knowledge worker or the professional. We chose to have project financial information as the first application on the system for management use. This financial planning and analysis tool proved to be most useful inasmuch as the system was used immediately (in other words, users took the time to become familiar with the system because they were getting something useful out of it). People will not take the time to learn a system that does not have useful information: if all they have are the note and message functions, its utility is small, (although these functions are important and some OA systems are designed just around notes).

We suggest that the system population be enriched as soon as possible. We added approximately 15 terminals per month (25 users per month), but doubling this number would have been more productive. Additionally, the service divisions or entities of the corporation should be made part of the system as soon as possible. This allows the support people to become productive almost instantaneously. The message here is to not be discouraged by the lack of enthusiasm among the users. At the beginning, having a sparse population is like having a telephone with no one to call.

In an early, sparse system, the financial systems and other individual productivity aids predominate. As the system becomes richer and the conductivity fuller, mail and documents become the most popular features.

We would now like to discuss the implications of having a "rich" vs. "sparse" network in terms of individual use of the system. From observation, the typical nondata processing user can be thought of as going through five phases. We call the first phase tinkering or learning. Depending on the number of people on the system, this can last anywhere from one to six months, with the average around three months. During this time the unsophisticated user (not data processing oriented) learns how to use the machine, not that it actually takes three months to learn, but rather that the user is "too busy" to read the manual or ask questions. After the initial tinkering stage, there is a two- to three-month getting acquainted period. The user starts to generate mail, type a few documents, and use some of the applications on the system. No (real) productivity is gained during this time, just an awareness of what can be done. We call the next phase the suggestions phase. During this phase the user realizes the potential of the computer and becomes an instant expert on how to do things better. Suggestions come pouring in on what to put on the system and how to make it more productive. Overlapping this suggestion phase is the *commitment* phase. At this point in the user profile, he will not move to another office when office moving time comes around unless there is a terminal in his office (similar to a telephone). The next phase is the most important, the synergistic phase. It is at this time that individual users help and compliment one another on the system, and we finally see corporate productivity increases rather than just individual productivity gains. From

beginning to end this cycle can take anywhere from 6 to 18 months depending on the background of the individuals involved. This is why we previously stated, "Don't get discouraged during the early life of the system or when suggestions come pouring in."

Initially, we spent about three months (one person) in developing the training manual and procedures. For the first 50 users, we trained on a one-to-one basis; for the next 100 users, we trained on a one-to-three ratio, with one-to-seven for the remainder of the early population, (the first 250 users). Our philosophy was that we should build a strong foundation during the first 50 users, so that they could be called upon to answer questions from their coworkers (the next generation of users). This philosophy works out very well.

Concurrent with training, we established a user services group (three staff); one telephone number was established by which all questions could be handled. We also instituted monthly user meetings where innovations and particular questions could be discussed and guest lecturers presented. We are now starting to use computer-aided instruction.

Although we feel that our initial training mode worked out well, we recommend a slightly different approach. More effort should be spent in the development of training material, and several skill-level/position-level materials should definitely be prepared. A training ratio of one-to-five with a largescreen terminal projection, followed by a 30-minute one-toone follow-up is recommended.

Once the network is enriched, users tend to help each other; so, the task of training should actually decrease as users are added to the system. Although there are more individuals to train, there are more training aides around.

We keep an accurate record of *all* questions and comments that come into our user services group as an example of the problems and questions that arise. The format is as follows:

- General PROFS (five categories)

- General "other" software

- Hardware (when system is down)

- Administrative (training requests (other than PROFS); documentation)

- software

- Word Processing (Wang or NBI questions)

- UNIX

- Cable Plant

- Personal Computer

- Miscellaneous

- Consulting (more than 15 minutes on the phone)

Once a significant number of users have been added to the network, system reliability is a major issue. Therefore, it is prudent to have accurate records of why the system, or any component, is down and what the "fix" or resolution is. This is important, since you will often hear, "the system is always down," when actually it may have been down for only five minutes during a given week.

In regard to our local area network (LAN), we found that there is plenty to choose from. But remember, a LAN may not be for you. In our installation the cost for the backbone cable ran from \$5 to \$10 per liner foot, depending on the building layout size (e.g., needing amplifiers). This averages \$300 to \$1,000 per drop or tap, depending on the building configuration. For comparison, point-to-point averages \$500 per terminal.

One important item is new skills; the type of person needed to run this type of activity is usually not within the organization. And, of course, the LAN facilitates office moves.

One is always asked, What are your productivity gains? How many people have you let go?, etc. The answer to the first is, "don't know and probably won't," and the answer to the second is, "none...but you can be sure, things get done faster, more efficient, and with better results." We usually don't get rid of people, but redefine their roles.

We make *no* attempt to get a productivity figure, but we do make an attempt to evaluate the system. This is done in several ways): first, we get user feedback on a daily basis; then meetings and our PROFS Answer Line (PAL) provide additional feedback. We also investigate the usefulness of the system by means of questionnaires, telephone interviews, and usage data.

Most importantly, we get feedback on how the system has changed the way we do business, both as individuals and as a group. As individuals, we see uses other than OA functions being used, e.g., spreadsheet. As a group, we see reports going electronically to our sponsors, remote sites sending their documents for review back to the main office, and more dialog among and between groups. We see the service organizations modernizing in large ways.

#### Health Effects

When the potential health effects of using VDTs came up, we performed a literature review in the area of terminal effect on operator fatigue. The study covered optical, musculoskeletal, morale, and radiation issues. The medical literature revealed little risk in all areas. We realize that the specific area of radiation is not satisfactorily documented and is still an area of volatile discussion. Additionally, VDT use and eye strain are still being investigated.

### The Computer

In this section, we describe the facilities we employ to deliver the office automation service to our customers.

The overriding goal in an office automation environment is excellent response. The most important aspect of excellent response is choosing the correct definition of excellent. At the MITRE Washington Computer Center (MWCC), we aim for a general consensus that our response is excellent. Customers are encouraged to send notes or mail to the computing center management whenever they see a response problem. Regular presentations are made to the community describing our response measurement techniques, and as a consulting company, we have an internal interest in both the techniques and the results.

Office automation makes everyone neighbors and removes (at least in its initial phases) the traditional management lines of filtering. Everyone becomes a performance expert, everyone wants a hand in running the computing center; and everyone has instant access to everyone else. Thus, the systems team must be selected and trained to be customer-oriented; and although we have a user services section, each member of the systems team and operations staff must always be aware, and willing, to work with any user or customer who is having a problem with the delivered system.

Our present configuration is an IBM 4341 with 16 million characters of main storage. Please note that this is a historical accident and not an endorsement of either IBM or the 4341 product line. While this device serves our needs very well, MITRE is in no way suggesting this as a recommended device, nor are we in the position to comment on the strength of this compared with other, similar configurations proposed by other vendors.

The local area network has substantial performance impact since it presents each terminal image to the central computer as though it were locally attached to the CPU, thus yielding substantial (over one second) performance improvements. The customer on the remote end of the local network sees these performance improvements directly.

The path between the central computer and the remote terminal is operated at 9,600 bits per second, roughly 1,000 characters per second. In a normal IBM remote terminal environment, the screen of a remote terminal remains blank until the full image is transmitted (1,920 characters plus overhead). Thus, in a normal multibuilding campus environment such as MITRE, the fastest response that can be delivered is a woeful two seconds per screen (assuming zero CPU).

Performance in a growth environment requires an understanding of both the growth effects and the prediction of added load to be placed on the system. As we described earlier, we have a clear understanding of our expected load growth. We are adding 15 terminals per month for the next three years (approximately). The main effect is in the increase in logged-on-users. We are growing at the rate of approximately five users per month (about one peak logged-on user per each three new terminals).

The number of active users is a better indication of the load on the central facility. It is well known that a CPU will support a large number of terminals if they are not used. In our office automation environment, logged-on terminals tend to be active because of a strange anomaly of our office automation software: it keeps a clock on the screen up to date by refreshing the screen once each minute. Thus, the active user count is also growing by about one user for each three terminals added to the network.

Capacity comes in chunks; a machine is typically either upgraded or replaced whenever there is insufficient capacity to support the required workload. Given this fact, we can expect response to degrade slowly as the user load grows until the response goals are no longer being met consistently. At that point (or ideally, just before), a capacity upgrade is required. This, in turn, causes an improvement in response and the cycle starts again.

There are many elaborate tools for capacity planning on the market. Each attempts to predict, based on past performance, when the present hardware will become saturated and require upgrade. If you are fortunate to locate a measure of performance that correlates well with response, you may save a lot of money and time. In our case, interactive response time is reported by the system. The reported figure is the inboard response and does not include communication software, line, and terminal delay. The time the user sees is not as good as this number, but it is a constant ratio.

We have determined from previous experiments that interactive response time below 200 milliseconds is excellent. We are not claiming that the end user sees response within 200 milliseconds of the pressing of a function key. While we believe it is close, we have not measured this number and can make no such claims. We prefer, however, to state that the response delivered is well correlated to the number presented, and the majority of our users feel that response is excellent when numbers below 200 milliseconds are reported by the system reporting software.

During a typical day, six to seven seconds per minute are devoted automatically by the computer scheduling software to the interactive OA users. This low percentage of the CPU resource (10%-12%) is sufficient to provide a repeatedly measured response time of less than two-tenths of a second for all interactive transactions of a short duration. Those interactive functions of a longer duration, such as database queries and massive report generations, are detected by the computer scheduler and scheduled over a one- or two-second period by the remaining 80% to 90% of the CPU resource.

Modern disk subsystems provide a large amount of data per disk. We have found that our disk access mechanism will serve between 15 and 30 simultaneous office automation users, providing for their storage and systems support needs in an efficient and timely manner. Currently disks yield about 10 million characters of storage per user by just providing sufficient disk drives to meet the needs of system responsiveness.

This leads to a very well balanced condition in a modern operating system environment that permits the mixing of system and user data. Each increment of user growth requires more storage for private data and more access arms to ensure excellent system response time. Both are delivered in a balanced package with modern disk subsystems.

Real memory is the critical factor in delivering excellent performance in a central support office automation configuration. Each vendor's scheme for mapping virtual storage into real memory differs in its implementation detail; however, all must be provided with sufficient real storage to ensure that most of a user's program is in real storage whenever required.

In our environment, we feel that a program portion, or page, once referenced should remain in real memory for a minimum of 10 seconds before being replaced by another user's pages. Our current 16 million bytes of real memory constantly better this goal for a peak of 180 simultaneous users.

Bottlenecks always exist in meeting the stated performance goals for any computing center. In an office automation environment, they extend beyond the traditional CPU and DISK SPACE numbers normally considered in a batch environment. The nontraditional bottlenecks extend to printers, communication ports, and terminals. High-quality printers are a must in an office automation environment. It is a myth that electronic mail replaces paper. Try to read a 500-line message on a video terminal. A hundred or so lines into it, you automatically reach for a magic marker and circle something to go back to for further study. The result, in our case, is needing a cloth and a spray bottle to clean the screen several times per day.

Our customers depend on the timeliness of the printing facility to meet their production schedules. Several very high quality printers must be utilized to ensure sufficient capacity and redundancy for any expected action. For example, this briefing was prepared electronically on an IBM 6670 LASER printer using software developed at the MWCC. The final charts were previewed on the terminal and only a single, camera-ready copy was produced on the printer.

You might think this would reduce the printing demands. Actually, the opposite has proven to be true. Our customers were expecting several-day turnaround for the production of high-quality VUGRAPHs by the reprographics department. We have shortened that time to 15 minutes. Unfortunately, the customer has also shortened the time before the briefing to work on the presentation by a like amount. Thus, the computing center must be able to deliver very rapid turnaround with extreme reliability whenever the VUGRAPH software is invoked.

CPU BUSY is the first number everyone wants to know when looking at response. It is not an important number in an OA environment since BUSY is normally a measure of batch rather than interactive workload. A better number is the number of seconds per minute the CPU spends servicing the interactive workload.

A channel is a path from memory to a direct access device, tape, or communications controller. In our environment, no more than six disk drives share a single channel. You may be able to support more or fewer disks per channel depending on the speed of the pack and the size of the disks.

There is no single value that can be determined for all hardware and software configurations; however, any one configuration should work for a balanced configuration, acquiring hardware and relocating data to meet this need.

In the environment shown, we began an aggressive balancing program in January and are now running a balanced I/O configuration.

Real memory is the critical determination of response in office automation or any other environment employing IBM equipment. We suspect real memory is the critical response factor in any environment. Real memory usage is a difficult item to measure precisely. We have examined many different reports to try and identify a single number of sets of numbers that characterize the utilization of real storage in our environment.

In doing this, we examined the dynamics of paging in our computing center. Our system operates in a demand paging environment. This means that a user's program does not require storage sufficient to hold the entire program before it can begin operating. The result, in a memory-constrained environment, is frequent suspension of the program while additional portions of the code or data are brought into memory from a backing storage device such as a disk.

When a user's program finishes executing, the code and data remain in storage for some time until that area of memory must be reused by other users for their code or data. Ideally, an active user will always have all code and data in storage for each execution of a program. Since OA customers tend to perform the same functions over and over, there is generally little or no paging or other I/O activity required; thus, excellent response is possible without exotic system tuning.

In our environment there is a table, called the CORE-TABLE (historical interest in core memory), that is scanned to find free pages. The system reports the rate of scanning of this table (SCAN RATE) in one of its regular performance charts. The change in SCAN RATE took place when we added an additional eight million characters of real memory to our overloaded computer.

SCAN TIME, the reciprocal of the SCAN RATE, is a derived number that IBM does not directly report in their performance software. A portion of a user program will remain in real memory for 10 seconds if it is not utilized. For example, if an OA customer uses a program section more often than once per 10 seconds, no I/O will result when the SCAN TIME is longer than 10 seconds.

There is a tendency to understate the costs of implementing an OA program throughout the company. Management is prone to forget the second-order costs and focus on the cost of the terminal and the terminal support cable plant.

Often there is a CPU replacement or upgrade required. There is always more printout, and printout of a more urgent nature. In our environment, much of the new printout can be of a sensitive nature (performance reviews, interview reports) and must be specially handled and retained for the users in a dispatch area.

The training demands jump. Prior to OA, our systems programmers conducted classes informally, as our user community was small and stable. Now, we have a very large percentage of nondata processing users with urgent training demands. Frequently, these training demands are placed on us by high executives who are satisfied only with, "Yes" or "Yes, sir," as answers to our schedule conflicts.

Documentation must often be written (or rewritten) to address customers who have never used a central computer before. Have you ever pondered how many different ways to spell ENTER as you survey the range of terminals that use RETURN or various graphic symbols rather than one consistent symbol?

Everyone wants to manage the computing staff. Systems team members suddenly get messages from vice presidents and are expected to be at their beck and call. Substantial interpersonnel training is required of the systems team. Members who were accustomed to hiding are suddenly connected electronically with everyone in the company.

Operations and system members must become diplomats! We have replaced nearly our entire systems team since the office automation project began. New systems programmers are selected as much for tact as for technical skills—it is a myth that systems people are hard to deal with and each systems programmer tries to cultivate that myth. There is a large group of professional systems programmers who understand they are responsible for many millions of dollars and long for the respect and responsibility that such investments 10

demand. Our staff has an excellent attitude toward our customers and recognizes that each of them directly contributes to support our mortgage, hobbies, growth, and professional aspirations.

One of the good (and bad) side effects of a centralized office automation configuration is that everyone in the company becomes a performance expert. Terms such as Q1TIME, SRM, RMF, PAGE RATE, and such are not the measure of excellence in performance. Use terms such as excellent, good, fair, and poor; and encourage complaints when response is other than excellent.

Measure everything easily available in your environment and look for items that correlate well. Hunt for those numbers that change sharply with a small change in response. Consider yourself, or your performance expert, as a detective. Request regular reports and expect presentations on trends and bottlenecks on a frequent basis.

Excellent performance is mandatory for office automation. Our software performance measurement tools report the introduce response time, excluding network delays, as 200 milliseconds maximum. This number is not an absolute measurement, but an indication of excellence. Users are consistently satisfied when the number is two-tenths of a second or below and begin to grumble when it rises above three-tenths of a second.

You must rethink and understand your goals in a large OA environment. Batch production must take second place on the machine dedicated to supporting the office automation customer.

The growth of the computing terminal network will be a byproduct of OA. The decision to introduce OA carries the decision to provide a very large number of terminals for use by professionals and support staff. It is MITRE's goal to install a terminal in every office occupied by professional or support staff. You cannot expect people to walk down the hall to use the telephone or read their morning mail.

User support is absolutely required in an OA environment. We select a portion of our user support team from the secretarial staff to ensure a minimum of jargon and ensure a goor relationship between the customers and the support peopl

### **Computer hardware and architectures**

Fayé Briggs, Track Chair

Achieving high performance in computer systems depends not only on using faster and more reliable hardware devices but also on major improvements in computer architecture and processing techniques. The Computer Hardware and Architecture track focuses on these issues. The track is composed of nine sessions that address the new generation of highperformance computers. The topics of these sessions are

- 1. Trends in Supercomputer Systems

- 2. The Fifth Generation

- 3. VLSI Design

- 4. 32-Bit Microprocessors

- 5. Attached Numerical Processors

- 6. New Microprocessor-Based Computer Architectures

- 7. Multiprocessor Systems

- 8. Distributed Processors

- 9. System Reliability

"Trends in Supercomputer Systems: Design and Use," a panel session, discusses five major issues: new system organizations, design trends, application software, the implications in operating systems and languages, and the Japanese effort in these areas. Another panel, "The Fifth Generation Revisited," follows the very successful panel on the same subject last year. The objective of this year's panel is to present an updated report on the status of the various worldwide programs that are fifth-generation computer research and development efforts.

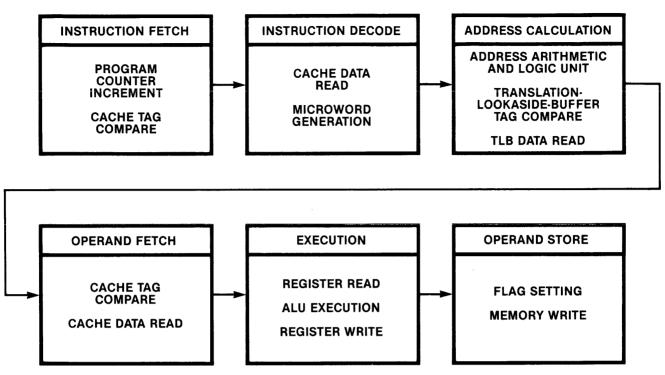

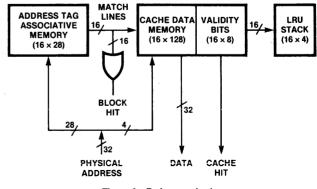

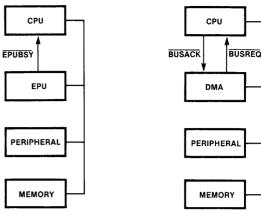

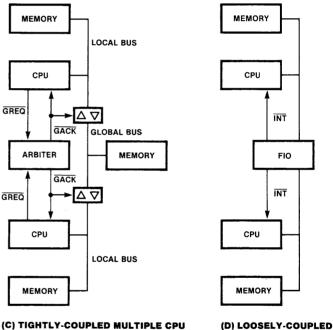

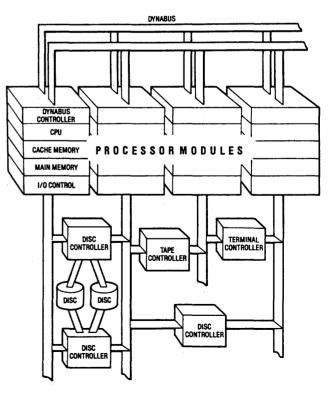

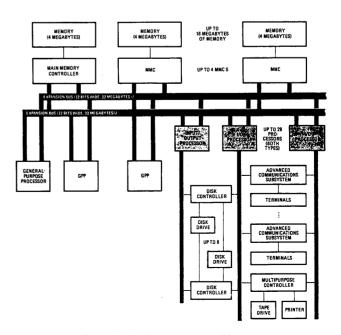

"VLSI Systems" is a paper session investigating the impact of VLSI designs and structures on computer architecture and hardware. The session starts with a tutorial paper on the status of VLSI. A design automation system and a sample design and application of a VLSI co-processor will be presented. The new generation of "32-Bit Microprocessors" and microcomputers is organized as a paper session. This session looks at the organization of these new high-performance microprocessors and the new challenge for integrating them into systems. They display advanced architectural features often found in minicomputers and mainframes. Examples of features presented are pipelining, prefetching schemes, larger virtual and physical address spaces, and data buffering schemes. "New Microprocessor-Based Computer Architectures" takes a look at complete computer systems based on these newer microprocessors.

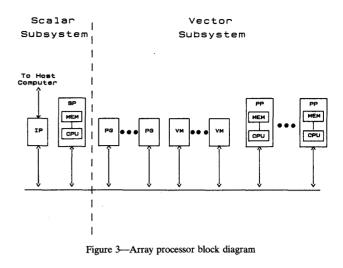

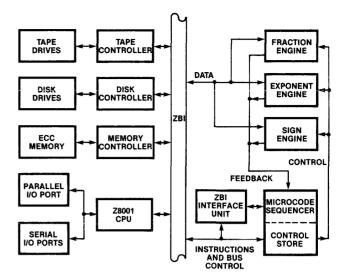

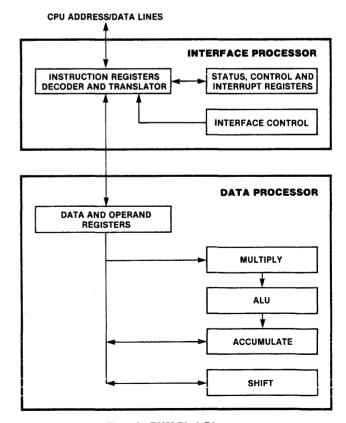

The next paper session, "Attached Numerical Processors," looks at the software and hardware approaches to implementing floating- and fixed-point arithmetics for use in the new generation of powerful microprocessors. The goals and design tradeoffs for one specific system are presented, and a new approach to designing a fast numerical workbench is also discussed. The latter scheme uses a set of replicated functional processors for fine and coarse granules of numerical processing.

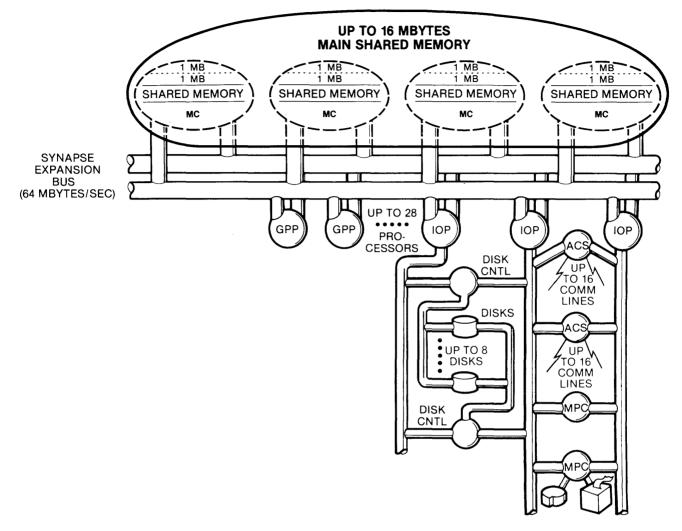

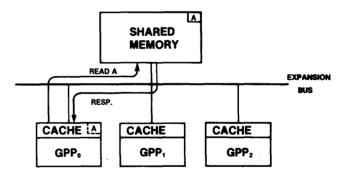

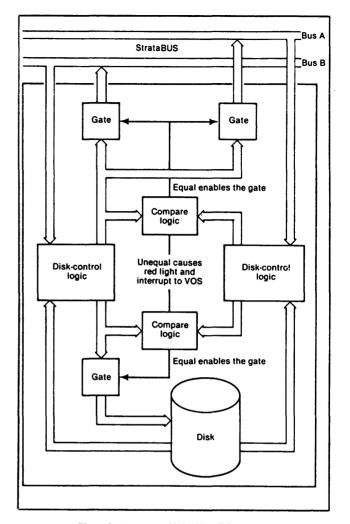

Two sessions are devoted to multiprocessing systems. The previously mentioned session, "New Microprocessor-Based Computer Architectures," focuses on how to exploit these new microprocessors in multiprocessing and other distributed applications. A paper session on multiprocessing investigates general multiprocessing concepts. The first paper illustrates the design of a high-performance multiprocessor using offthe-shelf microprocessors. The other two papers discuss new data-sharing techniques and models to estimate the throughput of multiprocessor systems.

The "Distributed Processors" session consists of papers looking at new techniques for network control. The first paper investigates a new bus arbitration scheme when VLSI functional units are destributed on the network. An innovative concurrency control mechanism and a practical implementation of a network operating system are also presented.

Finally, we have a paper session, "System Reliability." This session investigates innovative methods for diagnosing a multiprocessor system and methods for incorporating fault tolerance in system-level designs.

In summary, the Computer Architecture and Hardware track presents exciting continuity in the quest for reliable high-performance computing structures that are needed for the exploding computing needs of the late eighties and nineties.

### A multiaccess bus arbitration scheme for VLSI-densed distributed systems

by JIE-YONG JUANG and BENJAMIN W. WAH

Purdue University West Lafayette, Indiana

### ABSTRACT

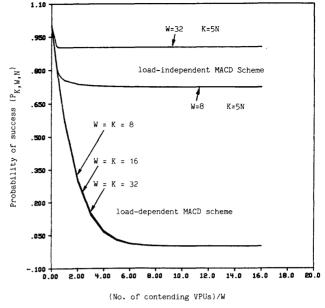

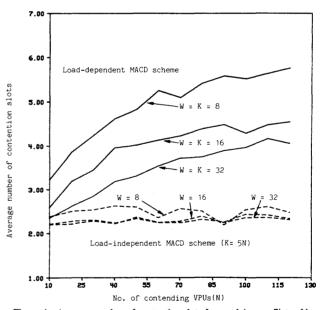

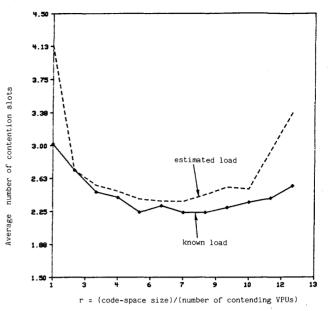

A VLSI-densed shared-bus distributed system is a computer system consisting of a large number of VLSI processing units (VPUs) connected to one another by a high-speed bus. Data traffic in such a system is characterized by three distinct features: large population, bursty transmission, and task-dependent accesses with priority. A bus arbitration scheme is required to resolve contentions when several VPUs generate requests simultaneously. Conventional schemes such as daisy chaining, polling, and independent requests are shown to be inadequate. In this paper, a multiaccess code-deciphering (MACD) scheme is proposed. Two versions of the scheme are studied. The first version is a load-dependent scheme that can resolve contentions of N VPUs in an average time of  $O(\log_{K/2} N)$  steps where K is equal to the bus width. The second version estimates the number of contending VPUs and resolves contention in a constant average time independent of load. The proposed schemes can support task-dependent accesses with priority.

. .

#### INTRODUCTION

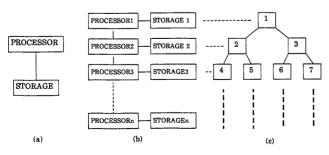

Recent advances in very large scale integrated logic (VLSI) and communication technology, coupled with the explosion in size and complexity of new applications, have led to the development of distributed computing systems. These systems possess a large number of general- and special-purpose processing units joined by an interconnection network. Notable examples are the PUMPS architecture,<sup>1</sup> the systolic-array architecture,<sup>2</sup> the recently announced Cyberplus computer,<sup>3</sup> and specialized systems, such as the processors at the joints of robot arms. PUMPS is a pattern analysis and image database machine that incorporates pools of special-purpose VLSI processing units. In a systolic-array architecture, sets of VLSI systolic processors, which perform functions such as matrix inversion, fast Fourier transform, and sorting, are connected to a host. The Cyberplus computer has a maximum configuration of 64 processors and a speed of 16 billion calculations per second. We call this kind of system a VLSI-densed system, and the processing unit, a VPU.

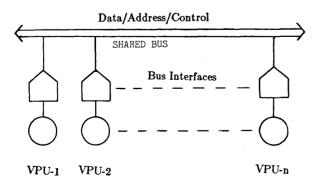

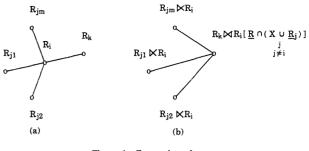

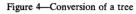

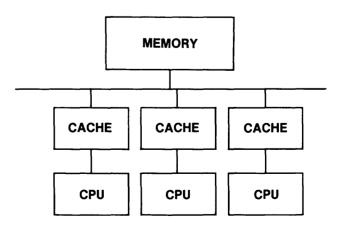

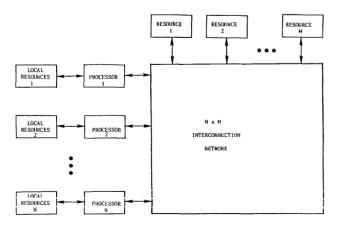

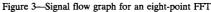

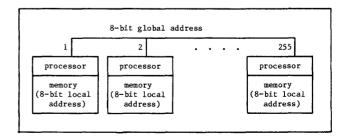

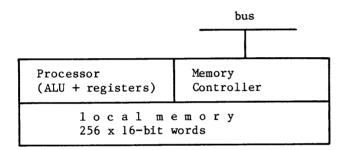

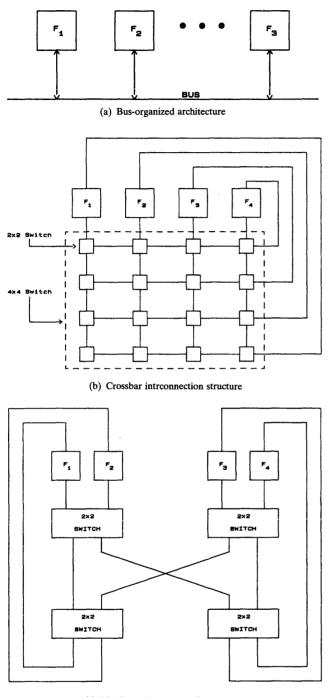

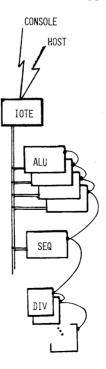

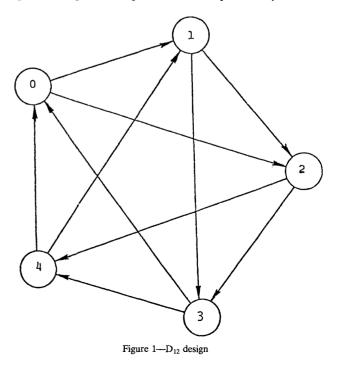

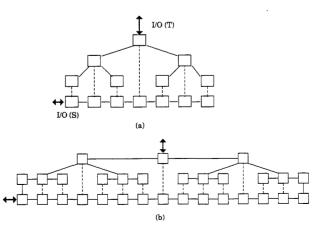

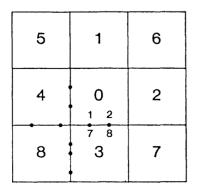

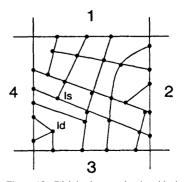

In a VLSI-densed system, one of the most important issues is the connection of the VPUs. A shared bus is widely used because of its simplicity in connection, flexibility in expansion, and efficiency in communication. Figure 1 depicts a typical configuration of such a system. Wah has shown that a shared bus provides enough bandwidth for a large class of VLSI-densed systems.<sup>4</sup> Large computer systems usually implement a number of relatively independent shared buses. The Cyberplus Computer has four independent "rings" that can partition the processors for four different applications.

In this paper, we propose a bus arbitration scheme for resolving contentions when several VPUs try to access the bus simultaneously. Characteristics of data traffic in a VLSI-densed system are discussed in the next section. Three conventional bus arbitration schemes, namely daisy chaining, polling, and independent requests are compared.<sup>5-7</sup> These

schemes are found to be inadequate for VLSI-densed systems. A load-dependent Multiaccess Code-Deciphering (MACD) bus arbitration scheme is proposed, and this scheme is extended so that an estimate of the number of contending VPUs is taken into account. The enhanced scheme can resolve contentions in a constant average time, independent of the number of contending stations.

### CONVENTIONAL BUS ARBITRATION SCHEMES

The operations of a VPU alternate between computations and data communications. We assume that when a VPU requests bus access, it has a large volume of data to transmit and requires a rapid response. That is, there is a large peak-to-average ratio of bus use. This type of data traffic is called *bursty* traffic.<sup>8</sup> Another characteristic of data traffic is that messages may have different priorities. Priority, in turn, depends on the urgency with which the bus is needed by a certain VPU for executing a task. The bus should be granted to the message with the highest priority.

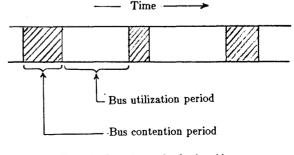

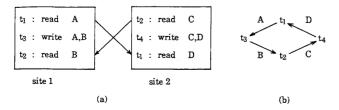

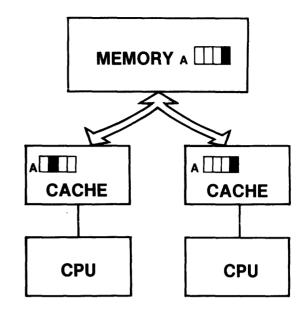

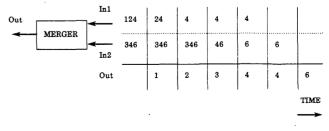

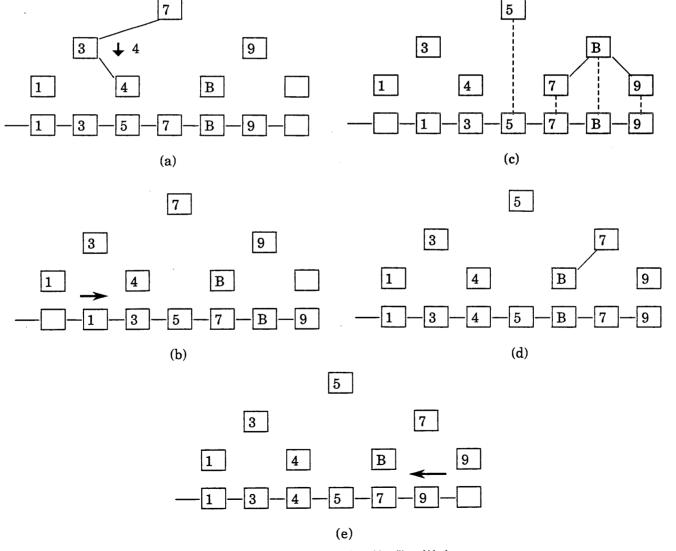

On the other hand, a bus shared by autonomous VPUs alternates between bus contentions and data transmissions (Figure 2). A VPU with data ready to transmit is allowed to contend for the bus during a contention period. In order to resolve the contentions in the minimum amount of time, a good bus arbitration scheme should be used. Three bus arbitration schemes have been proposed for conventional computer systems. They were identified by Thurber as daisy chaining, polling, and independent requests.<sup>7</sup>

In daisy chaining, all input-output devices are connected serially along a common control line. During the bus-granting process, a bus grant signal propagates sequentially, device by device, until a requesting device is encountered. This device blocks further propagation of the signal and gains control of the bus by setting the bus busy line. This scheme involves the

Figure 1-Configuration of a VLSI-densed system

Figure 2-Operation mode of a shared bus

use of at least three control lines: bus grant, bus request, and bus busy.

In a bus system with polling, a set of poll count lines is connected directly to all the devices on the bus. In response to bus requests, a sequence of numbers, each of which corresponds to the address of a device, is generated on the poll count lines. When a requesting device finds that its address matches the number on the poll count lines, the bus is granted to this device, and the bus busy line is set. This scheme requires  $[\log_2 M]$  poll count lines, where M is the number of devices on the bus, and two additional control lines are for bus request and bus busy.

In an independent-request scheme, each device has a separate pair of bus request and bus grant control lines connected to the arbitrator. When a device requests bus access, it sends a request signal on its bus request line. Bus control will be granted to one of the requesting devices based on predetermined priorities assigned to the devices. For M devices on a system implementing this scheme, more than 2M control lines are necessary. This scheme is the most costly as far as the number of control lines is concerned.

As VLSI-densed systems bear distinctions in the operating environment from that of conventional systems, the above bus arbitration schemes are found to be inadequate. We examined these schemes with respect to the control line complexity, the time complexity and the capability of task-dependent priority accesses.

- 1. Control-line complexity. The polling scheme is impractical when the number of VPUs is large because the number of poll count lines must be large enough so that each VPU can be identified by a unique address. A pair of control lines is needed for each VPU in the independent-request scheme. This is impractical even when the number of devices is moderately large.

- 2. Time complexity. Daisy chaining and polling are basically sequential schemes. They are inadequate for handling bursty traffic, which is characterized by a high ratio of peak-to-average data transmission rate and the fact that only a few VPUs are requesting bus access at any time. Suppose there are N out of M independent requesting devices, the average time to identify a requesting device is M/N. When N is small and the data transmission time is short, the overhead for bus arbitration is large.

- 3. Capability of task-dependent priority accesses. Priority of a device connected in a daisy chain is determined by its physical position in the chain. In a polling scheme, it is determined by the device's order in the sequence of polling counts. The priorities of the bus request lines in an independent-request scheme are usually fixed at design time. Since the priority of devices cannot be changed easily, the three existing schemes are incapable of handling task-dependent priority accesses.

The above observations reveal that none of the three conventional bus-arbitration schemes is sufficient for the needs of VLSI-densed systems. They call for a new arbitration scheme that can handle bursty traffic and that will access with priority.

### LOAD-DEPENDENT MULTIACCESS ARBITRATION SCHEME FOR VLSI-DENSED SYSTEMS

In this section, a deterministic MACD scheme is presented. The scheme is discussed with respect to access without and with priority.

### MACD Bus Arbitration for Access without Priority

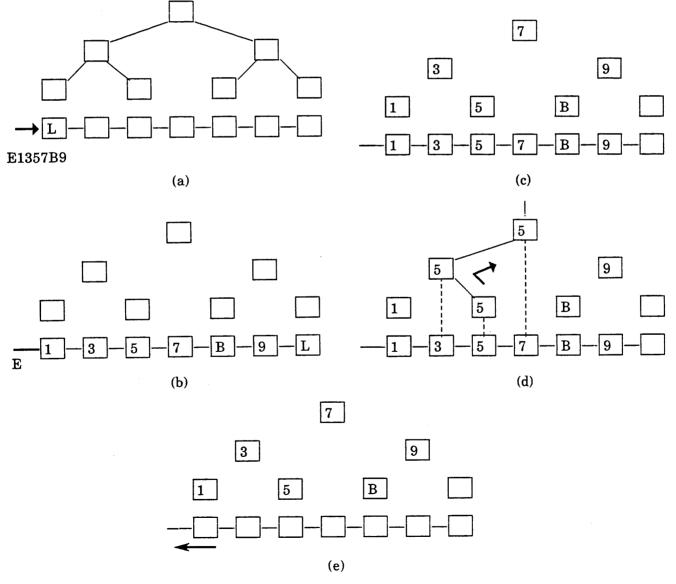

We have previously studied a window search scheme to resolve contentions in a local multiaccess network.<sup>9,10</sup> In that scheme, a global window is maintained by all the stations, and each contender generates a contending parameter. A contender is eliminated from contention if its parameter is outside the window. A distributed control rule is applied to expand or to shrink the window in each contention step. As the contending process proceeds, the window size becomes smaller and smaller. Eventually, a unique contender is isolated in the window.

We can adapt the above scheme for resolving bus contentions. To support the scheme, two mechanisms are needed: a collision detection mechanism and a window control mechanism. The collision detection mechanism can be implemented by using the Wired-OR property of the bus. When two or more VPUs write simultaneously on the bus, the result is simply the bitwise logical OR of these numbers. By interpreting the result after a write, each VPU can determine whether a collision has occurred. The window control scheme described in References 9 and 10 is based on information of previous contentions and an estimate of the channel load. It is too complicated to be useful in the bus environment. The MACD technique, however, is a fast and effective scheme that combines window control and collision detection in a simple manner.

To describe the scheme formally, let us assume that there are N requesting VPUs, and each VPU writes a binary number  $X_i$  (i = 1, 2, ..., N) to the bus. The  $X_i$ s are chosen from a structured code space S with the following properties:

$$\begin{array}{ll} X_i, X_j \in S, & i \neq j, \text{ are related, i.e.,} \\ & X_i \! > \! X_j \text{ or } X_i \! < \! X_j \end{array}$$

$$f(X_1 \oplus X_2 \oplus \dots \oplus X_N) \le \max\{X_1, X_2, \dots, X_N\} X_i \in S, N \ge 1$$

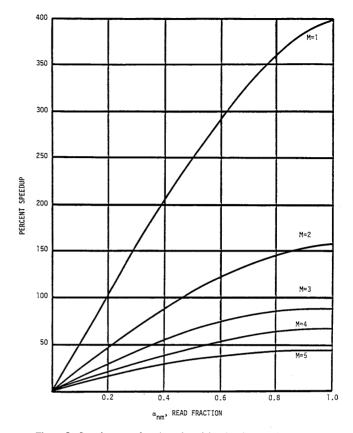

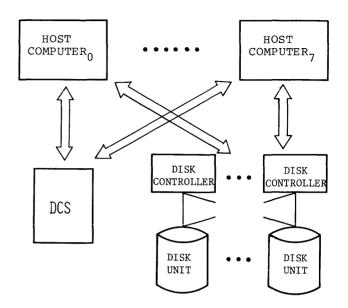

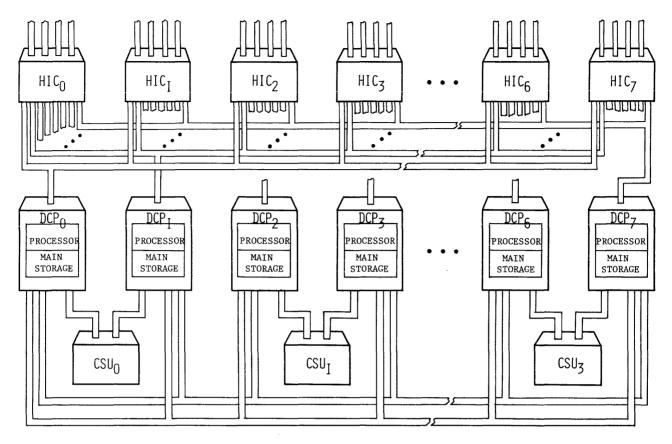

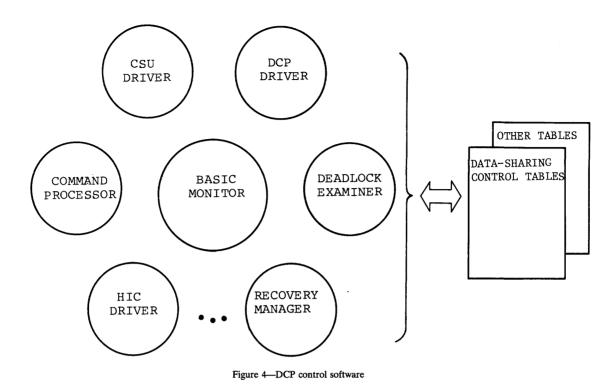

(2)