# TM 9-1220-221-10/1

# TECHNICAL MANUAL

# PROGRAMMING MANUAL

# FOR

# COMPUTER, GUN DIRECTION, M18 (FADAC)

# HEADQUARTERS, DEPARTMENT OF THE ARMY

**AUGUST 1972**

NO. 9-1220-221-10/1

HEADQUARTERS DEPARTMENT OF THE ARMY Washington, D.C., 4 August 1972

# PROGRAMMING MANUAL

COMPUTER, GUN DIRECTION, M18 (FADAC)

| CHAPTER 1.  | GENERAL DESCRIPTION            | PAGE |

|-------------|--------------------------------|------|

| 1.1         | Purpose                        | 1-1  |

| 1.2         | Physical and Operational       |      |

|             | Characteristics                | 1-1  |

| 1.3         | Functional Description         | 1-4  |

| 1.4         | Description of Memory          | 1-7  |

| 1.4.1       | Program Addressable Special    |      |

|             | Registers                      | 1-10 |

| 1.5         | Control Buttons                | 1-12 |

| 1.6         | Number Systems Used            | 1-13 |

| CHAPTER 2.  | WORD FORMAT AND                |      |

| CIMI IER 2. | INSTRUCTION REPERTOIRE         |      |

|             |                                |      |

| 2.1         | Word Formats                   | 2-1  |

| 2.2         | Instruction Repertoire         | 2-6  |

| 2.2.1       | Arithmetic                     | 2-8  |

| 2.2.2       | Store and Load                 | 2-10 |

| 2.2.3       | Transfer                       | 2-17 |

| 2.2.4       | Shift and Cycle                | 2-18 |

| 2.2.5       | Logic and Special Instructions | 2-22 |

| 2.2.6       | Discrete Input/Output          | 2-26 |

| 2.2.7       | Parallel Input/Output          | 2-34 |

| 2.2.8       | Read Commands                  | 2-36 |

| 2.2.9       | BCD and Alpha-numeric Input    | 2-38 |

| 2.2.10      | Write Commands                 | 2•42 |

| CHAPTER 3.  | CODING FOR FADAC               |      |

| 3.1         | Minimum Access Coding          | 3-1  |

| 3.2         | Optimizing Assignments -       |      |

| -           | Main Memory                    | 3-3  |

|             | ·· - ·                         |      |

|             |                                | i    |

PAGE

| 3.3        | Optimizing Assignments -       |              |

|------------|--------------------------------|--------------|

|            | R&Q-Loops                      | 3-7          |

| 3.4        | Use of Registers for Temporary |              |

|            | Storage                        | 3-9          |

| 3.5        | Use of R and Q-Loops           | 3-13         |

| 3.6        | Instruction Modification       | 3-14         |

| 3.7        | Store Instruction Restrictions | 3-17         |

| 3.8        | Linkage to Subroutines         | 3-18         |

| 3.9        | Table Look-up                  | 3-20         |

| 3.10       | Memory II/Memory III           |              |

|            | Addressing Technique           | 3-22         |

| 3.11       | Use of 146 NI                  | 3-32         |

| 3.12       | Word Input/Output              | 3-36         |

| CHAPTER 4. | FADAC OPERATING PROCEDU        | RES          |

| 4.1        | Control Panel                  | 4-1          |

| 4.2        | FADAC Field Table              | 4-8          |

| 4.3        | Signal Data Reproducer (SDR)   | 4-8          |

| 4.4        | Input                          | 4-11         |

| 4.4.1      | Octal Control Characters       | 4-13         |

| 4.4.2      | Preparation of Paper Tapes     | 4-15         |

| 4.5        | Preparation of the FADAC       |              |

| ,          | System                         | 4-16         |

| 4.5.1      | Starting the System            | 4-17         |

| 4.6        | Input Through External Control | 4-17         |

| 4.6.1      | Paper Tape (SDR)               | 4-17         |

| 4.6.2      | Paper Tape (Mechanical         |              |

| 4.0.2      | Reader)                        | 4-19         |

| 4.7        | Input Through Program Con trol | 4-19<br>4-22 |

| 4. /       | input Infough Program Control  | 4-22         |

| APPENDICES |                                |              |

| Α          | Powers of Two Table            | A-1          |

| В          | Octal-Decimal Integer          |              |

|            | Conversion Table               | B-1          |

|            |                                |              |

|        |                                                          | PAGE |

|--------|----------------------------------------------------------|------|

| C<br>D | Numeric Input/Output Codes<br>Alpha-numeric Input/Output | C-1  |

| 2      | Codes                                                    | D-1  |

| Е      | Optimization Table                                       | E-1  |

| F      | Summary of FADAC                                         |      |

|        | Instruction Repertoire                                   | F-1  |

|        | LIST OF FIGURES                                          |      |

| FIGURE |                                                          | PAGE |

| 1.1    | Functional Diagram of System                             | 1-5  |

| 1.2    | Conceptual Layout of FADAC                               |      |

|        | Memory                                                   | 1-8  |

| 2.1    | FADAC Octal Format                                       | 2-2  |

| 2.2    | Instruction Word Format                                  | 2-2  |

| 2.3    | Data Word Formats in BCD and                             |      |

|        | Alpha-numeric Codes                                      | 2-6  |

| 2.4    | Shift and Cycle Command                                  |      |

|        | Summary                                                  | 2-20 |

| 2.5    | DIA Pin and Line Connections                             | 2-28 |

| 2.6    | Matrix Position Codes                                    | 2-29 |

| 2.7    | DIA Command-Binary                                       |      |

|        | Information                                              | 2-29 |

| 2.8    | Discrete Output Command                                  |      |

|        | Summary                                                  | 2-34 |

| 2.9    | Input/Output Command Format                              | 2-36 |

| 3.1    | Multiplexing Diagram                                     | 3-2  |

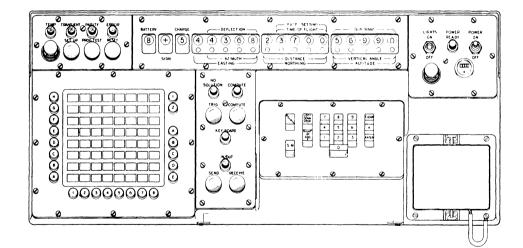

| 4.1    | Production Engineering FADAC                             | 4-2  |

| 4.2    | Relationship Between Nixie                               |      |

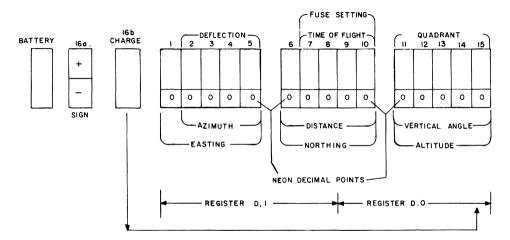

|        | Lights and D-Register                                    | 4-7  |

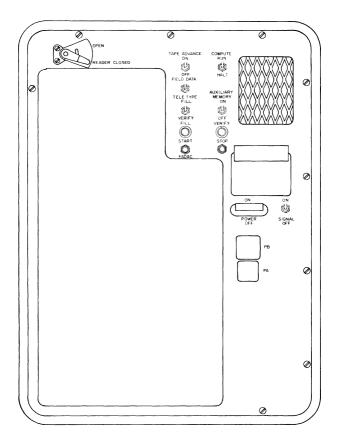

| 4.3    | Signal Data Reproducer (SDR)                             | 4-9  |

# LIST OF FIGURES (Cont'd)

| FIGURE |                                            | PAGE |

|--------|--------------------------------------------|------|

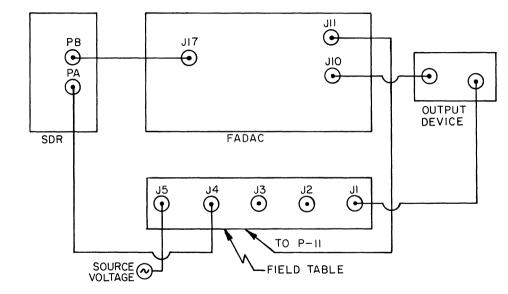

| 4.4    | Block Diagram of a Typical<br>FADAC System | 4-12 |

| 4.5    | Mechanical Reader                          | 4-20 |

# LIST OF TABLES

| TABLE |                               | PAGE |

|-------|-------------------------------|------|

| 1.1   | Summary of Register Addresses | 1-12 |

| 1.2   | Control Button Address        | 1-13 |

#### CHAPTER 1

#### GENERAL DESCRIPTION

#### 1.1 PURPOSE

The purpose of this publication is to describe techniques required to program the Computer, Gun Direction, M18 (FADAC).

#### 1.2 PHYSICAL AND OPERATIONAL CHARACTERISTICS

FADAC is a general purpose, transistorized digital computer designed for field use. By proper programming, it may be used to perform a variety of tasks. Information flow is serial by bit, parallel by function, allowing up to 12,800 operations per second.

Size.

24 inches by 14 inches by 34 inches.

Weight.

Approximately 210 lbs.

Power.

Three-phase, 4 wire, 400 Hz system, 120 volts line to neutral/208 volts line to line, approximately 750 watts.

Temperature.

$-25^{\circ}$ F to  $125^{\circ}$ F (external ambient at sea level); with rear cover installed, to  $-40^{\circ}$ F. Automatic temperature protection is provided.

#### Commands.

One command per word; each command contains both address of operand and address of next instruction (1 + 1 system).

#### Numbers.

Straight binary for internal operations; automatic conversion to other codes for input-output; two's complement notation for negative numbers.

#### Word Length.

Thirty-two programmable bits; sign bit and 31 magnitude bits for numerical value.

#### Memory Type.

Magnetic Disc, 6000 rpm nominal speed of rotation.

#### Storage Capacity.

Sixty-four channels of 128 words each (8192 words) in main memory. Also provided are two 16 word highspeed loops for rapid access, three 1-word registers for arithmetic operations and control, and one 2-word register for output display information storage. All channels and loops have one read and one write head, except the 16-word loops which have an additional read head.

#### Pulse Repetition Rate.

Nominal pulse repetition rate, 460 kilopulses per second.

#### Access Times.

One word-time is 78 to 83 micro-seconds. One disc revolution requires approximately 10 milliseconds.

Input.

Input to the computer is from the manual keyboard or the mechanical tape reader on the control panel, at approximately 10 characters/second, or from external sources, such as: Reproducer, Signal Data, AN/GSQ-64, a high speed photo electric reader designated the Signal Data Reproducer (SDR) (600 characters/sec); another FADAC; magnetic tape (4000 char/sec max); other devices. Input may be in 5-channel Teletype or 8-channel Fieldata code.

Output.

FADAC can transmit data to either the Nixie tube visual display unit on the control panel, or through the output plug, to any output device such as a printer, paper tape punch unit, another FADAC, or other Fieldata or Teletype equipment. Output information is in 5-level teletype, 8 level Fieldata or 2-wire Teletype codes, as required. In addition to the standard codes, FADAC can be programmed to generate any 8-bit code. Output rates depend on the output code selected, as well as the output equipment. Maximum rates are as follows:

- (1) 4000 char/sec in A/6

- (2) 3550 char/sec in A/5 and A/4

- (3) 650 char/sec in octal or BCD

Additional Features of the Computer.

(1) Parity check on information transfers.

(2) Verify indicator (located on the SDR) on input in Program-Fill mode.

(3) Gating for external support equipment to permit logic failure isolation to single printed circuit board.

(4) Marginal test circuit forpreventive maintenance.

(5) Voltage transient warning indicator.

(6) Temperature warning indicator.

(7) High speed (2 bits-at-a-time) multiplication, division, and shifts.

(8) Self-checking for overflow.

(9) Standardized printed circuit boards to minimize logistic problems.

# 1.3 FUNCTIONAL DESCRIPTION

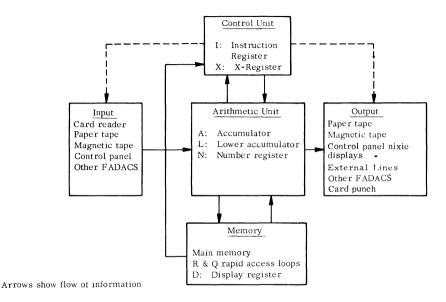

A functional diagram of the FADAC system is shown in Figure 1.1.

#### Control Unit.

The computer control unit interprets and processes the programmed instructions. Each instruction word called from memory is processed by the control logic through two non-program-addressable registers, X and I. During execution of the current instruction in the Iregister, the next instruction is stored in the X-register. On completion of execution of the current instruction, the next instruction is sent to the I-register, and the new next instruction is read into the X-register. If the next instruction is found just as execution of the current instruction is completed, the X-register is bypassed, and the instruction is sent directly to the Iregister. (See discussion of Multiplexing, Section 3.1.)

Arithmetic Unit.

The Arithmetic Unit performs the actual work involved in problet, solution. In addition to the four arithmetic operations, this section can shift and cycle numbers right and left, and assist in operations which make it possible for the computer to make decisions, to accept and store input information, and to format and transmit output information. The Arithmetic Unit is

Figure 1.1. Functional Diagram of System

comprised of arithmetic logic, input/output logic, and three one-word, program-addressable registers: the Accumulator (A), the lower Accumulator (L), and the Number register (N).

The A-register is the principal arithmetic register in FADAC. It is employed in all arithmetic, logical, input/output, and decision making operations.

The L-register is an extension of the A-register in some operations (as in Multiply and Divide); and functions independently of A in others (as in Zero L, Store L). It also serves as the location counter for input/ output operations.

The N-register holds the second operand for some operations (as in Multiply and Divide). It serves as an input/output buffer, and is used in program control transfer operations to store the transfer instruction, if that instruction is flagged.

The A, L, and N-registers are physically part of the FADAC memory disc.

Memory Unit.

The FADAC memory unit stores information in the form of instruction words and data words. It is comprised of 8192 words of main memory, plus two 16-word rapid access loops (R and Q) and one 2-word display loop (D).

#### Input.

Data and instructions can be placed in FADAC memory using any of the devices listed in Section 1.2. The Signal Data Reproducer (SDR) is the primary input device.

#### Output.

FADAC output is transmitted to the NIXIE display panel, or through the FADAC plug (J-10) to any external device, as listed in Section 1.2.

#### 1.4 DESCRIPTION OF MEMORY

#### General.

FADAC memory is a rotating disc, coated with ferrous oxide similar to the coating on conventional magnetic tape. The disc rotates at approximately 6000 rpm under stationary read and write heads. To record information on the disc, an electrical signal generates a magnetic field in a write head. This field produces magnetization on the disc which remains, even when the computer is de-energized, until replaced by new information. The read heads are similar to the write heads, but operate in reverse. A change in magnetization on the disc produces an electrical current in the head. These signals produce the 1's and 0's for the binary operation of the computer.

#### Memory Layout.

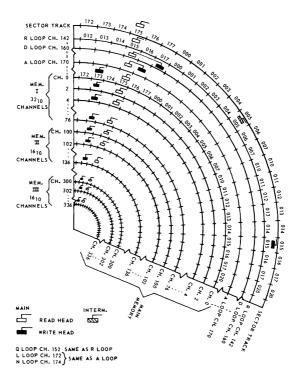

A conceptual layout of the FADAC memory is shown in Figure 1.2. Although the actual position of the heads and the relative positions of the tracks are not exactly as shown, this diagram provides a useful overall pictorial diagram. The disk is designed in channels, each equipped with read and write heads. The sector track is permanently recorded and has a read head only. The purpose of the sector track is to supply data which notifies the control unit which sector is about to pass under the read heads for the other channels. The main memory read heads are all at the same effective sector location at any given point in time.

Figure 1.2. Conceptual Layout of FADAC Memory

#### Sector Track Contents.

The sector track contains 128 words of factory recorded information, available serially from a read flip-flop. A binary number appears in every word of the sector track. In each successive word the number is increased by 1, such that the octal numbers 0 to 177 are represented. These numbers serve as reference for numbering the memory sectors. Also recorded on the sector tract are the Teletype (TT) and Fieldata (FD) tape codes, in inverted format, for each of the 16 BCD and Octal characters recognized by FADAC. The four least significant bits of each sector number represent the BCD and Octal translation of the TT and FD tape code for a given character. The tape codes are repeated eight times around the sector track. See Section 2.2.7 for a description of how this information is used during I/O operations and Appendix C for a list of BCD and OCTAL codes.

#### Main Memory.

The 64 main memory channels are addressed by the even octal numbers 0 through 136 and 300 through 336. The 128 words or sectors of each channel are addressed by consecutive octal numbers 0 through 177 inclusive. To clarify discussion, the channels in main memory will be referenced throughout this manual as follows:

#### Hot and Cold Memory.

Main memory is further divided into Working Storage (Hot Memory) in which both the read and write heads are energized, and Permanent Storage (Cold Memory) in which the read heads ONLY are energized. At programmer's option, the size of working storage may be specified as either 4, 12, or 16 channels, and the FADAC "Hot Channel Select Switch" (see Section 4.5) manually set to energize the write heads of specific Hot Channels, as listed below:

| Hot Channels<br>Set<br>(In Octal)                             |

|---------------------------------------------------------------|

| 70 - 76                                                       |

| $\begin{cases} 70 - 76 \\ 110 - 116 \\ 130 - 136 \end{cases}$ |

| (130 - 136<br>40 - 76                                         |

|                                                               |

With the SDR connected to FADAC and the Auxiliary Memory Switch on the SDR in the OFF position, all write heads in main memory are energized to allow all of memory to be filled. However, during normal field use, memory is filled, the SDR disconnected, and only the contents of Hot memory can be varied. This design was adopted to assure that the contents of permanent memory are not inadvertently destroyed because of operator error or power failure during field use.

#### 1.4.1 PROGRAM-ADDRESSABLE SPECIAL REGISTERS

#### Description.

The A, L, N, D, R, and Q-registers are short, 1-10

recirculating loops. Each bit is sensed by the read head and rewritten by the write head. Each word is shifted, bit-by-bit, through the loop. The loop information remains the same unless changed by some arithmetic or control operation. A, L, and N are 1-word loops whose contents are rewritten each word time. D is a 2-word loop, the contents of which are rewritten two sectors ahead of the read head. Both the R and Q-loops have an intermediate read head located in the middle of the loop. This head is not involved in the recirculation process. However, it is used automatically by FADAC to expedite execution of a command which causes the contents of a sector in the R or Q-loop to be read.

#### The R and Q-Loops.

The rapid access loops, R and Q, may have octal sector addresses 0 through 177. However, only the last four bits, (00 through 17) are recognized. When addressing the R and Q-loops, therefore, only sectors 00 through 17 should be used. Note the contents of each sector of the R and the Q-loops are repeated eight times around the R and Q-loop tracks. The channel address of the R-loop is 142.00 and of the Q-loop, 152.00.

#### One-Word Loops.

The A, L, and N-registers each effectively occupy a full track on the FADAC memory disc. The contents of each loop are always immediately available under a read head. They are addressed as 170.00, 172.00 and 174.00 respectively.

#### The D-Register.

When the main memory read heads are over any even numbered sector, the contents of D.O are under a read head; while when the main memory read heads are at any odd numbered sector, the contents of D.1 are available, since the D-register also effectively occupies a full track on the memory disc. Since the read and write heads of the D-loop are spaced two sectors apart both heads are effectively at the same sector of D at any given word time. The D-loop address is 160.000 (D.0) and 160.001 (D.1).

#### Summary of Register Address.

All register addresses are summarized in Table 1.1.

#### TABLE 1.1 SUMMARY OF REGISTER ADDRESSES

| Register | Channel<br>Address<br>(Octal) | Sector<br>Address<br>(Octal) | Description                        |

|----------|-------------------------------|------------------------------|------------------------------------|

| R        | 142                           | 000 - 017                    | 16 words                           |

| Q        | 152                           | 000 -017                     | 16 words                           |

| D.0      | 160                           | 000 or even sec.             | 1 word                             |

| D.1      | 160                           | 001 or odd sec.              | 1 word                             |

| A        | 170                           | 000                          | A•register (Accumulator)           |

| L        | 172                           | 000                          | L•register (Lower                  |

| N        | 174                           | 000                          | Accumulator)<br>N•register (Number |

|          |                               |                              | Accumulator)                       |

#### 1.5 CONTROL BUTTONS

The eight control buttons located on the front panel of FADAC are effectively wired directly to the memory locations shown in Table 1.2.

#### TABLE 1.2

#### CONTROL BUTTON

#### ADDRESS

| Control Buttons | Address (Octal) |  |  |  |  |  |  |

|-----------------|-----------------|--|--|--|--|--|--|

| Sample Matrix   | 000 . 000       |  |  |  |  |  |  |

| Test            | 000 . 001       |  |  |  |  |  |  |

| Set Up          | 000 . 002       |  |  |  |  |  |  |

| Recall          | 000 . 003       |  |  |  |  |  |  |

| Send            | 000 . 004       |  |  |  |  |  |  |

| Compute         | 000 . 005       |  |  |  |  |  |  |

| Trig            | 000 . 006       |  |  |  |  |  |  |

| Receive         | 000 . 007       |  |  |  |  |  |  |

When a control button is depressed, the flip-flop is set for Memory II, FADAC enters the compute mode, and the instruction stored in the control button location is executed. Computation is usually initiated in this manner. Note that the control button locations may be called in a program and their contents executed under program control.

#### 1.6 NUMBER SYSTEMS USED

Number systems applicable to the FADAC computer are the decimal system, the octal system and the binary system. Information going into or coming from the computer is either decimal, octal or alphabetic. However, the computer operates internally with binary numbers only, and all negative numbers are represented in two's complement notation.

# **CHAPTER 2**

# WORD FORMATS AND INSTRUCTION REPERTOIRE

#### 2.1 WORD FORMATS

#### General.

Information stored in FADAC memory contains no inherent distinction between numerical data and computer instructions. Both are stored as 36-bit binary coded numbers, of which 32 bits are programmable, and 4 a.e machine-generated. Of the 4 non-programmable bits, 1 is the parity bit, and 3 are used for synchronization. When a word is read from memory, the state of the computer logic will determine whether the information is to be interpreted as a data word or an instruction.

#### FADAC Octal Formats.

Each 32 bit FADAC word may be represented by 11 FADAC Octal digits. The first digit is formed from the two most significant bits of the binary word, and has a maximum value of 3. Each of the remaining digits is formed from three bits of the FADAC word, and has a maximum value of 7. Because of the short (i.e., two bits only) first digit in the FADAC format, a pure octal number and its FADAC-Octal representation are not the same.

#### Data Words in FADAC-Octal.

Information used as an operand is interpreted by the computer as a signed, 31 bit, binary-coded word, with a fixed point between the sign (bit position O) and the most significant bit. (See Fig. 2.1.) Positive numbers have a zero sign bit, and negative numbers a one. Negative numbers are represented in two's complement form.

- a) Bit Position

- b) Max. Binary Value

- c) Max. Octal Value

- d) FADAC Octal Position

#### Figure 2.1. FADAC Octal Format

Instruction Word Format in FADAC-Octal.

Commands are stored in the memory in the form of one instruction per computer word, represented by 11 FADAC-Octal digits. Each command consists of four separate fields; a flag, a next instruction address, an operation code (op code), and an operand address. (See Fig. 2.2.)

(A) Bit Position

#### (B) FADAC-Octal Position

# Figure 2.2. Instruction Word Format

The flag, which is in the sign position, provides for the modification of a FADAC instruction. The use of the flag is described for each instruction in the FADAC instruction list.

The Next Instruction Address, which tells the computer where to go next in the program sequence, consists of a channel and a sector portion. The channel portion consists of 7 bits. These are represented by 3 octal digits, which are evenly numbered from 000 to 174. The sector portion consists of 7 bits. These are represented by 3 octal digits which are numbered sequentially from 000 to 177.

The Operation Code, which represents the operation to be performed, usually consists of 6 bits. These are represented by 2 octal digits which are evenly numbered from 00 to 76. The shift, cycle, I/O, and most special instructions require a special format which is described in the sections covering these commands.

The Operand Address is the address of the number to be operated upon. It consists of a channel and sector portion and is in the same form as the Next Instruction Address.

A total of 15 octal digits seems to be required to represent an instruction word: 1 for the flag, 2 for the operation code, and 6 each for the addresses. Since a FADAC word is limited to only 11 digits, the four extra digits are combined in the following manner:

Let:

$x_1$  represent the octal digits in each of the four fields, and  $y_1$  represent the FADAC Octal digits:

FADAC Instruction Word

| Flag           | Next Ins                                                                      | struction                        | Op.                           | Address                       |                                                                      |                 |

|----------------|-------------------------------------------------------------------------------|----------------------------------|-------------------------------|-------------------------------|----------------------------------------------------------------------|-----------------|

| 1 145          | Channel                                                                       | Channel Sector Code              |                               | Channel                       | Sector                                                               |                 |

| ×1             | <sup>x</sup> <sub>2</sub> <sup>x</sup> <sub>3</sub> <sup>x</sup> <sub>4</sub> | <b>x</b> 5 <b>x</b> 6 <b>x</b> 7 | <b>x</b> 8 x9                 | *10 *11 *12                   | <b>x</b> <sub>13</sub> <b>x</b> <sub>14</sub> <b>x</b> <sub>15</sub> | Octal           |

| у <sub>1</sub> | <sup>y</sup> <sub>2</sub> <sup>y</sup> <sub>3</sub>                           | y <sub>4</sub> y <sub>5</sub>    | у <sub>6</sub> у <sub>7</sub> | <sup>y</sup> 8 <sup>y</sup> 9 | y <sub>10</sub> y <sub>11</sub>                                      | F ADAC<br>Octal |

Where:

| $y_1 = x_1 + x_2$                            | $\mathbf{y}_7 = \mathbf{x}_9 + \mathbf{x}_{10}$ |

|----------------------------------------------|-------------------------------------------------|

| $y_2 = x_3$                                  | $y_8 = x_{11}$                                  |

| $\mathbf{y}_3 = \mathbf{x}_4 + \mathbf{x}_5$ | $y_9 = x_{12} + x_{13}$                         |

| $y_4 = x_6$                                  | $y_{10} = x_{14}$                               |

| $\mathbf{y}_5 = \mathbf{x}_7$                | $y_{11} = x_{15}$                               |

| $y_6 = x_8$                                  |                                                 |

Note that all channels and operation codes are evenly numbered. Thus whenever an odd number ends a channel address field, a sector greater than or equal to 100 is called (i.e.,  $y_3 = x_4 + x_5$  or  $y_9 = x_{12} + x_{13}$ ). Whenever an odd number ends the op code field, the channel of the operand address is  $\geq 100$  (i.e.,  $y_7 = x_9 + x_{10}$ ).

The first digit is derived as follows:

$$y_1 = x_1 + x_2$$

$y_1 = 0$  when no flag is called and NI channel is < 100  $y_1 = 1$  when no flag is called and NI channel is  $\ge 100$  $y_1 = 2$  when a flag is called and NI channel is < 100  $y_1 = 3$  when a flag is called and NI channel is  $\ge 100$

To illustrate: Given the instruction "Clear and Add (24) the contents of channel 102, sector 133, and go to channel 112, sector 123," the word format is as follows:

|      | Next Instruction |         |   |    | 0      | Operand Address |      |     |    |      |      |    |     |    |                 |

|------|------------------|---------|---|----|--------|-----------------|------|-----|----|------|------|----|-----|----|-----------------|

| Flag | Ch               | Channel |   | Se | Sector |                 | Code |     | Cł | nanr | ne l | Se | ect | or |                 |

| 0    | 1                | 1       | 2 | 1  | 2      | 3               | 2    | 4   | 1  | 0    | 2    | Ţ  | 3   | 3  | Octal           |

|      |                  |         |   |    |        |                 | (C1  | LA) |    |      |      |    |     |    |                 |

| 1    |                  | 1       | 3 |    | 2      | 3               | 2    | 5   |    | 0    | 3    |    | 3   | 3  | FADAC-<br>Octal |

The FADAC octal word for this command is;

#### 11323250333

Or consider the coding required for the instructions "Subtract\* (02) the contents of channel 112, sector 113, and go to channel 112, sector 024."

|      | Next Instruction |   |        |   |   |      |          |          | Operand Address |   |        |   |   |   |                |

|------|------------------|---|--------|---|---|------|----------|----------|-----------------|---|--------|---|---|---|----------------|

| Flag | Channel          |   | Sector |   |   | Code |          | Channe I |                 |   | Sector |   |   |   |                |

| 2    | _1               | 1 | 2      | 0 | 2 | 4    | 0<br>(SU | 2<br>B*) | J               | 1 | 2      | 1 | 1 | 3 | Octal          |

| 3    |                  | 1 | 2      |   | 2 | 4    | 0        | 3        |                 | 1 | 3      |   | 1 | 3 | FADAC<br>Octal |

The FADAC octal word for this command is:

31224031313

2-5

#### Input/Output Code Formats:

In addition to Octal data words, information may be input and/or output in BCD, Alpha-4, Alpha-5, or Alpha-6 code. Fig. 2-3 illustrates the data word format for each of these codes.

- (a) Bit Position

- (b) BCD Code =4 bits/character; 8 characters/ FADAC word

- (c) Alpha-4 Code = 8 bits/character; 4 characters/ FADAC word (First bit of each character is inverted on output)

- (d) Alpha-5 Code = 6 bits/character; 5 characters/ FADAC word (Bits 0 and 1 are ignored)

- (e) Alpha-6 Code = 6 bits/character; 6 characters/ FADAC word (4 most significant bits of first character are stripped on input, machine-generated on output)

- Figure 2.3. Data Word Formats in BCD and Alphanumeric Codes

#### 2.2 INSTRUCTION REPERTOIRE

#### General.

All FADAC instructions fall into seven general categories according to function: Arithmetic Store and Load Transfer Shift & Cycle Logic and Special Discrete Input/Output Parallel Input/Output

Execution time for each instruction is shown in the Word Time portion of the description. Since one word time is approximately 78 to 83 microseconds, timing may be obtained by multiplying 80 x  $10^{-6}$  by the number of word times required to execute each instruction.

In the instruction descriptions, the following conventions are used:

(1) M represents the operand address of the instruction being executed.

(2) (M) represents the contents of location M.

(3) C represents the channel address of the operand address, or the 2 least significant digits of the 4 digit extended op codes required for shift, cycle, I/O and most special commands.

(4) S represents the sector address of the operand address in all categories except in instructions requiring a special format.

(5) A flagged instruction is represented in mnemonic form by writing an asterisk following the operation code, and in machine code by placing a 1 in bit position O. For example: CLA, CLA\*, STO, STO\*, TRA, TRA\*. The effect of the flag is specified in the description of each instruction.

(6) Unless explicitly mentioned under the description of each command, special registers are

not affected by the execution of a given command.

(7) All numbers are Octal unless otherwise specified, except numbers used to identify bit positions, which are designated in decimal.

#### 2.2.1 ARTHMETIC

#### General.

If overflow occurs upon execution of the following instructions, the computer will automatically flash the Error light indicator on the control panel. The next instruction will be recognized only if it is a TRANSFER ON OVERFLOW (TOV) instruction, in which case the Error light indicator will be turned off. If any other instruction follows, the computer will halt and the Error light will continue to flash.

#### Rules for the Sign in Arithmetic Operations.

The rules for the sign of an arithmetic operation are the same as those of algebra. A negative zero is never generated by an FADAC arithmetic operation. However, the number 20000000000, which is not interpreted as a negative zero, may be input to FADAC and operated upon.

$\begin{array}{c} ADD \\ 00 \ ADD \ M \\ \hline \end{array} \quad \text{Word Time} = 1 \end{array}$

The algebraic sum of the contents of M and the contents of the A-register replace the contents of the A-register. Overflow can occur. A flag bit of 1 will cause (M) to be put into the N-register. A flag bit of 0 leaves the contents of the N-register unaltered.

SUBTRACT 02 SUB M Word Time = 1

The word in location M is subtracted from the A-register, and the difference replaces the contents of the A-register. Overflow can occur. A flag bit of 1

will cause the contents of M to be put into the Nregister. A flag bit of 0 leaves the contents of the Nregister unaltered.

#### MULTIPLY 20 MPY M Word Time = 22

The contents of the memory location M are multiplied by the contents of the A-register. The product appears in the A and L-registers unrounded. The most significant 31 bits and the sign are in the A-register. The least significant 31 bits are in the L-register. Because the number in the L-register is the least significant part of the total product, it does not have a sign associated with it. The most significant bit of the 31 bits of the least significant part of the product appears in the sign position of the L-register. The least significant bit position of the L-register always contains a 0 after multiplication, which is not considered part of the product. Note that the contents of location M are stored in the N-register. The flag bit is ignored during execution of this instruction.

#### DIVIDE 30 DIV M Word Time = 22

The 63 bit number appearing in the A and Lregisters is divided by (M). The most significant bit of the portion of the dividend that appears in the Lregister is in the sign position. The least significant bit of the L-register is not considered part of the dividend and must be a zero. The quotient in the Aregister will be affected if the value of this bit is 1.

If the flag bit is 0, the A-register will contain a rounded quotient and the L-register will cortain a remainder whose value has no relationship to the rounded quotient.

If the flag bit is 1, the A-register will contain an unrounded quotient and the L-register will contain a remainder with the same sign as the divisor. This remainder satisfies the relation:

$(Divisor \times Quotient) + Remainder = Dividend$

The contents of location M are put into the Nregister. Overflow can occur if the absolute value of the contents of the A-register is equal to or greater than the value of the contents of location M.

CLEAR AND ADD 24 CLA M Word Time = 1

The contents of location M are transferred to the A-register. Location M can refer to any addressable location. A flag bit of 1 transfers the previous contents of the A-register into the L-register. If the flag bit is 0, the contents of the L-register remain unaltered.

CLEAR AND SUBSTRACT 26 CLS M Word Time = 1

The negative of the contents of memory location M (in 2's complement form), is transferred to the Aregister. Location M can refer to any addressable location. A flag bit of 1 transfers the previous contents of the A-register into the L-register. If the flag bit is 0, the contents of the L-register remain unaltered.

#### 2.2.2 STORE & LOAD

Most store instructions include a capability to write the specified information into the N-register as into location M. If M is in Hot memory, the indicated change occurs in M and in the special register. However, if M is in Cold memory, only the N-register is changed. Each instruction description includes information as to whether a flag is required to cause storage into N. Note particularly the special precautions required when an STO or STP command is executed.

STORE A-REGISTER 50 STA M Word Time = 1

The contents of the A-register are stored in location M. Location M can refer to any addressable location. If the flag bit is 1, the word in A will be put in the N-register as well as into location M.

NOTE: If M refers to registers A, L or N:

With flag bit = 0, no storage takes place into M or N. With flag bit = 1, no storage takes place into M, but the contents of A are sent to N. STORE L 52 STL M Word Time = 1

The contents of the L-register are stored in location M. M may be any addressable location. If the flag bit is one, the word in L will be put into the N-register as well as into location M.

NOTE: If M refers to registers A, L or N:

With flag bit = 0, no storage takes place into M or N.

With flag bit = 1, no storage takes place into M, but the contents of L are sent to N.

STORE N-REGISTER 40 STN M Word Time = 1

The contents of the N-register are stored in location M. M may be any addressable location. However, if M refers to the A, L or N-register, no storage takes place, and the instruction serves only as a one-word time delay. The flag bit is ignored in this instruction.

STORE D 42 STD M Word Time = 1

The contents of sector i of the 2-word D-register are stored in location M, where i = 00 if M is even, and i = 01 if M is odd. M may be any addressable location. If the flag bit is one, the contents of D.i will be stored in the N-register as well as in M. NOTE: If M refers to registers A, L, or N:

With flag bit = 0, no storage takes place into M or N  $\,$

With flag bit = 1, no storage takes place into M, but the contents of the D-loop under read head at time of execution are stored in N.

STORE OPERAND ADDRESS 70 STO M Word Time = 1 if M refers to R or Q. Word Time = 3 if M refers to any other loca-

tion.

(a) The operand address of the word in location M is replaced by the operand address of the word in the A-register (bits 19 through 31). The modified contents of M are stored in the N-register. M may be any addressable location.

(b) If M is located in Cold memory and no external input device, such as the SDR, is connected, the contents of M are always unchanged. However, the Nregister is modified to contain the instruction in M, with its operand address replaced by the operand address currently in the A-register.

(c) If M is located in Memory II or II, and this memory is Hot, the sign bit of the L-register will determine whether (M) is modified by an STO or an STP instruction. If L is negative, no modification of (M) will occur, although the modified instruction will be stored in N. If L is positive, both (M) and (N) will be modified by execution of an STO or STP instruction. Therefore, to assure the modification of (M) in a Hot Memory II or Memory III location, the STO or STP could be preceded by a ZEL (Zero L) instruction. If M is in Memory I, the sign bit in L has no effect on the execution of STO or STP commands.

(d) NOTE: If M refers to the A-register, A remains unchanged and the contents of A are stored in the N-register. If M refers to the L-register, the contents of L remain unchanged. However, the N-register is modified to contain the instruction in L, with its operand address (bits 19 thru 31) replaced by the operand address currently in A. If M refers to the N-register, bits 19 thru 31 in A are stored in bits 19 thru 31 of N. The remaining portion of the N-register is unchanged. The flag bit is ignored in this instruction.

STORE PROGRAM ADDRESS 60 STP M Word Time = 1 if M refers to R or Q. Word Time = 3 if M refers to any other location.

(a) The next instruction address of the word in location M is replaced by the next instruction address of the word in the A-register (bit positions 1 thru 13). The modified contents of M are stored in the N-register. M may refer to any addressable location.

(b) If M is located in Cold memory and the SDR is disconnected, the contents of M remain unchanged. However, the N-register is modified to contain the instruction in M, with its NI address replaced by the NI address currently in the A-register (bits 1 thru 13).

(c) See Part (c) under Store Operand Address. The contents of the L-register have the same affect on an STP instruction as on an STO.

(d) If M refers to the A-register, A remains unchanged and the contents of A are stored in N. If M refers to the L-register, L remains unchanged. However, the Nregister is modified to contain the instruction in L, with its NI address replaced by the NI address currently in the A-register (bits 1 thru 13). If M refers to the N-register bits 1 thru 13 are stored in bits 1 thru 13 of N. The remaining portion of N remains unchanged. The flag bit is ignored in this instruction.

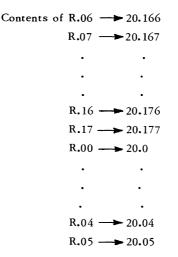

# STORE R 62 STR M Word Time = 22

The contents of the 20 words of the R-loop are transferred through the D-register to memory starting at location M. The flag bit is ignored. If M refers to a main memory location, each word transferred will be taken from that sector of the R-loop whose address agrees with the last four bits of the sector address into which the word is to be stored. For example, when an STR instruction with an operand sector address of 074 is executed, the first word stored will be taken from sector 14 of the R-loop. Successive words will be taken from sectors 15, 16, 17, 0, 1...13 of the R-loop and stored in sectors 075, 076, 077, 100, 101...113 of the main memory channel specified in M. The D-loop will contain the last two words transferred; that is, D.0 will hold the contents of the last even numbered location transferred, and D.1 the contents of the last odd numbered location transferred. In the example given above, D.0 will hold the new contents of sector 112, and D.1 will hold the new contents of sector 113.

If M refers to a main memory channel, and its sector is greater than 160, the word transmitted from R.0 will be stored in sector zero of the channel in which M is located.

Example: Given STR 20.166. Resultant storage will be:

If M refers to a location in the Q or R-loop, the contents of R will go into Q or R, displaced by two sectors. For example, if a STR instruction is given which has an operand address of Q-3, sectors 3, 4, 5, 6...2 of R will be transferred to sectors 5, 6, 7, 0...4 of Q. At the end of the execution, D.0 will contain the new contents Q.4, and D.1 the new contents of Q.3. Similarly, if a STR instruction is given which has an operand address of R.6, sectors 6, 7, 10, 11...5 of R will be transferred to sectors 10, 11, 12, 13...7 of R. At the end of the execution, D.0 and D.1 will hold the new contents of sectors R.6 and R.7 respectively.

If M refers to the D-loop, the first word transferred appears in the sector of D specified and the last word transferred in the remaining sector of D. If the operand address is D.0, the first word with an even numbered address to pass under the read head of the R-loop after the Instruction Read phase will be the first word transferred. For example, if channel 00, sector 55 contains the instruction STR D.0, the word in R.16 will appear in D.0 and the word in R.15 will appear in D.1 at the end of the execution phase. If the instruction were STR D.1, the contents of R.17 and R.16 would appear in D.1 and D.0 respectively.

LOAD Q-REGISTER72 LDQ MWord Time = 20LOAD R-REGISTER72 LDR\* MWord Time = 20

The contents of 20 consecutive words of memory starting with location M are transferred to the specified rapid access loop. The specific loop, i.e., R or Q, is determined by the flag bit. A flag bit of 1 indicates the R-loop, while a flag bit of 0 indicates the Q-loop.

Each word transferred to Q or R is stored in the sector corresponding to the last four bits of the sector from which the word was transferred. For example, when an LDQ instruction with an operand sector of 074 is executed, the first word transferred will go into sector 14 of the Q-loop. Successive words will go into sectors 15, 16, 17, 0, 1, 2, ...13. If M refers to a main memory channel, and the sector is greater than 160, the word transmitted from sector 177 will be followed by the word from sector 0 of the same channel.

The A, L, and N-registers and the D-loop are unaffected by the execution of these commands.

If M = A, L, or N, the contents of the specified register will replace the contents of all 20 sectors of the Q or R-loop. Similarly, if M = D.i, the contents of D.0 will go into all the even numbered sectors of the Q or R-loop, while the contents of D.1 will replace the contents of all the odd numbered sectors. If the operand of a LDR\* command is in the R-loop, or if the operand of a LDQ command is in the Q-loop, the contents of the referenced loop remain unchanged.

#### 2.2.3 TRANSFER

In each of the following instructions, a flag bit of 1 will cause the transfer instruction to be placed in the N-register if and only if the transfer to M is executed. A flag bit of 0 will leave the contents of the N-register unchanged.

# $\frac{\text{TRANSFER UNCONDITIONALLY}}{14 \text{ TRA M Word Time} = 1}$

Control is unconditionally transferred to the instruction found in location M. The NI is ignored in this instruction, except when the NI contains a 146 channel address. (See Section 3.10.)

TRANSFER ON PLUS 10 TPL M Word Time = 1

If the contents of the A-register are positive( $\geq$  zero), control is transferred to the instruction in location M; if not, control is transferred to the address specified in the NI portion of the transfer command.

TRANSFER ON ZERO 12 TZE M Word Time = 1

If the contents of the A-register equal zero, control is transferred to location M; if not, control is transferred to the address specified in the NI portion of the transfer command.

TRANSFER ON OVERFLOW 16 TOV M Word Time = 1

If overflow occurs, control is transferred to the instruction in location M. If not, control is transferred to the address specified in the NI portion of the transfer command. In either case, the Error light indicator on the control panel will not flash on execution of this command.

Note that if an instruction which results in overflow is not immediately followed by a TOV command, the Error light will flash, and all computation will halt.

#### 2.2.4 SHIFT & CYCLE

General.

In the following instructions the operand sector address portion of the instruction, designated by S, does not refer to a location in memory but to the number of binary positions the word in the A-register, or in the A and L-registers, is to be shifted or cycled. All shift and cycle op codes are made up of four octal digits, with the 2 least significant digits in the positions normally occupied by the channel portion of the operand address.

#### Overflow.

A change in the value of the sign bit in the Aregister is normally recognized as overflow. However, overflow caused by a right cycle command is always ignored by FADAC, and the next program instruction is executed. Overflow can never occur with a right shift command. The flag bit of all right shift and right cvcle instructions MUST be 0. Overflow caused by a left shift or cycle command will be ignored if the instruction flag bit is 0. However, a flag bit of 1 with a left shift or cycle command will cause the computer to check for overflow. If overflow occurs, the Error light indicator on the control panel will flash. The next instruction will be executed only if it is a TRANS-FER ON OVERFLOW (TOV) command, in which case the Error indicator will stop flashing. If any other instruction follows, the computer will halt, and the

Error indicator light will continue to flash.

CAUTION: The contents of the shifted register(s) are not predictable when overflow occurs since the overflow condition may terminate the command before it is completed.

Execution Time.

The execution time for all shift and cycle instructions is given by the following relationship:

Convert S to decimal S<sup>1</sup>. The number of word times equals the integer portion only of

$$1/2 (K + S' + 1)$$

where K = 0 for odd S<sup>I</sup> and where K = 1 for zero and even S<sup>I</sup>. This equation was derived from the following relationship:

Word Time =  $1/2 (1 + S' + COS^2 TT S'/2)$

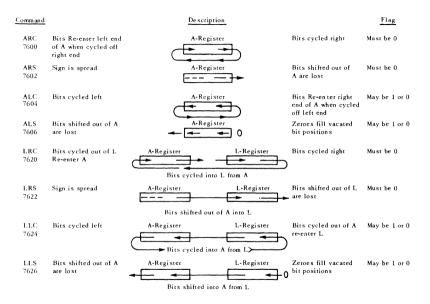

All shift and cycle commands are summarized in Fig. 2.4.

## Accumulator Right Cycle 7600 ARC S

The contents of the A-register are shifted right the number of binary positions designated by S. The bits shifted off the right end of the A-register enter the left end of the A-register, through the sign position, in the same sequence.

## Accumulator Right Shift 7602 ARS S

On execution of this command, the contents of the A-register are shifted right the number of binary places designated by S. The sign is spread in the left-hand bits; while bits shifted beyond the right-hand limits of the A-register are lost.

Figure 2.4. Shift and Cycle Command Summary

The contents of the A-register are shifted left through the sign bit position the number of binary places

indicated by S. The bits shifted off the left end of the A-register enter the right end, in the same sequence.

### Accumulator Left Shift 7606 ALS S

The contents of the A-register are shifted left through the sign bit the number of binary places indicated by S. Positions left vacant as the contents of the A-register are shifted are filled with zeros. Any bits shifted beyond the sign position are lost.

### Lona Right Cycle 7620 LRC S

The contents of the A and L-registers are shifted right the number of binary places designated by S. The bits shifted off the right end of the A-register are shifted into the L-register through its sign position. The bits shifted off the right end of the L-register are shifted into the left end of the A-register through its sign position.

### Long Right Shift

The contents of the A and L-registers are shifted right the number of binary places designated by S. The bits shifted off the right end of the A-register are shifted into the L-register through its sign bit position. The bits shifted off the right end of the L-register are lost. The sign of the A-register is spread.

## Long Left Cycle

The contents of the A and L-registers are shifted left the number of binary places indicated by S. The bits shifted left through the sign of the A-register are shifted into the right end of the L-register. Bits shifted through the sign position of the L-register are shifted into the right end of the A-register.

# Accumulator Left Cycle

2-21

7624 LLC S

## 7622 LRS S

The contents of the A and L-registers are shifted left the number of binary places designated by S. The bits shifted through the sign position of the L-register are shifted into the right end of the A-register. Bits shifted beyond the sign position of the A-register are lost. The bits of the L-register vacated in the shifting process are filled with zeros.

## 2.2.5 LOGIC AND SPECIAL INSTRUCTIONS

## General.

With the exception of the EXT, EQS and GES commands, all Logic and Special instructions are specified by a four digit op-code, with the two least significant digits in the positions normally occupied by the channel portion of the operand address. The sector portion of the operand address is ignored in these commands.

EXTRACT 34 EXT M Word Time = 1

The contents of the A-register are replaced by the logical AND of the contents of A and the contents of M. In other words, when both the bit in (M) and the corresponding bit in the A-register are 1, a one will appear in the same bit position of the A-register at the end of the execution. In all other cases, a zero will appear in that bit position of the A-register upon execution of this command. Location M can refer to any addressable location. The flag bit is ignored in this instruction.

TAKE ABSOLUTE VALUE 3770 ABS Word Time = 1

The contents of the A-register are replaced by their absolute value. If the contents are negative, they will be replaced by their corresponding positive value; while if the contents are positive they will remain unchanged. If the flag bit is zero, no further storage occurs. If the flag bit is one and the contents of A are negative, this negative value will be transferred to the L-register. If the flag bit is one and the contents of A are positive, L will remain unchanged. The operand sector is ignored in this command.

REPLACE A ON MINUS FROM L 3772 RML Word Time = 1

If the contents of the A-register are negative and the flag bit of this instruction is zero, the complement of the contents of the L-register is sent to A, and L is unchanged. If the contents of the A-register are negative and the instruction flag bit is one, the complement of the contents of L is sent to A, and the original contents of A are sent to L. If the contents of the A-register are positive, A and L are unchanged regardless of the value of the flag bit. The sign of the original contents of the L-register in no way affects the execution of this command.

REPLACE A ON MINUS FROM N 3774 RMN Word Time = 1

If the contents of the A-register are negative and the flag bit of this instruction is zero, the complement of the contents of the N-register is sent to A. The L and N-registers are unchanged. If the contents of the A-register are negative and the instruction flag bit is one, the complement of the contents of the N-register is sent to A; the original contents of A are sent to L; and N is unchanged. If the contents of the A-register are positive, A, L and N are unchanged. The sign of the original contents of the N-register in no way affects the execution of this command.

## EQUAL SEARCH 64 EQS M Word Time = i + 2(i = 0 to 176)

Starting with i = 0, the contents of the A-register

are compared with those in memory location (M + i), in bit positions indicated by a mask appearing in the L-register. This mask must have been stored previously in the L-register by the program. It directs which bits of the A-register and memory should be compared. Wherever a 1 appears in the L-register, the corresponding bits in the A-register and location (M + i) will be checked.

If in all the designated bit positions, the contents of the A-register are found to be equal to the contents of location (M + i), the contents of location (M + i + 1) replace the contents of the A-register, and control is transferred to the next instruction.

If the contents of the A-register in all the designated bit positions are not equal to the contents of location (M + i), then i is increased by one and the comparison is repeated. This comparison search continues until agreement has been reached, or until the contents of operand sector 176 have been compared. If no agreement is reached after comparison search through sector 176, then the contents of A remain unchanged, and control is transferred to the next instruction.

If a complete channel is to be searched, the starting operand sector should be 177. Then if agreement were reached, the first and last possible word that would be picked up would be in sectors 000 and 177 respectively. If the flag bit is a 1, and agreement is reached, the previous contents of the accumulator replace the contents of L. If agreement is not reached, the flag bit has no effect. The execution time is the number of sectors reached, i, plus 2.

## GREATER THAN 66 GES M Word Time = i + 2OR (i = 0 to 176) EQUAL SEARCH

The execution of this instruction is the same as EQS, except that the comparison is satisfied if the value of the bit positions of (M) which are compared is greater than or equal to the value of the corresponding bit positions of (A).

## HALT 3720 HLT Word Time = 1

Program computation is halted. The flag bit, operand sector and next instruction address are ignored in this command.

## ZERO-L-REGISTER 3762 ZEL Word Time = 1

The L-register is cleared to zero. The flag bit and operand sector are ignored in this instruction.

## INITIATE DISPLAY MODE 3764 IDM Word Time = 1

This command will cause the contents of the Dloop to be displayed, in BCD format, in the NIXIE tubes located on the control panels and will also activate the Battery display NIXIE. The Battery NIXIE is not part of the D-register, but is a wired-in display of the Battery button (A, B, C, D, or E) depressed on the matrix panel. Note that a battery button must be depressed when an IDM command is sensed, or no display will occur. Once activated, the NIXIE display will continue until a HALT DISPLAY MODE (HDM), or a READ or WRITE command is sensed. Computation can continue while in the display mode. The flag bit and operand sector are ignored in this command.

See Section 4.1 for a full description of the NIXIE display.

### HALT DISPLAY MODE 3766 HDM Word Time = 1

Visual display mode is halted. The flag bit and the operand sector address are ignored by this command. Successive IDM and HDM commands can be given at any time.

## INITIATE COMPUTE MODE 3726 ICM Word Time = 1

This command will turn on the Compute light located on the front panel of FADAC. If the Compute light is already on, the command will introduce a one word-time delay. It has no other effect on a program.

## HALT COMPUTE MODE 3724 HCM Word Time = 1

This command will turn off the Compute light located on the front panel of FADAC, but does NOT halt computation. It has no other effect on a program. After an HCM command is sensed, the Compute light can only be relit if:

(1) an ICM command is sensed; or

(2) FADAC is turned off, then turned on, and one of the eight control buttons is depressed.

## 2.2.6 DISCRETE INPUT/OUTPUT

### Input.

A single command, DIA, is available for a variety of input configurations to FADAC. These are described below:

## DISCRETE INPUT TO ACCUMULATOR 3640 DIA Word Time = 1

The DIA command places the following information into the A-register:

a. In bit position 0: A timing signal, with a period of 22 milliseconds, which is generated by an oscillator in FADAC. The signal is a square wave which remains at zero volts (0 to sign bit) for 11 milliseconds, and at -6 volts (1 to sign bit) for 11 milliseconds. The signal is provided primarily as a synchronization signal for output by bit to a standard two-wire teletypewriter, but may be used as a real-time clock in any application.

b. In bit position 1: Normally set to zero, this bit is set to one whenever any one of the 8 control buttons (Sample Matrix, Test, Set-up, Recall, Send, Compute, Trig, or Receive) is depressed; and remains at one only as long as pressure remains on the control button.

c. In bit positions 2 - 18: Up to 17 signals on lines connecting a single, or many, external devices to FADAC through Input Plug J - 17 and Output Plug J - 10. Note that the DIA command places information on specified pins of both plugs into the A-register simultaneously. (Figure 2.5 shows which pins on the I/O plugs are connected to each bit position.)

d. In bit positions 19 - 23: A 5 position switch is available to the programmer through the FADAC control panel buttons labelled A through E, which are located on the right hand side of the 8 x 8 matrix. With one of these buttons depressed, a DIA command will place its identifying code into bits 19 through 23 of the Aregister. (See figure 2.7.) (Note in the Cannon Program these buttons are referred to as the Battery Buttons. However, they are available for use in any application.)

e. In bit position 24: A 2 position switch is available to the programmer through the control panel buttons labelled (1) and (2) which are located immediately above the 5 position switch, buttons A to E. With Button (1) depressed, a DIA command will place a 1 in bit position 24 of the A-register; with Button (2) depressed, a 0 appears in bit position 24. (In the Cannon Program, these buttons are referred to as the Weapons Buttons.)

f. In bit positions 25 - 30: The 8 x 8 matrix on the FADAC control panel greatly extends the input

| BIT POSITION | F-LINE        | PIN DESIGNATION         |

|--------------|---------------|-------------------------|

| 2            | F-30-I        | m                       |

| 3            | F-29-I        | k                       |

| 4            | F-28-I        | J On Input Plug J - 17  |

| 5            | F-27-I        | i                       |

| 6            | F-26-I        | h                       |

| 7            | F-25-1        | g                       |

| 8            | F-24-1        | Г                       |

| 9            | F-23-I        | P                       |

| 10           | F-22-I        | p On Output Plug J - 10 |

| 11           | F-21-I        | n                       |

| 12           | F-20-I        | nı                      |

| 13           | F-19-I        | k                       |

| 14           | F <b>-</b> 18 | ММ                      |

| 15           | F-17          | LL                      |

| 16           | F-16          | KK On Input Plug J - 17 |

| 17           | F-15          | JJ                      |

| 18           | F-14          | НН                      |

Figure 2.5. DIA Command Pin and Line Connections -Bits 2 Thru 18

| COL. |    | IDENTIFYING CODES |    |    |    |    |    |    |

|------|----|-------------------|----|----|----|----|----|----|

| Н    | 70 | 71                | 72 | 73 | 74 | 75 | 76 | 77 |

| G    | 60 | 61                | 62 | 63 | 64 | 65 | 66 | 67 |

| F    | 50 | 51                | 52 | 53 | 54 | 55 | 56 | 57 |

| Е    | 40 | 41                | 42 | 43 | 44 | 45 | 46 | 47 |

| D    | 30 | 31                | 32 | 33 | 34 | 35 | 36 | 37 |

| С    | 20 | 21                | 22 | 23 | 24 | 25 | 26 | 27 |

| В    | 10 | 11                | 12 | 13 | 14 | 15 | 16 | 17 |

| Α    | 00 | 01                | 02 | 03 | 04 | 05 | 06 | 07 |

| RO₩→ | 1  | 2                 | 3  | 4  | 5  | 6  | 7  | 8  |

Figure 2.6. Identifying Codes for Each FADAC Matrix Position

Figure 2.7. DIA COMMAND - Binary Information

f. In bit positions 25-30 (Continued)

capabilities of FADAC by providing a 64 position switch to the programmer. Each position may be programmed as a pointer to a separate element of a given complex program. With a row (labelled A, B, ...., or H) and column (labelled 1, 2, ...., or 8) button depressed, a DIA command will place the identifying code of the combination in bits 25 - 30 of the A-register. Figure 2.6 shows the 2-digit octal identifying code for each combination. g. Bit 31: If only one button is depressed on the  $8 \times 8$  matrix (a row or a column, but not both) a 0 will appear in bit position 31; if both are depressed, a 1 will fill bit position 31.

h. Figure 2-7. summarizes the information sent to the A-register by a DIA command.

The following example illustrates a use of the DIA command:

## Example

## The Problem.

Code an input routine for Matrix Position A - 1 through A -5; test if proper row and column button has been depressed; if so, transfer to one of 5 subroutines; if not, cause the No Solution Light to flicker, and halt. Assume that subroutines 1 through 5 begin in locations 10.00, 12.00, 14.00, 16.00 and 20.00, respectively, and that a transfer table has been stored which has the following octal format:

Explanation of the Transfer Table Format:

Digit 1: Set to 2 to indicate that a match has been found, and a control word picked up from the transfer table (i.e. - the word in A is negative).

Digit 2 and 3: Always 0

Digit 4 and 5: Set to 14, the TRA op code.

Digit 6 through 9(XXXX): Entrance location of each subroutine 1 through 5.

Digit 10 and 11 (YY): Matrix Codes 00 through 04 (A-1 through A-5).

## TRANSFER TABLE

| Location | Contents    |

|----------|-------------|

| 0.172    | 0000000000  |

| 0.173    | 20014100001 |

| 0.174    | 20014120002 |

| 0.175    | 20014140003 |

| 0.176    | 20014160004 |

| 0.177    | 20014200000 |

Assume that when each selected subroutine has been executed, control is to return to the main program which starts at  $L_0$  2.100 (00300).

| L <sub>0</sub> | N <sub>1</sub> | Op Code | Operand | Explanation                                                                                                      |

|----------------|----------------|---------|---------|------------------------------------------------------------------------------------------------------------------|

| 0.0            | 00201          | 36      | 4000    | When sample matrix<br>button is depressed,<br>the program begins<br>by executing DIA<br>command (3640).          |

| 2.1            | 00202          | 76      | 0001    | ARC 1: To place bit<br>31 in signposition.                                                                       |

| 2.2            | 00203          | 10      | 0403    | TPL: if (+) go to Er-<br>ror Routine; if (-)<br>continue.                                                        |

| 2.3            | 00204          | 34      | 0604    | EXT: Matrix code<br>now in bit positions<br>26 to 31 in A-<br>register. L <sub>0</sub> 604<br>contains the Mask. |

INSTRUCTIONS

|        |        | NSIRUCI |         |                                                                                                                               |

|--------|--------|---------|---------|-------------------------------------------------------------------------------------------------------------------------------|

| L<br>0 | N<br>1 | Op Code | Operand | Explanation                                                                                                                   |

| 2.4    | 20205  | 24      | 0604    | CLA*: Matrix code<br>to L-register, Mask<br>to A-register.                                                                    |

| 2.5    | 20206  | 25      | 7200    | CLA*: Matrix code<br>to A-register, Mask<br>to L-register.                                                                    |

| 2.6    | 00207  | 64      | 0172    | EQS: Search table<br>stored in 0.172<br>through 0.177.                                                                        |

| 2.7    | 00210  | 10      | 0403    | TPL: If +, wrong<br>combo set in Matrix,<br>go to error routine;<br>if -, A-register now<br>contains transfer<br>instruction. |

| 2.10   | 00213  | 76      | 0206    | ARS 6: Position<br>transfer instruction<br>properly in A.                                                                     |

| 2.13   | 20300  | 15      | 7000    | TRA* A and return<br>to Main Program.                                                                                         |

| 4.3    | 00404  | 37      | 1600    | NSL-Error Routine -<br>Wrong matrix posi-<br>tion is set.                                                                     |

| 4.4    | 00000  | 37      | 2000    | HLT - Halt, correct<br>and start again.                                                                                       |

| 6.4    | 00000  | 00      | 0077    | Mask for EXT and<br>EQS command                                                                                               |

**INSTRUCTIONS (Continued)**

The DIA command may also be used to input any 2 to 16 bit code which is foreign to FADAC. This is accomplished by connecting up to 17 of the J10 and

J17 lines associated with the DIA command to any input device which generates the desired code. A timing signal generated by the external device must be connected to one of the 17 bits positions available. Duration of the timing signal must be long enough to allow input of each new character, and short enough to assure that each new character is sensed only once per input. With the period of the timing signal known, a program can be written to sample for this signal by a DIA, EXT, and TEST. When the timing signal is thus detected. the new code can be input by a second DIA command followed by an EXT (extract the number of bits which define a character), STA, and a delay designed to inhibit reinitiation of a loop back to test for the timing signal until the next character is available for input. An example of a code foreign to FADAC is USASCII, an 8 - bit code which can be input only in the manner described.

## Discrete Output:

The eight discrete output commands set 3 flipflops, OP1, OP2, and OP3, to any one of eight possible combinations. Each combination, in turn, either places a -6 volt signal on a given output line; or causes the No Solution Light (NSL) on the FADAC control panel to blink; or turns off the NSL or the signal on any output line (DOF). A description of each discrete output command is summarized in Figure 2.8.

Note that each Discrete Output command requires a four-digit operation code. The operand sector address is ignored in the execution of these commands. Also, note that the setting of the Discrete Output control flip-flops remains fixed until a new Discrete Output command is sensed. When FADAC is turned on, the output flip-flops are set to all zeros (effectively, a DOF command is executed).

| Command<br>Mnemonic | Octal<br>Op-Code | OP-Flip-Flop<br>Setting<br>(in Binary) |          | Octal OP-Flip-Flop which a -6<br>Setting signal appe<br>(in Binary) when the com |           | OPL Line on<br>which a -6 volt<br>signal appears<br>when the command<br>is executed: | Pin to which<br>given OPL<br>line is con-<br>nected on<br>specified<br>I/O Plug: | Function<br>of<br>Command |

|---------------------|------------------|----------------------------------------|----------|----------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------|

| DOF                 | 3700             | Op 3<br>0                              | Op2<br>0 | Op1<br>0                                                                         | None (All | None                                                                                 | Turns off the<br>NSL or Sets<br>all OPL lines<br>to Zero                         |                           |

| ODI                 | 3702             | 1                                      | 1        | 1                                                                                | OPL - 1   | X of J-10                                                                            | Sets OPL-1<br>to one                                                             |                           |

| OD2                 | 3704             | 0                                      | 1        | 0                                                                                | OPL - 2   | Y of J-10                                                                            | Sets OPL-2                                                                       |                           |

| OD3                 | 3706             | 0                                      | 1        | 1                                                                                | OPL - 3   | Z of J-10                                                                            | Sets OPL-3                                                                       |                           |

| IDI                 | 3710             | 1                                      | 0        | 0                                                                                | OPL - 4   | a of J-17                                                                            | Sets OPL-4                                                                       |                           |

| ID2                 | 3712             | 1                                      | 0        | 1                                                                                | OPL - 5   | <b>b</b> of J-17                                                                     | Sets OPL+5<br>to one                                                             |                           |

| ID 3                | 3714             | 1                                      | 1        | 0                                                                                | OPL - 6   | <del>c</del> of J-17                                                                 | Sets OPL-6                                                                       |                           |

| NSL.                | 37 16            | 1                                      | 1        | 1                                                                                | None      | None                                                                                 | Causes No<br>Solution Light<br>to blink                                          |                           |

## Figure 2.8. Discrete Output Command Summary

The function of the OD and ID commands is to to energize a given pin on the input or output plug, or de-energize all OPL line-connected pins on these plugs. They may be used to control external equipment by the presence or absence of -6 volts on a given line.

## 2.2.7 PARALLEL INPUT/OUTPUT

## Introduction.

The parallel I/O commands cause FADAC to read information input through the keyboard, mechanical reader, magnetic tape, or any external device; or to write information out to another FADAC or to any of several external devices. The command structure allows the programmer to designate the I/O device; the kind of block (word or character); the block size; the I/O code (octal, BCD, or alpha-numeric); and, in all numeric WRITE commands, the code level (either 5-level Teletype (TT), or 8-level Fieldata (FD)). During input, the level is designated by the setting of the SDR (or SDR simulator) TT/FD switch. Parallel I/O commands are so named since each character enters FADAC on 5 (for TT) or 8 (for FD) information lines, (designated "I" lines) in parallel; and each character is output from FADAC on 5 or 8 data lines (designated "D" lines) in parallel. Input through the Mechanical Reader on the FADAC control panel is specified by the READ TAPE commands. Input through the MLU is specified by the READ EXTERNAL DEVICE commands. The flow of information through the special registers during I/O is a function of the particular I/O command executed, and is described in the following sections. In general, it is recommended that the contents of all special registers be saved prior to execution of any I/O command if they are of any significance in the balance of a given program. Note that the number of word times required to execute a parallel I/O command cannot be fully predicted.

The I/O Command Format:

Figure 2.9 illustrates the I/O command format. The flag bit is set to 0 to designate I/O by character, or to 1 to designate I/O by word. The value of the flag is added to the most significant digit of the NI address to form the first octal digit of the command word. The operation code occupies the 6th, 7th, 8th and 9th octal digits of the word. The block size is in digits 8, 9, 10 and 11. Thus, digits 8 and 9 are the sum of the two least significant digits of the operation code and the two most significant digits of the block size. The block size is designated as one less than the actual

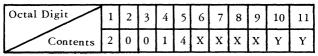

|                |    |       |      |       |    | - | DP-C | ode and | 4    |        |

|----------------|----|-------|------|-------|----|---|------|---------|------|--------|

| Octal<br>Digit | 1  | 2     | 3    | 4     | 51 | 6 | 7    | 1 8     | 9    | 10 11  |

| Meaning        | ۶I | ag an | d NI | Addre | ss |   |      | -       | Bloc | k size |

| Figure | 2.9. | I/0 | Command | Format |

|--------|------|-----|---------|--------|

|--------|------|-----|---------|--------|