# **INSIDE THE**

# **BUTTERFLY PLUS**

·

October 28, 1987

## Copyright © 1987 BBN Advanced Computers Inc. ALL RIGHTS RESERVED

### **RELEASE LEVEL**

This manual conforms to the Beta Test version of the Butterfly Plus Parallel Processor released October, 1987, and Version 4.0 of the Chrysalis operating system.

#### NOTICE

BBN Advanced Computers Inc. (BBNACI) has prepared this manual for use by BBN customers, personnel, and licensees. The information contained herein is the property of BBNACI. The contents of this manual may not be reproduced in whole or in part, nor used other than as allowed in the terms and conditions of sale of this manual.

The information in this manual is subject to change without notice, and should not be construed as a commitment by BBNACI. BBNACI assumes no responsibility for any errors that appear in this document.

Butterfly and Chrysalis are trademarks of BBN Advanced Computers Inc.

UNIX is a trademark of Bell Laboratories, Inc.

4.2BSD is a trademark of the Trustees of the University of California.

Multibus is a trademark of Intel Inc.

VMEbus is a trademark of Motorola Semiconductor Products, Inc.

Scheme and The X Window System are trademarks of Massachusetts Institute of Technology.

Ethernet is a trademark of Xerox Corp.

VAX is a trademark of Digital Equipment Corp.

Lisp Machine is a trademark of Symbolics, Inc.

# Preface

This manual describes the theory of operation of the Butterfly Plus system. It provides detailed descriptions of the important components of the system, including the Processor Node, Butterfly Switch, Multibus Adapter, and VMEbus Adapter circuit cards, as well as an introduction to the overall design of the system. The manual also contains an introductory Chrysalis programming chapter to allow the reader a glimpse of the Butterfly Plus programming environment. This manual assumes that the reader is an engineer or programmer, sufficiently knowledgeable in the area of parallel processors. .

• • • •

------

.

# Contents

# Chapter 1

# **Butterfly Plus Overview**

| Architectural Features            | 1-2  |

|-----------------------------------|------|

| System Components                 | 1-3  |

| Butterfly Plus Card Cage          | 1-6  |

| Multibus Card Cage                | 1-7  |

| Processor Node                    | 1-7  |

| Main Memory                       | 1-9  |

| Switch Card                       | 1-11 |

| Clock Card                        | 1-12 |

| Input/Output Capabilities         | 1-13 |

| Butterfly Plus I/O Link           | 1-14 |

| Multibus Adapter Card             | 1-14 |

| Multibus RAMboot Card             | 1-15 |

| Multibus Ethernet Controller Card | 1-16 |

| VME Interface                     | 1-16 |

| System Reset                      | 1-18 |

| Packaging                         | 1-19 |

# Chapter 2 The Processor Node

| Processing Elements        | 2-2 |

|----------------------------|-----|

| Processor                  | 2-3 |

| Floating Point Coprocessor | 2-3 |

| Memory Management Unit     | 2-4 |

| Address Decoding           | 2-5 |

| Processor Node Functions   | 2-5 |

| Interrupt System           | 2-7 |

| Processor Node Controller  | 2-7 |

| PNC Bitslice Processor                | 2-9  |

|---------------------------------------|------|

| Control Store and Microcode Sequencer | 2-10 |

| Microcoded Special Functions          | 2-10 |

| Microinterrupt Requirements           | 2-11 |

| Realtime Clock and Timer              | 2-12 |

| Switch Interface                      | 2-12 |

| Switch Receiver Micromachine          | 2-13 |

| Receiver Circuit Operation            | 2-14 |

| Switch Transmitter Micromachine       | 2-16 |

| Transmitter Circuit Operation         | 2-17 |

| Bootstrap EPROM                       | 2-20 |

| Diagnostic UART                       | 2-20 |

| USD Bootstrap Debugger                | 2-21 |

# Chapter 3 The Butterfly Plus Switch

| Alternative Switch Structures              | 3-6  |

|--------------------------------------------|------|

| Characteristics of a Butterfly Plus Switch | 3-10 |

| Butterfly Plus Switch Operation            | 3-11 |

| Handling Contention                        | 3-12 |

| Error Detection and Handling               | 3-13 |

| Block Transfers                            | 3-14 |

| Routing Decisions                          | 3-15 |

| Bidirectional Communication                | 3-17 |

| Conflict Resolution Strategies             | 3-19 |

| Parallel Data Paths                        | 3-22 |

| Alternate Paths and Extra Columns          | 3-22 |

| Speed Issues in Switch Design              | 3-25 |

| Dead States and Flow Control               | 3-26 |

| Switch Design Summary                      | 3-28 |

| Switch Node Implementation                 | 3-29 |

|                                            |      |

## Inside the Butterfly Plus

# Chapter 4 The Multibus Adapter

| Null Switch Interface                    | 4-3  |

|------------------------------------------|------|

| Watchdog Timer                           | 4-4  |

| Host and Console UARTs                   | 4-4  |

| EPROM                                    | 4-8  |

| Multibus Data Transfers                  | 4-10 |

| Multibus Access to Butterfly Plus Memory | 4-11 |

| Butterfly Plus Access to Multibus Data   | 4-12 |

| The Multibus Adapter Pipeline            | 4-14 |

| Pipelined Writes to the Butterfly Plus   | 4-15 |

| Pipelined Reads from the Butterfly Plus  | 4-15 |

| Multibus Data Transfer Timing            | 4-18 |

| Posting Events from the Multibus         | 4-18 |

| Servicing Multibus Interrupt Requests    | 4-20 |

| Programming the Interrupt Vector RAM     | 4-22 |

| Enabling Multibus Interrupts             | 4-24 |

| Multibus Memory Management               | 4-24 |

| LOCK Signal and Jumper Settings          | 4-26 |

| Installing the Multibus Adapter          | 4-28 |

| Multibus Adapter Register Summary        | 4-30 |

# Chapter 5

## The VME Interface

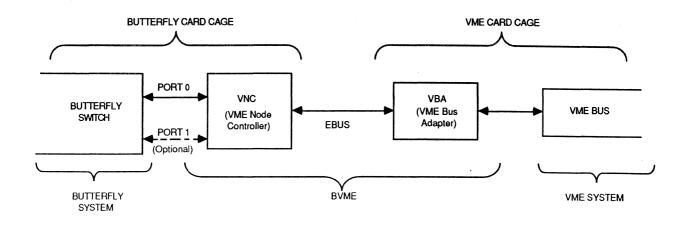

| Overview of the VME Interface  | -2 |

|--------------------------------|----|

| Performance                    | -2 |

|                                | -3 |

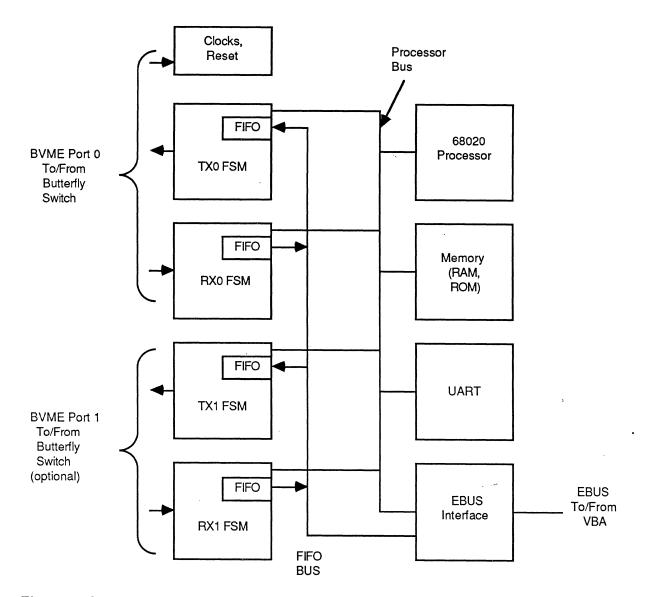

| VME Node Controller            | -4 |

|                                | -6 |

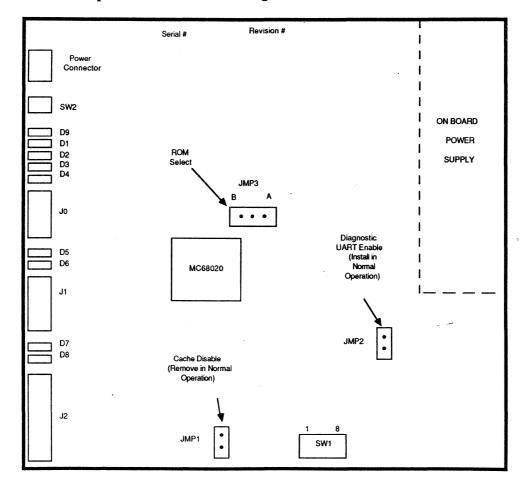

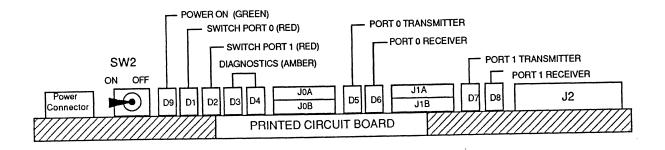

| Power Switch and Connectors    | -8 |

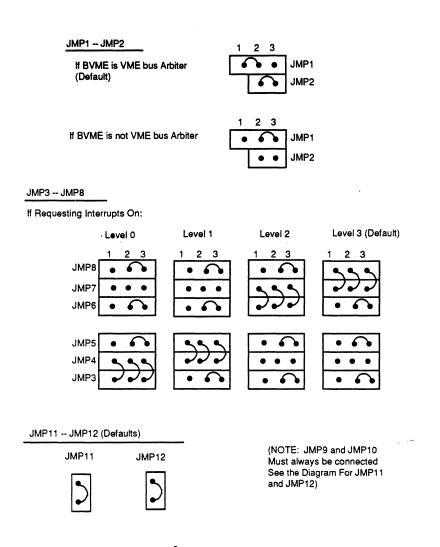

| Jumpers                        | -9 |

| DIP Switch Settings            | -9 |

| VME Bus Adapter                | 10 |

| VME Interface as Bus Requester | 13 |

| Configuration on the VMEbus    | 14 |

| VME Interface as Arbiter 5-1   | 14 |

| VME Address Space              | 14 |

| Address Translation            | 14 |

| Bank 0 Memory 5-1              | 15 |

.

| Control Registers                         | 5-16 |

|-------------------------------------------|------|

| VME Interrupt Requests                    | 5-21 |

| The VMEbus                                | 5-21 |

| VME Address Modifier                      | 5-21 |

| The VME Interface as a VMEbus Device      | 5-22 |

| Butterfly Plus and VMEbus Block Transfers | 5-24 |

| VME Data Alignment                        | 5-26 |

| Programming the VME Interface             | 5-27 |

| VME Node Controller and Port Numbering    | 5-29 |

| Subroutine Access Method                  | 5-30 |

| Mapping Method                            | 5-31 |

| Interrupts                                | 5-33 |

| Requesting VMEbus Interrupts              | 5-34 |

| Handling VMEbus Interrupts                | 5-34 |

| VME Interface Control Registers           | 5-35 |

| Parallel Transfers for Higher Bandwidth   | 5-35 |

| Library Routines and the Server Process   | 5-36 |

| Disk Data Transfer Example                | 5-36 |

| List of Calls                             | 5-37 |

|                                           |      |

## Chapter 6

# Programming the Butterfly Plus

| Server Functions<br>Kernel Functions<br>Multiprogramming Support<br>Multi-User Support<br>Memory Management | 6-3 |

|-------------------------------------------------------------------------------------------------------------|-----|

| Server Functions                                                                                            | 6-3 |

| Kernel Functions<br>Multiprogramming Support<br>Multi-User Support<br>Memory Management                     | 6-4 |

| Multi-User Support                                                                                          | 6-4 |

| Multi-User Support                                                                                          | 6-4 |

| Memory Management                                                                                           | 6-5 |

|                                                                                                             | 6-5 |

|                                                                                                             | 6-5 |

| Input/Output Support                                                                                        | 6-6 |

|                                                                                                             | 6-6 |

| Cooperating Sequential Processes                                                                            | 6-7 |

| The Uniform System                                                                                          | 6-7 |

| Programming With Butterfly Plus Scheme                                                                      | -15 |

| The RAMFile System                                                                                          | -18 |

.

## Appendix A PNC Microcode Functions

| Block Transfer Facility              | A-1  |

|--------------------------------------|------|

| Posting Events                       | A-3  |

| Dual Queue Functions                 | A-5  |

| Interrupt Control Register           | A-9  |

| Atomic Clear-then-Add                | A-11 |

| Local Bank 0 Memory Access           | A-12 |

| Other Kernel Functions               | A-12 |

| Enqueue, Dequeue, Push, and Remove   | A-13 |

| Clear-Then-XOR and Clear-Then-Add    | A-14 |

| The misc Register                    | A-14 |

| Interprocessor Interrupts and Resets | A-14 |

| PNC Status Register                  | A-15 |

| Processor Node Number                | A-16 |

| PNC Writable Control Store Control   | A-17 |

| Real-Time Clock                      | A-18 |

| Interval Timer                       | A-18 |

| Diagnostic UART                      | A-18 |

| Local Memory Control Registers       | A-19 |

|                                      |      |

## Appendix B

.

## Physical Memory Map

## Figures

| 1-1 | Butterfly Plus System Diagram            | 1-4  |

|-----|------------------------------------------|------|

| 1-2 | Processor Node                           | 1-8  |

| 1-3 | Switch Card                              | 1-12 |

| 1-4 | Multibus Adapter Card                    | 1-15 |

| 1-5 | VME Node Controller                      | 1-17 |

| 1-6 | VME Bus Adapter Card                     | 1-18 |

| 2-1 | Processor Node Block Diagram             | 2-1  |

| 2-2 | PNC Block Diagram                        | 2-8  |

| 2-3 | Switch Receiver Block Diagram            | 2-15 |

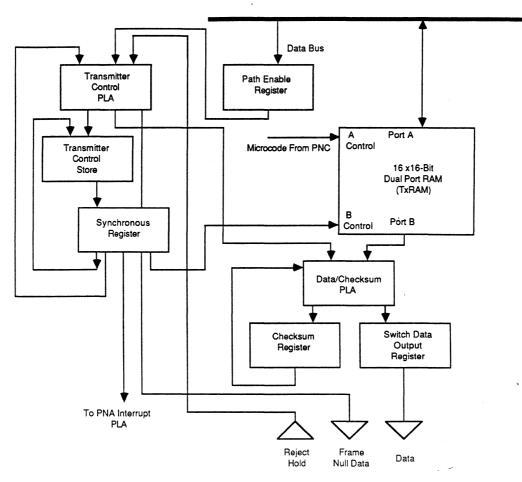

| 2-4 | Switch Transmitter Block Diagram         | 2-18 |

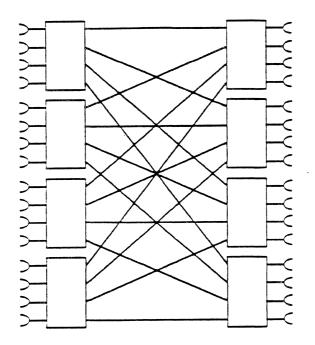

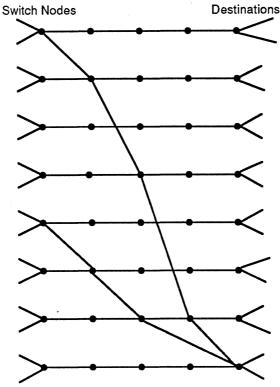

| 3-1 | 16-Port, 8-Node Switch                   | 3-2  |

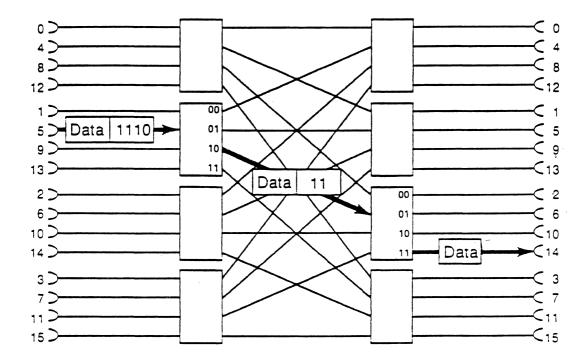

| 3-2 | A Packet Moves through an 8-Node Switch  | 3-3  |

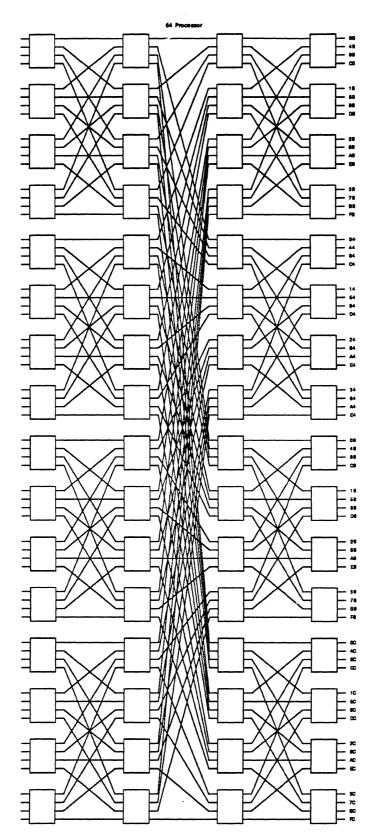

| 3-3 | Switch for a 64-Processor Butterfly Plus | 3-5  |

.

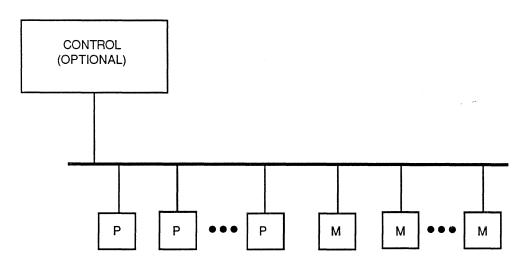

| 3-4  | Common Bus                                               | 3-6  |

|------|----------------------------------------------------------|------|

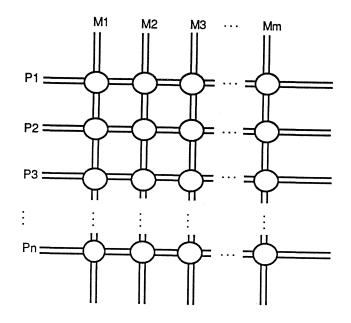

| 3-5  | Crossbar Switch                                          | 3-8  |

| 3-6  | Divided Crossbar Switch                                  | 3-9  |

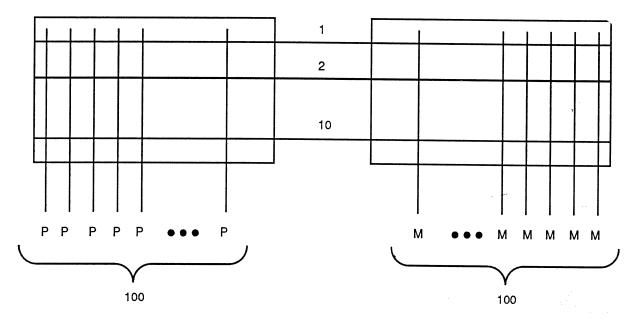

| 3-7  | Serial Decision Network                                  | 3-16 |

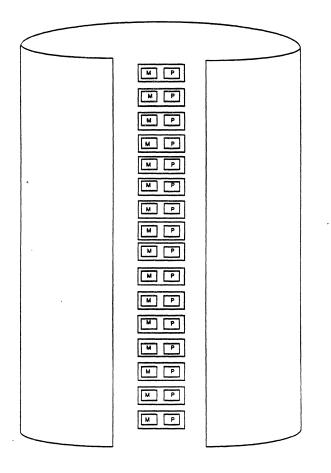

| 3-8  | Butterfly Plus Switch as a Cylinder                      | 3-18 |

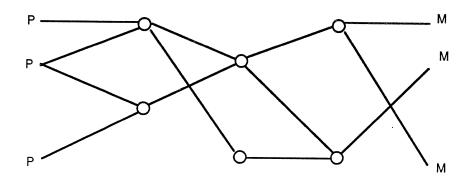

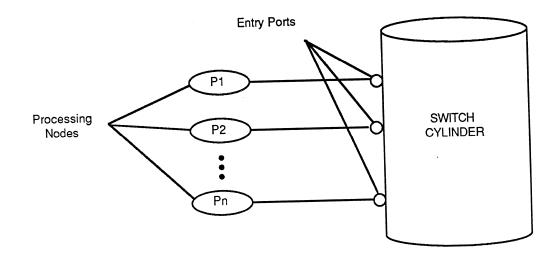

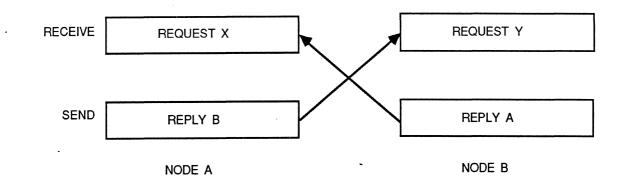

| 3-9  | Switch as a Channel between Processor Nodes              | 3-19 |

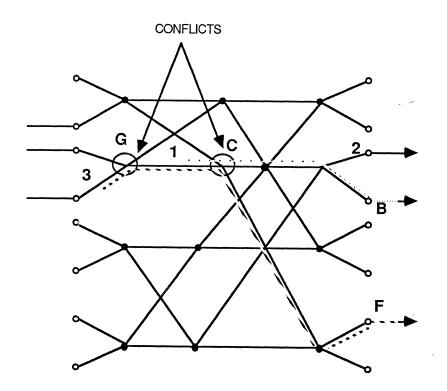

| 3-10 | Secondary Blockage in the Switch                         | 3-20 |

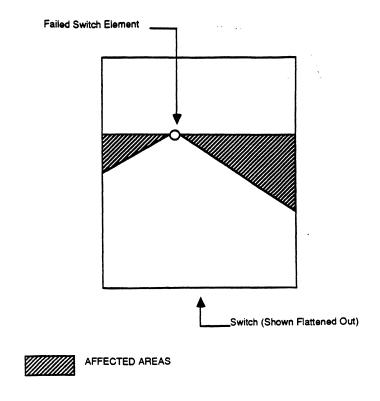

| 3-11 | Effects of Switch Failure                                | 3-23 |

| 3-12 | Alternate Paths through a Switch                         | 3-24 |

| 3-13 | Deadlock in a Switch                                     | 3-27 |

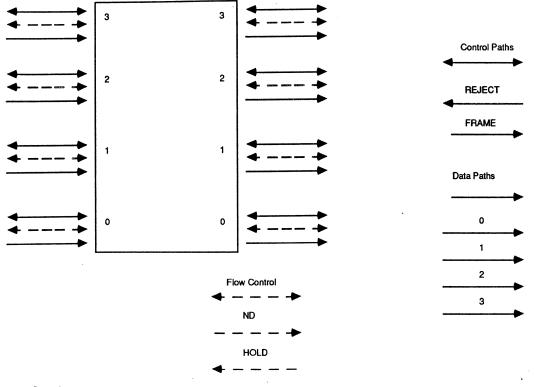

| 3-14 | Base 4 Switch Node I/O Diagram                           | 3-30 |

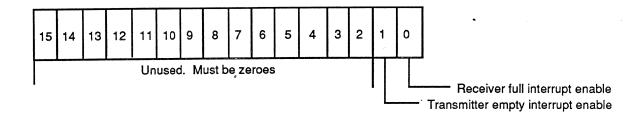

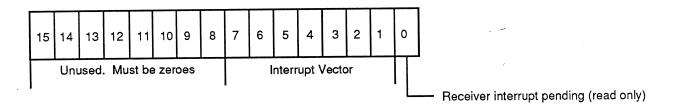

| 4-1  | UART Interrupt Control Register                          | 4-6  |

| 4-2  | UART Interrupt Vector Register                           | 4-6  |

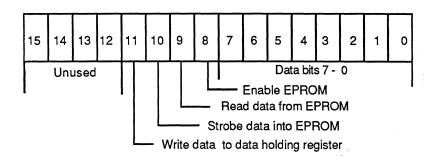

| 4-3  | EPROM Data and Control Register Bit Layout               | 4-9  |

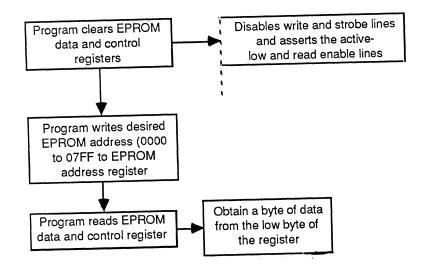

| 4-4  | Reading the EPROM                                        | 4-9  |

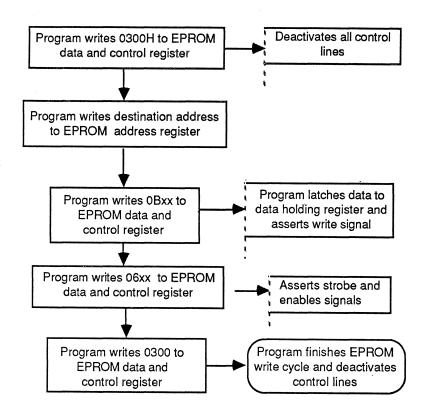

| 4-5  | Writing the EPROM                                        | 4-10 |

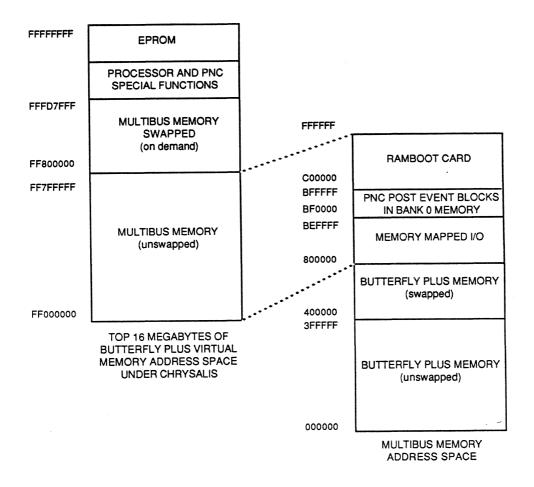

| 4-6  | Butterfly Plus and Multibus Address Maps under Chrysalis | 4-14 |

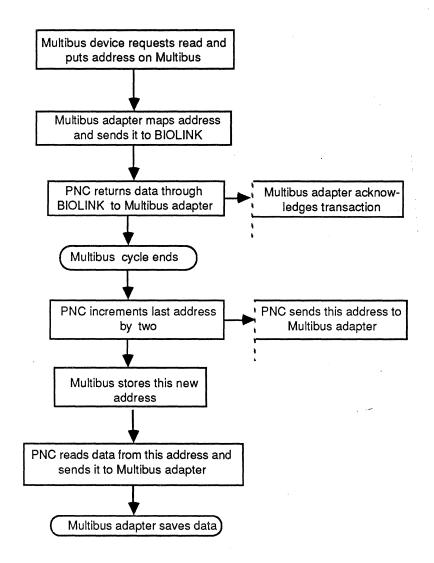

| 4-7  | Pipeline Empty Multibus Read                             | 4-16 |

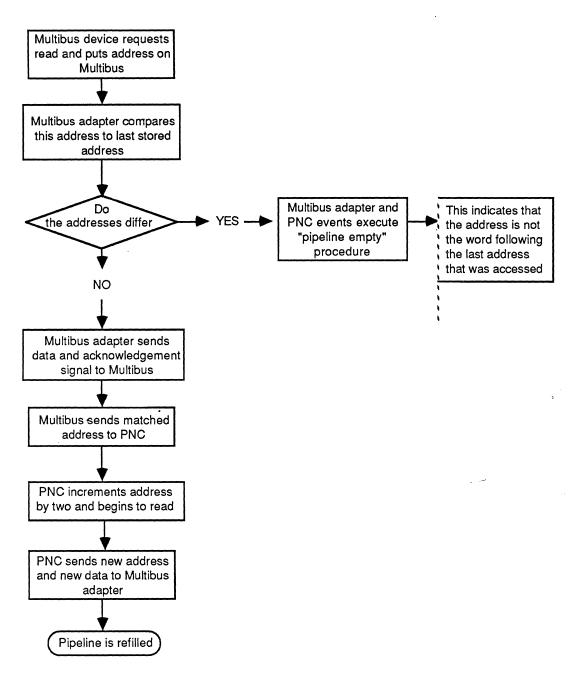

| 4-8  | Pipeline Full Multibus Read                              | 4-17 |

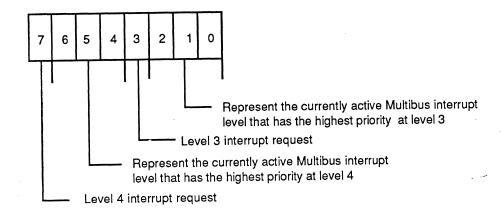

| 4-9  | Multibus Adapter Interrupt Status Register Bit Map       | 4-21 |

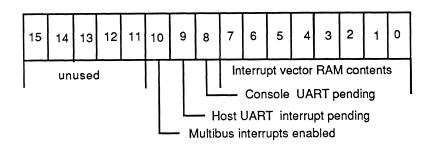

| 4-10 | Multibus Adapter Interrupt Vector RAM Bit Map            | 4-23 |

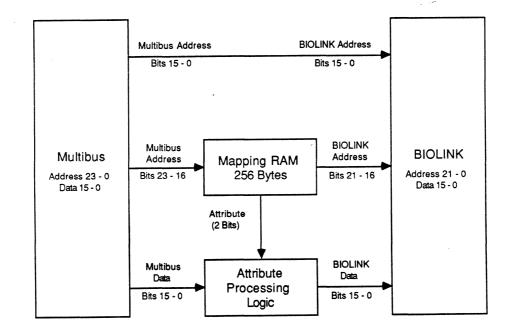

| 4-11 | Mapping Multibus Addresses onto the BIOLINK              | 4-25 |

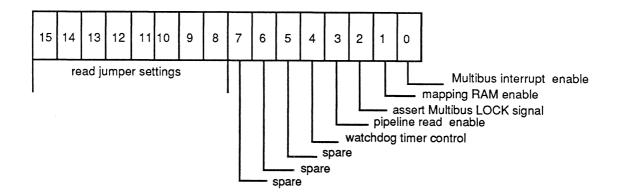

| 4-12 | Multibus Adapter Misc Register Bit Map                   | 4-27 |

| 5-1  | VME Interface Block Diagram                              | 5-4  |

| 5-2  | VME Node Controller Block Diagram                        | 5-5  |

| 5-3  | VME Node Controller Layout                               | 5-6  |

| 5-4  | VME Node Controller Front Edge                           | 5-7  |

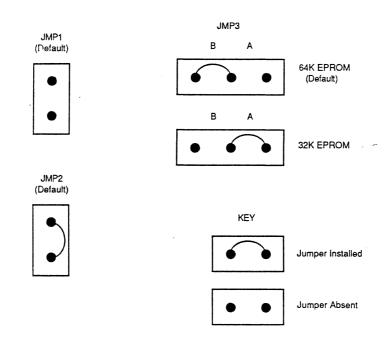

| 5-5  | VME Node Controller Jumper Positions                     | 5-9  |

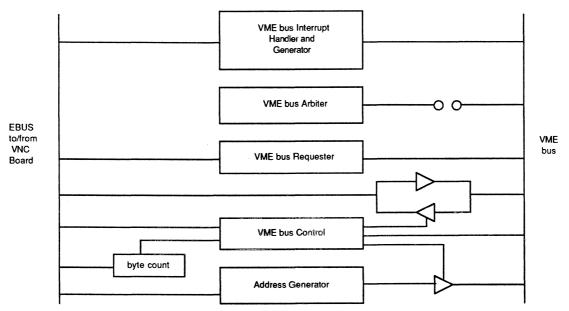

| 5-6  | VME Bus Adapter Block Diagram                            | 5-10 |

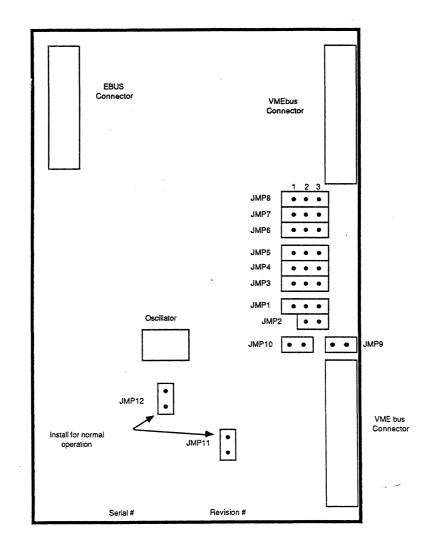

| 5-7  | VME Bus Adapter Card Layout                              | 5-12 |

| 5-8  | VME Bus Adapter Jumper Positions                         | 5-13 |

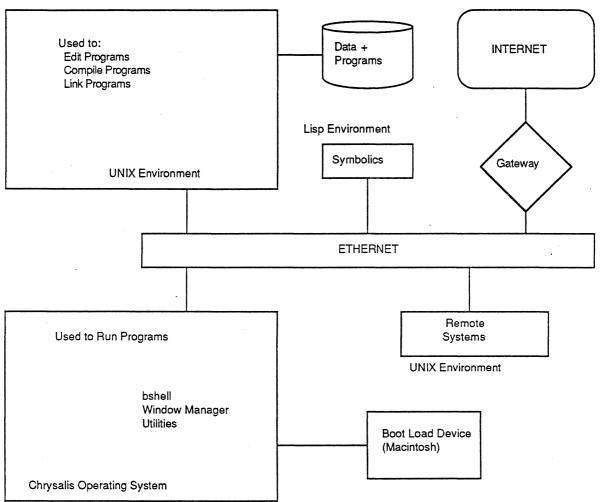

| 6-1  | Butterfly Plus Programming Environment                   | 6-2  |

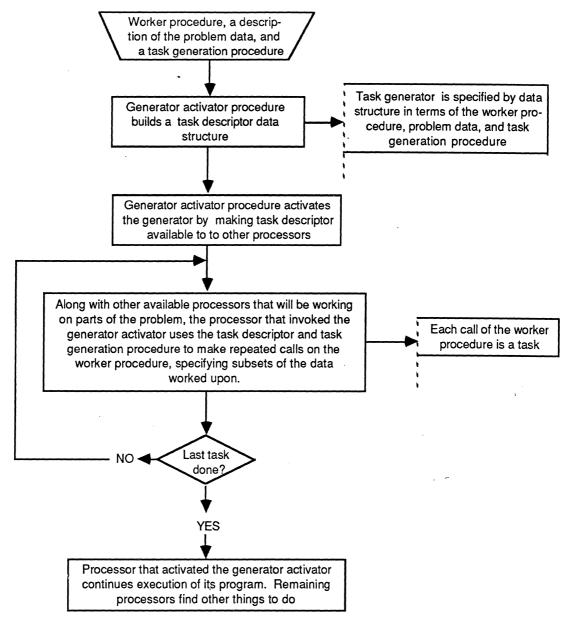

| 6-2  | Butterfly Plus Task Generator                            | 6-13 |

## Tables

| 1-1 | Minimal Butterfly Configuration Guide | 1-4  |

|-----|---------------------------------------|------|

| 1-2 | Butterfly Plus Product Specification  | 1-20 |

| 3-1 | Switch Bandwidth versus Message Size  | 3-25 |

`

X

.

| 4-1  | UART Control Register Addresses FFF7D000                   | 4-7  |

|------|------------------------------------------------------------|------|

| 4-2  | EPROM Data and Control Register (FFF7D022) Layout          | 4-8  |

| 4-3  | Multibus Data Transfer Timing                              | 4-18 |

| 4-4  | Multibus Adapter Interrupt Status Register Layout FFF7D028 | 4-21 |

| 4-5  | Multibus Adapter Interrupt Vector RAM Layout FFF7F000      | 4-23 |

| 4-6  | Vector RAM Programming Example                             | 4-24 |

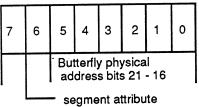

| 4-7  | Segment Attribute Tag Values                               | 4-25 |

| 4-8  | Multibus Adapter Misc Register (FFF7D026) Layout           | 4-27 |

| 4-9  | Multibus P2 Connector Pin Assignments                      | 4-29 |

| 4-10 | Multibus Adapter Control Registers                         | 4-30 |

| 5-1  | VME Node Controller LED Indicators                         | 5-8  |

| 5-2  | DIP Switch Settings                                        | 5-10 |

| 5-3  | Chrysalis VME Interface Access Methods                     | 5-29 |

| 6-1  | Atomic Memory Operations                                   | 6-6  |

| A-1  | p_state Bits                                               | A-4  |

| A-2  | Dual Queue Functions in PNC Microcode                      | A-6  |

| A-3  | Dual Queue Return Codes                                    | A-7  |

| A-4  | q_flags Bits                                               | A-8  |

| A-5  | Interrupt Control Register Bit Assignments                 | A-10 |

| A-6  | Interrupt Register Functions                               | A-10 |

| A-7  | Microcode Functions                                        | A-13 |

| A-8  | PNC Status Register (PNCsRC at FFF75000) Layout            | A-16 |

| A-9  | PNC Writable Control Store Control Registers               | A-18 |

| A-10 | Memory Control Registers                                   | A-19 |

.

.

Xİ

.

# **Chapter 1**

# **Butterfly Plus Overview**

The Butterfly Plus parallel processor is a powerful, modular computer system composed of multiple processors and memory modules connected by a high performance network interconnect. Each processor, along with an associated memory module, occupies one circuit card called a processor node. All processor nodes in a Butterfly machine are identical; all connect to the Butterfly Plus switch in the same way and can work together interchangeably to run an application program. The Butterfly Plus is a multiple instruction, multiple data stream (MIMD) machine in which each processor can execute an independent program on local or shared memory data.

Collectively, the memory modules of all the processor nodes form the shared memory of the machine. Although each memory module is local to one particular processor node, any processor can access the local memory of any other processor by using the Butterfly Plus switch to make remote memory references. Special circuitry in each processor node interprets ordinary memory references as either local or remote memory references, as appropriate. The switch can complete a remote memory reference within a maximum of a few microseconds, regardless of where the data resides.

The distributed, shared memory architecture of the Butterfly Plus, together with the firmware and software of the Chrysalis operating system, provides a program execution environment in which tasks can be distributed among processors regardless of where the task data is located. The Butterfly Plus can be programmed in several different ways. Processors can be dedicated to individual tasks, as in a realtime system, or used as a pool of interchangeable computing resources that are allocated to tasks dynamically. Interprocessor communication can occur through shared memory, with one processor writing data for another processor to read, or through message passing. The Chrysalis operating system and its associated set of programming languages, tools, and utilities support various different styles of parallel processing. The system software includes complete facilities for developing and debugging parallel programs.

#### **ARCHITECTURAL FEATURES**

The Butterfly Plus parallel processor has several important architectural features. Most importantly, the Butterfly Plus is an MIMD computer, able to execute multiple instruction streams on multiple data elements. The Butterfly Plus also has tightly coupled processors that allow for extensive interprocessor communications. In addition to these features, the Butterfly Plus architecture is flexible and expandable, and demonstrates a high degree of homogeneity and reliability.

Program instructions normally reside in the local memory of the processor that executes the instructions. As a result, each processor independently executes its own sequence of instructions on separate data in MIMD fashion, allowing programmers to structure programs and data in ways that are natural and efficient for their applications. The architecture supports a variety of software structures and allows Butterfly Plus systems to be used in a wide range of applications.

The processors in the Butterfly Plus are tightly coupled by the interconnect network, the Butterfly Plus switch. Tight coupling permits efficient interprocessor communication and gives each processor equal access to the global memory. As a result, programming is simplified, without sacrificing performance, by allowing programmers to organize data without undue concern for which memory module stores which part of the data. Program references to remote memory take only slightly longer to complete than references to local memory. Many applications achieve best performance when their data is scattered uniformly throughout the machine.

The Butterfly Plus is expandable over a wide range of configurations. Each processor node added to a Butterfly configuration contributes an increment of processing power, memory, and switch bandwidth. A Butterfly Plus system

can be configured with up to 256 processors to match the computational power needs of a particular application. Although the number of components increases with expansion, the complexity and cost of the interconnect network always remain at an acceptable level.

The Butterfly Plus is a homogeneous multiprocessor where each processor node is the same as every other. The uniformity of the Butterfly Plus architecture simplifies programming, since programmers need not allocate certain tasks to specific processors. Programmers can also write application software without concern for the number of processors that will be available to run the program. Such application software has several advantages. It can be developed and tested on small, inexpensive configurations, then run on larger, operational machines. Also, if the resource demands of an application exceed the capacity of its current Butterfly configuration, the application can be moved to a larger, more powerful Butterfly configuration and run without reprogramming. Application software written in this way improves overall system reliability and availability, since it can run on configurations reduced by missing or failed components.

The Butterfly Plus architecture is relatively insensitive to component failures, resulting in a reliable system. The machine can operate despite the absence of one or more of its processor nodes. A 128-processor machine can still run at approximately 98% of its capacity, for example, even after three of its processors are removed.

### SYSTEM COMPONENTS

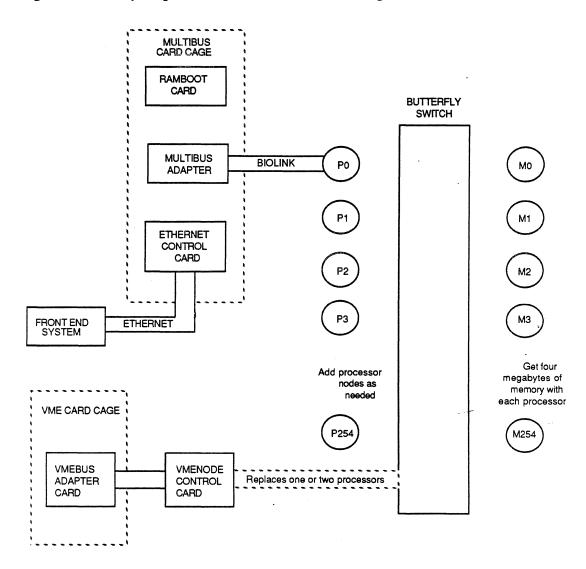

Butterfly Plus system components occupy from one to six freestanding 80inch high racks in which circuit cards, card cages, and peripheral devices are mounted. Racks have hinged doors both at the front, for access to the circuit cards, and at the rear, for access to the power distribution and cooling systems. Three types of card cages can be installed inside the rack. Butterfly card cages hold processor nodes, VME nodes, switch cards, and clock cards. Multibus card cages hold standard Multibus cards, and VME card cages hold standard VME cards. Figure 1–1 illustrates a block diagram of the Butterfly Plus system. Every Butterfly Plus system has at least one Butterfly card cage and one Multibus card cage. Larger systems have several Butterfly card cages but rarely require a second Multibus card cage. The VME card cage is always optional. Table 1–1 lists the minimal number of circuit cards and card cages

#### **Butterfly Plus Overview**

required for various system configurations. Some Butterfly Plus configurations may require more cards and card cages than are listed.

Figure 1-1 Butterfly Plus System Diagram

| Table | 1-1 |

|-------|-----|

|-------|-----|

| Minimal | Butterfly | <b>Configuration</b> | Guide |

|---------|-----------|----------------------|-------|

|         | Dattorn   | ooningaradon         | aurac |

| Racks | Processor<br>Nodes | Butterfly<br>Card Cages | Switch<br>Cards | Clock<br>Cards |   |

|-------|--------------------|-------------------------|-----------------|----------------|---|

| 1     | 1–16               | 1                       | 1               | 0              |   |

|       | 17–32              | 2                       | 4               | 1              |   |

| 2     | 33–48              | 3                       | 6               | 3.             |   |

|       | 49–64              | 4                       | 8               | 3              |   |

| 3     | 65–80              | 5                       | 10              | 4              |   |

|       | 81–96              | 6                       | 12              | 4              |   |

| 4     | 97–112             | 7                       | 14              | 5              |   |

|       | 113–128            | 8                       | 16              | 5              |   |

| 4     | 129–144            | 11                      | 22              | 8              |   |

|       | 145-160            | 12                      | 24              | 8              |   |

| 4     | 161–176            | 12                      | 24              | 9              | • |

|       | 177–192            | 13                      | 26              | 9              |   |

| 5     | 193–208            | 14                      | 28              | 10             |   |

|       | 209–224            | 14                      | 28              | 10             |   |

| 6     | 225–240            | 15                      | 30              | 11             |   |

|       | 241–256            | 16                      | 32              | 11             |   |

A power distribution unit at the bottom of each Butterfly rack accepts 5-wire, 3-phase, 208-volt AC power from the wall outlet and distributes this AC power to the main Butterfly power supply, located at the top of the cage. This main power supply rectifies the 3-phase AC power and distributes the resulting unregulated DC power to the individual power converters located on every processor node and switch card. Aside from the main AC power distribution cable that carries 3-phase AC power to the main power supply, the power distribution unit has six 120-volt AC outlets from which peripherals mounted in the rack can draw AC power. Three neon lamps on the top of the power distribution unit indicate the state of the three phases of AC power. A central circuit breaker enables and disables AC power to the rack.

#### **Butterfly Plus Card Cage**

A Butterfly Plus card cage normally holds three types of circuit cards: processor nodes and clock cards, which mount vertically in the lower portion of the card cage, and switch cards, which mount horizontally at the top of the card cage. (An optional VME node replaces one or two of the processor nodes when a VME card is installed in the rack.) A rack normally holds up to two Butterfly card cages, each with 18 vertical slots and two horizontal slots. The horizontal slots accept only switch cards. The clock card, if present, must occupy the rightmost vertical slot. Up to 16 processor nodes normally occupy all but one of the remaining vertical slots.

The Butterfly card cage has an integral main power supply that accepts 3phase AC power from the power distribution unit at the bottom of the rack and supplies unregulated DC power to the individual switching power supplies on each processor node, switch, and clock card. It also has an upper and lower fan bank for cooling, each with its own filter.

The Butterfly card cage has two AC circuit breakers and five DC circuit breakers. The two AC circuit breakers are located at the rear of the Butterfly card cage, above the lower fan assembly. The one on the left is a 4-handle breaker and the one on the right is a 3-handle breaker. The 3-handle breaker protects against current faults in either of the two cooling fan assemblies and trips the 4-handle circuit breaker when it detects a fault. If the 3-handle breaker is not in its on (up) position, the 4-handle breaker cannot be turned on. The 4-handle breaker detects current overloads on each of the three AC power phases and also detects ripple and phase faults.

The five DC circuit breakers are arranged in a row along the top of the front panel of the Butterfly card cage, between the processor nodes (installed vertically in card cage slots) and the lower Butterfly Plus switch card (installed horizontally in card cage slots). These breakers detect current or power cabling faults in the unregulated DC power that the DC power supply at the top of the cage provides to the Butterfly circuit cards. Each DC circuit breaker is a 20-ampere magnetic breaker that can power down a string of four processor, clock, or switch cards, allowing these cards to be removed without powering down the entire card cage. A Butterfly Plus is shipped with its processor nodes already installed in the Butterfly card cage and secured by a shipping bracket to prevent accidental slipping. This shipping bracket may be left in place or removed upon arrival.

## Multibus Card Cage

A Multibus card cage has nine horizontal slots. There are always at least three circuit cards in the first Multibus card cage: the Butterfly Plus Multibus adapter, which must occupy the topmost slot, a RAMboot card, and an Ethernet controller card. The lowest slot in the Multibus card cage cannot be occupied by a Multibus device requesting to be a master, and is generally kept empty.

Below the Multibus card cage is the Ethernet fantail, a narrow panel mounted horizontally, with cutouts for various types of cable connectors. The Multibus Ethernet controller card attaches to a DB-15 connector on the lefthand side of the fantail via a cable. Adjacent to the DB-15 Ethernet connector are two RS-232 host and console terminal ports. The UARTs of the Multibus adapter card connect to these two RS-232 connectors. The Ethernet fantail also provides a second Ethernet cable connector and a second pair of host and console terminal ports for use if a second Multibus card cage is needed. A bank of four additional RS-232 ports on the righthand side of the Ethernet fantail includes a pair of console and host ports on the left and right of the bank. These two ports terminate cables that attach to any processor node's diagnostic UART in the rack via that processor node's J4 connector. The middle two RS-232 connectors in this bank of four are unused, as are the two banks of RS-449 connectors. The Butterfly Plus needs only the ground, transmit data, and receive data signals on its RS-232 serial lines, all of which are standard DCE connections that accept male DB-25 connectors.

## Processor Node

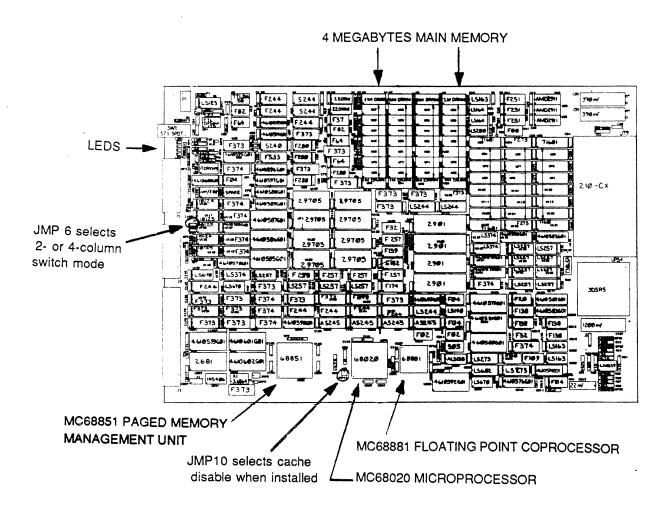

A Butterfly Plus can have up to 256 processor nodes. Each processor node is a single circuit card with the following components:

- MC68020 microprocessor with MC68881 floating point coprocessor and MC68851 paged memory management unit (PMMU)

- Four megabytes of main memory with memory controller

## **Butterfly Plus Overview**

- 128-kilobytes of programmable read only memory (EPROM)

- Address decoding logic

- Processor node controller (PNC)

- Dual UART

- I/O bus adapter

- Interface to the Butterfly Plus switch

- Switching power supply.

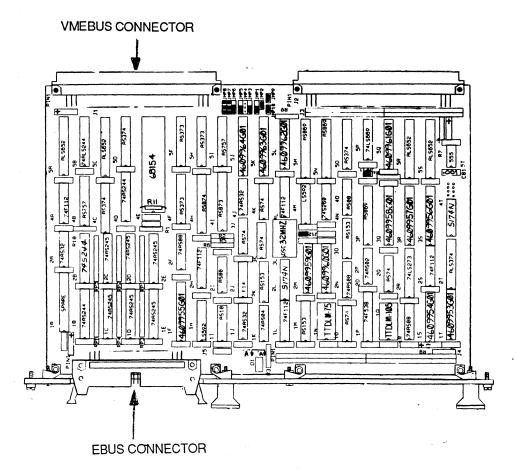

These processor node components communicate with one another over a fast internal bus. Figure 1-2 shows the processor node.

Figure 1-2 Processor Node

The MC68020 microprocessor is the main processing unit of a processor node. Associated with each MC68020 is an MC68881 floating point coprocessor. Paged memory management is provided by an MC68851. These three chips, combined with the address decoding logic, make up the primary computational elements of a processor node.

### Main Memory

Each processor node has four megabytes of semiconductor dynamic random access memory (DRAM) for local and remote memory accesses. The four megabyte memory bank serves as the local memory of its processor node, which accesses that memory directly over a fast local bus. Any processor node in the system can remotely access the local memory of any other processor node by using the Butterfly Plus switch. Together, all the processor node memories make up the shared memory of the Butterfly Plus.

Circuitry in each processor node monitors the high-order physical address bits during a memory reference to determine whether the memory access is local or remote. If the high-order address bits match the processor number, the access is a local one and can be made directly, without involving the switch. If these address bits differ from the processor number, the access is a remote one and must be made through the switch. From the viewpoint of a program running on one processor, the only difference between references to local memory on its own processor node and references to remote memory on other processor nodes is that remote references take slightly longer to complete. Typical memory reference instructions that access local memory take about one microsecond. Those accessing remote memory take about five microseconds. Speeds of the processors, memories, and switch are balanced to let the system work efficiently in a wide range of configurations. The memory bandwidth is 102-Megabytes-per-second. Every local memory access takes three cycles. The first cycle latches the memory address and type of operation (*e.g.*, read, word write, byte write). During a write operation, the new memory data is latched during the second cycle, thereby freeing the rest of the processor node to perform some other, unrelated operation during the third cycle. During a read operation, the memory returns the data to the processor node during the third cycle, leaving the rest of the processor node free to perform other work during the second cycle. The rest of the processor node is occupied during only two-thirds of the time it takes to access the memory.

Each four megabyte memory module has 36 one megabit DRAM chips organized into four banks of 8-bit bytes with one parity bit. A one megabit dynamic memory chip is a  $1024 \times 1024$  array of binary cells. The memory controller selects particular cells by asserting first a 10-bit row address, derived from the low-order address bits, and then a 10-bit column address, derived from the high-order bits.

Memory cycles are pipelined to maximize performance. When a processor begins to execute a memory reference instruction, the memory controller starts a memory cycle by strobing in the row address even before the memory reference is fully decoded. If the address decoding logic finds that the address is not a memory location, the memory controller aborts its cycle without ever strobing in the column address.

Byte parity provides single bit error detection to protect main memory data. When data is written into memory, a parity bit is calculated and stored with each byte. After the data is read back from memory, its parity bits are again calculated and compared with the stored parity bits. If they differ, a processor level 6 interrupt is requested.

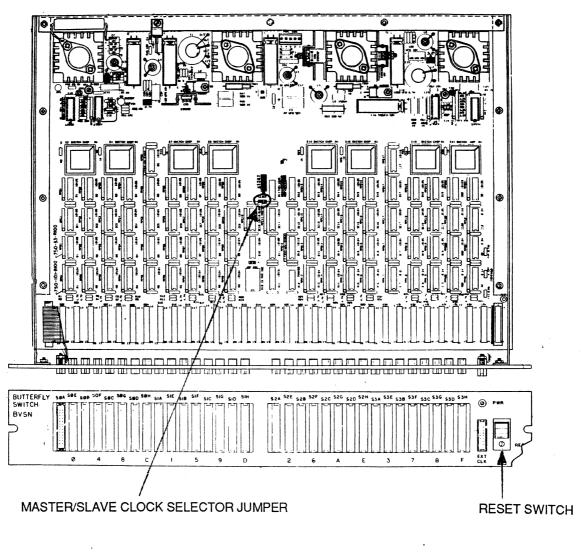

### Switch Card

Switch cards combine the techniques of packet switching and sorting networks to establish communication paths between processor nodes. Besides routing data, switch cards also distribute clock and system reset signals to the processor nodes. The switch operates much like a packet switched network, formatting requests to read or write memory locations into data packets, then routing them directly from the processor node that initiated the request to the processor node where the data resides. Like most packet switched networks, the Butterfly Plus switch can establish and hold many different communication paths simultaneously. Every processor node can read or write a memory location through the switch—all at the same time—and provided that these simultaneous memory accesses do not conflict with one another, all can be performed in parallel within the same time it would take one processor to read only one memory location. Named after the fast Fourier transform butterfly, which it resembles, the Butterfly Plus switch can be expanded to accommodate up to 256 processors.

Conceptually, the switch consists of an array of switch nodes that connect to one another and to the processor nodes. Each input to a switch node is driven by the output from a processor node or another switch node. Similarly, each output from a switch node in turn drives a processor node or another switch node. The switch logic uses sophisticated mechanisms for routing, timing, flow control, and collision resolution to transport packets reliably from switch node to switch node.

Physically, the switch is made up of switch cards plus the cables that connect the switch cards to one another and to the processor nodes. One or two switch cards can mount directly into the Butterfly card cage horizontal slots just above the processor node vertical slots. A switch card contains eight complete switch nodes, each with four inputs and four outputs, arranged in two columns of four nodes. A metal panel mounted at the front of each switch card has 32 connectors, 16 for input to the four switch nodes in the first column and 16 for output from the four switch nodes in the second column. A Butterfly Plus system with up to 16 processors needs one switch card, which implements a 2-column switch. Butterfly Plus systems with from 17 to 32 processors need four switch cards connected in pairs to implement a 4-column switch. Larger systems extend the 4-column switch by adding two additional switch cards for every 16 processors. Systems can be typically configured with extra switch nodes to provide alternate paths between processor nodes.

Figure 1–3 shows the Butterfly Plus switch card.

#### **Clock Card**

The Butterfly Plus is a fully synchronous machine in which all processor nodes use the same clock source. Systems with up to 16 processors use the single switch card clock as their system clock source. They do not need separate clock cards. Systems with more than 16 processors need a separate clock card and use the switch to distribute the system clock signal from this central source. The clock card occupies the rightmost slot of a Butterfly card cage. The Butterfly Plus clock card can operate as either a master or a slave.

#### Inside the Butterfly Plus

As master, it transmits a differential, emitter coupled logic signal, derived from an onboard oscillator, through the four connectors near the top of the card. The system reset signal, activated by the toggle switch near the top of the card, is distributed along with the clock signal. The four connectors mate with mass terminated cables that carry the clock and reset signals throughout the Butterfly Plus. One clock card can supply clock and reset signals to up to four switch cards (*i.e.*, two Butterfly card cages), which then redistribute these signals to their attached processor nodes.

When operating as a slave, the clock card receives system clock and reset signals from a master clock card through a connector on the front edge of the card, regenerates them, and passes them through its four output connectors. Systems with more than 32 processors have more than four switch cards and therefore require more than one clock source. Master and slave clock and reset signals are distributed through a hierarchical tree of clock cards in these larger configurations. The root clock card operates as master and sources the clock signals used by the next level of clock cards. Remaining clock cards operate as slaves, accepting signals from the previous level in the tree of clock cards and passing them on to the next level. Systems with 33–64 processors use a 2-level tree, and those with more than 64 processors use a 3-level tree.

There are two LEDs and a master reset toggle switch at the top of every clock card. The master reset switch asserts a system reset signal that resets every processor node. The red LED is lit to indicate that a system reset is in progress. The green LED is lit to indicate that power is applied.

### **INPUT/OUTPUT CAPABILITIES**

The Butterfly Plus parallel processor supports two types of I/O devices: Multibus peripherals and VMEbus peripherals. The Multibus adapter card occupies the topmost slot in a Multibus card cage housed inside a Butterfly rack. It communicates with the chosen processor node (designated as the king node) via a ribbon cable that attaches to the I/O connector at the bottom of the processor node. The VME interface consists of two cards, one that fits into a VME card cage inside a Butterfly rack and one that replaces a processor node in one of the Butterfly card cage slots. Two ribbon cables connect these two VME interface cards, and another set of cables attaches the VME interface card in the Butterfly card cage to the Butterfly Plus switch.

### **Butterfly Plus I/O Link**

Multibus I/O devices communicate with a processor node via a synchronous bus, called the Butterfly Plus I/O link (BIOLINK), that attaches the Multibus adapter to the processor node. Using the BIOLINK, a Butterfly Plus processor can access memory on the Multibus. The Butterfly Plus processor can also read or write the control registers and data registers of Multibus peripheral devices. On the other hand, a Multibus device can read or write the four megabytes of memory on the processor node to which the Multibus adapter is attached; it can issue an MC68020 interrupt request and supply an interrupt acknowledge response word to the Butterfly Plus processor; and it can also execute special multiprocessing functions on the processor node to which it is attached.

### **Multibus Adapter Card**

The Multibus adapter contains the circuitry for connecting a Butterfly Plus processor node to I/O cards that conform to the IEEE 796 (Multibus) standard. The Multibus adapter is a printed circuit card that occupies the top slot in the Multibus card cage and attaches to the processor node I/O connector via a ribbon cable. The Multibus adapter supports local data transfers, event posting, and interrupt processing. Each Multibus interrupt request level can be mapped into one of two processor interrupts. Multibus interrupts can be individually enabled, and there is a general interrupt disable feature.

Two Multibus cards are included in every Butterfly Plus parallel processor: The RAMboot card (a Micro Memory MM-9000D Dynamic RAM Memory Module) and the Ethernet Controller Card (an Excelan EXOS 301 Ethernet Front-End Processor). Both of these Multibus cards are off-the-shelf IEEE-796 compatible. Both can occupy any slot in the Multibus card cage except for the top slot, which holds the Multibus adapter card, and the bottom slot, which cannot be occupied by a Multibus master. Figure 1–4 shows the Multibus adapter card.

#### Inside the Butterfly Plus

| US         S151         D         S563         US         S564         S564 </td |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1/2         5533         6         5533         1/2         5533         1/2         5533           1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2         1/2                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Figure 1-4 Multibus Adapter Card

#### Multibus RAMboot Card

The Multibus RAMboot Card is a DRAM memory that stores the operating system and other program code needed to perform a Butterfly Plus system reset as quickly as possible when necessary. Provided with one megabyte of memory, the RAMboot card can be expanded to four megabytes by filling empty chip sites on newer boards.

#### **Multibus Ethernet Controller Card**

The Multibus Ethernet controller card is an IEEE 802.3 local area network controller that interfaces the Butterfly Plus parallel processor to an Ethernet (version 1 or version 2) or other IEEE 802.3 local area network. The Ethernet controller card attaches to the local area network via a DB-15 connector on the Ethernet fantail, which allows the connection of a customer-supplied Ethernet transceiver. The processor node communicates with the Ethernet card via supplied control and data registers. It supports the industry standard TCP/IP protocol using the Ethernet controller card.

#### VME Interface

The VME interface supports high speed I/O devices whose bandwidth requirements exceed the I/O capacity of a processor node. With this interface, many industry standard, high bandwidth devices, such as frame grabbers, can interface to the Butterfly Plus efficiently. The VMEbus is a 32-bit bus with a peak data transfer rate of 40-megabytes-per-second and a typical data transfer rate approaching 20-megabytes-per-second.

The VME interface transfers data directly to and from the Butterfly Plus switch without passing the data through a processor node, as does the Multibus adapter. Direct attachment of the VME interface to the switch has several advantages. With the VME interface attached directly to the switch, I/O transfers can be spread across memory on many processor nodes, thereby reducing the load on any particular memory module. Also, the 20-megabyteper-second nominal bandwidth of the VMEbus far exceeds the I/O bandwidth. Attaching the VME interface directly to either one or two switch ports allows the bandwidth of the connection between the Butterfly Plus switch and the VMEbus to be scaled up to about 20-megabytes. Physically, the VMEbus interface consists of two circuit cards connected by a cable up to 20 feet long. One of these, the VME Bus Adapter, is a double height VME card that plugs directly into the VME card cage. The other, the VME Node Controller, generally replaces two processor nodes in the Butterfly card cage and has four connectors that attach via ribbon cables to two separate ports on a Butterfly Plus switch card. Logically, the VME interface contains two complete interfaces to the Butterfly Plus switch, an interface to the VMEbus, and a microengine that translates between VMEbus transactions and Butterfly Plus switch messages.

Figure 1–5 shows the VME Node Controller and Figure 1–6 shows the VME Bus Adapter card.

: ] 23.99 ] [24.510 ] [ 78 700 \$ [ **23.00** ] Same 1 1000 2. 9 E FAL 6244 70798 ] [ [ 1 84 (1 7479) 70 3 0 70766 PE14540 F64 - P41532 P41510 pass. זוה HM62256 74415652 1 F14F187 ||F FAS244 1 [74[5374] nc seese 1415146 ------ TALS244 DΛ 7 III HÖL = \$ + [22 UF] Êź

DIP SWITCHES

Figure 1-5 VME Node Controller

Figure 1-6 VME Bus Adapter Card

#### SYSTEM RESET

A Butterfly Plus reset can occur when the system reset switch is activated, when a restart message is received from another processor, when one of the power supplies detects that the power bus input voltage is too low, or when circuitry on the processor node detects an abnormal condition that can impair proper functioning of the board. In systems with up to 16 processors, the system reset switch is located on the Butterfly Plus switch card. In systems with 17–32 processors, the reset switch is located on the clock card. The system reset switch for machines with more than 32 processors is the reset switch on the master clock card, which generally occupies the rightmost slot in the

lower Butterfly card cage of the second to last rack (*i.e.*, the rack to the right of the leftmost rack). Operating the system reset switch initializes all processor nodes and switch nodes without clearing main memory. Except for the fact that memory data is preserved, a system reset has the same effect on the processor nodes and the switch as a momentary power outage. Toggling the system reset switch also resets the Multibus card cage. However, it does not reset the VMEbus.

## PACKAGING

A 128-processor Butterfly Plus system, including the Multibus and VMEbus cages, occupies four Butterfly racks, each 36 inches deep by 24 inches wide by 80 inches high. Allow 40 inches by 100 inches of floor space for each Butterfly rack. This provides sufficient clearance to open the front and back doors, which are 19 inches wide. An additional 24 inches is required for the machine to be serviced.

The Butterfly Plus switch can be configured to provide any level of bandwidth needed for the machine. Alternate switch paths can be provided to reduce vulnerability to single point failures and potential contention. A 16-processor system uses a 1-card switch, for example, and a 64-processor system uses a switch distributed over eight cards.

## **Butterfly Plus Overview**

Table 1–2 lists the specifications for the Butterfly Plus.

#### Table 1-2

### Butterfly Plus Product Specification

| Power Requirements    | AC Plug                                             | NEMA L21-30                           |

|-----------------------|-----------------------------------------------------|---------------------------------------|

|                       | AC                                                  | 5-wire, 3-phase power<br>at 208 volts |

|                       | Per Processor Node<br>Dissipation                   | 65 watts                              |

|                       | Power Dissipation for 16-Node System                | 1450 watts                            |

|                       | Power Dissipation for 32-Node System                | 3275 watts                            |

| Operating Temperature | 20 - 40°C                                           |                                       |

| Humidity              | 40% to 70% relative<br>humidity, non-<br>condensing | ,<br>7                                |

# **Chapter 2**

# **The Processor Node**

A Butterfly Plus parallel processor can have up to 256 processor nodes connected by the Butterfly Plus switch. Each processor node contains an MC68020 microprocessor, MC68881 floating point coprocessor, MC68851 paged memory management unit, four megabytes of main memory, an AM2901 bitslice processor used as the processor node controller (PNC), an I/O bus adapter, a UART that drives the serial lines to the host and console diagnostic terminals, a bootstrap EPROM, and an interface to the switch. A local bus connects all of these various processor node elements, providing flexible control and minimal complexity. Figure 2–1 is a block diagram of the processor node.

Figure 2-1 Processor Node Block Diagram

#### The Processor Node

Each processor node consists of one 12 by 18 inch printed circuit card with an onboard switching power supply. Four cable connectors on the card edge provide unregulated DC power (upper, 5-wire connector), transmit and receive channels to the switch (the transmit connector is nearest to the power connector), and a BIOLINK channel that attaches to the Multibus adapter (the largest connector). A fifth connector, the J4 connector located near the card edge at the corner of the card, attaches to the dual UART for use by diagnostics.

Each processor node has four LEDs and one toggle power switch. The top LED is red and is controlled by software. The remaining three LEDs are green and are controlled by hardware. The red LED comes on at power up, or whenever the processor node is reset, to indicate that the processor node is running its power-up diagnostic tests. When the processor node completes its built-in diagnostic test, the red LED turns off to indicate that the processor node is now functioning properly. If the red indicator flashes or stays lit continuously, the card is probably faulty and must be checked.

The second LED is green and lights up when the processor node on-board power supply or regulator generates +5 volts of DC power. There can be live DC power on the processor node even if this green indicator light is off. Unregulated DC power might still be supplied from the power connector and distributed across the circuit card.

The third and forth LEDs are green and light up to indicate that a message is either being sent to the switch or being received from the switch, respectively.

#### **PROCESSING ELEMENTS**

The primary functional subsystem of a processor node is its processing elements group consisting of the main processor and floating point coprocessor, the paged memory management unit, the address decoding logic, and an arbiter for the processor node's internal bus. The MC68020 main processor and the MC68881 floating point coprocessor both run at their maximum rated speed of 16.MHz.

#### Processor

All Butterfly Plus application programs run on the MC68020 processor with MC68881 floating point coprocessor. These processing elements combine state-of-the-art technology and advanced circuit design techniques to achieve an architecturally advanced processing unit. The primary features of the MC68020 include:

- 32-bit data and address registers

- 16-gigabyte direct addressing range

- A wide variety of instruction types

- Five data types

- Memory mapped I/O for accessing peripheral devices through the main memory address space

- 14 memory addressing modes.

Refer to the Motorola MC68020 32-Bit Microprocessor User's Manual, Second Edition for further information.

## **Floating Point Coprocessor**

The MC68881 floating point coprocessor implements the full IEEE 754 specification for floating point arithmetic. It uses the short (32-bit), long (64-bit), and extended (80-bit) number formats and implements microcoded square root, trigonometric, logarithmic, and transcendental functions. Since the MC68881 uses the MC68020 coprocessor facility, hardware floating point operations can be invoked by executing ordinary MC68020 instructions. The major features of the MC68881 floating processor include:

- Eight general purpose floating point data registers, each supporting a full 80-bit extended precision real number format

- A 67-bit arithmetic unit for fast calculation with intermediate precision greater than the extended precision format

- A 67-bit barrel shifter for fast shifting operations

- 46 instructions, including 35 arithmetic operations

#### The Processor Node

- Support for trigonometric and transcendental functions

- Seven data types and 22 constants

- Virtual memory and virtual machine operations

- Instruction execution is fully concurrent with the main processor.

Refer to the Motorola MC68881 Floating-Point coprocessor User's Manual, First Edition for further information.

# MEMORY MANAGEMENT UNIT

The MC68851 paged memory management unit supports the paged virtual memory of the MC68020. It translates the virtual addresses used by the processors into the physical addresses used by the PNC, memory, switch, and bus adapters. At the start of a memory read or write, the memory management unit receives a 32-bit virtual address from the MC68020 processor. It uses page descriptors stored in its address translation cache to translate this virtual address into a  $\cdot$ 32-bit physical address. The MC68851 also handles all access privilege checking and allows reprogramming of access privileges during operation. Refer to Appendix B, "Physical Memory Map", for a physical memory address table.

All Butterfly Plus components except the MC68020 processor and MC68881 floating point coprocessor use physical memory addresses. A 32-bit Butterfly Plus physical address is formatted as an 8-bit processor node number followed by the 24-bit local address of a location in the four megabyte memory module of that processor node. The processor and floating point coprocessor use virtual addresses, and since these are the two processing elements that execute most program instructions, virtual addresses are the only addresses that normally concern a programmer. The main distinction between physical and virtual addresses is that the physical address of a location is the same on all processor nodes, whereas virtual addresses can differ from one process to the next.

The operating system establishes the layout of the virtual address space. Since pages are an integral power of two in size, the low-order bits of a virtual address are identical to the low-order bits of the corresponding physical address. By convention, the text segment of a Chrysalis program usually starts at 40000 and the data segment usually starts at 20000. This is not a requirement of the system, but merely a convention. The upper 16-megabytes of the virtual memory address space (addresses 0xFF000000 to 0xFFFFFFF) are reserved as a special function subspace used to access certain memory mapped devices such as EPROM and UART, PNC special functions and other microcoded control functions, and Multibus I/O address space and memory. References to the special function subspace are translated into physical addresses within the memory management unit, which generates a 32-bit physical address if the access is allowed.

# ADDRESS DECODING

Not all memory reference instructions access memory; some access memory mapped circuits that respond to memory reference instructions but do not necessarily store data. In general, the processors and other programmable components on a processor node can make four types of memory references:

- Dialog between the MC68020 processor and either the MC68851 paged memory management unit or the MC68881 floating point coprocessor

- Auxiliary system functions, such as executing code from EPROM, configuring main memory, downloading microcode to the writable control store of the processor node controller, or using the diagnostic UART serial channels to communicate with the host and console terminals

- Local memory access

- Any activity mediated by the processor node controller, including remote memory access; reading or writing Multibus memory or I/O device registers over the BIOLINK; and special functions like block transfer from one processor node to another, atomic queuing operations, and event posting.

# **PROCESSOR NODE FUNCTIONS**

A processor node can perform many operations at the same time. As an example, one processor node can execute all of the following operations simultaneously:

- Add two integers in the MC68020 processor

- Divide two real numbers in the MC68881 floating point coprocessor

- Receive a message from a different processor node

- Send one word of a block of data to a different processor node

- Arbitrate a Multibus device request to access Butterfly Plus memory.

In high-throughput environments these multiple concurrent operations are both normal and desirable. The processor node provides adequate communication bandwidth between the various autonomous hardware resources while controlling their interactions. In addition to these conventional computer functions, a parallel processing architecture requires many special functions that the MC68020 processor does not provide. These special processor node functions include:

- A 32-bit time-of-day clock and timer, capable of interrupting the processor, for scheduling timed or delayed events

- DRAM refresh logic

- Conversion of remote memory references to switch messages

- Block memory transfer between processor nodes

- Remote restart of processor nodes from other processor nodes

- Interprocess communication among multiple processor nodes

- Message timeout handling for transmissions and solicited replies

- Processor interrupt acknowledgement and interrupt vector handling

- Error reporting of timeouts, checksum errors, and parity errors

- Event posting for the operating system

- Power fail interrupt and power-up sequence generation

- Interaction with I/O device controllers when performing direct memory access and special functions

- Process scheduling.

However, most of these special functions are implemented by microcode in the processor node controller; the remainder are implemented by the operating system.

# INTERRUPT SYSTEM

The MC68020 responds to seven levels of prioritized, vectored interrupt requests. Level 7, the interrupt request level with highest priority, is the only level that is not maskable. When an interrupt is requested, the interrupt system software uses an interrupt vector supplied by the requestor to find the address of the appropriate interrupt service routine. Multiple interrupt requests can be pending simultaneously at all priority levels. Interrupt requests below a certain priority level can be masked off and ignored. The highest priority interrupt request triggers an interrupt if interrupts are enabled at that priority level. The highest priority element requesting an interrupt at that level then supplies an 8-bit interrupt vector to the processor.

The Butterfly Plus allocates the seven interrupt request levels, from highest to lowest priority, as follows:

- Level 7: PNC and switch errors and power failure

- Level 6: Memory parity error and diagnostic UART

- Level 5: EPROM based debugger (USD) interrupt request

- Level 4: High priority Multibus device interrupt request

- Level 3: Low priority Multibus device interrupt request

- Level 2: Interval timer interrupt request

- Level 1: Scheduler interrupt (process scheduler request).

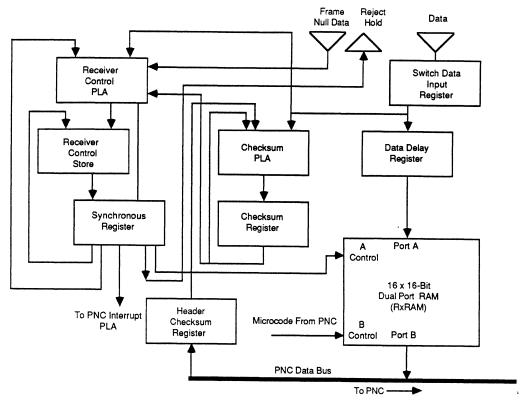

# PROCESSOR NODE CONTROLLER

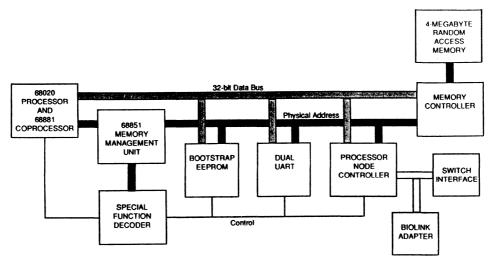

The processor node controller (PNC) consists of four basic subsystems. These include a microcode sequencer, a static RAM control store, an interrupt service routine address generator, and a bitslice processor. The main processing unit of the PNC is the AM2901 bitslice processor, which controls the various processor node resources and performs those functions that, because of throughput or indivisibility requirements, cannot be performed by the MC68020 processor. Microcode for the AM2901 is stored in an EPROM, from which it is downloaded into a 4096-word array of 64-bit static RAM control store. The AM2911 microsequencer controls the flow of the microprogram guided by the microcode. Figure 2–2 is a block diagram of the PNC showing its main components and how they interact.

Figure 2-2 PNC Block Diagram

The PNC performs certain operations that greatly extend the parallel processing capability of the MC68020 processor. These include a suite of atomic arithmetic and logical operations, queuing primitives, operations that implement an event handling mechanism, and a process scheduler that works with the queuing and event handling mechanisms to provide efficient communication and synchronization between application software modules. Many of these PNC special functions manipulate data, and it is important to perform them in a way that prevents other processors from accessing the data while it is being used. Because the PNC controls all memory references made by either its own MC68020 processor or any remote processor node via the switch, it ensures that these special functions are indivisible or *atomic*. The PNC also has two independent finite state machines, which work together with the AM2901 bitslice processor. The two finite state machines, called the switch receiver and the switch transmitter, manage the switch interface to handle incoming and outgoing messages.

The PNC regulates all Butterfly Plus switch transactions. It initiates all messages sent over the Butterfly Plus switch and processes all messages received from the switch.

The Butterfly Plus switch interface transfers message requests and replies between the processor node and the switch. Its two finite state machines have their own independent connectors on the processor node board. The switch interface communicates with the rest of the processor node through a pair of dual port memories. When a message is sent out across the switch, the message data is loaded into appropriate locations in the transmitter dual port memory, and the output finite state machine is notified. When a message comes in from the switch, the input finite state machine deposits it in the receiver dual port memory and notifies the processor node controller.

# **PNC Bitslice Processor**

The AM2901 bitslice processor allows the PNC to perform arithmetic and logical operations, including conditional microcode branches. The 4096-word array of 64-bit microcode resides in a static RAM control store during execution. Every 125 nanoseconds a microcode sequencer feeds selected control store bits into a pipeline register. The next microinstruction is then fetched from the control store in parallel with execution of the current microinstruction. The microcode is stored in EPROM and downloaded to the static RAM microstore, where it can be overwritten by the operating system if required. Distinctive characteristics of the bipolar AM2901 bitslice processor are:

- 17 registers, each 16 bits wide, used for temporary calculation and data storage, and as permanent, fast access variables for timers, status flags, and pointers and counters for direct memory access

- 8-function arithmetic and logic unit (ALU)

- Dual-address architecture allowing simultaneous access to two working registers

#### The Processor Node

- Flexible data source selection, which allows ALU data to be selected from five source ports, giving a total of 203 source operand pairs for every ALU function

- Left and right 16-bit rotates

- Carry, zero, and negative status flags for controlling conditional branches.

Refer to the Advanced Micro Devices Bipolar Microprocessor Logic and Interface Data Book for further information.

# **Control Store and Microcode Sequencer**

The 12-bit control store address is sourced by a conventional microprogram sequencer when its code is in the process of performing a microinterrupt service routine. If the code is just about to begin a microinterrupt service routine, its address is sourced by the microinterrupt service routine address generator. The microprogram sequencer is implemented using the AM2911 microsequencer, augmented by two multiplexers that allow 2-condition, 4-way branching. Microsequencer features include a pushdown stack for saving up to four return addresses, and an internal address register for storing the addresses of commonly used routines.

The microsequencer allows the microcode to branch unconditionally, call and return from subroutines, or branch conditionally on the state of various flags and signals. Microprograms run at one of two execution levels. Dispatch level is reserved for microcode functions that respond to requests from the local processor, such as reading the realtime clock, initiating a block transfer, or referencing a Multibus address. Interrupt level is used for microcode functions that handle requests from the switch receiver and transmitter, direct memory access requests, and the interval timer.

#### **Microcoded Special Functions**

The PNC also operates the Butterfly Plus switch, and is responsible for all interactions with the switch interface. These interactions take many forms. The simplest occurs when the processor accesses a word of memory on another processor node. The PNC notes that the memory reference is a remote one, places the remote processor node number and memory address in the switch transmitter's dual port RAM, and tells the transmitter to begin the

transaction. While the message is en route and the processor is held in a wait state, the PNC can service direct memory access requests or other microinterrupts. When the message reaches the destination processor node, the remote PNC completes the memory reference and, if the access was a read, sends back a reply message. The reply returns to the originating node, and the value of the referenced memory location is returned to the processor just as though it had performed a local memory reference. Because the hardware is heavily overlapped, this entire remote memory reference occurs in five microseconds under normal loads.

In addition to single word transfers, a PNC can transfer blocks of memory between any two processor nodes in the machine. Block transfers occur at high speed, limited only by the bandwidth of the switch port (about 32-megabits-per-second) and the bandwidth of the memory module (about 102-megabits-per-second). Note that this is *not* the aggregate bandwidth of the Butterfly Plus; it is only the bandwidth of one processor node.

The PNC also performs a variety of indivisible primitive operations. For example, the PNC can post events without using any system locks. The processor tells the PNC to post an event by writing the address of a parameter block into a special memory location that traps to the microcode. Writing the address of a parameter block into a memory location is a general mechanism used by such functions as block transfer, enqueue, and the like. It causes the PNC to send a special message to the destination node that specifies the location of the data structure associated with an event. The PNC at the destination node stops all other memory references and updates the event data structure. If the process that owns the posted event needs to run immediately, the destination PNC also invokes the process scheduler on that node. Other special functions implemented by the PNC include a realtime clock, an interval timer, indivisible mask-and-add-to-memory instructions, and dual queue functions. The operating system uses PNC primitives like these to build higher level synchronization primitives such as locks, semaphores, barriers, and monitors. Appendix B, "PNC Microcode Functions", describes the PNC special functions in detail.

# **Microinterrupt Requirements**

Most processor node functions involve a sequence of transfers from one internal bus element to another, and all activate bus element control lines. Each processor node function occurs when the PNC executes the appropriate sequence of microinstructions from its control store. Certain data transactions required during processor node functions must be performed as quickly as possible. The delay when a processor reads or writes its local memory, for example, has a dramatic impact on system performance. Other transactions can take somewhat longer to complete. Direct memory access operations that transfer data across the BIOLINK always require low latency. Memory refresh, in contrast, can tolerate a relatively long delay. Switch transactions have various timing requirements, depending on the priority of the message that initiated the transaction.

The microinterrupt driven PNC architecture is ideal for implementing functions with diverse timing requirements because low-priority functions can be kept pending while the PNC attends to higher priority tasks. Microinterrupt requests are issued to initiate processor node functions. Special circuitry locates the address of the microinterrupt service routine that performs the highest priority function among those with pending requests. Once PNC microinterrupts are enabled, that service routine begins executing almost immediately. Other microinterrupt requests remain active until the higher priority function has been performed.

# Realtime Clock and Timer

The PNC maintains a 32-bit realtime clock and a 16-bit interval timer, each with 62.5-microsecond resolution. The maximum timer interval is about four seconds and the realtime clock period is somewhat greater than 74 hours. The interval timer issues a level-2 interrupt request when it reaches zero. It is then reset to request another interrupt about four seconds later. This is normally subsequently changed by the system level 2 interrupt handler.

# SWITCH INTERFACE

The Butterfly Plus switch interface connects the processor node to the switch and is controlled by the PNC. All message transactions between a processor and a memory module on a different processor node—or between one processor and another—travel through the switch interface. Two finite state machines make up the switch interface: the switch receiver and the switch transmitter.

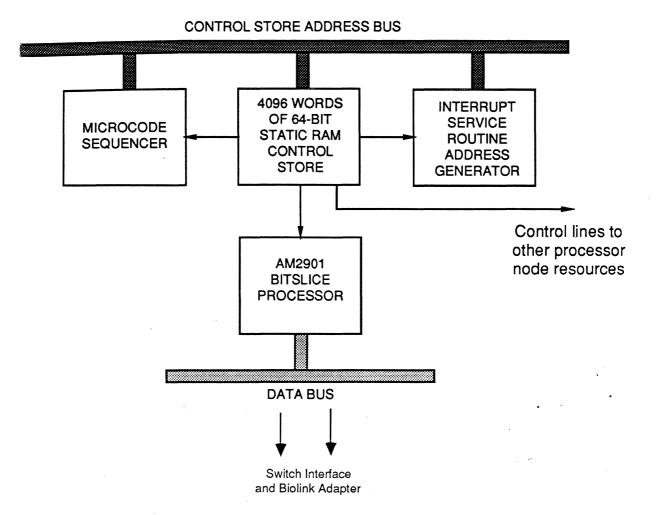

# Switch Receiver Micromachine