## APPENDIX 1

Extended Industry Standard Architecture (EISA) Specification 3.1

## TABLE OF CONTENTS

| Fo | preword .                                                                                              | ix                                                                 |

|----|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|    | otational Conventions                                                                                  | x                                                                  |

|    | nits of Measure                                                                                        | xi                                                                 |

| 1. | EISA Overview                                                                                          |                                                                    |

|    | 1.1 Compatibility with ISA                                                                             | 1                                                                  |

|    | 1.2 Memory Canacity                                                                                    | ī                                                                  |

|    | 1.3 Synchronous Data Transfer Protocol                                                                 | $\overline{2}$                                                     |

|    | 1.4 Enhanced DMA Functions                                                                             | $\bar{2}$                                                          |

|    | 1.4.1 32-bit Address Support for DMA Transfers                                                         | $\bar{2}$                                                          |

|    | 1.4.2 8-, 16- or 32-bit Data Transfers from DMA Devices                                                | - 3                                                                |

|    | 1.5 Bus Master Capabilities                                                                            | 4                                                                  |

|    | 1.6 Data Size Translation                                                                              | 4                                                                  |

|    | 1.7 Bus Arbitration 1.8 Edge/Level Triggered Interrupts                                                | 4                                                                  |

|    | 1.8 Edge/Level Triggered Interrupts                                                                    | 4                                                                  |

|    | 1.9 Automatic System Configuration                                                                     | 5                                                                  |

|    | 1.10 EISA Feature/Benefit Summary                                                                      | 6                                                                  |

| 2. | EISA Bus Specification                                                                                 | 1<br>1<br>2<br>2<br>2<br>3<br>4<br>4<br>4<br>5<br>6<br>8<br>8<br>8 |

|    | 2.1 Signal Descriptions                                                                                | 8                                                                  |

|    | 2.1.1 Address and Data Bus Signal Group                                                                | 8                                                                  |

|    | 2.1.2 Data Transfer Control Signal Group 2.1.3 Bus Arbitration Signal Group 2.1.4 Utility Signal Group | 11                                                                 |

|    | 2.1.3 Bus Arbitration Signal Group                                                                     | 16                                                                 |

|    | 2.1.4 Utility Signal Group                                                                             | 18                                                                 |

|    | 2.1.5 Summary of Signals                                                                               | 19                                                                 |

|    | 2.1.6 Signal Usage by System, Masters and Slaves                                                       | 19                                                                 |

|    | 2.2 ISA Cycles                                                                                         | 19<br>23<br>23<br>25<br>25<br>25<br>27<br>27                       |

|    | 2.2.1 ĆPU CYCLES                                                                                       | 23                                                                 |

|    | 2.2.2 MEMORY SLAVES                                                                                    | 25                                                                 |

|    | 2.2.3 I/O SLAVES                                                                                       | 25                                                                 |

|    | 2.2.3 I/O SLAVES<br>2.2.4 BUS MASTERS                                                                  | 25                                                                 |

|    | 2.3 ISA CPU and Bus Master Cycles                                                                      | 27                                                                 |

|    | 2.3.1 8-bit Memory Cycles                                                                              | 27                                                                 |

|    | 2.3.2 8-bit I/O Cycles                                                                                 | - 31                                                               |

|    | 2.3.1 8-bit Memory Cycles 2.3.2 8-bit I/O Cycles 2.3.3 16-bit Memory Cycles                            | 35                                                                 |

|    | 2.3.4 16-bit I/O Cycles                                                                                | 39                                                                 |

|    | 2.4 EISA CPU and Bus Master Cycles                                                                     | 42                                                                 |

|    | 2.4.1 Standard Memory and I/O Cycles                                                                   | 42                                                                 |

|    | 2.4.2 COMPRESSED Cycles                                                                                | 48                                                                 |

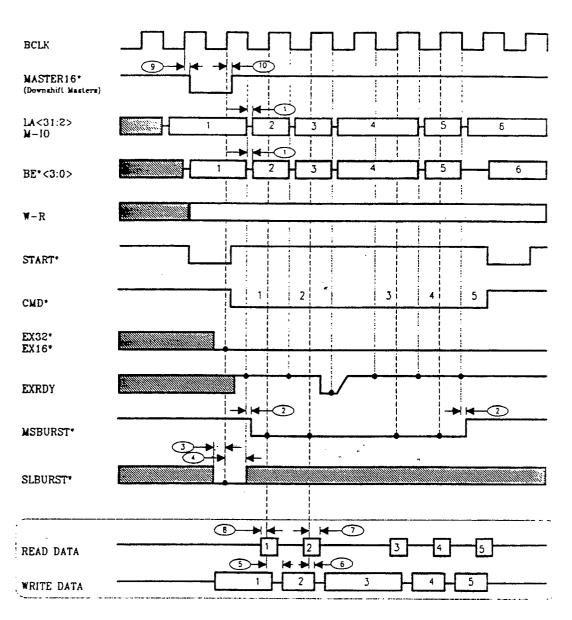

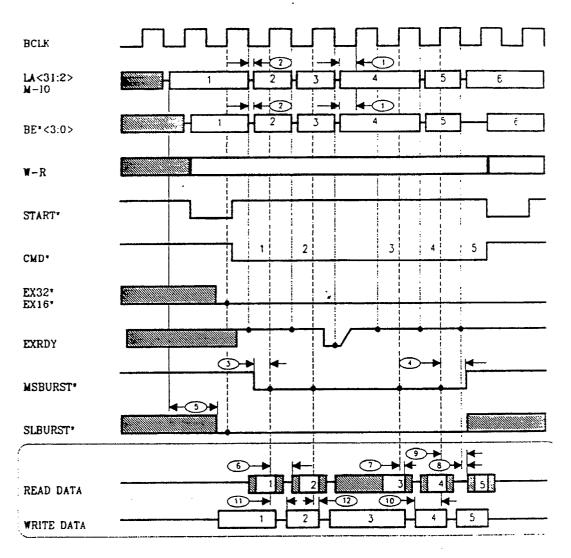

|    | 2.4.3 Burst Cycles                                                                                     | 50                                                                 |

|    | 2.5 DMA Cycles                                                                                         | . 55                                                               |

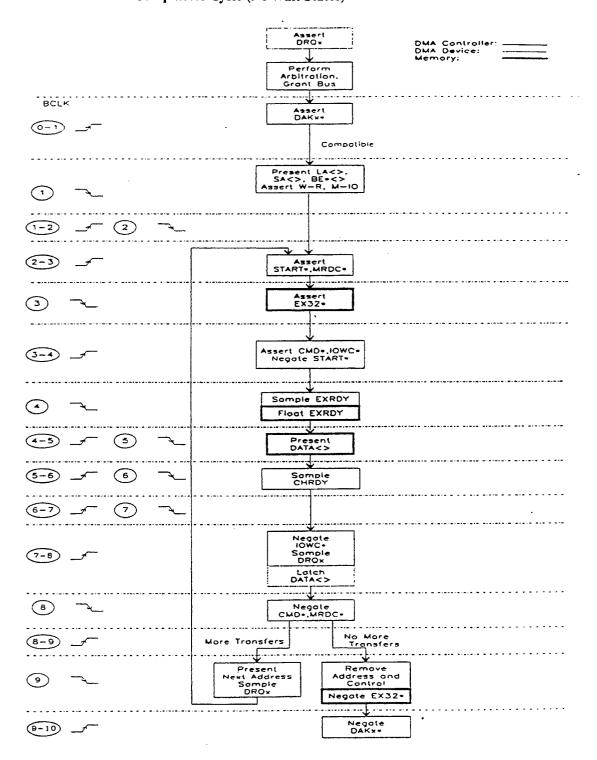

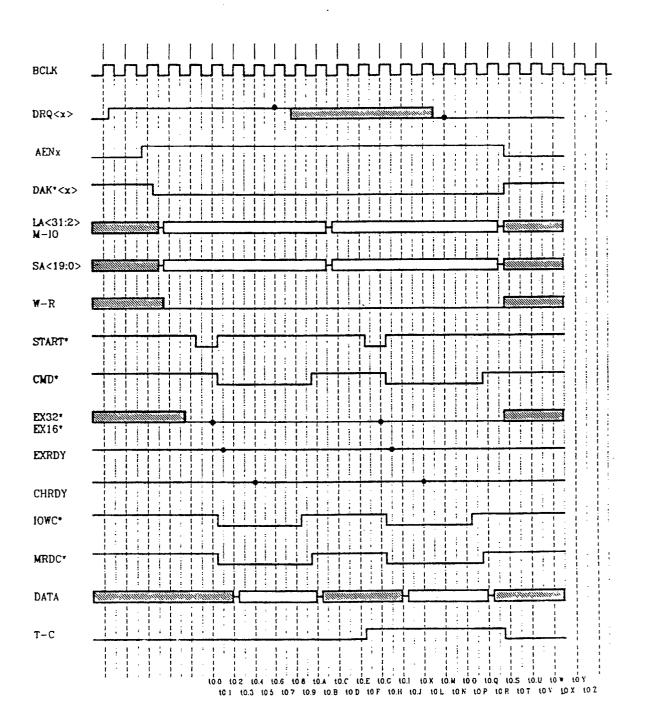

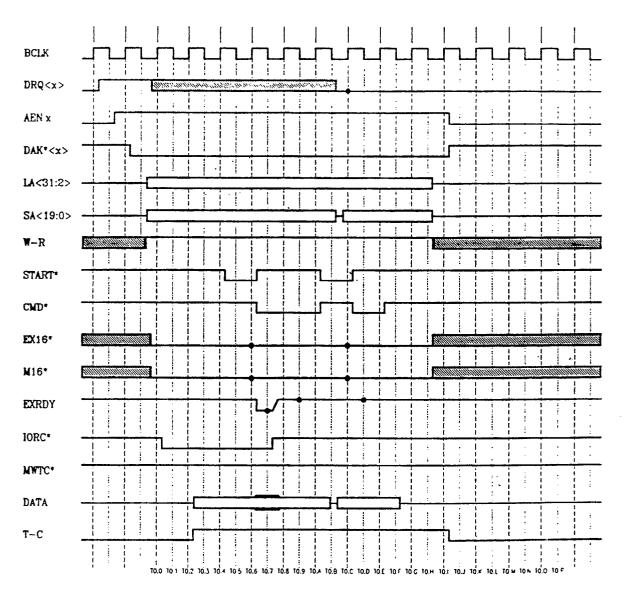

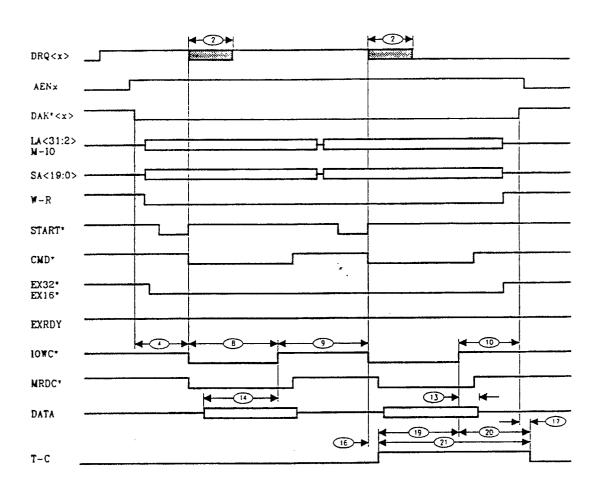

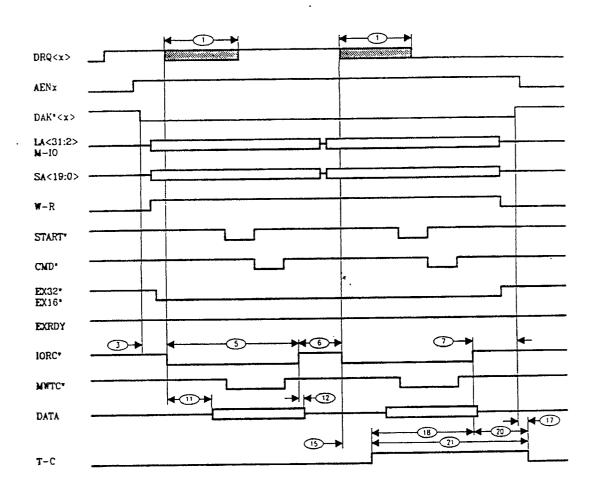

|    | 2.5.1 ISA Compatible DMA Cycles: ISA Compatible                                                        | 55<br>63                                                           |

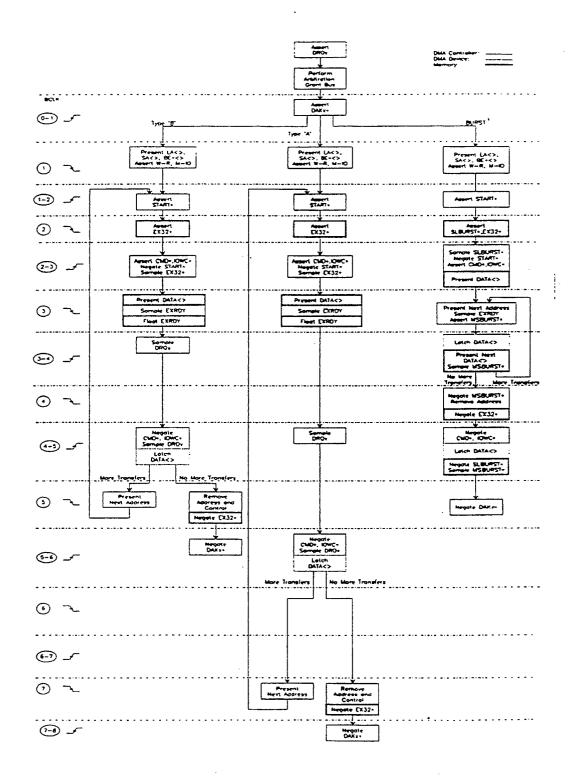

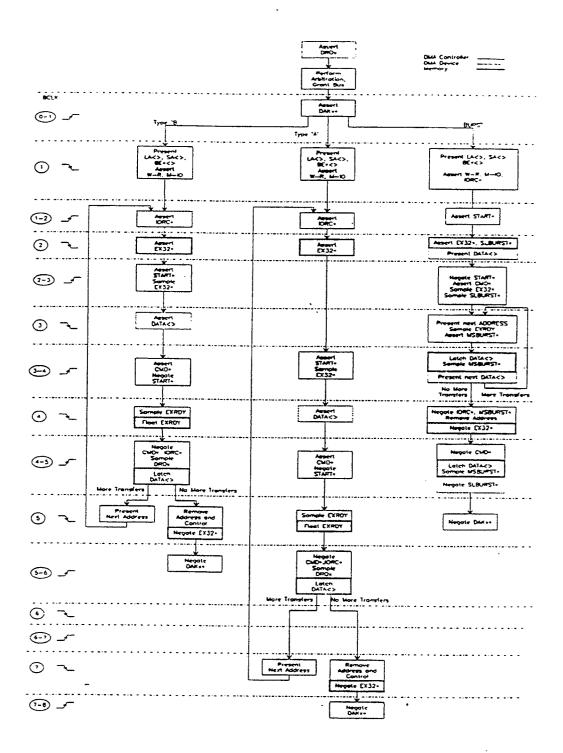

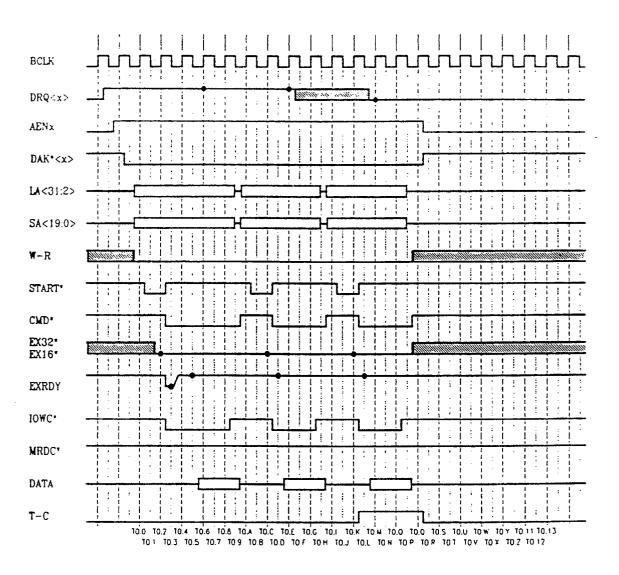

|    | 2.5.2 Type "A" DMA Cycles                                                                              | 63                                                                 |

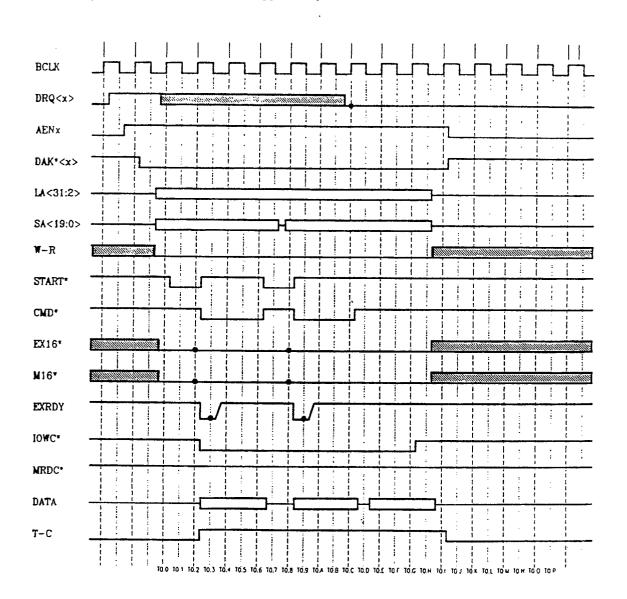

|    | 2.5.3 Type "B" DMA Cycles                                                                              | 68                                                                 |

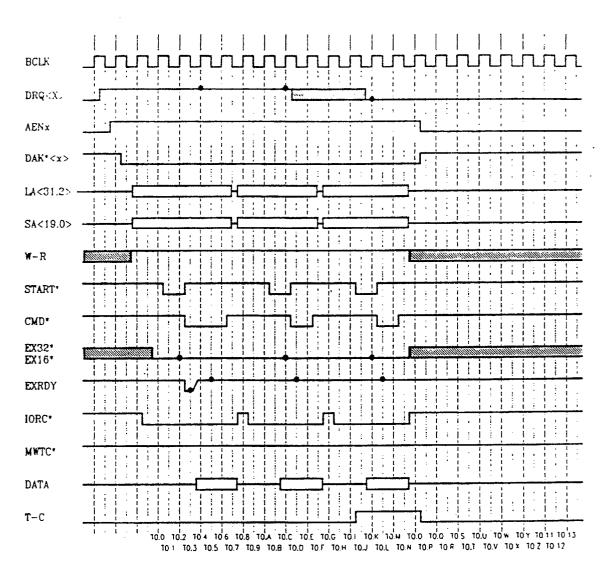

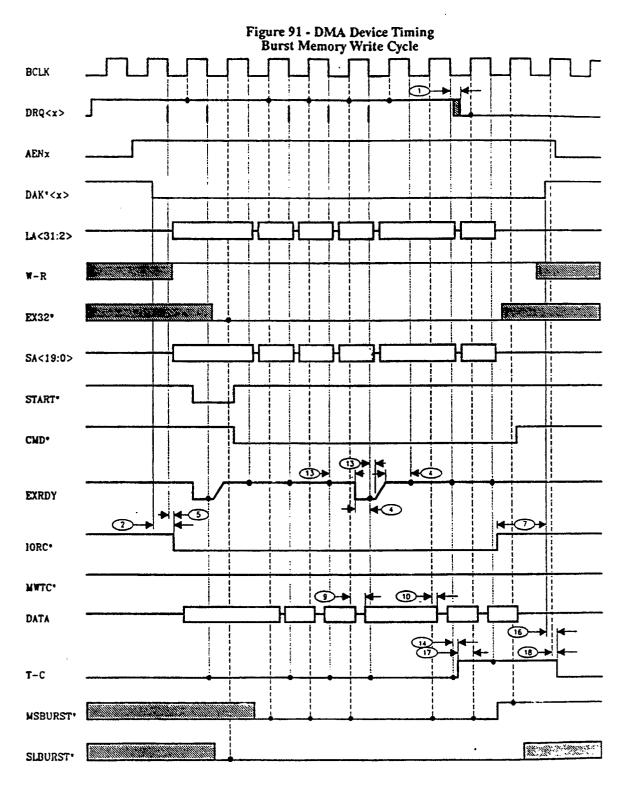

|    | 2.5.4 Burst DMA (Type "C") Cycles                                                                      | 73                                                                 |

| 2.6 Data    | a Bus Translations                                                           | 79          |

|-------------|------------------------------------------------------------------------------|-------------|

| 2.6.1       | 32-bit EISA Bus Master to 16-bit EISA Slave Transactions                     | 79          |

| 2.6.2       | 16-bit EISA Bus Master to 32-bit EISA Slave Transactions                     | 83          |

| 2.6.3       | 32-bit EISA Bus Master to 16-bit ISA Slave Transactions                      | 83          |

| 2.6.4       | 32-/16-bit EISA Bus Master to 8-bit ISA Slave Transactions                   | 85          |

| 265         | 16-bit ISA Bus Master to EISA Slaves Transactions                            | 86          |

| 2.6.6       | 32-bit DMA Device to 16-bit EISA Memory Transactions                         | 92          |

| 267         | 16-bit DMA Device to 32-bit EISA Memory Transactions                         | 93          |

| 2.6.8       |                                                                              | 93          |

| 2.6.9       |                                                                              |             |

| 2.0.5       | Transactions                                                                 | 94          |

| 27 Lock     | ked Cycles                                                                   | 95          |

| 2.8 EIS     |                                                                              | 97          |

|             | Memory Slaves                                                                | 97          |

| 2.8.1       | I/O Slaves                                                                   | 103         |

| 2.8.3       | I/O Slaves Bus Masters Burst Bus Masters                                     | 104         |

| 2.0.5       | Ruret Ruc Macters                                                            | 110         |

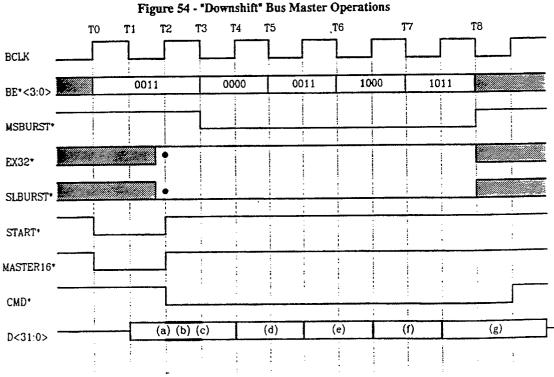

| 2.0.7       | Downshift Burst Bus Masters                                                  | 113         |

| 2.0.5       | DMA Devices                                                                  | 115         |

| 2,6.0       | 2.8.6.1 Non-Burst EISA DMA Devices                                           | 119         |

|             | 2.8.6.2 Burst EISA DMA Devices                                               | 122         |

|             | 2.8.6.3 Misaligned DMA Transfers                                             | 131         |

| 2.8.7       | System Board                                                                 | 131         |

| 2.0.7       | 2.8.7.1 Main Memory Access                                                   | 131         |

|             | 2.8.7.2 Back-to-Back I/O Delay                                               | 132         |

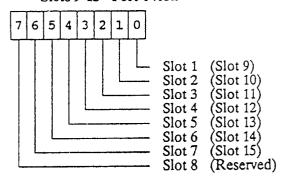

|             | 2.8.7.3 Slot-specific I/O                                                    | 132         |

|             | 2.8.7.4 I/O Address Decoding                                                 | 134         |

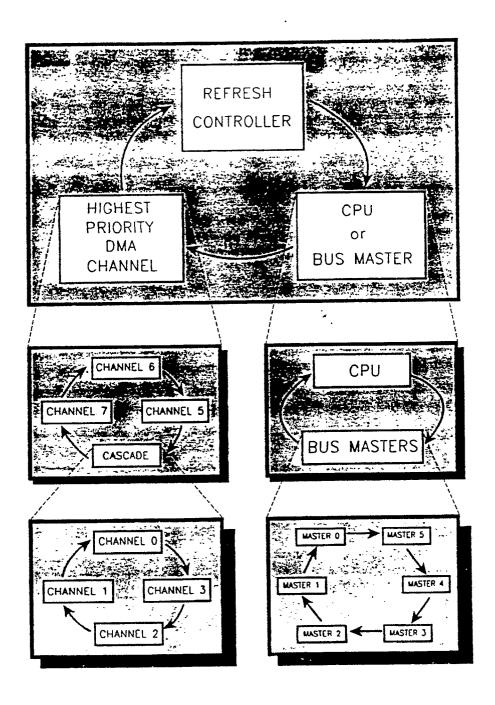

| 20 Rue      | Arbitration ·                                                                | 135         |

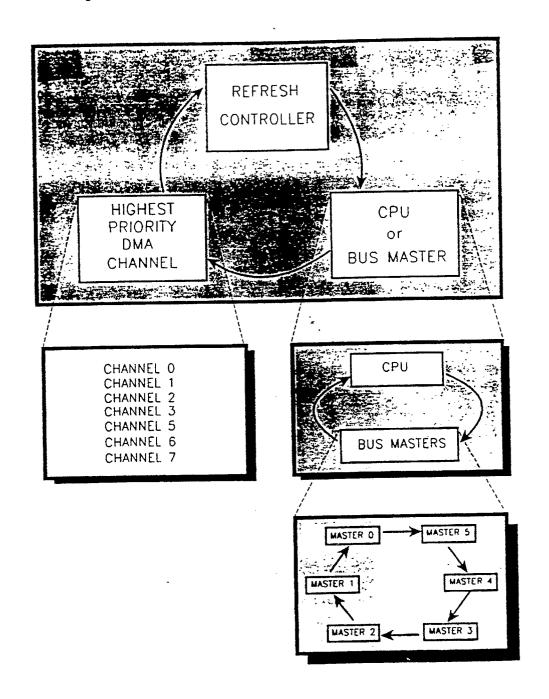

| 2.9.1       | System Arbitration Priorities                                                | 139         |

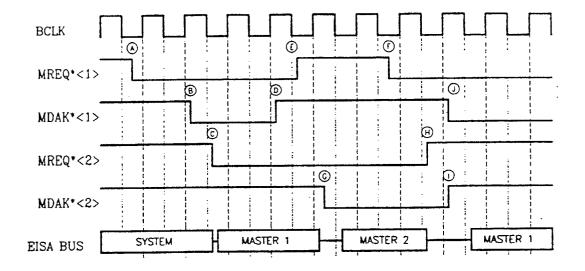

| 2.9.2       |                                                                              | 142         |

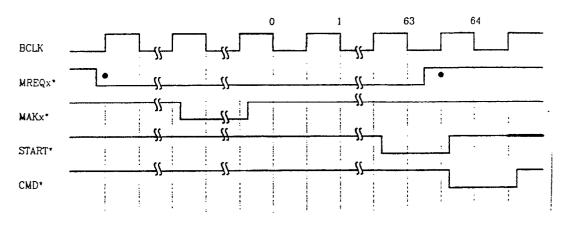

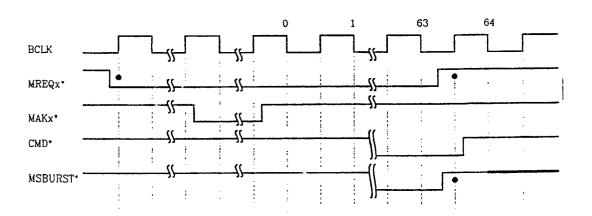

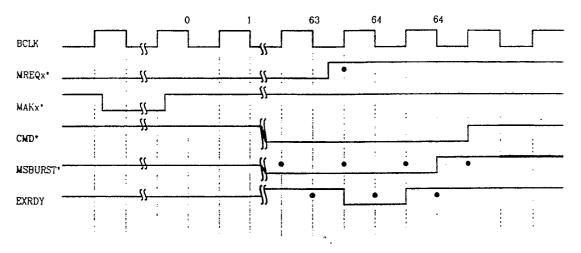

| 2.9.3       | EISA Bus Master Arbitration Cycle Descriptions                               | 147         |

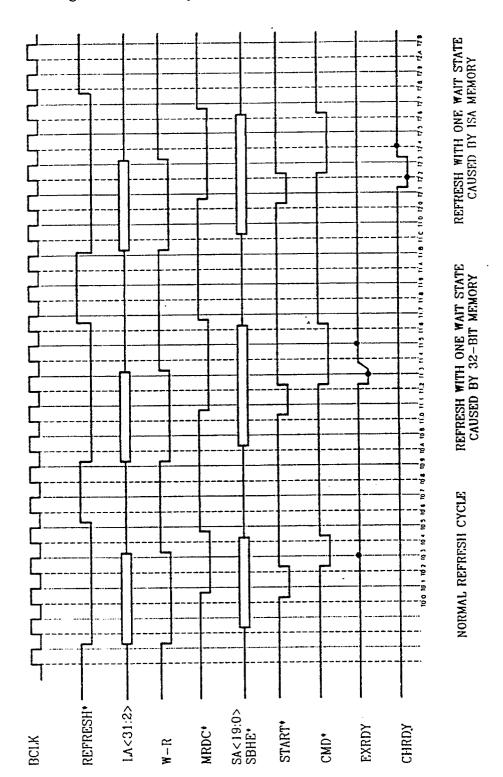

|             | nory Refresh                                                                 | 149         |

|             | trical Specifications                                                        | 151         |

|             | Power Consumption                                                            | 151         |

| 2.11.1      | DC Characteristics                                                           | 151         |

| 2.11.2      | Signal Routing and Capacitive Loading Requirements                           | 154         |

| 2.11.3      | AC Characteristics                                                           | 155         |

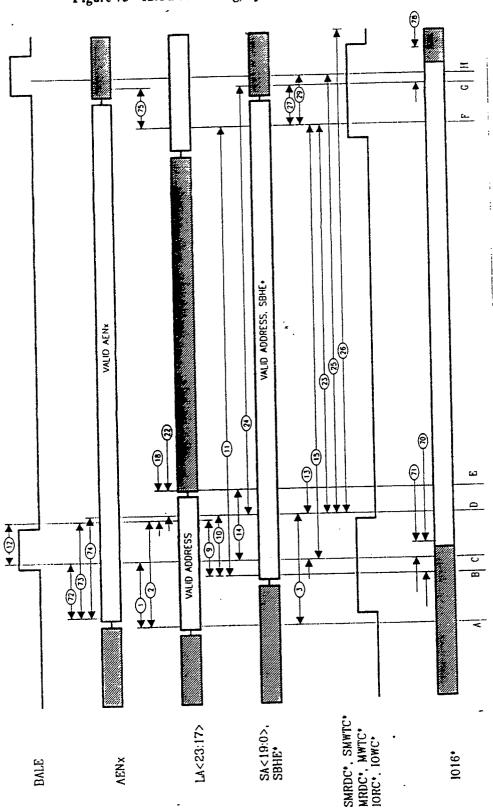

| 2.11.7      | 2.11.4.1 ISA-compatible Timing Parameters                                    | 156         |

|             | 2.11.4.2 EISA, DMA, and Refresh Timing Parameters                            | 181         |

| 2.12 Men    |                                                                              | 213         |

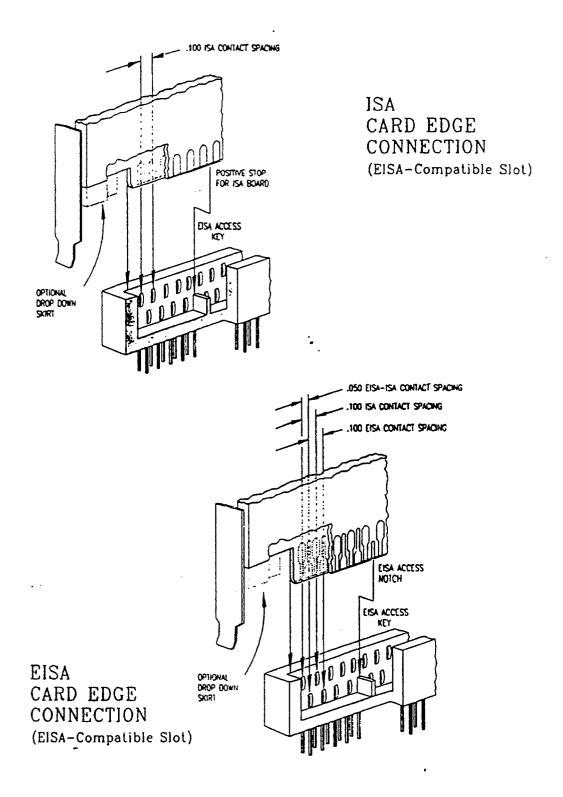

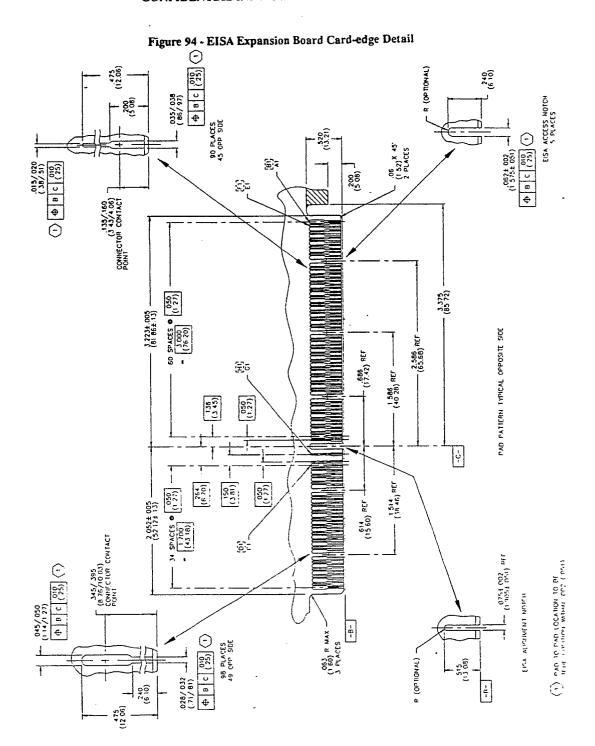

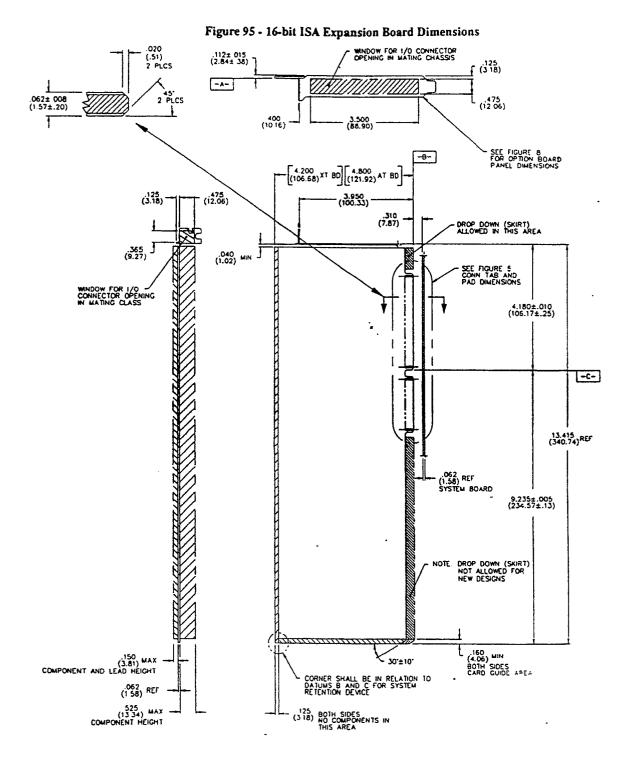

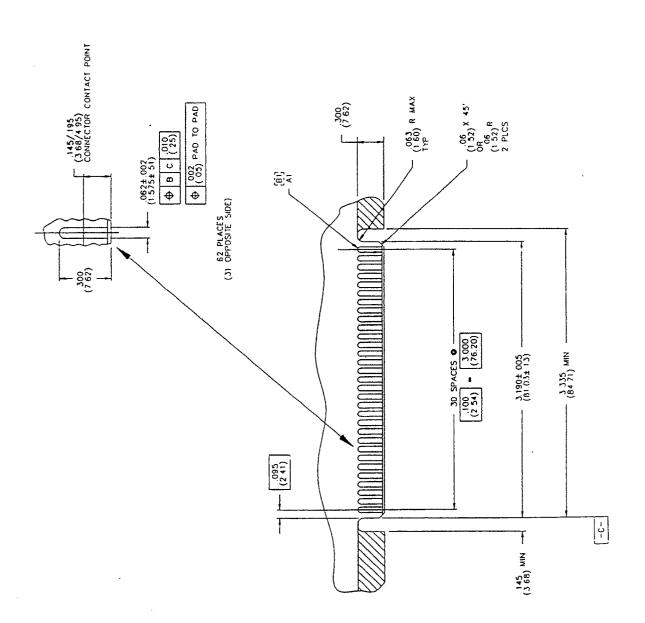

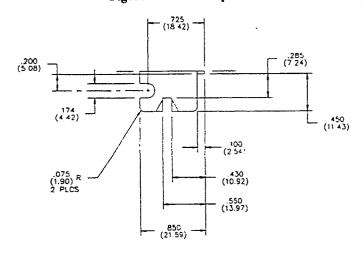

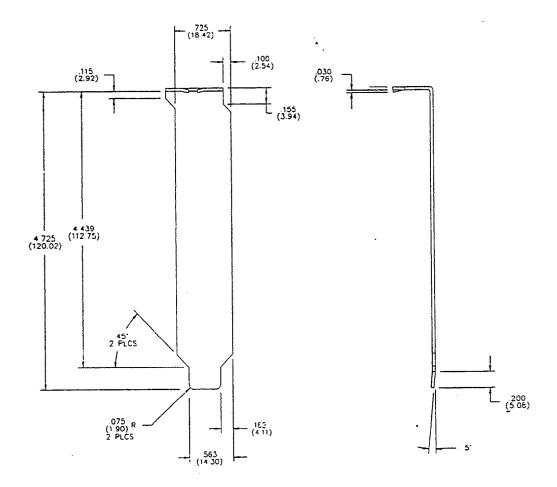

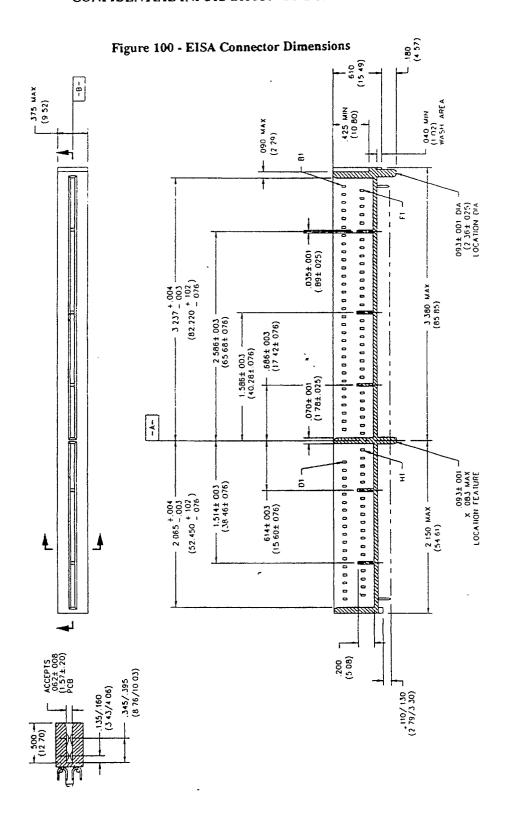

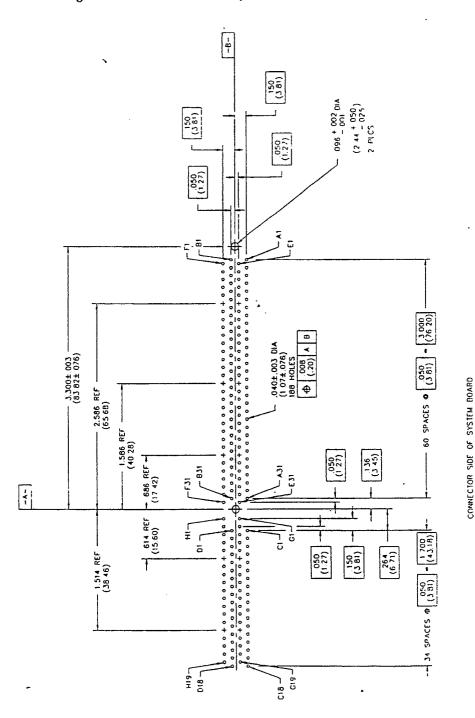

| 2.12 IVICU  | hanical Specifications A Connector and Expansion Board Description           | 213         |

| 2.13 2.13.1 |                                                                              | 214         |

| 2.13.1      | Physical Characteristics Connector Specifications                            | 215         |

|             | Connector Specifications                                                     | 226         |

|             | Pin Description                                                              | 228         |

|             | ard I/O Control Functions                                                    | <b>2</b> 35 |

|             | A Description DMA Controller Overview                                        | 235         |

| 3.1.1       |                                                                              | 236         |

| 3.1.2       | DMA Controller Description                                                   | 236         |

|             | 3.1.2.1 DMA Master Condition Operation 3.1.2.2 DMA Slave Condition Operation | 237         |

|             | J. 1. L. L. DIVITA DIAVE CUINGINON OPPLIANTA                                 |             |

| 3.1.3  | DMA Transfer Modes                                                                                                                  | 237         |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|-------------|

|        | 3.1.3.1 Single Transfer Mode                                                                                                        | 237         |

|        | 3.1.3.2 Block Transfer Mode                                                                                                         | 237         |

|        | 3.1.3.3 Demand Transfer Mode                                                                                                        | 238         |

|        | 3.1.3.4 Cascade Mode                                                                                                                | 239         |

| 3.1.4  |                                                                                                                                     | 239         |

|        | Transfer Types                                                                                                                      | 239         |

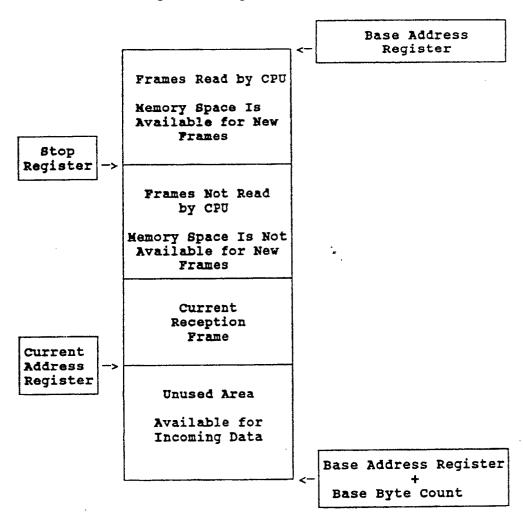

| 3.1.5  | Auto Initialize                                                                                                                     | 240         |

| 3.1.6  |                                                                                                                                     |             |

| 3.1.7  |                                                                                                                                     | 241         |

| 3.1.8  | Software Commands                                                                                                                   | 243         |

| 3.1.9  |                                                                                                                                     | 243         |

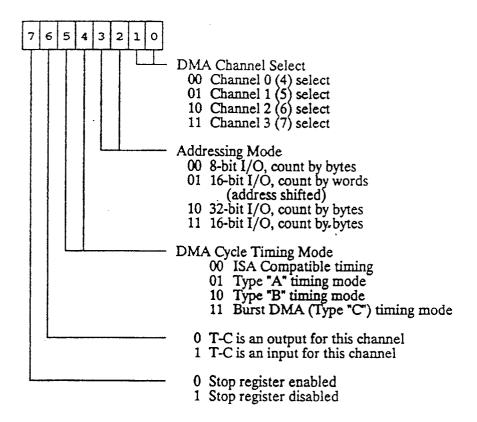

|        | 3.1.9.1 DMA Extended Mode Register                                                                                                  | 243         |

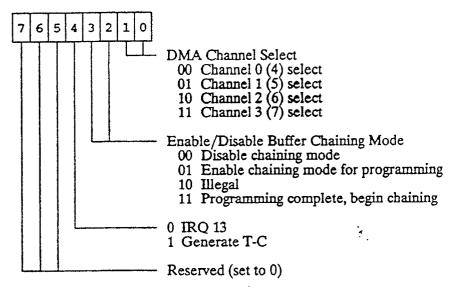

|        | 3.1.9.2 Chaining Mode Register                                                                                                      | 245         |

|        | 3.1.9.3 Chaining Mode Status Register                                                                                               | 247         |

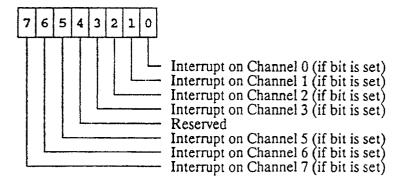

|        | 3.1.9.4 Channel Interrupt Status Register                                                                                           | 247         |

|        | 3.1.9.5 Address and Word Count Registers                                                                                            | 248         |

|        | 3.1.9.5.1 Base Word Count Register                                                                                                  |             |

|        | 3.1.9.5.2 Current Word Count Regis                                                                                                  | ter 249     |

|        | 3.1.9.5.3 Base Address Register                                                                                                     | 250         |

|        | 3.1.9.5.4 Current Address Register                                                                                                  | 251         |

|        | 3.1.9.5.5 Address and Word Count P                                                                                                  |             |

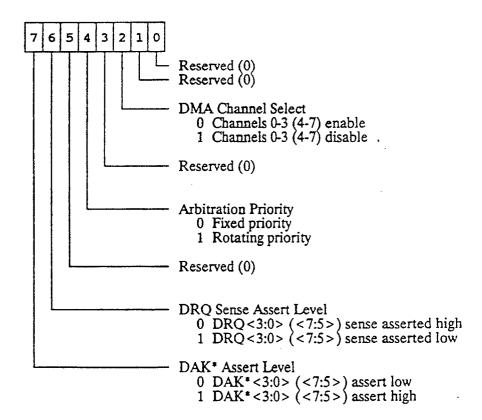

|        | 3 1 9 6 DMA Command Register                                                                                                        | 256         |

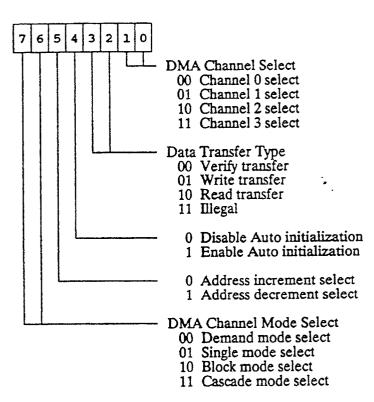

|        | 3.1.9.7 Mode Register                                                                                                               | 257         |

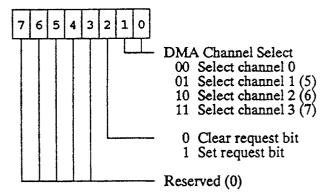

|        | 3.1.9.8 Request Register                                                                                                            | 258         |

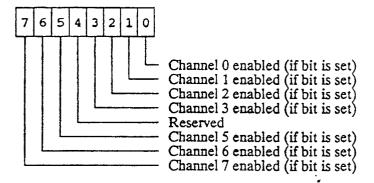

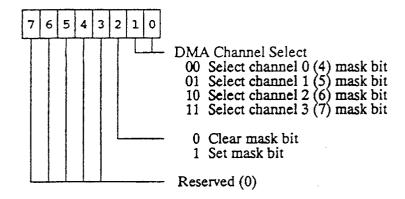

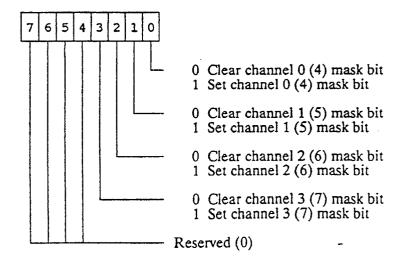

|        | 3.1.9.9 Mask Registers                                                                                                              | 258<br>258  |

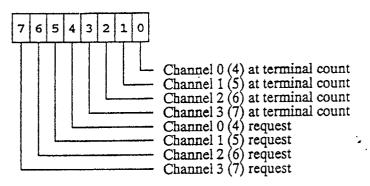

|        | 2.1.0.10 DMA Ctatus Desister                                                                                                        | 260         |

| 2 1 10 | 3.1.9.10 DMA Status Register                                                                                                        | 261         |

| 3.1.10 |                                                                                                                                     | 265         |

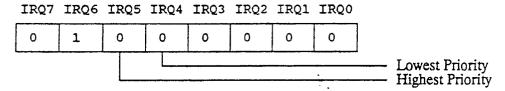

|        | errupt Controller                                                                                                                   |             |

| 3.2.1  | Interrupt Controller I/O Address Map                                                                                                | 265<br>265  |

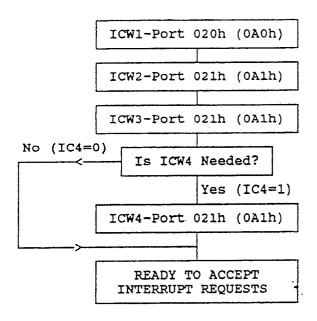

| 3.2.2  | Interrupt Sequence                                                                                                                  | 265<br>266  |

| 3.2.3  |                                                                                                                                     | 266         |

| 3.2.4  | Initialization and Control Registers                                                                                                | 268         |

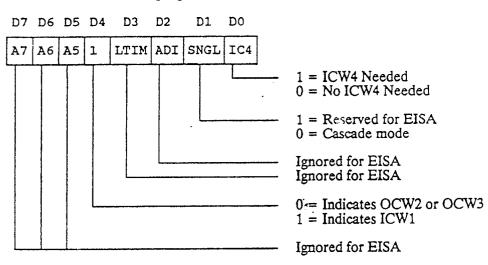

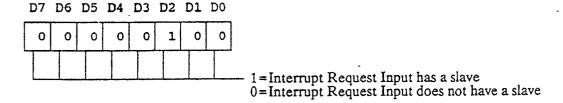

|        | 3.2.4.1 Initialization Command Word 1 (IC<br>3.2.4.2 Initialization Command Word 2 (IC<br>3.2.4.3 Initialization Command Word 3 (IC | CW1) 268    |

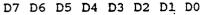

|        | 3.2.4.2 Initialization Command Word 2 (IC                                                                                           | CW2) 269    |

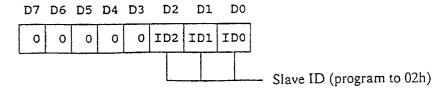

|        | 3.2.4.3 Initialization Command Word 3 (IC                                                                                           | CW3) 270    |

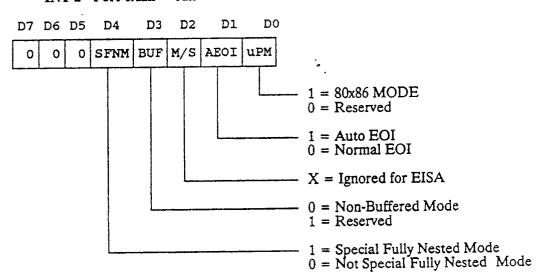

|        | 3.2.4.4 Initialization Command Word 4 (IC                                                                                           | CW4) 271    |

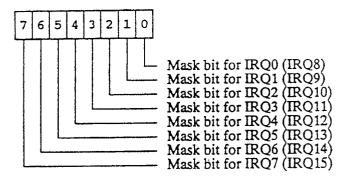

|        | 3.2.4.5 Interrupt Mask Register (OCW1)                                                                                              | 271         |

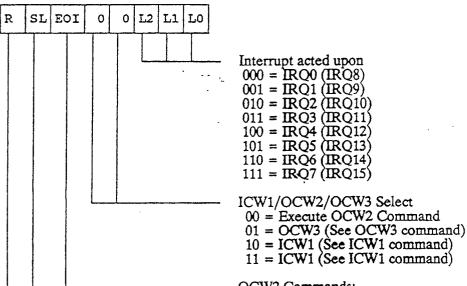

|        | 3.2.4.6 Operation Control Word 2 (OCW2)                                                                                             | ) 272       |

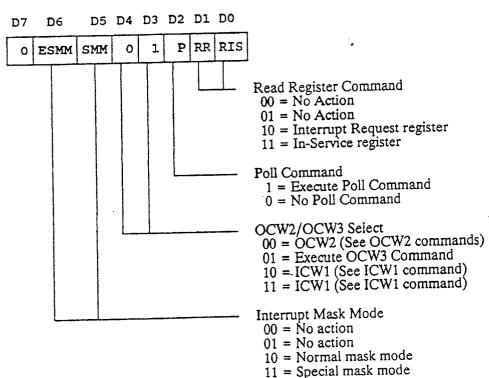

|        | 3.2.4.7 Operation Control Word 3 (OCW3)                                                                                             | ) 274       |

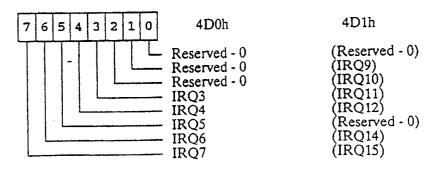

|        | 3.2.4.8 Edge/Level Control Register (ELC                                                                                            | (R) 275     |

|        | 3.2.4.9 Interrupt Request Register (IRR)                                                                                            | 276         |

|        | 3.2.4.10 In-Service Register (ISR)                                                                                                  | 276         |

| 3.2.5  | End-of-Interrupt                                                                                                                    | 277         |

| 5.4.5  | 3.2.5.1 End of Interrupt (EOI) Command                                                                                              | 277         |

|        | 3.2.5.2 Automatic End of Interrupt (AEOI)                                                                                           |             |

| 3.2.6  |                                                                                                                                     | 277         |

| 3.2.0  | Interrupt Controller Modes                                                                                                          | 277         |

|        | 3.2.6.1 Fully Nested Mode                                                                                                           |             |

|        | 3.2.6.2 Special Fully Nested Mode                                                                                                   | 278         |

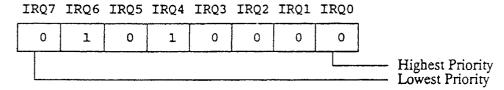

|        | 3.2.6.3 Fixed Priority Mode                                                                                                         | <b>27</b> 8 |

|        | 3.2.6.4 Rotating Priority Mode                                                                                                      | 278         |

|        | 3.2.6.5 Polled Mode                                                                                                                 | 279         |

|        | 3.2.6.6 Special Mask Mode                                                                                                           | • 280       |

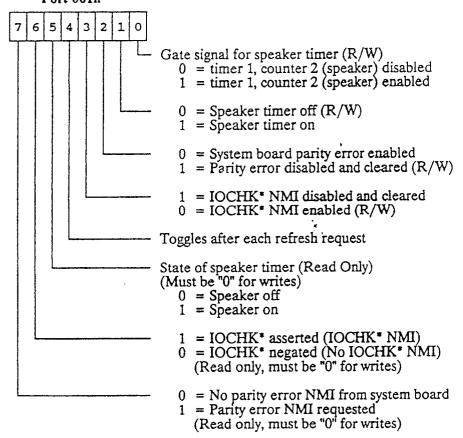

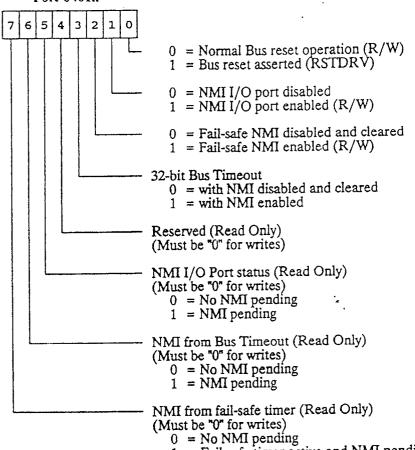

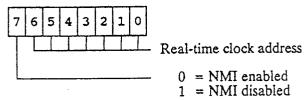

|    | 3.3 No:    | n-Maskable In   | terrupts (NMI)                                        | 281         |

|----|------------|-----------------|-------------------------------------------------------|-------------|

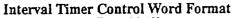

|    | 3.4 Inte   | rval Timers     | • • •                                                 | 287         |

|    | 3.4.1      |                 | ng the Interval Timers                                | 289         |

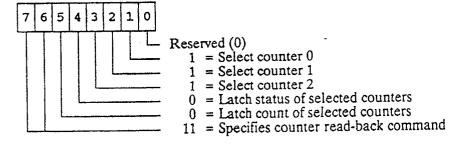

|    |            | 3411            | Interval Timer Control Word Format                    | 289         |

|    |            | 3.4.1.2         | Counter Operating Modes Counter Initial Count Value   | 290         |

|    |            | 3413            | Counter Initial Count Value                           | 291         |

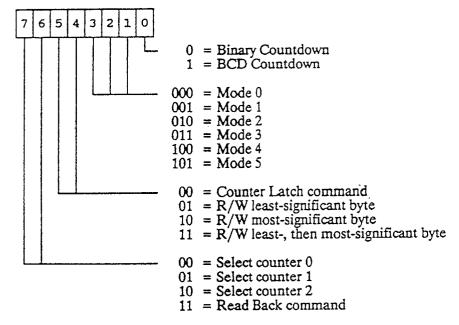

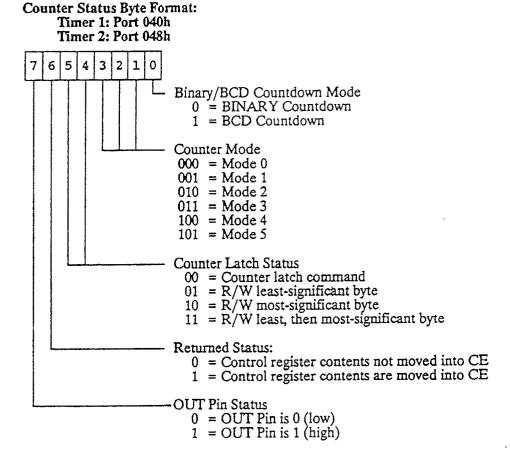

|    | 3.4.2      | Monitoring      | Timer Status                                          | 291         |

|    | 5.1.2      |                 | Counter Read Operation                                | 291         |

|    |            | 3422            | Counter Latch Command                                 | 292         |

|    |            | 3.4.2.3         | Counter Read-Back Command                             |             |

| 4. | EICA Sucta | em Configurat   |                                                       | 292         |

| ✝. |            |                 |                                                       | 294         |

|    |            |                 | d by Automatic Configuration                          | 295         |

|    | 4.1.1      | Expansion I     |                                                       | 295         |

|    |            | 4.1.1.1         |                                                       | 295         |

|    |            | 4.1.1.2         |                                                       | 295         |

|    | 4.1.2      | System Boar     |                                                       | 295         |

|    |            | 4.1.2.1         | System Board Peripherals That Use                     |             |

|    |            |                 | Slot-Specific I/O Space                               | 296         |

|    |            | 4.1.2.2         | System Board Peripherals That Use System              |             |

|    |            |                 | Board I/O Space                                       | 296         |

|    | 4.1.3      | Software Dr     | ivers That Require System Resources                   | 296         |

|    | 4.2 Con    | ifiguration Uti | lity                                                  | 297         |

|    | 4.3 Con    | figuration File | es •                                                  | 298         |

|    | 4.3.1      | Configuration   | on File Extensions                                    | 298         |

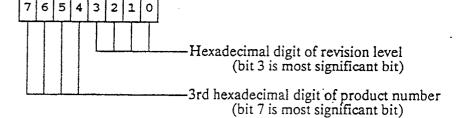

|    | 4.3.2      | Expansion E     | Soard Identifier (Product ID) tialization Information | 299         |

|    | 4.3.3      | I/O Port Ini    | tialization Information                               | 299         |

|    | 4.3.4      | System Reso     | ource Requests                                        | <b>2</b> 99 |

|    |            | figuration File | Filenames                                             | 300         |

|    | 4.5 The    | Configuration   | Procedure                                             | 301         |

|    | 4.5.1      | Configuration   | on File Syntax                                        | 301         |

|    | 452        | Symbol Con      | ventions                                              | 302         |

|    | 453        | Numerical V     | Value Conventions                                     | 303         |

|    | 454        | Kewword and     | d Field Specification Conventions                     | 303         |

|    | 4.6 Con    | figuration File | Format                                                | 305         |

|    |            |                 | ification Block                                       |             |

|    | 4.6.1      | Initialization  | Information Block                                     | 305         |

|    | 4.0.2      |                 |                                                       | 311         |

|    |            | 4.0.2.1         | I/O Port Initialization Statement Block               | 311         |

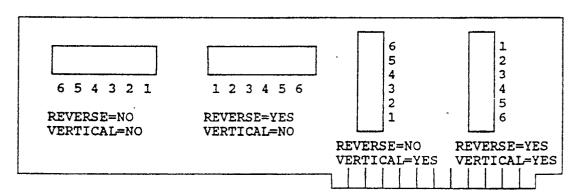

|    |            | 4.0.2.2         | Switch Configuration Statement Block                  | 313         |

|    |            | 4.6.2.3         |                                                       | 317         |

|    |            | 4.6.2.4         | SOFTWARE(Initialization) Statement Block              |             |

|    | 4.63       | TI DI COMO      | (Optional)                                            | 321         |

|    | 4.6.3      |                 | Statement Block                                       | 322         |

|    |            | 4.6.3.1         | CHOICE Statement Block                                | 325         |

|    |            | 4.6.3.2         | SUBCHOICE Statement Block                             | 327         |

|    |            | 4.6.3.3         | GROUP Statement Block                                 | 331         |

|    | 4.6.4      | Resource Do     | escription Block                                      | 334         |

|    |            | 4.6.4.1         | DMA Channel Description Block                         | 335         |

|    |            | 4.6.4.2         | Interrupt Description Block                           | 338         |

|    |            | 4.6.4.3         | I/O Port Description Block                            | 339         |

|    |            | 4.6.4.4         | Memory Description Block                              | 341         |

|    |            | 4.6.4.5         | INIT Statements                                       | 345         |

|    |            |                 |                                                       |             |

|    | 4.6.5     | Resource Group                                             | 348 |

|----|-----------|------------------------------------------------------------|-----|

|    |           | 4.6.5.1 LINK Groups                                        | 348 |

|    |           | 4.6.5.2 COMBINE Groups                                     | 349 |

|    |           | 4.6.5.2 COMBINE Groups 4.6.5.3 Free Groups                 | 351 |

|    | 4.6.6     | PORTVAR(j) Variable                                        | 352 |

|    |           | em Board Configuration File                                | 353 |

|    |           | Board Identification Block                                 | 353 |

|    |           |                                                            | 353 |

|    |           | System Description Block St. OT Statement Block (Optional) | 355 |

|    | 4.7.3     |                                                            | 356 |

|    |           | A System ROM Operations                                    |     |

|    | 4.8.1     | EÍSA System ROM BIOS Routine Calls                         | 356 |

|    |           | 4.8.1.1 Identify System Board Type                         | 357 |

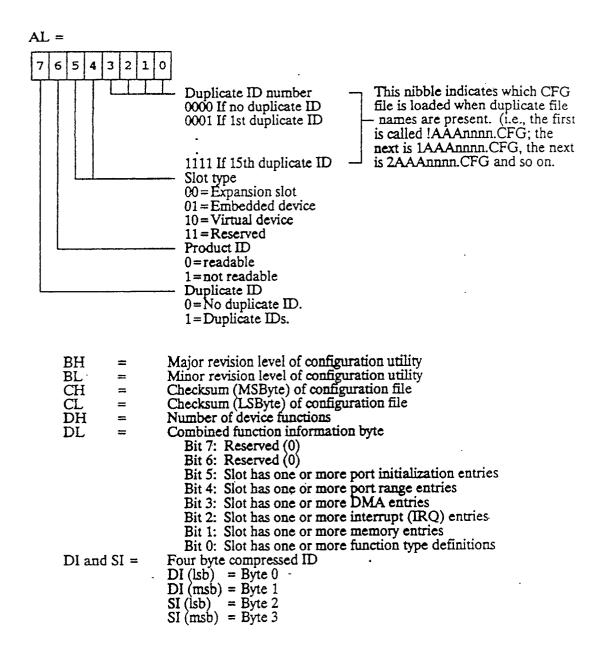

|    |           | 4.8.1.2 Read Slot Configuration Information, INT 15h,      | 250 |

|    |           | AH = D8h, AL = 00h (or 80h)                                | 358 |

|    |           | 4.8.1.3 Read Function Configuration Information,           | 450 |

|    |           | INT 15h, $AH = 0D8h$ , $AL = 01h$ (or 81h)                 | 359 |

|    |           | 4.8.1.4 Clear Nonvolatile Memory, INT 15h, AH = D8h,       |     |

|    |           | AL=02h (or $82h$ )                                         | 368 |

|    | -         | 4.8.1.5 Write Nonvolatile Memory INT 15h, AH=D8h,          |     |

|    |           | AL=03h (or $83h$ )                                         | 368 |

|    | 4.8.2     | Initializing Nonvolatile Memory                            | 379 |

|    | 4.8.3     | Power-up Initialization of EISA Systems                    | 379 |

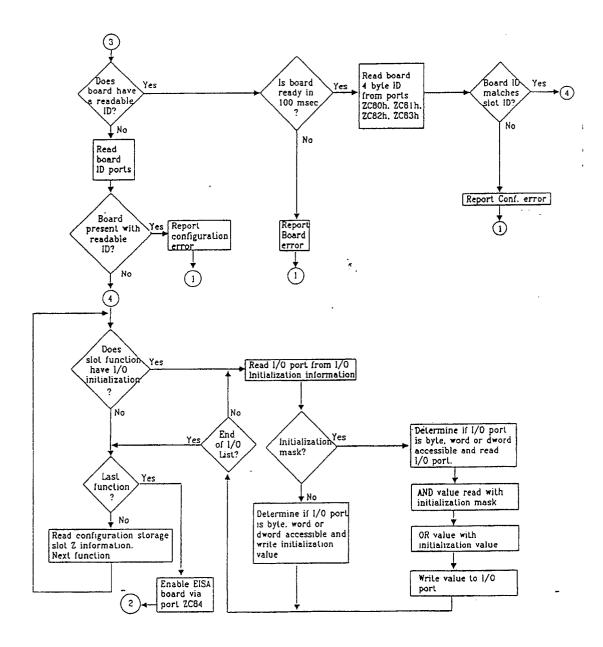

|    | 4.8.4     | Slot Initialization Sequence                               | 380 |

|    | 4.8.5     | Error Handling During Slot Initialization                  | 382 |

|    | 4.8.6     | Noncacheable Memory Map Initialization                     | 383 |

|    | 4.8.7     | Writable Memory Map Initialization                         | 383 |

|    |           | A System I/O Address Map                                   | 384 |

|    |           | Expansion Board Address Decoding                           | 385 |

|    |           | Embedded Slot Address Decoding                             | 387 |

|    | 4.9.3     |                                                            | 387 |

|    |           |                                                            | 389 |

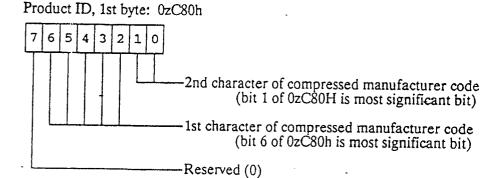

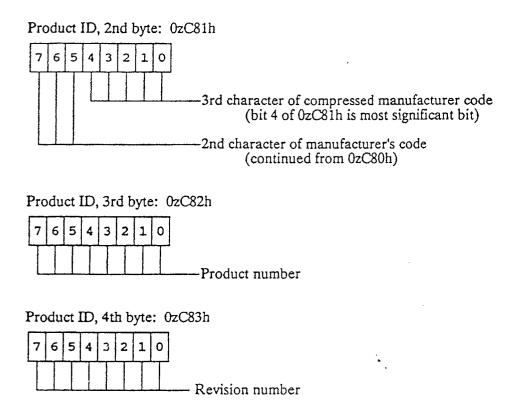

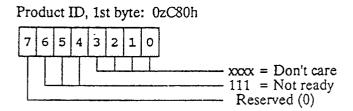

|    |           | A Product Identifier (ID)                                  | 390 |

|    |           | EISA System Board ID                                       | 392 |

|    | 4.10.2    | EISA Expansion Board Product ID                            |     |

|    |           | EISA Embedded Devices                                      | 394 |

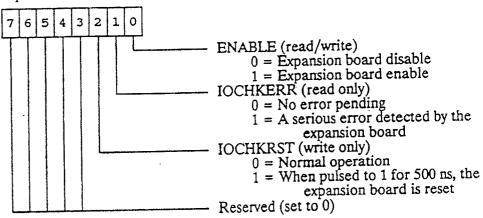

|    | 4.11 Exp  | ansion Board Control Bits                                  | 395 |

|    |           | em Software Use of Configuration Information               | 397 |

|    |           | Slot Search by Product Independent Device Driver           | 397 |

|    |           | Slot Search by a Product Dependent Device Driver           | 398 |

|    | 4.12.3    |                                                            | 399 |

|    | 4.13 Cres | ating TYPEs and SUBTYPEs for Devices                       | 400 |

|    | 4.13.1    | TYPE Strings                                               | 400 |

|    | 4.13.2    | SUBTYPE Strings                                            | 401 |

|    | 4.13.3    | Standard TYPE Table                                        | 402 |

|    | 4.14 Con  | afiguration Example                                        | 404 |

|    | 4.14.1    | Configuration File                                         | 404 |

|    | 4.14.2    | Read Slot Configuration Information BIOS Routine           | 408 |

|    | 4.14.3    | Read Function Configuration Information BIOS Routine Call  | 408 |

|    | 4.14.4    | Write Nonvolatile Memory BIOS Routine CALL                 | 416 |

| 5. | Glossary  |                                                            | 420 |

|    | 2.0000.   |                                                            |     |

| 1   | TOT | 0F  | FT | CII   | DFC |

|-----|-----|-----|----|-------|-----|

| . 1 |     | 111 |    | L) LJ | ハレン |

| CHRDY "Sample Window"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figure         |                                                                                                                | Page       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------|------------|

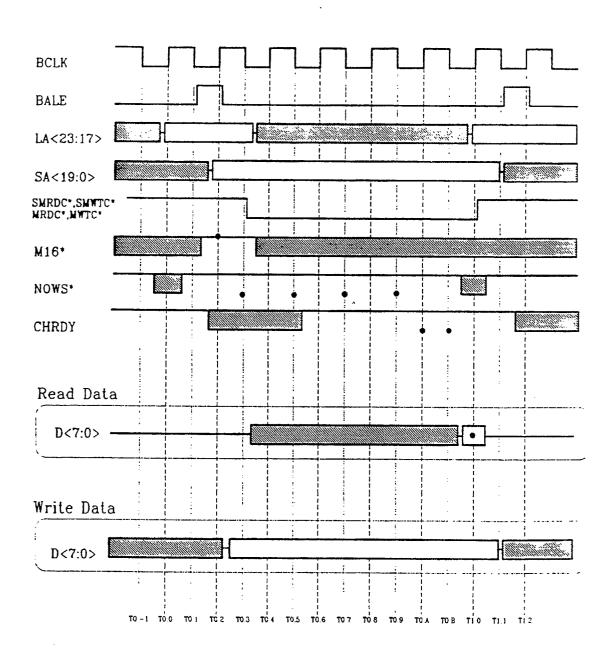

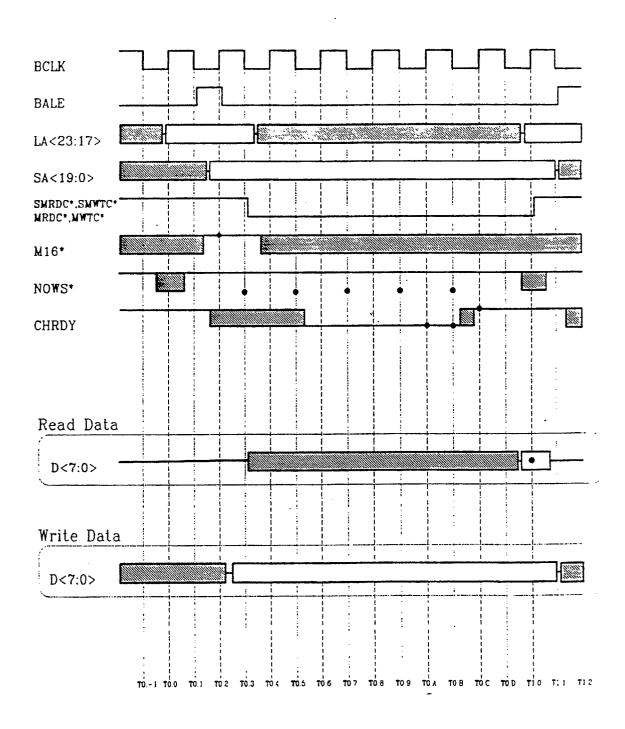

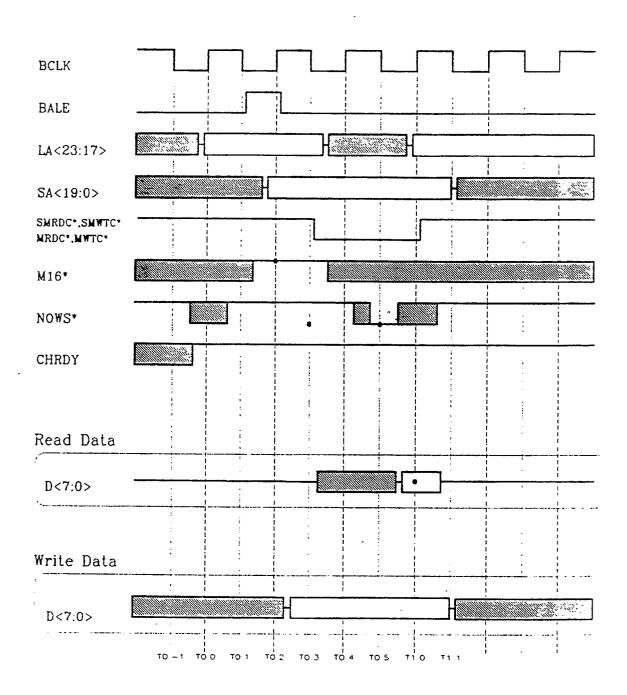

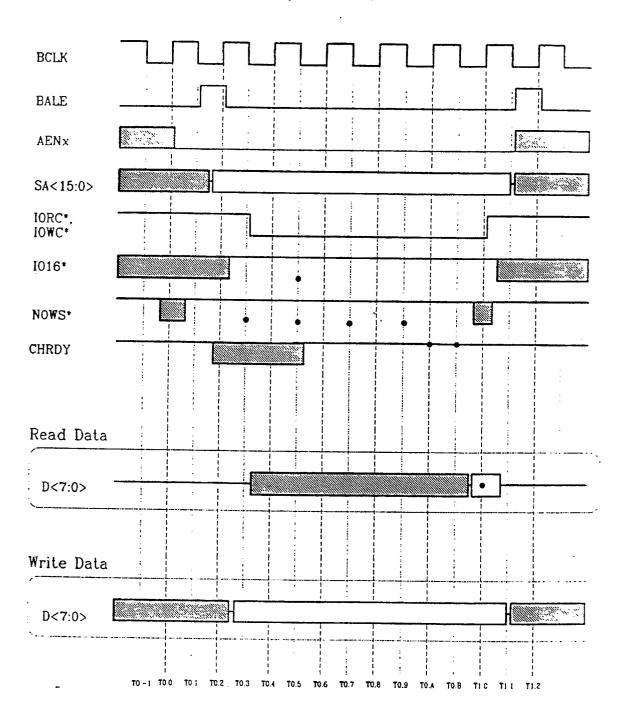

| Memory Access to 8-bit ISA Slave - Standard Cycle (6 BCLK)  Memory Access to 8-bit ISA Slave (7 BCLK)  Memory Access to 8-bit ISA Slave (3 BCLK)  I/O Access to 8-bit ISA Slave - Standard Cycle (6 BCLK)  I/O Access to 8-bit ISA Slave - Standard Cycle (6 BCLK)  Memory Access to 16-bit ISA Slave - Standard Cycle (3 BCLK)  Memory Access to 16-bit ISA Slave - Standard Cycle (3 BCLK)  Memory Access to 16-bit ISA Slave - Standard Cycle (3 BCLK)  Memory Access to 16-bit ISA Slave (6 BCLK)  Memory Access to 16-bit ISA Slave (8 BCLK)  Memory Access to 16-bit ISA Slave (9 BCLK)  Memory Access to 16-bit ISA Memory With Conversion - Type "A" Cycle: Demand Read  Memory Access to 16-bit EISA Memory With Conversion - Type "B" Cycle: Demand Read  Memory Access to 16-bit EISA Memory With Conversion - Type "B" Cycle: Demand Read  Memory Access to 16-bit EISA Memory With Conversion - Type "B" Cycle: Demand Write  Memory Access to 16-bit EISA Memory Wit | 1              | CHRDY "Sample Window"                                                                                          |            |

| Memory Access to 8-bit ISA Slave (7 BCLK)  Memory Access to 8-bit ISA Slave (3 BCLK)  I/O Access to 8-bit ISA Slave - Standard Cycle (6 BCLK)  I/O Access to 8-bit ISA Slave (7 BCLK)  I/O Access to 8-bit ISA Slave (7 BCLK)  I/O Access to 8-bit ISA Slave (8 BCLK)  Memory Access to 16-bit ISA Slave (9 BCLK)  Memory Access to 16-bit ISA Slave (8 BCLK)  Memory Access to 16-bit ISA Slave (8 BCLK)  I/O Access to 16-bit ISA Slave (8 BCLK)  Access to EISA Slave - Standard Cycle (3 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to EISA Slave - Standard Cycle (1 BCLK)  Access to E |                | Memory Access to 8-bit ISA Slave - Standard Cycle (6 BCLK)                                                     |            |

| Memory Access to 8-bit ISA Slave (3 BCLK)  I/O Access to 8-bit ISA Slave (3 BCLK)  I/O Access to 8-bit ISA Slave (7 BCLK)  Memory Access to 16-bit ISA Slave (3 BCLK)  Memory Access to 16-bit ISA Slave (6 BCLK)  Memory Access to 16-bit ISA Slave (8 BCLK)  Memory Access to 16-bit ISA Slave (9 BCLK)  Memory Access to 16-bit ISA Memory With Conversion  Memory Acce | 3              | Memory Access to 8-bit ISA Slave (7 BCLK)                                                                      |            |

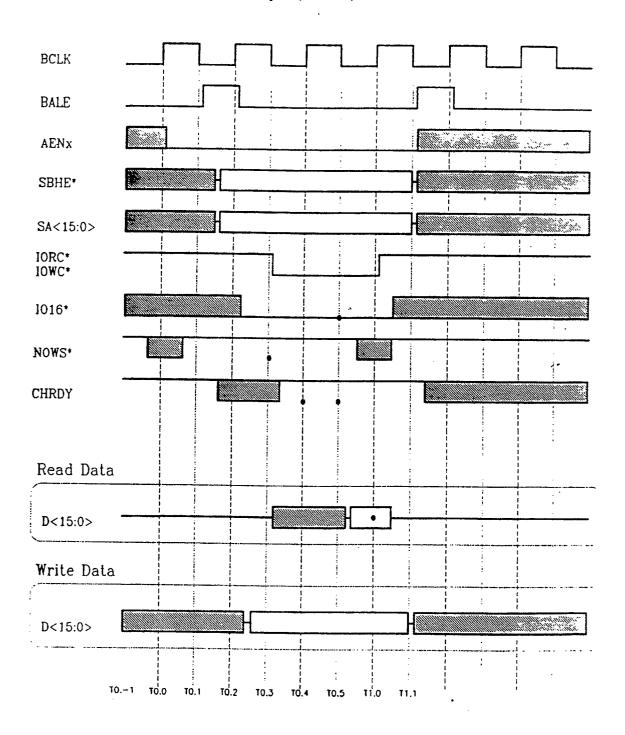

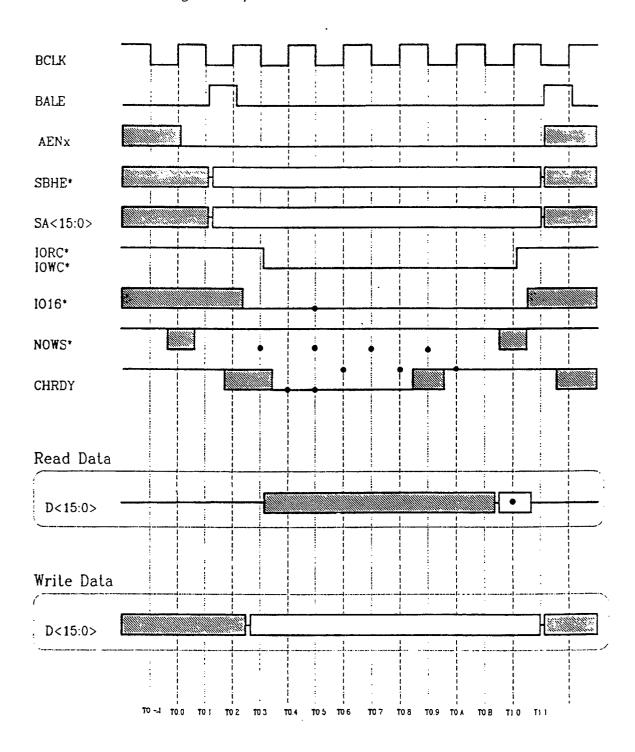

| 1/O Access to 8-bit ISA Slave - Standard Cycle (6 BCLK)   32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4              | Memory Access to 8-bit ISA Slave (3 BCLK)                                                                      |            |

| 7 I/O Access to 8-bit ISA Slave (3 BCLK) 8 Memory Access to 16-bit ISA Slave (5 BCLK) 9 Memory Access to 16-bit ISA Slave (6 BCLK) 10 Memory Access to 16-bit ISA Slave (6 BCLK) 11 I/O Access to 16-bit ISA Slave (2 BCLK) 12 I/O Access to 16-bit ISA Slave (2 BCLK) 13 32-bit Master to 32-bit ISA Slave (6 BCLK) 14 32-bit Master to 32-bit Slave Memory Read Accesses 15 Access to ISA Slave - Standard Cycle (3 BCLK) 16 Access to EISA Slave - 3 BCLK and Standard (2 BCLK) 17 32-bit Master to 32-bit Slave Memory Write Accesses 18 32-bit Master to 32-bit Slave Burst Read Transfers 19 Access to EISA Slave - COMPRESSED Cycle (1.5 BCLK) 10 32-bit Master to 32-bit Slave Burst Read Transfers 11 32-bit Master to 32-bit Slave Burst Write Transfers 12 32-bit DMA Slave - Burst Cycles (With and Without Wait States) 13 32-bit DMA Read Transfer from 32-bit Memory - Type "A," "B," 14 and Burst Cycles (No Wait States) 15 32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle 16 (No Wait States) 17 32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle 18 (No Wait States) 19 Access to Memory Without Conversion - Compatible Cycle 19 Cycles (No Wait States) 20 32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," 21 and Burst Cycles (No Wait States) 22 32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle 23 32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle 24 DMA Transfer from Memory Without Conversion - Compatible Cycle: 25 Demand Read 26 DMA Transfer from Memory Without Conversion - Type "A" Cycle: 26 Demand Read 27 32-bit DMA Transfer from 16-bit EISA Memory with Conversion 28 DMA Transfer to Memory Without Conversion - Type "A" Cycle: 29 32-bit DMA Transfer to 16-bit EISA Memory with Conversion 20 DMA Transfer from Memory Without Conversion - Type "B" Cycle 21 Demand Read 22 32-bit DMA Transfer from 16-bit EISA Memory with Conversion 23 32-bit DMA Transfer from 16-bit EISA Memory with Conversion 24 DMA Transfer to Memory Without Conversion - Type "B" Cycle: 25 Demand Write 26 DMA Transfer form  | 5              | I/O Access to 8-bit ISA Slave - Standard Cycle (6 BCLK)                                                        |            |

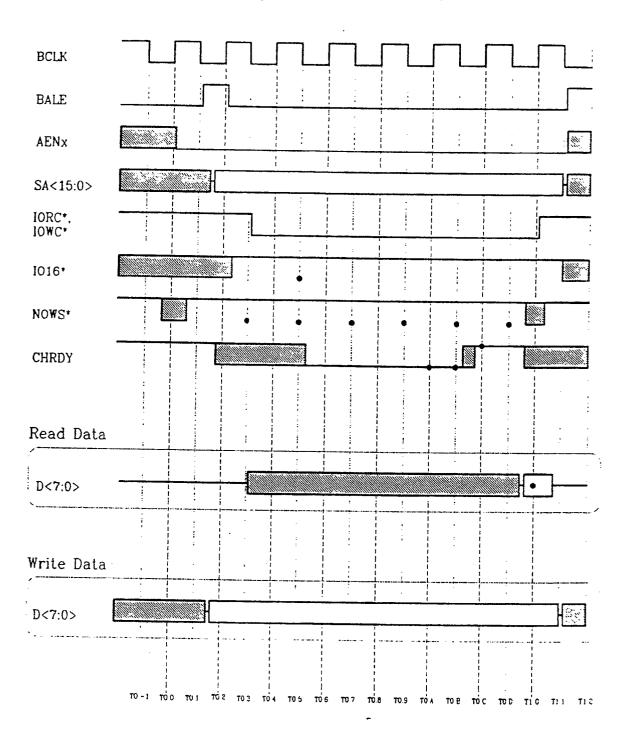

| I/O Access to 8-bit ISA Slave (3 BCLK)   34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6              | I/O Access to 8-bit ISA Slave (7 BCLK)                                                                         |            |

| Memory Access to 16-bit ISA Slave (6 BCLK)  Memory Access to 16-bit ISA Slave (2 BCLK)  I/O Access to 16-bit ISA Slave (6 BCLK)  32-bit Master to 32-bit Slave Memory Read Accesses  45  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles (No Wait States)  32-bit DMA Read Transfer from 32-bit Memory - Type "A," "B,"  and Burst Cycles (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B,"  and Burst Cycles (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle:  Demand Read  32-bit DMA Transfer from Memory Without Conversion - Type "A" Cycle:  Demand Read  Accest to Memory Without Conversion - Type "B" Cycle  Demand Read  Accest to Memory Without Conversion - Type "B" Cycle:  Demand Write  Accest to EISA Slave - 3 BCLK and Standard (2 BCLK)  Accest to EISA Slave - 3 BCLK and Standard (2 BCLK)  Accest to EISA Slave - 3 BCLK and Standard (2 BCLK)  Accest to EISA Slave - 10 Schlave - 10 Schlave - 10 S | 7              | I/O Access to 8-bit ISA Slave (3 BCLK)                                                                         |            |

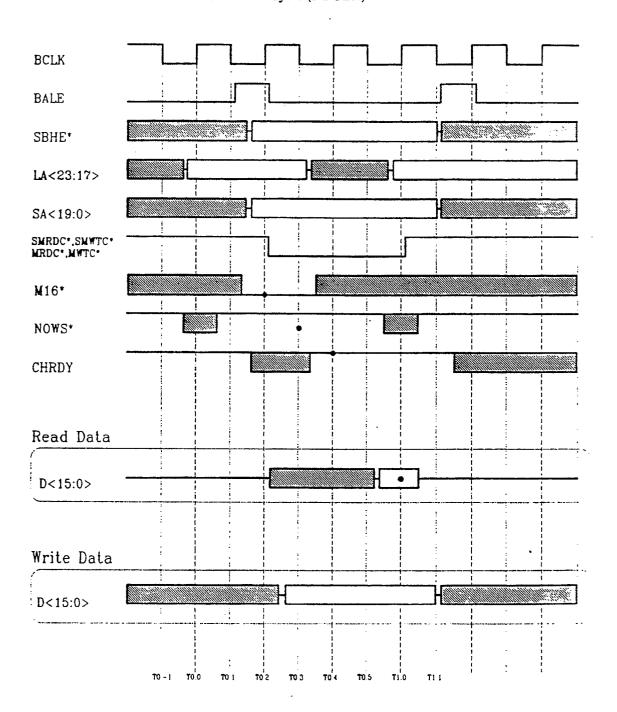

| Memory Access to 16-bit ISA Slave (2 BCLK)  1/O Access to 16-bit ISA Slave - Standard Cycle (3 BCLK)  1/O Access to 16-bit ISA Slave - Standard Cycle (3 BCLK)  1/O Access to 16-bit ISA Slave - Standard Cycle (3 BCLK)  1/O Access to 16-bit ISA Slave (6 BCLK)  1/O Access to 16-bit ISA Slave (6 BCLK)  1/O Access to 16-bit ISA Slave (6 BCLK)  1/O Access to 16-bit ISA Slave Accesses  1/O Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  1/O Access to EISA Slave - COMPRESSED Cycle (1.5 BCLK)  1/O Access to EISA Slave - OMPRESSED Cycle (1.5 BCLK)  1/O Access to EISA Slave - Burst Cycles (With and Without Wait States)  1/O Access to EISA Slave - Burst Cycles (With and Without Wait States)  1/O Access to EISA Slave - Burst Cycles (With and Without Wait States)  1/O Access to EISA Slave - Burst Cycles (With and Without Wait States)  1/O Access to EISA Slave - Burst Cycles (With and Without Wait States)  1/O Access to EISA Slave - Burst Cycles (With and Without Wait States)  1/O Access to EISA Slave - Burst Cycles (With and Without Wait States)  1/O Access to EISA Slave - Burst Cycles (With and Without Wait States)  1/O Access to EISA Slave - Burst Cycles (With and Without Wait States)  1/O Access to EISA Slave - Burst Write Transfers  1/O Access to EISA Slave - COMPRESSED Cycle (No Wait States)  1/O All Read Transfer from 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States)  1/O A Write Transfer to 32-bit Memory - Compatible Cycle: Demand Read  1/O DMA Transfer from Memory Without Conversion - Type "A" Cycle: Demand Read  1/O DMA Transfer from 16-bit EISA Memory with Conversion  1/O DMA Transfer from Memory Without Conversion - Type "B" Cycle Demand Read  1/O DMA Transfer from Memory Without Conversion - Type "B" Cycle: Demand Read  1/O DMA Transfer to Memory Without Conversion - Type "B" Cycle: Demand Write  1/O DMA Transfer to Memory Without Conversion - Type "B" Cycle: Demand | 8              | Memory Access to 16-bit ISA Slave - Standard Cycle (3 BCLK)                                                    |            |

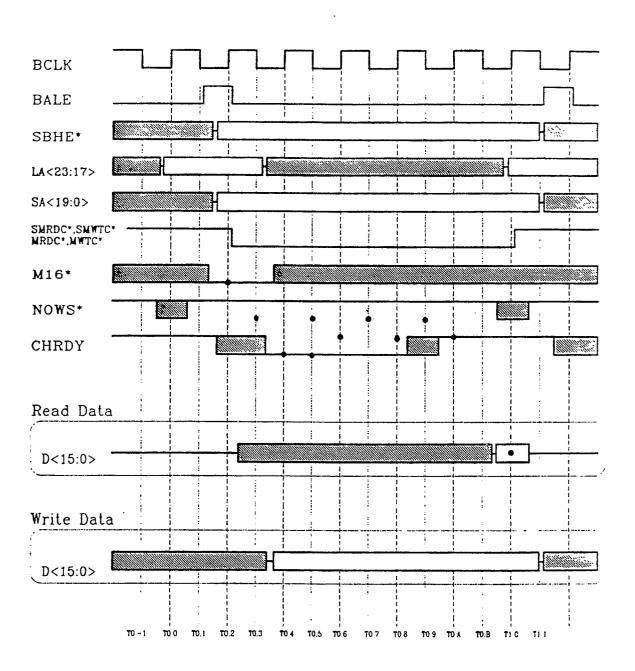

| 1/O Access to 16-bit ISA Slave - Standard Cycle (3 BCLK) 1/O Access to 16-bit ISA Slave (6 BCLK) 1/O Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles 1/O Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles 1/O Access to EISA Slave - COMPRESSED Cycle (1.5 BCLK) 1/O 32-bit Master to 32-bit Slave Burst Read Transfers 1/O 32-bit Master to 32-bit Slave Burst Write Transfers 1/O 32-bit Master to 32-bit Slave Burst Write Transfers 1/O 32-bit DMA Read Transfer from 32-bit Memory - Type "A," "B," 1/O and Burst Cycles (No Wait States) 1/O 32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle 1/O Wait States) 1/O 32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," 1/O and Burst Cycles (No Wait States) 1/O 32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," 1/O and Burst Cycles (No Wait States) 1/O DMA Transfer from Memory Without Conversion - Compatible Cycle: 1/O Demand Read 1/O DMA Transfer to Memory Without Conversion - Compatible Cycle: 1/O Demand Read 1/O DMA Transfer from Memory Without Conversion - Type "A" Cycle: 1/O Demand Read 1/O DMA Transfer from Memory Without Conversion - Type "A" Cycle: 1/O DMA Transfer to Memory Without Conversion - Type "A" Cycle: 1/O DMA Transfer to Memory Without Conversion - Type "A" Cycle: 1/O DMA Transfer to Memory Without Conversion - Type "B" Cycle: 1/O DMA Transfer from Memory Without Conversion - Type "B" Cycle: 1/O DMA Transfer from Memory Without Conversion - Type "B" Cycle: 1/O DMA Transfer from Memory Without Conversion - Type "B" Cycle: 1/O DMA Transfer from Memory Without Conversion - Type "B" Cycle: 1/O DMA Transfer from Memory Without Conversion - Type "B" Cycle: 1/O DMA Transfer to Memory Without Conversion - Type "B" Cycle: 1/O DMA Transfer to Memory Without Conversion - Type "B" Cycle: 1/O DMA Transfer to Memory Without Conversion - Type "B" C |                | Memory Access to 16-bit ISA Slave (6 BCLK)                                                                     |            |

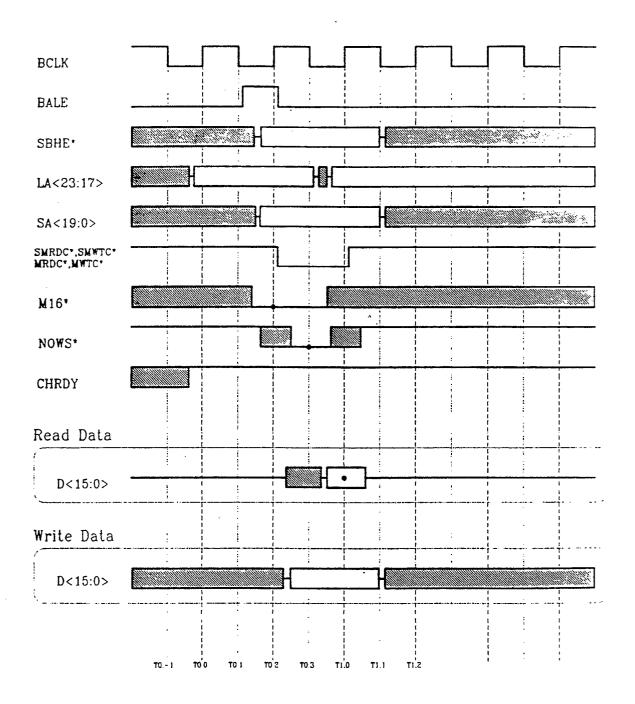

| 1/O Access to 16-bit ISA Slave (6 BCLK) 1/O Access to 16-bit ISA Slave (6 BCLK) 1/O Access to 16-bit ISA Slave (6 BCLK) 1/O Access to 132-bit Slave Memory Read Accesses 1/O Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles 1/O Access to EISA Slave - 3 BCLK and Standard (2 BCLK) 1/O Access to EISA Slave - COMPRESSED Cycle (1.5 BCLK) 1/O Access to EISA Slave - COMPRESSED Cycle (1.5 BCLK) 1/O Access to EISA Slave - Burst Read Transfers 1/O Access to EISA Slave - Burst Cycles (With and Without Wait States) 1/O Access to EISA Slave - Burst Cycles (With and Without Wait States) 1/O Access to EISA Slave - Burst Cycles (With and Without Wait States) 1/O Access to EISA Slave - Burst Cycles (With and Without Wait States) 1/O Access to EISA Slave - Burst Cycles (With and Without Wait States) 1/O Access to EISA Slave - Burst Cycles (With and Without Wait States) 1/O Access to EISA Slave - Burst Cycles (With and Without Wait States) 1/O Access to EISA Slave - Burst Cycles (With and Without Cycles (No Wait States)) 1/O Access to EISA Slave - Compatible Cycle (No Wait States) 1/O Access to EISA Slave - Compatible Cycle (No Wait States) 1/O Access to EISA Slave - Compatible Cycle (No Wait States) 1/O Access to EISA Slave - Compatible Cycle (No Wait States) 1/O Access to EISA Slave - Compatible Cycle (No Wait States) 1/O Access to EISA Slave - Compatible Cycle: Demand Write 1/O DAM Transfer from Memory Without Conversion - Compatible Cycle: Demand Write 1/O DAM Transfer from Memory Without Conversion - Type "A" Cycle Demand Write 1/O DAM Transfer to Memory Without Conversion - Type "A" Cycle Demand Read 1/O DAM Transfer to 16-bit EISA Memory with Conversion - Type "B" Cycle Demand Read 1/O DAM Transfer from Memory Without Conversion - Type "B" Cycle Demand Read 1/O DAM Transfer from Memory Without Conversion - Type "B" Cycle Demand Write 1/O DAM Transfer to Memory Without Conversion - Type "B" Cycle: Demand Write 1/O DAM Transfer to Memory Without Conversion - Type "B" Cycle: Demand Write 1/O DAM Transfer to Memory Wit |                | Memory Access to 10-bit ISA Slave (2 BCLK)                                                                     |            |

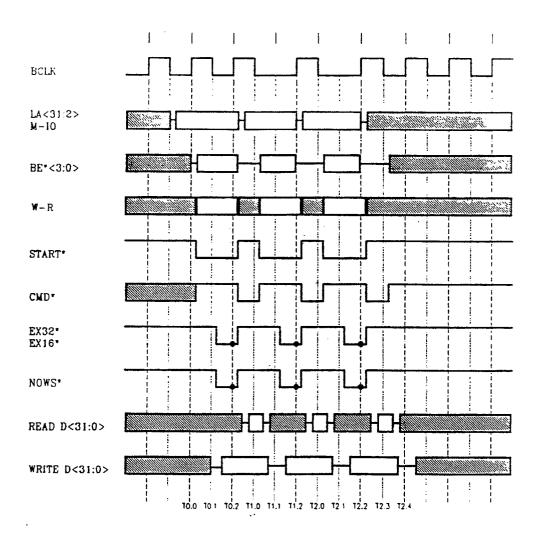

| 32-bit Master to 32-bit Slave Memory Read Accesses 45 32-bit Master to 32-bit Slave Memory Write Accesses 46 46 47 48 48 49 49 49 40 40 40 40 40 40 40 40 40 40 40 40 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                | I/O Access to 10-bit ISA Stave - Standard Cycle (5 DCLR)                                                       |            |

| 32-bit Master to 32-bit Slave Memory Write Accesses  Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles  Access to EISA Slave - COMPRESSED Cycle (1.5 BCLK)  32-bit Master to 32-bit Slave Burst Read Transfers  32-bit Master to 32-bit Slave Burst Write Transfers  32-bit Master to 32-bit Slave Burst Write Transfers  32-bit DMA Read Transfer from 32-bit Memory - Type "A," "B,"  and Burst Cycles (No Wait States)  32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B,"  and Burst Cycles (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  58  29  30-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  59  31-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  50  40  41  42  42  43  45  46  46  47  47  48  47  48  47  48  47  48  49  49  40  41  42  45  46  47  48  47  48  49  49  40  41  42  45  46  47  46  47  48  47  48  49  49  40  41  42  42  43  44  45  46  46  46  46  47  46  46  47  46  47  46  47  46  47  46  47  46  47  47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                | 1/U Access to 10-bit ISA Stave (0 BULK)                                                                        |            |

| Access to EISA Slave - 3 BCLK and Standard (2 BCLK) Cycles Access to EISA Slave - COMPRESSED Cycle (1.5 BCLK) Access to EISA Slave - COMPRESSED Cycle (1.5 BCLK) Access to EISA Slave - Burst Read Transfers Access to EISA Slave - Burst Write Transfers Access to EISA Slave - Burst Cycles (With and Without Wait States) Access to EISA Slave - Burst Cycles (With and Without Wait States) Access to EISA Slave - Burst Cycles (With and Without Wait States) Access to EISA Slave - Burst Cycles (With and Without Wait States) Access to EISA Slave - Burst Cycles (With and Without Wait States) Access to EISA Slave - Burst Cycles (With and Without Wait States) Access to EISA Slave - Burst Cycles (With and Without Prescription of Prescription |                |                                                                                                                |            |

| Access to EISA Slave - COMPRESSED Cycle (1.5 BCLK) 32-bit Master to 32-bit Slave Burst Read Transfers 53 19 Access to EISA Slave - Burst Write Transfers 54 20 32-bit DMA Read Transfer from 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States) 57 28 32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle (No Wait States) 58 29 32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States) 59 20 32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States) 59 20 32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States) 60 21 DMA Transfer from Memory Without Conversion - Compatible Cycle: Demand Read 61 DMA Transfer to Memory Without Conversion - Compatible Cycle: Demand Read 62 DMA Transfer from 16-bit EISA Memory with Conversion - Type "A" Cycle: Read 63 DMA Transfer to Memory Without Conversion - Type "A" Cycle Demand: Write 64 DMA Transfer to Memory Without Conversion - Type "A" Cycle Demand: Write 65 DMA Transfer to 16-bit EISA Memory with Conversion - Type "A" Cycle: Write 66 DMA Transfer from Memory Without Conversion - Type "B" Cycle Demand Read 67 DMA Transfer from Memory Without Conversion - Type "B" Cycle Demand Read 68 DMA Transfer from Memory Without Conversion - Type "B" Cycle Demand Read 69 DMA Transfer from Memory Without Conversion - Type "B" Cycle Demand Read 70 DMA Transfer from Memory Without Conversion - Type "B" Cycle: Demand Read 71 DMA Transfer from 16-bit EISA Memory with Conversion - Type "B" Cycle: Read 72 DMA Transfer from Memory Without Conversion - Type "B" Cycle: Demand Write 73 DMA Transfer from 16-bit EISA Memory with Conversion - Type "B" Cycle: Read 74 DMA Transfer to Memory Without Conversion - Type "B" Cycle: Demand Write 75 Demand Write 76 Demand Write 77 Demand Write 77 Demand Write 78 DMA Transfer to 16-bit EISA Memory with Conversion                                                                                                                                                |                | Access to FICA Slave - 3 RCI K and Standard (2 RCI K) Cycles                                                   |            |

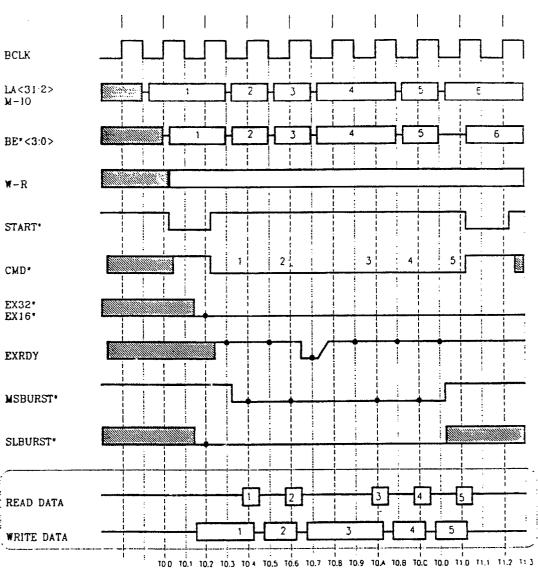

| 32-bit Master to 32-bit Slave Burst Read Transfers 32-bit Master to 32-bit Slave Burst Write Transfers 32-bit Master to 32-bit Slave Burst Write Transfers 32-bit DMA Read Transfer from 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States) 32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle (No Wait States) 32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States) 32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States) 32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States) 40 41 42 42 43-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle: Demand Read 45 46 47 48 49 40 40 40 40 40 40 40 41 41 41 41 41 41 41 41 41 41 41 41 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                | Access to EISA Slave - 5 DCLR and Standard (2 DCLR) Cycles  Access to EISA Slave - COMPRESSED Cycle (1 5 BCLK) |            |

| 32-bit Master to 32-bit Slave Burst Write Transfers  Access to EISA Slave - Burst Cycles (With and Without Wait States)  32-bit DMA Read Transfer from 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States)  32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  59  32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle: (No Wait States)  60  24  DMA Transfer from Memory Without Conversion - Compatible Cycle: Demand Read  25  DMA Transfer to Memory Without Conversion - Type "A" Cycle: Demand Read  26  27  32-bit DMA Transfer from 16-bit EISA Memory with Conversion - Type "A" Cycle: Read  28  DMA Transfer to Memory Without Conversion - Type "A" Cycle Demand: Write  29  32-bit DMA Transfer to 16-bit EISA Memory with Conversion - Type "A" Cycle: Write  30  DMA Transfer from Memory Without Conversion - Type "B" Cycle Demand Read  31  32-bit DMA Transfer from 16-bit EISA Memory with Conversion - Type "B" Cycle: Read  31  32-bit DMA Transfer from 16-bit EISA Memory with Conversion - Type "B" Cycle: Read  32-bit DMA Transfer from 16-bit EISA Memory with Conversion - Type "B" Cycle: Read  32-bit DMA Transfer from 16-bit EISA Memory with Conversion - Type "B" Cycle: Read  32-bit DMA Transfer from 16-bit EISA Memory with Conversion - Type "B" Cycle: Read  33  DMA Transfer to Memory Without Conversion - Type "B" Cycle: Demand Write  34  35  36  37  37  38  39  30  31  32-bit DMA Transfer to 16-bit EISA Memory with Conversion - Type "B" Cycle: Demand Write  39  30  31  32-bit DMA Transfer to 16-bit EISA Memory with Conversion - Type "B" Cycle: Demand Write  30  31  32-bit DMA Transfer to 16-bit EISA Memory with Conversion                                                                                                                                                                                                 |                | 22 hit Master to 32-hit Slave Rurst Read Transfers                                                             |            |

| Access to EISA Slave - Burst Cycles (With and Without Wait States)  32-bit DMA Read Transfer from 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States)  32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  59  20  21  22  23  23-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  24  25  26  27  28  29  29  20  20  20  20  20  21  21  22  23  24  25  26  27  28  29  29  20  20  20  20  20  21  21  22  23  24  25  26  27  28  29  29  20  20  20  20  20  20  21  21  22  23  24  25  26  26  27  28  29  29  20  20  20  20  20  20  20  20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                                                                                                                |            |

| 32-bit DMA Read Transfer from 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States)  32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  59  20  21  22  23  23-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  24  25  26  27  28  29  29  20  20  20  20  20  21  22  23  24  25  26  27  27  28  28  29  29  20  20  20  20  20  21  22  23  24  25  26  27  28  28  29  29  20  20  20  20  20  20  21  21  22  23  24  25  26  27  28  28  29  29  20  20  20  20  20  20  20  20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | Access to FISA Slave - Rurst Cycles (With and Without Wait States)                                             |            |

| and Burst Cycles (No Wait States)  32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle (No Wait States)  58  29  32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States)  20  32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  21  22  23  24  25  26  26  27  27  28  29  29  20  20  20  20  20  20  21  21  22  22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                | 32-bit DMA Read Transfer from 32-bit Memory - Type "A." "B."                                                   |            |

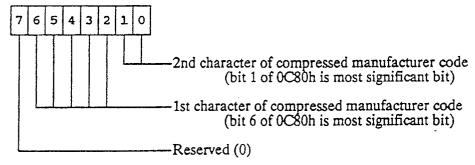

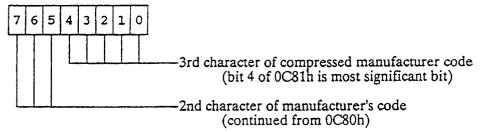

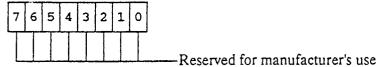

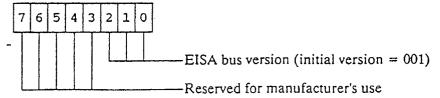

| 32-bit DMA Read Transfer from 32-bit Memory - Compatible Cycle (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Type "A," "B," and Burst Cycles (No Wait States)  32-bit DMA Write Transfer to 32-bit Memory - Compatible Cycle (No Wait States)  60  Chow Wait States)  10  11  12  12  13  13  13  13  13  14  15  15  15  15  15  15  15  15  15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20             |                                                                                                                | 57         |