### SERVICE MANUAL

### BEEHIVE MEDICAL ELECTRONICS, INC. 870 WEST 2600 SOUTH SALT LAKE CITY, UTAH

#### WARRANTY

Beehive Medical Electronics, Inc. certifies that each terminal will be free from defective materials and workmanship for 90 days from date of shipment to the original customer.

B.M.E.I. agrees to correct any of the above defects when the terminal is returned to the factory prepaid. Return authorization must be obtained and confirmed in writing by the Field Service Department before returning the terminal to the factory.

Under this warranty, B.M.E.I. will provide the nocessary components required by the customer to correct the terminal in the field. The components will be shipped, prepaid, on a billing memo which will be cancelled upon receipt of the defective components at the factory. When ordering components for repair or replacement, the model number and serial number must be included on the customer request.

This warranty is invalid if the terminal is subject to misuse, abuse, neglect, accident, improper installation or application, alteration or negligence in use, storage, transportation or handling and where the serial number has been removed, defaced or changed.

# Beehive Terminals Beehive Medical Electronics, Inc.

#### MALFUNCTION REPORT

Dear Customer:

We are trying to manufacture the most reliable product possible. You would do us a great courtesy by completing this form should you experience any failures.

| Type Unit       |                                                     | _Serial No |

|-----------------|-----------------------------------------------------|------------|

| Module (i       | f applicable)                                       |            |

| Part failed (N  | ame and Number)                                     |            |

| Cause of failu  | re (If readily available)                           |            |

|                 |                                                     |            |

| Approximate h   | ours/days of operation to f                         | ailure     |

| Failure occuri  | red during:                                         |            |

| Final Inspectio | on Customer Installation                            | Field Use  |

| Personal Com    | ment:                                               |            |

|                 |                                                     |            |

|                 |                                                     |            |

|                 | Customer                                            | ·····      |

|                 | Address                                             | *****      |

|                 | Signed                                              |            |

|                 | Date                                                |            |

|                 | Beehive Medical Electronics, I                      | nc.        |

|                 | c/o Field Service Department<br>870 West 2600 South |            |

|                 | P.O. Box 19244                                      |            |

|                 | Salt Lake City, Utah 84120                          |            |

#### RETURNING PARTS/EQUIPMENT FOR REPAIR

When the terminal requires service or repair in accordance with the enclosed warranty, unnecessary delays may be avoided when parts or equipment are returned to B.M.E.I. using the following procedures:

- 1. Contact B.M.E.I.'s Field Service Department for Return Authorization. An R.A. Number will be issued and used for future reference.

- 2. Package the unit or part in accordance with the method of shipment. Enclose a list of the material being returned and the reason for returning it. Reference the Return Authorization Number on the shipping label. If the number is not visible, the Receiving Department may refuse to accept the shipment.

- 3. Send the unit or part, transportation prepaid, to the address stipulated for returning parts and equipment.

All equipment and parts described in the warranty will be replaced provided B.M.E.I.'s examination discloses that the defects are within the limits of the warranty. If damages or defects are not within the limits of the warranty, the customer will be notified of the extent of repairs required and the cost. The unit will be repaired and returned upon agreement and receipt of a written purchase order number.

When returning parts and/or equipment for repair, please use the following address:

> Beehive Medical Electronics, Inc. 870 West 2600 South Salt Lake City, Utah 84119

## SUPER BEE COMPUTER TERMINAL

## SERVICE MANUAL

### **MARCH 1974**

This Document has been prepared by Beehive Medical Electronics and is furmished on the condition that it will be used by the custemer solely for the purpose of supporting the operation, service and maintenance of Beehive. Ferminals, The rights of the customer with respect to this Document will be governed by mutually acceptable provisions of the contract with Beehive Medical Electronics. This Document shall not be duplicated by the customer, nor be released, disclosed nor-used, in whole or in part, for any purpose other than stated hermiwithout the express written permission of said Beehivi. Medical Electronics.

### Beehive Medical Electronics, Inc.

870 West 2600 South P.O. Box 19244 Salt Lake City, Utah Phone: (801) 487-0741, TWX 910-925-5271

·

.

#### TABLE OF CONTENTS

#### SECTION I GENERAL INFORMATION

| 1.1 | INTRODUCTION 1-                      |      |

|-----|--------------------------------------|------|

| 1.2 | PRODUCT DESCRIPTION                  | 1-1  |

| 1.3 | PERFORMANCE CHARACTERISTICS          | 1-1  |

|     | 1.3.1 Modes of Communications        | 1-1  |

|     | 1.3.2 Operating Modes                | 1-4  |

|     | 1.3.3 Display Organization           | 1-5  |

|     | 1.3.4 Memory Organization            | 1-5  |

|     | 1.3.5 Memory Overwrite               | 1-6  |

|     | •                                    | 1-6  |

|     | 1.3.6 Space Overwrite (SPOW)         | 1-6  |

|     | 1.3.7 Character Overwrite            | 1-6  |

|     | 1.3.8 Special Function Keys          | 1-6  |

|     | 1.3.9 Printer Port                   | 1-6  |

|     | 1.3.10 Input/Output Port             | 1-7  |

|     | 1.3.11 I/O Processor Board Strapping | 1-7  |

| 1.4 | ACCESSORIES                          | 1-8  |

| 1.5 | SPECIFICATIONS                       | 1-8  |

| 1.6 | IDENTIFICATION                       | 1-12 |

### SECTION II

OPERATION

| 2.1 | INTRODUCTION                                 | 2-1       |

|-----|----------------------------------------------|-----------|

| 2.2 | OPERATOR CONTROLS AND INDICATORS             | 2-2       |

| 2.3 | TURN-ON PROCEDURES                           | 2-12      |

| 2.4 | OPERATOR CHECKOUT PROCEDURES                 | 2-12      |

|     | 2.4.1 Alternate Action Keys Checkout         | 2-12      |

|     | 2.4.2 Escape Code Sequences Checkout         | 2-13      |

|     | 2.4.3 Cursor Movement Checkout               | 2-13      |

|     | 2.4.4 Tab Checkout                           | 2-13      |

|     | 2.4.5 Scrolling and Erase Functions Checkout | 2-13      |

|     | 2.4.6 Enter and Print Checkout               | 2-14      |

|     | 2.4.7 Format Checkout                        | 2-14      |

| 2.5 | CONTROL AND EDIT FUNCTION OPERATIONS         | 2-15      |

| 2.6 | OPERATION CODES                              | 2-20      |

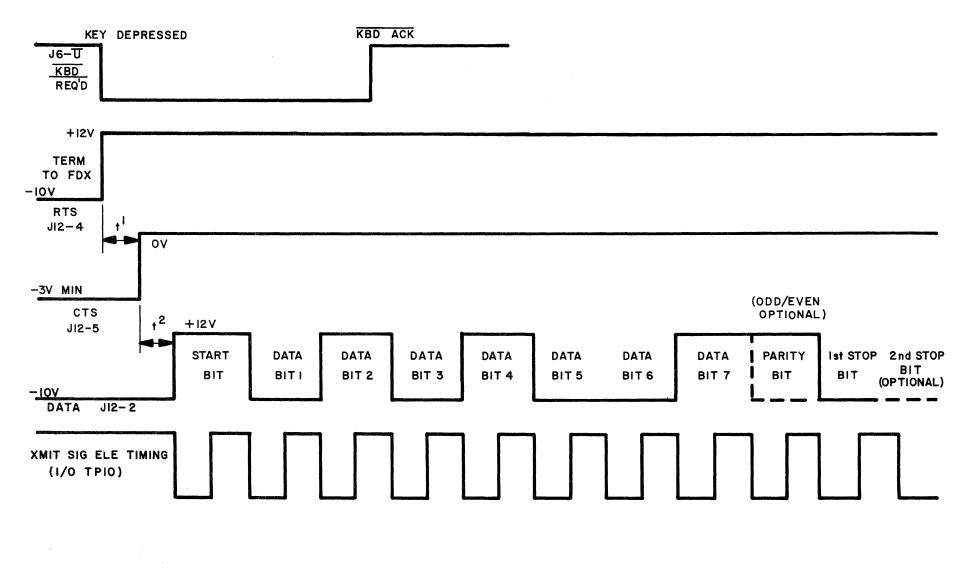

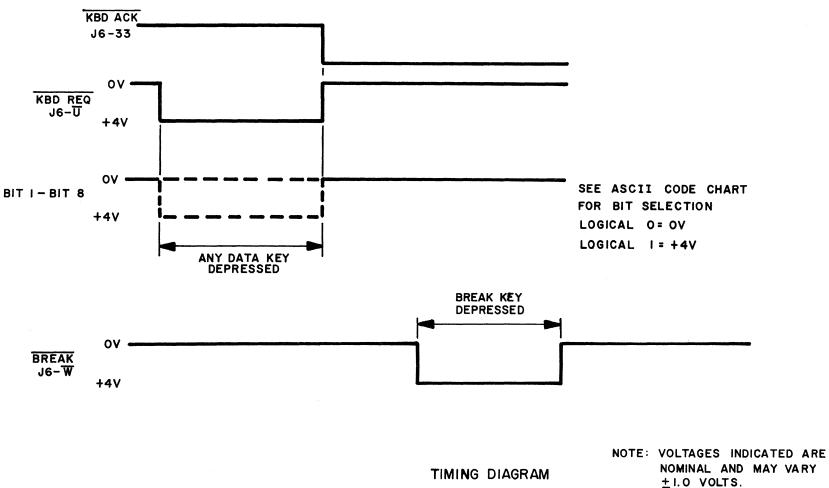

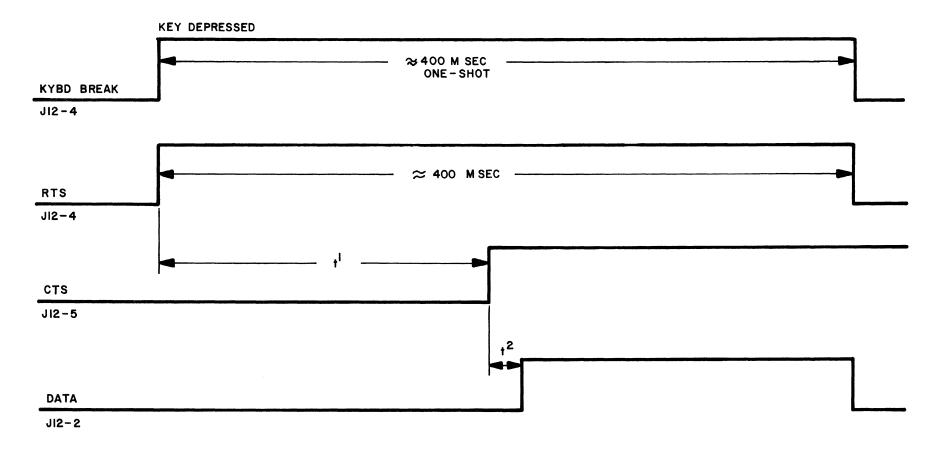

| 2.7 | TIMING CONSIDERATION                         | 2-23/2-24 |

## SECTION III

| 3.1            | INTRODUCTION                                         | 3-1 |

|----------------|------------------------------------------------------|-----|

| 3.2            | UNPACKING                                            | 3-1 |

| 3.3            | INSPECTION FOR IN-SHIPMENT DAMAGE                    | 3-1 |

| 3.4            | STANDARD ITEMS (FURNISHED)                           | 3-1 |

| 3.5            | INSTALLATION                                         | 3-1 |

|                | 3.5.1 Placement for Operation                        | 3-1 |

| а <sub>1</sub> | 3.5.2 Power Connection                               | 3-3 |

|                | 3.5.3 Data Interface Connections                     | 3-3 |

|                | 3.5.4 Printer Interface Connections                  | 3-4 |

|                | 3.5.5 Current Loop Adapter                           | 3-5 |

|                | 3.5.6 Video Output Connection                        | 3-5 |

| •              | 3.5.7 I/O Processor Baud Strapping                   | 3-5 |

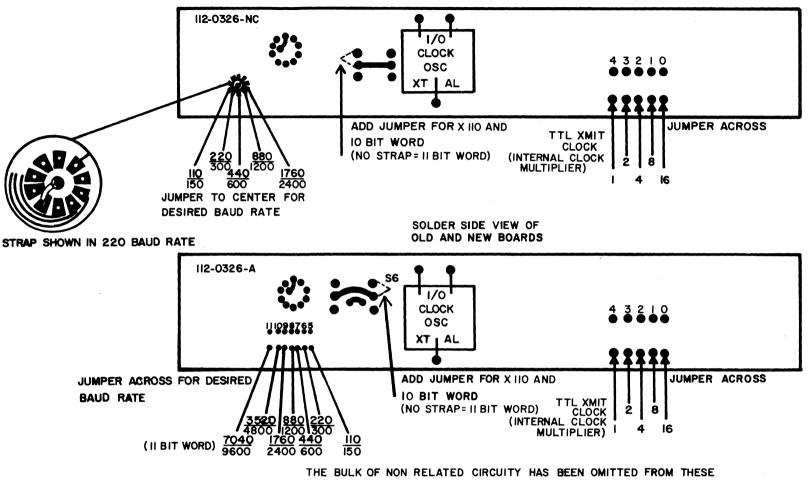

|                | 3.5.8 Printer Baud Rate and Internal Clock Strapping | 3-7 |

#### SECTION IV THEORY OF OPERATION

| 4.1 | INTRODUCTION                               | 4-1  |

|-----|--------------------------------------------|------|

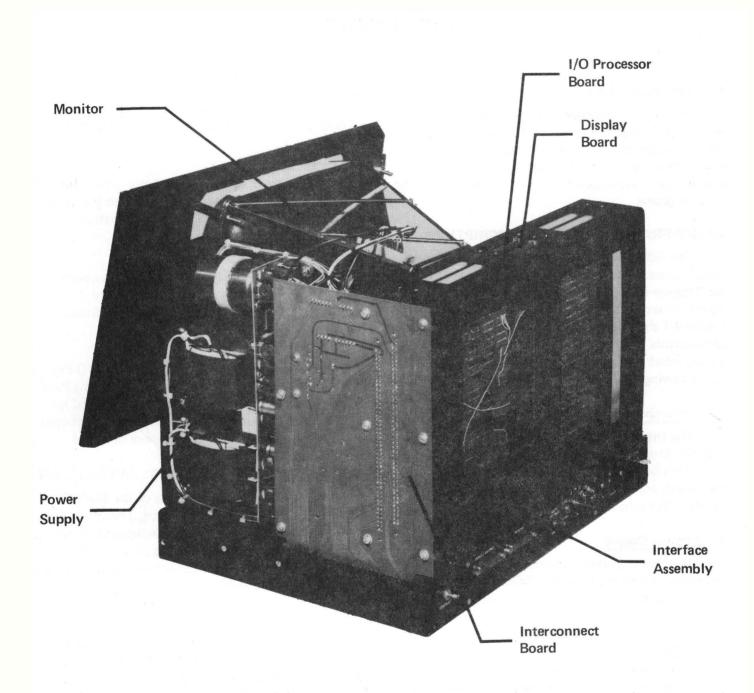

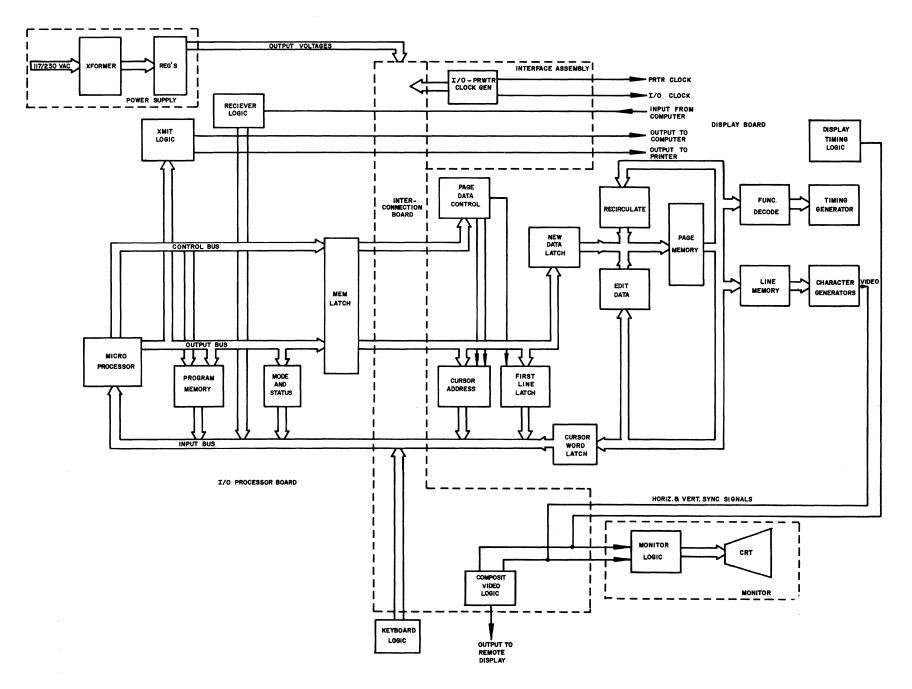

| 4.2 | GENERAL FUNCTIONAL DESCRIPTION             | 4-1  |

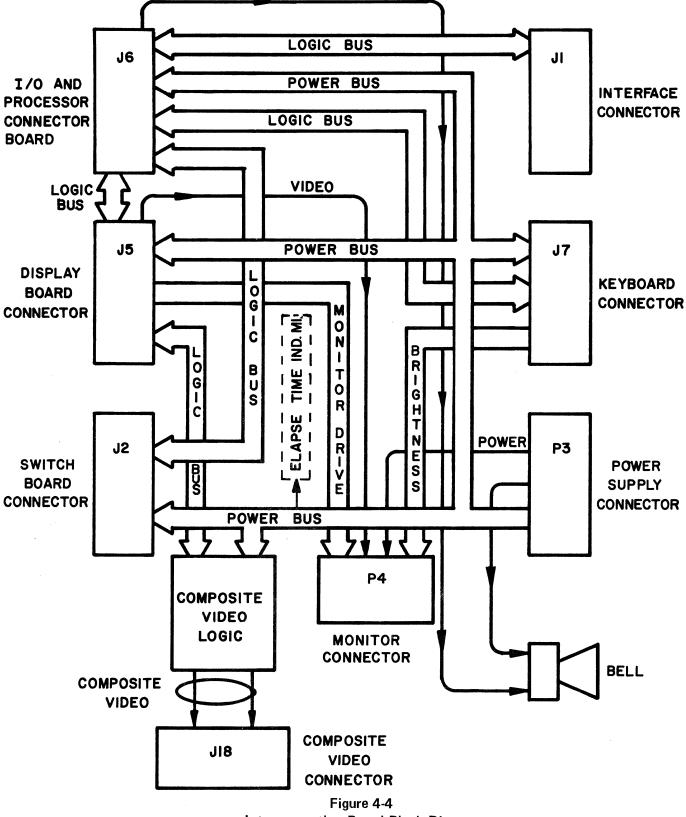

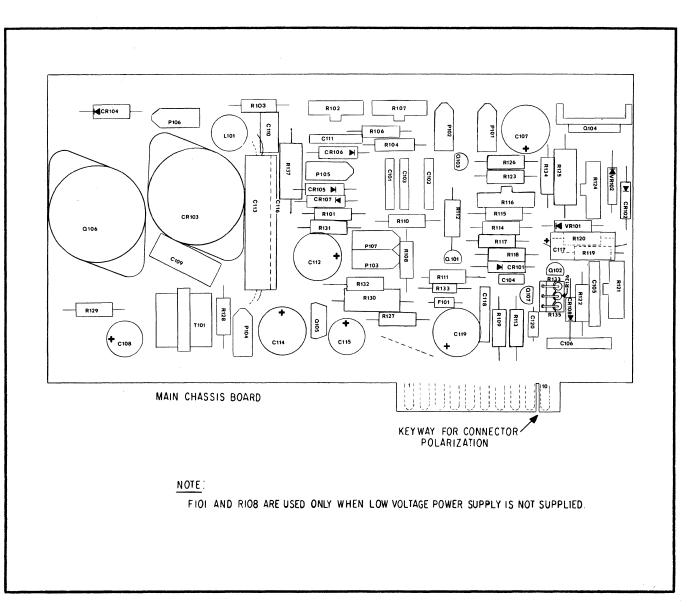

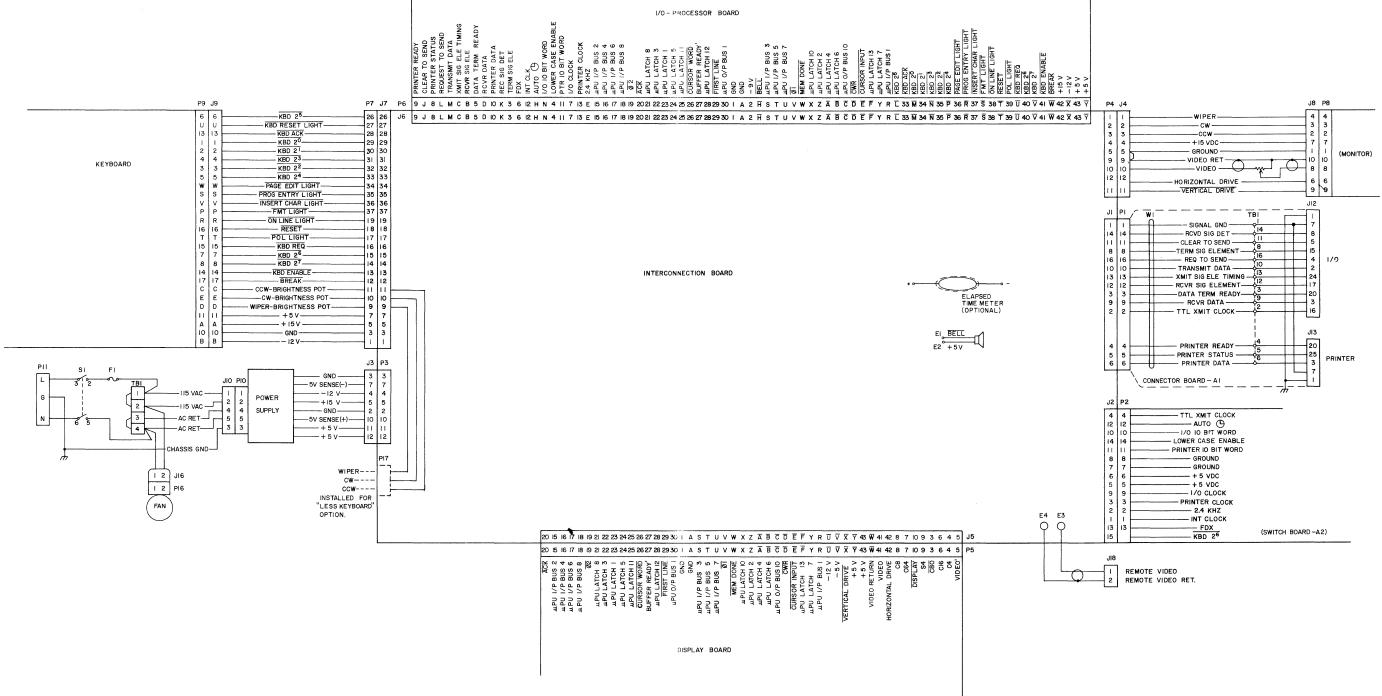

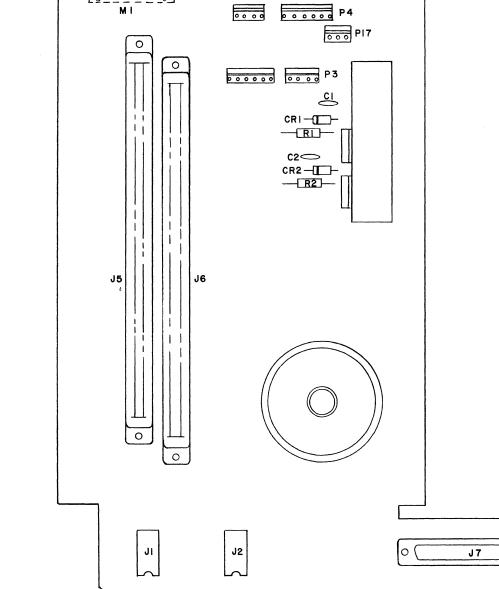

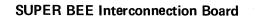

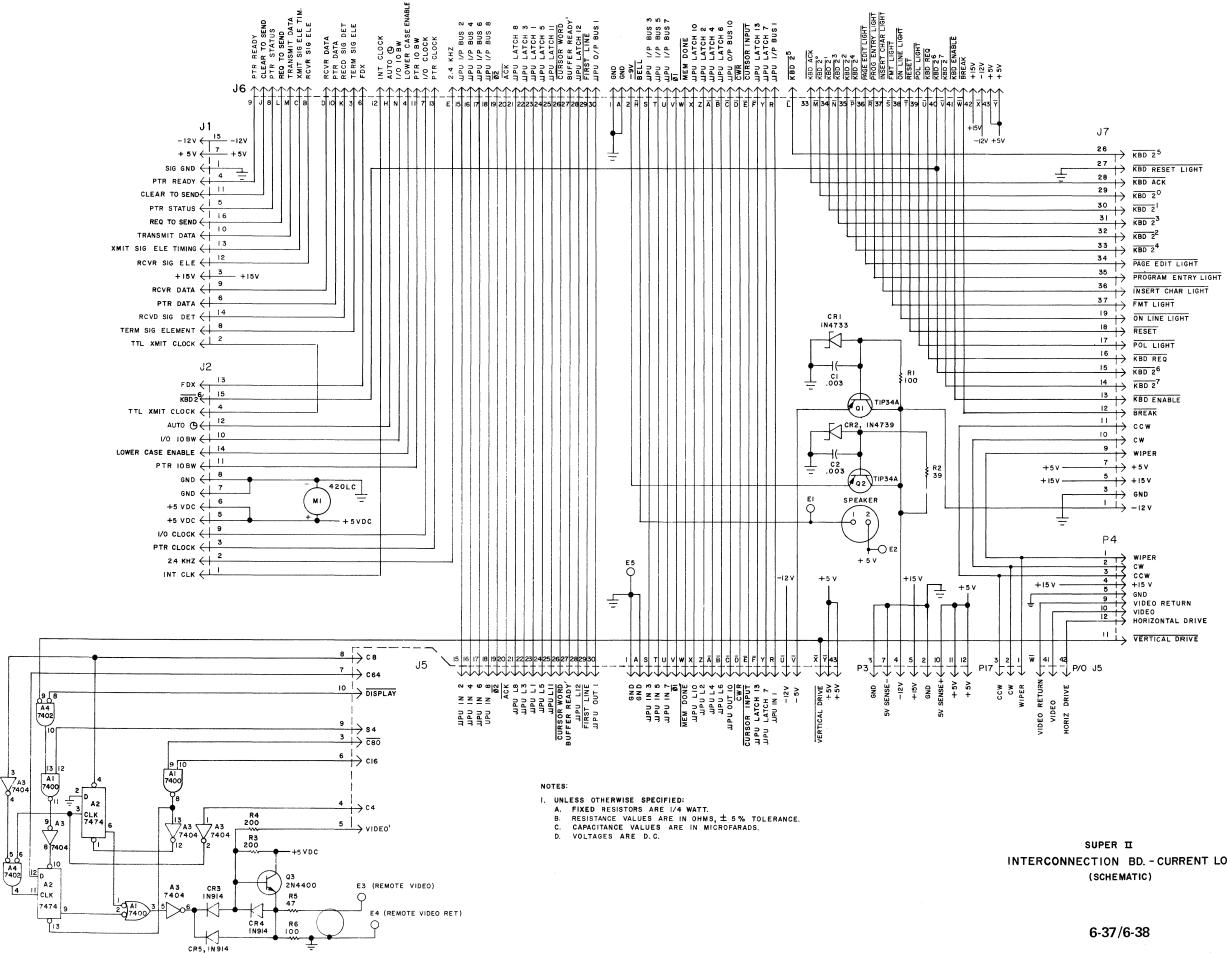

|     | 4.2.1 Interconnect Board                   | 4-1  |

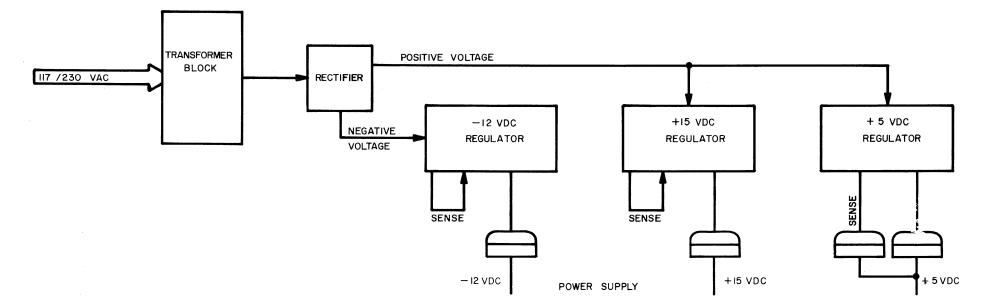

|     | 4.2.2 Power Supply                         | 4-1  |

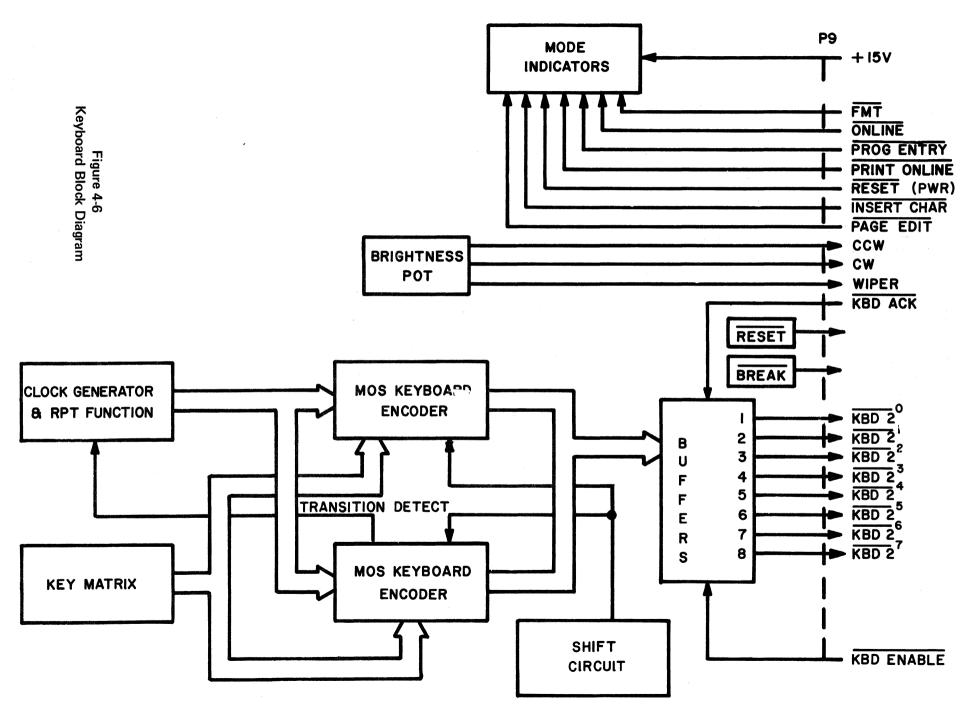

|     | 4.2.3 Keyboard                             | 4-1  |

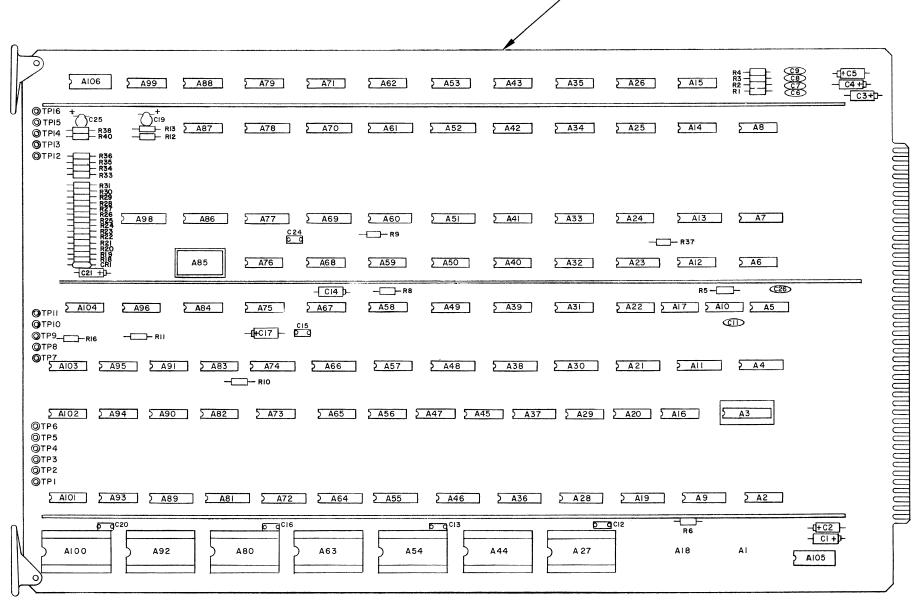

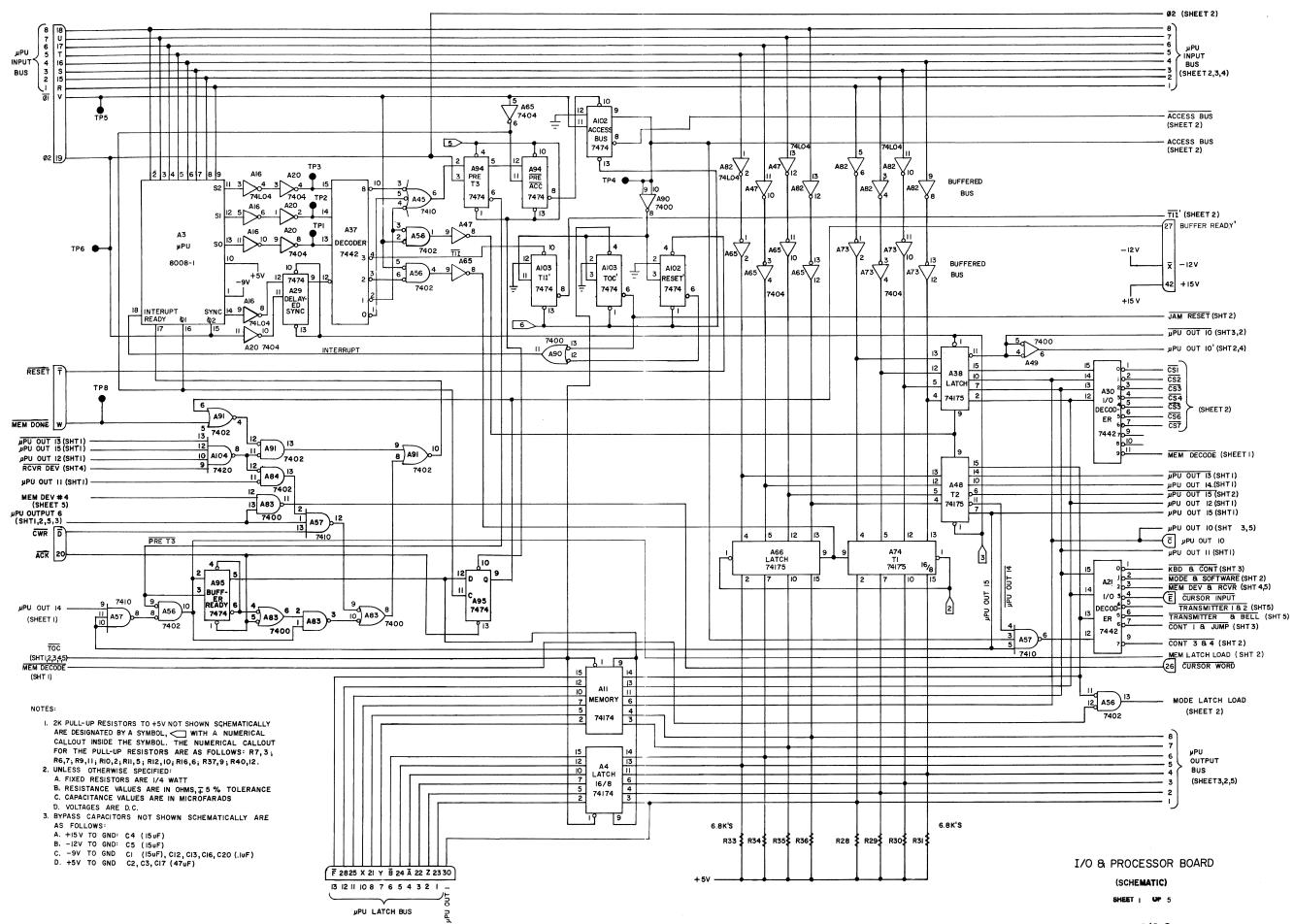

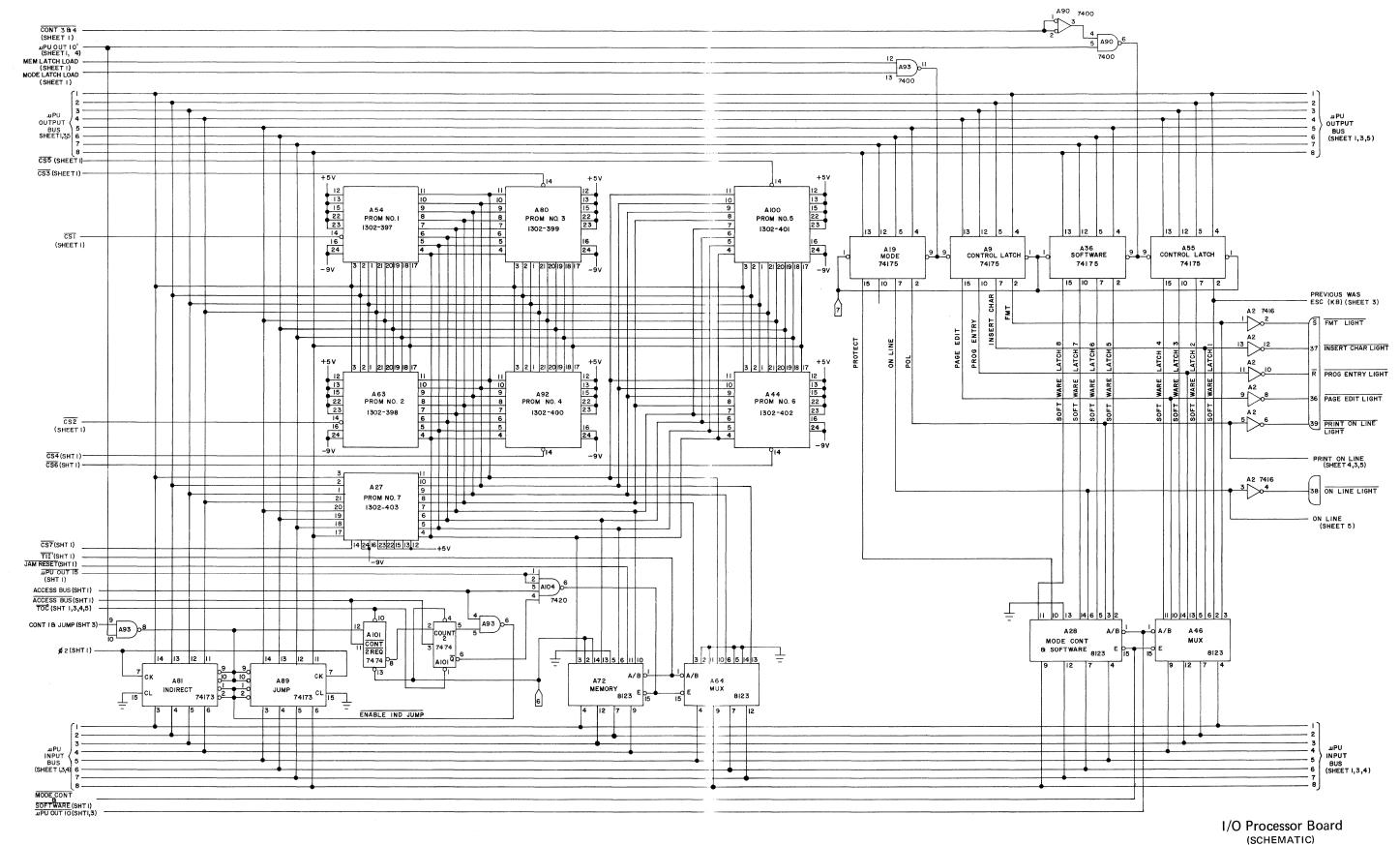

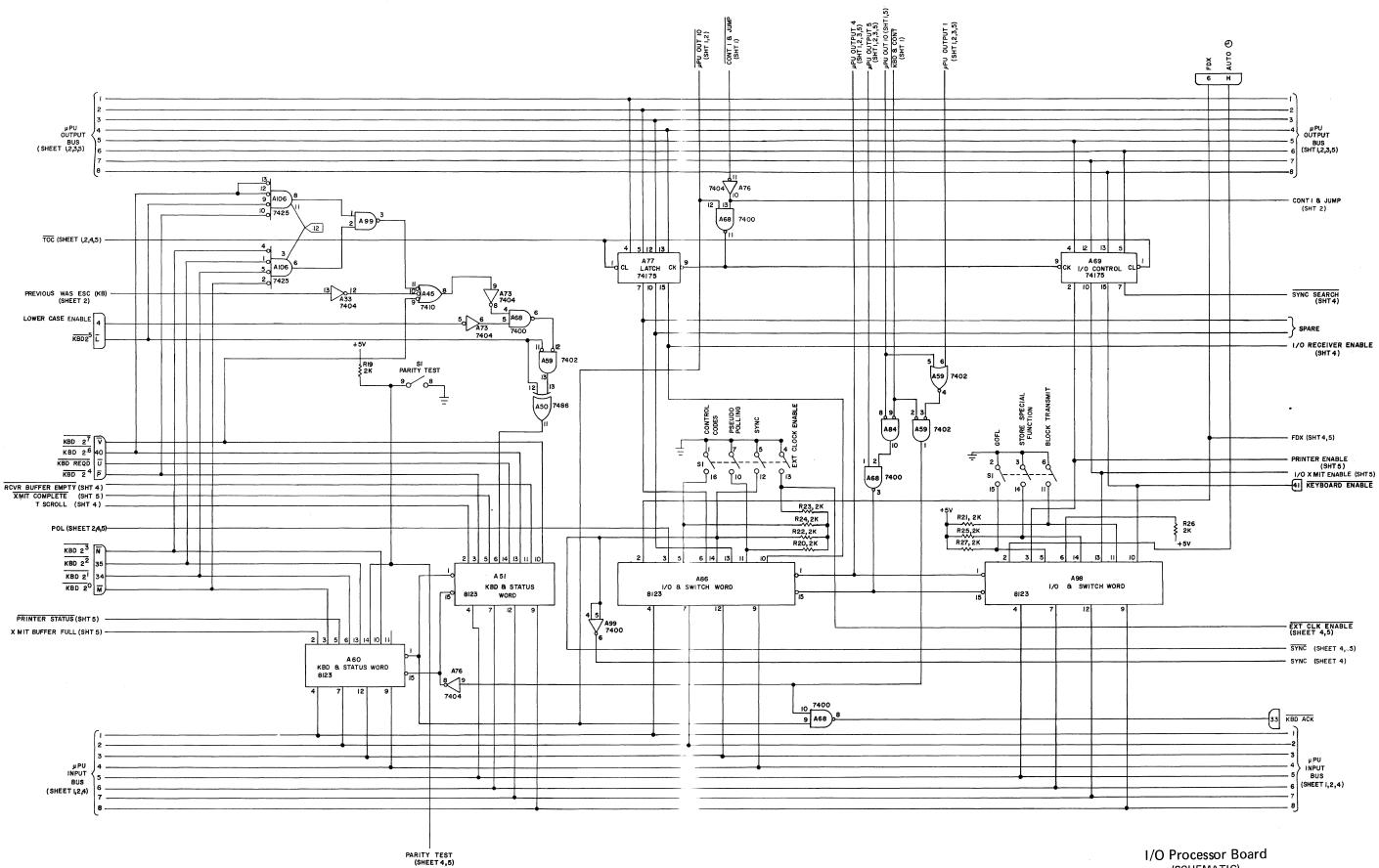

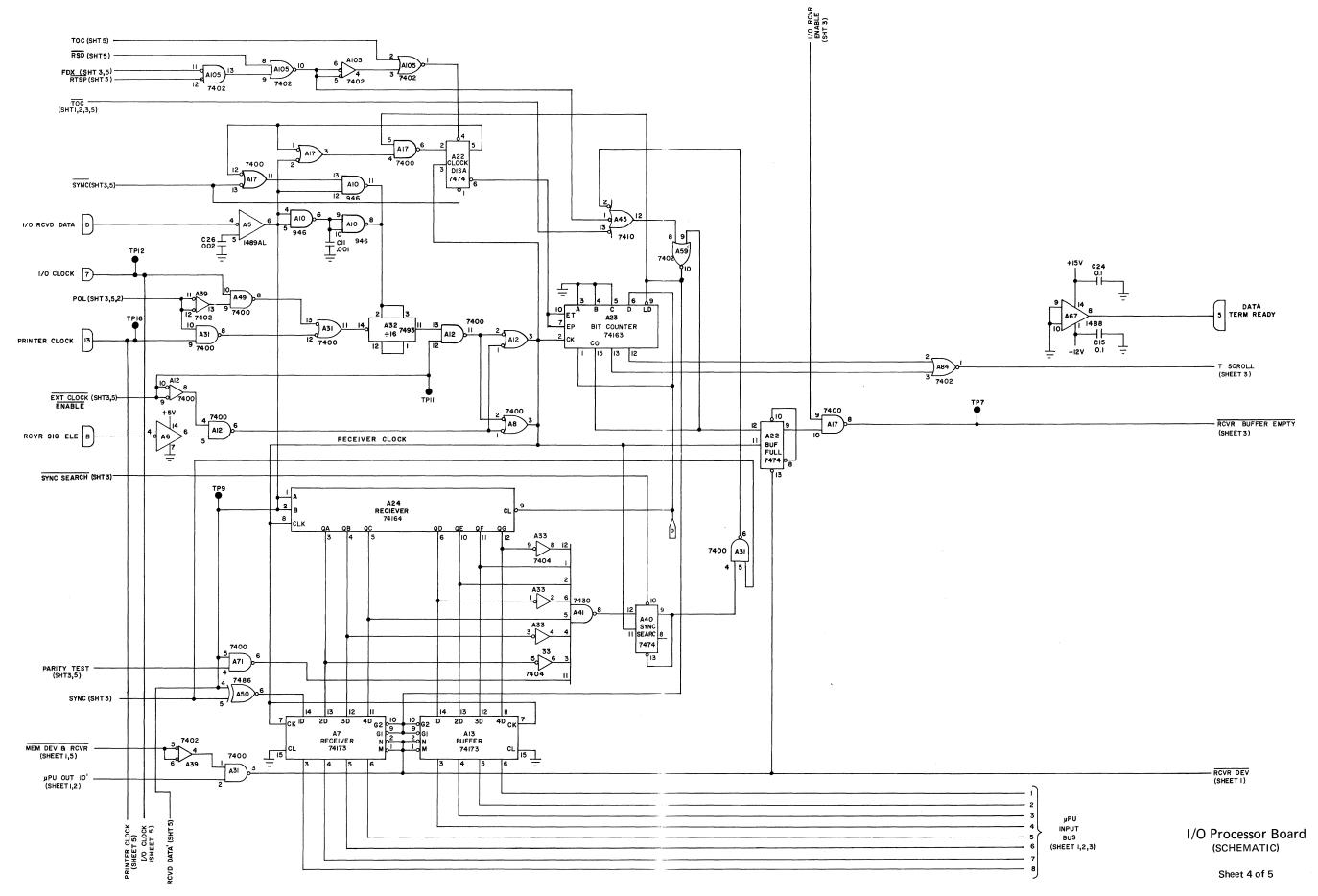

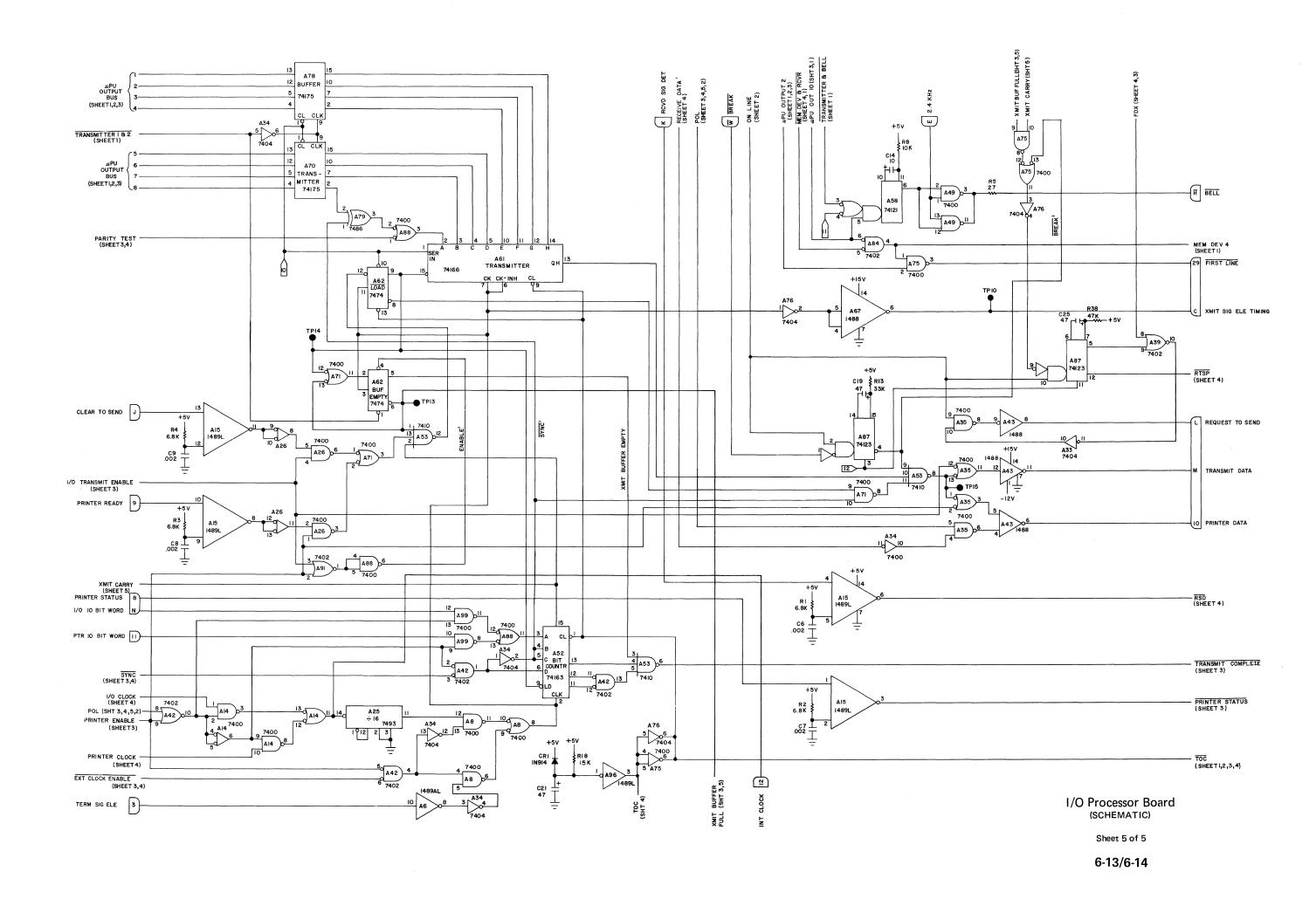

|     | 4.2.4 I/O Processor Board                  | 4-1  |

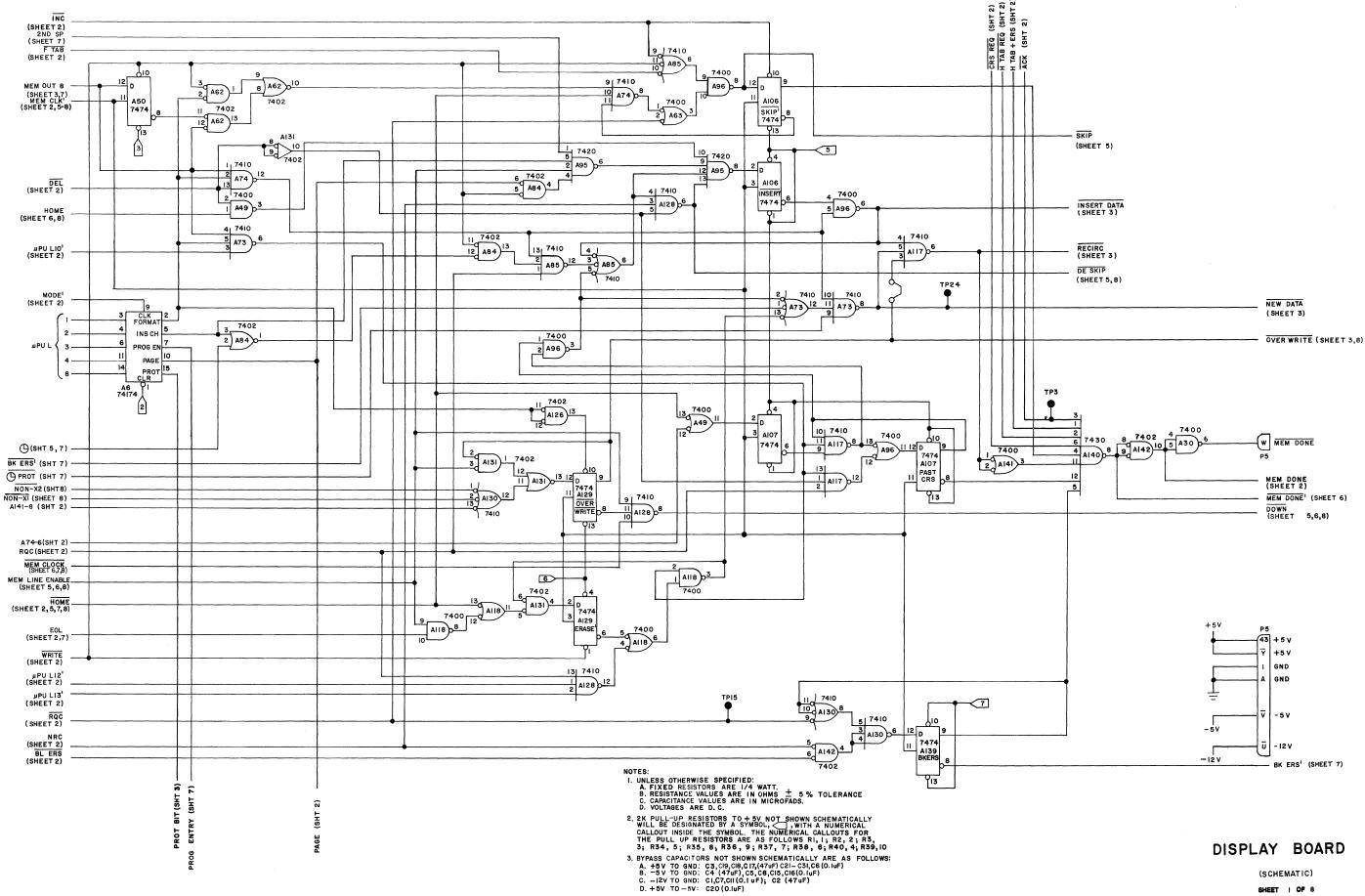

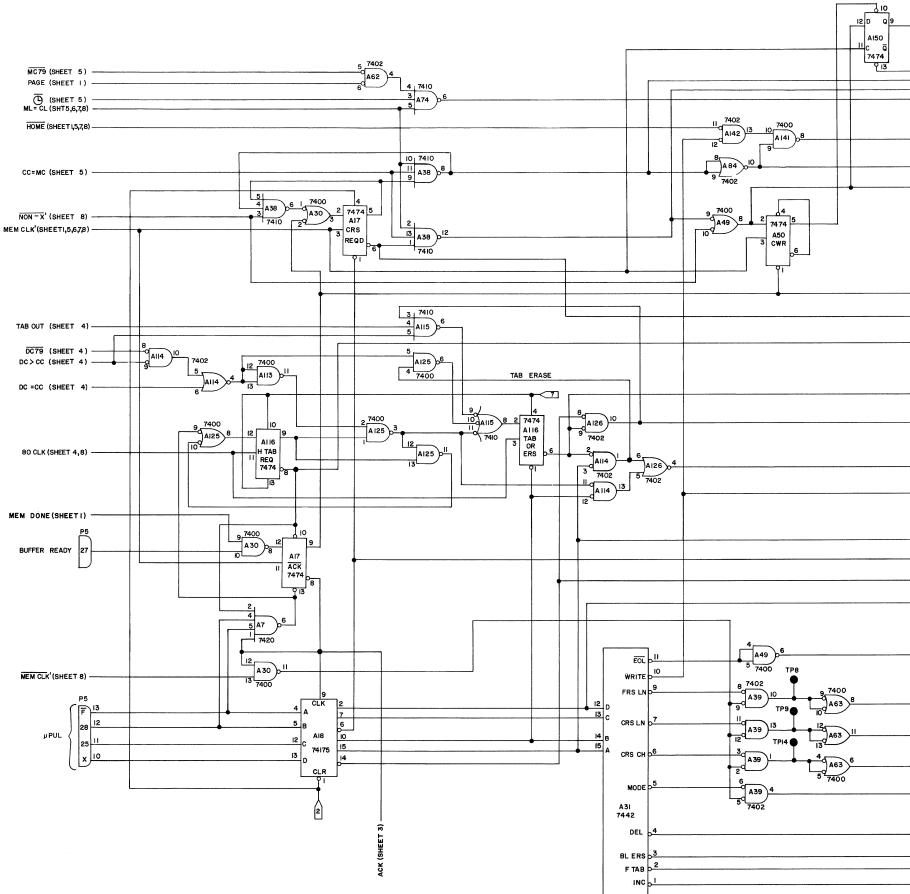

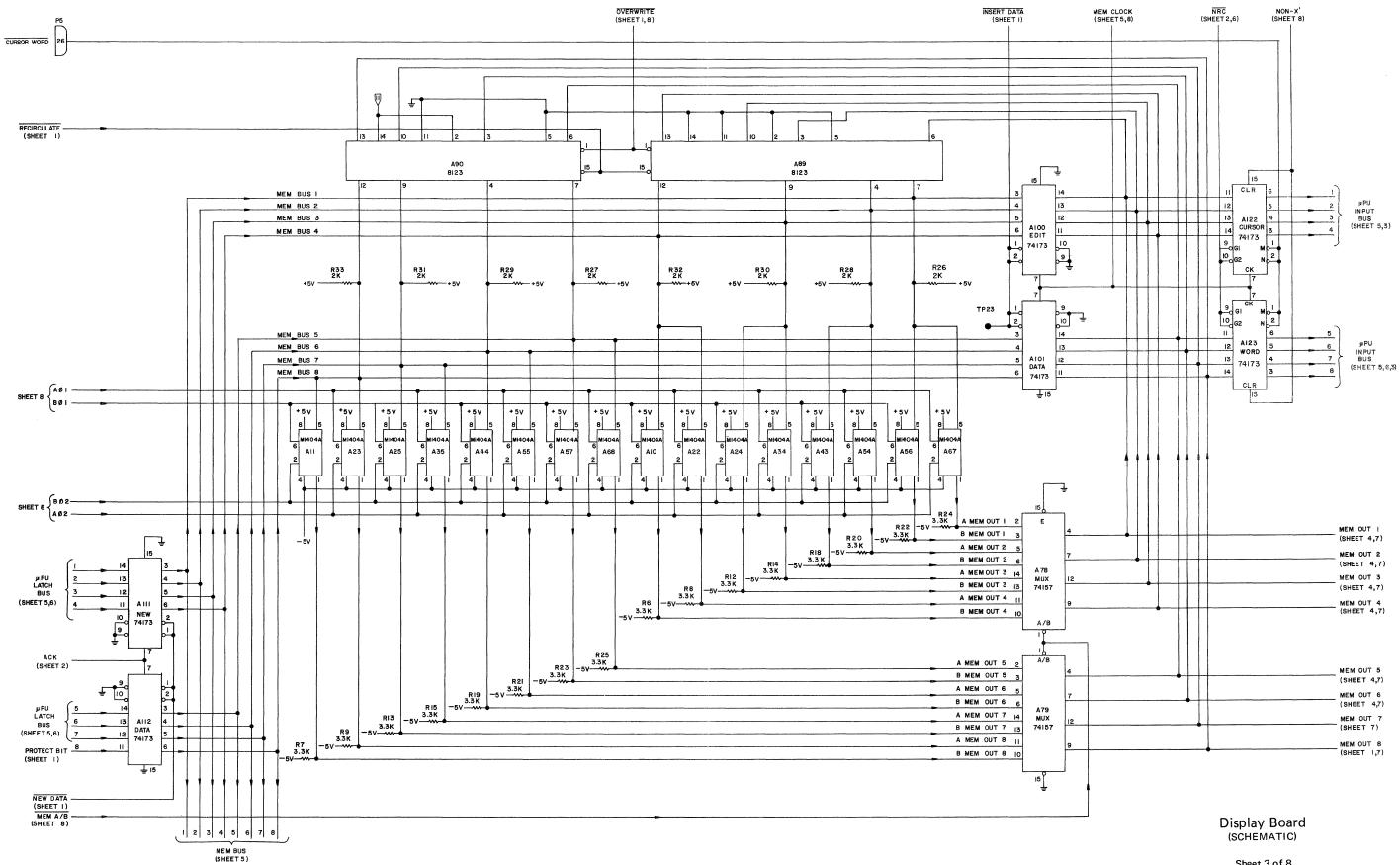

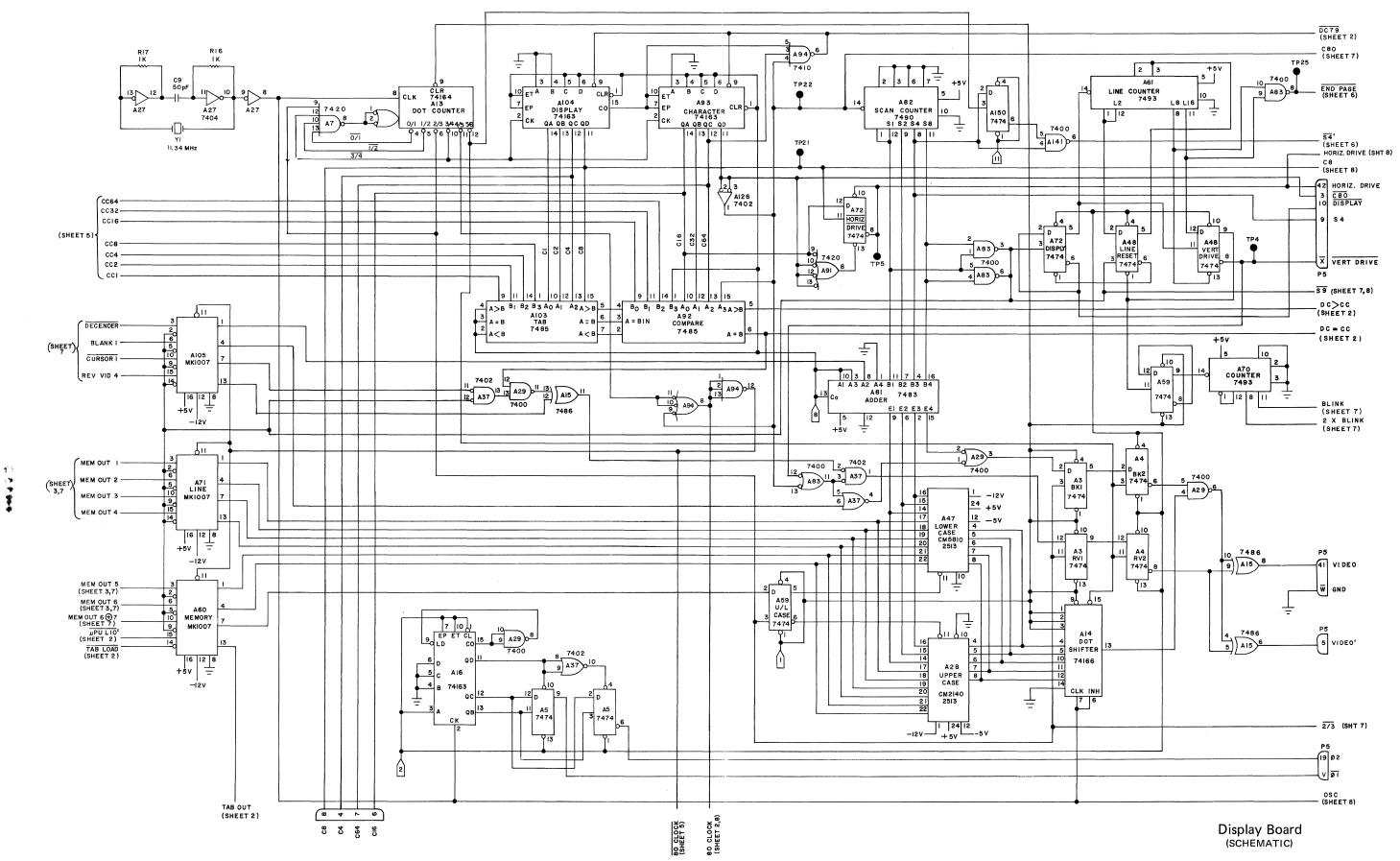

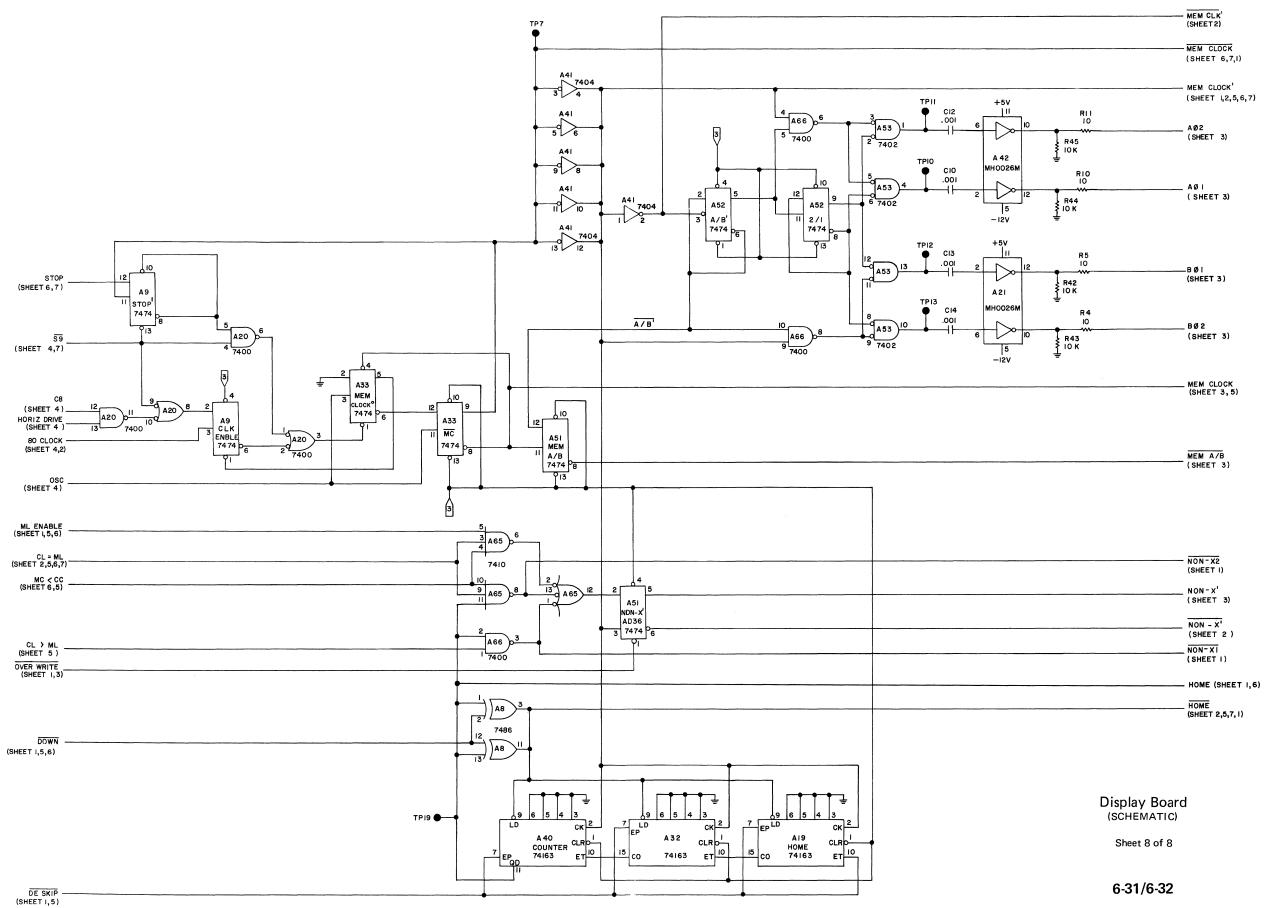

|     | 4.2.5 Display Board                        | 4-1  |

|     | 4.2.6 Monitor                              | 4-1  |

|     | 4.2.7 Interface Assembly                   | 4-1  |

| 4.3 | INTERMEDIATE FUNCTIONAL DESCRIPTION        | 4-1  |

|     | 4.3.1 Interconnect Board                   | 4-1  |

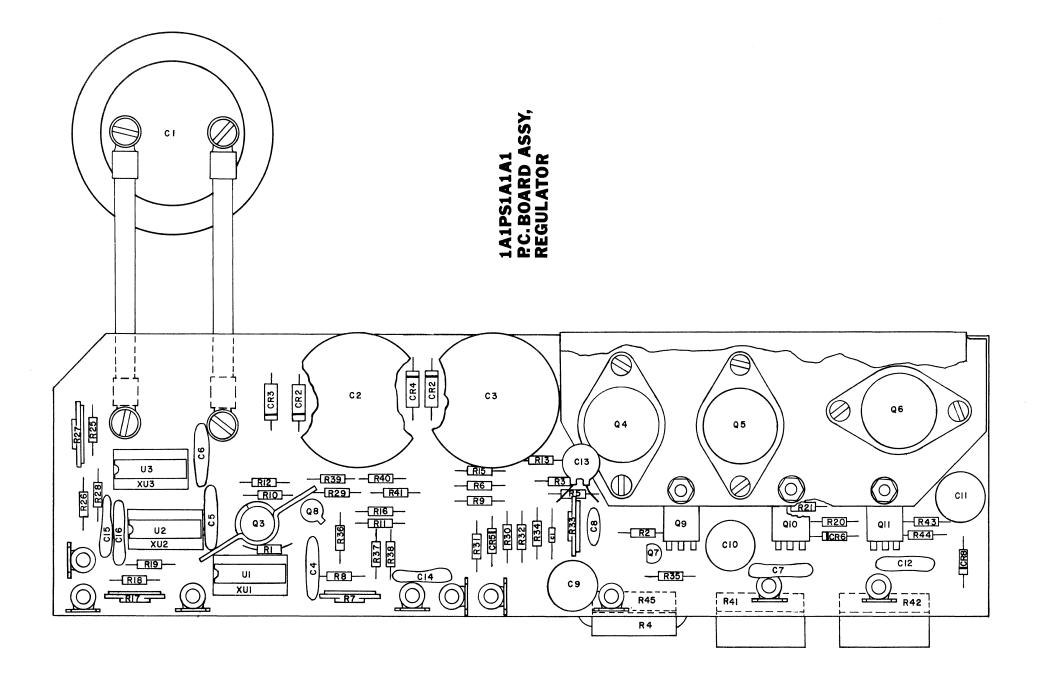

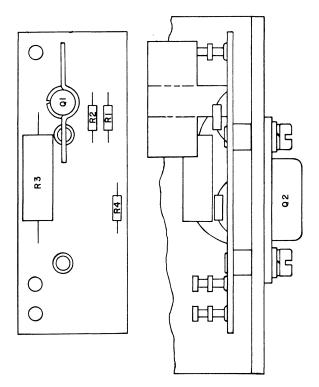

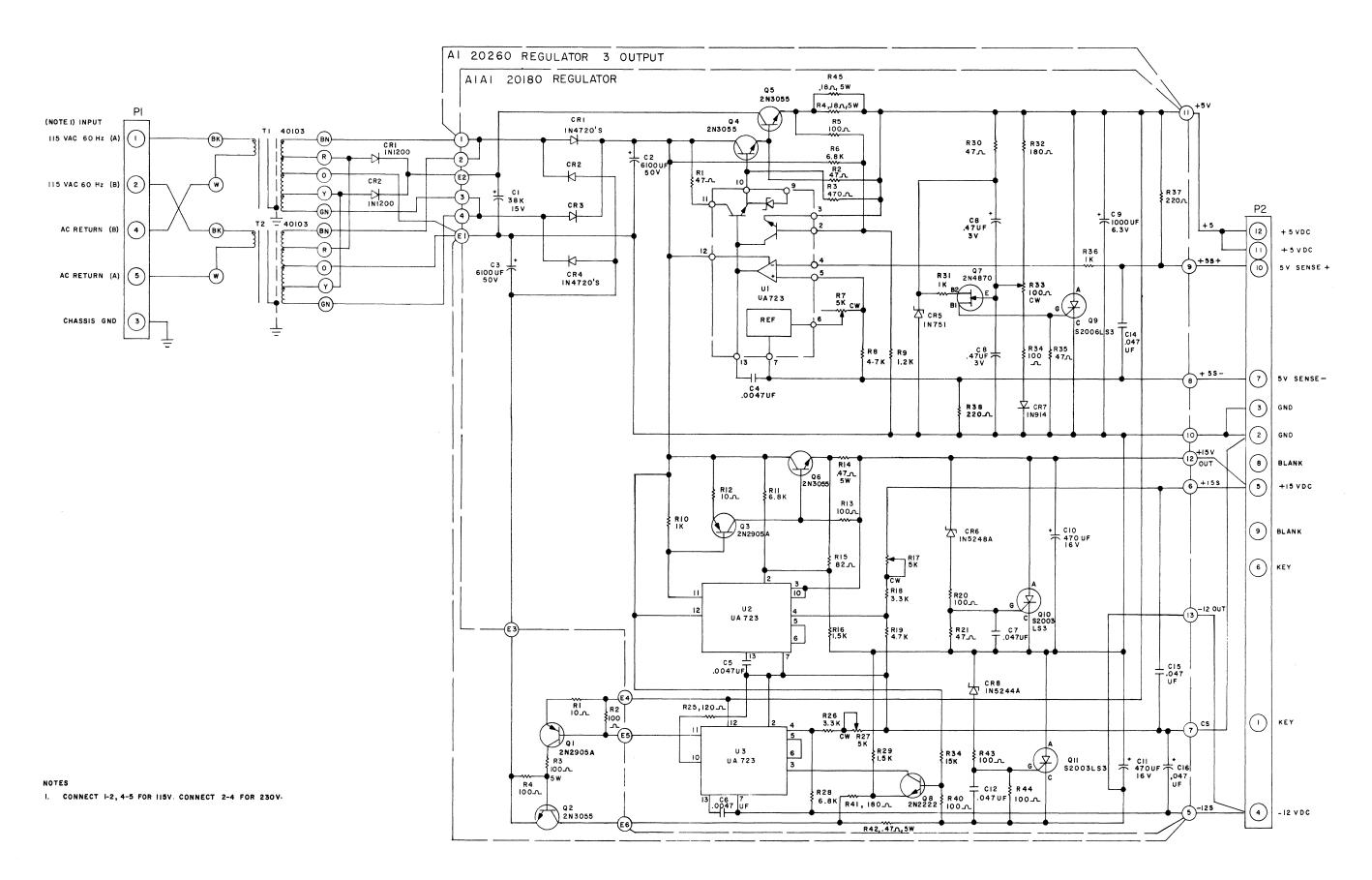

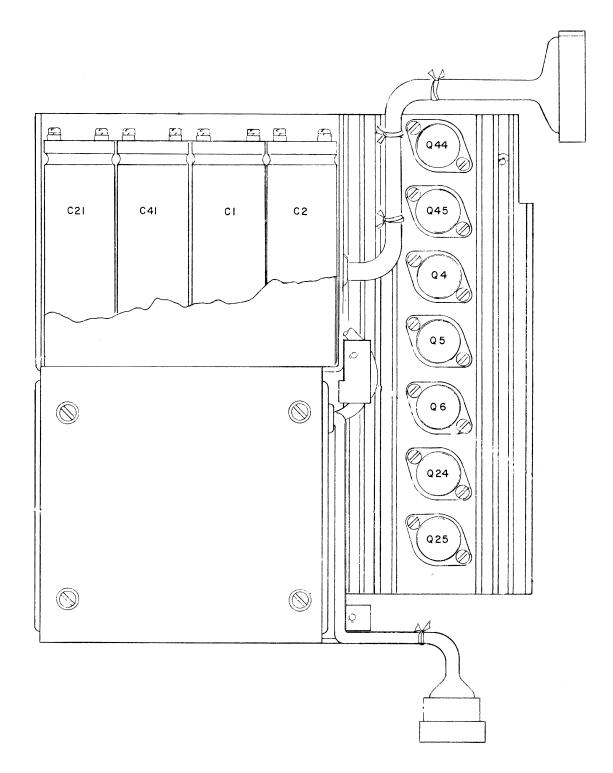

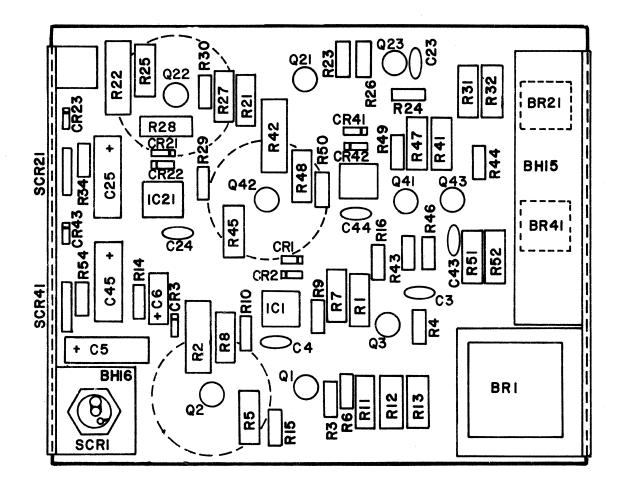

|     | 4.3.2 Power Supply                         | 4-6  |

|     | 4.3.3 Keyboard                             | 4-6  |

|     | 4.3.4 I/O Processor Board                  | 4-6  |

|     | 4.3.5 Display Board                        | 4-6  |

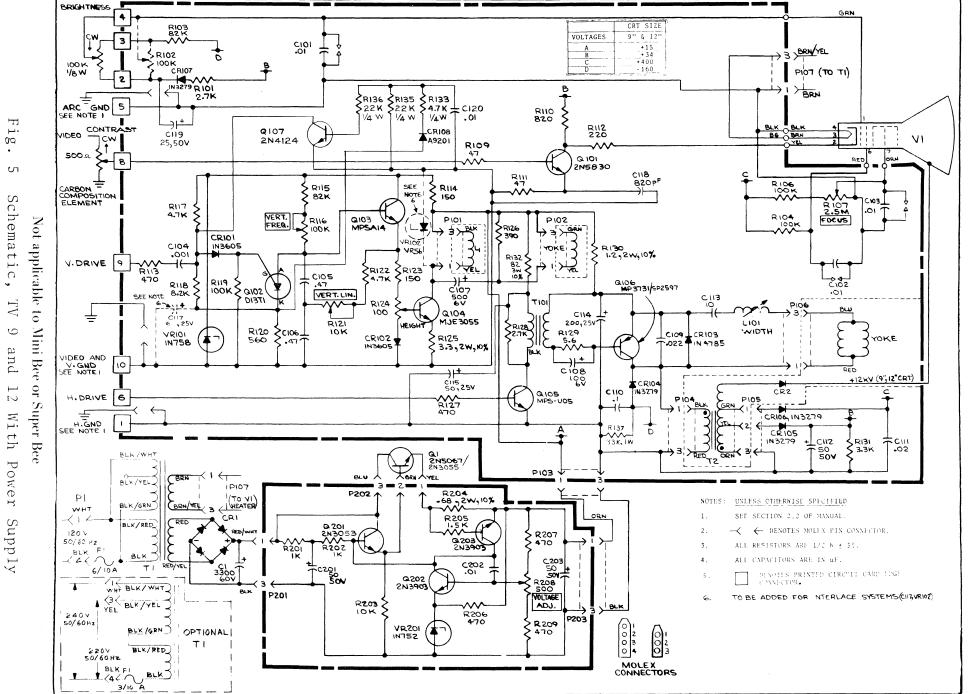

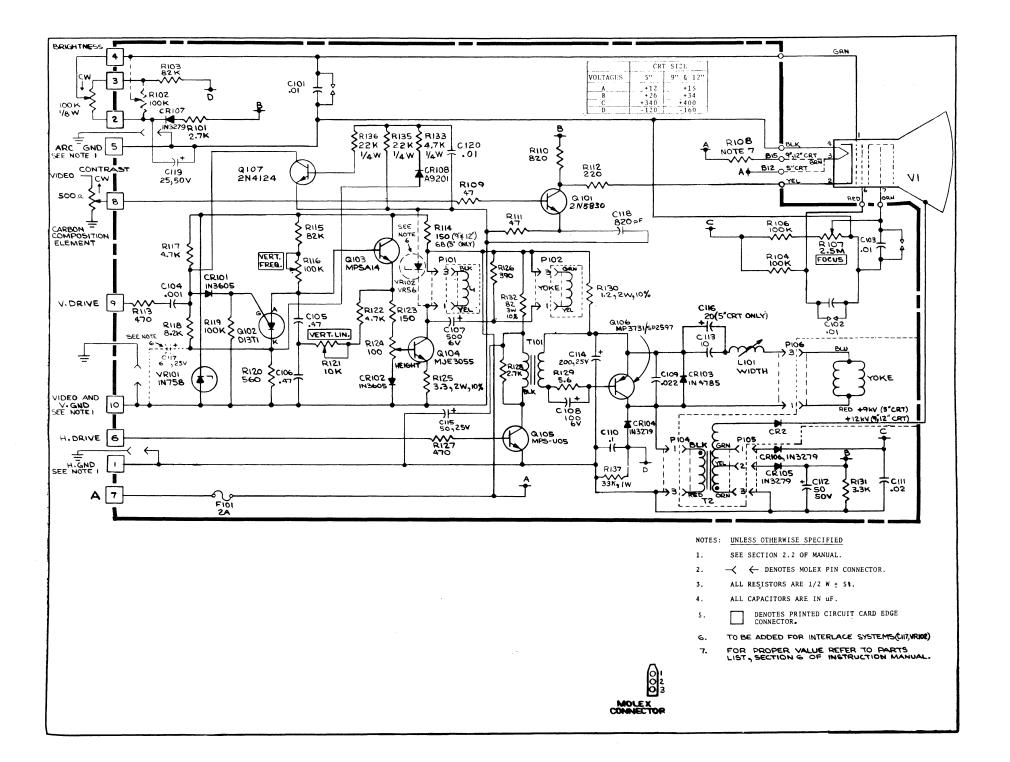

|     | 4.3.6 Monitor                              | 4-15 |

|     | 4.3.7 Interface Assembly                   | 4-15 |

| 4.4 | DETAILED CIRCUIT DESCRIPTION               | 4-15 |

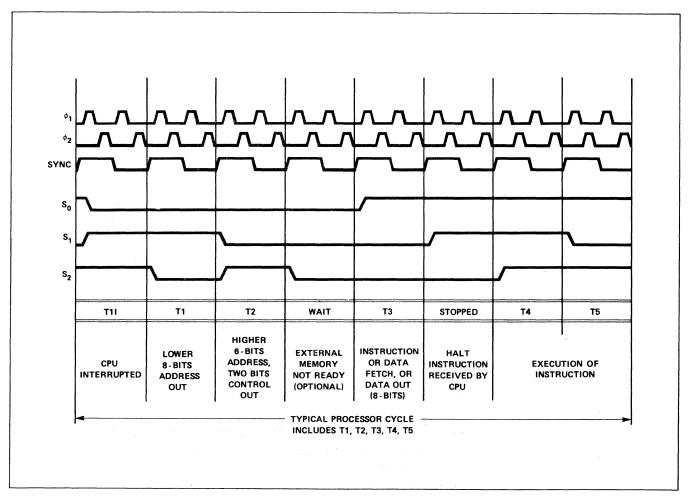

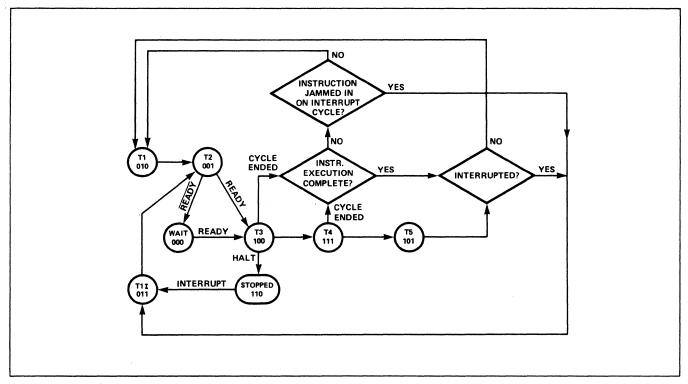

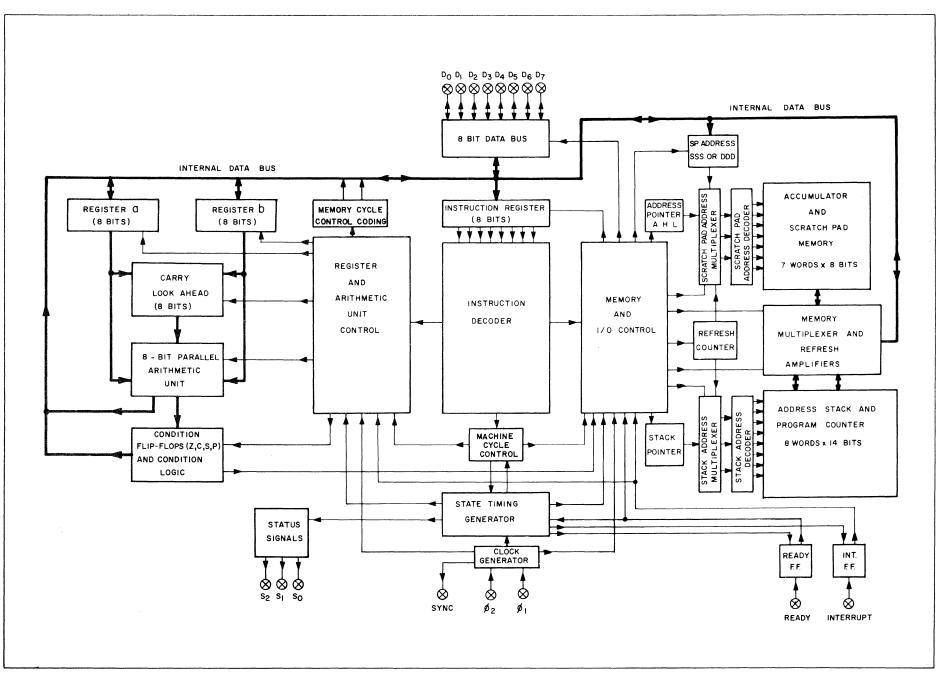

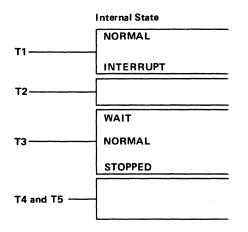

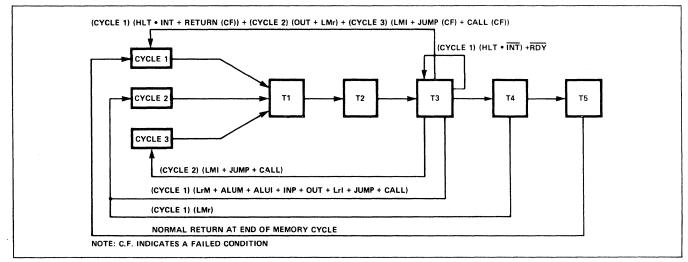

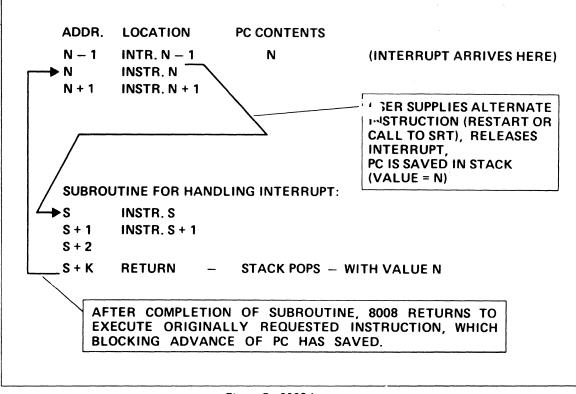

|     | 4.4.1 Instruction Fetch Cycle              | 4-15 |

|     | 4.4.2 Data Fetch Cycle                     | 4-18 |

|     | 4.4.3 I/O Control Cycle                    | 4-18 |

|     | 4.4.4 Indirect Jump Circuitry              | 4-18 |

|     | 4.4.5 Mode Latch and Software Latch        | 4-18 |

|     | 4.4.6 I/O Control Latch                    | 4-18 |

|     | 4.4.7 Keyboard and Status Word Multiplexer | 4-19 |

|     | 4.4.8 Receiver/Transmitter Functions       | 4-19 |

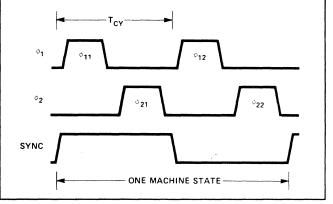

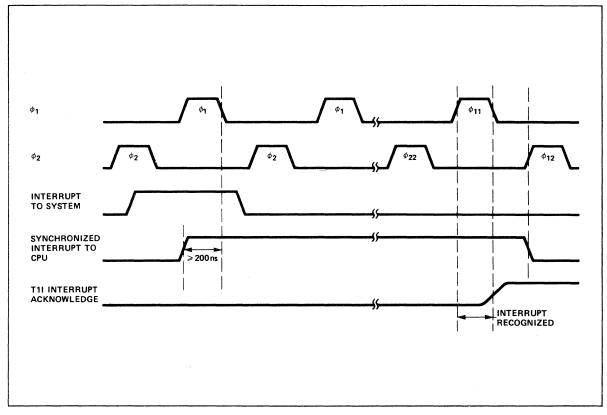

| 4.4.9  | Main Timing                        | 4-19      |

|--------|------------------------------------|-----------|

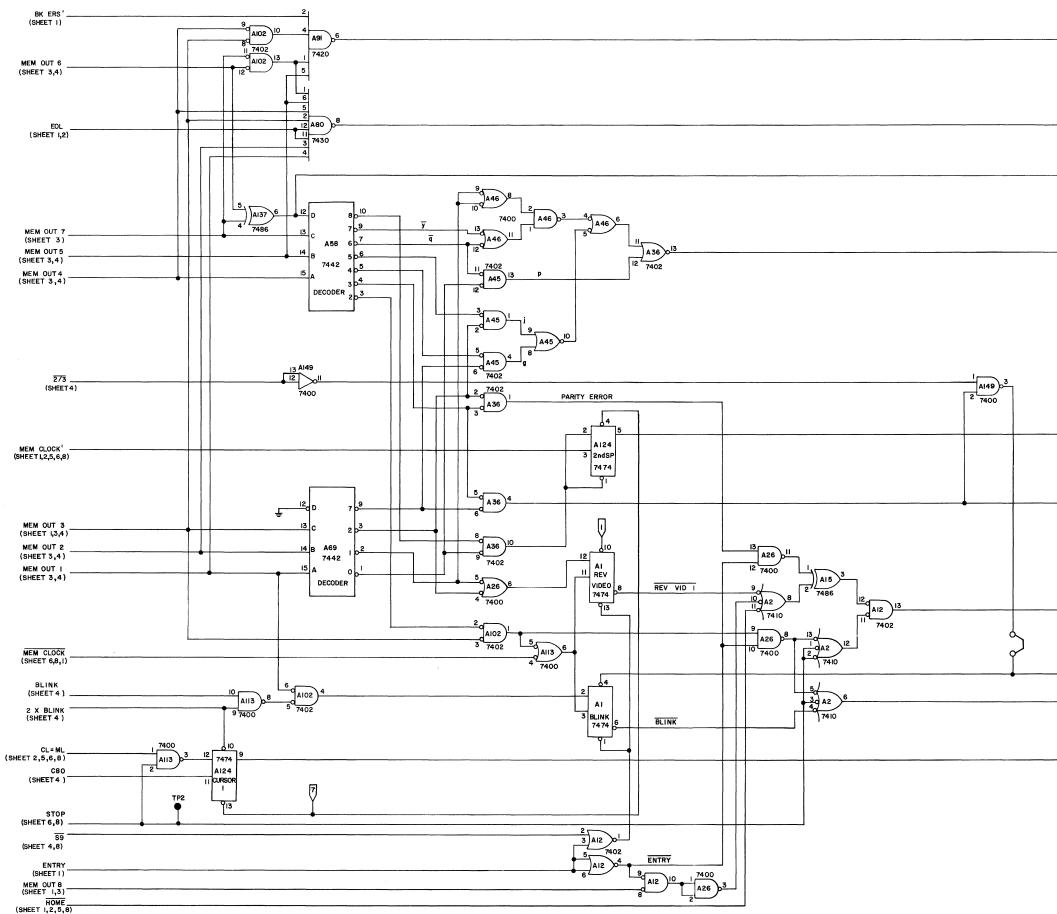

| 4.4.10 | Character Generation and Display   | 4-19      |

| 4.4.11 | Page Memory                        | 4-22      |

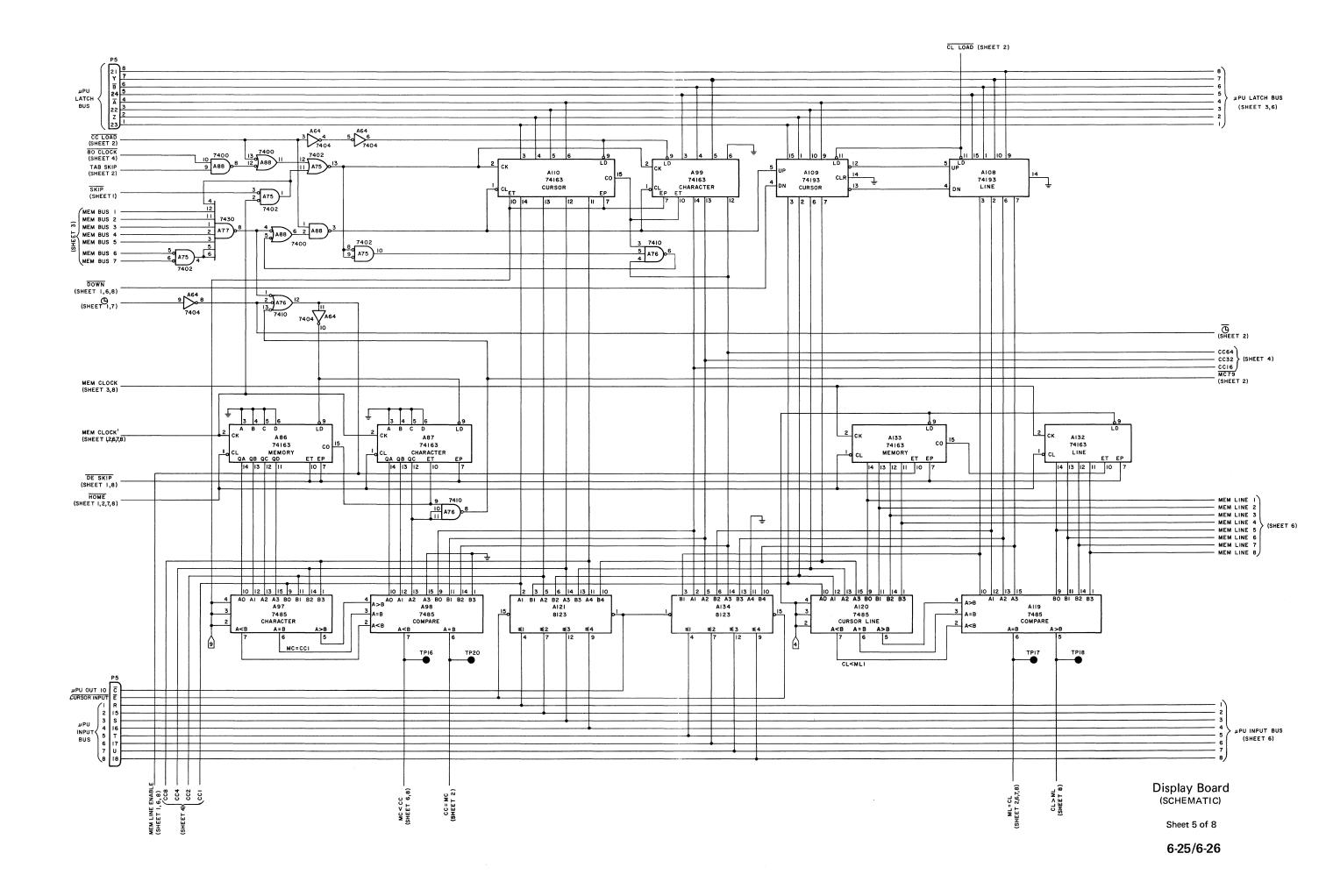

| 4.4.12 | Cursor Character and Line Counter  | 4-23/4-24 |

| 4.4.13 | Memory Character and Line Counters | 4-23/4-24 |

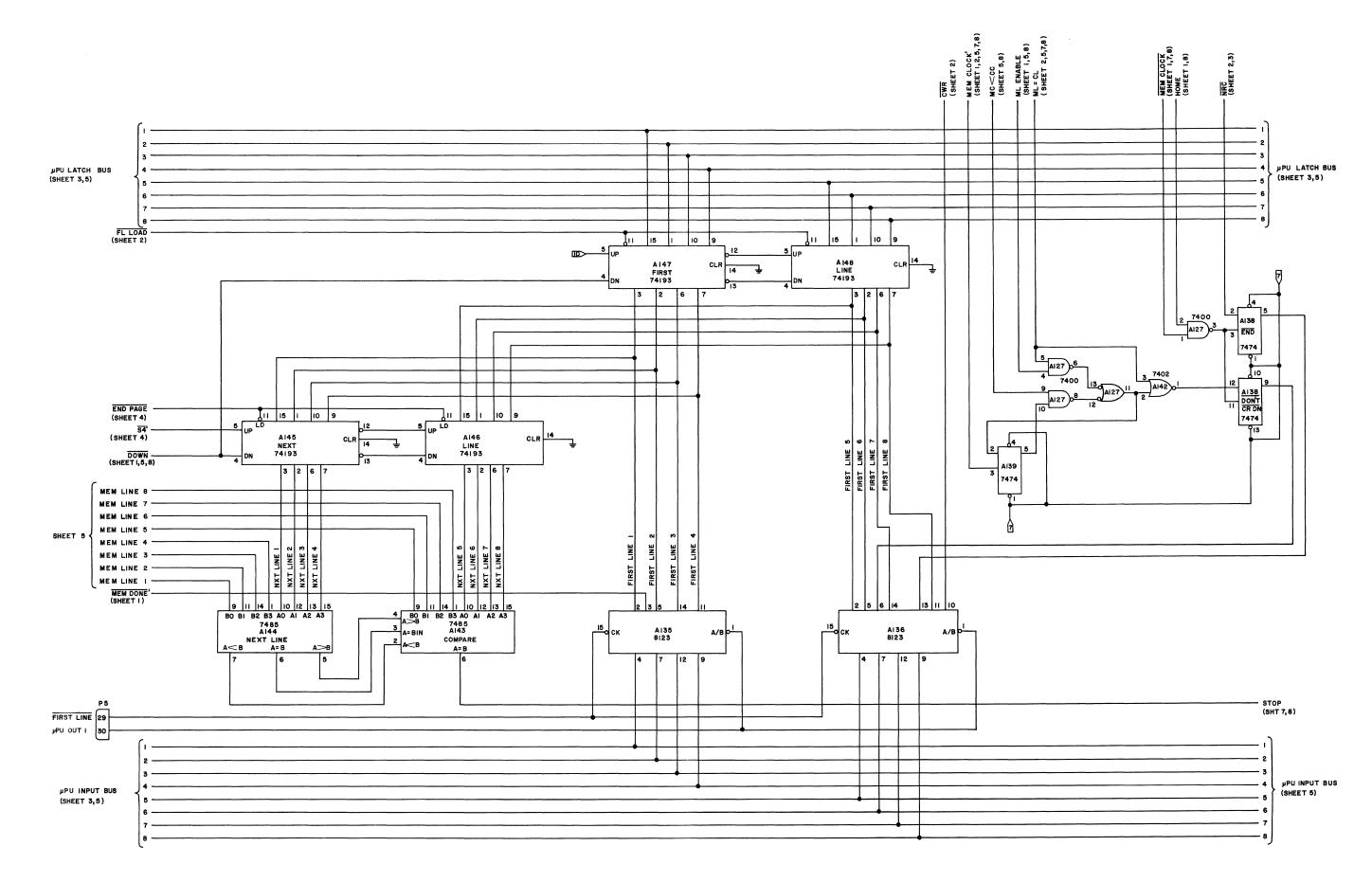

| 4.4.14 | Home Counter                       | 4-23/4-24 |

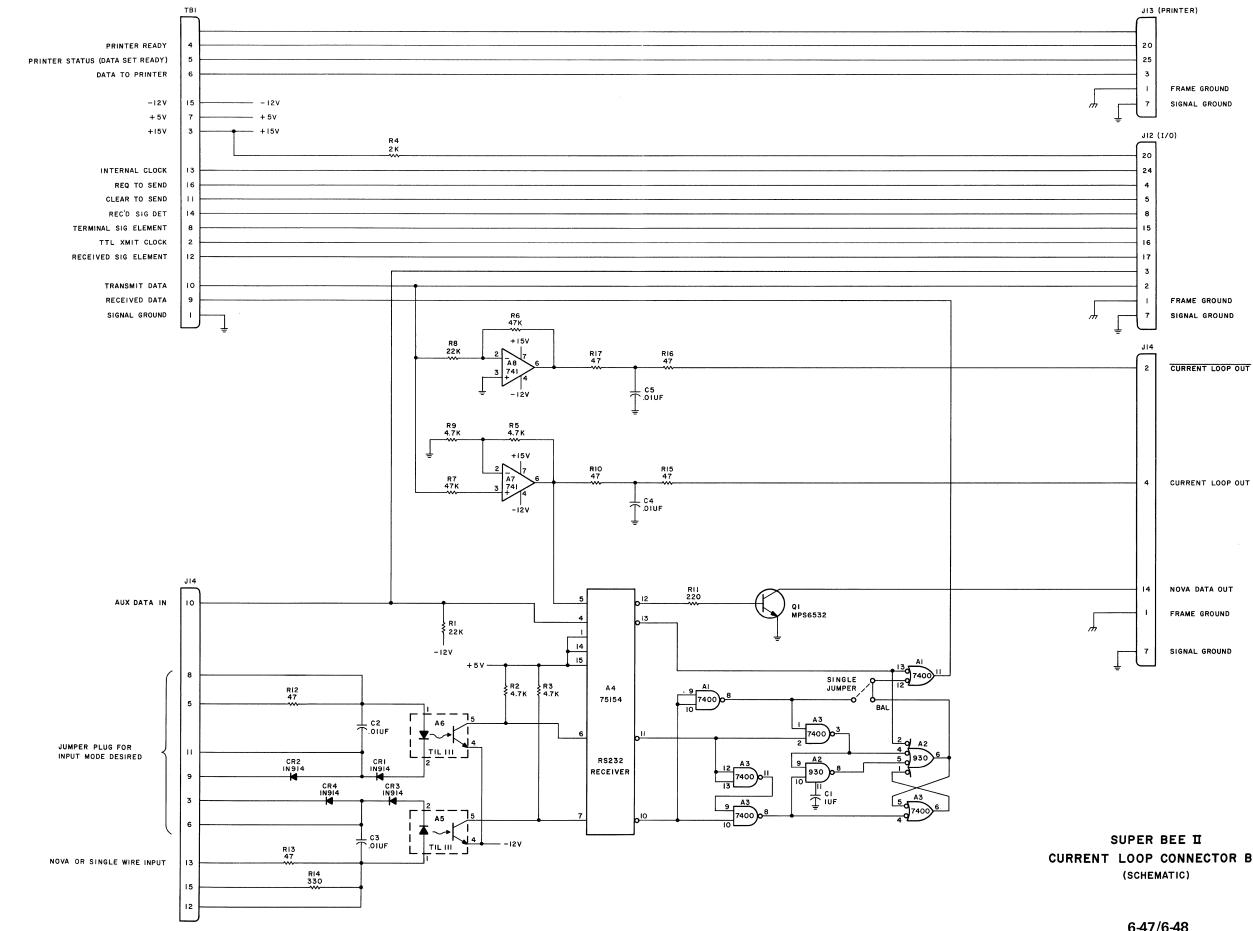

| 4.4.15 | Current Loop Adapter               | 4-23/4-24 |

#### SECTION V

#### MAINTENANCE

| 5.1 | INTRODUCTION                                     | 5-1  |

|-----|--------------------------------------------------|------|

| 5.2 | PREVENTIVE MAINTENANCE                           | 5-1  |

| 5.3 | CORRECTIVE MAINTENANCE                           | 5-1  |

|     | 5.3.1 Troublingshooting Aide                     | 5-1  |

|     | 5.3.2 Troublingshooting Equipment                | 5-1  |

|     | 5.3.3 Preliminary Troubleshooting Considerations | 5-2  |

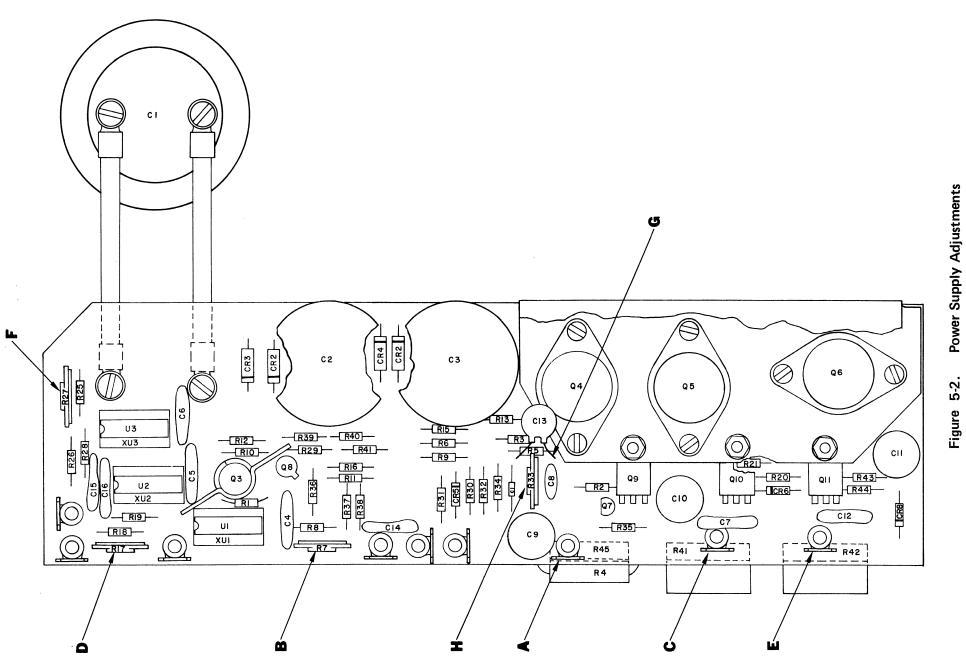

|     | 5.3.4 Adjustment Procedures                      | 5-24 |

|     | 5.3.5 Removal and Replacement Procedures         | 5-28 |

SECTION VI DIAGRAMS

SECTION VII GLOSSARY OF TERMS

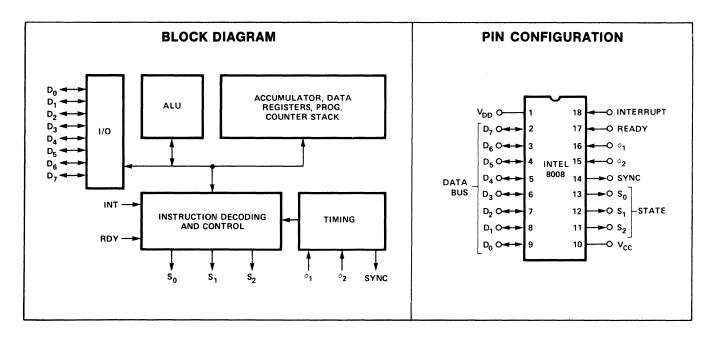

APPENDIX A EIGHT BIT PARALLEL CENTRAL PROCESSOR UNIT

#### APPENDIX B BALL MONITOR (TVB-12)

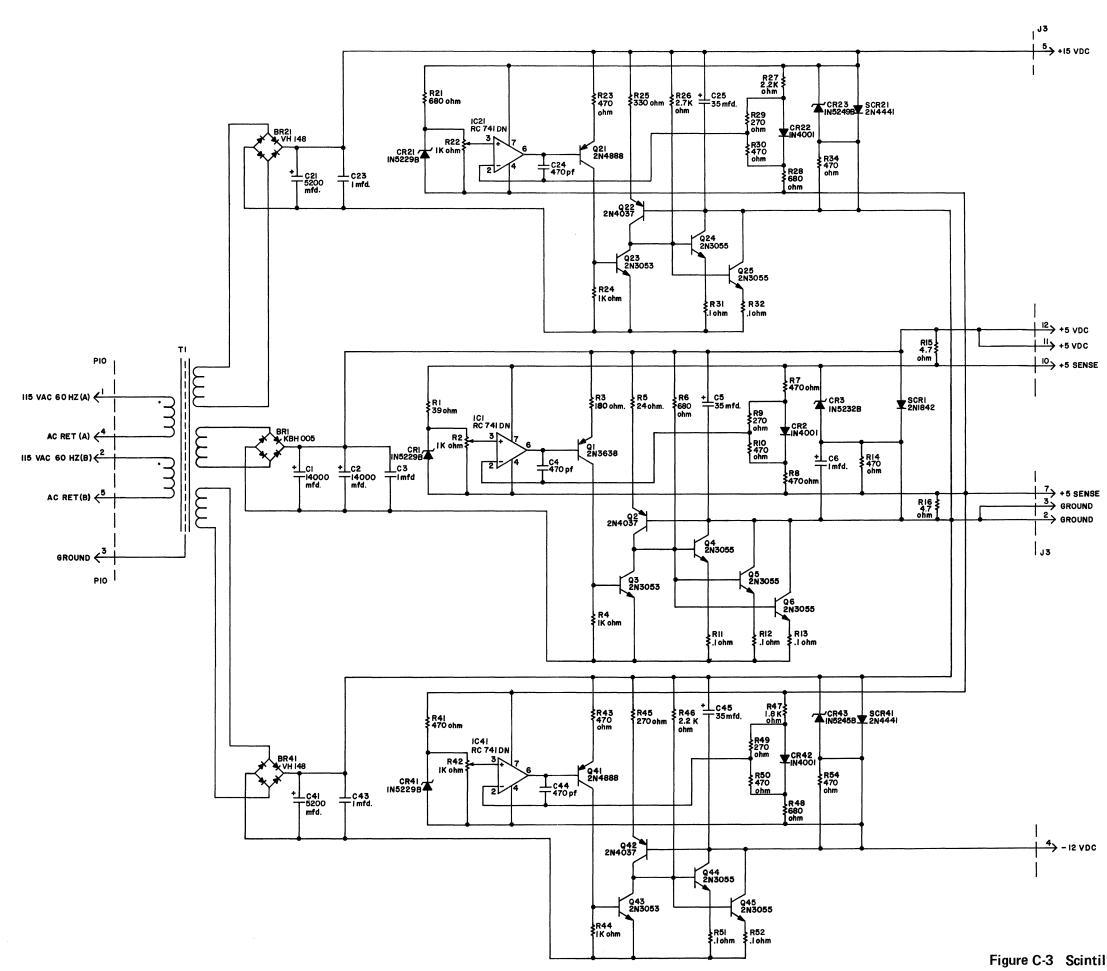

APPENDIX C SCINTILLONICS SECOND SOURCE POWER SUPPLY

v

### **FIGURES**

| FIGURE | TITLE                                                     | PAGE NO.  |

|--------|-----------------------------------------------------------|-----------|

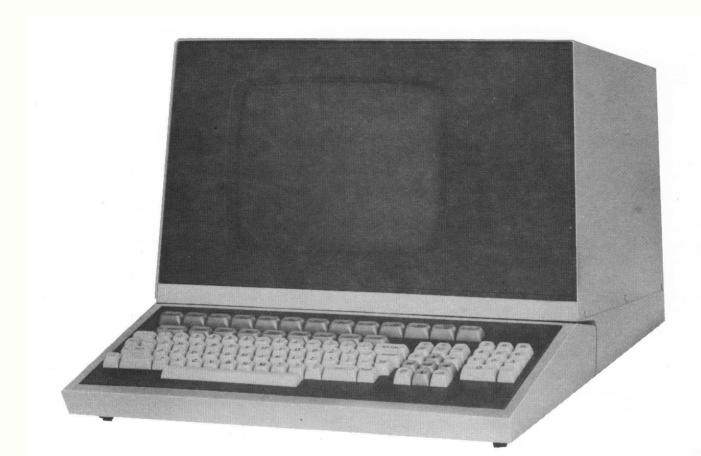

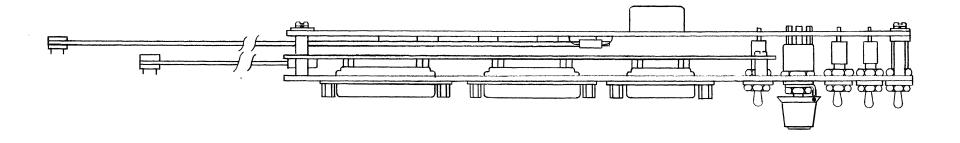

| 1-1    | SUPER BEE Computer Terminal                               | 1-2       |

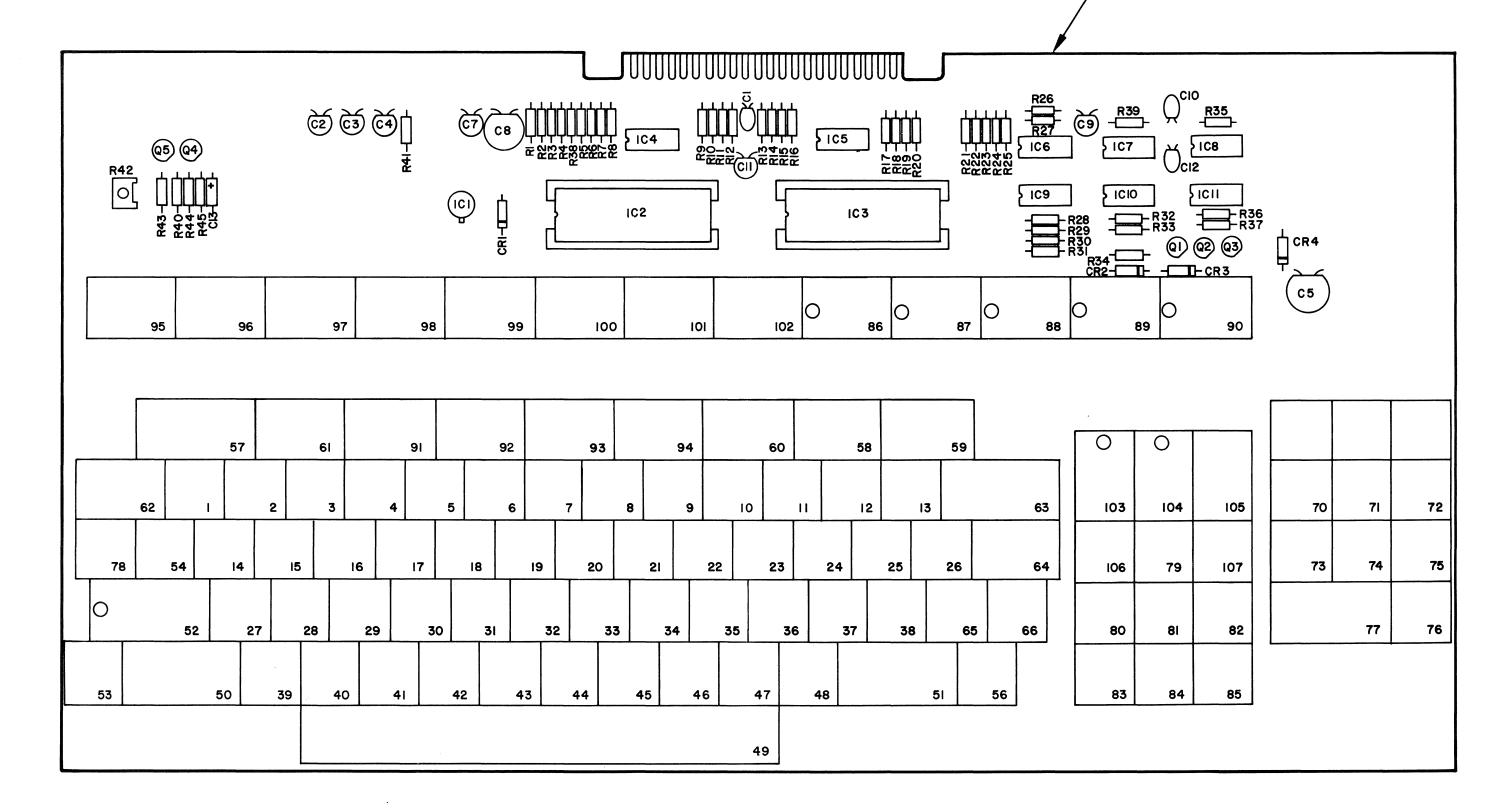

| 2-1    | Keyboard Controls and Indicators                          | 2-9       |

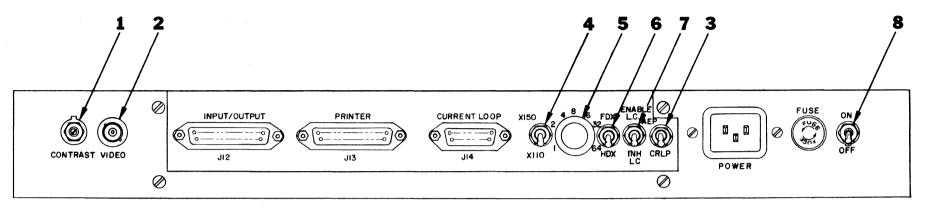

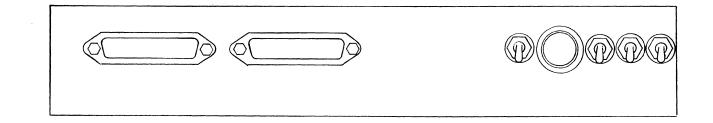

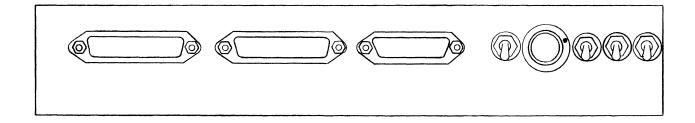

| 2-2    | Rear Panel Control                                        | 2-11      |

| 2-3    | ASCII Code Chart                                          | 2-19      |

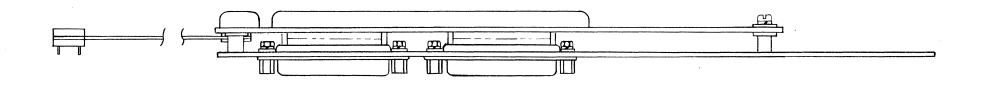

| 3-1    | SUPER BEE Mounting Requirements                           | 3-2       |

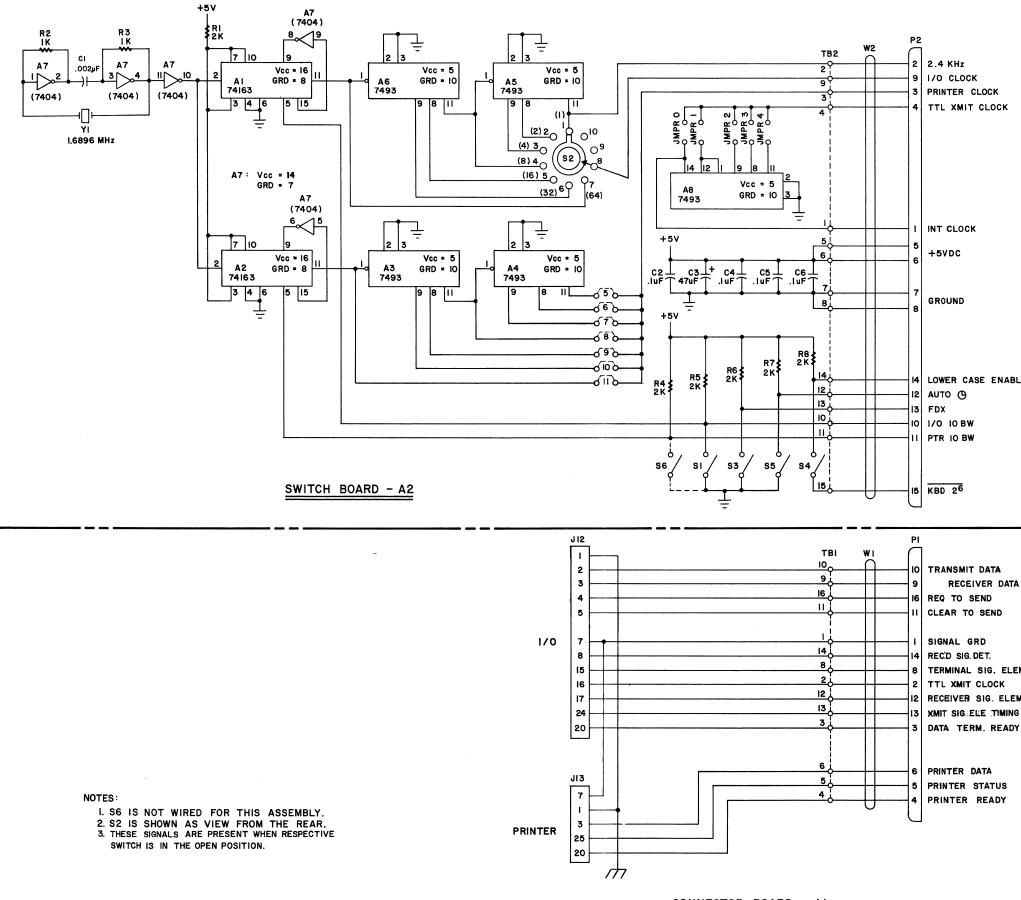

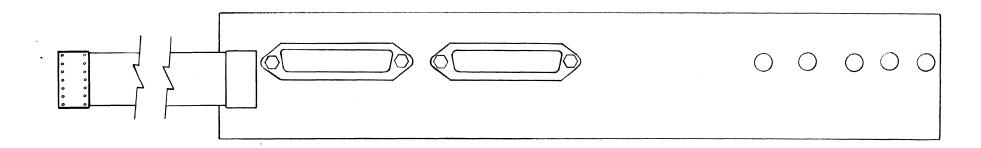

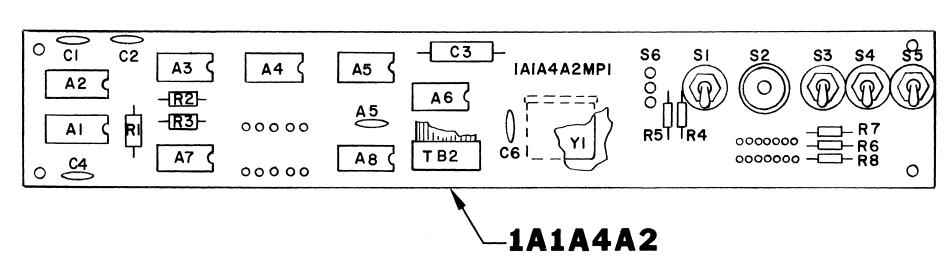

| 3-2    | I/O Processor Board Strapping Location                    | 3-6       |

| 3-3    | Printer Baud Rate and Internal Clock Multiplier Strapping | 3-8       |

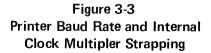

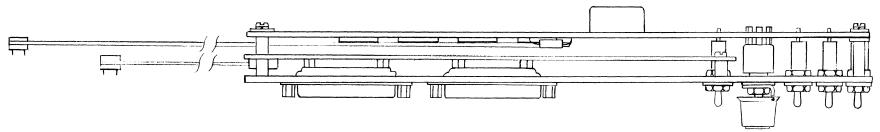

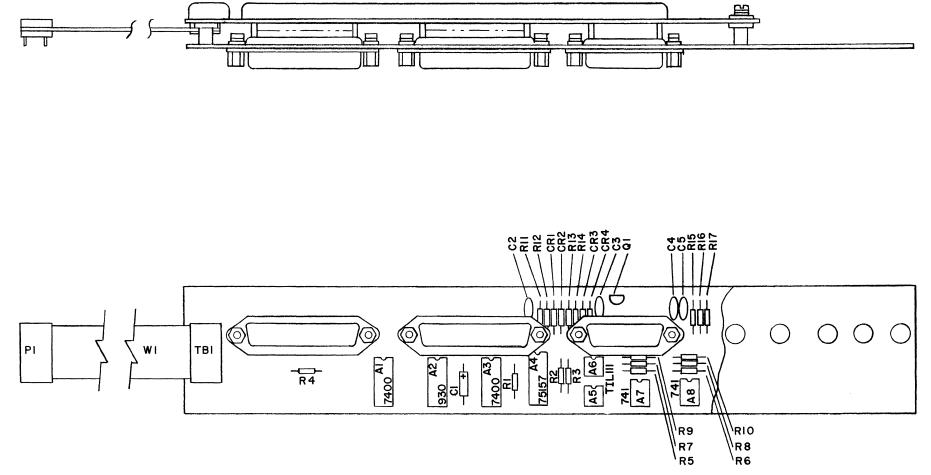

| 4-1    | SUPER BEE Major Components                                | 4-2       |

| 4-2    | Basic Block Diagram                                       | 4-3       |

| 4-3    | Intermediate Block Diagram                                | 4-4       |

| 4-4    | Interconnection Board Block Diagram                       | 4-5       |

| 4-5    | Power Supply Block Diagram                                | 4-7       |

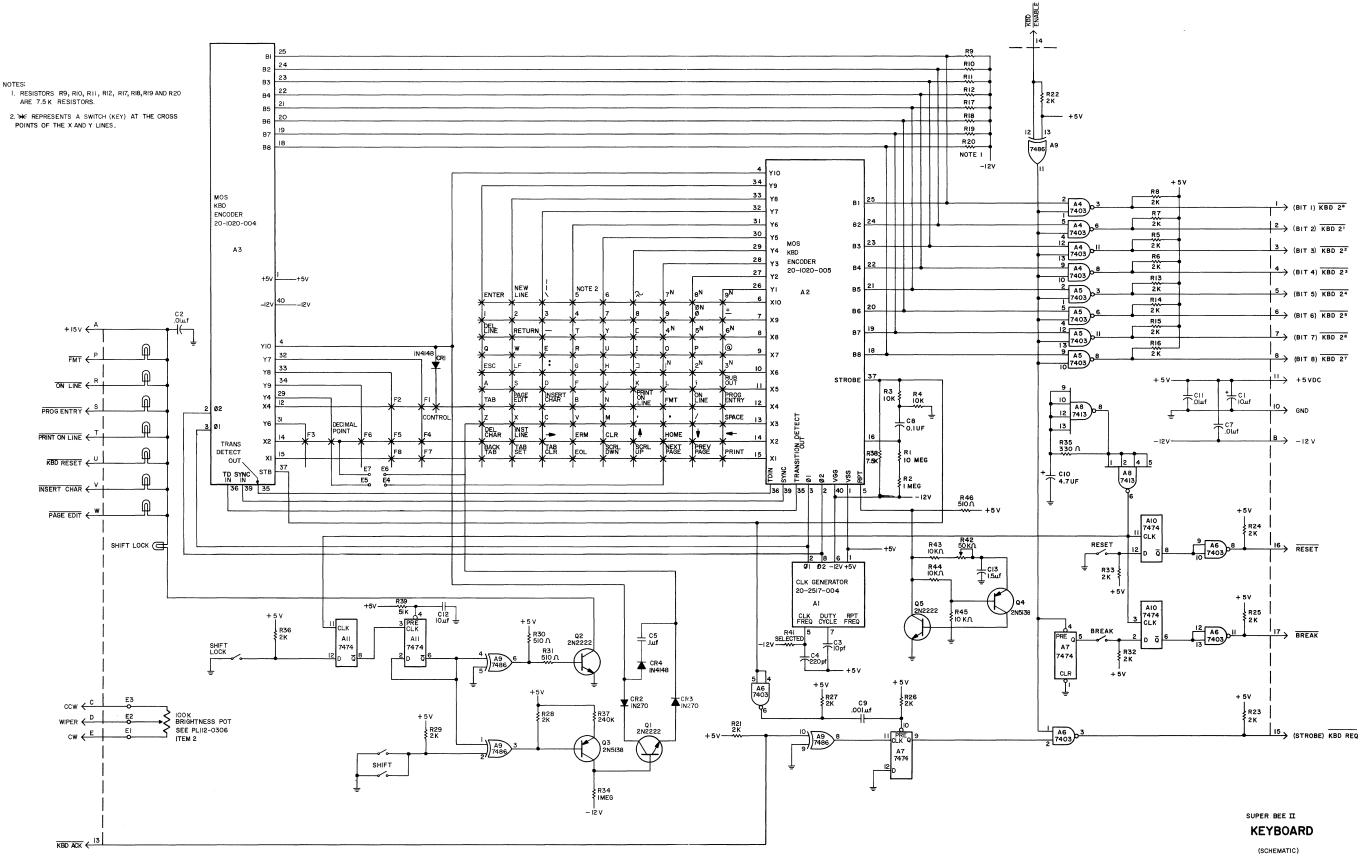

| 4-6    | Keyboard Block Diagram                                    | 4-8       |

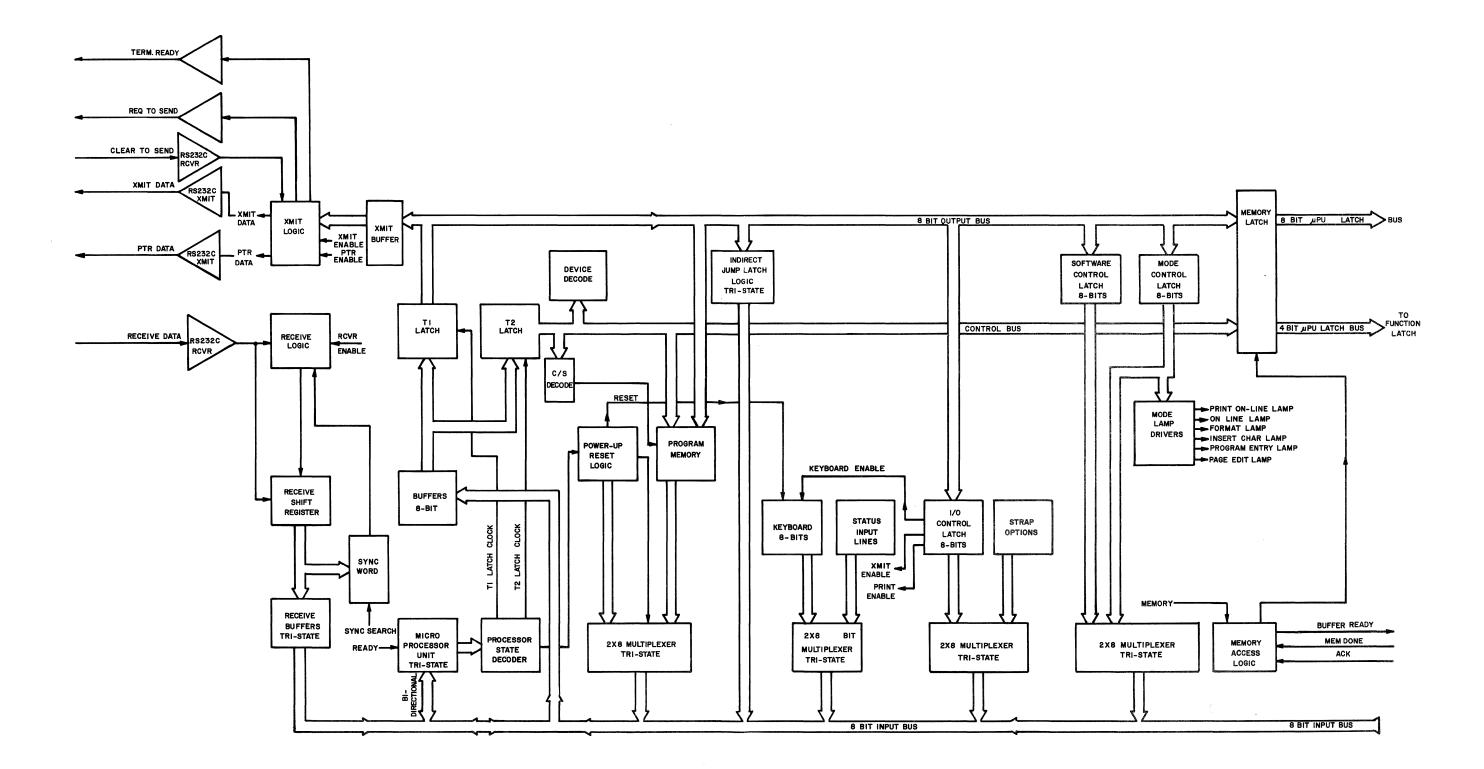

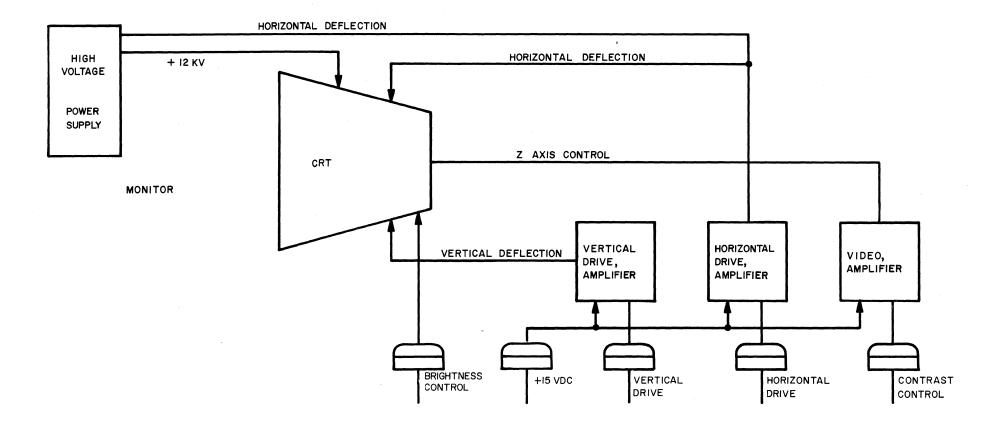

| 4-7    | I/O Processor Board Block Diagram                         | 4-9/4-10  |

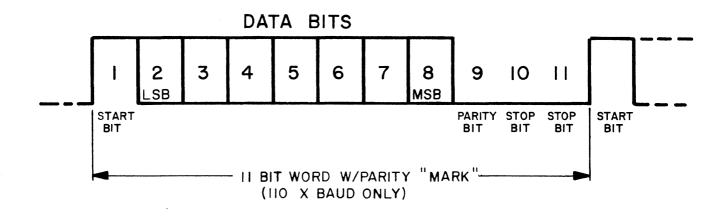

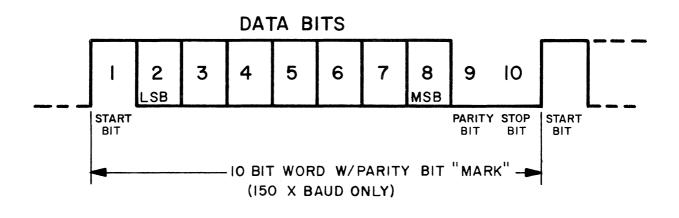

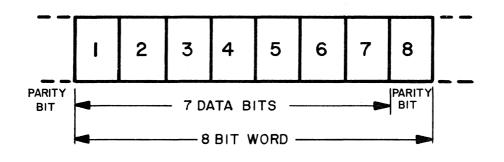

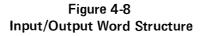

| 4-8    | Input/Output Word Structure                               | 4-11/4-12 |

| 4-9    | Display Board Block Diagram                               | 4-13/4-14 |

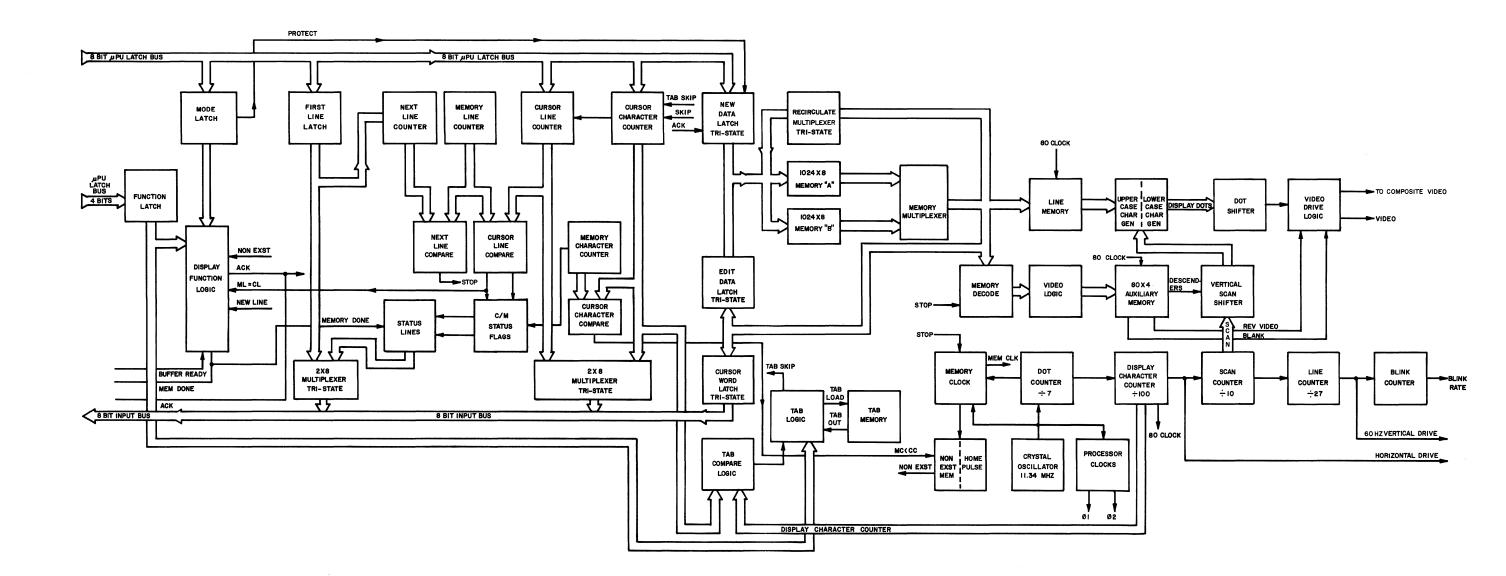

| 4-10   | Monitor Assembly Block Diagram                            | 4-16      |

| 4-11   | Interface Assembly Block Diagram                          | 4-17      |

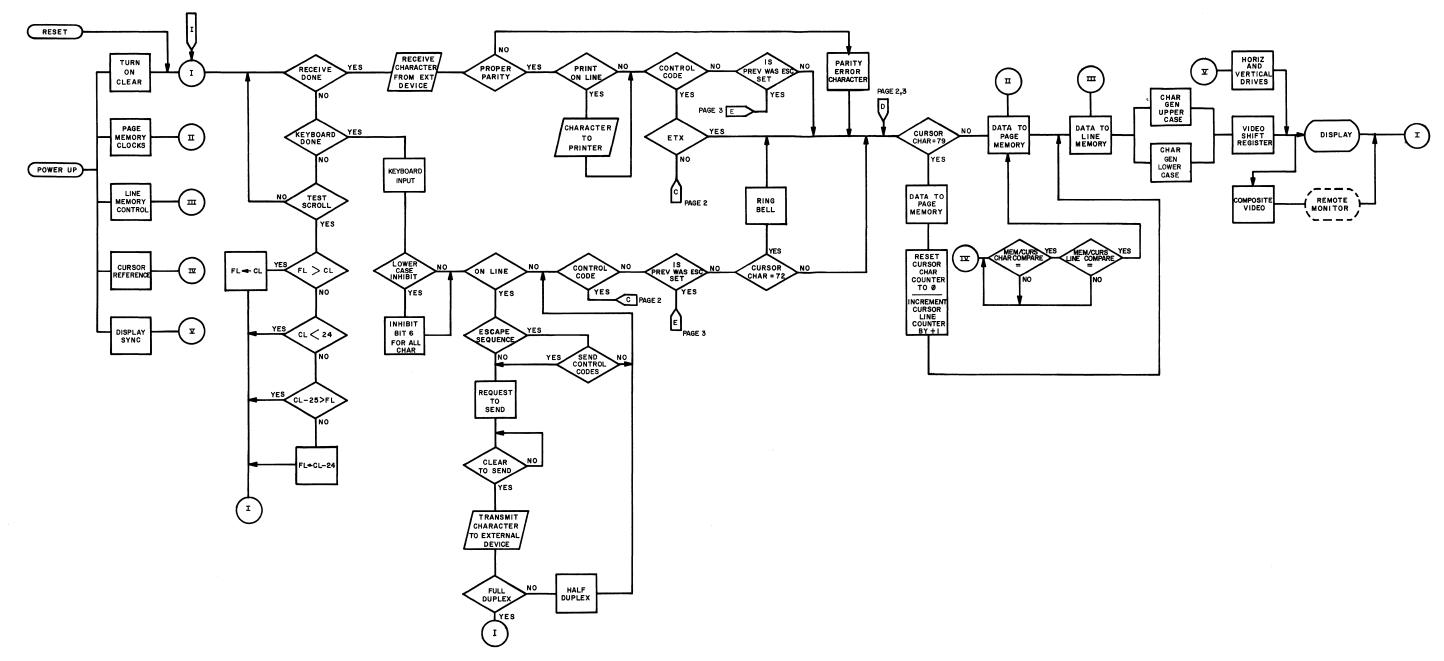

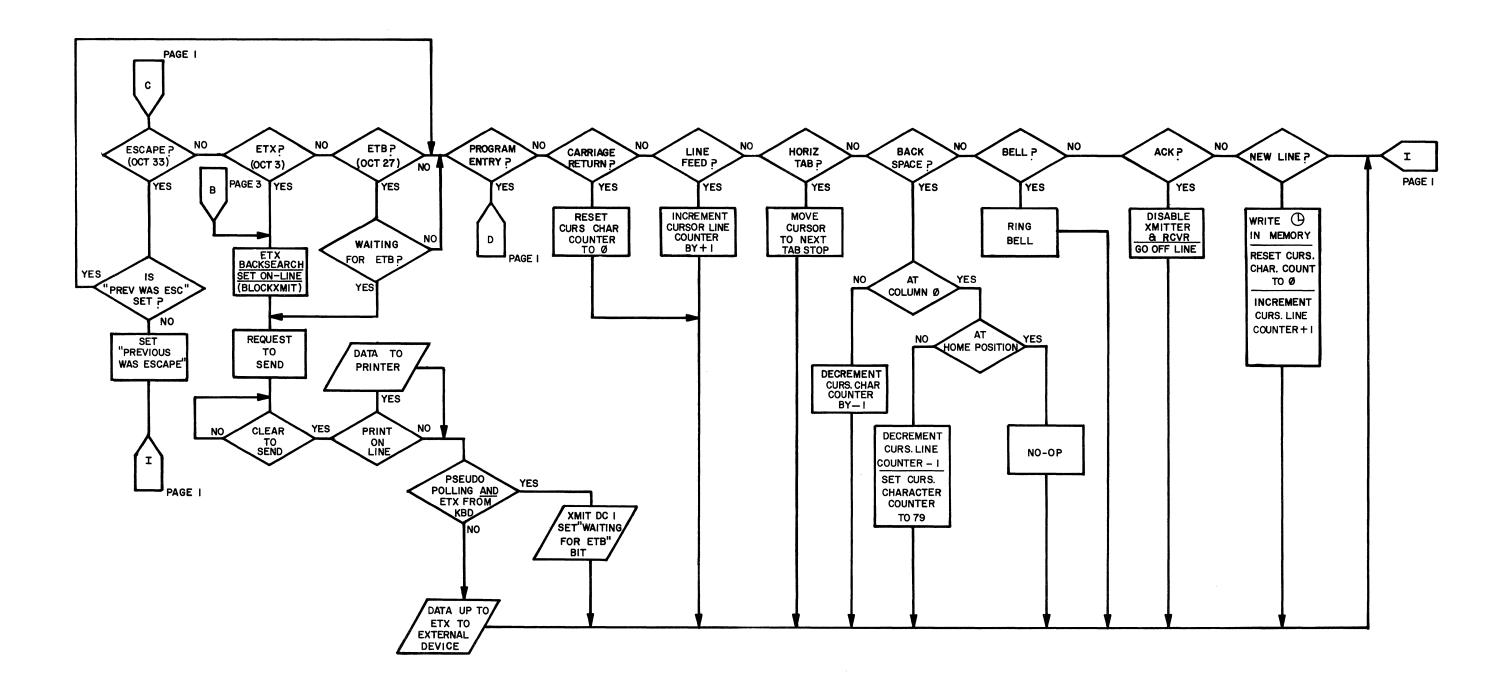

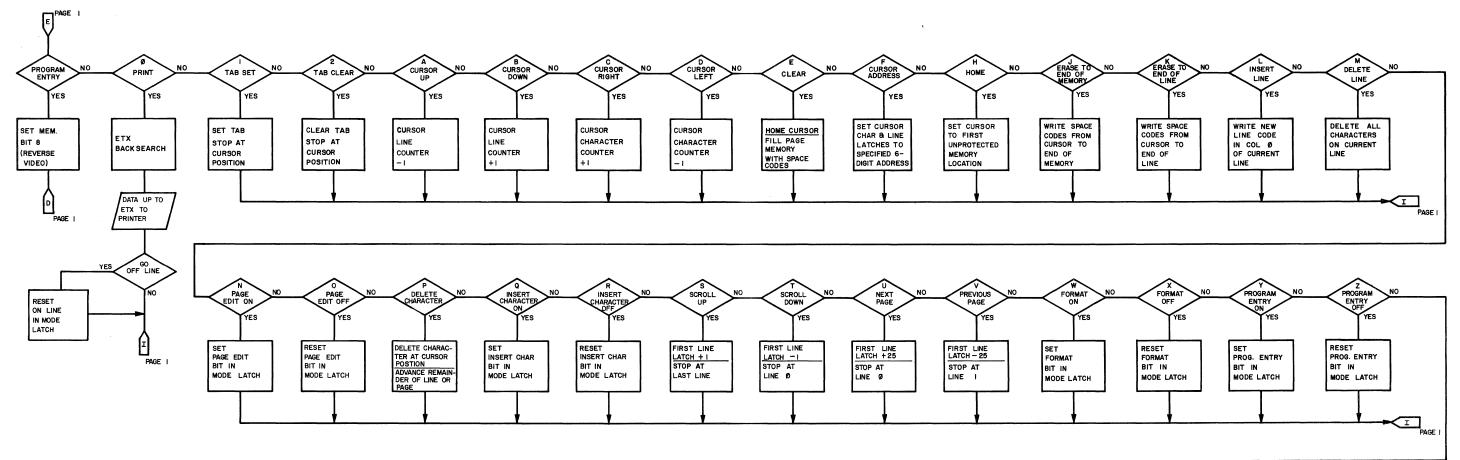

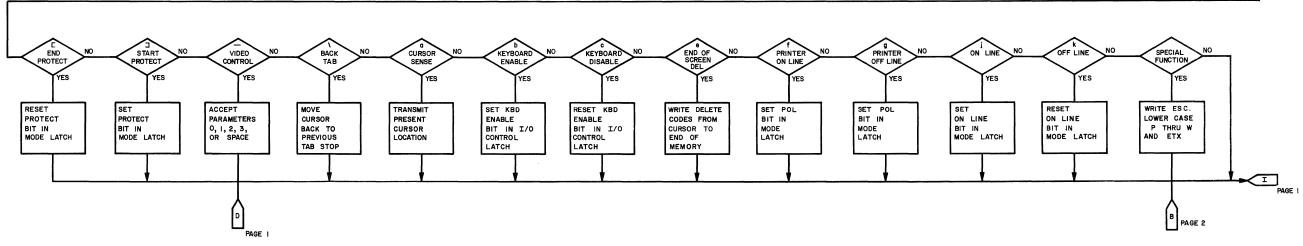

| 4-12   | Functional Flow Diagram                                   | 4-25/4-26 |

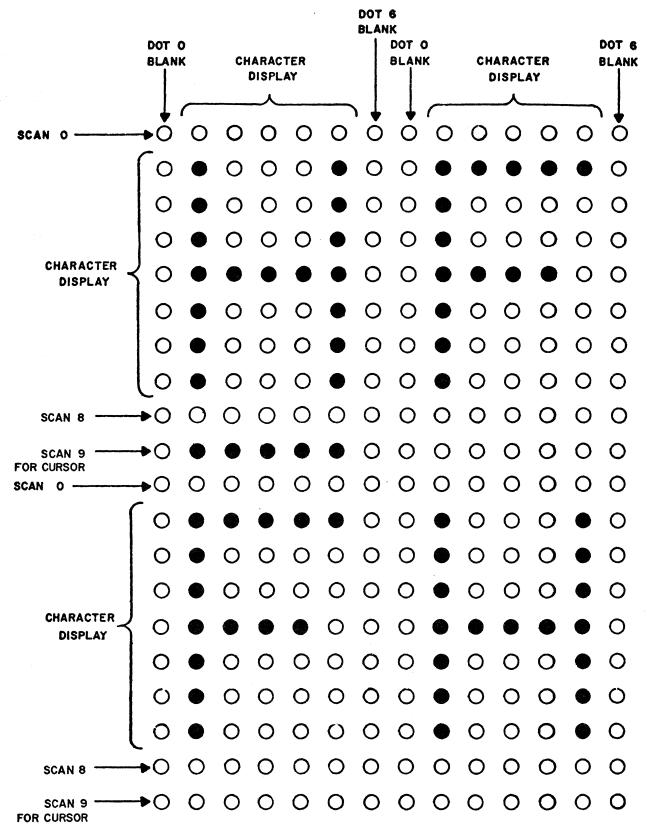

| 4-13   | Character Dot Matrix                                      | 4-20      |

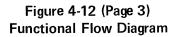

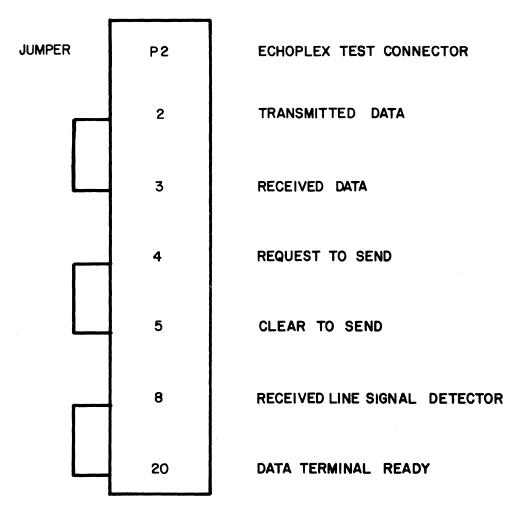

| 5-1    | Echoplex Connector                                        | 5-3       |

| 5-2    | Power Supply Adjustments                                  | 5-25      |

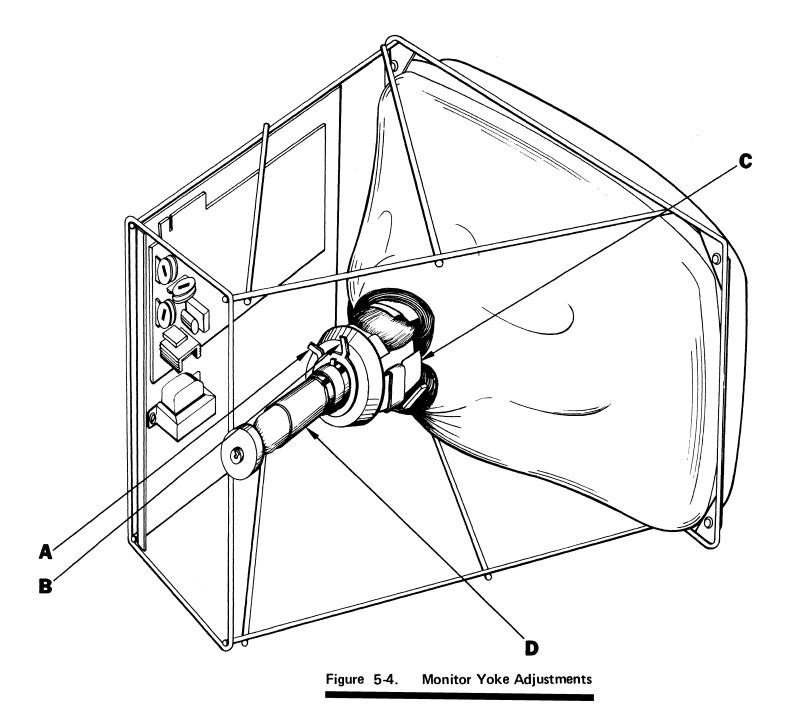

| j-3    | Monitor P. C. Card Adjustments                            | 5-26      |

| j-4    | Monitor Yoke Adjustments                                  | 5-27      |

### TABLES

| TABLE | NO. DESCRIPTION                                              | PAGE      |

|-------|--------------------------------------------------------------|-----------|

| 1-1   | SUPER BEE Computer Terminal Specifications                   | 1-8       |

| 2-1   | SUPER BEE Computer Terminal Keyboard, Controls and Indicator | 2-1       |

| 2-2   | Monitor Rear Panel Controls                                  | 2-10      |

| 2-3   | Control and Edit Function Operations                         | 2-15      |

| 2-4   | Operation Codes                                              | 2-20      |

| 2-5   | Timing Considerations                                        | 2-23/2-24 |

| 3-1   | Data Source Interface Connections                            | 3-3       |

| 3-2   | Printer Interface Connection                                 | 3-5       |

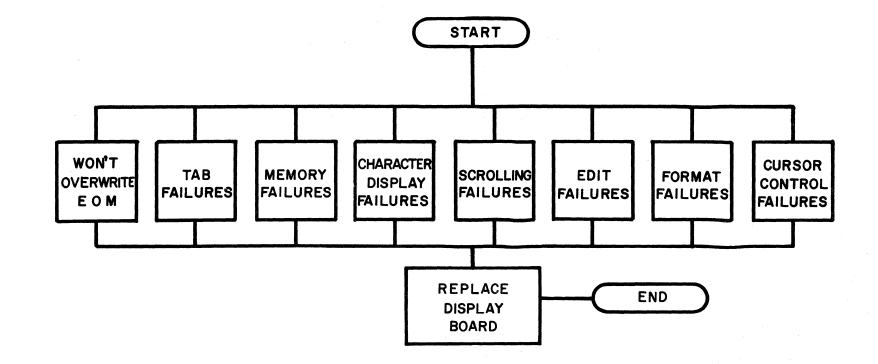

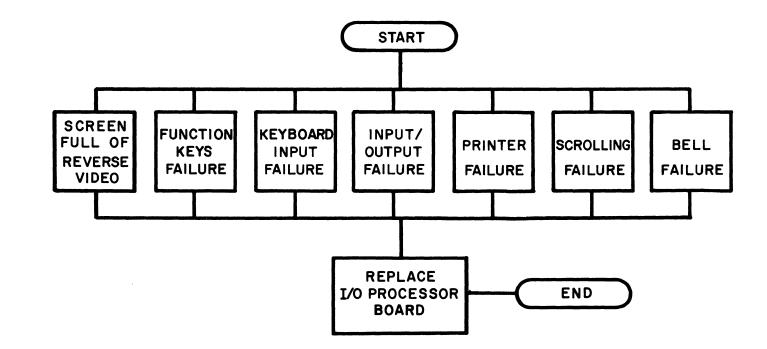

| 5-1   | Troubleshooting Flow Diagram Index                           | 5-2       |

| FUNCTION                        | BACK<br>PANEL                      | PROCESSOR<br>BOARD | INTERCONNECT<br>BOARD | SWITCH<br>BOARD                 | INTERNAL           |

|---------------------------------|------------------------------------|--------------------|-----------------------|---------------------------------|--------------------|

| HALF/FULL<br>DUPLEX             | SWITCH<br>HDX<br>FDX               |                    |                       |                                 |                    |

| LOWER CASE<br>INHIBIT           | SWITCH<br>ENBL L. C<br>INHBT L. C  |                    |                       |                                 |                    |

| I/O BAUD RATE<br>SELECT         | SWITCH<br>116<br>232<br>464<br>8   |                    |                       |                                 |                    |

| I/O BAUD RATE<br>MULTIPLIER     | SWITCH<br>110<br>150               |                    |                       |                                 |                    |

| AUTO EFFECIENT<br>PAGING        | SWITCH<br>AUTO EFF<br>PAGE<br>RRLF |                    |                       |                                 |                    |

| PSEUDO POLL                     |                                    | STRAP<br>IN<br>OUT |                       |                                 |                    |

| BACK SEARCH<br>BLOCK TRANSMIT   |                                    | STRAP<br>IN<br>OUT |                       |                                 |                    |

| PARITY TEST                     |                                    | STRAP<br>IN<br>OUT |                       |                                 |                    |

| ASYNC / SYNC<br>OPERATION       |                                    | STRAP<br>IN<br>OUT |                       |                                 |                    |

| SEND CONTROL<br>CODES           |                                    | STRAP<br>IN<br>OUT |                       |                                 |                    |

| GO-OFF-LINE                     |                                    | STRAP<br>IN<br>QUT |                       |                                 |                    |

| EXT CLOCK                       |                                    | STRAP<br>IN<br>OUT |                       |                                 |                    |

| STORE SPECIAL<br>FUNCTIONS      |                                    | STRAP<br>IN<br>OUT |                       |                                 |                    |

| PRINTER BAUD<br>RATE SELECT     |                                    |                    |                       | STRAP<br>116<br>232<br>464<br>8 |                    |

| PRINTER BAUD<br>RATE MULTIPLIER |                                    |                    |                       | 8 STRAP<br>110<br>150           |                    |

| TTL KMIT<br>CLOCK               |                                    |                    |                       | STRAP<br>1 8<br>216<br>4        |                    |

| POWER<br>OPTION                 |                                    |                    |                       |                                 | STRAP<br>IN<br>OUT |

#### SECTION I GENERAL INFORMATION

#### 1.1 INTRODUCTION

This manual provides a general equipment description and installation and operation instructions for the SUPER BEE Computer Terminal. Section I provides a general description and the specifications of the terminal and Section II provides basic operating procedures. Installation procedures are given in Section III. This manual provides the operator with sufficient information to obtain a thorough understanding of the operational characteristics of the equipment.

#### 1.2 PRODUCT DESCRIPTION

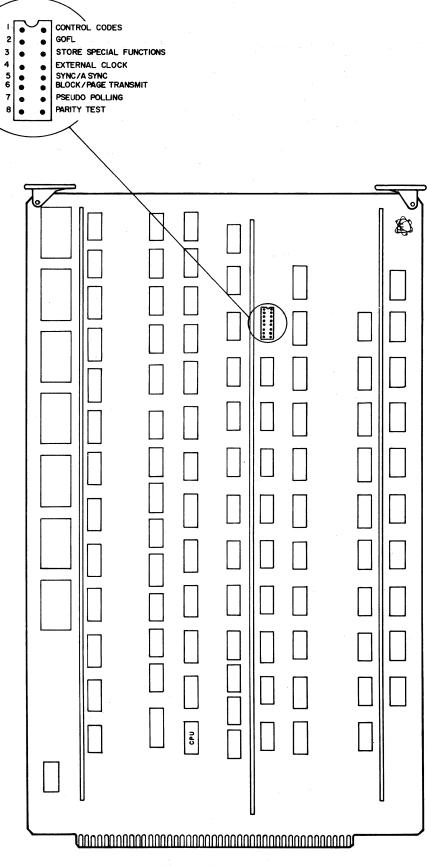

The SUPER BEE Computer Terminal shown in Figure 1-1, is a self-contained, operator controlled remote display terminal with a detached ANSI keyboard. The terminal is designed for use in serially transmitting information to, and reveiving information from, an interconnected data source. The terminal will operate to exchange data at any of several preselected transmission rates; 9600 baud maximum.

The SUPER BEE employs a 12-inch (measured diagonally) rectangular television type monitor which is implemented to display up to 25 lines with 80 characters. Each character is generated from a 5- by 7 -dot matrix with two-dot spacing between adjoining characters.

The SUPER BEE Terminal has a detached keyboard interfaced to the display unit by means of a flexible 4-foot cable. The keyboard employs the N-key rollover feature. When any alphanumeric key is held down for longer than half a second, it automatically repeats at a rate of approximately 30 characters per second. Some of the control keys also auto repeat, however auto repeat has been inhibited where not meaningful.

Interfacing is accomplished via the rear panel connectors. The Input/Output and Printer connectors are connected in parallel and will interface most standard serial ASCII printers. The printer data can be transmitted at a separate baud rate from that of the terminal and may be adjusted from 110 to 9600 baud. A Video connector is provided for connection to a remote display monitor. The output from this connector is a composite video signa capable of driving 1000 feet of 50-ohm coaxial cable.

#### 1.3 PERFORMANCE CHARACTERISTICS

#### **1.3.1** Modes of Communication

#### Half-Duplex/Full-Duplex Transmission

The SUPER BEE Terminal may be operated off-line or on-line. A rear panel switch allows the operator to select either half-duplex (HDX) or fullduplex (FDX) communications. Full-duplex operation allows data to be transmitted with each keyboard entry wherein the terminal's receiver input is enabled for immediate computer reply of the transmitted data (echoplex) to verify proper receipt of data. Half-duplex data transfer is generally used for sending precomposed messages, either a few lines at a time (block mode) or an entire memory dump at a time (page mode). While transmitting data in either the page or block modes, both the keyboard and the receiver inputs are disabled. Operation in the off-line mode allows the operator to edit the message before block transmission of the data. Operation in the on-line mode enables the transmitter and the receiver.

#### Synchronous or Asynchronous Transmission

The SUPER BEE Terminal allows the selection of either serial synchronous or serial asynchronous transmission. During synchronous operation, the word structure consists of eight bits; seven data bits and a parity bit. Synchronization is accomplished by receiving and identifying two or more sync codes at the beginning of a transmission; synchronous operation is not possible during conversational type transmission (character by character). The asynchronous word structure consists of a start bit, seven data bits, a parity bit, and one or two stop bits (One stop bit if baud rate switch is in

Figure 1-1 SUPER BEE Computer Terminal X150 position and 2 stop bits when in X110 position).

#### **Data Compression**

Delete codes are used in data compression to eliminate the transmission of trailing spaces. Transmission of only operator-entered data is possible by placing a delete code after the data to be transmitted. (Data on the line after a delete code is not transmitted.) When a delete code is encountered during transmission, a Carriage Return and Line Feed (CR-LF) are sent as a record separator and a CR-LF are performed by the terminal. Transmission continues at the first character location in the next line.

#### **Conversational Transmission**

During conversational transmission, the CRT terminal must be on-line. Received alphanumerics are stored in memory and displayed. Received control codes or ESC sequence codes cause the unit to perform the appropriate function and are not stored in memory or displayed. An exception is the "NEW LINE" code which is acted upon and displayed as a space. Keyboard-generated alphanumerics are transmitted to the computer. In full-duplex operation, control codes and ESC sequence codes are transmitted but not acted upon until echoplexed to the terminal.

#### **Block Transmission**

Block transmission is used to allow the operator to prepare data off-line and then transmit the data as a unit. The transfer can be initiated either from the keyboard or the I/O or the printer. A block transfer is initiated from the keyboard by depressing the ENTER key.

If the terminal is strapped for the Pseudopoll on and ETX search off, the following sequence is performed:

a. The cursor is positioned in the first character location in the memory or in format mode, the first character location in the first unprotected field.

b. The terminal transmits a DC1 code on the I/O and waits to receive an ETB (Control W) from the I/O. c. Upon receipt of the ETB, data is transmitted out on the I/O until an ETX code is transmitted, at which time transmission is stopped.

A block transfer initiated remotely from the I/O requires the ETX code to be received and the cursor to be positioned at the location where desired transmission will commence upon the receipt of an ETB (Control W). The transfer proceeds as though it were initiated from the keyboard. When Pseudopoll is configured to off, the data transmission begins as soon as the Clear-to-Send signal is received from the I/O.

If the ETX search is configured to on, a reverse search is made for the most recent ETX code in the memory. When located, the curosr is positioned at the first character location in the next line. The transfer will begin from that point.

When the terminal is strapped for pseudopolling off, it is the CPU's responsibility to see that an ETX is placed in memory before sending the terminal an ETB.

When a NEW LINE code of DELETE code is encountered in the memory during a block transfer and while operating in the Character mode, a CR-LF function is performed and is transmitted to the I/O and the printer's I/O. There should not be an ETX code stored after a DELETE code in the same line. When the DELETE code or a protected location in the memory is sensed, the CR-LF function codes are transmitted to the I/O and the printer I/O internally, a TAB function is performed.

The block transfer operations are performed the same for a PRINT command except that when an ETX is sensed, the CR-LF codes are transmitted in place of the PRINT command. The terminal can also be configured to switch to off-line (local) after printing.

When the CPU ends transmission of a block of data while in synchronous mode and the terminal is to remain on-line, the following codes can be used to re-establish sync with the computer: Cursor Sense: will start a sync search, after sending out the cursor address, until the CPU sends out a new block of data.

<u>Print:</u> Without go-off-line, will reply with fewer sync codes and go into sync search.

#### **Baud Rate Selection**

Transmission rates are switch-selectable at the rear of the terminal. The baud rate switch has seven positions 1, 2, 4, 8, 16, 32, and 64. The baud rate multiplier switch has two positions; 110 times or 150 times. The selected position causes the selected baud rate to be multiplied by 110 or 150. The switches produce rates of 150, 300, 600, 1200, 2400, 4800, and 9600 baud for 10-bit word operation; or 110, 220, 440, 880, 1760, 3520 and 7040 baud for 11bit word operation.

#### 1.3.2 Operating Modes

The SUPER BEE Computer Terminal normally operates in one of three modes; the Character mode, the Program Entry mode, and the Format mode. In each mode, the SUPER BEE can be operated either on-line or off-line.

#### **Character Mode**

Character mode is selected upon poweron or depression of the RESET key. In this mode, the monitor displays all characters and reacts to all control codes. Depression of RESET key automatically returns the terminal from any other mode to Character mode.

**Character Mode (Off-Line)** - Characters entered from the keyboard are stored in the terminal memory and displayed but not communicated to the I/O port. Control and escape sequence codes are dependent upon appropriate strapping. Characters received at the I/O port are ignored.

Character Mode (On-Line) Characters entered from the keyboard are transmitted from the I/O port as they are entered. If operated half duplex (HDX), the characters are stored in the memory and displayed as they are entered. When operated full duplex (FDX), the characters are transmitted to the I/O port only, and are stored in the memory and displayed if a remotely connected data source echoes each transmitted code.

#### **Program Entry Mode**

A Program Entry mode is selectable from the keyboard or from a remote data source intiated by an escape sequence code. When in the Program Entry mode, the terminal does not respond to control and escape codes, but stores these codes in memory and displays their associated character or symbol. NEW LINE and ENTER functions are exceptions. They are displayed in normal video and acted upon. The Program Entry mode is intended to display control characters and escape sequence characters prior to transmission or after receipt of a transmission Programming from the terminal is made possible through the implementation of the Program Entry mode.

Program Entry Mode (Off-Line)- Characters entered from the keyboard are stored in the terminal memory and displayed but not transmitted to the I/O port. Control codes are displayed as special symbols and are not acted upon, with the exception of NEW LINE and ENTER. Escape function characters are displayed in reverse video and are not acted upon.

Program Entry Mode (On-Line)- The terminal operates the same as that for the Program Entry mode (off-line), with the exception that data entered from the keyboard is transmitted to the I/O port. The transmitted control escape and sequence codes are dependent upon appropriate strapping.

#### Format Mode

A Format mode is selectable from the keyboard or from a remote data source initiated by an escape sequence code. In the Format mode, the terminal display has protected fields in which the cursor can be positioned, but no data may be entered. If desired, unprotected fields may be delimited by use of brackets or reverse video to indicate the area for data entry.

Format Mode (Off-Line)- Characters entered from the keyboard are stored in the unprotected locations in the terminal's memory and displayed but are not transmitted to the I/O port. Selectable edit functions (INSERT LINE and DELETE LINE) are inoperative in Format mode.

Format Mode (On-Line)- Operation in this mode is the same as that for Format mode (Off-Line), except that data entered from the keyboard is transmitted to the I/O port. A CR-LF is transmitted at the end of each field as a field delimiter.

#### Print-On-Line Mode

The Print-On-Line mode is a selectable keyboard function or initiated from a remote data source. The I/O baud rate is slaved to the selected printer baud rate of the SUPER BEE when the terminal is operating in the Print-On-Line mode. The data sent to or received by the terminal is both displayed on the terminal and printed by the printer. Data transmitted from the terminal is sent to both the I/O port and the printer port at the selected printer baud rate. The CPU will supply null codes for the "Line Full" on the print when the terminal in Printon-Line mode.

#### 1.3.3 Display Organization

The display is organized on a page basis, where the page contains 25 lines with 80 character positions in each line. Any of the 96 USASCII codes can be displayed on the monitor in a line-page organization. If a line in the memory has less than 80 characters, the displayed line contains blanks or spaces filled to the 80th character.

Upon power-up or depression of the RESET key, the Character mode is selected. In this mode of operation, the CRT monitor displays all characters and reacts to all control codes. A keyboard or I/O code selectable Program Entry mode prevents the terminal from reacting to control and escape function codes, and displays instead the control symbols and escape function codes as reverse video characters. In the Format mode of operation, protected areas of the display cannot be erased or overwritten.

When it is required that data serve as alarm or status indicators or direct attention, video can be displayed as follows: (1) normal video (white characters on a black background); (2) normal video blinking; (3) reverse video (black characters on a white background); and (4) reverse video, blinking. These functions are initiated by an escape sequence operation which stores a single video control character in memory and which is displayed as a space. The reverse video and/or blink field is terminated by the end of the line or by either the NEW LINE or Line-Blink-Off codes. Additionally, all level video and blink control codes in memory may be reset with space codes by the Page-Blink-Off command.

#### 1.3.4 Memory Organization

The memory in the SUPER BEE terminal is organized in such a manner that only the display characters and receiving control codes are stored in memory. This means that if only 10 characters are written on a line, only 10 memory locations are used for display of that line. The other 70 spaces on that line are not stored. This technique is known as "efficient paging." The total number of memory locations is 2048. This means, for instance, that through the use of efficient paging, 256 lines of 7 characters each can be stored (The maximum number of lines is limited to 256). Only 25 lines of memory data can be displayed at one time; however, the memory can be scrolled up or down to bring any 25-line window of the memory data into view.

When a CLEAR operation is performed the entire memory is filled with space codes and the cursor is positioned home. The memory is then organized as 80 characters per line and displayed as an entire blank screen. As data is entered, display characters replace the space character as defined by the cursor location. The memory organization remains the same until a "NEW LINE" code is entered into the terminal. The "NEW LINE" code is stored into the display memory at the cursor location and terminates the display of that particular line. (The remaining part of that line is displayed as blanks that occupy no memory locations.) The code entered immediately following the "NEW LINE" code in memory is displayed as the first character on the next

line. If the 80 character by 25 line format must be retained, the Carriage Return-Line Feed (CR-LF) functions may be keyed in to move the cursor to the first character position on the next line. After all 2048 memory locations are used up, the memory continues to receive data and scrolls up. At the end-ofmemory indicator, when a new character is received, a line of data is lost from the top of the memory.

The cursor is always displayed on screen and if any cursor control is given which would move the cursor off the display, the display will be scrolled up or down so that the cursor will remain displayed on the screen. With efficient paging, the cursor may be positioned to an undefined location on a particular line by moving it to the right of the New Line (N/L) position. When this happens, data cannot be entered on this portion of the line to the right of where the N/L code was entered. If insertions are to be made in a particular line, the cursor must be positioned to a character located to the left or under the N/L position. Any time the cursor is under the N/L position, the terminal automatically operates as though in the Insert Character mode.

#### 1.3.5 Memory Overwrite

When data input has filled all memory locations, Cursor Right and Cursor Down are inhibited to prevent the cursor from moving through end-of-memory. If the last line of memory appears as the first line of the display, Scroll Up, Next Page, Cursor Right and Cursor Down functions are inhibited so that they do not move the cursor beyond the end of the 2048 memory locations. Line Feed (LF), Horizontal Tab (HT), and simply writing data will cause Memory Overwrite to occur. When memory overwrite does occur, the first line of memory is filled with DEL codes and made available for additional data. Care must be taken that these DEL codes do not cause mistakes if the memory is to be retransmitted, as DEL codes are interpreted as CR-LF codes and will cause the ETX code to be missed if preceded by a DEL code in the same line.

#### 1.3.6 Space Overwrite (SPOW)

The space bar normally writes a space code in memory and advances the cursor one character position to the right. However, following the operation of a Carriage Return (CR), the space code re-acts to perform a Cursor Right function but does not write a space. The SPOW latch is reset by performing a NEW LINE, Line Feed, HOME or TAB function.

#### 1.3.7 Character Overwrite

When an error is made in entering a character (e.g., a misspelled word) a correction can be made by overwriting the character. The cursor is returned to the character in error by using Cursor Right, Left, Up or Down functions to locate the cursor directly under the character to be corrected. The correct character can then replace the old character. The use of Delete Character or Insert Character functions may be required to allow for a fewer or greater number of characters.

#### **1.3.8 Special Function Keys**

Eight special function sequence keys (F-1 through F8) are provided to allow the user to call up routines unique to the user. Any of the eight escape sequence codes (ESC and p through ESC and w), when generated by the keyboard, are stored as a two-code sequence starting at the cursor's location in the memory. When the terminal is configured to "store special function", the two-code sequence is stored in page memory. When the terminal is configured to "send special function", the two-code sequence followed by an ETX is stored in memory and the ENTER function is performed. During the ENTER function, if the terminal is configured for psudeopolling, the "Request For Service" code DC1 is sent and the terminal waits for an ETB to begin transmission,

#### 1.3.9 Printer Port

The serial printer port operates at RS232C logic levels and outputs negativetrue data. The SUPER BEE terminal has two printer communication modes: (1) Print-On-Line, and (2) Print. In the Print-

)

On-Line mode, the I/O baud rate is slaved to the selected printer baud rate of the SUPER BEE. Data sent to or received by the SUPER BEE terminal is both displayed on the terminal and printed by the printer. Data transmitted from the terminal is sent to both the I/O port and the printer port at the selected printer baud rate. The Print-On-Line mode is selectable from the keyboard or from a remote data source, initiated by an escape sequence code. The Print mode provides the capability of receiving data from the remote data source at a baud rate different from that of the printer. In this mode, the CRT terminal buffers between the printer and the remote data source. The Print mode is selectable from the keyboard or from a remote data source, initiated by an escape sequence code.

#### 1.3.10 Input/Output Port

The I/O port operates at RS232C logic levels and outputs and receives negative-true data. The I/O port outputs data to and inputs data from the remote data source when the terminal is in the on-line condition.

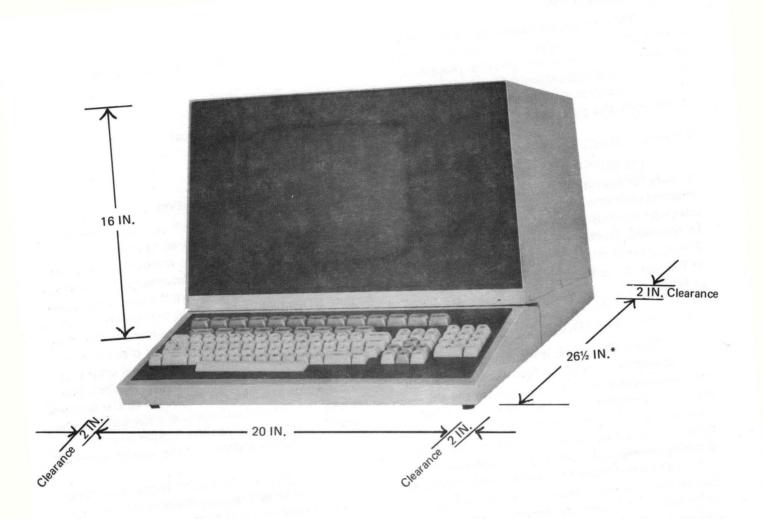

#### 1.3.11 I/O Processor Board Strapping

There are eight strappable options available on the SUPER BEE I/O Processor board. These options are implemented by installing the appropriate jumper on the 16-pin strapping pad (S1). A brief summary of these strapping selections is provided in the following paragraphs.

#### Send Control Codes

All escape codes entered by the keyboard will be performed and transmitted. With the control codes strap installed, all escape sequences are performed locally only, but not transmitted.

#### Go-Off-Line

At the end of a block transmit, an ETX is transmitted and the on-line mode is maintained. With a go-off-line strap installed, the unit goes off-line at the end of transmission and no ETX is transmitted.

#### **Store Special Functions**

Without this strap installed, special function codes are transmitted. With this strap installed, special functions are stored only and not transmitted.

#### External Clock

The SUPER BEE uses its own internal clock. However, with this strap installed, it provides for the use of external clocks provided by a modem or other interface.

#### Synchronous or Asynchronous Operation

The SUPER BEE is configured to operate asynchronously. With this strap installed, the terminal operates in the synchronous mode and generates words of eight bits. While operating in the asynchronous mode, the length of the generated word is determined by the multiplier toggle switch position. In the 110 position, an 11-bit word is generated. A 10-bit word is generated in the 150 position.

#### **Block Transmit**

With this strap installed, the SUPER BEE is configured to perform a block transmit. (This strap is installed as shipped from the factory.) Without this strap the SUPER BEE is configured to do a page transmission.

#### Pseudopolling/Immediate Block Transmit

Operation of the ENTER key or any of the eight special-function keys stores an ETX and positions the cursor at the beginning of the text. In the pseudopolling mode, a request for service code (DC1 octal 21) is transmitted and the terminal waits to receive a clear-to-transmit code (ETB octal 27) before transmission of the text begins.

#### Parity Test

SUPER BEE checks incoming data for even parity when operating asynchronously and odd parity when operating synchronously. With this strap installed, no parity check is made. Transmitted data is in the same sense as received data, with the exception that data is transmitted with a mark parity bit with strap installed. A parity error symbol (reverse video, backward question mark) is displayed whenever an invalid character is sensed by the parity test.

#### **1.4 ACCESSORIES**

The following accessories are available for use with the SUPER BEE Computer Terminal:

- a. Current loop adapter, part number 112-0606, (requires terminal to include interconnect Board, part number 112-0609, and Interface assy. part number 112-0605).

- b. Acoustic soupler cable, part number 112-0031.

- c. Nova computer serial I/O cable, part number 112-0040.

- d. Hewlett-Packard 2000-Series serial I/O cable, part number 112-0048

- e. Printer cable, part number 112-0106.

#### 1.5 SPECIFICATIONS

Specifications of the SUPER BEE Computer Terminal are given in Table 1-1.

-

| CHARACTERISTIC                       | DESCRIPTION                                                                                                                                                                              |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power Requirements                   | 115/230 Vac (± 10 percent), 50/60 Hz, single phase, 180W maximum,<br>225 VA maximum.                                                                                                     |  |

| Display Size<br>Standard<br>Optional | 12 inches (305 mm) rectangular.<br>15 inches (381 mm) rectangular.                                                                                                                       |  |

| Active Display Size<br>Standard      | $6-\frac{1}{2}$ inches x 7- $\frac{1}{2}$ inches (165 mm x 190 mm) approx.                                                                                                               |  |

| Optional                             | 8 inches x 10 inches (203 m/m x 254 mm) approx.                                                                                                                                          |  |

| Display Format                       | 25 lines of 80 characters.                                                                                                                                                               |  |

| Character Type<br>Standard           | 5 x 7 dot matrix (7 x 10 scan), approximately 0.08 x 0.20 inches.                                                                                                                        |  |

| Character Set                        | 224 displayable as follows:<br>32 control characters<br>64 upper case ASCII set<br>32 lower case ASCII set (with descenders shifted down two scans)<br>96 escape sequence control codes. |  |

| Page Overflow                        | Upward scroll - No loss of data until memory overflow.                                                                                                                                   |  |

| Memory Overflow                      | Wrap around and first line of data is lost from memory.                                                                                                                                  |  |

| Communications<br>Interface          | Per EIA Standard RS232C.                                                                                                                                                                 |  |

#### Table 1-1. SUPER BEE Computer Terminal Specifications

### Table 1-1. SUPER BEE Computer Terminal Specifications (Continued)

| CHARACTERISTIC                                      | DESCRIPTION                                                                                                                      |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Printer Interface                                   | Per EIA Standard RS232C.                                                                                                         |

| Video Port                                          | Composite video for remote monitor.                                                                                              |

| Signal Characteristics<br>Transmit<br>Mark<br>Space | –15 volts<br>+10 volts                                                                                                           |

| Receive<br>Mark<br>Space                            | -3 to -25 volts<br>+3 to +25 volts                                                                                               |

| Transmission Rates<br>11 bit<br>10 bit              | 110, 220, 440, 880, 1760, 3520, and 7040<br>150, 300, 600, 1200, 2400, 4800 and 9600                                             |

| Transmission Code                                   | 8-bit USASCII.                                                                                                                   |

| Baud Rate Selection                                 | Switch selectable.                                                                                                               |

| Parity                                              | Asynchronous-even/none (Parity Bit= Mark)<br>Synchronous-odd/none (Parity Bit = Mark)                                            |

| Refresh Rate                                        | 60 Hz (50 Hz optional)                                                                                                           |

| Display Memory                                      | MOS shift registers                                                                                                              |

| Memory Organization                                 | Efficient Paging                                                                                                                 |

| I/O Controller                                      | Microprocessor                                                                                                                   |

| Program Memory                                      | MOS ROM                                                                                                                          |

| Video                                               | Standard, Blinking, Reversed and Blinking Reversed                                                                               |

| Character Generation                                | MOS ROM                                                                                                                          |

| Erase Functions                                     | Clear Memory<br>Erase to end of line (end of field in format mode)<br>Erase to end of memory (unprotected fields in format mode) |

|                                                     |                                                                                                                                  |

#### Table 1-1 SUPER BEE Computer Terminal Specifications (Continued)

| CHARACTERISTIC     | DESCRIPTION                                                                                                                                                                                    |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Edit               | Page Mode or Line Mode<br>Insert Line<br>Delete Line<br>Insert Character<br>Delete Character                                                                                                   |

| Operation Modes    | Character<br>Format<br>On-Line<br>Program Entry<br>Print-On-Line<br>Page/Line Edit<br>Insert Character                                                                                         |

| Format             | Enable field protection                                                                                                                                                                        |

| Transmission Modes | Half Duplex or Full Duplex<br>11 Bits Asynchronous<br>10 Bits Asynchronous<br>8 Bits Synchronous<br>Block/Page<br>Data Compression (Format and Non-Format modes)                               |

| Printer Mode       | ON LINE/OFF LINE                                                                                                                                                                               |

| Strapping Options  | Printer Baud Rate<br>Auto Efficient Paging<br>Internal Clock Multiplier<br>Internal/External Clock<br>Parity<br>Pseudopolling<br>Go-Off-Line<br>Block/Page Transmit<br>Store Special Functions |

| Bell               | Audible alarm when Control G is received, and on the 72nd character of a line when keyboard data is being entered.                                                                             |

| Cursor Type        | Non-destructive blinking underscore.                                                                                                                                                           |

| CHARACTERISTIC                               | DESCRIPTION                                                                                                                                                                       |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cursor Controls                              | Horizontal tab (forward and back)<br>Cursor up<br>Cursor down<br>Cursor left<br>Cursor right<br>Home<br>Carriage return<br>Line feed<br>New line<br>Format tab (forward and back) |

| Cursor Address                               | Positions cursor to the character number and line number specified.                                                                                                               |

| Cursor Sense                                 | Cursor location transmitted upon request.                                                                                                                                         |

| Space Overwrite<br>(SPOW)                    | Space bar functions as cursor-right key which inhibits Space Code generation (Non-destructive).                                                                                   |

| Operator Controls<br>Keyboard/<br>Rear Panel | Brightness Control (thumb wheel)<br>FDX/HDX Switch (full-/half-duplex)<br>Lower Case Character inhibit switch<br>I/O Baud Rate Switch<br>Contrast Control<br>Power Switch         |

| Function Keys                                | PRINT<br>ENTER<br>ERM<br>EOL<br>PREV PAGE<br>NEXT PAGE<br>SCROLL UP                                                                                                               |

|                                              | SCROLL DOWN<br>TAB<br>TAB SET<br>TAB CLEAR                                                                                                                                        |

| Special Function Keys                        | 8 special function keys (F1 through F8)                                                                                                                                           |

| CHARACTERISTIC        | DESCRIPTION                                                                         | n ar sea<br>an<br>an |

|-----------------------|-------------------------------------------------------------------------------------|----------------------|

|                       |                                                                                     |                      |

| Dimensions            |                                                                                     |                      |

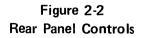

| Width                 | 20 inches (508 mm)                                                                  |                      |

| Height                | 16 inches (406.4 mm)                                                                |                      |

| Depth (w/Keyboard)    | 26-1/2 inches (673 mm)                                                              |                      |

| Depth (less Keyboard) | 17-¼ inches (438 mm)                                                                |                      |

| Depth (Keyboard only) | 12-½ inches (317 mm)                                                                |                      |

| Weight                |                                                                                     |                      |

| Monitor               | 55 pounds (25 kg), approx.                                                          |                      |

| Keyboard              | 10 pounds (4.54 kg), approx.                                                        |                      |

| Operating Temperature | +5- <sup>o</sup> F to 104 <sup>o</sup> F (+10 <sup>o</sup> C to +40 <sup>o</sup> C) |                      |

|                       |                                                                                     |                      |

|                       |                                                                                     |                      |

|                       |                                                                                     |                      |

#### Table 1-1 SUPER BEE Computer Terminal Specifications (Continued)

#### 1.6 IDENTIFICATION

An identification plate located on the bottom cover plate of the terminal provides the terminal model number, serial number, weight, voltage and current requirements, and frequency and power classification.

#### SECTION II OPERATION

#### 2.1 INTRODUCTION

This section provides operating instructions for the SUPER BEE Computer Terminal. The operating instructions include descriptions of the operator controls and indicators, general operating procedures and operating instructions. The general operating procedures provide information for operating personnel. The operation instructions provide information that allows a programmer to vary the operational format to the extent presented herein.

#### 2.2 OPERATOR CONTROLS AND INDICATORS

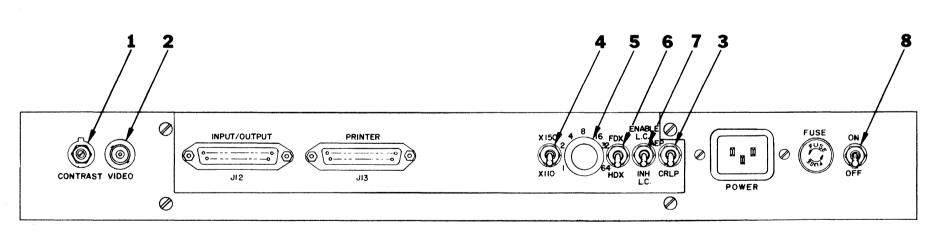

The operator controls and indicator are defined in Tables 2-1 and 2-2 and are depicted in Figures 2-1 and 2-2. Table 2-1 describes the keyboard controls and indicators and Table 2-2 describes the monitor rear panel controls. Figure 2-1 depicts the keyboard and Figure 2-2 depicts the monitor rear panel.

| KEY OR<br>CONTROL | FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | CONTROL AND FUNCTION KEY GROUP                                                                                                                                                                                                                                                                                                                                                                                                                        |

| F1 through F8     | Eight special function keys that generate two-code sequences which are entered in the memory when the terminal is on-line. Functions are undefined unless terminal is appropriately strapped.                                                                                                                                                                                                                                                         |

| FMT (Format)      | Terminal is placed in Format mode. Key includes indicator that lights<br>when the terminal is in Format mode. In this mode, the cursor is<br>moved to first unprotected memory location. When the key is pressed<br>and unlatched, the terminal is placed in Character mode and indicator<br>extinguishes.                                                                                                                                            |

| ON-LINE           | Terminal is placed in the On-Line Character mode, and the key indicator<br>lights. The transmit and receive circuitry, and keyboard are enabled. If<br>synchronous I/O has been selected, the terminal will wait for synchroniza-<br>tion from the computer. The terminal will not go on-line in response to a<br>command from the computer.                                                                                                          |

| PROG ENTRY        | Lights key indicator, resets Format (FMT) mode, sets Program Entry mode<br>to on. When this mode is on, all printing characters as well as control codes<br>and escape sequence codes display their assigned characters. The escape<br>sequence codes are displayed as reverse video and only the New Line and<br>ENTER functions can be performed. When the key is pressed and released,<br>Program Entry mode and the key indicator are turned off. |

| Table 2-1. SUPER BEE Computer Terminal Keyboard, |

|--------------------------------------------------|

| Controls and Indicators                          |

| KEY OR<br>CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CONTROL AND FUNCTION KEY GROUP (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PRINT ON LINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Sets the terminal to Print-On-Line mode and lights the key indicator.<br>All printing characters and control functions that are received or trans-<br>mitted by the terminal are applied to the printer I/O. In this mode, the<br>I/O baud rate can assume the printer's baud rate. This function can be<br>used as a high-low baud rate selection switch when a printer is not slaved<br>to the terminal. When the key is pressed and released, the key indicator<br>is turned off and the Print-On-Line function is reset. The I/O baud rate<br>is restored to the I/O switch setting.                                                                                                                                                                                                                   |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Resets the terminal mode of operation to Character off-line mode. The cursor is moved to the home position. The following functions or modes are reset to the off condition: FMT, ON-LINE, PROG ENTRY, PRINT-ON-LINE, PAGE EDIT, INS CHAR, page blink, and SPOW. The keyboard is enabled and the protect latch is set. (Note: The RESET function does not erase the display screen.)                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ENTER<br>Normalistic de la companya de | When the terminal is in Character mode, an ETX is written at the present cursor location, then the cursor returns to home or to the first character on the next line below the preceding ETX (strap option). The terminal is placed on-line and starts transmitting data from the cursor position to the next ETX. When the ETX is read and transmitted, the transmission stops and the cursor is located in the next character location following the ETX. If the unit is strapped for pseudopolling sequence, an ETX is written at the present cursor location and the terminal is placed on-line. However, before transmission starts, the terminal transmits a DCI (Control Q code) on the I/O and enables the data receiver to accept an ETB (Control W) from the I/O before initiating transmission. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | When the terminal is in the Format mode, the same sequence occurs as<br>that which occurs in the Character mode, except that only data in the un-<br>protected fields are transmitted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |