# User's Manual

# Engineering Capture System

# CAD/CAM Group, Inc.

Fourth Edition February 1992 COPYRIGHT © 1992 CAD/CAM Group, Incorporated. All rights reserved. No part of this document may be transmitted, reproduced, transcribed, stored in a retrieval system, or translated into any other language without the written consent of the CAD/CAM Group, Incorporated.

The information in this manual is subject to change without notice.

The CAD/CAM Group assumes no responsibility for any errors that might be contained in this document. The CAD/CAM Group reserves the right to revise this document or make changes to the specifications of the product described by this document without any obligation to notify any person of such revision or change.

The software described in this manual is furnished under a license agreement between you and the CAD/CAM Group, Incorporated. The license agreement authorizes the number of copies that may be made and the computer systems on which they may be used. Any unauthorized duplication or use of the Engineering Capture System in whole or in part is forbidden.

Microsoft Windows is a trademark of Microsoft Corporation.

MS\_DOS is a registered trademark of Microsoft Corporation.

PageMaker is a registered trademark of the Aldus Corporation.

IBM is a registered trademark of International Business Machines Corporation.

Sun Workstation, SPARC Station, SunOS, Sunview, Sun3, Sun4, and Sun Microsystems are trademarks of Sun Microsystems, Inc.

UNIX is a registered trademark of AT&T.

Apple, Apple LaserWriter II, Macintosh, MacPlus, Mac SE or Mac II and MacOS are registered trademarks of Apple Computer, Inc.

PostScript is a trademark of Adobe Systems Inc.

Hewlett-Packard Graphics Language, HPGL, and HP Laser Jet are registered trademarks of Hewlett-Packard Company.

CAD/CAM Group, Incorporated

ii Table of Contents February 1992

# **Table of Contents**

| Table of Contentsii                           | i   |

|-----------------------------------------------|-----|

| Prefacex                                      | iii |

| Using This Manualx                            | V   |

|                                               |     |

| Section I Before You Begin                    |     |

| ECS Conventions                               | -2  |

| ECS on Sun Workstations                       |     |

| Hardware Configuration I-                     | -3  |

| Software ConfigurationI-                      |     |

| Installing the ECSI-                          | -3  |

| Starting ECSI-                                | -4  |

| Using SunviewI-                               | -5  |

| What is a Window? I-                          | -5  |

| Using the MouseI-                             | -6  |

| SelectingI-                                   | -7  |

| Selecting the Active Window                   |     |

| Using Menus I-                                |     |

| Walk-Through MenusI-                          |     |

| Pull-Down MenusI-                             |     |

| Dialog BoxesI-                                |     |

| Using Scroll BarsI-                           |     |

| Arranging Windows I-                          |     |

| Making a Window into an Icon I-               |     |

| Quit an Application                           |     |

| The ECS Adaptation of Sunview                 |     |

| Mouse Buttons                                 |     |

| Selection                                     |     |

| Cut versus Delete                             |     |

| Copy/Paste versus Duplicate                   |     |

| Cut/Paste vs. Move                            |     |

| Undo and Redo                                 |     |

| Prompting and Error Messages                  |     |

| ECS on IBM PC Compatible Systems              |     |

| Hardware Configuration                        |     |

| Software Configuration                        |     |

|                                               |     |

| Installing the Engineering Capture System     |     |

| Starting ECS I-<br>Using Microsoft Windows I- |     |

| What is a Window?                             |     |

| Using the Mouse                               |     |

| Using the Mouse1-                             | .10 |

|                                                                                                                                                                                                                                                                                                                                                                                              | .I-17                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Selecting the Active Window                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             |

| Using Menus                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             |

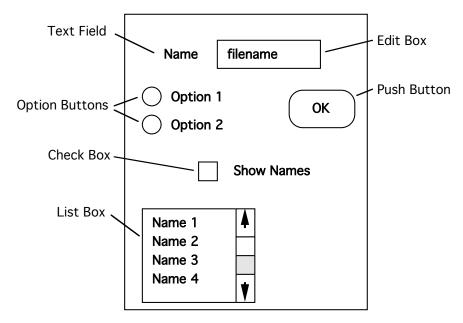

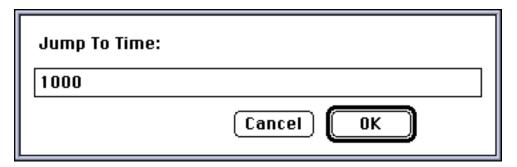

| Dialog Boxes                                                                                                                                                                                                                                                                                                                                                                                 | I-17                                                                                        |

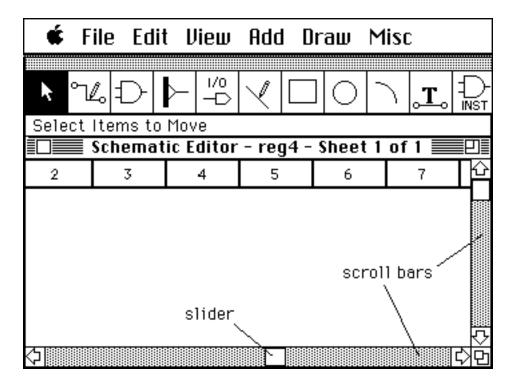

| Using Scroll Bars                                                                                                                                                                                                                                                                                                                                                                            | I-19                                                                                        |

| Arranging Windows                                                                                                                                                                                                                                                                                                                                                                            |                                                                                             |

| Enlarging a Window                                                                                                                                                                                                                                                                                                                                                                           | I-19                                                                                        |

| Making a Window into an Icon                                                                                                                                                                                                                                                                                                                                                                 |                                                                                             |

| Quit an Application                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             |

| Exiting Windows                                                                                                                                                                                                                                                                                                                                                                              | I-20                                                                                        |

| The WIN.INI Initialization File                                                                                                                                                                                                                                                                                                                                                              | I-20                                                                                        |

| The ECS Adaptation of Windows                                                                                                                                                                                                                                                                                                                                                                | I-21                                                                                        |

| Mouse Buttons                                                                                                                                                                                                                                                                                                                                                                                | I-21                                                                                        |

| Selection                                                                                                                                                                                                                                                                                                                                                                                    | I-21                                                                                        |

| Cut versus Delete                                                                                                                                                                                                                                                                                                                                                                            | I-22                                                                                        |

| Copy/Paste versus Duplicate                                                                                                                                                                                                                                                                                                                                                                  | I-22                                                                                        |

| Cut/Paste versus Move                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |

| Undo and Redo                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |

| Prompting and Error Messages                                                                                                                                                                                                                                                                                                                                                                 | I-23                                                                                        |

| Libraries and Directory Structures                                                                                                                                                                                                                                                                                                                                                           | .II-2                                                                                       |

| Program Directories                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             |

| User Directories                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |

| Library Directories                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             |

| Project Directories                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             |

| Model Directories                                                                                                                                                                                                                                                                                                                                                                            | 11 /1                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                              | .II-4                                                                                       |

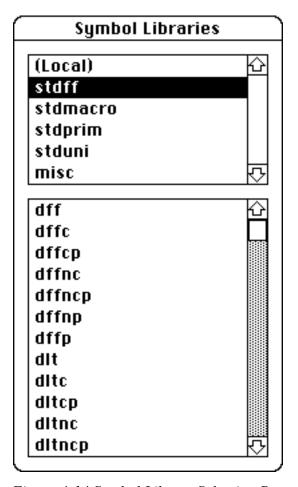

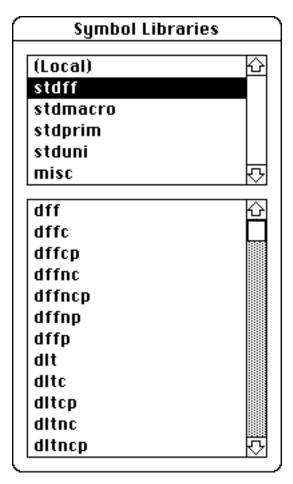

| Symbol Libraries                                                                                                                                                                                                                                                                                                                                                                             | II-4<br>II-4                                                                                |

| Symbol LibrariesLibrary Searching                                                                                                                                                                                                                                                                                                                                                            | .II-4<br>.II-4<br>.II-6                                                                     |

| Symbol Libraries  Library Searching  Memory Limitations                                                                                                                                                                                                                                                                                                                                      | .II-4<br>.II-4<br>.II-6<br>.II-7                                                            |

| Symbol Libraries                                                                                                                                                                                                                                                                                                                                                                             | .II-4<br>.II-4<br>.II-6<br>.II-7                                                            |

| Symbol Libraries  Library Searching  Memory Limitations  Memory Size Limit on IBM compatible PC  Segmentation Limit on IBM Compatible PC                                                                                                                                                                                                                                                     | .II-4<br>.II-4<br>.II-6<br>.II-7<br>.II-7                                                   |

| Symbol Libraries  Library Searching  Memory Limitations  Memory Size Limit on IBM compatible PC  Segmentation Limit on IBM Compatible PC  Subdividing a Schematic                                                                                                                                                                                                                            | .II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-7                                                   |

| Symbol Libraries  Library Searching  Memory Limitations  Memory Size Limit on IBM compatible PC  Segmentation Limit on IBM Compatible PC  Subdividing a Schematic  Subdividing the Hierarchy                                                                                                                                                                                                 | .II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-7                                                   |

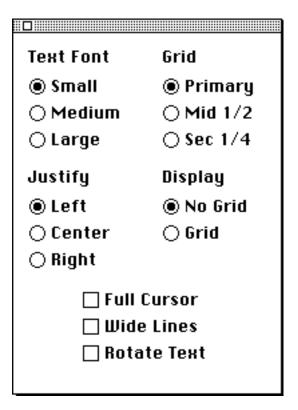

| Symbol Libraries  Library Searching  Memory Limitations  Memory Size Limit on IBM compatible PC  Segmentation Limit on IBM Compatible PC  Subdividing a Schematic  Subdividing the Hierarchy  Graphic Control                                                                                                                                                                                | .II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-7<br>.II-8                                          |

| Symbol Libraries Library Searching  Memory Limitations  Memory Size Limit on IBM compatible PC  Segmentation Limit on IBM Compatible PC  Subdividing a Schematic  Subdividing the Hierarchy  Graphic Control  Setup of ecs.ini                                                                                                                                                               | .II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-7<br>.II-8<br>.II-9                                 |

| Symbol Libraries Library Searching  Memory Limitations  Memory Size Limit on IBM compatible PC Segmentation Limit on IBM Compatible PC Subdividing a Schematic Subdividing the Hierarchy  Graphic Control  Setup of ecs.ini Location of the ecs.ini File on Sun Workstation                                                                                                                  | .II-4<br>.II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-8<br>.II-9<br>.II-10                       |

| Symbol Libraries Library Searching  Memory Limitations Memory Size Limit on IBM compatible PC Segmentation Limit on IBM Compatible PC Subdividing a Schematic Subdividing the Hierarchy  Graphic Control Setup of ecs.ini Location of the ecs.ini File on Sun Workstation Multiple ecs.ini Files                                                                                             | .II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-7<br>.II-8<br>.II-9<br>.II-10                       |

| Symbol Libraries Library Searching  Memory Limitations  Memory Size Limit on IBM compatible PC Segmentation Limit on IBM Compatible PC Subdividing a Schematic Subdividing the Hierarchy  Graphic Control  Setup of ecs.ini  Location of the ecs.ini File on Sun Workstation Multiple ecs.ini Files  Editing the Master ecs.ini File                                                         | .II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-8<br>.II-10<br>.II-11<br>.II-11                     |

| Symbol Libraries Library Searching  Memory Limitations  Memory Size Limit on IBM compatible PC Segmentation Limit on IBM Compatible PC Subdividing a Schematic Subdividing the Hierarchy  Graphic Control  Setup of ecs.ini Location of the ecs.ini File on Sun Workstation Multiple ecs.ini Files Editing the Master ecs.ini File  The ecs.ini Editor.                                      | .II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-8<br>.II-9<br>.II-11<br>.II-11                      |

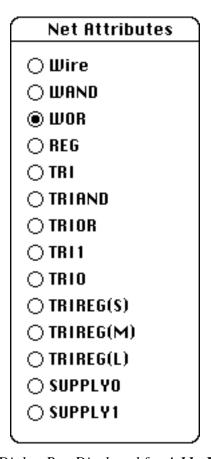

| Symbol Libraries Library Searching  Memory Limitations Memory Size Limit on IBM compatible PC Segmentation Limit on IBM Compatible PC Subdividing a Schematic Subdividing the Hierarchy  Graphic Control Setup of ecs.ini Location of the ecs.ini File on Sun Workstation Multiple ecs.ini Files Editing the Master ecs.ini File The ecs.ini Editor. Attributes->Net, Pin, Symbol Attributes | .II-4<br>.II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-8<br>.II-10<br>.II-11<br>.II-11<br>.II-11  |

| Symbol Libraries Library Searching  Memory Limitations  Memory Size Limit on IBM compatible PC Segmentation Limit on IBM Compatible PC Subdividing a Schematic Subdividing the Hierarchy  Graphic Control  Setup of ecs.ini Location of the ecs.ini File on Sun Workstation Multiple ecs.ini Files Editing the Master ecs.ini File  The ecs.ini Editor.                                      | .II-4<br>.II-6<br>.II-7<br>.II-7<br>.II-8<br>.II-18<br>.II-11<br>.II-11<br>.II-13<br>.II-14 |

Fehruary 1992

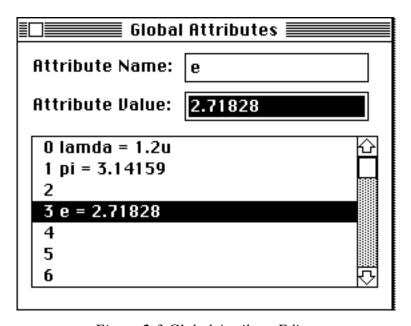

| Example Attributes         | II-17 |

|----------------------------|-------|

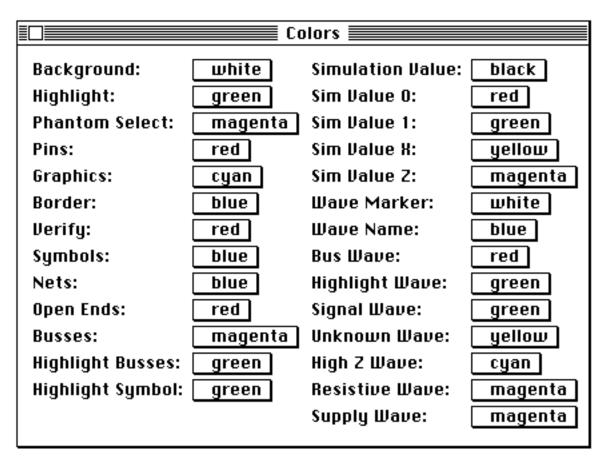

| Controls->Color Assignment | II-19 |

| Controls->Color Palette    | II-20 |

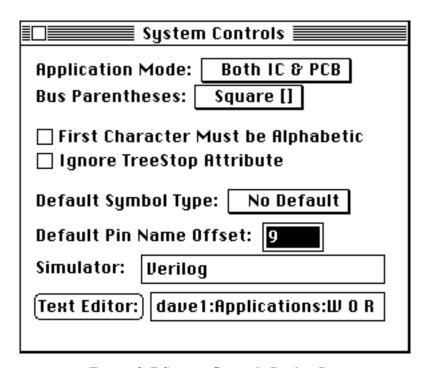

| Controls->ECS Controls     | II-21 |

| ApplicationMode            | II-21 |

| ClipboardFormat            |       |

| DontClipPrinter            |       |

| EditSuffix                 |       |

| FirstCharAlpha             |       |

| HierarchyChar              |       |

| IgnoreTreeStop             |       |

| MarkOpenEnds               |       |

| NameBarChar                |       |

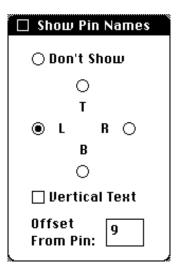

| PinNameOffset              |       |

| PlotScale                  |       |

| PrintFormat                |       |

| PrintScale                 |       |

| PullDownMenus              |       |

| RetainedParentheses        |       |

| RotateNetNames             |       |

| RotatePinNumbers           |       |

| ShowBorder                 |       |

| ShowCrossPageConnects      |       |

| ShowNetNos                 |       |

| ShowPinDots                |       |

| ShowPinNumbers             |       |

| ShowSimVals                |       |

| ShowSolderDots             |       |

| ShowSymbolAttributes       |       |

| ShowSymbolText             |       |

| SnapToPins                 |       |

| Symbol Type                |       |

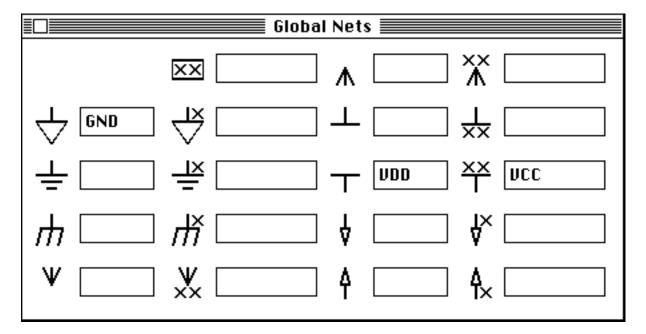

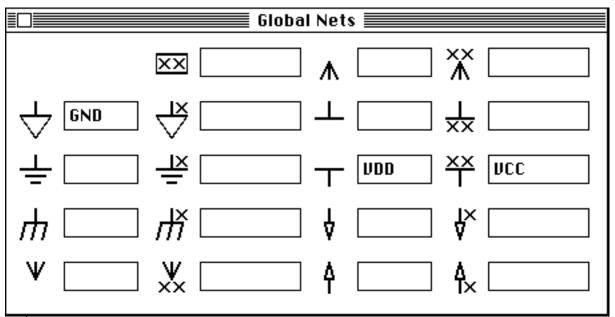

| Controls->Global Signals   |       |

| Controls->Processes.       |       |

| Controls->PS Printer       |       |

| Orientation                |       |

| TypeFace                   |       |

| Setup Line                 |       |

| PrinterName                |       |

| PaperWidth                 |       |

| PaperHeight                |       |

| SideMargin                 |       |

| TopMargin                  |       |

| Controls->Sheet Layout     |       |

| Horizontal Zones           |       |

| Direction                  |       |

| Vertical Zones                            | II-30  |

|-------------------------------------------|--------|

| Direction                                 | II-31  |

| Master Symbols                            | II-31  |

| Numbers on                                | II-31  |

| Units                                     | II-31  |

| Grid Size                                 | II-31  |

| Smallest Text                             | II-31  |

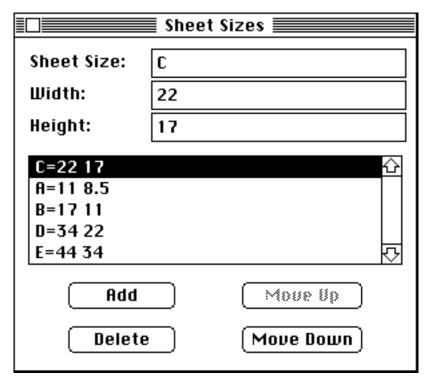

| Controls->Sheet Sizes                     | II-31  |

| Controls->Simulator Environment           | II-32  |

| Controls->Tools                           | II-32  |

| Controls->Waves Controls                  | II-33  |

| File->Exit                                | II-33  |

| File->Save                                | II-33  |

| Search Paths                              | II-33  |

|                                           |        |

|                                           |        |

| Section III Getting Started               |        |

| Section III Getting Started               |        |

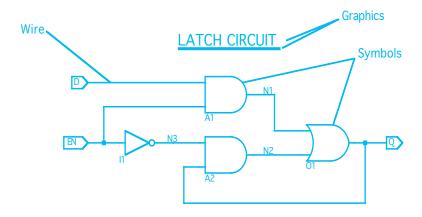

| Concept of Design Entry with ECS          | III-2  |

| Schematics                                |        |

| Symbols                                   |        |

| Graphic Entities                          |        |

| Pins                                      |        |

| Attributes                                |        |

|                                           |        |

| Iterated Instances (Arrays)               |        |

| Wires                                     |        |

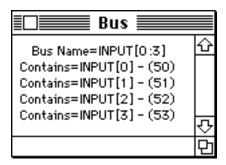

| Busing Features                           |        |

| Simple Buses                              |        |

| Ordered Buses                             |        |

| Bus Pins                                  |        |

| Attributes                                |        |

| Graphics                                  |        |

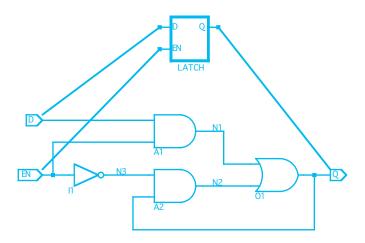

| Hierarchy                                 |        |

| Symbols, Schematics, and Hierarchy in ECS |        |

| Hierarchical Design Structure             | III-9  |

| Hierarchical Naming                       | III-9  |

| Nets in the Hierarchy                     | III-10 |

| Design Debugging and Verification Tools   | III-10 |

| Automatic Aliasing                        | III-11 |

| After Design Entry is Complete            |        |

| A Brief Tour                              |        |

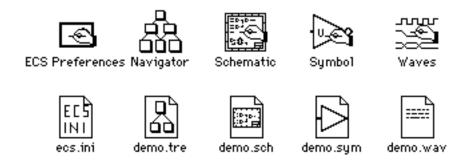

| Starting the System                       |        |

| Conventions Used in This Tutorial         |        |

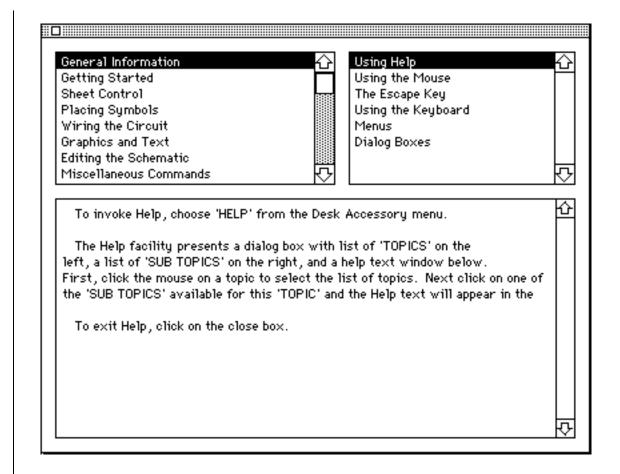

| On-Line Help                              |        |

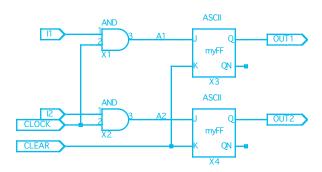

| Designing a Circuit                       |        |

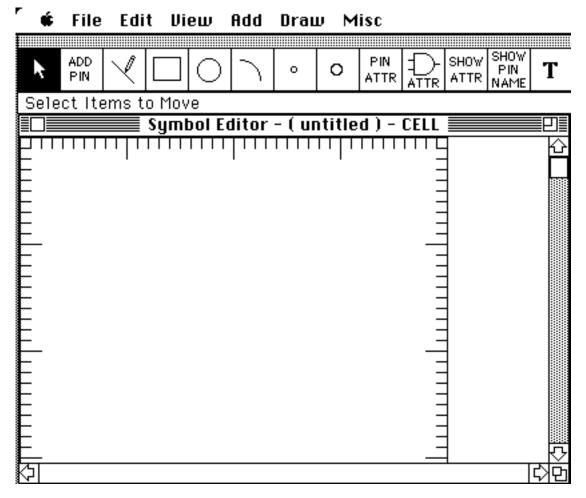

| Creating Symbols                          |        |

| - 0 - 1                                   |        |

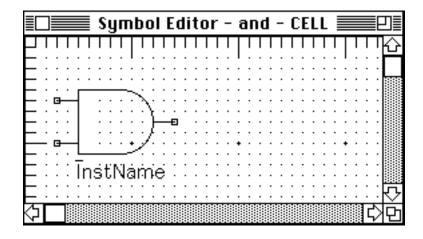

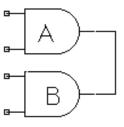

| Drawing the AND Gate  Creating the Latch Symbol                                                                                                                                                                                                                                                                                                                 |                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

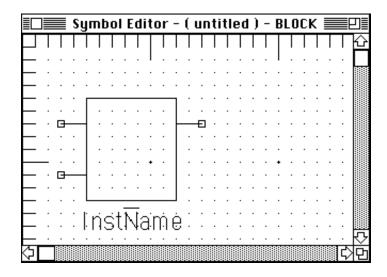

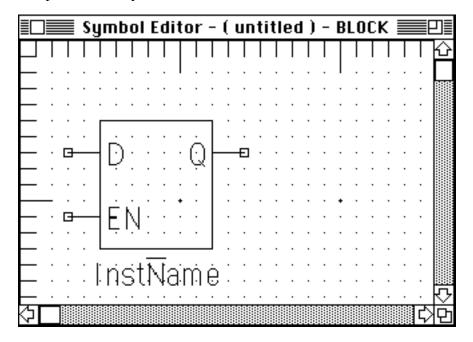

| Creating the Latch Symbol                                                                                                                                                                                                                                                                                                                                       |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

| Drawing the Symbol                                                                                                                                                                                                                                                                                                                                              | III-20                                               |

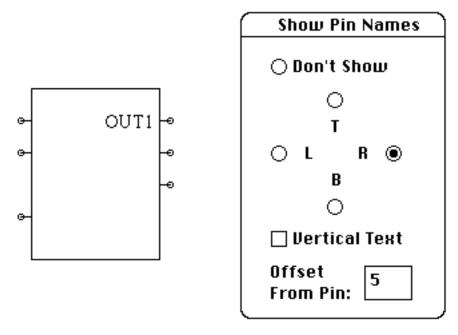

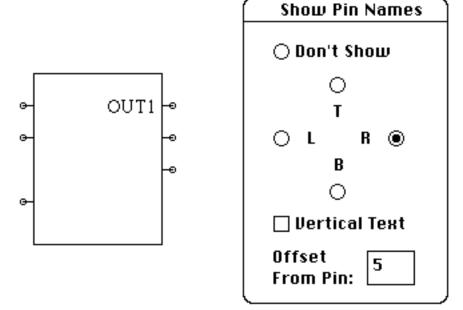

| Displaying Pin Names on Schematic                                                                                                                                                                                                                                                                                                                               | III-21                                               |

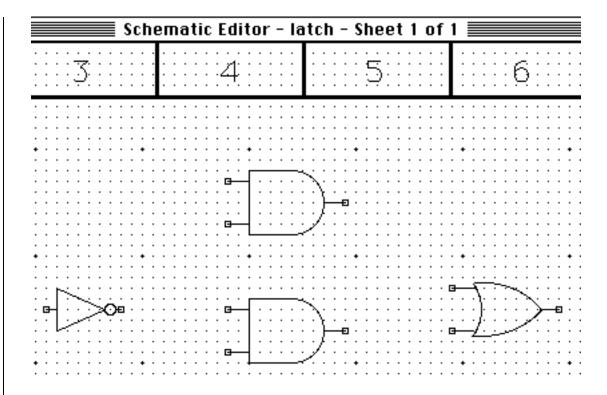

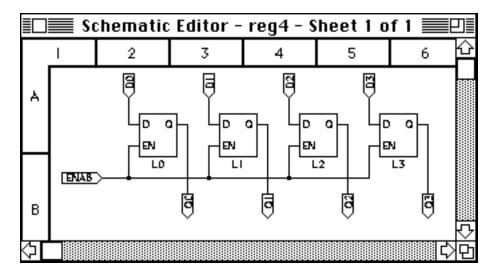

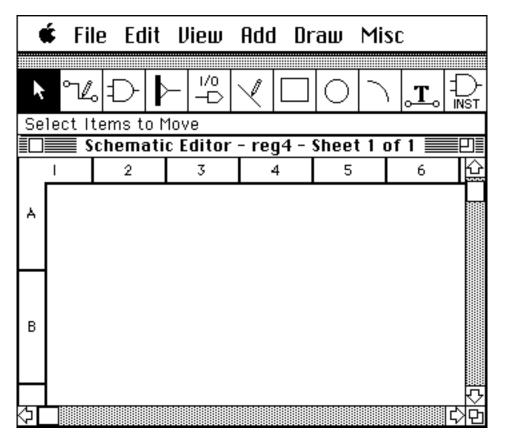

| Creating Schematics                                                                                                                                                                                                                                                                                                                                             | III-22                                               |

| Placing Symbols                                                                                                                                                                                                                                                                                                                                                 | III-22                                               |

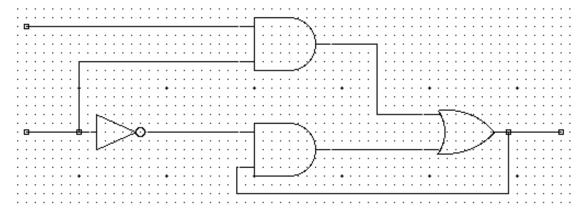

| Editing the Schematic                                                                                                                                                                                                                                                                                                                                           | III-23                                               |

| Wiring the Schematic                                                                                                                                                                                                                                                                                                                                            |                                                      |

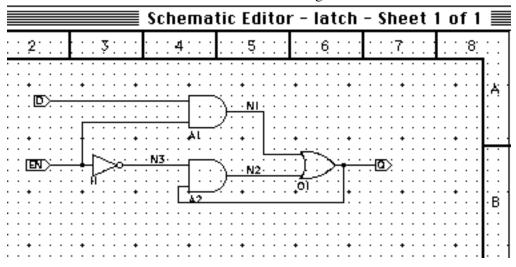

| Naming Symbol Instances                                                                                                                                                                                                                                                                                                                                         |                                                      |

| Naming Nets                                                                                                                                                                                                                                                                                                                                                     |                                                      |

| Saving the Schematic                                                                                                                                                                                                                                                                                                                                            |                                                      |

| Check for Errors.                                                                                                                                                                                                                                                                                                                                               |                                                      |

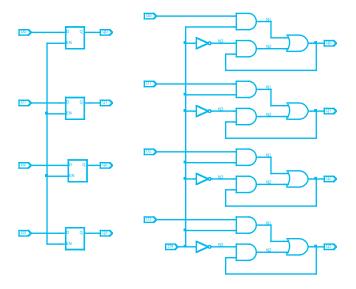

| Creating the Reg4 Schematic                                                                                                                                                                                                                                                                                                                                     |                                                      |

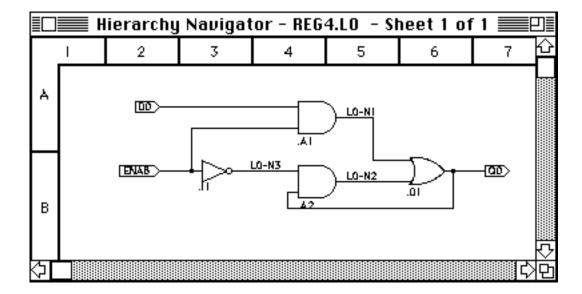

| Navigating the Hierarchy                                                                                                                                                                                                                                                                                                                                        |                                                      |

| Error Checking                                                                                                                                                                                                                                                                                                                                                  |                                                      |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                        |                                                      |

| Correct by Construction                                                                                                                                                                                                                                                                                                                                         |                                                      |

| Symbol and Schematic Checking                                                                                                                                                                                                                                                                                                                                   |                                                      |

| Engineering Analysis Tools                                                                                                                                                                                                                                                                                                                                      |                                                      |

| Simulation                                                                                                                                                                                                                                                                                                                                                      |                                                      |

| Creating a Netlist                                                                                                                                                                                                                                                                                                                                              |                                                      |

| Printing                                                                                                                                                                                                                                                                                                                                                        |                                                      |

| Exiting from the System                                                                                                                                                                                                                                                                                                                                         |                                                      |

| Summary                                                                                                                                                                                                                                                                                                                                                         | III-33                                               |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

| Section IV Entering Your Design                                                                                                                                                                                                                                                                                                                                 |                                                      |

| Section IV Entering Your Design                                                                                                                                                                                                                                                                                                                                 |                                                      |

| Section IV Entering Your Design The ECS Executive Program                                                                                                                                                                                                                                                                                                       | IV-2                                                 |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

| The ECS Executive Program                                                                                                                                                                                                                                                                                                                                       | IV-2                                                 |

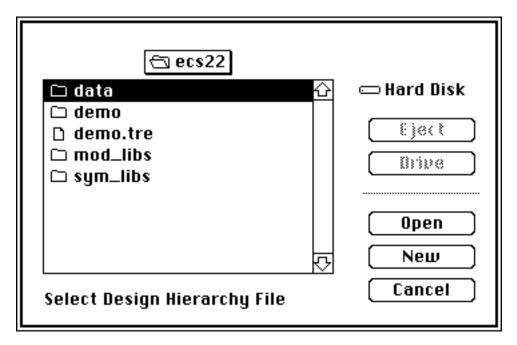

| The ECS Executive Program  Dialog Box Interface.                                                                                                                                                                                                                                                                                                                | IV-2                                                 |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program                                                                                                                                                                                                                                                                                            | IV-2<br>IV-3<br>IV-3                                 |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files.  Naming Design Files                                                                                                                                                                                                                                              | IV-2<br>IV-3<br>IV-3                                 |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program                                                                                                                                                                                                                            | IV-2<br>IV-3<br>IV-4<br>IV-4                         |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus                                                                                                                                                                                      | IV-2<br>IV-3<br>IV-4<br>IV-4                         |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus.  The ECS Symbol Editor                                                                                                                                                              | IV-2IV-3IV-4IV-4IV-5                                 |

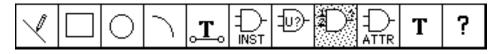

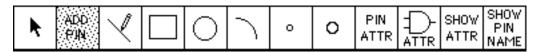

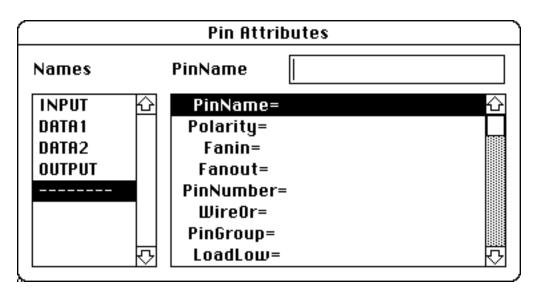

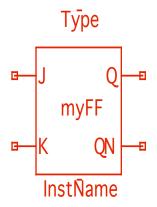

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus.  The ECS Symbol Editor  Symbol Components                                                                                                                                           | IV-2IV-3IV-4IV-4IV-5IV-7                             |

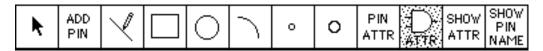

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus.  The ECS Symbol Editor  Symbol Components  Graphic Entities                                                                                                                         | IV-2IV-3IV-4IV-5IV-7                                 |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus.  The ECS Symbol Editor  Symbol Components  Graphic Entities  Pins                                                                                                                   | IV-2IV-3IV-4IV-4IV-5IV-7IV-7                         |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus  The ECS Symbol Editor  Symbol Components  Graphic Entities  Pins  Attributes                                                                                                        | IV-2IV-3IV-4IV-4IV-5IV-7IV-7                         |

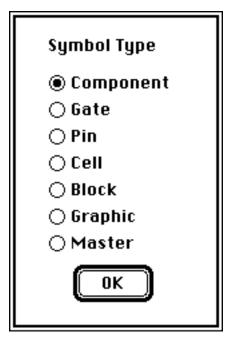

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus.  The ECS Symbol Editor  Symbol Components  Graphic Entities  Pins  Attributes  Symbol Types                                                                                         | IV-2IV-3IV-4IV-4IV-5IV-7IV-7IV-7IV-8                 |

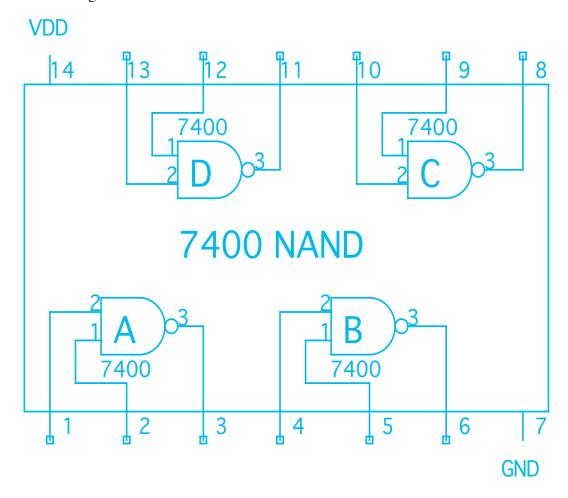

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus  The ECS Symbol Editor  Symbol Components  Graphic Entities  Pins  Attributes  Symbol Types  Component and Gate Symbols                                                              | IV-2IV-3IV-4IV-4IV-7IV-7IV-7IV-7IV-8IV-8             |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus.  The ECS Symbol Editor  Symbol Components  Graphic Entities  Pins  Attributes  Symbol Types  Component and Gate Symbols  Cell Symbols                                               | IV-2IV-3IV-4IV-4IV-5IV-7IV-7IV-7IV-8IV-8             |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus  The ECS Symbol Editor  Symbol Components  Graphic Entities  Pins  Attributes  Symbol Types  Component and Gate Symbols  Cell Symbols  Block Symbols                                 | IV-2IV-3IV-4IV-4IV-5IV-7IV-7IV-7IV-8IV-8IV-8         |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus  The ECS Symbol Editor  Symbol Components  Graphic Entities  Pins  Attributes  Symbol Types  Component and Gate Symbols  Cell Symbols  Block Symbols  Pin Symbols                    | IV-2IV-3IV-4IV-4IV-5IV-7IV-7IV-7IV-8IV-8IV-8IV-9     |

| The ECS Executive Program Dialog Box Interface Selecting a Program Selecting Design Files Naming Design Files Running a Program Utility, Print, View and Setup Menus The ECS Symbol Editor Symbol Components Graphic Entities. Pins Attributes Symbol Types  Component and Gate Symbols Cell Symbols Block Symbols Pin Symbols. Graphic Symbols Graphic Symbols | IV-2IV-3IV-4IV-4IV-5IV-7IV-7IV-7IV-8IV-8IV-8IV-9IV-9 |

| The ECS Executive Program  Dialog Box Interface  Selecting a Program  Selecting Design Files  Naming Design Files  Running a Program  Utility, Print, View and Setup Menus  The ECS Symbol Editor  Symbol Components  Graphic Entities  Pins  Attributes  Symbol Types  Component and Gate Symbols  Cell Symbols  Block Symbols  Pin Symbols                    | IV-2IV-3IV-4IV-4IV-5IV-7IV-7IV-7IV-8IV-8IV-8IV-9IV-9 |

| Creating S        | ymbols                        | IV-9    |

|-------------------|-------------------------------|---------|

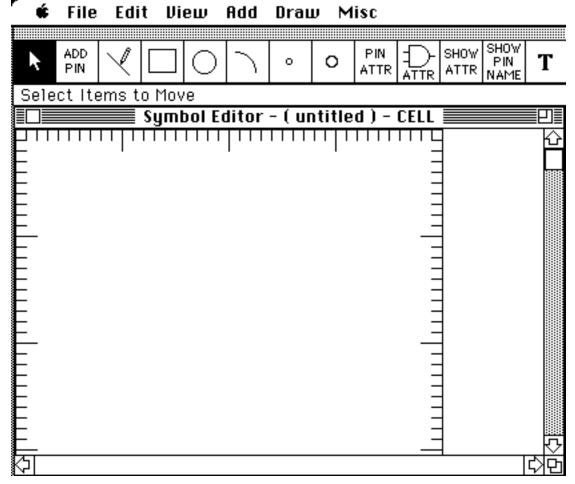

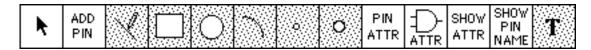

|                   | erting the Symbol Editor      |         |

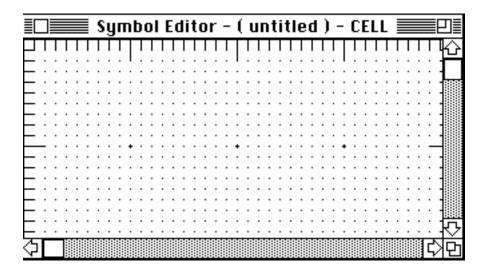

|                   | ids                           |         |

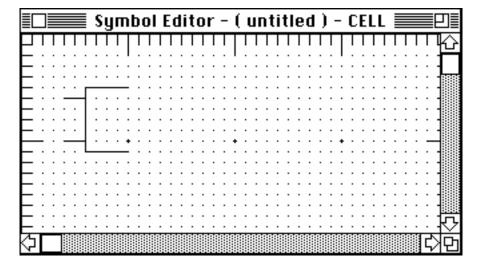

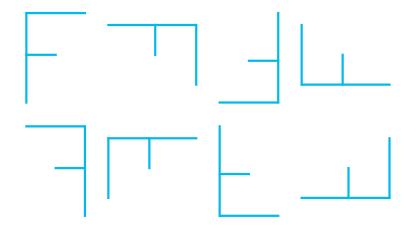

|                   | awing Graphics and Fixed Text |         |

|                   | Rectangles                    |         |

|                   | Circles and Arcs              |         |

|                   | Negation Bubbles              |         |

| Sax               | ving a Symbol                 |         |

|                   | nting the Symbol              |         |

|                   | mbols                         |         |

|                   | lete                          |         |

|                   | DVe                           |         |

|                   |                               |         |

|                   | plicate                       |         |

|                   | ag                            |         |

|                   | py, Cut, and Paste            |         |

|                   | do and Redo                   |         |

| •                 | reparation for Schematics     |         |

|                   | 18                            |         |

|                   | s Pins                        |         |

| Att               | tributes                      |         |

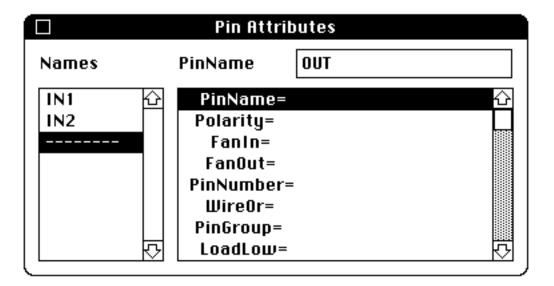

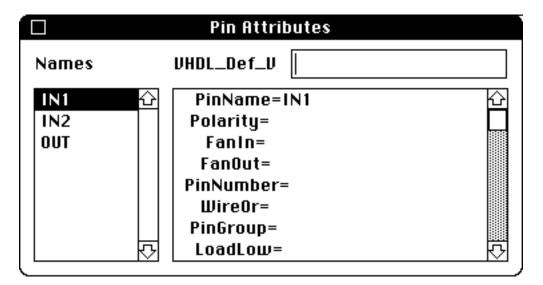

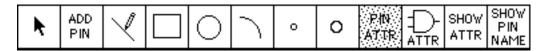

|                   | Pin Attributes                |         |

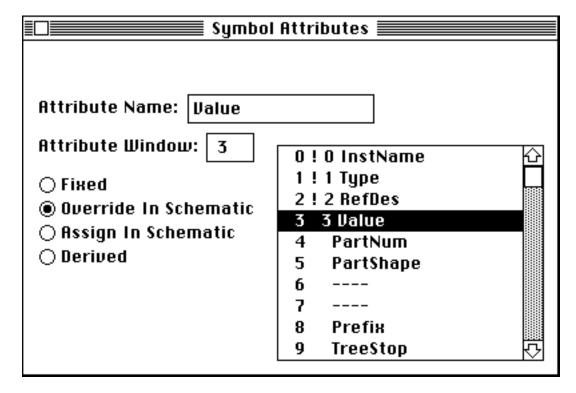

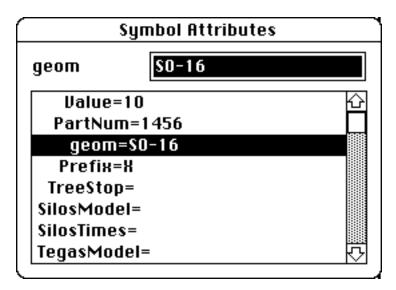

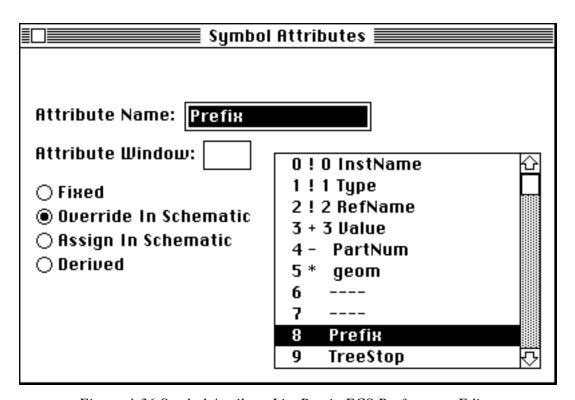

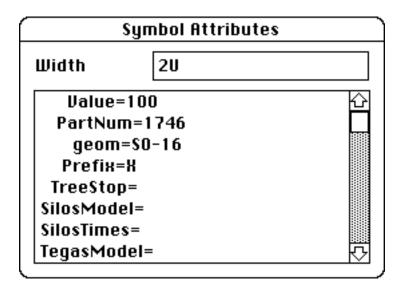

|                   | Symbol Attributes             |         |

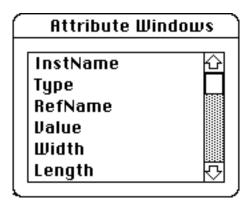

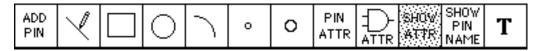

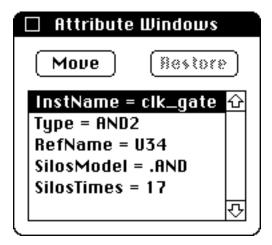

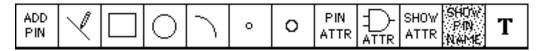

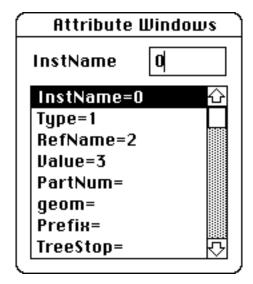

|                   | Attribute Windows             |         |

|                   | t Origin                      |         |

|                   |                               |         |

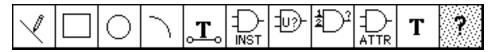

| Schematic Editor. |                               | IV-19   |

| Schematic         | Components                    | IV-19   |

| Syr               | mbols                         | IV-20   |

| Wi                | res                           | IV-20   |

| Att               | tributes                      | IV-20   |

| Gra               | aphics                        | IV-20   |

| Beginning         | the Design                    | IV-20   |

| Sta               | arting the Schematic Editor   | IV-20   |

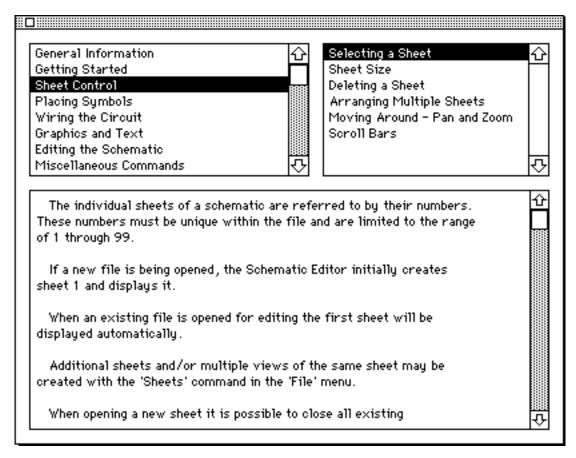

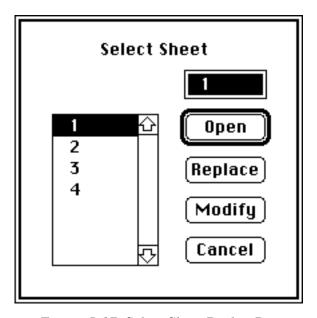

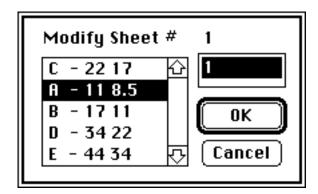

|                   | orking with Sheets            |         |

|                   | ids                           |         |

|                   | ntrolling Display Options     |         |

|                   | Connect Dots                  |         |

|                   | Border                        |         |

|                   | Symbol Pins                   |         |

|                   | Pin Numbers                   |         |

|                   | Symbol Text                   |         |

|                   | Symbol Attributes             |         |

|                   | Open Ends                     |         |

|                   | Cross Page Connects           |         |

| Dec               | awing Graphics                |         |

|                   | omponents                     |         |

| Adding Co         | mponents                      | 1 v -23 |

| Placing Symbols                         | IV-23 |

|-----------------------------------------|-------|

| Adding Instance Names                   |       |

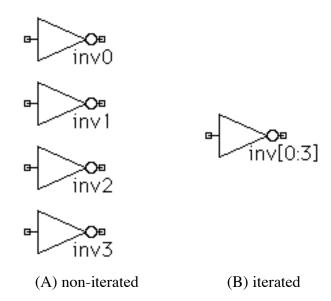

| Iterated Instances                      | IV-24 |

| Attributes                              | IV-25 |

| Editing Pin Attributes                  | IV-25 |

| Symbol Attributes                       | IV-26 |

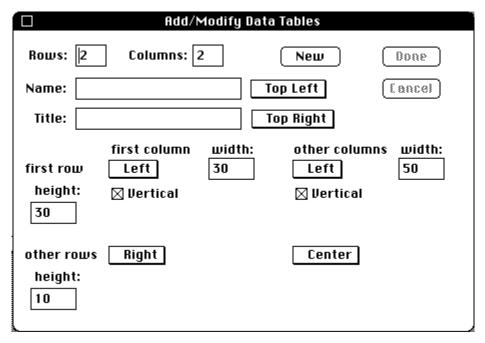

| Attribute Windows                       | IV-26 |

| Wiring the Schematic                    | IV-26 |

| Drawing Wires                           | IV-26 |

| Net Names                               | IV-27 |

| Identification                          | IV-27 |

| Interconnection                         | IV-27 |

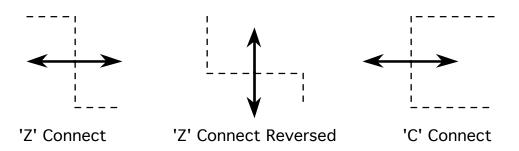

| Bus Entry                               | IV-27 |

| Hierarchy Connections                   | IV-27 |

| Ordered Bus Definition                  | IV-27 |

| Simple and Compound Names               | IV-28 |

| Entering Net Names                      | IV-28 |

| Renaming a Net                          | IV-29 |

| Attaching the Net Name to the Schematic | IV-29 |

| Buses                                   | IV-30 |

| Bus Taps                                | IV-31 |

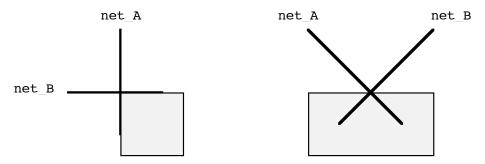

| Implicit Net Connections                | IV-31 |

| Specifying Polarity                     | IV-32 |

| Wiring Constraints                      | IV-32 |

| Editing the Schematic                   | IV-33 |

| Delete                                  | IV-33 |

| Move                                    | IV-33 |

| Duplicate                               | IV-34 |

| Drag                                    | IV-34 |

| Rotate and Mirror                       | IV-34 |

| The Clipboard and Copy, Cut, Paste      | IV-34 |

| Undo and Redo                           | IV-35 |

| Connectivity Aids                       | IV-35 |

| Check                                   | IV-36 |

| Output the Schematic                    | IV-37 |

| Saving the Schematic                    |       |

| Printing the Schematic                  | IV-37 |

| Netlisting                              | IV-37 |

| Creating Symbols in the Editor          |       |

| The Update Schematic Utility            | IV-39 |

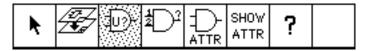

| Hierarchy Navigator                     |       |

| Navigating the Design                   |       |

| Push/Pop                                |       |

| Save                                    |       |

| Sheet                                   |       |

| Print                                   | IV-42 |

|                                         |       |

| Control                                    | IV-42 |

|--------------------------------------------|-------|

| Statistics                                 | IV-43 |

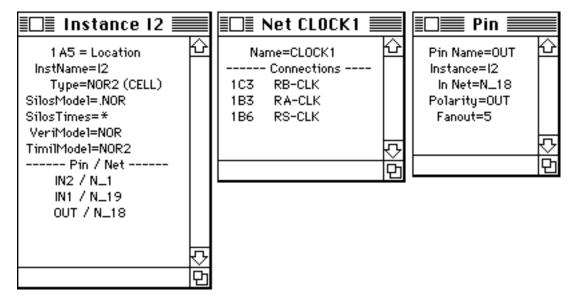

| Attributes                                 | IV-43 |

| Pin Attributes                             | IV-44 |

| Symbol Attributes                          | IV-44 |

| Attribute Windows                          |       |

| Verifying Design Entry                     | IV-45 |

| Tracing Signals                            |       |

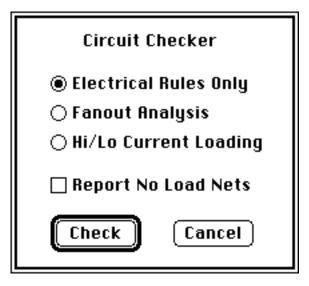

| Check Circuit                              | IV-47 |

| Circuit Analysis                           | IV-47 |

| Simulation                                 |       |

| Working with Split Hierarchy under DOS     |       |

| The Interactive Logic Analyzer             |       |

| ProbeItem                                  |       |

| FindItem                                   |       |

| Netlisting                                 | IV-49 |

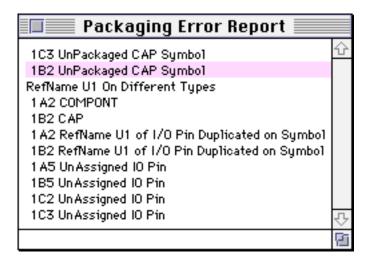

| Preparing for Manufacture                  |       |

| Pin Numbers                                |       |

| Reference Designators                      | IV-51 |

| Modify Attributes                          |       |

| Netlisting                                 |       |

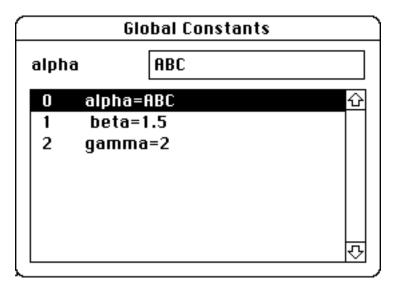

| Attributes                                 |       |

| Attribute Types                            |       |

| Creating Attributes                        |       |

| Assigning Values To Simple Attributes      |       |

| Displaying Attribute Values On A Schematic |       |

| Derived Attributes                         |       |

| Calculated Derived Attributes              | IV-61 |

| Derived Attributes and Hierarchy           | IV-62 |

| Case Study Using Derived Attributes        |       |

| Number Notation In Attributes              | IV-65 |

| Differences in IC and PCB Design Entry     | IV-67 |

| Symbol Types                               | IV-67 |

| DeMorgan Equivalent Gates                  |       |

| Instance Names and Reference Designators   | IV-68 |

| Assigning Reference Designators            |       |

| Pin Numbers                                | IV-69 |

| Gate Assignment                            |       |

| Pin Swapping                               |       |

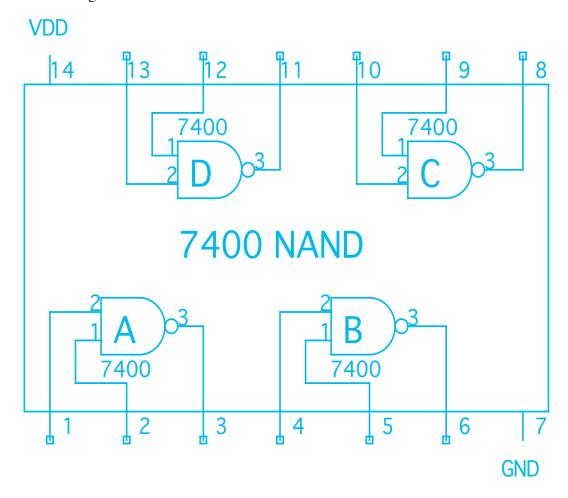

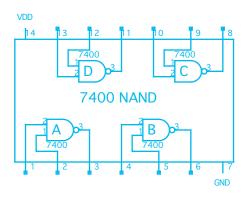

| Example PCB Design                         |       |

| System Configuration                       |       |

| Creating a Gate Symbol                     |       |

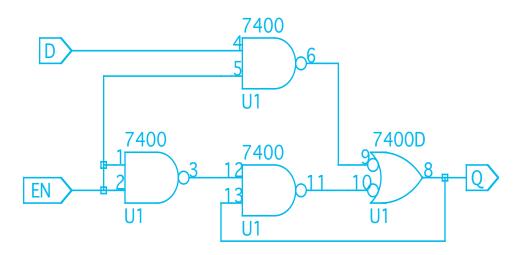

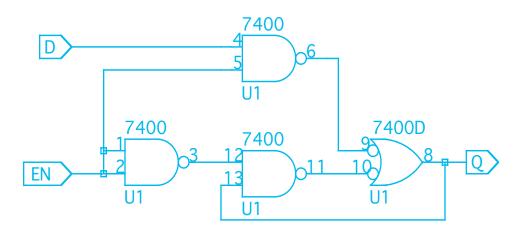

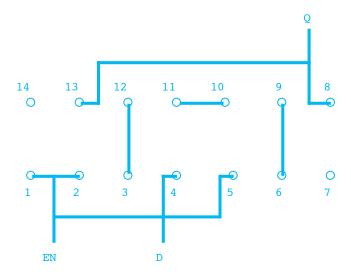

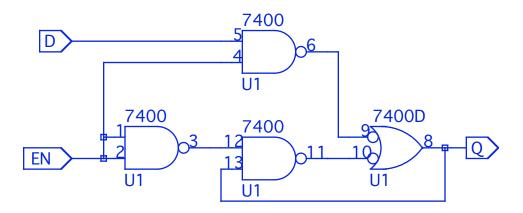

| Create the Latch Schematic                 |       |

|                                            |       |

# **Section V Command Reference**

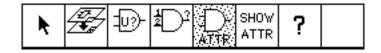

| Quick Command Reference   | V-3  |

|---------------------------|------|

| Add->Attribute            | V-5  |

| Add->Bus Tap              | V-7  |

| Add->Instance Name        | V-8  |

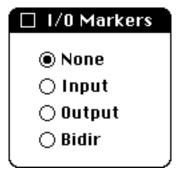

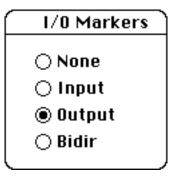

| Add->I/O Marker           | V-10 |

| Add->Net Name             | V-11 |

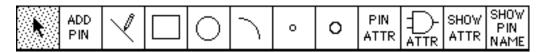

| Add->Pin                  | V-16 |

| Add->Pin Attribute        | V-17 |

| Add->Pin Name Location    | V-19 |

| Add->Pin Numbers          |      |

| Add->Reference Designator | V-22 |

| Add->Symbol               | V-23 |

| Add->Symbol Attribute     | V-25 |

| Add->Window               | V-27 |

| Add->Wire                 | V-29 |

| Draw->Arc                 | V-31 |

| Draw->Bubble / Big Bubble | V-32 |

| Draw->Circle              | V-33 |

| Draw->Line                | V-34 |

| Draw->Rectangle           | V-35 |

| Draw->Text                |      |

| Edit->Copy                | V-37 |

| Edit->Cut                 |      |

| Edit->Delete              |      |

| Edit->Drag                | V-41 |

| Edit->Duplicate           |      |

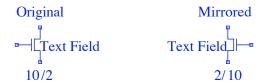

| Edit->Mirror              |      |

| Edit->Move                |      |

| Edit->Paste               |      |

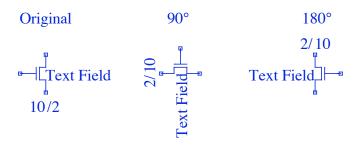

| Edit->Rotate              |      |

| Edit->Schematic / Symbol  |      |

| File->Create Symbol       |      |

| File->Exit                |      |

| File->Expand              |      |

| File->Help                |      |

| File->New                 |      |

| File->Open                |      |

| File->Print               |      |

| File->Print Window        |      |

| File->Save                |      |

| File->Save As             |      |

| File->Sheet               |      |

| Misc->Attribute           |      |

| Misc->Attribute Window    |      |

| Misc->Check               | V-67 |

| Misc->Control                                  | V-69       |

|------------------------------------------------|------------|

| Misc->Graphics Control                         |            |

| Misc->HiLite                                   |            |

| Misc->Mark                                     |            |

| Misc->Pin Numbers                              |            |

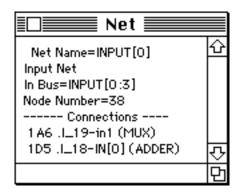

| Misc->Query                                    |            |

| Misc->Redo                                     |            |

| Misc->Reference Designator                     |            |

| Misc->Set Origin                               |            |

| Misc->Statistics                               |            |

| Misc->Undo                                     |            |

| Tools->FindItem.                               |            |

| Tools->ProbeItem.                              |            |

| View->Full Fit                                 |            |

| View->Pan/Win                                  |            |

| View->ZoomIn                                   |            |

| View->ZoomOut                                  |            |

|                                                |            |

| Section VI Interfaces                          |            |

|                                                |            |

| ASCII Interface                                | ASCII-1    |

| ASCII Symbol Interface                         | ASCII-1    |

| Example ASCII Symbol File                      | ASCII-3    |

| ASCII Schematic Interface                      |            |

|                                                |            |

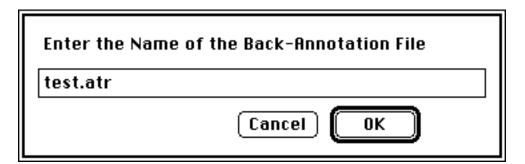

| Back Annotation Interface                      | Annotate-1 |

| Attribute Update File                          | Annotate-1 |

| Example Attribute Update File                  | Annotate-2 |

|                                                |            |

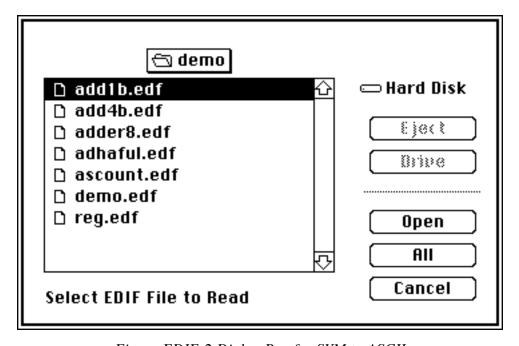

| The EDIF Interface                             |            |

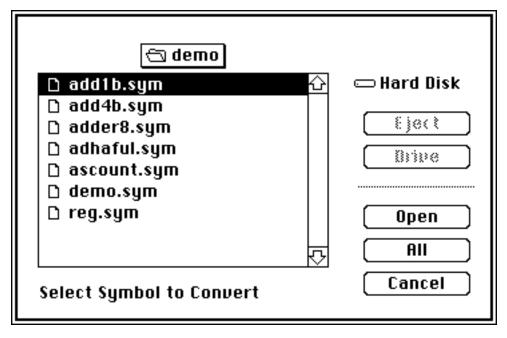

| Translating ECS Symbols To EDIF Files          |            |

| Translating EDIF Files to ECS Symbol Files     |            |

| EDIF File Format                               |            |

| Key Points For Creating EDIF Files             | EDIF-3     |

|                                                | C : 1      |

| Generic Netlists                               |            |

| Processes->Net List By Net (netorder)          |            |

| Processes->Net List By Pin (pinorder)          | Generic-2  |

| The PADS Interface                             | PADS-1     |

| Setting up the ecs.ini File                    |            |

| Adding a Menu Entry to the Hierarchy Navigator |            |

| Necessary Attributes                           |            |

| Preparation of Schematics                      |            |

| Error Messages for Pads                        |            |

| 1/101 1/1000agoo 101 1 aus                     | 1100-0     |

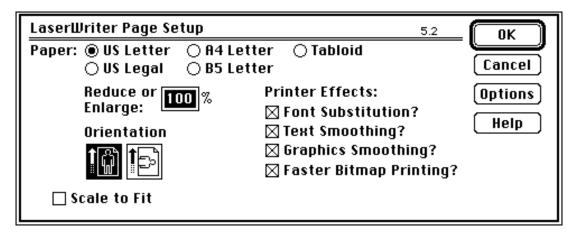

| Hardcopy Output                                                   | Printing-1 |

|-------------------------------------------------------------------|------------|

| ECS Configuration Printing Controls                               | Printing-1 |

| Menu Printing Controls                                            | Printing-1 |

| From the ECS Executive                                            | Printing-1 |

| From the Symbol Editor, Schematic Editor, and Hierarchy Navigator |            |

| Printing on Sun Workstation                                       |            |

| Interface to Other Applications on the Sun                        | Printing-3 |

| Printing Under DOS                                                |            |

| Selecting the Output Device                                       | _          |

| Scaling the Output                                                | Printing-3 |

| Print Status Messages                                             | Printing-4 |

| Batch Printing                                                    | Printing-5 |

| Interface to Other Applications in DOS                            | Printing-5 |

| The Redac Interface                                               | RINF-1     |

| Setting up the ecs.ini File                                       | RINF-1     |

| Adding a Menu Entry to the Hierarchy Navigator                    | RINF-1     |

| Necessary Attributes                                              | RINF-1     |

| Preparation of Schematics                                         | RINF-2     |

| Setting Up The Power Pins                                         | RINF-3     |

| Error Messages                                                    | RINF-3     |

| The SILOS Interface                                               | SILOS-1    |

| Installing SILOS                                                  | SILOS-1    |

| Setting up the ecs.ini File                                       | SILOS-1    |

| Adding a Menu Entry to the Hierarchy Navigator                    | SILOS-1    |

| Necessary Attributes                                              | SILOS-2    |

| Creating the Pattern File                                         | SILOS-3    |

| Controlling The Netlist Extraction                                | SILOS-4    |

| SILOS Format Conversions                                          | SILOS-5    |

| Building SILOS Symbol Libraries                                   | SILOS-5    |

| Examples                                                          | SILOS-7    |

| Negative Edge-Triggered J-K Flip Flop                             | SILOS-7    |

| Four-Bit Inverter                                                 | SILOS-8    |

| Error Messages                                                    | SILOS-8    |

| The SPICE Interface                                               | SPICE-1    |

| Setting up the ecs.ini File                                       |            |

| Adding a Menu Entry to the Hierarchy Navigator                    | SPICE-1    |

| Necessary Attributes                                              |            |

| Controlling The Netlist Extraction                                |            |

| SPICE Format Conversions                                          |            |

| Working with the Hierarchical Netlist                             |            |

| Working with the Flat Netlist                                     |            |

| Preprocessing a Control File                                      |            |

| Attributes Required for SPICE Elements.                           |            |

| Examples                                               | SPICE-10    |

|--------------------------------------------------------|-------------|

| Independent Voltage Source                             | SPICE-10    |

| MOSFET                                                 | SPICE-10    |

| Error Messages                                         | SPICE-11    |

| The Timemill Interface                                 | Timemill-1  |

| Installation of Timemill and Pathmill                  | Timemill-1  |

| Setting up the ecs.ini File                            | Timemill-1  |

| Adding a Menu Entry to the Hierarchy Navigator         | Timemill-2  |

| Necessary Attributes                                   |             |

| Preparing Additional Files                             |             |

| Sample Timemill Stimulus File                          | Timemill-4  |

| Sample Pathmill Static Setup File                      |             |

| Controlling The Netlist Extraction                     |             |

| Invoking the Timemill Simulator (PC only)              | Timemill-5  |

| Invoking the Pathmill Critical Path Analyzer (PC only) | Timemill-7  |

| Timemill Format Conversions                            |             |

| Building Timemill Symbol Libraries                     | Timemill-8  |

| Examples                                               | Timemill-9  |

| Functional Model for J-K Flip Flop:                    | Timemill-9  |

| Dummy Symbol Using Bus                                 | Timemill-9  |

| Error Messages                                         | Timemill-10 |

| The Verilog Interface                                  | Verilog-1   |

| Setting up the ecs.ini File                            | Verilog-1   |

| Controls->Verilog Controls                             | Verilog-1   |

| Adding a Menu Entry to the Hierarchy Navigator         | Verilog-2   |

| Necessary Attributes                                   |             |

| Controlling The Netlist Extraction                     | Verilog-4   |

| Verilog Format Conversions                             |             |

| Building Verilog Symbol Libraries                      | Verilog-5   |

| Example                                                | Verilog-6   |

| Error Messages                                         | Verilog-6   |

# **Preface**

Schematic drafting systems are used extensively in the electronics industry. They are one of the primary tools used for making drawings that represent the circuits built on printed circuit boards (PCBs) and integrated circuit (IC) chips.

These systems provide two essential services. They provide a working environment where the design engineer can perform and document the creative tasks. The systems can also extract a data description of a drawing and interface to verification tools that are used in the development process.

A variety of schematic systems are available. At one end of the spectrum are the workstation-based products that offer the greatest capability at the highest price. At the other extreme are the low-cost, personal-computer-based systems that offer a few features but are unable to handle the complex design tasks that face the modern design engineer.

The Engineering Capture System (ECS) offers the best of both extremes. The tool suite runs on many platforms, UNIX workstations, IBM compatible PCs, and Macintosh computers. Data can be exchanged among the different platforms. This allows you to perform schematic entry on a low-cost PC and then, if necessary, migrate the design to a workstation that has the capacity to handle the largest IC designs.

Some of the highlights of the ECS are:

- The system maintains connectivity as you draw a schematic. This prevents many common errors because you are not relying on post-process checking programs to find the errors after the design is almost complete.

- Multi-sheet schematics are supported throughout the system. Connectivity is instantly established between sheets. There is no need to perform a special linking process to connect signals that span multiple sheets.

- Hierarchy is an integral part of the system. Top-down and/or Bottom-up methodologies are fully supported. The complete design can be viewed in its hierarchical context with hierarchical names on the nets, pins, and symbol instances.

- Specific instances of circuit elements in the hierarchy can be identified and annotated with attributes that represent the physical implementation of the circuit. These attributes can be viewed and passed on to other design processes.

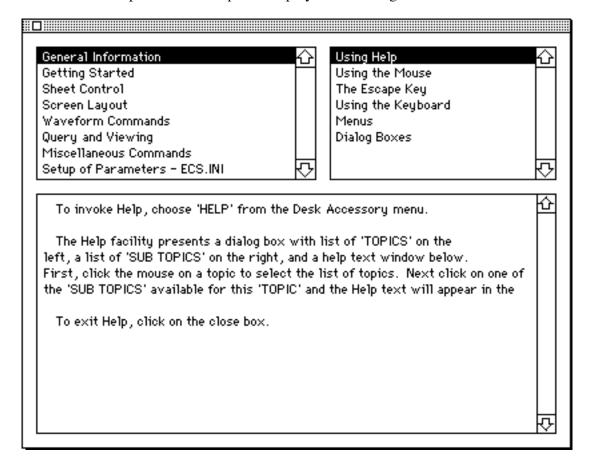

- The user interface includes an on-line help facility that provides needed information at the touch of a key.

- Operator errors are easily corrected with the use of the Undo and Redo commands. These commands can be used repetitively to backtrack in the work session.

• Symbols are easily created without stopping the schematic editing session. The symbols are immediately available for placement into the schematic.

The ECS uses the window environments of Sunview, Motif, Microsoft Windows, and MacOS as a foundation. These environments provide a consistent and friendly user interface. Multi-window and multi-task operations allow you to work concurrently on several portions of design. Many of the features common to workstations are supported on MacOS and MS\_DOS.

xvi Preface February 1992

# Using This Manual

This manual is divided into ten sections.

### Section 1, Before You Begin

Covers material that you need to know before using the ECS. This includes conventions used in the ECS and throughout this manual. Necessary hardware and software configurations are also described. The different window environments used on the Sun workstation, IBM compatible PC, and Macintosh are explained. Installation for each platform is also described.

You should look at the conventions used throughout this manual. If you are familiar with the graphics environment described for your platform, you can skip the graphics environment discussion in this section.

### **Section 2, System Configuration**

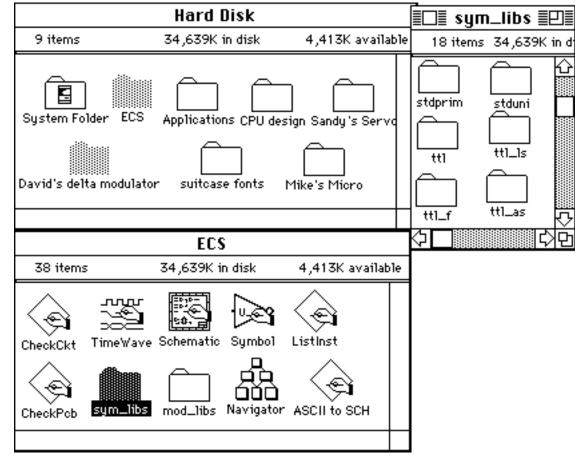

Explains how design directories are organized and libraries are accessed. The Preferences Editor is explained in detail. This editor is responsible for setting colors, creating attributes, setting library search paths, setting default display parameters, and much more.

You should read this before attempting a serious design with the ECS. The information about libraries and search paths can have a large impact on the way you structure your design.

### **Section 3, Getting Started**

Provides an overview of the way ECS treats schematics and hierarchy. Understanding the philosophy of the system enables you to use it more effectively.

A brief tutorial guides you through the fundamental operation of the ECS while building a small hierarchical design.

First-time ECS users should read through this section because the fundamental organization of data in the ECS is different from other design systems.

### **Section 4, Entering Your Design**

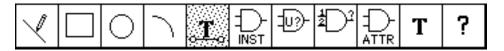

Gives you a detailed explanation of how to enter your design. It covers the Symbol Editor, Schematic Editor, and Hierarchy Navigator. The differences between entering an IC design and a PCB design are explained in this section. The use of attributes in the ECS is also explained.

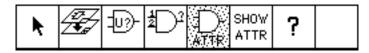

### Section 5, Command Reference

Contains a detailed alphabetical listing of commands used in the Symbol Editor, Schematic Editor, and the Hierarchy Navigator.

### Section 6, Interfaces

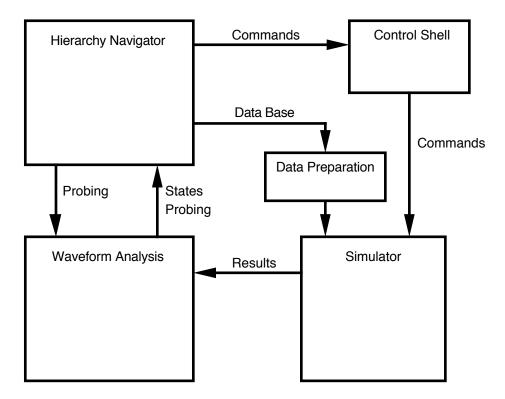

Explains several interfaces to the ECS. These include simulation interfaces for Verilog, SILOS, Timemill, SPICE, PADS, and Racal-Redac. Data transfer interfaces are supported for EDIF and ASCII. More interfaces are being added. Explains how to interface any digital simulator to the Hierarchy Navigator and the Waveform Tool. Refer to the *Interfaces* section for the latest list of supported interfaces. Printing is also explained in this section.

### Section 7 Design Analysis Tools

Describes the tools that help identify errors in designs. Also shows how to calculate an attributes value based on other attributes. Lists and describes the necessary attributes required to perform the checks. Explains the operation of the Electrical Rules Checker and the Critical Path Viewer. The PCB Packager and derived attributes are described.

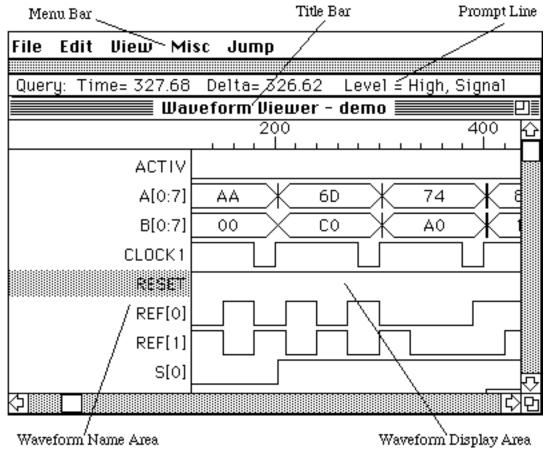

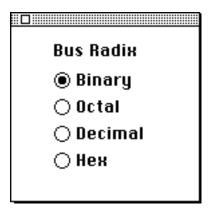

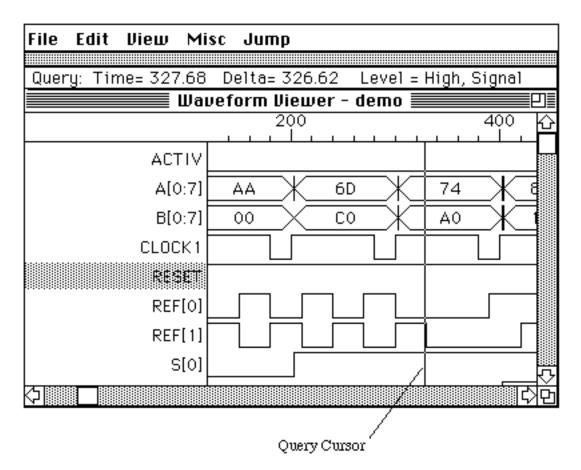

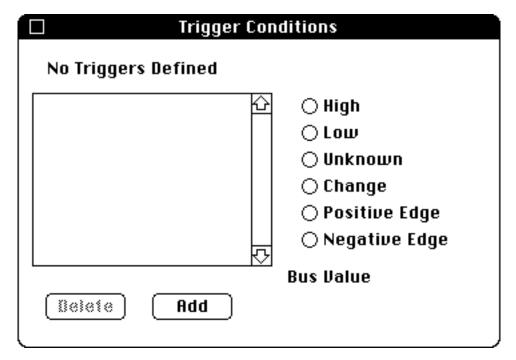

### **Section 8 Waveform Tool**

Describes the operation of the Waveform Tool. Shows how to manipulate waveforms and extract information for analysis. Indicates how to use this tool in conjunction with the Hierarchy Navigator and as a standalone tool.

### **Application Notes**

Application notes describing various short cuts, advanced techniques, or other useful information are added to this section.

### **Appendix**

This section will be used for future enhancements, additions or revisions to the manual.

xviii Using This Manual February 1992

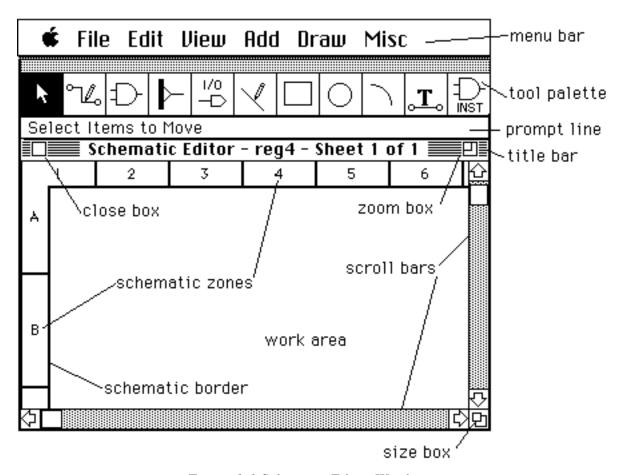

# Before You Begin

This section contains information describing the different hardware and software environments that support the Engineering Capture System (ECS).

The major topics covered in this section are:

- Conventions used throughout this manual

- Hardware and software configurations of Macintosh computers

- Installation procedures

# **ECS Conventions**

The following conventions are used throughout the ECS system on all platforms and in all the documentation. Platform-dependent information is described in the relevant section for your platform.

- ECS commands always appear in **boldface type**.

- ECS commands appear with the name of the menu where the command is found.

**Draw->Line** refers to the **Line** command found under the **Draw** menu