# **CDC® NETWORK PROCESSOR UNIT**

2551-1

2551-2

2551-3

2551-4

2552-2

HARDWARE REFERENCE MANUAL

|                | REVISION RECORD                                                                    |

|----------------|------------------------------------------------------------------------------------|

| REVISION       | DESCRIPTION                                                                        |

| 01             | Preliminary edition                                                                |

| 9/77           |                                                                                    |

| A              | Initial release                                                                    |

| (04-28-78)     |                                                                                    |

| В              | Revised to incorporate Engineering Change Orders 8050, 8062, 8130, 8039, 8240,     |

| (12-15-78)     | 8216, and 8110. Editorial change only on page 1-5. Page 4-1 deleted.               |

| С              | Revised to incorporate latest configuration changes and requests on comment sheet. |

| (04-15-80)     | This edition obsoletes the previous revisions.                                     |

| D              | Manual revised; includes Engineering Change Order 44344. Front Cover through vii,  |

| (03-04-83)     | ix, x, 1-1 through 1-17, 2-2, and 2-12 are revised. Pages 1-18 through 1-20 are    |

|                | added.                                                                             |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                | ·                                                                                  |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

|                |                                                                                    |

| ·              |                                                                                    |

| ublication No. |                                                                                    |

REVISION LETTERS I, O, Q, S, X AND Z ARE NOT USED

© 1977, 1978, 1980, 1983 by Control Data Corporation All rights reserved Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation

Publications and Graphics Division

4201 North Lexington Avenue

St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

# LIST OF EFFECTIVE PAGES

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE               | REV    | PAGE         | REV   | PAGE         | REV      | PAGE | REV  | PAGE | REV |

|--------------------|--------|--------------|-------|--------------|----------|------|------|------|-----|

| Front Cover        | -      | 3-12         | С     | 4-35         | С        |      |      |      |     |

| Title Page         | -      | 3-13         | C     | 4-36         | C        |      |      |      | 1   |

| ii                 | D      | 3-14         | C     | 4-37         | С        |      |      |      |     |

| iii/iv             | D      | 3-15         | C     | 4-38         | С        | •    |      |      |     |

| v                  | D      | 3-16         | C     | 4-39         | C        | •    |      |      |     |

| vi                 | D      | 3-17         | C     | 4-40         | C        |      |      |      | l   |

| vii                | D      | 3-18         | C     | 4-41         | C        |      | .    |      | i   |

| viii               | C      | 3-19         | C     | 4-42         | 00000    |      |      |      |     |

| ix                 | D      | 3-20         | C     | 4-43         | 0        |      | 1 1  |      | 1   |

| x<br>1-1           | D<br>D | 3-21<br>3-22 | C     | 4-44         |          |      | 1    |      | 1   |

| 1-2                | D      | 3-22         | C     | 4-46         | ا کا     |      |      |      | 1   |

| 1-3                | D      | 3-23         | c     | 4-47         | c        |      | 1 1  |      | 1   |

| 1-4                | D      | 3-25         | c     | 4-48         | č        |      |      |      | 1   |

| 1-5                | D      | 3-26         | č     | 4-49         | ١č١      |      | 1 1  |      |     |

| 1-6                | D      | 3-27         | Č     | 4-50         | C<br>C   |      |      |      | 1   |

| 1-7                | D      | 3-28         | c     | 4-51         | c        |      | 1 1  |      | 1   |

| 1-8                | D      | 3-29         | l č l | 4-52         | 0000     |      |      |      |     |

| 1-9                | D      | 3-30         | c     | 4-53         | c        |      |      |      | 1   |

| 1-10               | D      | 3-31         | C     | 4-54         | C        |      |      |      |     |

| 1-11               | D      | 3-32         | c     | 4-55         | C        |      | 1 1  |      |     |

| 1-12               | D      | 3-33         | C     | 4-56         | С        |      | 1    | İ    | 1   |

| 1-13               | D      | 3-34         | C     | 4-57         | С        |      | 1    |      | 1   |

| 1-14               | D      | 3-35         | C     | 4-58         | 0000000  | 1    |      |      | 1   |

| 1-15               | D      | 3-36         | C     | 4-59         | С        | İ    | 1 1  |      | 1   |

| 1-16               | D      | 4-1          | C     | 4-60         | C        |      |      |      | 1   |

| 1-17               | D      | 4-2          | C     | 4-61         | C        |      |      |      | 1   |

| 1-18               | D      | 4-3          | C     | 4-62         | 0        |      |      | 1    | 1   |

| 1-19<br>1-20       | D<br>D | 4-4<br>4-5   | C     | 4-63<br>4-64 |          |      | 1 1  |      | l   |

| 2-1                | C      | 4-5          | C     | 4-65         | 2        |      |      |      | 1   |

| 2-2                | D      | 4-7          | c     | 4-66         | ا م      |      |      |      |     |

| 2-3                | c      | 4-8          | c     | 5-1          | C<br>C   |      | 1 1  |      | 1   |

| 2-4                | č      | 4-9          | c     | 5-2          | č        |      | 1 1  | '    | 1   |

| 2-5                | č      | 4-10         | c     | 5-3          | Č        |      | 1 1  |      | 1   |

| 2-6                | č      | 4-11         | Č     | 5-4          | 00000000 | 1    |      | •    | 1   |

| 2-7                | c      | 4-12         | l č   | 5-5          | c        |      | 1 1  |      | 1   |

| 2-8                | C      | 4-13         | c     | 5-6          | С        |      |      |      |     |

| 2-9                | c      | 4-14         | c     | 5-7          | C        | · ·  |      |      |     |

| 2-10               | C      | 4-15         | c     | 5-8          | C        |      | 1 1  |      |     |

| 2-11               | С      | 4-16         | C     | A-1          | C        |      | 1 1  |      |     |

| 2-12               | D      | 4-17         | c     | B-1          | C        |      | 1 1  | `    |     |

| 2-13               | C      | 4-18         | C     | B-2          | С        | -    |      |      | 1   |

| 2-14               | C      | 4-19         | C     | Comment      |          |      |      |      |     |

| 2-15               | C      | 4-20         | C     | Sheet        | D        |      | 1    |      |     |

| 2-16               | C      | 4-21         | C     | Back Cover   | -        |      |      |      | 1   |

| 2-17               | C      | 4-22         | C     |              |          |      |      |      | I   |

| 2-18               | C      | 4-23         | C     |              |          |      | 1. 1 |      |     |

| 3-1<br>3-2         |        | 4-24         | C     |              |          |      |      |      | 1   |

| 3-2                | C      | 4-25<br>4-26 | C     |              |          | l    | 1 1  |      |     |

| 3-3                | c      | 4-26         | C     | 1            |          |      |      |      |     |

| 3-5                | c      | 4-27         | c     |              |          |      |      |      | 1   |

| 3-6                | c      | 4-28         | c     | 1            |          |      |      | · [  |     |

| 3-7                | . ~ !  |              | 1 2   | 1            | l 1      | 1    | 1    |      | 1   |

|                    | וחו    | 14-30        | 1 "   | 1            | ,        | 1    |      |      | 1   |

| 3-8                | C      | 4-30         | C     |              |          |      |      |      | 1   |

| 3-8<br>3-9         | c      | 4-31         | C     |              |          |      |      |      |     |

| 3-8<br>3-9<br>3-10 |        |              | 0000  |              |          |      |      |      |     |

# **PREFACE**

This manual describes the physical, functional, operational, and programming characteristics of the CDC® 2551-1, 2551-2, 2551-3, 2551-4, and 2552-2 Network Processor Units (NPUs). The manual includes the various NPU configurations, which are available to the user by addition of standard product options and upgrade kits.

This manual is intended for use by customer, marketing, training, and programming personnel. For an in-depth analysis of the product structure, operation, and maintenance, refer to the NPU hardware maintenance manual.

The related publications listed below are available through CDC Literature and Distribution Services, 308 North Dale Street, St. Paul, Minnesota 55103.

| Publication Title                                                                                                                | Publication Number |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Basic Microprogrammable Processor,<br>Hardware Maintenance Manual                                                                | 39451400           |

| 1714 Computer System,<br>Reference Manual                                                                                        | 60364900           |

| 3000L Communications Coupler DY161-A, Hardware Reference/Maintenance Manual                                                      | 60470400           |

| 2552-1 6000 Coupler,<br>Hardware Maintenance Manual                                                                              | 60471900           |

| Cyclic Encoder DY180-A,<br>Hardware Maintenance Manual                                                                           | 60472600           |

| 2550-101 Emulation Controlware, Reference Manual                                                                                 | 60474000           |

| 2550-101 Installation Handbook                                                                                                   | 60474100           |

| 2551-1, 2551-2, 2551-3, 2551-4, 2552-2<br>Network Processor Unit Host Communications<br>Processor 2550-2 Site Preparation Manual | 74641200           |

| Synchronous Communications Line<br>Adapter DU138-A, DU139-A, DU140-A,<br>Hardware Maintenance Manual                             | 74700700           |

| Asynchronous Communications Line<br>Adapter DU137-A, Hardware Maintenance<br>Manual                                              | 74700900           |

| Communications Line Adapter,<br>Synchronous Data Link Control DY162-A,<br>Hardware Maintenance Manual                            | 74873290           |

60472800 D

| MAP                                                                                                 |          |

|-----------------------------------------------------------------------------------------------------|----------|

| Communications Coupler DK106-B, Hardware Maintenance Manual                                         | 74873946 |

| Network Processor Unit Equipment<br>Cabinets, Hardware Maintenance Manual                           | 74873971 |

| System Autostart Module DY204-A,<br>Hardware Maintenance Manual                                     | 74874450 |

| Emulation Coupler DY159-A, XA226-A, Hardware Maintenance Manual                                     | 74879600 |

| Tape Cassette Controller FA104-A,<br>Hardware Maintenance Manual                                    | 96711900 |

| 255X Host Communications Processor/<br>Network Processor Unit, Reference<br>Manual, CCP Version 1.0 | 60470000 |

| Transform with Micromemory DE402-A/1700, Hardware Maintenance Manual                                | 96728700 |

| I/O TTY Controller CW212-A,<br>Hardware Maintenance Manual                                          | 96728900 |

| MP17 Communications Processor,<br>Hardware Reference Manual                                         | 96768300 |

| 1700 Enhanced Processor with MOS<br>Memory and Interface AA109-A/B,<br>Hardware Maintenance Manual  | 96768600 |

| AA109-A/B (AA135-A) Communications Controller<br>Field Print Package                                | 60475150 |

### WARNING

This equipment generates, uses and can radiate radio frequency energy, and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A peripheral computing device pursuant to Subpart J of Part 15 of the FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

# **CONTENTS**

| 1. SYSTEM DESCRIPTION         | 1-1  | 2. FUNCTIONAL DESCRIPTION             | 2-1             |

|-------------------------------|------|---------------------------------------|-----------------|

| Major Features                | 1-1  | NPU Main Data Paths                   | 2-1             |

| Network Communications System |      | Basic Emulation Concepts              | 2-1             |

| Concepts                      | 1-5  | Interrupt System                      | 2-3             |

| Physical Description          | 1-5  | Macrointerrupts                       | 2-3             |

| 2551-1 NPU Equipment          | 1-7  | Microinterrupts                       | 2-3             |

| 2551-2 NPU Equipment          | 1-7  | Status/Mode and                       |                 |

|                               | 1-7  | Interrupt Bits                        | 2-4             |

| 2551-3 NPU Equipment          | 1-7  | Automatic Data Transfer               |                 |

| 2551-4 NPU Equipment          | 1-8  | Mode                                  | 2-4             |

| Communications Processor      | 1-8  | Multiplex Loop Interface              | 4 7             |

| 2552-2 NPU Equipment          | 1-8  | •                                     | 2-4             |

| Base Processor                |      | Adapter Interrupts<br>Real-Time-Clock | 4- <del>4</del> |

| Multiplex Processor           | 1-12 |                                       | 2-5             |

| Cross-Control and Console     | 1 10 | Interrupts                            | 2-5             |

| Switch                        | 1-12 | Interrupt Holding Registers           | 2-5             |

| Communications Console        | 1-12 | NPU Components Functional             | 2 5             |

| Communications Coupler        | 1-12 | Description                           | 2-5             |

| Multiplex Subsystem           | 1-12 | Single Processor                      | 2-5             |

| Communications Line           |      | Microprocessor                        | 2-6             |

| Adapters                      | 1-13 | Panel/Console Interface               | 2-10            |

| Loop Multiplexer              | 1-13 | I/O Subsystem                         | 2-11            |

| Multiplex Loop Interface      |      | Cyclic Encoder                        | 2-11            |

| Adapter                       | 1-13 | Main Memory                           | 2-12            |

| Maintenance Panel             | 1-13 | Dual Processor                        | 2-13            |

| Cassette Tape Drive           | 1-13 | Console Switch                        | 2-13            |

| System Autostart Module       | 1-13 | Processor Cross Control               | 2-13            |

| Power Supplies                | 1-13 | Multiplex Subsystem                   | 2-14            |

| Cabling                       | 1-13 | Multiplex Loop Interface              |                 |

| Air Blowers and Filter        |      | Adapter                               | 2-15            |

| Assemblies                    | 1-14 | Loop Multiplexer                      | 2-15            |

| Expansion Systems             | 1-14 | Communications Line Adapter           | 2-16            |

| Electromagnetic Interference  |      | Tape Cassette                         | 2-17            |

| Protection                    | 1-14 | System Autostart Module               | 2-17            |

| Functional Description        | 1-14 | Communications Coupler                | 2-18            |

| Processor                     | 1-15 |                                       |                 |

| Coupler                       | 1-15 |                                       |                 |

| Multiplex Subsystem           | 1-15 | 3. OPERATING INSTRUCTIONS             | 3-1             |

| Operating Programs and        |      |                                       |                 |

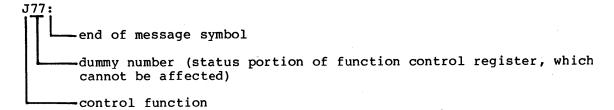

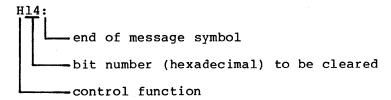

| Diagnostics                   | 1-17 | Function Control Register             | 3-1             |

| Maintenance                   | 1-18 | Control and Indicators                | 3-4             |

| Communications Software       | 1-18 | Maintenance Panel                     | 3-4             |

| Host Software                 | 1-18 | Communications Console                | 3-4             |

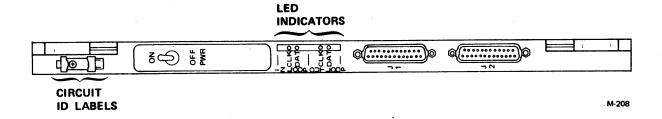

| Communications Control        |      | I/O TTY Interface                     | 3-4             |

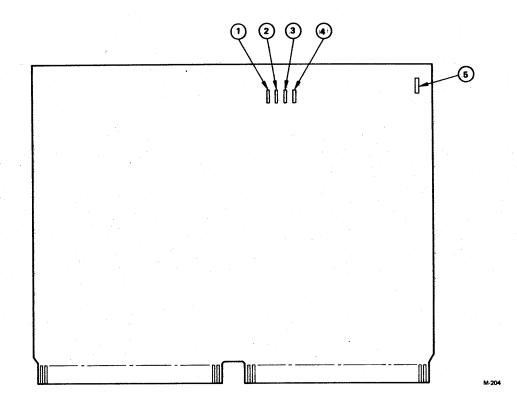

| Software                      | 1-19 | Cyclic Encoder                        | 3-4             |

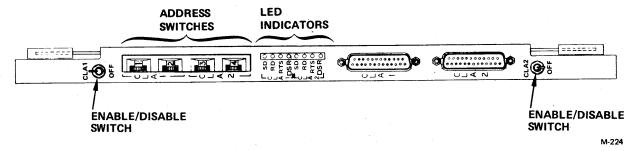

| Base System Software          | 1-19 | Loop Multiplexer                      | 3-15            |

| Network Communications        |      | Multiplex Loop Interface              |                 |

| Software                      | 1-20 | Adapter                               | 3-15            |

|                               | 1-20 | naupter                               |                 |

| Interface Programs            | 1-20 |                                       |                 |

| Support Software              | 1-20 |                                       |                 |

vii •

| Communications Line          |              | Emergency-Off Procedure      | 3-36         |

|------------------------------|--------------|------------------------------|--------------|

| Adapter                      | 3-15         | Checks and Adjustments       | 3-36         |

| Communications Coupler       | 3-17         | Shutdown Procedure           | 3-36         |

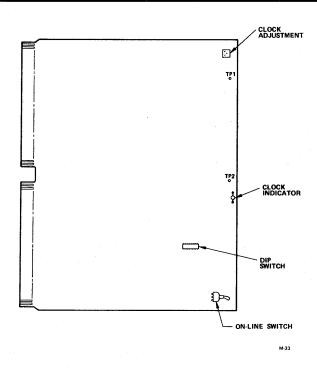

| Clock Adjustment             | 3-17         |                              |              |

| Clock Indicator              | 3-19         |                              |              |

|                              |              | 4. COMMUNICATIONS PROCESSOR  |              |

| On-Line Switch               | 3-19         | INSTRUCTIONS                 | 4-1          |

| DIP Switch                   | 3-19         |                              |              |

| Micromemory                  | 3-19         | Macroinstruction Formats and |              |

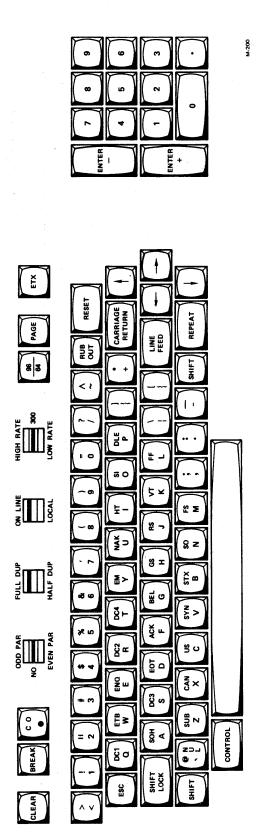

| Cassette Tape Controller     | 3-22         | Instructions                 | 4-1          |

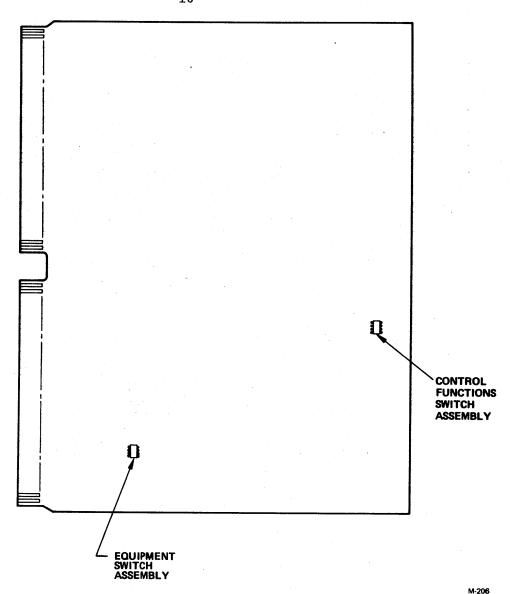

| Equipment Switch Assembly    | 3-22         | Basic Macroinstruction       |              |

| Control Functions Switch     |              | Formats                      | 4-1          |

| Assembly                     | 3-23         | Enhanced Macroinstruction    |              |

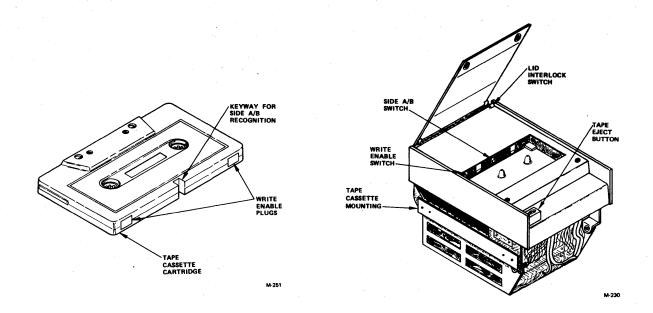

| Cassette Tape Drive          | 3-24         | Formats                      | 4-1          |

| Lid Interlock Switch         | 3-24         | Storage Reference            |              |

| Side A/B Switch              | 3-24         | Instruction Format           | 4-2          |

| Write Enable Switch          | 3-25         | Storage Reference            |              |

| Console Switchbox            | 3-25         | Instructions                 | 4-6          |

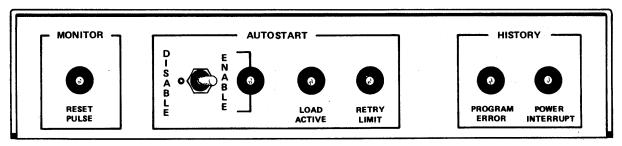

| System Autostart Module      | 3-25         | Register Reference           | - •          |

| Start-Up Procedure           | 3-25         | Instruction Format           | 4-8          |

| System Autostart Module      |              | Register Reference           |              |

| Operation                    | 3-25         | Instructions                 | 4-8          |

| Operating Procedures         | 3-27         | Enhanced Instructions        | 4-14         |

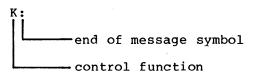

| Master Clear                 | 3-27         | Type 2 Storage Reference     |              |

| Display Contents             | 3-27         | Instructions                 | 4-14         |

| Clear Bit                    | 3-28         | Field Reference              | 1 11         |

| Set Bit                      | 3-28         | Instructions                 | 4-22         |

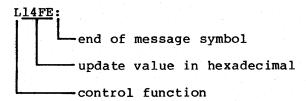

| Change Contents (Digit Mode) | 3-28         | Type 2 Skip Instructions     | 4-23         |

| Change Contents (Bit Mode)   | 3-29         | Decrement and Repeat         | 4 <b>2</b> 5 |

| Toggle Upper Indicator       | 3-29         | Instructions                 | 4-24         |

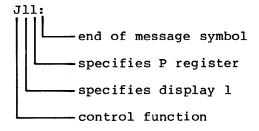

| Display Register Contents    | 3 <b>2</b> , | Type 2 Interregister         | 7 27         |

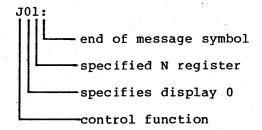

| (Display 0)                  | 3-30         | Instructions                 | 4-25         |

| Display Register Contents    |              | Miscellaneous Instructions   | 4-25         |

| (Display 1)                  | 3-30         | Autodata Transfer            | 4-32         |

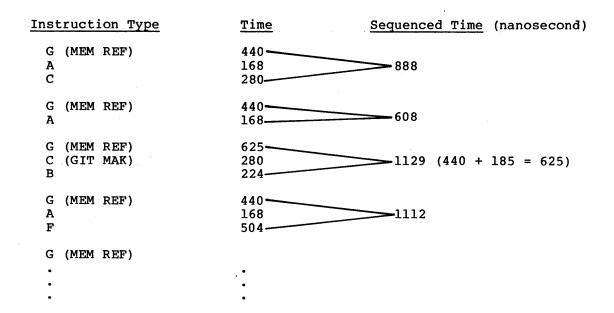

| Load A Register (Display 0)  | 3-31         | Macroinstruction Timing      | 4-35         |

| Load A Register (Display 1)  | 3-31         | Microprogramming Usage       | 4-35         |

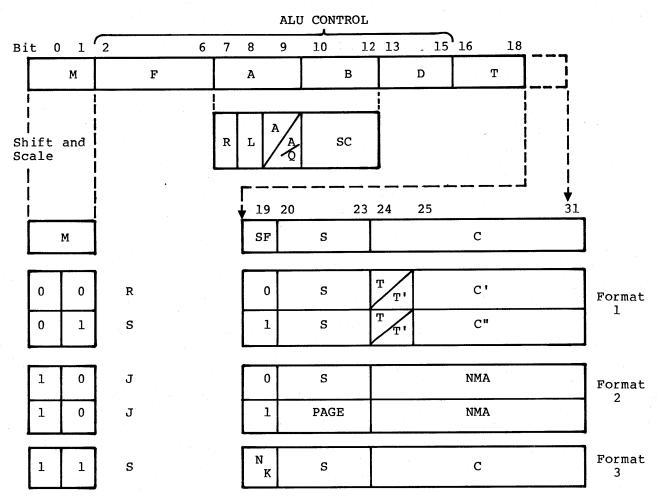

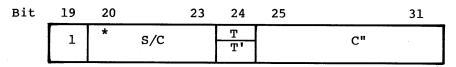

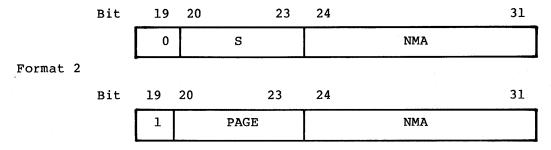

| Tape Cassette Autoload       | 3-32         | Microinstruction Formats     | 4-40         |

| Host Computer Autoload       | 3-32         | Detailed Microinstruction    | 4-40         |

| Start Processor              | 3-33         | Coding                       | 4-43         |

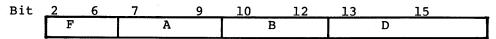

| Stop Processor               | 3-33         | M Field (Bits 0 and 1)       | 4-43         |

| Procedure Examples           | 3-33         | F Field (Bits 2 Through 6)   | 4-43         |

| Display Main Memory          | 5 55         | Logical Operations           | 4-43         |

| Location                     | 3-33         | Arithmetic Operations        |              |

| Write Into Main Memory       | 3-34         | Shift Operations             | 4-44         |

| Display P Register in        | 3-34         |                              | 4-45         |

| Repeat Mode                  | 3-34         | Scale Operations             | 4-47         |

| Operation in Step Mode       | 3-34<br>3-35 | Microinstruction Timing      | 4-64         |

|                              | 3-35         |                              |              |

| Load and Execute             | 2 25         | E I/O PROCESSMENTE PORTE     | <b>.</b> .   |

| Macroprogram                 | 3-35         | 5. I/O PROGRAMMING FORMATS   | 5-1          |

|                              |              |                              |              |

|                              |              |                              |              |

# **APPENDIXES**

| Α | Hexadecimal/Decimal |     |   |                   |     |

|---|---------------------|-----|---|-------------------|-----|

|   | Conversion          | A-1 | В | Mnemonics Listing | B-1 |

# **FIGURES**

| 1-1        | 2551-1, 2551-2, 2551-3, and                     | đ    | 3-10 | 2K RAM Micromemory Page                          |      |

|------------|-------------------------------------------------|------|------|--------------------------------------------------|------|

|            | 2551-4 Network Processor                        |      | 2 11 | Select Switches                                  | 3-20 |

| 1-2        | Unit Block Diagram<br>2552-2 Network Processor  | 1-3  | 3-11 | 8K RAM Micromemory Page<br>Selelct Switches      | 3-21 |

| 1-2        | Unit Block Diagram                              | 1-4  | 3-12 | Cassette Tape Controller                         | J Z1 |

| 1-3        | Single Node System,                             |      | 3 12 | Controls                                         | 3-22 |

|            | Block Diagram                                   | 1-6  | 3-13 | Cassette Tape Drive                              |      |

| 1-4        | Multinode System (One                           |      |      | Controls                                         | 3-24 |

|            | Local and Three Remote                          |      | 3-14 | System Autostart Module                          |      |

|            | Nodes), Block Diagram                           | 1-6  |      | Controls and Indicators                          | 3-26 |

| 1-5        | 2551-1, 2551-2, 2551-3, and                     | a a  | 4-1  | Storage Reference<br>Instruction Format          | 4-2  |

|            | 2551-4 Network Processor<br>Unit Front and Side |      | 4-2  | Register Reference                               | 4-2  |

|            | Views                                           | 1-9  | 7 2  | Instruction Format                               | 4-9  |

| 1-6        | 2552-2 Network Processor                        |      | 4-3  | Interregister Instruction                        |      |

|            | Unit                                            | 1-10 | -    | Format                                           | 4-11 |

| 1-7        | NPU Simplified Block                            |      | 4-4  | Skip Instruction Format                          | 4-12 |

|            | Diagram                                         | 1-14 | 4-5  | Shift Instruction Format                         | 4-14 |

| 1-8        | Communications Software                         |      | 4-6  | ADT Table for Multiple                           |      |

|            | Overview                                        | 1-19 |      | AQ Devices                                       | 4-34 |

| 2-1        | 2551-1, 2551-2, 2551-3, and                     | d    | 4-7  | Microinstruction Formats                         | 4-4] |

|            | 2551-4 NPU Major                                |      | 4-8  | Microinstruction Classification                  | 4-65 |

|            | Functional Areas and<br>Data Paths              | 2-2  | 4-9  | Calculation of                                   | 4-05 |

| 2-2        | 2552-2 NPU Major                                | 22   | 4-3  | Microprogram Sequence                            |      |

|            | Functional Areas and                            |      |      | Execution Time                                   | 4-66 |

|            | Data Paths                                      | 2-2  | 5-1  | Communications Coupler                           |      |

| 2-3        | Microprocessor Functional                       |      |      | PPU Function Codes                               | 5-1  |

|            | Block Diagram                                   | 2-7  | 5-2  | Communications Coupler                           |      |

| 2-4        | Maintenance Panel/Com-                          |      |      | Status Format                                    | 5-2  |

|            | munications Console,                            |      | 5-3  | Communications Coupler                           |      |

| 2 5        | Interface Block Diagram                         | 2-11 |      | Input Switch Status                              | 5-2  |

| 2-5        | Communications Coupler<br>Interfaces Block      |      | 5-4  | Format Communications Coupler-                   | 3-2  |

|            | Diagram                                         | 2-18 | J4   | Processor Set/Sample                             |      |

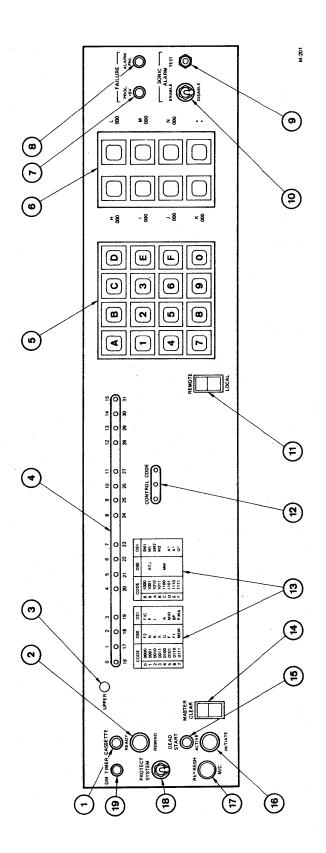

| 3-1        | Maintenance Panel Controls                      | 2 10 |      | Instruction Format                               | 5-3  |

| <b>J 1</b> | and Indicators                                  | 3-7  | 5-5  | Cassette Tape Controller                         |      |

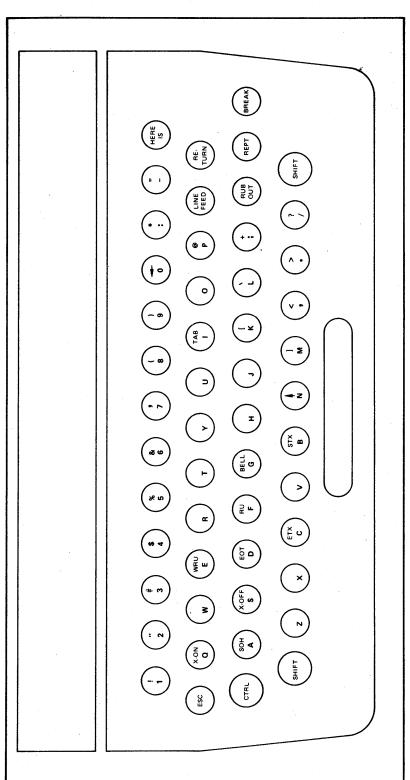

| 3-2        | Typical Teletypewriter                          |      |      | Control Functions                                |      |

|            | Keyboard and Controls                           | 3-12 |      | Format                                           | 5-4  |

| 3-3        | Typical Cathode Ray Tube                        |      | 5-6  | Cassette Tape Controller                         |      |

|            | 752 Conversational                              |      |      | Motion Controls                                  | 5-4  |

|            | Display Keyboard and                            | 2 12 | 5-7  | Cassette Tape Controller                         |      |

| 2.4        | Controls                                        | 3-13 | E 0  | Status Response Format<br>Card Reader Controller | 5-5  |

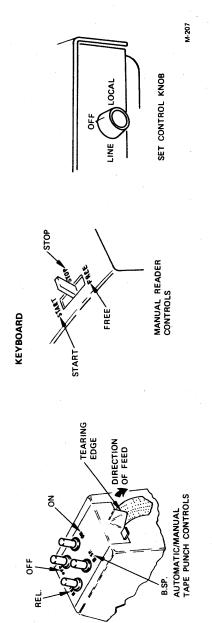

| 3-4        | I/O TTY Interface                               | 3-14 | 5-8  | Director Function                                |      |

| 3-5        | Controls Cyclic Encoder Indicator               | 3-14 |      | Format                                           | 5-5  |

| 3-6        | Loop Multiplexer                                | 3 14 | 5-9  | Card Reader Controller                           |      |

| 3 0        | Controls and Indicators                         | 3-16 | •    | Director Status 1                                |      |

| 3-7        | Multiplex Loop Interface                        |      |      | Format                                           | 5-6  |

|            | Adapter Output Loop                             |      | 5-10 | Card Reader Controller                           |      |

|            | Interface Indicators                            | 3-16 |      | Director Status 2                                |      |

| 3-8        | Communications Line                             |      |      | Format                                           | 5-6  |

|            | Adapter Controls                                | 2 16 | 5-11 | Card Reader Controller                           |      |

| 2 0        | and Indicators                                  | 3-16 |      | Data Transfer Command                            | 5-7  |

| 3-9        | Communications Coupler CYBER Interface Controls |      |      | Format                                           | J /  |

|            | and Indicators                                  | 3-18 |      |                                                  |      |

|            | and indicators                                  | 2 10 |      |                                                  |      |

60472800 D ix

|      |                            |      |       | •                         |      |

|------|----------------------------|------|-------|---------------------------|------|

|      |                            |      |       |                           |      |

|      |                            | TABL | ES    |                           |      |

|      |                            |      |       |                           |      |

| 1-1  | NPU Functional             |      | 3-12  | Control Functions Switch  | 3-23 |

|      | Characteristics            | 1-16 | 3-13  |                           | 5-25 |

| 2-1  | Interrupt Bit              |      |       | Controls and Indicators   | 3-26 |

|      | Assignments                | 2-6  | 4-1   | Storage Reference         |      |

| 3-1  | Function Control Register  |      |       | Instruction Addressing    | 4-3  |

|      | Bit and Digit Functions    | 3-2  | 4-2   | Interregister Instruction |      |

| 3-2  | Function Control Register  |      |       | Truth Table               | 4-11 |

|      | Display Code               |      | 4-3   | Type 2 Storage Addressing |      |

|      | Definitions                | 3-3  |       | Relationships             | 4-16 |

| 3-3  | Function Control Register  |      | 4 - 4 | Macroinstruction          |      |

|      | Bit Descriptions           | 3-5  |       | Execution Times           | 4-36 |

| 3-4  | Maintenance Panel Controls |      | 4-5   | M Field Operations        | 4-44 |

|      | and Indicators             | 3-8  | 4-6   | Logical Operations        | 4-45 |

| 3-5  | Control Character Code/    |      | 4-7   | Arithmetic Operations     | 4-46 |

|      | Functions                  | 3-10 | 4-8   | Shift Operations          | 4-47 |

| 3-6  | Switch Settings for I/O    |      | 4-9   | Scale Operations          | 4-48 |

|      | TTY Interface              | 3-15 | 4-10  | A Input Operations        | 4-49 |

| 3-7  | Loop Multiplexer Switch    |      | 4-11  | A' Input Operations       | 4-50 |

|      | and Indicators             | 3-17 | 4-12  | B Codes                   | 4-51 |

| 3-8  | Communications Line        |      | 4-13  | B' Codes                  | 4-52 |

|      | Adapter Switches and       |      | 4-14  | D Code Transfers          | 4-53 |

|      | Indicators                 | 3-18 | 4-15  | D' Code Transfers         | 4-54 |

| 3-9  | Switch Settings for        |      | 4-16  | D" Code Transfers         | 4-55 |

|      | Communications Coupler     |      | 4-17  | DD" Codes                 | 4-55 |

|      | Synchronizer               | 3-19 | 4-18  |                           | 4-56 |

| 3-10 | Switch Setting for 2K      |      | 4-19  | T' Addressing Modes       | 4-57 |

|      | RAM Micromemory Page       |      | 4-20  | S Field Codes             | 4-58 |

3 - 20

3-21

5-7

5-7

5-14 Line Printer Controller

Director Status

Response Format

5-15 Line Printer Controller

Data Transfer Command

Format

4-21 C Code Actions

4-22 Microinstruction

Execution Times

5-8

5-8

5-12 Peripheral Controller Self-Test Command

5-13 Line Printer Controller Director Function

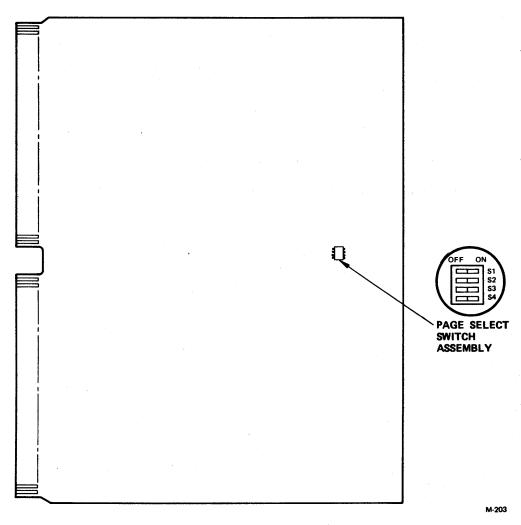

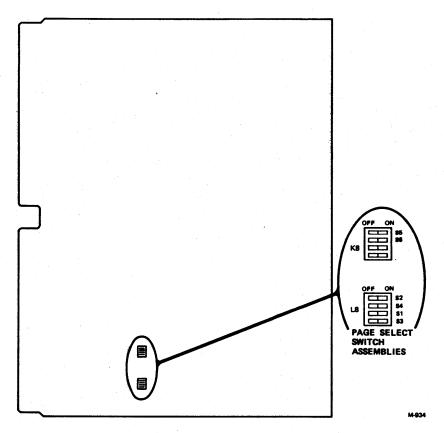

Select Switches

Select Switches

3-11 Switch Settings for 8K RAM Micromemory Page

Format

Format

4-60

4-65

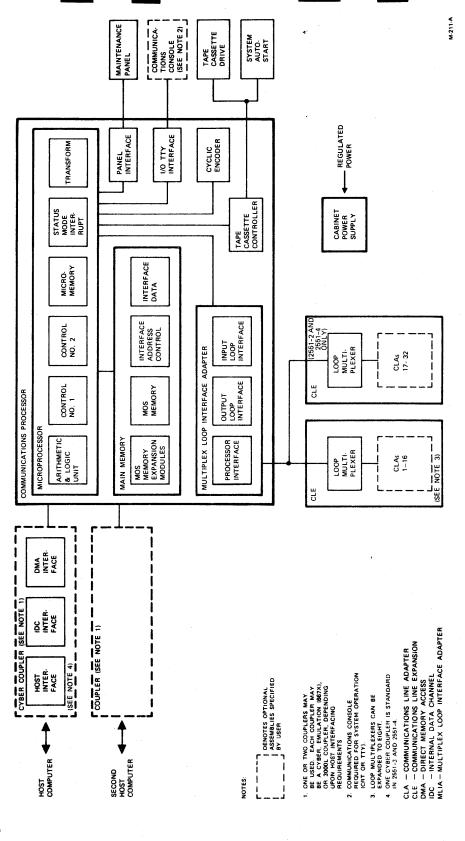

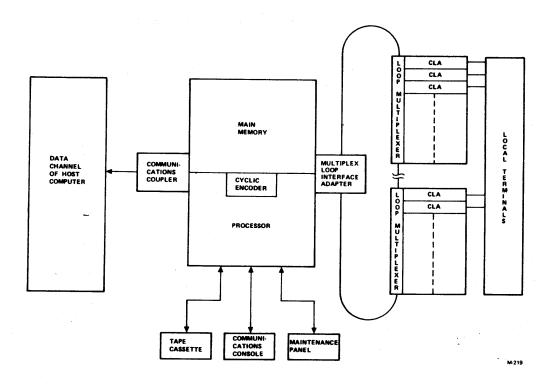

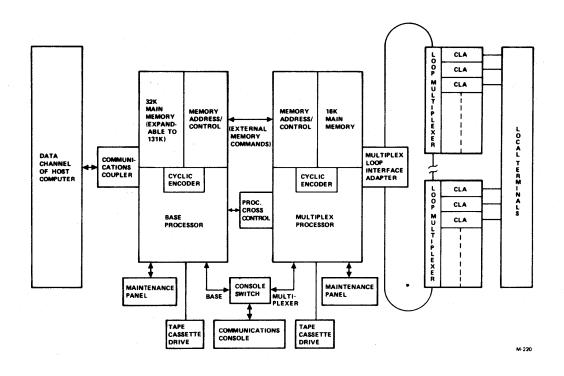

This section contains a description of the 2551-1, 2551-2, 2551-3, 2551-4, and 2552-2 NPUs and the major features and components of the systems. The NPU is a medium-size digital data communications system that serves as a front-end to a host computer and interfaces with a variety of terminal devices. The NPU can serve a CDC $^{\textcircled{\$}}$  6000, CYBER 170, CYBER 70, or a lower 3000 series host computer. Figures 1-1 and 1-2 are block diagrams of typical 2551-1, 2551-2, 2551-3, 2551-4, and 2552-2 NPU configurations.

#### NOTE

The 2552-2 NPU is no longer available as a CDC product. However, information is retained herein, for reference only.

# **MAJOR FEATURES**

The 2551-1 NPU configuration contains the following features:

- Single-bay cabinet

- Single processor

- 32K words MOS memory (expandable to 128 words)

- Interfaces up to 32 communications lines

- Expandable to 2551-2 configuration that provides interface with 32 additional communications lines

- Forms a front-end to a single CDC host computer when connected by appropriate coupler

The 2551-2 configuration contains the following features:

- Single-bay cabinet

- Single processor

- 32K words MOS memory (expandable to 128 words)

- Interfaces up to 64 communications lines

- Expandable to 128 lines with addition of a loop multiplexer expansion cabinet that contains two loop multiplexer expansion chassis and communications line adapters

- Forms a front-end to a single CDC host computer when connected by appropriate coupler.

60472800 D

The 2551-3 NPU configuration contains the following features:

- Single-bay cabinet

- Single processor

- CYBER Coupler

- 64K words MOS memory (expandable to 128 words)

- Interfaces up to 32 communications lines

- Expandable to 2551-4 configuration that provides interface with 32 additional communications lines

- Forms a front-end to a single CDC host computer

The 2551-4 configuration contains the following features:

- Single-bay cabinet

- Single processor

- CYBER Coupler

- 96K words MOS memory (expandable to 128 words)

- Interfaces up to 64 communications lines

- Expandable to 128 lines with addition of a loop multiplexer expansion cabinet that contains two loop multiplexer expansion chassis and communications line adapters

- Forms a front-end to a single CDC host computer

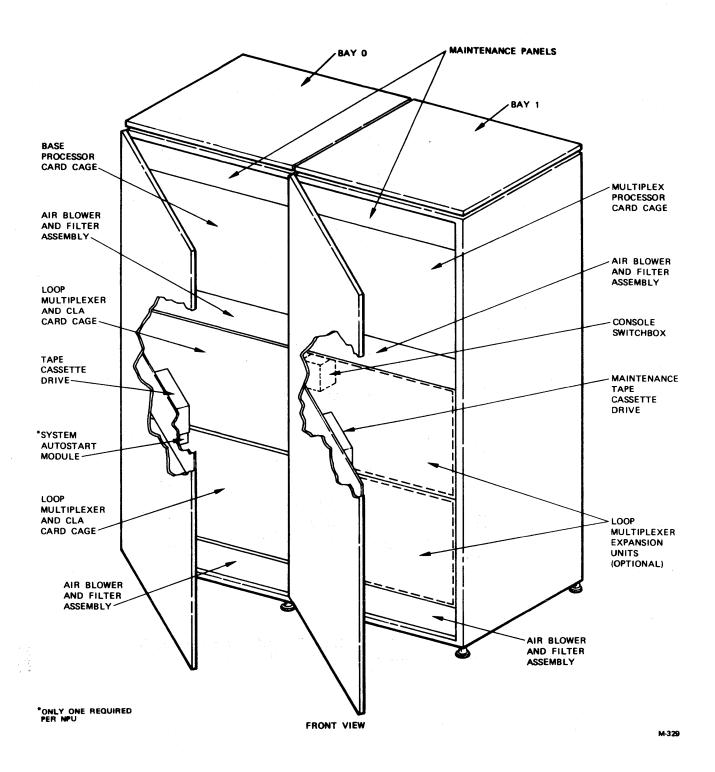

Figure 1-1. 2551-1, 2551-2, 2551-3, 2551-4 Network Processor Unit Block Diagram

Figure 1-2. 2552-2 Network Processor Unit Block Diagram

The 2552-2 NPU configuration contains the following features:

- Double-bay cabinet

- Two processors

- Base processor contains 32K word MOS memory (expandable to 128K words)

- Multiplex processor contains 16K words MOS memory (expandable but usually not required)

- Interfaces up to 64 communications lines

- Expandable up to 128 lines with addition of two loop multiplexer expansion chassis and communications line adapters

- Forms front-end to a single CDC host computer with one host coupler, or two hosts with addition of a second host coupler

# NETWORK COMMUNICATIONS SYSTEM CONCEPTS

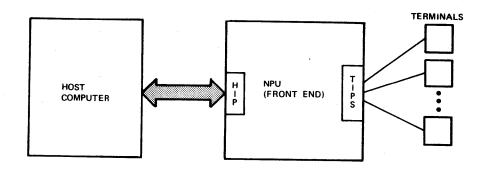

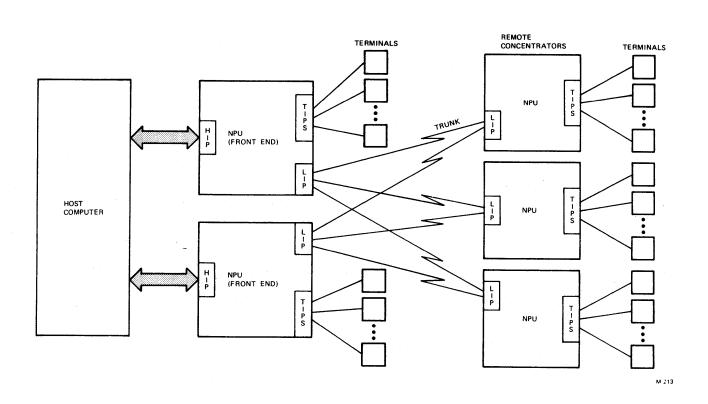

The NPU operates as an integral part of a CDC network communications system (NCS). This system provides for the vast majority of communications (message handling) tasks to be handled at intermediate points between the message source and destination. This is accomplished by NPUs, also called nodes, which are designed to allow almost any combination of functions to be attended by hardware common to all nodes.

The NPU acts as an intermediate communications handler or communications node between a host computer and the user terminals. Figure 1-3 illustrates a single node system. The NPU is limited to two host computers. The host computer can have two or more NPU front-ends and can be extended by common trunk lines linked to remote nodes, which act as message concentrators from multiterminal interfaces to form a multinode system. See figure 1-4.

The network communications system concept allows open-ended linkage of the host computer and front-end nodes and a variety of geographically distributed remote NPUs. In the multinode system one host is designated to maintain circuits that control the entire network communications process.

# PHYSICAL DESCRIPTION

The following is a brief physical description of the major equipments in each NPU configuration. For a detailed physical description, refer to the appropriate equipment maintenance manual. See preface.

60472800 D

Figure 1-3. Single Node System, Block Diagram

Figure 1-4. Multinode System (One Local and Three Remote Nodes), Block Diagram

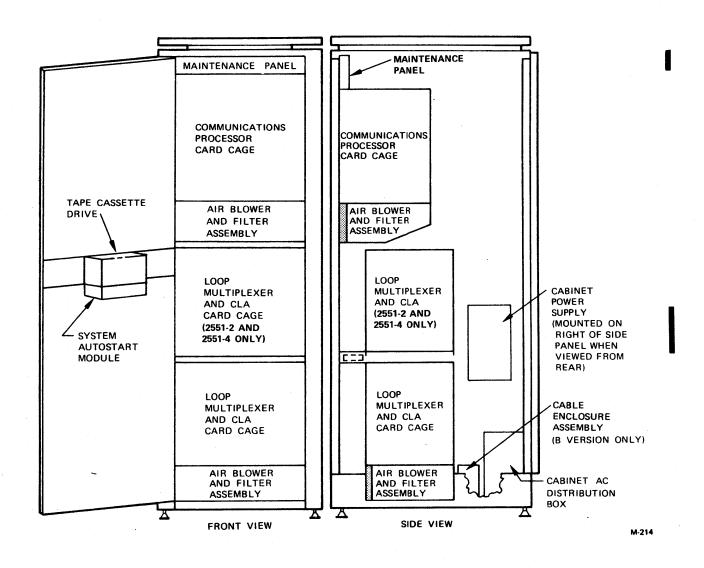

### 2551-1 NPU EQUIPMENT

The 2551-1 NPU (figure 1-5) consists of NPU cabinet assembly DW117-A, processor AA135-A, and 32K MOS Memory AT241-B. The DW117-A contains the basic cabinet, loop multiplexer and CLA card cage, multiplex loop interface adapter (MLIA), cyclic encoder, power supply, and associated signal and power cabling. Also, a maintenance panel, power distribution box, cable enclosure assembly, and two air blower and filter assemblies are included with the cabinet. The processor is contained in the communications processor card cage, which also provides the card slots for the 32K MOS memory, cyclic encoder, and MLIA cards. One loop multiplexer card and from 1 to 16 CLA cards can be located in the loop multiplexer and CLA card cage.

#### 2551-2 NPU EQUIPMENT

The 2551-2 NPU (figure 1-5) contains the same components as the 2551-1 and includes an additional loop multiplexer and CLA card cage. The NPU can service up to 64 CLAs in the system; thus, the 2551-2 NPU has double the line capacity of the 2551-1. The B version cabinet contains the same electromagnetic interference shielding as the 2551-1.

### 2551-3 NPU EQUIPMENT

The 2551-3 NPU (figure 1-5) consists of NPU cabinet assembly DW117-A, processor AA135-B, 64K MOS memory AT241-B, and CYBER coupler DK106-C. The DW117-A contains the basic cabinet, loop multiplexer and CLA card cage, multiplex loop interface adapter (MLIA), cyclic encoder, power supply, and associated signal and power cabling. Also, a maintenance panel, power distribution box, cable enclosure assembly, and two air blower and filter assemblies are included with the cabinet. The processor is contained in the communications processor card cage, which also provides the card slots in the 64K MOS memory, cyclic encoder, MLIA, and CYBER coupler cards. One loop multiplexer card and from 1 to 16 CLA cards can be located in the loop multiplexer and CLA card cage.

#### 2551-4 NPU EQUIPMENT

The 2551-4 NPU (figure 1-5) contains the same components as the 2551-3 and includes an additional loop multiplexer and CLA card cage. The NPU can service up to 64 CLAs in the system; thus, the 2551-4 NPU has double the line capacity of the 2551-3. The cabinet has EMI shielding.

60472800 D

# **Communications Processor**

The processor card cage used in 2551-1, 2551-2, 2551-3, and 2551-4 NPUs contains the following functional elements:

- Microprocessor

- Main memory

- Maintenance panel interface

- Cyclic encoder

- Input/output Teletype interface

- Tape cassette controller (optional)

- Multiplex loop interface adapter

- CYBER Coupler (2551-3 and 2551-4 only)

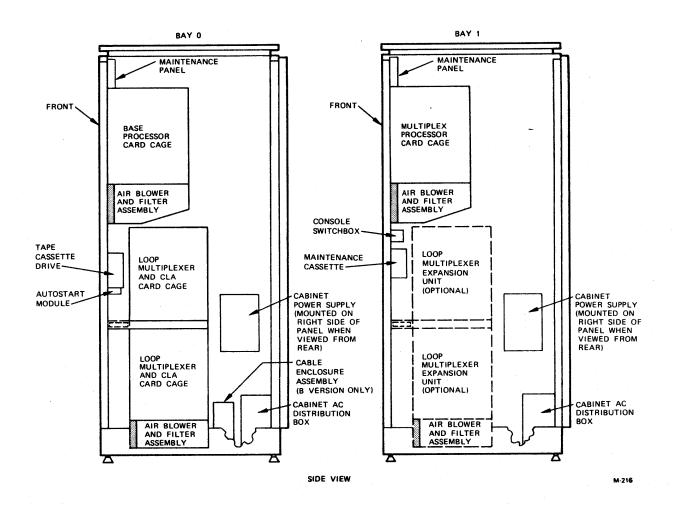

### 2552-2 NPU EQUIPMENT

The 2552-2 NPU contains two processor card cages mounted in a double-bay cabinet. See figures 1-2 and 1-6. The base processor card cage is located in bay 0 and the multiplex processor card cage is in bay 1. Each bay contains identical cabinet wiring, power supplies, air blower and filter assemblies, and tape cassette drives. The 2552-2 NPU contains two loop multiplexers and communications line adapter card cages located in bay 0. Two optional card cages can be installed in bay 1 to expand communications line capacity up to 128 lines.

### **Base Processor**

The base processor card cage contains those elements required to perform the main data storage and processing functions. It includes the 32K-word memory. The base processor components are as follows:

- Microprocessor

- Main memory

- Maintenance panel interface

- Cyclic encoder

- Input/output TTY interface

- Tape cassette controller

Figure 1-5. 2551-1, 2551-2, 2551-3, and 2551-4 Network Processor Unit Front and Side Views

Figure 1-6. 2552-2 Network Processor Unit (Sheet 1 of 2)

Figure 1-6. 2552-2 Network Processor Unit (Sheet 2 of 2)

### **Multiplex Processor**

The multiplex processor card cage contains the elements required to perform the primary command processing functions and interfaces with the input and output loops. This processor has only a 16K-word memory and includes the multiplex loop interface adapter circuit cards. The multiplex processor components are as follows:

- Microprocessor

- Main memory

- Maintenance panel interface

- Cyclic encoder

- Input/output TTY interface

- Tape cassette controller

- Multiplex loop interface adapter

#### Cross-Control and Console Switch

The multiplex processor contains a cross-control module to generate interrupts and a console switch, which allows the NPU operator to select either the base or multiplex processor.

# COMMUNICATIONS CONSOLE

A communications console is required to operate the NPU and may be either a teletype (TTY) or cathode-ray tube (CRT) conversational terminal. The console is not supplied with the standard NPU but is selected according to the user application. Among the CDC products, the user may select a 722-10, 752 Display Terminal, or a 1711-4, -5 (KSR TTY), or a 1713-4, -5 (AST TTY) terminal as the communications console.

# COMMUNICATIONS COUPLER

The communications couplers used in conjunction with the 2551-1, 2551-2, 2551-3, 2551-4, and 2552-2 NPU configurations can be one or two of the following types:

- CYBER communications coupler to interface with CYBER series 70/170 or 6000 series host computers.

- 6671/6676 emulation coupler to interface with CYBER SERIES 70/170 or 6000 series host computers, permitting the NPU to emulate a 6671 or 6676 Data Set Controller.

- 3000L coupler to interface with 3000L series host computers

### MULTIPLEX SUBSYSTEM

The multiplex subsystem consists of the communications line adapters, the loop multiplexer, and the multiplex loop interface adapter.

# Communications Line Adapters

Each communications line adapter circuit card contains two complete, independent circuits. The communications line adapter is installed in the loop multiplexer and communications line adapter card cage. The card cage accommodates up to 16 communications line adapter cards which can service a maximum of 32 communications lines.

### Loop Multiplexer

The loop multiplexer is located in the loop multiplexer and communications line adapter card cage. Each loop multiplexer can accommodate 32 communications line adapters (16 communications line adapter cards) and can be series-connected to a maximum of eight loop multiplexers per loop for up to 254 communications line adapters.

# Multiplex Loop Interface Adapter

The multiplex loop interface adapter consists of three circuit cards located in the communications processor card cage.

#### MAINTENANCE PANEL

A maintenance panel is located above the processor in each bay. See figures 1-5 and 1-6. Controls and indicators on the panel can be used by the operator to monitor the status of the system.

# **CASSETTE TAPE DRIVE (OPTIONAL)**

A cassette tape drive is mounted on the door of each cabinet bay. See figures 1-5 and 1-6. The drive operates at a speed of 7.5 inches (190 mm) per second and recording density is 800 bits per inch (31.5 bits per mm). Rewind speed is approximately 50 inches (1270 mm) per second. The drive uses Phillips style cassettes.

#### SYSTEM AUTOSTART MODULE

The system autostart module is an assembly attached to the bottom of the cassette tape drive. See figures 1-5 and 1-6.

### **POWER SUPPLIES**

The NPU contains a power supply which provides -5 V dc, +5 V dc, -12 V dc and +12 V dc outputs. In the 2551-1, 2551-2, 2551-3, and 2551-4 NPUs the power supply is mounted internally on the right rear cabinet wall. See figure 1-5. In the 2552-2 NPU a power supply is mounted on the right rear cabinet wall of each bay. See figure 1-6.

### CABLING

Cabling for the NPU consists of signal cables and power cables. Refer to the 2550 series site preparation manual (see preface) for information on cabling.

# AIR BLOWERS AND FILTER ASSEMBLIES

Two air blowers and filter assemblies are provided with the basic NPU, and additional units are provided to accommodate extra processor and communications line extension units in the 2552-2 NPU. Refer to the 2550 series site preparation manual (see preface) for information on blower and filter assemblies.

# **EXPANSION SYSTEMS**

The NPU can be expanded for greater use by addition of optional standard products and upgrade kits, such as host couplers and communications line expansion units.

# **ELECTROMAGNETIC INTERFERENCE PROTECTION**

Electromagnetic compatibility measures are included in the NPU design. However, the NPU should not be located in the area of influence by strong, electromagnetic interferences (EMI) such as radar, X-ray equipment, radio signals, and electrical equipment. EMI protection is provided in the NPU cabinets (B version) by special shielding on the top and sides of the cabinets. A cable enclosure assembly is included to ensure the CYBER cable shields are grounded to the cabinet. Additional provisions for grounding communications line adapter cable shields consists of copper pressure strips that contact the cable shields at the bottom entrance to the cabinets.

# **FUNCTIONAL DESCRIPTION**

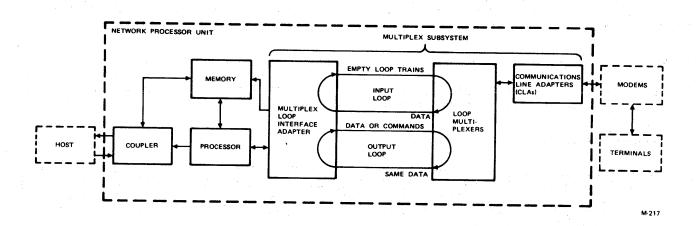

The major functional elements of the NPU are the processor and memory, the coupler, and the multiplex subsystem. See figure 1-7.

Figure 1-7. NPU Simplified Block Diagram

#### **PROCESSOR**

The processor, the primary element, contains firmware (microinstructions) and software (macroinstructions) to control the coupler and multiplex subsystem. Specific parameters of the NPU are listed in table 1-1.

#### NOTE

Macroinstructions are compatible with the CDC 1700 instruction repertoire and are stored in the processor main memory. Microinstructions control operation of the processor and are stored in the processor micromemory.

The processor has a direct memory access channel to the host computer for both input and output and for input only from the multiplex subsystem. The internal data channel is controlled mostly by firmware microinstructions and provides a high throughput of 10K characters per second between the multiplex subsystem and the processor. This forms the main access path to and from the processor and the multiplex subsystem.

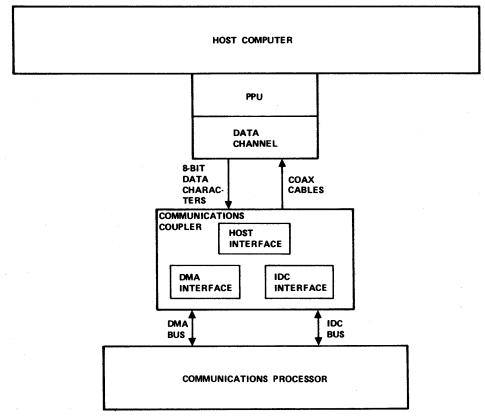

### COUPLER

The processor is linked to the host computer through the coupler which provides data paths and synchronizing clocks between the computers. The coupler provides the means for direct memory-to-memory transfers between the host and the base processor at a 1-MHz character rate. It is controlled by both host and NPU software commands. The coupler also enables the host to start, clear, and stop the processor. In addition to single-word transfers, the coupler provides block data transfers in either direction (e.g., downline load, upline dump) plus the ability to store and retrieve data via the standard buffer format. The coupler selected must be compatible with the host computer.

#### MULTIPLEX SUBSYSTEM

The multiplex subsystem transfers digital information on input and output loops between the processor and the terminals. The input and output loops are two high-speed serial data transmission links. The multiplex feature allows transmission of messages from many communications lines over one circuit by sampling data (up to 8 bits per byte) on each line and assembling the data in a data train (loop cells).

Data transferred to and from the loops via the multiplex loop interface adapter are checked for accuracy by use of a cyclic redundancy checksum generated by the cyclic encoder. The cyclic redundancy checksum characters are used in error code generation and verification of both incoming and outgoing data to the terminals.

The multiplex loop interface adapter receives commands from the processor and accepts or provides parallel data to a circulating buffer in the memory. The input loop to the multiplex loop interface adapter carries input data and status as well as output data demand signals from the communications line adapters to the memory. The output loop carries output data and supervision commands to the communications line adapters.

# TABLE 1-1. NPU FUNCTIONAL CHARACTERISTICS

#### Main Memory

Capacity: (standard)

2551-1 - 32K words (32 768) AT241-B

2551-2 - 32K words (32 768) AT241-B

2551-3 - (2) 32K words (32 768) AT241-B

2551-4 - (3) 32K words (32 768) AT241-B

2552-2 - 48K words (49 152) AT241-B and AT275-B

Maximum capacity can be extended to 131 072 (128K) words for all configurations by the addition of CDC 2554-32 (AT241-B) 32K MOS memory expansion modules. If a 2554-16 (AT275-B) module is fitted, as in the 2552-2 configuration, it must be replaced by a 2554-32 (AT241-B) module.

Word length: 16 bits (plus a parity bit and protect bit)

Read-Access Time: 550 nanoseconds

Memory Addressing Modes: 8

Memory Word and Region Protection

Memory Parity Protection

Direct Memory Access (4 users)

External CPU Access

Automatic Interfaced Refresh

# Micromemory (2K RAM)

Capacity: 3K (3072) words (2K (2048) words read/write; 1K (1024) words read only emulator)

Word Length: 32 bits

Read-Access Time: 168 nanoseconds

### Micromemory (8K RAM)

Capacity: 8K (8192) words (7K (7168) words read/write:

1K (1024 words read-only emulator)

Word Length: 32 bits

Read-Access Time: 168 nanoseconds

#### TABLE 1-1. NPU FUNCTIONAL CHARACTERISTICS (Contd)

#### Interrupts

Macrointerrupts: 16 (corresponds to CDC 1700 interrupts)

Microinterrupts: 16 (internal)

Registers: 256 words

Files: File 1, 256 words; File 2, 32 words

The loop multiplexer accepts input data in parallel from the communications line adapters and serializes the data. The loop multiplexer also assembles loop cells from the output loop and presents the data in parallel form to the communications line adapters.

The communications line adapters provide the interface between the loop multiplexer and the terminals with or without a modem. On input from the terminals, the communications line adapters are serial-to-parallel converters, assembling serial data at the signal rate of the terminal, and transferring the data to the loop multiplexer in 8-bit bytes. On output, the communications line adapters are parallel-to-serial converters, receiving the data characters in bytes of 8 bits from the loop multiplexer and outputting them serially at the signal rate of the terminal.

# **OPERATING PROGRAMS AND DIAGNOSTICS**

NPU operating programs and diagnostic test programs are loaded from cassette tapes. The cassette tape controller serves as the access path for all data transfer between the tape drive and the processor. The cassette tape drive can be used as a standard peripheral or as a deadstart device.

When the NPU is program loaded and placed on-line, the NPU operation is initiated and controlled by the host. NPU operation is monitored by the host and by internal checks within the NPU. Processor operation can be interrupted at any time of error detection within the multiplex subsystem or on command from the host.

The system autostart module monitors the program status. If a program error is detected, a system master clear is issued, and the program tape is automatically reloaded. Then the system restarts and runs until another error is detected and the reload cycle automatically repeats. If no error is detected, the autostart reload operation remains inhibited.

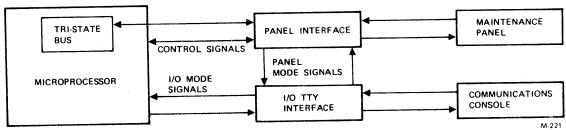

The operator can access the NPU via the console (TTY or CRT) or by the maintenance panel to perform all common computer control panel functions. The panel interface card in the processor provides the interface between the operator panels and the processor main bus and internal processor control signals. Operations performed at the maintenance panel are local and those performed at the console are remote.

60472800 D 1-17

The 2552-2 NPU with dual processors provides better response time and greatly increased message handling capability to accommodate any user requirements. See figure 1-2. In the dual processor configuration, the processors share the NPU functions which allows different operations to be performed simultaneously. The base processor performs host signal interface operations, main data storage, and processing functions. The multiplex processor performs the primary command functions to control the multiplex subsystem operations.

#### MAINTENANCE

Maintenance and troubleshooting procedures for the NPU consist of a series of diagnostic test procedures which are performed on-line and off-line. On-line diagnostics are performed to determine whether the fault is with the vendor equipment, such as communications drives, modems, and input power, or with CDC equipment.

The objective of the off-line diagnostics is to allow fault isolation for all components. Fault detection is performed automatically by the diagnostic test program. Fault isolation is performed by the operator observing the results of the tests and determining, with the aid of charts, which circuit card is at fault.

# **COMMUNICATIONS SOFTWARE**

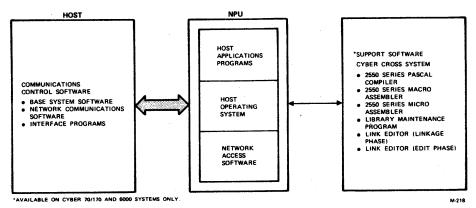

The communications software is divided into three major groups as follows:

- Host Processor Network: Access Software

- 255X Network Processor Unit: Communications Control Software

- 255X Support Software

The following paragraphs briefly describe the various functions and relationships of the software groups. See figure 1-8.

### **HOST SOFTWARE**

The host operating system software controls the operations of a network operating system. The network access software (also resident in the host) serves as the interface between the host operating system software and the communications control software resident in the NPU. The host applications programs process messages passed to them and also pass messages to the network to be distributed to terminals.

# COMMUNICATIONS CONTROL SOFTWARE

The communications control software consists of base system software, network communications software, and interface programs. Available programs are as follows:

- Communications Control Program (CCP), NOS Version, used on CYBER 6000 and 70/170 computers.

- Communications Control INTERCOM (CCI), NOS/BE Version, used on CYBER 70/170 computer.

- Communications Control Master (CCM), used on 3000L computers.

For detailed information on the communications control software, refer to the applicable software reference manual.

### **Base System Software**

The base system software, which includes the multiplex subsystem, comprises those elements of the communications control software that are required for

Figure 1-8. Communications Software Overview

all system applications. The base system software contains subroutines that provide:

- NPU resource management

- Memory space management

- Control of the local NPU console

- Facilities to add line-dependent or terminal dependent logic at various software levels.

- Multiplex subsystem elements operating with NPU hardware to establish data and control paths for information exchange between the communications lines and appropriate protocol handlers (terminal interface program) within the NPU.

#### Network Communications Software

The network communications software accomplishes the following:

- Network routing and service message processing to establish line and terminal configuration.

- Reports alarm conditions and error and traffic statistics.

- Provides common support modules for terminal interface programs.

# Interface Programs

The interface programs provide the logical interaction necessary to transmit information to and from the NPU.

- Host Interface Program (HIP) accomplishes block data transfers with the host computer, monitors the host for failure and recovery, and reports host status to the NPU.

- Terminal Interface Programs (TIPs) provide the logic to control the line and terminal protocol and to ensure orderly transmission (in either direction) between the NPU and the connected terminal. These programs transform data between terminal protocols and block protocols.

- Link Interface Program (LIP) accomplishes data transfers between a local and a remote NPU. A special protocol (CDCCP) is used for these transfers. The LIPs are responsible for transforming data between CDCCP and block protocols at both ends of the trunk.

### SUPPORT SOFTWARE

The CCP support software (CYBER CROSS System) includes a PASCAL compiler, two assemblers, and system generation programs for the development and maintenance of CCP software. The CYBER CROSS System executes only on the CYBER 70/170 series computer systems and executes under control of NOS as an application system. Refer to applicable documents for information on support software on the CYBER CROSS System.

This section contains a functional description of the NPU subsystems and components.

# NPU MAIN DATA PATHS

The NPU receives input data from the modems and terminals, via the communications line adapters and loop multiplexer, and transforms the input data to a format compatible with the internal processing of the NPU. See figures 2-1 and 2-2. The multiplex loop interface adapter controls the data flow from the loop multiplexer and supplies data to the memory buffers under firmware and internal interrupt control. The cyclic encoder generates a cyclic redundancy checksum to verify accuracy of the data. The processor removes all protocol and language-dependent characters of the modified input data and provides storage and access to the data under firmware control. The communications coupler interfaces the host and serves as a transmittal device by moving NPU data in buffer format to the host memory. Conversely, the coupler transports data from the host to the NPU and stores it in the internal format used by the NPU processor. Data flow through the NPU from the communications line adapters in the direction of the host is referred to as inbound traffic. Data flow from the host through the NPU to the communications line adapters is outbound traffic.

The tape cassette is used for autoloading NPU microprograms and diagnostic test programs. The communications console allows operator remote control over the display of the NPU processing data and commands. The console normally is the primary NPU control, but may be used for maintenance or troubleshooting of the NPU. During normal operation the NPU operates unattended.

The maintenance panel gives the operator, programmer or maintenance personnel direct control over the display of NPU processing and commands from the NPU. The maintenance panel is used primarily for troubleshooting the NPU system or examining elements of the operating program.

The dual processor NPU functions the same as the single processor NPU except for expanded equipment and capabilities. In general, the main difference is that the single processor functions are divided between two processors for increased performance. In the following paragraphs the single processor system and the dual processor system are described separately.

# **BASIC EMULATION CONCEPTS**

The 1700 series of computers, including the 1704 described in appendix A, consists of special-purpose hardware designed to perform the tasks indicated by the repertoire of instructions. The 255X system contains a totally different processor which responds to a series of instructions at the micro level. Microcode is a basic and flexible form of control, exercising and sequencing the flow between the various hardware elements and the operating

60472800 C 2-1

Figure 2-1. 2551-1, 2551-2, 2551-3, and 2551-4 NPU Major Functional Areas and Data Paths

Figure 2-2. 2552-2 NPU Major Functional Areas and Data Paths

modes of these same elements. Instructions used by the microprocessor are stored as 32-bit words in the read/write and/or read-only portions of micromemory. Real-time operations are accomplished by executing microcode stored in the read/write portion of micromemory. These real-time operations are concerned primarily with time-critical tasks, such as character traffic on the communications lines.

Other, nonreal-time operations are written in 1700-style code stored in the processor main memory. These are executed through emulation. By this means, instructions are fetched from main memory one at a time, the various bit structures in an instruction are analyzed for content, converted into one or more microinstructions capable of performing the operation requested, and executed. The operation then continues in this manner, producing the same results as would be accomplished by the code executing in a 1700 series machine. To permit this emulation, a firmware instruction repertoire is included, stored in read/write memory. This emulation operation becomes practical, even though several microinstructions are required for each microinstruction (1700), because the microprocessor is significantly faster and simpler. Since the repertoire of instructions to be emulated is determined simply by the contents of a read-only memory, addition of a series of instruction set enhancements becomes practical.

# **INTERRUPT SYSTEM**

While emulating the 1700 computer, the NPU microprocessor firmware (controlware) program actually accesses, under microprogram control, all 32 of the interrupts. As a byproduct of this processing, the 16 external interrupts are made available to the macroinstruction while the 16 internal interrupts are available only to the microinstruction, either within the emulation controlware package or the special communications firmware. It is more accurate to define the interrupts as macro- and microinterrupts rather than external and internal interrupts, respectively.

#### **MACROINTERRUPTS**

Macrointerrupts are associated with external I/O devices and perform traditional tasks such as flagging end-of-operation status and fault conditions. Microinterrupts, however, perform the important internal tasks of establishing priorities and queuing up tasks and in general providing communication and signaling between the various firmware/controlware routines. At the microinstruction level, there is no executive or monitor or scheduler; these functions must be performed by the microinterrupt priority and processing system.

## **MICROINTERRUPTS**

In general, the microinterrupt system responds to three groups of interrupts: emulator interrupts, special firmware interrupts, and high-priority data such as multiplex loop interface adapter microinterrupts of which two are available at the microinterrupt level. Processing is typically split into low- and high-priority tasks so that time-critical tasks are handled immediately with subsequent processing set up for deferred processing in response to a lower priority microinterrupt.

60472800 C 2-3

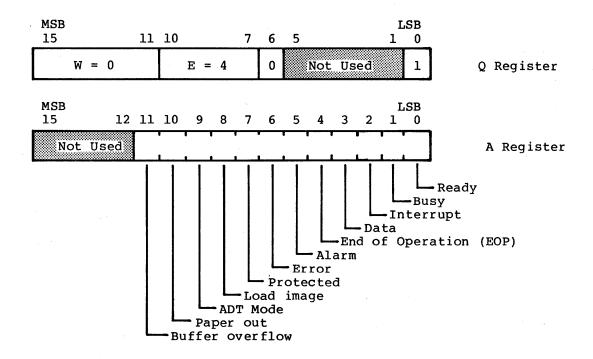

#### Status/Mode and Interrupt Bits

The 1700 computers use interrupt registers in which pulse-type interrupts are stored until processed or cleared. Because of the emulation nature of interrupt handling, the NPU processor uses a different approach. The macrointerrupt and microinterrupt registers operate on a direct current rather than pulse basis. An external device must hold the interrupt line active until the interrupt has been serviced. The interrupt registers are used to prevent the interrupt status from changing while they are being interrogated. As such, the interrupt registers are clocked as a part of the reading process. The signals are stored in the status mode register. The bits of this register can be wired so that they can be set via external means and cleared under program control.

Microprocessing is organized so that certain response time standards are established for macrointerrupt response time. This is necessary since activating a macrointerrupt does not interrupt the processor but merely sets a bit in an interrupt register which can then be read and acted upon by the microprogramming. Only through the action of the firmware/controlware is the effect of the macrointerrupt felt. Because of this, two service standards are provided:

- Emulation controlware examines the state of the interrupt line through the mask during the read-next-instruction phase of each emulated macroinstruction. When an active interrupt is found (and the interrupt system enabled), normal macroprogram execution is delayed and macrointerrupt instruction routines are executed.

- Special firmware routines are organized so that every 20 microseconds (or less) the interrupt system is interrogated and, if an interrupt is found, processing is delayed.

Users can expect an interrupt latency time of no more than 20 microseconds (for the highest priority interrupt). This accommodates 56-kilobit communications lines.

Besides storing events, status/mode bits also serve another special function of driving special control lines for external I/O operation. Thus I/O timing, such as strobing and handshaking, is driven under firmware/controlware control rather than by dedicated hardware.

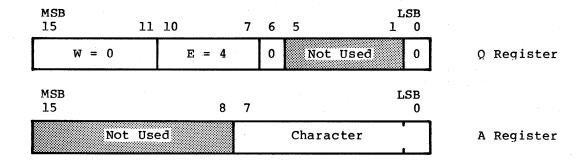

#### Automatic Data Transfer Mode

Devices capable of automatic data transfer mode operations require both macrointerrupts and microinterrupts. Such devices include the tape cassette and the optional card reader and line printer. Each time a character is available and required during automatic data transfer operations, the microinterrupt line is activated. (For circuit simplicity the macrointerrupt line can also be raised, but the microinterrupt will be seen first by the controlware and it is therefore the one upon which action will be taken.) Thus, character transfer is handled at the microlevel.

### Multiplex Loop Interface Adapter Interrupts

Owing to their time-critical nature, two multiplex loop interface adapter interrupts are available as microinterrupts. However, these microinterrupts

are not available to macroprograms such as MSMP17/ODS diagnostics. Thus, to provide for diagnosability, these two interrupts are parallel-wired as both macrointerrupts and microinterrupts. The third multiplex loop interface adapter is of routine priority and is available as a macrointerrupt only.

#### Real-Time-Clock Interrupts

Every 3.3 milliseconds a real-time-clock microinterrupt occurs. Via program control, this interrupt is counted down n times (n is a programmable limit). Only when n microinterrupts have occurred is a macrointerrupt generated. Thus, real-time-clock microinterrupts occur every 3.3 milliseconds and real-time-clock macrointerrupts occur every 3.3 divided by n milliseconds.

### Interrupt Holding Registers

The interrupt holding registers are designated as Il and I2. Register Il provides internal microinterrupts; register I2 provides external macrointerrupts. Each register contains 16 bits, and the bits are numbered from left to right as follows:

| Register | Bit Numb | oers |

|----------|----------|------|

| Il       | Il00 to  | 1115 |

| 12       | T200 to  | T215 |

The priority levels of the interrupt bits are in numerical order. Bit I100 has the highest priority in register I1; bit I115 has the lowest priority. Similarly, bit I200 has the highest priority in register I2, and bit I215 has the lowest. The bit assignments for registers I1 and I2 are listed in table 2-1.

# NPU COMPONENTS FUNCTIONAL DESCRIPTION

#### SINGLE PROCESSOR

The single processor provides buffer storage for input and output data, storage and execution of various firmware and software programs, and provides the hardware interfaces for both the host computer and the multiplexing subsystem. For a detailed functional description, refer to the Basic Microprogrammable Processor Hardware Maintenance Manual (see preface).

The functional elements of the single processor are as follows:

- Microprocessor

- Panel/Console Interface

- I/O Subsystem

- Cyclic Encoder

- Main Memory

The main data paths for the single processor configuration are shown in figure 2-1.

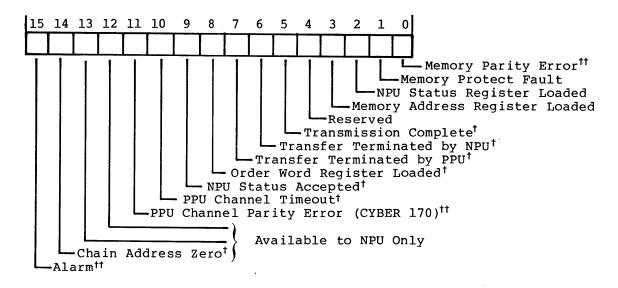

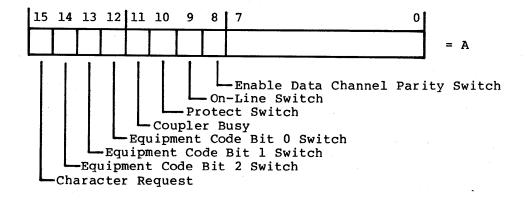

TABLE 2-1. INTERRUPT BIT ASSIGNMENTS

| Register |                                                  |

|----------|--------------------------------------------------|

| Bit      | Function                                         |

|          | Tunocton                                         |

| 1100     | Multiplex Loop Interface Adapter                 |

| 1101     | Communications Console (TTY or CRT)              |

| 1102     | Multiplex Loop Interface Adapter                 |

| 1103     | (unassigned)                                     |

| 1104     | 2571/2570 Line Printer Controller                |

| 1105     | (unassigned)                                     |

| 1106     | (unassigned)                                     |

| 1107     | Tape Cassette Controller                         |

| 1108     | Real-Time Clock                                  |

| 1109     | (unassigned)                                     |

| I110     | (unassigned)                                     |

| I111     | 2571/2572 Card Reader Controller                 |

| I112     | 1700 Emulator                                    |

| I113     | 1700 Emulator                                    |

| I114     | 1700 Emulator                                    |

| I115     | 1700 Emulator                                    |

| 1200     | Power Fail/Memory Parity                         |

| 1201     | Communications Console                           |

| 1202     | Multiplex Loop Interface Adapter                 |

| 1203     | Multiplex Subsystem Priority 3 (source is SM205) |

| 1204     | 2571/2570 Line Printer Controller                |

| 1205     | CYBER Coupler 2 (2558-1)                         |

| 1206     | CYBER Coupler                                    |

| 1207     | Tape Cassette Controller                         |

| 1208     | Real-Time Clock                                  |

| 1209     | 1732/608-609 Mag Tape Controller (QSE)           |

| 1210     | 1740-1742 Line Printer Controller (QSE)          |

| 1211     | 2571/2572 Card Reader Controller                 |

| 1212     | Multiplex Loop Interface Adapter                 |

| 1213     | Multiplex Loop Interface Adapter                 |

| 1214     | (unassigned)                                     |

| 1215     | Macro Breakpoint                                 |

|          | -                                                |

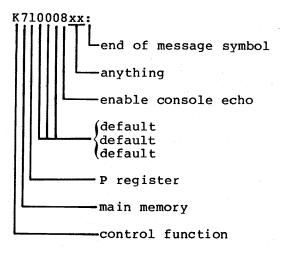

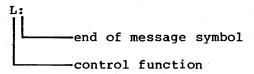

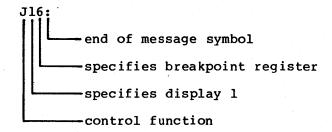

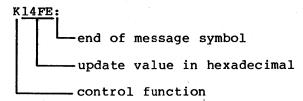

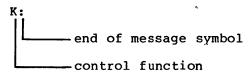

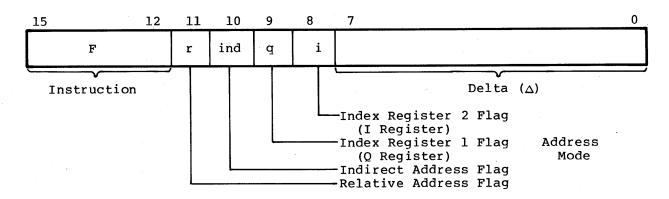

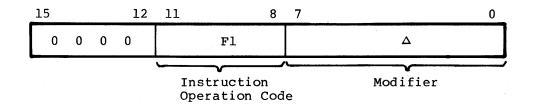

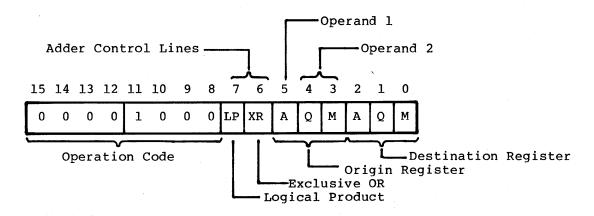

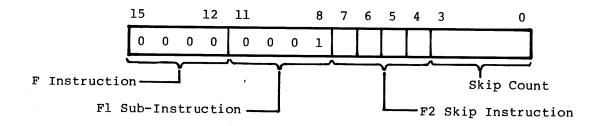

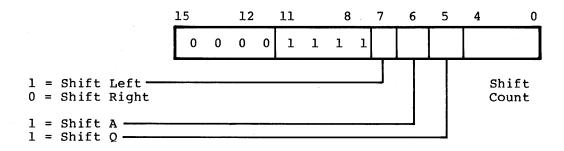

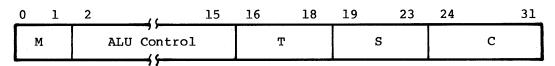

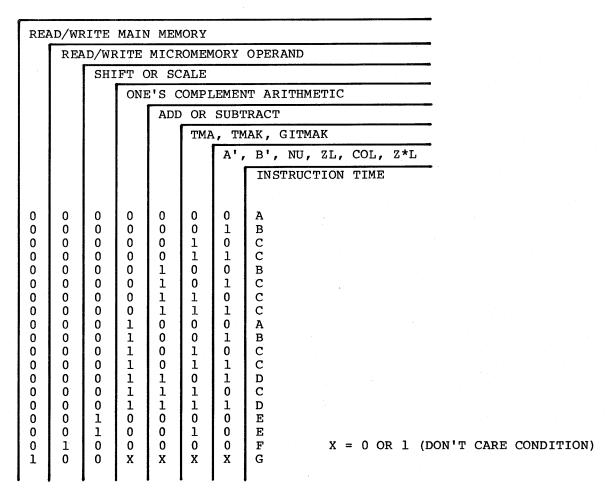

### Microprocessor