# ETA SYSTEMS

ETA10 Instruction Set Reference Manual

**ETA10** Computer System

PUB-1264

A Control Data Company

ETA Systems, Incorporated 1450 Energy Park Drive St. Paul, MN 55108

.

# **ETA**SYSTEMS

# ETA10 Instruction Set Reference Manual

PUB-1264 Rev. A March, 1989

**ETA10** Computer System

The items listed below are referenced in this document and are names, products, or trademarks associated with the following companies:

ETA is a trademark of ETA Systems, Incorporated.

Disclaimer:

ETA<sup>TM</sup> Systems, Incorporated reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should consult ETA Systems to determine whether any such changes have been made. (At non-U.S. installations, the reader should consult the local marketing representative.) This manual may not be reproduced and is intended for the exclusive use of ETA Systems' customers.

The terms and conditions governing the sale of ETA Systems hardware products and the licensing and use of ETA Systems software consist solely of those set forth in the written contracts between ETA Systems and its customers. No statement contained in this publication, including statements regarding capacity, suitability for use, or performance of products, shall be considered a warranty by ETA Systems for any purpose or give rise to any liability of ETA Systems.

In no event will ETA Systems be liable for any incidental, indirect, special, or consequential damages (including lost profits) arising out of or relating to this publication or the information contained in it, even if ETA Systems has been advised, knew, or should have known of the possibility of such damages.

The copyright laws prohibit the copying of this manual without the written consent of ETA Systems. Copying, under the law, includes translating into another language or format.

Prepared by: ETA Systems, Incorporated Technical Communication Dept. 1450 Energy Park Drive St. Paul, MN 55108

© 1989 by ETA Systems, Incorporated. All rights reserved.

# **Revision Record**

Documents that are complete and approved for release carry an alphabetic code. The first release is identified as revision A, the second as revision B, and so on.

| Document | Date |  |

|----------|------|--|

| Revision |      |  |

|          |      |  |

Rev. A March 1989

# **Changes in This Revision**

Revision A is the first release of this manual.

# **Table of Contents**

| About This Do   | cument xv                                                                                                                                                               |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Purpose xv                                                                                                                                                              |

|                 | Intended Audience xv                                                                                                                                                    |

|                 | How This Document Is Arranged xv                                                                                                                                        |

|                 | How to Use This Document xvii                                                                                                                                           |

|                 | Conventions Used in This Document xvii                                                                                                                                  |

| Introduction    |                                                                                                                                                                         |

|                 | Introduction to the ETA10 Hardware 1-2                                                                                                                                  |

|                 | Operations Performed by ETA10 Instructions                                                                                                                              |

|                 | ETA10 Instruction Formats 1-3                                                                                                                                           |

|                 | ETA10 Instruction Functions and Operands                                                                                                                                |

|                 | ·                                                                                                                                                                       |

| Introduction to | the ETA10 Instruction Set Chapter 2                                                                                                                                     |

|                 | Hardware for Machine Instructions                                                                                                                                       |

|                 | Central Processing Units 2-2                                                                                                                                            |

|                 | Input/Output Units and the Service Unit                                                                                                                                 |

|                 | Memories                                                                                                                                                                |

|                 | Instruction Operations                                                                                                                                                  |

|                 | Scalar and Vector Operations                                                                                                                                            |

| ~               | Memory Transfer                                                                                                                                                         |

|                 | Monitor Operations                                                                                                                                                      |

|                 | Accessing special fulpose registers $\dots \dots \dots$                 |

|                 |                                                                                                                                                                         |

|                 | Bit and Byte Operations 2-5                                                                                                                                             |

|                 | Bit and Byte Operations2-5Branching and Indexing2-5Floating-Point Arithmetic2-5                                                                                         |

|                 | Bit and Byte Operations2-5Branching and Indexing2-5Floating-Point Arithmetic2-5Machine Instruction Formats2-6                                                           |

|                 | Bit and Byte Operations2-5Branching and Indexing2-5Floating-Point Arithmetic2-5Machine Instruction Formats2-6Instruction Function Field2-12                             |

|                 | Bit and Byte Operations2-5Branching and Indexing2-5Floating-Point Arithmetic2-5Machine Instruction Formats2-6Instruction Function Field2-12Instruction Subfunctions2-12 |

|                 | Bit and Byte Operations2-5Branching and Indexing2-5Floating-Point Arithmetic2-5Machine Instruction Formats2-6Instruction Function Field2-12                             |

| Introduction to the H | ETA10 Instruction Set Continued |

|-----------------------|---------------------------------|

|                       | Broadcast Operands              |

| ETA10 Instruction D   | escriptions Chapter 3           |

| Instr                 | ruction Description Formats     |

| 00 .                  |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

| 11 .                  |                                 |

| 12 .                  |                                 |

| 13 .                  |                                 |

| 14 .                  |                                 |

| 15 .                  |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

|                       |                                 |

| ETA10 Instruction | Descriptions                            | Continued |

|-------------------|-----------------------------------------|-----------|

| 26                |                                         | 3–35      |

| 27                |                                         | 3-36      |

| 28                |                                         | 3-37      |

| 29                |                                         |           |

| 2A                |                                         |           |

| 2B                |                                         |           |

| 2D<br>2C          |                                         |           |

|                   |                                         |           |

| 2D<br>2E          |                                         |           |

|                   |                                         |           |

| 2F                |                                         |           |

| 30                | ••••••••••••••••••••••••••••••••••••••• |           |

| 31                | ••••••••••••••••••••••••••••••••••••••• |           |

| 32                | ••••••••••••••••••••••••••••••••••••••• |           |

| 33                | ••••••••••••••••••••••••••••••••••••••• |           |

| 34                |                                         | 3–48      |

| 35                |                                         | 3–49      |

| 36                |                                         | 3-50      |

| 37                |                                         | 3–52      |

| 38                |                                         | 3-52      |

| 39                |                                         |           |

| 3A                |                                         |           |

| 3B                |                                         |           |

| 3D<br>3C          |                                         |           |

| 3D                |                                         |           |

| 3D<br>3E          |                                         |           |

|                   |                                         |           |

| 3F                |                                         |           |

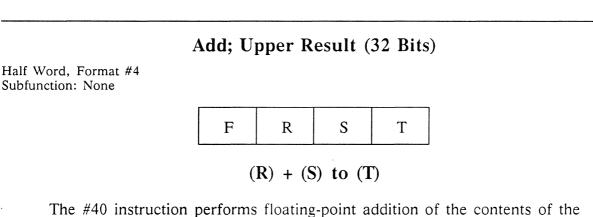

| 40                | ••••••••••••••••••••••••••••••••••••••• |           |

| . 41              | ••••••••••••••••••••••••••••••••••••••• |           |

| 42                |                                         |           |

| 44                | ••••••••••••••••••••••••••••••••••••••• |           |

| 45                | ••••••••••••••••••••••••••••••••••••••• |           |

| 46                |                                         | 3–59      |

| 48                |                                         | 3–59      |

| 49                | ••••••••••••••••••••••••••••••••••••••• | 3-60      |

| 4B                | ••••••••••••••••••••••••••••••••••••••• | 3-60      |

| 4C                |                                         |           |

|                   | )                                       |           |

|                   | · · · · · · · · · · · · · · · · · · ·   |           |

| 4E<br>4F          |                                         |           |

| 50                |                                         |           |

|                   | ······································  |           |

|                   |                                         |           |

| 52                | ••••••••••••••••••••••••••••••••••••••• | 3-03      |

|                   |                                         |           |

| ETA10 Instruction | Descriptions                            | Continued |

|-------------------|-----------------------------------------|-----------|

| 53                |                                         | 3-66      |

| 54                |                                         |           |

| 55                |                                         |           |

| 56                |                                         |           |

| 57                |                                         |           |

| 58                |                                         |           |

| 59                |                                         |           |

|                   | ······································  | -         |

| 5E                |                                         |           |

|                   | · · · · · · · · · · · · · · · · · · ·   |           |

|                   | )                                       |           |

|                   |                                         |           |

|                   | }                                       |           |

| 5F                |                                         | -         |

| 60                |                                         |           |

| 61                | ••••••••••••••••••••••••••••••••••••••• |           |

| 62                |                                         |           |

| 63                |                                         |           |

| 64                |                                         |           |

| 65                |                                         | -         |

| 66                | ••••••••••••••••••••••••••••••••••••••• |           |

| 67                | ••••••••••••••••••••••••••••••••••••••• | 3-80      |

| 68                |                                         |           |

| 69                |                                         | 3-81      |

| 6E                | }                                       | 3-82      |

| 60                | ۹<br>/                                  | 3-82      |

| 6E                | )                                       | 3–83      |

| 6E                | ]                                       | 3-83      |

| 6F                | ۱                                       | 3-84      |

| 70                |                                         | 3-85      |

| 71                |                                         | 3-86      |

| 72                |                                         | 3-87      |

| 73                |                                         | 3–88      |

| 74                |                                         | 3–89      |

| 75                |                                         | 3-90      |

| 76                |                                         | 3-91      |

| 77                |                                         | 3-92      |

|                   |                                         |           |

|                   |                                         |           |

|                   | ·····                                   |           |

|                   |                                         |           |

|                   | · · · · · · · · · · · · · · · · · · ·   |           |

|                   | )                                       |           |

| /L                | /                                       |           |

| ETA10 Instruction Descriptions | Continued |

|--------------------------------|-----------|

| 7E                             | 3–97      |

| 7F                             | -         |

| 80                             |           |

| 81                             |           |

| 82                             |           |

| 83                             |           |

| 84                             |           |

| 85                             |           |

| 86                             |           |

| 87                             |           |

| 88                             |           |

| 89                             |           |

| 8A                             |           |

|                                |           |

| 8B                             |           |

| 8C                             |           |

| 8F                             |           |

| 90                             |           |

| 91                             |           |

| 92                             |           |

| 93                             |           |

| 94                             |           |

| 95                             |           |

| 96                             |           |

| 97                             |           |

| 98                             |           |

| 99                             |           |

| 9A                             |           |

| 9B                             |           |

| 9C                             |           |

| 9D                             |           |

| A0                             |           |

| A1                             |           |

| A2                             |           |

| A4                             |           |

| A5                             |           |

| A6                             |           |

| A8                             |           |

| A9                             | 3-144     |

| AB                             | 3-146     |

| AC                             | 3-148     |

| AF                             | 3-150     |

| B0                             | 3-152     |

| ETA10 Instruction | Descriptions   | Continued |

|-------------------|----------------|-----------|

| В                 | 1              | 3-154     |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 |                |           |

|                   |                |           |

| B                 |                |           |

| -                 | 4              |           |

|                   |                |           |

| B                 |                |           |

| B                 |                |           |

| B                 | 2              |           |

| B                 |                |           |

| В                 |                |           |

| В                 |                |           |

| B                 |                |           |

| В                 | 7              |           |

| В                 |                |           |

|                   | Α              |           |

|                   | B              |           |

|                   | С              |           |

| B                 |                |           |

|                   | Ε              |           |

|                   | F              |           |

|                   | 0              |           |

|                   | 1              |           |

|                   | 2              |           |

|                   | 3              |           |

|                   | 4              |           |

|                   | 5              |           |

|                   | <sup>1</sup> 6 |           |

|                   | 7              |           |

|                   | 8              |           |

| C                 | 9              | 3–206     |

.

| ETA10 Instru | ction Descriptions Co                     | ntinued                                             |

|--------------|-------------------------------------------|-----------------------------------------------------|

|              | CA<br>CB<br>CC<br>CD<br>CE<br>CF<br>D0    | 3-208<br>3-209<br>3-210<br>3-210<br>3-211           |

|              | D1<br>D4<br>D5<br>D8<br>D9                | 3-213<br>3-214<br>3-215<br>3-216<br>3-218           |

|              | DA<br>DB<br>DC<br>DF<br>F0<br>F1          | . 3-221<br>. 3-222<br>. 3-223<br>. 3-224            |

|              | F2<br>F3<br>F4<br>F5<br>F6                | . 3-226<br>. 3-227<br>. 3-228<br>. 3-229<br>. 3-230 |

|              | F7                                        | . 3-232<br>. 3-233<br>. 3-235<br>. 3-237            |

| Appendix A:  | FE<br>FF<br>Instructions by Function Code |                                                     |

| Appendix B:  | Instructions By Mnemonic                  | B-1                                                 |

|              | Instructions With Sign Control            |                                                     |

| Appendix E: | Instruction Termination Rules                                                                                  | E-1               |

|-------------|----------------------------------------------------------------------------------------------------------------|-------------------|

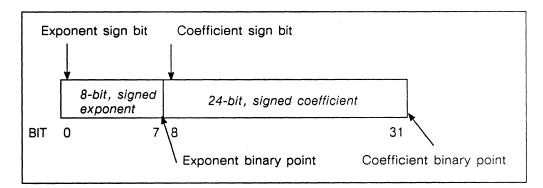

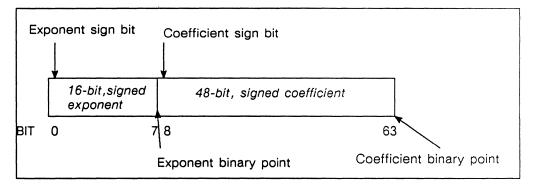

| Appendix F: | Floating-Point Operations                                                                                      | F-1               |

|             | Floating-Point Format                                                                                          |                   |

|             | Two's Complement Notation                                                                                      |                   |

|             | Floating-Point Arithmetic                                                                                      |                   |

|             | Right Normalization                                                                                            |                   |

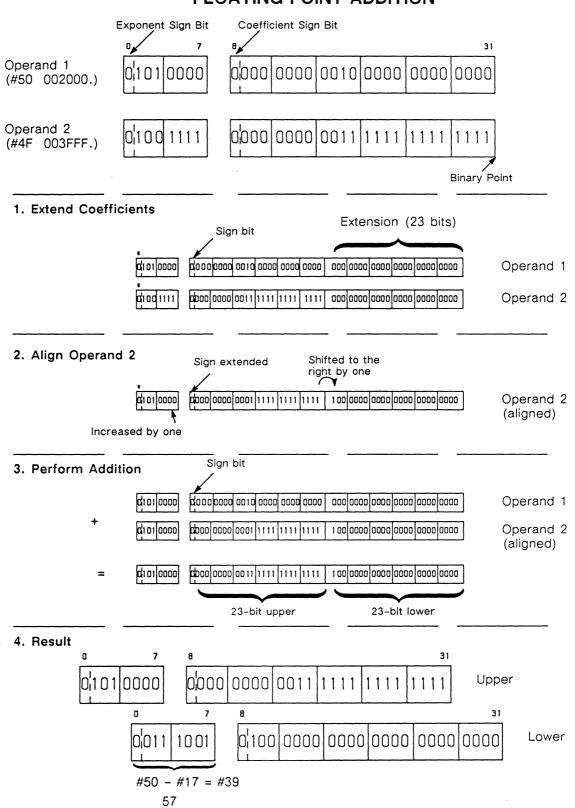

|             | Floating-Point Addition                                                                                        |                   |

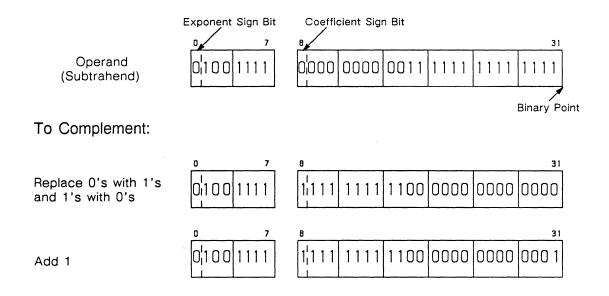

|             | Floating-Point Subtraction                                                                                     | F-8               |

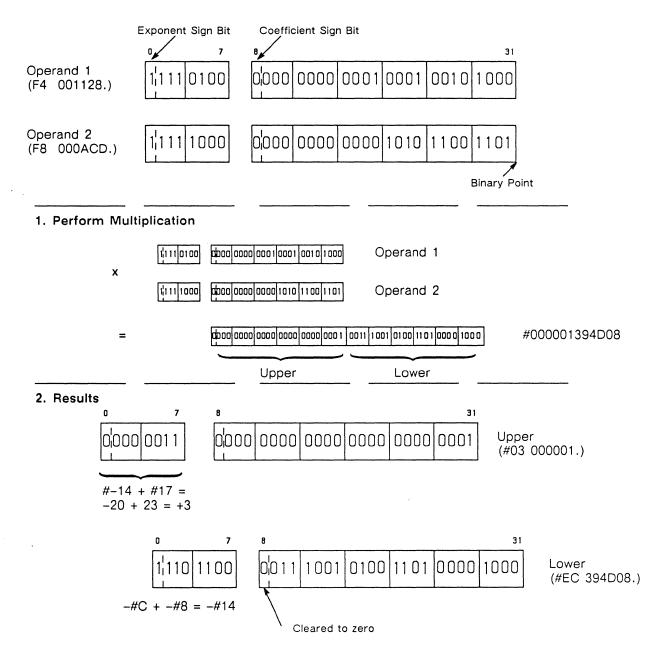

|             | Floating-Point Multiplication                                                                                  |                   |

|             | Floating-Point Division                                                                                        |                   |

|             | Normalized Upper Results                                                                                       |                   |

|             | Double-Precision Results                                                                                       |                   |

|             | Floating-Point Square Root Operations                                                                          |                   |

|             | Significant Results                                                                                            |                   |

|             | Floating-Point Comparison Rules                                                                                |                   |

|             | Indefinite Operand(s)                                                                                          |                   |

|             | Operand(s) Not Indefinite or Machine Zero                                                                      |                   |

|             |                                                                                                                | 1 17              |

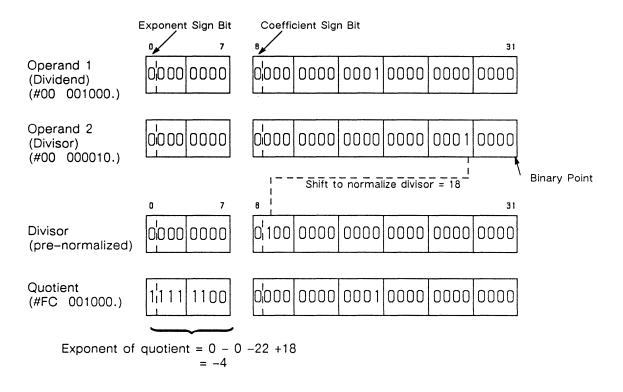

| Appendix G: | The Data Flag Register                                                                                         | G-1               |

|             | Data Flag Register FormatData FlagsThe Mask FieldProduct Field BitsData Flag Branch Enable Bit                 | G-2<br>G-2<br>G-2 |

|             | •                                                                                                              |                   |

|             | Causing a Data Flag Branch                                                                                     |                   |

| ,           | Data Flag Register Bit Assignments                                                                             |                   |

|             | Free Data Flags Instructions Affecting Data Flag Register Bits                                                 |                   |

|             | Instructions Affecting Data Mag Register Dits                                                                  | 0-0               |

| Appendix H: | Addressing Vector Operands                                                                                     | H-1               |

| <i>.</i>    | Addressing Vector Source OperandsSource Operand OffsetsAddressing Vector Result OperandsResult Operand Offsets | H-1<br>H-2        |

| Appendix I: | Illegal Instructions                                                                                           | I-1               |

|             | Type One Illegal Instructions                                                                                  | I-1               |

|             | Type Two Illegal Instructions                                                                                  | I-1               |

| Glossary                  | Glossary-1 |

|---------------------------|------------|

| Referenced Documents List | Ref.Doc1   |

| Index                     | Index      |

#### List of Figures

| Figure | Title                                                | Page   |

|--------|------------------------------------------------------|--------|

| 2-1.   | Components of an ETA10 central processing unit (CPU) | . 2-2  |

| 3–1.   | Structure of Register R for the #04 Instruction.     | . 3–5  |

| 3–2.   | Structure of Register R for the #08 Instruction      | . 3–8  |

| 3-3.   | Register T after an #0E instruction.                 | . 3–12 |

| 3-4.   | Structure of Register R for the #0F instruction      | . 3–15 |

| 3-5.   | Bit Compress Operations.                             | . 3–19 |

| 3-6.   | Bit Merge Operations.                                | . 3–20 |

| 3-7.   | Bit Mask Operations.                                 | . 3–22 |

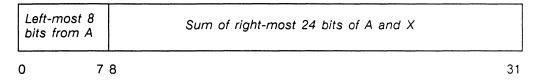

| F-1.   | A 32-Bit Floating-Point Number's Format.             |        |

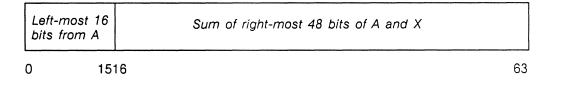

| F-2.   | A 64-Bit Floating-Point Number's Format.             | . F-2  |

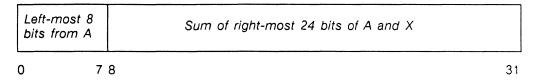

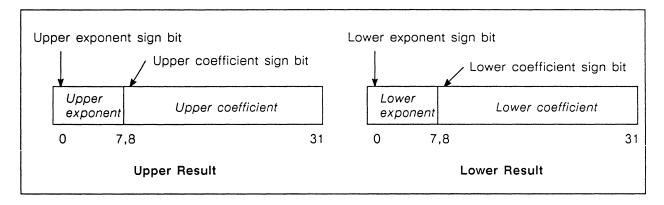

| F-3.   | Floating-Point Result Format for Add, Subtract, and  |        |

|        | Multiply Operations.                                 | . F-4  |

| F-4.   | Floating–Point Addition                              | . F-7  |

| F-5.   | To perform floating point subtraction,               |        |

|        | complement the subtrahend, then add                  | . F-9  |

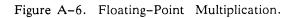

| F-6.   | Floating–Point Multiplication.                       | . F-11 |

| F-7.   | Floating-Point Division.                             |        |

| G-1.   | Data Flag Register Format.                           | . G-1  |

|        |                                                      |        |

#### List of Tables

| Table | Title                                                             | Page    |

|-------|-------------------------------------------------------------------|---------|

| 2-1.  | Instruction Qualifiers.                                           | . 2–13  |

| 2-2.  | Qualifiers and valid G-bit settings for vector operations.        | . 2-14  |

| 3-1.  | Vector instructions that can be used in a Link operation.         | 3-69    |

| 3–2.  | Valid Combinations for Linked Vector Instructions.                | . 3-70  |

| 3-3.  | Logical Operations on vector A and B elements.                    | . 3–128 |

| 3-4.  | Logical Functions on X and Y to Produce Order Vector Z            | . 3–130 |

| 3-5.  | Results of the logical operations performed by the source vectors | . 3–131 |

| 3–6.  | Logical Functions on X and Y to Produce Order Vector Z            | . 3–132 |

| 3–7.  | Results of the logical operations performed by the source vectors | . 3–133 |

| 3–8.  | Logical Functions on X and Y to Produce Order Vector Z            | . 3–134 |

| 3-9.  | Results of the logical operations performed by the source vectors | . 3–135 |

| 3–10. | Logical Functions on X and Y to Produce Order Vector Z            |         |

| 3–11. | Results of the logical operations performed by the source vectors |         |

| 3–12. | Logical Functions on X and Y to Produce Order Vector Z            |         |

| 3–13. | Results of the logical operations performed by the source vectors |         |

| 3–14. | Logical Functions on X and Y to Produce Order Vector Z            | . 3–140 |

| Table          | Title                                                                                                                       | Page  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|-------|

| 3-15.          | Results of the logical operations performed by the source vectors                                                           | 3-141 |

| 3–16.<br>3–17. | Logical Functions on X and Y to Produce Order Vector Z<br>Results of the logical operations performed by the source vectors |       |

| 3–18.          | Logical Functions on X and Y to Produce Order Vector Z                                                                      |       |

| 3–19.          | Results of the logical operations performed by the source vectors                                                           |       |

| 3-20.          | Logical Functions on X and Y to Produce Order Vector Z                                                                      |       |

| 3-21.          | Results of the logical operations performed by the source vectors                                                           |       |

| 3–22.<br>3–23. | Logical Functions on X and Y to Produce Order Vector Z<br>Results of the logical operations performed by the source vectors |       |

| 3-23.          | Logical Functions on X and Y to Produce Order Vector Z                                                                      |       |

| 3-24.          | Results of the logical operations performed by the source vectors                                                           |       |

| A-1.           | Instructions by Function Code                                                                                               |       |

| B-1.           | Instructions by Mnemonic                                                                                                    | B-1   |

| C-1.           | Instructions for which sign control is valid                                                                                |       |

| D-1.           | Instructions Allowing Broadcasting.                                                                                         |       |

| E-1.           | Instruction Terminating Conditions                                                                                          |       |

| G-1.           | Data Flag Bit Settings                                                                                                      |       |

| G-3.<br>G-4.   | Definitions For Free Data Flag Bits 53–55 Data Flag Bits set by function codes                                              |       |

| U-4.<br>I-1.   | The Domain Package's Illegal Instruction Mask                                                                               |       |

#### Purpose

This document is a reference manual for the ETA10 instruction set. It is **not** intended for use as a guide for assembly language programmers. (Refer to the **Referenced Documents List** for the title of manuals that contain assembly language information.) The manual is designed to provide quick access to reference information about each instruction's format and function.

Refer to PUB-1005, *ETA10 System Reference Manual*, for detailed information about ETA10 operations.

# **Intended Audience**

The manual's audience includes:

- Programmers in higher-level languages such as FORTRAN, C, and CYBIL, who may be reading assembler output from programs

- Programmers who may be writing Q8 calls in FORTRAN programs

- Site analysts

- On-site engineers

#### How This Document Is Arranged

There are 3 chapters and 9 appendices in this document.

Chapter 1, Introduction, covers the manual's contents, summarizing the information presented in each chapter.

Chapter 2, Introduction to the ETA10 Instructions, gives an overview of the ETA10 hardware, and summarizes the types of operations the machine can perform. The thirteen instruction formats are laid out, with an explanation of designator meanings for each format. Instruction subfunctions are also described.

Chapter 3, Instruction Descriptions, lists each instruction in hexadecimal function code order. The description covers the

instruction's function, valid qualifiers and G-bit settings, with an explanation of the operations performed. See Appendix B for a listing of the instructions in mnemonic order.

Appendix A, Instructions by Function Code, contains each instruction organized by function code, with its mnemonic, format type, the G-bit settings, and a brief definition of its operation.

Appendix B, Instructions by Mnemonic, contains each instruction organized by its mnemonic, function code, format type, the G-bit settings, and a brief definition of its operation.

Appendix C, Instructions Using Sign Control, is a table of instructions for which sign control is valid. The list is organized by function code. The sign control G-bits valid for each instruction are included in the list.

Appendix D, Instructions Allowing Broadcasting, lists, by function code, those instructions that can have broadcast A or B operands. The entry for each instruction includes whether A, B, or both can be broadcast.

Appendix E, Instruction Terminating Conditions, lists the terminating conditions for instructions, depending on their operands.

Appendix F, Floating-Point Operations, discusses how floating-point arithmetic is performed on the ETA10.

Appendix G, Data Flag Register Bit Settings, describes the function and format of the data flag register, with the meanings of bit settings that cause branching.

Appendix H, Vector Operands, explains how designators on vector instructions refer to registers that address source and destination vectors, and may specify offsets.

Appendix I, Illegal Instructions, describes which instructions are illegal and the consequences of issuing illegal instructions.

The **Glossary** provides definitions of important terms found in this manual.

# How to Use This Document

The information provided in this manual assumes that the reader is familiar with the information in PUB-1005, *ETA10 System Reference Manual*.

For an overview of topics presented in this manual, read chapter one. Read chapter two for details about instruction formats and designator meanings, and for information about instruction subfunctions, particularly for instructions that use sign control.

To find information about how a specific instruction operates, refer to the instruction's description in chapter three.

See the appendices for tables summarizing certain instruction characteristics, and for subjects referred to in the instruction descriptions, such as floating-point operations.

#### **Conventions Used in This Document**

Numbers that are represented in hexadecimal format in the text have a pound sign (#) as prefix.

The mnemonics used throughout this manual are those of the ETA System V assembler, "as".

# Introduction

# In This Chapter . . .

Chapter one introduces topics about the ETA10 and its instruction set that are covered in chapters two and three and the appendices of this manual. This chapter contains the following sections:

- Introduction to the ETA10 Hardware

- Operations Performed by ETA10 Instructions

- ETA10 Instruction Formats

- ETA10 Instruction Functions and Operands

### Introduction to the ETA10 Hardware

The ETA10 is a multi-processor system consisting of Central Processor Units (CPU), Input-Output Units (IOU), the Service Unit, and a hierarchical memory.

IOUs are processors responsible for data movement through the system. The Service Unit allows operators to interact with the ETA10, monitoring and controlling its functions.

CPUs interpret and execute instructions in the system. Each CPU has scalar and vector processors, 256 general purpose registers, and its own central processor (CP) memory.

The hierarchical memory system consists of three memories: shared memory (SM), the communication buffer (CB), and CP memory (CPM). Shared memory is a large auxiliary storage area for CP memory data, accessible from each CPU. Each CPU has its own CP memory, holding machine instructions and data. The communication buffer, a fast memory used for high-speed synchronization messages and semaphore operations, is accessible from each CPU.

The section "Hardware For Machine Instructions" in chapter 2 briefly describes the system components.

# **Operations Performed by ETA10 Instructions**

There are 216 hardware instructions performing:

- Scalar and vector operations

- Memory transfers

- Monitor operations

- Access to special purpose registers

- Bit and byte manipulation

- Branching and indexing

- Floating-point arithmetic

The section "Instruction Operations" in chapter 2 expands on these topics.

#### **ETA10 Instruction Formats**

Instructions are 32 or 64 bits long. There are 13 instruction formats, six of which are 64-bit instructions. The other seven formats are 32 bits long.

Each instruction word is divided into fields, bit groups that have instruction designators defining the function and operands. Each designator field is usually 8 bits long; some formats have designators that are longer.

The instruction formats and designator descriptions are laid out in the chapter 2 sections "Machine Instruction Formats" and "Instruction Designators".

#### **ETA10** Instruction Functions and Operands

All instructions have a function code, a number from #00 through #FF, that describes the operation performed. An instruction performs its function on operands. The number, format, and meaning of instruction operands depend on each instruction format.

Many instructions have an 8-bit subfunction field that further defines the function. For example, instructions performing vector operations have a subfunction field describing: operand size, whether a control vector acts on zeros or ones, the offset applied to the output field, whether operands are broadcast, and what sign control is valid.

"Instruction Command Field" in chapter 2 provides details about the function and subfunction fields.

Introduction

# Chapter 2

# **Introduction to the ETA10 Instruction set**

# In This Chapter . . .

Chapter two introduces the instruction set in terms of:

- Hardware for Machine Instructions

- Instruction Operations

- Machine Instruction Formats

- Instruction Designators

- Instruction Function Field

- Instruction Subfunctions

# Hardware for Machine Instructions

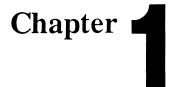

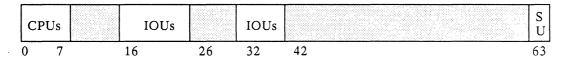

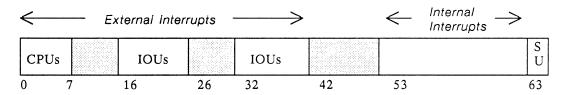

The ETA10 is a multiprocessor computer system, all processors having access to a large shared memory. All peripheral and network connections are through I/O units into shared memory. The components of an ETA10 central processing unit (CPU) are shown in figure 2–1, and introduced in the following sections. Refer to PUB-1005, *ETA10 System Reference Manual*, for a more detailed discussion of the ETA10 components.

Figure 2-1. Components of an ETA10 central processing unit (CPU).

#### **Central Processing Units**

A central processor unit (CPU) is the functional unit that interprets and executes instructions in the system. Each CPU has a central processor that operates independently, with its own scalar and double-pipelined vector processors, 256 general purpose 64-bit registers, and CP memory.

Each CPU is directly connected to shared memory and communication buffer ports for data transfers, and to the communication buffer for communication with other system processors. Maintenance Interface logic on each component allows the Service Unit to perform diagnostic and maintenance functions on each CPU.

A CPU runs in Job or Monitor mode. Modes change when the #09 exchange instruction executes. Some operating characteristics change, depending on the new mode. In Monitor mode, memory is physically addressed, register #03 points to the next branch instruction, and a #09 exchange to Job mode instruction is the last instruction executed. Job mode addresses memory virtually, the Invisible Package holds the next branch instruction, and any instruction can be the last executed before an exchange to Monitor mode occurs.

#### Input/Output Units and the Service Unit

An Input/Output Unit (IOU) is a specialized multi-processor, bus-connected computer system that contains a set of channel processors, 2 SIO lines, a data pipe controller, and global memory. IOUs are responsible for all data movement through the system to peripherals (including networks). They provide a means to attach peripheral devices and networks. A super-cooled ETA10 supports up to 18 IOUs.

The Service Unit (SU) provides access for operator display and control, system reconfiguration, and maintenance functions.

#### Memories

The ETA10's hierarchical memory system consists of CP memory, shared memory, and the communication buffer.

Each CPU has its own CP memory that holds machine instructions and data. CP memory is accessible by its central processor and the service unit, and under direction of the CPU, data can be transferred between CP memory and shared memory.

CP memory can be addressed two ways, virtually and physically. Virtual storage is divided into regions with contiguous address called 'pages.' Each page is identified by a unique virtual page address, and is associated with a unique physical page address while in CP memory.

Shared memory provides large bulk auxiliary storage for CP memory data. In super-cooled systems, access is via the shared memory interface (SMI) that supports up to 8 high-speed CPU ports, and 20 low-speed ports for IOU and SU connections. Data is transferred in blocks in half-word or full-word transfer units, ranging from a half-word to 64K words.

The communication buffer (CB) offers fast auxiliary storage, and is used to transmit high-speed synchronization messages and signals among the system components. In a super-cooled sytem, it can be divided into halves. Each half has its own interface that connects CB to 10 ports supporting up to 8 CPUs and the system's IOUs. Base/Limit/Access Pairs (BLAPs) denote the lowest numbered (base) and highest numbered (limit) CB address accessible by a CPU, and the operations that the CPU can perform on a range of CB addresses (access rights). The BLAPs are defined in domains in the CPU. Each domain has a set of 4 BLAPs, and can permit access to up to 4 ranges of CB memory at once.

## **Instruction Operations**

The ETA10's 216 instructions are model-independent. Instructions #0x through #7x are 32-bits long, and instructions #8x through #Fx are 64-bits long. The CPU's register file has registers that are available to the instructions as a source of operands, and as a destination for the result. Instructions perform a variety of operations; the main ones are summarized in this section.

#### **Scalar and Vector Operations**

Designators in scalar instructions point to registers that are sources and destinations. Registers contain the source operands and results.

The emphasis of the ETA10 is on vector operations. Vector instructions process vectors that stream data from source to destination locations in CP memory. Instruction designators point to registers that describe the sources and destinations; the sources and destinations are usually vectors, not single quantities. Vector instructions address vector operands and control how results are stored. Qualifiers modify the instruction's function.

#### **Memory Transfer**

All central processors can access the communication buffer to synchronize and coordinate system-wide programs. Instructions perform word and half word transfers between CB and the register file, semaphore post and wait operations, conditional word/half-word swap from CB to the register file, and conditional test and set with word/half word load from CB to register file.

Shared memory instructions manage data transfer between CP memory and shared memory by setting up a queue of information to transfer. Instructions build Transfer Request Blocks (TRBs) describing the type of transfer, set up an input queue in CP memory, and place TRBs awaiting execution in the input queue. The hardware reads TRBs off the input queue, and transfers the data until the queue is exhausted. After a TRB is read from CP memory, it may be placed in a completion queue residing in CP memory.

Shared memory instructions check for the transfer's completion status, and can also stop and restart I/O between TRBs to allow the input queue to be adjusted.

#### **Monitor Operations**

Instructions are available to perform privileged monitor operations unavailable in Job mode. These instructions function in Monitor mode only. Their operations include address translation, loading and storing associative registers, loading keys, and loading the Monitor Interval Timer.

#### **Accessing Special Purpose Registers**

Access to special purpose registers such as the Real-Time Clock, the Job Interval Timer, the Monitor Interval Timer, and the Breakpoint Register is possible using instructions. An important special purpose register is the Data Flag Register, which provides for status conditions, and causes an automatic branch to a special routine upon encountering certain operands, results, or conditions.

#### **Bit and Byte Operations**

Data can be manipulated by instructions at the bit and byte level. Bytes can be moved, loaded, and stored. Bit streams may be compressed, merged, masked, counted, and logically processed.

#### **Branching and Indexing**

Execution can proceed elsewhere in a program unconditionally or based on the result of a comparison. Single bit, 24– or 48-bit integer, 32– or 64-bit integer, 32– or 64-bit floating-point operands can be compared.

Special branching occurs when the #09 Exit Force Instruction passes control between Monitor and Job mode programs. The #36 (Branch or Forward Domain Change), and #17 (Backward Domain Change) instructions go between different domains of a job program.

Indexing is applied to addressing to load and store instructions, branch instructions, and string instructions.

#### **Floating-Point Arithmetic**

Instructions perform floating-point arithmetic on 32- or 64-bit floating-point numbers, returning upper, lower, normalized, and significant results. Numbers may also be compared according to floating-point comparison rules. Several instructions produce double-precision results. Appendix F explains floating-point arithmetic in detail.

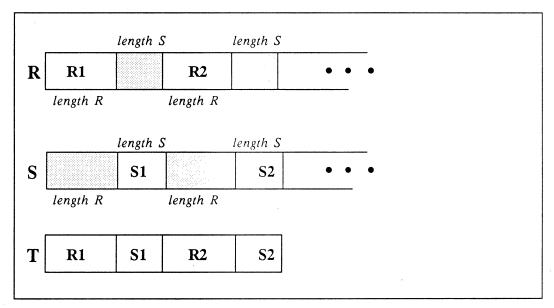

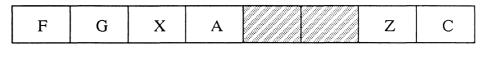

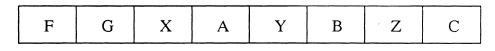

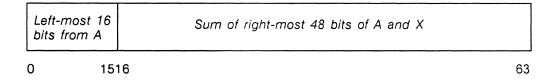

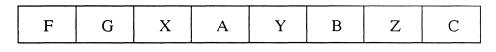

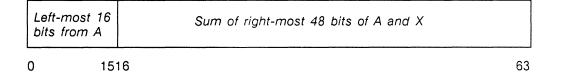

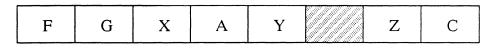

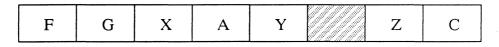

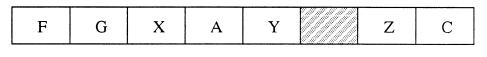

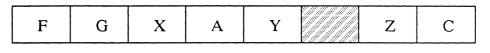

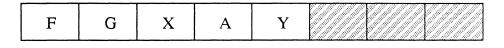

#### Machine Instruction Formats

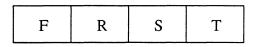

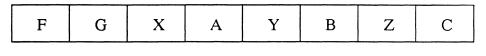

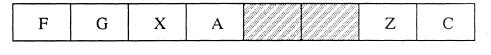

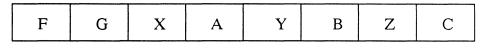

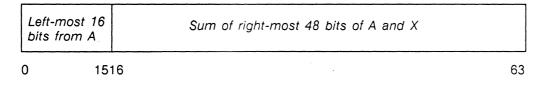

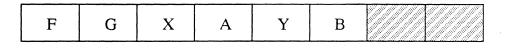

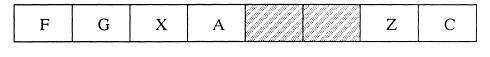

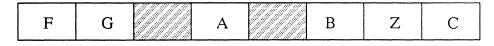

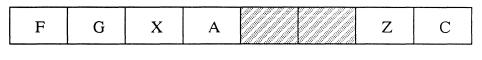

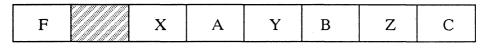

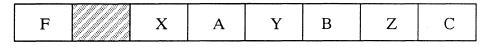

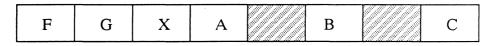

The ETA10 instructions have thirteen formats, numbered #1 through #D. Six formats are 64 bits long, and seven are 32 bits long. Each format is divided into bit groups that have assigned instruction designators. The thirteen formats are described below, with their designators labeled by letters (F, G, X, A etc.). Shaded areas are unused. The meaning of each designator is listed. All fields are 8 bits long unless otherwise specified.

|--|

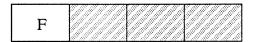

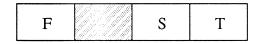

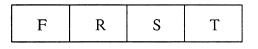

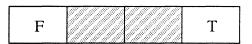

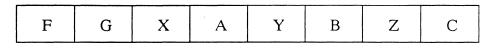

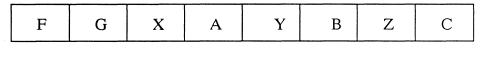

#### Format #1

- F Function code of instruction.

- G An 8-bit designator that specifies certain subfunction conditions. Subfunctions include length of operands (32- or 64-bit), normal or broadcast source vectors, and so on. The number of bits used in the G designator varies with instructions.

- X Specifies a register that contains the offset or index for vector or string source field A.

- A Specifies a register that contains a field length and base address for the corresponding source vector or string field.

- Y Specifies a register that contains the offset or index for vector or string field B.

- B Specifies a register that contains a field length and base address for the corresponding source vector or string field.

- Z Specifies a register that contains the base address for the order vector used to control the result vector in field C.

- C Specifies a register that contains the field length and base address for storing the result vector or string field. C+1 specifies a register containing the offset for C and Z vector fields. If the C+1 designator is used, the C designator must specify an even-numbered register.

| F G X A | Y | В | z | С |

|---------|---|---|---|---|

|---------|---|---|---|---|

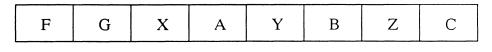

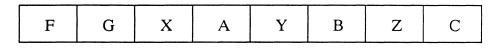

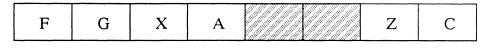

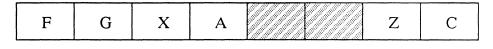

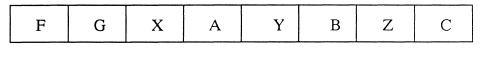

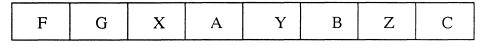

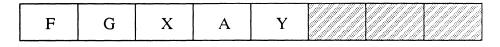

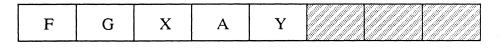

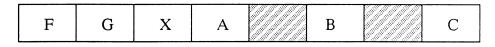

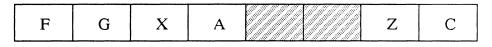

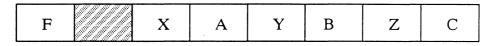

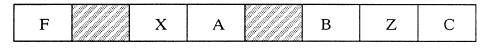

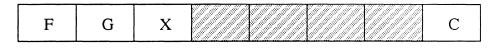

Format #2

- F Function code of instruction.

- G An 8-bit designator that specifies certain subfunction conditions. Subfunctions include length of operands (32- or 64-bit), normal or broadcast source vectors, and so on. Number of bits used in the G designator varies with instructions.

- X Specifies a register that contains length and base address for order vector corresponding to source sparse vector field A.

- A Specifies register containing the base address for a source sparse vector field.

- Y Specifies a register that contains the length and base address for the order vector corresponding to source sparse vector field B.

- B Specifies register containing the base address for a source sparse vector field.

- Z Specifies a register that contains the length and base address for the order vector corresponding to result sparse vector field C.

- C Specifies a register that contains the field length and base address for storing the result vector or string field.

| F G X A | Y B | Z C |

|---------|-----|-----|

|---------|-----|-----|

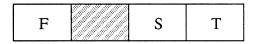

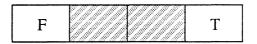

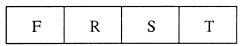

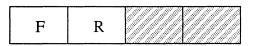

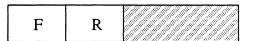

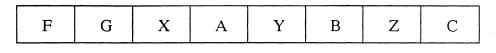

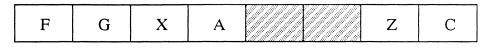

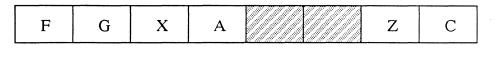

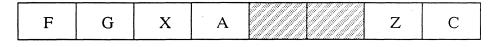

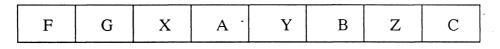

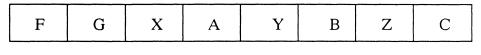

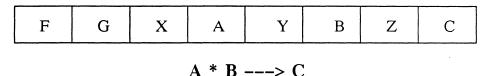

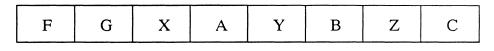

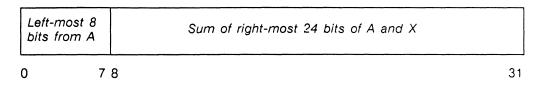

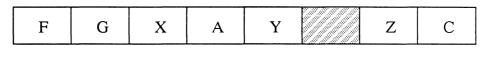

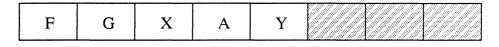

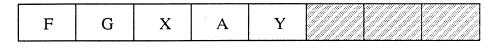

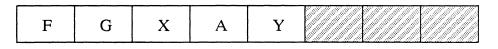

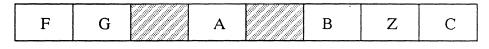

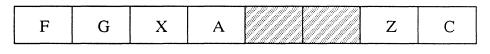

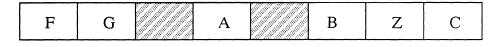

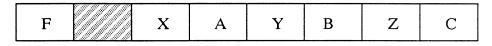

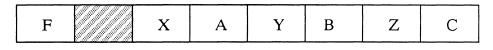

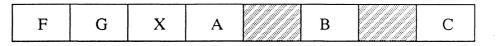

Format #3

- F Function code of instruction.

- G An 8-bit designator that specifies certain subfunction conditions. Subfunctions include length of operands (32- or 64-bit), normal or broadcast source vectors, and so on. The number of bits used in the G designator varies with instructions. For some format 3 instructions, the G designator is used as an immediate byte I8.

- X Specifies a register that contains the offset or index for vector or string source field A.

- A Specifies a register that contains a field length and base address for the corresponding source vector or string field.

- Y Specifies a register that contains the offset or index for vector or string field B.

- B Specifies a register that contains a field length and base address for the corresponding source vector or string field.

- Z Specifies a register that contains the index for result field C.

- C Specifies a register that contains the field length and base address for storing the result vector or string field.

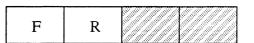

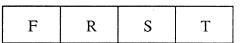

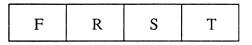

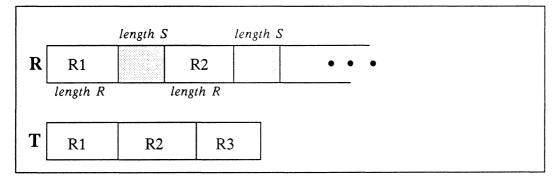

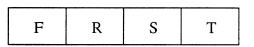

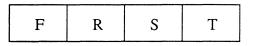

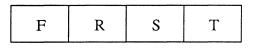

| F R | S | т |

|-----|---|---|

|-----|---|---|

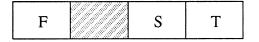

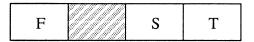

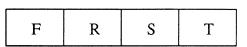

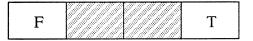

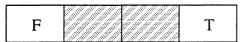

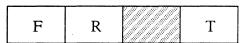

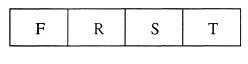

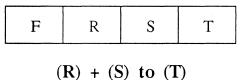

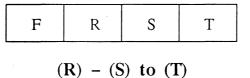

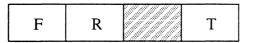

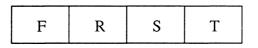

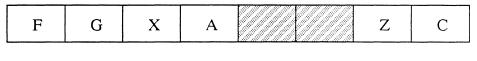

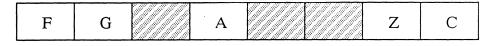

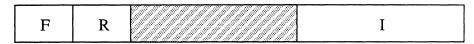

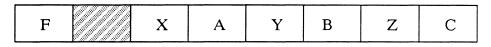

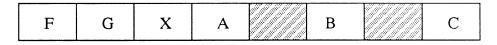

Format #4

- F Function code of instruction.

- R Specifies a register containing an operand for use in an arithmetic operation.

- S Specifies a register containing an operand for use in an arithmetic operation.

- T Specifies a destination register for the transfer of the arithmetic results.

| F R I (48 bits) |

|-----------------|

|-----------------|

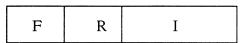

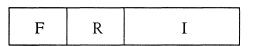

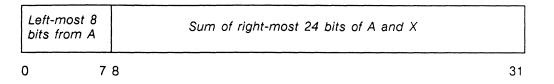

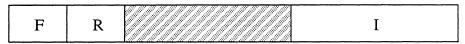

Format #5

- F Function code of instruction.

- R Specifies a destination register for the transfer of an operand or operand sum.

- I 48-bit index used to form the branch address in a #B6 branch instruction. In #BE and #BF index instructions, I is a 48-bit operand.

| F R I (16 bits) | F | R | I (16 bits) |

|-----------------|---|---|-------------|

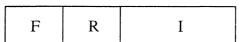

|-----------------|---|---|-------------|

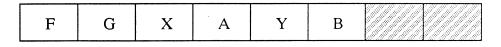

Format #6

- F Function code of instruction.

- R Specifies a destination register for the transfer of an operand or operand sum.

- I A 16-bit operand.

| F R* S* T* |  | F | R* | S* | T* |

|------------|--|---|----|----|----|

|------------|--|---|----|----|----|

Format #7

- F Function code of instruction.

- \* Described where used.

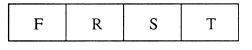

| F R | s | т |

|-----|---|---|

|-----|---|---|

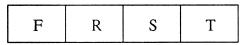

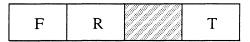

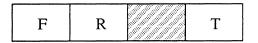

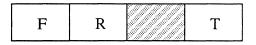

Format #8

- F Function code of instruction.

- **R** Specifies registers and branching conditions given in the individual instruction descriptions.

- S Specifies registers and branching conditions given in the individual instruction descriptions.

- T Specifies a register that contains the base address and, in some cases, the field length of the corresponding result field or branch address.

| F | R | S* | T* |

|---|---|----|----|

| L |   |    |    |

#### Format #9

- F Function code of instruction.

- **R** Specifies registers and branching conditions given in the individual instruction descriptions.

- \* Described where used.

| F R T |

|-------|

|-------|

#### Format #A

- F Function code of instruction.

- **R** Specifies registers and branching conditions given in the individual instruction descriptions.

- T Specifies a register containing the old state of a register, DFB register, and so on; in an index, branch, or inter-register transfer operation.

| F | R |  | l<br>6 bits | Т |  |

|---|---|--|-------------|---|--|

|---|---|--|-------------|---|--|

Format #B

- F Function code of instruction.

- **R** Specifies registers and branching conditions given in the individual instruction descriptions.

- I In the #33 branch instruction, the 6-bit I is the number of the DFB object bits used in the branching operation.

- T Specifies a register containing the old state of a register, DFB register, and so on; in an index, branch, or inter-register transfer operation.

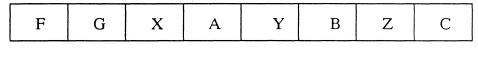

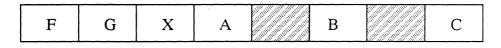

| F G X A Y | В | Z | С |

|-----------|---|---|---|

|-----------|---|---|---|

#### Format #C

- F Function code of instruction.

- G An 8-bit designator that specifies certain subfunction conditions. Subfunctions include length of operands (32- or 64-bit), normal or broadcast source vectors, and so on. The number of bits used in the G designator varies with instructions.

- X Specifies a full word or half word register that contains an operand, the length and type of which is determined by G field bits.

- A Specifies a full word or half word register, the length and type of which is determined by G field bits.

- Y Specifies one of the following: a register that contains an index used to form the branch address; part of the half word item count in a relative branch; or a destination register for storing a one if the condition is met, and zero otherwise.

- B Specifies a register that contains the branch base address in the rightmost 48 bits, or must be set to zero, depending on G bit 2.

- Z Contains a two's complement or unsigned integer that determines whether the condition is met.

- C Specifies a full word or half word register that contains the sum of (A) + (X) for indexed branch instructions, but must be set to zero for compare floating-point instructions.

| F G X* A* B* C* |

|-----------------|

|-----------------|

Format #D

- F Function code of instruction.

- G An 8-bit designator that specifies certain subfunction conditions. Subfunctions include length of operands (32- or 64-bit), normal or broadcast source vectors, and so on. The number of bits used in the G designator varies with instructions.

- \* Described where used.

# **Instruction Function Field**

Each instruction has a function and most have operands. All instructions have a function field, the first byte in the instruction. The function value ranges from #00 through #FF. #00 through #7F are 32-bit instructions, and #80 through #FF are 64-bit instructions. The function defines the operation that the instruction performs.

The instruction performs its function on operands, and the operands' number, format, and meaning depend on the instruction. In the instruction word, operands are generally defined by 8-bit designators that are translated into register numbers, address offsets and bases, and immediate data.

## **Instruction Subfunctions**

Many machine instructions have a subfunction field (referred to as the "G-field"), which further defines the instruction's function. Bits 0-7 in the G field ('G-bits' 0-7) are set to determine the subfunction. Bit setting meanings may vary, depending on the instruction. (Note that in some instructions, #56 for example, the R-field contains subfunctions and uses 'G-bits.')

Table 2–1 lists the qualifier mnemonics used with the instructions in this manual, their hexadecimal values, and the qualifier's meaning. Note that the hexadecimal values listed in the table must be added when more than one qualifier is specified for an instruction.

For the convenience of program developers, the qualifier associated with each of the G-bits is also included in the table. The description for each instruction in this manual refers to G-bit usage by means of these qualifiers. The absence of a qualifier in an instruction description means that the corresponding G-bit must be a zero; the presence of a qualifier means that the corresponding G-bit must be a one.

The first digit of the value is the hexadecimal value of G-bits 0-3, the second digit is the hexadecimal value of G-bits 4-7. For example, qualifier *rel* has a hexadecimal values of 0 and 4. The bit settings are then 00000100.

Table 2–2 lists the G-bit definitions associated with most vector instructions.

Table 2–1. Instruction Qualifiers.

| Qualifier           | #Value               | G-bits Set           | Meaning                                                                                                      |

|---------------------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------|

| a<br>b<br>br<br>brb | 10<br>08<br>40<br>06 | 3<br>4<br>1<br>5 & 6 | Broadcast A operand<br>Broadcast B operand<br>Unconditional branch<br>Relative branch backward               |

| brf                 | 04                   | 5                    | Relative branch forward                                                                                      |

| bro<br>brz          | 80<br>C0             | 0<br>0 & 1           | Branch on one<br>Branch on zero                                                                              |

| c<br>ca0            | 02<br>00             | 6<br>none            | Complement A operand<br>CB address base, limit, access select 0                                              |

| ca1                 | 01                   | 7                    | CB address base, limit, access select 1                                                                      |

| ca2<br>ca3          | 02<br>03             | 6<br>6&7             | CB address base, limit, access select 2<br>CB address base, limit, access select 3                           |

| fia                 | 04                   | 5                    | Use fixed increment A                                                                                        |

| fwc                 | 10                   | 3                    | Full word boolean compare (64 bits)                                                                          |

| grp                 | 02                   | 6                    | Transmit elements in groups                                                                                  |

| ivg                 | 60                   | 1&2                  | Implication vector generation                                                                                |

| h                   | 80                   | 0                    | Half word operand                                                                                            |

| lh                  | 20                   | 2                    | Start at last hit                                                                                            |

| ma<br>mb            | 04<br>01             | 5<br>7               | Magnitude of A operand<br>Magnitude of B operand                                                             |

|                     | 01                   |                      |                                                                                                              |

| n                   | 06                   | 5&6                  | Negative A operand                                                                                           |

| neq                 | 01                   | 7                    | Search for inequality                                                                                        |

| o<br>pa0            | 20<br>00             | 2<br>none            | Offset destination and control vector<br>CB process word address base, limit, access select 0                |

| pa0<br>pa1          | 01                   | 7                    | CB process word address base, limit, access select 0<br>CB process word address base, limit, access select 1 |

| pa2                 | 02                   | 6                    | CB process word address base, limit, access select 2                                                         |

| pa3                 | 03                   | 6&7                  | CB process word address base, limit, access select 3                                                         |

| ra                  | 10                   | 3                    | First operation's result replaces A input to second operator                                                 |

| rb<br>rel           | 08<br>04             | 4<br>5               | First operation's result replaces B input to second operator<br>Relative branch (forward or backward)        |

|                     | 04                   |                      | Relative Drahen (forward of Dackward)                                                                        |

| rf                  | 01                   | 7                    | Source/destination resides in the register file                                                              |

| rvg                 | 20                   | 2                    | Reverse vector generation                                                                                    |

| sa0<br>sa1          | 00<br>10             | none<br>3            | CB semaphore address base, limit, access select 0<br>CB semaphore address base, limit, access select 1       |

| sa1<br>sa2          | 20                   | 2                    | CB semaphore address base, limit, access select 1<br>CB semaphore address base, limit, access select 2       |

| sa3                 | 30                   | 2&3                  | CB semaphore address base, limit, access select 3                                                            |

| sb                  | 01<br>20             | 7 2                  | Skip B on each A stored<br>Set condition                                                                     |

| sc<br>so            | 20                   | 2                    | Set bit to one                                                                                               |

| sz                  | 30                   | 2 & 3                | Clear bit to zero                                                                                            |

| t                   | 10                   | . 3                  | Toggle bit                                                                                                   |

| usi                 | 08                   | 4                    | Use 48-bit unsigned integers                                                                                 |

| xvg                 | 40                   | 1                    | Exclusive OR vector generation                                                                               |

| Z                   | 40                   | 1                    | Control vector on zeros                                                                                      |

#### **Subfunctions For Vector Operations**

Vector instructions all have an 8-bit G-field. The G-field bit settings for a particular instruction affect its operand size, how the control vector operates, whether operands are broadcast, and if there is any sign control. Table 2–2 shows only the qualifiers used with vector instructions, the G-bits set by each qualifier, and the meaning. Explanations of the different subfunctions follow the table. Refer to table 2–1 for a complete list of instruction qualifiers.

| Qualifier     | G-bit | State  | Meaning                                                                                               |

|---------------|-------|--------|-------------------------------------------------------------------------------------------------------|

| h             | 0     | 0<br>1 | Operands are 64 bits long (word)<br>Operands are 32 bits long (half word)                             |

| z             | 1     | 0<br>1 | Control vector operates on binary ones<br>Control vector operates on binary zeros                     |

| 0             | 2     | 0<br>1 | No offset for destination field and control vector<br>Offset for destination field and control vector |

| a             | 3     | 0<br>1 | Vector A is the source operand<br>Broadcast repeated constant in register A                           |

| b             | 4     | 0<br>1 | Vector B is the source operand<br>Broadcast repeated constant in register B                           |

| ma,mb,<br>c,n | 5,6,7 | 0      | Sign control                                                                                          |

Table 2-2. Qualifiers and valid G-bit settings for vector operations.

#### **Control Vectors**

The Z designator specifies a register containing the control vector's base address. A control vector is a bit vector. Each bit is associated with storing a result in the corresponding element of the destination vector. If a control vector is specified in an instruction (non-zero Z designator), the z qualifier can be used to set bit 1 of the G-field. z determines whether a zero or one control vector bit allows a result to be stored. Data flag bits are set only for operands that are stored. If z is specified, the result is stored if the corresponding bit in the control vector bit is set to one. A Z designator of zero causes all result elements to be stored in the destination field without regard to the z qualifier. The control vector uses the same length used by the destination field.

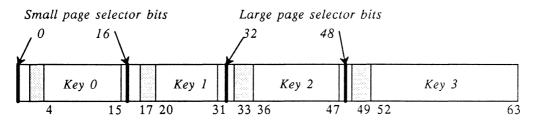

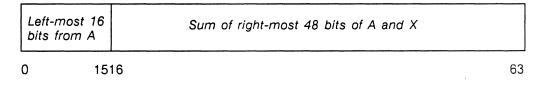

#### **Destination Vector and Control Vector Offsets**

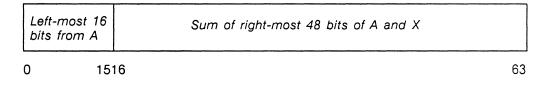

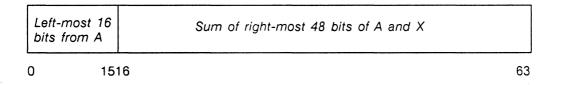

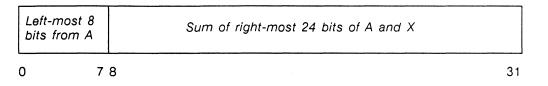

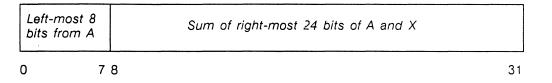

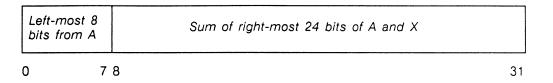

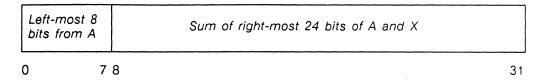

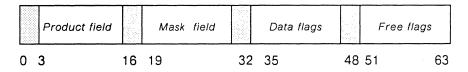

The C designator specifies a register containing the destination vector's field length and base address. If the o qualifier is specified (setting G-bit 2), register C+1 contains an offset into the destination. The same offset applies to the control vector. The format of register C+1 is:

|   |       | 32-bit extended sign |    | offse | t  |   |

|---|-------|----------------------|----|-------|----|---|

| 0 | 15 16 |                      | 47 | 48    | 63 | , |

If an offset is specified, C must be specified as an even number. The offset is added to the base address to get the destination and control vector starting addresses (it is a bit offset for the control vector). The offset is an item count. Before being added to the base address, the offset is multiplied by a factor adjusting for the size of the operands. It is shifted left six places for 64-bit operands, and five places for 32-bit operands. The offset is subtracted from the field length specified for the destination field. A C designator of zero has no destination field. Note that offsets also apply to input vectors, refer to Appendix H.

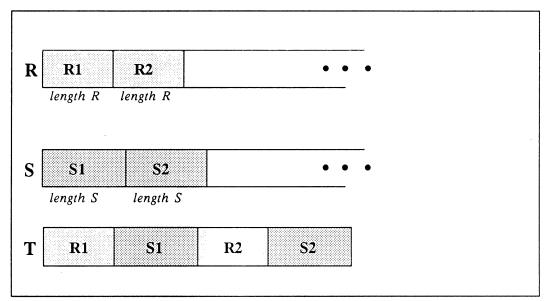

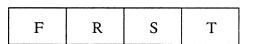

#### **Broadcast Operands**

Qualifiers a and b control the setting of G-bits 3 and 4 that define broadcasts for the A and B source operand streams. If G-bits 3 and 4 are not set, vectors A and B from CPU memory are the sources. If they are set, the A or B source field is a constant obtained from the respective register, a repeated operand that is broadcast for the length of the operation. The constant becomes each element of the A or B vector stream. If the h qualifier is set to define 32-bit operands, the source operand registers are 32-bit registers. Some instructions do not permit the use of one or both of the a and b qualifiers.

Registers A and B contain the field length and base address of the two source operand streams when broadcast is not specified. Registers X and Y, respectively, contain the offsets. The offsets modify the field length and base address of the source fields just as described for the destination field. A non-broadcast source field that is shorter than the destination field is extended with operands (as described in Appendix E).

#### **Sign Control**

On some vector operations, G-bits 5, 6, and 7 are used to define sign control for input operands. Four qualifiers -c, ma, mb, and n - control the state of the three G bits. If no qualifiers are set, vector A and B stream operands are used in the normal way.

The c qualifier sets G-bit 6 to complement the coefficients of the A stream operands before they are used. The ma qualifier sets G-bit 5 to use the magnitude of the coefficients of A stream operands. mb sets G-bit 7 to use the magnitude of the coefficients of B stream operands. The n qualifier may be used only if neither ma nor mb is specified. n sets bits 5 and 6 to use the negative form of A operands; all positive coefficients of the A stream operands are complemented before being used. Negative operands are not changed.

Appendix C lists the instructions for which sign control is valid.

# Chapter **3** ETA10 Instruction Descriptions

### In This Chapter . . .

The ETA10 instruction descriptions are listed in hexadecimal order of the function code. They include the instruction format, G-bit settings and qualifier mnemonics, as well as a short description of the operation.

3-1

### **Instruction Description Formats**

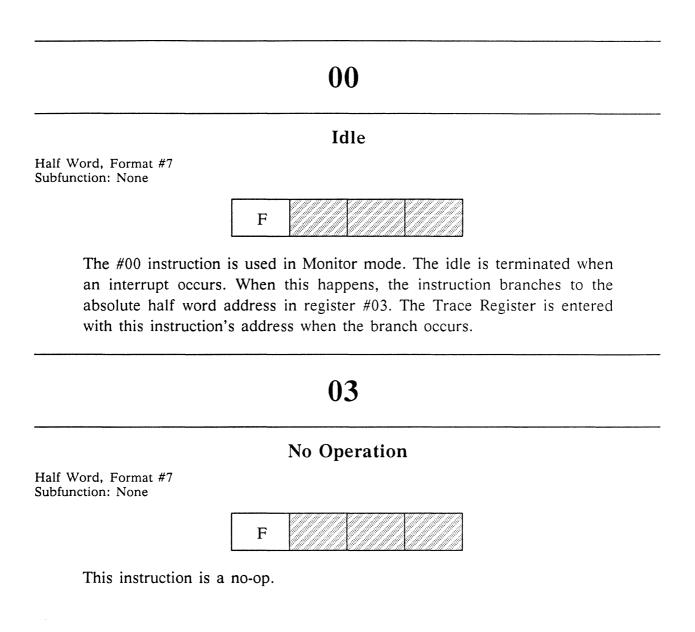

The instruction descriptions in this chapter occupy one-half, one, or two pages. Instruction are arranged by their numeric function code, #00 through #FF.

The description includes the instruction's:

- Length (half word or full word).

- Format (#1 through #D).

- Subfunction and qualifiers, if applicable. In the example below, all subfunction bits in the G-field may be set. The valid qualifiers are *h*,*z*,*o*,*a*,*b*,*ma*,*c*,*n*, and *mb*.

Subfunction: hzoabsss Qualifiers: h,z,o,a,b,sss=[ma,c,(n=ma+c),mb]

- Instruction word layout, showing the designators (F,G,A,B, and so on). Shading indicates unused areas. (Unused areas of an instruction must always be cleared to zero.)

- Operations performed. A brief discussion of how the instruction functions, with any resulting data flag bit settings. (Some string and vector macro instructions that return a result to the register file, and the Data Flag Register, do not alter the location in register file nor the Data Flag Register if the instruction is a no-op.)

Hexadecimal numbers are prefixed by a pound sign (#).

For information about instruction operations mentioned in the descriptions, refer to chapter two and the appendices of this manual. Refer to PUB-1005, *ETA10 System Reference Manual*, for information about such topics as Job and Monitor mode, domain changes, virtual and physical addressing, and so on.

#### **Breakpoint On Address**

Half Word, Format #4 Subfunction: None

The #04 instruction transfers to the breakpoint register the contents of the 64-bit register designated as R. The breakpoint register is a maintenance and programming debugging aid.

The breakpoint function compares addresses of specified categories of requests with the address in the breakpoint register. In Job mode, virtual addresses are compared; in Monitor mode, absolute addresses. Breakpoint compares are disabled for the absolute addressing of CP memory by exchanges, domain changes, space table searches, and shared memory transfers.

When an instruction writes or reads a CP memory address matching the breakpoint address, (for the current domain only, in Job mode), bit 47 of the data flag register is set, indicating that a condition that can cause automatic branching has occurred. The data flag register can be set to cause a branch to a special routine provided for support of debugging operations, for example, a routine to trap the current program address.

3-4

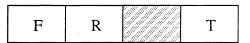

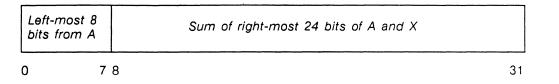

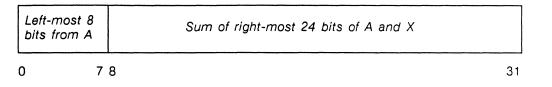

Figure 1–1 shows the contents of register R for the breakpoint instruction.

|   |    | Breakpoint Address |    | W  | R  |    |

|---|----|--------------------|----|----|----|----|

| 0 | 16 |                    | 58 | 61 | 62 | 63 |

Figure 1-1. Structure of Register R for the #04 Instruction.

Bits 16-58 of register R hold the breakpoint address, the CP memory address which initiates the breakpoint function. Bits 61 and 62 can be set to specify the breakpoint function. Usage bit 61 specifies the breakpoint function for CP memory write instructions, and usage bit 62 specifies the breakpoint function for CP memory read instructions. Either or both bits 61 and 62 may be set. Bits 0-15, 59-60, and 63 are unused and must be cleared to zero.

In Job mode, the breakpoint address is saved in the breakpoint register, and stored in the current invisible package for mode or domain changes. Since a Job to Monitor mode change clears the breakpoint register, and Monitor mode has no invisible package saved, the monitor program must reload the breakpoint register if the breakpoint function is needed.

#### Void Stack and Branch

Half Word, Format #4 Subfunction: None