### **GD** MAGNETIC PERIPHERALS, INC. a Control Data Company

### INTERFACE SPECIFICATION

FOR

IPI PHYSICAL LEVEL

DOCUMENT NO. 64731602 REV A JULY 1987

CONTROL DATA COMPANY

# ENGINEERING SPECIFICATION

•••

SPEC

64731602

CD

5

REV

A

DATE

7/8/87

PAGE

1 of 99

TWIN CITIES DISK DIVISION

1831A 0233D

#### INTERFACE SPECIFICATION

#### FOR

IPI PHYSICAL LEVEL

Approved <u>7-8-87</u> Released

Control Data Company

# ENGINEERING SPECIFICATION

SPEC 64731602 CD 5 REV DATE PAGE 2

### TWIN CITIES DISK DIVISION

#### TABLE OF CONTENTS

|                                              | Page |

|----------------------------------------------|------|

| 1.0 SCOPE                                    | 6    |

| 2.0 APPLICABLE DOCUMENTS                     | . 6  |

| 3.0 EDITORIAL CONVENTIONS                    | 6    |

| 4.0 GLOSSARY OF TERMS                        | 7    |

| 5.0 PHYSICAL CHARACTERISTICS OF THE HARDWARE | 10   |

| 5.1 Cable-Connector Assemblies               | 10   |

| 5.2 Cables                                   | 10   |

| 5.2.1 28 AWG Internal Round Cable            | 10   |

| 5.2.2 28 AWG External Round Cable            | 10   |

| 5.3 Connectors                               | 11   |

| 5.4 Terminators                              | 11   |

| 5.5 Differential Drivers/Receivers           | 11   |

| 6.0 SYSTEM CONFIGURATIONS                    | 11   |

| 6.1 Master                                   | 11   |

| 6.2 Slave                                    | 12   |

| 6.3 Facility                                 | 12   |

| 6.4 Multi-Tier Structure                     | 12   |

| 6.5 Cable Configuration                      | 13   |

| 7.0 INTERFACE                                | 14   |

| 7.1 Signals                                  | 16   |

| 7.1.1 Signal Nomenclature                    | 16   |

CONTROL DATA COMPANY

•

# ENGINEERING SPECIFICATION

SPEC 64731602 CD 5 REV DATE PAGE 3

••

TWIN CITIES DISK DIVISION

#### TABLE OF CONTENTS (Cont.)

|                |                                                                 | Page     |

|----------------|-----------------------------------------------------------------|----------|

| 7.1.2          | Signal Usage                                                    | 16       |

| 7.2            | States                                                          | 18       |

| 7.2.1          | Idle                                                            | 18       |

| 7.2.2          | Maintenance                                                     | 18       |

| 7.2.3          | Request                                                         | 18       |

| 7.2.4          | Selective Reset 1                                               | 18       |

| 7.2.5          | Selective Reset 2                                               | 18       |

| 7.2.6          | Deselected                                                      | 19       |

| 7.2.7          | Select                                                          | 19       |

| 7.2.8          | Slave Acknowledge                                               | 19       |

| 7.2.9          | Bus Acknowledge                                                 | 20       |

| 7.2.10         |                                                                 | 20       |

| 7.2.11         |                                                                 | 21       |

| 7.2.12         |                                                                 | 21       |

| 7.2.13         |                                                                 | 22       |

| 7.2.14         |                                                                 | 22       |

| 7.2.15         |                                                                 | 22       |

| 7.2.16         |                                                                 | 23       |

| 7.2.17         | Slave End Without Information Transfer                          | 23       |

| 7.2.18         | Master End Without Information Transfer                         | 24       |

| 7.2.19         | Slave Action On Bus A Parity Errors                             | 24       |

| 7.3            | Sequences                                                       | 24       |

| 7.3.1          | Request Sequences                                               | 25       |

| 7.3.2          | Selection Sequence                                              | 26       |

| 7.3.3          | Normal Deselection Sequence                                     | 26       |

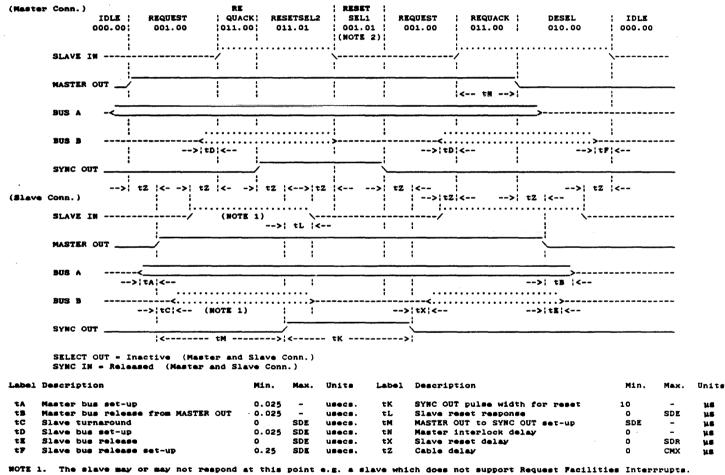

| 7.3.4          | Master Reset Sequence                                           | 27<br>27 |

| 7.3.5          | Selective Reset Sequence                                        | 27       |

| 7.3.6<br>7.3.7 | Bus Exchange Sequence                                           | 27       |

| 7.3.7          | Information Transfer Sequence                                   | 28       |

| 7.3.8          | Data Streaming Sequence<br>Slave-to-Slave Information Transfers | 32       |

| 7.4            | Bus Octet Definitions                                           | 33       |

| 7.4.1          | Bus A Selection Octet Bit Definitions                           | 33       |

| 7.4.2          | Bus B Select Status Octet                                       | 37       |

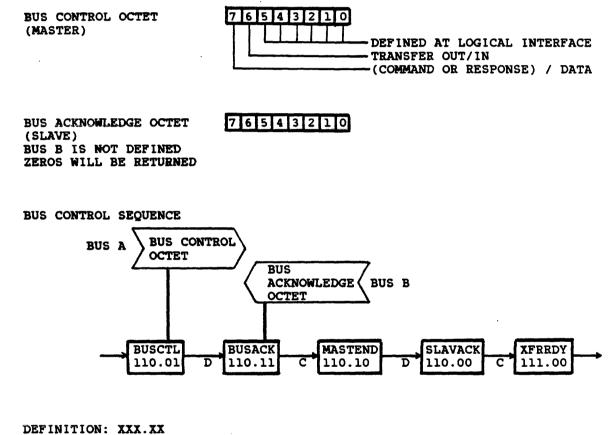

| 7.4.3          | Bus A Bus Control Octet                                         | 37       |

| 7.4.4          | Bus B Bus Acknowledge Octet                                     | 38       |

| 7.4.5          | Bus A Master Status Octet                                       | 39       |

| 7.4.6          | Bus B Slave Status Octet                                        | 40       |

| 7.4.7          | Bus A Request Modifier Octet                                    | 40       |

| 7.4.8          | Bus B Responds to Request Modifier Octet                        | 46       |

| 7.5            | Maintenance Mode                                                | 49       |

| 7.5.1          | Maintenance Mode 1                                              | 51       |

| 7.5.2          | Other Maintenance Considerations                                | 52       |

| 7.6            | Timing                                                          | 53       |

| 7.6.1          | Terms                                                           | 53       |

| 7.6.2          | Data Streaming Sync Out Pulse Width                             | 53       |

SPEC 64731602 CD 5 REV DATE PAGE 4

Page

TWIN CITIES DISK DIVISION

#### TABLE OF CONTENTS (Cont.)

#### ILLUSTRATIONS

#### <u>Figures</u>

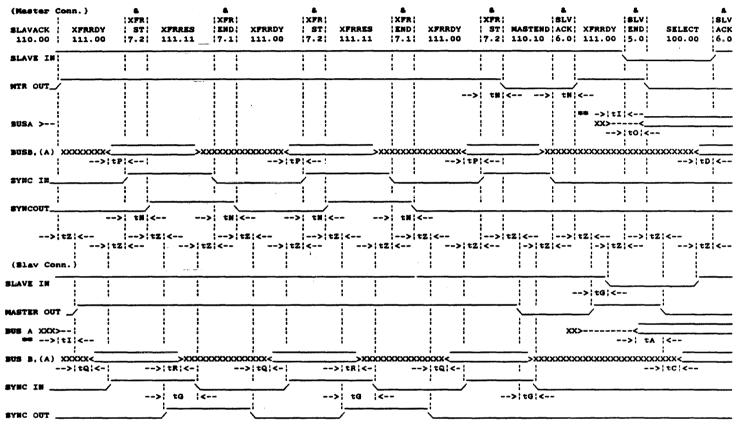

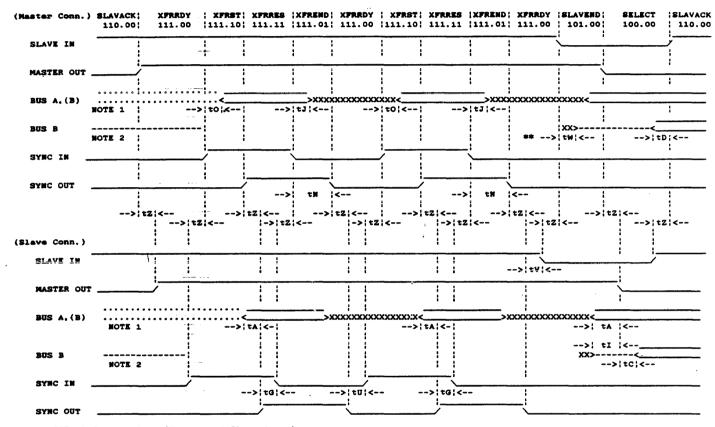

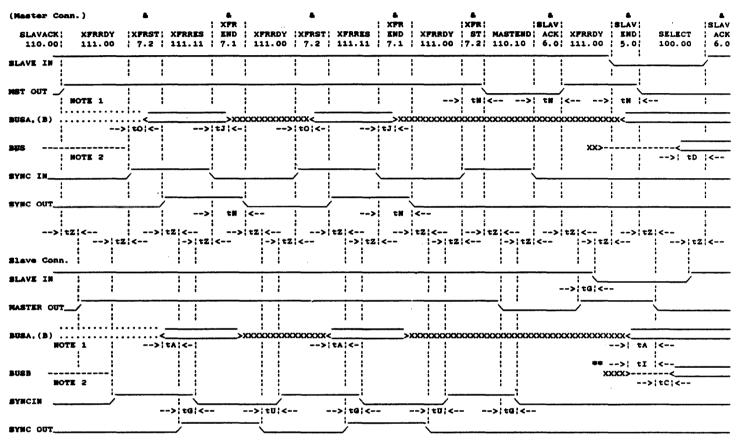

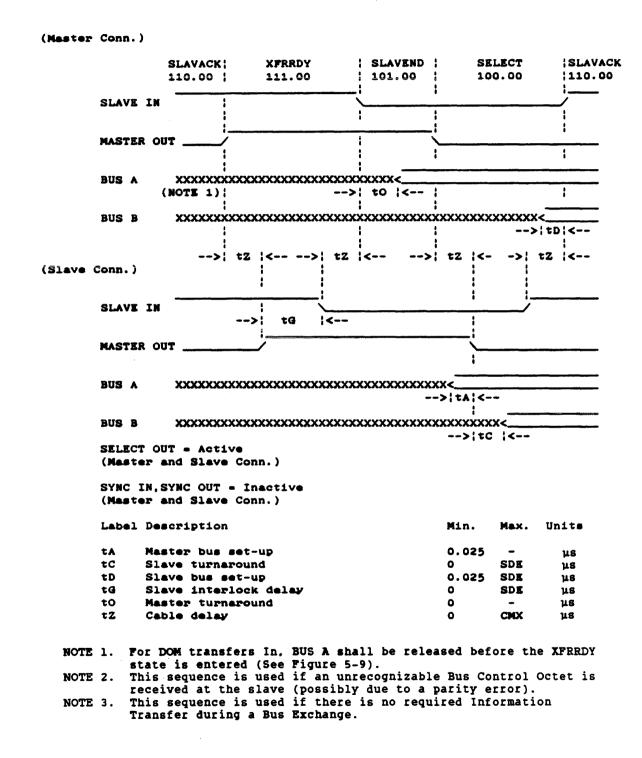

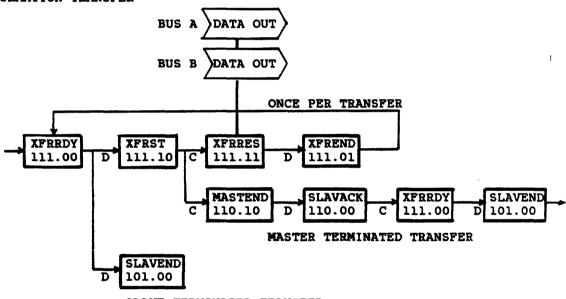

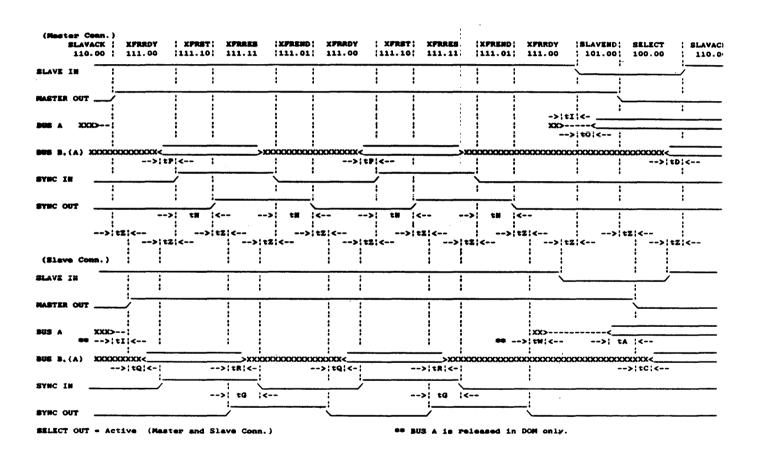

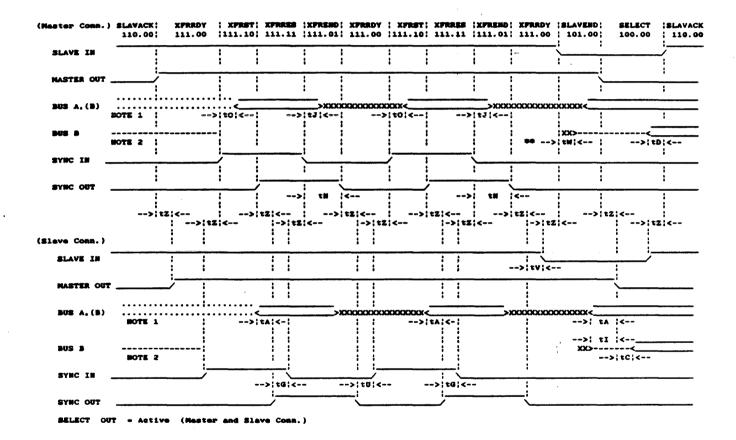

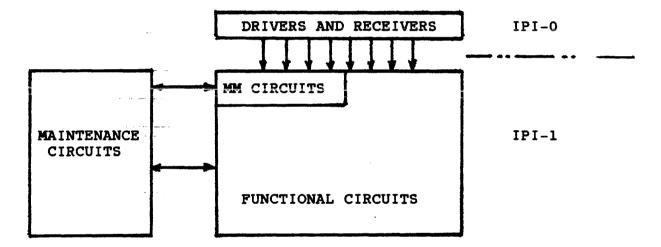

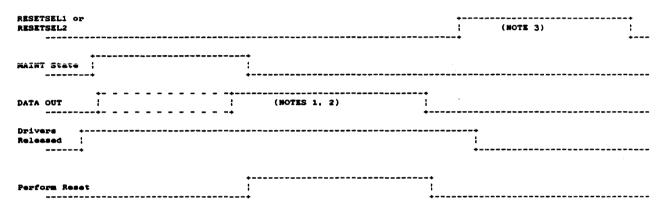

Schematic of IPI Cabling 54 1 Multi-tier Structure 2 55 Cabling Alternatives 3 56 4 IPI Interface Signals 57 Bus State Diagram 5 58 Request Interrupts Sequence 6 59 Request Interrupts Timing 7 60 Request Transfer Settings Sequence 8 61 9 Request Transfer Settings Timing 62 Selection Sequence 63 10 11 Selection Timing 64 12 Deselection Sequence 65 13 Deselection Timing 66 14 Master Reset Sequence 67 15 Master Reset Timing 68 16 Selective Reset Sequence 69 17 Selective Reset Timing 70 18 Bus Control Sequence 71 19A Bus Control Timing Preceding Transfer In 72 19B Bus Control Timing Preceding Transfer Out 73 20 Ending Status Sequence 74 21A Ending Status Timing (Input, Slave Terminated) 75 21B Ending Status Timing (Input, Master Terminated) 76 21C Ending Status Timing (Output, Slave Terminated) 77 21D Ending Status Timing (Output, Master Terminated) 78 21E Ending Status Timing (Without Information Transfer) 79 22 Output Information Transfer Sequence 80 23A Interlocked Input Timing Slave End 81 23B Interlocked Output Timing Slave End 82 23C Interlocked Input Timing Master End 83 23D Interlocked Output Timing Master End 84 24A Data Streaming Input Timing Slave End 85 24B Data Streaming Output Timing Slave End 86 24C Data Streaming Input Timing Master End 87 24D Data Streaming Output Timing Master End 88 25 Block Diagram of Maintenance Mode 89 26 Maintenance Mode 1 90

-----

# ENGINEERING SPECIFICATION

SPEC

64731602

CD

5

REV

5

DATE

5

PAGE

5

Page

TWIN CITIES DISK DIVISION

#### TABLE OF CONTENTS (Cont.)

#### ILLUSTRATIONS

#### **Tables**

| Pin Assignments            |                                                                                                                                                          | 91                                                                                                                                                       |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Nomenclature        |                                                                                                                                                          | 92                                                                                                                                                       |

| State Definitions          |                                                                                                                                                          | 93                                                                                                                                                       |

| Interface States           | ٥                                                                                                                                                        | 94                                                                                                                                                       |

| Interface States           |                                                                                                                                                          | 95                                                                                                                                                       |

| Interface States           |                                                                                                                                                          | · 96                                                                                                                                                     |

| Facility Address Mapping   |                                                                                                                                                          | 97                                                                                                                                                       |

| MM1 Scenario Summary       |                                                                                                                                                          | 98                                                                                                                                                       |

| MM Signal Line Assignments |                                                                                                                                                          | 99                                                                                                                                                       |

|                            | Signal Nomenclature<br>State Definitions<br>Interface States<br>Interface States<br>Interface States<br>Facility Address Mapping<br>MM1 Scenario Summary | Signal Nomenclature<br>State Definitions<br>Interface States<br>Interface States<br>Interface States<br>Facility Address Mapping<br>MM1 Scenario Summary |

AND THE REV. 2/83 CDC

SPEC

64731602

CD

5

REV

5

DATE

5

PAGE

6

TWIN CITIES DISK DIVISION

#### 1.0 SCOPE

This Specification covers the physical aspects of the IPI I/Os (IPI-0, IPI-1, IPI-2, IPI-3); i.e., the hardware involved, the system configurations, the control sequences, and the timing, without regard to the content of the information being processsed.

The purpose is to help in the development and use of computer systems by providing a common IPI physical interface for connecting a variety of peripheral devices (disk and tape drives, printers, terminals, etc.).

2.0 APPLICABLE DOCUMENTS

SPEC 64731600- Interface Specification for IPI-2ANSC X3.129-1986- IPI Physical Level StandardANSC X3T9.3/83-4- IPI Device Generic - Disk SpecificationEIA Standard RS-485- Electrical Characteristics of Generators and<br/>Receivers

#### 3.0 EDITORIAL CONVENTIONS

Certain terms used in this document which are proper names of signals, state mnemonics, or similar terms are printed in uppercase to avoid possible confusion with other uses of the same words. Any lowercase uses of these words have the normal English meaning. Examples printed in uppercase are BUS A, SLAVE IN, SYNC OUT, DESEL, SLAVEND.

A number of conditions, sequence parameters, events, English text, states or similiar terms are printed with the first letter of each word in uppercase and the rest lowercase. Any lowercase uses of these words have the normal English meaning. Examples printed with the first letter uppercase are In, Out, Selective Reset, Bidirectional, Bus Control, Operation Response. Control Data Company

### ENGINEERING SPECIFICATION

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

7

TWIN CITIES DISK DIVISION

#### 4.0 GLOSSARY OF TERMS

Bidirectional - This term refers to the use of signal lines which may be asserted by either the master or a slave, but not concurrently.

Bus Acknowledge - In the optional configuration where the master permits the slave to define the type of Information Transfer to be executed, Bus Acknowledge is the BUS B equivalent of Bus Control.

Bus Control - This term refers to the Physical Interface Bus Control octet asserted on BUS A by the master during the Bus Control sequence. It is used to define the bus configuration for the subsequent Information Transfer.

Bus Exchange - This term refers to the Bus Control sequence (initiated by the master) and the Ending Status sequence (initiated by the slave), which are used to frame an Information Transfer (which may or may not have occurred). For every Bus Control sequence there shall be an Ending Status sequence.

Busy - A slave is Busy when it is currently unable to process Bus Exchanges or Information Transfers.

Data - This term refers to information transferred over the Physical Interface, other than that defined as Operation Commands and Operation Responses by the Logical Interface.

Data Streaming - This term refers to the transfer of information in a non-interlocked manner in order to achieve faster transfer rates.

Dominant Slave - A slave capable of assuming the role of the master for slave to slave Information Transfers.

DOM (Double Octet Mode) - This term refers to a mode of Information Transfer which uses BUS A and BUS B in parallel in a bidirectional manner to transfer 16 bits concurrently.

Ending Status - This term refers to the Physical Interface status octets presented by the master (optional) and the slave (mandatory), immediately following an Information Transfer.

SPEC 64731602 CD 5 REV DATE PAGE 8

TWIN CITIES DISK DIVISION

Facility - This term refers to the entity addressable by the master through the slave.

Housekeeping - This is a function made available at the Logical Interface which permits the master to ascertain the attributes of the attached slaves.

Information Transfer - This term refers to interchanges on the interface associated with the Logical Interface; i.e., Operation Commands, Operation Responses and Data)

Interlocked - This term refers to the handshake between master and slave of signals on the interface.

Level 0 - This term refers to the electrical and mechanical characteristics of the Physical Interface.

Level 1 - This term refers to the bus states, sequences and other rules (excepting electrical and mechanical characteristics of Level 0) that govern the use of the Physical Interface.

Logical Interface - This term refers collectively to all protocols higher than the Physical Interface specified in this document.

Maintenance Mode - This term refers to the capability for a master to initiate analysis of the interface, and restore operation after a failure condition.

Mandatory - Unless otherwise described as Optional or MPI Unique, the definition of the Physical Interface as described is mandatory for all masters and slaves. The functions must be implemented as defined in this document.

Master - This term refers to the entity in control of the interface.

Master Status - In the optional configuration where the master permits the slave to define the type of Information Transfer to be executed, Master Status is the BUS A equivalent of Slave Status.

### ENGINEERING SPECIFICATION

SPEC 64731602 CD 5 REV DATE PAGE 9

TWIN CITIES DISK DIVISION

Operation Command - This term refers to a command issued by the master to initiate some specific operation which is outside the Physical Interface and is associated with a Logical Interface function.

Operation Response - This term refers to the response of a slave to an Operation Command. It is associated with the Logical Interface.

Optional - This term describes features which are not required by this document. However, if any feature defined by this document is implemented, it must be done as defined herein.

Physical Interface - This term denotes the mechanical, electrical, and interface protocols specified in this document. In use this term contrasts with the term Logical Interface.

Sequence - This term refers to a series of states which follow each other in a definite order to accomplish a function.

SOM (Single Octet Mode) - This term refers to a mode of Information Transfer which uses BUS A in a unidirectional manner to transfer 8 bits of information from master to slave, and BUS B in a unidirectional manner to transfer 8 bits of information from slave to master.

Slave - This term refers to the addressable entity under control of, and directly connected to, the master.

Slave Status - This is the status asserted on BUS B by the slave at the completion of an Information Transfer (which may or may not have occurred).

State - This term is used to define the immediate condition of the interface, excluding transitions, as indicated by the control signals.

Unidirectional - This term refers to the use of signal lines which are not asserted by both the master and slave (either concurrently or successively). Control Data Company

# ENGINEERING SPECIFICATION

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

10

TWIN CITIES DISK DIVISION

- 5.0 PHYSICAL CHARACTERISTICS OF THE HARDWARE

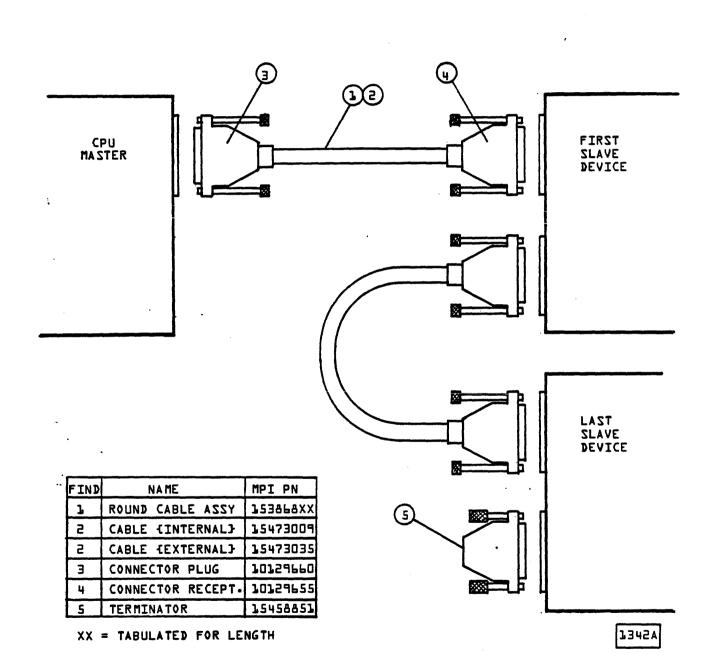

- 5.1 Cable-Connector Assemblies (See Figure 1)

Each cable shall be assembled with a male cable connector on one end and a female connector on the other end.

The outer shield of the 50 conductor shielded cable is terminated at the connector shell.

Cable assembly pin assignments are shown in Table 1.

5.2 Cables

The following cables are representative of the types used for the IPI. Cables may have an overall shield, suitable for terminating in a metal shielded connector. This overall shield serves the purpose of a signal shield.

5.2.1 28 AWG Internal Round Cable

This type cable may be used to interconnect several devices inside a common cabinet.

Cable shall consist of 50 conductors (25 twisted pair) of 28 AWG. The following characteristics apply to the twisted pairs within the bulk cable assembly.

5.2.2 28 AWG External Round Cable

This type of cable may be used to interconnect several devices cabinet to cabinet.

Cable shall consist of 50 conductors (25 twisted pair) of 28 AWG. The following characteristics apply to the twisted pairs within the bulk cable assembly.

CHARACTERISTIC IMPEDANCE: $120 \pm 12 \Omega$ DC RESISTANCE: $65 \Omega \max/1000$  feet at  $20^{\circ}C$ SIGNAL ATTENUATION:0.029 db max/foot at 5 MHzVELOCITY OF PROPAGATION: $77\% \pm 05\%$  CPAIR TO PAIRPROPAGATION DELAY DELTA:0.10 ns max/foot

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

11

TWIN CITIES DISK DIVISION

#### 5.3 Connectors

The connectors used shall be the industry standard 50 Pin Subminiature D, plug and receptacle.

The shells of shielded connectors shall be plated with conductive material to ensure the integrity of the cable shield to chassis current path. The resistance of the cable shield to equipment chassis shall not exceed 5 m $\Omega$ , after a minimum of 500 connect and disconnect cycles.

#### 5.4 Terminators

The terminators shall fit within the same dimensions as the cable end connectors, and shall be secured by the same retention method as the cable connectors.

5.5 Differential Drivers/Receivers

The differential driver and receiver shall meet the requirements of the EIA Standard RS-485, which specifies the electrical characteristics of generators (drivers) and receivers for use in a balanced digital multipoint system.

Transceiver pin assignments are shown in Table 1.

6.0 SYSTEM CONFIGURATIONS

The IPI has been designed to operate with three defined elements of a computer system; master, slave, and facility.

6.1 Master

The master manages the slave(s) and is responsible for control of the interface. It is the master's responsibility to operate the slaves according to their capabilities.

SPEC

64731602

CD

5

REV

5

DATE

5

PAGE

12

TWIN CITIES DISK DIVISION

#### 6.2 Slave

The slave is managed by the master and may or may not have intelligence, depending on the command set it is capable of executing. In an intelligent configuration it can support a master which is oriented to generic device characteristics such as a disk with 22,000 blocks of data, each 512 bytes long. In a device-oriented configuration it can support a master oriented to specific device characteristics; e.g., a disk with 10,000 bytes/track, 7 tracks/cylinder, 500 cylinders/actuator.

#### 6.3 Facility

The facility is addressable through the slave. It is the responsibility of the slave to manage the facility. A facility may or may not have generic functionality and may or may not be a device.

#### 6.4 Multi-Tier Structure

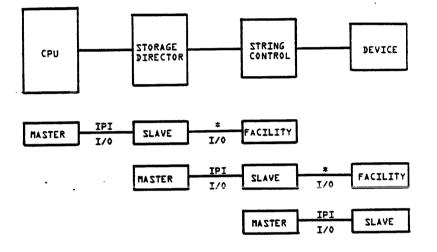

Figure 2 (A) illustrates a mainframe configuration and in a parallel manner shows that the Storage Director can be both slave to the CPU and master to the String Control. The CPU can directly address the String Control through the Storage Director.

The figure also shows the String Control can be both slave to the Storage Director and master to the Device. The Storage Director can directly address devices through the String Control.

Figure 2 (B) illustrates a minicomputer configuration and in a parallel manner shows that the Controller can be both slave to the CPU and master to the Device. The CPU can directly address devices through the Controller.

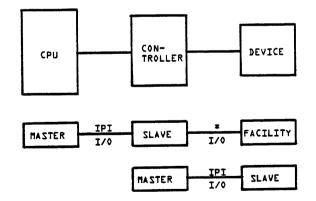

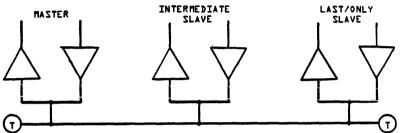

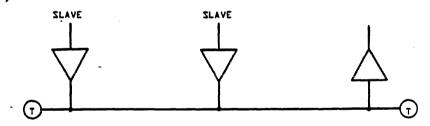

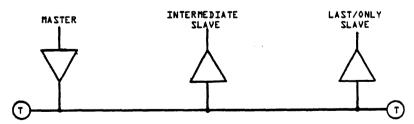

Figure 3 illustrates cabling alternatives for configurations that have a master at one end of the cable, a slave at the other, with intermediate slave(s). Other electrically valid configurations may be used, even if they are not shown. CD MAGNETIC PERIPHERALS INC.

# ENGINEERING SPECIFICATION

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

13

TWIN CITIES DISK DIVISION

#### 6.5 Cable Configuration

A maximum of 8 slaves may be connected to the master. Typically, this would be by a daisy chain signal cable configuration, but radial connection is permitted. Some precautions must be taken to properly handle interface features such as dominant slaves if radial connections are used.

Flat and round cable assemblies may be interconnected. Cables with 50-pin connectors allow cables to be joined if a slave has to be removed from the interface for any reason (this is the rationale for requiring alternating retention hardware on opposite ends of the cable). It is also possible to use a single connector with both an in and an out cable such that the daisy chain is not broken by the removal of a slave or facility.

When using the shielded connector in a daisy chain configuration, the master shall have a female panel connector per channel, and each slave shall have both a female and a male panel connector per channel. Line termination shall be provided at both ends of the daisy chain.

The maximum cumulative cable length in a daisy chain is 213 feet.

The minimum cable configuration dependent time period is 200 ns

The maximum streaming transfer rates are:

| Single octet mode – 5 MB/s  | Interlocked transfer rates may |

|-----------------------------|--------------------------------|

|                             | exceed these rates over short  |

| Double octet mode - 10 MB/s | distances.                     |

SPEC

64731602

CD

5

REV

5

DATE

5

PAGE

14

TWIN CITIES DISK DIVISION

#### 7.0 INTERFACE

The purpose of the interface is to exchange information between connected devices and meet the criteria of:

- 1. Content Independence The operation of the interface is not affected by the contents of Information Transfers.

- 2. Speed Independence The control of the interface is not timing critical in handling of the interface protocol.

- 3. Protocol Integrity The integrity of the protocol sequences is ensured by requiring that each signal change be handshaked. No more than one signal is permitted to change at any time, except during optional Data Streaming transfers.

The characteristics of the physical interface are:

- 1. A daisy chained cable consisting of 24 signal pairs.

- 2. Master/Slave mode of execution.

- 3. One master only.

- 4. Up to 8 slaves allowed, with up to 16 facilities per slave.

- 5. Master selection of slave.

- 6. Except for Selection, a master can allocate control of interface functions to a dominant slave.

- 7. Bus Exchanges are used to frame Information Transfers and are executed only as interlocked and unidirectional.

- 8. Information Transfers occur using either the unidirectional configuration or in a 16 bit bidirectional configuration. The two can co-exist on the same cable.

- 9. Information Transfers are asynchronous and interlocked except during Data Streaming.

- 10. Information Transfers can be terminated in either direction by either the master or the slave.

- 11. The terms In and Out are always used in reference to the master.

SPEC 64731602 CD 5 REV DATE PAGE 15

TWIN CITIES DISK DIVISION

The following apply to the use of BUS A and BUS B.

- 1. The uses of BUS A and BUS B are structured to optimize operations between Bus Exchanges and Information Transfers.

- 2. The Bus Control sequence is initiated by the master and is associated with control of the Physical Interface. The Ending Status sequence is initiated by the slave and is associated with reporting the status of the Bus Exchange or the preceding Information Transfer.

- 3. During Bus Exchanges BUS A is unidirectional Out from the master for Bus Control and Master Status (optional), and BUS B is unidirectional In to the master for Bus Acknowledge (optional) and Slave Status.

- 4. Information Transfer is the term used to indicate the various types of information (Data, Operation Command, or Operation Response) that are transparently transferred across the Physical Interface.

- 5. Bus Exchanges are defined as framing (bracketing) Information Transfers. The differentiation between Bus Exchanges and Information Transfers allows a simple state machine to control Bus Exchanges e.g. the timing independent Bus Exchanges can be interpreted by a general purpose microprocessor.

- 6. Only one control signal shall change at a time between master and slave, and an In control signal change shall be interleaved with an Out control signal change such that the source of control signal changes is alternated between them, thus effectively interlocking all control functions. Optional Data Streaming transfers need not comply with this requirement.

- Operation Commands are issued by the master and are associated with operation of the Logical Interface. Operation Responses are returned by the slave. Both occur as Information Transfers.

- 8. During Information Transfers there can be two modes:

- a. In Single Octet Mode, Information Transfers are 8 bit unidirectional; i.e., BUS A Out, BUS B In.

- b. In Double Octet Mode BUS A and BUS B are used to transfer

16 bits in parallel either In or Out as required.

- 9. If unused bits are listed as "Reserved" they shall be set to zero. The sender is responsible for ensuring zeros. The receiver may choose whether or not to verify that the zeros are present.

SPEC

64731602

CD

5

REV

5

DATE

5

PAGE

16

TWIN CITIES DISK DIVISION

- 10. If unused bits are listed as undefined then there is no requirement for either sender or receiver to care about content. Octet parity must still be maintained.

- 11. In states where the Bus contents are bit significant addresses, octet parity need not be correct.

- 12. Parity shall be generated by the originator and checked by the receiver, except where noted.

7.1 Signals

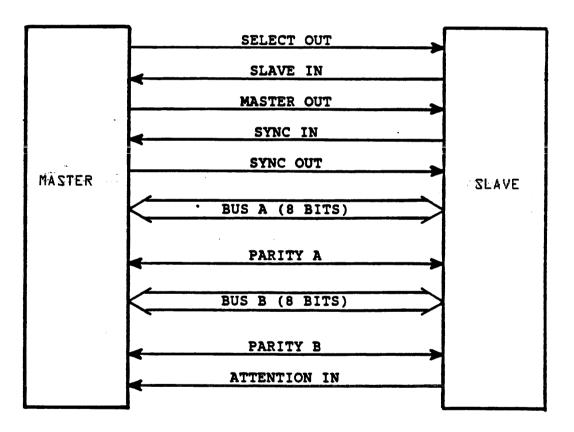

The interface signals are summarized in Figure 4.

7.1.1 Signal Nomenclature

The nomenclature used to define voltage levels, signal states, logical states, and their correlation to each other is defined in Table 2.

- 7.1.2 Signal Usage

- 7.1.2.1 Select Out

SELECT OUT is sent from the master to the slave(s) to select a slave and maintain selection. When SELECT OUT is inactive all slaves shall release BUS A. Dominant slaves shall release MASTER OUT and SYNC OUT drivers upon sensing the negation of SELECT OUT by the master.

7.1.2.2 Slave In

SLAVE IN is used by the slave to either indicate acknowledgement of master initiated control sequences, or to terminate Information Transfers.

7.1.2.3 Master Out

MASTER OUT is used by the master to initiate or terminate Information Transfers, Request Interrupts, Request Transfer Mode, or Reset slave(s).

7.1.2.4 Sync In

When SYNC IN is asserted during transfers In, information is valid on the Bus(es). When SYNC IN is asserted during transfers Out the slave is ready to accept information.

NOTE: To deskew, the information In is asserted on the bus(es) a minimum time before SYNC IN is asserted. SYNC IN is asserted to acknowledge the Bus Control octet during the Bus Control sequence.

SPEC 64731602 CD 5 REV DATE. PAGE 17

TWIN CITIES DISK DIVISION

7.1.2.5 Sync Out

When SYNC OUT is asserted during transfers In the information has been accepted by the master. When SYNC OUT is asserted during transfers Out information is valid on the bus(es).

NOTE: To deskew, the information Out is asserted on the bus(es) a minimum time before SYNC OUT is asserted. SYNC OUT is asserted to initiate the Bus Control sequence.

During reset. SYNC OUT is asserted without response for a minimum time (see Figures 12 and 16).

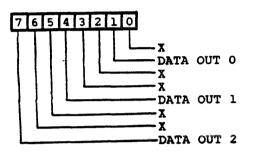

#### 7.1.2.6 Bus A

BUS A consists of nine lines (Bits 7 - 0 plus parity). Bit 7 is the most significant bit. Parity is odd.

BUS A is used by the master for all control sequences. For Information Transfers in Single Octet Mode, all information is passed from the master to the slave on BUS A. In Double Octet Mode information is passed from the master to the slave or from the slave to the master on BUS A. BUS A is considered to be the first octet of double octet information. BUS A shall be released by all slaves when SELECT OUT is negated.

#### 7.1.2.7 Bus B

BUS B consists of nine lines (Bits 7 - 0 plus parity). Bit 7 is the most significant bit. Parity is odd.

BUS B is used by the slave for all control sequences. For Information Transfers in Single Octet Mode, all information is passed from the slave to the master on BUS B. In Double Octet Mode information is passed from the slave to the master or from the master to the slave on BUS B. BUS B is the other octet in a double octet of information.

#### 7.1.2.8 Attention In

ATTENTION IN is not considered a control signal.

ATTENTION IN is a wired-OR signal for all slaves to inform the master that service is requested. The master has the responsibility to service the interrupts (or class of interrupts) as required.

This signal does not contribute to determining the state of the interface. It can be asserted regardless of whether a slave is selected or not.

The ATTENTION IN signal shall not be driven to inactive.

SPEC

64731602

CD

5

REV

DATE

PAGE

18

TWIN CITIES DISK DIVISION

#### 7.2 States

The states of the interface are defined by the condition of the control signals: SELECT OUT, SLAVE IN, MASTER OUT, SYNC IN, and SYNC OUT. With the exception of Data Streaming transfers (optional), these signals are interlocked between the master and the slave.

#### 7.2.1 Idle

When all the control signals are inactive the interface is in the IDLE state. Abnormal entries to this state shall occur whenever the master and slave(s) recognize an undefined state or state transition. The buses are released prior to entering the IDLE state except during the Request Interrupts and Master Reset sequences.

#### 7.2.2 Maintenance

The master negates MASTER OUT, SYNC OUT and then SELECT OUT. The master then releases BUS B, negates BUS A, and then asserts SYNC OUT to enter the MAINT (Maintenance Mode) state.

This state initiates Maintenence Mode on all slaves.

7.2.3 Request

While in IDLE the master sets the Request Modifier octet on BUS A, then asserts MASTER OUT to enter the REQUEST state.

This state causes the slave(s) to respond with either the Address octet, the Transfer Settings octet, or to initiate Selective Reset.

7.2.4 Selective Reset 1 - RESETSEL1

While in REQUEST the master asserts SYNC OUT to enter the RESETSEL1 state.

This state initiates a reset of the slave identified by the Selective Reset Control octet on BUS A, and terminates Maintenance Mode.

#### 7.2.5 Selective Reset 2 - RESETSEL2

The slave entered REQUACK (Request Acknowledge) state in response to REQUEST. While in the REQUACK state the master asserts SYNC OUT to enter the RESETSEL2 state. The slave shall release or negate all interface lines upon recognition of this state, which then causes an entry to RESETSEL1.

While in REQUEST, the slave sets the requested response on BUS B, then asserts SLAVE IN to enter the REQUACK state.

SPEC

64731602

CD

5

REV

5

DATE

5

PAGE

19

TWIN CITIES DISK DIVISION

7.2.6 Deselected - DESEL

While in REQUACK the master negates MASTER OUT to enter the DESEL state. While in SLAVACK the master negates SELECT OUT to enter the DESEL state.

This state initiates the deselection of the slave by the master.

7.2.7 Select - SELECT

While in IDLE the master sets the Selection octet on BUS A then asserts SELECT OUT to enter the SELECT state. This state initiates the Selection Sequence.

While in SLAVEND the master sets the Master Status octet on BUS A, and negates MASTER OUT to enter the SELECT state.

- NOTE: In the SELECT state it is necessary to know the previous transition in order to respond correctly. When entered from IDLE, it is a true Selection (and the slave responds with Select Status on BUS B). When entered from SLAVEND, SELECT is an intermediate state following an Information Transfer between the master and the selected slave.

- 7.2.8 Slave Acknowledge SLAVACK

While in SELECT following IDLE the addressed slave sets its Select Status on BUS B, then asserts SLAVE IN to enter the SLAVACK state.

While in SELECT following SLAVEND the selected slave sets the Slave Status octet on BUS B, then asserts SLAVE IN to enter the SLAVACK state.

While in MASTEND the selected slave negates SYNC IN to enter the SLAVACK state. BUS B is not valid during this transition.

This state acknowledges either selection, the end of a Bus Control sequence, or the end of an Information Transfer.

NOTE: In the SLAVACK state it is necessary to know the previous transition because BUS B contains different contents depending upon the state from which SLAVACK was entered.

While in SLAVACK the master sets the Bus Control octet on BUS A then asserts SYNC OUT to enter the BUSCTL (Bus Control) state.

This state initiates control of the subsequent Information Transfer.

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

20

TWIN CITIES DISK DIVISION

7.2.9 Bus Acknowledge - BUSACK

While in BUSCTL the slave sets the Bus Acknowledge octet on BUS B, then asserts SYNC IN to enter the BUSACK state.

This state is complementary to BUSCTL to acknowledge that the Bus Control octet has been accepted.

7.2.10 Master End - MASTEND

While in BUSACK the master negates SYNC OUT to enter the MASTEND state.

While in XFRST the master negates MASTER OUT to enter the MASTEND state.

This state either acknowledges that the Bus Acknowledge octet has been accepted, or it initiates termination of an Information Transfer by the master. CONTROL DATA COMPANY

# ENGINEERING SPECIFICATION

SPEC

64731602

CD

5

REV

DATE

PAGE

21

TWIN CITIES DISK DIVISION

#### 7.2.11 Ready To Transfer - XFRRDY

While in SLAVACK the master asserts MASTER OUT to enter XFRRDY state.

When beginning transfers In, the assertion of MASTER OUT indicates to a slave operating in Double Octet Mode that the master has released BUS A.

When beginning transfers Out, the assertion of MASTER OUT directs a slave operating in Double Octet Mode to release BUS B.

While in XFREND the master negates SYNC OUT to enter the XFRRDY state.

This state is initiated by the master to transfer each octet (or double octet) of an Information Transfer.

While in XFRRDY for transfers In the slave sets information on the bus(es), then asserts SYNC IN to enter the XFRST (Start To Transfer) state.

While in XFRRDY for Transfers Out, the slave asserts SYNC IN to enter the Start To Transfer state. The master maintains control of the Bus(es).

This state is initiated by the slave to acknowledge the start of Information Transfer. For transfers Out it indicates that the slave is ready to accept information and for transfers In it is used to validate that the Bus(es) have stable information.

7.2.12 Respond To Transfer - XFRRES

While in XFRST for transfers Out the master sets information on the Bus(es) then asserts SYNC OUT to enter the XFRRES state.

While in XFRST for transfers In, the master accepts information on the Bus(es), then asserts SYNC OUT to enter the Respond To Transfer state. The slave maintains control of the Bus(es).

This state is initiated by the master to acknowledge the acceptance of information on the Bus(es) for transfers In, or to validate that the Bus(es) have stable information on transfers Out.

Printed in U.S.A.

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

22

TWIN CITIES DISK DIVISION

#### 7.2.13 End Of Transfer - XFREND

While in XFRRES the slave negates SYNC IN to enter the XFREND state. For transfers Out the master maintains control of the Bus(es). For transfers In the slave maintains control of the Bus(es).

This state is initiated by the slave to acknowledge the acceptance of information on transfers Out, and to complete the transferring of each octet (or double octet) of an Information Transfer.

#### 7.2.14 Slave End - SLAVEND

While in XFRRDY the slave negates SLAVE IN to enter the SLAVEND state. When in Double Octet Mode for transfers Out the master releases control of BUS B; for transfers In during Double Octet Mode, this acknowledges the release of BUS A by the slave.

This state is initiated by the slave to terminate an Information Transfer.

#### 7.2.15 State Summary

The determination of bus contents requires remembering the previous state transition in two states. The two states which have defined bus contents only when entered from a particular previous state are SLAVACK when entered from SELECT or MASTEND, and SELECT when entered from IDLE or SLAVEND.

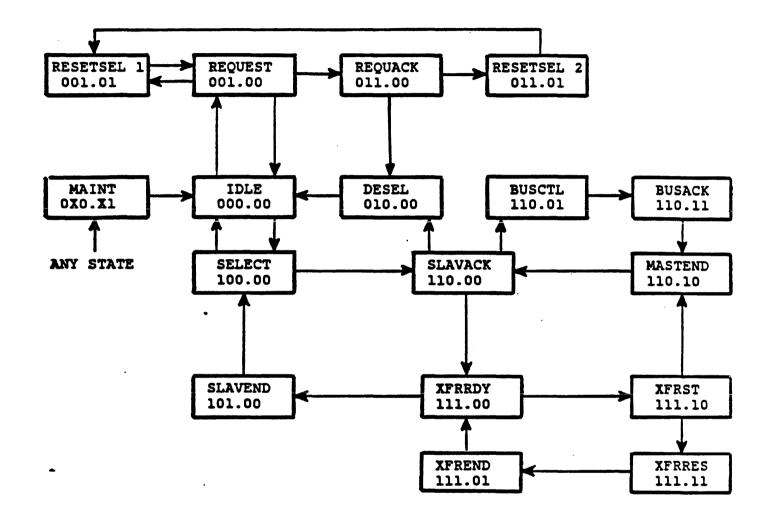

The states are summarized in Table 3 and are schematically shown in Figure 5.

Table 4 defines BUS A and BUS B for every valid state transition for both input and output. It also notes the interface signals.

The table supplements the timing diagrams. Its purpose is to provide a snapshot at two different times, from the perspective of the initiator and the respondee:

Initiator - the table identifies the responsibility of the initiator for bus contents at the time it changes a signal to begin transition to a new state.

Respondee - the table identifies the bus contents at the time that the respondee recognizes the state signalled by the initiator.

Wherever DOM is referenced it identifies that there is a special requirement to release the bus other than that used in SOM and control functions. It is also implied that the bus is undefined in SOM. In SOM configurations it is not necessary for the master or selected slave to release the buses.

CONTROL DATA COMPANY

# ENGINEERING SPECIFICATION

SPEC 64731602 CD 5 REV DATE PAGE 23

TWIN CITIES DISK DIVISION

#### 7.2.16 Undefined State Recovery

An undefined state or state transition induced by a slave shall cause the master to begin abnormal deselection by releasing the Bus(es) and negating all OUT signals. SELECT OUT shall be the last signal line negated, unless Slave to Slave Informations Transfers are in progress (see 7.3.9.2). When the slave is deselected it releases the Bus(es) it may be driving, then negates SYNC IN and SLAVE IN. The interface is thus returned to the IDLE state, and the master can resume operations.

An undefined state or state transition induced by a master shall cause the slave to release the Bus(es) it may be driving, then negate SYNC IN and SLAVE IN. When the master recognizes the negation of SLAVE IN outside of a valid sequence it releases the Bus(es) and negates all OUT signals. SELECT OUT shall be the last signal line negated. The interface is thus returned to the IDLE state, and the master can resume operations.

NOTE: The negation of SLAVE IN and SYNC IN is valid during defined sequences such as SLAVEND from XFRRDY. SLAVE IN and SYNC IN are not active during REQUEST, SELECT and SLAVEND.

7.2.17 Slave End Without Information Transfer

There is no requirement that an Information Transfer has to occur between Bus Control and Slave Status. The following refers to sequences when an Information Transfer is expected to occur.

If a slave senses a parity error or illegal Bus Control octet on BUS A during a Bus Control Sequence, it shall terminate the sequence normally. When the master attempts the subsequent information transfer, the slave shall negate SLAVE IN upon sensing the assertion of MASTER OUT, and enter SLAVEND from XFRRDY.

Entering SLAVEND without an Information Transfer indicates to the master that the slave did not accept the Bus Control octet. The cause of the slave rejection of the Bus Control shall be reported to the master in the Slave Status Octet during the SLAVACK state.

SPEC 64731602 CD 5 REV DATE PAGE 24

TWIN CITIES DISK DIVISION

#### 7.2.18 Master End Without Information Transfer

During a slave-controlled Information Transfer (optional), if the master detects a parity error or an illegal Bus Acknowledge octet on BUS B during the Bus Control sequence, it shall terminate the sequence normally. The sequence shall proceed normally from BUSACK through MASTEND to SLAVACK. While in SLAVACK the master can either assert SYNC OUT to enter BUSCTL and restart the Bus Control sequence, or negate SELECT OUT to enter DESEL and deselect the slave.

The deselection sequence, or the restarting of the Bus Control sequence indicates to the slave that the master did not accept the Bus Acknowledge octet.

7.2.19 Slave Action on Bus A Parity Errors

7.2.19.1 Selection Octet

If the slave detects a parity error on BUS A during SELECT, it shall not respond to the contents of the octet for selection purposes. If the master fails to receive a response from the selected slave within a time-out period, it shall retry the SELECT sequence.

7.2.19.2 Request Modifier Octet

If the slave detects a parity error on BUS A during REQUEST, it shall not respond to the contents of the octet. If the master fails to receive a response from at least one slave within a time-out period, it shall retry the REQUEST sequence.

7.2.19.3 Master Status Octet

If the slave detects a parity error on BUS A during the SELECT state, it shall not interpret the contents of the octet. It shall assume the Information Transfer, if any, was unsuccessful and post accordingly in the Slave Status octet.

7.2.19.4 Bus Control Octet

If the slave detects a parity error on BUS A during BUSCTL, it shall not interpret the octet and shall post the parity error in Slave Status octet.

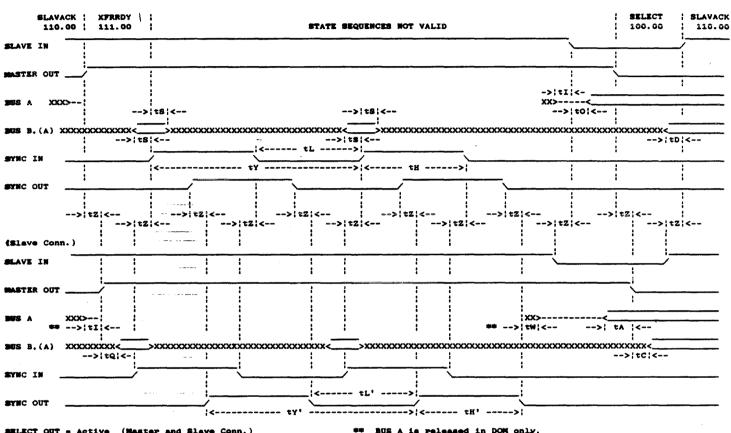

7.3 Sequences

The Bus State diagram of Figure 5 summarizes the possible state transitions. The condition of the buses during all of the states and transitions is shown in Table 4. CONTROL DATA COMPANY

# ENGINEERING SPECIFICATION

SPEC

64731602

CD

5

REV

DATE

PAGE

25

TWIN CITIES DISK DIVISION

#### 7.3.1 Request Sequences

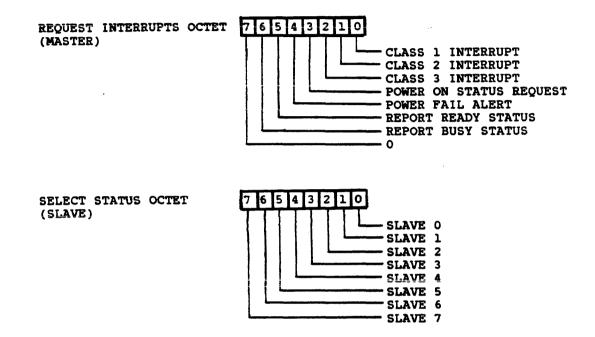

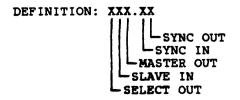

7.3.1.1 Request Interrupts Sequence (See Figure 6)

This sequence allows the master to interrogate the slaves to determine the service (or class of service) desired.

The master initiates the sequence by setting the Request Modifier on BUS A and asserting MASTER OUT. Slave(s) with interrupts meeting the required Request Modifier conditions (See 7.4.7) place their bit significant address in the Address octet on BUS B. Appropriate latching may be required at the master because interrupts from the slaves can change dynamically. Parity on BUS B shall not be checked by the master. The master negates MASTER OUT to return to IDLE state.

NOTE: The response of the slaves is not synchronous, and the master must wait a time equal to that of the slowest and/or furthest slave to respond before latching or sampling BUS B. In addition, the master must wait for a time equal to that of the slowest and/or furthest slave to detect the IDLE state, and release its bit significant address on BUS B before starting another sequence.

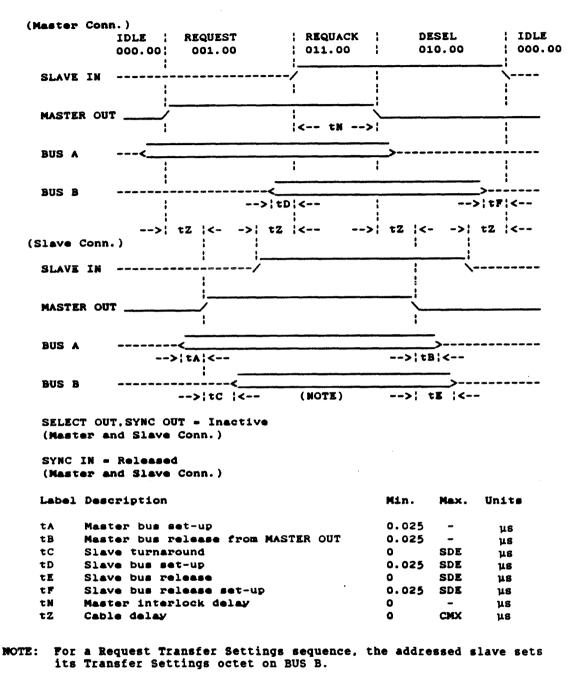

See Figure 7 for timing details.

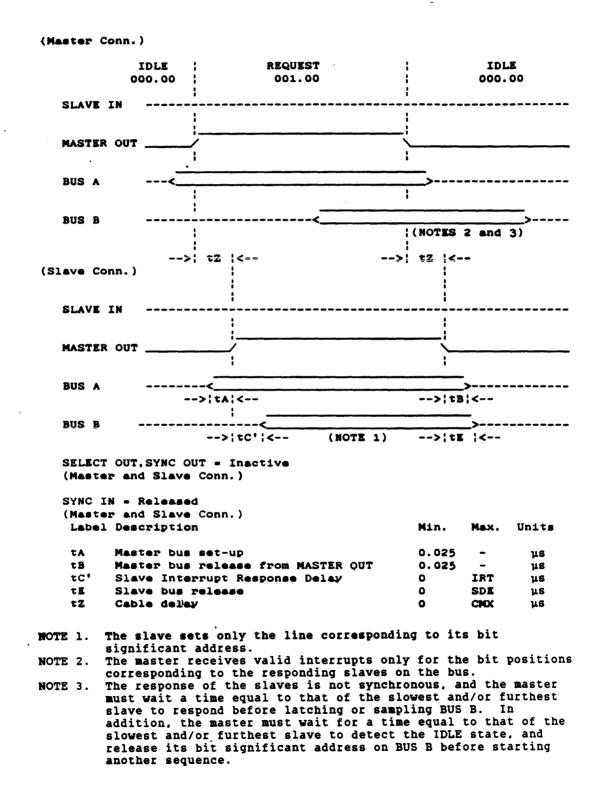

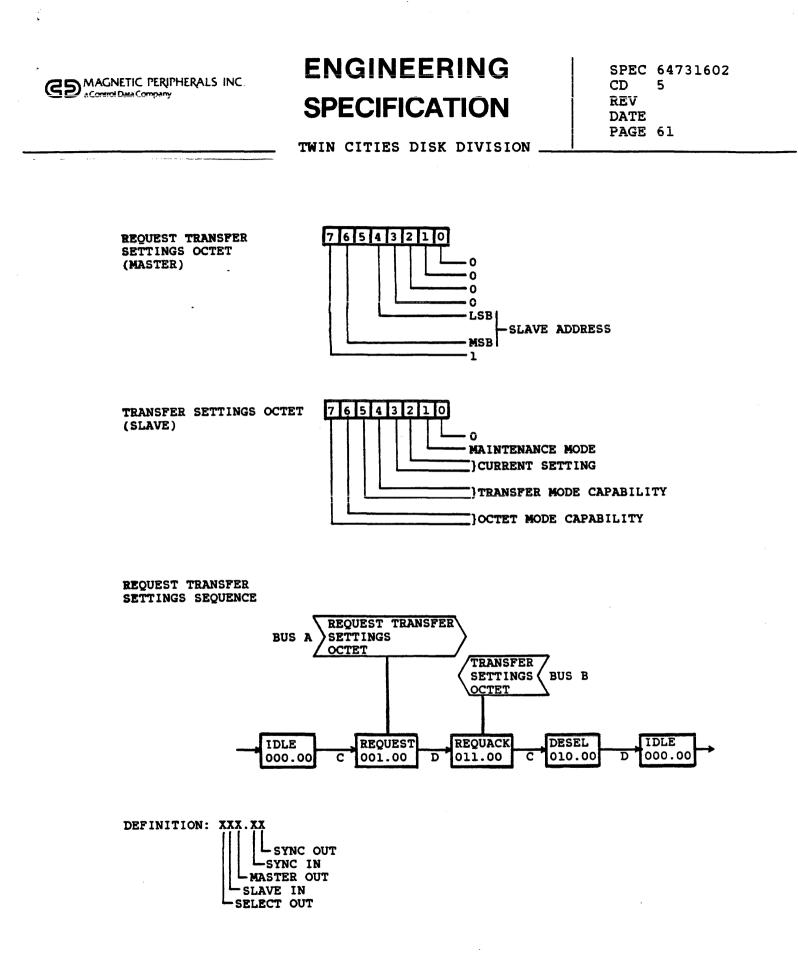

7.3.1.2 Request Transfer Settings Sequence (See Figure 8)

This sequence allows the master to interrogate the specified slave as to its Information Transfer characteristics.

The master initiates the sequence by placing the Request Transfer Settings octet on BUS A (See 7.4.7.3) and asserting MASTER OUT. The addressed slave responds by setting the Transfer Settings Response octet on BUS B, and asserting SLAVE IN. The master then negates MASTER OUT to reach the Deselection State and SLAVE IN is negated to return to IDLE State.

See Figure 9 for timing details.

7.3.1.3 Request Facility Interrupts Sequence (Optional)

This sequence allows the master to interrogate the facilities of the specified slave to determine the service (or class of service) desired. The sequence is the same as that for Request Transfer Settings. The contents of the Request Modifier octet affect the slave's octet response.

SPEC

64731602

CD

5

REV

5

DATE

5

PAGE

26

TWIN CITIES DISK DIVISION

The master initiates the sequence by placing the Request Facility Interrupts octet on BUS A (See 7.4.7.2) and asserting MASTER OUT. Facilities on the specified slave which have interrupts meeting the required Request Modifiers conditions set the Address octet on BUS B, and the slave asserts SLAVE IN. Appropriate latching may be required at the master because interrupts from the facilities can change dynamically. Parity shall not be checked on BUS B by the master. The master then negates MASTER OUT to reach the DESEL state, and SLAVE IN is negated to return to IDLE state.

See Figure 9 for timing details.

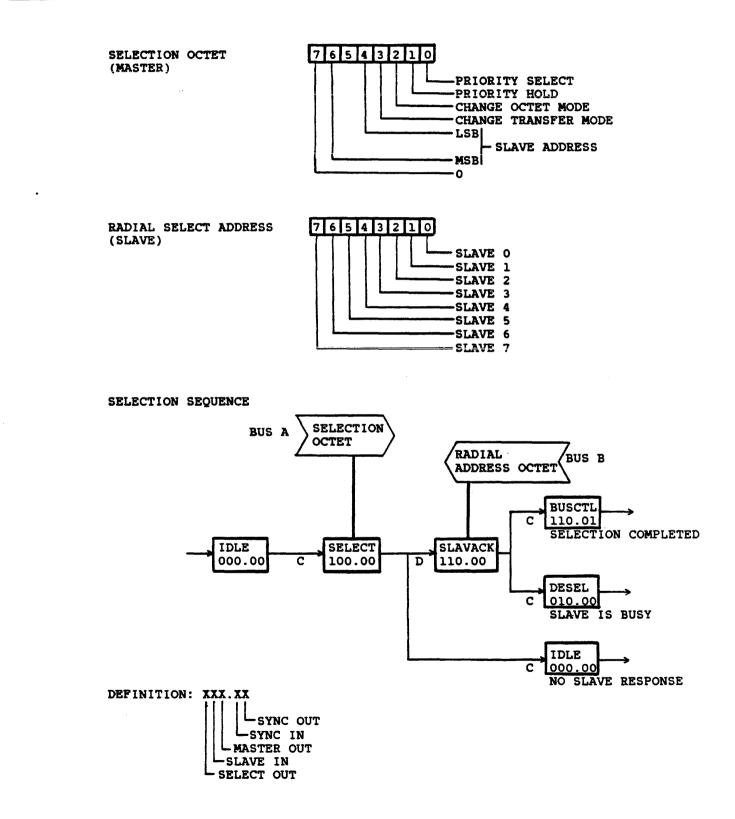

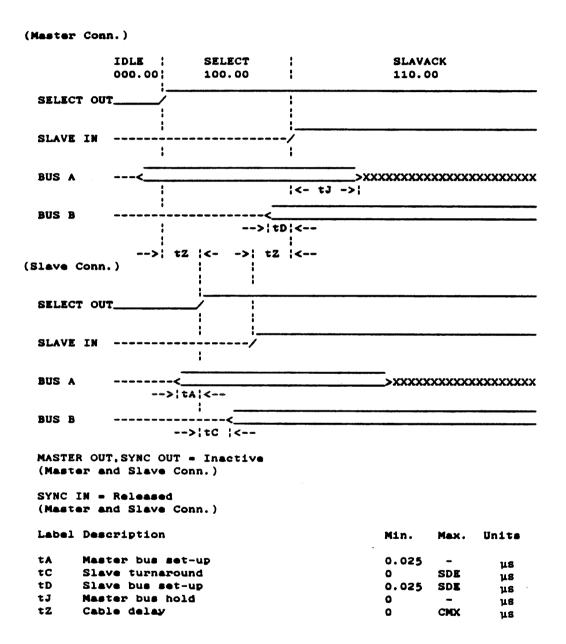

7.3.2 Selection Sequence (See Figure 10)

The Selection sequence occurs when the master addresses a slave (or a slave and its facilities). The selection sequence is as follows:

The master places the Selection octet containing the slave address, andoptionally the facility address on BUS A, then asserts SELECT OUT to enter the SELECT state.

If the slave can process Bus Exchanges or Information Transfers, the slave places its (the slave's) bit significant address in the Address octet on BUS B and then asserts SLAVE IN to enter the SLAVACK state.

If the slave cannot process Bus Exchanges or Information Transfers, but is otherwise functioning normally, the slave asserts only SLAVE IN to report the Busy condition by entering the SLAVACK state. This Busy condition reflects only the current condition of the slave and does not necessarily reflect the current condition of the addressed facility when the facility address is optionally placed on BUS A.

If there is a parity error on BUS A, none of the slaves are selected, and SLAVE IN is not asserted.

See Figure 11 for timing details.

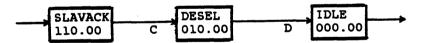

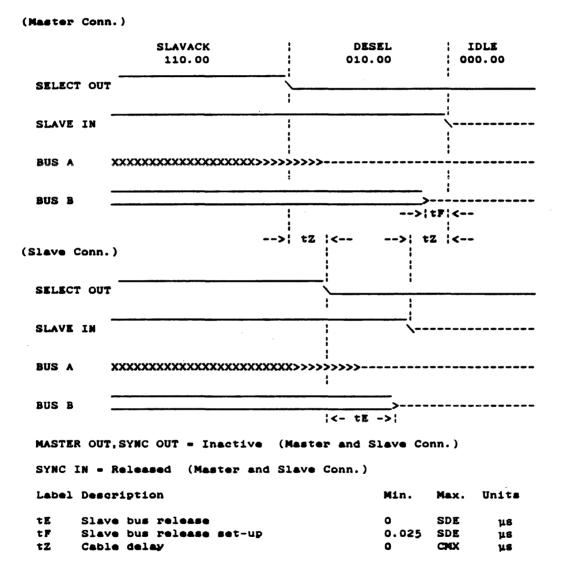

7.3.3 Normal Deselection Sequence (See Figure 12)

Selection is maintained while SELECT OUT remains active. When SELECT OUT is negated, the addressee is deselected. The sequence is as follows:

See Figure 13 for timing details.

SPEC 64731602 CD 5 REV DATE PAGE 27

TWIN CITIES DISK DIVISION

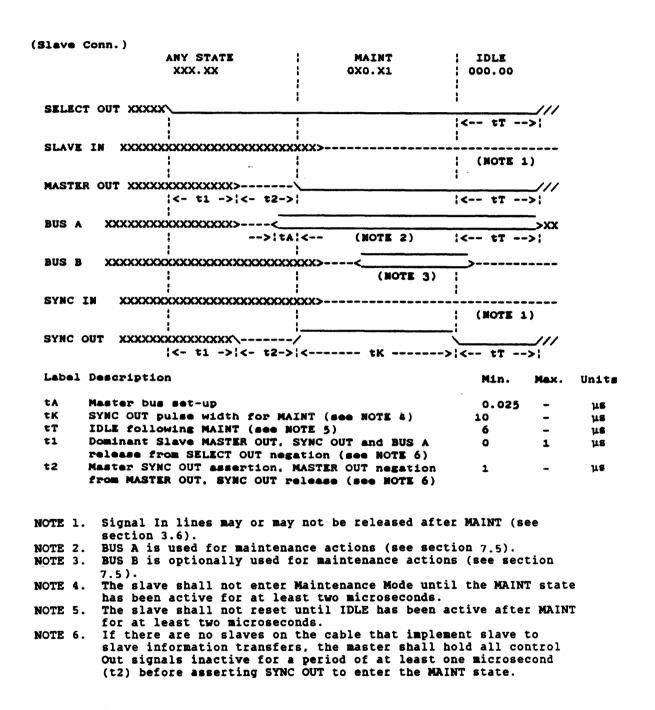

7.3.4 Master Reset Sequence (See Figure 14)

The Master Reset sequence allows the master to initiate Maintenance Mode.

The master initiates the sequence by ensuring that SELECT OUT and MASTER OUT are not active, and then asserting SYNC OUT for a minimum of 10  $\mu s$ .

Recognition of the MAINT state shall be independent of normal state processing logic. The slave shall not enter Maintenance Mode until the MAINT state has been active for at least 2 µs.

See Figure 15 for timing details.

See 7.5 for details on Maintenance Mode.

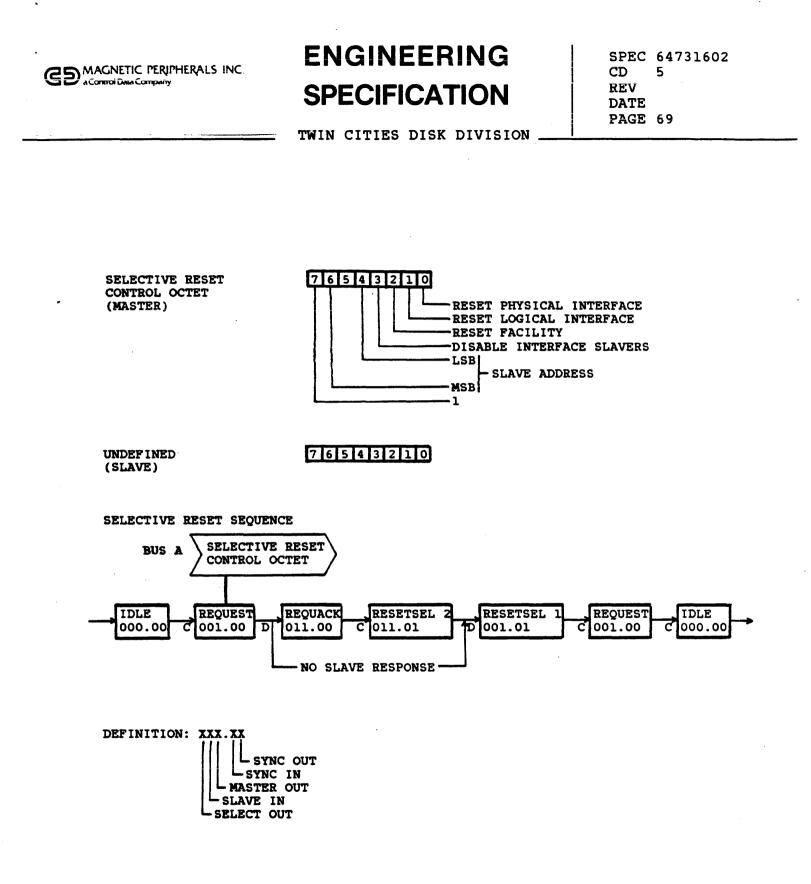

7.3.5 Selective Reset Sequence (See Figure 16)

The Selective Reset sequence allows the master to reset a single slave and terminate the Maintenance Mode. The sequence is as follows:

The master initiates the sequence by placing the Selective Reset Control octet on BUS A and asserting MASTER OUT. The master shall then allow the slave time to respond by asserting SLAVE IN but will disregard SLAVE IN and the contents of BUS B if asserted by the slave. The master shall then assert SYNC OUT for a minimum of 10  $\mu$ s, before negating SYNC OUT and returning to the REQUEST state.

The slave shall neither initiate its reset action nor release its interface lines until RESETSEL1 has been active for at least 2  $\mu$ s. The master shall then allow the slave time to respond by asserting SLAVE IN. Whether the slave responds or not the master completes the sequence by negating MASTER OUT and monitoring the interface to ensure that the slave completes the sequence by negating SLAVE IN.

Recognition of Selective Reset shall be independent of normal state processing logic.

See Figure 17 for timing details.

7.3.6 Bus Exchange

The Bus Exchange is started by the master with a Bus Control sequence to set up an Information Transfer, and completed by the slave with an Ending Status sequence when the transfer is ended.

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

28

TWIN CITIES DISK DIVISION

7.3.6.1 Bus Control Sequence (See Figure 18)

The Bus Control sequence allows the master (or optionally the slave), to establish the bus configuration for the subsequent Information Transfer.

The Bus Control sequence is initiated by the master after either Select Status (following selection) or Slave Status (following an Information Transfer) has been accepted. The master sets the Bus Control octet on BUS A and asserts SYNC OUT. The slave responds by setting the Bus Acknowledge octet on BUS B, and asserting SYNC IN. The master ends the sequence by negating SYNC OUT. Note that although the interface returns to SLAVACK when the slave responds by negating SYNC IN that there is no Slave Status octet on BUS B because it is simply an intermediate state on the way to beginning an Information Transfer.

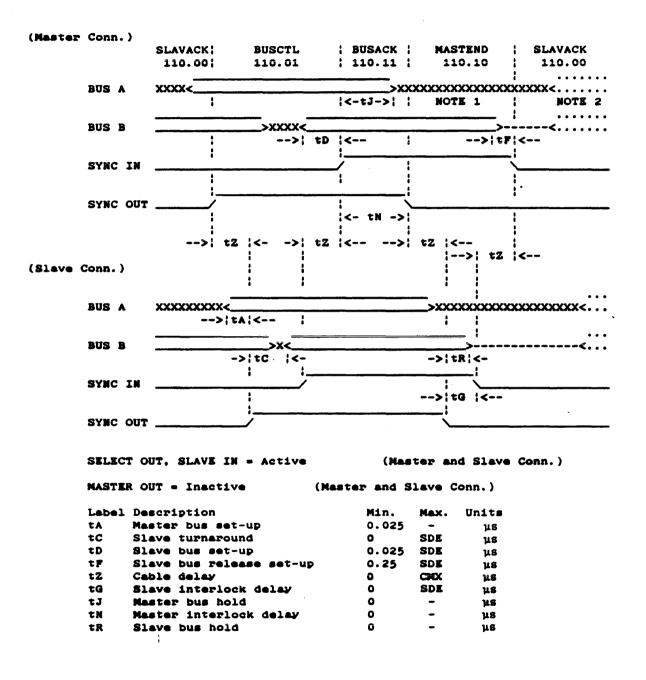

See Figure 19 for timing details.

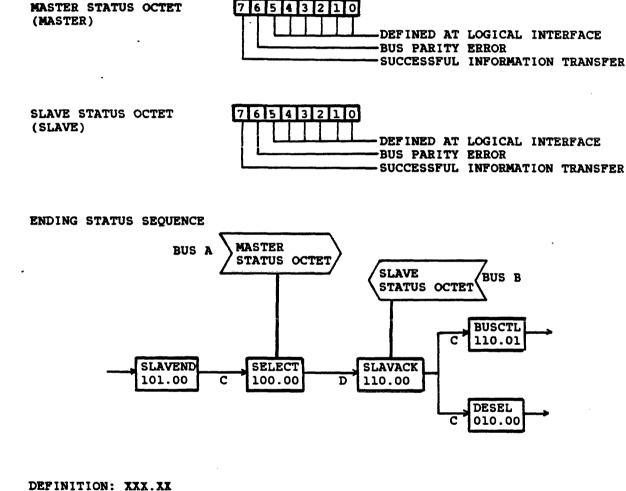

7.3.6.2 Ending Status Sequence (See Figure 20)

The Ending Status sequence allows the slave (or optionally the master and the slave), to present the status of the previous Information Transfer (if any).

To enter SLAVEND, the slave terminates the Information Transfer by releasing BUS B (Double Octet Mode, transfers In) and negating SLAVE IN. The master responds by releasing BUS B (Double Octet Mode, transfers Out), setting the Master Status octet on BUS A and negating MASTER OUT. The slave then sets the Slave Status octet on BUS B and re-asserts SLAVE IN to enter the SLAVACK state.

See Figures 21A through 21E for timing details.

7.3.7 Information Transfer Sequence

Information Transfer sequences differ depending on whether the ending of a transfer is initiated by the master or by the slave. The slave may terminate a sequence without the transfer of information.

Figures 22, 23, and 25 represent the sequence of states necessary for Information Transfers. In the following paragraphs (7.3.7.1 through 7.3.7.4) each line is labelled A-E, corresponding to the description below, to illustrate the separate parts of the sequence. An Information Transfer is framed by a Bus Exchange:

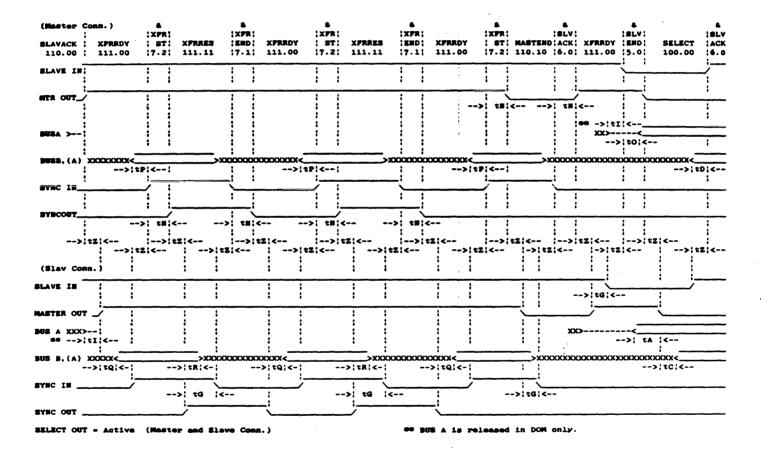

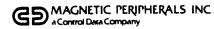

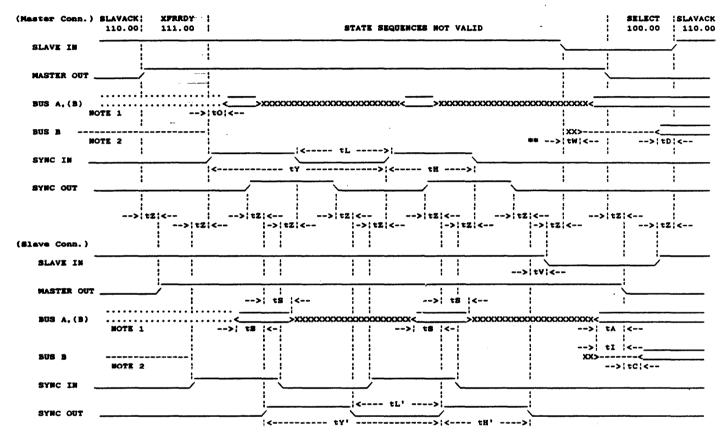

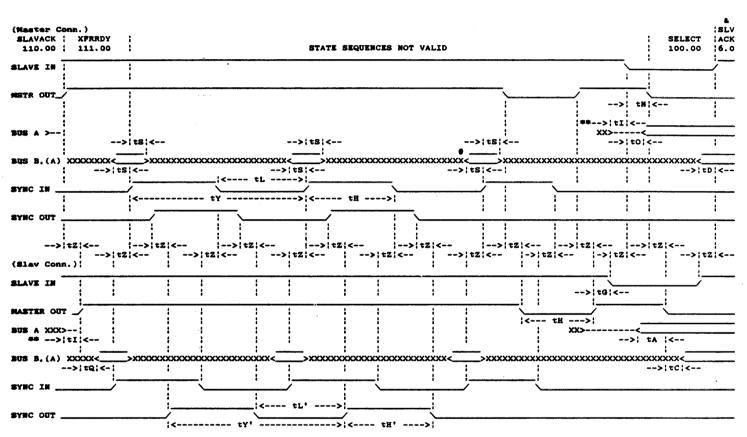

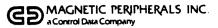

See Figures 24 and 26 for timing details.

| A                  | A B-C-D                              |                               |

|--------------------|--------------------------------------|-------------------------------|

| Bus Control <br>++ | ++<br>  Information Transfer  <br>++ | ++<br>  Ending Status  <br>++ |

SPEC 64731602 CD 5 REV DATE PAGE 29

TWIN CITIES DISK DIVISION

7.3.7.1 Operation Command Transfer

A Condition Bus for transfers Out

Bus Control sequence

Bus Control sequence

Ending Status sequence

Out Bus Control sequence

Ending Status sequence

Ending Status sequence

Information Transfer sequence

Information Transfer sequence

Information Transfer sequence

Information Transfer sequence

D Master initiated termination (if any) Ending Status sequence

7.3.7.2 Operation Response Transfer

- A Condition Bus for transfers In

- B First transfer In

B Request transfer Out

- C Additional transfers In

- E Ending Status

C Transfers Out

E Ending Status

7.3.7.3 Data Transfer Out

- A Condition Bus for transfers

- B Request transfer Out

- C Transfers Out

- D Master initiated termination (if any)

- E Ending Status

7.3.7.4 Data Transfer In

- A Condition Bus for transfers In Bus Control sequence B First transfer In

- C Additional transfers In

- D Master initiated termination (if any)

- E Ending Status

7.3.7.5 Termination Of Information Transfer

The slave terminates an Information Transfer sequence with the Ending Status Sequence. The master initiates the end of the Information Transfer, and the slave terminates with the Ending Status sequence.

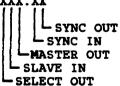

7.3.8 Data Streaming (Optional)

Data streaming is the technique that allows high transfer rates over long cable lengths. This is accomplished by not interlocking SYNC IN and SYNC OUT, which eliminates a round trip cable delay. This allows cable delay to be eliminated in determining transfer rate. Data streaming shall only be used during Information Transfers. All control and status sequences shall be interlocked.

Normal state sequences do not apply during Data Streaming, Note: since fully interlocked operation is not required.

SPEC

64731602

CD

5

REV

0ATE

PAGE

30

TWIN CITIES DISK DIVISION

The Request Transfer Settings sequence is used to ascertain what modes of transfer are possible. Slave attributes may be: interlocked only, Data Streaming only, or both. In the latter case, the master will select the mode to be used during slave selection.

7.3.8.1 Transfer Technique (See Figure 22)

The transfer begins with the slave asserting SYNC IN and then negating it to generate a pulse. The period between succesive pulses is defined by the transfer rate. Upon recognizing the SYNC IN pulse, the master generates a complementary SYNC OUT pulse. The master must "answer" every SYNC IN pulse with a complementary SYNC OUT pulse.

The period between successive SYNC IN pulses is determined by the transfer rate. Upon recognizing the SYNC IN pulse, the master generates a SYNC OUT pulse in response. The SYNC OUT pulse may be generated by the master in two ways:

- 1. Mirror the SYNC IN pulse by detection of leading and trailing edges.

- 2. Use a clock value to create a pulse which is at least 40% of CCD.

- NOTE: The CCD (Cable Configuration Dependent) value that a slave can recognize at the interface is at least equal to, but may be faster than, the rate at which it can transfer data.

The transmitter must insure the proper set-up and hold times with respect to the active edge of its sync pulse.

If the hold time is greater than the one-way cable delay plus set up times the effect is to cause the transfers to appear interlocked.

7.3.8.2 Throttling Transfers (Optional)

A slave transferring from a buffer may be able to permit the master to stop and start the transfer stream.

If at any point in the transfer the slave has transmitted X unanswered SYNC IN pulses where X = 8 (unless X is specified by the master during housekeeping), it shall wait a minimum of 25 ms for a complementary SYNC OUT pulse. If a SYNC OUT pulse is received, operations shall continue normally. If a SYNC OUT pulse is not received, the slave shall end the transfer sequence.

SPEC 64731602 CD 5 REV DATE PAGE 31

TWIN CITIES DISK DIVISION

The effect of this is that after the first X SYNC IN pulses are transmitted by the slave at its chosen transfer rate, all successive SYNC IN pulses shall only be generated upon receipt of a SYNC OUT pulse, thus allowing the master to dictate the period between SYNC IN pulses and throttling the speed at which the slave can transfer.

It is the responsibility of the master to ensure that the SYNC OUT pulses provided to the slave exceed 40% of the CCD (Cable Configuration Dependent) value.

7.3.8.3 Slave Termination of Data Streaming (See Figure 22)

To terminate a Data Streaming transfer, the slave first stops transmitting SYNC IN pulses. It then waits until it has received an equal number of SYNC OUT pulses from the master, or a minimum of 25 milliseconds has expired without pulses, after which it terminates the transfer by negating SLAVE IN and following the normal interlocked Ending Status Sequence.

7.3.8.4 Master Initiated Termination of Data Streaming (See Figure 22)

To terminate a Data Streaming transfer, the master substitutes a SYNC OUT pulse with an inactive pulse on the MASTER OUT line having the same pulse width and period requirements of the SYNC OUT pulse. The master then continues to "answer" every SYNC IN pulse with complementary SYNC OUT pulses.

For transfers Out, the master shall not transmit information with the MASTER OUT pulse or subsequent SYNC OUT pulses.

For transfers In, the master shall accept information with up to 8 SYNC IN pulses, following generation of the MASTER OUT pulse. This allows all information transmitted by the slave before its recognition of the MASTER OUT pulse, to be received by the master, thus maintaining the capability for data integrity.

NOTE: If master initiated termination of Data Streaming is used when the master does not require a precise match between the number of octets transferred by the master and the slave, the master is not required to accept information after generation of the MASTER OUT pulse.

When the slave senses the MASTER OUT pulse, it stops transmitting SYNC IN pulses and waits until it has received an equal number of SYNC OUT pulses, including the MASTER OUT pulse. For transfers Out, the slave shall not latch any information on the MASTER OUT pulse and subsequent SYNC OUT pulses.

SPEC

64731602

CD

5

REV

5

DATE

5

PAGE

32

TWIN CITIES DISK DIVISION

After the slave detects the number of SYNC IN pulses equalling the number of SYNC OUT pulses, including the MASTER OUT pulse, or a minimum of 25 milliseconds has expired without pulses, it negates SLAVE IN and the normal interlocked Ending Status Sequence is followed.

7.3.9 Slave-to-Slave Information Transfers (Optional)

The master can permit transfers to occur between any two slaves on the interface by defining a dominant slave that shall control MASTER OUT and SYNC OUT. The master remains master of the interface because it retains control of SELECT OUT.

7.3.9.1 Information Transfers

It is possible to set up transfers between slaves so that data movement can be accomplished external to the master. This requires the designation of a dominant slave and a subservient slave. The following is a description of how the two are required to operate:

The master first selects the slave that shall be designated the dominant Slave.

Using Operation Commands/Operation Responses the master supplies the identity of the subservient slave to the dominant slave. The dominant slave shall monitor the interface and be prepared to assume control after the master selects the subservient slave. The subservient slave shall have its Select Status octet on BUS B during the SLAVACK state.

If the subservient slave is not busy, the master shall release BUS A and the dominant slave shall assume control of MASTER OUT and SYNC OUT (thus assuming the role of the master on the interface). The master thus permits the dominant slave to initiate Information Transfers with the subservient slave (which is operating normally), but retains through SELECT OUT the ability to abort the operation.

Each time the intermediate SELECT state is entered the dominant slave sets Master Status octet on BUS A. The master monitors this octet to detect the Slave-Slave Operation Completed bit.

The dominant slave relinquishes control to the master by posting the Slave-Slave Operation Completed bit in the Master Status octet. The subservient slave shall proceed normally to enter SLAVACK.

The master terminates the Slave-to-Slave Information Transfer by deselecting the subservient slave. The master shall reselect the dominant slave to obtain the Operation Response.

| 0 | 5 | MAGNETIC          | PERIPHERALS | INC. |

|---|---|-------------------|-------------|------|

| 9 | 2 | a Control Data Co | mpany       |      |

SPEC

64731602

CD

5

REV

0

DATE

9

PAGE

33

TWIN CITIES DISK DIVISION

7.3.9.2 Error Recovery Considerations

If the subservient slave is busy during initial selection the master can continue to retry until successful, or re-select the dominant slave to terminate the process.

If the master must regain control of the bus during the process it does so by de-selecting the subservient slave. The dominant slave shall detect the de-selection as an abnormal termination, and prepare Operation Response for presentation to the master when it is next selected. The subservient Slave shall proceed through normal deselection, if it was in the SLAVACK state when SELECT OUT was negated.

- NOTE: The implementation described in 7.3.9 requires the use of features in the interface which are defined as Optional. In addition, a master which intends to support Slave-Slave Information Transfers must be able to monitor the MASTER OUT and SYNC OUT lines which are under control of the dominant slave.

- 7.4 Bus Octet Definitions

Table 4 defines the usage of bus octets for each state and transition. 7.4.1 specifies the BUS A octet(s), 7.4.2 the associated BUS B response octet(s).

NOTE: The optional functions defined within each each octet are identified by the bits being enclosed in parentheses.

If the octet itself is optional, required bits within it do not have parentheses, only optional bits in an optional octet have parentheses.

7.4.1 BUS A Selection Octet Bit Definitions Presented during the SELECT state.

During the selection sequence, BUS A contains the addressing information for the selection.

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

34

TWIN CITIES DISK DIVISION

7.4.1.1 BUS A Selection Octet

| 7 | 6   |       | 5     | 1  | 4 | 3 | 2                       | 1                     | 0                       |

|---|-----|-------|-------|----|---|---|-------------------------|-----------------------|-------------------------|

| 0 | SL4 | AVE 2 | ADDRE | SS |   |   | CHANGE<br>OCTET<br>MODE | PRIOR-<br>ITY<br>HOLD | PRIOR-<br>ITY<br>SELECT |

When Bit 7=0 the addressed slave shall respond on BUS B to the Selection octet on BUS A (See 7.4.2).

• Slave Address

Bit 4 is the least significant bit (LSB) of the slave address.

• Change Transfer Mode

When Bit 3=1 the addressed slave shall change its current mode of transfer (Interlocked or Data Streaming). See 7.4.8.3

• Change Octet Mode

When Bit 2=1 the addressed slave shall change its current mode of octet operation (SOM or DOM). See 7.4.8.3

• Priority Hold

When Bit 1=1 and a selection is established, the slave shall maintain an explicit allegiance after deselection to this port until:

- a subsequent selection is established without the Priority Hold bit set in the Selection octet or

- a selection by another port is established with both the Priority Hold and Priority Select bits set in the Selection octet or

- an appropriate Reset is executed by the slave.

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

35

TWIN CITIES DISK DIVISION

• Priority Select

When Bit 0=1 the specified slave shall release the current port to which it is dedicated provided that an alternate port does not have a Priority Hold in effect, and shall respond to the requesting master.

If two or more channels of a given slave are in the SELECT state at the same time with the Priority Select bit set in the Selection octet and the slave does not have a Priority Hold in effect for any port not attempting a selection, the slave will connect to one and only one of the channels. The other port(s) shall receive a Busy indication.

A successful selection with the Priority Select bit set in the Selection octet shall cause any other channel with a selection established and not in the SELECT state to terminate its selection. The termination may be orderly or abrupt depending on the slave's implementation.

• Priority Hold and Priority Select

When both Bit 1=1 and Bit 0=1 the specified slave shall release the current channel to which it is dedicated regardless of its previous condition providing another channel had not previously established selection with both of the bits set.

The specified slave shall maintain allegiance to the selected post after deselection until:

- a subsequent selection is established without the Priority Hold and Priority Select bits set or

- an appropriate reset is executed by the slave.

The Truth table provides a definition of the interaction of two channels given that Channel A action occurs prior to Channel B action. For the conditions under Channel A Not Selected, the slave was last selected by Channel A with the given value of PH (Priority Hold) and PS (Priority Select). For the conditions under Channel A Selected, the slave is currently selected on Channel A when Channel B attempts selection.

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

36

TWIN CITIES DISK DIVISION

|              |    |    | Channel B |       |       |       |  |  |  |  |

|--------------|----|----|-----------|-------|-------|-------|--|--|--|--|

|              | PH | PS | PH PS     | PH PS | PH PS | PH PS |  |  |  |  |

|              |    |    | 00        | 01    | 10    |       |  |  |  |  |

| Channel A    | 0  | 0  | B         | B     | B     | B     |  |  |  |  |

| Not Selected | 0  | 1  | В         | B     | В     | B     |  |  |  |  |

|              | 1  | 0  | A         | A     | A     | B     |  |  |  |  |

|              | 1  | 1  | A         | A     | A     | A     |  |  |  |  |

| Channel A    | 0  | 0  | A         | B     | A     | B     |  |  |  |  |

| Selected     | 0  | 1  | A         | B     | A     | B     |  |  |  |  |

|              | 1  | 0  | A         | A     | A     | В     |  |  |  |  |

|              | 11 | 1  | A         | A     | A     | A     |  |  |  |  |

If any of the optional bits (bits 0-3) set are not supported by the slave, the addressed slave shall not acknowledge selection; i.e., the slave shall not assert SLAVE IN.

7.4.1.2 BUS A Facility Selection Octet (Optional)

The master has the ability to select any of 8 slaves and indirectly address up to 16 facilities. The slave is responsible for facility selection on behalf of the master.

| 7 | 6   | 5       | i    | 4 | 3 | 2        | 1       | 0 |

|---|-----|---------|------|---|---|----------|---------|---|

| 1 | SLA | VE ADDE | RESS |   |   | FACILITY | ADDRESS | 5 |

When Bit 7=1 the addressed slave shall respond to the selection request for the facility with the Select Status octet (See 7.4.2).

• Slave Address

Bit 4 is the least significant bit (LSB) of the slave address.

• Facility Address

Bit 0 is the least significant bit of the facility address.

If this option is not supported the slave identified in Bits 4-6 shall not acknowledge selection; i.e., the slave shall not assert SLAVE IN.

If it is supported, and the facility address is not valid then the Slave Status octet shall be used to indicate an invalid selection address. CONTROL DATA COMPANY

### ENGINEERING SPECIFICATION

SPEC

64731602

CD

5

REV

0

DATE

0

PAGE

37

TWIN CITIES DISK DIVISION

7.4.2 Bus B Select Status Octet Presented during the SLAVACK state.

> The slave responds to selection by driving its (the slave's) bit significant address and releasing all other bus bits to provide Select Status, which is defined as follows:

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SLAVE |

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | O     |

NOTE: The parity line shall be released by the slave and parity shall not be checked by the master.

If the addressed slave is not present on the interface, or does not recognize its address, SLAVE IN will not be asserted and no address bits shall be asserted.

The master can detect invalid selection conditions by analysis of Select Status e.g. incorrect selection will have the wrong address bit posted, multiple selection will have more than one address bit posted. To detect multiple selection, the master must wait until all slaves have had enough time to respond.

7.4.3 Bus A Bus Control Octet Presented during the BUSCTL state.

> The Bus Control octet describes the subsequent Information Transfer and bus configuration. If the master sets up a Bus Control that is not recognizable at the slave, the slave shall end the subsequent Information Transfer sequence without an Information Transfer (See Figure 24).

SPEC

64731602

CD

5

REV

5

DATE

5

PAGE

38

TWIN CITIES DISK DIVISION

The Bus Control octet is defined as follows:

| 7   | 6    | 5 |   | 4        | 3    | L      | 2     | 11     | 1 | 0 |

|-----|------|---|---|----------|------|--------|-------|--------|---|---|

| 0 * | 0 ** |   | D | ef i nei | ) BY | LOGICA | L INI | ERFACE |   |   |

|     | -    |   |   |          |      |        |       |        |   |   |

\* 0 = OPERATION COMMAND/OPERATION RESPONSE 1 = DATA

\*\* 0 = INFORMATION OUT 1 = INFORMATION IN

The use of Bits 0-5 is is established by the master and the slave at the Logical Interface. The use of these bits shall not affect the Physical Interface hardware.

7.4.4 Bus B Bus Acknowledge Octet Presented during the BUSACK state.

> The contents of this octet are optional, and if none are supported it is the responsibility of the slave to ensure that the bus contents are stable with correct parity during the BUSACK state, and that zero is posted.

In an intelligent subsystem there may be a need for the master to receive responses from the slave immediately after Bus Control.

| 7   | 6    | 5 | 4    |      | 3  |      | 2   |       | 1     | 1 | 0 |

|-----|------|---|------|------|----|------|-----|-------|-------|---|---|

| 0 * | 0 ** |   | DEF  | INED | BY | LOGI | CAL | INTER | RFACE |   |   |

| 1   | ĩ    |   |      |      |    |      |     |       |       |   |   |

|     |      |   | <br> |      |    |      |     |       |       |   |   |

\* 0 = OPERATION COMMAND/OPERATION RESPONSE 1 = DATA

\*\* 0 = INFORMATION OUT 1 = INFORMATION IN

The use of Bits 0-5 is is established by the master and the slave at the Logical Interface. The use of these bits shall not affect the Physical Interface hardware. COMPAGNETIC PERIPHERALS INC.

## ENGINEERING SPECIFICATION

SPEC

64731602

CD

5

REV

0

DATE

9

TWIN CITIES DISK DIVISION

7.4.5 Bus A Master Status Octet Presented during the SELECT state.

> The Master Status octet is used by the master to inform the slave whether or not the previous Information Transfer was successful, and if a bus parity error had been detected.

| 7                                                   | 6                      | 5 | 4   | 1    | 3  | 1    | 2   | 1    | 1      |   | 0 |

|-----------------------------------------------------|------------------------|---|-----|------|----|------|-----|------|--------|---|---|

| SUCCE-<br>SSFUL<br>INFOR-<br>MATION<br>TRANS<br>FER | BUS<br>PARITY<br>ERROR |   | DEF | INED | BY | LOGI | CAL | INTE | ERFACI | 2 |   |

• Successful Information Transfer

When Bit 7=1 the previous Information Transfer as viewed by the master completed successfully.

• Bus Parity Error

When Bit 6=1 the master detected a bus parity error on the Bus Acknowledge octet or the Information Transfer In.

The use of Bits 0-5 is is established by the master and the slave at the Logical Interface. The use of these bits shall not affect the Physical Interface hardware.

SPEC

64731602

CD

5

REV

0

DATE

9

PAGE

40

TWIN CITIES DISK DIVISION

7.4.6 Bus B Slave Status Octet Presented during the SLAVACK state.

The Slave Status octet describes the slave-determined ending status of the previous Information Transfer, if any.

| 7                                                   | 6                      | 5 | 4   |      | 3  |     | 2     |    | 1              | 0 |

|-----------------------------------------------------|------------------------|---|-----|------|----|-----|-------|----|----------------|---|

| SUCCE-<br>SSFUL<br>INFOR-<br>MATION<br>TRANS<br>FER | BUS<br>PARITY<br>ERROR |   | DEF | INED | ВҮ | LOC | GICAL | IN | <b>TERFACE</b> |   |

• Successful Information Transfer

When Bit 7=1 the previous Information Transfer completed successfully.

• Bus Parity Error

When Bit 6=1 the slave detected a parity error in the Bus Control octet, the Information Transfer Out, or the Master Status octet.

The use of Bits 0-5 is is established by the master and the slave at the Logical Interface or may be Vendor Unique. The use of these bits shall not affect the Physical Interface hardware.

7.4.7 Bus A Request Modifier Octet Presented during the REQUEST state.

> The Request Modifier octet is presented during the REQUEST state and is used by the master in various forms to request interrupt class(es), status, or transfer settings, and is also used to initiate Selective Reset.

SPEC 64731602 CD 5 REV DATE PAGE 41

TWIN CITIES DISK DIVISION

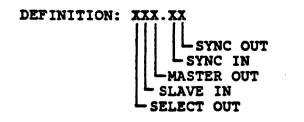

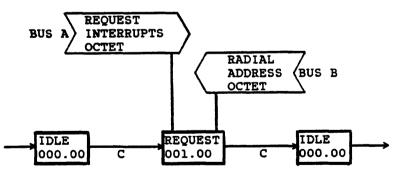

7.4.7.1 Request Interrupts Octet

| 7 | 6                        | 5                         | 4                      | 3  | 2              | 1                         | 0                         |