SPEC

77653473

CD

7

REV

B

DATE

June

1981

1

SPECIFICATION FOR LARK MICRO INTERFACE

MAGNETIC PERIPHERALS INC.

SPEC

77653473

CD

7

REV

B

DATE

June

1981

PAGE

1 of

71

# SPECIFICATION FOR LARK MICRO INTERFACE

**MAGNETIC PERIPHERALS INC. GD** <sup>a subsidiary of</sup> control data conformation

| PC                   | SPEC. NO. | SHEET | REV. |

|----------------------|-----------|-------|------|

| A                    | 77653473  | 2     | В    |

| • _ / <sup>™</sup> • |           |       |      |

# TABLE OF CONTENTS

en a conservation de la sec

| 1.0 | SCOPE .                                                                                     | • • • • • • •                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • • • • • •                                                               | • • • • • • | • • • • • | • • • | 5        |

|-----|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------|-----------|-------|----------|

| 2.0 | APPLICA                                                                                     | BLE DOC                                                                                     | MENTS                                                                                                                                                                                                                                                                                                                                                                                                                                            | • • • • • •                                                               | ••••        | • • • • • | • • • | 5        |

| 3.0 | GENERAL                                                                                     | , DESCRI                                                                                    | TION                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           | • • • • • • | • • • • • | • • • | 5        |

|     | 3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3 | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9<br>1.10<br>1.11<br>1.12<br>1.13 | ABLE SIGNAL DEFINITION<br>vent<br>ddress<br>us (Bidirectional)<br>us Ready<br>cknowledge<br>ead Gate<br>rite Gate<br>arly Strobe<br>ate Strobe<br>ndex Pulse<br>ector Pulse<br>ead/Write Fault (R/W Fault<br>E SIGNAL DEFINITION<br>elect<br>ervo Clock<br>ead Clock<br>rite Clock<br>rite Data                                                                                                                                                  | t)                                                                        |             |           |       | 24<br>24 |

| 4.0 | BUS COM                                                                                     | IMAND DE                                                                                    | INITION                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |             |           |       |          |

|     | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 | .1.1<br>.1.2<br>.1.3<br>.1.4<br>.1.5<br>.1.6<br>.1.7<br>.1.8                                | E (ADDRESS 111)<br>pindle Power Off (Bus Bit<br>nterrupt Mode (Bus Bit 1)<br>ault Reset (Bus Bit 2)<br>pindle Power On (Bus Bit 3)<br>eturn to Zero (RTZ) (Bus B<br>ead Select (Bus Bit 5)<br>eak (Bus Bit 6)<br>ead Escape Register (Bus B<br>TE (ADDRESS 000)<br>end Detailed Status (Bus B<br>end MC Status Code (Bus Bi<br>end Device ID (Bus Bit 2)<br>oop Low Cylinder Register<br>ervo Offset Plus (Bus Bit<br>ervo Offset Minus (Bus Bit | 0)<br>3)<br>Bit 4)<br><br>Bit 7)<br><br>Bit 0)<br>it 1)<br><br>(Bus<br>4) |             |           |       |          |

| · · · · · · · · · · · · · · · · · · · | PC | SPEC. NO. | SHEET | REV. |

|---------------------------------------|----|-----------|-------|------|

|                                       | Α  | 77653473  | 3     | В    |

|                                       |    |           |       |      |

# TABLE OF CONTENTS (Continued)

| 5.0 | 4.3<br>4.4<br>4.5<br>BUS S | 4.2.8 Reserved (Bus Bit 7)<br>LOW CYLINDER BYTE (ADDRESS 110)<br>HIGH CYLINDER BYTE (ADDRESS 100)<br>HEAD BYTE (ADDRESS 101)                                                                                                                                                                                                                                                                                                                                                                                                            | 36                         |

|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 5.0 |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |

|     | 5.1<br>5.2<br>5.3<br>5.4   | <pre>5.1.1 Fault (Bus Bit 0)<br/>5.1.2 Reserved (Bus Bit 1)<br/>5.1.3 Seek Error (Bus Bit 2)<br/>5.1.4 Reserved (Bus Bit 3)<br/>5.1.5 Unit Ready (Bus Bit 4)<br/>5.1.6 On Cylinder (Bus Bit 5)<br/>5.1.7 Write Protected (Bus Bit 6)<br/>5.1.8 Ready to Load (Bus Bit 7)<br/>MC STATUS CODE (ADDRESS 001)<br/>DEVICE ID BYTE (ADDRESS 000)<br/>5.4.1 Removable Protect Switch (Bus Bit 0)<br/>5.4.2 Fixed Protect Switch (Bus Bit 1)<br/>5.4.3 Reserved (Bus Bit 2)<br/>5.4.4 Reserved (Bus Bit 3)<br/>5.4.5 Reserved (Bus Bit 4)</pre> | 42                         |

| 6.0 | MICRO                      | UNIT INTERFACE COMPONENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43                         |

|     | 6.1                        | <ul><li>6.1.1 Command Cable Characteristics</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46<br>46<br>46<br>46       |

|     | 6.2<br>6.3                 | CABLE/CONNECTOR PART NUMBERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47<br>49<br>49<br>49<br>49 |

|     | 6.4                        | DIFFERENTIAL SIGNAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52<br>52                   |

|     | PC | SPEC. NO. | SHEET | REV. |

|-----|----|-----------|-------|------|

|     | A  | 77653473  | 4     | в    |

| 5 M |    |           | 1.    |      |

# TABLE OF CONTENTS (Continued)

| /.0 | DATA | FORMAT AND DATA CONTROL TIMING         | 54  |

|-----|------|----------------------------------------|-----|

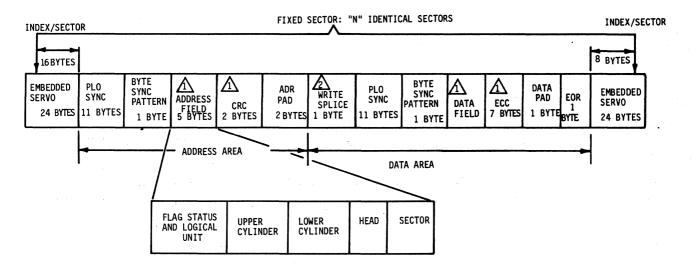

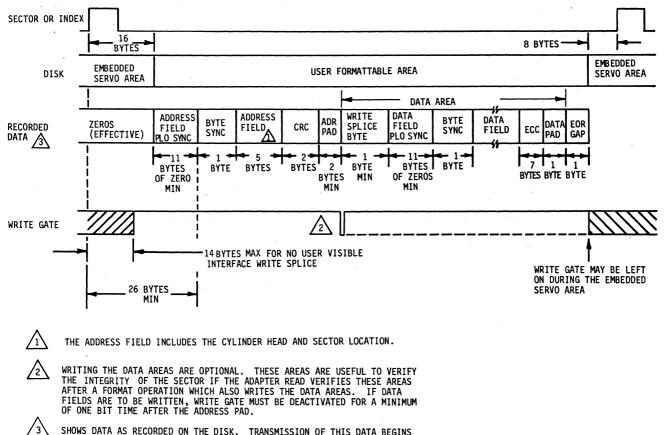

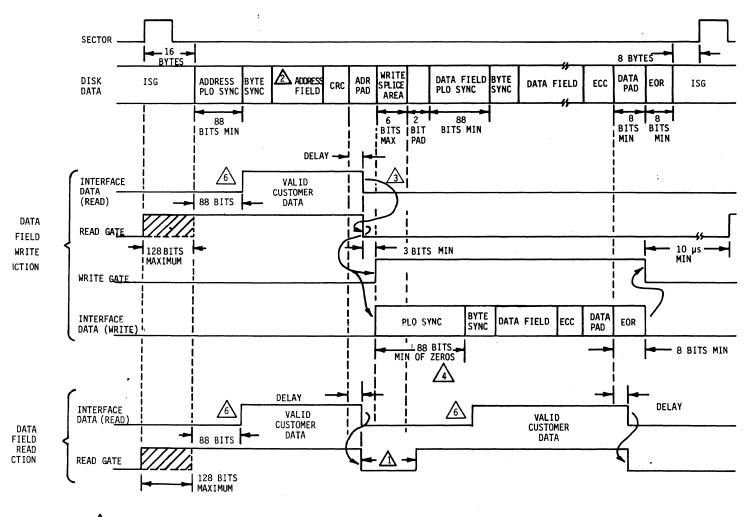

|     | 7.1  | FORMAT DEFINITION                      | 54  |

|     |      | 7.1.1 Embedded Servo Area              |     |

|     |      | 7.1.2 Address Area                     |     |

|     |      | 7.1.3 Data Area                        |     |

|     |      | 7.1.4 Read/Write Timing Considerations |     |

|     | 7.2  | WRITE FORMAT PROCEDURE                 | • • |

|     | 7.3  | READ/WRITE CONTROL TIMING              |     |

|     |      | 7.3.1 Read Function                    |     |

|     |      | 7.3.2 Write Function                   | 68  |

| <b>[</b> | PC | SPEC. NO. | SHEET | REV. |

|----------|----|-----------|-------|------|

|          | A  | 77653473  | 5     | В    |

1.0 SCOPE

This document presents the interface specifications for the Lark Micro Interface used with the Model 9454 Lark Micro Unit. Within this specification the disk storage device will be referred to as the Lark Micro Unit, LMU, Micro Unit, or simply as the drive; and the interface will be referred to as the Lark Micro Interface (LMI). The user-designed controller which allows information transfer between the LMU and the central processing unit will be referred to as the adapter.

This document only defines the digital signal interface. For power requirements, refer to the device Product Specification for the specific disk storage device being used.

This document will be the common interface specification for future MPI products utilizing the Lark Micro Interface. Future products will utilize commonality in definition and timing conditions wherever possible.

2.0 APPLICABLE LOCUMENTS

9454 Lark Micro Unit Product Specification, 77653527

3.0 GENERAL DESCRIPTION

The Lark Micro Unit (LMU) utilizes an asynchronous bus interface which allows flexibility in the adapter design. The bus timing and protocol is controlled by a micro-computer within the LMU to also provide maximum flexibility and expandability of the interface for future product enhancements. Bus timing requirements (that is, setup times, hold times, response times, etc.) have been defined to require minimal hardware within the adapter. These timing requirements also allow a wide range of technologies (such as MOS, LSI, TTL, and/or micro-computers) to be used to implement an adapter design. The physical interface consists of a 40-pin command (C'') cable and a 26-pin data

| ſ                                                                                                                |                                                                                                                  | РС | SPEC. NO. | SHEET          | REV. |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----|-----------|----------------|------|

|                                                                                                                  | N.                                                                                                               | A  | 77653473  | <u></u> .6     | В    |

| and the second | and the second |    |           | and the second |      |

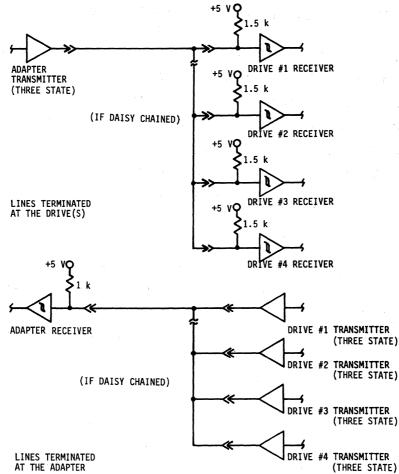

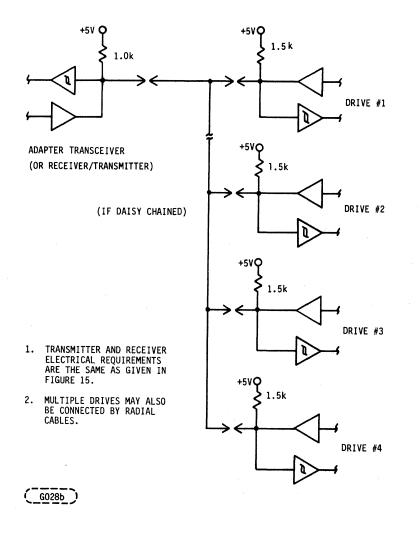

("D") cable. The command cable can be daisy-chained and is based on an 8-bit bidirectional bus for command/status transfers between the adapter and the drive.

#### NOTE

The user must provide the daisy-chain facilities; only one command I/O connector is provided on the LMU.

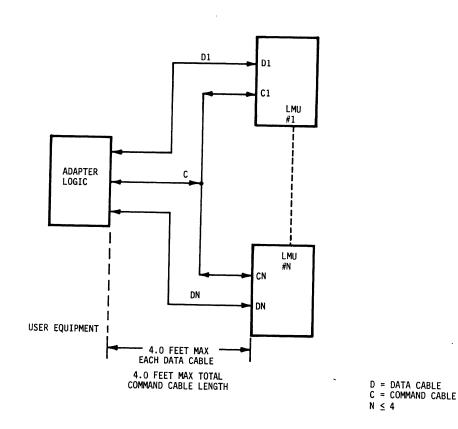

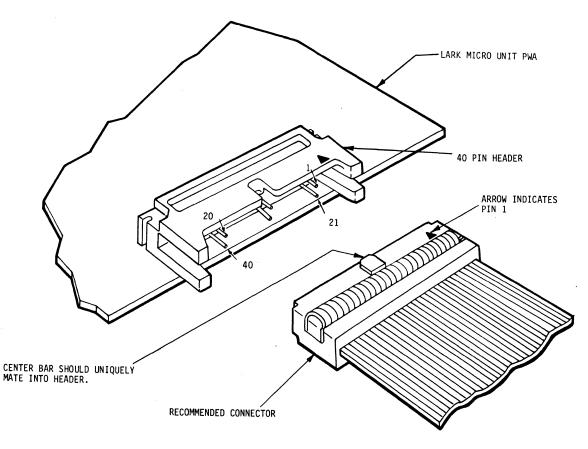

A maximum of four LMU's may be daisy-chained. The data cable, which contains high frequency (9.67 MHz) read/write signals, must be radially connected. The maximum cumulative interface cable length is 4.0 feet. Refer to Figure 1.

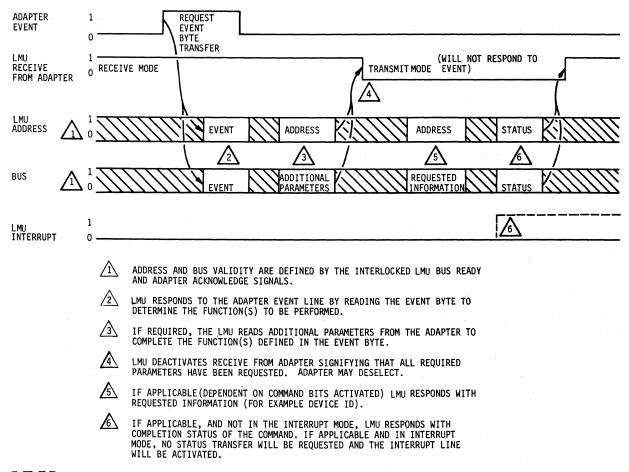

Interface dialogue is initiated by the adapter via a dedicated signal line called the "Event" line. The LMU then responds by requesting the adapter to transmit the Event Byte which contains information relative to the desired activity. Subsequent requests for additional bytes of information from the adapter may occur as a function of the original Event Byte transfer.

For example, if the Event Byte requested a head change, the LMU would respond by asking for the desired head address. Multiple operations may be requested within a single Event Byte transfer to minimize interface dialogue. Table 1 details combinations of valid multiple events and the complementary information that will be requested by the drive necessary to execute the specific Events. After the adapter has transmitted this complementary information, the LMU will begin execution of the Event in a prescribed manner. At the completion of the Event(s), the LMU will request the adapter to receive current status of the LMU in one of two modes. In one of these modes an automatic status

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653473  | 7     | В    |

# (172a)

# Figure 1. Lark Micro Interface Cabling

transfer will be requested. The adapter should be prepared to respond to this request.

The LMU also provides an alternate method of handling status returns via a dedicated bit within the Event Byte called the Interrupt Bit. If this bit is true, the drive will signal the adapter of a Status change by means of the Interrupt Request line in the data cable. This line will function independently of Unit Select and will allow the user a capability to perform overlapping operations in a multiple-LMU or interrupt-driven system.

|                                                                                                                | Sec. 19 here to the paper of the second | PC | SPEC. NO. | SHEET | REV. |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------|----|-----------|-------|------|

| and and a second se |                                         | A  | 77653473  | 8     | В    |

|                                                                                                                |                                         |    |           |       | L    |

A micro-computer within the LMU monitors all critical drive activity and will store conditions relative to this activity in its memory. As an aid to fault diagnosis, this information can be requested by the adapter and subsequently transferred across the interface. The interface also incorporates Early and Late Data Strobing capabilities to aid in read data recovery.

A comprehensive and detailed description of each signal line and commands/status will be contained in the following sections.

3.1 COMMAND CABLE SIGNAL DEFINITION

Interface signals for the command and data cables are illustrated in Figure 2 and discussed in the following paragraphs.

# 3.1.1 Event

The Event signal indicates the drive must execute a command. The drive will request the adapter's Event Byte to determine the operation to be performed. Response to the Event signal will be delayed if the LMU is currently performing the operation(s) specified by a previous Event (that is, the drive will honor a new Event after completion of a previous Event) or if the drive is responding to a status change.

The drive will inhibit writing of the media when Event is active. Writing is inhibited by drive electronics as soon as the leading edge of the Event signal is detected. The adapter must not activate Event while a data read or write operation is in progress. Writing will be inhibited until Event is deactivated. Depending upon the operation, writing may also be inhibited until the operation specified by Event is completed. Attempting to write during these times will generate a fault condition.

|                                          | PC SPEC                                                                                                                                                                                                                                                                                                                                                                                                       | . NO. SHEET                              | REV. |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|

|                                          | A 7                                                                                                                                                                                                                                                                                                                                                                                                           | 7653473 9                                | В    |

| ADAPTER<br>COMMAND<br>CABLE<br>INTERFACE | MICRO INTERFACE         1       EVENT         8       BUS         3       ADDRESS         1       RECEIVE FROM ADAPTER         1       BUS READY         1       ACKNOWLEDGE         1       READ GATE         1       WRITE GATE         1       EARLY STROBE         1       LATE STROBE         1       INDEX         1       SECTOR         1       R/W FAULT         1       RESERVED FOR INCREMENT HEAD | DRIVE<br>COMMAND<br>CABLE<br>INTERFACE   |      |

| ADAPTER<br>DATA<br>CABLE<br>INTERFACE    | 1       SELECT         2       SERVO CLOCK         2       READ CLOCK         2       READ DATA         2       WRITE CLOCK         2       WRITE DATA         1       INTERRUPT REQUEST         1       RESERVED FOR INDEX         1       RESERVED FOR INVALID INDEX/SECTOR         1       RESERVED FOR INVALID INDEX/SECTOR                                                                               | A   DRIVE   DATA   CABLE   INTERFACE   A |      |

|                                          | <ul> <li>REAL TIME CONTROL SIGNALS FOR DISK READ/WRITE DATA</li> <li>SELECT SIGNAL FOR 1 OUT OF 4 POSSIBLE DAISY CHAINED</li> <li>SERIAL DISK READ/WRITE DATA PLUS CLOCKS</li> </ul>                                                                                                                                                                                                                          | DRIVES                                   |      |

RESERVED SIGNAL LINES

.

Figure 2. Lark Micro Interface Signals

The Micro Unit Interface has been designed to require a minimal utilization of the Event signal. Anytime the drive is selected and the status of the drive changes, the drive automatically requests to send the updated Status Byte to the adapter. Thus, the adapter need only use the Event function to specify operations to be performed and need not utilize Event to Request status. The LMU can, therefore, dedicate time to performing internal tests (such as RPM tests, etc.) without being continuously interrupted by status transfer commands from the adapter.

| N |    |           |       |      |

|---|----|-----------|-------|------|

|   | PC | SPEC. NO. | SHEET | REV. |

|   | А  | 77653473  | 10    | В    |

If the Interrupt bit is active when the Event Byte is transferred or if the drive is deselected, the LMU will respond to a status change by raising the Interrupt Request line. The adapter may then respond by selecting the drive (if deselected), initiating an Event request, and sending an Event Byte requesting the updated status.

To ensure the drive has detected that a command is to be executed, Event should remain activated until the Bus Ready signal requesting the Event Byte (Address 111 with Receive From Adapter active) is received from the LMU. The Event line must be deactivated after the adapter acknowledges the Event Byte transfer to the LMU to ensure that the drive will not execute a redundant command.

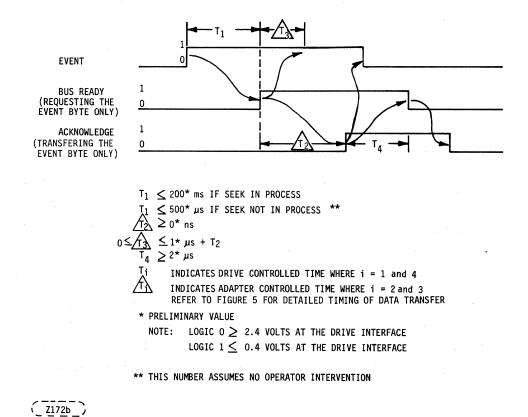

See Figure 3 for timing requirements and Section 4.1 for a definition of the Event Byte.

Figure 3. Event Timing

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| A  | 77653473  | 11    | В    |

### 3.1.2 Receive From Adapter

The Receive From Adapter signal specifies the direction of information transfer on the Bus lines. A logic 1 signifies that information is to be transferred from the adapter to the drive; a logic 0 signifies that information is to be transferred from the drive to the adapter.

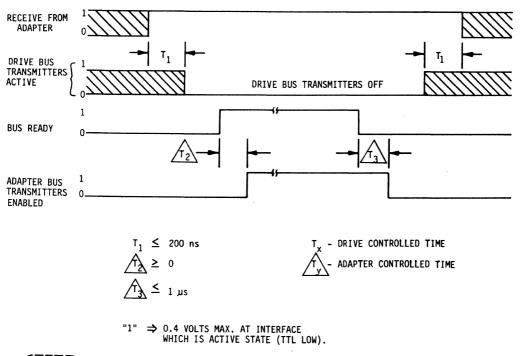

See Figures 4, 5, and 6 for detailed timing of this signal.

The line may be used for a secondary function of signaling when the drive can be deselected (when in the Interrupt mode) following an event in which positioner movement occurs. Receive From Adapter will switch states and be in the transmit mode immediately following the transfer of the Event Byte and complementary parameters.

<u>G259a</u>

#### Figure 4. Bus Transceiver Control

| i na sente en esta esta en en esta esta esta esta esta esta esta esta | PC | SPEC. NO. | SHEET | REV. |

|-----------------------------------------------------------------------|----|-----------|-------|------|

|                                                                       | Α  | 77653473  | 12    | В    |

#### 3.1.3 Address

The three Address lines specify up to eight different interpretations of the information on the bidirectional Bus lines. The state of the Address lines is controlled by the LMU in response to the adapter-controlled Event request and are used in both directions of transfer.

The following Address Line configurations have been defined.

| Bytes             | Received from the Adapter |

|-------------------|---------------------------|

| Address Bit (210) | Bus Byte                  |

| 111               | Event Byte                |

| 000               | Escape Byte               |

| 110               | Low Cylinder Byte         |

| 100               | High Cylinder Byte        |

| 101               | Head Byte                 |

| 001               | Reserved for future use   |

| 010               | Reserved for future use   |

| 011               | Reserved for future use   |

| Byt               | es Sent to the Adapter    |

| Address Bit (210) | Bus Byte                  |

| 111               | Status Byte               |

| 001               | MC Status Codes Byte      |

| 011               | Auxiliary Byte            |

| 000               | Device ID Byte            |

| 010               | Detailed Status Byte      |

| 100               | Reserved for future use   |

| 101               | Reserved for future use   |

| 110               | Reserved for future use   |

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| A  | 77653473  | 13    | В    |

### 3.1.4 Bus (Bidirectional)

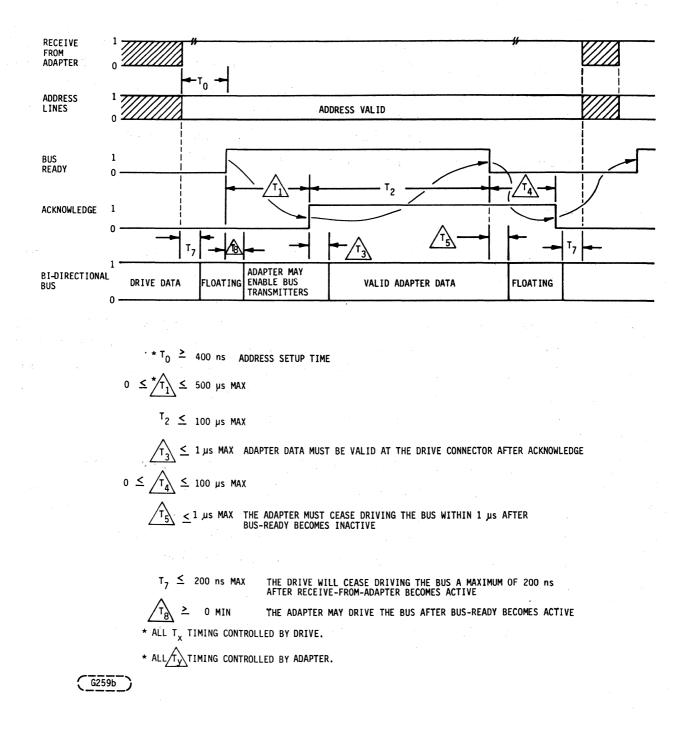

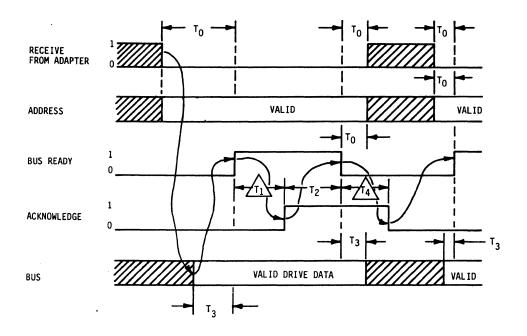

The Bus signal is an 8-bit 3-state bidirectional bus used for information transfers between the drive and the adapter. The Bus dialogue is defined in Figures 5 and 6. When the Bus is valid, the bit interpretations shown in Figure 10 are defined by the state of the Address lines and the Receive from Adapter signal levels. Refer to sections 4.0 and 5.0.

### 3.1.5 Bus Ready

Bus Ready is a handshaking line from the drive to the adapter which initiates all Bus transfer requests.

For Bus transfers from the drive to the adapter, the leading edge of the Bus Ready signal signifies that the contents of the Address and Bus lines are valid and that the adapter may accept the information. The trailing edge acknowledges the acceptance of the Bus information by the adapter.

For Bus transfers from the adapter to the drive, the leading edge of the Bus Ready signal signifies that the drive is ready to accept a Bus byte from the adapter as specified by the address lines. The trailing edge of Bus Ready signifies that the drive has accepted the Bus byte from the adapter.

Refer to Figure 5 for detailed timing of these lines.

Figure 5. Read an Adapter Byte Timing

|  | РС | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | A  | 77653473  | 15    | В    |

$$T_0 \ge 400 \text{ ns}$$

- THE ADDRESS IS VALID 400 ns BEFORE BUS READY

BECOMES ACTIVE.

0 ≤  $T_1 \le 500 \text{ µs}$  MAX - THE ADAPTER MUST RESPOND TO BUS READY ACTIVATION

0 ≤  $T_2 \le 100 \text{ µs}$

$T_3 \ge 400 \text{ ns}$  - DRIVE DATA TO BUS READY SET UP AND HOLD TIME.

0 ≤  $T_4 \le 100 \text{ µs}$  MAX

NOTE: "1" > 0.4 VOLTS MAX AT INTERFACE (TTL LOW)

$T_i \Rightarrow drive controlled time$  $<math>\uparrow \uparrow \Rightarrow adapter controlled time$

G050a

Figure 6. Send a Byte to the Adapter Timing

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| Α  | 77653473  | 16    | В    |

|    | 1 × 1     | ž.    |      |

# 3.1.6 Acknowledge

Acknowledge is a handshaking line from the adapter to the drive which indicates acceptance of a Bus byte from the drive or the presence of a valid Bus byte to the drive.

For Bus transfers from the drive to the adapter, the leading edge of Acknowledge signifies that the adapter has accepted the Bus byte (the response to the leading edge of the drive's Bus Ready signal.) The trailing edge of Acknowledge signifies detection of the trailing edge of Bus Ready.

For Bus transfers from the adapter to the drive, the leading edge of Acknowledge signifies that the data requested by the leading edge of Bus Ready is available on the bus. The trailing edge of Acknowledge signifies detection of the trailing edge of the Bus Ready signal.

Refer to Figures 5 and 6 for detailed timing.

If the adapter decides to terminate a dialogue sequence by not responding to Bus Ready with Acknowlege, the drive will wait for approximately 500 microseconds, Fault, and then close the dialogue sequence. A micro-computer detected status code (MC Status Code) will be stored since the drive does not know that the "no response" condition was intentional. Commands for which processing has been completed before the dialogue is terminated will be executed; all others will be ignored.

| ſ | PC | SPEC. NO. | SHEET | REV. |

|---|----|-----------|-------|------|

|   | А  | 77653473  | 1:7   | В    |

# 3.1.7 Read Gate

The Read Gate signal enables serial NRZ Read Data on the radial Read Data lines. The leading edge of Read Gate triggers the drive to synchronize on the PLO synchronization pattern. (See Section 7.0 for application and timing information.)

The Early Strobe or Late Strobe line may be enabled simultaneously with Read Gate as an aid in recovering marginal data. (Refer to Sections 3.1.9 and 3.1.10.)

3.1.8 Write Gate

The Write Gate signal enables the drive to write the serial NRZ write data defined by the data cable Write Data and Write Clock signals. (See Section 7.0 for application and timing information.)

3.1.9 Early Strobe

#### NOTE

The Early Strobe signal is intended to be an aid in recovering marginal data and is only valid when Read Gate is true.

When this line is true, the drive's PLO data separator will strobe the data at a time earlier than nominal. Normal strobe timing will be returned when the line is false.

|  |                                        | PC | SPEC. NO. | SHEET | REV. |

|--|----------------------------------------|----|-----------|-------|------|

|  |                                        | A  | 77653473  | 18    | В    |

|  | <br>a construction of the construction | 1  |           |       |      |

#### 3.1.10 Late Strobe

#### NOTE

The Late Strobe signal is intended to be an aid in recovering marginal data and is only valid when Read Gate is true.

When this line is true, the drive's PLO data separator will strobe the data at a time later than nominal. Normal strobe timing will be returned when the line is false.

# 3.1.11 Index Pulse

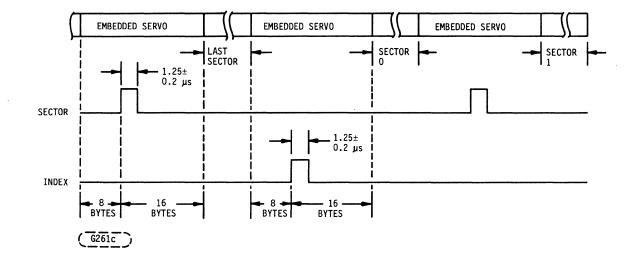

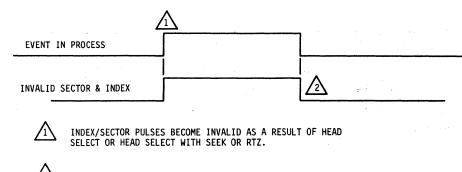

The Index Pulse  $(1.25 \pm 0.2 \text{ microseconds})$  occurs once per revolution; its leading edge is considered the sector pulse for sector zero (see Figures 7 and 8). Index pulses may be missed when a head change is performed. Index timing will become valid (that is, accurately reflect the location of sector zero) when On Cylinder is true after a head change.

If a head switch occurs during an Index Pulse, the pulse will not be gated off, but will be allowed its full pulse width.

# 3.1.12 Sector Pulse

The Sector Pulse  $(1.25 \pm 0.2 \text{ microseconds})$  is derived from the embedded servo (see Figures 7 and 8). Sector Pulse integrity is retained when Ready is active and throughout seek operations in which no head change is effected. There are 63 sector pulses available per revolution for the 64 sector-per-track format (see Figure 8). When combined with

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | А  | 77653473  | 19    | В    |

Figure 7. Relative Index and Sector Relationship

Index in the adapter, this divides the tracks into 64 equallength sectors.

#### NOTE 1

Sector pulses will be missed as a consequence of a head change (Figure 8). If the adapter counts sector pulses to determine sector location, it should wait until the next Index pulse following the On Cylinder indication to establish rotational position orientation after a head change. Head changes occur due to Head Select or RTZ commands.

#### NOTE 2

The phase relationship of index/sector pulses to Servo Clock is not guaranteed.

| the state of the s | ورسر والمنافر ما      | the second s | a sa ini ini ini ini ini ini ini ini ini in | PC | SPEC. NO. | SHEET | REV. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------|----|-----------|-------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |                                                                                                                |                                             | Α  | 77653473  | 20    | В    |

| 1. A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | and the second second |                                                                                                                |                                             |    |           |       |      |

AFTER COMPLETION STATUS RETURN IN WHICH ON CYLINDER IS TRUE, SECTOR PULSES WILL DEFINE THE BEGINNING OF A SECTOR; HOWEVER, ANY ROTATIONAL POSITION SENSING MECHANISM IMPLEMENTED BY THE ADAPTER MAY NOT BE VALID UNTIL THE NEXT INDEX PULSE.

# Figure 8. Index and Sector Pulse Validity During Head Change

#### NOTE 3

Thirty-two equal-length sectors per track are available via a different device configuration (that is, different assembly number).

### 3.1.13 Read/Write Fault (R/W Fault)

G299a

The Read/Write Fault signal is a real time indicator of a read or write fault. The adapter should monitor this signal to verify that a hardware write fault did not occur during a read or a write function. The line is deactivated following a Fault Reset Command bit in the Event Byte provided the fault no longer exists. Refer to Section 5.1.1, Fault (Bit 0), which is also activated when a read/write fault occurs.

#### NOTE

This signal is the only active high line in the interface.

| 1 - 4 - 22 | PC | SPEC. NO. | SHEET | REV. |

|------------|----|-----------|-------|------|

|            | А  | 77653473  | 21    | В    |

# 3.2 DATA CABLE SIGNAL DEFINITION

The radial data cable contains real time Data and Clock lines, a Select line to enable or disable the command cable interface for daisy-chained operation, and an Interrupt Request line from the drive to signify a status change has occurred within the drive.

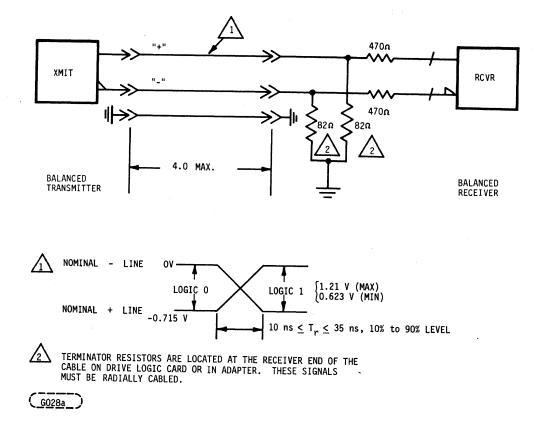

The data cable signals are a combination of single-ended and differential signal levels. The driver and receiver electrical characteristics are defined in Section 6.0.

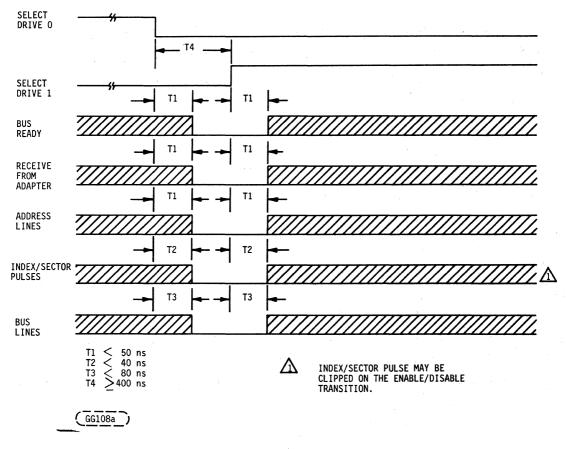

#### 3.2.1 Select

This single-ended signal from the adapter to the drive is used to enable or disable the command cable interface for daisychained operation. When a drive is deselected, all command cable inputs will be ignored and all command cable drivers will assume a high impedance state.

#### NOTE

The adapter need not request the current drive status when a new drive is selected unless that drive's Interrupt Request line is active.

In a daisy-chained configuration, the interface drivers and receivers will be enabled within 200 nanoseconds from the leading edge of the Select line. The interface transmitters and receivers will assume the high impedance state within 200 nanoseconds from the trailing edge of the Select line. Refer to Figure 8A.

|            |        | (a) A set of the se |                |                                                                                                                  |       | 1          |

|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------|-------|------------|

|            | ······ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PC             | SPEC. NO.                                                                                                        | SHEET | REV.       |

|            |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A              | 77653473                                                                                                         | 22    | : <b>B</b> |

| - 1<br>- 1 |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | and the second | and the second |       |            |

Figure 8A. Deselect/Select Timing

### 3.2.2 Servo Clock

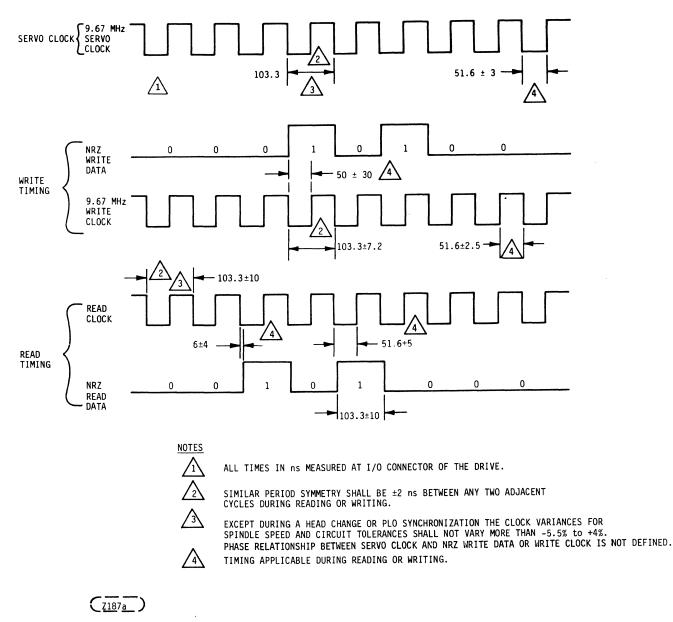

The differential Servo Clock (Figure 9) is a drive generated, continuously transmitted, phase-locked 9.677 MHz (nominal) clock which must be used by the adapter to generate write clocks. Servo Clock is not gated with Select. Servo Clock is frequently locked to the disk rotational speed by sampling a field within the embedded servo.

# 3.2.3 Read Clock

The differential Read Clock defines the beginning of a data cell. It is an internally derived clock signal and is synchronous with the detected data as specified in Figure 9. This signal is transmitted continously, but not in phase with data unless reading.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653473  | 23    | B    |

Figure 9. NRZ Data and Clock Timing

When Read Gate in the command cable is true, Read Clock will begin phase synchronization at the end of the embedded servo zone and will be synchronized to data within 11 bytes of the PLO sync field. Phase discontinuities may be present on Read Clock between the embedded servo field and the beginning of the PLO sync field.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | A  | 77653473  | 24    | В    |

|  |    |           |       | 1. 1 |

# 3.2.4 Read Data

This differential line transmits the recovered data in the NRZ form (Figure 9). There is a 9-bit delay from detection of a bit by the head until that bit is available on the Read Data line at the drive connector. This delay results from the read decoder circuits that convert the recorded flux reversals to NRZ data.

# 3.2.5 Write Clock

This differential line transmits the Write Clock signal which must be synchronized to the NRZ data as illustrated in Figure 9. The Servo Clock (transmitted from the drive to the adapter) is intended to be used by the adapter to generate the Write Clock signal. Since the Servo Clock is synchronized to the servo information, the Write Clock and Write Data will, therefore, be timed precisely, irrespective of the variation in revolutions per minute of disk speed.

The Write Clock need not be transmitted continuously, but must be transmitted at least 250 nanoseconds prior to Write Gate.

# 3.2.6 Write Data

This differential line carries NRZ data which is to be recorded on the disk pack (see Figure 9 for timing). A data bit received at the drive connector is delayed 8-bit times before it is recorded. This delay results from the write encoder circuits that convert the interface NRZ data to the coded pattern that is written on the disk.

# 3.2.7 Interrupt Request

This single-ended signal signifies that a Status change has occurred within the drive if deselected. Thus, in an interrupt-

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653473  | 25    | В    |

driven system, Interrupt Request can be used to signal seek complete with overlapping operations.

If the drive is selected, this line can be used in lieu of automatic Status returns. To use this feature, the Interrupt Mode bit within the Event Byte must be active. The adapter may respond to this line and request updated status at any time.

The Interrupt Request line will be deactivated after the adapter has activated Event and before the drive requests transmission of the Event Byte. Refer to Section 4.1.2.

4.0 BUS COMMAND DEFINITION

The Bus Commands are defined in Figure 10 and in the following paragraphs.

4.1 EVENT BYTE (ADDRESS 111)

The Event Byte (refer to Table 1 and Figure 11) consists of bitencoded commands which are to be performed by the LMU. The drive will execute the command specified by each activated bit each time this byte is read by the drive. The adapter should deactivate all bits in the Event Byte after the drive has read the byte to prevent multiple executions of a single operation. In general, the descriptions are given as if only one command is given in the Event Byte; however, multiple commands may be given. Multiple commands that are contradictory (such as Spindle Power Off with Seek, RTZ, Head Select, or Spindle Power On) will generate a fault that can be identified by reading MC Status Codes. The normal Event Byte dialogue sequence will be ignored if contradictory commands are received. The illegal Event will cause the Interrupt Request line to become active if the Interrupt Mode had been set to a logic 1 on the last valid Event Byte transfer; otherwise, the drive will request to make a status transfer to signify the fault condition.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653473  | 26    | В    |

|                                                   | RECEIVE<br>FROM | ADDRESS                                             | ····· | (MSB)-                         |                           |                          | BUS                     | BIT                    |                |                           | -(LSB)                      |

|---------------------------------------------------|-----------------|-----------------------------------------------------|-------|--------------------------------|---------------------------|--------------------------|-------------------------|------------------------|----------------|---------------------------|-----------------------------|

|                                                   | ADAPTER         | (2 <sup>2</sup> , 2 <sup>1</sup> , 2 <sup>0</sup> ) |       | 7                              | 6                         | 5                        | 4                       | 3                      | 2              | 1                         | 0                           |

|                                                   |                 | EVENT<br>(111)                                      | 7     | READ<br>ESCAPE<br>REG          | SEEK                      | HEAD<br>SELECT           | RTZ                     | SPINDLE<br>POWER<br>ON | FAULT<br>RESET | INTERRUPT<br>MODE         | SPINDLE<br>POWER<br>OFF     |

| BYTES<br>RECE I VED<br>FROM                       |                 | ESCAPE<br>(000)                                     | 0     | ⚠                              | ß                         | SERVO<br>OFFSET<br>MINUS | SERVO<br>OFFSET<br>PLUS | LOOP<br>LOW<br>CYL REG | SEND<br>DEV ID | SEND<br>MC STATUS<br>CODE | SEND<br>DETAILED<br>STATUS  |

| THE<br>ADAPTER                                    | 1               | LOW CYL<br>(110)                                    | 6     | 27                             | 26                        | 25                       | 24                      | 2 <sup>3</sup>         | 22             | 21                        | 2 <sup>0</sup>              |

| 1 HIGH CYL 4 RESERVED FOR HIGH CYLINDER EXPANSION |                 |                                                     |       |                                |                           |                          |                         |                        |                |                           |                             |

|                                                   |                 | HEAD<br>(101)                                       | 5     | RESERVED FOR HEAD EXPANSION 21 |                           |                          |                         |                        |                |                           | 20                          |

|                                                   |                 |                                                     |       | 7                              | 6                         | 5                        | 4                       | 3                      | 2              | 1                         | 0                           |

|                                                   | <b>0</b>        | STATUS<br>(111)                                     | 7     | READY<br>TO LOAD               | WRITE<br>PROTECTEI        | ON<br>D CYLINDER         | UNIT<br>READY           | 3                      | SEEK<br>ERROR  | A                         | FAULT                       |

| BYTES                                             | 0               | MC STATUS<br>CODE (001)                             | 1     | 2 <sup>7</sup>                 | 26                        | 25                       | 2 <sup>4</sup>          | 2 <sup>3</sup>         | 22             | 21                        | 20                          |

| SENT<br>TO THE<br>ADAPTER                         | <b>1</b> 0      | DEV ID<br>(000)                                     | 0     | ıd₃ ∕∕∖                        | 10 <sub>2</sub> \Lambda   | <sup>ID</sup> 1∕∆        | ID <sub>0</sub>         | св <sub>3</sub> 🖄      | св₂∕₂          | св, 🖄                     | св <sub>о</sub> 🖄           |

|                                                   | 0               | DETAILED<br>STATUS (010)                            | 2     | STOP<br>SWITCH                 | SPINDLE<br>STOPPED        | RPM<br>OK                | ふ                       | 3                      | ♪              | FIXED PROTECT<br>SWITCH   | REMOVABLE<br>PROTECT SWITCH |

|                                                   | 0               | AUXILIARY<br>(011) WHEN<br>USED:                    | 3     |                                | S OF ADAPTI<br>Y LOOP LOW |                          |                         |                        |                | · .                       | •                           |

|                                                   | ( '             |                                                     |       |                                |                           |                          |                         |                        |                | · · · ·                   |                             |

(<u>G263a</u>)

DEVICE ID CODE FOR THE LMU IS 0001

DEVICE CONFIGURATION CODE 0001 = 64 SECTORS PER TRACK 0000 = 32 SECTORS PER TRACK

3 RESERVED - MUST BE ZERO

Figure 10. Bus Definition

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653473  | 27    | В    |

Table 1. Valid Adapter Commands and Drive Responses

|                                           | EV                                                                         | ENT                   | B      | YTE              | :                        |                                        | ESC                                           | APE                                                                                           | BYTE                                          |                          | REQUESTED                                                  | TRANSMISSION AT                                                                                                                                                      |

|-------------------------------------------|----------------------------------------------------------------------------|-----------------------|--------|------------------|--------------------------|----------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | 76                                                                         | 5                     | 4      | 3                | 2                        | 10                                     | 76                                            | 54                                                                                            | 3 2                                           | 1 0                      | BYTES<br>OTHER                                             | CONCLUSION OF<br>EVENT                                                                                                                                               |

|                                           | R S<br>D E<br>E K<br>C                                                     | H<br>D<br>S<br>E<br>L |        |                  | L<br>T                   | IS<br>NP<br>TI<br>EN<br>F<br>F         | 00                                            | S S<br>V V<br>O O<br>F F<br>F F<br>- +                                                        | L S<br>O E<br>O N<br>P D<br>C I<br>Y D<br>L   | N N<br>D D<br>M D<br>C T | THAN<br>ESCAPE<br>BYTE                                     |                                                                                                                                                                      |

| STATUS<br>REQUEST                         | 0 0                                                                        | 0                     | 0      | 0                | 0                        | ко                                     |                                               |                                                                                               |                                               |                          | NONE                                                       | PRESENT STATUS                                                                                                                                                       |

| ESCAPE                                    | 1 0<br>1 0<br>1 0<br>1 0<br>1 0<br>1 0<br>1 0<br>1 0                       | 0<br>0<br>0<br>0<br>0 | 000000 | 0                | 00000                    | ( 0<br>( 0<br>( 0<br>( 0<br>( 0<br>( 0 | 0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0 | $\begin{array}{cccc} 1 & 0 \\ 0 & 1 \\ 0 & 0 \\ 0 & 0 \\ 0 & 0 \\ 0 & 0 \\ 0 & 0 \end{array}$ | 0 0<br>0 0<br>1 0<br>0 1<br>0 0<br>0 0<br>0 0 | 0 0<br>0 0<br>0 0<br>1 0 | NONE<br>NONE<br>LOW CYL<br>NONE<br>NONE<br>NONE<br>NONE    | COMPLETION STATUS<br>COMPLETION STATUS<br>AUXILIARY (LOOPED LOW CYL)<br>DEVICE ID<br>MC STATUSCODE<br>DETAILED STATUS<br>COMPLETION STATUS                           |

| POSITIONER<br>EVENTS                      | $\begin{smallmatrix} 0 & 1 \\ 0 & 0 \\ 0 & 1 \end{smallmatrix}$            |                       | 1      | 0                | 0 )                      | ( 0<br>( 0<br>( 0                      |                                               |                                                                                               |                                               |                          | LOW CYL<br>HD ADDRESS<br>F1ST HD ADDR<br>2ND LOW CYL       | COMPLETION STATUS A<br>COMPLETION STATUS A<br>COMPLETION STATUS A                                                                                                    |

| RTZ<br>WITH<br>POSITIONER<br>EVENT        | $\begin{array}{ccc} 0 & 0 \\ 0 & 0 \\ 0 & 1 \\ 0 & 1 \\ 0 & 1 \end{array}$ | 0<br>1<br>0<br>1      | 0<br>1 | 0<br>0<br>0<br>0 |                          | 0<br>0<br>0<br>0                       |                                               |                                                                                               |                                               |                          | NONE<br>HD ADDR<br>LOW CYL<br>FIST HD ADDR<br>L2ND LOW CYL | COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS                                                                                     |

| FLT RS<br>WITH<br>POSITIONER<br>EVENT     | $\begin{array}{ccc} 0 & 0 \\ 0 & 0 \\ 0 & 1 \\ 0 & 1 \end{array}$          |                       |        |                  | 1 )                      | 0<br>0<br>0<br>0                       |                                               |                                                                                               |                                               |                          | NONE<br>HD ADDR<br>LOW CYL<br>TIST HD ADDR<br>L2ND LOW CYL | COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS |

| FLT RS,<br>RTZ AND<br>POSITIONER<br>EVENT | 0 0<br>0 1<br>0 1<br>0 0                                                   | 1                     | 1 (    | 0                | 1 X<br>1 X<br>1 X<br>1 X | 0<br>0                                 |                                               |                                                                                               |                                               |                          | HD ADDR<br>LOW CYL<br>F1ST HD ADDR<br>L2ND LOW CYL<br>NONE | COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS<br>COMPLETION STATUS                                                                                     |

| SPINDLE<br>POWER ON                       | 0 0<br>0 0                                                                 | 0 (<br>1 (            |        |                  | ) X<br>) X               |                                        |                                               |                                                                                               |                                               |                          | NONE<br>HD ADDR                                            | COMPLETION STATUS                                                                                                                                                    |

| SPINDLE<br>POWER OFF                      | 00                                                                         | 0 (                   | 0      | ) (              | ) X                      | 1                                      |                                               |                                                                                               |                                               |                          | NONE                                                       | COMPLETION STATUS                                                                                                                                                    |

NOTES

COMPLETION STATUS IS AUTOMATICALLY SENT IF INTERRUPT MODE INACTIVE. IF ACTIVE, INTERRUPT REQUEST LINE IS ACTIVATED AND ADAPTER MUST REQUEST STATUS. INTERRUPT REQUEST IS RESET BY ANY EVENT.

<u>/2</u>

A STATUS IS RETURNED IMMEDIATELY WITHOUT SETTING INTERRUPT (INDEPENDENT OF THE INTERRUPT BIT). THE INTERRUPT BIT IN THE COMMAND SETS THE MODE FOR LATER STATUS CHANGES (I.E., DEFINES IF INTERRUPT REQUEST LINE IS SET OR STATUS IS SENT IF A FAULT OCCURS).

/3 SPECIAL CODE WHICH MAY BE USED TO TERMINATE OFFSET COMMANDS.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | А  | 77653473  | 28    | В    |

(\_G263b )

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653473  | 29    | В    |

As a general rule, there will be one completion Status (Address 111) return for each Event or multiple Event when completed. An exception to this rule is when reading the Escape Byte (which can be viewed as an extension of the Event Byte), commands such as Loop Low Cylinder, Send Device ID, Send MC Status Codes, or Send Detailed Status will transfer the information requested without sending the customary completion Status (Address 111).

4.1.1 Spindle Power Off (Bus Bit 0)

This bit allows power to be removed from the spindle motor. If the spindle motor is up to speed, the activation of this bit should stop the spindle motor in less than 60 seconds. Completion Status will be available after the spindle has stopped.

4.1.2 Interrupt Mode (Bus Bit 1)

When inactive in the Event Byte, a transfer (usually completion Status, Table 1) will be requested by the drive at the completion of the Event, or before if Status changes due to an error condition. While in the non-Interrupt Mode, the drive should not be deselected. If the adapter cannot respond to this Status request by acknowledging Bus Ready within 500 microseconds, a Fault will be stored. Refer to Figure 6.

When active in the Event Byte, the Interrupt Request line is activated after the Event is complete, or Status changes due to an error condition. The Interrupt Request line will be reset with any new Event request.

| T | PC | SPEC. NO. | SHEET | REV. |

|---|----|-----------|-------|------|

|   | A  | 77653473  | 30    | В    |

|   |    |           |       |      |

The Interrupt Mode, thus, provides two methods of handling Status returns: either automatically, or by request, as the user may choose.

There are, however, characteristics of each of these modes that should be considered by the user. The Auto Status mode (non-Interrupt Mode) does not require Status Request logic and is more efficient because a Status Request Event is not necessary. The adapter is expected to wait for Event completion and receive new Status.

On the other hand, the Interrupt Mode may simplify bus control logic by not allowing the drive to transmit Status without an Event. It also allows the adapter to perform overlapping operations and operate in an Interrupt-driven mode. A Status Request Event will be necessary to retrieve new Status.

When in the Auto Status mode, the user should be aware of a situation that could occur due to an unpredictable error condition within the LMU. If an error should occur before the Event dialogue sequence, the drive may request to send Status. The adapter must honor this request to avoid a subsequent Fault. After the error condition is cleared, the adapter may reinitiate the Event. In the Interrupt mode, when an error condition occurs before the Event dialogue sequence, the Interrupt Request line will be activated. The adapter should terminate the Event dialogue and honor the Interrupt Request line before attempting to complete the current Event.

4.1.3 Fault Reset (Bus Bit 2)

This bit will clear MC Status Codes and reset the fault bit in the Status Byte providing the fault condition no longer exists. Refer to section 5.1.8.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | А  | 77653473  | 31    | В    |

4.1.4 Spindle Power On (Bus Bit 3)

This bit, when a logic 1, will command the drive to start the spindle motor provided that DC power is on, AC power is on, the control panel start/stop switch is in the start position, and the access-door-closed and pack-in-place interlocks are satisfied, and the Fault bit in Status is zero. To allow operator control of the LMU via the front panel, the default power-on condition of this bit is always considered active. A Spindle Power Off command will disable operator control and cause the drive to enter the remote spindle on/ off mode. The Spindle Power On command, unlike other Event Bytes will be stored in the LMU's memory and does not require the adapter to reissue this bit with every Event Byte.

A single completion Status will be requested when the drive is up to speed, heads loaded, and ready for operation.

4.1.5 Return to Zero (RTZ) (Bus Bit 4)

This bit will deactivate the seek error bit in Status, cause the actuator to select head O, and then seek to track O. Completion status as described for the Head Select and Seek functions (sections 4.1.6 and 4.1.7) will be sent to the adapter for this command. A head change operation will always be performed even though head O may be previously selected. Any Seek or Head Select request received in the same Event with an RTZ will determine the cylinder or head that will be selected after the RTZ. If the Fault status bit is a logic 1, Status will not change and the RTZ will not be performed if the Fault Reset bit is inactive in this Event.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| A  | 77653473  | 32    | В    |

4.1.6 Head Select (Bus Bit 5)

When this bit is a logic 1, the drive will read the Head Address Byte and perform the most appropriate action described below:

- If the new head address is greater than 3, the drive will set the Seek Error bit in Status to a logic 1 and take no further action until an RTZ command is received from the adapter. If a valid head address other than 0 is desired, it may be issued with the RTZ Event Byte transfer as a multiple event execution. Refer to section 4.1.5.

- 2. If the new head address is the same as the head currently selected, there will be no action or change in Status although completion Status will be returned.

- 3. If a seek was requested with a valid Head Select, the following will happen: the Head and Cylinder Address Bytes will be requested from the adapter; Head Select will be performed followed by the seek operation; and at the completion of the seek, Status transmission will be requested.

- 4. If a valid Head Select is received without a seek in the same Event Byte, the head change will be performed immediately. On Cylinder timing will be identical to Case 3 above. In this case, the Cylinder Address Byte will not be read.

If Seek Error or Fault is a logic 1, the Head Address Byte will be requested, but Status will not change and Head Select will not be performed although completion Status will be returned.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653473  | 33    | В    |

4.1.7 Seek (Bus Bit 6)

This bit signifies that a seek function is to be performed. The drive will request transmission of the adapter's Low Cylinder Byte, and verify that the cylinder address specified by this byte is 205 or less. If an invalid address (such as 206 or greater) is received, the drive will activate the Seek Error bit in the Status Byte and request a Status transfer. If the drive is unable to complete the seek within 500 milliseconds, the drive will activate the Fault bit in Status and request a Status Byte transfer.

If the Seek Error bit in the Status Byte is a logic 1 or if the Fault bit in Status is a logic 1, the cylinder address will be requested, but Status will not change and the seek will not be performed although completion Status will be returned.

4.1.8 Read Escape Register (Bus Bit 7)

The drive will read the adapter's Escape Byte to determine what additional command functions are to be executed.

4.2 ESCAPE BYTE (ADDRESS 000)

The Escape Byte consists of additional bit-encoded operations which are to be performed by the LMU. The adapter should deactivate all bits of the Escapte Byte after it is read by the drive to prevent multiple executions of a single command.

The Servo Offset Plus and Servo Offset Minus commands are not used in the LMU due to the embedded servo positioning system, but are included for future products.