CONTROL DATA®

LARK 50 MICRO UNIT

**MODEL 9457**

GENERAL DESCRIPTION OPERATION INSTALLATION AND CHECKOUT THEORY OF OPERATION DIAGRAMS MAINTENANCE (Non-Sealed Area) PARTS DATA (Non-Sealed Area)

MAGNETIC PERIPHERALS INC.

# MODULE II

HARDWARE MAINTENANCE MANUAL

77711044

### PREFACE

Module II of this manual provides the information needed to install, operate, maintain, and troubleshoot the Lark Micro Unit (LMU).

This module is a compilation of Control Data Corporation's Lark Micro Unit Installation/Operation Manual (# 77711044) and Lark Micro Unit Hardware Maintenance Manual (# 77711050).

The total content of this module is comprised of seven sections:

| SECTION | TITLE                     |

|---------|---------------------------|

| 1       | GENERAL DESCRIPTION       |

| 2       | OPERATION                 |

| 3       | INSTALLATION AND CHECKOUT |

| 4       | THEORY OF OPERATION       |

| 5       | DIAGRAMS                  |

| 6       | MAINTENANCE               |

| 7       | PARTS DATA                |

### NOTE

The Lark Micro Unit (LMU) and the Power Supply & I/O Adapter (PIO) are separate and distinct devices, with their own unique documentation. The LMU is identified as Model 9454 (the 16MB unit) or 9457 (the 50MB unit). The 16MB unit is used with the No Problem Shared System<sup>™</sup> and requires Lanier Service Manual Z-200-299 for the PI/O and Z-200-300 for the Model 9454 Micro Unit. This manual on the 50MB unit consists of three modules--Module I covers the PI/O, Module II covers the Model 9457 Micro Unit, and Module III contains a listing of the Lark Status Codes.

<u>EMI NOTICE</u>: This equipment has been designed as a component to high standards of design and construction. The product, however, must depend on receiving adequate power and environment from its host equipment in order to obtain optimum operation and to comply with applicable industry and governmental regulations. Special attention must be given by the installers and CSRs in the areas of safety, input power, grounding, shielding, and environment temperature of the device to insure specified performance and compliance with all applicable regulations.

i

### OPERATOR SAFETY INSTRUCTIONS

- 1. All operator controls can be found on the front panel.

- 1.1 Start/Stop Switch

This switch energizes the spindle motor. The indicator light flashes until motor is up to speed.

### 1.2 Requirements

The following conditions must be met to initiate operation of the On/Off switch:

- a. The external power source must be on.

- b. The disk cartridge must be properly inserted and the access door tightly closed.

- 1.3 <u>Fixed Prot Switch</u> This switch has an error interrupt indicator lamp. An error is present in the drive when the lamp is flashing.

- 2. OPERATING TEMPERATURE The operating temperature of the drive is 10° to 40° C with a maximum temperature change of 10° C per hour.

- 3. Additional information on the drive can be found in Hardware Maintenance Manual 77711050.

- 4. The corresponding VDE regulations must be observed during installation.

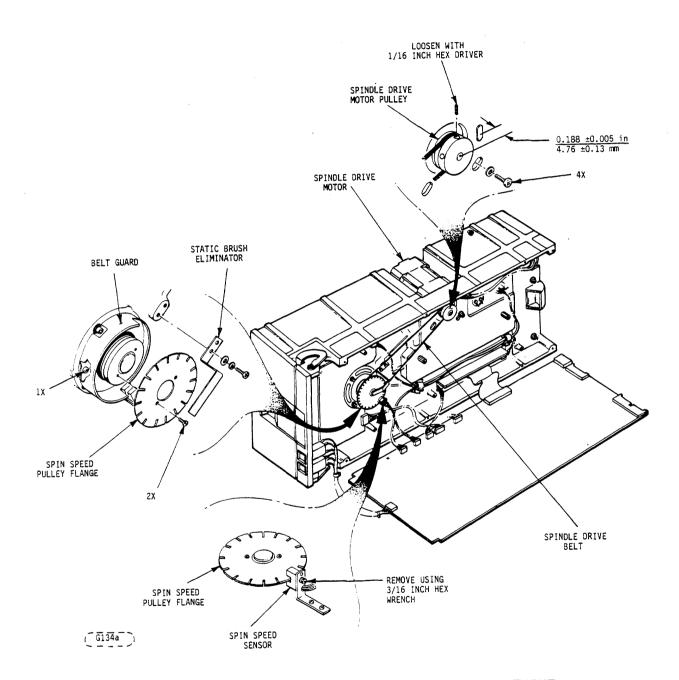

- 5. Note: The spindle drive motor may reach a temperature of 70° C.

- 6. In case of a malfunction the unit is to be serviced only by trained personnel. The access door can be opened only by trained personnel after the power has been switched off.

### BEDIENUNGSANLEITUNG

- 1. Alle Benienungseinrichtungen befinden sich an der Frontseite.

- 1.1 Ein-und Ausschalter: Dieser Schalter hat die Funktion den Motor und die Logik mit Strom zu versorgen. Die eingebaute Kontrollampe blinkt so lange bis der Antriebsmotor seine Drehzahl erreicht hat.

- 1.2 VORAUSSETZUNG

- Voraussetzung zur Funktion des Aus-Einschalters ist:

- a) Die aussere Stromversorgung muss einshaltet sein.

- b) Die Kasette lst eingeschoben und die Bedienungsklappe ist geschlossen.

- 1.3 Der zweite Drunkschalter (FIXED PROT) ist ebenfalls mit einer Fehleranzeigelampe ausgestattet. Ein Fehler im Gerat ist vorhanden wenn diese Anzeige blinkt.

- 2. <u>BETRIEBSTEMPERATUR</u> 10° C bis 40° C bei einer 'A'nderung von 10° C innerhalb einer Stunde.

- 3. Zusätzliche Informationen sind zu ersehen im Hardware Maintenance Manual - 77711050.

- 4. Beim Einbau des Gerätes sind die einschlagigen VDE-Vorschriften einzuhalten.

- 5. Zu beachten ist, dass der Antriebsmotor eine Betriebstemperatur von ca. 70° C erreichen kann.

- 6. In Falle eines Defektes darf das Gerät nur von Fachpersonal nach Abschalten der Stromzufuhr geoffnet werden.

# MODULE II TABLE OF CONTENTS

| SECTI                                                       | ION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPERA                                                       | CE<br>TOR SAFETY INSTRUCTIONS<br>Benutzer Sicherheitsanweisung)                                                                                                                                                                                                                                                                                                                                                                                                                        | i<br>ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GENE                                                        | RAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.1<br>1.2<br>1.3                                           | INTRODUCTION<br>GENERAL DESCRIPTION<br>1.2.1 Standard Features<br>1.2.2 Major Components<br>1.2.3 Operational Characteristics<br>FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                              | 1-1<br>1-1<br>1-1<br>1-1<br>1-4<br>1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OPER.                                                       | ATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | INTRODUCTION<br>OPERATOR CONTROLS AND INDICATORS<br>OPERATING PRECAUTIONS<br>2.3.1 Power Up For On-Line Operation<br>2.3.2 Write Protect Operation<br>2.3.3 Stop Operation<br>2.3.4 Power Down<br>FAULT OPERATING INSTRUCTIONS<br>AUTOMATIC SELF TEST CAPABILITY<br>REMOVABLE DISK CARTRIDGE HANDLING AND STORAGE<br>REMOVABLE DISK CARTRIDGE INSTALLATION.<br>DISK CARTRIDGE REMOVAL<br>2.8.1 Normal Removal<br>2.8.2 Power Failure or Emergency Stop Removal<br>MAINTENANCE FEATURES | 2-1 2-1 2-1 2-4 2-4 2-4 2-5 2-7 2-7 2-8 2-9 2-9 2-10 2-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| INSTA                                                       | ALLATION AND CHECKOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                      | INTRODUCTION<br>UNPACKING<br>SPACE ALLOCATION<br>COOLING REQUIREMENTS<br>3.4.1 LMU Cooling<br>POWER REQUIREMENTS<br>3.5.1 Primary Power Requirements<br>CABLING AND MATING CONNECTORS<br>3.6.1 General<br>3.6.2 Command/Data Interface Cabling and Connectors<br>3.6.3 AC and DC Power Cabling and Connectors<br>3.6.4 I/O and Power Cable Routing                                                                                                                                     | 3-1<br>3-1<br>3-2<br>3-2<br>3-6<br>3-6<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8 |

# TABLE OF CONTENTS (CONTD.)

| SECTI      | ION                                                                                                                                      | PAGE         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3.8<br>3.9 | GROUNDING<br>ENVIRONMENT<br>INITIAL CHECKOUT AND STARTUP PROCEDURE<br>ACCESSORIES<br>3.10.1 I/O CABLE CHARACTERISTICS AND CONNECTOR PART | 3-14<br>3-15 |

|            | NUMBERS3.10.2AC and DC Power Connector Part Numbers                                                                                      |              |

### THEORY OF OPERATION

| 4.1 | INTROD | UCTION                                         | <b>l-1</b> |

|-----|--------|------------------------------------------------|------------|

| 4.2 | ASSEMB | LIES 4                                         | -1         |

|     | 4.2.1  | Mechanical/Electromechanical Assemblies 4      | 1-2        |

|     | 4.2.2  | Electronic Assemblies 4                        | 1-12       |

| 4.3 | FUNCTI | ONAL DESCRIPTION 4                             | 1-13       |

|     | 4.3.1  | General 4                                      | 1-13       |

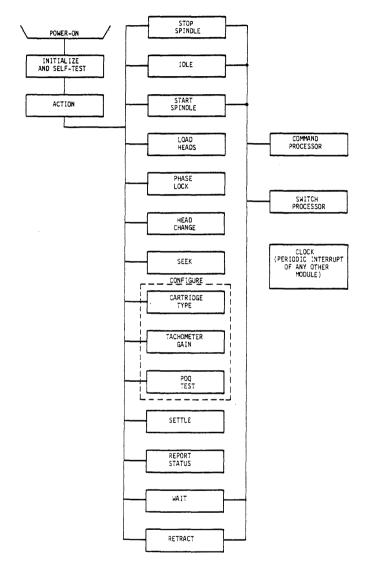

|     | 4.3.2  | Drive Overall Control System 4                 | -14        |

|     | 4.3.3  | Power On/Off Sequencing and Spindle Start/Stop |            |

|     |        | Functions 4                                    | 1-23       |

|     | 4.3.4  | Read/Write Head Positioning System 4           | 1-24       |

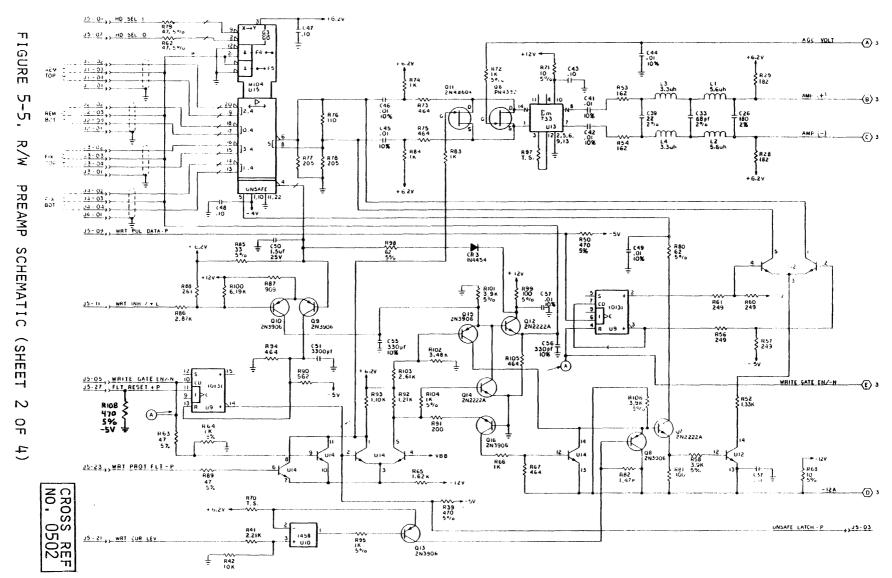

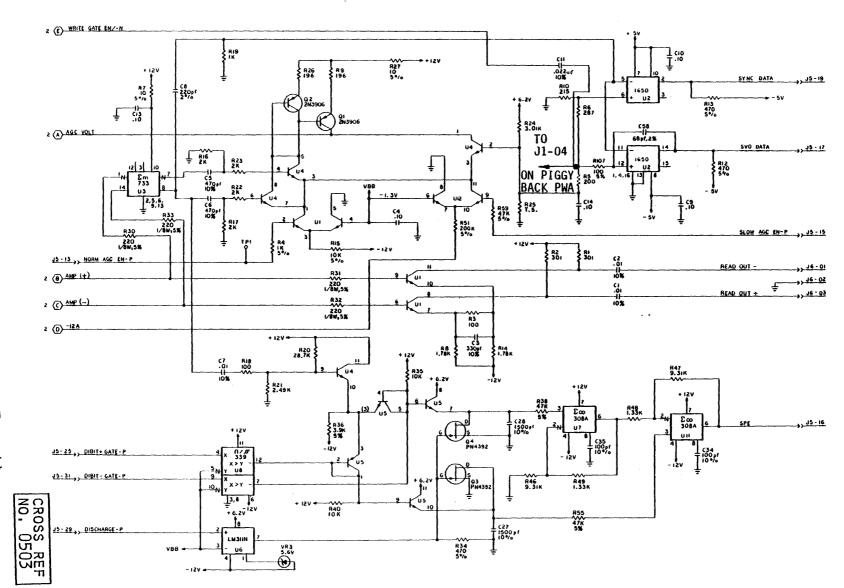

|     | 4.3.5  | Read/Write System 4                            | 1-47       |

|     | 4.3.6  | Fault Detection 4                              | - 65       |

|     |        |                                                |            |

### APPENDIX SERVO LSI CKTS (I/O)

| 4A.1 | SVO DA | TA RCVY (SERVO DATA RECOVI  | ERY) IC PIN | DEFINITIONS                     | .4A-1 |

|------|--------|-----------------------------|-------------|---------------------------------|-------|

|      | 4A.1.1 | Inputs                      |             | • • • • • • • • • • • • • • • • | 4A-1  |

|      | 4A.1.2 | SVO Data Revy Outputs       |             |                                 | 4A-4  |

| 4A.2 | SVO-PH | OSC CNTR-CNT-IC PIN DEFINIT | rions       |                                 | 4A-7  |

|      | 4A.2.1 | Inputs                      |             |                                 | 4A-7  |

|      | 4A.2.2 | Outputs                     |             |                                 | 4A-9  |

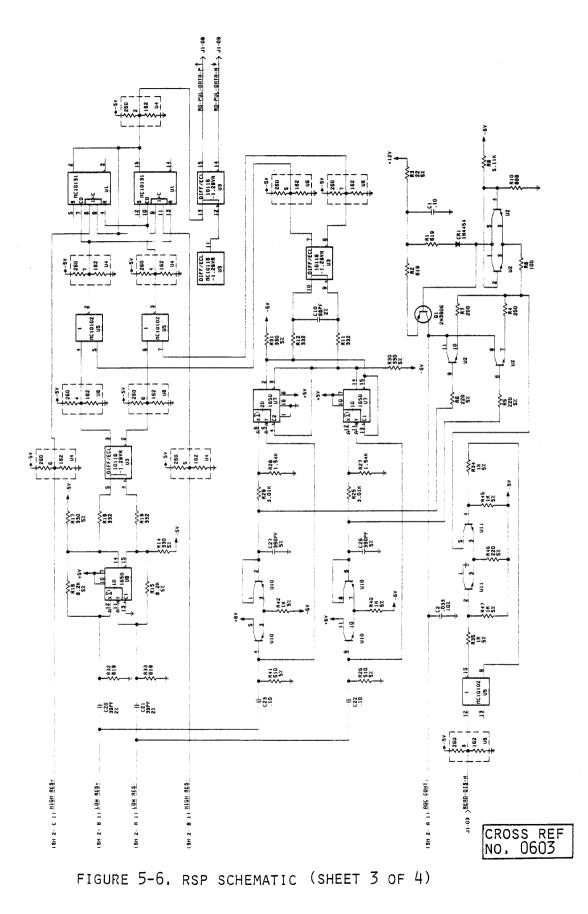

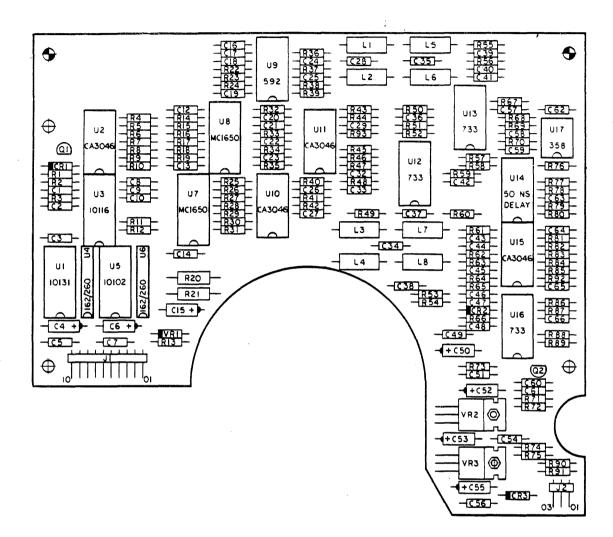

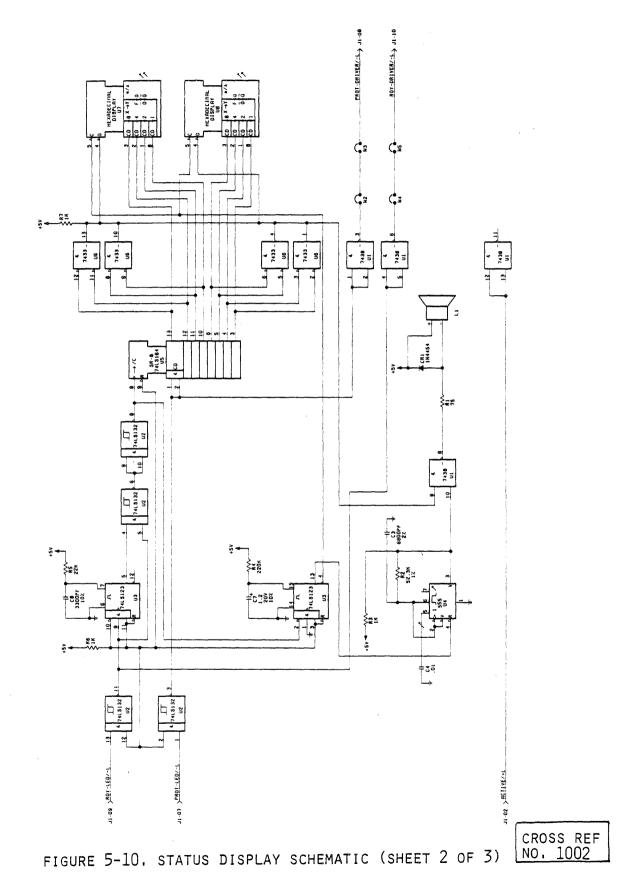

### DIAGRAMS

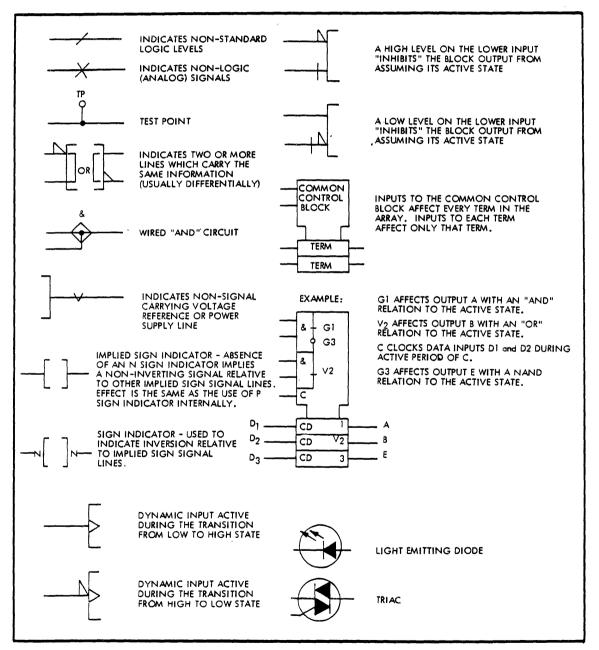

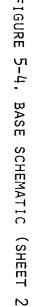

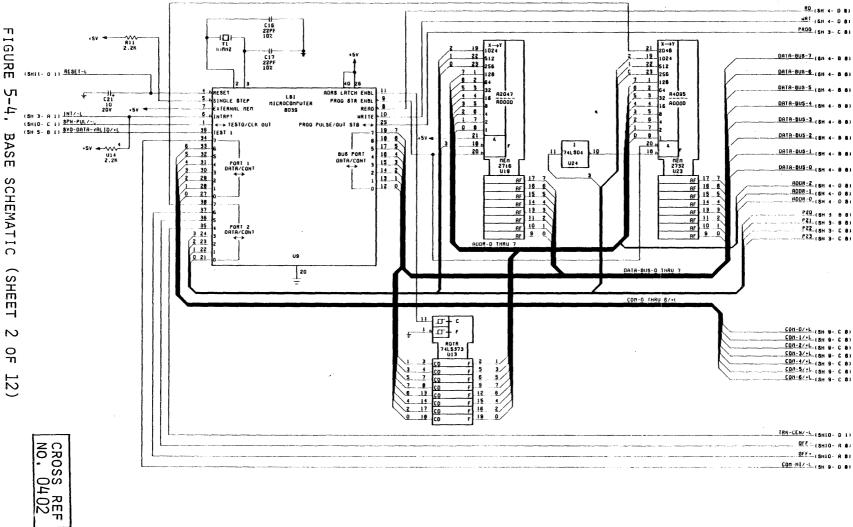

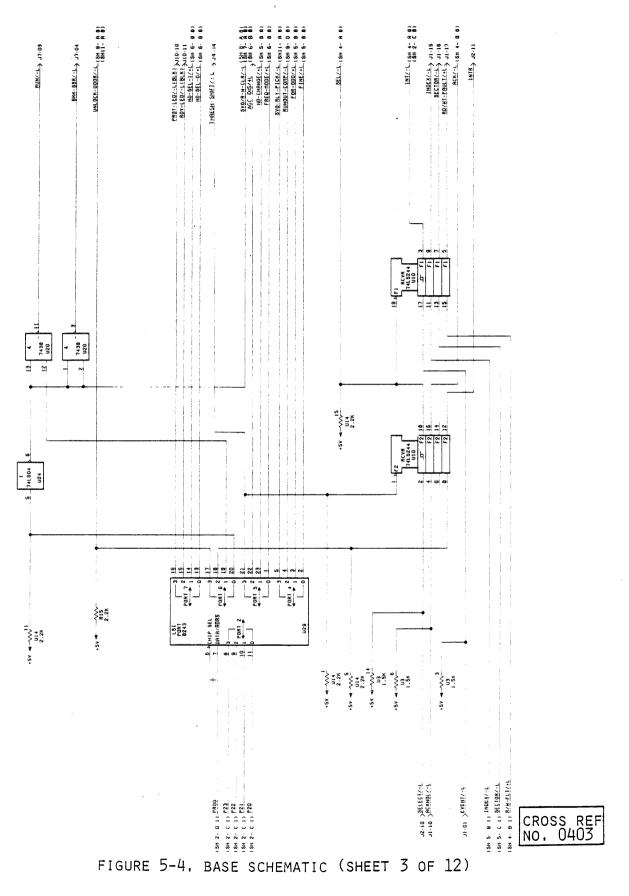

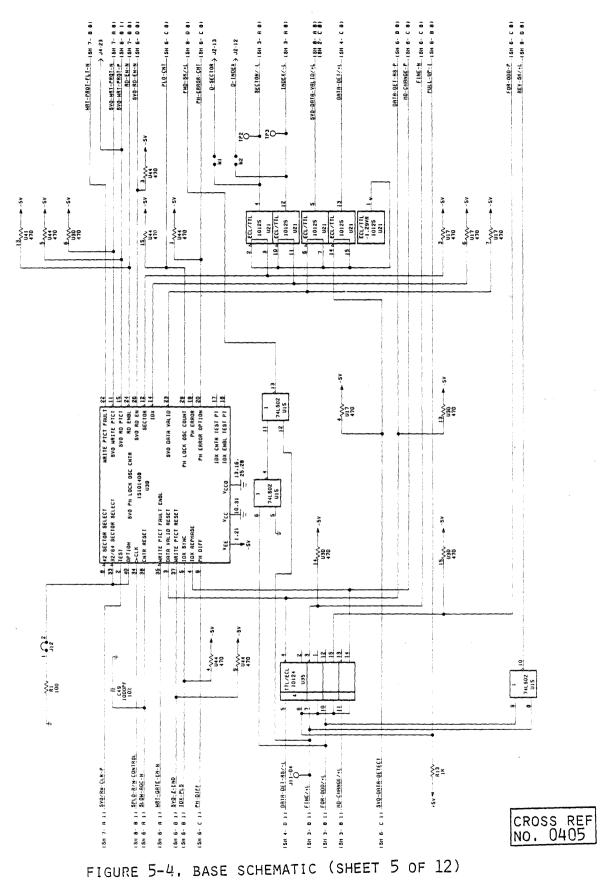

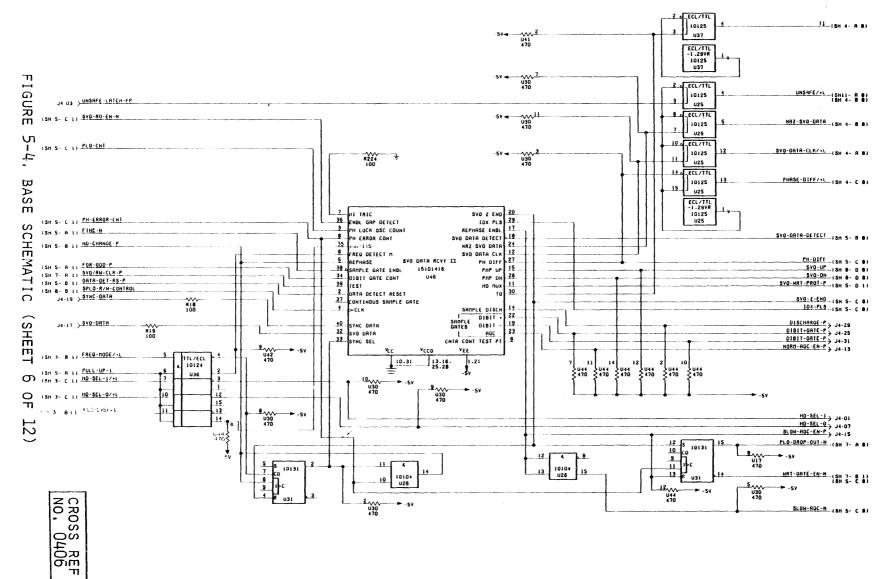

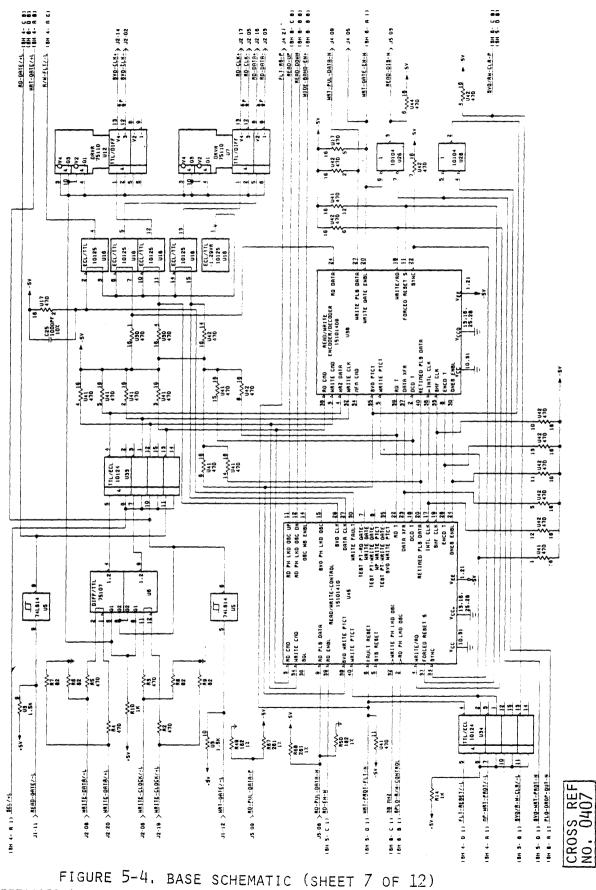

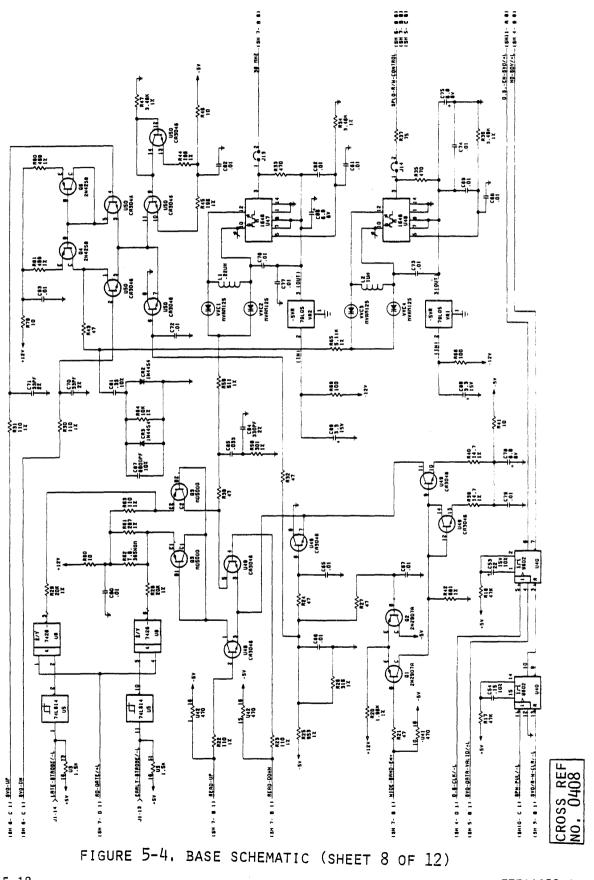

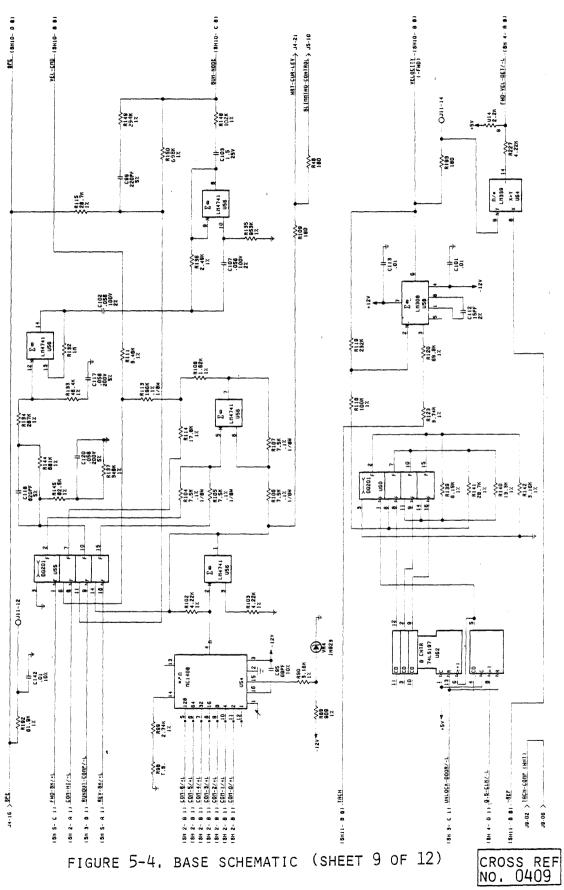

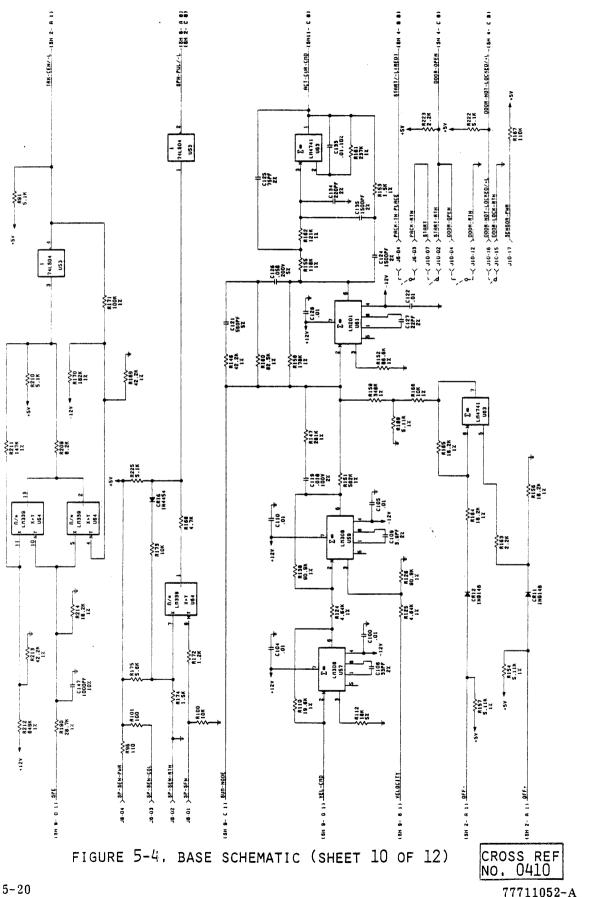

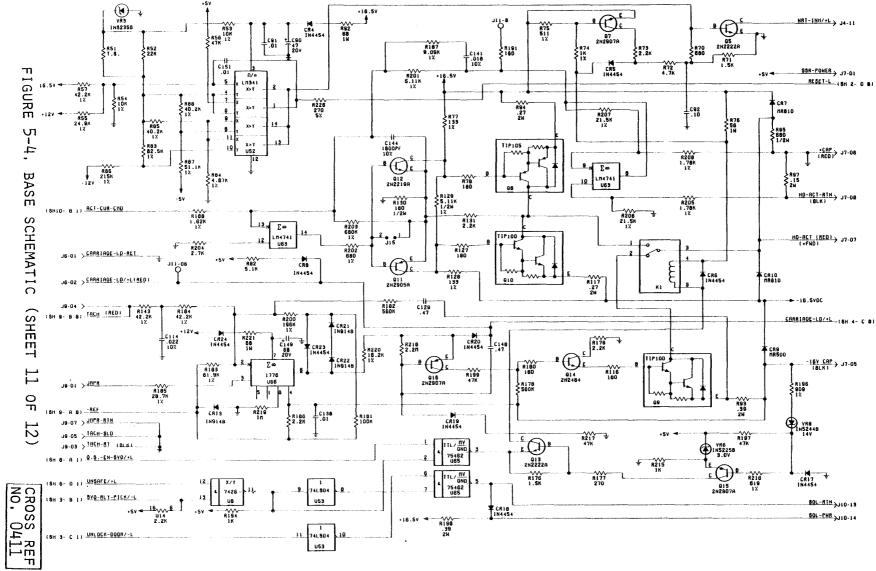

| 5.1 | INTRODUCTION                                                 | 5-1  |

|-----|--------------------------------------------------------------|------|

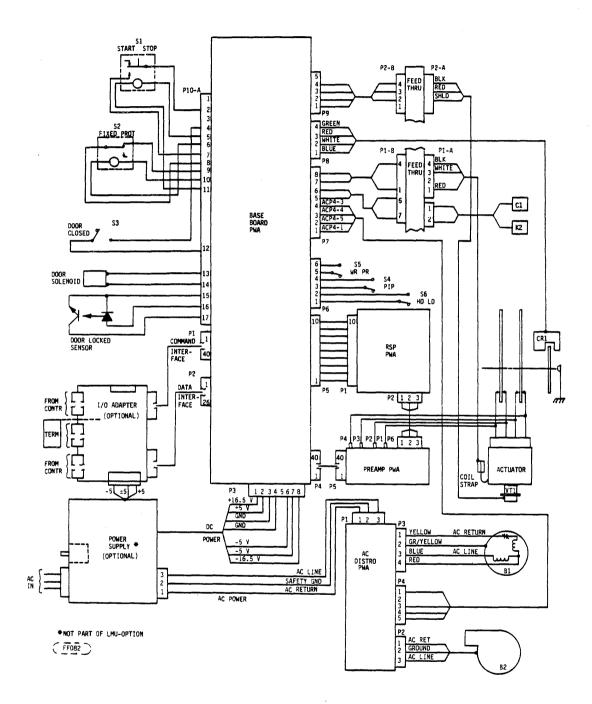

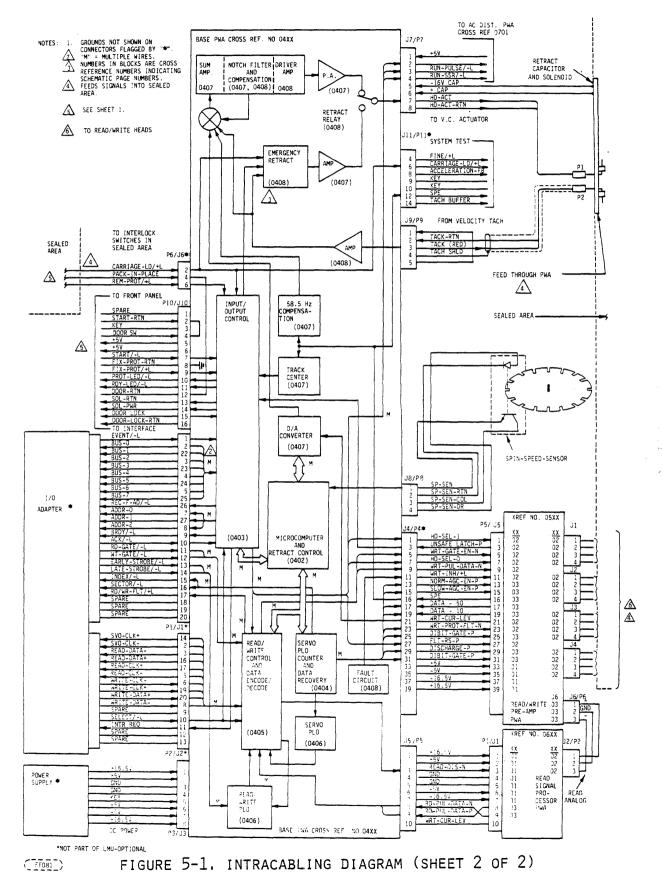

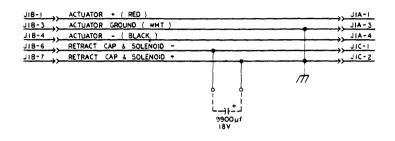

| 5.2 | INTRACABLING DIAGRAM                                         | 5-1  |

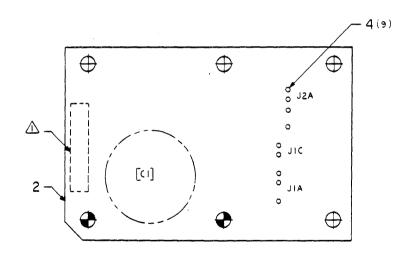

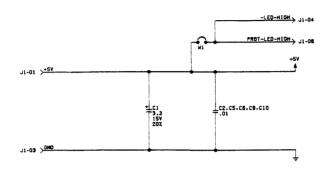

| 5.3 | CIRCUIT BOARD DIAGRAMS                                       | 5-1  |

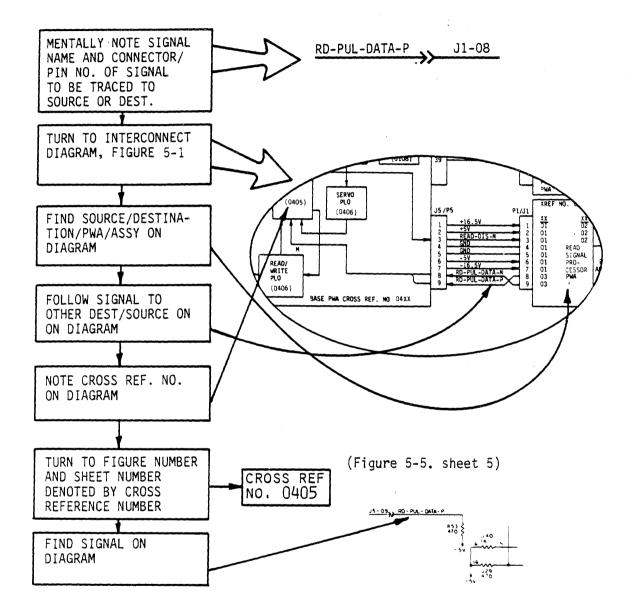

|     | 5.3.1 Point-to-Point Logic Interconnections Between          |      |

|     | Circuit Boards                                               | 5-1  |

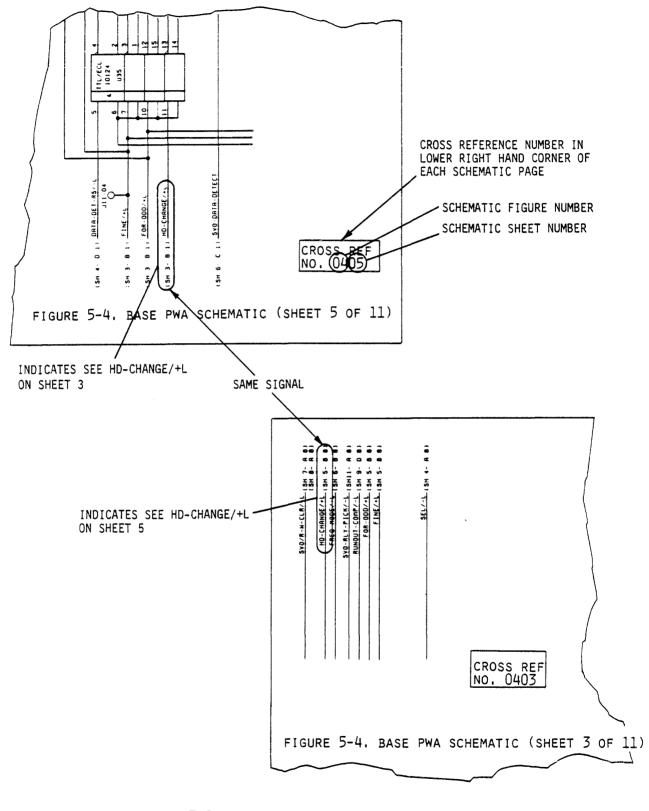

|     | 5.3.2 Cross Reference Numbers                                | 5-6  |

|     | 5.3.3 Summary: Point-to-Point Interconnection Signal Tracing | 5-6  |

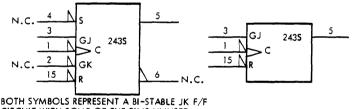

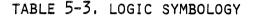

| 5.4 | LOGIC DIAGRAM SYMBOLOGY                                      |      |

|     | 5.4.1 General Information                                    | 5-6  |

|     | 5.4.2 General Signal Annotation                              | 5-6  |

|     | 5.4.3 Symbology                                              |      |

|     | 5.4.4 Function Symbology                                     | 5-9  |

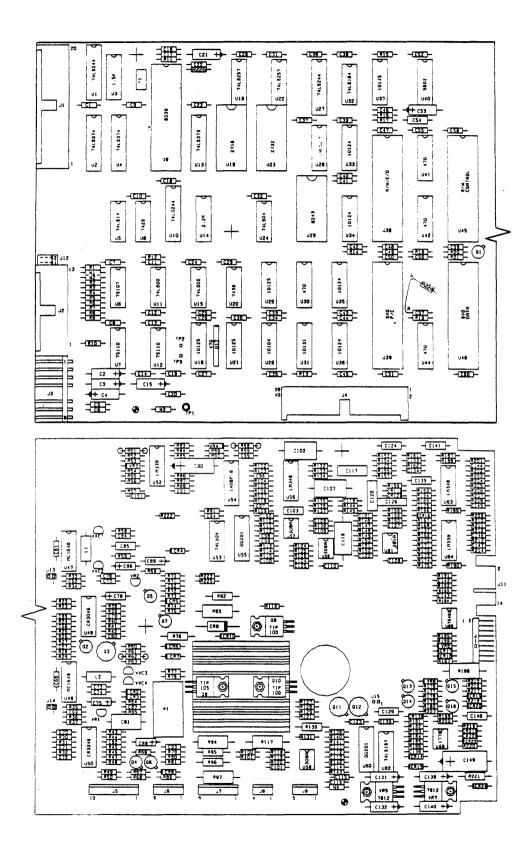

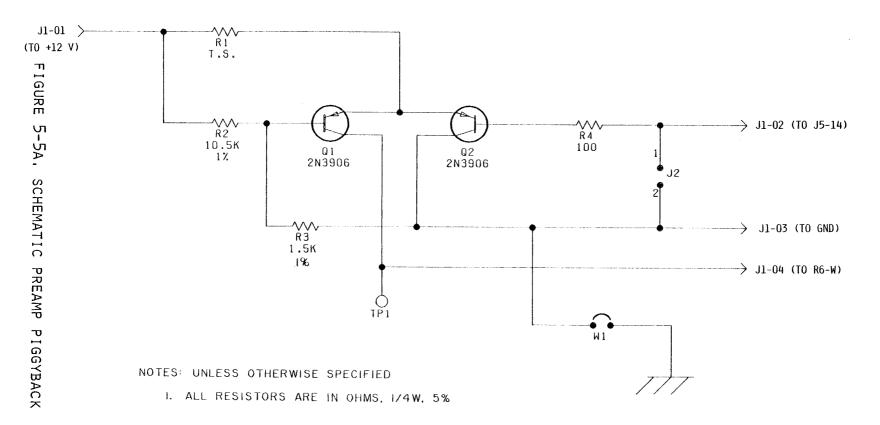

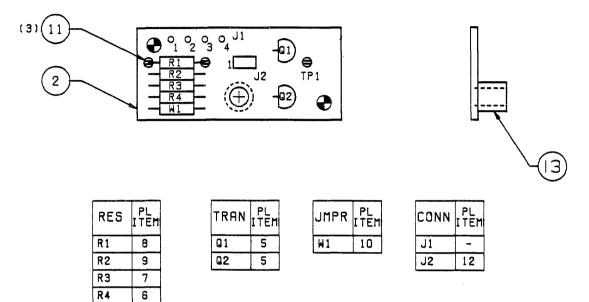

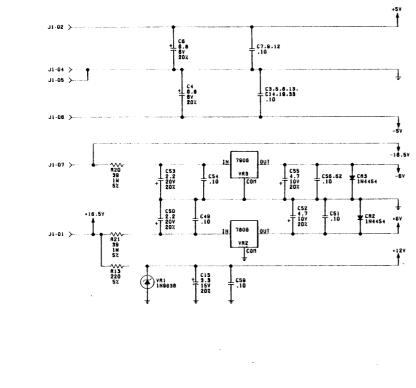

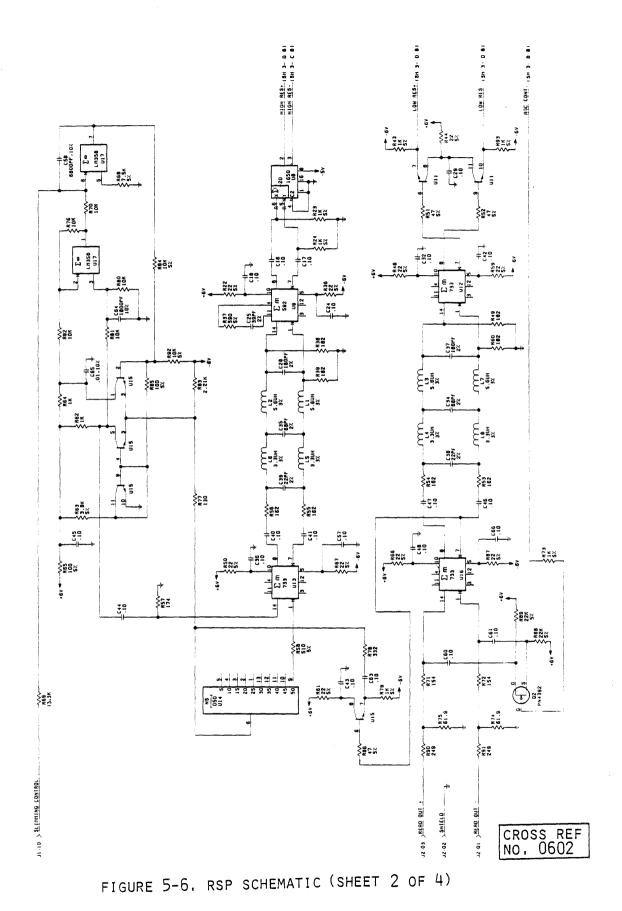

| 5.5 | LOGIC DIAGRAMS AND SCHEMATICS                                | 5-9  |

|     | 5.5.1 Base PWA Matrix                                        |      |

| 5.6 | I/O INTERFACE-LMU TO I/O ADAPTER                             | 5-39 |

# TABLE OF CONTENTS (CONTD.)

# SECTION

## PAGE

| 6.3   | INTRODUCTION       6         SAFETY AND SPECIAL MAINTENANCE PRECAUTIONS       6         6.2.1       Safety Precautions       6         6.2.2       Special Maintenance Precautions       6         MAINTENANCE TOOLS       6 | -1<br>-1<br>-1<br>-2 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|       | MAINTENANCE PROCEDURES66.4.1Index and Schedule66.4.2Removal and Replacement Procedure List6                                                                                                                                  | -2                   |

| PARTS | DATA                                                                                                                                                                                                                         |                      |

|       | INTRODUCTION 77<br>ORDERING PARTS 77                                                                                                                                                                                         |                      |

### 1.1 INTRODUCTION

The Lark 50 Micro Unit (9457) is a small, low cost, medium performance, random access, rotating disk mass memory device featuring both removable and fixed storage. The Lark 50 Micro Unit (LMU) employs the latest 8 inch rigid disk technology using low mass flying read/write heads attached to a precisely controlled linear head positioner. The unformatted storage capacity of the LMU is 50 Mbytes. 25 Mbytes of storage is provided by the removable disk (cart-ridge) and 25 Mbytes of storage is provided by the non-removable disk.

### 1.2 GENERAL DESCRIPTION

### 1.2.1 STANDARD FEATURES

The following are standard features of the LMU:

- 25 MB front-loading cartridge receiver (cartridge not included)

- 32 or 64 hard sector configurations

- Early/late data strobing

- Independent manual write protect on fixed and/or cartridge media (switch for fixed; special tab on cartridge)

- Internal fault monitoring

- LSI and Microcomputer control

- No electrical adjustments required

- No head alignment required

- Low power consumption

- Low acoustic noise

- Small physical size

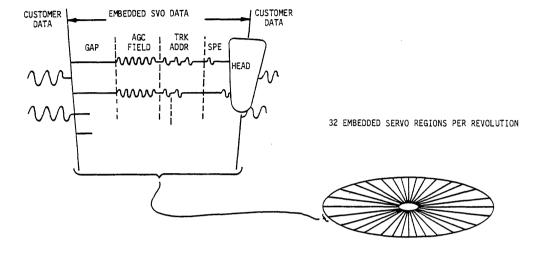

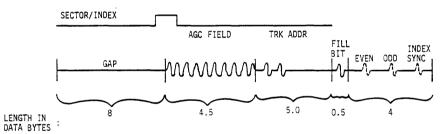

- Embedded servo

- Self circulating air filtration system

- Vertical or Horizontal Operation

### 1.2.2 MAJOR COMPONENTS

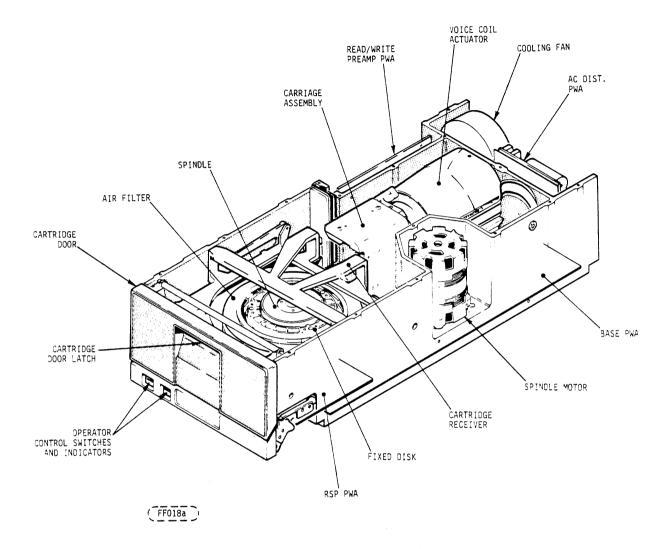

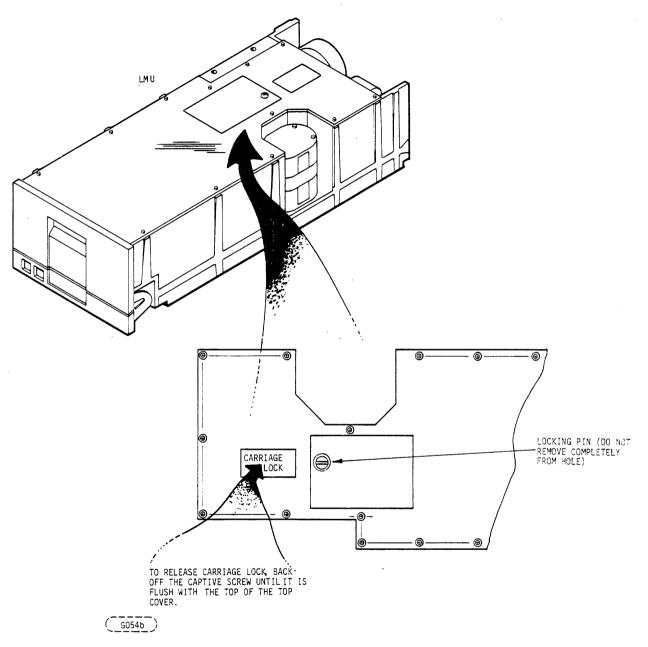

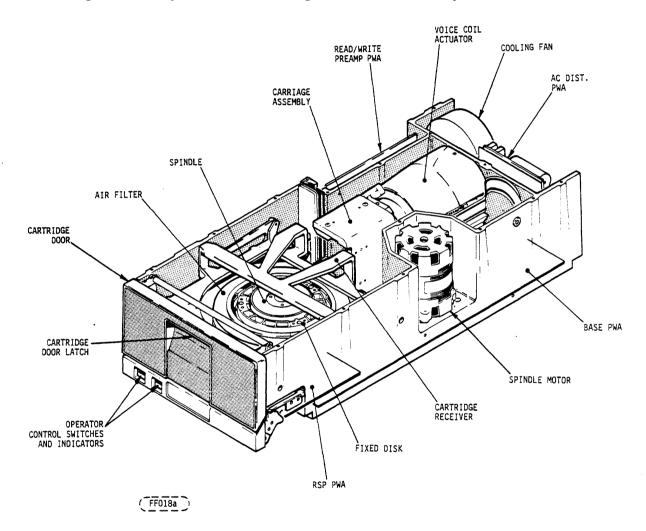

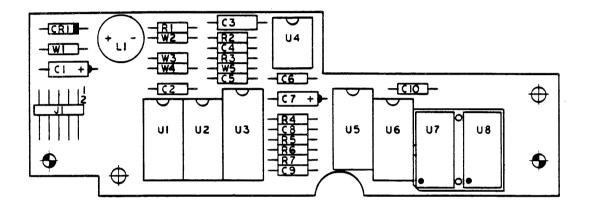

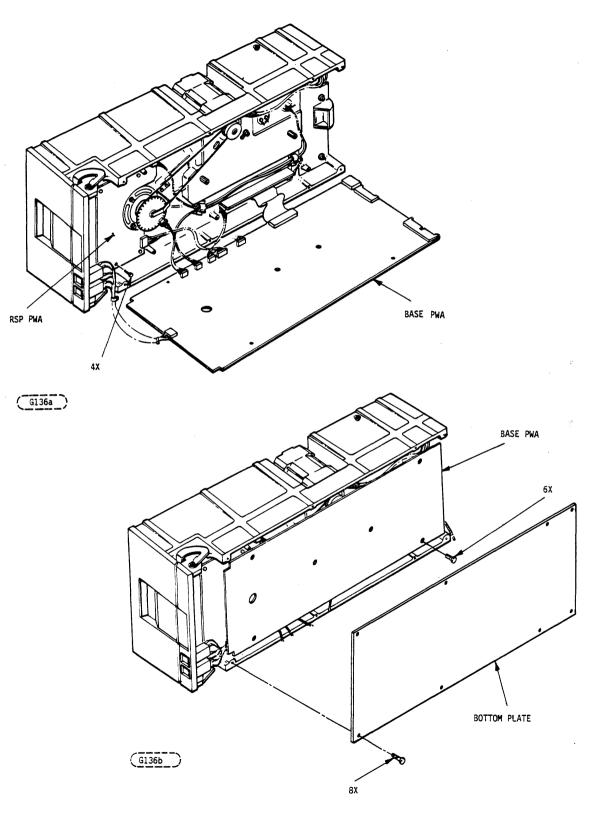

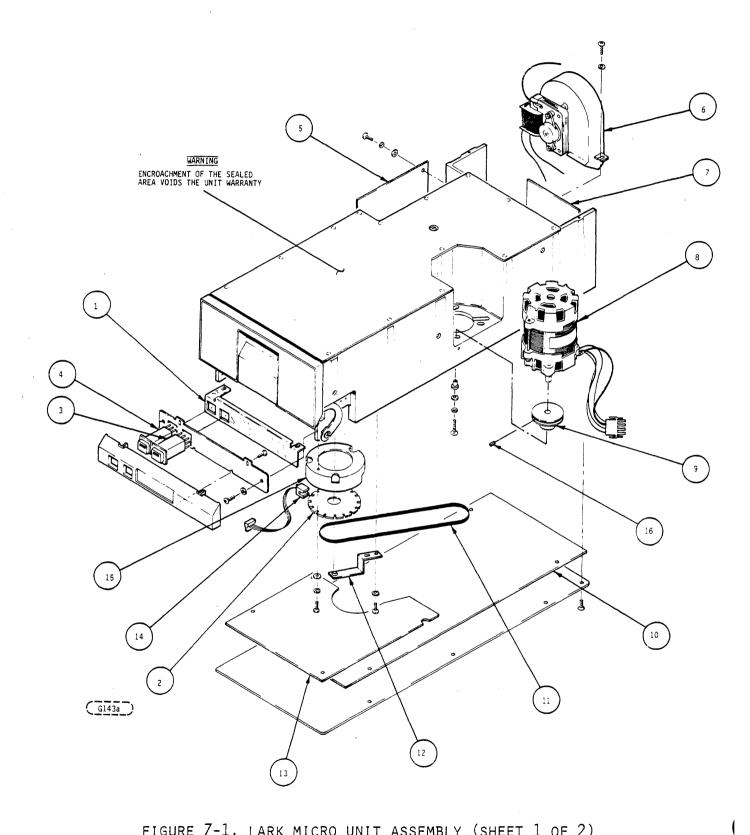

The LMU consists of major assemblies as illustrated in Figure 1-1.

The following major components make up the LMU:

• Electronics

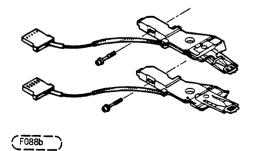

The logic is implemented using low power Schottky for commands and control logic and standard Schottky and ECL for the read/write and servo logic. The microprocessor is designed with standard microcomputer building blocks. The logic is mounted on three PWA's: Base PWA, Read/Write Preamp PWA and Read Signal Processor PWA.

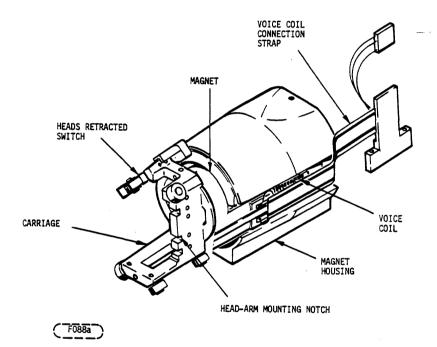

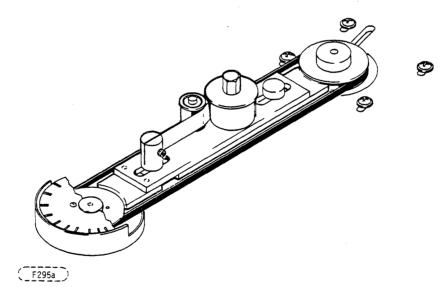

• Voice-Coil Head Positioner

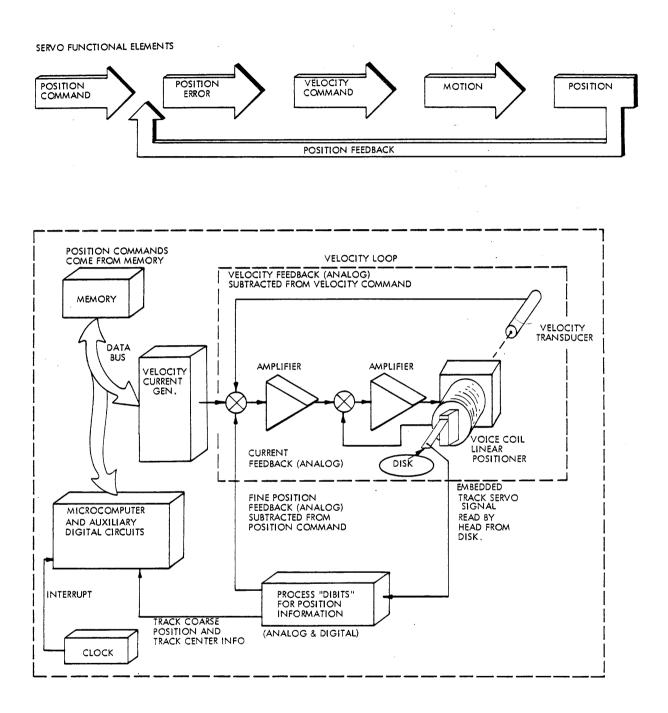

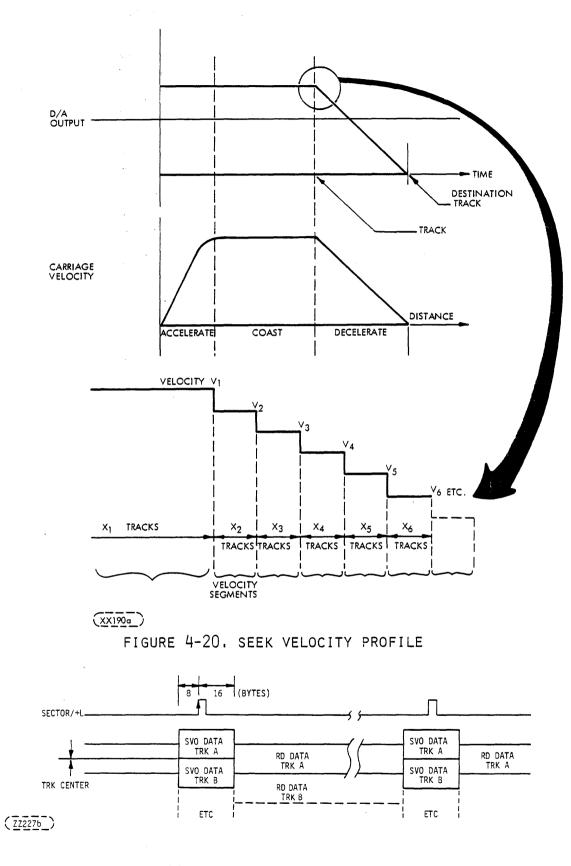

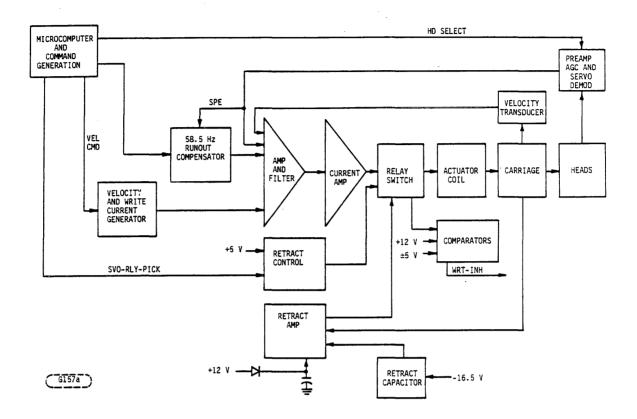

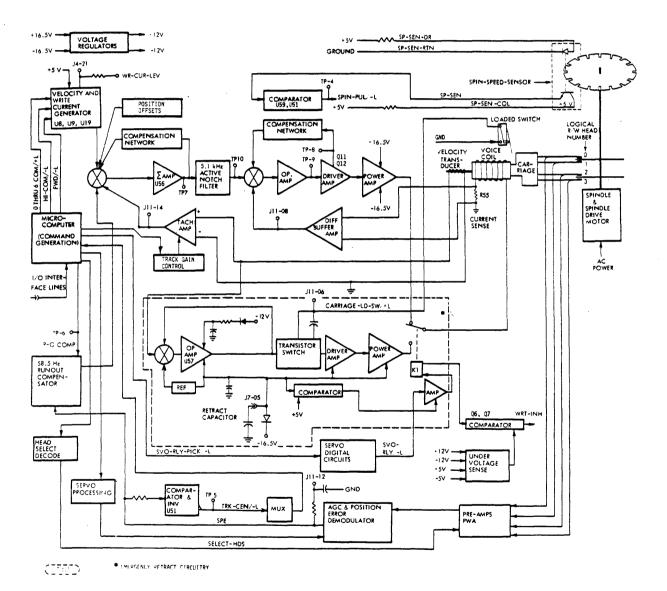

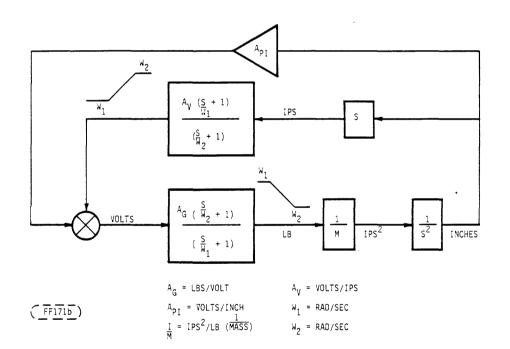

Head positioning is performed using a closed-loop proportional servo system with acceleration, velocity and position feedbacks. The carriage is driven by a voice-coil linear actuator utilizing positioning information from embedded servo information.

FIGURE 1-1. LMU MAJOR COMPONENTS

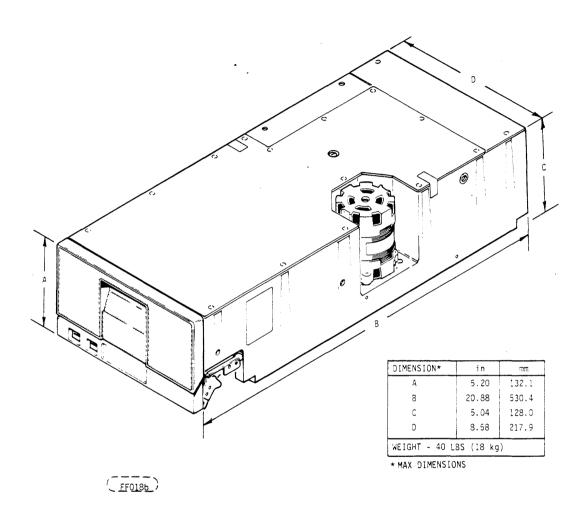

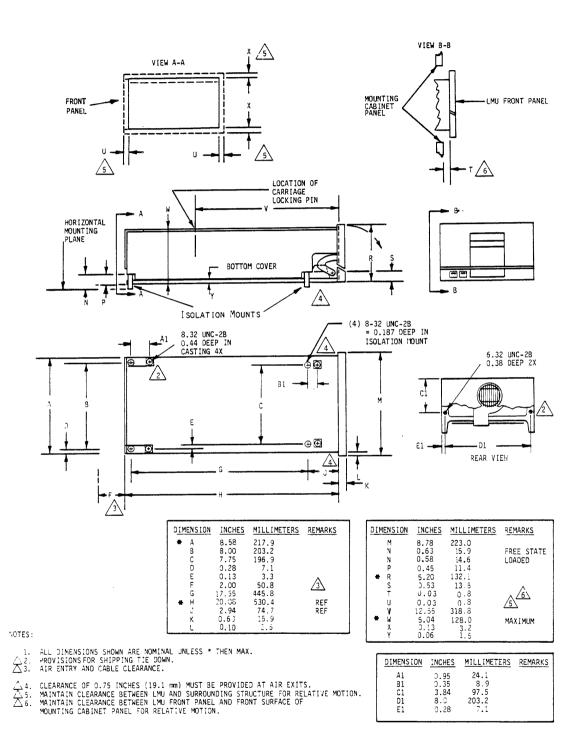

## FIGURE 1-2. LMU PHYSICAL CHARACTERISTICS

• Deck and Spindle

A rigid cast-aluminum deck and precision spindle insures positive registration and seating of cartridge. An AC induction motor provides spindle rotation through a belt and pulley.

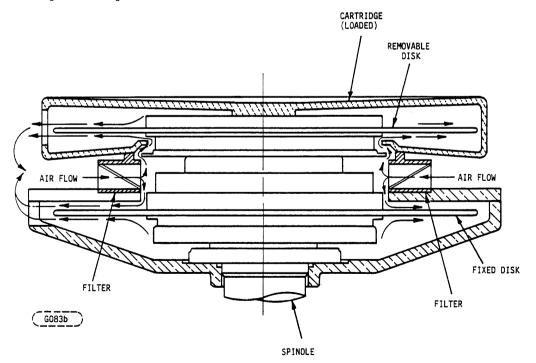

• Air Supply and Filtering

A direct drive blower provides external cooling air for the electronics located outside sealed area. Internal air in the sealed area of the unit is continually recirculated through a filter that separates the fixed disk area from the cartridge receiver area, provided the disk cartridge is installed.

• Cartridge Receiver

A front-load cartridge-receiving mechanism integral to the deck assembly facilitates the insertion and removal of cartridge media.

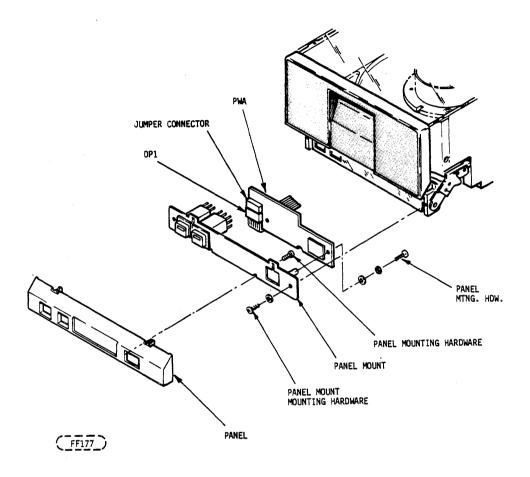

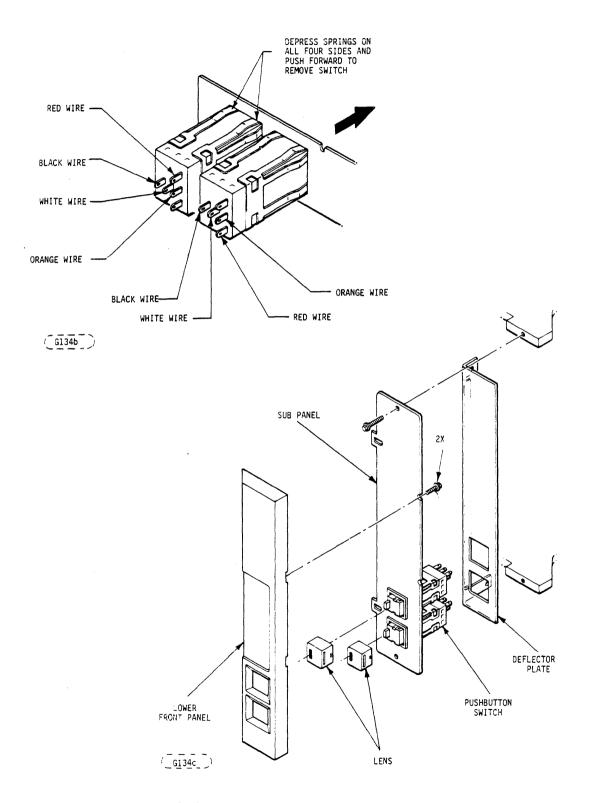

• Operator Control Panel

Controls and indicators for use by the operator are located in the LMU front panel. These are START/STOP switch, READY indicator (part of START/STOP switch), FIXED PROT switch, and FAULT indicator (part of FIXED PROT switch).

NOTE The LMU is a component and therefore does not require a FCC label.

### 1.2.3 OPERATIONAL CHARACTERISTICS

Operational characteristics of the LMU are summarized in Table 1-1.

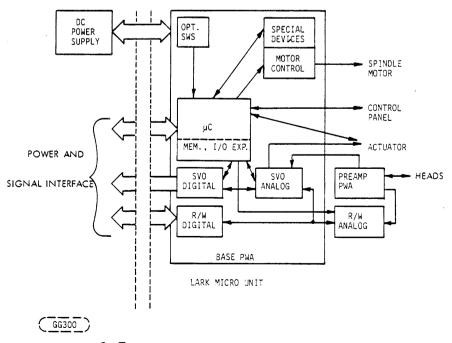

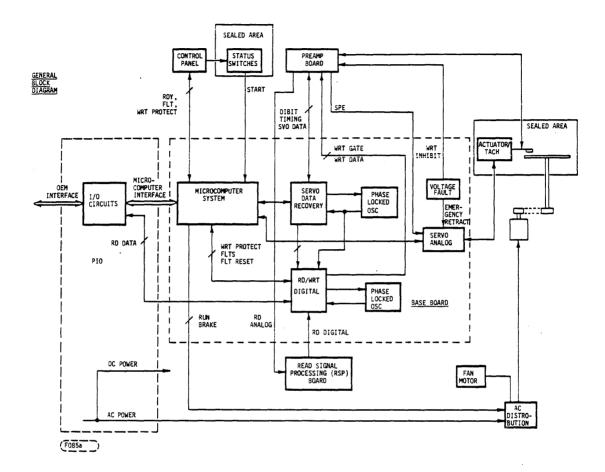

## 1.3 FUNCTIONAL BLOCK DIAGRAM

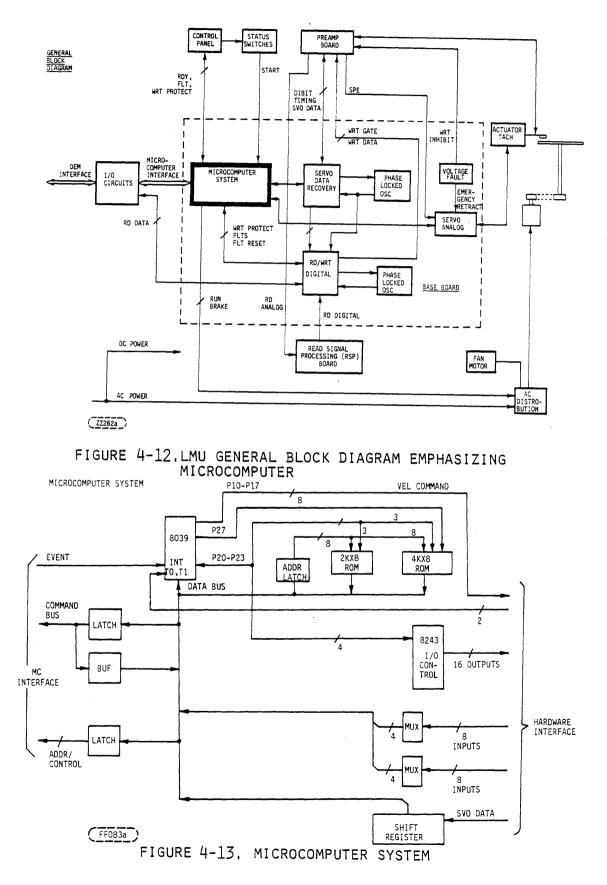

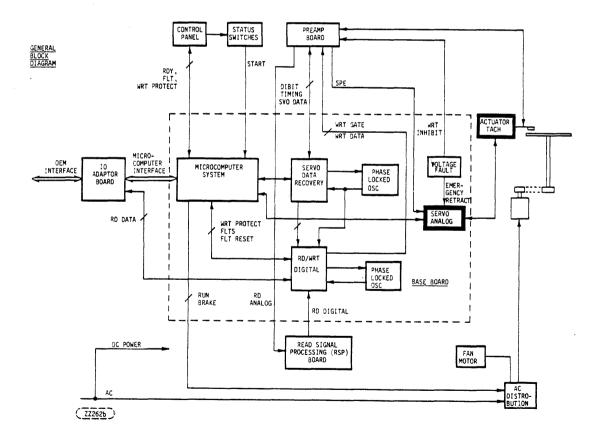

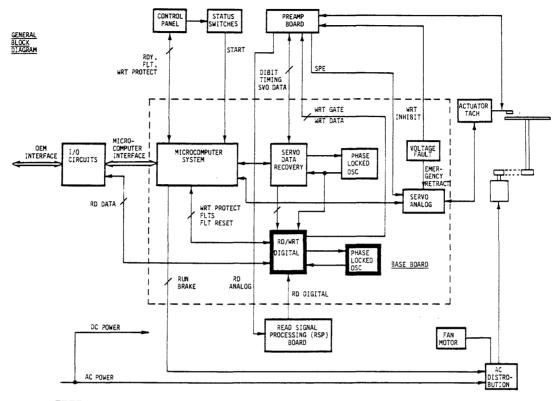

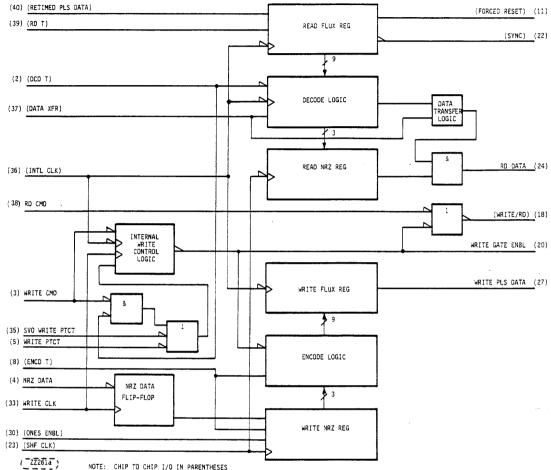

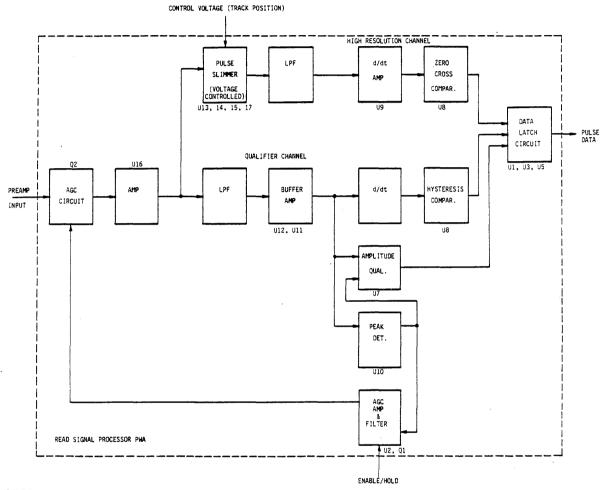

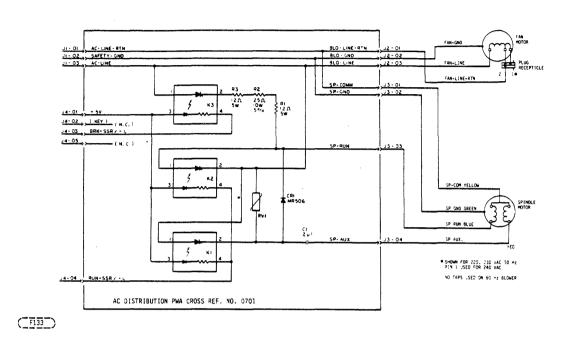

A functional block diagram of the LMU is shown in Figure 1-3. The majority of the electronics is located on one large printed circuit board called the Base PWA which is mounted in the base of the LMU (shown enclosed by dotted lines in Figure 1-1). The Preamp PWA and the RSP PWA amplify and process the signals read from the disk. The AC Distribution PWA controls the AC power distribution to the fan motor and the spindle drive motor.

| TOTAL CAPACITY (UNFORMATTED)                    | LARK 50                 |

|-------------------------------------------------|-------------------------|

| Removable Disk Cartridge<br>Fixed Disk<br>Total | 25 MB<br>25 MB<br>50 MB |

| Number Cylinders (Total)                        | 624                     |

| Number Heads:                                   |                         |

| Removable<br>Fixed<br>Total                     | 2<br>2<br>4             |

| Unformatted Track Capacity                      | 20,672 Bytes            |

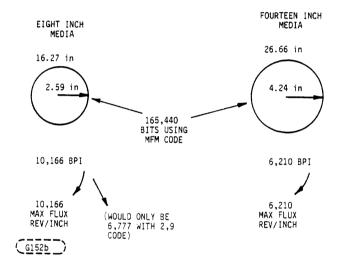

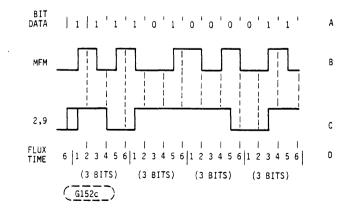

| Recording Mode<br>BPI<br>TPI                    | (2,9)<br>10,166<br>715  |

| Spindle Speed                                   | 3510 +3.0% r/min        |

| Data Transfer Rate (Nominal)                    | 9.677 MHz               |

| Maximum Latency<br>Average Latency              | 17.94 ms<br>8.55 ms     |

TABLE 1-1. OPERATIONAL CHARACTERISTICS SUMMARY

FIGURE 1-3. LMU FUNCTIONAL BLOCK DIAGRAM

.

· · · •

## OPERATION

### 2.1 INTRODUCTION

This section provides the instructions and information required to operate the Lark 50 Micro Unit.

### 2.2 OPERATOR CONTROLS AND INDICATORS

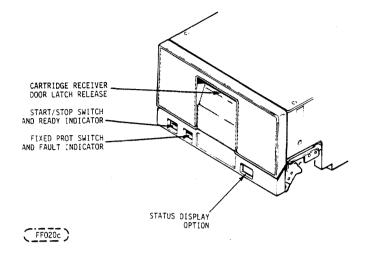

Figure 2-1 shows the location of the operator controls and indications. All operator controls and indicators are on the front panel. A functional description of these controls and indicators is given in Table 2-1.

### 2.3 OPERATING PRECAUTIONS

The following precautions and practices are to be observed while operating the LMU to obtain best performance and reliability of the equipment:

- 1. Keep a cartridge in the unit at all times and keep the access door closed to prevent unnecessary entry of atmospheric contaminants.

- 2. To prevent damage and/or data loss, follow the Disk Cartridge Installation procedure of this section.

- 3. The operator should not attempt to override any interlocks in the system.

### WARNING

Removing seal or top cover on sealed area voids warranty.

### NOTE

If a pinging or scratching sound (caused by head-to-disk contact) is heard and persists, stop the unit by using the Stop and Power down procedure of this section.

### NOTE

If while the drive is operating the Cartridge Receiver Door Latch Release (Figure 2-1) is inadvertantly operated sufficiently to cause the spindle to begin slowing (READY indicator blinks), place the START/STOP switch in the STOP position and allow the spindle to come to a complete stop. Remove the cartridge and inspect the door mechanism for any damage. In the absence of damage, re-insert the cartridge and restart the drive in a normal manner.

# FIGURE 2-1. OPERATOR CONTROLS AND INDICATORS

TABLE 2-1. CONTROLS AND INDICATORS (SHEET 1 OF 2)

| CONTROL OR INDICATOR        | FUNCTION                                                                                                                                                                          |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START/STOP switch/indicator | Start switch energizes spindle motor and initiates the first seek mode provided the following conditions are met:                                                                 |

|                             | 1. AC Power is present (ON) at the LMU.                                                                                                                                           |

|                             | <ol> <li>Disk cartridge loading door closed and<br/>latched with cartridge in place.</li> </ol>                                                                                   |

|                             | <ol> <li>WRITE PROT indicator is not blinking,<br/>indicating a no fault condition.</li> </ol>                                                                                    |

| READY indicator             | Located within the START/STOP switch.<br>READY indicates unit ready status. READY<br>indicator is illuminated whenever unit<br>has completed purge cycle and heads are<br>loaded. |

|                             | The READY light will blink throughout the spindle start and stop procedure.                                                                                                       |

|                             | As long as the heads are on cylinder, the<br>READY indicator will be illuminated even<br>though the WRITE/PROT indicator may blink<br>to show a fault.                            |

2 - 2

TABLE 2-1. CONTROLS AND INDICATORS (SHEET 2 OF 2)

| <b></b>                           | TIMOTICATORS (SHEET Z OF Z)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTROL OR INDICATOR              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| READY indicator (contd.)          | The Lark 50 indicator will rapid blink<br>during drive activity to indicate that<br>the drive is either seeking, reading,<br>writing or doing self test.                                                                                                                                                                                                                                                                                                                                                                                                       |

| FIXED PROT switch/FAULT indicator | When operated to the inward position, this<br>alternate action switch disables the write<br>driver to the fixed media. The indicator,<br>when illuminated steadily, indicates that<br>the fixed disk is write protected. When<br>the indicator blinks, it indicates a<br>fault condition occurred or exists.<br>Rapid blinking (with READY inactive)<br>indicates a cartridge "Protect Data<br>Quality" fault (see Section 2.5).                                                                                                                               |

| Disk Cartridge Access Door Latch  | The Disk Cartridge Access Door is unlatch-<br>ed by lifting with the fingers on the<br>latch that is under the lip of the recess<br>in the access door. The latch will<br>not release the door catch until the<br>spindle motor has stopped rotating and<br>the interlock solenoid releases the<br>catch. The START/STOP switch must also<br>be released (OUT) before the solenoid<br>will release the catch. In the event of<br>the loss of AC power, the interlock<br>solenoid does not release the catch<br>in order to prevent damage to the<br>cartridge. |

| Status Display Option             | Detailed status of the operation of the<br>drive can be obtained for faults which<br>the controller is unable to clear. The<br>FIXED PROTECT switch may be depressed<br>twice which will attempt to clear the<br>fault and display up to sixteen status<br>codes that occurred since the last fault<br>clear command was sent (either thru the<br>interface or the same front panel switch).<br>These alphanumeric codes should be re-<br>corded and given to qualified maintenance<br>personnel for interpretation.                                           |

### 2.3.1 POWER UP FOR ON-LINE OPERATION

The following procedure is to be performed after the installation procedure has been completed including initial checkout and for normal day-to-day on-line operation.

- 1. Install disk cartridge in accordance with "Disk Cartridge Installation Procedure". Insure correct cartridge is selected (correct number of sectors, etc.)

- 2. Position START/STOP switch to START (inner) position. The front panel door will lock, READY will blink, and the spindle will start if the door is fully closed with a cartridge installed. If the spindle reaches the proper speed, the heads should load, servo adjustments will be made, and READY will rapid blink during cartridge "Protect Data Quality" tests (see Automatic Self Test section). READY should then stop blinking and remain illuminated (indicating the drive is READY for commands from the controller). Any seek, read, or write activity requested over the interface will then cause the READY Indicator to rapid blink again.

If the FAULT indicator starts blinking after a START sequence, attention should be given to the type of FAULT indicated. If FAULT blinks at a normal rate, the problem is probably drive related and attempts should be made to clear the fault using the FIXED PROT switch (see Section 2.4). READY should be active after the fault is cleared.

If the FAULT indicator rapid blinks after a START sequence, a cartridge "Protect Data Quality" fault has occurred indicating that the cartridge should be replaced after the fault is cleared (see Section  $\cdot 2.5$  for details). READY will be active after the fault is cleared.

### 2.3.2 WRITE PROTECT OPERATION

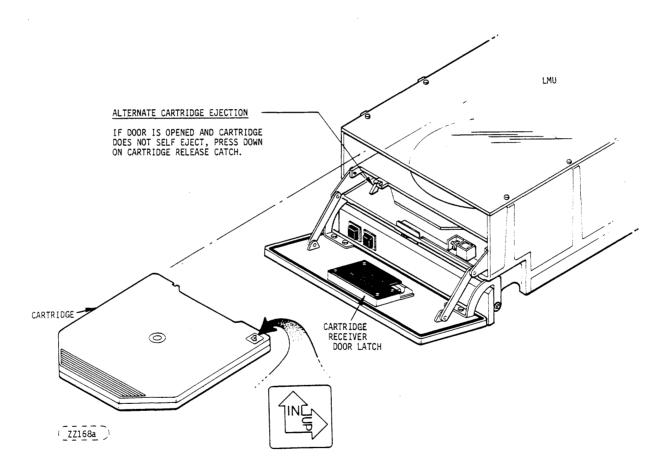

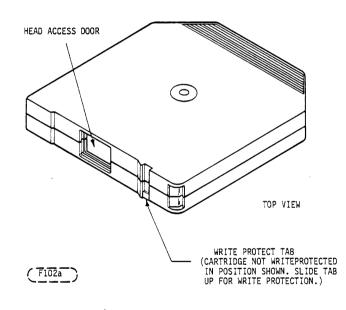

- 1. Prepare disk cartridge by sliding write protect tab to the "up" position in slot (see Figure 2-3).

- 2. Perform "Power up for on-line operation" procedure.

- 3. Place drive in "Write Protect Mode" by pushing in FIXED PROT switch. FIXED PROT indicator will illuminate.

### 2,3,3 STOP OPERATION

- 1. Depress the START/STOP switch to STOP (extended) position. The READY indicator will blink until spindle has stopped rotating and then extinguish when spindle has stopped. Note that a "Protect Data Quality" test will occur during rapid blinking.

- 2. Remove the disk cartridge (if desired) in accordance with the "Normal Disk Cartridge Removal" procedure. The LMU front door panel does not unlock until READY indicator stops blinking and then extinguishes.

## 2.3.4 POWER DOWN

Position the AC power source switch to OFF (ON/OFF switch is not on the LMU). Preferably, this is to be done only after the LMU has been stopped in accordance with the normal "Stop Operation" procedures.

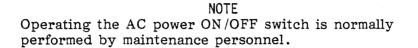

FIGURE 2-2. DISK CARTRIDGE; CARTRIDGE INSTALLATION AND REMOVAL

# FIGURE 2-3. DISK CARTRIDGE SHOWING PROTECTIVE JACKET AND WRITE PROTECT TAB

### 2.4 FAULT OPERATING INSTRUCTIONS

A blinking FIXED PROT indicator indicates a fault exists in the drive. If this condition occurs, proceed as follows:

- 1. Actuate FIXED PROT switch twice to initiate a Fault Reset and return switch to original position. If FIXED PROT has ceased blinking, normal operation can be resumed. If the indicator still blinks, proceed to step 2.

- 2. Perform the "Stop Operation" and "Power Down" procedures then power up and start the unit again. If the FIXED PROT indicator still blinks, contact qualified maintenance personnel.

NOTE See next section if FAULT is rapid blinking.

## 2.5 AUTOMATIC SELF TEST CAPABILITY

Upon initial power application, a Micro Processor within the LMU performs a self test function. This test is limited to the Micro Processor, its memory and I/O ports. A fault during this test sequence will be indicated by the Fixed Write Protect/Fault LED's failure to be reset within six seconds.

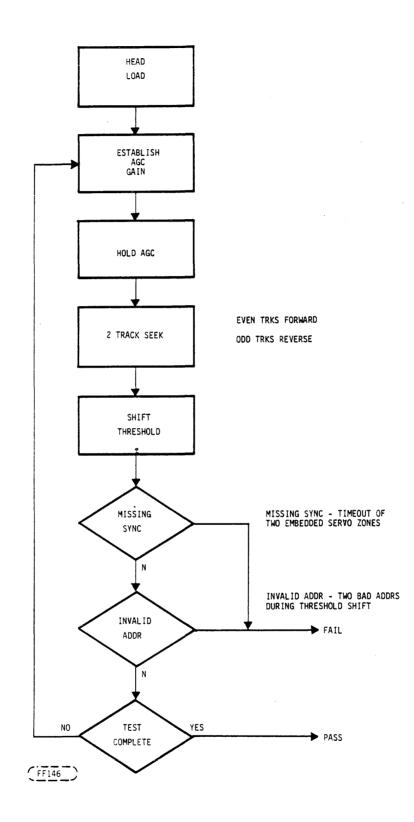

The next level of testing will occur after initial head loading. The Micro Processor will issue a series of seek commands while automatically adjusting velocity feed back to optimize access time. If the LMU should retract its heads during normal operation due to a fault condition, this test will be re-initiated via a Fault Clear command that results in a successful head load attempt.

The final phase of automatic testing is performed on the removable media and heads after each head load and prior to each head unload. Because of its industry uniqueness, based on a "Lark Technology" enhancement, it is named the Lark "PDQ" (Protect Data Quality) feature. It consists of a head/media performance test that will allow early detection of impending head/media failure before serious damage can occur. Three significant benefits are available to the user from this technology advancement: First, data is almost always recoverable, second, drive damage requiring depot level refurbishment is significantly reduced if not eliminated, and third, the undesirable effects of propagation to other components are eliminated.

When the velocity calibration test is complete, the Lark will automatically perform a sequential forward/reverse seek on each removable media surface while monitoring relative embedded servo amplitudes. If the amplitude delta exceeds a defined limit, the user is notified of a potential problem via the interface Fault line (SMD interface) or Fault bit (LDI interface) and a rapid blinking Fault indicator on the front operator panel with Ready indicator off.

If the "PDQ" fault is indicated, the user may, if desired, reinitiate the test by issuing a Fault Clear command either over the interface or by manual intervention using operator panel Fixed Write Protect/Fault Clear switch. The retest may be commanded a maximum of five times at which time the fault will be unclearable. It is recommended if the drive passes any subsequent retest to copy data from the removable media immediately and remove the failing cartridge from use. Due to the characteristics of "Lark Technology" and early detection of failure, the drive will usually remain serviceable by installing a new cartridge.

In those cases where subsequent retries are unsuccessful, the user has still another option. However, it will require the assistance of a Field Engineer. The Engineer can disable the "PDQ" protective feature which effectively lowers the read threshold circuit. This allows another opportunity to recover the data and still keep the drive serviceable.

Customers may further identify a "PDQ" fault by recording the status codes. Any series of codes that include 88, 8A, 8C, 8D indicate a cartridge with a PDQ fault which should be replaced. 8A and 88 indicate a fault (on head 0 or head 1 respectively) which may be retried. 8D indicates that no further retries are available. The two status codes following one of these codes indicate the first defective cylinder address (in a modified form).

### 2.6 REMOVABLE DISK CARTRIDGE HANDLING AND STORAGE

The following practices should be observed when handling or storing disk cartridges.

NOTE

The cartridge is not to be shipped in the disk drive.

- 1. The cartridge should be stored in its protective jacket when not in the disk receiver, see Figure 2-3.

- 2. Cartridges can be stored flat or on edge. Avoid stacking Disk Cartridges on one another.

### 2.7 REMOVABLE DISK CARTRIDGE INSTALLATION

The removable disk cartridge must be stored in the same environment as the LMU for 60 minutes immediately preceding its use. In the event that it becomes necessary to use a Cartridge which has not been allowed to stabilize at the ambient LMD environment temperature for at least one hour or; a cartridge which was exposed to temperatures below 60° F (16° C) immediately prior to the stabilization period then the following procedures must be employed:

- a. The cartridge must be visually inspected or examined to insure that condensation is not present on any part of cartridge and;

- b. The cartridge must be allowed to spin on the LMU for a period of not less than five minutes prior to attempting to read or write on that cartridge.

Install the disk cartridge using the following procedure and refer to Figure 2-2.

1. Release latch under lip of front panel door recess and pull down cartridge area access door.

### NOTE

Power must be applied to LMU, START/STOP in STOP (OUT) Position. READY indicator must be off and FIXED PROT indicator not blinking to release latch on front door panel.

- 2. Remove cartridge from protective jacket. Store jacket in such a way as to prevent dust from collecting inside the jacket.

- 3. Slide disk cartridge into receiver track, ensuring that the head opening is towards rear of drive and top surface\* of cartridge is up.

- 4. Push disk cartridge in until it stops.

- 5. Close disk cartridge access door and press the door closed until it is latched. The disk cartridge seats into place on the spindle automatically as the access door is closed.

- 6. Operate the START/STOP switch to apply power to the spindle motor.

- 7. If the spindle motor will not rotate, the disk cartridge access door may not be completely closed or the disk cartridge may not be properly seated on the spindle chuck or the cartridge receiver/base may not be positioned properly on the lower chassis. If this occurs remove the cartridge and reinstall as outlined in the previous steps.

- 2.8 DISK CARTRIDGE REMOVAL

- 2.8.1 NORMAL REMOVAL

Refer to Figure 2-2 for the following procedure.

- 1. Operate START/STOP switch to STOP (out).

- 2. Pull down the Cartridge access door after the READY indicator ceases blinking and extinguishes entirely. When the access door is completely open the disk cartridge will partially eject out of the receiver.

- 3. Pull the cartridge out of the receiver.

- 4. Close the access door if another disk cartridge is not to be installed at this time. However, a disk cartridge should be in the drive at all times to prevent unnecessary entry of atmospheric contaminants into the sealed area of the drive. The drive will not operate without the disk cartridge installed.

NOTE

It is important that the door on the LMU remain closed when the drive is not in use. Good housekeeping accentuates high reliability.

\*Top is marked "TOP".

77711046-A

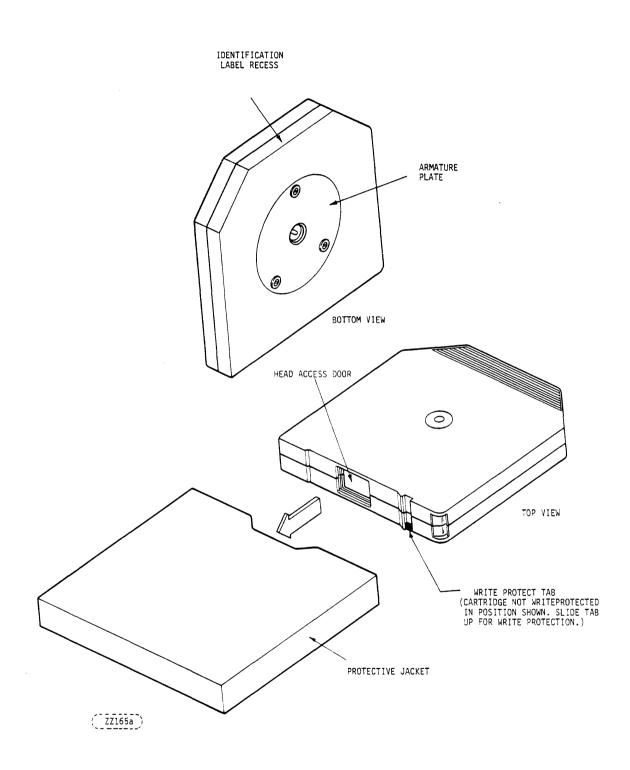

## 2.8.2 POWER FAILURE OR EMERGENCY STOP REMOVAL

In case of an emergency need to remove the cartridge, perform the following procedure. (Refer to Figure 2-4):

### NOTE

The procedures below should be performed only by qualified maintenance personnel.

- 1. If possible, check to see if the heads are unloaded. A small area of clear plastic over the carriage area is provided for that purpose.

- 2. If the heads are loaded (they are still flying over the disks), they must be carefully retracted manually before stopping the spinning of the disks (if they are still spinning). To manually retract the heads, carefully lift the front of the unit until the heads slide back into unloaded position. When the carriage is fully retracted, screw the lock pin into place to prevent the heads from rolling out of the fully unloaded position. There is a carriage locking solenoid, but it does not lock the carriage back until AC power is removed. However, the cartridge door cannot be opened in the normal manner if power is removed from the LMU.

- 3. Stop the unit and wait approximately 3 minutes for the disk cartridge to stop spinning.

### CAUTION

Verify spindle rotation does not exist prior to defeating the door interlock. Refer to Disk Cartridge Removal Procedure. The cartridge removal procedure must be performed only by qualified maintenance personnel and should be only for drive failure. The cartridge access door should always be closed after the cartridge is replaced with a dummy cartridge.

4. Open the disk cartridge access door. This automatically removes disk cartridge from spindle chuck. Door will not open if a fault exists. Power must be ON and START/STOP switch out to retract door latch solenoid. Pull disk cartridge out and store in protective jacket. Close door if another disk cartridge is not to be installed. However, it is best to install a scratch disk cartridge having no valuable data.

In an emergency (emergency only) if the disk cartridge access door will not open proceed as follows:

1. Make sure the spindle motor has completely stopped. Either observe the motor or wait a full 3 minutes after initiating a stop. Make sure heads are retracted.

### FIGURE 2-4. EMERGENCY/DRIVE FAILURE CARTRIDGE DOOR OPENING PROCEDURE

2. See Figure 2-4. Insert a plastic credit card or similar object into the space between the access door and the lower front panel. Push the small release tab behind the panel (about 3 inches from the right edge) toward the right with the card and hold while pushing up with the fingers on the door latch release. Pull the door open and remove cartridge. Close front door.

## 2.9 MAINTENANCE FEATURES

The FAULT indicator blinks when a fault is detected in the drive.

The AC ON/OFF power switch (not on the LMU) when operated applies AC power to the LMU. The LMU fan motor energizes and the front door panel will unlock. This control is not available to the operator.

The LMU requires no electrical/mechanical adjustments or preventive maintenance procedures.

## INSTALLATION AND CHECKOUT

## 3.1 INTRODUCTION

This section provides the information and procedures necessary to install the LMU.

### 3.2 UNPACKING

During the unpacking, exercise take care so that tools being used do not cause damage to the unit. As the unit is unpacked, inspect it for possible shipping damage. All claims for this type of damage should be filed promptly with the transporter involved.

Retain the shipping container and packing material if a claim is to be filed for damage, unit is to be reshipped, or shipped to service center.

Unpack the unit as follows:

- a. Remove the tape from the shipping container.

- b. Open the container and remove the LMU assemblies and cables.

### CAUTION

Do not release the carriage lock until the LMU is installed in its designated location. Damage may occur as a result of accidental loading of the heads. The carriage is to be locked in the retracted position any time the LMU is to be moved.

- c. Do not connect the input power cable until all other installation steps have been completed and the LMU is ready for initial checkout.

- d. Remove the isolation mounts from the accessory pack in the shipping container. Shown in Figure 3-1 is the location of isolation mounts for a horizontally mounted LMU. Figure 3-2 shows the location of isolation mounts for the vertically mounted LMU. Screw the four isolation mounts into the four 8-32 tapped holes in the base deck.

#### CAUTION

In handling the LMU care should be taken to not damage the exposed Base PWA in the bottom of the LMU.

## 3.3 SPACE ALLOCATION

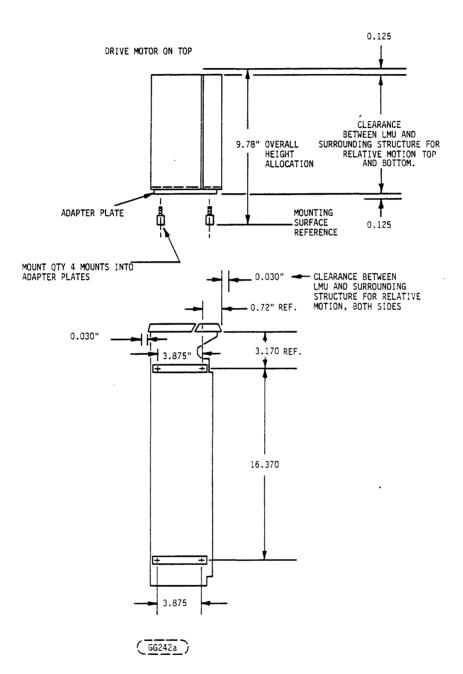

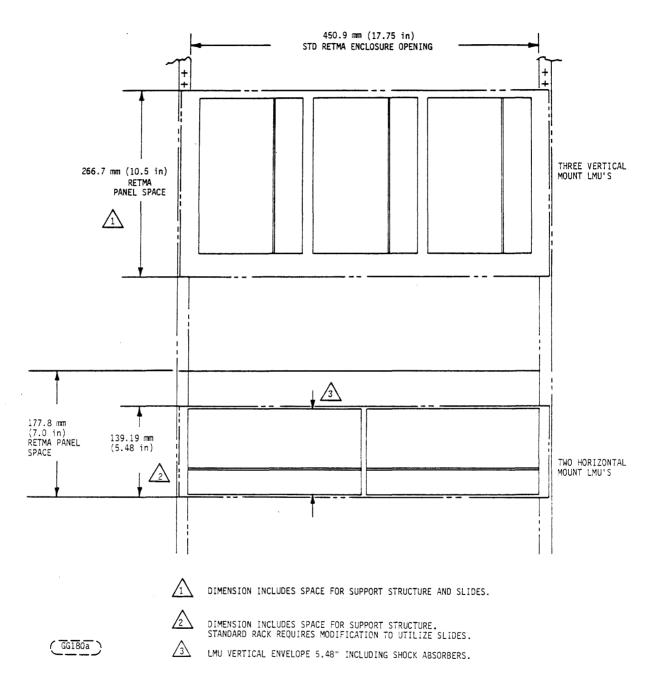

Figure 1-2 shows the LMU overall dimensions for determining space allocation. Detailed mounting hole data is provided in Figures 3-1 and 3-2. Example configurations are shown in Figure 3-3.

## 3.4 COOLING REQUIREMENTS

## 3.4.1 LMU COOLING

A fan draws air in at the rear of the LMU that is used to cool the electronics and PWA's. The air is exhausted on each side of the unit near the front. A minimum of 0.75 inch (19.05 mm) clearance must be provided at the air exits from both vertical and horizontal mountings. The maximum ambient air temperature at the blower inlet is not to exceed 104° F (40° C). The maximum ambient air temperature when measured 1/4 inch (8.4 mm) from the LMU surface shall not exceed 120° F (49° C) excluding hot spots. Positive pressure near the exhaust holes should not exceed 0.06 inches of water (14.9 Pascal).

(<u>GG039a</u>)

# FIGURE 3-1. LARK MODULE UNIT MOUNTING HOLE DATA

FIGURE 3-2. LMU VERTICAL MOUNTING DIMENSIONS

FIGURE 3-3. EXAMPLE LMU CONFIGURATIONS

## 3.5 POWER REQUIREMENTS

## 3.5.1 PRIMARY POWER REQUIREMENTS

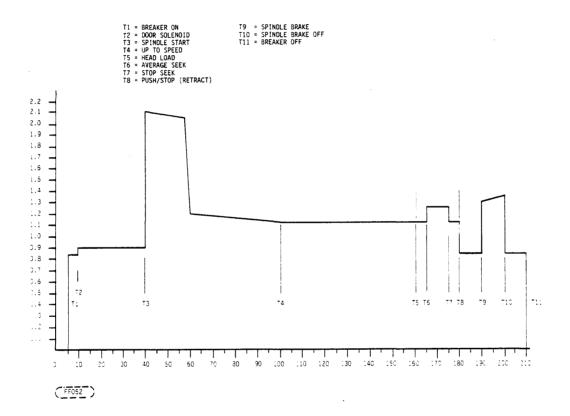

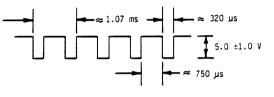

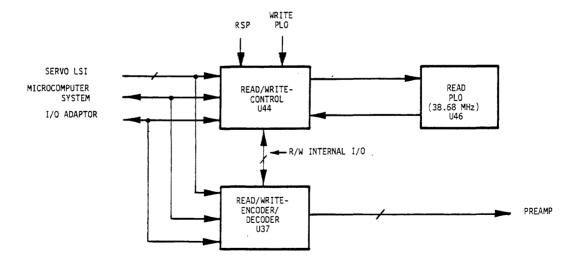

The primary voltage and current requirements are shown in Tables 3-1 and 3-2. The operational line currents are described in Figure 3-4.

FIGURE 3-4. OPERATIONAL NOMINAL LINE CURRENTS TO POWER SUPPLY VS TIME (120 V INPUT)(WITH CDC POWER SUPPLY)

| TABLE 3-1. R | PRIMARY | VOLTAGE | REQUIREMENTS |

|--------------|---------|---------|--------------|

|--------------|---------|---------|--------------|

| VOLTAGE (VAC)                                                                                                         | TOLERANCE (VAC)                             | FREQUENCY (Hz)       | TOLERANCE (Hz)                                       |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------|------------------------------------------------------|--|--|--|--|--|--|

| 120<br>220*<br>230*<br>240*                                                                                           | +8, -16<br>+15, -29<br>+16, -32<br>+16, -32 | 60<br>50<br>50<br>50 | +0.6, -1.0<br>+0.5, -1.0<br>+0.5, -1.0<br>+0.5, -1.0 |  |  |  |  |  |  |

| *Voltage can be anything in 220-240 volt range, though this table only shows tolerances at three points in the range. |                                             |                      |                                                      |  |  |  |  |  |  |

77711047-A

|                                                                                                                                                                                                        | CURRENTS AND (WATTAGE)<br>ON TRACK SEEKING STARTING                                                                                      |            |                     |                    |                 |               |                             | TNC     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|--------------------|-----------------|---------------|-----------------------------|---------|--|--|

| DRIVE INPUTS                                                                                                                                                                                           | NOMINAL                                                                                                                                  |            | MAXIMUM             | NOMINAL            | MAXIMUM         |               | STARTING<br>NOMINAL MAXIMUM |         |  |  |

| NOM                                                                                                                                                                                                    |                                                                                                                                          |            | MAXIMUM             |                    | MAXIMU          | 1             |                             | MAXIMUM |  |  |

| 120 VAC                                                                                                                                                                                                | 0.5 A<br>(60 W)                                                                                                                          |            |                     | 0.5 A<br>(60 W)    |                 |               | 0.85 A<br>(102 W)           |         |  |  |

| 220-240 VAC                                                                                                                                                                                            | 0.35 A<br>(60 W)                                                                                                                         |            |                     | 0.35 A<br>(60 W)   |                 |               | 0.8 A<br>(190 W)            |         |  |  |

| +16.5 V                                                                                                                                                                                                | 0.4 A<br>(6.6 W)                                                                                                                         |            |                     | 0.72 A<br>(11.9 W) |                 |               | -                           | -       |  |  |

| -16.5 V                                                                                                                                                                                                | 0.35 A<br>(5.8 W)                                                                                                                        |            |                     | 0.67 A<br>(11.1 W) |                 |               | -                           | -       |  |  |

| +5 * V                                                                                                                                                                                                 | 1.4                                                                                                                                      |            | 1.8 A<br>(9.0 W)    | 1.4 A<br>(7.0 W)   | 1.8 A<br>(9.0 W |               |                             | -       |  |  |

| -5 V                                                                                                                                                                                                   | 2.88                                                                                                                                     |            | 3.25 A<br>(16.25 W) | 2.88 A<br>(14.4 W) | 3.25<br>(16.25  |               | -                           | -       |  |  |

| TOTAL WATTAGE                                                                                                                                                                                          | (93.                                                                                                                                     | .8W)       |                     | (104.4 W)          |                 |               | -                           | -       |  |  |

|                                                                                                                                                                                                        |                                                                                                                                          |            |                     |                    |                 | CURRENT DRAIN |                             |         |  |  |

| VOLTAGE (V dc)                                                                                                                                                                                         |                                                                                                                                          | REGULATION |                     | MAX RIPPLE P/P     |                 | MIN           |                             | МАХ     |  |  |

| +5*                                                                                                                                                                                                    |                                                                                                                                          |            | ±2%                 | 50 mV              |                 | 0.05 A        |                             | 1.8 A   |  |  |

| -5.2                                                                                                                                                                                                   |                                                                                                                                          | ±2%        |                     | 50 mV              |                 | 0.07 A        |                             | 3.25 A  |  |  |

| +16.5                                                                                                                                                                                                  |                                                                                                                                          |            | ±10%                | 500 mV             |                 |               | 0.1 A                       | 1.3 A   |  |  |

| -16.5                                                                                                                                                                                                  |                                                                                                                                          |            | ±10%                | 500 mV             |                 | 0.04 A        |                             | 1.3 A   |  |  |

| NOTE 1: PEAK CURRENT FOR THE ±16.5 VOLT SUPPLIES MAY REACH 3.0 AMPERES<br>FOR 24 MILLISECONDS DURATION FROM EITHER SUPPLY (NOT BOTH) WITH<br>A 80 MILLISECOND MINIMUM INTERVAL BETWEEN CURRENT PULSES. |                                                                                                                                          |            |                     |                    |                 |               |                             |         |  |  |

| NOTE 2: THE $\pm 5$ VOLTS SHALL SHARE A DC COMMON. THE $\pm 16.5$ VOLTS SHALL SHARE A SEPARATE DC COMMON.                                                                                              |                                                                                                                                          |            |                     |                    |                 |               |                             |         |  |  |

| NOTE 3: IN<br>PR                                                                                                                                                                                       | TE 3: IN REGARD TO DC POWER SEQUENCING, THE $\pm 5$ V DC SUPPLY MUST NOT PRECEDE THE REMAINING DC VOLTAGES IN EXCESS OF 50 MILLISECONDS. |            |                     |                    |                 |               |                             |         |  |  |

| * Includes optional status display requirement of 300 mA nominal and excludes PIO adapter board power requirements.                                                                                    |                                                                                                                                          |            |                     |                    |                 |               |                             |         |  |  |

TABLE 3-2. CURRENT/POWER REQUIREMENTS

.

### 3.6 CABLING AND MATING CONNECTORS

## 3.6.1 GENERAL

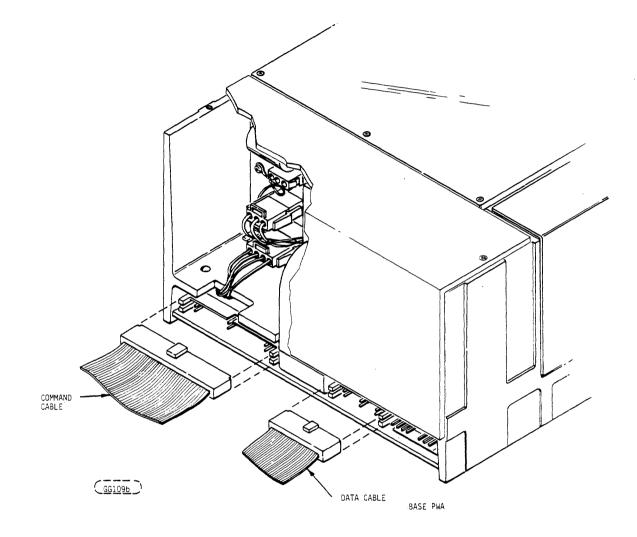

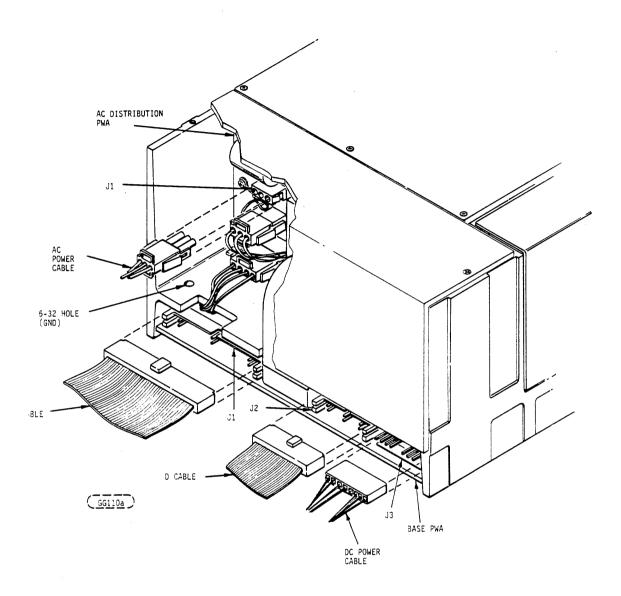

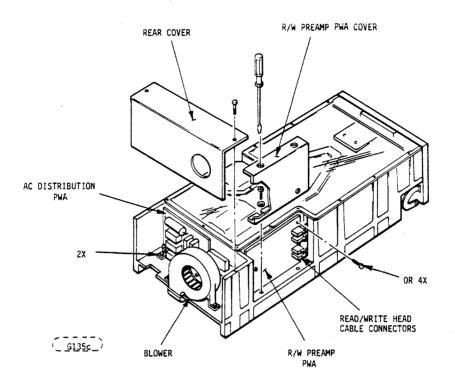

The connectors for interfacing LMU command/data signals to the Host Adapter and the DC power are located on the Base PWA at the rear of the unit. (See Figure 3-5). The connector for the AC power is located on the AC Distribution PWA (See Figure 3-6).

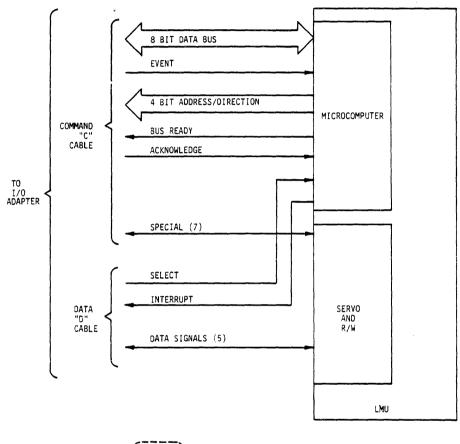

## 3.6.2 COMMAND/DATA INTERFACE CABLING AND CONNECTORS

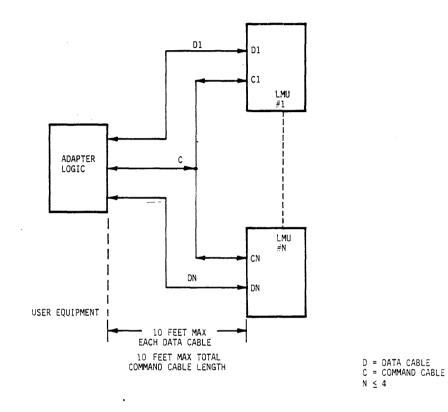

The Command/Data physical interface consists of a 40-pin command ("C") cable and a 26-pin data ("D") cable. The command cable can be daisy-chained. However, since there is only one command I/O connector provided on the LMU Base PWA, the user must provide the daisy-chain facilities. A maximum of four LMU's can be daisy-chained. The data cable must be radially connected. The maximum cummulative daisy-chained cable length is 10 feet. The maximum radial cable length is 10 feet. Refer to Figure 3-7.

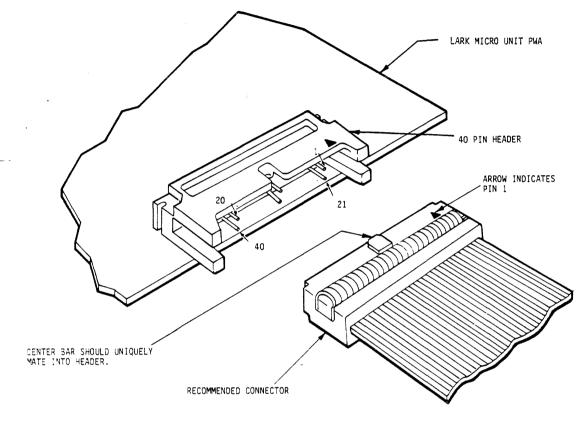

Figure 3-8 illustrates the type of connector used on the Base PWA and the cable connector required to mate with it. Section 3-10 lists the recommended components that can be used to interconnect the drive(s) to the user adapter. The connector pin and signal name assignments are shown in Figures 3-9 and 3-10. Timing and electronic information about the interface command/data signals is given in more detail in Volume II of the LMU Manual (P/N 77711050), Section 5.6.

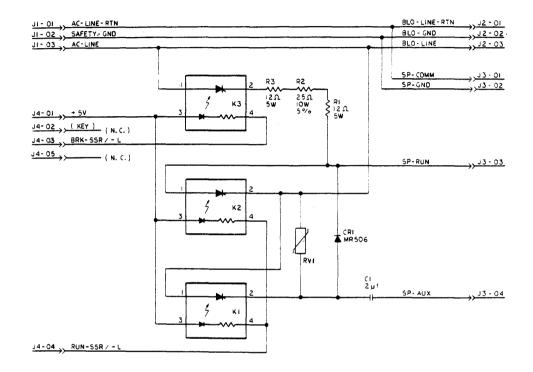

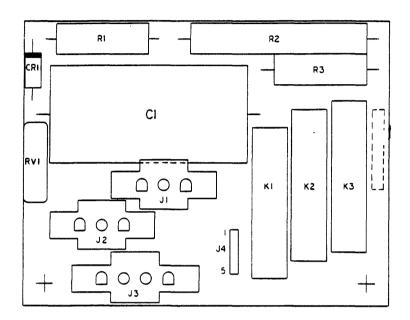

# 3.6.3 AC AND DC POWER CABLING AND CONNECTORS

The AC power input connector is mounted on the AC Distribution PWA. It is a three circuit position Mate 'N' Lock Type female housing with male contacts. The DC power connector is an 8 circuit position male header mounted on the Base PWA. Locations of the above connectors are shown in Figure 3-6. Recommended mating connectors for the AC and DC power input cables are given in Section 3-10 "ACCESSORIES".

## 3.6.4 I/O AND POWER CABLE ROUTING

For sliding rack mounted drives, it is recommended that a cable retract mechanism be incorporated in the rack design. Retract mechanisms can be purchased from a number of available manufacturers.

### 3.7 GROUNDING

In order to ensure reliable interface operation and prevent damage to drivers or receivers, a DC ground should exist between the drive and the adapter. This ground should be carefully incorporated into the overall grounding system to prevent circulating ground currents. The ground connection, while necessary, is not within the scope of this manual. Figure 3-6 shows the location of the LMU system ground tie point.

FIGURE 3-5. COMMAND/DATA CABLE CONNECTIONS

FIGURE 3-6. AC AND DC CABLING

1

\_

FIGURE 3-7. LARK MICRO INTERFACE CABLING

DATA CABLE IS SIMILAR EXCEPT 26 PIN.

(<u>G043b</u>)

FIGURE 3-8. PICTORIAL REPRESENTATION OF COMMAND CABLE AND CONNECTOR

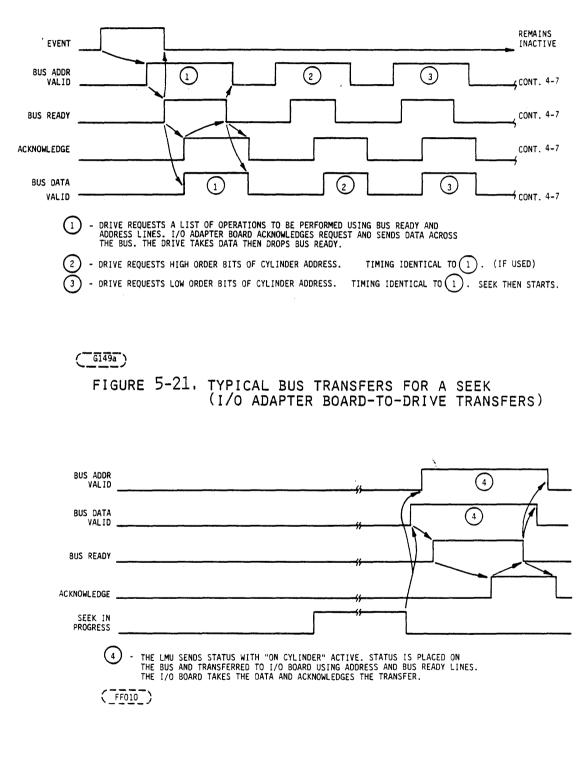

| $\Lambda$                                                                                                        | EVENT                                                   |               | 1             |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------|---------------|

|                                                                                                                  | GROUND                                                  |               | $\frac{3}{3}$ |

| A                                                                                                                | BUS BIT 0                                               |               | 2             |

| A                                                                                                                | BUS BIT 1                                               | $\rightarrow$ | 22            |

| Ā                                                                                                                | BUS BIT 2                                               | $\rightarrow$ | 3             |

| A                                                                                                                | BUS BIT 3                                               |               | 23            |

| $\overline{\mathbb{A}}$                                                                                          | BUS BIT 4                                               |               | 4             |

| Ā                                                                                                                | BUS BIT 5                                               |               | 4             |

| $\overline{\mathbb{A}}$                                                                                          | BUS BIT 6                                               |               | 5             |

| $\overline{\mathbb{A}}$                                                                                          | BUS BIT 7                                               | 2             | 25            |

|                                                                                                                  | GROUND                                                  |               | 6             |

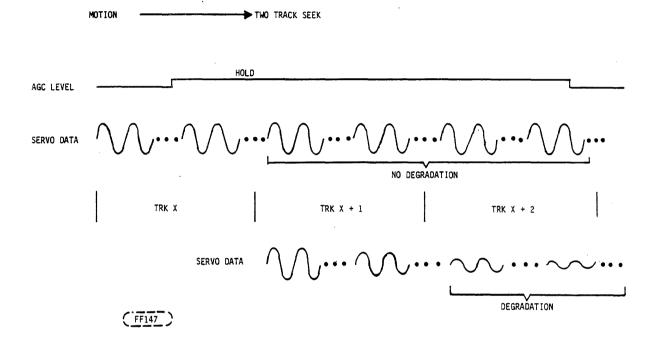

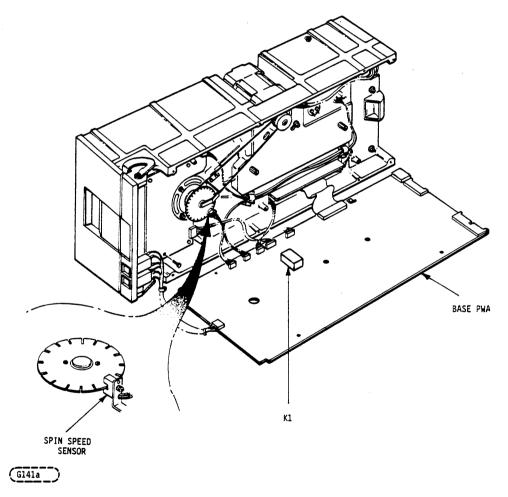

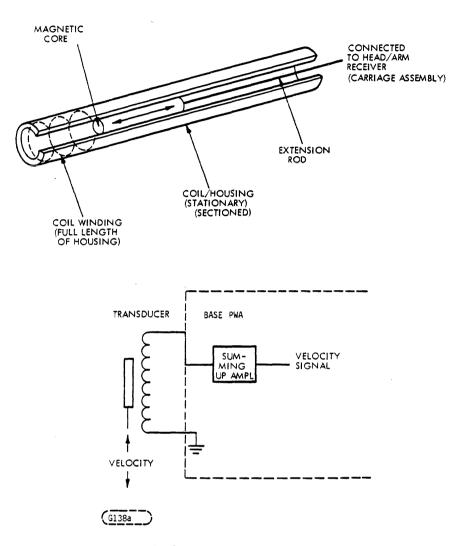

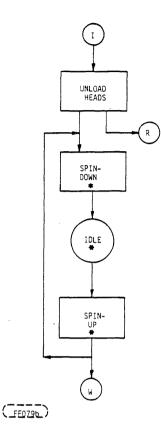

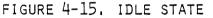

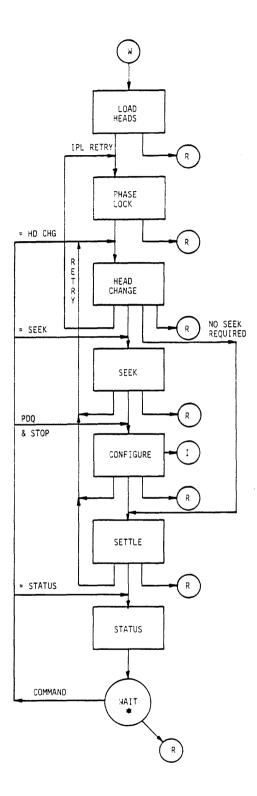

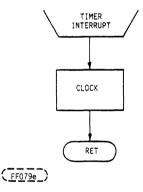

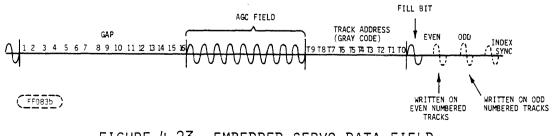

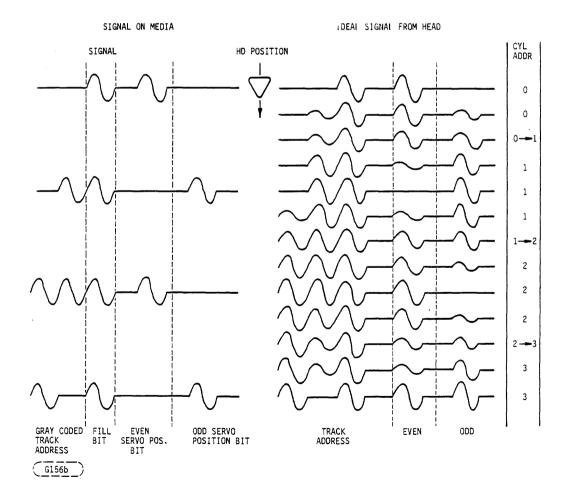

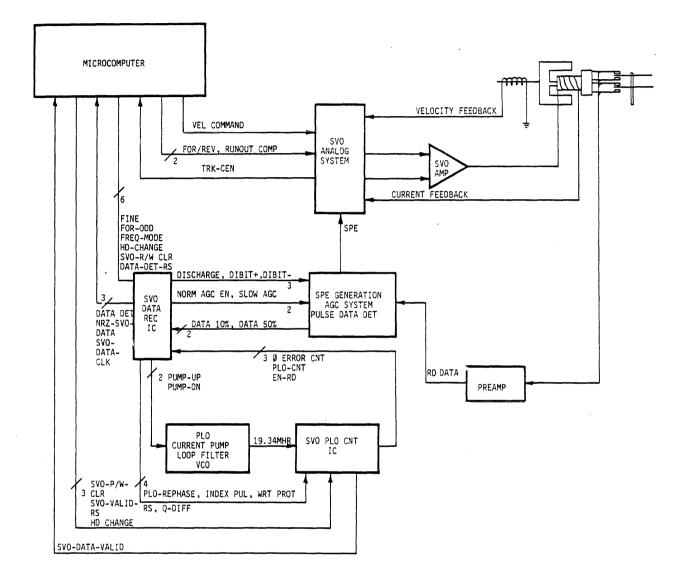

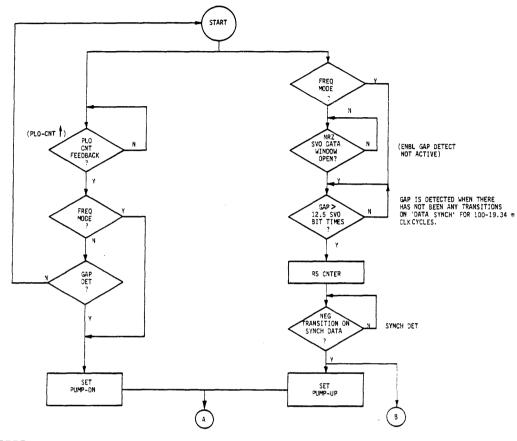

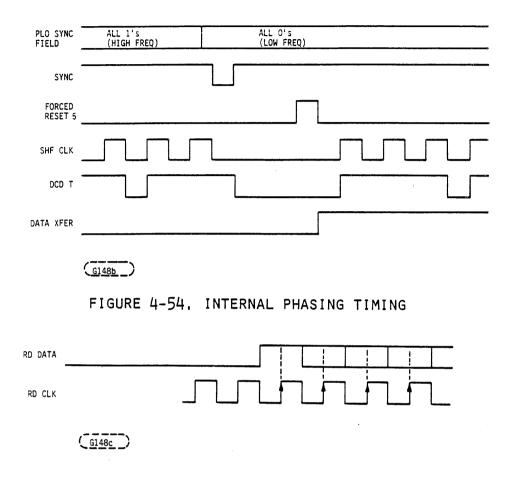

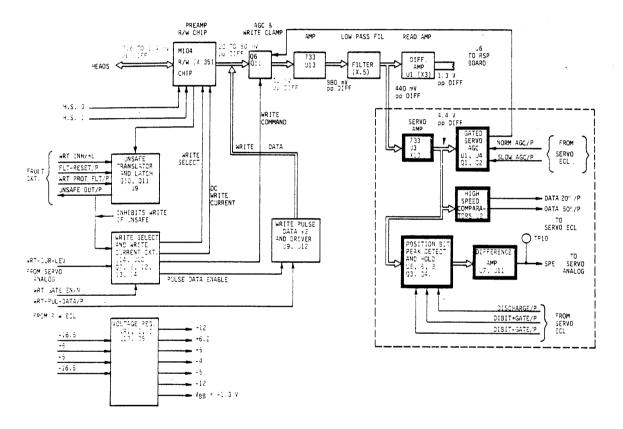

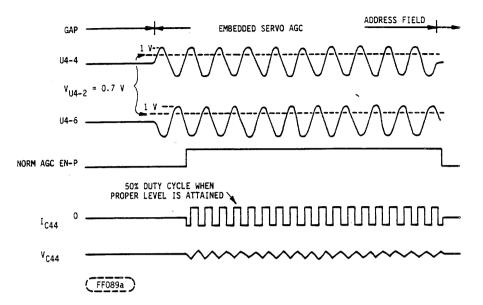

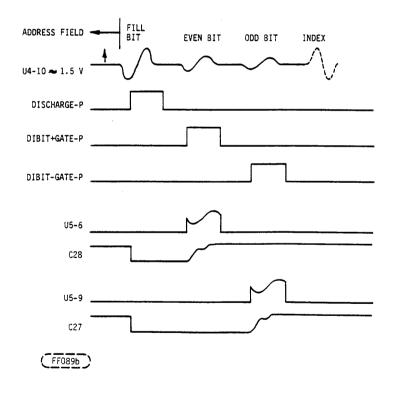

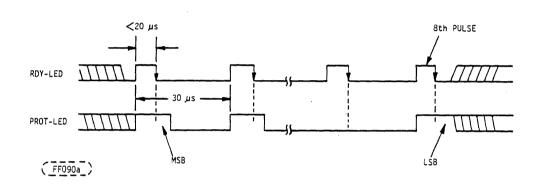

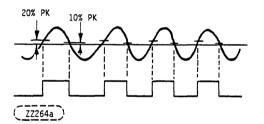

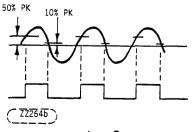

| $\triangle$                                                                                                      | RECEIVE FROM ADAPTER                                    |               | 6             |