# CODATA SYSTEMS CORPORATION Winchester Disk Controller Hardware Reference Manual

# WINCHESTER DISK CONTROLLER

# DESCRIPTION, OPERATION AND MAINTENANCE

|    | CONTENTS                                |     |     |    |      |   | PAGE       |

|----|-----------------------------------------|-----|-----|----|------|---|------------|

| 1. | GENERAL                                 |     |     |    |      |   | 3          |

|    | Features                                | •   | •   | •  | •    | • | 3          |

| 2. | PHYSICAL DESCRIPTION .                  | •   |     |    | •    |   | 5          |

|    | Options                                 | •   | •   | •  | •    | • | 5          |

|    | Adjustments                             | •   | •   | •  | •    | • | 5          |

| 3. | FUNCTIONAL DESCRIPTION                  | J   | •   |    | •    | • | 7          |

|    | Disk Storage                            |     |     |    |      | • | 7          |

|    | Overview                                | •   | •   | •  | •    | • | 7          |

|    | Memory                                  | •   | •   | •  | •    | • | 9          |

|    | 796 Bus Interface                       | •   | •   | •  | •    | • | 11         |

|    | Control and Status                      | •   | •   | •  | •    | • | 15         |

|    | Read and Write Logic                    | •   | •   | •  | •    | • | 19         |

|    | Phase-Locked Data Recovery              | •   | •   | •  | •    | • | 21         |

| 4. | SPECIFICATIONS                          |     | •   | •  | •    | • | 23         |

| 5. | OPERATION AND PROGRAM                   | лмн | NG  |    |      |   | 25         |

| •. | Options                                 |     |     |    | •    | • | 25         |

|    | Controller Programming –                | •   | •   | •  | •    | • | 20         |

|    | General                                 |     |     |    |      |   | 25         |

|    | I/O Ports – CPB Pointer                 |     |     |    |      | • | 25         |

|    | Command Parameter Blo                   |     |     |    |      | • | 28         |

|    | Status Block                            |     |     |    |      | • | 29         |

|    | Data Block                              |     | •   |    |      | • | 29         |

|    | Interrupts                              |     |     | •  |      | • | 30         |

|    | Power On Sequence .                     |     |     |    |      | • | 30         |

|    |                                         |     |     |    |      | • |            |

|    | Configuration Option Jun                |     |     |    |      | • | 32         |

|    | I/O Address                             |     |     |    |      | • | 32         |

|    | Interrupt Priority Level                |     |     |    |      | • | 33         |

|    | 796 Bus INIT* Master/SI                 |     |     |    |      | • | 33         |

|    | 796 Bus Priority In .                   |     |     |    |      |   | 33         |

|    | Drive Address Assignmen                 | π   | •   | •  | •    | • | 34         |

| 6. | MAINTENANCE                             | •   | •   | •  | •    | • |            |

|    | Diagnostics                             | •   | •   | •  | •    | • | 35         |

|    | Diagnostic Commands                     | •   | •   | •  | •    | • | 35         |

|    | – Command Parameter E                   |     | <   | •  | •    | • | 35         |

|    | <ul> <li>Command Description</li> </ul> | S   | •   | •  | •    | • | <b>3</b> 5 |

|    | Warranty Service                        | •   | •   | •  | •    | • | 36         |

|    | Returning Material for Repairs          | •   | •   | •  | •    | • | 36         |

| 7. | REFERENCE                               |     | •   |    |      |   | 37         |

|    | bigram and Replace، لا Logic            |     | Par | ts | List | t | 37         |

|    | IEEE 796 Microcomputer B                | lus |     |    |      |   | 37         |

|    | Technical Manual Revisions              | •   | •   |    | •    |   | 37         |

| ILLUSTRATIONS                                          | PAGE |

|--------------------------------------------------------|------|

| Figure 2-1 – Winchester Disk Controller –              |      |

| 92-1011-xx                                             | 4    |

| Figure 3-1 – Winchester Disk Controller Block          |      |

| Diagram                                                | 6    |

| Table 3-1 – Fast IV Select Decode Signals              | 8    |

| Figure 3-2 – Memory Block Diagram                      | 10   |

| Figure 3-3 – 796 Bus Interface Block Diagram           | 12   |

| Table 3-2 – Winchester Disk Controller Active          |      |

| 796 Bus Signals                                        | 14   |

| Figure 3-4 – Control and Status Block Diagram .        | 16   |

| Figure 3-5 — Read and Write Logic Block                |      |

| Diagram                                                | 18   |

| Figure 3-6 — Phase-Locked Data Recovery Block          |      |

| Diagram                                                | 20   |

| Table 4-1 – Winchester Disk Controller                 |      |

| 92-1011-xx Specifications                              | 23   |

| Table 5-1 – Winchester Disk Controller Options –       |      |

| P/N 92-1011-xx                                         | 26   |

| Table 5-2 – I/O Port Address Assignments               | 27   |

| Table 5-3 – Command Parameter Address Block            |      |

| Assignments                                            | 28   |

| Table 5-4 – Command Byte Code    .                     | 29   |

| Table 5-5 – Status Block Address Assignments         . | 29   |

| Table 5-6 - Status Byte Code    .    .    .            | 30   |

| Table 5-7 – 8-Bit Address Option Jumpers               | 31   |

| Table 5-8 – 16-Bit Address Option Jumpers –            |      |

| Digits w, y                                            | 32   |

| Table 5-9 – 16-Bit Address Option Jumpers –            |      |

| Digit x                                                | 33   |

| Table 5-10 — Interrupt Priority Level Option           |      |

| Jumper                                                 | 34   |

| Table 6-1 – Command Parameter Block Address            |      |

| Assignments                                            | 35   |

| Table 6-2 – Command Byte Code                          | 37   |

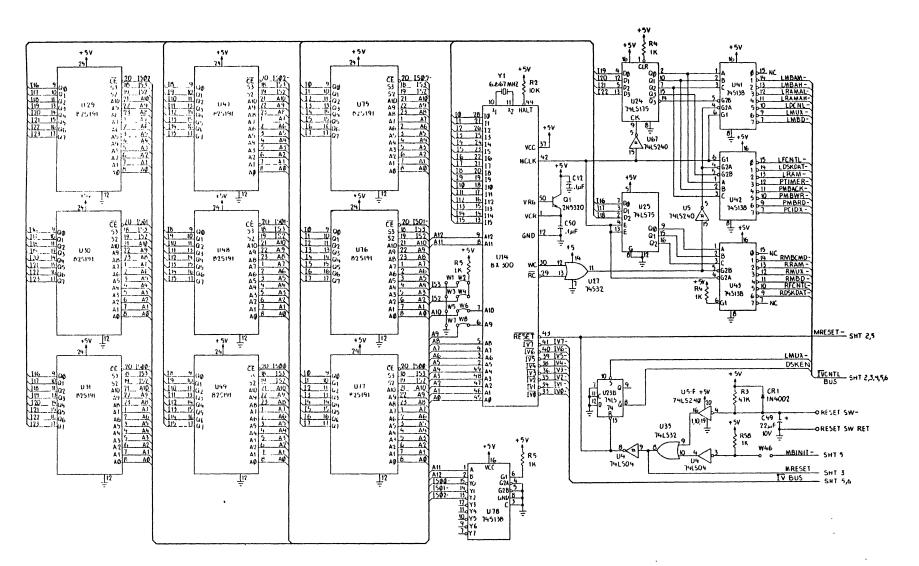

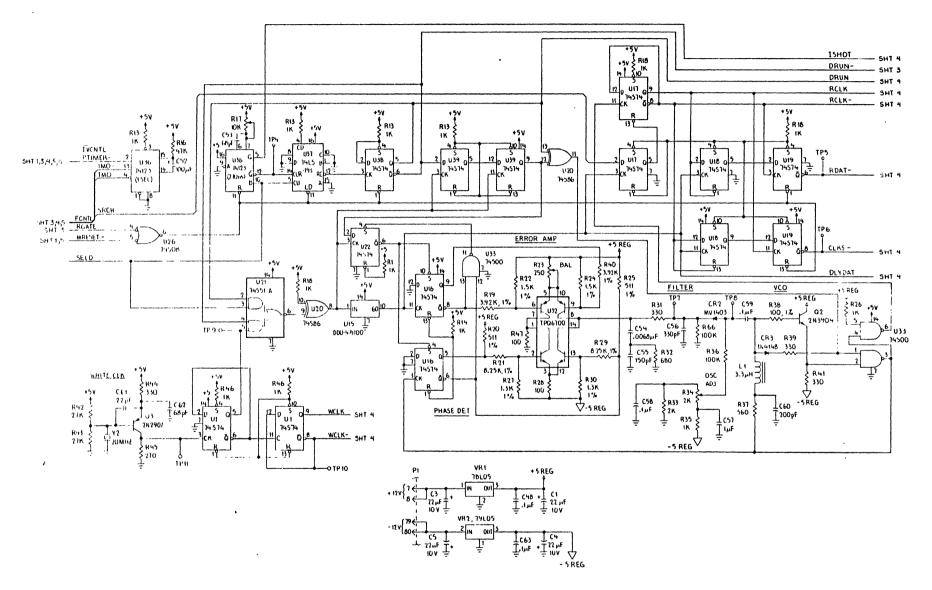

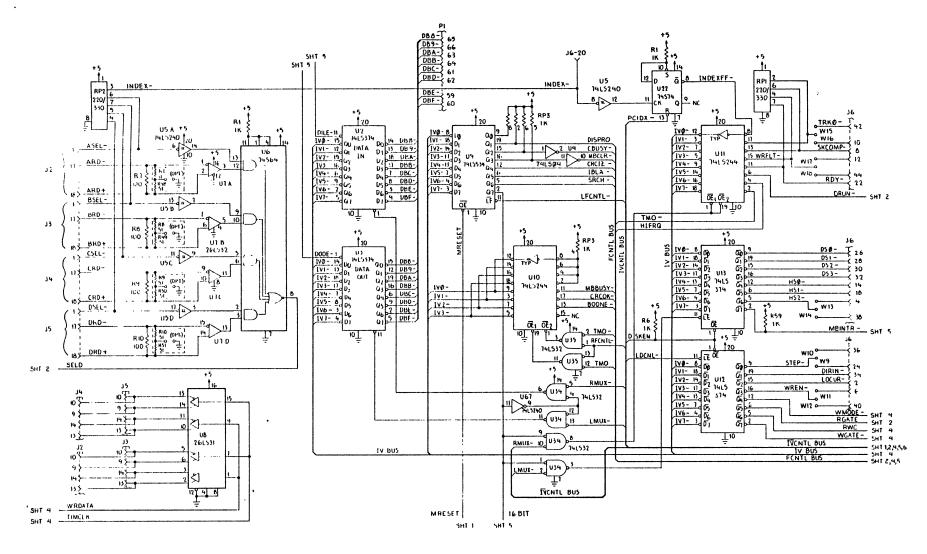

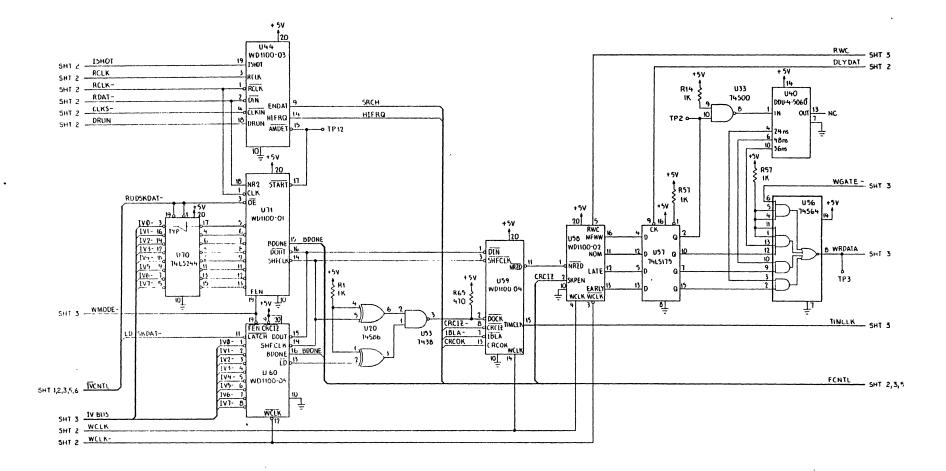

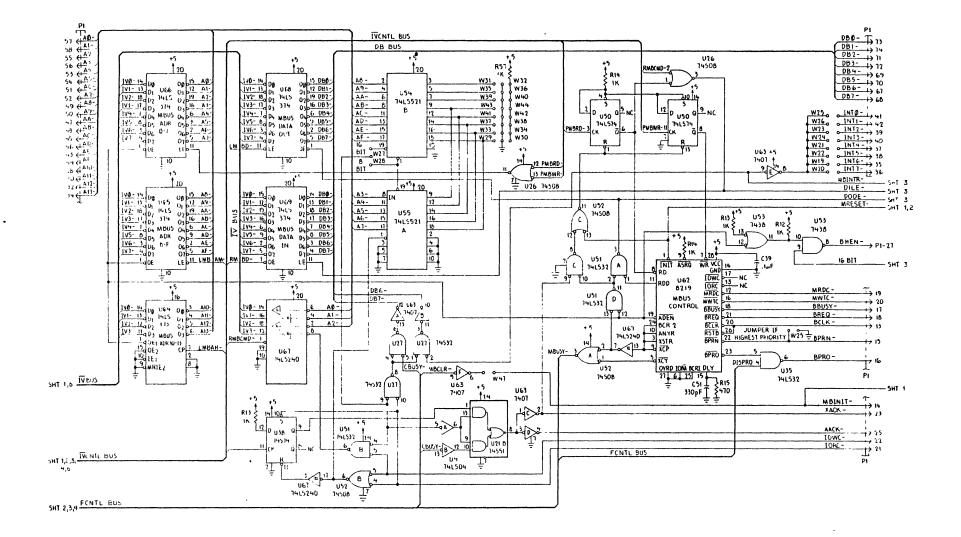

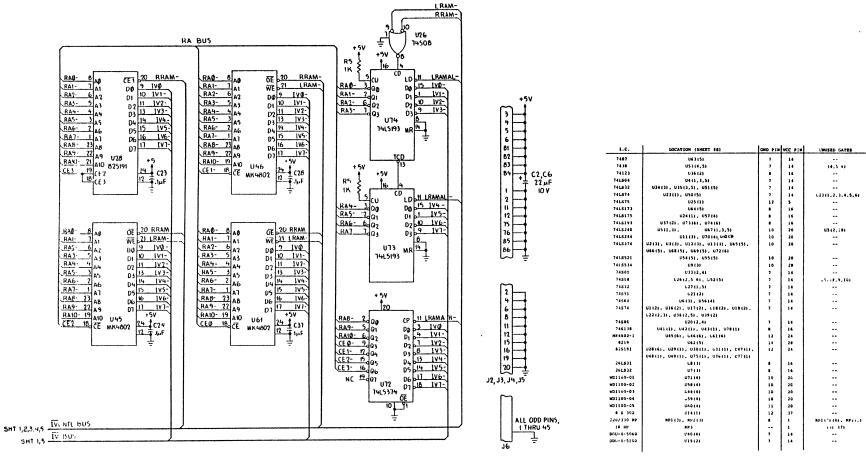

| Figure 7-1 — Winchester Disk Controller Logic          |      |

| Diagram                                                | 38   |

| Table 7-1 – Winchester Disk Controller –               |      |

| Replaceable Parts List                                 | 44   |

| Table 7-2 – Pin Assignments of Bus Signals on Bus      |      |

| Board Connector (P1)                                   | 50   |

| Table 7-3 — Pin Assignments of Bus Signals on Bus      |      |

| Board Connector (P2)                                   | 51   |

|                                                        |      |

.

1. GENERAL

1.01 This manual provides a physical and functional description and operating theory for effective field maintenance of the Codata Systems Winchester Disk Controller (WDC) 92-1011-xx.

1.02 This Controller is supplied as a single printed circuit assembly (PCA) for use as a system component in Codata Systems Corp.:

- (1) CTS-Series Mainframes,

- (2) CTW-Series Mainframes.

# Features

1.03 The Controller utilizes a microprocessor  $(\mu P)$  in an intelligent controller design providing for mass storage on either 8.0-inch or 5.25-inch Winchester disks in an easy to use command/status structure. Blocking/deblocking, bad sector detection/reassignment and retry on error are performed by the WDC firmware minimizing system software complexity. WDC features include:

- IEEE 796 microcomputer bus compatible.

- The entire WDC is on a single PCA.

- Controls up to four Winchester Disk Drives.

- Supports full 20-bit 796 Bus address for command blocks and data transfers.

- Retry on error automatically performed by the WDC firmware.

- Data transfers to Mainframe RAM through direct memory access (DMA) 8-bit or 16-bit word transfers program selectable.

- Bad sector detection/alternate sector reassignment performed by the Controller firmware.

- Blocking/deblocking from logical sectors to blocks of 4096 bytes performed in the WDC firmware providing ease of implementation with operating systems such as CP/M(TM), MP/M(TM), UNIX(TM) and MERLIN(TM) while maintaining fast system access times.

- Convenient logical sector size of 128 bytes.

- Contiguous sector transfers up to 4096 bytes long may be performed which eliminates the need to interleave sectors to obtain high system through put.

- Byte count as high as 64k, 16-bit, is allowed.

- MFM data separation and write precompensation is provided by the WDC.

- Device address and interrupt level set with option jumpers.

# NOTE

The following reference notations apply in this technical manual.

- (1) A \* suffix to a signal name indicates logical NOT and active low.

- (2) In and out references are in respect to CPU or bus master.

- (3) Ik byte equals 1,024 bytes, i.e., 64k bytes equals 65,536 bytes.

- (4) Codata Systems Corp. part numbers are made up of eight digits, e.g., the part number of this manual is 05-0003-01.

- (5) A suffix -xx to a part number indicates the part or assembly may have more than one configuration in production, i.e., Winchester Disk Controller is 92-1011-xx.

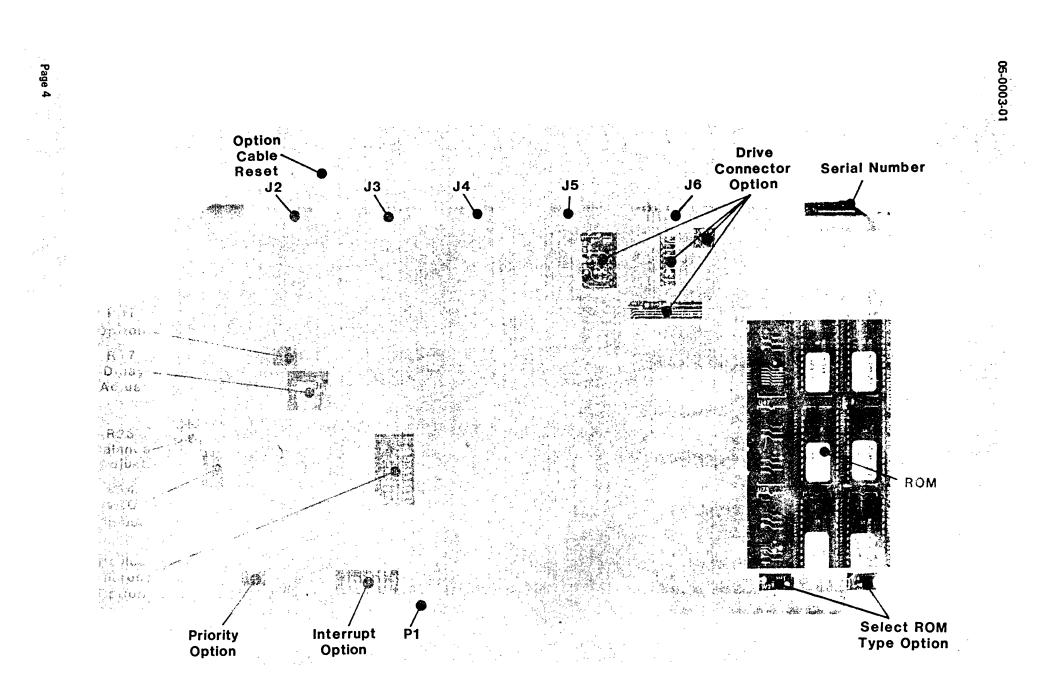

# Figure 2-1 – Winchester Disk Controller – 92-1011-xx

# 2. PHYSICAL DESCRIPTION

2.01 The Winchester Disk Controller (WDC) 92-1011-xx is an integrated system component incorporating all the necessary component parts to provide the Mainframe with a single PCA Controller. Figure 2-1 illustrates the WDC. The PCA contains:

- (1) A  $\mu$ P section. A dedicated 8-bit  $\mu$ P designed specifically for control applications,

- (2) A memory section for storage of the control program and variables,

- (3) 796 Bus Interface section to provide for bus arbitration,

- (4) Control and Status Register section,

- (5) Read and Write section,

- (6) Phase-Locked Data Recovery section.

2.02 The PCA measures 6.0 inches by 12.0 inches. A pair of edge-type PC connectors,P1 and P2, mate with the 796 Bus backplane connectors.

- P1 is a dual 43-position, 86-conductor PC connector. The pin assignments conform to the 796 Bus specifications.

- (2) P2 is a dual 30-position, 60-conductor PC connector. The pins are vacant and are not used by the bus.

2.03 Five edge-type PC connectors, J2 through J6, provide for the data control and status to control up to four drives.

J2 through J5 are dual 10-position, 20-conductor PC connectors. These provide for the data communication between the WDC and each drive. A separate cable is connected to each drive, i.e., star connection.

(2) J6 is a dual 25-position, 50-conductor PC connector. This provides for the status and control signals between the WDC and Drives. A single cable is connected to each drive, i.e., daisy chain connection.

# Options

- 2.04 Several alternate features can be configured through option jumpers on the PCA. Refer to Figure 2-1.

- (1) W1 through W8 select the ROM type when WDC is optioned for ROM.

- (2) W9 through W18 configures the disk drive connectors for 8.0-inch or 5.25-inch drive signal locations.

- (3) W19 through W26 select the interrupt level for WDC.

- (4) W27 through W28 select WDC for 8- or 16bit data transfers.

- (5) W29 through W44 set the I/O port address. Normally this is 90-97H.

- (6) W45 sets WDC to highest bus master priority.

- (7) W46 and W47 set the INIT\* for master or slave operation.

# Adjustments

2.05 Three multi-turn trim potentiometers are provided for adjustments in the analog sections:

- (1) R17 sets the delay for the Synch Field Detector.

- (2) R23 balances the VCO Error Amplifier.

- (3) R34 adjusts the VCO frequency.

Refer to Figure 2-1 for the locations of these adjustments.

•

# 3. FUNCTIONAL DESCRIPTION

**3.01** The basic function of a disk drive controller is to provide dedicated electronics for con-

trol and positioning of the drive read/write head(s) and the logic for read/write operations.

# Disk Storage

3.02 The Winchester Disk Controller (WDC) stores random access data and program files on two non-removable 5.25-inch disks. Each of these disk surfaces employs one movable head to service 153 data tracks. The media is made up of a rigid aluminum disk substrate coated on both sides with ferrous oxide similar to that found on audio tape. Read/write head(s) do not come into physical contact with the media.

3.03 Low cost and high drive reliability are achieved through the use of a band actuator and an open loop stepper motor positioned head.Refer to the OEM Disk Drive Technical Manual for a detailed functional description.

3.04 Formatting the disk divides the media read/write area into logically numbered tracks. Individual tracks are further subdivided into logical sectors. Each sector is 128 Bytes with 38,144 sectors per drive. Sector locations are determined logically and termed Soft Sectored. Information is stored on both surfaces of the disk(s). A single disk index position is monitored by the drive status logic. This logic issues an INDEX\* pulse to the WDC each time the disk starts a new revolution. The computer Operating System uses the logical sector location and the indexing information to randomly access the stored files.

# Overview

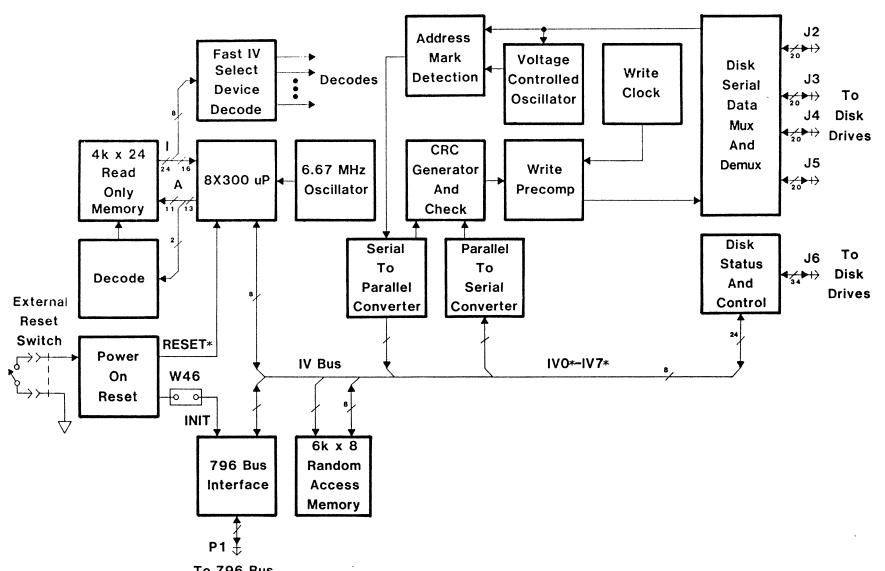

3.05 Figure 3-1 illustrates the principal sections of the WDC in block diagram. This figure and Figures 3-2 through 3-6 should be used in conjunction with the WDC logic diagram for the descriptions which follow.

3.06 Direct Memory Access (DMA) operation is performed by the WDC or Bus Master, as well as, Bus slave operation through the use of a unique device; a 8X300 microprocessor ( $\mu$ P). This 8-Bit  $\mu$ P is designed for fast control applications, such as, disk controllers. It has a limited instruction set of eight instruction types. 3.07 A 6.67 MHz oscillator clocks the  $\mu$ P resulting in a 300 ns instruction cycle time.

3.08 A firmware control program is stored in the  $4k \times 24$  ROM. Thirteen  $\mu$ P lines address this ROM and its associated *Decode* device. A 16-Bit instruction is returned to the  $\mu$ P and an additional 8-Bits are appended to the instruction used by the *Fast IV Select Decode* for direct I/O addressing.

3.09 Both the source device, first 4 bits, and the destination device, remaining 4 bits, are specified in the 8 bit word furnished to the Fast IV Select Decode for data to be transferred over the 8-bit bi-directional IV Bus, IV0\*-IV7\*. Table 3-1 lists the decoded signals by their functions. This method of device addressing permits greatly increase system speed over conventional  $\mu$ P design since conventional I/O addressing requires individual instructions.

3.10 The  $8X300 \ \mu P$  can address a source device, have that device place data on the IV Bus, and this data can then be taken into the  $\mu P$  all in the first half cycle or 150 ns. Data can be processed by an arithematic function included in the instruction read from ROM and the result placed back on the IV Bus targeted for storage in another device during the second half cycle.

3.11 A RESET\* issued from *Power-On-Reset* causes the  $\mu$ P to initialize. Activation of the *Power-On-Reset* can be through these channels.

- (1) Application of power to the +5 Vdc Bus.

- (2) An INIT\* received from the 796 Bus.

Optionally, a INIT\* can be issued to the 796 Bus.

3.12 I/O information can be transferred over the IV Bus between any of the WDC devices with or without passing through the  $\mu P$ .

- (1) 6k x 8 Random Access Memory WDC status and control variables are stored in RAM, e.g., data transferred to or from the 796 Bus.

- (2) 796 Bus Interface this device handles 796 Bus arbitration.

# Table 3-1 - Fast IV Select Decode Signals

| Mnemonic | Function                                     |

|----------|----------------------------------------------|

| LMBAM*   | Load 796 Bus Address Middle, A8-AF.          |

| LMBAH*   | Load 796 Bus Address High, A10-A13.          |

| LRAMAL*  | Load RAM Address Low, RA0-RA7.               |

| LRAMAH*  | Load RAM Address High, RA8-RA10 and CE0-CE3. |

| LDCNL*   | Load Disk Control Register.                  |

| LMUX*    | Load Multiplexer.                            |

| LMBD*    | Load 796 Bus Data, DB0-DB7 or DB8-DB15.      |

| LFCNL*   | Load Function Control Register.              |

| LDSKDAT* | Load Disk Data Register.                     |

| LRAM*    | Load RAM Data Register.                      |

| PTIMER*  | Pulse Timeout Timer.                         |

| PMBACK*  | Pulse 796 Bus Acknowledge.                   |

| MBRD*    | Pulse 796 Bus Read Request Flip Flop.        |

| PCIDX*   | Pulse Clear Index Flip Flop.                 |

| RMBCMD*  | Read 796 Bus Command Register.               |

| RRAM*    | Read RAM Data Register.                      |

| RMUX*    | Read Mux.                                    |

| RMBD*    | Read 796 Bus Data Register.                  |

| RFCNTL*  | Read Function Control Register.              |

| RDSKDAT* | Read Disk Data Register.                     |

- (3) Read and Write Logic data is transferred between the IV Bus and disk drive(s).

- (4) Disk Status and Control contains disk status buffers and control registers.

- (5) Interrupt provides for setting WDC interrupt level.

- **3.13** The on-card  $6k \times 8$  RAM stores control variables and data. Addressing of this memory is controlled by external registers in the form of counters. The  $\mu$ P loads these initially with the device decoder.

- 3.14 The WDC has both 796 Bus Master or slave device attributes.

- (1) As a master device the WDC generates requests to the 796 Bus Interface for storing and receiving data in other 796 Bus devices.

- (2) As a slave device, other 796 Bus Master devices, e.g. CPU, can address the WDC.

The on-card RAM is not accessable by 796 Bus devices.

3.15 The most complex portion of the WDC is the Read and Write Logic. Complexity is greatly reduced through the use of a five device set which performs the functions:

The Address Mark Detection is used by the WDC to find an ID address mark or data address mark in the serial data stream.

(2) The Serial to Parallel and Parallel to Serial Converters are shift registers used to convert serial data to the parallel IV Bus.

(3) Write serial data has a CRC word calculated and appended for each block of data as it is written to the disk. A check of this CRC word is made for each block of data read. Both of these operations are performed by the CRC Generation and Check.

(4) Write Precompensation is performed to data depending on the disk location which the data is to be written. An individual recording transition is either made slightly early or late to compensate for bit crowding on the disk. The write data passes through a multiplexer associated with a delay line to provide the actual compensation in time. Individual line drivers are used to supply write data to up to four drives due to the high data rate of 5 MHz.

(5) The Voltage Controlled Oscillator is used to develop the read clock. It is referenced to the VCO center frequency when reading is inactive.

3.16 The WDC can generate interrupts to the 796 Bus on any of the eight 796 Bus levels, INTO\*-INT7\*, through option jumpers. An interrupt is used to tell the 796 Bus an WDC operation is completed.

Memory

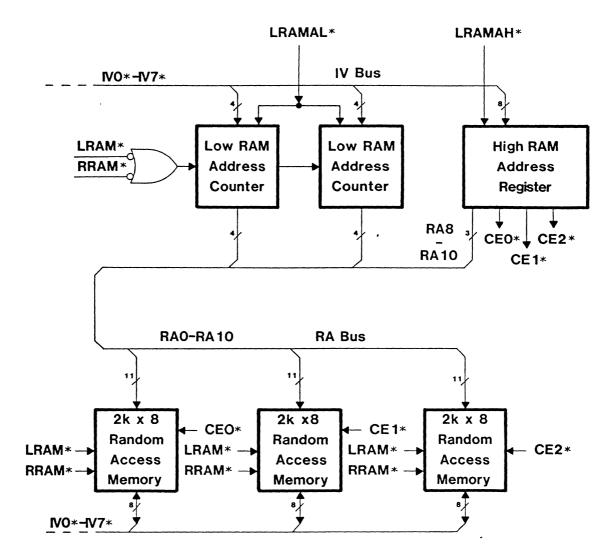

3.17 Refer to Figure 3-2 for the description which follows. The contents of the 6k x 8 Random Access Memory is exchanged as data to the IV Bus, IVO\*-IV7\*, with one of two instructions:

- (1) LRAM\* Load RAM Data Register,

- (2) RRAM\* Read RAM Data Register.

**3.18** The starting *RAM* address is stored in a counter and a register from the IV Bus with the commands LRAMAL\* and LRAMAH\* issued by the control program.

- (1) The Low RAM Counter stores the least significant 8 bits.

- (2) The *High RAM Register* stores the most significant 3 bits and the chip enables for individual 2k RAM devices.

Both of these form the 11-bit RAM Address Bus, RAO-RA10. This method of addressing provides for performing block data exchanges with memory using a single instruction once the control program initializes them. The *Address Counter* is incremented at the completion of each read, RRAM\*, or write, LRAM\*, operation. This auto-incrementing feature permits very fast data transfers.

3.19 The High RAM Address Register is reloaded, LRAMH\*, by the control program when a boundary is crossed, e.g., when the 8-bit Low RAM Counter might overflow. Individual memory device selects, CEO\*-CE3\*, are generated

Figure 3-2 - Memory Block Diagram

by the remaining portion of the *Address Register* eliminating the need for an individual device decoder.

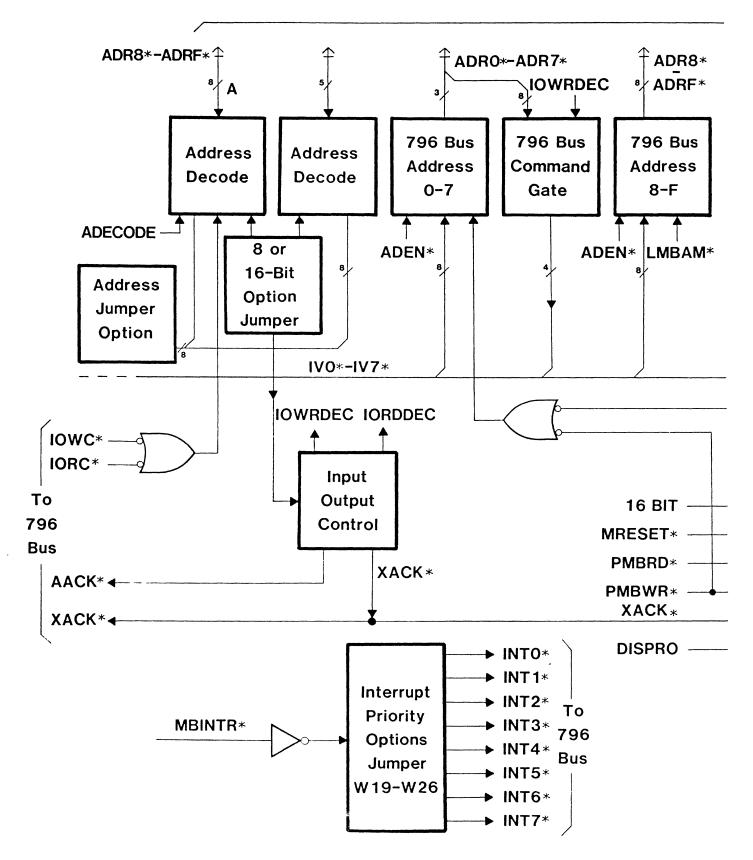

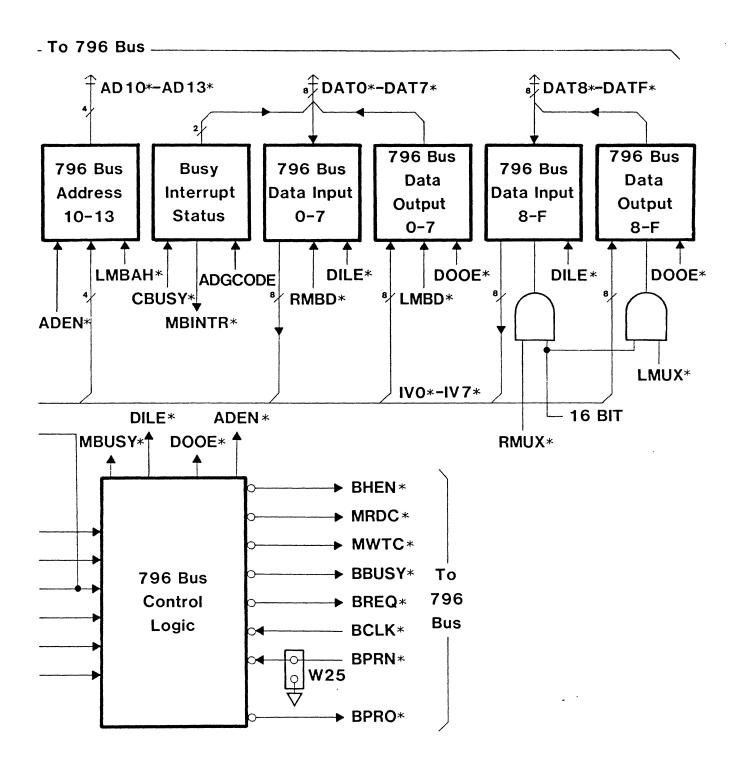

#### 796 Bus Interface

3.20 Refer to Figure 3-3 for the description which follows. The 796 Bus Interface is made up of two subsections.

- Data and address registers which communicate with the 796 Address Bus, AD0\*-AD13\*, and 796 Data Bus, DAT0\*-DATF\*.

- (2) Control signals and logic for timing data transfers with the 796 Bus.

3.21 Signal ADEN\* from the 796 Bus Control Logic gates the 796 Address 0-7, 8-F, and 10-13 registers on to the 796 Bus. The 796 Address registers are loaded from the IV Bus, IV0\*-IV7\*. Fast IV device decodes are supplied to load each register.

- (1) LMBAM\* to 796 Bus 8-F register,

- (2) LMBAH\* to 796 Bus 10-13 register,

- (3) PMBRD\* or PMBWR\* to 796 Bus Address 0-7 register.

Each time read or write request, PMBRD\* or PMBWR\*, is made to the 796 Bus Control Logic the least significant bits of the address are loaded into the  $\mu$ P.

3.22 The  $\mu$ P monitors the 796 Address Bus, ADR0-ADR2, and IOWRDEC during I/O cycles through the 796 Bus Command Gate, if the WDC is idle, the  $\mu$ P checks IOWRDEC. If set, ADR0-ADR3, are checked to determine what to do with the data presented on the 796 Data Bus. It will interpret this as:

- (1) The least significant 8 bits of a Command Block Pointer.

- (2) The next 8 bits of a Command Block Pointer.

- (3) The most significant 8 bits of a Command Block Pointer.

This operation performs the function of an address decoder normally performed by firmware. After this is stored in a  $\mu$ P register, an external acknowledge, XACK\* is issued completing the 796 I/O cycle. Typically this cycle will be 1.5  $\mu$ s, because of the fast  $\mu$ P response time.

3.23 796 Bus address lines, ADR3\* through

ADF\*, are input to Address Decode and compared to the Address Option Jumper thereby determining the unique 796 Bus device I/O address. The 8 or 16-bit Option Jumper determines the address length. The address option jumpers apply to A4-A7 and A8-AF. For example, if the desired address for 8-bit addressing is 90H, the same strapping would make the 16-bit address 9090H.

**3.24** The output of the Address Decoder(s) is a device select to Input Output Control created from:

- (1) 796 Bus I/O Write, IOWC\*, or I/O Read, IORC\*.

- (2) A comparison between the address presented on the 796 Bus and the unique WDC address.

- **3.25** *Input Output Control* performs two functions.

- (1) On an I/O Read, and I/O Read Decode, IORDDEC, is issued to the Busy Interrupt Status.

- (2) On an I/O Write, and I/O Write Decode, IOWDEC, is issued to the 796 Bus Command Gate.

- **3.26** The WDC data register is made up of four 8-bit registers.

- (1) 796 Bus Data Input 0-7.

- (2) 796 Bus Data Input 8-F.

The 796 Data Bus is connected to the register inputs and the IV Bus is connected to the register outputs.

- (3) 796 Bus Data Output 0-7.

- (4) 796 Bus Data Output 8-F.

The IV Bus is connected to the register inputs and the 796 Bus is connected to the register outputs.

Figure 3-3 - 796 Bus Interface Block Diagram

Figure 3-3 - 796 Bus Interface Block Diagram (Continued)

3.27 In the DMA mode, the loading and reading of these registers is in part under control of the 796 Control Logic.

- (1) DILE\* Data Input Load Enable,

- (2) DOOE\* Data Output Output Enable,

To load data from the 796 Bus into the 796 Bus Input register DILE\* is asserted. Data is sent to the 796 Bus from the 796 Bus Outout register when DOOE\* is asserted. Both of these signals apply to the external side of the WDC and are dependent on the direction or transfer of data. 3.28 On the internal side, Fast IV select decode signals handle loading and reading of these registers to IV Bus.

- (1) RMBD\* Read 796 Bus Data Register.

- (2) LMBD\* Load 796 Bus Data Register.

- (3) RMUX\* Read Multiplexer.

- (4) LMUX\* Load Multiplexer.

| Diagram<br>Mnemonic | 796 Bus<br>Mnemonic (1) | Pin     | Function                     |

|---------------------|-------------------------|---------|------------------------------|

| BCLK*               | BCLK*                   | 13      | Bus Clock.                   |

| MBINIT*             | INIT*                   | 14      | Initialize.                  |

| BPRN*               | BPRN*                   | 15      | Bus Priority In.             |

| BPRO*               | BPRO*                   | 16      | Bus Priority Out.            |

| BBUSY*              | BUSY*                   | 17      | Bus Busy.                    |

| BREQ*               | BREQ*                   | 18      | Bus Request.                 |

| MRDC*               | MRDC*                   | 19      | Memory Read Command.         |

| MWTC*               | MWTC*                   | 20      | Memory Write Command.        |

| IORC*               | IORC*                   | 21      | I/O Read Command.            |

| IOWC*               | IOWC*                   | 22      | I/O Write Command.           |

| XACK*               | XACK*                   | 23      | Xfer Acknowledge.            |

| AACK*               | LOCK*                   | 25      | Lock.                        |

| BHEN*               | BHEN*                   | 27      | Byte High Enable.            |

| INT0*—INT7*         | INTO*—INT7*             | 35-42   | Parallel Interrupt Requests. |

| A0*-A13*            | ADR0*                   | Various | 20-Bit Address Bus.          |

| DB0*DBF*            | DAT0*-DATF*             | Various | 16-Bit Data Bus.             |

| Table 3-2 – Winchester Disk Controller Active 796 Bus Signals | Table | 3-2 | Winchester | Disk | Controller | Active | 796 Bus | Signals |

|---------------------------------------------------------------|-------|-----|------------|------|------------|--------|---------|---------|

|---------------------------------------------------------------|-------|-----|------------|------|------------|--------|---------|---------|

Note:

<sup>(1)</sup> Address and data bus lines are in hexadecimal notation.

- **3.29** The **796** Bus Control Logic exchanges the 796 Bus arbitration signals.

- (1) BHEN\*,

- (2) MRDC\*,

- (3) MWTC\*,

- (4) BBUSY\*,

- (5) BREQ\*,

- (6) BCLK\*,

- (7) BPRN\*,

- (8) BPRO\*,

The functions of each are described in Table 3-2. Option Jumper, W25, provides for making the WDC highest priority Bus Master.

3.30 On the other side of the 796 Bus Control Logic are the signals generated on the WDC or used to control the 796 Bus signals.

- 16 BIT defines whether the WDC is transferring 8- or 16-bit words to the 796 Bus.

- (2) MRESET\* is the WDC reset.

- (3)  $PMBRD^* a$  Fast IV Select Decode signal.

- (4) PMBWR\* a Fast IV Select Decode signal.

When (3) or (4) are strobed, the 796 Bus Control Logic initiates the 796 Bus handshaking, and transfers the data. During the transfer, the  $\mu P$  checks:

(5) MBUSY\* - 796 Bus Busy over the IV Bus to determine when the transfer is completed.

3.31 Option Jumpers, W16-W26, set the Interrupt Priority for MBINTR\* to the 796 Bus Interrupt Levels, INTO\*-INT7\*. MBINTR\* is generated by the  $\mu$ P over the IV Bus at the end of a data transfer.

- 3.32 The transfer acknowledge, XACK\*, has two possible directions.

- (1) This signal is created on the WDC and sent to the 796 Bus in response to an I/O read or write.

- (2) This signal is input to the WDC from the 796 Bus at the completion of a data tranfer from another Bus Master.

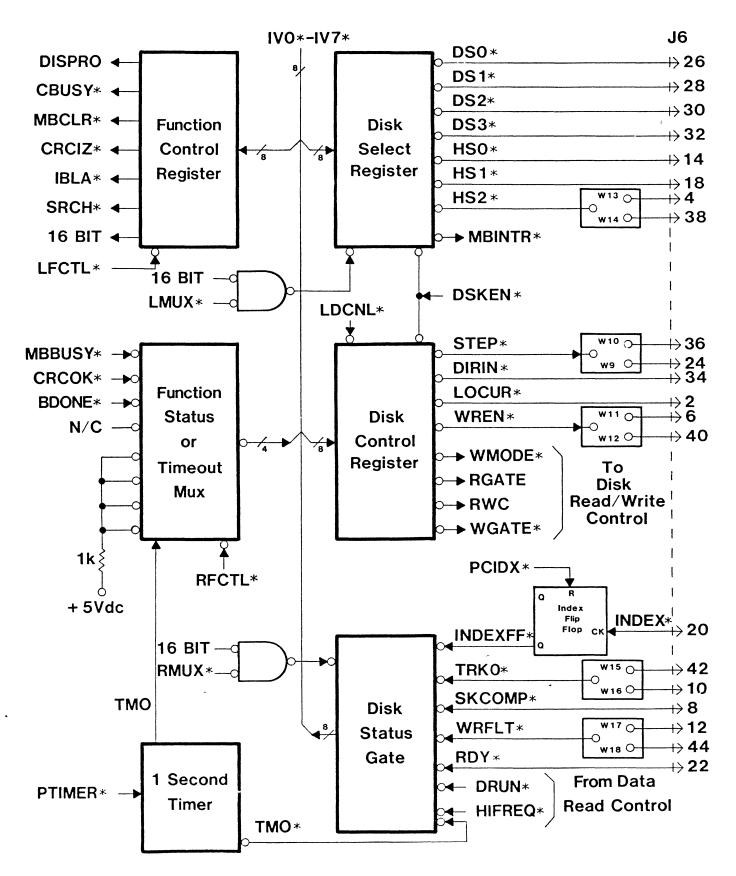

# **Control and Status**

3.33 Figure 3-4 illustrates the internal WDC status and control registers and transfer gates in block diagram. The *Disk Select Register*, *Disk Control Register*, and *Disk Status Gate* connect directly to the Winchester Drive by the disk status and control cable.

3.34 Option Jumpers, W13-W18, provide for alternate, J6, wiring to accommodate two different Winchester disk drives.

- (1) Seagate Technology 506. The 506 uses a 34-conductor connector.

- (2) Shugart Associates 1000. The 1000 uses a 50-conductor connector.

- 3.35 The Disk Select and Control Registers are enabled with DSKEN\*. This provision is made to prevent invalid write operation to the disk drive before the  $\mu$ P sets up the initial values in the registers, e.g., during power on operation. The Disk Select Register determines which drive and surface is accessed.

- DS0\*-DS3\* are the drive select lines for up to four drives. Only one of these are asserted at a time.

- (2) HS0\*-HS2\* are coded head select lines for up to 8 heads.

The remaining register output is used internally to the WDC.

(3) MBINT\* is the interrupt generated by the  $\mu$ P and furnished to the 796 Bus. Refer to Figure 3-3. 16 BIT and LMUX\* furnish the control for this register.

Figure 3-4 - Control and Status Block Diagram

3.36 Head position and write control information are determined by the value in the Disk Control Register.

- (1) STEP\* moves the head one increment.

- (2) DIRIN\* determines the direction of the head movement.

(3) LOCUR\* is a control signal furnished to the drive to reduce the write current on different tracks. These tracks vary for different drive types. This line allows the control program to adjust the current when appropriate.

(4) WREN\* is the write enable signal to the drive.

The four remaining lines are supplied to the Disk Read Write Control. Refer to Figure 3-5.

- (5) WMODE\* sets the Read/Write logic to Write Mode.

- (6) RGATE\* sets the Read/Write logic to Read Mode.

- (7) RWC\* is Reduce Write Current and means to internally perform write precompensation in the Read/Write logic.

- (8) WGATE\* is the Write Gate or data.

LDCNL\* from the Fast IV Select Decode furnishes the control for this register.

3.37 Current disk status information is gated onto the IV Bus, IV0\*-IV7\*, through the Disk Status Gate.

INDEX\* is a short duration pulse furnished by the drive at the start of each disk revolution. The *Index Flip Flop* functions as a storage register and is cleared by the control program with Fast IV Select Decode PCIDX\*.

(2) TRK0\* indicates the drive heads are positioned at Track 0, the lateral indexing location on the disk.

- (3) SKCOMP\* is the Seek Complete signal.

- (4) WKFLT<sup>\*</sup> is the Write Fault signal.

- (5) RDY\* is the disk drive Ready signal.

The three remaining status signals are generated within the WDC.

- (6) DRUN\* indicates the Synch Field Detector has detected a field of all zero's. This is the synch field before the Address Mark.

- (7) HIFREQ\* indicates the Address Mark Detector has detected a high frequency field.

This is a 5 MHz signal which may be an all zero's pattern. The all zero's pattern is the bitsynch field preceeding an ID Address Mark or a Data Address Mark.

- (8) TMO\* indicates the data transfer was abortive and must be restarted.

- 3.38 The Function Status or Timeout Multiplexer monitors the WDC status lines:

- (1) MBBUSY\* is the signal furnished from the 796 Control Logic indicating the 796 Bus is performing a data transfer.

- (2) CRCOK\* is the signal furnished from the Read and Write logic indicating that the CRC check was made.

- (3) BDONE\* is the signal furnished from the Read and Write logic indicating serial to parallel conversion was performed.

The control program cannot interleave the statusing of these lines within every data transfer operation and maintain high speed operation. At the start of transfer the control program asserts Fast IV Select Decode PTIMER\* starting the 1 Second Timer. Should any of lines (1), (2) or (3) above not go high in 1 second, the WDC control program considers the operation abortive. The WDC logic must be cleared and the operation restarted. After one second TMO\* forces the outputs high and asserts TMO\* to the Disk Status Gate. At the completion of each transfer, the control program checks TMO\*. If a time out has decoded, it asserts RFCTL\* and checks the Function Status to determine which input caused the aborted operation and then restarts the data transfer.

- **3.39** The Function Control Register outputs are used within the WDC.

- (1) DISPRO\* disables the priority out. Refer to Figure 3-3.

Figure 3-5 - Read and Write Logic Block Diagram

(2) CBUSY\* indicates the controller is busy and is used by the Busy Interrupt Status.

(3) MBCLR\* generates a 796 Bus INIT\* and will initialize the Bus if Option Jumper

W47 is installed.

- (4) CRCIZ\* initializes the CRC Generation and Check. Refer to Figure 3-5.

- (5) IBLA\* generates an Address Mark.

- (6) SRCH\* initiates a search for an Address Mark in the read data. Refer to Figure 3-5.

- (7) 16 BIT indicates a 16 bit data transfer.

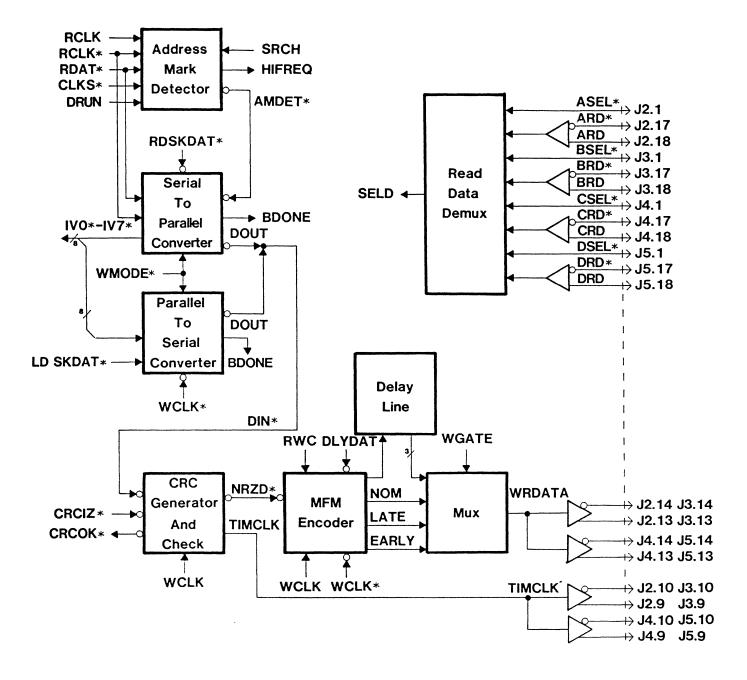

Read and Write Logic

3.40 Refer to Figure 3-5 for the description which follows. The Read and Write Logic perform the function of MFM Generation and Decode.

3.41 In the Read Mode, the first operation to perform is to locate the Address Mark in the Read data, so the preamble can be checked for addressed sector and cylinder number. The Address Mark Detector has four signals from the Phase-Locked Data Recovery input to it.

(1) RCLK and RCLK\* are the Read Clock generated by the VCO.

(2) RDAT\* is the Read Data and is synchronized to the VCO. A RDAT\* transition indicates a data transition.

- (3) CLKS\* is the signal clock. CLKS\* indicates a clock transition.

- (4) DRUN\* indicates the Synch Field Detector has detected a field of all zero's. This is the synch field before the Address Mark.

- 3.42 The  $\mu$ P uses two signals to control and monitor the *Address Mark Detector*.

- (1) SRCH\* initiates a search for an Address Mark in the read data.

- (2) HIFREQ\* indicates the Address Mark Detector has detected a high frequency field.

This is a 5 MHz signal which may or may not be all zero's.

When the Address Mark Detector detects the Address Mark, AMDET\* is asserted to the Serial to Parallel Converter.

3.43 RCLK\* and RDAT\* are both used as inputs to the Serial to Parallel Converter.Read Data is shifted into an internal shift register until an 8-bit word has been assembled. The converter then asserts BDONE.

(1) BDONE at this time indicates to the  $\mu P$  that a word has been assembled and been transferred to a separate internal buffer register. This provides the  $\mu P$  with one word time to read the assembled word onto the IV Bus and clear BDONE.

The Fast IV Select Decode asserts RDSKDAT\* to gate this word onto the IV Bus and clear BDONE.

3.44 The last operation performed in the Read Mode is to make a CRC check on the Preamble and the Read Data words. RCLK\* clocks these words through the CRC Generator and Check. If the check is determined to be correct:

- (1) CRCOK\* is asserted to the Disk Status Gate.

- (2) CRCIZ\* is issued from the Function Control Register to clear out the CRC Generator and Check before it is used again.

- 3.45 In the Write Mode, the first operation to perform is a Read Mode operation until the addressed sector is located. A switch is made at the end of the Preamble to the Write Mode by asserting WMODE\*.

3.46 LDSKDAT\* loads the 8-bit Write Data word from the IV Bus into an internal register of the *Parallel to Serial Converter*. The Write Data word is shifted out as serial data, DOUT\*, and on to DIN\* of the *CRC Generator* and Check. The clocking is performed by WCLK\*.

- **3.47** A CRC word is calculated from and appended to the Write Data. Output data:

- (1) NRZD\* is Non-Return to Zero data format.

Figure 3-6 - Phase-Locked Data Recovery Block Diagram

- **3.48** The *MFM Encoder* performs two operations to the Write Data.

- (1) The Write Data is converted from NRZ format to a MFM encoded signal.

(2) The Encoder provides the control lines NOMINAL, LATE or EARLY for the write precompensation. A particular write transition will be held at its true position which falls on either a data or clock transition, if the NOMINAL line is selected. If the LATE line is selected, the write transition will shift 12 ns after the true position, or if the EARLY line is selected, the shift will be 12 ns before the true position. The true position is referenced to the WCLK\* transition.

- **3.49** A Delay Line furnishes the delay outputs to the Multiplexer.

- (1) Early is a 24 ns delay.

- (2) Nominal is a 36 ns delay.

- (3) Late is a 48 ns delay.

3.50 Write precompensation is necessary when the disk has bit crowding. Bit crowding is caused by higher bit densities in sectors toward the center of the disk. Exact cylinder positions to begin with precompensation depend on the disk drive type. For this reason, exact cylinder locations for write precompensation are provided in the control program. Write precompensation has the effect of restoring the phase relationship in the Read Data during data recovery.

- **3.51** Two control lines are input to the *MFM Encoder*.

- (1) RWC activates write precompensation to the Write Data. RWC is not asserted in those sectors of the disk which do not have bit crowding.

- (2) DLYDAT is generated in the Read Data Phase Detector. It is the Write Clock delayed by 60 ns.

3.52 WRDATA, the Write Data output line, is distributed through two differential line drivers to up to four disk drives. Each drive has a separate disk data connectors, J2-J5. Additionally, TIMCLK, Time Clock, a general purpose reference frequency required by some drive types, is also distributed from these disk data connectors.

3.53 MFM Encoded Read Data is input to four

differential receivers connected to the disk data connectors as lines:

- (1)  $ARD^*/ARD$ .

- (2) BRD\*/BRD.

- (3) CRD\*/CRD.

- (4)  $DRD^*/DRD$ .

Note each differential line has an associated select line, A/B/C or DSEL\*. Incorrect cable connections between the disk drives and the WDC are eliminated through a unique design. The select line from the accessed disk drive is asserted by the drive. The *Read Data Multiplexer* then connects its input to the associated receiver. SELD, Selected Data, is output to the Phase-Locked Data Recovery.

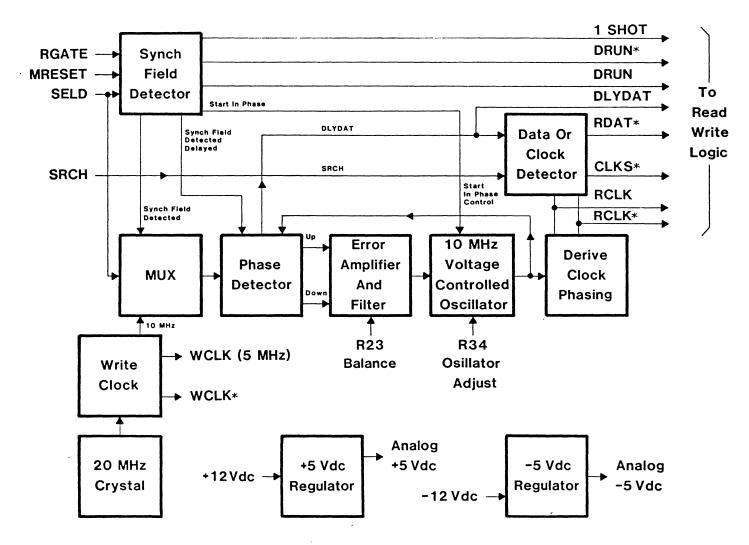

Phase-Locked Data Recovery

3.54 Figure 3-6 illustrates the Phase-Locked Data Recovery in block diagram for the description which follows. Initially, the MFM encoded Selected Data Line, SELD, is input to the Synch Field Detector which looks for a series of zero's proceeding an Address or Data Mark. Since this same pattern can also appear in a normal data field, the  $\mu$ P causes the detector to read the incoming data for a preset interval until it does or does not read an Address Mark.

3.55 Once a synch field is detected, the *Multiplexer* is switched by the Synch Field Detected line. The *Multiplexer* has two inputs.

- (1) A 10 MHz reference from the Write Clock is initially connected to the Phase

Detector to develop DLYDAT for Write Mode.

- (2) When a potential synch field is detected, the *Multiplexer* switches to SELD as the input to the *Phase Detector* because the incoming Read Data is potential valid data.

**3.56** The Phase-Lock loop is made up of three sections.

(1) The *Phase Detector* which produces an error signal derived from a phase comparison of Read Data and the 10 MHz output of the *Voltage Controlled Oscillator* (VCO).

- (2) The error signals, Up and Down, are filtered in the *Error Amplifier and Filter* to provide the proper loop response.

- (3) The 10 MHz Voltage Controlled Oscillator is adjusted in frequency by the error signal.

The VCO output is phase-locked to the incoming Read Data.

3.57 The purpose of the *Derived Clock Phasing* is to produce a 5 MHz Read Clock, RCLK/RCLK\*, which is in half bit synchronization with the incoming Read Data.

3.58 The DLYDAT line derived in the Phase Detector is input to the Data or Clock Detector and output to the Read Write Logic for the Write Mode. RCLK/RCLK\* is input to the Data or Clock Detector as a reference. The outputs are:

- (1) RDAT\* is the Read Data. A transition indicates Read Data.

- (2) CLKS\* is the Signal Clock. A transition indicates a clock.

**3.59** A second input to the *Data or Clock Detector* is search, SRCH, a control line from the  $\mu$ P. Once a possible synch field has been located and the VCO is locked onto the Read Data, SRCH is asserted. This causes the *Data or Clock Detector* to start generating data for the Read Logic.

3.60 The  $\mu$ P monitors DRUN\* to determine when a possible synch field has been detected, phase locked and acquiring data. A built in delay is provided in the control program to allow for the phase lock to take place before the  $\mu$ P asserts SRCH. 3.61 Exceptionally fast aquisition time is provided by the Start in Phase line from the Synch Field Detector. The phase lock does not have to go through a long initialization period since the VCO is started in phase. The oscillator is actually stopped and restarted again to assure proper phasing. There is some phase delay between the VCO and the Read Data immediately after starting the oscillator. For this reason, a delay of about 1 ns is built into the control program to allow for the phase lock to take place.

3.62 The status line, ONE SHOT, is used by the  $\mu P$  to determine if the Synch Field Detector is still in a possible synch field. A One Shot is held retriggered while a 5 MHz signal is detected, as soon as it becomes untriggered, the bounds of a possible synch field have been exceeded. In this case, the  $\mu P$  restarts the phase lock procedure by looking for a synch field. The trigger is set for 270 ns or 1.5 clock times.

- 3.63 The criteria for a valid synch field are:

- (1) The ONE SHOT is retriggered.

- (2) 16 bits of all zero's counted by the Synch Field Detector.

# 4. SPECIFICATIONS

4.01 The following furnishes the user with information for shipping and installation and should be used to establish acceptance criteria

.

if they are performed. Minor deviations from the specifications tabulated in Table 4-1 which do not affect the Winchester Disk Controller performance are excluded from the Codata Systems Corp. warranty.

| Signetics 8X300.                                                                                                |

|-----------------------------------------------------------------------------------------------------------------|

|                                                                                                                 |

| ST506.<br>Four.<br>4,882,432 bytes.                                                                             |

| MFM.<br>5 MHz.                                                                                                  |

| 16-bit CRC.                                                                                                     |

| 4k bytes.                                                                                                       |

| 128 bytes.<br>38,144 maximum.                                                                                   |

| 256.<br>32.<br>4.<br>153.<br>4.                                                                                 |

| 4096 bytes.<br>28.                                                                                              |

| IEEE 796 Bus Specification.<br>Master or slave.<br>16 bit.<br>20 bit.<br>IEEE 796 Bus Specification.<br>Vacant. |

| 8 or 16 bit.<br>Option jumper.<br>90-97H; 8 bit.                                                                |

|                                                                                                                 |

| PARAMETER                                                                                                                                  | CHARACTERISTICS                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt<br>Operation<br>Type<br>Levels                                                                                                   | Option jumper.<br>Level.<br>Eight.                                                                                                            |

| Reset<br>796 Bus INIT*<br>External                                                                                                         | Option jumper; master or slave.<br>Switch contact closure optional.                                                                           |

| PCA Dimensions<br>Length<br>Width<br>Spacing                                                                                               | <ul> <li>IEEE 796 Bus Specification.</li> <li>30.5 cm (12.0 inch).</li> <li>17.1 cm (6.75 inch).</li> <li>1.3 cm (0.5 inch).</li> </ul>       |

| Input Output Connector, J2-J5<br>, J6                                                                                                      | 20-conductor; mates to Ansley 609-2015M.<br>50-conductor; mates to Ansley 609-5015M.                                                          |

| Environment<br>Temperature<br>Operating<br>Storage<br>Humidity<br>Power Requirements<br>+12 Vdc Bus<br>+5 Vdc Bus<br>-12 Vdc Bus<br>Weight | 4 C to 55 C (32 F to 131 F).<br>0 C to 65 C (32 F to 149 F).<br>5% to 90%, noncondensing.<br>0.5 A.<br>2.5 A.<br>0.5 A.<br>397 g. (14.0 oz.). |

.

# Table 4-1 – Winchester Disk Controller 92-1011-xx Specifications (Continued)

# 5. OPERATION AND PROGRAMMING

# Options

5.01 Before the Winchester Disk Controller WDC is installed into the Mainframe card cage, the PCA options should be verified.

- (1) Check the W1 through W47 Option Jumpers. Refer to Table 5-1.

- (2) Check U30, U31, U48, U49, U76, and U77 ROM. Refer to Table 5-1.

5.02 Install the PCA into card position designated for the WDC. Refer to the Mainframe Hardware Reference Manual. Connect the disk I/O cables to J1 through J6.

# Controller Programming - General

5.03 Disk commands and addressing parameters are sent to the WDC by a Command Parameter Block (CPB) located in system RAM. The pointer to the CPB address is sent to the WDC by a series of bytes output via I/O ports.

5.04 The CPB contains information defining two other blocks of system RAM, the Data Block and a Status Block. A typical command sequence is:

- (1) Read I/O port WDCBASE+0 and wait until the WDC is not busy.

- (2) Set up the CPB in system RAM for the next operation.

- (3) Issue the pointer to the CPB using I/O writes to WDCBASE+0, WDCBASE+2, and WDCBASE+4 in that order.

- (4) Start the controller by issuing WDCBASE+6.

- If not operating under interrupts, wait until:

- (5) The WDC is not busy by reading I/O port WDCBASE+0 until the busy bit is reset.

(6) Check the status of the last operation by referring to the status block in system RAM.

If operating under interrupts:

- (7) Return to normal processing until an interrupt from the WDC occurs.

- (8) When the interrupt has occurred, check that the interrupt was caused by this device by reading I/O port WDCBASE+0 and inspecting the interrupt bit. If this device caused the interrupt, clear the interrupt by issuing a write to I/O port WDCBASE+7 to clear the interrupt.

- (9) Determine the status of the last operation by referring to the status block in system RAM.

I/O Ports - CPB Pointer

5.05 Eight Consecutive I/O port addresses are used by the WDC to provide the following control information described below. The base address of the block WDCBASE is set by option jumpers. Table 5-2 tabulates these I/O port address assignments.

5.06 WDC Busy and Interrupt Status – The byte read at WDCBASE+0 represents the following:

- (1) Bit 7 WDC Busy. If set, the WDC is busy with an operation. If reset, the WDC may accept a new command.

- (2) Bit 6 WDC Interrupting. If set, the WDC is currently interrupting at the priority level set by option jumpers.

- (3) Bits 5-0 are not assigned.

- 5.07 CPB Address The 20-bit address formed by the three bytes of CPB Address point to a Command Parameter Block (CPB) which determines the type of operation, disk address, data address, block length and status block address.

| OptionDescription $01$ ROM Type SelectW1xIS3 = L.W2xIS3 = L.W3xIS2 = L.W4xIS2 = H.W5xA10 = GND.W6xA10 = GND.W7xA9 = GND.W8xA9 = A9.W10xWREN* to J6-24.W11xWREN* to J6-6.W12wREN* to J6-6.W13xHS2* to J6-38.W14xHS2* to J6-10.W16xWRFLT* to J6-10.W17xWRFLT* to J6-12.                                                                                                                                                                                                                                                                                |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| W1       x       IS3 = L.         W2       x       IS3 = H.         W3       x       IS2 = L.         W4       x       IS2 = H.         W5       x       IS2 = H.         W6       x       A10 = GND.         W7       x       A9 = GND.         W8       x       A9 = A9.         8.0-Inch or 5.25-Inch Disk       STEP* to J6-24.         W10       x       WREN* to J6-66.         W11       x       WREN* to J6-60.         W13       x       HS2* to J6-38.         W15       x       TRK0* to J6-10.         W16       x       TRK0* to J6-42. |  |

| W2       x       IS3 = H. $W3$ x       IS2 = L. $W4$ x       IS2 = H. $W5$ x       A10 = GND. $W6$ x       A9 = GND. $W7$ x       A9 = A9. $W8$ x       STEP* to J6-24. $W10$ x       WREN* to J6-36. $W11$ x       WREN* to J6-6. $W12$ x       HS2* to J6-40. $W14$ x       HS2* to J6-38. $W15$ x       TRK0* to J6-10. $W16$ x       TRK0* to J6-42.                                                                                                                                                                                             |  |

| W3       x       IS2 = L.         W4       x       IS2 = H.         W5       x       A10 = GND.         W6       x       A10 = A10.         W7       x       A9 = GND.         W8       x       A9 = A9.         W10       x       X         W11       x       WREN* to J6-36.         W12       x       WREN* to J6-40.         W13       x       HS2* to J6-4.         W14       x       TRK0* to J6-10.         W16       x       TRK0* to J6-42.                                                                                                 |  |

| W5<br>$W6$<br>$W7$<br>$W8$ x       x $W7$<br>$W8$ x       A10 = GND.<br>A9 = GND.<br>A9 = A9. $W9$<br>$W10$<br>$W11$<br>$W12$<br>$W13$<br>$W13$<br>$W15$<br>$W16$ x       STEP* to J6-24.<br>STEP* to J6-36.<br>WREN* to J6-6.<br>WREN* to J6-6.<br>WREN* to J6-40.<br>HS2* to J6-38.<br>TRK0* to J6-10.<br>TRK0* to J6-42.                                                                                                                                                                                                                          |  |

| W6       x       A10 = A10.         W7       x       A9 = GND.         W8       x       A9 = A9.         W9       x       STEP* to J6-24.         W10       x       WREN* to J6-36.         W12       x       WREN* to J6-6.         W13       x       HS2* to J6-40.         W14       X       TRK0* to J6-10.         W15       x       TRK0* to J6-42.                                                                                                                                                                                            |  |

| W7       X       A9 = GND.         W8       X       A9 = A9.         W9       X       STEP* to J6-24.         W10       X       STEP* to J6-36.         W11       X       WREN* to J6-6.         W12       X       HS2* to J6-40.         W13       X       HS2* to J6-38.         W15       X       TRK0* to J6-10.         W16       X       TRK0* to J6-42.                                                                                                                                                                                       |  |

| W9       x       STEP* to J6-24.         W10       STEP* to J6-36.         W11       x         W12       WREN* to J6-6.         W13       x         W14       HS2* to J6-38.         W15       x         W16       TRK0* to J6-42.                                                                                                                                                                                                                                                                                                                   |  |

| W9       x       STEP* to J6-24.         W10       STEP* to J6-36.         W11       x         W12       WREN* to J6-6.         W13       x         W14       HS2* to J6-4.         W15       x         W16       TRK0* to J6-42.                                                                                                                                                                                                                                                                                                                    |  |

| W10       x       STEP* to J6-36.         W11       x       WREN* to J6-6.         W12       WREN* to J6-40.         W13       x       HS2* to J6-4.         W14       HS2* to J6-38.         W15       x       TRK0* to J6-10.         W16       TRK0* to J6-42.                                                                                                                                                                                                                                                                                    |  |

| W11       x       WREN* to J6-6.         W12       WREN* to J6-40.         W13       x         W14       HS2* to J6-4.         W15       x         W16       TRK0* to J6-10.                                                                                                                                                                                                                                                                                                                                                                         |  |

| W12       WREN* to J6-40.         W13       x         W14       HS2* to J6-4.         W15       x         W16       TRK0* to J6-10.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| W14     HS2* to J6-38.       W15     TRK0* to J6-10.       W16     TRK0* to J6-42.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| W15         x         TRK0* to J6-10.           W16         TRK0* to J6-42.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| W16 TRK0* to J6-42.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| W17   x       WRFLT* to J6-12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| W18 WRFLT* to J6-44.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Interrupt Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| W19 MBINTR* to INT6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| W20<br>W21<br>MBINTR* to INT7.<br>MBINTR* to INT4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| W21<br>W22<br>MBINTR* to INT4.<br>MBINTR* to INT5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| W23 MBINTR* to INT2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| W24 MBINTR* to INT3.<br>W25 MBINTR* to INT0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 16-Bit or 8-Bit I/O Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| W27<br>W28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| W28 x 8-Bit I/O Address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| I/O Address Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| W29 $x$ ADRF = 1, ADR7 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| $ \begin{array}{c c} W30 \\ W31 \end{array} \qquad \qquad ADRF = 0, ADR7 = 0. \\ ADR8 = 1. \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| $\begin{array}{c c} W31 \\ W32 \\ \end{array} \qquad \qquad ADR8 = 1. \\ ADR8 = 0. \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| W33 $ADRE = 1, ADR6 = 1.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| $W34 \qquad x \qquad ADRE = 0, ADR6 = 0.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

Table 5-1 – Winchester Disk Controller Options – P/N 92-1011-xx

| Option Flag                                                                                                                                                                       |                                 | 3<br>1 | Description |                                                                         |                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------|-------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| W38       x       ADRD = 0, A         W39       ADRA = 1.         W40       x         W41       x         W42       x         W43       x         W45       x         W46       x |                                 |        |             | ADR9 = 0.<br>ADRD = 1, ADR5 = 1.<br>ADRD = 0, ADR5 = 0.<br>ADRA = 1.    |                                                                                  |

| Option                                                                                                                                                                            |                                 | Flag   | 3           | Description                                                             |                                                                                  |

|                                                                                                                                                                                   | 01                              |        | -           | Mnemonic                                                                | Codata Part Number                                                               |

| U77<br>U49<br>U31<br>U76<br>U48<br>U30                                                                                                                                            | x<br>x<br>x<br>x<br>x<br>x<br>x |        |             | ROM0A HX0<br>ROM0A HX1<br>ROM0A HX2<br>ROM1 HX0<br>ROM1 HX1<br>ROM1 HX2 | 27-0030-01<br>27-0029-01<br>27-0028-01<br>27-0027-01<br>27-0026-01<br>27-0025-01 |

# Table 5-1 - Winchester Disk Controller Options - P/N 92-1011-xx (Continued)

#### Notes:

(1) An X in the Flag column indicates a jumper is installed, a wrapped wire is installed, the switch is set or the ROM is installed.

| Table 5-2 | - I/O Port | Address | Assignments |

|-----------|------------|---------|-------------|

|-----------|------------|---------|-------------|

| Address   | Туре  | Function                             |

|-----------|-------|--------------------------------------|

| WDCBASE+0 | Read  | WDC Busy and Interrupt Status.       |

| WDCBASE+0 | Write | CPB Address Bits 0-7.                |

| WDCBASE+2 | Write | CPB Address Bits 8-15.               |

| WDCBASE+4 | Write | CPB Address Bits 16-19.              |

| WDCBASE+6 | Write | WDC Configuration Parameters and GO. |

| WDCBASE+7 | Write | Reset WDC Interrupt.                 |

#### 05-0003-01

5.08 WDC Configuration and GO - Issuing this byte performs two functions. Certain configuration parameters of the WDC are defined and the WDC is commanded to GO. This byte should be issued only after the CPB has been defined in system RAM, and all three bytes of the CPB pointer have been output. The meaning of the configuration portion of this byte are:

- (1) Bit 7 Interrupt Enable. If set an interrupt will be generated at the end of the current operation. If reset no interrupt will be issued.

- (2) Bit 6 Data Word Length. If set the Data Word Length is 16 bits. If reset the Data Word Length is 8 bits.

- (3) Bits 5-0 are not assigned.

- 5.09 Reset WDC Interrupt Issuing an I/O write to this port causes the Interrupt from the WDC to be reset. In addition, the interrupt status, Bit 6, of WDCBASE+0 Read will be reset.

# **Command Parameter Block**

5.10 The CPB organization is listed in Table 5-3. The *Command Byte* code description is listed in Table 5-4.

| Table 5-3 – Command Parameter Address Block |  |  |  |  |  |

|---------------------------------------------|--|--|--|--|--|

| Assignments                                 |  |  |  |  |  |

| Location                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                                 |                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| CPB+0<br>CPB+1<br>CPB+2<br>CPB+3<br>CPB+4<br>CPB+5<br>CPB+6<br>CPB+7<br>CPB+8<br>CPB+7<br>CPB+8<br>CPB+10<br>CPB+11<br>CPB+12<br>CPB+13<br>CPB+14<br>CPB+15 | Command Byte.<br>Unit Number.<br>Logical Sector Number<br>Logical Sector Number<br>Byte of 00 (1)<br>Byte Count<br>Byte Count<br>System RAM Address<br>System RAM Address<br>System RAM Address<br>Byte of 00 (1)<br>Status Block Pointer<br>Status Block Pointer<br>Status Block Pointer<br>Byte of 00 (1) | Bits 8-15.<br>Bits 16-23.<br>Bits 0-7.<br>Bits 8-15.<br>Bits 0-7.<br>Bits 8-15. |

| CPB+15                                                                                                                                                      | Byte of 00 (1)                                                                                                                                                                                                                                                                                              |                                                                                 |

Note:

(1) Reserved for expansion.

Page 28

5.11 Unit Number - This defines the logical unit number of the disk drive. Option jumpers on each drive define the individual disk. The allowed range of unit is 0 to 3.

5.12 Logical Sector Number (LSN) — Refers to the 128 byte logical sector used to address the disk. The range of addressing is 0 to 094FFH.

5.13 Byte Count - Refers to the number of bytes to be transferred. If a count is given which when taken with the System RAM Address exceeds the currently defined 64k Bank, transfer will continue into the next bank.

5.14 If a byte count is given which when taken with the LSN, exceeds the capacity of the drive, an error flag will be returned.

# IMPORTANT

If an odd byte count is specified, the Controller will transfer data in an 8-bit word length even if a word length of 16 bits was specified in the data sent to I/O port WDCBASE+5.

5.15 System RAM Address – The System RAM Address defined in the CPB consists of a 16-bit RAM address and a 4-bit bank address. If the address specified does not exist, then MBTMO, 796 Bus TIMEOUT, status will be returned.

# IMPORTANT

If the starting address specified is an odd address, DMA data transfers will be performed on a 8-bit basis even if the word length was defined to be 16 bit.

The WDC uses the INTEL (R) convention of byte addressing when using 16-bit memory addressing:

- (1) Least significant byte is an even address.

- (2) Most significant byte is an odd address.

| Table 5-4 | Command | Byte | Code |

|-----------|---------|------|------|

|-----------|---------|------|------|