ROBERT S. LEDLEY

Digital Computer and Control Engineering

MCGRAW-HILL

## DIGITAL COMPUTER AND CONTROL ENGINEERING

. .

## McGRAW-HILL ELECTRICAL AND ELECTRONIC ENGINEERING SERIES

FREDERICK EMMONS TERMAN, Consulting Editor W. W. HARMAN AND J. G. TRUXAL,

Associate Consulting Editors

AHRENDT AND SAVANT · Servomechanism Practice **ANGELO** · Electronic Circuits ASELTINE · Transform Method in Linear System Analysis ATWATER · Introduction to Microwave Theory BAILEY AND GAULT · Alternating-current Machinery BERANEK · Acoustics BRACEWELL · The Fourier Transform and Its Application BRENNER AND JAVID · Analysis of Electric Circuits BROWN · Analysis of Linear Time-invariant Systems BRUNS AND SAUNDERS · Analysis of Feedback Control Systems CAGE · Theory and Application of Industrial Electronics **CAUER** · Synthesis of Linear Communication Networks CHEN · The Analysis of Linear Systems CHEN · Linear Network Design and Synthesis CHIRLIAN · Analysis and Design of Electronic Circuits CHIRLIAN AND ZEMANIAN · Electronics CLEMENT AND JOHNSON · Electrical Engineering Science COTE AND OAKES · Linear Vacuum-tube and Transistor Circuits CUCCIA · Harmonics, Sidebands, and Transients in Communication Engineering CUNNINGHAM · Introduction to Nonlinear Analysis D'AZZO AND HOUPIS · Feedback Control System Analysis and Synthesis EASTMAN · Fundamentals of Vacuum Tubes **FEINSTEIN** · Foundations of Information Theory FITZGERALD AND HIGGINBOTHAM · Basic Electrical Engineering FITZGERALD AND KINGSLEY · Electric Machinery **FRANK** · Electrical Measurement Analysis FRIEDLAND, WING, AND ASH · Principles of Linear Networks **GHAUSI** · Principles and Design of Linear Active Circuits **GHOSE** · Microwave Circuit Theory and Analysis **GREINER** · Semiconductor Devices and Applications HAMMOND · Electrical Engineering HANCOCK · An Introduction to the Principles of Communication Theory HAPPELL AND HESSELBERTH · Engineering Electronics HARMAN · Fundamentals of Electronic Motion HARMAN · Principles of the Statistical Theory of Communication HARMAN AND LYTLE · Electrical and Mechanical Networks HARRINGTON · Introduction to Electromagnetic Engineering HARRINGTON · Time-harmonic Electromagnetic Fields HAYASHI · Nonlinear Oscillations in Physical Systems HAYT · Engineering Electromagnetics HAYT AND KEMMERLY · Engineering Circuit Analysis HILL · Electronics in Engineering JAVID AND BRENNER · Analysis, Transmission, and Filtering of Signals JAVID AND BROWN · Field Analysis and Electromagnetics JOHNSON · Transmission Lines and Networks KOENIG AND BLACKWELL · Electromechanical System Theory KRAUS · Antennas **KRAUS** · Electromagnetics KUH AND PEDERSON · Principles of Circuit Synthesis

LEDLEY · Digital Computer and Control Engineering LEPAGE · Complex Variables and the Laplace Transform for Engineering LEPAGE AND SEELY · General Network Analysis LEY, LUTZ, AND REHBERG · Linear Circuit Analysis LINVILL AND GIBBONS · Transistors and Active Circuits LITTAUER · Pulse Electronics LYNCH AND TRUXAL · Introductory System Analysis LYNCH AND TRUXAL · Principles of Electronic Instrumentation LYNCH AND TRUXAL · Signals and Systems in Electrical Engineering MILLMAN · Vacuum-tube and Semiconductor Electronics MILLMAN AND SEELY · Electronics MILLMAN AND TAUB · Pulse and Digital Circuits MILLMAN AND TAUB · Pulse, Digital, and Switching Waveforms MISHKIN AND BRAUN · Adaptive Control Systems MOORE · Traveling-wave Engineering NANAVATI · An Introduction to Semiconductor Electronics PETTIT · Electronic Switching, Timing, and Pulse Circuits PETTIT AND MCWHORTER · Electronic Amplifier Circuits PETTIT AND MCWHORTER · Concepts of Probability Theory **PFEIFFER** · Linear Systems Analysis REZA · An Introduction to Information Theory REZA AND SEELY · Modern Network Analysis **ROGERS** · Introduction to Electric Fields **RYDER** · Engineering Electronics SCHWARTZ · Information Transmission, Modulation, and Noise SCHWARZ AND FRIEDLAND · Linear Systems SEELY · Electromechanical Energy Conversion SEELY · Electron-tube Circuits SEELY · Electronic Engineering SEELY · Introduction to Electromagnetic Fields SEELY · Radio Electronics SEIFERT AND STEEG · Control Systems Engineering SISKIND · Direct-current Machinery Skilling · Electric Transmission Lines SKILLING · Transient Electric Currents SPANGENBERG · Fundamentals of Electron Devices SPANGENBERG · Vacuum Tubes STEVENSON · Elements of Power System Analysis STEWART · Fundamentals of Signal Theory STORER · Passive Network Synthesis STRAUSS · Wave Generation and Shaping Su · Active Network Synthesis **TERMAN** · Electronic and Radio Engineering **TERMAN AND PETTIT** · Electronic Measurements THALER · Elements of Servomechanism Theory THALER AND BROWN · Analysis and Design of Feedback Control Systems THALER AND PASTEL · Analysis and Design of Nonlinear Feedback Control Systems **THOMPSON** · Alternating-current and Transient Circuit Analysis Tou · Digital and Sampled-data Control Systems Tou · Modern Control Theory **TRUXAL** · Automatic Feedback Control System Synthesis VALDES · The Physical Theory of Transistors VAN BLADEL · Electromagnetic Fields WEINBERG · Network Analysis and Synthesis WILLIAMS AND YOUNG · Electrical Engineering Problems

• •

tan Antonio de la companya de la companya de la companya Antonio de la companya de la companya de la companya de la Antonio de la companya de la companya de la companya

# DIGITAL COMPUTER AND CONTROL ENGINEERING

## **ROBERT STEVEN LEDLEY**

ASSOCIATE PROFESSOR OF ELECTRICAL ENGINEERING THE GEORGE WASHINGTON UNIVERSITY CONSULTANT MATHEMATICIAN TO THE NATIONAL BUREAU OF STANDARDS

#### WRITTEN WITH THE ASSISTANCE OF

LOUIS S. ROTOLO

JAMES BRUCE WILSON

Research Scientist The Georg

cientist Research Associate The George Washington University

## McGRAW-HILL BOOK COMPANY, INC.

New York Toronto London 1960

## DIGITAL COMPUTER AND CONTROL ENGINEERING

Copyright (1960 by the McGraw-Hill Book Company, Inc. Printed in the United States of America. All rights reserved. This book, or parts thereof, may not be reproduced in any form without permission of the publishers. Library of Congress Catalog Card Number 59-15055

VII

#### 36981

THE MAPLE PRESS COMPANY, YORK, PA.

## TO MY SONS FREDDY AND GARY

## FOREWORD

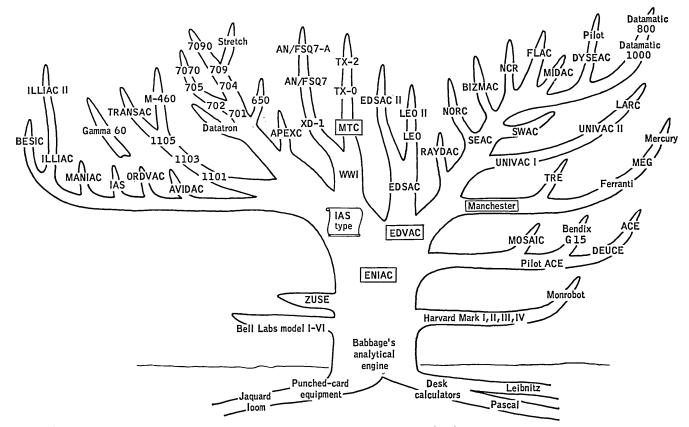

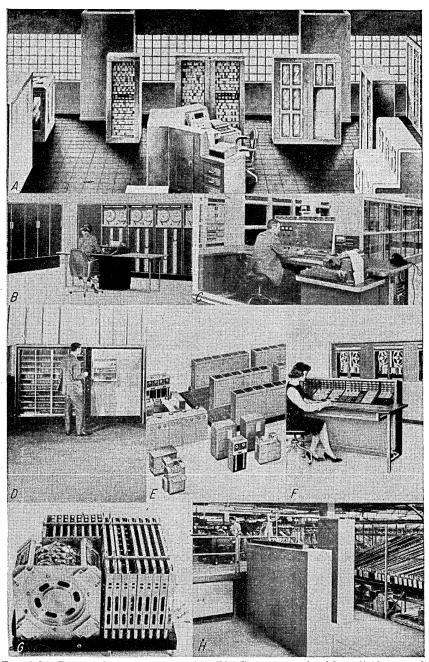

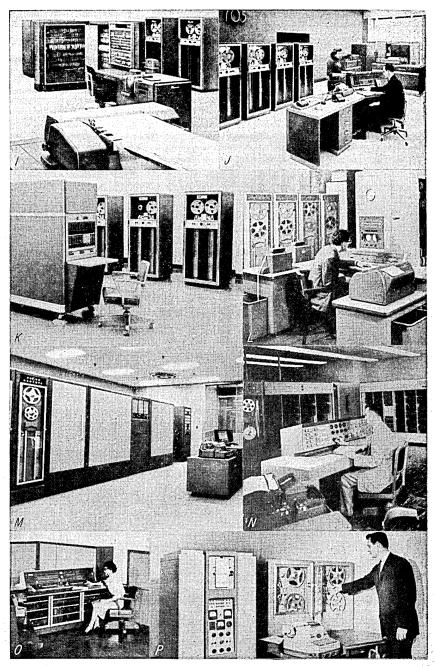

Until less than a century ago, men toiled manually to produce the very clothes they wore, shelters they lived in, and food they ate. The industrial revolution-derived from the invention of machines that automatically make commodities—was a revolution that vastly enlarged man's The effect is observed upon comparing the daily productive capabilities. life of a man of a century ago with that of a modern man, in his highly mechanized economic and interdependent social civilization. Now we are on the threshold of a new kind of revolution, a revolution that may in the future have even more far-reaching effects, vastly increasing man's "thinking" capabilities of planning, analyzing, computing, controlling. This new revolution derives from the availability of machines that automatically compute and control. We know its effects will be great, but we now can only speculate on the forms they will take. Not only will its influence be directly marked in the physical sciences and in technology, but, perhaps even more significantly, it will have a tremendous effect on the biological sciences and on the economic, political, and social aspects of our civilization. Its effects during the productive life span of the infant of 1960 will certainly be greater than those the industrial revolution has had during the life span of the infant of 1900. Pivotal in the growth and development of this newest of mankind's capabilities will be the digitalcomputer and -control engineer, whose primary occupation is the creation -the research, development, and production-of these new machines.

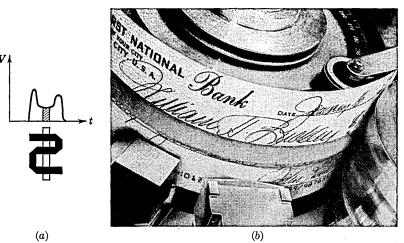

There is another quite remarkable aspect of digital-computer and control engineering. Never before in the history of human endeavor has a new development of such scope and complexity emerged so rapidly. Within a single decade this entirely new field, constructing and utilizing thousands of new computers, has already penetrated almost all phases of our modern society, from nuclear-energy production and missile design to the processing of bank checks, business invoices, and medical diagnoses. And in the research stages there are already components that might make it feasible to build computers manyfold more complex than present-day computers.

Beyond the unique potential to mankind and the phenomenal growth of the field is yet a third relatively unique aspect of digital-computer and control engineering. It is fast becoming one of the broadest in scope and most demanding of all engineering fields, encompassing fundamental aspects of logic, mathematics, systems engineering, as well as solid-state

#### FOREWORD

physics and electrical engineering. Since an error of only a single bit in a program or the breakdown of a single gate or component of a digital computer or control can result in the failure of the entire system, high meticulousness is demanded of the engineer. Thus his training must not only cover a wide range of topics but must as well emphasize precise attention to detail.

This book is the first comprehensive elementary engineering text in the digital-computer- and digital-control-engineering field (although there are several excellent advanced books in more specialized aspects of the field). The book seeks to present a new synthesis of educational material possessing a unity and breadth arising from the organization of the various aspects of digital-computer and -control engineering as a whole. It provides the material of a basic field of study for all students of electrical engineering, regardless of their ultimate specialty. However, it is hoped that this book may help stimulate a number of young engineers to enter this dynamic and vitally young field.

Samuel N. Alexander Chief, Data Processing System Division The National Bureau of Standards

#### PREFACE

General Information. The purpose of this book is to fill the need for a comprehensive elementary-engineering textbook in the large and still rapidly growing field of digital computers and controls. (The term *control* is used to emphasize that digital control and digital computers are based on the same principles.) The need for such a text is not confined to engineering schools; in industry as well, the graduate engineer with a few sporadic encounters with digital circuitry needs a sound introduction to the burgeoning literature on all phases of digital computers and controls.

Within the first five years after he earns his degree almost every electrical engineer will deal with some phase of digital circuitry. Therefore a course on digital computers is required for all candidates for the bachelor of electrical engineering degree at The George Washington University. This is indicative of a trend in engineering schools throughout the country.

This text is based on experience I gained in teaching courses on digital computers at The George Washington University School of Engineering. It is directed to senior undergraduate engineering students and first-year graduate students and is intended primarily for a year's course. Prerequisites are college physics, calculus, and at least a first course in electronic circuits, although no great proficiency in these subjects is required. Since it is an elementary exposition of the principles of digitalcomputer and control engineering, the book covers topics in all three phases of the subject: the over-all design of digital systems (Parts 1 and 2); the logical design of digital circuitry (Parts 3 and 4); and the electronic design of digital circuits (Part 5).

An introductory exposition of a field as large and complex as this can never hope to treat all subjects exhaustively. Full treatment must be left to specialized source books, handbooks, and journal articles. Almost without exception, each chapter of this book could be used as the basis for an entire book in itself—this is in fact true of some sections as well. Each chapter is designed to introduce the student to certain fundamental concepts and techniques of development. The method of teaching is by example rather than by generalized exposition. It is felt that the student is more capable of grasping abstractions from specifics than of extracting concepts from discussions based on generalizations alone. Hence I have tried wherever it was possible to guide the student by means of specific, concrete examples. From experience I have found that this

#### PREFACE

pedagogical method is particularly well suited to engineering students.

Since there has been no previous comprehensive text in the field, there is no precedent for the choice of topics. The subjects covered were chosen to present a continuous, natural development of the major aspects of the field in the limited time available to the engineering student. Of course in any field of this size there will exist differences of opinion as to which topics should and should not be included. I feel that I have chosen those topics of greatest importance and that this comprehensive treatment will satisfy the needs of the largest number of readers.

Much attention was paid to the exercises, of which more than 750 appear in the book. The exercises at the end of each section serve to illustrate the material of the section, to enable the student to gain computational facility, and to extend the material to closely related topics not covered in the section. Almost every chapter ends with Additional Topics, a section designed to introduce the reader to new material not covered in the chapter and to stimulate his further reading in the field. The text includes many new results of original research never previously compiled into book form, some of which here appear in publication for the first time (see Special Technical Features below).

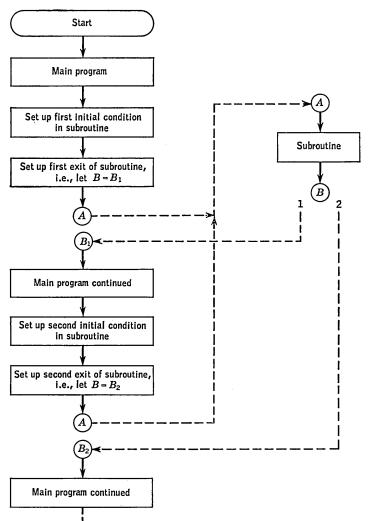

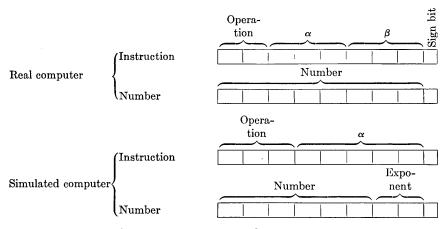

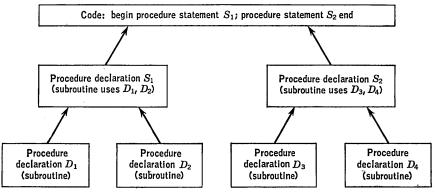

Outline of the Text. Perhaps the most outstanding capability afforded by digital techniques is that of decision making, as exemplified by the programmed system. Thus Part 1, the first of two parts on digital systems, is concerned with the digital programmed system. Its first two chapters are introductory in nature: the first is intended to motivate the student by delineating the wide range of applications of digital systems and controls; the second is designed to orient the student with respect to the digital-computer-engineering field. The next three chapters are directly concerned with programming; their purpose is to expose the engineering student to a large variety of instruction and operation formats, as well as to the practice of coding. Sequencing of instructions in four-, three-, two-, and one-address-system instruction formats is considered. The fundamental concepts of the loop, or iteration, and the subroutine are introduced, followed by a discussion of the various kinds of operations that instructions can involve. At the end of Part 1 we consider the formulation of program-checking and computer-maintenance programs. Further automatic-programming techniques lay the groundwork for a simplified presentation of the international algebraic automatic program called ALGOL.

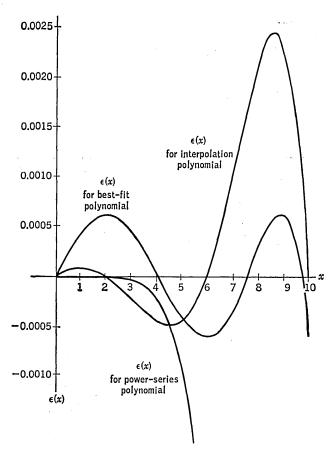

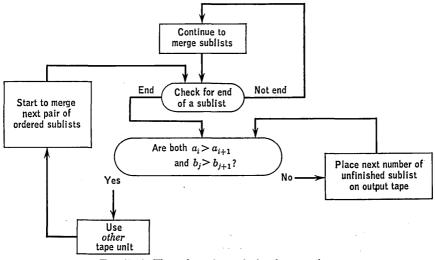

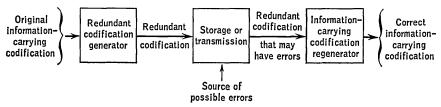

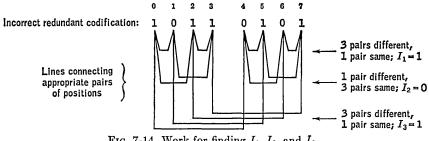

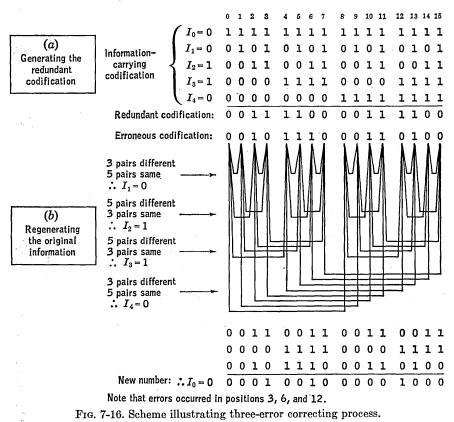

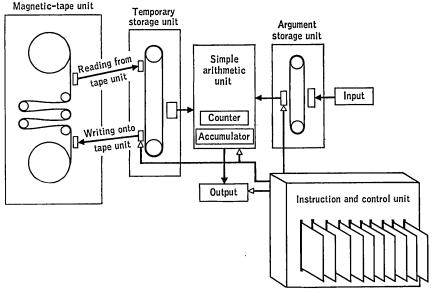

Part 2 is concerned with the functional approach to digital-systems design; here again the purpose is to expose the student to a variety of possible systems-design concepts. Numerical analysis is considered, as the basis of the systems design of the general-purpose digital computer. Here the concept of the polynomial-approximation approach is stressed as a fundamental method for reducing most mathematical computation to additions, subtractions, multiplications, and divisions. Next are described computational methods other than those of classical numerical analysis, methods which are, however, of fundamental importance in business and in other activities requiring data reduction. Besides techniques for searching and sorting, examples of methods for redundant and irredundant coding are considered. In order to demonstrate clearly the possibility of other than general-purpose computers, the digital differential analyzer is considered, along with real-time control and other techniques. Also a general discussion is included of the concepts underlying the "super" computers now in the research and developmental stages. Finally I introduce the Pedagac, a small general-purpose computer intended to provide the necessary *thread of continuity* to the study of digital-computer engineering (see below for further discussion of the Pedagac).

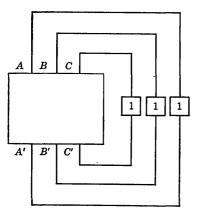

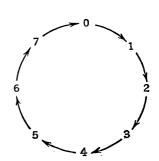

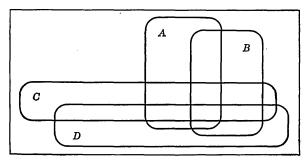

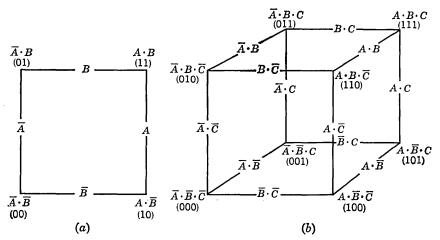

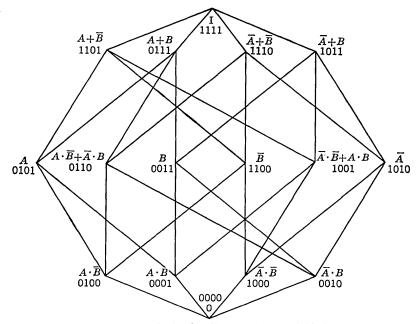

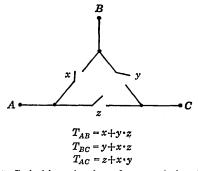

Probably the "newest" of the concepts confronting the uninitiated reader in digital-computer and -control engineering is that concerned with Boolean algebra as the basis for the logical design of digital circuits. Thus Part 3, the first of two parts on the logical design of digital circuitry, is concerned with the mathematical foundations of Boolean algebra. First Boolean algebra is introduced in terms of propositions, for it is advisable that the engineer understand the relation of Boolean algebra to other concepts as well as digital circuitry. Hence we take up the propositional-calculus representation and the class, or set, representation before the digital-circuit representation. The method of using bases and associated designation numbers in the succeeding chapters (which was first fully developed by the author, although it appeared implicitly in some earlier writings) has been found admirably suited to the teaching of the logical design of digital circuits. On the basis of this method, several modern procedures for the simplification of Boolean functions are explained, leading into the design of digital circuits to compute elementary synchronous recursive functions. In the final three chapters of this part, digital computational methods of importance in logical circuit design are considered. With few exceptions the methods presented are based on the author's original research. Elementary algorithms, including methods for solving Boolean equations and their application to circuit design, are given. Chapters 13 and 14 consider computations with Boolean matrices, the former being concerned with the theoretical development of the methods, the latter with applications of these results. (Should it be desired to study the applications of the computational methods before delving into the details of the proofs, Chap. 13 has been written so that the applications of Chap. 14 may be considered directly after Sec. 13-3 with no loss of continuity.)

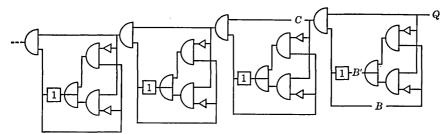

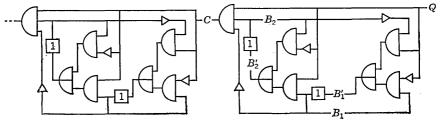

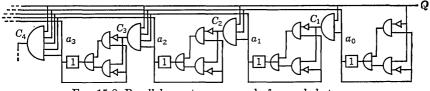

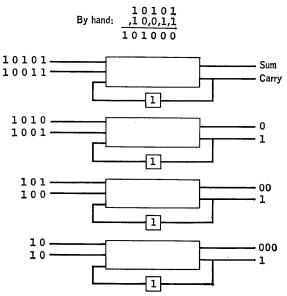

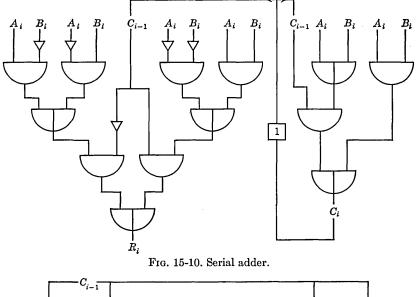

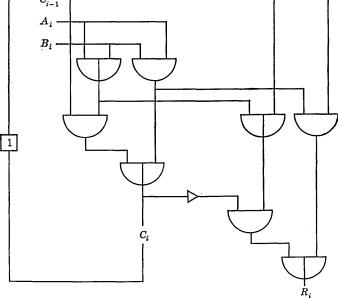

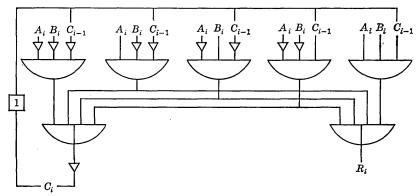

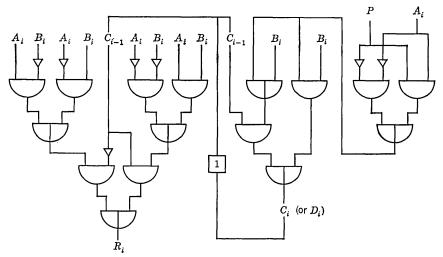

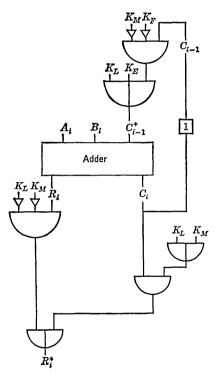

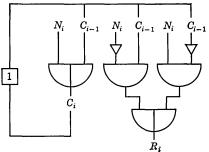

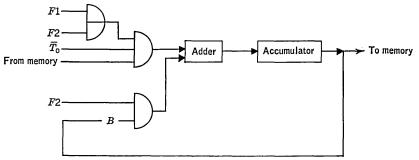

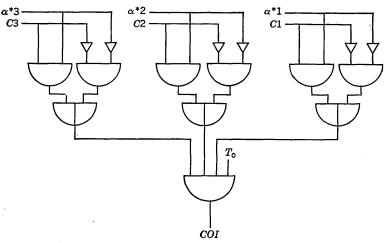

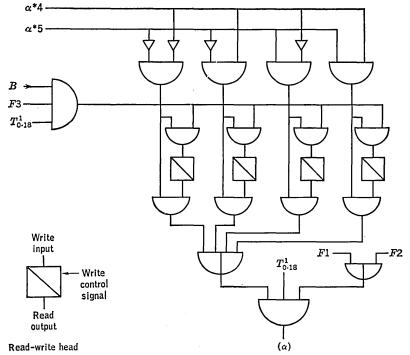

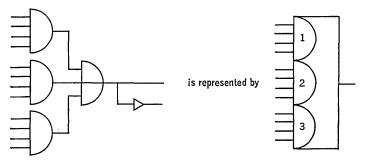

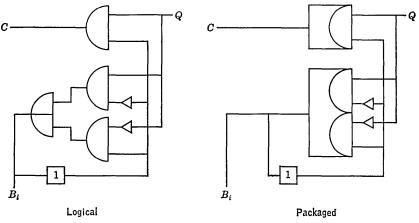

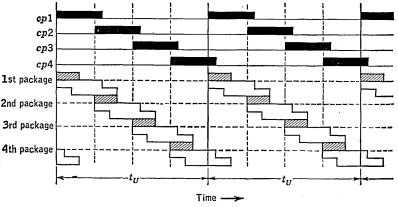

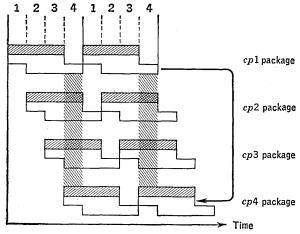

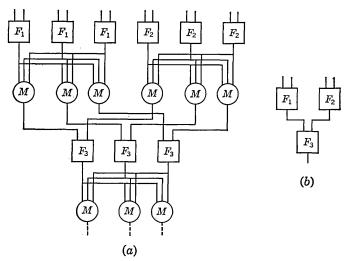

Part 4 is concerned with the logical design of specific computer components. First the serial arithmetic unit is considered, then parallel and rapid arithmetic operations. Since the philosophy of teaching general principles by specific example is used, a survey of methods of performing arithmetic operations is not given. Instead the discussions are centered round a few illustrations, carefully chosen for their suitability in demonstrating clearly the concepts involved in circuits that perform arithmetic operations. Next the various problems are considered that arise in the computation of control functions, beginning with a general discussion of minimum decoding procedures. Finally the concept of packaging is introduced, and with the logical design of the Pedagac as an illustrative example, many of the important aspects of the final logical design of a complete digital system are elucidated.

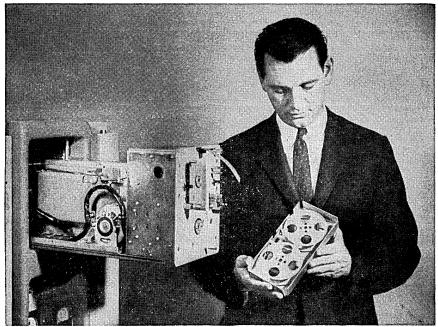

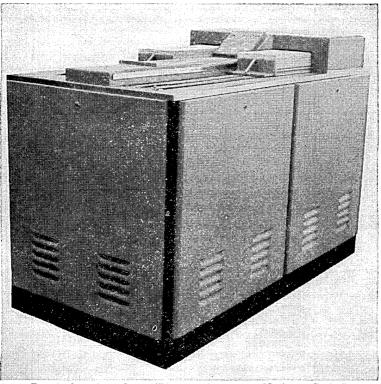

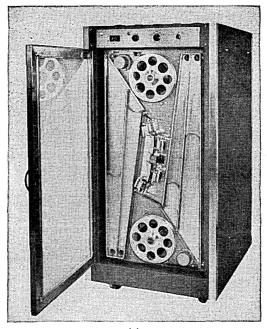

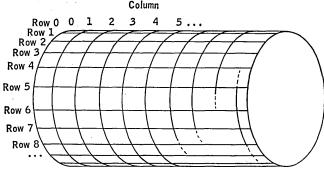

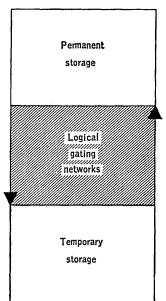

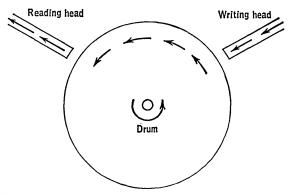

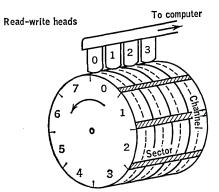

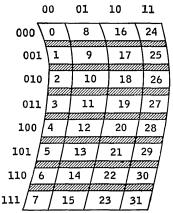

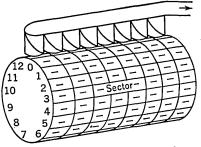

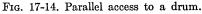

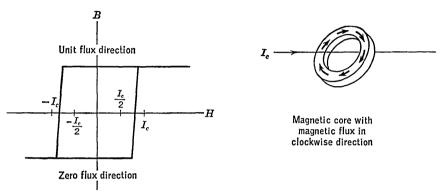

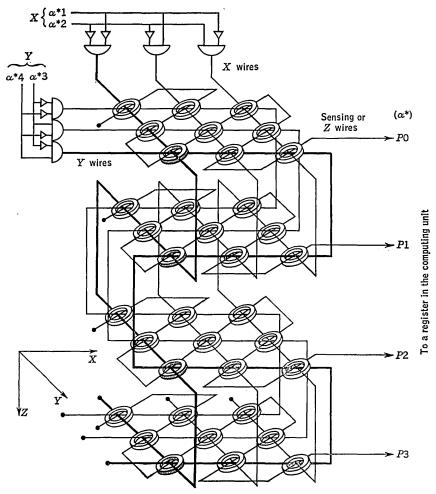

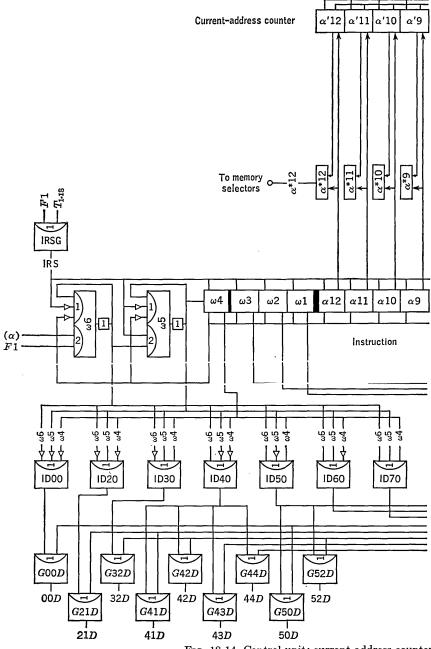

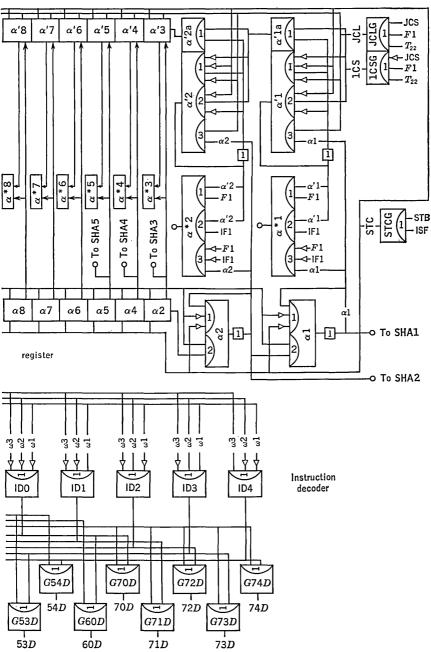

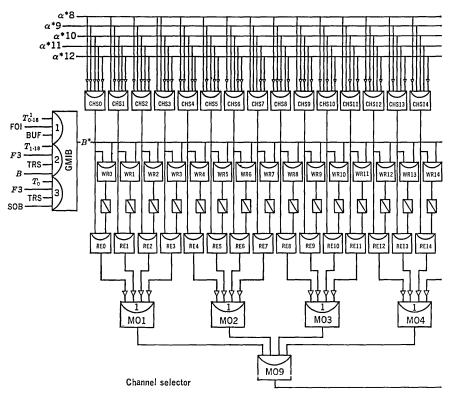

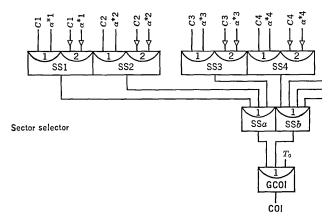

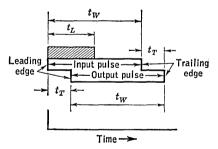

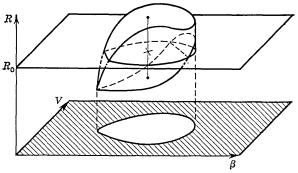

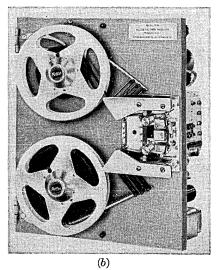

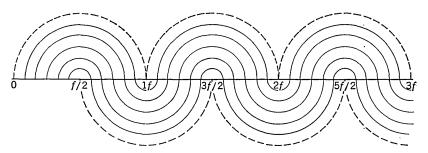

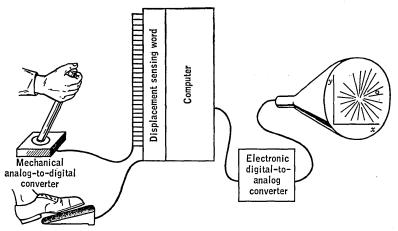

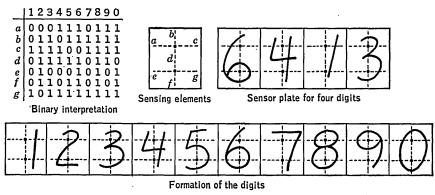

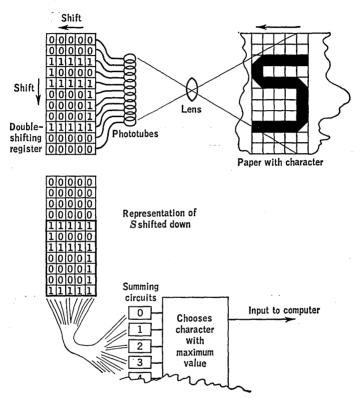

The last part. Part 5, is concerned with what is probably the most active field in digital-computer and -control engineering, the electronic design of digital circuits. The goals of the electronic design of circuits for use in digital computers and controls are derived from considerations of the digital-systems design and the logical design already covered. Here again the attempt is made to teach concepts through selected examples of circuits. Clearly, in these rapidly developing and dynamic fields, detailed discussions of many different specific circuits are not justified—many of them would certainly be obsolescent before publication of the book. Hence specific circuits are used only as concrete illustrations of the more general underlying principles. The experienced reader will observe that the topics covered in many of the individual sections can well afford entire books to themselves. The first chapter of this part is concerned with the two most important problems involved in the transition from abstract systems and logical design to the electronic realization of digital circuits, namely, timing, or clock phasing, and reliability. Then aspects of the use of semiconductor devices, diodes and transistors, in electronic-digital-circuit design are considered. Here the most important concept to be learned is a thorough understanding of the use of the devices; hence much space is devoted to discussion of the physical operation and the equivalent circuit of transistors. Consideration of magnetic elements in digital-circuit design follows, encompassing magnetic-core and multiaperture gating devices as well as magnetic amplifiers. The discussion ends with a section on two most promising modern circuit developments, Cryotron and microwave circuits. The next chapter is concerned with the closely related memory methods and input-output techniques. Only core and film high-speed memories are considered, since the use of other high-speed memory forms is rare; for the same reason only tape and drum low-speed memories are described. Many of the most important input-output methods depend on analog-to-digital and digital-to-analog conversion, and these are accordingly included in this chapter. In this context a full explanation of the important sampling theorem is given. The final chapter illustrates some exceedingly important topics in the final design of a computer, through the electronics and wiring diagram of the Pedagac.

Special Technical Features. In Part 1 of the text Sec. 5-9 is concerned with the International Algebraic Language (ALGOL). This general automatic algebraic programming language contains the primary features of other automatic programs, such as FORTRAN, IT, etc., and has the advantage of becoming widely accepted. Sponsored by the Association for Computing Machinery and several foreign societies, the universal acceptance of ALGOL would undoubtedly have a great beneficial effect on the national and international exchange of ideas and methods of programming.

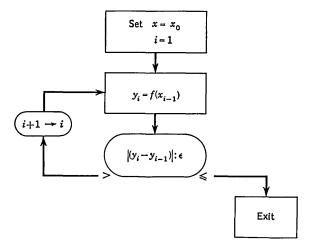

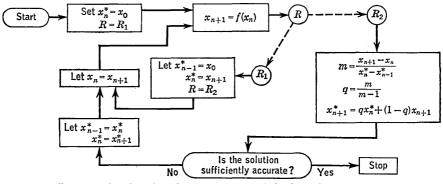

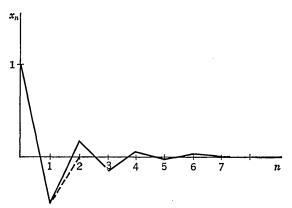

Special features of Part 2 include J. H. Wegstein's general method for accelerating the convergence of iterative solutions to equations, in Sec. 6-3. The Tabledex method and the techniques of searching with relaxed conditions given in Secs. 7-3 and 7-4, as well as the new, more accurate formulas for evaluating superimposed coding given in Sec. 7-7, are the original work of the author. The specific method of Sec. 8-3 for coding the control computer was developed by the author, while the method for coding the logistics and business computer, appearing in Sec. 8-5, is based on the work of W. H. Marlow.

In Part 3 the computational methods for constraints, logical dependence and independence, solution to Boolean algebraic equations, and transformation to the absolute simplest form, given in Secs. 12-2 through 12-10, are the author's original developments. The method of antecedence and consequence solutions, the fundamental Boolean matrix formulas and their proofs, given in Secs. 14-1 through 14-6, are the result of the author's original research, as are also the extension of the use of designation numbers to three (or more) -valued logic and their application to the design of three-valued digital circuits (Sec. 12-11). The extension of the fundamental Boolean matrix formulas to multivalued logic, as given in Sec. 14-7, was developed by W. R. Smith and N. F. J. Matthews; the general solution to the logical matrix equation given in that section was developed by W. R. Smith. R. D. Elbourn deserves credit for the direct method of finding prime implicants given in Sec. 11-7.

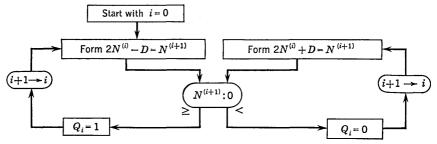

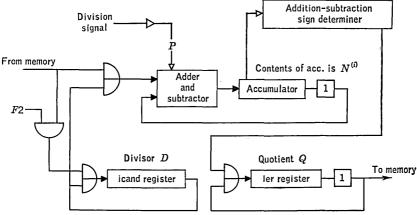

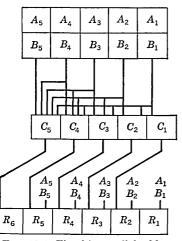

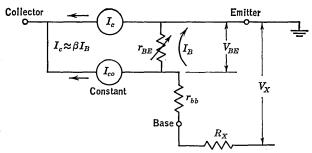

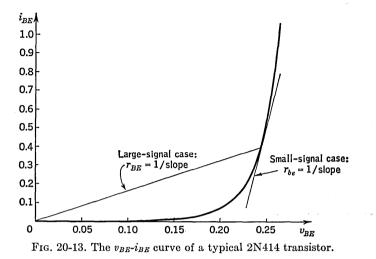

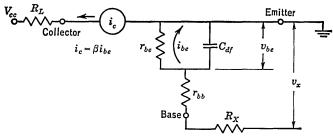

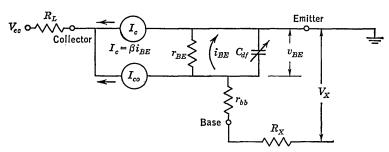

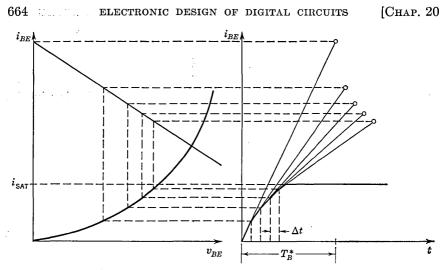

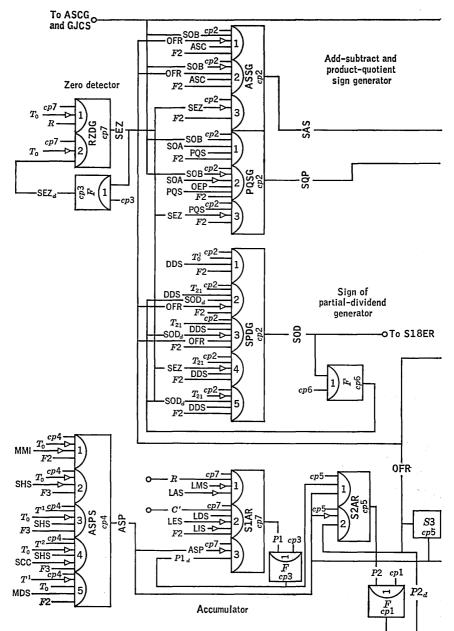

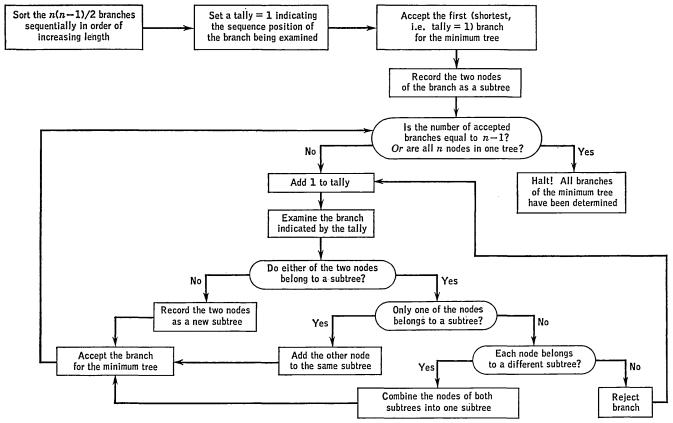

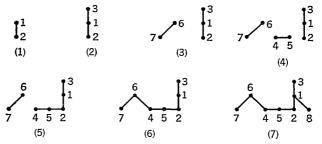

The discussions of the parallel adder and of rapid multiplication, in Secs. 16-2 and 16-4 of Part 4, are based on the work of A. Weinberger and J. L. Smith. The rapid-division method of Sec. 16-5 was developed by the author and J. B. Wilson. The treatment of minimum decoding methods is based on a development of C. H. Page. In Part 5 the probabilistic-logic approach to increasing circuit reliability (Sec. 19-4) is the author's adaptation of a development of W. S. McCulloch. The transistor equivalent circuit, described in Sec. 20-4 for the most commonly used grounded-emitter voltage-drive configuration, is based on an original development of S. B. Geller. The magnetic amplifier of E. W. Hogue in Sec. 21-3 presents a new technique for magnetic amplification. Section 23-4 on minimum-wiring theory is based on the works of H. Loberman and A. Weinberger.

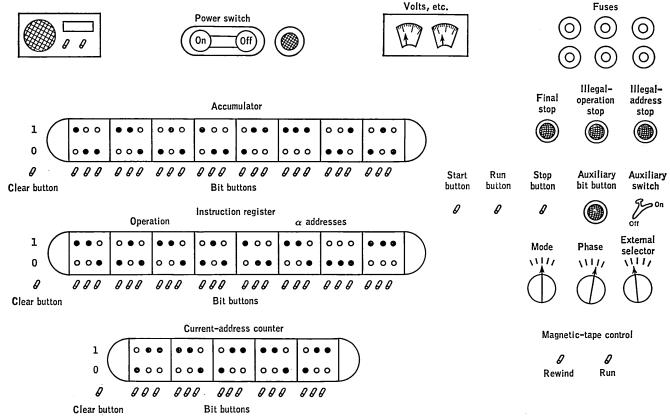

Special Pedagogical Feature: The Pedagac. It has been my experience that, although students might understand most of the various isolated aspects of computer engineering, they still might not visualize the complete process of designing and building a computer. In order to provide the necessary thread of continuity to the study of computer engineering, a simple computer, the Pedagac ("Pedagogic Automatic Computer") is designed from start to finish in the book (see Chaps. 9, 18, and 23). At

#### PREFACE

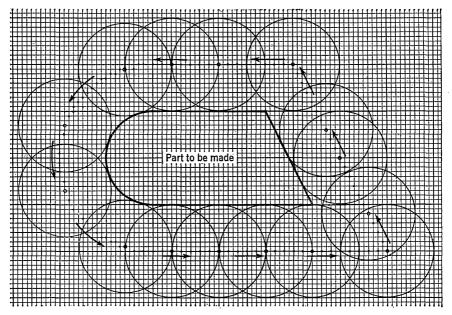

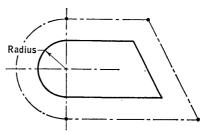

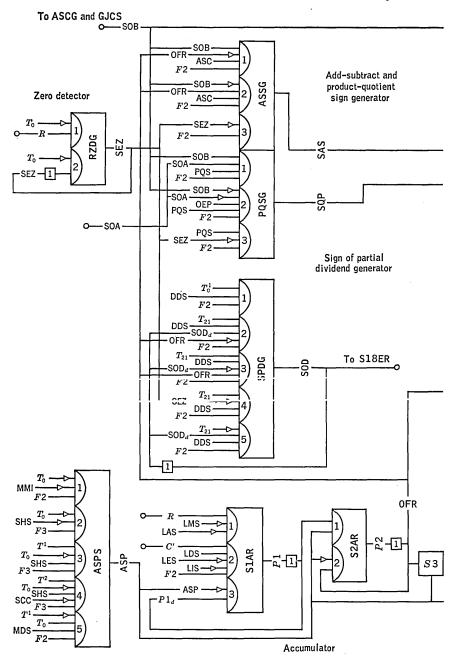

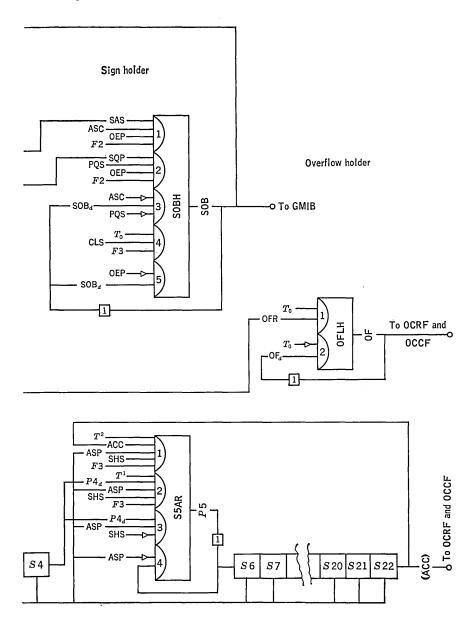

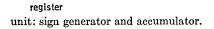

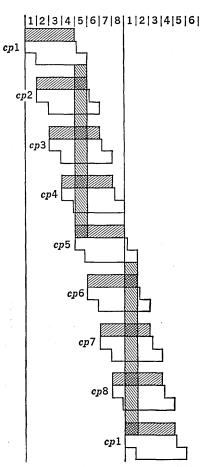

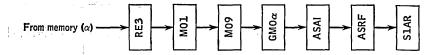

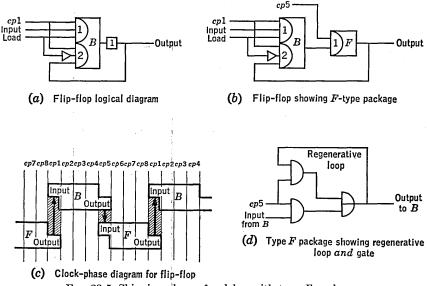

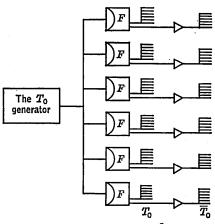

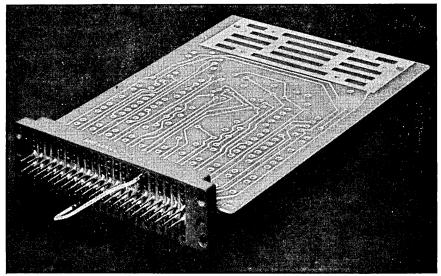

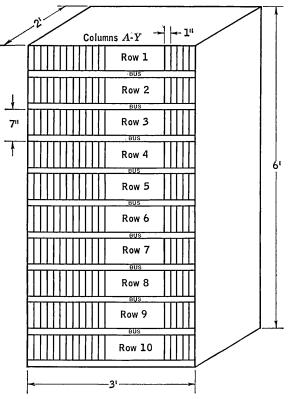

first glance the Pedagac may seem unduly specific. However, this is far from true, for the Pedagac serves as a concrete example by means of which many exceedingly important points are illustrated. Many of these points would be completely meaningless to the student if they were not developed in the context of an entire system. The Pedagac was specially designed to illustrate pertinent subject matter most clearly from a pedagogical (rather than cost or production, etc.) point of view. The arithmetic unit is serial, since a parallel arithmetic unit would have overwhelmed the student with primarily repetitive circuitry. The registers are static flip-flops, for these are the most easily understood in relation to arithmetic operations. The control is of a parallel nature, which is in general easier to comprehend. Eight clock phases are used to simplify the transition from logical to electronic design. The specially designed packages were made as simple in concept as possible.

Possible Course Structures. This text may be used for college courses in several different ways. For a *two-term* course the first term may cover Parts 1 and 2, and Part 3 through Chap. 12; the second term, the remainder of the book. Or the book may be used for a two-term composite elementary-advanced course: the elementary course may include much of the fundamentals of digital-computer engineering, and then those students who wish to pursue the subject in more detail may continue in the more advanced course. One suggested elementary course would consider Chaps. 1 to 4 of Part 1, Chaps. 6 and 7 of Part 2, Chaps. 10 and 11 of Part 3, Chaps. 15 and 16 of Part 4, and Chaps. 19 and 20 of Part 5; the more advanced course that follows would complete the text. A more leisurely treatment of the subject may be given in a *three-term* course. with more attention being paid to the selected readings and other projects and subjects mentioned in the Additional Topics sections. Here Parts 1 and 2 may be covered the first term, Part 3 the second term, and Parts 4 and 5 the third term. Other, perhaps quite eclectic, arrangements will certainly occur to the experienced instructor.

Acknowledgments. It gives me the greatest pleasure to acknowledge the help and cooperation I have received from many persons during the preparation of this book. My sincerest thanks go to James B. Wilson, who carefully and tirelessly edited the entire manuscript, contributing many important and valuable improvements to the style and technical presentation; to Louis S. Rotolo, who assisted in the designing of the Pedagac and with the Pedagac chapters, was extremely helpful in the preparation of the manuscript, and contributed many valuable suggestions; and to William R. Smith, who critically read the entire manuscript, prepared most of the technical illustrations, and helped in numerous other ways. I would like also to express my gratitude to R. D. Elbourn for reviewing the manuscript, making many constructive criticisms. The encouragement and support given by E. Frank and N. T. Grisamore have been greatly appreciated. Many colleagues helped by supplying advice and information on various technical points. Of these the author particularly wishes to mention A. Weinberger, J. A. Cunning-

#### PREFACE

ham, S. B. Geller, E. W. Hogue, J. H. Wegstein, the late M. Abramowitz, H. Loberman, S. Greenwald, E. R. Toense, W. W. Youden, J. L. Smith, D. R. Boyle, C. H. Page, W. H. Marlow, N. F. J. Matthews, and J. Rabinow. The author is indebted to G. U. Uyehara, N. T. Grisamore, and R. A. Toense for assisting in the design of the Pedagac package. The quality of the illustrations is in large part due to the skill and talent of J. E. Ozefovich, D. K. Anand, and A. Bucek, as well as W. R. Smith. The author wishes to thank Eva March Cuddy, Edna Crum, and Judith Holsberg for typing most of the manuscript. He gratefully acknowledges the partial support of the Mathematics Division of the Air Force Office of Scientific Research, Air Research and Development Command, and the Information Systems Branch of the Office of Naval Research, without which the preparation of the manuscript would have been impossible.

#### Robert Steven Ledley

·

.

·

.

.

. (

## CONTENTS

| Foreword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PART 1. INTRODUCTION TO DIGITAL PROGRAMMED SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Chapter 1. Applications of Digital Computers and Control 1                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>1-1. Introduction 1</li> <li>1-2. Numerical Solution to Equations 2</li> <li>1-3. Process Control 9</li> <li>1-4. Simulations 13</li> <li>1-5. Data Processing 18</li> <li>1-6. Additional Topics 23</li> </ul>                                                                                                                                                                                                                                                                                       |

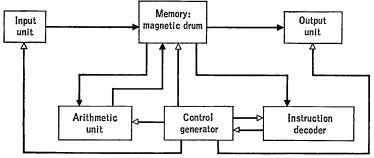

| Chapter 2. Principles and Block Diagram of a Digital Computer 25                                                                                                                                                                                                                                                                                                                                                                                                                                               |

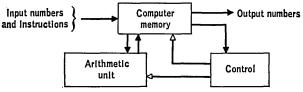

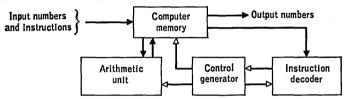

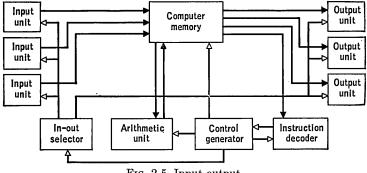

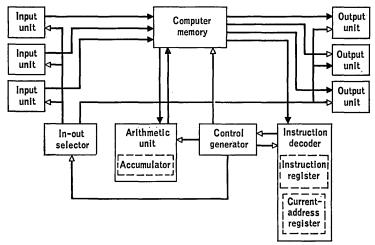

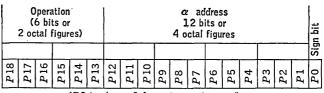

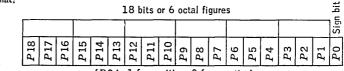

| <ul> <li>2-1. Introduction 25</li> <li>2-2. Block Diagram of a Computer 26</li> <li>2-3. Functional Description of a Computer 30</li> <li>2-4. Words and Pulses 34</li> <li>2-5. Logical Building Blocks 38</li> <li>2-6. Input, Output, and Memory Systems 44</li> <li>2-7. Digital-computer and -control Engineering 54</li> <li>2-8. Additional Topics 55</li> </ul>                                                                                                                                        |

| Chapter 3. Coding and Programming a Digital Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

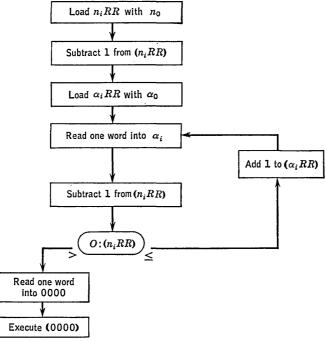

| <ul> <li>3-1. Introduction 60</li> <li>3-2. Number Systems: Conversion 62</li> <li>3-3. Number Systems: Arithmetic 69</li> <li>3-4. Coding: Sequences of Instructions 71</li> <li>3-5. Coding Decisions 76</li> <li>3-6. Coding: Flow Charting and Symbolic Code Aids 78</li> <li>3-7. Three-address Instruction Systems 81</li> <li>3-8. Two-address Instruction Systems 84</li> <li>3-9. One-address Instruction Systems 86</li> <li>3-10. Decimal Systems 90</li> <li>3-11. Additional Topics 92</li> </ul> |

| Chapter 4. Programming Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>4-1. Introduction 94</li> <li>4-2. Recursion Codes and Instruction Modification 95</li> <li>4-3. The Subroutine 104</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

CONTENTS

| 4-5.<br>4-6.<br>4-7.                                   | Instruction Types108Instruction Types (Continued)114Special Coding Techniques118The Control Panel124Additional Topics128                                                                                                                                         |     |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapte                                                 | er 5. Advanced Programming                                                                                                                                                                                                                                       | 130 |

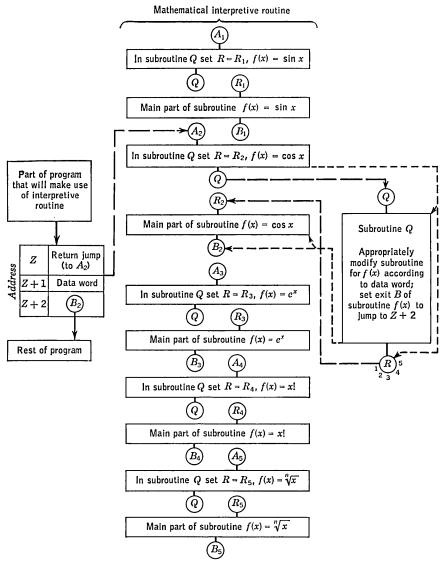

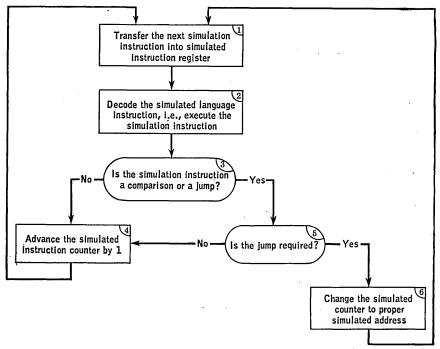

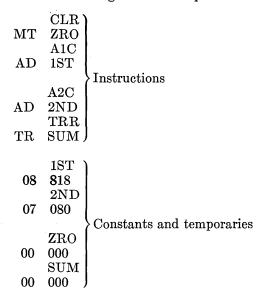

| 5-2.<br>5-3.<br>5-4.<br>5-5.                           | Introduction130Program Debugging Methods and Routines131Computer Maintenance Routines135Interpretive Routines: Mathematical139Interpretive Routines: Simulational142Memory Space, Speed of Computation, and Automatic Programming148                             |     |

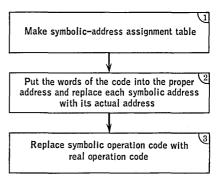

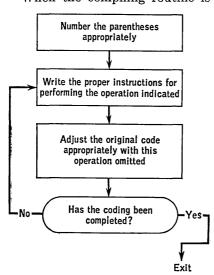

| 5-8.<br>5-9.                                           | Compiling Routines: Translator; Address Assigner150Compiling Routines: Algebraic155The International Algebraic Language (ALGOL)159Additional Topics171                                                                                                           |     |

|                                                        | PART 2. FUNCTIONAL APPROACH TO SYSTEMS DESIGN                                                                                                                                                                                                                    |     |

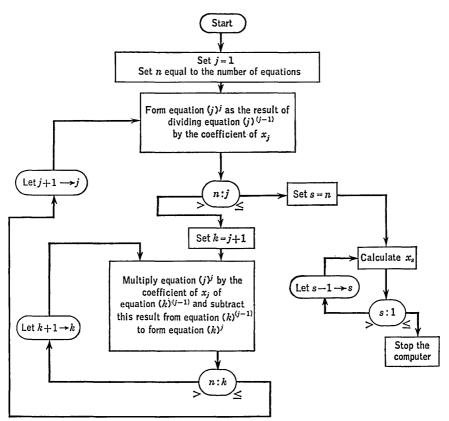

| Chapte                                                 | er 6. Fundamentals of Numerical Analysis                                                                                                                                                                                                                         | 173 |

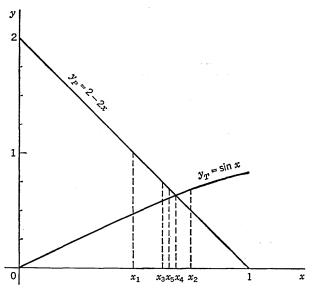

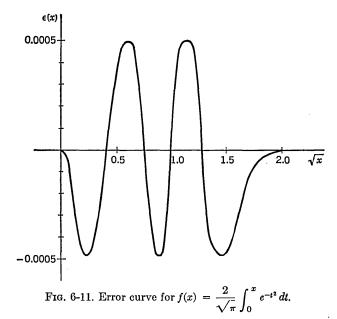

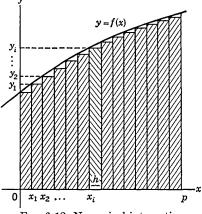

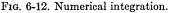

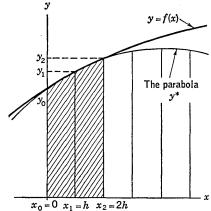

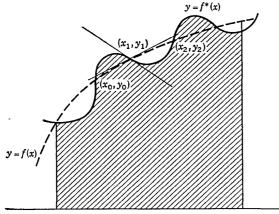

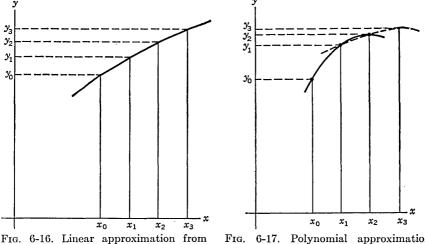

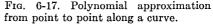

| 6-2.<br>6-3.                                           | Introduction173Simultaneous Linear Equations174Algebraic and Transcendental Equations178Function Evaluation: Series and Continued Fractions183                                                                                                                   |     |

| 6-5.<br>6-6.<br>6-7.<br>6-8.<br>6-9.<br>6-10.<br>6-11. | Function Evaluation: Interpolation 186<br>Function Evaluation: Best-fit Polynomial Approximation 190<br>Integration 193<br>Differentiation 196<br>Undetermined Coefficients 198<br>Differential Equations 200<br>Accuracy and Error 203<br>Additional Topics 211 |     |

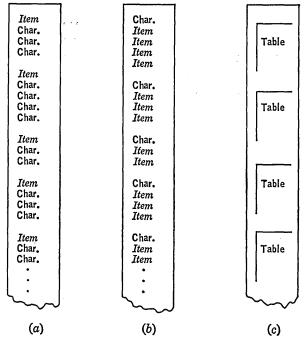

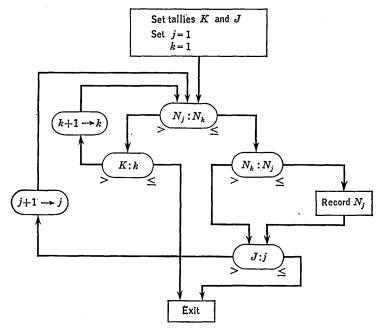

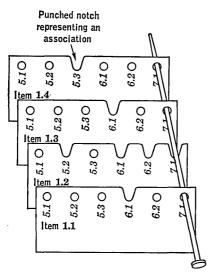

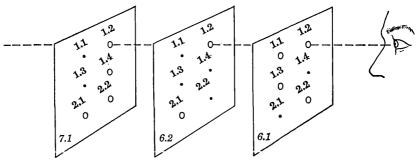

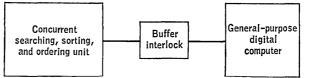

| Chapte                                                 | er 7. Searching, Sorting, Ordering, and Codifying                                                                                                                                                                                                                | 215 |

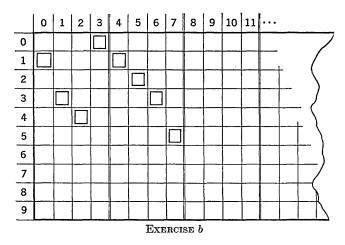

| 7-2.<br>7-3.<br>7-4.<br>7-5.<br>7-6.<br>7-7.           | Introduction215Methods of Searching218Manual Searching Methods223Searching with Relaxed Conditions226Sorting and Ordering230Ordering by Merging236Codifying: Error Correction and Superimposition242Additional Topics253                                         |     |

| Chapte                                                 | er 8. Special-purpose Digital-computer Systems Design                                                                                                                                                                                                            | 256 |

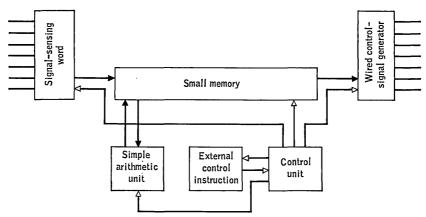

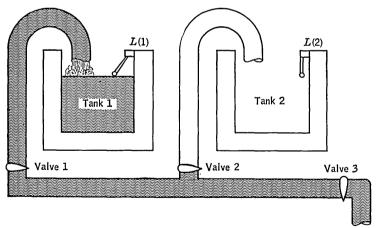

| 8-2.<br>8-3.                                           | Introduction 256<br>The Digital Differential Analyzer 257<br>Real-time Logical Systems Control: A Real-time Control Computer<br>262                                                                                                                              | •   |

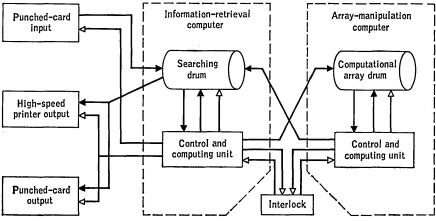

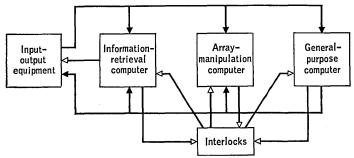

| 8-4.                                                   | Systems Design for Special-purpose Information-retrieval Computer 268                                                                                                                                                                                            |     |

٠

хx

|                                                                                                                                                          | CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XXI |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8-5.                                                                                                                                                     | Manipulations with Rectangular Arrays: A Business and Logistics Com-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 0.0                                                                                                                                                      | puter 271                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|                                                                                                                                                          | The Large-scale Data Processor     281       Additional Topics     286                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|                                                                                                                                                          | er 9. Systems Design of the Pedagac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 288 |

| •                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|                                                                                                                                                          | PART 3. FOUNDATIONS FOR THE LOGICAL DESIGN OF<br>DIGITAL CIRCUITRY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Chapte                                                                                                                                                   | er 10. Introduction to Boolean Algebra and Digital-computer Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 295 |

| 10-1.                                                                                                                                                    | Introduction 295                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 10-2.                                                                                                                                                    | Definition of Logic and Propositions 296                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 10-3.                                                                                                                                                    | Definition of Propositional Operations 297                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                          | Implication, Equivalence, and Tautology 299                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|                                                                                                                                                          | Truth Tables 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 10-6.                                                                                                                                                    | Boolean Algebra 302                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

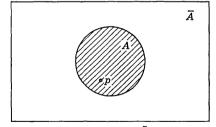

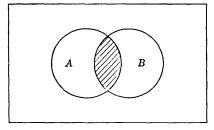

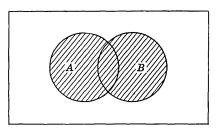

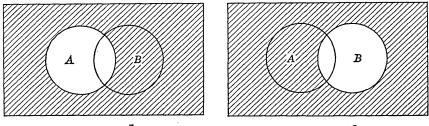

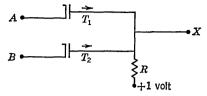

| 10-7.                                                                                                                                                    | Boolean Algebra as the Algebra of Sets 304                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

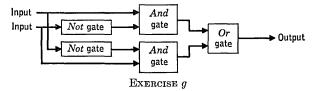

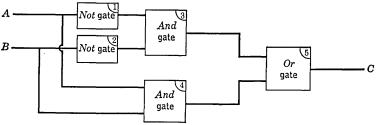

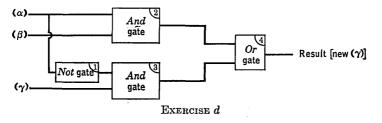

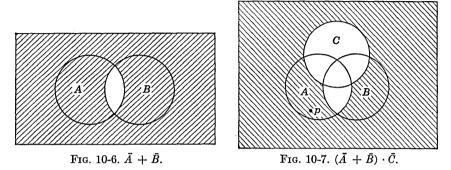

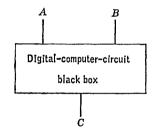

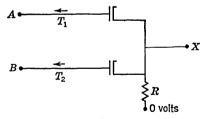

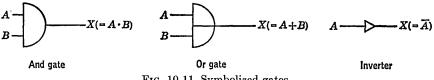

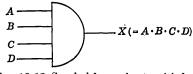

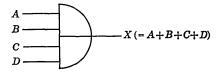

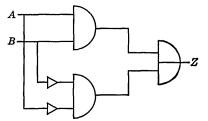

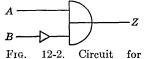

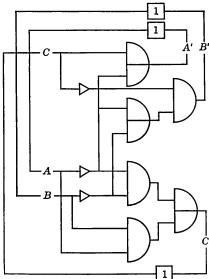

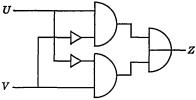

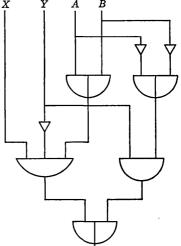

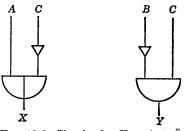

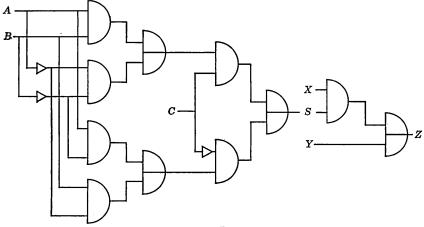

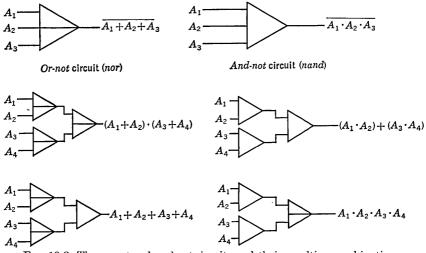

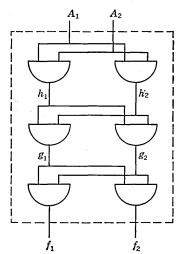

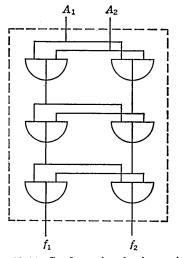

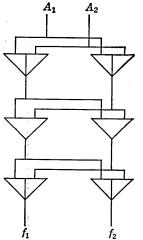

|                                                                                                                                                          | Digital-computer Circuits 306                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                                                                                                                                                          | Boolean Algebra as the Algebra of Digital-computer Circuits 308                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

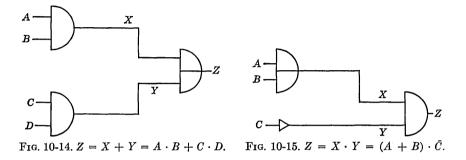

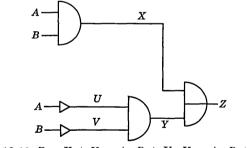

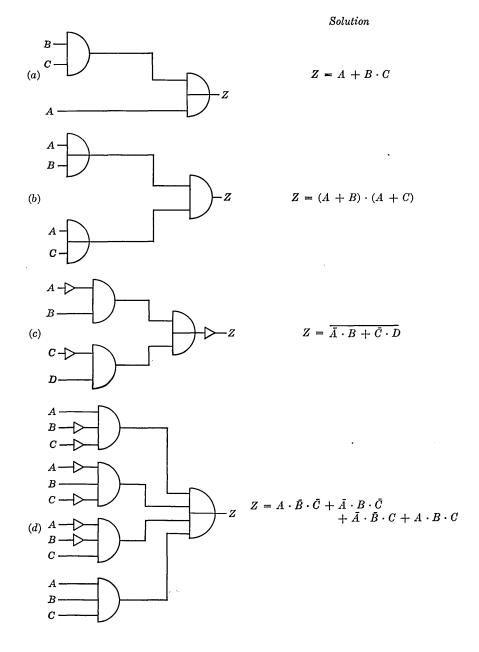

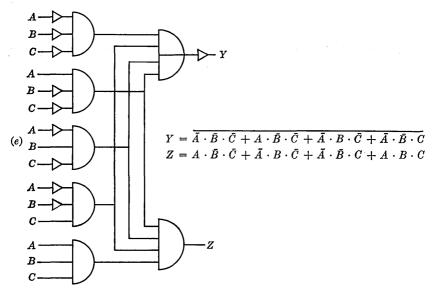

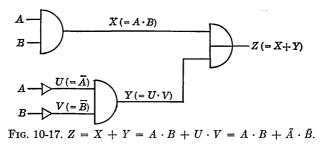

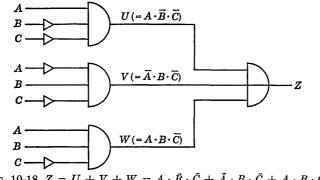

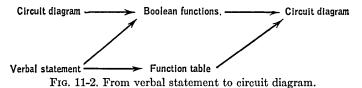

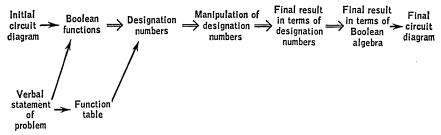

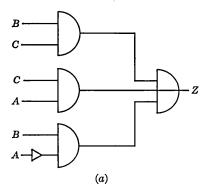

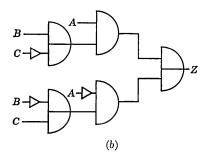

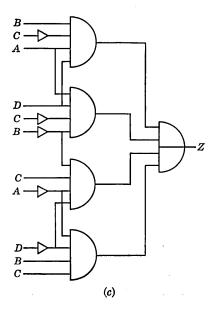

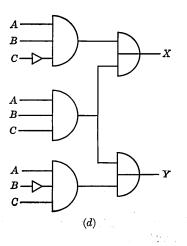

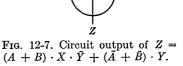

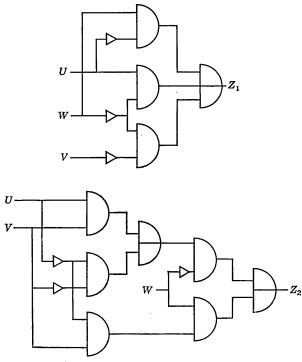

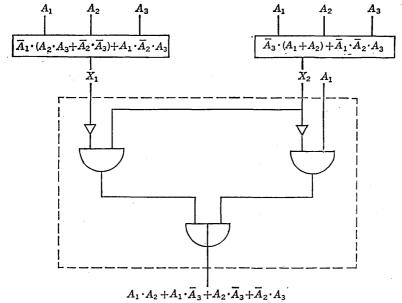

|                                                                                                                                                          | From Circuit Diagram to Boolean Function 309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|                                                                                                                                                          | From Boolean Function to Circuit Diagram 314                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|                                                                                                                                                          | Additional Topics 315                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ъ.  |

| 11-2.<br>11-3.<br>11-4.<br>11-5.<br>11-6.                                                                                                                | Introduction       320         The Designation Numbers       321         The First and Second Canonical Forms       324         Included and Nonincluded Elementary Elements       326         Mongrel Forms       329         Simulation Computation       321                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|                                                                                                                                                          | Simplest Sum-of-products Representation 331<br>Obtaining Essential Prime Implicants Directly 336                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 11-8.                                                                                                                                                    | Obtaining Essential Prime Implicants Directly 336<br>Simplification of Computer-circuit Design 344                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 11-8.<br>11-9.                                                                                                                                           | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

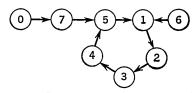

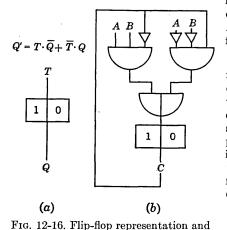

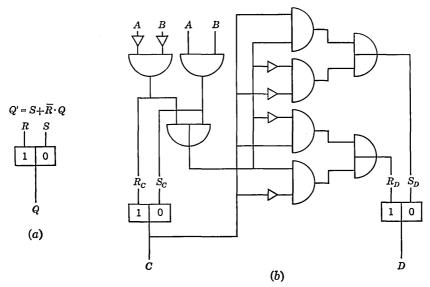

| 11-8.<br>11-9.<br>11-10.                                                                                                                                 | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •   |

| 11-8.<br>11-9.<br>11-10.<br>11-11.                                                                                                                       | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •   |

| 11-8.<br>11-9.<br>11-10.<br>11-11.                                                                                                                       | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •   |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.                                                                                                             | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br>Chapte                                                                                                   | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361                                                                                                                                                                                                                                                                                                                                                                                                                                          | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br>Chapte<br>12-1.                                                                                          | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361er 12. Elementary Computational Methods in Circuit Design                                                                                                                                                                                                                                                                                                                                                                                 | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br>Chapte<br>12-1.<br>12-2.                                                                                 | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361er 12. Elementary Computational Methods in Circuit Design.Introduction368Constraints368                                                                                                                                                                                                                                                                                                                                                   | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br>Chapte<br>12-1.<br>12-2.<br>12-3.                                                                        | Obtaining Essential Prime Implicants Directly       336         Simplification of Computer-circuit Design       344         The Design of Circuits That Compute Functions       346         Synchronous Recursive-function Circuits       351         The States of Circuits       356         Additional Topics       361         er 12. Elementary Computational Methods in Circuit Design       .         Introduction       368         Constraints       368         Logical Dependence and Independence       374                                                                                                                                                      | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br>Chapte<br>12-1.<br>12-2.<br>12-3.<br>12-4.                                                               | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361er 12. Elementary Computational Methods in Circuit Design.Introduction368Constraints368Logical Dependence and Independence374Constraints in Circuit Design376                                                                                                                                                                                                                                                                             | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-11.<br>11-12.<br>Chapte<br>12-1.<br>12-2.<br>12-3.<br>12-4.<br>12-5.                                            | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361er 12. Elementary Computational Methods in Circuit Design.Introduction368Constraints368Logical Dependence and Independence374Constraints in Circuit Design376                                                                                                                                                                                                                                                                             | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br>Chapte<br>12-1.<br>12-2.<br>12-3.<br>12-4.<br>12-5.<br>12-6.<br>12-7.                                    | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361er 12. Elementary Computational Methods in Circuit Design.Introduction368Constraints368Logical Dependence and Independence374Constraints in Circuit Design376Linear Boolean Equations379The General Method for Solution to Any Number of SimultaneousEquations in Any Number of Unknowns384Solution to Equations in Circuit Design389                                                                                                     | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br>Chapte<br>12-1.<br>12-2.<br>12-3.<br>12-4.<br>12-5.<br>12-6.<br>12-7.                                    | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361er 12. Elementary Computational Methods in Circuit Design.Introduction368Constraints368Logical Dependence and Independence374Constraints in Circuit Design376Linear Boolean Equations379The General Method for Solution to Any Number of Simultaneous<br>Equations in Any Number of Unknowns384                                                                                                                                           | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br><b>Chapte</b><br>12-1.<br>12-2.<br>12-3.<br>12-4.<br>12-5.<br>12-6.<br>12-7.<br>12-8.                    | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361er 12. Elementary Computational Methods in Circuit Design.Introduction368Constraints368Logical Dependence and Independence374Constraints in Circuit Design376Linear Boolean Equations379The General Method for Solution to Any Number of SimultaneousEquations in Any Number of Unknowns384Solution to Equations in Circuit Design389                                                                                                     | 368 |

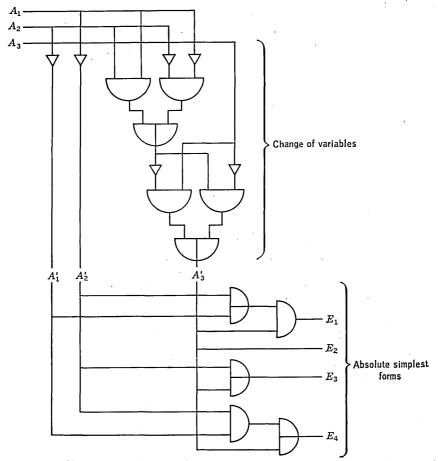

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br><b>Chapte</b><br>12-1.<br>12-2.<br>12-3.<br>12-4.<br>12-5.<br>12-6.<br>12-7.<br>12-8.<br>12-9.           | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361er 12. Elementary Computational Methods in Circuit Design.Introduction368Constraints368Logical Dependence and Independence374Constraints in Circuit Design376Linear Boolean Equations379The General Method for Solution to Any Number of SimultaneousEquations in Any Number of Unknowns384Solution to Equations in Circuit Design389The Absolute Simplest Form and Change of Variables393                                                | 368 |

| 11-8.<br>11-9.<br>11-10.<br>11-11.<br>11-12.<br><b>Chapte</b><br>12-1.<br>12-2.<br>12-3.<br>12-4.<br>12-5.<br>12-6.<br>12-7.<br>12-8.<br>12-9.<br>12-10. | Obtaining Essential Prime Implicants Directly336Simplification of Computer-circuit Design344The Design of Circuits That Compute Functions346Synchronous Recursive-function Circuits351The States of Circuits356Additional Topics361er 12. Elementary Computational Methods in Circuit Design.Introduction368Constraints368Logical Dependence and Independence374Constraints in Circuit Design376Linear Boolean Equations379The General Method for Solution to Any Number of SimultaneousEquations in Any Number of Unknowns384Solution to Equations in Circuit Design389The Absolute Simplest Form and Change of Variables393Transformation to the Absolute Simplest Form396 | 368 |

CONTENTS

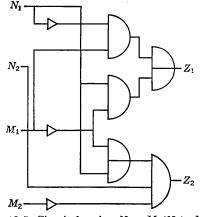

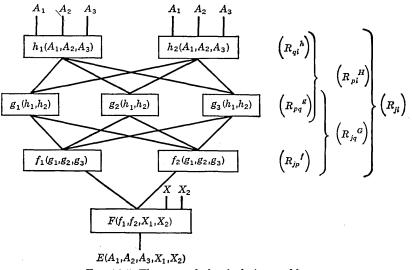

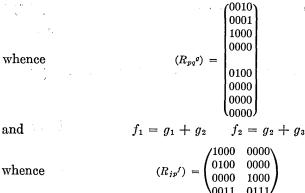

| Chapte                                    | r 13. Boolean Matrix Equations and the Fundamental Formulas                                                                                                                                                                                                                                                                                           | 414         |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

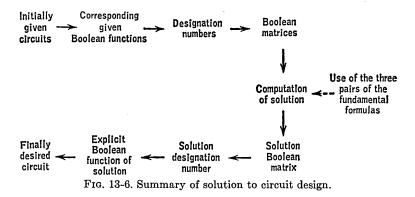

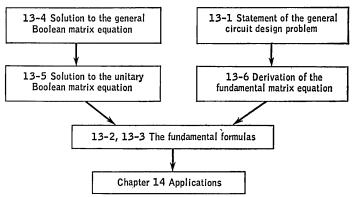

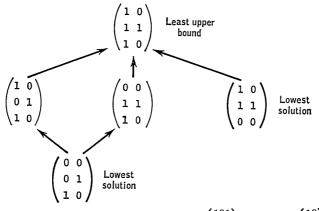

| 13-2.<br>13-3.<br>13-4.<br>13-5.<br>13-6. | Introduction and Statement of the Problem414Designation Numbers and Boolean Matrices419Antecedences and Consequences, and the Fundamental Formulas424Solution to the General Boolean Matrix Equation428Solution to the Unitary Matrix Equation434Derivation of the Fundamental Matrix Equation and the Fundamental<br>Formulas439Additional Topics441 |             |

| Chapter                                   | r 14. Applications of Matrix Equations in Circuit Design                                                                                                                                                                                                                                                                                              | <b>4</b> 48 |

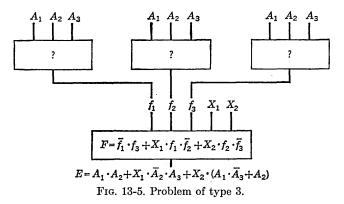

| 14-2.<br>14-3.<br>14-4.<br>14-5.<br>14-6. | Type 1 Problems in Circuitry448Type 2 Problems in Circuitry450Type 3 Problems in Circuitry453Constraints in the Problems462Ordinary Equations465More General Circuit-design Problems470Additional Topics476                                                                                                                                           |             |

| PAF                                       | RT 4. LOGICAL DESIGN OF DIGITAL-COMPUTER CIRCUITRY                                                                                                                                                                                                                                                                                                    | Y           |

| Chapter                                   | r 15. Serial Arithmetic Operations                                                                                                                                                                                                                                                                                                                    | 485         |

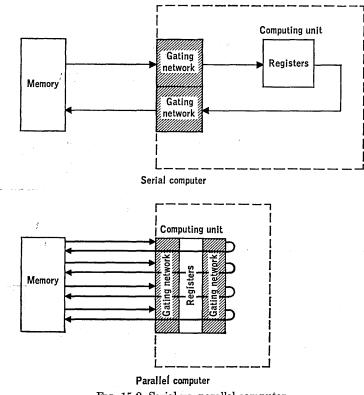

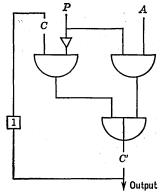

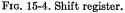

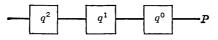

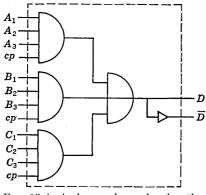

| 15-2.<br>15-3.<br>15-4.<br>15-5.<br>15-6. | Introduction485Common Computer Components487Common Computer Components (Continued)491Preliminaries to Synchronous Operation498Serial Arithmetic Unit: Addition and Subtraction502Serial Arithmetic Unit: Multiplication and Division511Additional Topics517                                                                                           |             |

| Chapter                                   | r 16. Parallel and Rapid Arithmetic Operations                                                                                                                                                                                                                                                                                                        | <b>5</b> 19 |

| 16-2. /<br>16-3. ]<br>16-4. ]<br>16-5. ]  | Introduction519The Parallel Adder: Logical Design519Parallel Arithmetic Units525Rapid Multiplication528Rapid Division533Floating Operations538Additional Topics540                                                                                                                                                                                    | · · · · ·   |

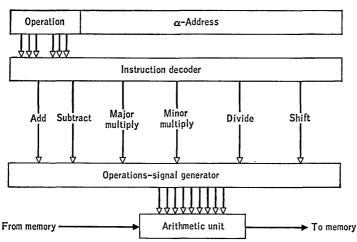

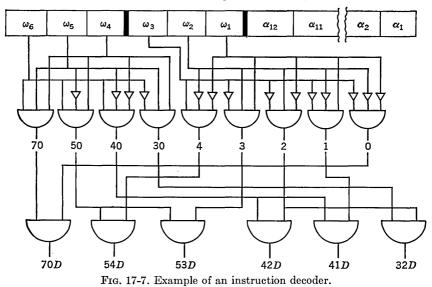

| Chapter                                   | r 17. Control                                                                                                                                                                                                                                                                                                                                         | 543         |

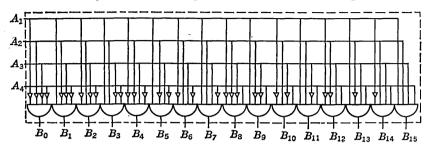

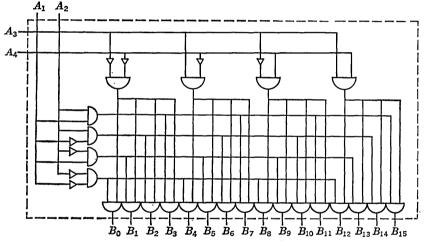

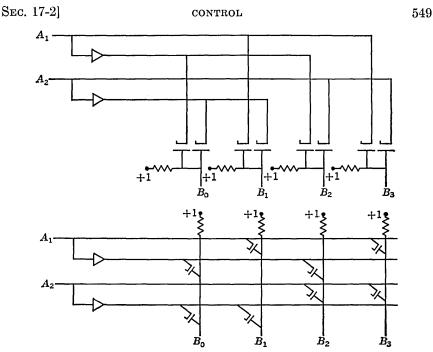

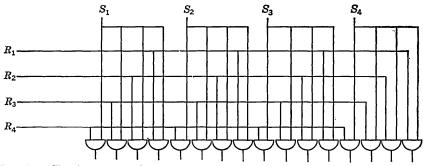

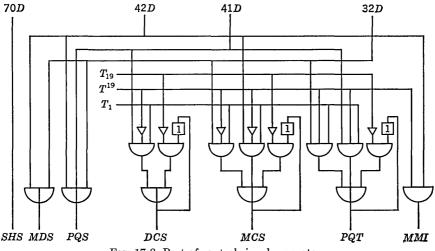

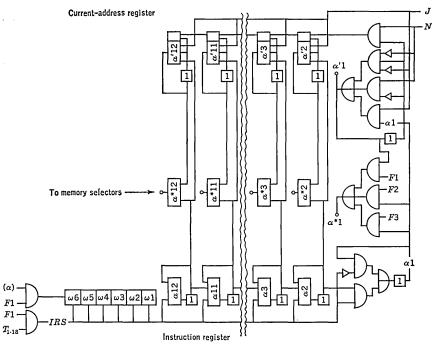

| 17-2.<br>17-3.                            | Introduction 543<br>The Decoding Circuit 547<br>Arithmetic Control: Instruction Decoder and Operations Signal Gener-<br>ator 553<br>Arithmetic Control: Internally Generated Signals and Register Con-                                                                                                                                                |             |

|                                           | trol 557                                                                                                                                                                                                                                                                                                                                              |             |

| 17-6. 1<br>17-7. (                        | Control of Memory Address Selection and Instruction Sequencing559Memory Selection562Control of Instruction Execution568Timing and Counters571                                                                                                                                                                                                         | •           |

xxii

|                                                             | CONTENTS                                                                                                                                                                                                                                                                                                                                        | xxiii       |