# Capability-Based Computer Systems

Henry M. Levy

Capability-Based Computer Systems

.

## Capability-Based Computer Systems

Henry M. Levy

Copyright © 1984 Digital Equipment Corporation

All rights reserved. Reproduction of this book, in part or in whole, is strictly prohibited. For copy information contact: Digital Press, 12 Crosby Dr., Bedford, Mass. 01730

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

Documentation Number: EY-00025-DP ISBN: 0-932376-22-3

#### Library of Congress Cataloging in Publication Data

Levy, Henry M., 1952-Capability-based computer systems.

Bibliography: p. 205 Includes index. 1. Computer architecture. 2. Operating systems (Computers) 3. System design. I. Title. QA76.9.A73L48 1983 621.3819'58 83-21029 ISBN 0-932376-22-3

#### Trademarks

Bell Laboratories: UNIX. Burroughs Corporation: B5000. Cambridge University: CAP. Control Data Corporation: CDC 6400, SCOPE. Digital Equipment Corporation: DEC, LSI-11, PDP-1, PDP-11, TOPS-20. Hewlett-Packard Company: HP 3000. Intel Corporation: iAPX 432, iMAX, Intel 8086. IBM: CPF, IBM 370, IBM System/38, SWARD. International Computers Ltd.: Basic Language Machine. Plessey Telecommunications Ltd. Plessey System 250. Xerox Corporation: Smalltalk. In Memory of Manny and Sonia

.

## Preface

The purpose of this book is to provide a single source of information about capability-based computer systems. Although capability systems have existed for nearly two decades, only recently have they appeared in architecture and operating system textbooks. Much has been written about capability systems in the technical literature, but finding this information is often difficult.

This book is an introduction, a survey, a history, and an evaluation of capability- and object-based computer systems. It is intended for students, computer professionals, and computer-system designers. The book assumes a knowledge of the assembly-level architecture of at least one computer, an understanding of memory addressing and virtual memory systems, and some familiarity with operating systems. It can be used as a tutorial or reference text in advanced undergraduate or graduate courses in computer organization, computer architecture, or operating systems.

Chapter 1 introduces the concept of a capability and examines the use of capabilities in computer systems. It compares and contrasts simplified models of capability and conventional addressing and protection systems. The object-based design methodology is introduced, and the use of capabilities to support object-based systems is discussed.

Chapter 2 describes machines that preceded the formal definition of capabilities but had similar addressing mechanisms. Developed in the late 1950s and early 1960s, these machines include the Burroughs B5000, the Rice University computer, and the Basic Language Machine. Chapter 3 examines the Dennis and Van Horn hypothetical supervisor that introduced the concept of capability, and the early university attempts to implement that concept: the MIT PDP-1 system, the Chicago Magic Number Machine, and the CAL-TSS system.

Chapter 4 describes the Plessey System 250. Built in the U.K., the Plessey 250 multiprocessor was the first commercially available capability-based computer system. Also built in the U.K., Cambridge University's CAP computer system, examined in Chapter 5, was the first successful university implementation of capability hardware.

Chapters 6 and 7 concentrate on two capability-based multiprocessor operating systems built at Carnegie-Mellon University: Hydra and STAROS. These systems were the first major object-based systems and used capabilities to provide objectlevel addressing and protection.

Chapters 8 and 9 examine the new generation of capability/ object-based systems designed for the commercial marketplace: the IBM System/38 and the Intel iAPX 432. The System/38 is the first use of object-based methodology to build a business-oriented computer system. The Intel 432 is the first highly-integrated object-based microprocessor. Both systems use object-based methodology to raise the level of the architecture interface. This allows them to support sophisticated operating-systems operations in hardware.

Chapter 10 reviews many of the important design issues in capability- and object-based systems in light of the implementations discussed throughout the book. Alternative implementation decisions and their implications are examined.

Each survey section presents the important features of a particular system. For this reason, different systems may be described at somewhat different levels. However, all systems are discussed in sufficient detail to give the reader an understanding of both the concepts and the low-level capability addressing and object-support mechanisms. An important goal of the book is examination of hardware and operating-system implementations of capabilities. Although all of the systems begin with a similar conceptual view of capabilities, the implementations are vastly different.

All attempts have been made to see that the system presentations are accurate, and most of the sections have been reviewed by one or more of the system's designers. Still, these discussions should not be taken as the final word and the interested reader is referred to the latest technical literature for more detailed study. Each section contains suggestions for further reading, and a complete bibliography on capability and object systems is included at the end of the book.

### Acknowledgments

I was fortunate to have as reviewers many of the creative people who helped design and build the systems described in the book. I would like to thank them for providing an interesting topic of study and for lending their valuable time. I was privileged to have the benefit of the technical and historical insight of Maurice Wilkes and Earl Van Horn. Pete Lee and Guy Almes provided detailed reviews (and re-reviews) of the entire manuscript. These contributed heavily to the book. I would like to thank the many other people who provided critiques of individual chapters.

This book is the result of a study that began when I was a Digital Equipment Corporation resident at the University of Washington. I would like to thank Bill Strecker for supporting my stay at Washington and for providing a creative working environment at Digital. Sam Fuller, Dieter Huttenberger, and Dick Eckhouse also helped to make the residency a success. At Washington, Guy Almes, Ed Lazowska, and John Bennett provided helpful reviews of early drafts of this work. Finally, I would like to thank Sandy Kaplan for her technical assistance, encouragement, patience, and humor that made the writing process more enjoyable.

### Contents

**1** Capability- and Object-Based System Concepts 1 Capability-Based Systems 3 Memory Addressing in Computer Systems 5 The Context of an Address 9 Protection in Computer Systems 10 The Object-Based Approach 13 Capabilities and Object-Based Systems - 15 Summary 17 For Further Reading 18 2 Early Descriptor Architectures 21 Introduction 21 The Burroughs B5000 22 The Rice University Computer 25 The Basic Language Machine 30 Discussion 34 For Further Reading 38 **3** Early Capability Architectures 41 Introduction 41 Dennis and Van Horn's Supervisor 41 The MIT PDP-1 Timesharing System 47 The Chicago Magic Number Machine 48 The CAL-TSS System 52 Discussion 57 For Further Reading 61 The Plessey System 250 65 4 Introduction 65

xi

|   | System Overview 66<br>Capability Addressing 66<br>Capability Register Usage 69<br>Inform and Outform Capabilities 69<br>Instructions and Addressing 71<br>Protected Procedure Calls 72<br>Operating System Resource Management 73                                                                                                                                              |     |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | Input and Output 74<br>Discussion 75<br>For Further Reading 77                                                                                                                                                                                                                                                                                                                 |     |

| 5 | The Cambridge CAP Computer                                                                                                                                                                                                                                                                                                                                                     | 79  |

| 5 | Introduction 79<br>Hardware Overview 79<br>CAP Process Structure 80<br>CAP Addressing Overview 81<br>Capabilities and Virtual Addresses 83<br>Process Data Structures 85<br>Memory Address Evaluation 86<br>Subprocess Creation 87<br>The Capability Unit 89<br>Protected Procedures 90<br>Long-Term Storage and Long-Term Names 95<br>Discussion 96<br>For Further Reading 99 |     |

| 6 | The Hydra System                                                                                                                                                                                                                                                                                                                                                               | 103 |

| • | Introduction 103<br>Hydra Overview 103<br>Hydra Objects and Types 105                                                                                                                                                                                                                                                                                                          |     |

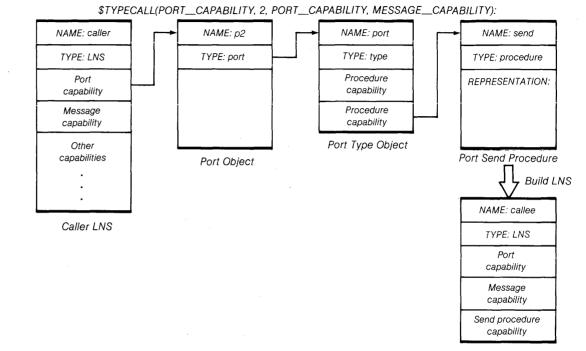

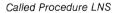

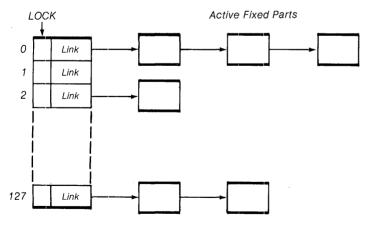

|   | Processes, Procedures, and Local Name Spaces<br>Hydra Operations 109<br>Capabilities and Rights 111<br>Supporting Protected Subsystems 113<br><i>Templates</i> 113<br><i>Typecalls</i> 116<br>Hydra Object Storage System 116<br>Capability Representation 120<br>Reference Counts and Garbage Collection 121                                                                  | 107 |

|   | Discussion 122<br>For European Panding 125                                                                                                                                                                                                                                                                                                                                     |     |

|   | For Further Reading 125                                                                                                                                                                                                                                                                                                                                                        |     |

| 7 | The STAROS System                                                                                                                                                                                                                                                                                                                                                              | 127 |

|   | Overview of STAROS 127<br>STAROS Object Support 129                                                                                                                                                                                                                                                                                                                            |     |

xii

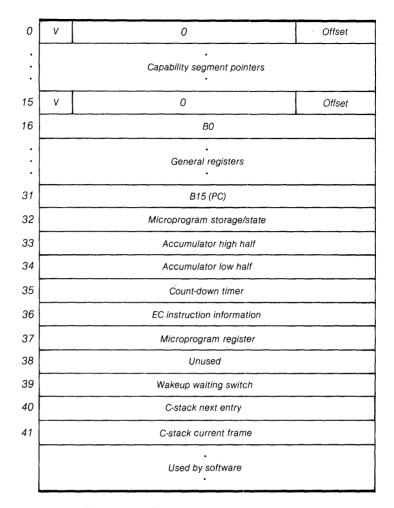

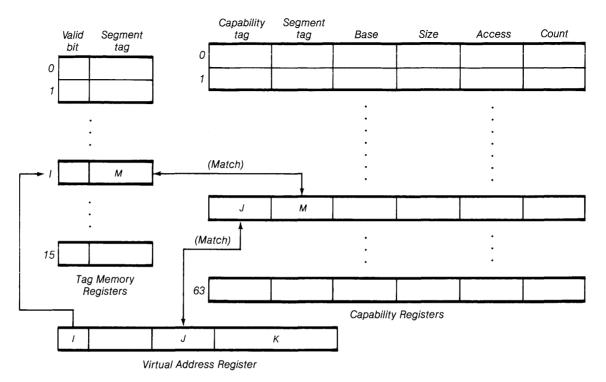

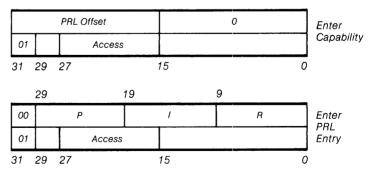

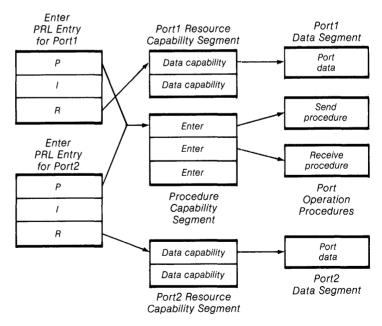

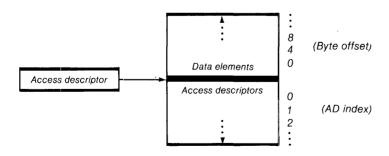

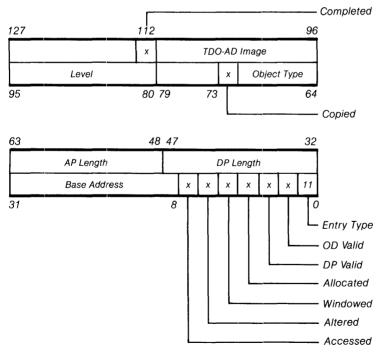

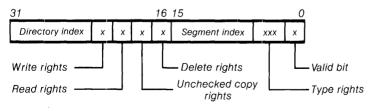

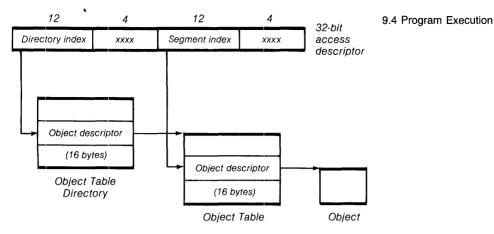

**STAROS Capabilities** 130 Object Addressing 131 STAROS Abstract Type Management 133 Discussion 134 For Further Reading 135 The IBM System/38 137 Introduction 137 System Objects 139 Object Addressing 141 Virtual Memory 141 Pointers 142 Contexts 144 Physical Address Mapping 145 Profiles and Authority 147 Authority/Pointer Resolution 148 Programs/Procedures 150 The Instruction Stream 151 Program Activation and Invocation 152 Protected Procedures 153 Special Privileges 154 Discussion 154 For Further Reading 157 The Intel iAPX 432 159 Introduction 159 Segments and Objects 161 Object Addressing 163 **Object** Descriptors 163 Access Descriptors 165 **Program Execution** 167 Domains and Instruction Objects 168 Procedure Call and Context Objects 169 Instruction Operand Addressing 171 Context Allocation 172 Parameter Passing 173 Abstraction Support 173 Domains and Refinements 174 Creation of Typed Objects 176 Programmer-Defined Types 177 Storage Resources 179 Instructions 182 Discussion 184 For Further Reading 186

8

9

Contents

xiii

Capability and Object System Bibliography 205

Index

217

#### **Figures**

- 1-1. A Capability 3

- 1-2. Conventional Segment Address Translation 6

- 1-3. Capability Register Addressing 7

- 1-4. System Object Access Matrix 11

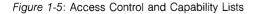

- 1-5. Access Control and Capability Lists 11

- 2-1. B5000 Program Reference Table 23

- 2-2. B5000 Descriptor Formats 24

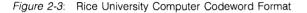

- 2-3. Rice University Computer Codeword Format 27

- 2-4. Rice University Computer Memory Organization 29

- 2-5. Example of BLM Numeric Formats 32

- 2-6. Basic Language Machine Addressing 33

- 2-7. BLM Address and Codeword Formats 34

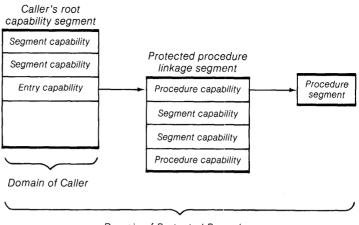

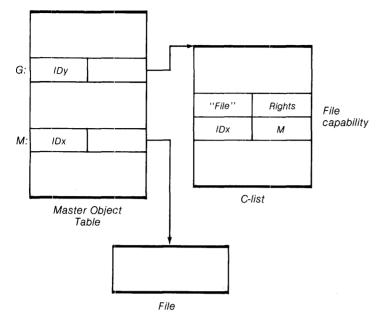

- 3-1. Processes, Computations, and C-lists 43

- 3-2. Protected Procedure Protection Spheres 46

- 3-3. Chicago Magic Number Machine Linkage Segment 52

- 3-4. CAL-TSS Object Addressing 55

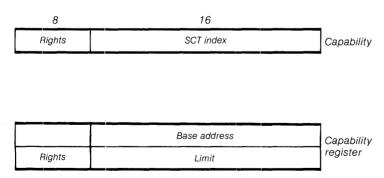

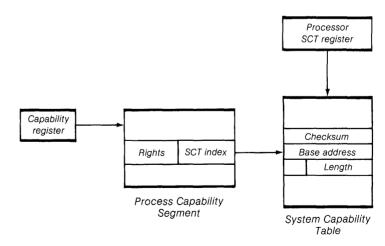

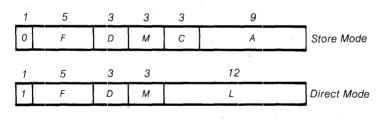

- 4-1. Plessey System 250 Capability Formats 67

- 4-2. Plessey System 250 Capability Loading 68

- 4-3. System 250 Instruction Formats 71

- 4-4. Protected Procedure Resource Subsystem 74

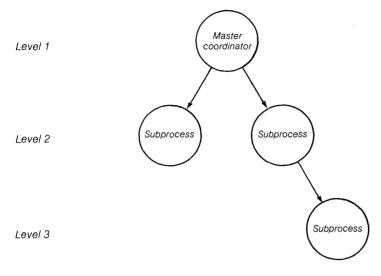

- 5-1. CAP Process Hierarchy 81

- 5-2. CAP Process Addressing 82

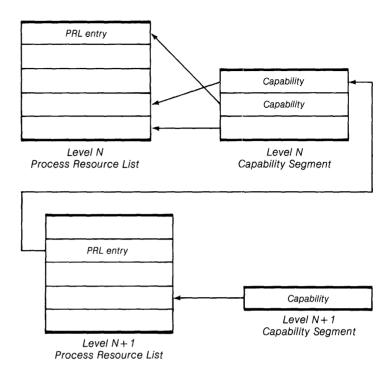

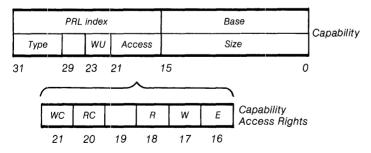

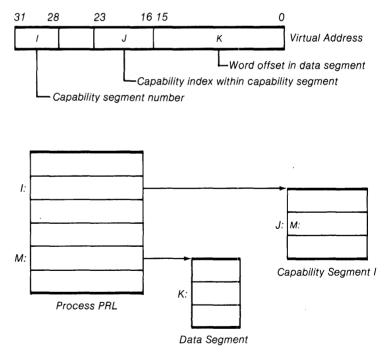

- 5-3. CAP Capability and Access Rights Formats 83

- 5-4. CAP Virtual Address 84

- 5-5. CAP PRL Entry 85

- 5-6. CAP Process Base 86

- 5-7. Capability Unit Register Format 89

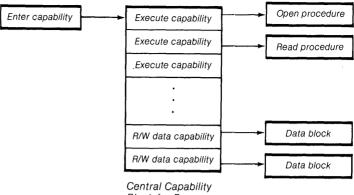

- 5-8. CAP Capability Unit 91

- 5-9. CAP Enter Capability and Enter PRL Formats 92

- 5-10. CAP Protected Object Implementation 94

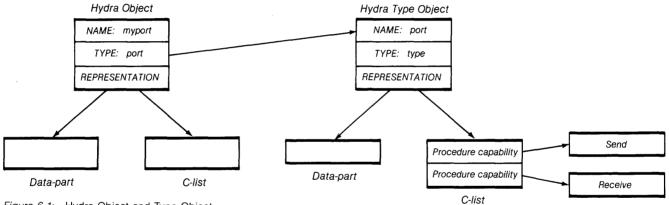

- 6-1. Hydra Object and Type Object 106

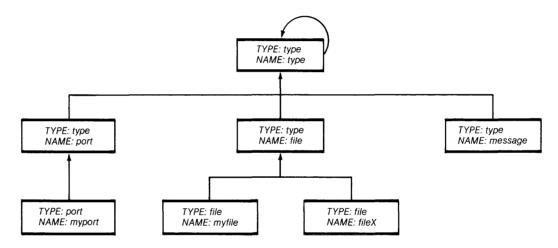

- 6-2. Hydra Type Hierarchy 108

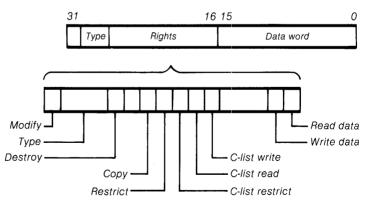

- 6-3. Hydra Capability 111

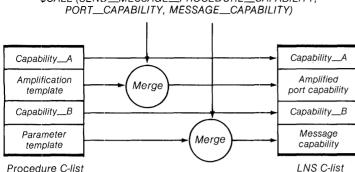

- 6-4. Hydra Procedure Call 115

- 6-5. Hydra TypeCall 117

- 6-6. Active Fixed Part Directory 119

- 6-7. Hydra Capability Formats 121

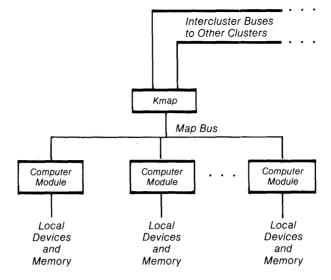

- 7-1. A CM\* Cluster 128

- 7-2. STAROS Capability and Capability Rights Word 130

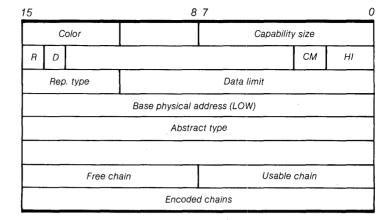

- 7-3. STAROS Object Descriptor Format 132

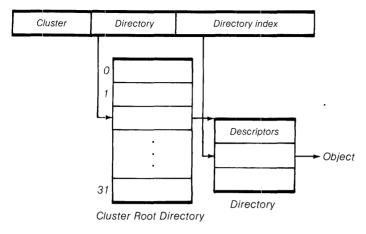

- 7-4. STAROS Directory Structure 133

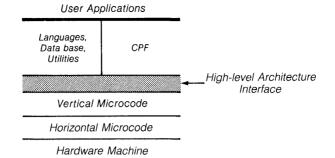

- 8-1. System/38 Implementation Layers 138

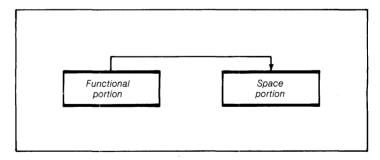

- 8-2. IBM System/38 System Object 140

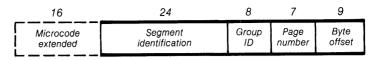

- 8-3. System/38 Virtual Address 142

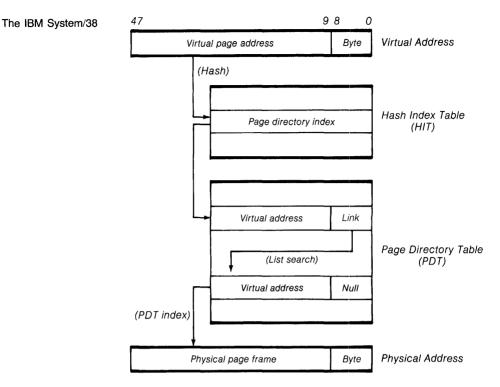

- 8-4. System/38 Virtual Address Translation 146

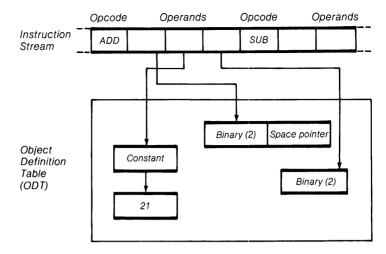

- 8-5. System/38 Example High-level Instruction 152

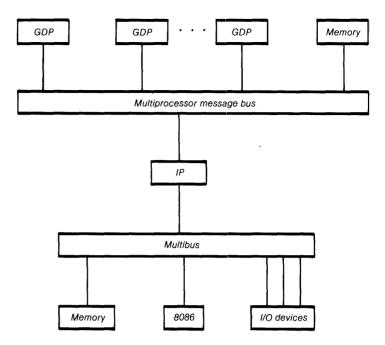

- 9-1. Intel iAPX 432 Structure 160

- 9-2. Intel 432 Segment 161

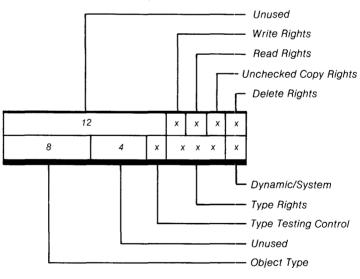

- 9-3. Intel 432 Storage Segment Descriptor 163

- 9-4. Intel 432 Access Descriptor 165

- 9-5. Intel 432 Address Translation 167

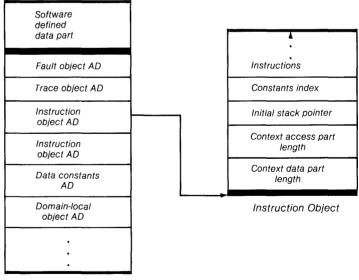

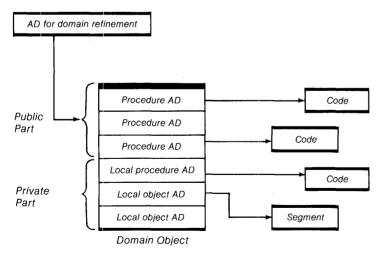

- 9-6. Intel 432 Domain and Instruction Objects 168

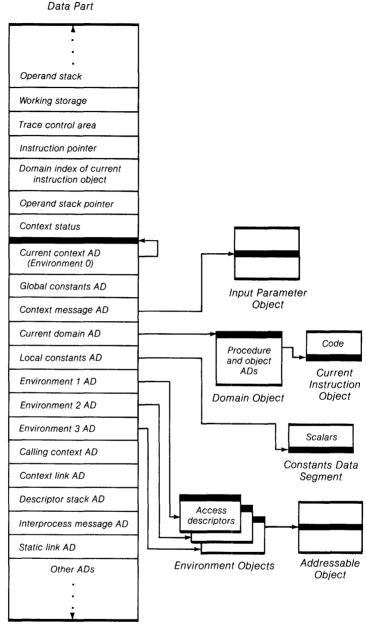

- 9-7. Intel 432 Context Object Representation 170

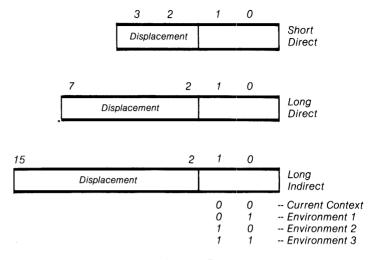

- 9-8. Intel 432 Access Selector Formats 172

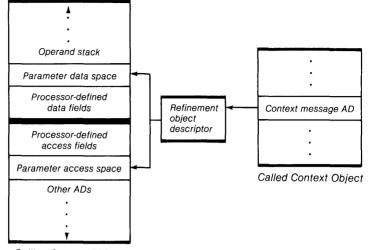

- 9-9. Intel 432 Parameter Passing 174

- 9-10. Intel 432 Domain Refinement 175

- 9-11. Intel 432 Type Control Object Data Part 176

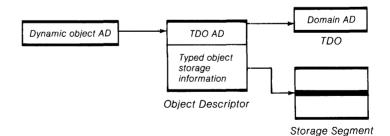

- 9-12. Intel 432 Dynamic Object Addressing 178

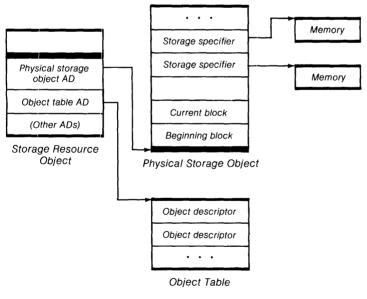

- 9-13. Intel 432 Storage Resource Object 179

- 9-14. Intel 432 Instruction Format 182

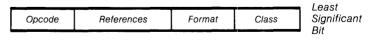

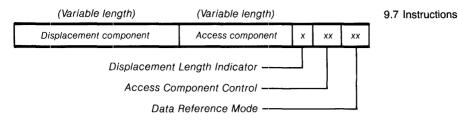

- 9-15. Intel 432 Reference Format 183

#### Tables

- 1-1. Major Descriptor and Capability Systems 2

- 3-1. Dennis and Van Horn Supervisor Capability Operations 44

- 3-2. Chicago Magic Number Supervisor Capability Operations 51

Contents

- 6-1. Hydra Kernel-Implemented Types 107

- 6-2. Generic Object and Capability Operations 110

- 6-3. Capability and Generic Object Access Rights 111

- 6-4. Hydra Active and Passive Fixed Parts 118

- 7-1. STAROS Representation Types 129

- 7-2. STAROS Capability Types 131

- 8-1. System/38 System Object Types 139

- 8-2. System/38 Pointer Instructions 144

- 8-3. System/38 Context Instructions 145

- 8-4. System/38 Authority Management Instructions 149

- 9-1. Intel 432 System Object Types 162

- 9-2. Intel 432 Storage Segment Descriptor Fields 164

- 9-3. Intel 432 Access Descriptor Instructions 166

xvi

Capability-Based Computer Systems

.

### Capability- and Object-Based System Concepts

Although the complexity of computer applications increases yearly, the underlying hardware architecture for applications has remained unchanged for decades. It is, therefore, not surprising that the demands of modern applications have exposed limitations in conventional architectures. For example, many conventional systems lack support in:

- 1. Information sharing and communications. An essential system function is the dynamic sharing and exchange of information, whether on a timesharing system or across a network. Fundamental to the sharing of storage is the addressing or naming of objects. Sharing is difficult on conventional systems because addressing is local to a single process. Sharing would be simplified if addresses could be transmitted between processes and used to access the shared data.

- 2. Protection and security. As information sharing becomes easier, users require access controls on their private data. It must also be possible to share information with, or run programs written by, other users without compromising confidential data. On conventional systems, all of a user's objects are accessible to any program which the user runs. Protection would be enhanced if a user could restrict access to only those objects a program requires for its execution.

- 3. Reliable construction and maintenance of complex systems. Conventional architectures support a single privileged mode of operation. This structure leads to monolithic design; any module needing protection must be part of the single operating system kernel. If, instead, any module could execute within a protected domain, systems could be built as a collection of independent modules extensible by any user.

1

Over the last several decades, computer industry and university scientists have been searching for alternative architectures that better support these essential functions. One alternative architectural structure is *capability-based* addressing. Capability-based systems support the *object-based* approach to computing.

This book explains the capability/object-based approach and its implications, and examines the features, advantages, and disadvantages of many existing designs. Each chapter presents details of one or more capability-based systems. Table 1-1 lists the systems described, where they were developed, and when they were designed or introduced.

| System                                    | Developer                                                   | Year | Attributes                                                          |

|-------------------------------------------|-------------------------------------------------------------|------|---------------------------------------------------------------------|

| Rice University<br>Computer               | Rice University                                             | 1959 | segmented memory<br>with "codeword"<br>addressing                   |

| Burroughs B5000                           | Burroughs Corp.                                             | 1961 | stack machine with descriptor addressing                            |

| Basic Language<br>Machine                 | International<br>Computers Ltd., U.K.                       | 1964 | high-level machine with codeword addressing                         |

| Dennis and Van<br>Horn Supervisor         | MIT                                                         | 1966 | conceptual design for<br>capability supervisor                      |

| PDP-1 Time-<br>sharing System             | MIT                                                         | 1967 | capability supervisor                                               |

| Multicomputer/<br>Magic Number<br>Machine | University of<br>Chicago Institute<br>for Computer Research | 1967 | first capability<br>hardware system<br>design                       |

| CAL-TSS                                   | U.C. Berkeley<br>Computer Center                            | 1968 | capability operating system for CDC 6400                            |

| System 250                                | Plessey Corp., U.K.                                         | 1969 | first industrial<br>capability hardware<br>and software system      |

| CAP Computer                              | University of<br>Cambridge, U.K.                            | 1970 | capability hardware<br>with microcode support                       |

| Hydra                                     | Carnegie-Mellon<br>University                               | 1971 | object-based multi-<br>processor O.S.                               |

| STAROS                                    | Carnegie-Mellon<br>University                               | 1975 | object-based multi-<br>processor O.S.                               |

| System/38                                 | IBM, Rochester, MN.                                         | 1978 | first major commercial<br>capability system,<br>tagged capabilities |

| iAPX 432                                  | Intel, Aloha, OR.                                           | 1981 | highly-integrated<br>object-based micro-                            |

Before surveying these systems at a detailed architectural level, it is useful to introduce the concepts of capabilities and object-based systems. This chapter defines the concept of capability, describes the use of capabilities in memory addressing and protection, introduces the object-based programming approach, and relates object-based systems to capability-based addressing.

Simplified examples of capability-based and conventional computer systems are presented throughout this chapter. These examples are meant to introduce the capability model by contrasting it with more traditional addressing mechanisms. In fact, many design choices are possible in both domains, and many conventional systems exhibit some of the properties of capability systems. No one of the following models is representative of all capability or conventional systems.

#### 1.1 Capability-Based Systems

Capability-based systems differ significantly from conventional computer systems. Capabilities provide (1) a single mechanism to address both primary and secondary memory, and (2) a single mechanism to address both hardware and software resources. While solving many difficult problems in complex system design, capability systems introduce new challenges of their own.

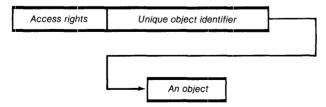

Conceptually, a capability is a token, ticket, or key that gives the possessor permission to access an entity or object in a computer system. A capability is implemented as a data structure that contains two items of information: a *unique object identifier* and *access rights*, as shown in Figure 1-1.

The identifier *addresses* or *names* a single object in the computer system. An object, in this context, can be any logical or physical entity, such as a segment of memory, an array, a file, a

Figure 1-1: A Capability

#### Capability- and Object-Based System Concepts

line printer, or a message port. The access rights define the *operations* that can be performed on that object. For example, the access rights can permit read-only access to a memory segment or send-and-receive access to a message port.

Each user, program, or procedure in a capability system has access to a *list of capabilities*. These capabilities identify all of the objects which that user, program, or procedure is permitted to access. To specify an object, the user provides the *index* of a capability in the list. For example, to output a record to a file, the user might call the file system as follows:

PUT( file\_capability , "this is a record" );

The capability specified in the call serves two purposes. First, it identifies the file to be written. Second, it indicates whether the operation to be performed (PUT in this case) is permitted.

A capability thus provides addressing and access rights to an object. Capabilities are the basis for object protection; a program cannot access an object unless its capability list contains a suitably privileged capability for the object. Therefore, the system must prohibit a program from directly modifying the bits in a capability. If a program could modify the bits in a capability, it could forge access to any object in the system by changing the identifier and access rights fields.

Capability system integrity is usually maintained by prohibiting direct program modification of the capability list. The capability list is modified only by the operating system or the hardware. However, programs can obtain new capabilities by executing operating system or hardware operations. For example, when a program calls an operating system routine to create a new file, the operating system stores a capability for that file in the program's capability list. A capability system also provides other capability operations. Examples include operations to:

- 1. Move capabilities to different locations in a capability list.

- 2. Delete a capability.

- 3. Restrict the rights in a capability, producing a less-privileged version.

- 4. Pass a capability as a parameter to a procedure.

- 5. Transmit a capability to another user in the system.

Thus, a program can execute direct control over the movement of capabilities and can share capabilities, and therefore, objects, with other programs and users. It is possible for a user to have several capability lists. One list will generally be the master capability list containing capabilities for secondary lists, and so on. This structure is similar to a multi-level directory system, but, while directories address only files, capabilities address objects of many types.

#### 1.1.1 Memory Addressing in Computer Systems

This section presents simplified models for both conventional and capability-based memory addressing systems. Although capabilities can control access to many object types, early capability-based systems concentrated on using capabilities for primary memory addressing. The first use of capabilities for memory protection was in the Chicago Magic Number Machine [Fabry 67, Yyngve 68], and an early description of capability-based memory protection appeared in Wilkes' book on timesharing systems [Wilkes 68]. Later, [Fabry 74] described the advantages of capabilities for generalized addressing and sharing.

For purposes of a simplified model, consider a conventional computer supporting a multiprogramming system in which each program executes within a single process. A program is divided into a collection of segments, where a segment is a contiguous section of memory that represents some logical entity, such as a procedure or array. A process defines a program's address space: that is, the memory segments it can access. The process also contains data structures that describe the user, and a directory that contains the names of a set of files. These files represent the user's long-term storage.

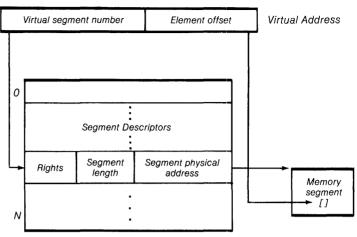

When a program is run, the operating system creates a process-local segment table that defines the memory segments available to the program. The segment table is a list of *descriptors* that contain physical information about each segment. Figure 1-2 shows example formats for a process virtual address and segment table descriptor. The operating system loads various segments needed by the program into primary memory, and loads the segment table descriptors with the physical address and length of each segment. A process can then access segments by reading from or writing to virtual addresses.

Each virtual address contains two fields: the segment number and the offset of a memory element within that specified segment. On each virtual address reference the hardware uses the segment number field as an index to locate an entry in the

#### Capability- and Object-Based System Concepts

Process-Local Segment Table

Figure 1-2: Conventional Segment Address Translation

process segment table. This descriptor contains the physical location of the segment. The length field in the descriptor is used to check that the offset in the virtual address is within the segment bounds. The rights field in the segment table entry indicates the type of access permitted to that segment (for example, read or write).

The model shown in Figure 1-2 has the following properties:

- 1. The system supports a segmented process virtual address space. A virtual address is local to the process and is translated through the process-local segment table.

- 2. A program can construct any virtual address and can attempt to read or write that address. On each reference, the hardware ensures that (a) the segment exists, (b) the offset is valid, and (c) the attempted operation is permitted. Otherwise, an error is signaled.

- 3. Loading of segment table entries is a privileged operation and can be accomplished only by the operating system. In general, a segment table is created at the time a program is loaded. The program then executes in a static addressing environment.

- 4. Sharing of segments between processes requires that the operating system arrange for both process-local segment tables to address the shared segments. If two processes wish to use the same virtual address to access a shared segment,

the segment descriptors must be in the same locations in both segment tables.

5. Any dynamic sharing of segments requires operating system intervention to load segment descriptors.

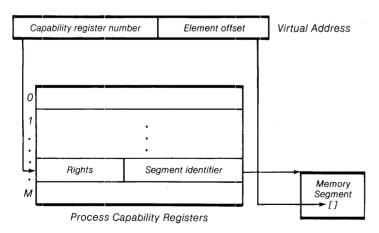

A capability-based system also supports the concept of a process that defines a program's execution environment. In the capability system, each process has a capability list that defines the segments it can access. Instead of the segment table descriptors available to the conventional system hardware, the capability addressing system consists of a set of *capability registers*. The *program* can execute hardware instructions to transfer capabilities between the capability list and the capability registers. The number of capability registers is generally small compared to the size of the capability list. Thus, at any time, the capability registers define a subset of the potentially accessible segments that can be physically addressed by the hardware. A simplified hardware model for this system is shown in Figure 1-3.

The model shown in Figure 1-3 has the following properties:

1. The system has a segmented virtual address space. A segment of memory can only be addressed by an instruction if a capability for that segment has been loaded into a capability register.

Figure 1-3: Capability Register Addressing

- 2. While loading of a segment descriptor in the conventional system is privileged, loading of a capability register is not. Instead of controlling the loading of the register, the capability system controls *the pattern of bits* that can be loaded. Only a valid capability can be loaded into a capability register.

- 3. The capability system provides a dynamically changing address space. The address space changes whenever the program changes one of the capability registers.

- 4. A virtual address identifies a process-local capability register. In this sense, a virtual address has similar properties to a virtual address in the conventional system. Sharing a virtual address does not in itself give access to the same segment.

- 5. A capability, however, is *not* process-local. Capabilities are *context independent*; that is, the segment addressed by a capability is independent of the process using that capability. A process can share a segment by copying or sending a capability from its capability list to the capability list of a cooperating process. Each of the processes can then access the segment.

One important difference between the conventional and capability approaches involves the ability of a program to affect system-wide or process-local objects. In the conventional system, a program executes within a virtual address space defined by a process. Every procedure called by that program has access to the process address space, including segments and files. Every procedure executes within an identical protection environment.

In the capability system, a procedure can only affect objects for which capability registers have been loaded. It is possible, therefore, for different procedures called by the same program to have access to different segments. Although all procedures may have the potential to load capability registers from the capability list, some procedures may choose to execute within a very small addressing sphere.

The ability to restrict the execution or addressing environment of a procedure has several benefits. First, if a procedure is allowed access only to those segments absolutely needed, the hardware can detect any erroneous references. For example, a reference past the end of an array might be caught before it destroys another variable. Second, if a procedure is found to be in error, it is easy to determine what segments might have been affected. If the segments that could have been modified were local to the procedure, recovery might be substantially easier.

Most capability systems go a step further by allowing each procedure to have a *private* capability list. A procedure can

thus protect its objects from accidental or malicious access by its callers, and a program can protect its objects from access by called procedures. Every procedure can have, in effect, its own address space. To permit a procedure access to a local object, a program can pass a capability for the object as a parameter when the procedure is called. Therefore, in a capability system, every procedure can be protected from every other procedure because each has a private capability list. When one procedure calls another, it knows that the called procedure can access only local objects for which capabilities are passed.

### 1.1.2 The Context of an Address

Each object in a capability system has a unique identifier. Conceptually, each object's identifier is unique for all time. That is, an identifier is assigned when an object is created and that identifier is never reused, even after the object is deleted. During the object's lifetime, its unique identifier is used within capabilities to specify the object. An attempt to use a capability with an identifier for a deleted object causes an error.

In practice, the object identifier field of a capability must be used by hardware to locate the object. From the hardware viewpoint, the identifier is an address—either the address of a segment or perhaps the address of a central descriptor that contains physical information about the segment. The need to handle addresses efficiently in hardware typically causes addresses to be small—16 or 32 bits, for example. For this reason, identifiers tend to have too few bits to be unique for all time. However, the choice of the number of bits in an identifier is an important system design decision that dictates the way in which capabilities can be used.

In conventional systems, an address is meaningful only within a single process. In a capability system, addresses (capabilities and their identifiers) are context-independent. That is, the interpretation of a capability is independent of the process using it. The unique identifier within a capability must have a system-wide interpretation. Unique identifiers must be large enough to address all of the segments likely to be in use by all executing processes at any time. This allows capabilities to be freely passed between processes and used to access shared data.

Addressing on most conventional systems is restricted in terms of time as well as context. An address is meaningful only within the lifetime of a single process. Therefore, addresses cannot be used to name objects whose lifetimes are greater than the process creating the objects. If a process wishes to create a long-term storage object, such as a file, it must interface to the file system. Files typically require different naming, protection, and storage mechanisms than memory segments.

A significant advance made possible by capabilities is the naming and protection of both long-term and short-term objects with a single mechanism. If the identifier field is very large, it may be possible to implement identifiers unique for all time. Each object is addressed by capabilities containing its unique identifier, independent of whether it is stored in primary or secondary memory. The operating system or hardware can maintain data structures that indicate the location of each object. If a program attempts to access an object in secondary memory, the hardware or operating system can bring the object into primary memory so that the operation can be completed. From the program's point of view, however, there is a single-level address space. Capabilities, as well as data, can be saved for long periods of time and stored in secondary memory.

There are, therefore, several contexts in which an address can have meaning. For example, for:

- 1. Primary memory segments of a single process.

- 2. Primary memory segments of all existing processes.

- 3. All existing segments in both primary and secondary memory.

Most conventional systems support only type 1, while capabilities allow for any of the listed addressing types. More importantly, while conventional systems are concerned only with the protection of *data*, capability systems are concerned also with the protection of *addresses*. A process on a capability system cannot fabricate new addresses. As systems become more general in their addressing structure as in types 2 and 3, the protection of addresses becomes crucial to the integrity of the system.

#### 1.1.3 Protection in Computer Systems

Lampson contrasts the capability approach with the traditional approach by showing the structure of protection information needed in a traditional operating system [Lampson 71]. Figure 1-4 depicts an access matrix showing the privileges that each system user is permitted with respect to each system object. For example, user Fred has read and write privileges to File1 and no privileges to File2, while user Sandy is allowed to read both files.

#### File1 File2 File3 ProcessJ Mailbox10 . . . Read Read Delete Send Fred Write Suspend Wakeup System Úsers Read Read Send Sandv Receive Read Send Molly Write

System Objects

Figure 1-4: System Object Access Matrix

One conventional approach to the maintenance of protection information is access control lists, in which the operating system keeps an access list for each object in the system. Each object's list contains the names of users permitted access to the object and the privileges they may exercise. When a user attempts to access an object, the operating system checks the access list associated with that object to see if the operation is authorized. Each of the columns of Figure 1-4 represents an access control list.

The capability system offers an alternative structure in which the operating system arranges protection information by user instead of by object. A *capability list* is associated with each user in the system. Each capability contains the name of an object in the system and the user's permitted privileges for accessing the object. To access an object, the user specifies a capability in the local capability list. Each of the rows of Figure 1-4 represents a capability list. Figure 1-5 shows an access list

| Access List for Mailbox10                        | Capability list for Fred                                                               |

|--------------------------------------------------|----------------------------------------------------------------------------------------|

| Fred(send)<br>Sandy(send,receive)<br>Molly(send) | File1(read,write)<br>File3(read)<br>ProcessJ(delete,suspend,wakeup)<br>Mailbox10(send) |

| •                                                | •                                                                                      |

| •                                                | •                                                                                      |

|                                                  |                                                                                        |

and a capability list derived from the protection matrix in Figure 1-4.

One important difference between the capability list and access list is the user's ability to *name* objects. In the access list approach, a user can attempt to name any object in the system as the target of an operation. The system then checks that object's access list. In the capability system, however, a user can only name those objects for which a capability is held: that is, to which some access is permitted.

In either case, the integrity of the system is only as good as the integrity of the data structures used to maintain the protection information. Both access control list and capability list mechanisms must be carefully controlled so that users cannot gain unauthorized access to an object.

Similar protection options exist outside the computer world. A useful analogy is the control of a safe deposit box. Suppose, for example, that Carla wishes to keep all of her valuables in a safe deposit box in the bank. On occasion, she would like one or more trustworthy friends to make deposits or withdrawals. There are basically two ways that the bank can control access to the box. First, the bank can maintain a list of people authorized to access the box. To make a transaction, Carla or any of her friends must prove their identity to the bank's satisfaction. The bank checks the (access control) list for Carla's safe deposit box and allows the transaction if the person is authorized. Or, instead of maintaining a list, the bank can issue Carla one or more keys to her safe deposit box. If Carla needs to have a friend access the box, she simply gives a key to the friend.

A number of observations can be made about these two alternative protection systems. The properties of the access list scheme are:

- 1. The bank must maintain a list for each safe deposit box.

- 2. The bank must ensure the validity of the list at all times (e.g., it cannot allow the night watchman to add a name).

- 3. The bank must be able to verify the identity of those asking to use a box.

- 4. To allow a new person to use the box, the owner must visit the bank, verify that he or she is the owner of the box, and have the new name added to the list.

- 5. A friend cannot extend his or her privilege to someone else.

- 6. If a friend becomes untrustworthy, the owner can visit the bank and have that person's name removed from the list.

The alternative scheme involving keys has the following properties:

- 1. The bank need not be involved in any transactions once the keys are given, except to allow a valid keyholder into the vault.

- 2. The physical lock and key system must be relatively secure; that is, it must be extremely difficult to forge a key or to pick the lock on a safe deposit box.

- 3. The owner of a box can simply pass a key to anyone who needs to access the box.

- 4. Once a key has been passed to a friend, it is difficult to keep them from giving the key to someone else.

- 5. Once a friend has made a transaction, the owner can ask for the key back, although it may not be possible to know whether or not the friend has made a copy.

The advantage of the key-based system is ease of use for both the bank and customer. However, if today's friends are likely to become tomorrow's enemies, the access list has the advantage of simple guaranteed access removal. Of course, the access control list and the key (or capability) systems are not mutually exclusive, and can be combined in either the computer or banking world to provide the advantages of both systems for increased protection.

#### 1.2 The Object-Based Approach

Over the last few decades, several areas of computer science have converged on a single approach to system design. This approach, known as *object-based computing*, seeks to raise the level of abstraction in system design. The events that have encouraged object-based design include:

- 1. Advances in computer architecture, including capability systems and hardware support for operating systems concepts.

- 2. Advances in programming languages, as demonstrated in Simula [Dahl 66], Pascal [Jensen 75], Smalltalk [Ingalls 78], CLU [Liskov 77], and Ada [DOD 80].

- 3. Advances in programming methodology, including modularization and information hiding [Parnas 72] and monitors [Hoare 74].

This section introduces the object approach and discusses its relationship to capability-based computer systems.

What is object-based computing? Simply stated, the object approach is a method of structuring systems that supports *ab*-

Capability- and Object-Based System Concepts

straction. It is a philosophy of system design that decomposes a problem into (1) a set of *abstract object types*, or resources in the system, and (2) a set of *operations* that manipulate *instances* of each object type.

To make this idea more concrete, consider the following simplified example. Imagine that we are programming a traffic simulation for a city. First, define a set of objects that represent, abstractly, the fundamental entities that make up the traffic system. Some of the object *types* for the traffic simulation might be:

- passenger

- bus

- bus stop

- taxi

- car

Then, for each object type, define the operations that can be performed. Bus objects, for example, might support the operations:

- PUT\_BUS\_INTO\_SERVICE( bus\_number )

- MOVE\_BUS( bus\_number, bus\_stop )

- LOAD\_PASSENGERS( bus\_number, passenger\_list )

- UNLOAD\_PASSENGERS( bus\_number, passenger\_list )

- GET\_PASSENGER\_COUNT( bus\_number )

- GET\_POSITION( bus\_number )

- REMOVE\_BUS\_FROM\_SERVICE( bus\_number )

Each bus operation accepts a bus number as a parameter. At any time there may be many bus objects in the system, and we identify each bus by a unique number. Each of these bus objects is an *instance* of the *type* bus. The *type* of an object identifies it as a member of a class of objects that share some behavioral properties, such as the set of operations that can be performed on them.

What has been gained by defining the system in this way? First, there now exist a fundamental set of objects and operations for the simulation. We can now implement the procedures to perform the operations on each type of object. Since only a limited number of procedures operate on each object type, access to the internal data structures used to maintain the state of each type can be restricted. This isolation of the knowledge of those data structures should simplify any future changes to one of the object abstractions because only a limited set of procedures is affected.

Second, and more importantly, we have raised the *level of* abstraction in the simulation program. That is, we can now program the simulation using buses, passengers, and bus stops as the fundamental objects, instead of bits, bytes, and words, which are normally provided by the underlying hardware. The buses and passengers are our data types just as bits and bytes are the data types supported in hardware. The simulation program will consist mainly of control structures plus procedure calls to perform operations on instances of our fundamental objects.

Of course, in this example, the procedures implementing the operations are programmed using lower-level objects, such as bytes, words, and so on. Or, they may be further decomposed into simpler abstract objects that are then implemented at a low level. Object-based systems provide a fundamental set of objects that can be used for computing. From this basis, the programmer constructs new higher-level object types using combinations of the fundamental objects. In this way the system is extended to provide new features by creating more sophisticated abstractions.

This methodology aims to increase productivity, improve reliability, and ease system modification. Through the use of well-defined and well-controlled object interfaces, systems designers hope to simplify the construction of complex computer systems.

#### 1.2.1 Capabilities and Object-Based Systems

In the simulation example, each object is identified by a unique number. To move a bus from one stop to another, we call the MOVE\_BUS operation with the unique number of the bus to move. For purposes of the simple simulation, a small set of integers suffices to identify the buses or other objects. No protection is needed because these objects are implemented and used by a single program.

The use of the object approach to build operating system facilities presents different requirements. For example, suppose we wish to build a calendar system to keep track of scheduled meetings, deadlines, reminders, and so on. The fundamental object of the calendar system, from the user's point of view, is a calendar object. Our calendar management system provides routines that create a new calendar, and modify, Capability- and Object-Based System Concepts

query, or display an existing calendar. Many users in the system will, of course, want to use this facility.

Several familiar issues now arise: (1) how does a user name a calendar object, (2) how is that calendar protected from access by other users, and (3) how can calendars be shared under controlled circumstances? Only the owner of a calendar should be able to make changes, and the annotations in each calendar must be protected from other users, since they might contain confidential information. However, a user might permit selected other users to check if he or she is busy during a certain time, in order to automate the scheduling of meetings.

Capabilities provide a solution to these problems. When a user creates a new calendar, the calendar creation routine allocates a segment of memory for which it receives a capability. This segment is used to store data structures that will hold the calendar's state. The create routine uses this capability to initialize the data structures, and then returns it to the caller as proof of ownership of the calendar. In order to later modify or query the calendar, the user specifies the returned capability; the capability identifies the calendar and allows the modify or query procedure to gain access to the data structures. Only a user with a valid capability can access a calendar.

A weakness with this scenario is that the calendar system cannot prevent the calendar owner from using its capability to access the data structures directly. The calendar system would like to protect its data structures both to ensure consistency and to guarantee that future changes in data format are invisible outside of the subsystem. In addition, if a user passes a calendar capability to another user, the second user can then modify the data structures or read confidential information.

These problems exist because the calendar system returns a fully-privileged calendar capability to the user. Instead, what is needed is a capability that identifies a specific calendar and is proof of ownership, but does not allow direct access to the underlying data structures. In other words, the calendar system would like to return only *restricted* capabilities to its clients. However, the calendar system must retain the ability to later *amplify* the privileges in one of its restricted capabilities so that it can access the data structures for a calendar.

There are several ways of providing type managers with this special ability. (These mechanisms are examined in detail throughout the book.) However, given this power over capabilities for its objects, a type manager can ensure that its clients operate only through the well-defined object operation interface. A client can pass a capability parameter to the type man-

1.3 Summary

ager when requesting a service, but cannot otherwise use the capability to read or write the object it addresses. This facility is fundamental to any system that allows creation and protection of new system types.

#### 1.3 Summary

The capability concept can be applied in hardware and software to many problems in computer system design. Capabilities provide a different way of thinking about addressing, protection, and sharing of objects. Some of the properties of capabilities illustrated in this chapter include their use in:

- 1. Addressing primary memory in a computer system.

- 2. Sharing objects.

- 3. Providing a uniform means of addressing short- and long-term storage.

- 4. Support for a dynamic addressing environment.

- 5. Support for data abstraction and information hiding.

These, of course, are advantages of capability-based systems. The most important advantage is support for objectbased programming. Object-based programming methodology seeks to simplify the design, implementation, debugging, and maintenance of sophisticated applications. While capabilities solve a number of system problems, their use raises a whole new set of concerns. And, as is often the case in computer system design, the concept is much simpler than the implementation.

The remainder of this book is devoted to examining many different capability-based and object-based designs. The characteristics of each system are described with emphasis on addressing, protection, and object management. Each system represents a different set of tradeoffs and presents different advantages and disadvantages. When comparing the systems, consider the differences in goals, technologies, and resources available to the system developers.

The final chapter of this book considers issues in capability system design common to all of the systems described. A few of the questions to be considered follow. It may be useful to remember these questions when examining each system design.

- 1. What is the structure of an address?

- 2. How is a capability represented? How is a capability used to locate an object?

Capability- and Object-Based System Concepts

- 3. How are capabilities protected?

- 4. What is the lifetime of a capability?

- 5. What types of objects are supported by the hardware and software?

- 6. What is the lifetime of an object?

- 7. How can users extend the primitive set of objects provided by the base hardware and software?

## 1.4 For Further Reading

The concept of capability is formally defined in the 1966 paper by Dennis and Van Horn [Dennis 66]. Chapter 3 examines this paper in some detail. The paper by Fabry [Fabry 74] compares capability addressing and conventional segmented addressing of primary memory, while Redell [Redell 74a] describes issues in capability systems and the use of sealing mechanisms that support the addition of new object types to a system. These papers are a fundamental part of capability literature.

Capability systems have been discussed in various contexts. Two papers by Lampson [Lampson 69 and Lampson 71] describe the requirements for protection in operating systems and the capability protection model. The surveys by Linden [Linden 76] and Denning [Denning 76], which appeared in a special issue of ACM Computing Surveys, describe capability systems and their relationship to security and fault tolerance in operating systems.

The architecture books by Myers [Myers 82] and Iliffe [Iliffe 82] also discuss some of the systems described in this book. Myers' book contains details of Sward [Myers 80], a capability-based research system built at IBM that is omitted here. A capability system model, as well as discussion of some existing capability systems, appears in the book by Gehringer [Gehringer 82]. Jones [Jones 78a] provides a good introduction to the concepts of object-based programming.

The Burroughs B5000 computer. (Courtesy Burroughs Corporation.)

# Early Descriptor Architectures

### 2.1 Introduction

During the late 1950s and early 1960s a host of architectural experiments attacked significant problems in computer system utilization. Most computers of that era were batch systems that ran one program at a time. A program was loaded into a contiguous section of primary memory and run until completion; then another program was loaded and run. This static execution and memory environment made inefficient use of the costly processor, memory, and peripherals. In addition, programs had little flexibility for meeting dynamic programming demands.

Multiprogramming systems showed increased processor utilization as long as several runnable programs could be kept in primary memory. However, multiprogramming required more sophisticated memory management techniques and forced operating systems to deal with dynamic storage allocation and compaction. These tasks were greatly eased by the introduction of paged systems in which all storage units were the same size.

Although paging helped the operating system to manage storage, it did little to help the programmer with the task of programming. A program still had to manage a conventional linear address space. It was difficult to protect instructions or data separately, to catch array bounds violations, to increase the size of arrays and other data structures dynamically, or to create new data structures dynamically.

The concept of segmentation, however, aided both the pro-

grammer and the operating system. A segment is a contiguous section of memory that represents some logical entity, such as a procedure or array. The programmer views memory as a collection of segments, each separately addressable. A program addresses each memory element by a segment number and the offset of that element within the specified segment. Because each segment has a size, array bounds violations can be caught by placing the array within a single segment.

An operating system can load each segment into memory separately or relocate segments if needed (for example, to enlarge the size of the segment). However, for an operating system to manipulate segments easily, it must ensure that physical memory addresses are not embedded in the program. The simplest way to isolate the program from its physical memory location is to provide a level of indirection between program-generated addresses and the primary memory addresses of data elements. Just as page tables provide this indirection in the paged virtual memory system, segment descriptors-or segment base/limit registers in some hardware implementations-provide the indirection in a segmented system. A segment descriptor is a data element that contains the primary memory address and size of a segment. An operating system need only modify the relevant descriptors when relocating segments.

This chapter examines several early descriptor-based computer designs: the Burroughs B5000, the Rice University Computer, and the Basic Language Machine. Although these systems preceded the formal definition of capability, each system implemented capability-like structures in its addressing mechanisms. These machines were distinguished from their contemporaries by the generalized way in which they applied the concept of descriptor.

## 2.2 The Burroughs B5000

Much of the innovation in commercial computer architectures in the early 1960s emanated from the Burroughs Corporation. Introduced in 1961, the Burroughs B5000 system had several features unique for its time [Burroughs 61]. Most important was the use of segmentation for structuring memory and the use of descriptors for addressing segments. Also, the B5000 was geared to execute high-level language programs, particularly ALGOL and COBOL. In fact, assembly language was not available to the user. The system was designed to compile and execute high-level languages efficiently, and relied on a stack-oriented instruction set to aid in expression evaluation and procedure activation. The B5000 supported multiprocessing as well as multiprogramming by allowing connection of two processing units.

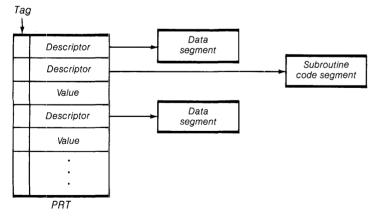

On the B5000 a program consists of many data segments and code segments. Each executing program has a local addressing environment consisting of its memory segments, its private stack, and a private *Program Reference Table* (PRT). The Program Reference Table, up to 1024 48-bit words in length, contains *descriptors* that locate the user's code and data segments in memory, and *values* of scalar elements, as shown in Figure 2-1. A *tag* field in each word in the table indicates whether the entry is a descriptor or a scalar data element. All memory references, including procedure calls, are made through Program Reference Table descriptors; thus, the Program Reference Table completely defines the domain of execution for each user program. When a program is running, a hardware register holds the address of its Program Reference Table.

The B5000 supports three different descriptor types: data descriptors, program descriptors, and input/output descriptors. The formats of these descriptors are shown in Figure 2-2. Data descriptors contain the size, primary memory address, and drum unit number and address of a data segment. Program descriptors are allocated for each procedure and every segment of the main program. Reference to a program descriptor automatically causes a procedure call. Input/output descriptors are

Figure 2-1: B5000 Program Reference Table

| Tag P | Drum   | Segment | Drum    | Memory  |

|-------|--------|---------|---------|---------|

|       | number | size    | address | address |

Data and Program Descriptor

Figure 2-2: B5000 Descriptor Formats

command words for the operating system, specifying the size and type of transfer and any special device control or formatting information. The operating system selects a physical unit and allocates primary memory for the operation if needed.

The presence bit (P) in data and program descriptors indicates whether or not the segment is currently in primary memory. If reference is made to a segment not in primary memory, a trap occurs and the operating system automatically loads the segment from drum.

The B5000 is a stack machine and all instructions operate on the stack. The stack is stored in memory; however, the top two stack elements are held in hardware registers called the A and B registers. As items are pushed onto the stack, they move first into the A register, then to the B register, and finally into memory as more items are pushed. As items are popped from the stack, data moves from memory into the B register. All arithmetic operations are performed on operands held in the A and B registers, leaving a single result in the B register.

Each 48-bit B5000 instruction word is divided into four 12bit instruction *syllables*. There are four types of instruction syllables: operators, literals, operand calls, and descriptor calls. An *operator* syllable operates on the top one or two elements of the stack, leaving a single-word result. A *literal* syllable simply causes a 10-bit literal field in the syllable to be pushed on the stack.

A program executes an *operand call* syllable to load a data item onto the stack. The operand call references an entry in the Program Reference Table, with three possible results depending on the type of entry encountered. First, if the PRT entry is a scalar, the scalar is pushed onto the stack. Second, if the PRT entry contains a program descriptor, a subroutine call takes place. Third, if the entry is a descriptor for a segment with length greater than zero, then array indexing takes place as follows. The contents of the B register, which contains the array index, is validated against the length stored in the descriptor. The index is then added to the segment base address to locate the selected word in memory. The word is read from memory and loaded into the B register, replacing the index.

Descriptors can also be loaded from the PRT onto the stack. This is required, for example, to execute the STORE operator, which saves the contents of the B register in the location addressed by the A register. A *descriptor call* syllable, used to push an address onto the stack, operates in a mode similar to the operand call. If the referenced PRT entry is a scalar, a descriptor is constructed pointing to its location in the PRT. If a PRT entry contains a descriptor, the descriptor is copied to the stack, with possible address modification by an index value in the B register. Reference to a program descriptor causes a subroutine call.

B5000 subroutines execute in *subroutine mode* which provides some special syllable formats. When a subroutine is called, input parameters (as well as linkage information) are saved on the stack by the caller. A hardware register is loaded with the address of the next available stack location past the saved parameters; this is the first location used by the subroutine for its local variables. One of the subroutine mode syllables allows stack addressing relative to the register in the positive direction (to access locals) or the negative direction (to access inputs). A subroutine can also address constants stored in the subroutine code segment using a type of program counter relative addressing. References to the caller's PRT are still permitted within the subroutine.

The B5000's use of the stack, segmentation, descriptor addressing, and high-level languages made it one of the most advanced systems of its time. These features have been expanded and generalized in later Burroughs systems and have had an effect on other manufacturers' products as well. The 16-bit Hewlett-Packard 3000 [HP 72], in particular, is an outgrowth of early Burroughs B5000 ideas. More important, the B5000 Program Reference Tables and their use in addressing and separation of process address spaces directly influenced early capability thinking.

## 2.3 The Rice University Computer

In 1959, development of a new machine began at Rice University. Called the Rice University Computer [Iliffe 62, Jodeit

The Rice University computer. Jane Jodeit is seated at the control console with Martin Graham looking on (Courtesy Dr. Martin Graham.)

68], this system was designed for the single-program environment and was never intended to support multiprogramming. In fact, the original physical memory of the Rice machine was only 8K 56-bit words. However, this computer—operational until 1971—provided important experimentation with program addressing of memory.

The Rice architecture focused on several deficiencies in conventional linear address space machines. First, conventional hardware did not support entities corresponding to high-level programming objects. Second, for scientific problems, conventional architectures did not support the addressing of single or multidimensional arrays. Third, dynamic growth of data structures was difficult on conventional machines. Programmers had to code the maximum possible size of each array into their programs, so that contiguous storage could be preallocated. Support of ALGOL-like languages, with array size determination at block entry time, was difficult.

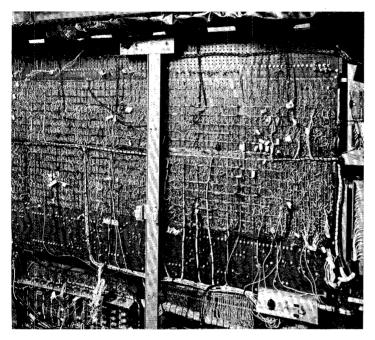

To solve these problems, the Rice designers chose a segmented architecture based on the use of *codewords*. Codewords are descriptors for logical program entities; they can be stored in the computer's memory or registers. Each program (as

| 15 | 12 | 1 | 1 | 1 | 8 | 15 |

|----|----|---|---|---|---|----|

| L  | 1  | х | p | * | К | F  |

F Physical address of the segment.

- K Specifies one of eight index registers whose contents can be used to select an array element at location F I + (K).

- p Valid bit, indicates whether physical storage is allocated or not.

- \* Indirect bit.

- X Specifies that the named segment contains codewords.

- I Index of the first array element (origin of the array).

- L Length of the segment in words.

viewed by both the programmer and the machine) consists of a collection of segments, called blocks or arrays in the Rice design. A segment contains instructions, data, or codewords and is addressed indirectly by means of a codeword. Each segment is homogeneous, and data types cannot be mixed within a single segment. A single-bit tag within each codeword is set if the addressed segment contains codewords.

In one sense, a codeword is simply a single-word descriptor used to address a segment, similar to a segment base register or Burroughs B5000 descriptor. In another sense, a codeword *names* the block of storage it addresses. The logical machine address space seen by the program on the Rice system is totally defined by a list of *principal codewords* that it can access. The actual maintenance of codewords is provided by the operating system. The basic structure of Rice codewords (omitting unused bits) is shown in Figure 2-3.

The physically addressable memory of the Rice machine is divided into several fixed regions, as defined below:

- A 64-word table for accumulators, trap addresses, boot code, etc.

- Two 64-word directories of codewords defining array blocks for the operating system and programmer, respectively. These are the principal codewords through which all other storage is reached, including the following structures.

- A 128-word stack.

- A symbol table defining each named global object in the system.

- A corresponding *value table* containing values for scalars and codewords for arrays named in the symbol table.

The remainder of memory is allocated dynamically to user programs and data, including those addressed through the value table.

Figure 2-4 shows the structure of a Rice University Computer sample procedure. Procedure instructions can address variables within the procedure segment without reference to codewords (that is, relative to the program counter). However, external arrays, procedures, and variables are addressed through linkage words stored at the end of the procedure segment. When a procedure is compiled, the linkage words are initialized with the names of the global variables to be addressed. At procedure load time, the operating system locates the names in the symbol table and modifies the linkage words to point to the corresponding entries in the value table.

A value table entry can be a value if the object is scalar, or a codeword if it is an array, requiring one or more additional levels of indirection. Indirection is possible through a tree of codewords, and each successive level can specify one of eight index registers. For example, in addressing the two-dimensional array (2DArray) shown in Figure 2-4, each codeword in the secondary codeword segment addresses one row of the array. Indirection terminates when a scalar object is found. Measurements performed on the Rice University Computer showed that 10-15% of total data references were made through codewords.

Arrays can be extended in length by allocating additional storage and modifying the codeword. Multidimensional array addressing is aided by the fact that each codeword can specify an index register. For example, a two-dimensional array can be described by a primary codeword pointing to a table of codewords, one for each row. No address computation is required because the index registers are used to hold the column and row indices. In addition, the rows can be of different lengths.

Although the designers stressed the importance of array addressing and extensibility, perhaps more important is the use of codewords as object names. Using the Rice scheme, a procedure need only specify a codeword parameter to pass an object to another procedure. The codeword completely defines access to the object, including its address and length.

The Rice University Computer had several limitations, but they were often due to implementation decisions. For example, codewords contained the length of the block they defined, but the length was not used by hardware to validate an array index. Instead, a trap facility was provided to allow software to check

Figure 2-4: Rice University Computer Memory Organization

array bounds. There was also no hardware-enforced memory protection in the system; however, this was due to the simplified goals of the machine. One of the more troublesome shortcomings was that procedure return address links were stored as physical addresses, so procedures could not be relocated easily.

Iliffe and Jodeit suggest that extensions for multiprogramming would be straightforward and require that each user have a separate primary codeword list. Virtual arrays would be possible also, but the only secondary storage on the Rice computer was a magnetic tape system. The Rice implementation of codewords closely resembles the capability concept in the sense that possession of the codeword (or knowledge of its address) is required to access an object. The designers also suggest that Rice codewords could be extended to include usage statistics and that device controllers could be developed to understand codeword formats. These additions were never made, but several architectural advances were made in a follow-on design, the Basic Language Machine.

## 2.4 The Basic Language Machine

The Basic Language Machine (BLM) [Iliffe 68, Iliffe 69] attempted to extend the capabilities of the Rice University Computer and correct some of its shortcomings. Like the Rice University machine, the BLM incorporated a codeword mechanism, but it added data type tagging and address manipulation as well. An additional goal of the BLM project was to build a machine defined in terms of higher level functions, hiding from the programmer the bit-level details of the machine. The Basic Language (not the familiar BASIC programming language used today) defined this high-level architectural interface in terms of an assembly-level command structure. Design of the BLM was started in 1964, and an experimental version was built by the research division of International Computers Limited (ICL) in the United Kingdom.

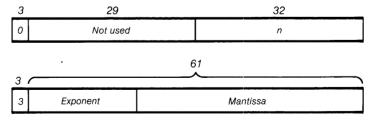

The Basic Language Machine supports 8-bit byte, 32-bit word, and 64-bit double-word information units. There are 16 general-purpose registers, each 64 bits long. One of the registers is the program counter (called the *control number*), one points to a data structure containing the context local to the current process (called the *Process Base*), and two are reserved for special escape actions. Memory on the BLM is segmented, the largest segment containing 64K elements of the largest information unit. The BLM supports a 24-bit physical address space.

The BLM computer. (Courtesy International Computers Ltd.)

BLM segments are addressed through codewords, as on the Rice computer. However, BLM codewords contain a *type* field indicating the type of information elements stored in the segment they address. The defined data types are:

- 32-bit binary word,

- 8-bit byte,

- 64-bit long numeric,

- 32-bit short numeric,

- mixed type,

- instruction,

- absolute codeword, and

- relative codeword.

The type field also indicates what access is permitted to the segment: data segments can be read-only or read/write; code-word and instruction segments are read-only.

Most of the type encodings specify segments that are homogeneous, that is, segments with only one data type. If the codeword type field specifies a mixed-type segment, the segment can contain elements of any type. However, in mixedtype segments, each element must contain its own tag. A tag is a field contained within the information unit indicating its interpretation. All elements in a mixed-type segment are 64 bits long and contain a 3-bit tag. The four tags defined are:

- 32-bit binary word,

- escape (an attempt to use such an element as an operand causes a trap to software),

- 45-bit address (stored in 64 bits), and

- 61-bit floating numeric element.

The BLM automatically performs conversion and tagging of data elements on fetch or store operations. In homogeneous sets, tags do not need to be stored with each data item, but are constructed from the type stored in the codeword used to load the item into a register. Therefore, homogeneous information can be tightly packed without tagging overhead. The format of 32-bit and 61-bit numeric elements when stored in registers, for example, is shown in Figure 2-5. The tag values of zero and three in the figure indicate 32- and 61-bit numerics, respectively. If an 8-bit byte is fetched, it is automatically signextended to 32 bits, and the tag is set to zero.

The BLM is a multiprogrammed computer, and a Process Base defines the execution environment for each process. It is possible for several processes to share the same base and, hence, share access to the same objects. The process address space is composed of a collection of segments, each of which is described by a codeword. The segments may be arranged in a tree structure, but all nodes are reachable only through codewords originating in the Process Base. That is, the terminal nodes of the tree structure contain data or instructions, while the intermediate or branching nodes are codeword sets. Codewords are thus used both to separate user address spaces and to separate logical entities within a program.

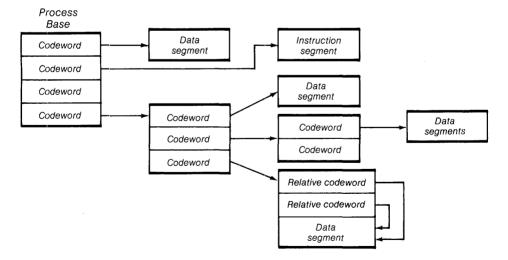

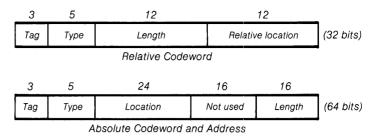

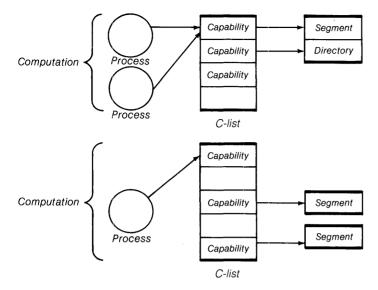

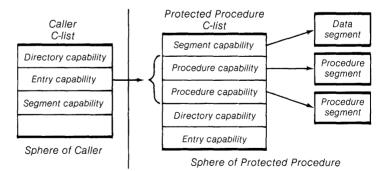

Figure 2-5: Example of BLM Numeric Formats