# **Computer Programming** and Architecture The VAX

HENRY M. LEVY / RICHARD H. ECKHOUSE, JR.

Computer Programming and Architecture: The VAX

# **Digital Press**

# Computer Programming and Architecture: The VAX

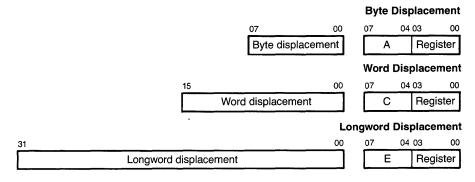

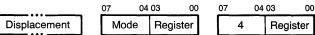

**Second Edition**

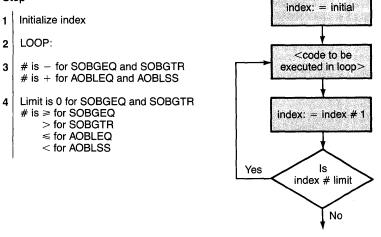

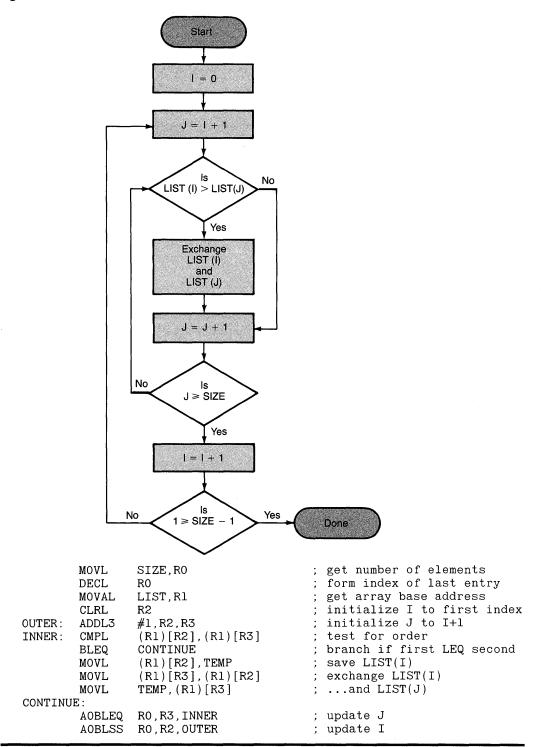

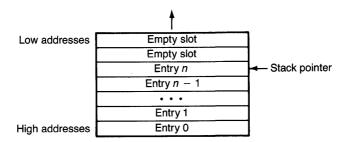

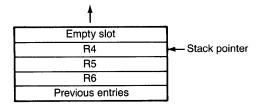

Henry M. Levy/Richard H. Eckhouse, Jr.

- .

Copyright © 1980, 1989 by Digital Equipment Corporation.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, photocopying, recording, or otherwise, without prior written permission of the publisher.

98765432

Order number EY-6740E-DP

Printed in the United States of America.

Interior design: Richard Bartlett Cover design: David Ford Art coordination: Carol Keller Illustrations: Network Graphics Production coordination: Nancy Benjamin

#### Trademarks

AT&T Bell Laboratories: UNIX Bolt Beranek and Newman, Inc.: Butterfly Control Data Corporation: Cyber Cray Research, Inc.: Cray-1, Cray-2, Cray X-MP Digital Equipment Corporation: DEC, VAX, MicroVAX, VMS, Ultrix, VAXclusters, PDP, UNIBUS, BI, MASSBUS Intel Corporation: 8086, 80286, 80386, 80387, iPSC International Business Machines Corporation: System 360/370, System 4300 Motorola, Inc.: 68000, 68010, 68020 Sequent Computer Systems, Inc.: Balance, Symmetry, Dynix Thinking Machines Corporation: Connection Machine

#### Library of Congress Cataloging-in-Publication Data

Levy, Henry M. Computer programming and architecture.

Bibliography: p. Includes index.

1. VAX computers. 2. VAX computers—Programming. 3. Computer architecture.

I. Eckhouse, Richard H. II. Title.

QA76.8.V32L48 1988 005.2'45 88-22887 ISBN 1-55558-015-7 In memory of Samuel J. Levy

# Contents

Preface xvii

**1** Architecture and Implementation 1 Organization of This Book 1 Review of Number Systems 3

> Number Systems 3 Binary and Hexadecimal Representations 5 Negative Numbers 6 Exercises 8

# **2** Computer Structures and the VAX 10

Computer Structures 10 The Memory 10 The Central Processing Unit 13 Instruction Execution 13 Classes of Instruction Architectures 16 The Input/Output System 17 Describing Computer Structures 18 Introduction to the VAX 20 VAX Information Units and Data Types 22 Integers 24 Floating-Point Numbers 25 Alphanumeric Characters 29 Decimal Strings 30 Summary of Data Types 31 3

Summary 33 Exercises 34

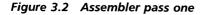

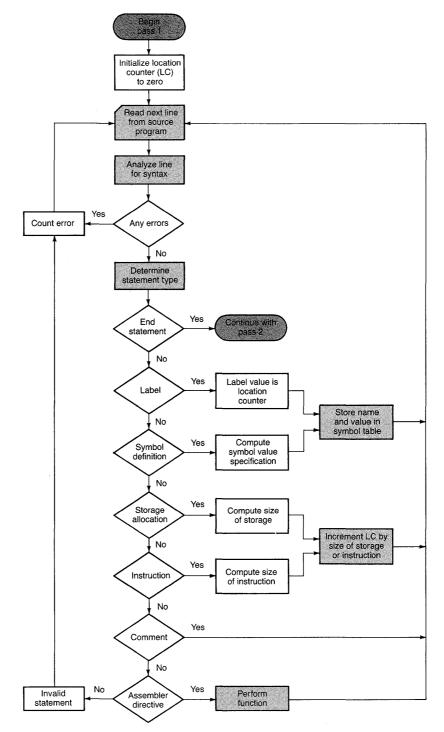

# The Program Assembler and Debugger 36 Assembler Statement Types 37 VAX Instruction Format 38 The Functions of a Symbolic Assembler 41 The Location Counter 42 Symbols 43 Constants 44 Storage Allocation 44 Storing Strings 46 Expressions 48 Control Statements 49 Labels 50 The Listing 51 The Assembly Process 51 The Program Debugger 53 Using the Debugger 56 Examining and Depositing 57 Basic Control Flow 58 Setting Breakpoints, Watchpoints, and Tracepoints 59 Using the Screen 60 First Program Example: Simple Output 60 Conventions for Writing Programs 65 Exercises 66

4 Instruction and Addressing Fundamentals 69 VAX Instruction Characteristics 69 Generic Operations 70 Control Flow 70

viii

Operand-Addressing Techniques 77 Simple Addressing 77 Immediate Mode 80 General-Purpose Registers 82 Indirect Mode 84 Register Autoincrement and Autodecrement Modes 87 Operand Context 89 Displacement Mode 91 Index Mode 94 A Simple Example 96 Exercises 98

# **5** VAX Instruction Encoding 101

General Instruction Format 101 Encoding an Instruction 102 Program-Counter Relative Addressing 105 Immediate Addressing 108 Absolute Addressing 110 Branch Addressing 111 Summary 112 Exercises 116

#### **6** Advanced Control Structures 118

The Jump Instruction 118 Case Statements 119 Loops 122 The Stack 125 Subroutines and Procedures 131 Argument Lists and Call Instructions 133 The Argument Pointer 135 Saving Registers 135 An Example Procedure 137 The Call Frame 138 Local Variables 141 Fast Linkages 142 Recursion 145 Reentrant Routines 148 Macros 150 Creating Local Labels 152 Macro Calls within Macro Definitions 153 Argument Concatenation 154 Repeat Blocks 154 Conditional Assembly 157 Summary 159 Exercises 159

### 7 More VAX Data Types 162

Bits and Bit Fields 162 Logical Bit Instructions 162 Single-Bit Instructions 164 Variable-Length Bit Fields 168 Converting Integer Data Types 171 Character Strings 174 Packed Decimal String Instructions 178 Multiple-Precision Integer Arithmetic 180 Floating-Point Arithmetic 182 Exercises 184

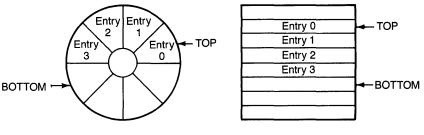

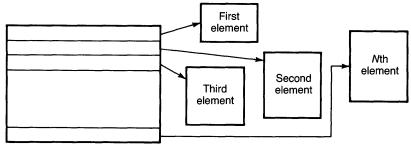

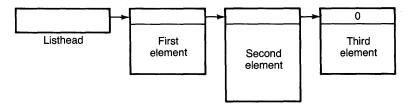

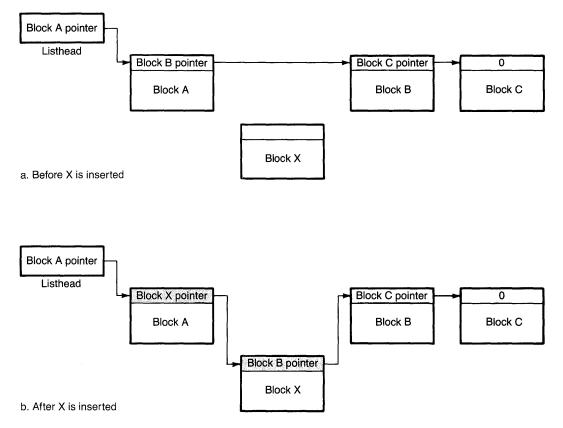

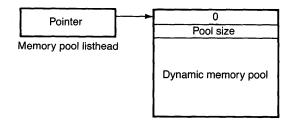

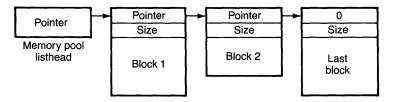

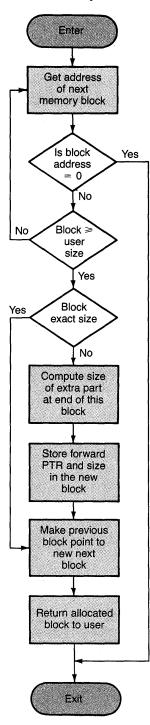

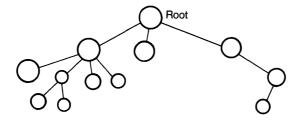

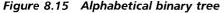

## **8** Linked Data Structures 186

Multi-Element Structures and Records 186 Arrays 187 Circular Lists 188 Linked Lists 191 Doubly Linked Lists 197 Self-Relative Queues 204 Trees 206 Summary 210 Exercises 211

# **9** Analysis of the VAX Instruction Set 212

Exercises 216

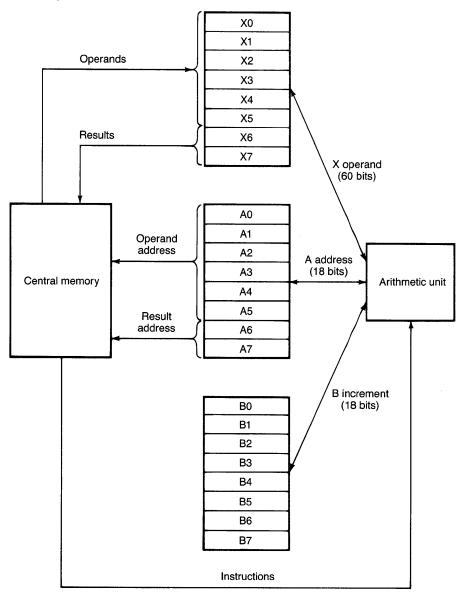

## **10** Comparative Architectures 218

General Issues in Instruction Set Design 218 The IBM System 360/370 219 The CDC Cyber Series 225 The Intel 80386 Microprocessor 231 Reduced Instruction Set Computers 234 *Berkeley RISC II 236* Summary 241 Exercises 242

# **11** Physical Input and Output 243

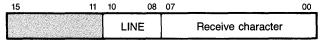

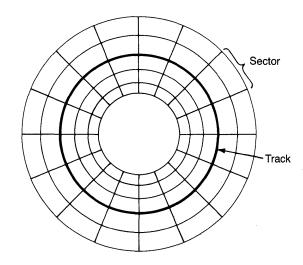

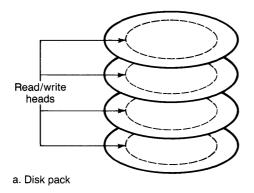

I/O Processing 244 Control and Status Registers and I/O Space 246 Low-Speed Devices 247 *The Line Printer 247 Terminal Multiplexing 249* High-Speed Devices 251 *Magnetic Disks 251 Simplified Disk Control 253 Magnetic Tape 258* Mass Storage Control Protocol 259 xii

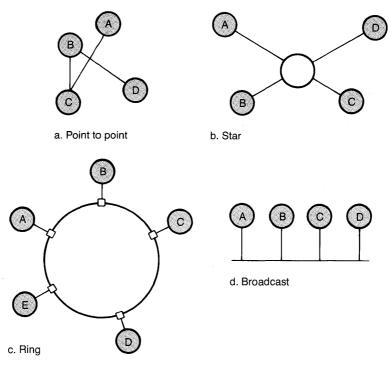

Networks 261 The Initial Bootstrap Problem 264 Summary 264 Exercises 265

# 12 The Support of an Operating System 266

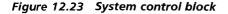

Sharing the Processor 267 Sharing the Memory 268 Processes 273 Processor Access Modes 274 Process Access Mode Stacks 275 Changing Modes 276 Checking for Accessibility 278 Process Context Switching 279 Summary of Process Concepts 280 VAX Memory Management 281 VAX Memory Structure 282 VAX Page Tables 284 VAX Address-Space Regions 285 System Space 287 Process Space 287 Privileged Processor Registers 290 Summary of Memory Management Concepts 292 Interrupt and Exception Handling 293 Interrupts and Exceptions 293 Interrupts 294 Exceptions 294 Interrupt and Exception Vectors 296 Software Interrupts 297 Summary of Condition and Exception Handling 299 Summary 299

Exercises 300

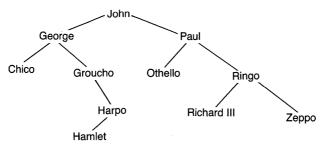

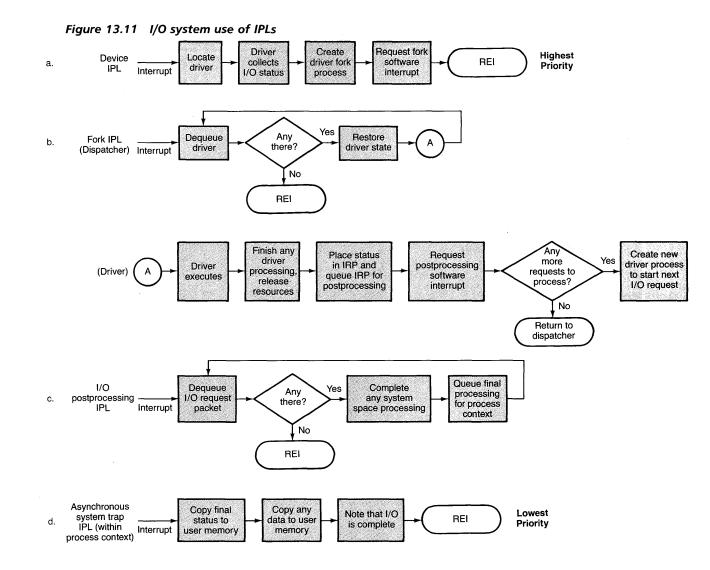

# **13** The Structure of a VAX Operating System 302

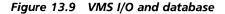

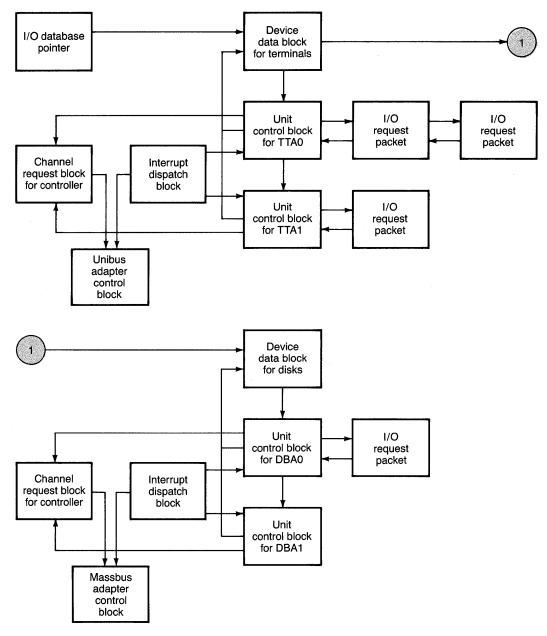

Process Scheduling 302 VMS Process Scheduling 303 VMS Scheduler Context-Switch Example 307 Process Paging 310 VMS Memory Management 313 Paging under VMS 314 Swapping under VMS 316 Input and Output Processing 317 The VMS I/O System 318 VMS I/O Database 319 VMS I/O System Components 321 I/O Control Flow 322 The Use of Interrupt Priority Levels 324 Synchronizing I/O Database Access 327 System Service Implementation 328 Summary 329 Exercises 330

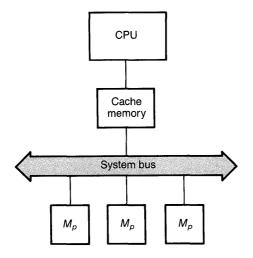

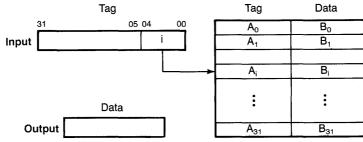

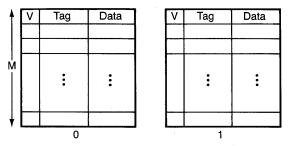

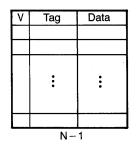

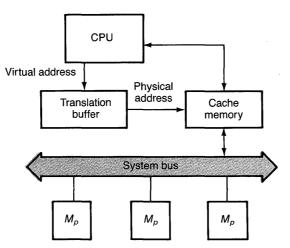

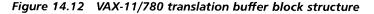

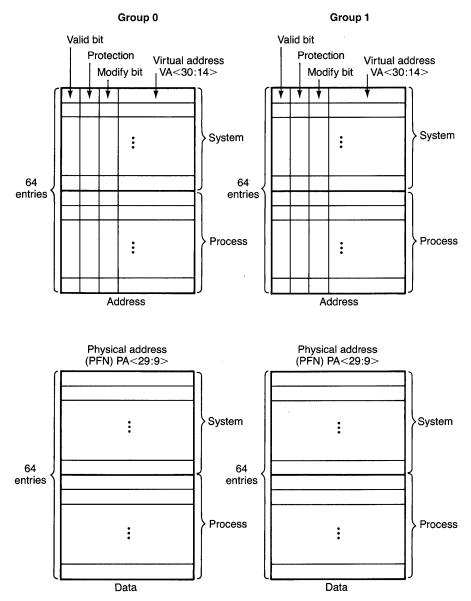

# 14 Caches and Translation Buffers 331

Choice of Memory Technology and Structure 331 The Fastest Technology Approach 332 Cache Memory Approach 332 Associative Memories and Cache Organization 333 Issues in Cache Design 336 Cache Coherency in Multiprocessors 339 Multilevel Caches 340 An Example Cache Organization: The VAX 6200 341 The Translation Buffer 344 The Instruction Buffer 347 Summary 348 Exercises 348

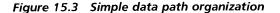

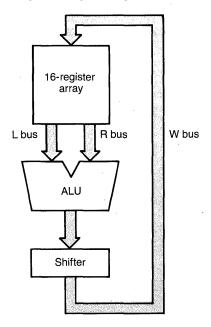

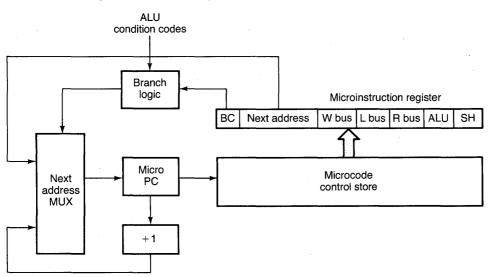

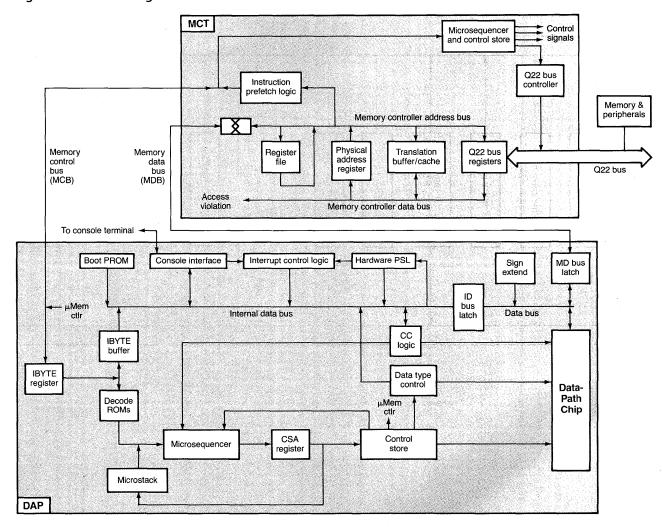

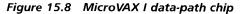

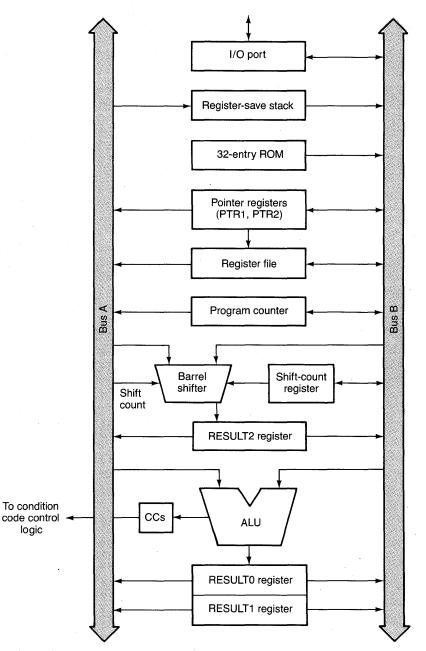

# 15 Microprogramming 350

Instruction to Microprogramming 350 Organization of a Simple Micromachine 352 *The Data Path in a Simple Machine 353* The Control Unit in a Simple Machine 356 The MicroVAX I Microarchitecture 358 *The MicroVAX I Data Path 360 MicroVAX I Data-Path Control 364 Microinstruction Branching 367 Execution of a VAX Instruction 370* Microarchitecture Alternatives 373 Exercises 374

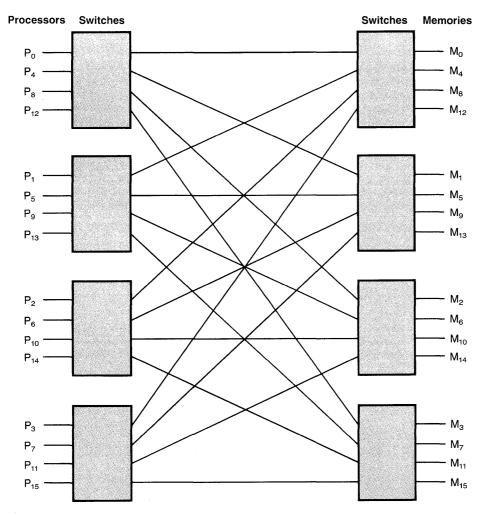

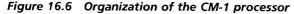

# 16 Parallelism and Parallel Computer Systems 376

Classifying Multicomputer Systems 378 Pipelined Processors 381 Multiple Functional Units and Hazards 383 Vector Machines: The Cray-1 385 Multiprocessors 387 *Multiprocessor Organizations 389 What Is Required for Multiprocessing? 393* Examples of Multiprocessor Systems 395 *The Connection Machine: A Highly Parallel SIMD Machine 395 The Butterfly: An Interconnection Network Machine 397 MIMD Hypercube Machines 398* Summary 400 Exercises 401 Contents

# Appendix A The Ultrix Assembler 403

Appendix B VAX Instruction Set Description 411

Bibliography 425

Index 429

# Preface

Like the first edition of our book, the intention of this second edition is twofold: to teach the architecture and organization of computer systems, and to provide a single reference on the details of one specific computer system, the VAX. Since the first edition, there have been many changes in the field and we wanted to reflect those changes in this edition. Also, we have used this book for several years to teach an undergraduate course in computer architecture and assembly language at the University of Washington. Based on this experience, we wanted to revise and expand the book to further develop our conceptual and pedagogical approach, particularly with respect to assembly language programming.

The book is divided into two parts. The first part, Chapters 1 through 10, is concerned with the architecture of a computer as seen by the assembly language or systems programmer. Chapters 1 through 8 cover the essentials normally taught in an assembly language or systems programming course. We have expanded the material from the first edition, added more examples, updated our coverage of the VAX and the VAX family, and provided a complete chapter on the assembler and debugger. Our examples use the VAX/VMS assembler syntax and I/O routines, but for those who wish to use Ultrix or Berkeley VAX/Unix, Appendix A describes the Ultrix assembler and how it differs from the VAX/VMS assembler. Chapter 9 is a short but unique new chapter on systems performance evaluation. It describes methods used to evaluate architectures and presents measurements that show how the VAX is used by real programs.

We believe that the best way to understand computer architecture is first to gain detailed experience with one specific architecture, and then to examine general principles. Thus, after examining the specifics of one machine, the VAX, Chapter 10 turns to architectural concepts that apply to all computers. The reader is introduced to instruction set design and the instruction-level architectures of four diverse computers for comparison with the VAX. The four systems chosen are the IBM 370, the CDC 6400, the Intel 80386, and the Berkeley RISC. The final section of that chapter examines the move toward reduced instruction set computers and the reasons for that trend, as well as describing the Berkeley RISC architecture.

The second part of the book, Chapters 11 through 16, considers

system-level issues in computer architecture, including high-level operating system support and low-level implementation alternatives. We believe that these chapters contribute to the unique aspect of our book, and have therefore developed them in several directions. Chapter 11 considers physical level I/O and related issues, such as network interconnection alternatives. Chapters 12 and 13 are a study of the relationship between architecture and operating systems. Chapter 12 provides a substantial discussion of architectural support for operating systems, and how the VAX architecture supports virtual memory, protection, processes, and so on. Chapter 13 describes the structure of the VAX/VMS operating system, concentrating on how it uses the architectural features described in Chapter 12.

Caches are now essential for increasing system performance, even on low-end computer systems, and Chapter 14 concentrates on the design of caches and translation buffers. The chapter describes issues and alternatives in cache design. Additionally, the chapter includes a discussion of the difficulties encountered with today's high-performance machines, such as cache coherency in multiprocessors and the need for multilevel caches.

To understand how a complex instruction set such as the VAX is implemented, and to appreciate alternatives such as the reduced instruction set (RISC) and very-long instruction word (VLIW) machine designs, one must examine the use of microprogramming. Chapter 15 is a new addition to the book; it presents the concepts and develops the multiple facets of microprogramming. Once the general concepts are presented, this chapter describes the microarchitecture of a real VAX implementation, examines the format and operation of its microinstructions, and shows how those microinstructions are used to execute the VAX instruction set.

Our final chapter, also new to the second edition, is concerned with parallel processing techniques that are becoming commonplace in the computer marketplace. Chapter 16 examines the internal use of parallelism within a processor (for example, pipelining), as well as the external use of parallelism through different interconnection structures to build multiprocessor systems. Examples of important multiprocessor systems are presented.

The reader of this book will most likely have programming experience in a high-level language and a knowledge of basic data structures. With that background and a thorough reading of our text, the reader will gain a sound understanding of computer organization and the important issues in contemporary computer architecture. The reader will also come to appreciate the relationship between the complex demands of today's operating systems and applications and the underlying support that is provided by the hardware.

Although the story is told with the VAX as the main character, we believe the book is generally applicable to the understanding of any

computer system. The techniques developed should enable the reader to quickly master any new machine encountered. It should also aid the reader in assessing the strengths and weaknesses of a particular architecture. Therefore, we believe that this book can be used successfully both as a teaching text for the college student and as a guide for the practicing professional.

#### Acknowledgments

We would like to thank the many people who helped in the production of both the first and second editions of this book. The many readers of our first edition and the reviewers of this second edition gave us valuable feedback on content and style. In particular, the students and teaching assistants of CS378 at University of Washington provided us with a wealth of experience in the use of the book for teaching, which we have used to produce this second edition. Robert Short helped us in understanding the operation of the MicroVAX microarchitecture. Finally, we would like to thank Digital Equipment Corporation and Digital Press for their technical and production support.

> Henry M. Levy Richard H. Eckhouse, Jr.

# Architecture and Implementation

There are two major levels at which we usually examine any computer system: architecture and implementation. Because we often refer to these terms, it is important to understand the distinction between them.

The architecture of a computer system is the user-visible interface: the structure and the operation of the system as seen by the programmer. Implementation is the construction of that interface and structure from specific hardware (and possibly software) components. There can be several different implementations of an architecture, each using different components, but each providing exactly the same interface to the user.

For example, let's examine the architecture of a piano. The definition of a piano's architecture is the specification of the keyboard, as shown in Figure 1.1a. The keyboard is the user (player) interface to the instrument. It consists of eighty-eight keys, thirty-six black keys and fifty-two white keys. Striking a key causes a note of specified frequency to be played. The size and the arrangement of the keys are identical for all piano keyboards. Therefore, anyone who can play the piano can play any piano.

There are many implementations of the piano, as shown in Figure 1.1b. The implementation is concerned with the materials used to build the instrument. The kinds of wood used, the selection of ivory or plastic keys, the shape of the instrument, and so forth, are all implementation decisions made by the piano builder. Regardless of the implementation decisions made, however, the final product can be played by any piano player.

In a computer system, the architecture consists of the programming interface: the instruction set, the structure and addressing of memory, the control of input/output (I/O) devices, and so on. There can be several implementations of an architecture, for example, one with vacuum tubes, one with transistors, and one with very large scale integrated (VLSI) circuits. Clearly, each of these implementations would have different size, cost, and performance characteristics. However, a program that runs on one machine would run on all of the machines following the architecture.

#### **Organization of This Book**

This book deals primarily with the architecture of one computer system: the VAX. VAX computers are manufactured by Digital Equipment Corporation. The best way to learn about the VAX architecture is by using

Figure 1.1 Architecture and implementation of the piano

a. Piano keyboard architecture

b. Piano implementations

#### Organization of This Book

it, and to use it you must become an assembly language programmer. As an assembly language programmer, you will learn how to control the operation of the hardware system directly. You will also gain a better understanding of how a compiler translates a high-level language program, and how the processor executes that program.

The first half of this book develops the basics of assembly language programming on the VAX. First, the elementary concepts of processors, memories, and instruction execution are introduced. More sophisticated addressing techniques are presented, and we build an instruction repertoire suitable for problem solving. From there, you will see how the VAX instruction set is used to manipulate more complex data structures.

Later, we use the concepts developed through the VAX to examine the instruction set architectures of several other machines: the IBM 360/370, the Control Data Corporation Cyber, the Intel 80386, and the Berkeley RISC II. This material provides an interesting basis for comparison and helps solidify the material already learned.

The second half of the book deals with the VAX architectural features used by the operating system. We show how the VAX supports the resource management activities of the operating system and how the VAX/VMS operating system uses these facilities. We also examine caches, which are memory buffers used to increase performance; microprogramming, a technique used for implementing complex systems such as the VAX; and multiprocessing, which is becoming a common technique for building cost-effective computer systems.

#### **Review of Number Systems**

Before beginning our examination of computer structures, it is worthwhile to review the basics of number systems. Throughout the book we use decimal, binary, and hexadecimal number systems. Therefore, the reader should be comfortable with these representations and with converting one to the other. Some readers may want to skip this section.

#### Number Systems

All data stored and manipulated in the computer is stored in binary form. Integers, floating-point numbers, characters, and instructions are all represented as a sequence of binary zeros and ones. When the value of a data item is output to a terminal or printer, or when we specify a value for input, we usually *display* the contents using base 8 (octal), base 10 (decimal), or base 16 (hexadecimal). These bases are easier for humans to deal with than long strings of binary digits. However, the *value* of a unit is the *same* regardless of the base used to represent it. Different bases are suitable for different applications. Bases 8 and 16 are particularly useful for looking for patterns of bits within a word, while base 10 is useful for understanding the decimal value of a word.

In the weighted numbering system, the value of a numeral depends on its position in a number. For example, in base 10

$$347 = 3 \times 100 = 300 +4 \times 10 = 40 +7 \times 1 = \frac{7}{347}$$

The value of each position in a number is its *positional coefficient*. The second factor or power of the base is called the digit-position weighting value, weighting value, or simply *weight*.

Using the positional coefficients and weights, we can express any weighted number system in the following generalized form:

$$X = x_n w_n + x_{n-1} w_{n-1} + \cdots + x_{-1} w_{-1} + \cdots + x_{-m} w_{-m}$$

where

$$w_i = r^i$$

( $r^i$  = weighting values and r = radix or base)

and

$$0 \le x_i \le r-1$$

( $x_i = \text{positional coefficients}$ )

This formalism makes it clear that the largest value of a positional coefficient is always one less than base value. Thus, for base 2 (binary), the largest coefficient is one; for base 10 (decimal), it is nine. Although this may seem intuitively obvious, it is not uncommon for the novice programmer or even some old-timers to write illegal numbers while coding programs, for instance, 10853 in base 8 or 102 in base 2. Equally confusing are bases greater than 10, in which positional coefficients are denoted by letters rather than numbers. In hexadecimal, for example, the letters A through F represent the numerical values 10 through 15, respectively.

Examples of writing the full expressions for weighted number systems follow:

$$140 = 1 \times 10^{2} + 4 \times 10^{1} + 0 \times 10^{0} \text{ (base 10)}$$

= 1 × 2<sup>7</sup> + 0 × 2<sup>6</sup> + 0 × 2<sup>5</sup> + 0 × 2<sup>4</sup> + 1 × 2<sup>3</sup>

+ 1 × 2<sup>2</sup> + 0 × 2<sup>1</sup> + 0 × 2<sup>0</sup> (base 2)

= 2 × 8<sup>2</sup> + 1 × 8<sup>1</sup> + 4 × 8<sup>0</sup> (base 8)

= 8 × 16<sup>1</sup> + C × 16<sup>0</sup> (base 16)

In other words,

$140_{10} = 10001100_2 = 214_8 = 8C_{16}$

Although these examples assume a positive radix, negative radices are also possible. For example, assuming a radix of -3, the value 140 can be expressed as

$140_{10} = 2 \times (-3)^4 + 1 \times (-3)^3 + 1 \times (-3)^2 + 2 \times (-3)^1 + 2 \times (-3)^0 =$  $21122_{-3}$

It is even possible to conceive of nonweighted number systems-and such systems do exist-such as "Excess -3" and "2 out of 5," but discussion of these systems is beyond the scope of this book.

#### **Binary and Hexadecimal Representations**

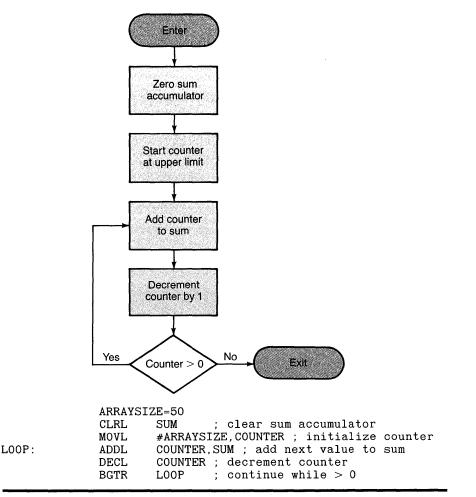

Because of the inherent binary nature of all computer components, modern digital computers are based on the binary number system. However, no matter how convenient the binary system may be for computers, it is exceedingly cumbersome for human beings. Consequently, most computer programmers use base 8 or base 16 representations instead, leaving it to the various system components—assemblers, compilers, loaders, and so on—to convert such numbers to their binary equivalents. Modern assemblers also permit decimal numbers, both integer and real (floating-point), to be input directly, a useful convenience for most applications programs. Table 1.1 shows the binary, octal, and hexadecimal equivalents of the decimal values zero through sixteen.

| Table 1.1 | Conversion Table |       |             |

|-----------|------------------|-------|-------------|

| Decimal   | Binary           | Octal | Hexadecimal |

| 0         | 0000             | 0     | 0           |

| 1         | 0001             | 1     | 1           |

| 2         | 0010             | 2     | 2           |

| 3         | 0011             | 3     | 3           |

| 4         | 0100             | 4     | 4           |

| 5         | 0101             | 5     | 5           |

| 6         | 0110             | 6     | 6           |

| 7         | 0111             | 7     | 7           |

| 8         | 1000             | 10    | 8           |

| 8<br>9    | 1001             | 11    | 9           |

| 10        | 1010             | 12    | Α           |

| 11        | 1011             | 13    | В           |

| 12        | 1100             | 14    | С           |

| 13        | 1101             | 15    | D           |

| 14        | 1110             | 16    | E           |

| 15        | 1111             | 17    | F           |

| 16        | 1 0000           | 20    | 10          |

Base 8 and base 16 representations of binary numbers are not only convenient but also easily derived. Conversion simply requires the programmer to separate the binary number into 3-bit (for octal) or 4-bit (for hexadecimal) groups, starting with the least significant digit and replacing each binary group with its equivalent. Thus, for the binary number 010011100001,

$010 \ 011 \ 100 \ 001_2 = 2341_8$

and

$0100 \ 1110 \ 0001_2 = 4E1_{16}$

This process is performed so naturally that most programmers can mentally convert visual representations of binary numbers (computer displays) to their octal or hexadecimal representation without conscious effort. Special pocket calculators that operate in both octal and hexadecimal are available as an aid in debugging programs. Fortunately, the tools of the assembly language programmer—the program listings, linker maps (showing locations of variables and modules), and dumps (displays of the contents of memory)—are expressed in at least octal or hexadecimal. Programmers need not be concerned with bits and binary numbers unless they choose to. However, when examining the bit patterns that make up the different data elements within the computer, the programmer has no alternative but to use bits and binary numbers. The next section examines these patterns.

#### **Negative Numbers**

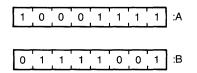

For any base, there are three common ways to represent negative numbers. Negative binary numbers, for example, can be represented in <sup>-</sup> sign-magnitude form, one's-complement form, or two's-complement form. One might ask, therefore, which form a computer would use in performing arithmetic calculations.

Sign-magnitude numbers are represented by treating the most significant bit as the sign bit and the remaining bits as the magnitude. Therefore, the 6-bit representation of  $\pm 18$  would be:

| $+18_{10}$ | 010010 <sub>2</sub> |

|------------|---------------------|

| $-18_{10}$ | 110010 <sub>2</sub> |

Addition and subtraction require a consideration of both the signs of the numbers to be added as well as the relative magnitudes in order to carry out the required operation.

Complement form for negative numbers takes advantage of the

continuum of representation. While the most significant bit remains the sign bit, the representation of the magnitude is different for negative numbers and positive numbers. The one's-complement representation is formed by taking the positive number and inverting all the bits. The two's-complement representation is formed by adding one to the one's-complement representation. For example, the 8-bit representations of  $\pm 18$  are:

| $+18_{10}$ | $00010010_2$          |                       |

|------------|-----------------------|-----------------------|

| $-18_{10}$ | 11101101 <sub>2</sub> | One's-complement form |

| $-18_{10}$ | $11101110_2$          | Two's-complement form |

Sign-magnitude form is rejected in favor of complement form because it is more complex to add or subtract numbers using sign-magnitude arithmetic. Thus, the choice of form for negative binary numbers is really between one's-complement and two's-complement representations. In reality, the choice is frequently one of the designer's preference. Generating one's-complement numbers is easier than generating two'scomplement form. Moreover, from the computer hardware point of view, it is more "uniform" to build a one's-complement adder than a two'scomplement adder. On the other hand, one's-complement notation has two representations of zero, both a positive and a negative zero:

| 0000 | $0000_{2}$ | Zero                           |

|------|------------|--------------------------------|

| 1111 | $1111_{2}$ | Minus zero in one's complement |

whereas only one zero exists in two's-complement form:

|                                   | 0000 | $0000_{2}$ | Zero                     |

|-----------------------------------|------|------------|--------------------------|

|                                   | 1111 | $1111_{2}$ | One's complement         |

|                                   |      | $+1_{2}$   | Plus one                 |

| <i>discarded</i> $\rightarrow$ 1) | 0000 | 00002      | Two's complement of zero |

Mathematically speaking, it is inconvenient to have two representations for zero. It is also more difficult to test for zero, an operation performed frequently on computers. As a result, most machines today use two's-complement notation to represent negative numbers. Remember that one's-complement and two's-complement are simply methods for *representing* signed integers in binary. Positive integers have the same representation in both one's complement and two's complement, but negative integers have different representations.

Forming the complement of a hexadecimal number may seem strange at first. Compared with binary, where one simply "inverts" the bits, hexadecimal complementation requires a subtraction of each digit from hexadecimal "F" (and an addition of one for the two's-complement result). For example,

| 3C8E | Original number  |

|------|------------------|

| C371 | One's complement |

| +1   |                  |

| C372 | Two's complement |

Fortunately, as with all such techniques, familiarity comes with use.

After this brief digression, we can now turn our attention to the general structure of computer systems and the architecture of the VAX. You will find that an understanding of hexadecimal and binary number systems is helpful to your understanding of computer concepts.

#### **Exercises**

- 1. Describe the architecture of a typewriter. What parts of the typewriter are not part of the architecture? What are some implementation differences among different typewriters?

- 2. Why do you think it is important to define precisely a computer's architecture?

- 3. Why do you think different computer manufacturers build computers with different architectures? What does this imply about the importance of high-level languages? Why is there a need for standardizing high-level languages?

- 4. What effect do you think the standardization of operating systems will have on computer architectures?

- 5. What range of integers can be represented in a 12-digit unsigned binary number? In a 12-digit two's-complement signed number?

- 6. Why are octal and hexadecimal useful for recognizing patterns of binary digits but decimal is not?

- 7. Is 10234 a legal value in base 8? base 16? base 5? base 4? Express the value  $10234_5$  in base -3.

- 8. Convert 101010101 into hexadecimal and octal. Convert 10A34<sub>16</sub> into octal and decimal. Negate both values using 32-bit binary two's-complement form.

- 9. Add +18 and -18 using each of the three representations for negative numbers. Use 8-bit arithmetic and either binary or hexadecimal representations.

- 10. Perform the following hexadecimal arithmetic:

a. 205 - 6 b. AF9 + 9 c. 10 \* 10 d. 1CFF + F2FF

- 11. Write a high-level language program that inputs a decimal number and a radix and outputs the value of that decimal number in the specified radix. For example, if the inputs are 10 and 16, the output should be A (that is, the value of 10 decimal is A in base 16). Limit yourself to bases less than or equal to 16.

- 12. Subtraction can be implemented by complementation followed by addition. Suppose you are to subtract  $-56_{10}$  (*C*8<sub>16</sub>) from  $27_{10}$  (1*B*<sub>16</sub>). Show how this could be done.

# **2** Computer Structures and the VAX

Depending on the nature of the application and the language chosen, programming a computer requires different levels of understanding. For most programmers writing in Pascal, for example, the computer appears to be a machine that executes Pascal statements and manipulates highlevel data structures. The structure of the underlying hardware is invisible.

This chapter introduces the fundamentals needed by the assembly language programmer. To program at the assembly level, you need a thorough understanding of the structure of a computer system, the process of program execution, and the nature of memory addressing. Once you have this foundation, you can begin to focus on the basics of instructions and elementary programming for a particular machine.

#### **Computer Structures**

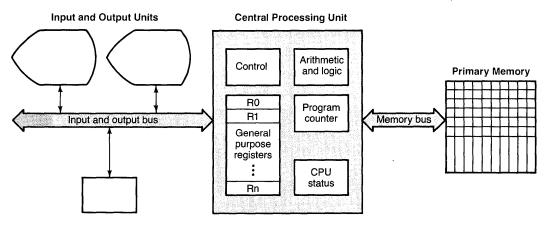

Most general-purpose computers have the same basic structure, consisting of the high-speed primary memory, the arithmetic control unit (typically called the *central processing unit*, or CPU), and the peripheral *input* and *output* devices (the I/O system). One or more *buses* (described in more detail later) move data between these components. Although there are other components of interest, these units are directly visible to the machine-level programmer and are part of the user architecture. Figure 2.1 shows an organizational representation of this basic structure.

#### The Memory

The memory of a computer is a repository for both instructions and data. Memory can be implemented by any device that can retain two or more distinguishable states that can be set and sensed. All common memories are composed of two-state devices that can represent the values zero and one. Hence, each device—such as a magnetic core, a semiconductor flip-flop, or a two-sided coin—can represent one binary digit, or *bit*.

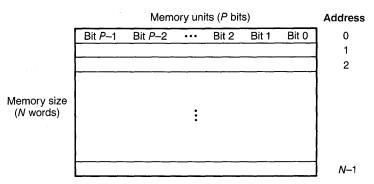

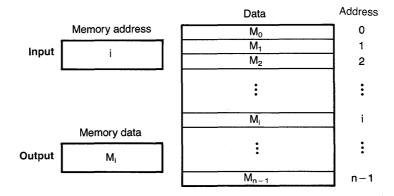

Bits in memory are arranged as an array of information units, with each information unit composed of a fixed number of bits. Each information unit resides in a distinct location in memory, and each location is capable of holding one such unit, as shown in Figure 2.2.

Figure 2.1 Basic computer structure

All memories share two organizational features:

- 1. Each information unit is the same size.

- 2. An information unit has a numbered address associated with it by which it can be uniquely referenced.

Thus, we say that a memory unit is characterized by two things:

- 1. An *address*, which is its relative position in memory.

- 2. The *contents*, which is a number that is physically stored at the particular location in memory.

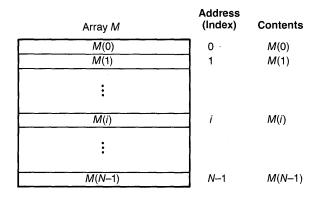

As Figure 2.3 shows, memory can be viewed as a large onedimensional array, M(i), where each element of the array contains one unit

#### Figure 2.2 Memory organization

#### Figure 2.3 Memory as an array

(word) of information. The index, i, is the address of the unit. Using its address, we can determine the contents of any unit. It is important to remember, however, the difference between the address of a unit, i, and the contents of the unit, M(i).

When a computer is designed, the size of its information units is chosen according to the applications for which the computer is intended. On many machines, each information unit is known as a *word*. Word sizes typically range from 8 bits on early microprocessors to 64 bits on large scientific computers. A word is usually divided into a number of *bytes*, with each byte representing one character. Machines designed for administrative data processing, in which information to be processed includes names and letters as well as numbers, are often *byte addressable*. In these machines, the byte is the basic information unit, and each byte has a unique address by which it can be accessed. On the other hand, wordaddressable machines are generally used for scientific calculations in which large numbers are manipulated and precise numerical results are required.

The key difference between byte and word machines is the size of the smallest addressable information unit. For a byte machine, this unit is one byte, that is, a unit of information capable of holding a small number or representing a letter of the alphabet or a digit. For a word machine, the smallest addressable unit is one word, a unit of information capable of holding several characters or a large number. Words can often be subdivided into a fixed number of characters or digits. In a true word machine, however, we can reference only the collection, not the individual characters. Thus, the value of the subdivision is its storage efficiency.

The *address space* is the set of all addresses, or the collection of distinct information units that a program can reference. The size of the address space is determined by the number of bits used to represent an address. An address is usually less than or equal to the word size for a given machine. Early minicomputers and microprocessors typically used 16-bit addresses, yielding 2<sup>16</sup>, or 65,536, unique memory locations. Programmers

quickly discovered, however, that 16 bits of address were insufficient for representing large data structures or solving complex problems. Typical modern computers, including the VAX, use 32-bit addresses that provide a memory address space of  $2^{32}$ , or 4,294,967,296, unique addresses and therefore can support much larger programs and data structures. While it may be hard to imagine using up 4 *gigabytes* of address space, programmers are ingenious in their ability to consume all available computer resources. Some applications do require this much data, and we can already see machines with address spaces even larger than  $2^{32}$ .

#### The Central Processing Unit

The central processing unit (CPU) is the brain of the computer. The CPU is capable of fetching data from and storing data into memory. It requests instructions from memory and executes them, performing arithmetic and logic operations specified by the instructions. The CPU can manipulate addresses as well as data. In addition, the processor can examine a memory location and follow different program paths, depending on its value. Finally, the CPU can execute instructions that initiate input and output operations on peripheral devices.

Internal to the CPU are a number of *registers* that provide local, high-speed storage for the processor. These registers can hold program data and memory addresses. Some computers have different sets of registers to perform different functions, for example, to address arrays or to represent floating-point numbers; others have general-purpose registers that can be used for any function.

Also internal to the CPU are one or more status words that describe the state of the processor, the instruction being processed, any special conditions that have occurred, and the actions to take for special conditions.

#### Instruction Execution

A computer is controlled by a *program*, which is composed of a sequence of *instructions*. Each instruction specifies a single operation to be performed by the CPU. Instructions can be classified into five basic categories:

- 1. *Data movement* instructions move data from one location in memory to another or between memory and I/O devices.

- 2. *Arithmetic* instructions perform arithmetic operations on the contents of one or more memory locations, for example, they add the contents of two locations together or increment the contents of a location.

- 3. *Logical* instructions perform logic operations such as AND, OR, and EXCLUSIVE OR.

- 4. *Comparative* instructions examine the contents of a location or compare the contents of two memory locations.

- 5. *Control* instructions change the dynamic execution of a sequence of instructions by causing program execution to be transferred to a specified instruction, either unconditionally or based on the result of a comparative, arithmetic, or logical instruction.

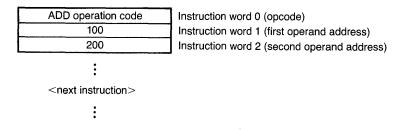

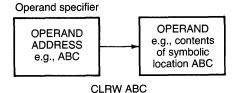

Instructions are stored in memory along with the data on which they operate. The processor fetches an instruction from memory, interprets what function is to be performed, and executes the function on its operands. Each computer has its own representation of instructions, but all instructions are composed of two basic components:

- 1. An *operation code* (opcode), which specifies the function to be performed, for example, Add, Subtract, Compare.

- 2. One or more *operand specifiers*, which describe the *locations* of the information units on which the operation is performed. These information units are the *operands* of the instruction.

An instruction in memory can occupy several consecutive words (or bytes): one for the operation code and, optionally, several more for the operand addresses. For instance, an instruction to add the contents of memory location 100 to memory location 200, shown symbolically as

ADD 100,200

can be represented in computer memory as follows:

The processor executes a program by fetching and interpreting instructions. The location (memory address) of the next instruction to be executed is held in a special internal CPU register called the *program counter* (PC). When the program is loaded into memory, the PC is loaded with the address of the first instruction. Using the PC, the CPU fetches this instruction, along with any operand specifiers. The operands themselves are then fetched, the operation is performed, and any results generated are

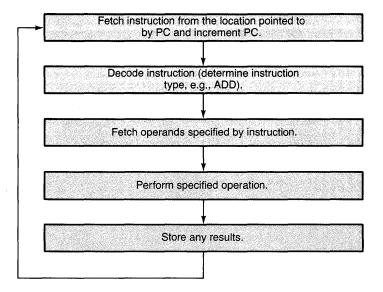

stored back in memory. Figure 2.4 shows the complete cycle of fetching, interpreting, and executing an instruction.

Note that each time an instruction is fetched, the PC is modified to point to the next instruction. Thus, the processor executes instructions one after another. Some instructions, like "branch" (the machine-level GO TO), affect the flow of control by explicitly changing the contents of the PC so that a new location, not the next one in sequence, is taken to be the one containing the next instruction to be executed. Otherwise, instructions are fetched and executed sequentially from memory.

A computer program, then, consists of two parts: instructions and data. When loaded into memory, each instruction and data element is located at a unique address. Looking at the program as a string of words or bytes, we are unable to differentiate data from instructions because both are merely strings of numbers coded in binary. We are also unable to differentiate data types because integers, floating-point numbers, character strings, and so on, are represented as strings of binary numbers, too. Only in context does the program have meaning.

The key to making sense of the string of numbers representing a program is the starting address of that program, since that tells the CPU where to find the first instruction to execute. The first instruction in the program can be located anywhere in the memory of the computer. The programmer specifies the starting address of the program by means of a directive to the language translator or to the program loader. (In a high-level language, this is the main program or procedure.) When the operating system loads the program into memory, it transfers control to that initial instruction by making sure that the initial contents of the PC "point to" the address of the starting instruction. As each instruction and operand is fetched in sequence, the PC is incremented so that it points to the next byte or word to be fetched.

## **Classes of Instruction Architectures**

Computer instruction sets vary greatly from machine to machine. A later chapter looks at some different architectures to contrast them with the VAX, which is presented in more detail. In general, however, we can classify instruction sets into several categories. These categories are chosen based on the operand-addressing techniques available in the machine.

Simplest of the categories are *zero-address* instruction sets, also known as stack-based instruction sets. Part of the processor state for such a machine includes a stack pointer to the top of a stack. The stack, which is simply a last-in first-out list, can be stored in memory or in the processor. The stack pointer is an implicit operand for most instructions and does not need to be specified explicitly. For example, on such a machine, the instructions

```

PUSH A

POP B

```

cause the contents of memory location A to be placed on the top of the stack (as a result of the PUSH); the contents of the top of the stack are then removed and copied into memory location B (as a result of the POP). Arithmetic instructions always operate on the top one or two elements of the stack, depending on whether they are unary or binary operations. For example, the instruction

ADD

would add the two top elements of the stack together, popping those elements from the stack and pushing the sum onto the top of the stack. Such machines are called zero-address machines, because arithmetic operations such as ADD have no operands; the operands are implicitly known to be the top two stack elements. Not only do some computers operate in this fashion, but some calculators use stacks also.

A *one-address* instruction set has, as its name implies, instructions with one address. Typically, such machines have a single register, called the *accumulator*. Just as the stack is an implied operand for instructions on the stack machine, the single accumulator is the implied operand for instructions on the one-address machine. Suppose we want to add the contents of memory locations A and B, putting the result in location C. On a one-address machine we would probably write

LOAD A ADD B STORE C

The LOAD instruction loads the contents of memory location A into the accumulator, while the ADD adds the contents of location B to the accumulator. Finally, the STORE instruction copies the contents of the accumulator into memory location C. Architectures such as this, in which arithmetic can be done only in registers, are known as *load and store* machines. In such machines, it is not possible to add a number directly to a memory location. Instead, one operand must first be loaded into a register and the summation formed there.

A *two-address* instruction set allows two operands to be specified in the instruction, for example,

ADD A, B

adds the contents of location A to the contents of location B. When the addition is completed, the contents of location A are unchanged, and location B contains the sum. Finally, *three-address* instructions such as

ADD A, B, C

allow the result of the summation to be written to a third location.

These are just some of the options available to the designer of an instruction set, and many tradeoffs can be made. Some instruction sets have characteristics of several of these options. In general, the more operands an instruction set allows, the more powerful instructions tend to become. But as the instruction set becomes more powerful, the hardware required to implement that instruction set becomes more complex.

## The Input/Output System

Connected to the processor and memory are several input and output (I/O) devices. The I/O devices allow the processor to communicate with humans, with other processors, and with secondary storage devices that are slower than main memory but larger in capacity.

The most common devices are magnetic disks, magnetic tapes, terminals, and printers. Magnetic disks and tapes provide large online or backup storage for programs and data. These devices are usually capable of transferring large blocks of data directly to primary memory. In contrast, the processor must feed or retrieve one character at a time to or from most terminal devices.

Because all these devices are slow compared to the execution speed of a modern CPU, systems are designed to overlap processing with I/O. That is, the processor begins an I/O operation on a device and then continues executing program instructions. The processor can check later to see if the operation is complete, or the device can signal when it is done.

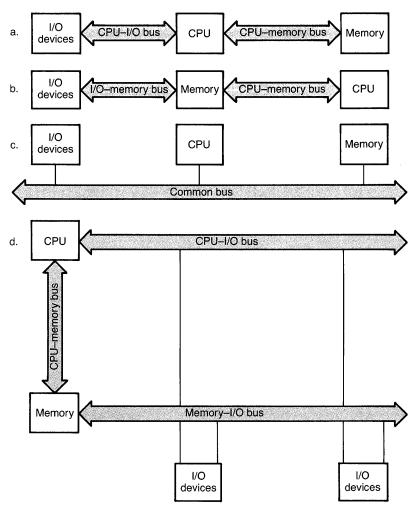

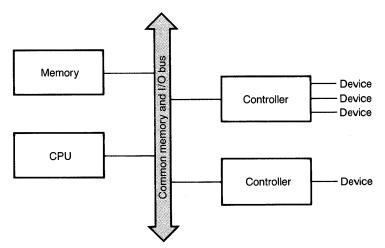

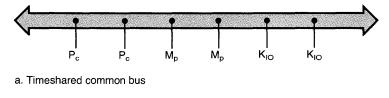

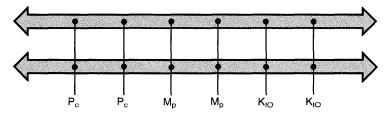

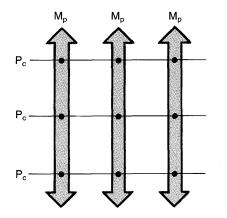

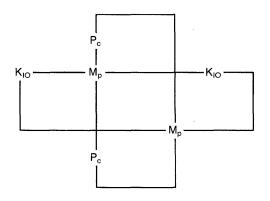

One or more data buses can be used to interconnect the CPU, memory, and I/O devices. Some computers have two (or more) buses, one to connect the memory to the CPU, another to connect I/O devices to the CPU. Other computers use one bus for all transfers among I/O devices, memory, and the CPU. Figure 2.5 shows some alternatives in the interconnection of the CPU, memory, and I/O devices.

Whether there is one bus or several, the purpose remains the same: to carry address, data, and control signals among the devices connected to the bus. The address and control signals specify the device and the function to be performed on the data. The bus is like a common highway for computer information flow. Any device connected to it can place information onto the highway; conversely, any device can take information from the bus. The bus thus provides an efficient means for passing information among the functional units connected to it.

## **Describing Computer Structures**

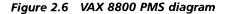

From a structural level, computers consist of the basic components we have described: processors, memories, buses, I/O devices, and so on. One way to describe the structure of a computer is to use a notation called PMS, for processor, memory, and switch. PMS notation is described in detail in *Computer Structures: Principles and Examples* by Siewiorek, Bell, and Newell. The objective of PMS is to provide a pictorial means of showing the high-level organization of a system.

A PMS diagram consists of a stick-figure drawing of a system's components connected with lines showing the physical interconnection. Some of the component types shown are

- *P* (processors). The central processor, shown as  $P_c$ , controls the overall operation of a computer. However, a computer can have other processors, for example, an I/O processor,  $P_{io}$ , or a slave processor,  $P_{slave}$ .

- *M* (memories). Computers have several levels of memories, such as the primary memory, *M<sub>p</sub>*, or secondary memories, *M<sub>s</sub>*.

- *S* (switches). A switch is a bus or any device that interconnects several components of the system, transferring information to one or more components at a time.

- *L* (links). A link is a point-to-point interconnect between two specific components of a system.

- *T* (transducers). A transducer changes information from one form to another, for example, from electrical impulses to mechanical actions.

Figure 2.5 Alternative bus structures

Terminals, line printers, tape readers, and card readers are all transducers.

• *K* (controllers). A controller is a unit that manages the actions of another device, typically an I/O device.

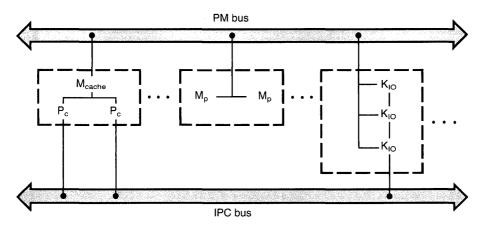

Figure 2.6 shows a PMS diagram of a VAX 8800 configuration. A component description can be augmented with details about specific characteristics of the component, or the details can be listed as a footnote, for example,

P<sub>c</sub>['CVAX; 80ns cycle time; technology: CMOS VLSI microprocessor]

#### Notes

- 1. P<sub>c</sub>['VAX 8810; 45ns cycle; 64 KB cache; variable-length instructions; 8-, 16-, 32-, 64- and 128-bit data types; technology: 1200-gate ECL gate array]

- 2. Pc['Second processor on dual processor VAX 8820]

- 3. S['Memory interconnect bus; 32-bit; synchronous; 4/16/32 byte transfer; 45ns cycle; 60 megabytes/second]

- 4. M<sub>o</sub>[16 megabytes/module; MOS dynamic RAM]

- 5. K['Memory bus to BI adapter]

- 6. S['BI bus; 32 bit; synchronous; 200ns cycle]

# Introduction to the VAX

The VAX is a general-purpose digital computer manufactured by Digital Equipment Corporation. The VAX architecture was designed to extend the addressing capabilities of its predecessor, the PDP-11 minicomputer; hence, the name VAX, for Virtual Address eXtension. Over a dozen VAX implementations have been produced. The VAX has a high-level architecture that contains many features to support operating systems and compiler code generation. The VAX instruction set currently includes over 300 instructions and over 20 formats for operand specifiers, called addressing modes. This flexibility enables the programmer and the compiler to select instruction and addressing combinations that are both space- and time-efficient. Thus, algorithms implemented with the VAX instruction set architecture are generally compact (compared to the same algorithm implemented on other architectures, including the PDP-11) and fast (compared to programs running on other machines using the same hardware technology).<sup>1</sup>

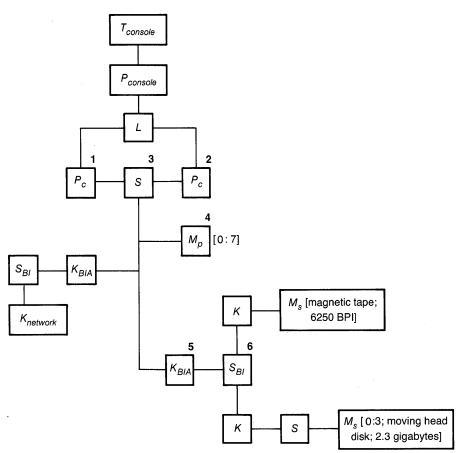

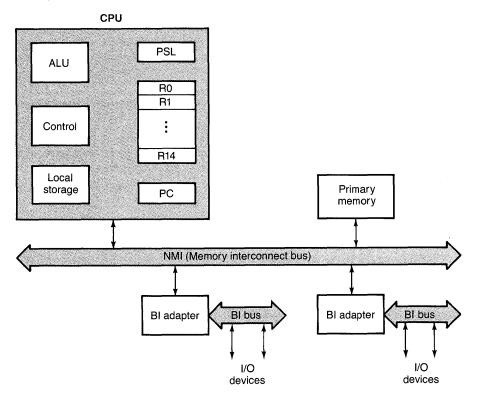

Figure 2.7 shows the logical organization of a VAX 8810 computer system. In fact, each VAX implementation has a different internal structure that was chosen for the particular price and performance range of the machine. Figure 2.7 resembles the structure of the general computer shown in Figure 2.1. The VAX CPU shown in the center of Figure 2.7 is the

## Figure 2.7 VAX organizational structure

<sup>1</sup>In fact, there is controversy as to whether high-level architectures like the VAX or much simpler "reduced instruction set computers" (RISCs) will achieve better performance. We discuss this further in Chapter 10.

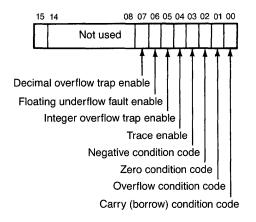

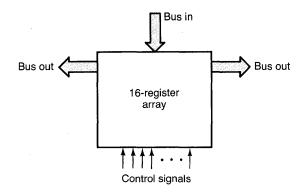

master controller of the VAX system. The processor contains sixteen 32-bit general-purpose registers that provide high-speed local storage for programs. Several of these registers have special uses; in particular, one is the program counter and one is used as a stack pointer. Also internal to the CPU is the 32-bit processor status longword (PSL) that contains information about the processor and the current state of the program being executed. The PSL is composed of two 16-bit words. The lower 16 bits, called the program status word (PSW), contain information about the user program and are user accessible. The upper 16 bits contain privileged processor information and can be modified only by the operating system. Thus, the user program can examine and change program state information, but processor state is protected from user modification.

A common system bus connects the CPU, memory, and I/O buses. Through this bus, all input and output devices are connected so that they can communicate with each other, as well as with the CPU and memory. Indeed, it may be possible for I/O devices to send and receive data among themselves and memory without processor intervention.

A memory controller connects the CPU to the memory subsystem. The controller can perform functions such as reading large amounts of data at a time in anticipation of future requests, buffering read and write requests, and so on. Current large VAX systems allow for several hundred megabytes of primary memory; smaller single-user VAXes are typically configured with 10 to 20 megabytes.

New VAXes are typically designed with their own internal system bus through which memory and components of the CPU communicate. To allow existing I/O devices to be attached to the new bus, special *bus adapters* are designed. These adapters allow existing devices to be connected to the VAX system without change, thereby offering benefits in development cost and time. Devices can thus be made immediately available for a new machine by providing an interface between the new computer bus and existing I/O buses.

For example, many VAX implementations use an I/O bus called the backplane interconnect (BI), to which numerous device controllers connect. If a user has peripherals that use an older bus called the Unibus, a special BI-to-Unibus adapter can be used; the older Unibus devices connect to a Unibus, which attaches to the BI-to-Unibus adapter, which attaches to the BI bus.

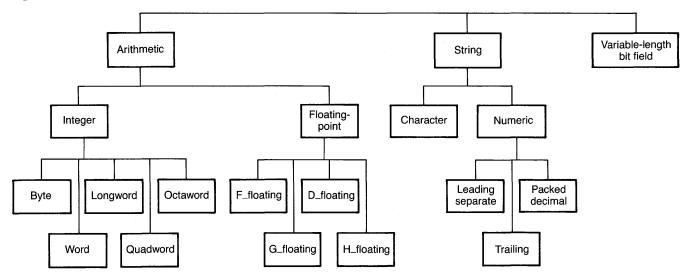

## VAX Information Units and Data Types

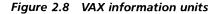

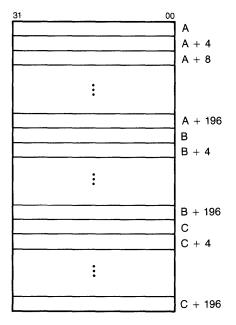

We have already described byte-addressable and word-addressable machines. In the context of that discussion, it is appropriate to say that the VAX is a byte-oriented computer. The basic information unit on the VAX is the 8-bit byte. However, the instruction set is also capable of operating on a

number of other information units formed by groups of bytes and bits. The multiple-byte units are the 16-bit *word* (two bytes), the 32-bit *longword* (four bytes), the 64-bit *quadword* (eight bytes), and the 128-bit *octaword* (16 bytes), shown in Figure 2.8. Each of these information units is formed by a sequence of contiguous bytes. The unit is always addressed by the low-order byte of the group. Note that the bits within any information unit are numbered from the least significant bit, bit 0, on the right. The most significant bit (bit 7, 15, 31, 63, or 127 for byte, word, longword, quadword, or octaword, respectively) is on the left.

For example, suppose the bytes beginning at location 400 in memory have the values shown below:

| 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | :400 |

|----|----|----|----|----|----|----|----|------|

|----|----|----|----|----|----|----|----|------|

Location 400 is the address of a byte whose value is  $01_{16}$ . It is also the address of the word whose value is  $0201_{16}$ , the longword whose value is  $04030201_{16}$ , and the quadword whose value is  $0807060504030201_{16}$ . Similarly, location 401 is the address of the byte whose value is  $02_{16}$ , the word whose value is  $0302_{16}$ , and so on. Every information unit is addressed by its low-order byte; it is up to the compiler or the assembly language programmer to determine what information units are stored at which addresses and to use the proper instructions to manipulate them.

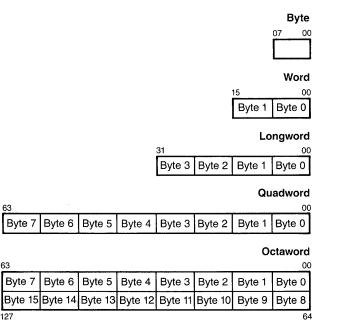

#### Figure 2.9 Variable-length bit field

VAX registers can store any of the VAX information units. Since each register is 32 bits, a register typically holds a single longword. However, two adjacent registers can hold a quadword and four adjacent registers can hold an octaword. In this case, the entire information unit is named by the lower numbered of the adjacent registers. That is, if a quadword is stored in register 2 (R2) and register 3 (R3), we specify the unit by R2.

Another information unit found in the VAX is the variable-length *bit field*. The bit field is different in that the basic addressable unit is based on a length measured not in bytes but in bits. A bit field can be from 0 to 32 contiguous bits in length and can be located arbitrarily with respect to the beginning of a byte. To describe a bit field, three attributes are required: (1) a *base address* of a particular byte in memory chosen as a reference point for locating the bit field; (2) a *bit position* that is the starting location of the field with respect to bit 0 of the base address byte; and (3) a *size* giving the length of the bit field in bits. For example, Figure 2.9 shows a bit field with base address A, bit position P, and size S.

Bit fields are commonly used to pack multiple information fields tightly together. For example, Boolean values (sometimes called "flags") can be packed eight per byte. In this context, bit field instructions allow the programmer to manipulate fields smaller than a byte.

The byte, word, longword, quadword, and octaword are the fundamental information units of the VAX. Built on these information units are *data types*, which are *interpretations* of the bits contained in the units. All information units contain a string of binary digits, but a unit can represent an integer, a letter of the alphabet, a real number, and so forth. The VAX processor is capable of manipulating a great variety of data types. The choice of data type allows the programmer (or the compiler) to produce compact programs using those data types most closely tailored to his or her needs. There is also a full set of instructions for converting easily from one data type to another, which reduces the complexity of many programs.

#### Integers

Integers are represented as both unsigned binary numbers and two's-complement signed numbers, and can be stored in byte, word, longword, quadword, or octaword elements. The choice of storage representation for an integer determines both the maximum value of the number to be stored and the efficiency of the representation (that is, the number of bits used effectively). Table 2.1 shows the numeric range for the various integer sizes. The VAX has a complete set of instructions for adding, subtracting, dividing, multiplying, complementing, and shifting integers. (In fact, quadword and octaword arithmetic is not fully supported by VAX instructions, for example, there is no single instruction to add quadwords or octawords, so programmers should be careful when designing algorithms using those information units. However, the VAX does have instructions for implementing multiprecision arithmetic on large unsigned numbers using multiple longword add with carry instructions.)

A complete set of conditional branch instructions allows the programmer to alter the flow of control based on the result of previous arithmetic operations. Because the most significant bit of a two's-complement number always indicates the sign, the hardware can easily test for positive or negative.

|              | Range (decimal) |                           |                    |  |  |  |

|--------------|-----------------|---------------------------|--------------------|--|--|--|

| Integer Type | Size            | Signed                    | Unsigned           |  |  |  |

| Byte         | 8 bits          | -128 to +127              | 0 to 255           |  |  |  |

| Word         | 16 bits         | -32768 to +32767          | 0 to 65535         |  |  |  |

| Longword     | 32 bits         | $-2^{31}$ to $2^{31}-1$   | 0 to $2^{32}-1$    |  |  |  |

| Quadword     | 64 bits         | $-2^{63}$ to $2^{63}-1$   | 0 to $2^{64} - 1$  |  |  |  |

| Octaword     | 128 bits        | $-2^{127}$ to $2^{127}-1$ | 0 to $2^{128} - 1$ |  |  |  |

|              |                 |                           |                    |  |  |  |

Table 2.1 Integer Data Types

## Floating-Point Numbers

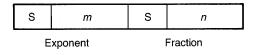

Integers are useful for data representation and problem solution in many areas, but they often lack the dynamic range necessary for a variety of scientific applications. Although integers represent the data with sufficient precision, the magnitude of the data or the intermediate results may exceed the range defined by the width of the data word. A *floatingpoint* number, like an integer, is a sequence of contiguous bits in memory. However, the bits are interpreted as having two distinct parts, the *fraction* (or mantissa) and the *exponent*. That is, a floating-point number might be stored in a computer word as

and interpreted as  $\pm 0.n \times 2^{\pm m}$ , where *n* represents the bits in the fraction

field and *m* represents the bits in the exponent field. Note that we have arbitrarily allocated two sign bits to allow positive and negative fractions and exponents. It is more common to assign only one sign bit to a word. Thus, a different representation is used in which the most significant bit of the word is the sign of the fraction and the exponent is represented as a positive (*biased*) value. In other words, although the exponent is a positive number in the range 0 through m-1, half of the exponent range (0 to m/2-1) is used to represent negative numbers while the other half (m/2 to m-1) represents positive numbers.

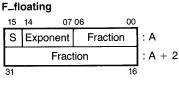

The VAX has four floating-point formats: F\_floating, D\_floating, G\_floating, and H\_floating. The formats of these floating-point data types are shown in Figure 2.10, and their range is described in Table 2.2. Originally the VAX had only F and D, which were designed to be somewhat compatible with the PDP-11 (hence, their somewhat unusual format, with the sign on a 16-bit boundary instead of a 32-bit boundary). While D has more fraction bits than F, it has the same size exponent and therefore no more range (just greater precision). G and H (sometimes called "grand" and "huge") were added later to provide a larger exponent range in 64 bits and a larger exponent and fraction range in 128 bits, respectively. A floating-point data type can start on any byte boundary and is addressed by the byte containing bit 0. Bit 15 of the first longword contains the sign of the number.

## Figure 2.10 VAX floating-point data type formats

|  |  |  | <br> |  | <br> | - | <br> |  |

|--|--|--|------|--|------|---|------|--|

|  |  |  |      |  |      |   |      |  |

|  |  |  |      |  |      |   |      |  |

| U_11 | oau | ng     |          |         |     | Г  |

|------|-----|--------|----------|---------|-----|----|

| 15   | 14  | 07     | 06 0     | 00      |     | _1 |

| s    | Exp | ponent | Fraction |         | : A | 3  |

|      |     | Fract  | : A + 2  |         |     |    |

| 1    |     | Fract  |          | : A + 4 | 31  |    |

|      |     | Fract  |          | : A + 6 |     |    |

| 63   |     |        |          | 48      |     |    |

## G\_floating

| 15               | 14 04    | 03 00             | ) |  |  |  |

|------------------|----------|-------------------|---|--|--|--|

| s                | Exponent | Exponent Fraction |   |  |  |  |

|                  | Fraction | ] : A + 2         |   |  |  |  |

|                  | : A + 4  |                   |   |  |  |  |

| Fraction : A + 0 |          |                   |   |  |  |  |

| 63               |          | 4                 | 3 |  |  |  |

| H_flo | ating    |          |

|-------|----------|----------|

| 15    | 14 0     | 0        |

| s     | Exponent | : A      |

|       | Fraction | : A + 2  |

|       | Fraction | : A + 4  |

|       | Fraction | : A + 6  |

|       | Fraction | : A + 8  |

|       | Fraction | : A + 10 |

|       | Fraction | : A + 12 |

|       | Fraction | : A + 14 |

| 127   | 11       | 12       |

| Data<br>Type | Total<br>Size | Exponent<br>Size | Fraction<br>Size | Range                                             | Precision |

|--------------|---------------|------------------|------------------|---------------------------------------------------|-----------|

| F            | 32            | 8                | 23               | $.29 \times 10^{-38}$ to $1.7 \times 10^{38}$     | 7 digits  |

| D            | 64            | 8                | 55               | $.29 	imes 10^{-38}$ to $1.7 	imes 10^{38}$       | 16 digits |

| G            | 64            | 11               | 52               | $.56 \times 10^{-308}$ to $.9 \times 10^{308}$    | 15 digits |

| н            | 128           | 15               | 112              | $.84 \times 10^{-4932}$ to $.59 \times 10^{4932}$ | 33 digits |

| Table 2.2 | VAX | Floating-Point | Data | Types |

|-----------|-----|----------------|------|-------|

|-----------|-----|----------------|------|-------|

Let's take a close look at G\_floating, which is now the standard double-precision floating-point representation for VAX high-level languages.

- The fraction is expressed as a 53-bit positive fraction, where  $0.5 \le fraction < 1$ , with the binary point positioned to the left of the most significant bit. (This is similar to scientific notation, although in scientific notation we typically show a number with the decimal point to the right of the most significant digit.) Since the most significant bit must be 1 if the number is nonzero, it is redundant and not stored. This effectively enables the fraction to be stored in 52 bits. This form is called a *normalized* fraction.

- The exponent is stored as a biased 11-bit positive integer, providing what is called an *excess 1024* binary exponent.That is, when 1024 ( $2^{10}$ ) is subtracted from the exponent, the result represents the power of 2 by which the fraction is multiplied to obtain the true value of the floating-point number. Thus, exponent values of 1 through 2047 indicate binary exponents of -1023 through +1023. An exponent of zero together with a sign bit of of zero indicates that the value of the number is zero, regardless of the value of the fraction.

- The sign of the number is positive when S, the sign bit, is 0, and negative when S = 1.

A floating-point number represented by the 64-bit G\_floating datum is described by the equation

$$X = (1-2 \times S) \times fraction \times 2^{(exponent-1024)}$$

where

$$2^{-1024} = .56 \times 10^{-308} \le X < 2^{1023} = .9 \times 10^{308}$$

As an example, suppose we have a G\_floating number whose hexadecimal representation is

0000000 18004080

and we want to convert this to decimal. If we rearrange the digits to correspond to the G\_floating format shown in Figure 2.10, we have

| 15   | 14   | 04 | 03 | 00 |  |  |

|------|------|----|----|----|--|--|

| 0    | 408  |    | (  | )  |  |  |

| 1800 |      |    |    |    |  |  |

|      | 0000 |    |    |    |  |  |

|      | 0000 |    |    |    |  |  |

The sign bit is 0, so we know this is a positive number. Next, the exponent field contains  $408_{16}$ , or  $1032_{10}$ . Because this is a biased, excess 1024 exponent, we know that the value of the exponent is 1032 - 1024, or 8. The fraction field is formed by concatenating the high-order part in bits <0:3> with the low-order bits below, giving us a fraction of 0180000000001<sub>16</sub>. In binary this is

0000 0001 1000 0000 ... 0000

However, the fraction is actually stored as a normalized fraction with the decimal point to the left of the most significant one bit, and that one bit is not stored. The value of the fraction (in binary) is thus

```

.1 0000 0001 1000 0000 ... 0000

```

We had an exponent of 2<sup>8</sup>, so we simply shift the decimal point eight digits to the right, and the value of our G\_floating number in binary is

1000000.11

To convert to decimal,  $1000000 = 80_{16} = 128_{10}$  and .11 = 1/2 + 1/4 = .5 + .25 = .75, so the number stored is 128.75 decimal.

As with integers, floating-point data types can be stored in registers. For D, G, and H floating-point formats, the data types are stored in adjacent registers. Once again, a data type stored in multiple adjacent registers is addressed by the lowest numbered register. For example, if we move a G\_floating number to R5 (register 5), the low-order 32 bits of the number will be placed in R5 and the high-order bits of the number will be placed in R6.

## Alphanumeric Characters

Although all information units contain binary numbers, alphanumeric characters can be represented by a numeric code for each character. In the VAX, the American Standard Code for Information Interchange (ASCII) is used. The ASCII character set includes both uppercase and lowercase alphanumeric characters, the numerics (0 through 9), punctuation marks, and special control characters. The ASCII code, shown in Table 2.3, was developed by the American National Standards Institute (ANSI) to allow the connection of computers and peripherals by different manufacturers. Therefore, all ASCII character-oriented peripherals, such

| Hex<br>Code   | ASCII<br>Char | Hex<br>Code | ASCII<br>Char | Hex<br>Code | ASCII<br>Char | Hex<br>Code | ASCII<br>Char |

|---------------|---------------|-------------|---------------|-------------|---------------|-------------|---------------|

| 00            | NUL           | 20          | SP            | 40          | @<br>A        | 60          | ,             |

| 01            | SOH           | 21          | !             | 41          | Α             | 61          | а             |

| 02            | STX           | 22          | "             | 42          | в             | 62          | b             |

| 03            | ETX           | 23          | #             | 43          | С             | 63          | с             |

| 04            | EOT           | 24          | \$            | 44          | D             | 64          | d             |

| 05            | ENQ           | 25          | %             | 45          | E             | 65          | e<br>f        |

| 06            | ACK           | 26          | &             | 46          | F             | 66          | $\mathbf{f}$  |

| 07            | BEL           | 27          | ,             | 47          | G             | 67          | g<br>h        |

| 08            | BS            | 28          | (             | 48          | Н             | 68          |               |

| 09            | $\mathbf{HT}$ | 29          | )             | 49          | I             | 69          | i             |

| 0A            | LF            | 2A          | *             | 4A          | J             | 6A          | j<br>k        |

| $0\mathbf{B}$ | VT            | 2B          | +             | 4B          | Κ             | 6B          | k             |

| 0C            | FF            | 2C          | ,             | 4C          | L             | 6C          | 1             |

| 0D            | CR            | 2D          | -             | 4D          | Μ             | 6D          | m             |

| 0E            | SO            | 2E          | •             | 4E          | Ν             | 6E          | n             |

| 0F            | SI            | 2F          | /             | 4F          | 0             | 6F          | 0             |

| 10            | DLE           | 30          | 0             | 50          | Р             | 70          | р             |

| 11            | DC1           | 31          | 1             | 51          | Q             | 71          | q             |

| 12            | DC2           | 32          | 2             | 52          | R             | 72          | r             |

| 13            | DC3           | 33          | 3             | 53          | S             | 73          | S             |

| 14            | DC4           | 34          | 4             | 54          | Т             | 74          | t             |

| 15            | NAK           | 35          | 5             | 55          | $\mathbf{U}$  | 75          | u             |

| 16            | SYN           | 36          | 6             | 56          | V             | 76          | v             |

| 17            | ETB           | 37          | 7             | 57          | W             | 77          | w             |

| 18            | CAN           | 38          | 8             | 58          | X             | 78          | х             |

| 19            | EM            | 39          | 9             | 59          | Y             | 79          | у             |

| 1A            | SUB           | 3A          | :             | 5A          | Z             | 7A          | Z             |

| 1B            | ESC           | 3B          | ;             | 5B          | [             | 7B          | {             |

| 1 <b>C</b>    | FS            | 3C          | <             | 5C          | Ň             | 7C          | Ì             |

| 1D            | GS            | 3D          | =             | 5D          | ]             | 7D          | }             |

| 1E            | RS            | 3E          | >             | 5E          | ~             | 7E          | ~             |

| 1 <b>F</b>    | US            | 3F          | ?             | 5F          | <u> </u>      | 7F          | DEL           |

## Table 2-3 ASCII Character Encoding

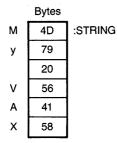

Figure 2.11 ASCII representation of the string My VAX

as line printers and terminals, will output an A when the ASCII code for A (41 hexadecimal) is presented. The ASCII table also includes values for special control characters. When you press a line feed key on a keyboard, the terminal transmits the eight-bit value 0A (00001010). Another useful feature of the ASCII encoding is that the uppercase and lowercase characters differ by only a single bit. Uppercase A is 41 hex (01000001), and lowercase a is 61 hex (01100001). This simplifies case conversions.

Figure 2.11 shows the ASCII representation for the alphanumeric string *My VAX*. Note that each character uses one byte of storage, or two hex digits. The string is referenced by the address of the first byte, the one containing the character *M*, at symbolic address STRING. The space is an ASCII character whose value is 20 hexadecimal.

The VAX has instructions to manipulate strings of contiguous bytes, called character string instructions. A character string has two attributes: an address and a length in bytes (or characters). On the VAX, character strings can be from 0 to 65,535 bytes in length.

## **Decimal Strings**

In addition to binary representations, numbers can be represented within the computer as a string of decimal digits. Numbers are usually entered in ASCII format and converted to binary for arithmetic operations. For some applications, however, it may be more convenient to operate in a decimal format. This is often true in a business (COBOL) environment, where programs require only simple computations.

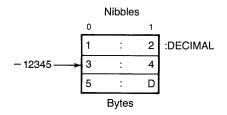

The VAX supports two forms of decimal strings. In the form known as numeric string, each digit occupies one byte. Numeric strings can be in leading separate or trailing numeric format depending on whether the sign appears before the first digit or is superimposed on the last digit. The second decimal form, known as packed decimal, packs two decimal digits per byte.

Table 2.4 shows the format for a packed decimal string. A packed decimal string is composed of a sequence of bytes in memory, with each byte divided into two 4-bit nibbles. Each nibble contains a representation for one of the decimal digits. The last nibble contains a representation of

|                  | Decimar St       | mg hepresentation |

|------------------|------------------|-------------------|

| Digit<br>or Sign | Decimal<br>Value | Hex<br>Value      |

| 0                | 0                | 0                 |

| 1                | 1                | 1                 |

| 2                | 2                | 2                 |

| 3                | 3                | 3                 |

| 4                | 4                | 4                 |

| 4<br>5           | 5                | 5                 |

| 6                | 6                | 6                 |

| 7                | 7                | 7                 |

| 8                | 8                | 8                 |

| 9                | 9                | 9                 |

| +                | . 12             | С                 |

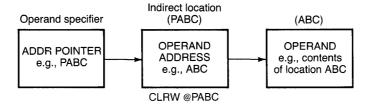

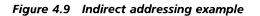

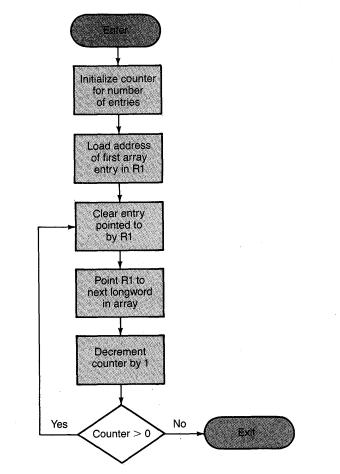

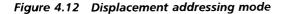

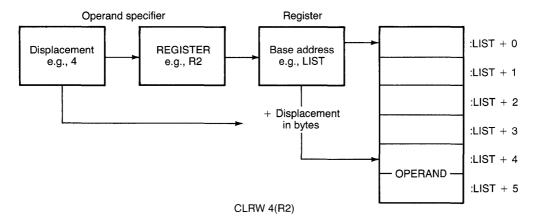

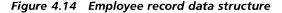

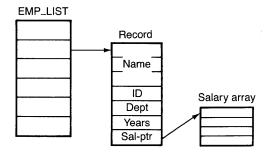

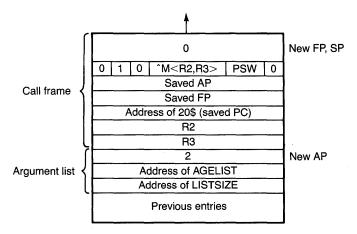

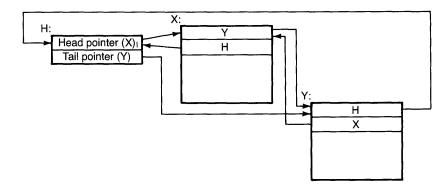

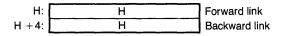

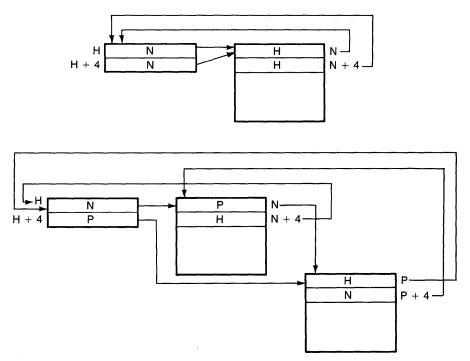

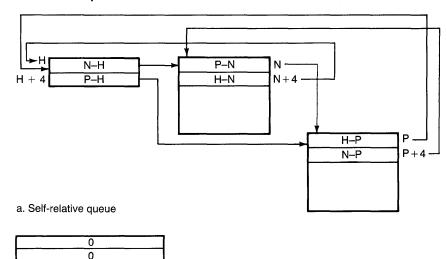

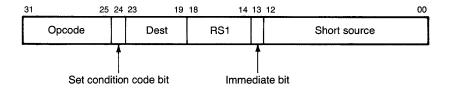

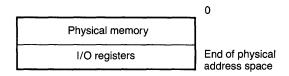

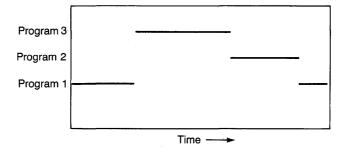

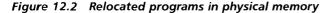

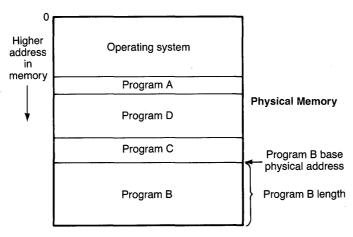

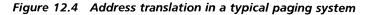

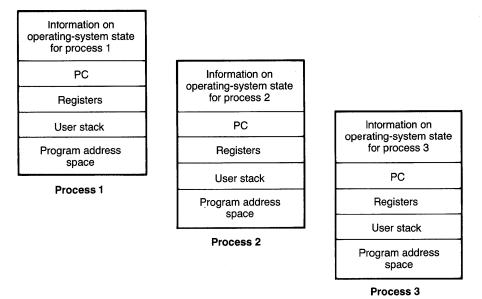

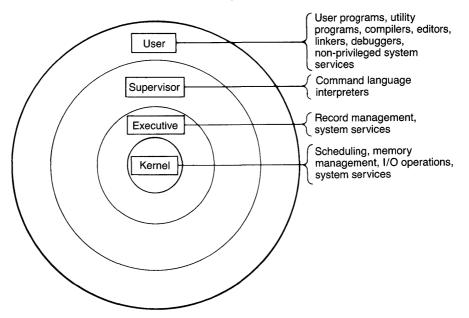

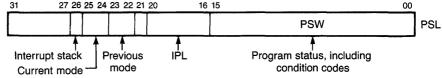

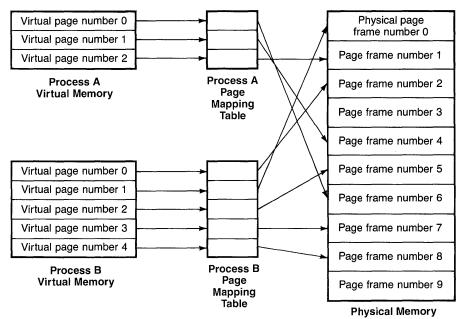

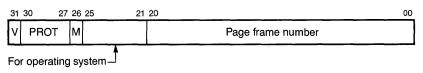

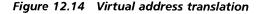

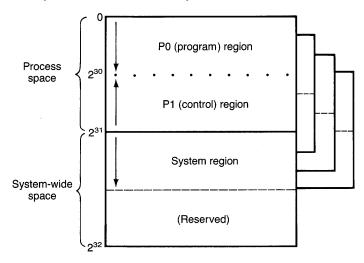

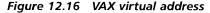

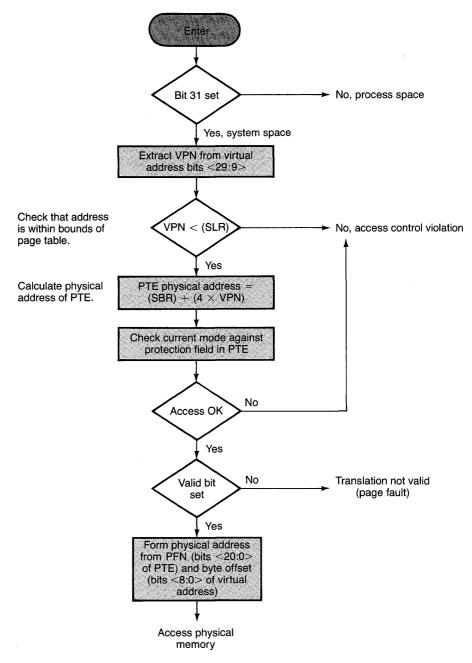

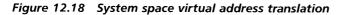

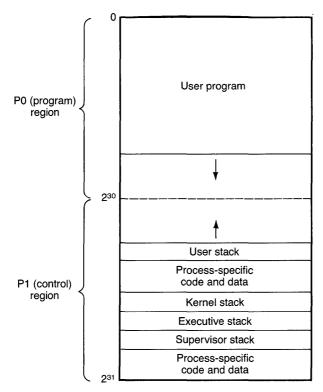

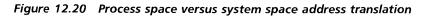

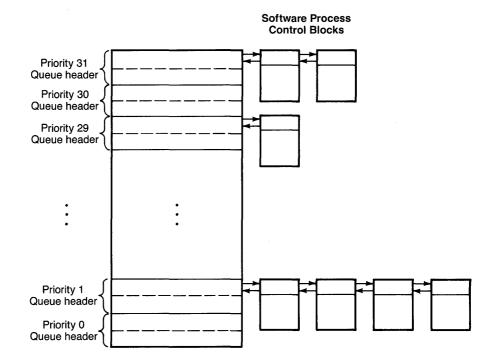

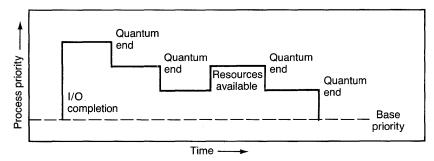

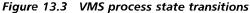

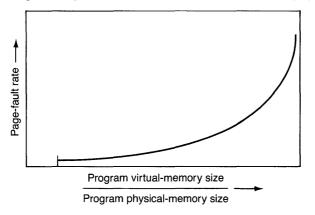

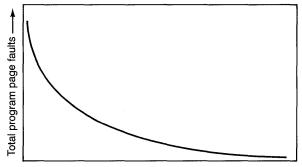

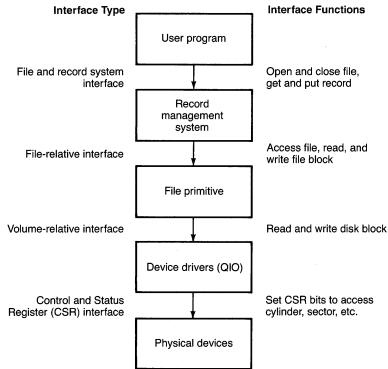

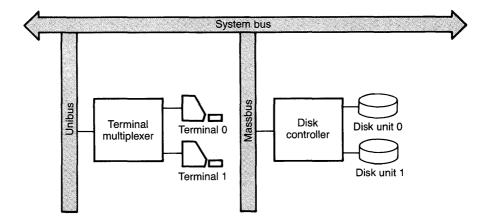

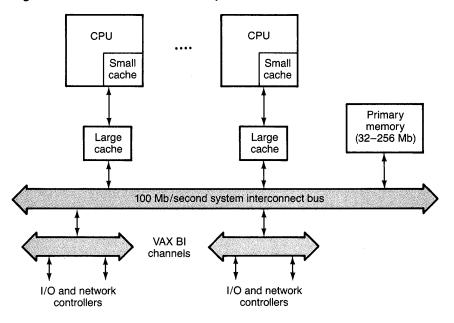

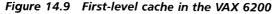

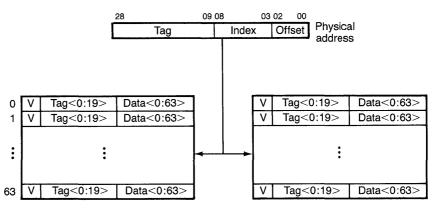

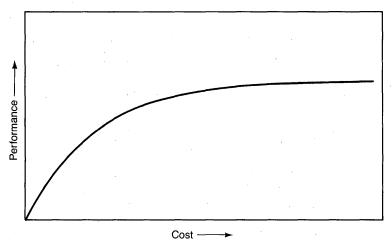

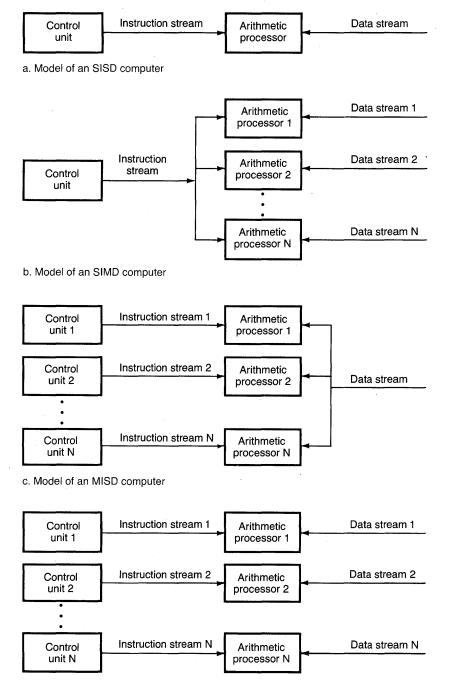

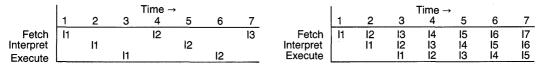

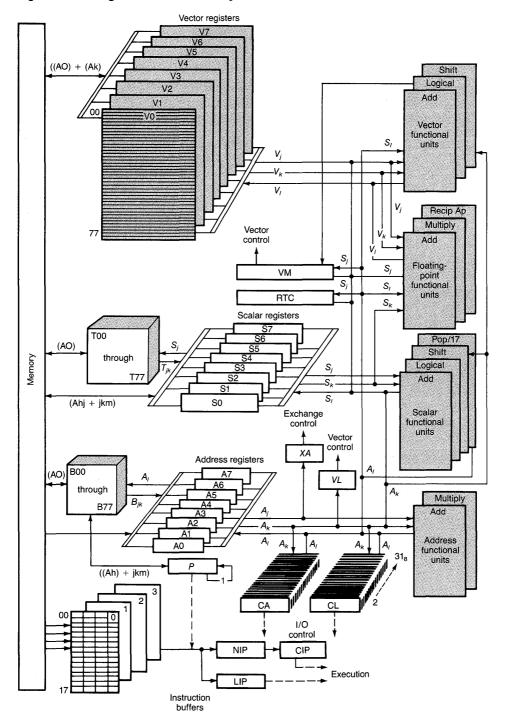

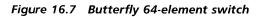

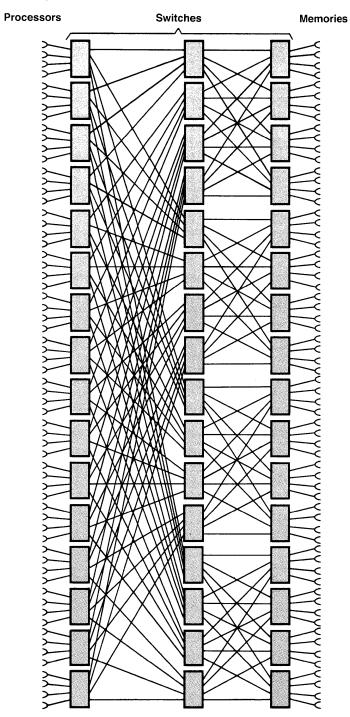

| —                | 13               | D                 |