# The Theory and Practice of Reliable System Design

## DANIEL P. SIEWIOREK ROBERT S. SWARZ

## The Theory and Practice of Reliable System Design

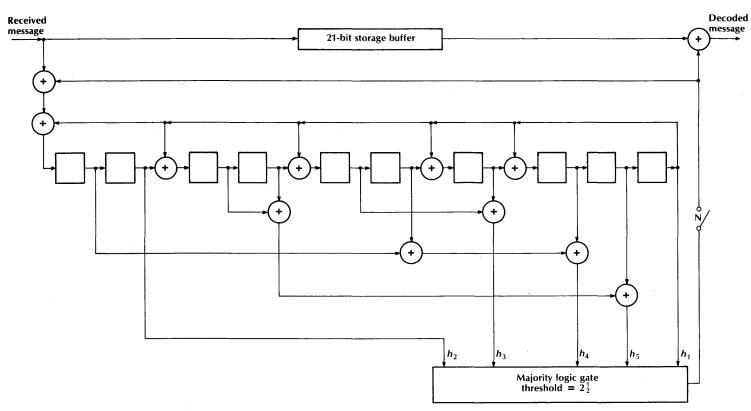

DANIEL P. SIEWIOREK ROBERT S. SWARZ

Copyright @ 1982 by Digital Equipment Corporation.

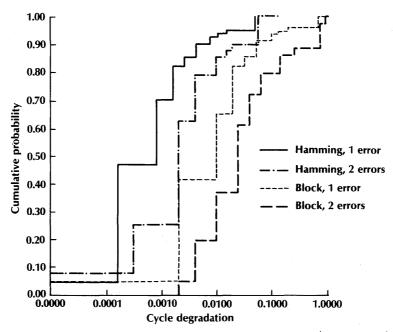

All rights reserved. Reproduction of this book, in part or in whole, is strictly prohibited. For copy information write Digital Press, Educational Services, Digital Equipment Corporation, Bedford, Massachusetts 01730.

Printed in U.S.A. 10 9 8 7 6 5 4 3 2

Documentation number EY-AX016-DP ISBN 0-932376-13-4

#### Library of Congress Cataloging in Publication Data

Siewiorek, Daniel P.

The theory and practice of reliable system design.

Bibliography: p. Includes index.

1. Electronic digital computers—Reliability. 2. Fault-tolerant computing. I. Swarz, Robert. II. Title.

| QA76.5.S538     | 001.64 | 81-9696 |

|-----------------|--------|---------|

| ISBN 0-932376-1 | 3-4    | AACR2   |

Trademarks appear on p. 749.

#### CREDITS

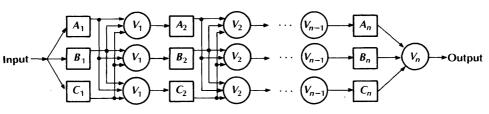

#### Figures 5-12, 5-13, 5-14, 5-15

Jacob A. Abraham and Daniel P. Siewiorek, "An Algorithm for the Accurate Reliability Evaluation of Triple Modular Redundancy Networks," IEEE TRANSACTIONS ON COMPUTERS (July 1974). Copyright © 1974 IEEE. Reprinted by permission.

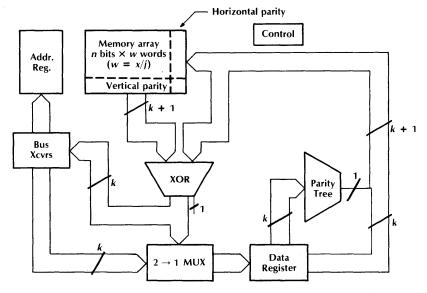

#### Figure 3–68

D.G. Armstrong, "A General Method of Applying Error Correction to Synchronous Digital Systems," THE BELL SYSTEM TECHNICAL JOURNAL, vol. 40, p. 580. Copyright © 1961, American Telephone and Telegraph Company. Reprinted by permission.

Credits are continued on p. 751 and are considered part of the copyright page.

To Karon and Lonnie

### Contents

2

Preface xxi

#### PART I THE THEORY OF RELIABLE SYSTEM DESIGN 1

1 Fundamental Concepts 3

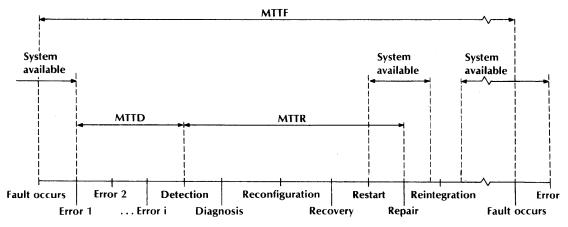

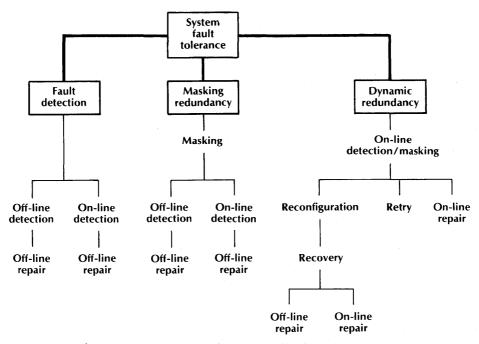

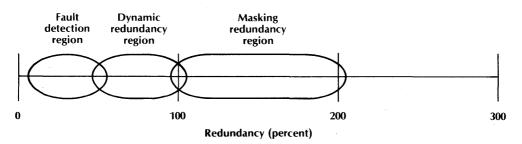

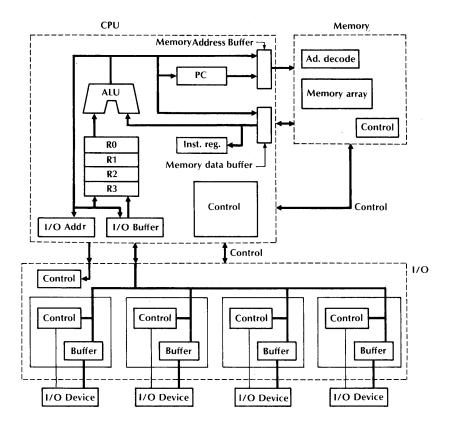

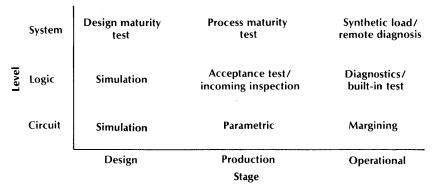

The Importance of Reliability 3 Levels in a Digital System 4 Stages in System Life 5 Attributes of Fault-Tolerant Computing and Their Definitions 6 Availability 7 Reliability 7 The Manufacturing Stage 7 Design Maturity Testing 7 Incoming Inspection 8 Process Maturity Testing 11 The Operational Life Stage 12 Cost of Ownership 14 Universe of Models 15 The Designable Parameters 16 References 16 Faults and Their Manifestations 17

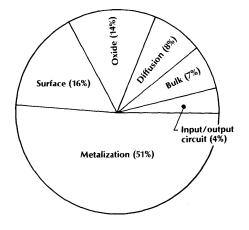

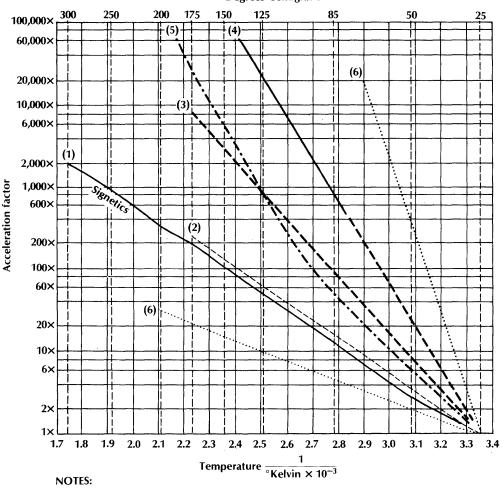

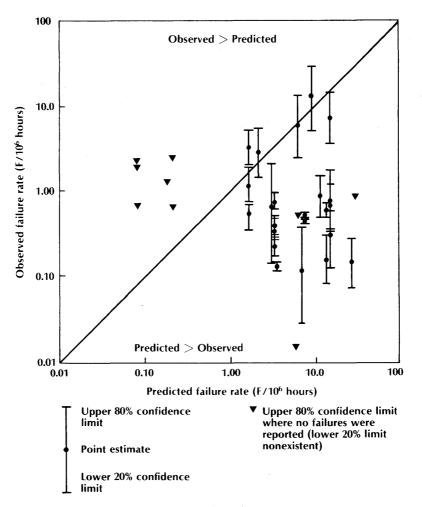

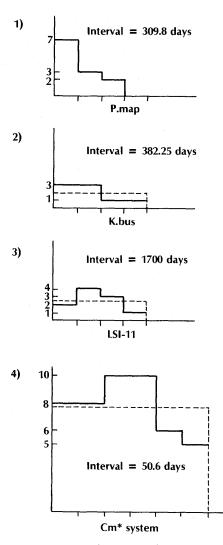

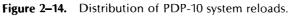

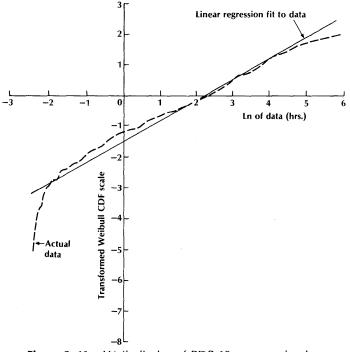

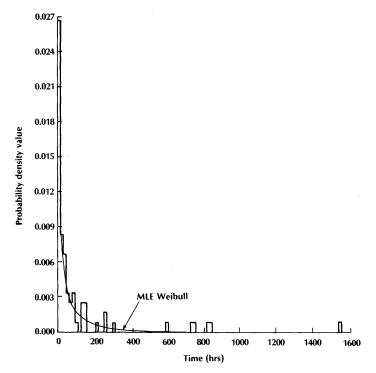

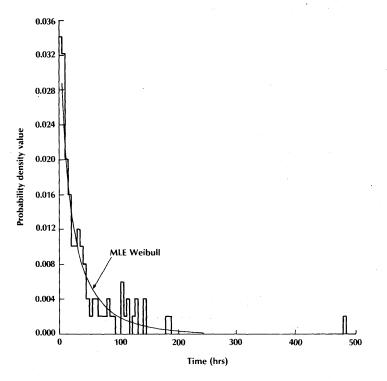

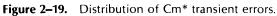

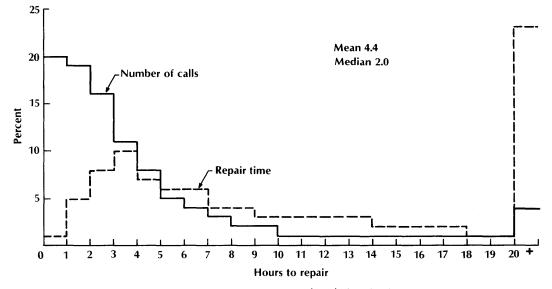

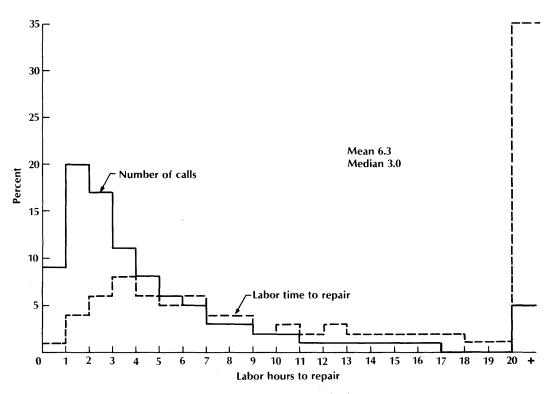

#### Introduction 17 Fault Manifestations 19 Physical Defects 19 Logic-Level Fault Classes 26 System-Level Abstractions 26 Fault Distributions 30 Probability Review 30 Matching Sampled Data to Math Distributions 33 Maximum Likelihood Estimators 33 Maximum Likelihood Estimation of Weibull Parameters 34 Linear Regression Analysis - 34 Confidence Intervals 34 Goodness-of-Fit Tests 35 Distributions for Permanent Faults: The MIL-HDBK-217 Model 37 Life-Cycle Testing and Field Data 37 Analysis of Permanent Failure Data: Estimating the Distribution and Its Parameters 44 Automated Failure Rate Calculation 49

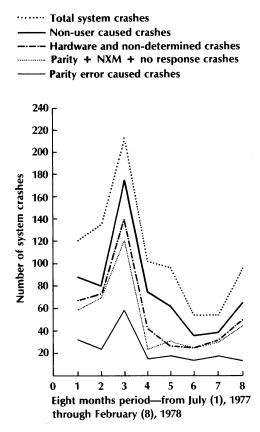

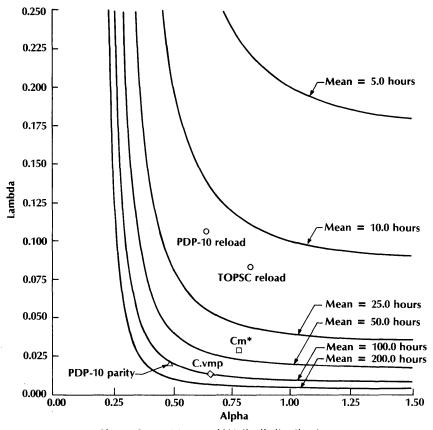

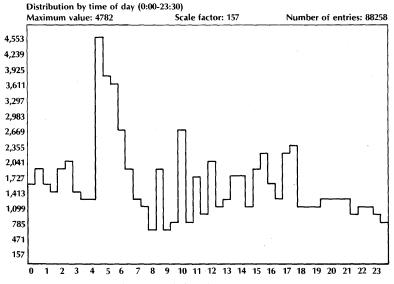

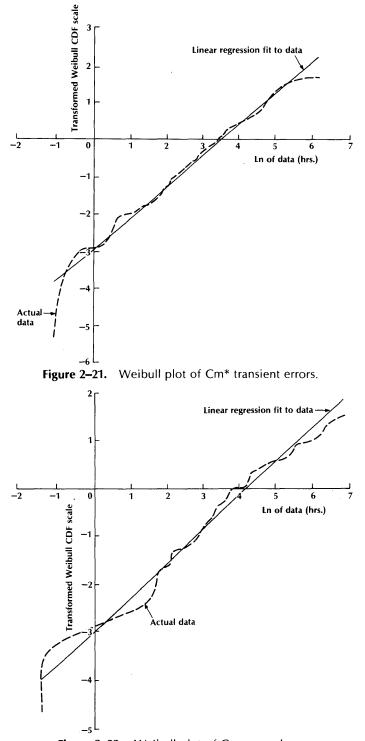

Distributions for Transients and System Errors 51 Data Collection 51 Graphical Data Analysis 53 Confidence Intervals for the Parameters 56 Goodness-of-Fit Tests 56 Summary 57 References 61 Problems 61

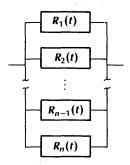

#### 3 Reliability and Availability Techniques Steven A. Elkind 63

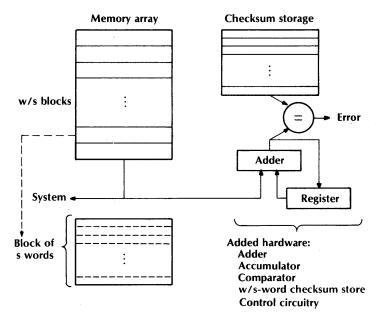

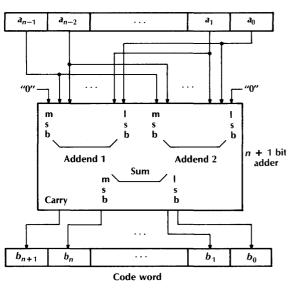

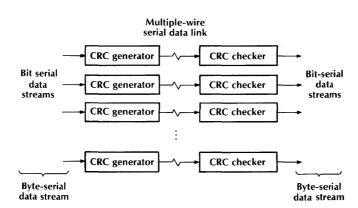

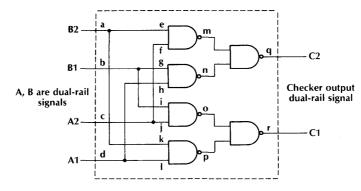

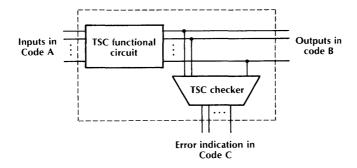

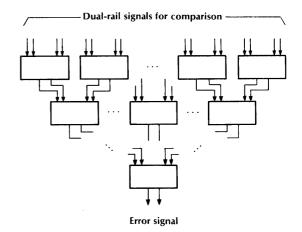

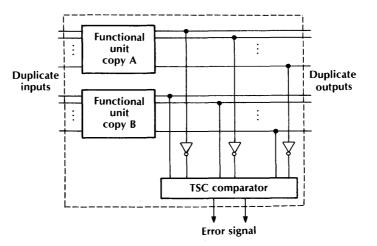

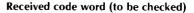

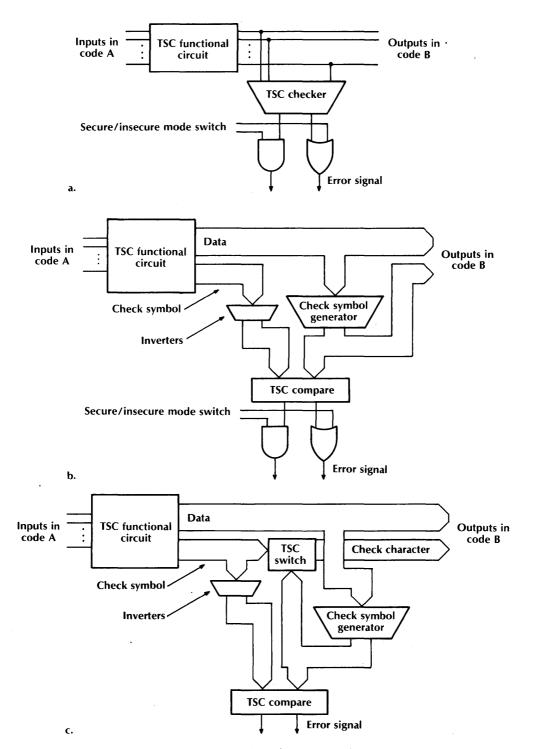

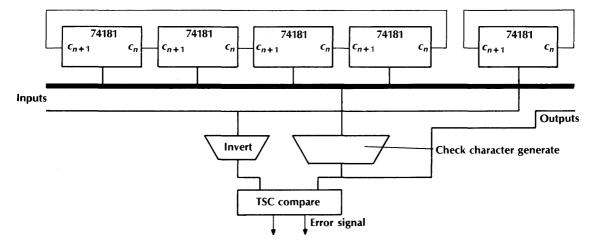

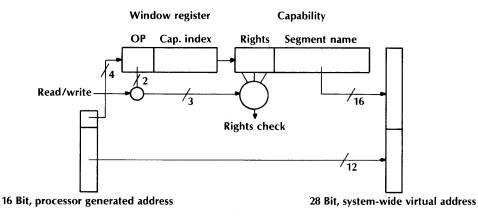

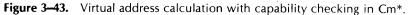

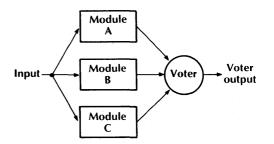

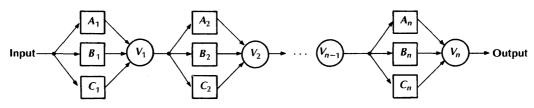

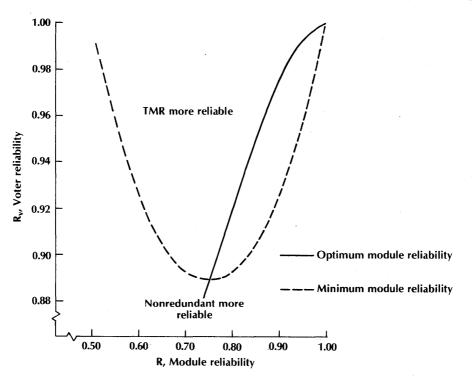

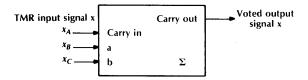

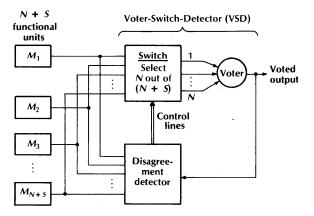

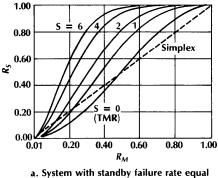

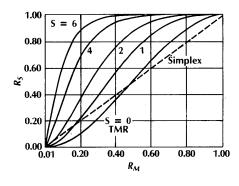

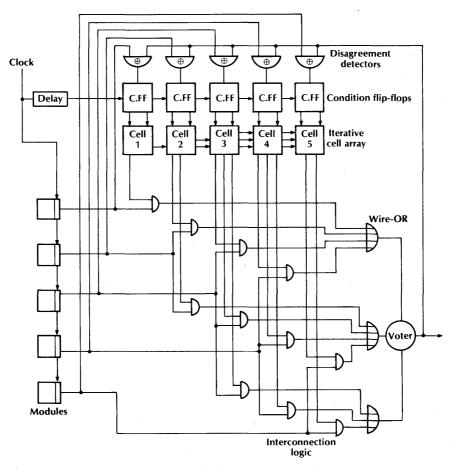

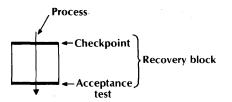

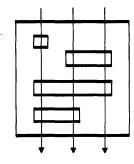

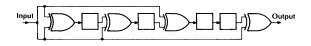

Fault-Avoidance Techniques 67 Environmental Changes 68 Quality Changes 71 Component Integration Level 75. Fault-Detection Techniques 77 Duplication 79 Error-Detection Codes 84 Self-Checking, Fault-Secure, and Fail-Safe Logic 104 Watchdog Timers and Timeouts 110 Consistency and Capability Checking 112 Masking Redundancy 113 N-Modular Redundancy with Voting 114 Error-Correcting Codes 122 Masking Logic 133 Dynamic Redundancy 140 Reconfigurable Duplication 141 Reconfigurable NMR 145 Backup Sparing 154 Graceful Degradation 158 Reconfiguration 160 Recovery 169 Summary 175 References 175 Problems 176

#### 4 Maintainability and Testing Techniques 183

Production 184 Parametric Testing 185 Acceptance Testing 185 Design for Testability 191 Field Operation 196 References 200 Problems 200

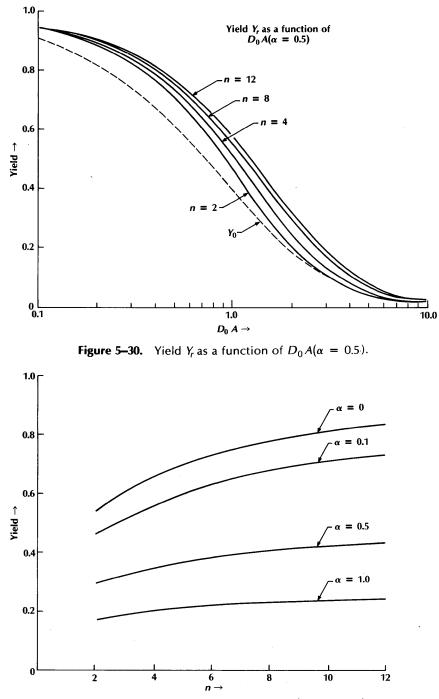

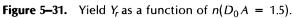

5 Evaluation Criteria Stephen McConnel and Daniel P. Siewiorek 201

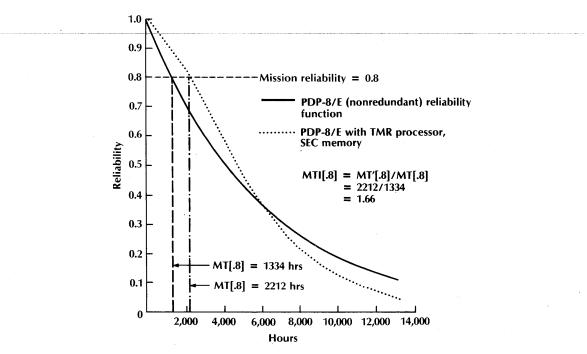

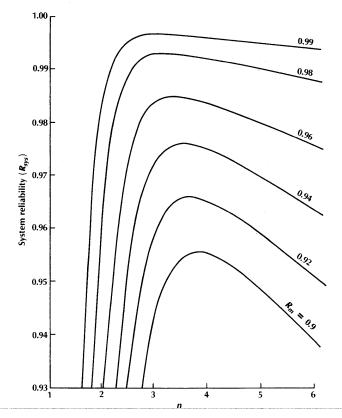

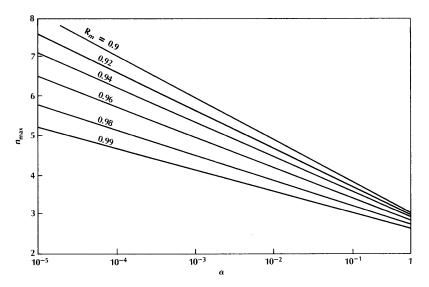

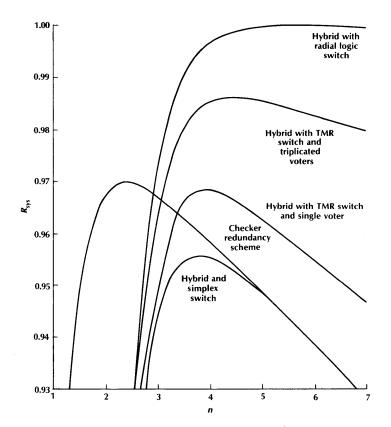

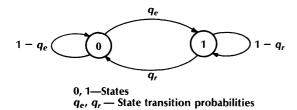

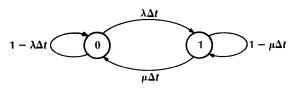

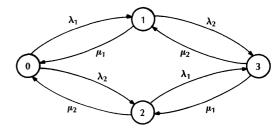

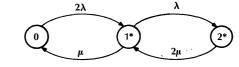

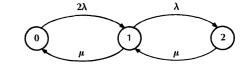

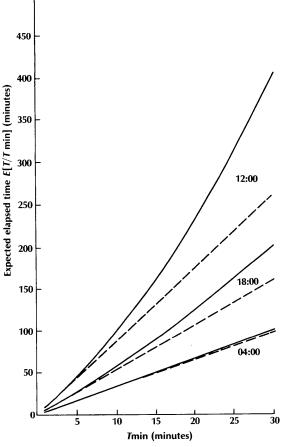

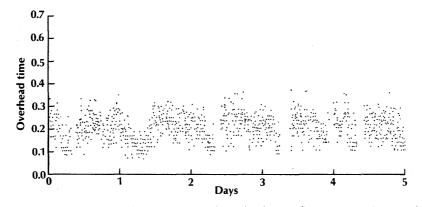

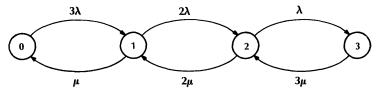

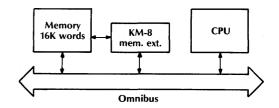

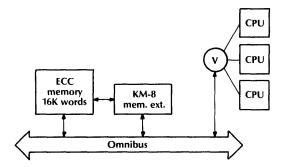

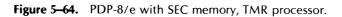

Survey of Evaluation Criteria 202 Hardware Evaluation 202 Software Evaluation 206 Modeling Techniques 211 Combinatorial Modeling 211 Markov Models 246 System Availability Models 275 Modeling Performance Impact of Redundancy 281 Trade-Off Analysis in System Design 285 Design Example: The PDP-8/e 286 Analyses of the Example 291 Summary 296 References 296 Problems 297

#### 6 Financial Considerations 303

Introduction and Fundamental Concepts 303 Definitions 303 Sources of Maintenance Costs 304 Cost of Customer Ownership 306 Field Service Overview and Cost Models 308 Maintenance Cost Models 309 Life-Cycle Cost (LCC) Models 311 LCC Model with Generalized Data Elements 314 Conclusions 317 References 320 Problems 321

#### PART II THE PRACTICE OF RELIABLE SYSTEM DESIGN 323

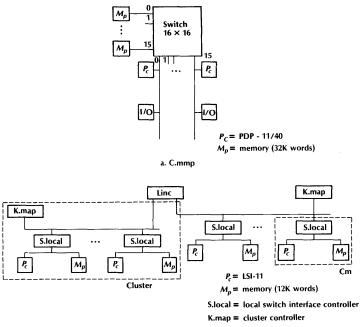

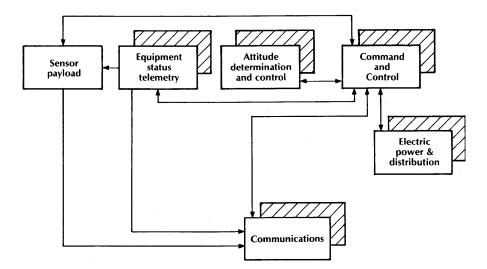

C.vmp 325 Commercial Computers 325 DEC 325 IBM 326 UNIVAC 326 High-Availability Systems 330 Tandem 330 ESS Processors 332 Pluribus 335 Spacecraft and Avionic Systems 337 FTMP and SIFT 342 References 344

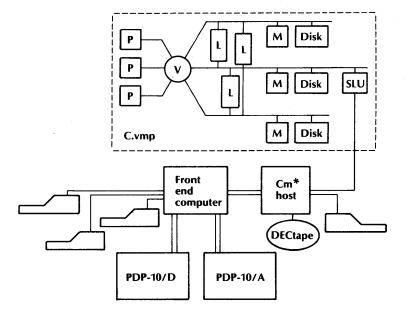

7 C.vmp: A Voted Multiprocessor Daniel P. Siewiorek, Vittal Kini, Henry Mashburn, Stephen McConnel, and Michael Tsao 345

Design Goals 345

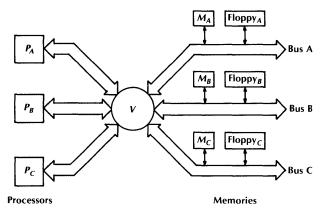

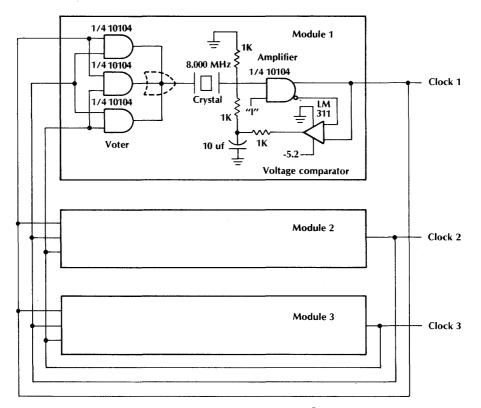

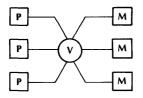

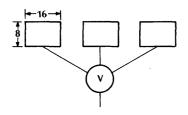

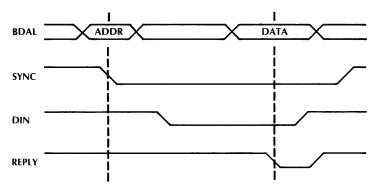

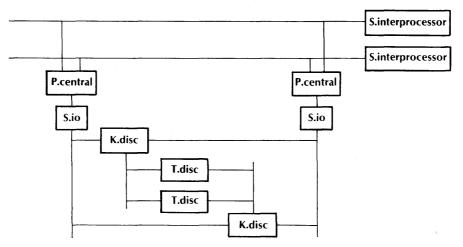

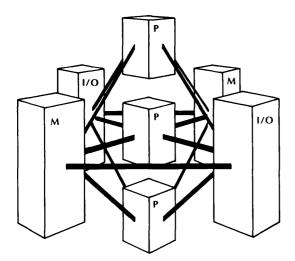

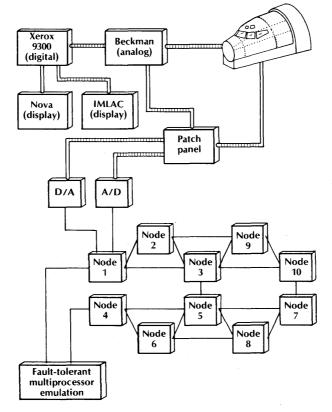

System Architecture 346

Actual System Configuration 346

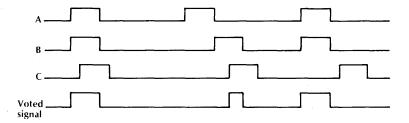

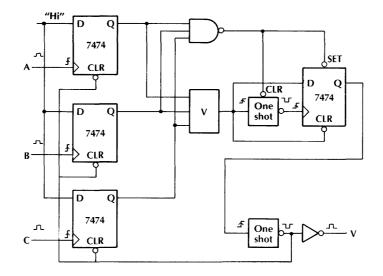

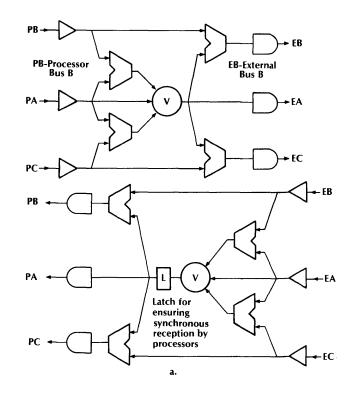

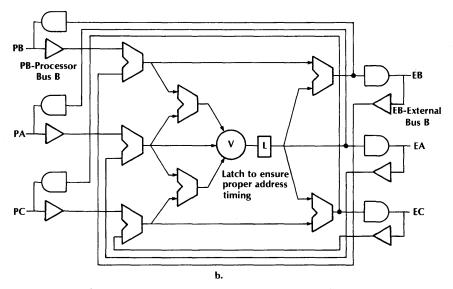

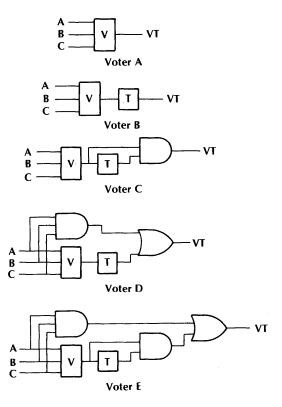

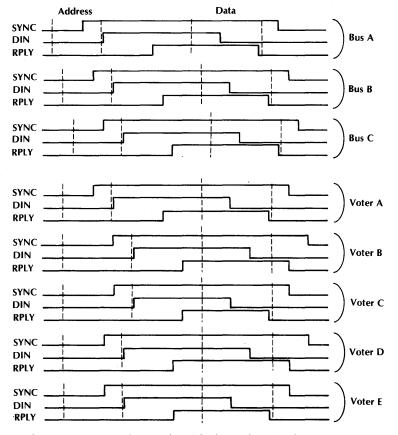

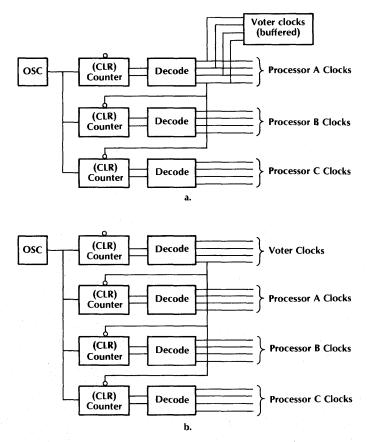

Voter Modes of Operation 348

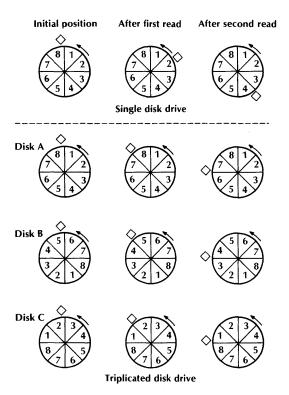

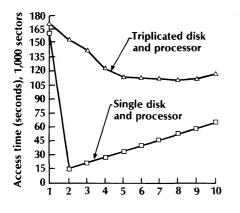

Peripheral Devices 350 Issues of Processor Synchronization 350 Dynamic Voting Control 350 Bus Control Signal Synchronization 351 System Clock 353 Performance Measurements 354 Processor Execution/Memory Fetch Time 354 Disk Access Time 355 Operational Experiences 357 Operating History 357 C.vmp System Reliability 357 On-Line Maintenance 359 References 360

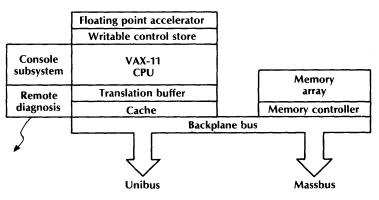

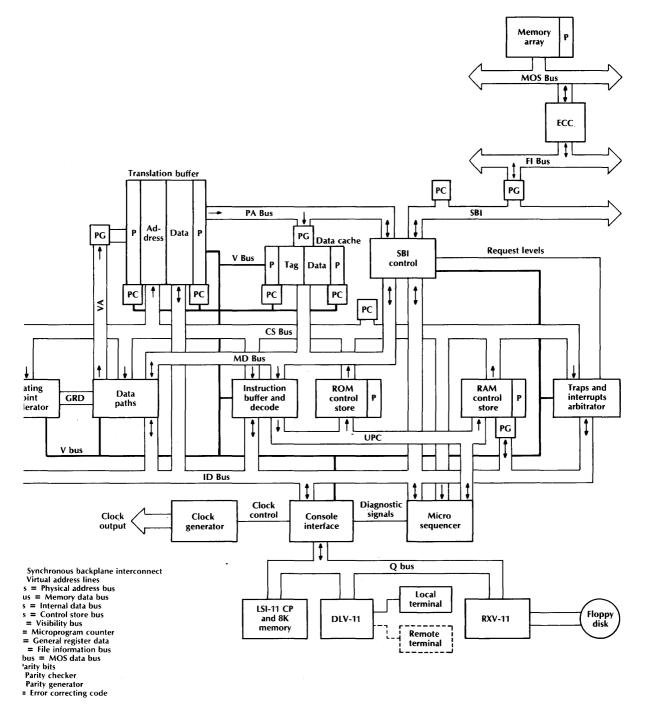

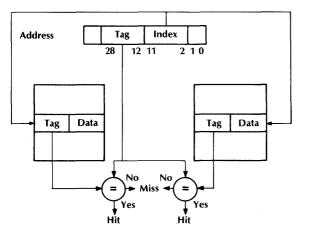

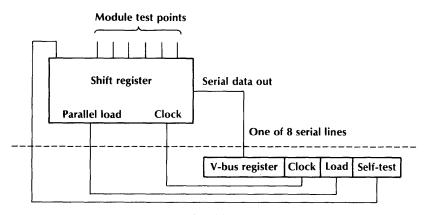

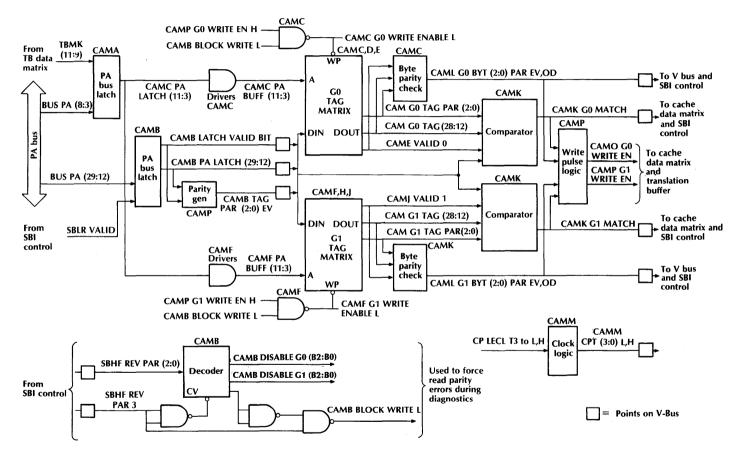

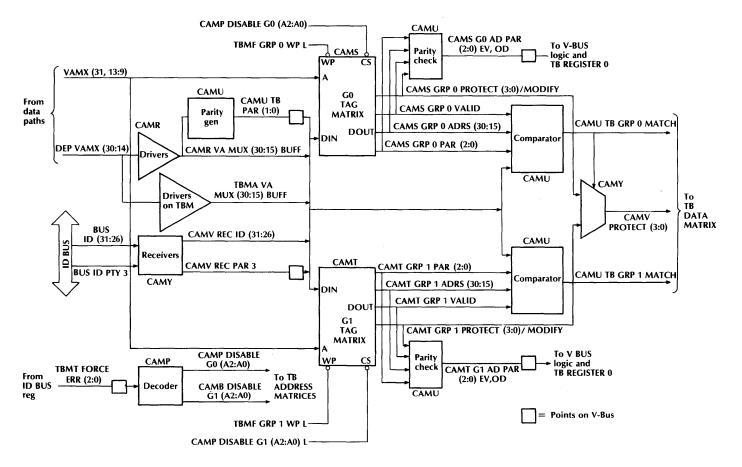

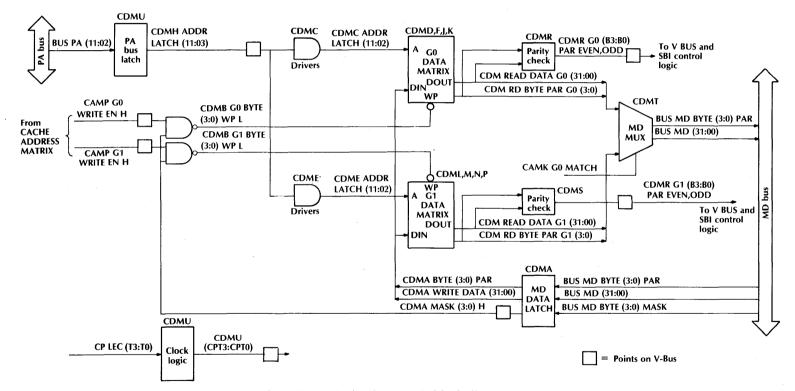

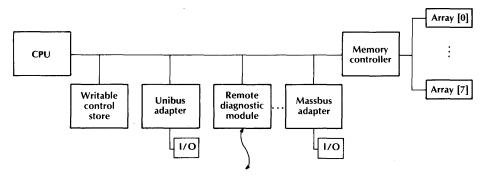

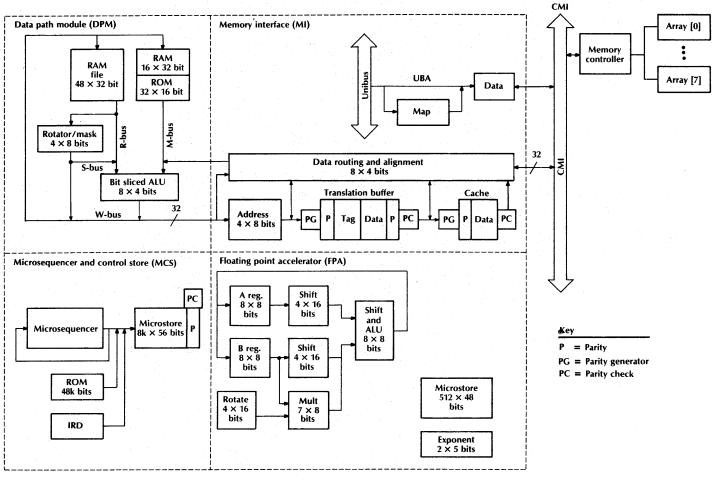

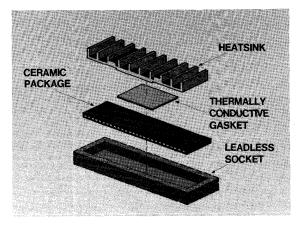

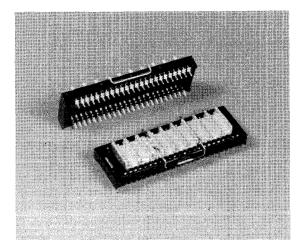

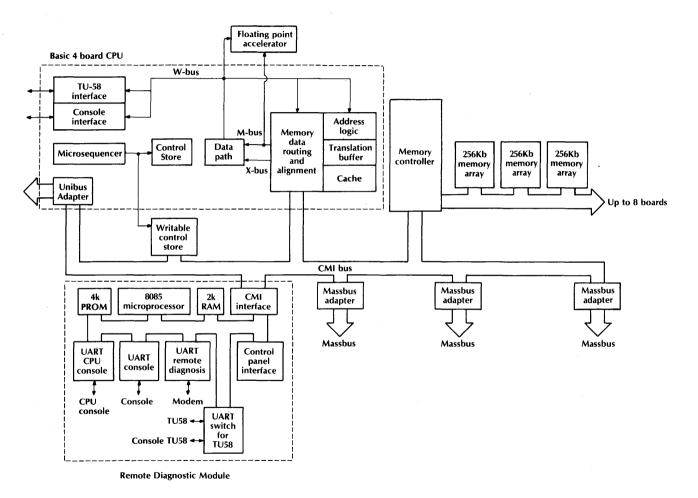

#### 8 RAMP in the VAX Family: VAX-11/780 and VAX-11/750 361

The VAX Architecture 361 Archetypical VAX-11 Implementation 367 The VAX-11/780 Implementation 370 Internal Processor Registers 372 ID Bus Registers 377 Main Memory Registers 379 Console Subsystem 381 Micro- and Macrodiagnostics 384 The VAX-11/750 Implementation 386 Design Evolution 386 **RAMP** Features 395 Processor Registers 397 Main Memory Registers 398 Diagnostics and Repair 402 Summary 404 References 404

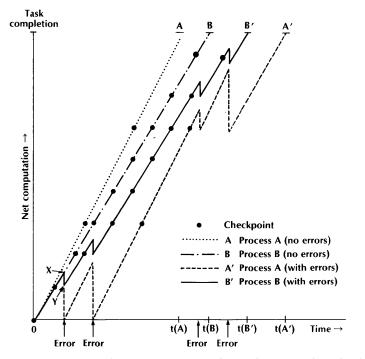

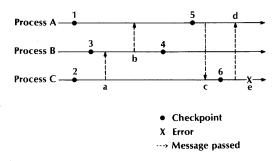

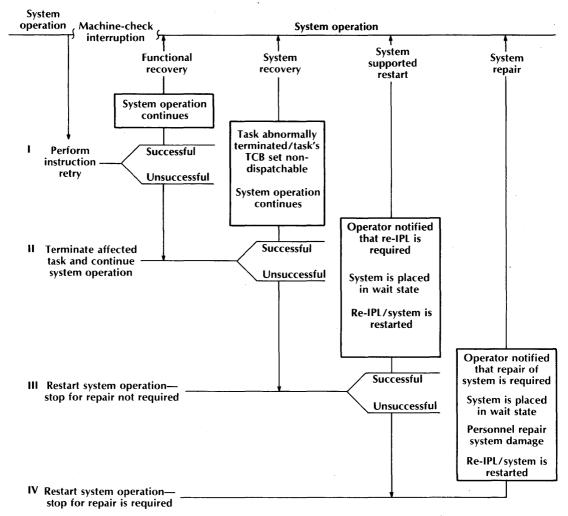

9 Recovery through Programming System/360—System 370 Donald L. Droulette 409

Introduction 409 The Recovery Management Objective 410 Functional Recovery 411 System Recovery 411 System-Supported Restart 411 System Repair 411 User Personnel Involvement 411 Summary Description of Facilities 412 I/O Device/Unit Recovery Facilities 413 IBM Standard Error Recovery Procedures 413 Optional User-Written Routines 413 On-Line Test System 414

CONTENTS xi

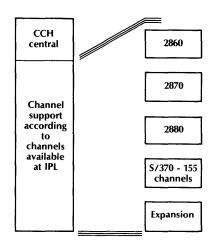

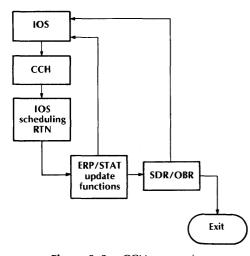

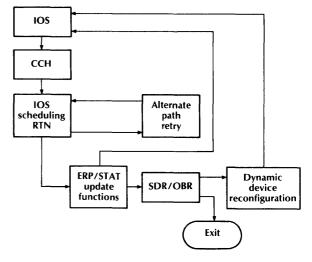

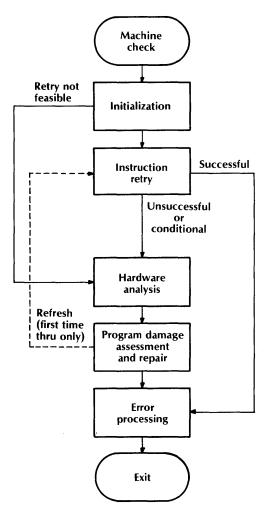

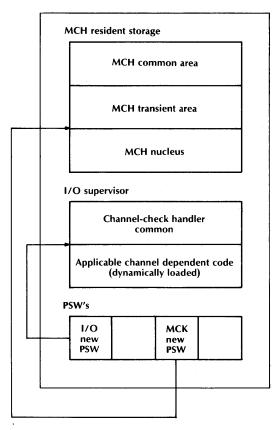

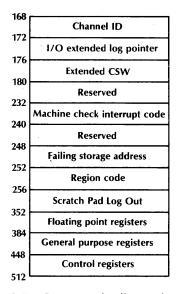

Channel-Check Handler (CCH) 414 I/O Recovery Management Support 415 APR 415 DDR 416 CPU/Processor Storage Recovery Facilities 417 Machine-Check Handler (MCH) 417 System Environment Recording (SER0 and SER1) 418 System Associated Recovery Facilities 418 System Restart 418 Checkpoint/Restart 418 Error Record Retrieval Facilities 418 Environment Record Editing and Printing Utility 419 System Environment Recording, Editing and Printing Program 419 RMS/65 Relationship to the Operating System 419 System/370 Considerations 419 Conclusion 421 Reference Materials 421

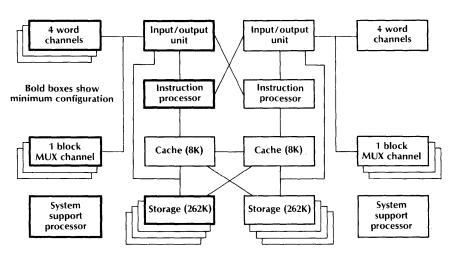

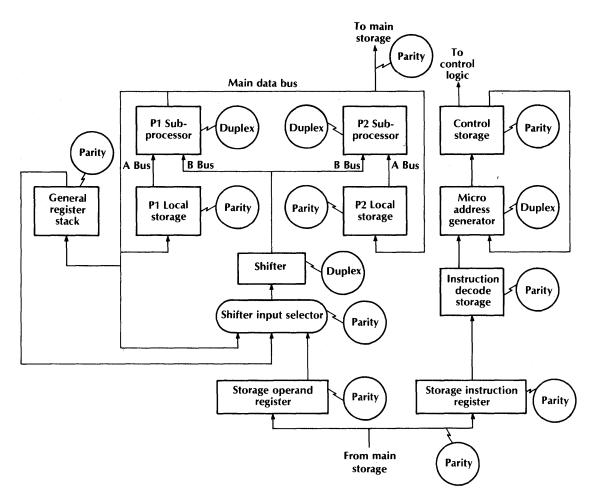

#### 10 Availability, Reliability, and Maintainability Aspects of the SPERRY UNIVAC 1100/60 L. A. Boone, H. L. Liebergot, and R. M. Sedmak 423

Abstract 423 Introduction 423 ARM Philosophy for 1100/60 424 ARM in Previous SPERRY UNIVAC 1100 Series Systems 424 ARM in the 1100/60—General Approach 424 Detailed ARM Implementation 425 System Characteristics 425 Fault Detection 427 Error Correction 428 Fault Isolation 428 Error Recovery 429 Fault Injection 431 Maintenance 432 ARM Evaluation 432 Summary 433 References 433

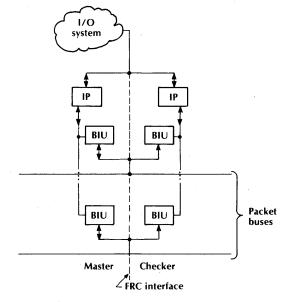

#### 11 A Fault-Tolerant Computing System James A. Katzman 435

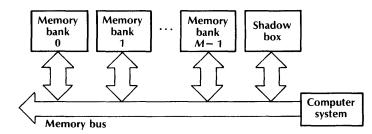

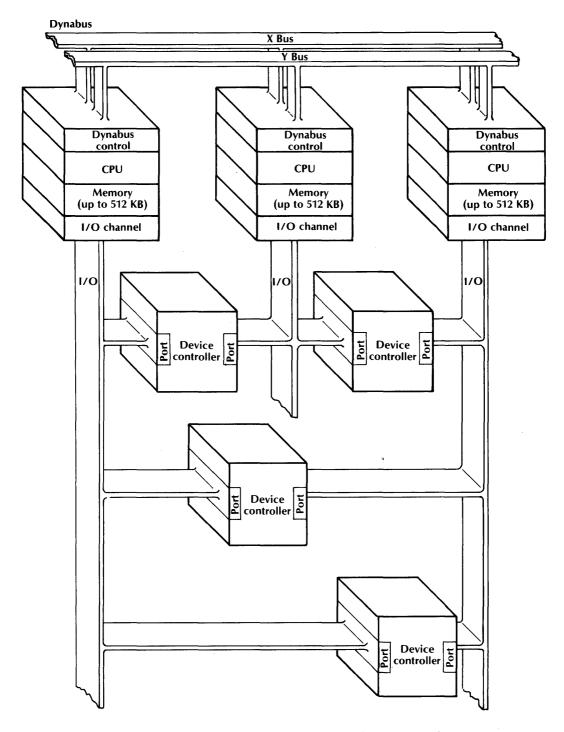

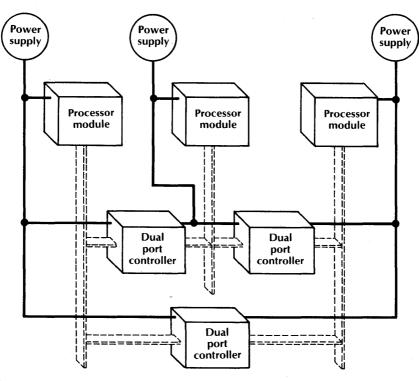

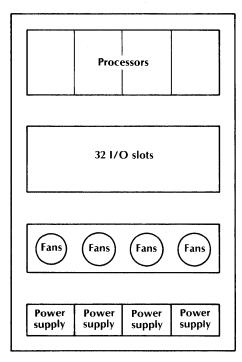

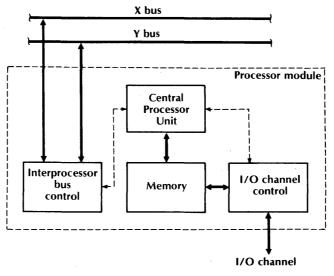

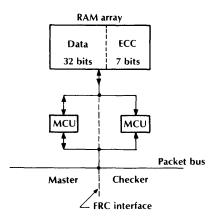

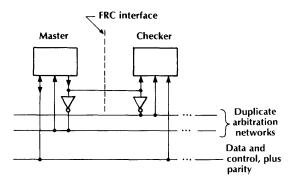

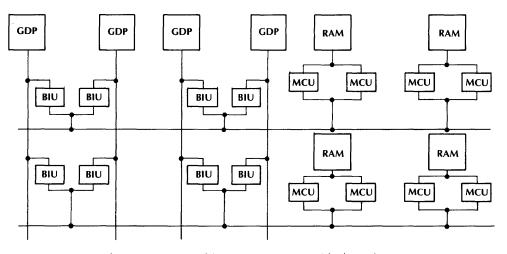

Abstract 435 Introduction 435 System Organization 438 System Packaging 439 Interconnections 440 Processor Module Organization 440 The CPU 441 Main Memory 441 The Dynabus 444 The Input/Output Channel 447 I/O System Organization 447 Dual-Port Controllers 447 Controller Buffer Considerations 450 Disc Controller Considerations 450 NonStop I/O System Considerations 451 Power, Packaging, On-Line Maintenance 451 Further Packaging and On-Line Maintenance Considerations 452 Summary 452

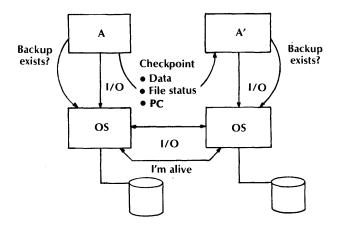

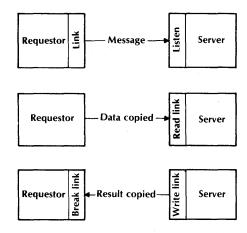

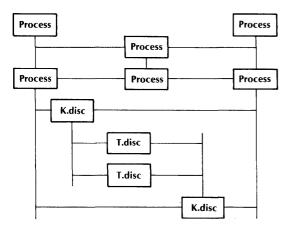

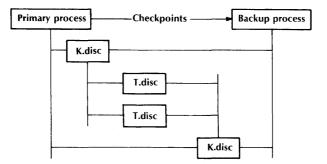

A "NonStop" Operating System Joel F. Bartlett 453

Abstract 453 Background 453 System Overview 453 System Design Goals 454 Integrated Hardware/Software Design 454 **Operating System Design Goals** 454 Operating System Structure 455 Processes 455 Messages 456 Process-Pairs 456 System Processes 458 Application Process Interface 459 Initialization and Processor Reload 459 **Operating System Error Detection** 459 Acknowledgments 460 References 460

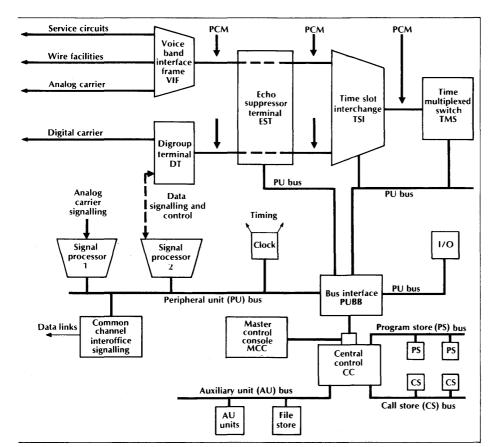

#### 12 Fault-Tolerant Design of Local ESS Processors W. N. Toy 461

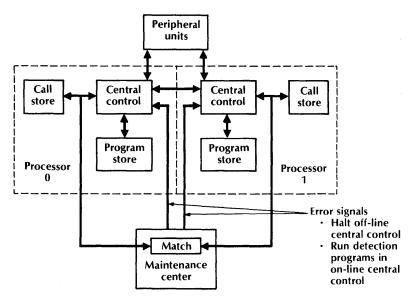

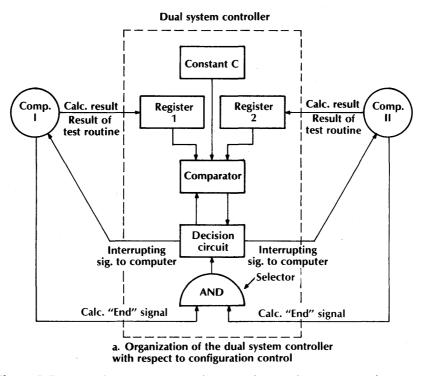

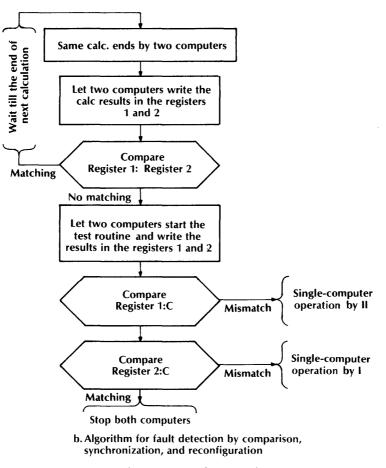

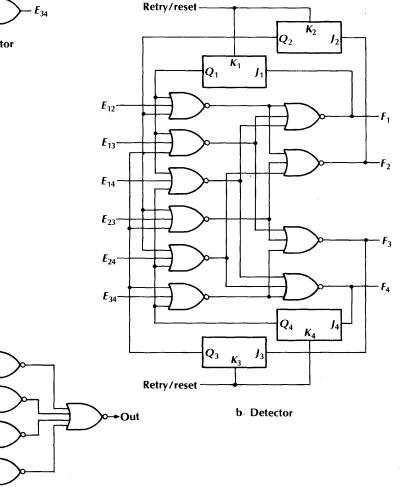

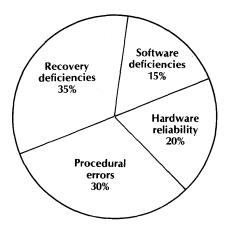

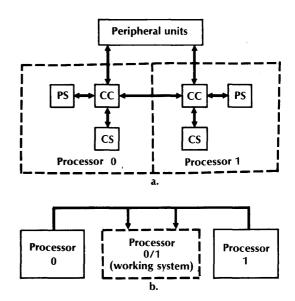

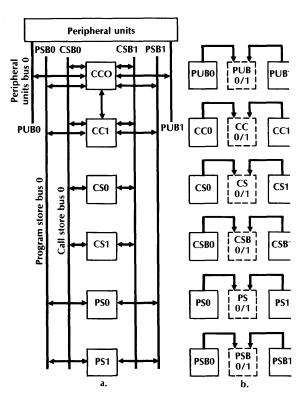

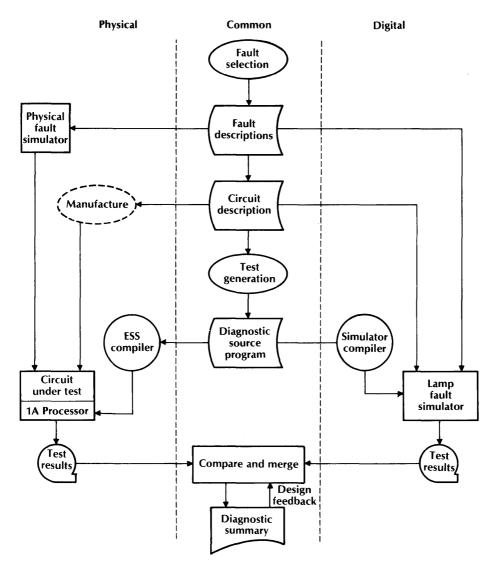

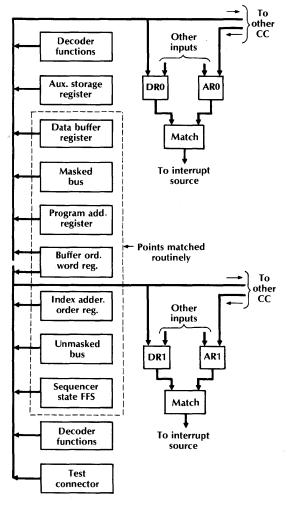

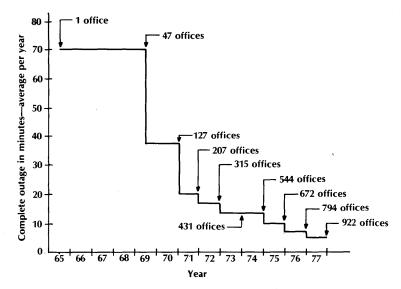

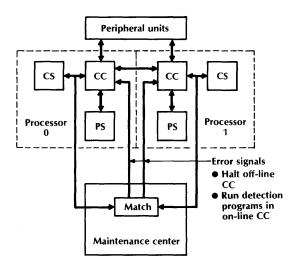

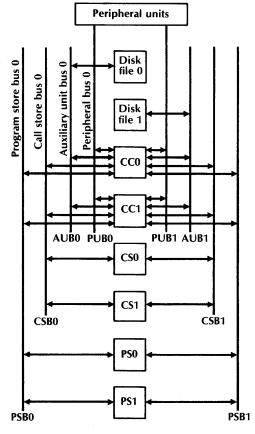

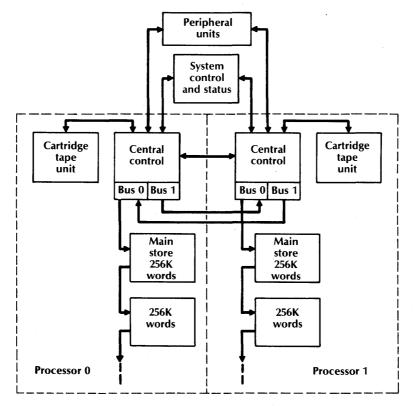

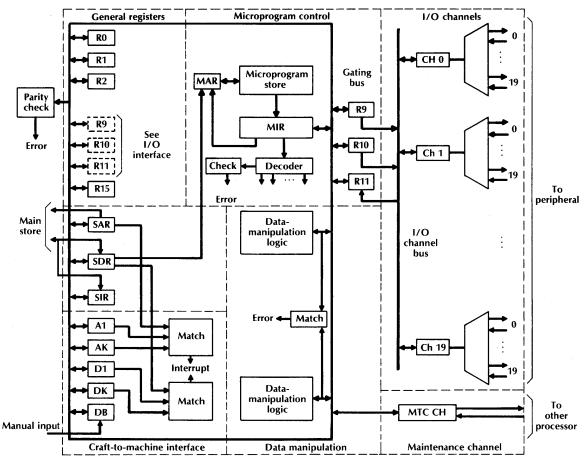

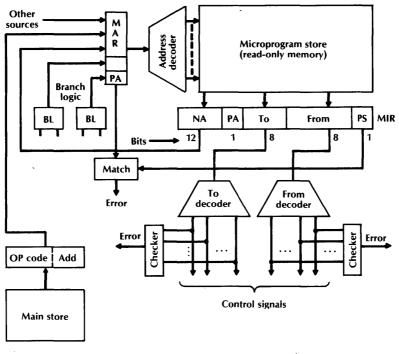

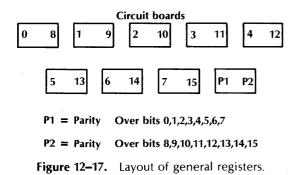

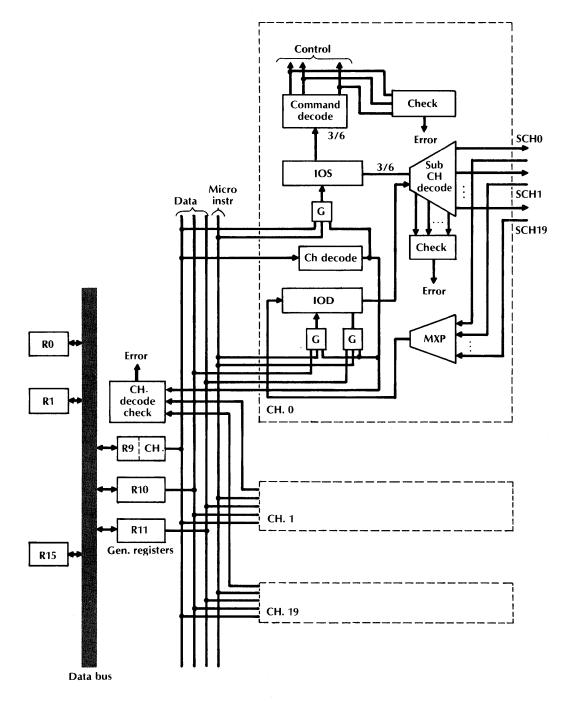

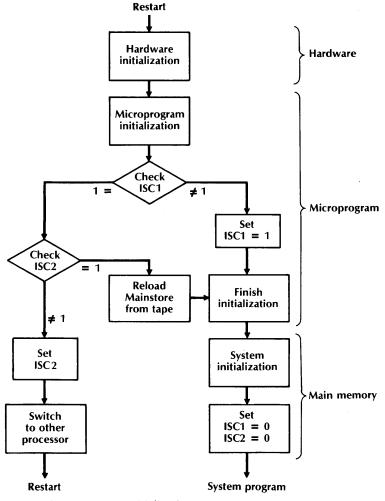

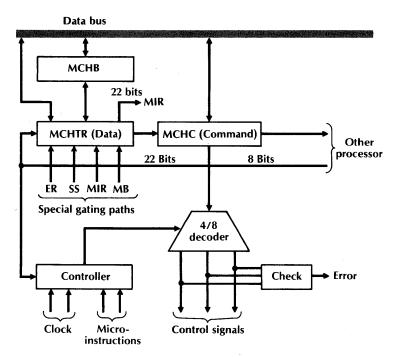

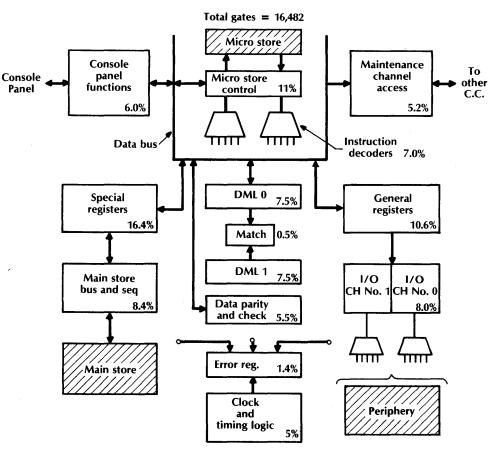

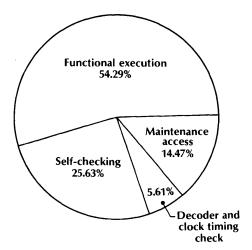

Abstract 461 Introduction 461 Allocation and Causes of System Downtime 462 *Hardware Reliability 462 Software Deficiencies 462 Recovery Deficiencies 463 Procedural Errors 463* Duplex Architecture 463 Fault Simulation Techniques 465 First Generation ESS Processors 466 *No. 1 ESS Processor 466 Operational Results of No. 1 ESS 469 No. 2 ESS Processor 470* Second Generation of ESS Processors 472 *No. 1 A Processor 472*  No. 3A Processor 474 Maintenance Design of No. 3A Processor 476 General Systems Description 476 General Processor Description 477 Detection Techniques 478 Recovery Techniques 487 Diagnostic Hardware 491 Repair 493 Hardware Implementation 494 Summary 495 Acknowledgment 496 References 496

#### 13 Pluribus—An Operational Fault-Tolerant Multiprocessor David Katsuki,

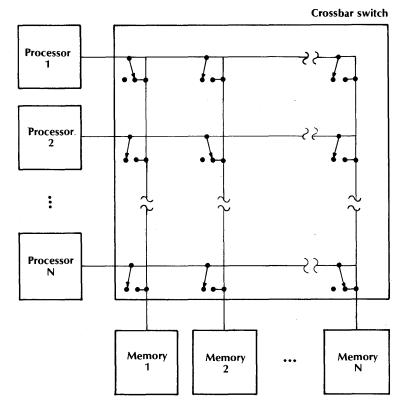

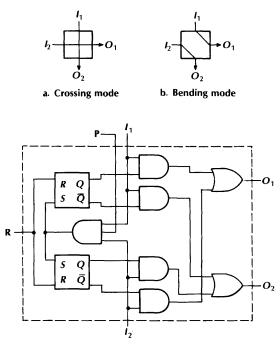

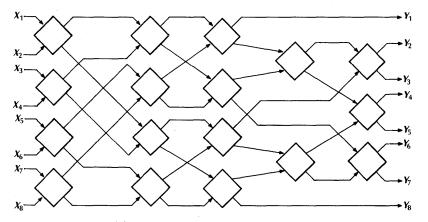

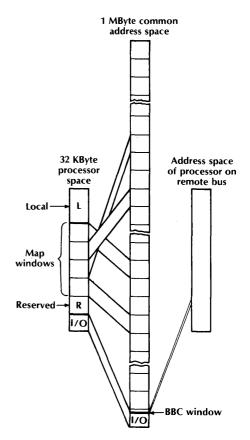

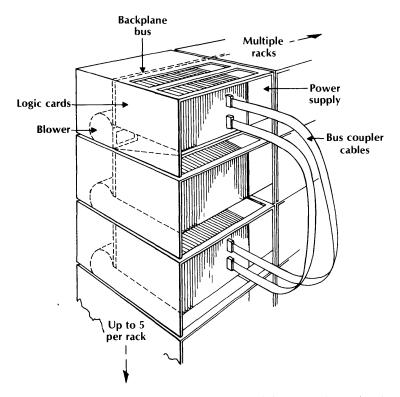

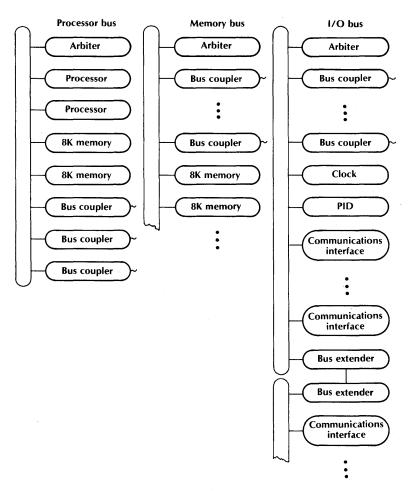

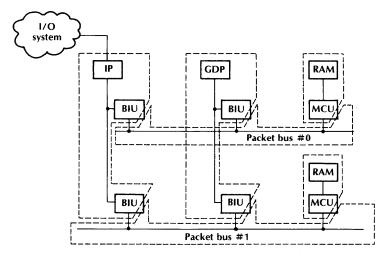

Eric S. Elsam, William F. Mann, Eric S. Roberts, John G. Robinson, F. Stanley Skowronski, and Eric W. Wolf **497**

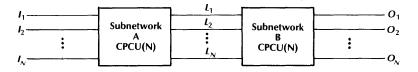

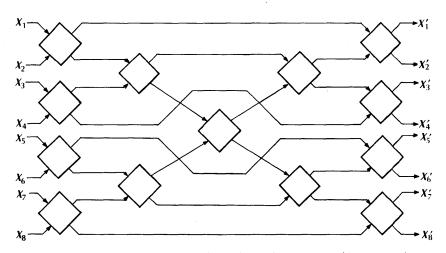

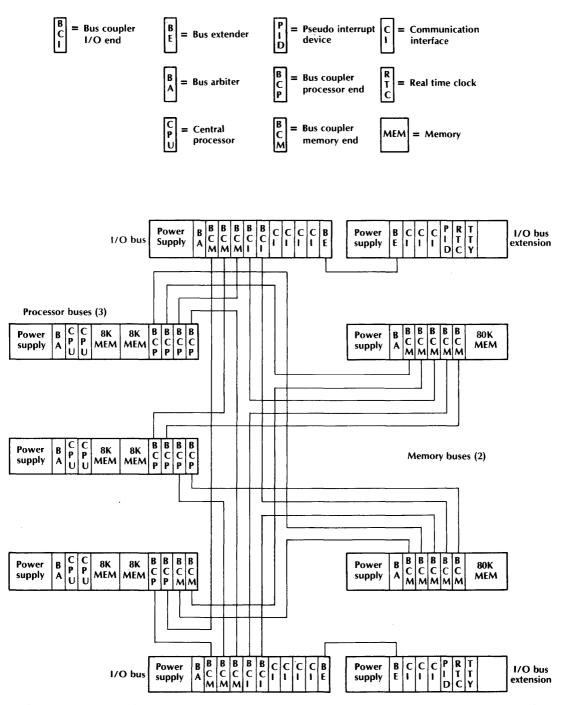

Abstract 497 Introduction 497 Pluribus System Architecture 499 Major Design Decisions 499 System Overview 500 Physical System Structure 502 Redundancy 507 The Pluribus Operating System 507 General Responsibility of the Operating System 508 Hierarchical Structure of the STAGE System 508 Establishing Communication 509 The Consensus Mechanism 510 Application-Dependent Checking 511 An Example of Application Reliability 512 Advantages of the Pluribus Approach to Fault-Tolerance 513 Recent Field Experience 513 Pluribus System Maintainability 516 **Reporting Facilities** 517 Remote Diagnosis and Repair 517 Partitioning 518 Reloading and Down-Line Loading 518 Maintenance Experience 518 Other Applications and Extensions 519 Message Systems 519 Real-Time Signal Processing 520 General-Purpose Timesharing Sytems 520 Reservation Systems 520 Process Control 520 Acknowledgment 521 References 521

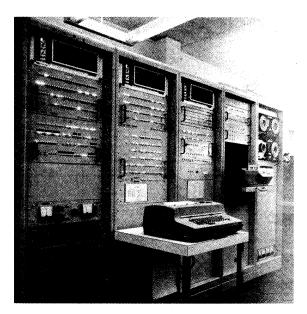

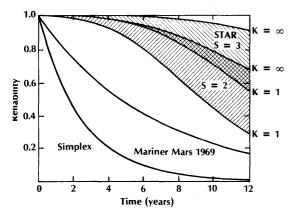

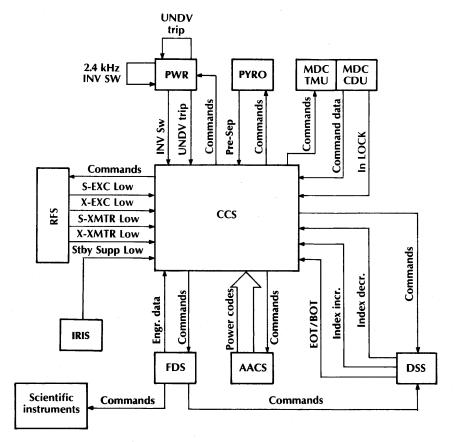

14 The STAR (Self-Testing And Repairing) Computer: An Investigation of the Theory and Practice of Fault-Tolerant Computer Design Algirdas Avižienis, George C. Gilley, Francis P. Mathur, David A. Rennels, John A. Rohr, and David K. Rubin 523

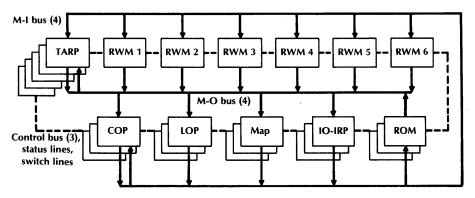

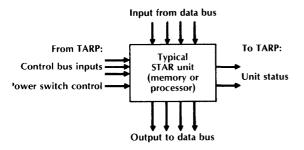

Abstract 523 Introduction: Chronology and Rationale 523 Architecture of the STAR Computer 525 Methods of Fault Tolerance 525 Hardware System Organization 526 Standard Operation 527 Computer Words: Formats and Encoding 528 Control Error Detection 529 Properties of Functional Units 530 The Test and Repair Processor (TARP) and Recovery Mode 530 Comparative Reliability Analysis 532 STAR Computer Software System 535 Extension of STAR Techniques to Peripheral Systems 536 Design of the TOPS Control Computer 537 Current Research 538 Acknowledgment 538 References 539

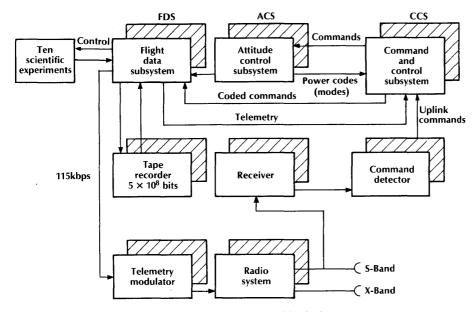

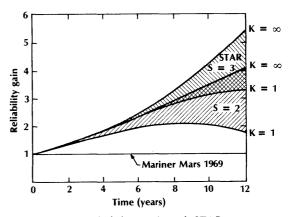

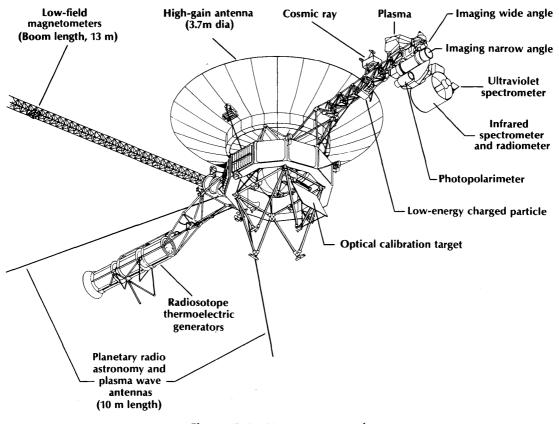

15 Automatic Fault Protection in the Voyager Spacecraft C. P. Jones 541

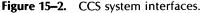

Abstract 541 Introduction 541 The Mission 541 The Spacecraft 542 Achieving Reliability 542 Automatic Fault Protection Design 544 Requirements 544 Implementation of the Requirements in Hardware 544 Implementation of the Requirements in Software 545 Command Computer Subsystem Functional Description 546 CCS Routine Structure 547 Fault-Protection Software 547 Fault Protection in CCS 548 Design Validation 554 In-Flight Experience 556 Failures and Degraded Performance 556 Environmental Factors 556 Sequence Errors 556 Conclusions and Recommendations 557 Acknowledgment 557 Reference 557

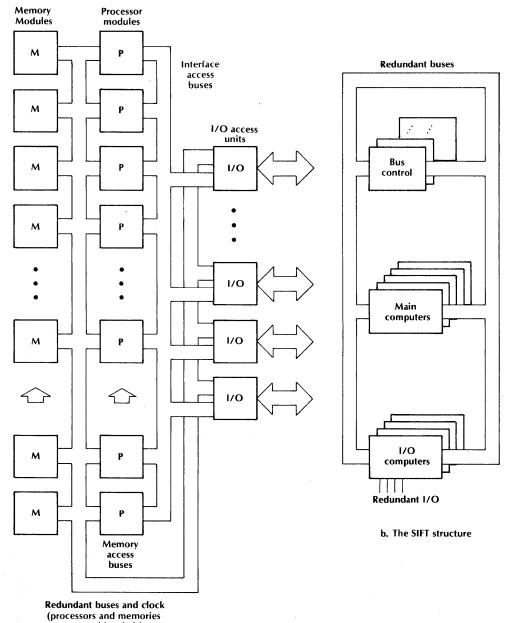

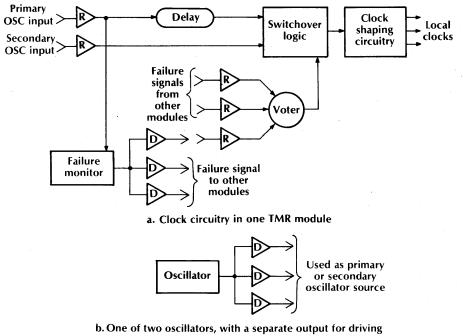

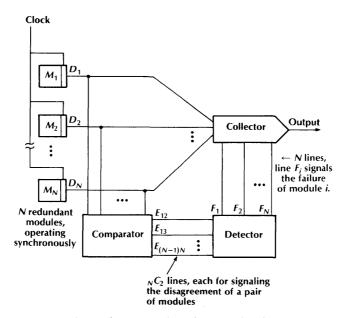

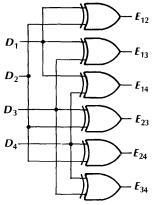

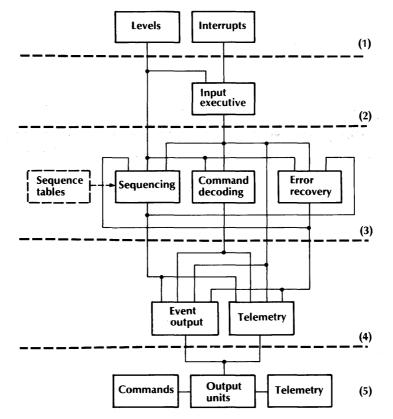

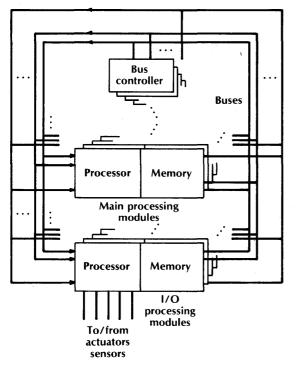

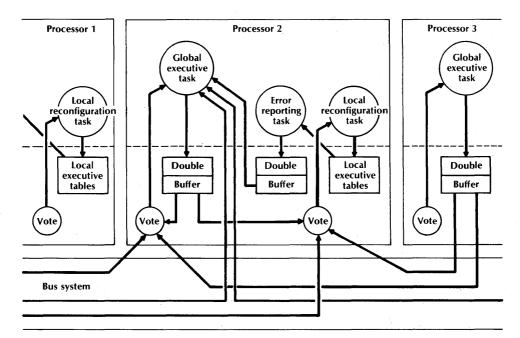

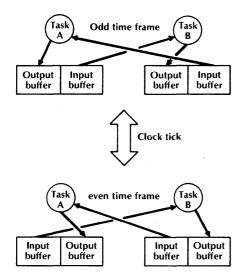

16 SIFT: Design and Analysis of a Fault-Tolerant Computer for Aircraft Control John H. Wensley, Leslie Lamport, Jack Goldberg, Milton W. Green, Karl N. Levitt, P. M. Melliar-Smith, Robert E. Shostak, and Charles B. Weinstock 559 Abstract 559 Introduction 559 Motivation 560 Background 560 SIFT Concept of Fault Tolerance 561 System Overview 561 Fault Isolation 562 Fault Masking 563 Scheduling 563 **Processor Synchronization** 564 Reliability Prediction 567 The SIFT Hardware 568 The Software System 572 The Application Software 572 The SIFT Executive Software 572 Fault Detection 576 The Simulator 577 The Proof of Correctness 577 Concepts 577 Models 578 The Reliability Model 579 The Allocation Model 579 Future Work 581 Conclusions 582 Appendix: Sample Special Specification 582 Notes 583 Acknowledgment 584 References 584

#### 17 FTMP—A Highly Reliable Fault-Tolerant Multiprocessor for Aircraft

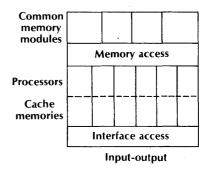

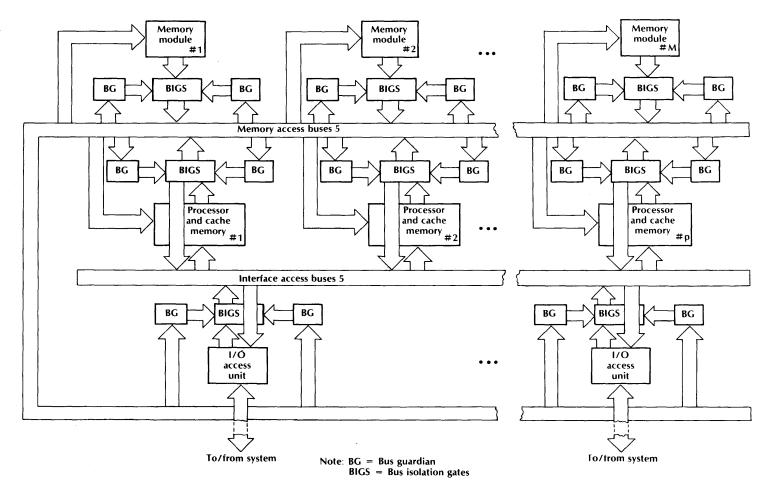

Albert L. Hopkins, Jr., T. Basil Smith, III, and Jaynarayan H. Lala 585

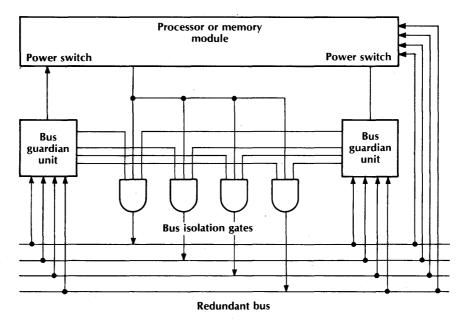

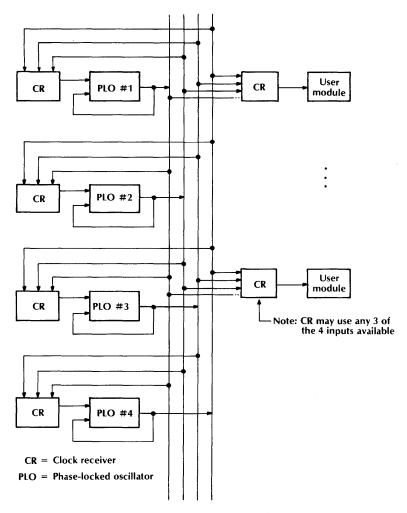

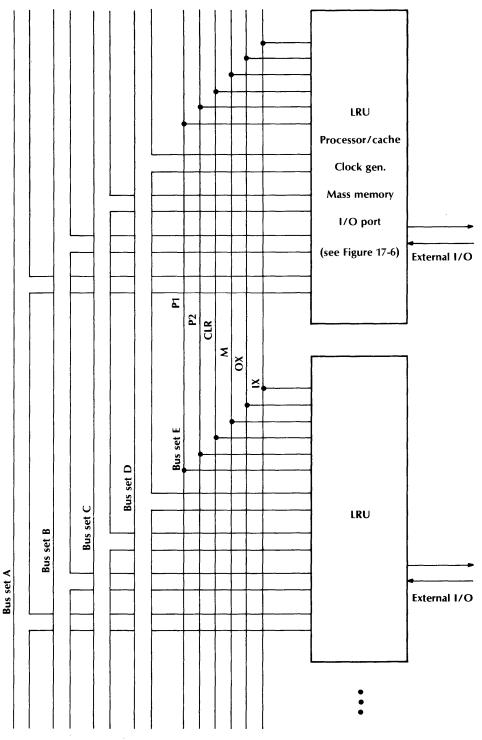

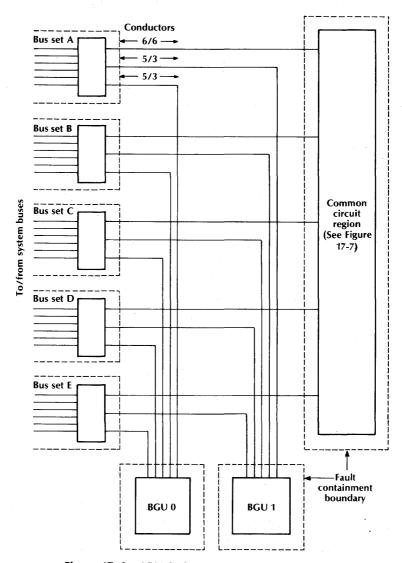

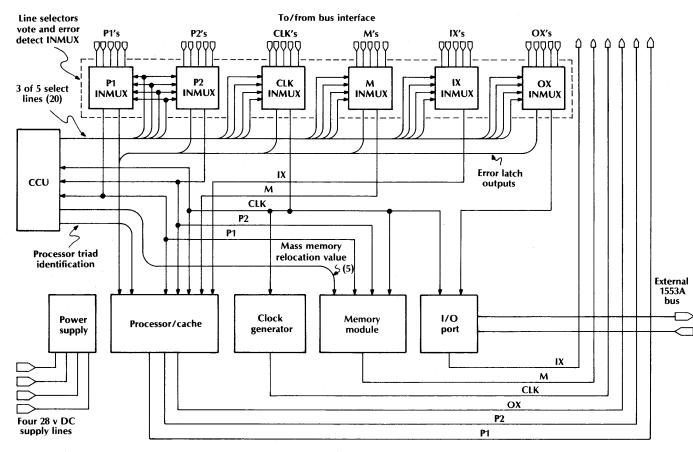

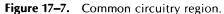

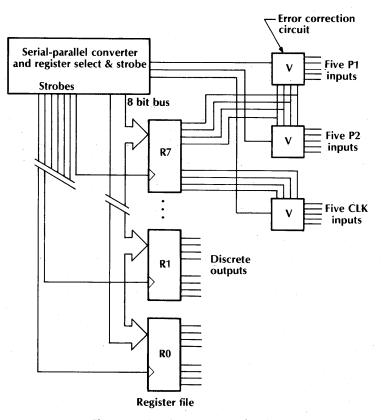

Abstract 585 Introduction 586 Background and Context 586 Rationale of the FTMP Approach 587 Theory of the FTMP 588 Nominal Organization 588 Redundant Organization 590 Synchronization 593 Malfunction Management 594 Description of an Engineering Prototype of the FTMP 598 The Redundant Bus Structure 602 LRU Interfacing to the Bus System 602 System Control Units 603 The Principal Fault-Containment Region 603 Primary Power 607 Survival and Dispatch Probability Models for the FTMP 607 Survival Probability Models 607 Impact of Intermittent Faults 612 Dispatch Reliability of the FTMP Computer 615 Experimental Results 616 Fault Diagnostic Capabilities 617 Software Experience 617 Conclusion 619 Critical Areas of the FTMP Design 619 Summary 619 Acknowledgments 620 References 620

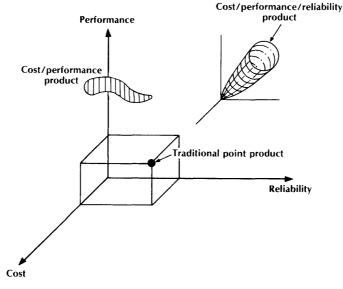

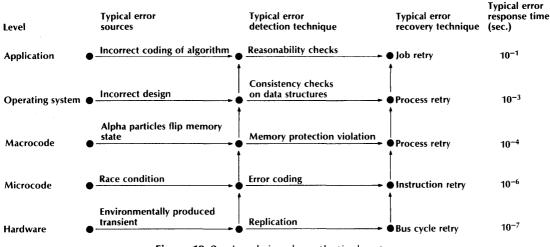

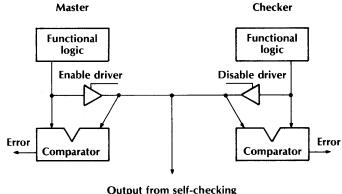

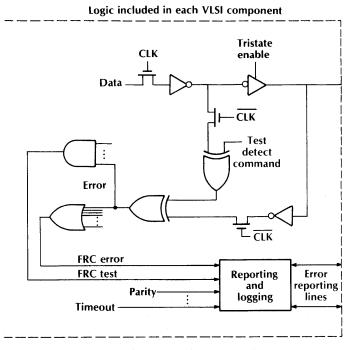

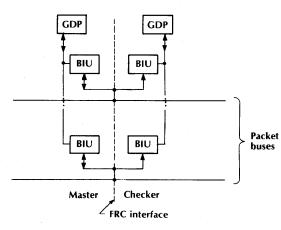

**18 Design Methodology for High Reliability Systems: The Intel 432**<sup>®</sup> Daniel P. Siewiorek and David Johnson 621

A Design Methodology for a High Reliability System 621 Define System Objectives 621 Limit the Scope 623 Define the Layers of Fault Handling 623 Define Reconfiguration and Repair Boundaries 625 Design the Fault-Handling Mechanisms 626 Identify the Hardcore 626 The Impact of Technology 626 The Intel 432 Detection Mechanisms 627 Define System Objectives 627 Limit the Scope 627 Define Layers of Fault Handling 628 Define Reconfiguration and Repair Boundaries 628 Design the Fault-Handling Mechanisms 630 Identify the Hardcore 633 The Intel 432 Error Isolation and Reporting Mechanisms 634 Summary 636 Reference 636

#### APPENDIXES 637

A Coding for Error Control D. T. Tang and R. T. Chien 639

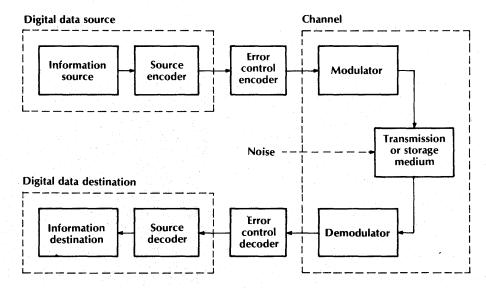

Abstract 639 Basic Definitions 640 Redundancy 640 Source Codes 640

CONTENTS xvii

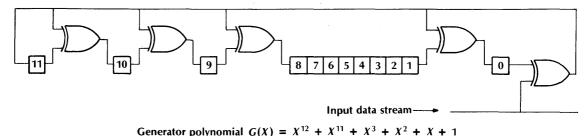

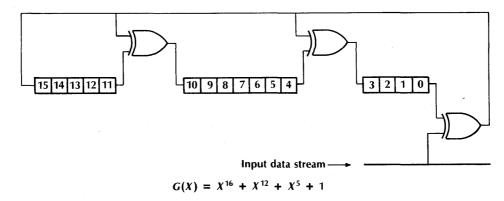

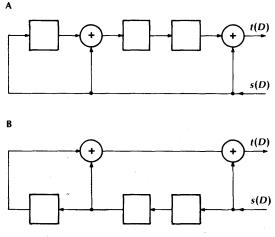

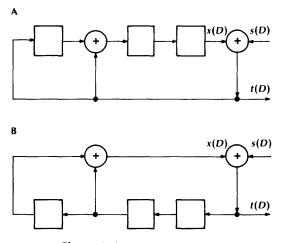

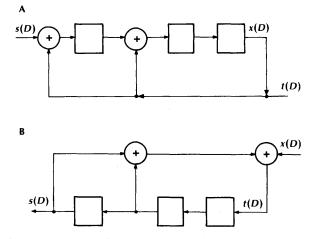

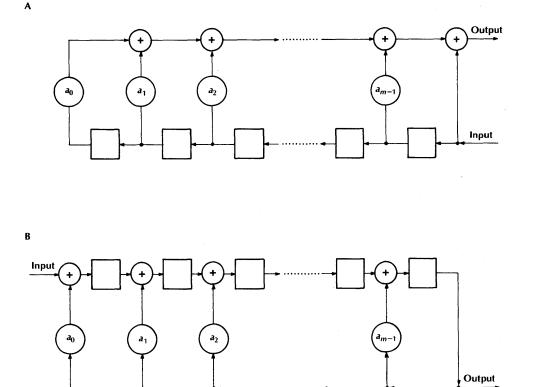

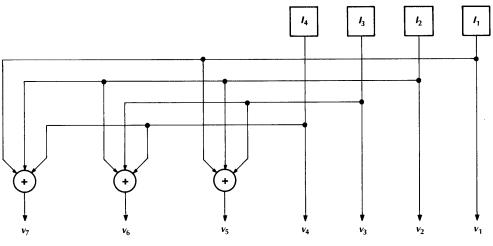

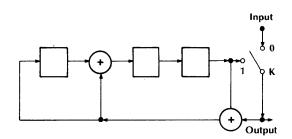

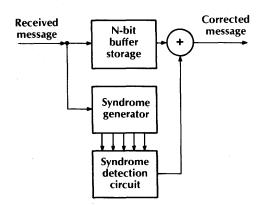

Block Codes 640 Binary Codes 640 Errors in Digital Data Channels 640 Transmission and Storage 640 Source Encoding 641 Modulation and Demodulation 641 Error Sources 642 Error Statistics 642 Storage 642 Channel Models 642 Mathematical Structures in Coding 643 Linear Separable Codes 643 Polynomial Cyclic Codes 644 General Requirements for Encoding and Decoding 644 Error Syndromes 644 Conditional Maximum Likelihood Decoding 645 Maximum Likelihood Decoding 645 Minimum Distance Decoding 645 Linear Switching Circuits and Shift Registers 646 Polynomials in Delay Operator D 646 Encoders and Decoders 648 Functional Classes of Error-Control Codes 650 Coding Strategy 651 Error Detection 651 Partial Correction 652 Erasures 653 Adaptive Coding Schemes 653 Sequential Decoding 654 Some Error-Control Applications 654 Data Communications 654 Data Storage 654 Auxiliary Storage 655 Digital Cypress Error Control 655 Concluding Remarks 655 Appendix 1: Structure of Linear Codes 656 Appendix 2: Structure of Polynomial Codes 657 Appendix 3: Methods for Finding Generator Polynomials 658 Single-Error-Correcting Codes 658 Burst-Error-Correcting Codes 658 Independent-Error-Correcting Codes 659 BCH Codes 659 Examples 659 Multiple-Burst-Correcting Codes 660 Reed-Solomon Codes 661 Example Decoders 661 Appendix 4: Specialized Error-Control Codes 662 Interleaved Codes 662

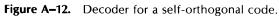

N-Dimensional Codes 663 Shortened Codes 663 Threshold-Logic-Decodable Codes 663 Self-Orthogonal Decoding Example 664 Synchronization Codes 665 Convolutional Codes 665 Constant-Weight Codes 667 Arithmetic Codes 667 Appendix 5: Cyclic Redundancy Checking 668 References 669

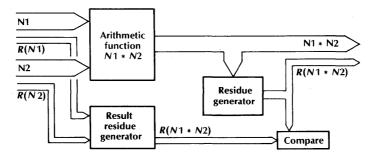

B Arithmetic Error Codes: Cost and Effectiveness Studies for Application in Digital System Design Algirdas Avižienis 671

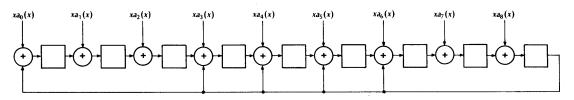

Abstract 671 Methodology of Code Evaluation 671 Scope of the Problem 671 The Criteria of Cost 672 The Criteria of Effectiveness 673 Classes of Logic Faults 674 Fault Effects in Binary Arithmetic Processors 675 Basic Faults in Parallel Arithmetic 675 Repeated-Use Faults in Binary Processors 677 Low-Cost Radix-2 Arithmetic Codes 678 Implementation of Arithmetic Error Codes 678 The Low-Cost Checking Algorithm 679 Fault-Effectiveness: One-Use Faults 680 Fault-Effectiveness: Determinate Repeated-Use Faults 680 Fault-Effectiveness: Indeterminate Repeated-Use Faults 681 Repeated-Use Faults in Residue Codes 682 Multiple Arithmetic Error Codes 683 Multiple Low-Cost Codes 683 "Hybrid-Cost" Forms of Multiple Codes 685 Acknowledgment 686 References 686

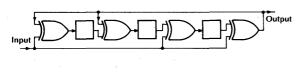

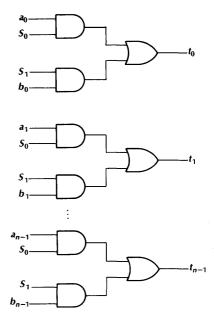

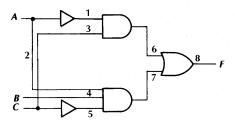

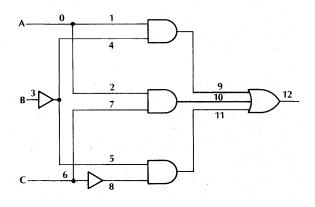

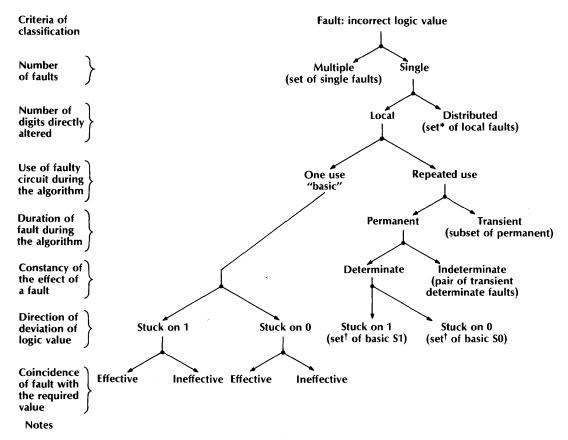

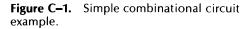

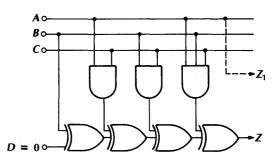

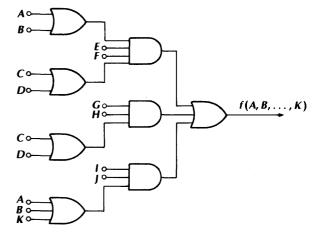

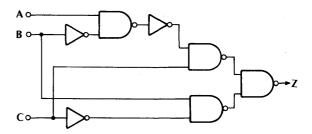

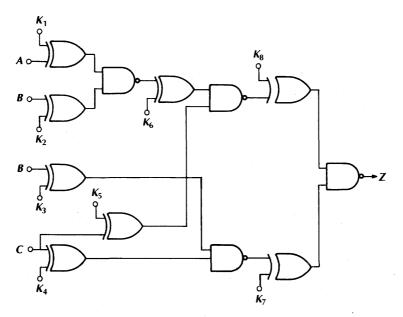

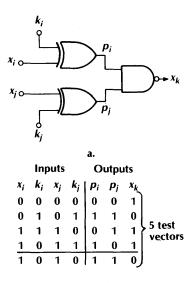

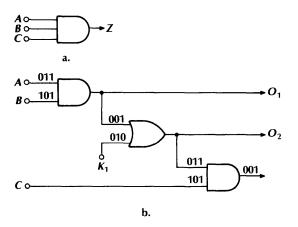

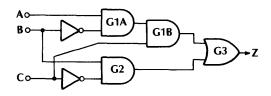

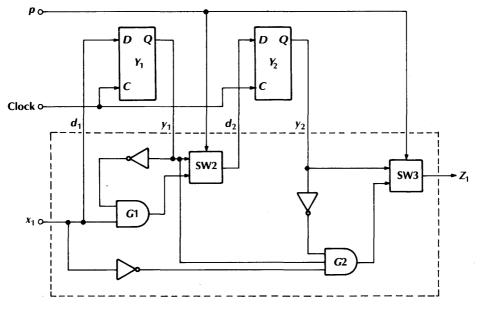

C Recent Developments in the Theory and Practice of Testable Logic Design R. G. Bennetts and R. V. Scott 687

Abstract 687 Introduction 687 Theoretical Developments 688 Combinational Circuits 688 Sequential Circuits 696 Iterative Arrays 702

Practical Aspects of Testable Logic Design 703

Guideline 1: Give the tester access to internal circuit board nodes 70

Guideline 2: As a general rule, avoid logically redundant circuits 70

Guideline 3: Make faults as easy to locate as possible 705 Guideline 4: Use synchronous (clocked) circuitry whenever possible 706 Guideline 5: Take precautions to isolate the clock from the logic 706 Guideline 6: Make it possible to initialize sequential circuits prior to testing 706 Guideline 7: Take into account the operational characteristics of the tester to be used for a particular board 706 Guideline 8: Take test economics into consideration when developing a new logic design 706 Concluding Remarks 707 Acknowledgment 708 References 708

#### D Summary of MIL-HDBK-217B Reliability Model 709

#### E Summary of MIL-HDBK-217C Reliability Model 715

217C Model 715 217C Notice 1 Model 716 Reference 719

References 721

Contributing Authors 749

Trademarks 749

Credits 751

Index 753

## Preface

System reliability has been a major concern since the beginning of the electronic ligital computer age. The earliest computers were constructed of components such is relays and vacuum tubes that would fail to operate correctly as often as once every hundred thousand or million cycles. This error rate was far too large to enure correct completion of even modest calculations requiring tens of millions of operating cycles. The Bell relay computer (c. 1944) performed a computation wice and compared results; it also employed error-detecting codes. The first comnercial computer, the UNIVAC I (c. 1951), utilized extensive parity checking and wo arithmetic logic units (ALUs) in a match-and-compare mode. Today, interest n reliability pervades the computer industry, from large mainframe manufacturers o semiconductor fabricators, who produce not only reliability-specific chips (such is for error-correcting codes) but also entire systems (such as the Intel 432).

Computer designers have to be students of reliability, and so do computer sysem users. Our dependence on computing systems has grown so great that it is becoming difficult or impossible to return to less sophisticated mechanisms. When an urline seat selection computer "crashes," for example, the airline can no longer evert to assigning seats from a manual checklist; since the addition of roundtrip heck-in service, there is no way of telling which seats have been assigned to pasengers who have not yet checked in without consulting the computer. The last esort is a free-for-all rush for seats. The computer system user must be able to inderstand the advantages and limitations of the state-of-the-art in reliability deign; determine the impact of those advantages and limitations upon the applicaion or computation at hand; and specify the requirements for the system's eliability so that the application or computation can be successfully completed.

The literature on reliability has been slow to evolve. During the 1950s reliability vas the domain of industry, and the quality of the design often depended on the leverness of an individual engineer. Notable exceptions are the work of Shannon 1948] and Hamming [1950] on communication through noisy (hence error-nducing) channels, and of Moore and Shannon [1956] and von Neumann [1956] in redundancy that survives component failures. Shannon and Hamming inauguated the field of coding theory, a cornerstone in contemporary systems design. Moore, Shannon, and von Neumann laid the foundation for development and nathematical evaluation of redundancy techniques.

During the 1960s the design of reliable systems received systematic treatment in ndustry. Bell Telephone Laboratories designed and built an Electronic Switching System (ESS), with a goal of only two hours down-time in 40 years [Downing, Novak, and Tuomenoksa, 1964]. The IBM System/360 computer family had extenive serviceability features [Carter et al., 1964]. Reliable design also found ncreasing use in the aerospace industry, and a triplicated computer helped man and on the moon [Cooper and Chow, 1976; Dickinson, Jackson, and Randa, 1964]. The volume of literature also increased. In 1962 a Symposium on Redundancy

| Chapters                                              | Remarks                                                                                                                             |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>Fundamental Concepts                             |                                                                                                                                     |

| 2<br>Faults and Their<br>Manifestations               |                                                                                                                                     |

| 3<br>Reliability and<br>Availability<br>Techniques    | A suitable subset such as one branch of the taxonomy (i.e. fault avoidance, fault detection, masking redundancy dynamic redundancy) |

| <b>4</b><br>Maintainability and<br>Testing Techniques | • · · ·                                                                                                                             |

| <b>5</b><br>Evaluation Criteria                       | Through to, but not including, Markov models                                                                                        |

| <b>6</b><br>Financial Considerations                  |                                                                                                                                     |

| 7<br>C.vmp                                            | As time permits, augment by other examples                                                                                          |

| <b>18</b><br>Intel 432                                |                                                                                                                                     |

Table P-1.

Proposed structure for undergraduate course.

Techniques held in Washington, D.C. led to the first comprehensive book on the topic [Wilcox and Mann, 1962]. Later, Pierce [1965] published a book generalizing and analyzing the Quadded Redundancy technique proposed by Tryon and reported in Wilcox and Mann [1962]. A community of reliability theoreticians and practitioners was developing.

During the 1970s interest in system reliability expanded explosively. Companies were formed whose major product was a reliable system (such as Tandem). Due to the effort of Algirdas Avizienis and other pioneers, a Technical Committee or Fault Tolerant Computing (TCFTC) was formulated within the Institute of Electrical and Electronic Engineers (IEEE). Every year since 1971, the TCFTC has held an International Symposium on Fault-Tolerant Computing. The time is ripe for a book on the design of reliable computing structures.

This book has three audiences. The first is the advanced undergraduate studen interested in reliable design; as prerequisites, this student should have had courses in introductory programming, computer organization, digital design, and probabil ity. Part I of the book, selected chapters of Part II, and end-of-chapter problems are sufficient for a quarter- or semester-length course like that suggested in Table P-1.

The second audience is the graduate student seeking a second course in reliable design, perhaps as a prelude to engaging in research. The more advanced portion

**ble P-2.** Proposed structure for graduate course.

| hapters                                    | Augmentation                                                                                                                                                               |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| undamental Concepts                        |                                                                                                                                                                            |

| aults and Their<br>lanifestations          | Ross [1972] and/or Shooman [1968] for random variables, statistical parameter estimation                                                                                   |

|                                            | ARINC [1964] for data collection and analysis                                                                                                                              |

| eliability and<br>vailability<br>echniques | Appendix A, Peterson and Weldon [1972] for coding theory<br>Sellers, Hsiao, and Bearnson [1968b] for error detection<br>techniques                                         |

|                                            | Proceedings of Annual IEEE International Symposium on Fault-Tolerant Computing                                                                                             |

| 2 Contraction                              | Special issues of the <i>IEEE Transactions on Computers</i> on Fault-Tolerant Computing (e.g., Nov 1971, March 1973, July 1974, May 1975, June 1976, June 1980, July 1982) |

|                                            | Special issues of <i>Computer</i> on Fault-Tolerant Computing (e.g., March 1980)                                                                                           |

| laintainability and esting Techniques      | Breuer and Friedman [1976] for testing<br>Proceedings of Cherry Hill Test Conference                                                                                       |

|                                            | Special issues of <i>Computer</i> on Testing (e.g., Oct. 1979)<br>ARINC [1964] for maintenance analysis                                                                    |

| valuation Criteria                         | Ross [1972], Howard [1971], Shooman [1968], Craig [1964] for Markov models and their solutions                                                                             |

| inancial Considerations                    | Phister [1979]                                                                                                                                                             |

| art II                                     | Oct. 1978 special issue of the Proceedings of the IEEE.                                                                                                                    |

F Part I and the system examples of Part II should be augmented by other books nd current research literature as suggested in Table P-2. A project, such as design a dual system with a factor of 20 greater Mean-Time-To-Failure, while minimizig Life-Cycle Costs, would help to crystallize the material for students. An extenve bibliography provides access to the literature.

The third audience is the practicing engineer. A major goal of this book is to rovide enough concepts to enable the practicing engineer to incorporate compreensive reliability techniques into his or her next design. Part I provides a taxonmy of reliability techniques and the mathematical models to evaluate them. esign techniques are illustrated through the series of articles in Part II, which escribe actual implementations of reliable computers. These articles were written y the system designers. The final chapter provides a methodology for reliable system design and illustrates how this methodology can be applied in an actual design situation (the Intel 432).

The book is divided into two parts. Part I deals with the theory and Part II with the practice of reliable design. The appendixes provide detailed information or coding theory, design for testability, and the MIL-HDBK-217 component reliability model.

The authors wish to express deep gratitude to many colleagues in the faulttolerant computing community. Without their contributions and assistance this book could not have been written. We are especially grateful to the authors of the papers who shared their design insights with us. Special thanks go to Sudhir Bhagwani and Justin Rattner for assistance with Chapter 18. John Shebell provided material and insight for Chapter 6.

Xavier Castillo and Vittal Kini provided material on mathematical modeling and computer aids, respectively. Ashok Ingle assisted in an earlier draft and provided several problems at the end of chapters. Comments from several reviewers and students were particularly helpful.

Special thanks are due to colleagues at both Carnegie-Mellon University and Digital Equipment Corporation (DEC) for providing an environment conducive to generating and testing ideas. The entire staff of Digital Press provided excellent support for a timely production.

This book would not have been possible without the patience and diligence of Mrs. Dorothy Josephson, who typed and retyped the many drafts of the manuscript.

Dan Siewiorek Bob Swarz

#### **REFERENCES\***

ARINC [1964]; Breuer and Friedman [1967]; Carter et al. [1964]; Cooper and Chow [1976]; Craig [1964]; Dickinson, Jackson, and Randa, [1964]; Downing, No wak, and Tuomenoksa [1964]; Hamming [1950]; Howard [1971]; Moore and Shan non [1956]; Peterson and Weldon [1972]; Phister [1979]; Pierce [1965]; Ross [1972]; Sellers, Hsiao, and Bearnson [1968b]; Shannon [1948]; Shooman [1968] von Neumann [1956]; Wilcox and Mann [1962].

\* For full citations of the shortened references at the end of each chapter, see References at the back o the book.

# THE THEORY OF RELIABLE SYSTEM DESIGN

<sup>2</sup>art I of this book presents the many disciplines required to construct a reliable omputing system. Chapter 1 explains the motivation for reliable systems and rovides the theoretical framework for their design, fabrication, and mainteiance. First we consider the motivation for interest in fault-tolerant systems. Next we present the hierarchical levels into which a computer system is ustomarily divided to enable the engineer to deal with it efficiently and ffectively; we also explain the reasons for introducing divisions into the life cycle of a computer system. After defining several terms and metrics important to ault-tolerant computing, Chapter 1 provides a detailed discussion of two stages n a system's life: manufacturing and operation. Last, the chapter explains some of the mathematical models used in the design of a computer system and specifies he parameters that are under the engineer's control.

Chapter 2 discusses faults in a computer system: failure mechanisms, fault nanifestations at several levels in the structural hierarchy (physical, logical, and ystem), fault prediction, and fault measurement. A review of applicable probaility theory is presented as an aid to understanding the mathematics of the arious fault distributions. Common techniques for matching empirical data to ault distributions, such as the maximum likelihood estimator, linear regression, nd the chi-square goodness-of-fit test are discussed.

Chapter 2 introduces methods for estimating permanent failure rates, including ne MIL-HDBK-217 procedure, a widely used mathematical model of permanent aults in electronic equipment, and the life-cycle testing and data analysis pproaches. It then addresses the problem of finding an appropriate distribution or transient errors by analyzing field data from four mainframe time-sharing omputers operated by Carnegie-Mellon University.

Chapter 3 deals with reliability techniques, that is, ways to improve the mean me to failures. A comprehensive taxonomy of reliability and availability echniques is presented. There is also a catalog of techniques, along with valuation criteria.

Chapter 4 deals with maintainability techniques, that is, ways to improve the tean time to repair of a failed computer system. It provides a taxonomy of esting and maintenance techniques and describes ways to detect and correct purces of errors at each stage of a computer's life cycle. Specific strategies are iscussed for testing during the manufacturing phase. Several logic-level acceptnce tests are explained, such as exclusive-OR testing, signature analysis, oolean difference, path sensitization, and the D-algorithm. The chapter also itroduces a discipline, called design for testability, which attempts to define roperties of easy-to-test systems. PART

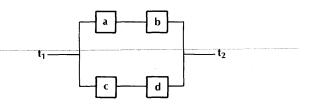

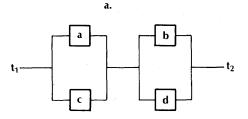

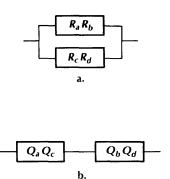

How can a reliable or maintainable design be mathematically evaluated? That is, if a system is supposed to be down no more than two hours in 40 years, how can one avoid waiting that long to confirm success? Chapter 5 defines a host of evaluation criteria, establishes the underlying mathematics, and presents deterministic models and simulation techniques. Simple series-parallel models are introduced as a method for evaluating the reliability of nonredundant systems and systems with standby sparing. Next, several types of combinatorial (failureto-exhaustion) models are described. The chapter also introduces ways of reducing nonseries, nonparallel models to more tractable forms.

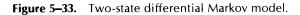

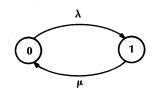

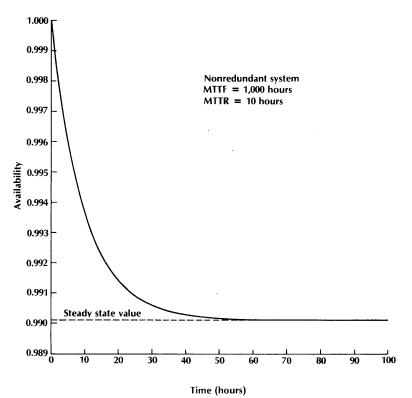

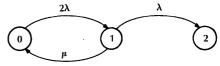

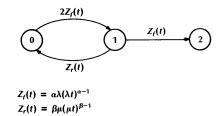

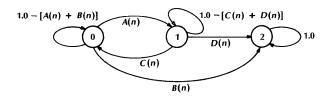

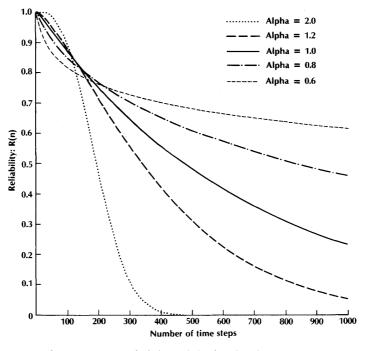

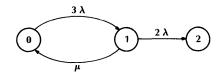

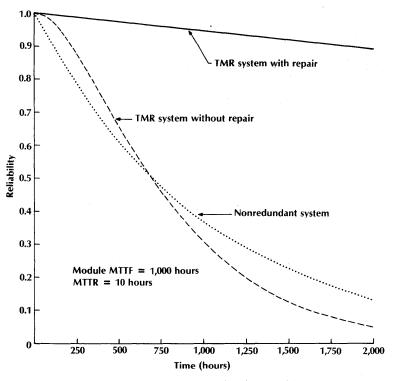

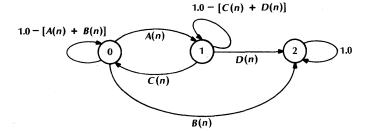

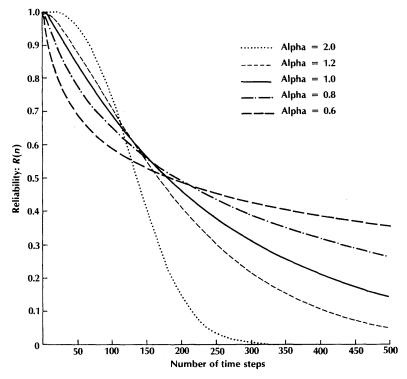

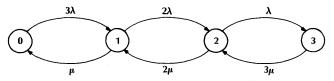

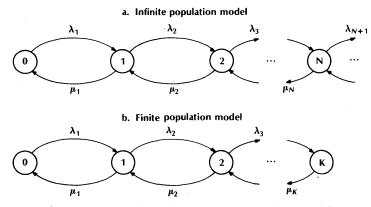

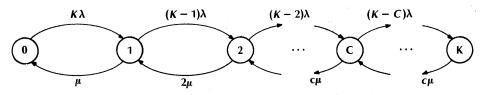

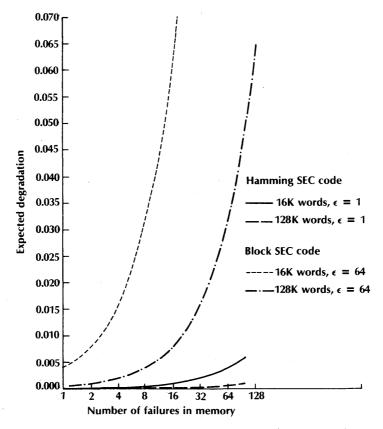

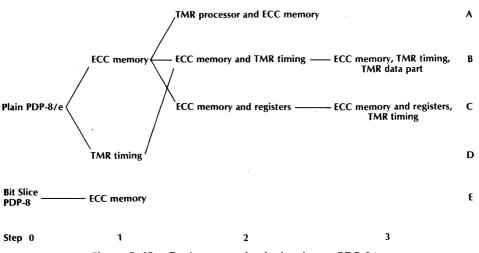

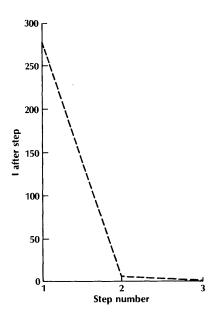

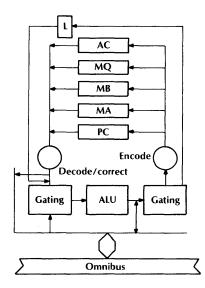

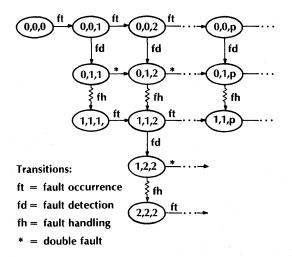

Chapter 5 continues with Markov models, which define various system states and express the probability of going from one state to another. In these models, the probability depends only on the present state and is independent of how the present state was reached. After describing several other simulation and modeling techniques, the chapter culminates in a case study of an effort to make a more reliable version of the PDP-8/e, using the techniques defined in Chapter 3.

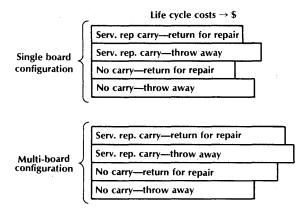

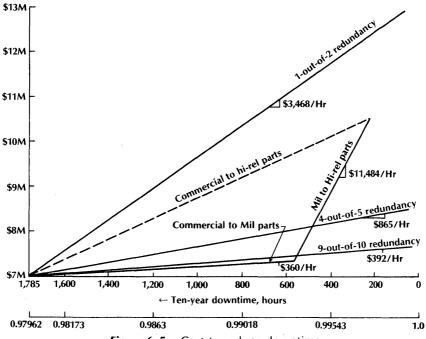

Finally, Chapter 6 is concerned with the financial considerations inherent in the design, purchase, and operation of a computer system. The discussion adopts two major viewpoints: that of the maintenance provider and that of the system's owner/operator. An explanation of the various sources of maintenance costs, such as labor and material, is followed by an overview of the field service business. Several maintenance cost models are suggested, along with a method for assessing the value of maintainability features. The chapter describes two of the many ways of modeling the life-cycle costs of owning and operating a computer system; these cost models are essential to the system designer in understanding the financial motivations of the customer.

2

## **Fundamental Concepts**

### HE IMPORTANCE OF ELIABILITY

listorically, reliable computers have been limed to military, industrial, aerospace, and comlunications applications in which the conseuence of computer failure is significant ecoomic impact and/or loss of life. Reliability is of itical importance wherever a computer malinction could have catastrophic results, as in le space shuttle, aircraft flight-control systems, ospital patient monitors, and power system ontrol. Reliability techniques have become of creasing interest to general purpose computer stems because of several recent trends, a few of hich are listed below:

Harsher Environments. With the advent of icroprocessors, computer systems have moved om the clean environments of computer rooms industrial environments. The cooling air conins more particulate matter. Temperature and imidity vary widely and are frequently subject spontaneous changes. The primary power pply fluctuates, and there is electromagnetic terference.

*Novice Users.* As computers proliferate, the pical user knows less about proper operation of e system. Consequently, the system has to be le to tolerate more inadvertent user abuse.

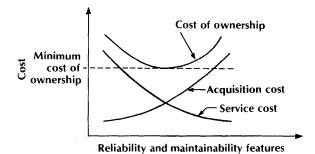

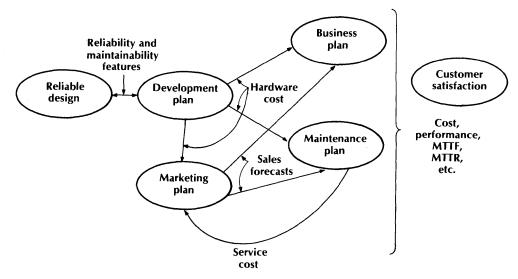

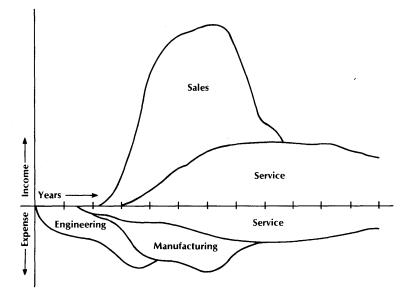

Increasing Repair Costs. As hardware costs ntinue to decline and labor costs escalate, a er cannot afford frequent calls for field service. gure 1-1 depicts the relation between cost of mership and the addition of reliability, mainnability, and availability features. Note that as rdware costs increase, service costs decrease e to fewer and shorter field service calls.

# 1

**Figure 1–1.** Cost of ownership as a function of reliability and maintainability.

Larger Systems. As systems become larger, there are more components that can fail. Because the overall failure rate is directly related to the sum of the failure rates of individual components, fault-tolerant designs may be required to keep the overall system failure rate at an acceptable level.

The increased interest in fault tolerance has already had an impact on the industrial world. Manufacturers of large mainframe computers, such as IBM, Univac, and Amdahl, use redundancy both for improving reliability and for assisting field service personnel in fault isolation. Minicomputer manufacturers have also been incorporating fault-tolerant features, such as Hamming error-correcting codes in memory. Special Large Scale Integration (LSI) chips have been introduced to perform cyclic redundancy coding and decoding. Some companies, such as Tandem, have been formed solely to market faulttolerant computers.

#### LEVELS IN A DIGITAL SYSTEM\*

Digital computer systems are enormously complex. To make them more comprehensible it is necessary to divide the system into several levels. One can then proceed upward from the most primitive level to the highest conceptual level through a series of abstractions. Each abstraction contains only information important to its level and suppresses unnecessary information about lower ones. Because system designers utilize the hierarchical concept to manage the complexity of a digital system, the levels frequently coincide with the system's physical boundaries. Table 1-1 describes a typical set of levels for a digital computer.

| Table 1–1. | Levels of | fabstraction | for | digital |

|------------|-----------|--------------|-----|---------|

| computers. |           |              |     |         |

| Level   | Sublevel               | Components                    |

|---------|------------------------|-------------------------------|

| PMS     |                        | Processors                    |

|         |                        | Memories                      |

|         |                        | Switches                      |

|         |                        | Controllers                   |

|         |                        | Transducers                   |

|         |                        | Data operators                |

|         |                        | Links                         |

| Program | High-level<br>language | Software                      |

|         | ISP                    | Memory state                  |

|         |                        | Processor state               |

|         |                        | Effective address calculation |

|         |                        | Instruction decode            |

|         |                        | Instruction execution         |

| Logic   | Register               | Data paths                    |

|         | transfer               | Registers                     |

|         |                        | Data operators                |

| 1       |                        | Control                       |

|         |                        | Hardwired                     |

|         |                        | Sequential logic machines     |

|         |                        | Microprogramming              |

|         |                        | Microsequencer                |

|         |                        | Microstore                    |

(Table continues on next page

<sup>&</sup>lt;sup>•</sup> This discussion is adapted from D. Siewiorek, G. Bell, and A. Newell, *Computer Structures: Principles and Examples*, (New York, McGraw-Hill, 1981).

**Table 1–1**—Continued

| Level   | Sublevel  | Components        |

|---------|-----------|-------------------|

|         | Switching | Sequential        |

|         | circuit   | Flip-flops        |

|         |           | Latches           |

|         |           | Delays            |

|         |           | Combinatorial     |

|         |           | Gates             |

|         |           | Encoders/Decoders |

|         |           | Data operators    |

| Circuit | Circuit   | Resistors         |

|         |           | Capacitors        |

|         |           | Inductors         |

|         |           | Power sources     |

|         |           | Diodes            |

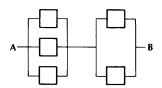

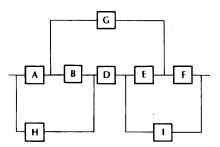

|         |           | Transistors       |

*Circuit Level.* The circuit level consists of uch components as resistors, capacitors, inducors, and power sources. The metrics of system ehavior include voltage, current, flux, and harge. The circuit level is not the lowest possible evel at which to describe a digital system. Varous electromagnetic and quantum mechanical henomena underlie circuit theory, and the opertion of electromechanical system devices (such s disks) requires more than circuit theory to to the their operation.

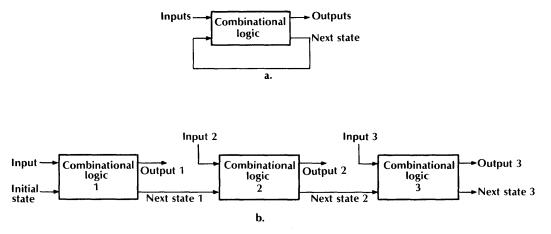

Logic Level. The logic level is unique to gital systems. The switching-circuit sublevel is proposed of such things as gates and data perators built out of gates. The logic level is rther subdivided into combinatorial and seiential logic circuits, the fundamental differice being the absence of memory elements in publication of the second se

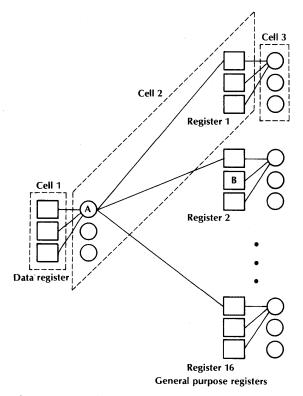

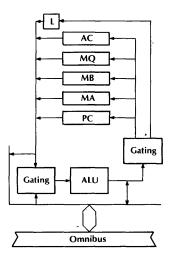

A register is a digital device that remembers e state of a set of binary digits. The Register 'ansfer (RT) sublevel deals with the next higher level of abstraction, namely, registers and functional transfers of information among registers. **RT** sublevels frequently are further subdivided into a data part and a control part. The data part is composed of registers, operators, and data paths. The control part provides the time-dependent stimuli that cause transfers between registers to take place.

In some computers, the control part is implemented as a hard-wired state-machine. With the availability of low-cost Read-Only Memories (ROMs), microprogramming is now a more popular way to implement the control function.

*Program Level.* The program level is unique to digital computers. At this level a sequence of instructions in the device is interpreted and causes action upon a data structure. This is the Instruction Set Processor (ISP) sublevel. The ISP description is used in turn to create software components that are easily manipulated by programmers—the high-level-language sublevel. The result is software, such as operating systems, runtime systems, application programs, and application systems.

*PMS Level.* Finally, the various elements input/output devices, memories, mass storage, communications, and processors—are interconnected to form a complete system.

#### **STAGES IN SYSTEM LIFE**

Not only are system levels important for describing a digital computer; a time dimension is also required. At what point a technique or methodology is applied during the life cycle of a system may be more important than at what physical level.

From a user's viewpoint, a digital system can be treated as a "black box" that produces outputs in response to input stimuli. Table 1-2 lists the numerous stages in the life of the box as it progresses from concept to final implementation. These stages include specification of input/output relationships, logic design, prototype debug-

#### 6 THE THEORY OF RELIABLE SYSTEM DESIGN

| Stage                       | Error Sources              | Error Detection<br>Techniques |

|-----------------------------|----------------------------|-------------------------------|

| Specification<br>and design | Algorithm<br>design        | Simulation                    |

|                             | Formal specifications      | Consistency checks            |

| Prototype                   | Algorithm<br>design        | Stimulus/<br>response testing |

|                             | Wiring and assembly        |                               |

|                             | Timing                     |                               |

|                             | Component<br>failure       |                               |

| Manufacture                 | Wiring and assembly        | System testing                |

|                             | Component<br>failure       | Diagnostics                   |

| Installation                | Assembly                   | System testing                |

|                             | Component<br>failure       | Diagnostics                   |

| Operational life            | Component failure          | Diagnostics                   |

|                             | Operator errors            |                               |

|                             | Environmental fluctuations |                               |

Table 1–2. Stages in the development of a system.

ging, manufacturing, installation, and field operation. Deviations from intended behavior, or errors, can occur at any stage as a result of incomplete specifications, incorrect implementation of a specification into a logic design, and assembly mistakes during prototyping or manufacturing.

During the system's operational life, errors can result from change in the physical state or damage to hardware. Physical changes may be triggered by environmental factors such as fluctuations in temperature or power supply voltage, static discharge, and even alpha particle emissions. Inconsistent states can also be caused by operator errors and by design errors in hardware or software.

Design errors, whether in hardware or software, are those caused by improper translation of a concept into an operational realization. Closely tied to the human creative process, design errors are difficult to predict. Gathering statistical information about the phenomenon is difficult because each design error occurs only once per system. The rapid rate of development in hardware technology constantly changes the set of design trade-offs, further complicating the study of hardware design errors. In the last five years there has been some progress in the use of redundancy—using additional resources beyond the minimum required to perform the task successfully—to control software design errors.

Any source of error can appear at any stage; however, it is usually assumed that certain sources of error predominate at particular stages. Furthermore, error-detection techniques can be tailored to the manifestation of fault sources. Thus, at each stage of system life there is a primary methodology for detecting errors. In the following discussion, the student of systems reliability must keep in mind the question, "At what level and at what stage of the system development does the subject matter apply?" The two dimensions of physical level and temporal stage serve as a framework to relate otherwise mutually exclusive factors. Later a third dimension, cost, will be considered.

#### ATTRIBUTES OF FAULT-TOLERANT COMPUTING AND THEIR DEFINITIONS

Fault-tolerant computing is the correct execution of a specified algorithm in the presence of de fects. The effect of defects can be overcome by the use of redundancy. This redundancy can b either temporal (repeated executions) or physica (replicated hardware or software). As in all systems design, system specifications constrain the design space and thus the design techniques that can be used. At the highest level of specification, fault-tolerant systems are categorized as either highly available or highly reliable.

#### **\vailability**

The availability of a system as a function of ime, A(t), is the probability that the system is perational at the instant of time, t. If the limit f this function exists as t goes to infinity, it xpresses the expected fraction of time that the ystem is available to perform useful computaons. Activities such as preventive maintenance nd repair reduce the time that the system is vailable to the user. Availability is typically sed as a figure of merit in systems in which ervice can be delayed or denied for short periods without serious consequences.

#### eliability

he reliability of a system as a function of time, (t), is the conditional probability that the sysm has survived the interval [0, t], given that it as operational at time t = 0. Reliability is used describe systems in which repair cannot take ace (as in satellite computers) or in which the imputer is serving a critical function and canit be lost even for the duration of a repair (as

flight computers on aircraft) or in which the pair is prohibitively expensive. In general, it is ore difficult to build a highly reliable computg system than a highly available one because of e more stringent requirements imposed by the liability definition. An even more stringent finition than R(t), sometimes used in aeroace applications, is the maximum number of lures anywhere in the system that the system n tolerate and still function correctly. Two important stages in the development of a system will be discussed next: the manufacturing stage and the operational life stage. A third important stage, design, is the subject of the remaining chapters in Part I.

#### THE MANUFACTURING STAGE

A careless manufacturing process can make even the most careful design useless. The manufacturing stage begins with the final portion of the prototype stage in a process called Design Maturity Testing.

#### **Design Maturity Testing**

A Design Maturity Test (DMT) estimates the Mean Time To Failure (MTTF) for a new product before it is committed to volume manufacturing. The DMT is conducted to isolate and correct repetitive systemic problems that, if left in the design, would result in higher service costs and customer dissatisfaction.

The DMT is accomplished by operating a set of sample devices for a prolonged time (typically six to eight units for two to four months) to simulate actual field operation. In cases in which the duty cycle of the equipment is less than 100 percent, the duty cycle under test may be increased to 100 percent to accelerate testing. As failures are observed and recorded, they are classified according to such factors as failure mode, time, or environmental cause. Similar failures are then ranked in groups by decreasing frequency of occurrence.

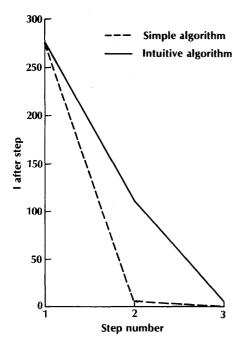

This procedure establishes priorities for eliminating the causes. After the fundamental cause of the failure is found and corrective design action is taken, the operation of the modified or repaired test samples provides a closed-loop evaluation of the efficacy of the change. Repeating the procedure improves the design of the test samples until their estimated MTTF meets the

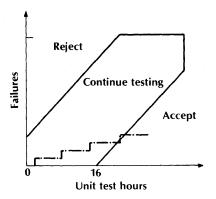

Figure 1–2. Reliability Demonstration Chart for monitoring the progress of a Design Maturity Test.

specifications with a certain statistical confidence.

The progress of the test can be monitored with a chart prepared in advance for the product under test, shown in Figure 1-2 [von Alven, 1964], which provides an objective criterion for judging the MTTF of a product with a predetermined statistical risk. The construction of the chart is determined by four parameters:

- Specified MTTF,  $\Theta_0$

- Minimum acceptable MTTF,  $\Theta_1$

- Consumer's risk,  $\alpha$ . This is the probability that a product with an MTTF lower than  $\Theta_0$  will be accepted.

- Producer's risk,  $\beta$ . This is the probability that a product with an MTTF higher than  $\Theta_0$  will be rejected.

A ratio of  $\Theta_0$  to  $\Theta_1$  between 1.5 and 2 to 1 is typically used. Consumers' and producers' risks are commonly taken to be 20 percent. Operating time in unit hours is the abscissa, and number of failures is the ordinate. The resultant performance line is a staircase that moves up and to the right as test experience accumulates. The chart is divided into three areas: accept, reject, or continue testing. When the performance line crosses into the accept region, the test samples' MTTF is at least equal to the minimum acceptable MTTF (with the predetermined risk of error), and the design should be accepted. If the performance line crosses into the reject region, the MTTF of the design is probably lower than the acceptable minimum with its corresponding probability of error; testing should be suspended until the design has been sufficiently improved and it can reasonably be expected to pass the test.

#### **Incoming Inspection**

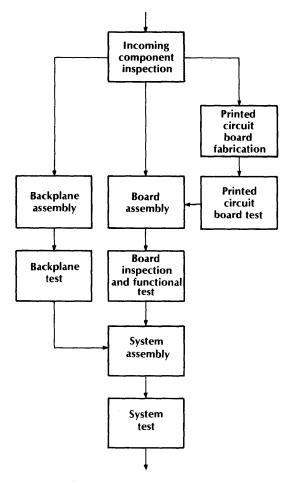

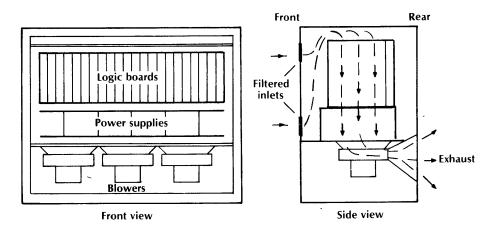

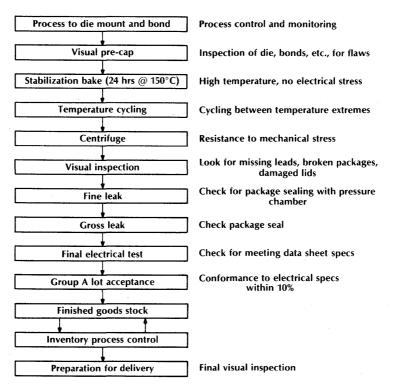

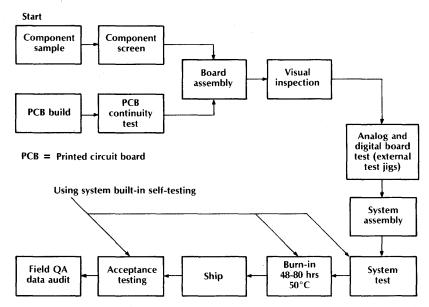

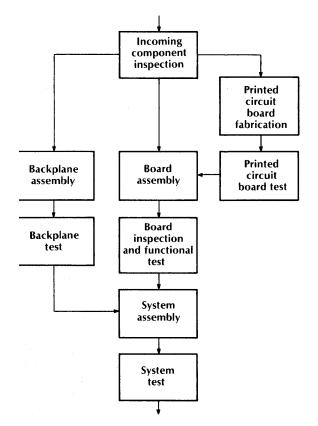

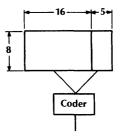

Figure 1-3 depicts typical steps in the volume manufacturing process. Note the alternating pattern of test/inspect and fabrication [Foley, 1979].

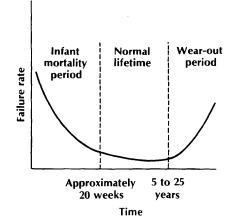

Incoming inspection is an attempt to cull weak or defective components prior to assembly into subsystems. All semiconductor processes yield a certain number of defective devices. Even after the semiconductor manufacturer has detected and removed these defective devices, failures will continue to occur for a time known as the "infant mortality period." This period is typical ly 20 weeks or less, during which the rate of failures continues to decline. At the end of this period, failures tend to stabilize at a constan rate for a long time, sometimes 25 years or more Ultimately the failure rate begins to rise again, in a period known as wear-out. This variation in failure rate as a function of time is illustrated b the bathtub-shaped curve shown in Figure 1-4.

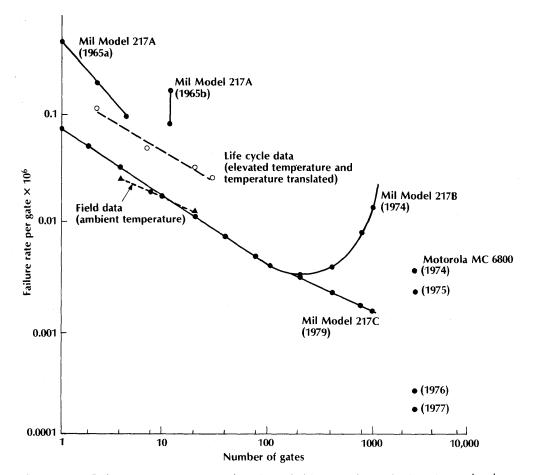

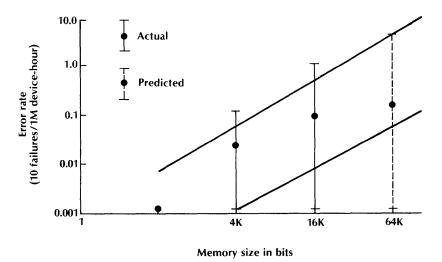

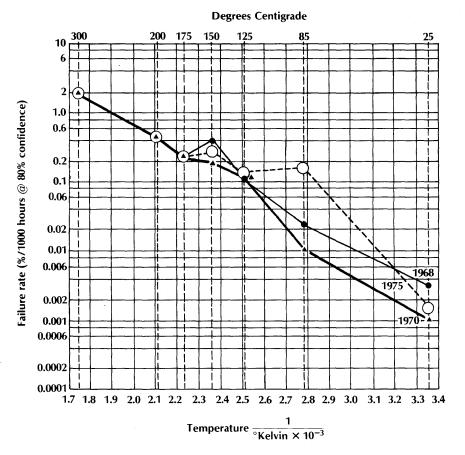

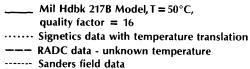

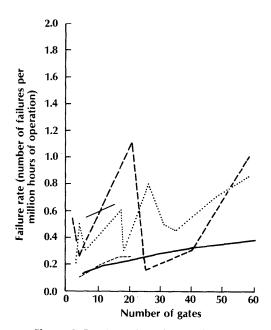

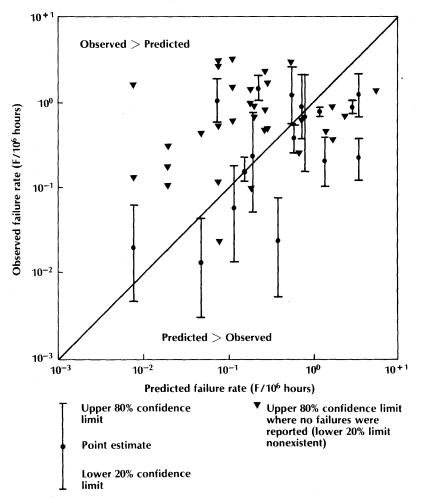

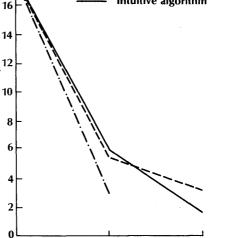

Over the years, with the accumulation of expe rience in the manufacture of semiconducto components, the failure rate per logic device ha steadily declined. Figure 1-5 depicts the numbe of failures per million hours for bipolar techno. ogy as a function of the number of gates on chip. The curves Mil Model 217A were derive from 1965 data. The curves Mil Model 217B (se Appendix D) and Mil Model 217C (see Apper dix E) were generated from a 1974 reliabilit prediction model. Actual failure data are als plotted to calibrate the 217B and 217C model The curve Field data was derived from a yea long reliability study of a sample of video term nals [Harrahy, 1977]. The curve Life cycle da was derived from elevated temperature testing

9

**igure 1–3.** Typical steps in the manufacture of a ligital system. (© 1979 IEEE.)

:hips, followed by application of a mathematical nodel that translated the failure rates to ambient emperatures [Siewiorek et al., 1978b]. Finally, he improvement in the 3,000-gate Motorola  $\Lambda$ C6800 is plotted [Queyssac, 1979].

Two trends are noteworthy. First, there is nore than an order of magnitude decrease in ailure rate per gate. Plots of failure per bit of ipolar random access memory indicate that the ailure rates per gate and per bit are comparable or comparable levels of integration.

Obviously, the chip failure rate is a function of

**Figure 1–4.** Bathtub curve depicting component failure rate as a function of time.

chip complexity and is not a constant. Failure rate per function (gate or bit) decreases by one order of magnitude over two orders of magnitude of gate complexity and two to three orders of magnitude of memory complexity. The failure rate decreases in direct proportion to increases in complexity.

The second trend is that the MIL-HDBK-217B model predicted an increase in failure rate per function beyond about 200-gate complexity, presumably because of the immaturity of the fabrication process at that scale of integration at that time.<sup>\*</sup>

Now consider a system composed of a constant number of semiconductor chips. Because the chips double in density every one to two years, the number of functions, f, in the system is proportional to changes in time,  $\Delta t$ :

$f \propto 2^{\Delta t}$

where t is time in years. The failure rate per function, from Figure 1-5, is proportional to the

<sup>\*</sup> The switch from a polynomial to an exponential function in number of gates occurs at 100 in 217B and 1,000 in 217C. This reflects the improvements in the fabrication process over time. See Appendixes D and E.

THE THEORY OF RELIABLE SYSTEM DESIGN

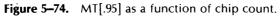

Figure 1–5. Failure rate per gate as a function of chip complexity for bipolar technology.

square root of the number of functions per chip:

$$r \propto f^{1/2}$$

Hence

$$r \propto 2^{\Delta t/2}$$

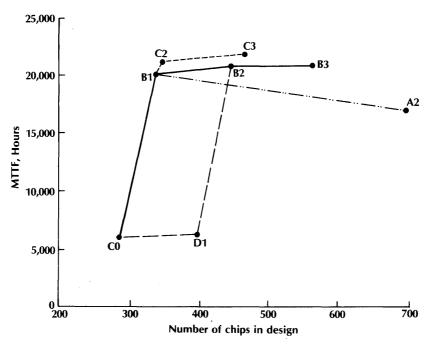

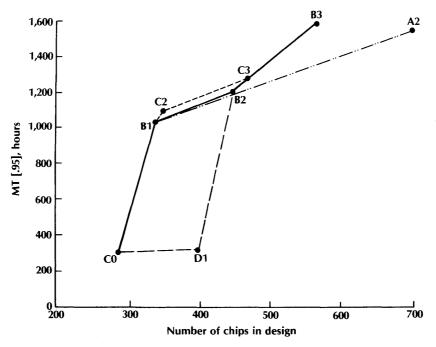

and the Mean Time To Failure (MTTF) is

MTTF

$$\propto \frac{1}{r} \propto \frac{1}{2^{(\Delta t/2)}}$$

This implies that over a 10-year period a system with the same number of semiconductor chips has increased its logic complexity by a factor of 1,024 and decreased its MTTF by a factor of 32. Hence, system reliability has not kept pace with system complexity. Complex, high-performance machines are on the verge of becoming virtually unusable. For example, when the Los Alamos Scientific Laboratory evaluated the reliability of its CRAY-1 over a 6-month period, the mean time to failure was found to be four hours [Keller, 1976]. The average repair time was only about 25 minutes, due to the skilled on-site maintenance crew. Even so, this represented the loss of about 100 billion potential machine operations [Avizienis, 1978]. Gains in system reli-

10

ability cannot be attained from improved component reliability alone. Redundancy must be introduced. Redundancy techniques are the subject of Chapter 3.\*

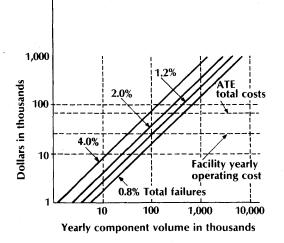

The cost of component failure depends upon the level at which the failure is detected: the higher the level, the more expensive the repair. Fault detection at the semiconductor component level minimizes cost. Fault detection at the next highest level, the board, has been estimated at \$5; at the system test level, \$50; and at the field service level, \$500 [Russel, 1980]. The level at which a computer manufacturer detects initial and infant mortality failures is a function of the incoming test program chosen.

Even relatively low semiconductor failure rates can cause substantial board yield problems, aggravated by the density of the board. Consider a board with forty semiconductor devices that have an initial failure rate of 1 percent:

Probability board not defective  $= (0.99)^{40}$

= 0.669

The benefits of an incoming inspection program can be easily quantified. The value of culling bad semiconductor components before they are inserted into the board is the most easily measured benefit. Board/system test savings, inventory reduction, and service personnel savings depend on the particular strategy used. To calculate the

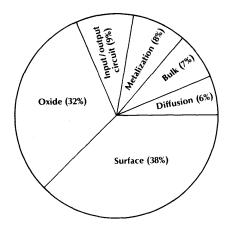

The loss of memory information caused by the decay of radioactive trace elements in packaging material has been documented. Studies show that even in sheltered environments such as well-conditioned computer rooms, soft errors are 20 to 50 times more prevalent than hard failures. Soft errors also exhibit clustering (a high probability that, once one error has occurred, another will occur soon), workload dependence (the heavier the system workload, the more likely an error), and common failure modes (more than one system, or portion of a system, affected simultaneously). Semiconductor failure rates and failure modes are discussed in detail in Chapter 2. value of removing defective components at incoming inspection, multiply the number of bad parts found by the cost of detecting, isolating, and repairing failures at higher levels of integration. The following formula estimates the total savings:

$$D = 5B + 50S + 500F$$

where

- D =dollar savings,

- B = number of failures at board test level,

- S = number of failures at system test level, and

- F = number of failures in the field.

This formula can be translated into annual savings by considering total component volume and mean failure rate data:

Potential annual savings

= annual component volume  $\times$

[(% initial failures)

(% failures detected at board level  $\times$  \$5

+ % failures detected at system level  $\times$  \$50)

+(% infancy failures)

(% failures detected at system level  $\times$  \$50

+ % failures detected in the field  $\times$  \$500)]

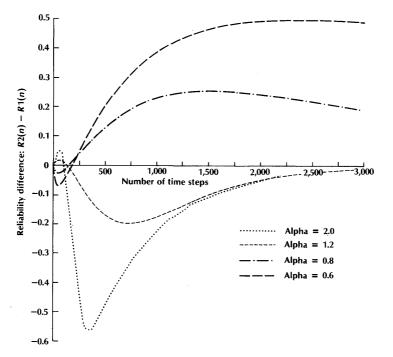

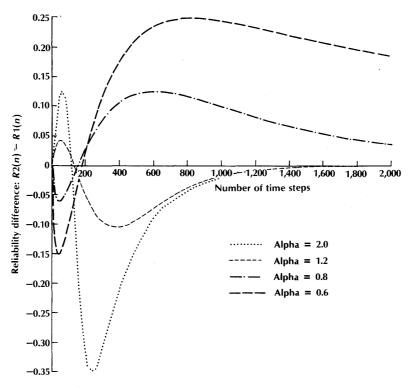

Typical savings for 100 percent incoming inspection can be estimated and compared with the cost of the Automatic Test Equipment (ATE) required to carry out such testing. Figure 1-6 (from [Russell, 1980]) shows the potential annual savings as a function of annual component volumes. A family of curves is shown for overall failure rates of 0.8, 1.2, 2.0, and 4.0 percent.

#### **Process Maturity Testing**

The term *process* includes all manufacturing steps to acquire parts, assemble, fabricate, in-

The same semiconductor evolution that has led to increased reliability per gate or bit has also introduced new failure modes. The smaller dimensions of semiconductor devices have decreased the amount of energy required to change the state of a memory bit.

12

**Figure 1–6.** Savings from screening and testing as a function of defective component rate and annual device volume.

spect, and test a product during volume production. The rationale for Process Maturity Testing (PMT) is that newly manufactured products contain some latent defects built in by the process that produced them.

A large number of units, about the first 120 off the production line, are operated for 96 hours, often in lot sizes convenient to the particular production process. They are operated (burned in) in a manner that simulates the normal production process environment as closely as possible. If the burn-in and production process environments differ significantly, appropriate test results must be adjusted accordingly.

Infant mortality characteristics may fluctuate significantly throughout the test lot. The composite of these individual failure characteristics is considered the "normal infancy" for the device.

The end of the burn-in period for production equipment is determined by the normal infancy curve thus derived from the PMT. The objective is to ship products of consistently good quality and acceptable MTTF after a minimum burn-in period. Typical production burn-in times are 20 to 40 hours. PMT is used to identify several classes of failures. Infancy failures are problems generally caused by parts that were defective from the time they were received. In largely solid-state devices, component problems will remain in this category until identified and controlled by either incoming inspection or changes implemented by the component vendor.

Manufacturing/inspection failures are generally failures repaired by readjustments or retouching, such as a part damaged by the assembly process or defects that bypassed the normal incoming test procedures.

Engineering failures are recurrent problems in the design that have not yet been corrected or new problems not yet resolved because of lack of experience.

Residual failures are problems that have not yet recurred and for which there is no corrective action except to repair when they occur. These are the truly random failures.

Experience has shown that the three major recurring problems usually account for 75 percent of all failures. It is reasonable to expect that the correction of the top four to six recurring problems will yield a tenfold improvement in MTTF.

#### THE OPERATIONAL LIFE STAGE

Maintenance and repair during the field operational stage are the customer's primary contacts with system reliability. In the early days of computers, repairing a downed system was an art. Diagnostics that were halted or trapped when executing certain instructions did give clues to the location of the failure but did not pinpoint the failing Field Replaceable Unit (FRU). To identify the failing FRU, technicians swapped circuit boards one by one with "known good boards" in the hope of eventually restoring the system to proper operation. In time, diagnostic techniques became better able to identify the specific failed FRU before swapping any boards;

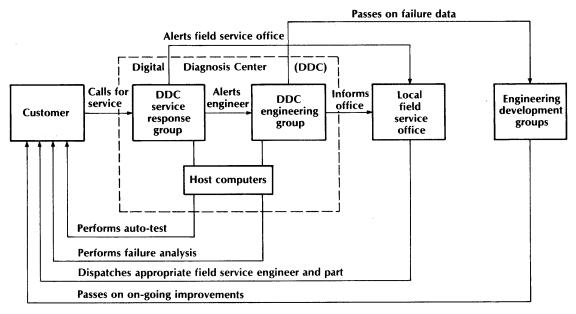

Figure 1–7. Overview of DEC's Remote Diagnosis Network.

then the failed board could rapidly be replaced with a good one.

Unfortunately, as on-site repair time is decreased by better diagnosis, travel time to the site becomes a limiting factor. At today's labor and transportation rates, the cost of travel time frequently exceeds the cost of the actual repair. Return trips, because the failed FRU was identified but the field service engineer had no replacement along, are very cost inefficient. Alternative service strategies have developed in response to these factors, such as customer carry-in service for small computers and service vans that carry enough sets of spare parts to permit long absences from the branch field service office.

A good example of a current field service approach is Digital Equipment Corporation's Digital Diagnosis Center (DDC). An overview of the network operation is shown in Figure 1-7. When customers detect or suspect a computer malfunction, they call a special telephone response line that is attended 24 hours a day, seven days a week. The heart of the DDC is a dual PDP-11/70 configuration with auto-dial equipment. Once attached to the customer's failing computer (typically within 15 minutes), the DDC host system directs the diagnosis process based on results produced by the system under test. A configuration file is kept on each system supported. The DDC host executes the appropriate diagnostic "scripts," which simulate the thought processes of an on-site field service engineer. Each script executes a diagnostic sequence that can be modified according to the error responses generated by the computer being tested.

At the same time, the remote diagnosis specialist puts the local field service office on alert for a probable call. When initial diagnostic results are available, an engineer in the DDC reviews them and may then initiate further automatic tests or take direct control of the system under test.

When the analysis is complete, the problem will be described to the local field service branch office, which then dispatches the right person with the right part to the site. The on-site field engineer replaces the predetermined failed part and verifies the resolution of the problem. Final results of the corrective action are transmitted to the DDC to update the system's maintenance log. Information about problem areas in various computer systems is passed on to the engineering development groups for improvements in the future.

#### COST OF OWNERSHIP

The third dimension of the reliability framework, in addition to physical and temporal stage is cost. The cost of a computer system is not limited to initial purchase; significant costs recur during the life of a system. As a result, computer owners frequently develop mathematical models that enable them to make optimal decisions, minimizing the total cost of ownership.<sup>\*</sup> Following is a description of some of the more significant costs:

*Purchase Price.* The purchase price of a computer, though significant, can represent less than half the cost of ownership, computed on the basis of net present value. The purchase price usually includes system hardware, documentation, software license fees, training, and installation. The potential owner of a computer always has renting and leasing alternatives to consider, which can sometimes be advantageous in terms of cash flow or net present value.

Site Preparation. Many computers require special operating environments. This may include special air conditioning, with closely controlled temperature, humidity, and airborne particulate matter size and density. A large computer may also require a raised floor for cabling. The main power supply may require a separate transformer with three-phase service and Radio Frequency Interference (RFI) filters. In some installations, an Uninterruptible Power Supply (UPS) is essential to increase system availability or prevent loss of data.

Maintenance. All computers require some degree of preventive and corrective maintenance. The user usually has the option of purchasing a field service contract at a fixed price or paying for field service on a time-and-materials basis. The maintenance can come from the computer manufacturer, Original Equipment Manufacturer (OEM), a third party, or may be performed by the customer. The trade-offs inherent in decisions about when and how often to perform preventive maintenance also affect cost of ownership.

Supplies. A computer system requires paper for the printers, disks and tapes for the mass storage devices, and other periodically replaced material. Very significant, too, is the power required to run the computer. With ever-escalating energy costs, supplying power to a computer for its operational lifetime can be one of the most significant expenses associated with ownership.

*Cost of Downtime.* Depending on the application of the system, the cost of downtime can be trivial or crucial. In a system that acquires revenue, for example, the cost of downtime can far exceed the actual purchase price. This parameter requires careful evaluation by the potential customer.

Consider a system that has only an initial cost, I, and a failure rate  $\lambda$ . The cost, C, of owning this system for n years can be expressed as:

$$C = I + \sum_{i=1}^{n} \frac{S_i P_i}{(1+D)^i}$$

where

- $S_i$  = the cost of one corrective maintenance call in year *i*

- $P_i$  = the expected number of failures during year *i*, and

- D = the discount rate.

<sup>&</sup>lt;sup>•</sup> These financial considerations are discussed in detail in Chapter 6.

Figure 1–8. Major activities in the design and marketing of a computer system.

The discount rate expresses the value of money in terms of time. For example, if you need \$100 in two years and can get 10 percent annual interest in a savings account, you need to put away only  $100/1.1^2 = 82.65$  today. Here 10 percent represents the discount rate.

Assume that the failure rate is constant over the period in question. Then

$$C = I + P \sum_{i=1}^{n} \frac{S_i}{(1+D)^i}$$

Further assume that the system has a five-year life, that a service call costs \$300, and that the discount rate is 20 percent. Expressing  $\lambda$  in failures per million hours and noting the fact that there are 8,760 hours in a year results in:

$$C = I + (300) \frac{8760\lambda}{10^6} \sum_{i=1}^5 \frac{1}{(1.2)^i}$$

$$= I + 7.86\lambda$$

Consider a system that costs \$21,000 and has a failure rate of 6,500 per million hours (equivalent to a Mean Time To Failure of 154 hours). Its cost of ownership, using the assumptions above, is \$72,090. Now consider another system that

costs more to purchase, \$27,500, but is more reliable. Its failure rate is 4,400, or an MTTF of 227 hours. Its cost of ownership is \$62,084. Although the second system is 31 percent more expensive to purchase, its 47 percent increase in reliability results in a 14 percent reduction in five-year cost of ownership.

#### **UNIVERSE OF MODELS**

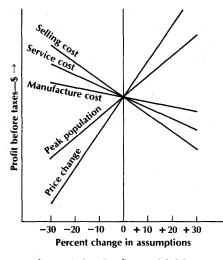

Figure 1-8 depicts the major activities in the design and marketing of a computer system. Each activity has a model that can be used for predictive and evaluation purposes. The goal of all these activities is to produce a system which fulfills its intended use, thereby satisfying the customer. Customer satisfaction is a complex function of system cost, performance, reliability, and maintainability.

Once the need for a system is established, usually by technological or market pressures, a design is developed. Enhanced reliability usually involves some degree of hardware redundancy, and maintainability improvements usually involve the addition of self-testing circuits, both of **Table 1–3.** Parameters a designer can control, their impact on system design goals, and typical techniques used to achieve these goals.

| Designable<br>Parameters | Goals            | Example<br>Techniques |  |  |  |

|--------------------------|------------------|-----------------------|--|--|--|

|                          | Hard Failures    |                       |  |  |  |

| MTTF                     | Tolerate         | Replication           |  |  |  |

| MTTR                     | Isolate          | Detection             |  |  |  |

|                          | Transient Faults |                       |  |  |  |

| MTTC                     | Tolerate         | Detection/Retr        |  |  |  |

which increase the design effort and the product cost. The goal should be to minimize the cost of ownership.

Ideally, sales forecasts are expressed as a function of selling price. Thus, the cost of hardware affects the sales forecasts and the business plan. Reliability (MTTF) and maintainability (MTTR) influence the field service plan. The sales forecasts affect both the field service and business plans. Coupled with the MTTF, MTTR, and sales forecasts, the field service plan produces the service costs, which further affect the business plan. Finally, the business plan determines the marketing, manufacturing, and field service strategies. Thus, all the components interact with and influence one another, and a modeling process underlies each component. Because financial plans vary greatly according to markets, and indeed between companies in the same market, this book focuses on evaluating reliability (see Chapter 5).

#### THE DESIGNABLE PARAMETERS

The designer influences reliability (MTTF), availability, and maintainability (MTTR) parameters in the model space of Figure 1-8. Table 1-3 illustrates the implication of these parameters on the system design.

With increased customer interest in fault tolerance and constantly decreasing hardware costs, there is a significant trend to implement more fault tolerance in hardware. Hardware error tolerance has many advantages:

- Simplifies recovery for software and user applications

- Saves time

- Provides transparency to the user

- Increases probability of successful recovery, given early detection

- Decreases MTTR

- Increases MTTF, MTTE (Mean Time To Error), and MTTC (Mean Time To Crash)

- Simplifies software recovery and reduces dependence on implementation

- Error detection logic can help isolate design errors so that future implementations are even more reliable.

The goal of this book is to provide methodologies for designing and evaluating the use of MTTF, MTTE, MTTC, and MTTR improvement techniques in computer systems.

### REFERENCES

Avizienis [1978]; Foley [1979]; Harrahy [1977]; Keller [1976]; Queysac [1979]; Russel [1980]; Siewiorek et al. [1978b]; Siewiorek, Bell, and Newell [1982]; von Alven [1964].

# **Faults and Their Manifestations**

## INTRODUCTION

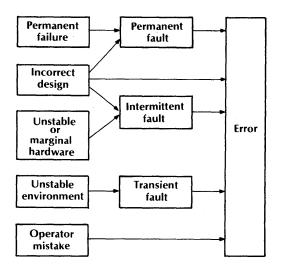

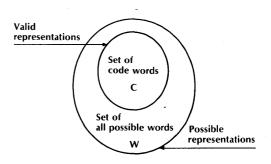

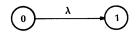

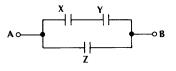

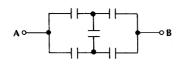

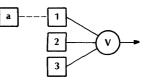

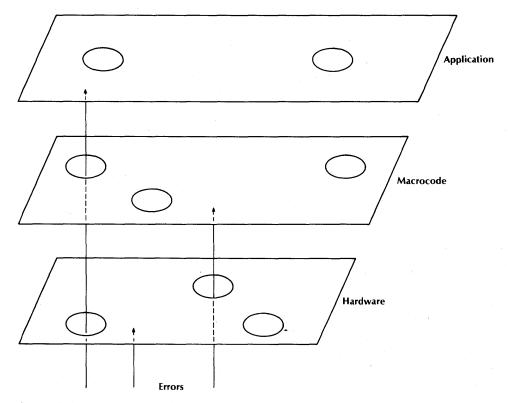

Designing a fault-tolerant system requires finding a way to prevent the logical fault that arises from a physical failure from causing an error. Figure 2-1 depicts the possible sources of an error. The following apply [Avizienis, 1975]:

- Failure. Physical change in hardware.

- *Fault*. Erroneous state of hardware or software resulting from failures of components, physical inteference from the environment, operator error, or incorrect design.

- *Error*. Manifestation of a fault within a program or data structure. The error may occur some distance from the fault site.

- *Permanent*. Describes a failure, fault, or error that is continuous and stable. In hardware, permanent failure reflects an irreversible physical change. The word *hard* is used interchangeably with *permanent*.

- Intermittent. Describes a fault or error that is only occasionally present due to unstable hardware or varying hardware or software states (for example, as a function of load or activity).

- *Transient.* Describes a fault or error resulting from temporary environmental conditions. The word *soft* is used interchangeably with *transient*.

A fault can be caused by a physical failure, an nadequacy in the design of the system, an environmental influence, or the operator of the system. A permanent failure may lead to a bermanent fault. Intermittent faults can be saused by unstable, marginally stable, or incorect designs. Environmental conditions can lead o transient faults. All these faults can cause errors. Incorrect designs and operator mistakes an lead directly to errors.

The distinction between intermittent and tranient faults is not always made in the literature Kamal, 1975; Tasar and Tasar, 1977]. The di-

Figure 2–1. Sources of errors.

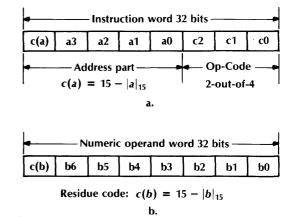

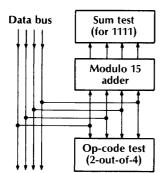

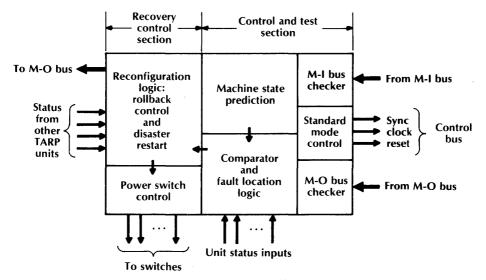

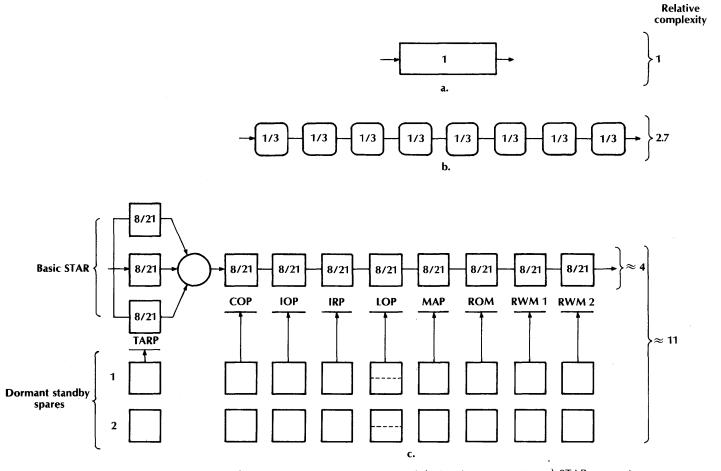

viding line is the applicability of repair [Breuer, 1973; Kamal and Page, 1974; Losq, 1978; Savir, 1978]. Faults resulting from physical conditions of the hardware, incorrect hardware or software design, or unstable but repeated environmental conditions are potentially detectable and repairable by replacement or redesign; faults due to temporary environmental conditions, however, are incapable of repair because the hardware is physically undamaged. It is this attribute of transient faults that magnifies their importance. Even in the absence of all physical defects, including those manifested as intermittent faults, errors will still occur.