# DECchip 21164-AA (EV5 CPU) Functional Specification

The DECchip 21164-AA CPU Chip is a high-performance, single-chip implementation of the Alpha Architecture.

#### **Revision/Update Information:**

This is Revision 1.9 of this specification. Relative to Revision 1.5, all chapters are updated. This is the last release expected prior to tape-out.

Product Manager: John Fortune, RICKS::FORTUNE Engineering Manager: Paul Rubinfeld, ROCK::RUBINFELD

#### DIGITAL RESTRICTED DISTRIBUTION

This information shall not be disclosed to persons other than DIGITAL employees or generally distributed within DIGITAL. Distribution is restricted to persons authorized and designated by the originating organization. This document shall not be transmitted electronically, copied unless authorized by the originating organization, or left unattended. When not in use, this document shall be stored in a locked storage area. These restrictions are enforced until this document is reclassified by the originating organization.

Semiconductor Engineering Group Digital Equipment Corporation, Hudson, Massachusetts

This is copy number | 6

#### December 1992

The drawings and specifications in this document are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of items without written permission.

The information in this document may be changed without notice and is not a commitment by Digital Equipment Corporation. Digital Equipment Corporation is not responsible for any errors in this document.

This specification does not describe any program or product that is currently available from Digital Equipment Corporation, nor is Digital Equipment Corporation committed to implement this specification in any program or product. Digital Equipment Corporation makes no commitment that this document accurately describes any product it might ever make.

Copyright ©1992 by Digital Equipment Corporation All Rights Reserved Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEC DECnet DECUS MicroVAX MicroVMS PDP ULTRIX ULTRIX-32 UNIBUS VAX VAXBI VAXCluster VAXstation VMS VT

# Contents

| CHAPTER 1 | INTRODUCTION                                                                                                                                                                                                                              | 1–1                                                                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 1.1       | SCOPE                                                                                                                                                                                                                                     | 1–1                                                                   |

| 1.2       | CHIP FEATURES                                                                                                                                                                                                                             | 1–1                                                                   |

| 1.3       | TERMINOLOGY AND CONVENTIONS1.3.1Numbering1.3.2UNPREDICTABLE And UNDEFINED1.3.3Data Field Size1.3.4Ranges And Extents1.3.5Register Format Notation                                                                                         | 1–2<br>1–2<br>1–3<br>1–3<br>1–3                                       |

| 1.4       | CHIP SUMMARY                                                                                                                                                                                                                              | 1–5                                                                   |

| 1.5       | REVISION HISTORY                                                                                                                                                                                                                          | 1–6                                                                   |

| CHAPTER 2 | DECCHIP 21164-AA MICRO-ARCHITECTURE                                                                                                                                                                                                       | 2–1                                                                   |

| 2.1       | INTRODUCTION                                                                                                                                                                                                                              | 2–1                                                                   |

| 2.2       | OVERVIEW                                                                                                                                                                                                                                  | 2-1                                                                   |

| 2.3       | IBOX2.3.1Instruction Prefetch2.3.2Branch Execution2.3.3ITB2.3.4Interrupt Logic2.3.5Performance Counters                                                                                                                                   | 24<br>25<br>2-5<br>2-6<br>2-8                                         |

| 2.4       | EBOX                                                                                                                                                                                                                                      | 2–8                                                                   |

| 2.5       | MBOX2.5.1Big Endian Support2.5.2DTB2.5.3Replay Traps2.5.4Load Instruction Execution and the Miss Address File2.5.5Store Execution2.5.6Write Buffer and the WMB Instruction2.5.7MB Instruction2.5.8Ibox Read Requests2.5.9Mbox Arbitration | 28<br>28<br>29<br>210<br>2-12<br>2-13<br>2-15<br>2-15<br>2-15<br>2-15 |

| 2.6       | THE CBOX                                                                                                                                                                                                                                  | 2–15                                                                  |

| 2.7       | FBOX                                                                                                                                                                                                                                      | 2–17                                                                  |

| 2.8       | CACHE ORGANIZATION<br>2.8.1 Data Cache<br>2.8.2 Instruction Cache<br>2.8.3 Second Level Cache<br>2.8.4 External Cache - Bcache                                                                                                            | 2–18<br>2–18<br>2–18<br>2–18<br>2–18<br>2–19                          |

| 2.9       | PIPELINE ORGANIZATION                                                                                                                                                                                                                     | 2–19                                                                  |

# DIGITAL RESTRICTED DISTRIBUTION

iii .

## Contents

| 2.10      | SCHEDUL  | ING AND IS           | SUING RULES                                                                                               | 2–24 |

|-----------|----------|----------------------|-----------------------------------------------------------------------------------------------------------|------|

|           | 2.10.1   |                      | Class Definition and Instruction Slotting<br>Slotting • 2-25                                              | 2–24 |

|           | 2.10.2   | Instruction          | -                                                                                                         | 2–26 |

|           | 2.10.3   | Producer-F           | Producer Latency                                                                                          | 2–28 |

|           | 2.10.4   | DECchip 2            | 1164-AA Issue Rules                                                                                       | 2–28 |

| 2.11      | REVISION | HISTORY              |                                                                                                           | 2–30 |

| CHAPTER 3 | PALCODE  | AND IPRS             |                                                                                                           | 3–1  |

| 3.1       | OVERVIEV | N                    |                                                                                                           | 3-1  |

| 3.2       | PALCODE  | ENTRY PO             | NTS                                                                                                       | 3–1  |

|           | 3.2.1    | CALL_PAL             |                                                                                                           | 32   |

|           | 3.2.2    | Traps                |                                                                                                           | 3–3  |

| 3.3       | PAL OPCO | DDES                 |                                                                                                           | 3–3  |

|           | 3.3.1    | HW_LD                |                                                                                                           | 3–4  |

|           | 3.3.2    | HW_ST                |                                                                                                           | 35   |

|           | 3.3.3    | HW_REI               |                                                                                                           | 36   |

|           | 3.3.4    | HW_MFPR              | and HW_MTPR                                                                                               | 3-7  |

| 3.4       | PAL STOP | RAGE REGIS           | STERS                                                                                                     | 39   |

| 3.5       | SRM DEF  | INED STATE           | - OPENVMS                                                                                                 | 3–9  |

| 3.6       | SRM DEF  | INED STATE           | - OSF                                                                                                     | 3–10 |

| 3.7       | PERFORM  | IANCE                | ·                                                                                                         | 3–11 |

| 3.8       | TBMISS F | LOWS                 |                                                                                                           | 3–12 |

| 3.9       | IPRS     |                      |                                                                                                           | 3–13 |

|           | 3.9.1    | Ibox IPRs            |                                                                                                           | 3–13 |

|           |          | 3.9.1.1              | ITB_TAG • 3–14                                                                                            |      |

|           |          | 3.9.1.2<br>3.9.1.3   | ITB_PTE • 3–14<br>Address Space Number, ITB_ASN • 3–15                                                    |      |

|           |          | 3.9.1.3              | ITB PTE TEMP • 3–15                                                                                       |      |

|           |          | 3.9.1.5              | Istream TB Invalidate All Process, ITB_IAP • 3-16                                                         |      |

|           |          | 3.9.1.6              | IStream TB Invalidate All, ITB_IA • 3-16                                                                  |      |

|           |          | 3.9.1.7              | ITB_IS • 3–16                                                                                             |      |

|           |          | 3.9.1.8              | Formatted Faulting VA register, IFAULT_VA_FORM • 3-16                                                     |      |

|           |          | 3.9.1.9              | Virtual Page table Base register, IVPTBR • 3-17                                                           |      |

|           |          | 3.9.1.10             | Icache Parity Error Status register, ICPERR_STAT • 3-17                                                   |      |

|           |          | 3.9.1.11             | ICache Flush Control register, IC_FLUSH_CTL • 3–17                                                        |      |

|           |          | 3.9.1.12<br>3.9.1.13 | Exception Address register, EXC_ADDR • 3–18<br>Exception Summary register, EXC_SUM • 3–18                 |      |

|           |          | 3.9.1.13             | Exception Mask Register, EXC_MASK • 3–19                                                                  |      |

|           |          | 3.9.1.15             | PAL Base Register, PAL_BASE • 3–19                                                                        |      |

|           |          | 3.9.1.16             | Processor Status, PS • 3–20                                                                               |      |

|           |          | 3.9.1.17             | Ibox Control/Status Register, ICSR • 3-20                                                                 |      |

|           |          | 3.9.1.18             | Interrupt Priority Level Register, IPL • 3–21                                                             |      |

|           |          | 3.9.1.19             | Interrupt Id Register, INTID • 3-22                                                                       |      |

|           |          | 3.9.1.20             | Aynchronous System Trap Request Register, ASTRR • 3–22                                                    |      |

|           |          | 3.9.1.21<br>3.9.1.22 | Aynchronous System Trap Enable Register, ASTER • 3–23<br>Software Interrupt Request Register. SIRR • 3–23 |      |

DIGITAL RESTRICTED DISTRIBUTION

iv

| 3.10<br>CHAPTER 4<br>4.1 | EXTERN                                         | Possible                                                                                                              | Definitions • 3–56                                                                                                                                                  | 3–56<br>3–60<br>4–1<br>4–2<br>4–3<br>4–3<br>4–3<br>4–4 |

|--------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| CHAPTER 4                | REVISIO<br>EXTERN<br>CHIP IN<br>4.1.1<br>4.1.2 | 3.9.3.8<br>3.9.3.9<br>3.9.3.10<br>PAL Rest<br>3.9.4.1<br>ON HISTORY<br>NAL JNTERF<br>ITERFACE<br>Overview<br>Physical | Bcache Tag Address Register, BC_TAG_ADDR • 3–53<br>Fill_Syndrome Register, FILL_SYN • 3–54<br>Load Lock Register, LD_LOCK • 3–56<br>rrictions<br>Definitions • 3–56 | 3–60<br>4–1<br>4–2<br>4–3                              |

| CHAPTER 4                | REVISIO<br>EXTERN<br>CHIP IN<br>4.1.1          | 3.9.3.8<br>3.9.3.9<br>3.9.3.10<br>PAL Rest<br>3.9.4.1<br>ON HISTORY<br>NAL JNTERF<br>ITERFACE<br>Overview             | Bcache Tag Address Register, BC_TAG_ADDR • 3–53<br>Fill_Syndrome Register, FILL_SYN • 3–54<br>Load Lock Register, LD_LOCK • 3–56<br>rrictions<br>Definitions • 3–56 | 3–60<br>4–1<br>4–1<br>4–2                              |

| CHAPTER 4                | REVISIO<br>EXTERN<br>CHIP IN                   | 3.9.3.8<br>3.9.3.9<br>3.9.3.10<br>PAL Rest<br>3.9.4.1<br>ON HISTORY<br>NAL JNTERF                                     | Bcache Tag Address Register, BC_TAG_ADDR • 3–53<br>Fill_Syndrome Register, FILL_SYN • 3–54<br>Load Lock Register, LD_LOCK • 3–56<br>rictions<br>Definitions • 3–56  | 3–60<br>4–1<br>4–1                                     |

| CHAPTER 4                | REVISIO<br>EXTERN                              | 3.9.3.8<br>3.9.3.9<br>3.9.3.10<br><b>PAL Rest</b><br>3.9.4.1<br><b>DN HISTORY</b>                                     | Bcache Tag Address Register, BC_TAG_ADDR • 3–53<br>Fill_Syndrome Register, FILL_SYN • 3–54<br>Load Lock Register, LD_LOCK • 3–56<br>rictions<br>Definitions • 3–56  | 3–60<br>4–1                                            |

|                          | REVISIO                                        | 3.9.3.8<br>3.9.3.9<br>3.9.3.10<br><b>PAL Rest</b><br>3.9.4.1<br><b>DN HISTORY</b>                                     | Bcache Tag Address Register, BC_TAG_ADDR • 3–53<br>Fill_Syndrome Register, FILL_SYN • 3–54<br>Load Lock Register, LD_LOCK • 3–56<br>rictions<br>Definitions • 3–56  | 3–60                                                   |

| 3.10                     |                                                | 3.9.3.8<br>3.9.3.9<br>3.9.3.10<br><b>PAL Rest</b><br>3.9.4.1                                                          | Bcache Tag Address Register, BC_TAG_ADDR • 3–53<br>Fill_Syndrome Register, FILL_SYN • 3–54<br>Load Lock Register, LD_LOCK • 3–56<br>rictions                        |                                                        |

|                          | 3.9.4                                          | 3.9.3.8<br>3.9.3.9<br>3.9.3.10<br><b>PAL Rest</b>                                                                     | Bcache Tag Address Register, BC_TAG_ADDR • 3–53<br>Fill_Syndrome Register, FILL_SYN • 3–54<br>Load Lock Register, LD_LOCK • 3–56<br>rictions                        | 3–56                                                   |

|                          | 0.0.4                                          | 3.9.3.8<br>3.9.3.9<br>3.9.3.10                                                                                        | Bcache Tag Address Register, BC_TAG_ADDR • 3–53<br>Fill_Syndrome Register, FILL_SYN • 3–54<br>Load Lock Register, LD_LOCK • 3–56                                    |                                                        |

|                          |                                                | 3.9.3.8<br>3.9.3.9                                                                                                    | Bcache Tag Address Register, BC_TAG_ADDR • 3–53<br>Fill_Syndrome Register, FILL_SYN • 3–54                                                                          |                                                        |

|                          |                                                | 3.9.3.8                                                                                                               | Bcache Tag Address Register, BC_TAG_ADDR • 3-53                                                                                                                     |                                                        |

|                          |                                                |                                                                                                                       |                                                                                                                                                                     |                                                        |

|                          |                                                |                                                                                                                       |                                                                                                                                                                     |                                                        |

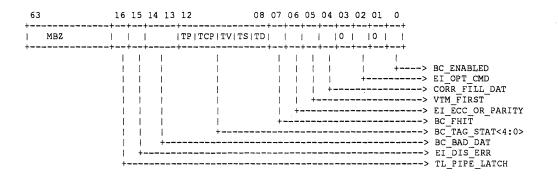

|                          |                                                | 3.9.3.6                                                                                                               | External Interface Status Register, EI_STAT • 3-51                                                                                                                  |                                                        |

|                          |                                                | 3.9.3.5                                                                                                               | Bcache Configuration Register, BC_CONFIG • 3-49                                                                                                                     |                                                        |

|                          |                                                | 3.9.3.4                                                                                                               | Bcache Control Register, BC_CONTROL • 3-46                                                                                                                          |                                                        |

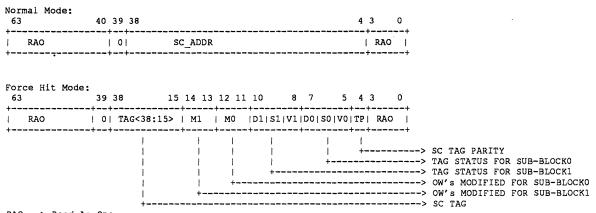

|                          |                                                | 3.9.3.3                                                                                                               | Scache Address Register, SC_ADDR • 3-45                                                                                                                             |                                                        |

|                          |                                                | 3.9.3.2                                                                                                               | Scache Status Register, SC_STAT • 3-44                                                                                                                              | -                                                      |

|                          |                                                | 3.9.3.1                                                                                                               | Scache Control Register, SC_CTL • 3-42                                                                                                                              |                                                        |

|                          | 3.9.3                                          | Cbox IPR                                                                                                              | •                                                                                                                                                                   | 3-42                                                   |

|                          |                                                | 0.0.2.20                                                                                                              | Register • 3–40                                                                                                                                                     |                                                        |

|                          |                                                | 3.9.2.23                                                                                                              | DC_TEST_TAG_TEMP, Dcache Test TAG Temp                                                                                                                              |                                                        |

|                          |                                                | 3.9.2.21                                                                                                              | DC_TEST_TAG, Dcache Test TAG Register • 3–39                                                                                                                        |                                                        |

|                          |                                                | 3.9.2.20                                                                                                              | DC_TEST_CTL, Dcache Test TAG Control Register • 3–38                                                                                                                |                                                        |

|                          |                                                | 3.9.2.19<br>3.9.2.20                                                                                                  | CC, Cycle Counter • 3–37<br>CC_CTL, Cycle Counter Control • 3–37                                                                                                    |                                                        |

|                          |                                                | 3.9.2.18                                                                                                              | ALT_MODE, Alternate mode • 3–36                                                                                                                                     |                                                        |

|                          |                                                | 3.9.2.17                                                                                                              | DC_FLUSH, Dcache Flush Register • 3–36                                                                                                                              |                                                        |

|                          |                                                | 3.9.2.16                                                                                                              | MAF_MODE, MAF Mode Register • 3–35                                                                                                                                  |                                                        |

|                          |                                                | 3.9.2.15                                                                                                              | DC_MODE, Dcache Mode Register • 3-34                                                                                                                                |                                                        |

|                          |                                                | 3.9.2.14                                                                                                              | MCSR, Mbox Control Register • 3–33                                                                                                                                  |                                                        |

|                          |                                                | 3.9.2.13                                                                                                              | DTBIS, Dstream TB Invalidate Single • 3-32                                                                                                                          |                                                        |

|                          |                                                | 3.9.2.12                                                                                                              | Dstream TB Invalidate All, DTBIA • 3–32                                                                                                                             |                                                        |

|                          |                                                | 3.9.2.11                                                                                                              | Dstream TB Invalidate All Process, DTBIAP • 3-32                                                                                                                    |                                                        |

|                          |                                                | 3.9.2.10                                                                                                              | DC_PERR_STAT, Dcache Parity Error Status • 3-31                                                                                                                     |                                                        |

|                          |                                                | 3.9.2.9                                                                                                               | MVPTBR, Mbox Virtual Page Table Base Register • 3-31                                                                                                                |                                                        |

|                          |                                                | 3.9.2.8                                                                                                               | VA_FORM, Formatted Virtual Address • 3-30                                                                                                                           |                                                        |

|                          |                                                | 3.9.2.7                                                                                                               | VA, Faulting Virtual Address • 3-30                                                                                                                                 |                                                        |

|                          |                                                | 3.9.2.6                                                                                                               | MM_STAT, Dstream MM Fault Status Register • 3-29                                                                                                                    |                                                        |

|                          |                                                | 3.9.2.5                                                                                                               | DTB_PTE_TEMP • 3–28                                                                                                                                                 |                                                        |

|                          |                                                | 3.9.2.4                                                                                                               | Dstream TB PTE, DTB PTE • 3–27                                                                                                                                      |                                                        |

|                          |                                                | 3.9.2.2<br>3.9.2.3                                                                                                    | DTB_CM, Dstream TB Current Mode • 3–26<br>DTB_TAG, Dstream TB TAG • 3–27                                                                                            |                                                        |

|                          |                                                | 3.9.2.1                                                                                                               | DTB_ASN, Dstream TB Address Space Number • 3–26                                                                                                                     |                                                        |

|                          | 3.9.2                                          |                                                                                                                       | Dcache IPRs                                                                                                                                                         | 3–26                                                   |

|                          |                                                | 3.9.1.27                                                                                                              | Serial line receive, SL_RCV • 3–26                                                                                                                                  | 0.00                                                   |

|                          |                                                | 3.9.1.26                                                                                                              | Serial line transmit, SL_XMIT • 3–25                                                                                                                                |                                                        |

|                          |                                                | 3.9.1.25                                                                                                              | Interrupt Summary register, ISR • 3-24                                                                                                                              |                                                        |

|                          |                                                | 3.9.1.24                                                                                                              | HW Interrupt Clear register, HWINT_CLR • 3-24                                                                                                                       |                                                        |

|                          |                                                | 3.9.1.23                                                                                                              | Software Interrupt Clear Register. SICR • 3–23                                                                                                                      |                                                        |

۷

|       |      | 4.1.6    | •                     | 1164-AA Interface                                                      | 46   |

|-------|------|----------|-----------------------|------------------------------------------------------------------------|------|

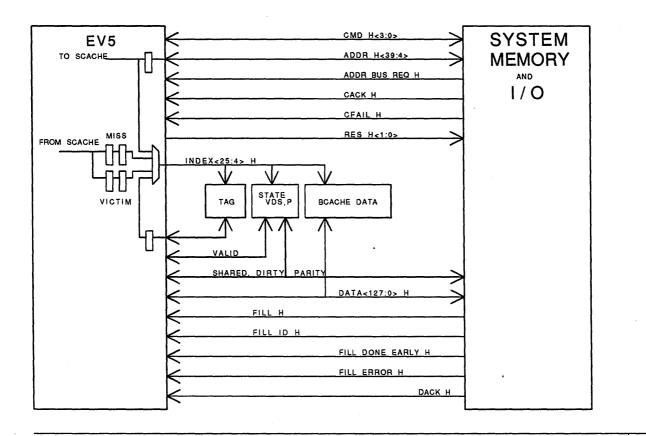

|       |      |          | 4.1.6.1               | System Interface • 4-7                                                 |      |

|       |      |          | 4.1.6.2               | Bcache Interface • 4–10                                                |      |

|       |      | 4.1.7    | •                     | 1164-AA Interface Command Descriptions                                 | 4-12 |

|       |      | 4.1.8    | Transactio<br>4.1.8.1 | ns<br>Read Miss • 4–14                                                 | 4–14 |

|       |      |          | 4.1.8.2               | Read Miss • 4–14<br>Read Miss with victim • 4–15                       |      |

|       |      |          | 4.1.8.2.1             | Without a Victim Buffer • 4–15                                         |      |

|       |      |          | 4.1.8.2.2             | With a Victim Buffer • 4–16                                            |      |

|       |      |          | 4.1.8.3               | Fill • 4–16                                                            |      |

|       | •    |          | 4.1.8.4               | Write Block • 4–17                                                     |      |

|       |      |          | 4.1.8.5               | Set Dirty, Lock • 4–18                                                 |      |

|       |      |          | 4.1.8.6               | Flush • 4–19                                                           |      |

|       |      |          | 4.1.8.7               | Read Dirty, and Read Dirty/INV • 4-19                                  |      |

|       |      |          | 4.1.8.8<br>4.1.8.9    | Invalidate • 4–20<br>Set Shared • 4–21                                 |      |

|       |      |          | 4.1.8.10              | Non-cached Reads • 4–21                                                |      |

|       |      |          | 4.1.8.11              | Non-cached Writes • 4-21                                               |      |

|       |      |          | 4.1.8.12              | Locks • 4-22                                                           |      |

|       |      | 4.1.9    | Clocks                |                                                                        | 4–22 |

|       |      |          | 4.1.9.1               | CPU Clock • 4-22                                                       |      |

|       |      |          | 4.1.9.2               | System Clock • 4-23                                                    |      |

|       |      |          | 4.1.9.3               | Reference Clock • 4-23                                                 |      |

|       |      |          | 4.1.9.4               | Sysclock to Bcache cycle time ratios • 4-23                            |      |

|       |      | 4.1.10   | Tri-state C           | •                                                                      | 4-24 |

|       |      | 4.1.11   | Restrictio            |                                                                        | 425  |

|       |      |          | 4.1.11.1<br>4.1.11.2  | Fills after other transactions • 4–25                                  |      |

|       |      |          | 4.1.11.2              | Sending System commands • 4–25<br>CACK for WRITE BLOCK commands • 4–25 |      |

|       |      |          | 4.1.11.4              | No Bcache Systems • 4-25                                               |      |

|       |      |          | 4.1.11.5              | Scache duplicate tag store • 4-25                                      |      |

|       |      | 4.1.12   | ECC/Parit             | · –                                                                    | 4-26 |

|       | 4.2  |          |                       | -                                                                      | 4.00 |

|       | 4.2  | REVISION | N HISTORY             |                                                                        | 4–28 |

| СНАРТ | FR 5 | RESET A  | ND INITIAL            | IZATION                                                                | 5-1  |

| ••••• |      |          |                       |                                                                        |      |

|       | 5.1  |          | SET_L AND             |                                                                        | 51   |

|       |      | 5.1.1    | •                     | Requirements                                                           | 5–2  |

|       |      | 5.1.2    | Pin State             | with DC_OK_H Not Asserted                                              | 5–2  |

|       | 5.2  | SYSCLO   | CK RATIO A            | ND DELAY                                                               | 5–2  |

|       | 5.3  | BIST     |                       |                                                                        | 5–3  |

|       | 5.4  | SERIAL I | ROM                   |                                                                        | 5–3  |

|       | 5.5  | CACHE I  | NITIALIZATI           | ON                                                                     | 5-4  |

|       | 5.6  |          | ALIZATION             |                                                                        | 5-4  |

|       | 5.7  | UNITIALI | ZED STATE             |                                                                        | 54   |

|       | 5.8  | TIMEOUT  | <b>FRESET</b>         | •                                                                      | 5-4  |

|       | 5.9  | CLOCK F  |                       |                                                                        | 5-4  |

|       |      |          |                       |                                                                        |      |

|       | 5.10 | IEEE 114 | 9.1 TEST P            | DRT RESET                                                              | 5–5  |

| 5.11       | REVISION HISTORY                                                                                                                                                                                                                                                                   | 5–6                                           |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| CHAPTER 6  | ERROR HANDLING                                                                                                                                                                                                                                                                     | 6–1                                           |

| 6.1        | OVERVIEW                                                                                                                                                                                                                                                                           | 6–1                                           |

| 6.2        | REVISION HISTORY                                                                                                                                                                                                                                                                   | 6–3                                           |

| CHAPTER 7  | DC CHARACTERISTICS                                                                                                                                                                                                                                                                 | 7–1                                           |

| 7.1        | OVERVIEW<br>7.1.1 Power Supply<br>7.1.2 Input Clocks<br>7.1.3 Signal pins                                                                                                                                                                                                          | 7–1<br>7–1<br>7–1<br>7–2                      |

| 7.2        | ECL 100K MODE7.2.1Power Supply7.2.2Reference Supply7.2.3Inputs7.2.4Outputs7.2.5Bidirectionals                                                                                                                                                                                      | 7-3<br>7-3<br>7-3<br>7-3<br>7-3<br>7-3<br>7-3 |

| 7.3        | POWER DISSIPATION                                                                                                                                                                                                                                                                  | 7–4                                           |

| 7.4        | REVISION HISTORY                                                                                                                                                                                                                                                                   | 7–5                                           |

| CHAPTER 8  | AC CHARACTERISTICS                                                                                                                                                                                                                                                                 | 8-1                                           |

| 8.1        | REVISION HISTORY                                                                                                                                                                                                                                                                   | 8–1                                           |

| CHAPTER 9  | PINOUT                                                                                                                                                                                                                                                                             | 9–1                                           |

| 9.1        | DECCHIP 21164-AA PINOUT OVERVIEW                                                                                                                                                                                                                                                   | 9–1                                           |

| 9.2        | DECCHIP 21164-AA SIGNAL PINS                                                                                                                                                                                                                                                       | 9–1                                           |

| 9.3        | REVISION HISTORY                                                                                                                                                                                                                                                                   | 9–6                                           |

| CHAPTER 10 | ) THE PACKAGE                                                                                                                                                                                                                                                                      | 10–1                                          |

| 10.1       | REVISION HISTORY                                                                                                                                                                                                                                                                   | 10–1                                          |

| CHAPTER 11 | TEST INTERFACE AND TESTABILITY FEATURES                                                                                                                                                                                                                                            | 11–1                                          |

| 11.1       | INTRODUCTION                                                                                                                                                                                                                                                                       | 11–1                                          |

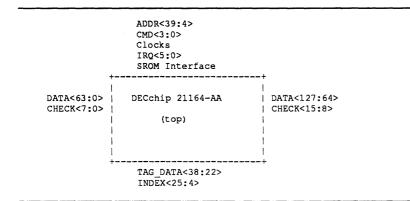

| 11.2       | TEST PORT           11.2.1         Normal Test Interface Mode           11.2.1.1         SROM Port • 11–2           11.2.1.2         Serial Terminal Port • 11–3           11.2.1.3         IEEE 1149.1 Test Access Port • 11–3           11.2.1.4         Test Status Pins • 11–5 | 11–1<br>11–2                                  |

|            | 11.2.2 Manufacturing Test Interface Mode<br>11.2.3 Debug Test Interface Mode                                                                                                                                                                                                       | 11–6<br>11–9                                  |

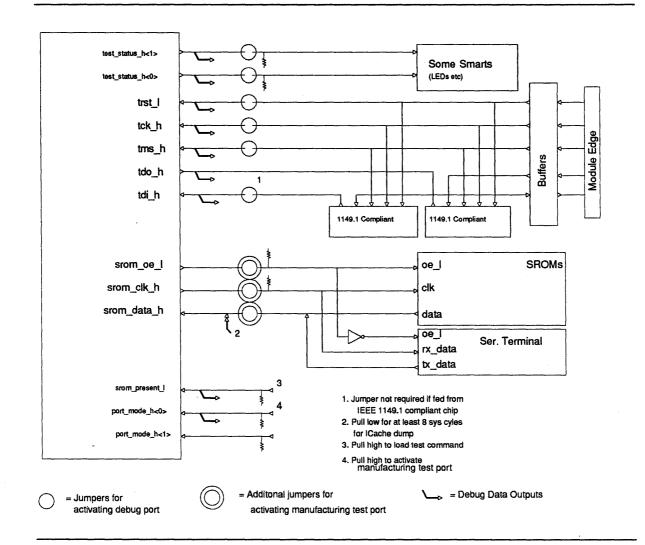

|            | 11.2.4 Activating Debug/Manufacturing Port Modes in a System                                                                                                                                                                                                                       | 11–10                                         |

| 11.3       | ICACHE BIST                                                                                                                                                                                                                                                                        | 11–10                                         |

.

vii

# Contents

| 11.4  | ICACHE SERIAL WRITE AND READ OPERATIONS                                            | 11–12                   |

|-------|------------------------------------------------------------------------------------|-------------------------|

| 11.5  | SCACHE/DCACHE TEST FEATURES                                                        | 11–13                   |

| 11.6  | OBSERVABILITY LFSRS (OBLS)<br>11.6.1 Organization<br>11.6.2 On-line LFSR Operation | 11–14<br>11–14<br>11–15 |

| 11.7  | OBSERVABILITY SCAN REGISTERS (OBSS)                                                | 11–15                   |

| 11.8  | CONTROLLABILITY FEATURES                                                           | 11–16                   |

| 11.9  | BOUNDARY SCAN REGISTER                                                             | 11 <b>–17</b>           |

| 11.10 | TESTABILITY IPRS                                                                   | 11–19                   |

| 11.11 | TEST FEATURE RESET AND INITIALIZATION                                              | 11–19                   |

| 11.12 | OPEN ISSUES                                                                        | 1120                    |

| 11.13 | REVISION HISTORY                                                                   | 11–21                   |

# FIGURES

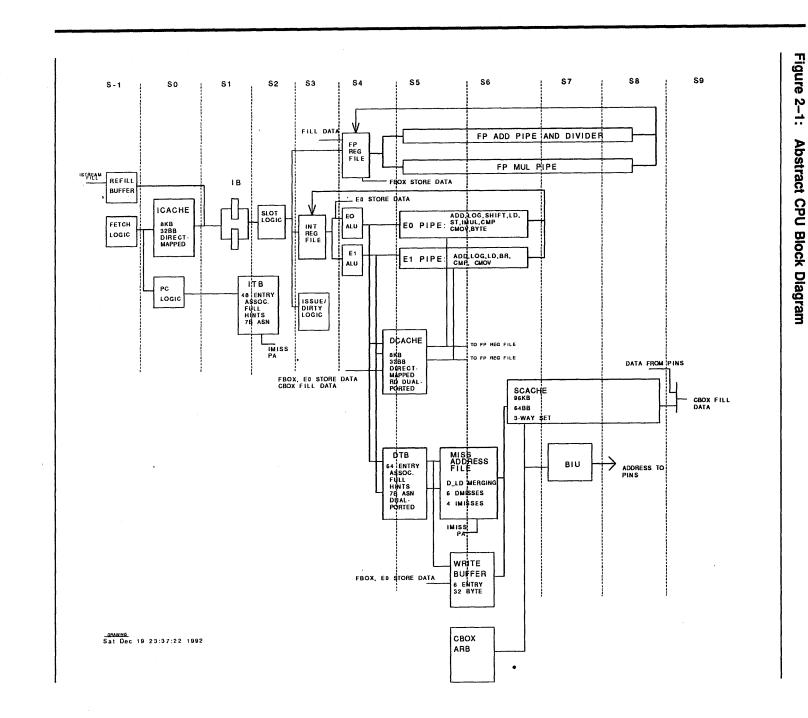

| 2–1             | Abstract CPU Block Diagram                      | 23   |

|-----------------|-------------------------------------------------|------|

| 2–2             | Pipeline Examples                               | 2–20 |

| 3–1             | HW_LD instruction                               | 3-4  |

| 32              | HW_ST instruction                               | 3–5  |

| 3–3             | HW_REI instruction                              | 3–6  |

| 3–4             | HW_MFPR, HW_MTPR instruction                    | 3–7  |

| 3–5             | Istream TBmiss flow                             | 3–12 |

| 3–6             | Dstream TBmiss flow                             | 3–13 |

| 3–7             | Istream TB Tag, ITB_TAG                         | 3–14 |

| 3–8             | Istream TB PTE Write Format, ITB_PTE            | 3–14 |

| 3– <del>9</del> | Istream TB PTE Read Format, ITB_PTE             | 3–15 |

| 3–10            | Address Space Number Read/Write Format, ITB_ASN | 3–15 |

| 3–11            | Istream TB PTE Temp Read Format, ITB_PTE_TEMP   | 3–15 |

| 3–12            | ITB_IS                                          | 3–16 |

| 3–13            | IFAULT_VA_FORM in non NT mode                   | 3–16 |

| 3–14            | IFAULT_VA_FORM in NT mode                       | 3–17 |

| 3–15            | IVPTBR                                          | 3–17 |

| 3–16            | ICPERR_STAT Read format                         | 3–17 |

| 3–17            | EXC_ADDR Read/Write format                      | 3–18 |

| 3–18            | Exception Summary register Read Format, EXC_SUM | 3–18 |

| 3–19            | Exception Mask register Read Format, EXC_MASK   | 3–19 |

| 3–20            | PAL_BASE                                        | 3–20 |

| 3–21            | Processor Status, PS                            | 3–20 |

| 3-22            | Ibox Control/Status Register ICSR               | 320  |

| 3–23            | Interrupt Priority Level Register, IPL          | 3–22 |

| 3–24            | Interrupt Id Register, INTID                    | 3–22 |

DIGITAL RESTRICTED DISTRIBUTION

•

viii

.

| 3–25 | Asynchronous System Trap Request Register, ASTRR       | 3–23 |

|------|--------------------------------------------------------|------|

| 326  | Asynchronous System Trap Enable Register, ASTER format | 3–23 |

| 327  | Software Interrupt Request Register, SIRR write format | 3–23 |

| 3–28 | Software Interrupt Clear Register, SICR write format   | 3–24 |

| 3–29 | Hardware Interrupt Clear Register, HWINT_CLR           | 3–24 |

| 3–30 | Interrupt Summary Register, ISR read format            | 3–24 |

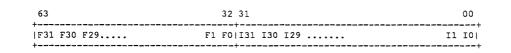

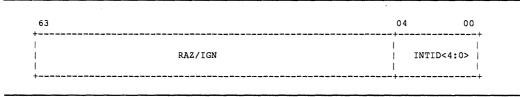

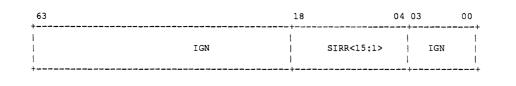

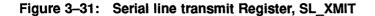

| 331  | Serial line transmit Register, SL_XMIT                 | 3–25 |

| 3–32 | Serial line receive Register, SL_RCV                   | 3–26 |

| 3–33 | DTB_ASN                                                | 3–26 |

| 3–34 | DTB_CM                                                 | 3–27 |

| 3–35 | DTB_TAG, Dstream TB Tag                                | 3–27 |

| 3–36 | DTB_PTE, Dstream TB PTE                                | 3–28 |

| 3–37 | DTB_PTE_TEMP                                           | 329  |

| 3–38 | MM_STAT, Dstream MM Fault Register                     | 3–29 |

| 3–39 | VA, Faulting VA Register                               | 330  |

| 3-40 | VA_FORM, Formatted VA Register for NT_Mode=0           | 3–30 |

| 3-41 | VA_FORM, Formatted VA Register, NT_Mode=1              | 3–31 |

| 3-42 | MVPTBR                                                 | 3–31 |

| 3–43 | DC_PERR_STAT, Dcache Parity Error Status               | 3–32 |

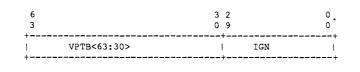

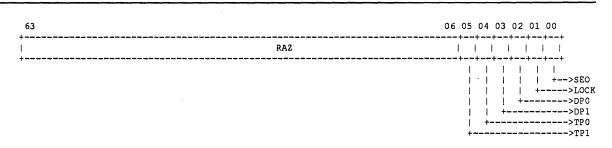

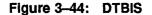

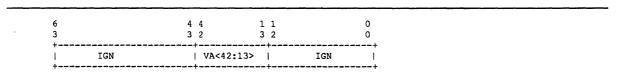

| 3-44 | DTBIS                                                  | 3–33 |

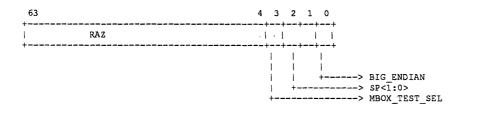

| 3–45 | MCSR, Mbox Control Register                            | 3–33 |

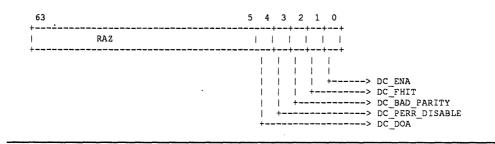

| 3–46 | DC_MODE, Dcache Mode Register                          | 3–34 |

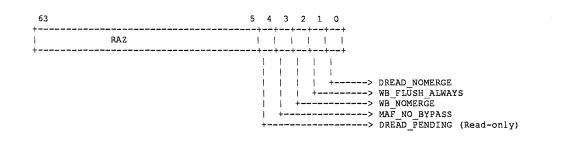

| 3-47 | MAF_MODE, MAF Mode Register                            | 3–35 |

| 348  | ALT_MODE                                               | 3–36 |

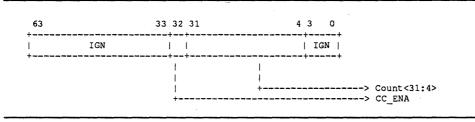

| 3-49 | CC, Cycle Counter Register                             | 3–37 |

| 3–50 | CC_CTL, Cycle Counter Control Register                 | 3–38 |

| 3–51 | DC_TEST_CTL, Dcache Test TAG Control Register          | 3–38 |

| 3–52 | DC_TEST_TAG, Dcache Test TAG Register                  | 3–39 |

| 353  | DC_TEST_TAG_TEMP, Dcache Test TAG Temp Register        | 3-40 |

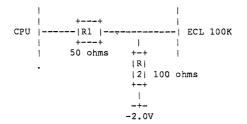

| 4–1  | DECchip 21164-AA System Interface                      | 4–1  |

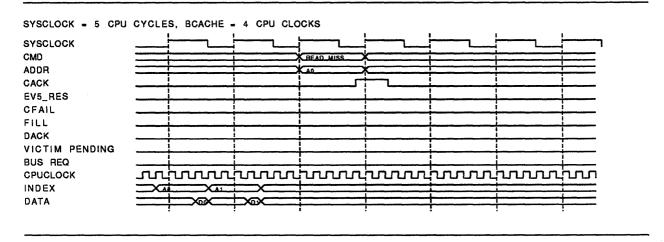

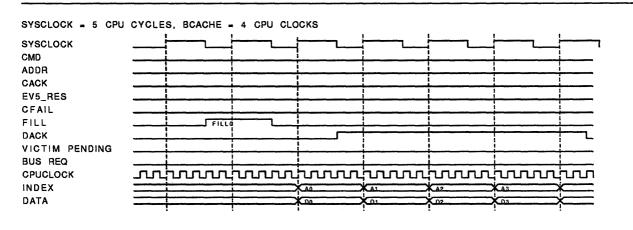

| 4–2  | Read Miss                                              | 4–15 |

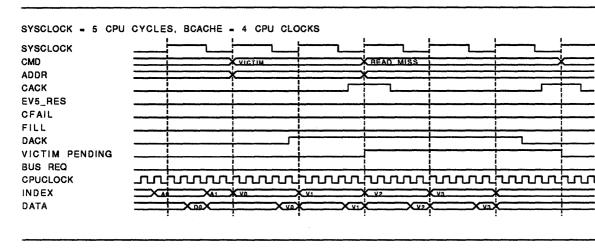

| 4–3  | Read Miss with Victim                                  | 4–16 |

| 44   | Read Miss with Victim Buffer                           | 4–16 |

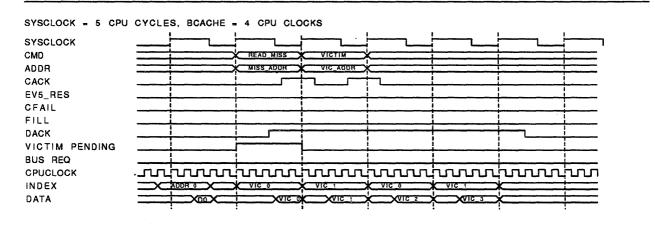

| 4–5  | Fill                                                   | 4–17 |

| 46   | Write Block                                            | 4–18 |

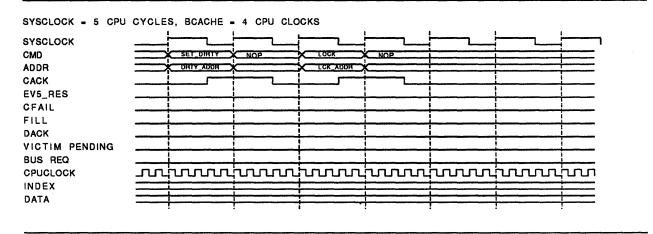

| 4-7  | Set Dirty, and Lock                                    | 4–19 |

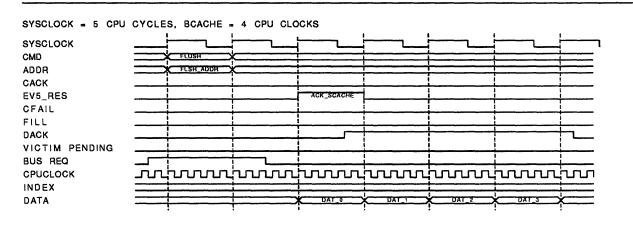

| 48   | Flush                                                  | 4–19 |

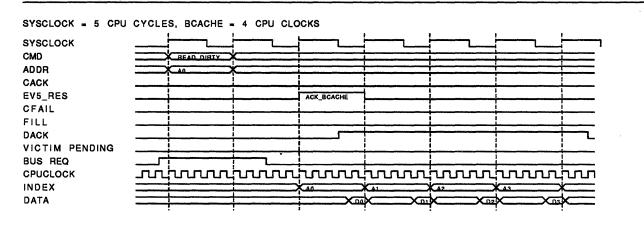

| 49   | Read Dirty                                             | 420  |

| 4–10 | Invalidate                                             | 4–20 |

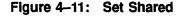

| 4-11 | Set Shared                                             | 421  |

| 4–12 | Reference Clock Timing                                 | 4–23 |

| 4–13 | Driving the CMD/ADDRESS Bus                            | 4–24 |

| 4-14 | ECC code                                               | 4-26 |

ix

| 415  | x4 bit arrangement                | 4–27  |

|------|-----------------------------------|-------|

| 5-1  | Serial ROM Load Timing            | 5–3   |

| 9–1  | DECchip 21164-AA Pinout           | 9–1   |

| 11-1 | IEEE 1149.1 Test Access Port      | 11–4  |

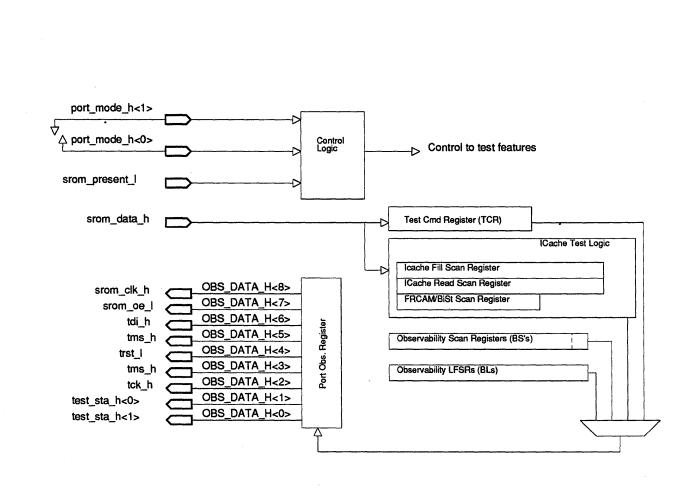

| 11–2 | Manufacturing Test Interface Mode | 11–7  |

| 113  | Tes Port Connections on Module    | 11–11 |

| 11–4 | SROM Fill Scan Path Bit Order     | 11–13 |

| 11–5 | Read Scan Path Bit Order          | 11–13 |

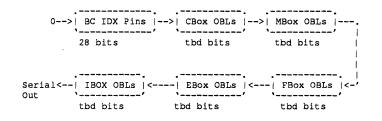

| 11–6 | LFSR Chain Organization           | 11–14 |

# TABLES

| 1    | REVISION History                                     | 1    |

|------|------------------------------------------------------|------|

| 1-1  | Register Field Type Notation                         | 1–4  |

| 1–2  | Register Field Notation                              | 1–4  |

| 1–3  | DECchip 21164-AA Chip Summary and Micro-architecture | 1–5  |

| 1-4  | Revision History                                     | 1–6  |

| 2–1  | Interrupt Priority Level Effect                      | 2–6  |

| 2–2  | Pipeline Examples - All Cases                        | 2–20 |

| 2–3  | Pipeline Examples - Integer Add                      | 220  |

| 2–4  | Pipeline Examples - Floating Add                     | 2–21 |

| 25   | Pipeline Examples - Load (Dcache hit)                | 2–21 |

| 26   | Pipeline Examples - Load (Dcache miss)               | 2–21 |

| 2–7  | Pipeline Examples - Store (Dcache hit)               | 2–21 |

| 28   | Instruction Classes and Slotting                     | 2–24 |

| 2–9  | Instruction Latencies                                | 2–26 |

| 2–10 | Revision History                                     | 2–30 |

| 3-1  | PALcode Trap Entry Points                            | 3–3  |

| 3–2  | HW_LD Format description                             | 3–4  |

| 3–3  | HW_ST Format description                             | 3–5  |

| 3-4  | HW_REI Format description                            | 3–6  |

| 3-5  | HW_MTPR and HW_MFPR Format description               | 3–7  |

| 3–6  | IPR Encodings                                        | 3–7  |

| 3–7  | OpenVMS SRM defined State                            | 3–9  |

| 3–8  | OSF SRM defined State                                | 3–11 |

| 3–9  | Description of GHD bits in ITB_PTE_TEMP read format  | 3–15 |

| 3-10 | ICPERR_STAT Field Descriptions                       | 3–17 |

| 3–11 | EXC_SUM Field Descriptions                           | 3–19 |

| 3–12 | ICSR Field Descriptions                              | 3–20 |

| 3–13 | Performance Counter 0 Programming information        | 3–21 |

| 3–14 | Performance Counter 1 Programming information        | 3–21 |

| 315  | HWINT_CLR Field Descriptions                         | 3–24 |

| 3–16 | ISR read format Field Descriptions                   | 3–25 |

| 3–17             | DTB_CM Mode Bits                                        | 3–27  |

|------------------|---------------------------------------------------------|-------|

| 3–18             | MM_STAT Field Descriptions                              | 3–29  |

| 3–19             | VA_FORM Field Descriptions                              | 3–31  |

| 3–20             | DC_PERR_STAT Field Descriptions                         | 3–32  |

| 3–21             | MCSR Field Descriptions                                 | 3–33  |

| 3–22             | DC_MODE Field Descriptions                              | 3–34  |

| 3–23             | MAF_MODE Field Descriptions                             | 3–35  |

| 3–24             | ALT Mode                                                | 3–37  |

| 3–25             | CC_CTL Field Descriptions                               | 3–38  |

| 3–26             | DC_TEST_CTL Field Descriptions                          | 3–38  |

| 327              | DC_TEST_TAG Field Descriptions                          | 3–39  |

| 3–28             | DC_TEST_TAG_TEMP Field Descriptions                     | 3–40  |

| 3–2 <del>9</del> | CBOX_IPRS Descriptions                                  | 3-42  |

| 3–30             | SC_CTL Field Descriptions                               | 3–43  |

| 331              | SC_TAG_STAT Field Description                           | 3–44  |

| 3–32             | SC_STAT Field Descriptions                              | 3–45  |

| 3–33             | SC_CMD Field Descriptions                               | 3-45  |

| 3–34             | BC_CONTROL Field Descriptions                           | 3–47  |

| 3–35             | BC_TAG_STAT Field Description                           | 349   |

| 3–36             | BC_CONFIG Field Descriptions                            | 3-49  |

| 3–37             | BC_SIZE Field Descriptions                              | 3–50  |

| 3–38             | Loading/Locking Rules for External Interface Registers  | 351   |

| 339              | EI_STAT Field Descriptions                              | 3–52  |

| 3–40             | Syndromes For Single-Bit Errors                         | 3–54  |

| 3–41             | PAL Restrictions Table                                  | 3–57  |

| 3-42             | Cbox IPR Restrictions Table                             | 3-59  |

| 3–43             | Revision History                                        | 3–60  |

| 4-1              | Physical Memory Regions                                 | 4–3   |

| 42               | System Designs                                          | 4–4   |

| 4–3              | Cache States                                            | 4–5   |

| 4-4              | System Actions                                          | 4–5   |

| 4–5              | Processor Actions                                       | 46    |

| 46               | DECchip 21164-AA Commands to the System                 | 4–7   |

| 4–7              | System Commands to DECchip 21164-AA                     | 4-8   |

| 4-8              | DECchip 21164-AA Responses to System Commands           | 4-9   |

| 49               | Revision History                                        | 4–28  |

| 5-1              | System Clock Divisor                                    | 5–2   |

| 5–2              | System Clock Delay                                      | 53    |

| 5–3              | Revision History                                        | 56    |

| 6–1              | Revision History                                        | 6–3   |

| 7-1              | CMOS DC Characteristics                                 | . 7–2 |

| 72               | DECchip 21164-AA Estimated Power Dissipation @Vdd=3.45V | 7-4   |

| 7–3              | Revision History                                        | 7-5   |

.

Xİ

Contents

| 8-1             | Revision History                               | 8–1   |

|-----------------|------------------------------------------------|-------|

| 9–1             | Clock Pins                                     | 9-2   |

| <del>9</del> –2 | System Interface Pins                          | 9–3   |

| 9-3             | Bcache Pins                                    | 9-4   |

| 94              | Interrupt and Misc. Pins                       | 9-5   |

| <del>9</del> –5 | Revision History                               | 9–6   |

| 10-1            | Revision History                               | 10–1  |

| 11-1            | DECchip 21164-AA Test Port Pins and Port Modes | 11–2  |

| 11–2            | Instruction Register                           | 11–5  |

| 11–3            | Test Command Register                          | 11–8  |

| 11–4            | FRCAM Scan Register Organization               | 11–12 |

| 11–5            | Observability LFSR Organization                | 11–14 |

| 116             | Observability Scan Register Organization       | 11–16 |

| 11–7            | Boundary Scan Register Organization            | 11–17 |

| 118             | Revision History                               | 11–21 |

| Revision | Date             | Description                                 |

|----------|------------------|---------------------------------------------|

| 1.0      | 2-March-1992     | Initial release.                            |

| 1.5      | 8-May-1992       | Updates including some significant changes. |

| 1.9      | 21-December-1992 | Further updates.                            |

Table 1: REVISION History

.

# Chapter 1

# Introduction

## 1.1 Scope

This document describes the DECchip 21164-AA chip, a microprocessor that implements the Alpha architecture. This specification describes the external interface and programming information specific to the actual implementation. It does not describe the detailed implementation of the chip nor the Alpha architecture. The reader is referred to the Alpha System Reference Manual for the architectural specification.

### 1.2 Chip Features

The DECchip 21164-AA microprocessor is a CMOS-5 (.5 micron) super-scalar super-pipelined implementation of the Alpha architecture. It will be the basis of a family of Alpha products. The DECchip 21164-AA chip is designed to meet the requirements of a wide variety of systems, ranging from uni-processor workstations to multiprocessors. DECchip 21164-AA is intended to integrate well into a certain style of system environment, one with a particular kind of cache coherence protocol and a pipelined or lock-step style of bus and memory subsystem operation. A number of configuration options allow its use in a range of system designs ranging from extremely simple systems with minimum component count to high-performance systems with very high cache and memory bandwidth. DECchip 21164-AA design compromises are made with the intention of achieving maximum performance in high-performance systems while offering competitive performance and reasonable implementation constraints in lower cost systems.

DECchip 21164-AA features:

- Alpha instructions to support byte, word, longword, quadword, DEC F\_floating, G\_floating and IEEE S\_floating and T\_floating data types. Limited support is provided for DEC D\_ floating operations. Partial implementation of the architecturally optional instructions: FETCH and FETCH\_M.

- Demand paged memory management unit which in conjunction with properly written PALcode fully implements the Alpha memory management architecture appropriate to the operating system running on the processor. The translation buffer can be used with alternative PALcode to implement a variety of page table structures and translation algorithms.

- On-chip 48-entry I-stream TB and 64-entry D-stream TB in which each entry maps one 8Kbyte page or a group of 8, 64, or 512 8Kbyte pages, with the size of each TB entry's group specified by hint bits stored in the entry.

#### DIGITAL RESTRICTED DISTRIBUTION

Introduction 1–1

- World class performance.

- Low average cycles per instructions (CPI). The DECchip 21164-AA chip can issue four Alpha instructions in a single cycle, thereby minimizing the average CPI. A number of low-latency and/or high-throughput features in the instruction issue unit and the on-chip components of the memory subsystem further reduce the average CPI.

- On-chip high-throughput floating point units, capable of executing both DEC and IEEE floating point data types.

- On-chip 8Kbyte virtual instruction cache with seven-bit ASNs (MAX\_ASN=127).

- On-chip dual-read-ported 8Kbyte data cache (implemented as two 8Kbyte data caches containing identical data).

- On-chip write buffer with six 32-byte entries.

- On-chip 96Kbyte 3-way set associative writeback second level cache.

- Bus interface unit, which contains logic to directly access an optional external third-level cache without CPU module action. The size and access time of the external third-level cache is programmable.

- On-chip performance counters to measure and analyze CPU and system performance.

- An instruction cache diagnostic interface to support chip and module level testing.

- An internal clock generator which generates both a high-speed clock needed by the chip itself, and a pair of system clocks for use by the CPU module.

- The DECchip 21164-AA chip is packaged in 503 pin IPGA packages. The heat sinks are separable and application specific.

## **1.3 Terminology and Conventions**

#### 1.3.1 Numbering

All numbers are decimal unless otherwise indicated. Where there is ambiguity, numbers other than decimal are indicated with the name of the base following the number in parentheses, e.g., FF(hex).

# **1.3.2 UNPREDICTABLE And UNDEFINED**

Throughout this specification, the terms UNPREDICTABLE and UNDEFINED are used. Their meanings are quite different and must be carefully distinguished. One key difference is that only privileged software (that is, software running in kernel mode) may trigger UNDEFINED operations, whereas either privileged or unprivileged software may trigger UNPREDICTABLE results or occurrences. A second key difference is that UNPREDICTABLE results and occurrences do not disrupt the basic operation of the processor; the processor continues to execute instructions in its normal manner. In contrast, UNDEFINED operation may halt the processor or cause it to lose information.

A result specified as UNPREDICTABLE may acquire an arbitrary value subject to a few constraints. Such a result may be an arbitrary function of the input operands or of any state information that is accessible to the process in its current access mode. UNPREDICTABLE results may be unchanged from their previous values. UNPREDICTABLE results must not be security holes. Specifically, UNPREDICTABLE results must not do any of the following:

1–2 Introduction

- Depend on or be a function of the contents of memory locations or registers which are inaccessible to the current process in the current access mode.

- Write or modify the contents of memory locations or registers to which the current process in the current access mode does not have access.

- Halt or hang the system or any of its components.

For example, a security hole would exist if some UNPREDICTABLE result depended on the value of a register in another process, on the contents of processor temporary registers left behind by some previously running process, or on a sequence of actions of different processes.

An occurrence specified as UNPREDICTABLE may happen or not based on an arbitrary choice function. The choice function is subject to the same constraints as are UNPREDICTABLE results and, in particular, must not constitute a security hole.

Results or occurrences specified as UNPREDICTABLE may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. Software can never depend on results specified as UNPREDICTABLE.

Operations specified as UNDEFINED may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. The operation may vary in effect from nothing to stopping system operation. UNDEFINED operations must not cause the processor to hang, i.e., reach an unhalted state from which there is no transition to a normal state in which the machine executes instructions. Only privileged software (that is, software running in kernel mode) may trigger UNDEFINED operations.

## 1.3.3 Data Field Size

The term INTnn, where nn is one of 2, 4, 8, 16, 32, or 64, refers to a data field of nn contiguous naturally aligned bytes. INT4 refers to a naturally aligned longword, for example.

# 1.3.4 Ranges And Extents

Ranges are specified by a pair of numbers separated by a ".." and are inclusive, e.g., a range of integers 0..4 includes the integers 0, 1, 2, 3, and 4.

Extents are specified by a pair of numbers in angle brackets separated by a colon and are inclusive, e.g., bits <7:3> specify an extent of bits including bits 7, 6, 5, 4, and 3.

# 1.3.5 Register Format Notation

This specification contains a number of figures that show the format of various registers, followed by a description of each field. In general, the fields on the register are labeled with either a name or a mnemonic. The description of each field includes the name or mnemonic, the bit extent, and the type.

The "Type" column in the field description includes both the actual type of the field, and an optional initialized value, separated from the type by a comma. The type denotes the functional operation of the field, and may be one of the values shown in Table 1–1. If present, the initialized value indicates that the field is initialized by hardware to the specified value at powerup. If the initialized value is not present, the field is not initialized at powerup.

#### DIGITAL RESTRICTED DISTRIBUTION

Introduction 1–3

| Notation | Description                                                                                                                                                                                                                                                                                                                         |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RW       | A read-write bit or field. The value may be read and written by software.                                                                                                                                                                                                                                                           |  |

| RO       | A read-only bit or field. The value may be read by software. It is written by hardware software writes are ignored.                                                                                                                                                                                                                 |  |

| WO       | A write-only bit or field. The value may be written by software. It is used by hardware and reads by software return an UNPREDICTABLE result.                                                                                                                                                                                       |  |

| WZ       | A write bit or field. The value may be written by software. It is used by hardware and reads by software return a 0.                                                                                                                                                                                                                |  |

| W1C      | A write-one-to-clear bit. If reads are allowed to the register then the value may be<br>read by software. If it is a write-only register then a read by software returns ar<br>UNPREDICTABLE result. Software writes of a 1 cause the bit to be cleared by hard<br>ware. Software writes of a 0 do not modify the state of the bit. |  |

| WOC      | A write-zero-to-clear bit. If reads are allowed to the register then the value may<br>be read by software. If it is a write-only register then a read by software returns<br>an UNPREDICTABLE result. Software writes of a 0 cause the bit to be cleared by<br>hardware. Software writes of a 1 do not modify the state of the bit. |  |

| WA       | A write-anything-to-the-register-to-clear bit. If reads are allowed to the register the<br>the value may be read by software. If it is a write-only register then a read by softwar<br>returns an UNPREDICTABLE result. Software write of any value to the register caus<br>the bit to be cleared by hardware.                      |  |

| RC       | A read-to-clear field. The value is written by hardware and remains unchanged unti<br>read. The value may be read by software at which point, hardware may write a new<br>value into the field.                                                                                                                                     |  |

Table 1–1:

Register Field Type Notation

In addition to named fields in registers, other bits of the register may be labeled with one of the four symbols listed in Table 1–2. These symbols denote the type of the unnamed fields in the register.

| Notation | Description                                                                                                                                                                                                          |  |

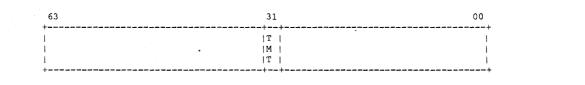

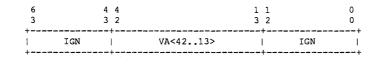

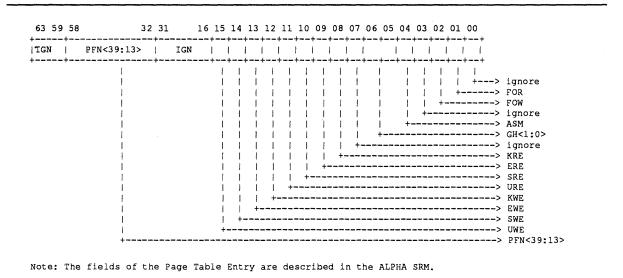

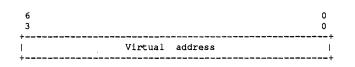

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|