# EV5 CPU Chip Internal Specification

The EV5 CPU Chip is a high-performance, single-chip implementation of the Alpha Architecture.

Revision/Update Information: This is Revision 0.0 of this specification.

Product Manager: John Fortune, RICKS::FORTUNE Engineering Manager: Paul Rubinfeld, ROCK::RUBINFELD

## DIGITAL RESTRICTED DISTRIBUTION

This information shall not be disclosed to persons other than DIGITAL employees or generally distributed within DIGITAL. Distribution is restricted to persons authorized and designated by the originating organization. This document shall not be transmitted electronically, copied unless authorized by the originating organization, or left unattended. When not in use, this document shall be stored in a locked storage area. These restrictions are enforced until this document is reclassified by the originating organization.

Semiconductor Engineering Group Digital Equipment Corporation, Hudson, Massachusetts

This is copy number

#### February 1992

The drawings and specifications in this document are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of items without written permission.

The information in this document may be changed without notice and is not a commitment by Digital Equipment Corporation. Digital Equipment Corporation is not responsible for any errors in this document.

This specification does not describe any program or product that is currently available from Digital Equipment Corporation, nor is Digital Equipment Corporation committed to implement this specification in any program or product. Digital Equipment Corporation makes no commitment that this document accurately describes any product it might ever make.

Copyright ©1992 by Digital Equipment Corporation All Rights Reserved Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEC DECnet DECUS MicroVAX MicroVMS PDP ULTRIX ULTRIX-32 UNIBUS VAX VAXBI VAXCluster VAXstation VMS VT

# Contents

| CHAPTER 1 | THE IBOX                         | ζ.                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–1               |

|-----------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1.1       | OVERVIE                          | w                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–1               |

| 1.2       | <b>FUNCTIO</b><br>1.2.1<br>1.2.2 | NAL DESCR<br>ICache<br>Instructior                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–5<br>1–5<br>1–5 |

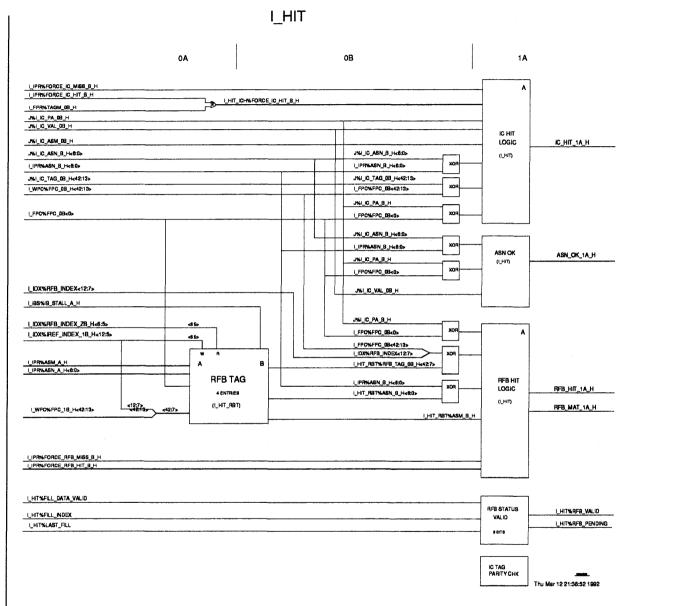

| •         |                                  | 1.2.2.1<br>1.2.2.2<br>1.2.2.3<br>1.2.2.4                                                                                                                                                                                                                                                             | Instruction Fetch Flow • 1–7<br>Prefetch Addressing • 1–12<br>I-Cache Hit Logic • 1–12<br>Refill Buffer Hit Logic • 1–13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

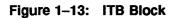

|           | 1.2.3                            | ITB                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–18              |

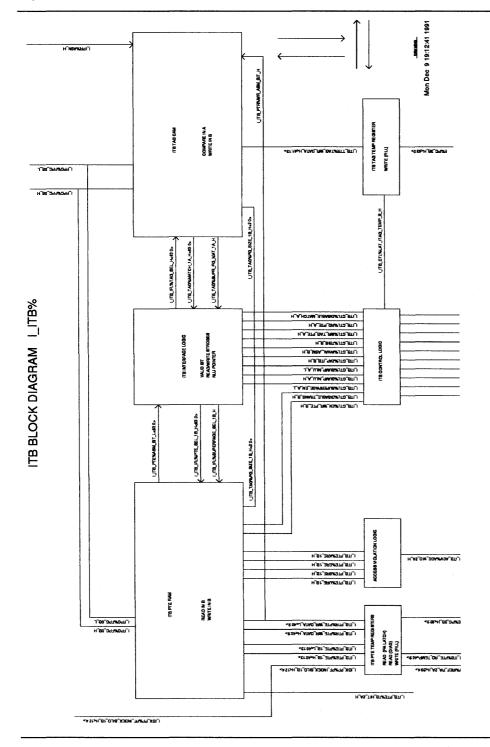

|           | 1.2.4                            | Branch Hi                                                                                                                                                                                                                                                                                            | story Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1–22              |

|           |                                  | 1.2.4.1                                                                                                                                                                                                                                                                                              | HUP Logic • 1-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|           | 1.2.5                            | I-Stream F<br>1.2.5.1<br>1.2.5.2<br>1.2.5.3                                                                                                                                                                                                                                                          | Flow Prediction<br>Branch Predictor • 1–25<br>Target Calculation • 1–26<br>Return Prediction Stack • 1–28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1–25              |

|           | 1.2.6                            | PC<br>1.2.6.1<br>1.2.6.2<br>1.2.6.2.1<br>1.2.6.2.2<br>1.2.6.2.3                                                                                                                                                                                                                                      | Fetch PC • 1–31<br>Execution PC • 1–34<br>BR_ALT_PC • 1–34<br>JSR_HW_RELPC • 1–34<br>PC Mispredict • 1–34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1–31              |

|           | 1.2.7                            |                                                                                                                                                                                                                                                                                                      | n <b>Buffer(IB)</b><br>HW_REI - stall prefetch • 1–38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1–37              |

|           | 1.2.8                            | Instruction                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–40              |

|           | 1.2.9                            | Instruction<br>1.2.9.1<br>1.2.9.2<br>1.2.9.3<br>1.2.9.3.1<br>1.2.9.3.2<br>1.2.9.3.3<br>1.2.9.4<br>1.2.9.4.1<br>1.2.9.4.2<br>1.2.9.4.3<br>1.2.9.4.4<br>1.2.9.4.5<br>1.2.9.4.6<br>1.2.9.4.7<br>1.2.9.4.8<br>1.2.9.4.9<br>1.2.9.5<br>1.2.9.6<br>1.2.9.7<br>1.2.9.7<br>1.2.9.7.1<br>1.2.9.7.2<br>1.2.9.8 | n Issue<br>Interface with the Slot Stage • 1–48<br>Instruction Interface with the E,F,M Boxes • 1–48<br>Dirty Checks • 1–50<br>DEST-SOURCE Checks • 1–50<br>DEST-DEST Checks • 1–50<br>Current Issue Conflicts • 1–51<br>Resource Availability Checks • 1–51<br>IMUL_BUSY • 1–51<br>IMUL_DONE_SOON • 1–52<br>FDIV_BUSY • 1–52<br>FDIV_DONE_SOON • 1–52<br>STORE_STALL • 1–52<br>FILL_STALL • 1–52<br>DRAINT_Stall • 1–53<br>MB_MB_STALL • 1–53<br>Instruction Stall • 1–53<br>Instruction Stall • 1–53<br>Serialization • 1–54<br>Bypasses • 1–54<br>EBOX Bypasses • 1–56<br>Register File Writes • 1–57 | 1–48              |

1.2.9.9 LOADs and STOREs • 1-58 Additional LOAD Checks • 1-58 1.2.9.9.1 Floating Loads • 1-58 1.2.9.9.2 Floating Stores • 1-59 1.2.9.9.3 1.2.9.9.4 LOAD HITs • 1-59 1.2.9.9.5 LOAD Fills • 1-59 1.2.9.9.6 EBOX LD MUX • 1-60 1.2.9.10 EBOX IMUL MUX • 1-60 1.2.9.11 Conditional Move • 1–60 1.2.9.12 Memory Barriers • 1-60 1.2.9.13 **DRAINT • 1-62** Setting the DRAINT FLAG • 1-62 1.2.9.13.1 1.2.9.13.2 Clearing the DRAINT\_FLAG • 1-63 DRAINT Latency • 1-63 1.2.9.13.3 1.2.9.14 Illegal/Reserved Opcodes • 1-64 Opcodes Reserved to Digital • 1-64 1.2.9.14.1 1.2.9.14.2 PAL Instruction in "native" mode • 1-64 Priviledged CALL\_PALs • 1-64 1.2.9.14.3 1.2.9.14.4 Illegal CAL\_PAL functions • 1-64 1.2.9.14.5 Floating Point • 1-65 1.2.9.15 Aborting Instructions • 1--65 1.2.9.15.1 TRAPs, REPLAYs, and INTERRUPTS • 1-65 ERROR aborts • 1-66 1.2.9.15.2 1.2.9.16 Special Stuff • 1-66 LOAD MISS-AND-USE Replay • 1-66 1.2.9.17 1.2.9.18 PAL Shadow Support • 1-68 1.2.9.18.1 EBOX Register File Control • 1-68 1.2.9.18.2 Dirty Checks for the PAL\_SHADOW registers • 1-68 Switching betweeen PAL SHADOW and NORMAL 1.2.9.18.3 banks • 1-68 **IBOX IPR's and PAL\_TEMP registers** 1--69 ITB\_TAG • 1--69 1.2.10.1 **ITB PTE • 1-70** 1.2.10.2 Address Space Number, ITB\_ASN • 1-70 1.2.10.3 1.2.10.4 **ITB PTE TEMP • 1–71** 1.2.10.5 Istream TB Invalidate All Process, ITB IAP • 1-71 IStream TB Invalidate All, ITB IA • 1-71 1.2.10.6 1.2.10.7 ITB IS • 1-72 1.2.10.8 Formatted Faulting VA register, IFAULT\_VA\_FORM • 1-72 Virtual Page Table Base register, IVPTBR • 1-72 1.2.10.9 Icache Parity Error Status register, ICPERR\_STAT • 1-73 1.2.10.10 1.2.10.11 ICache Flush Control register, IC FLUSH CTL • 1-73 Exception Address register, EXC\_ADDR • 1-74 1.2.10.12 1.2.10.13 Exception Summary register, EXC\_SUM • 1-74 1.2.10.14 Exception Mask Register, EXC\_MASK • 1–75 1.2.10.15 PAL Base Register, PAL\_BASE • 1-75 1.2.10.16 Processor Status, PS • 1-76 1.2.10.17 Ibox Control/Status Register, ICSR • 1-76 1.2.10.18 Interrupt Priority Level Register, IPL • 1-77 1.2.10.19 Interrupt Id Register, INTID • 1-77 1.2.10.20 Aynchronous System Trap Request Register, ASTRR • 1-78 1.2.10.21 Aynchronous System Trap Enable Register, ASTER • 1-78 1.2.10.22 Software Interrupt Request Register. SIRR • 1-79 1.2.10.23 HW Interrupt Clear register, HWINT\_CLR • 1-79

DIGITAL RESTRICTED DISTRIBUTION

1.2.10

|           |         | 1.2.10.24 Interrupt Summary register, ISR • 1–80<br>1.2.10.25 Serial line transmit, SL_XMIT • 1–81<br>1.2.10.26 Serial line receive, SL_RCV • 1–81                                                                                                                                                                          |                 |

|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

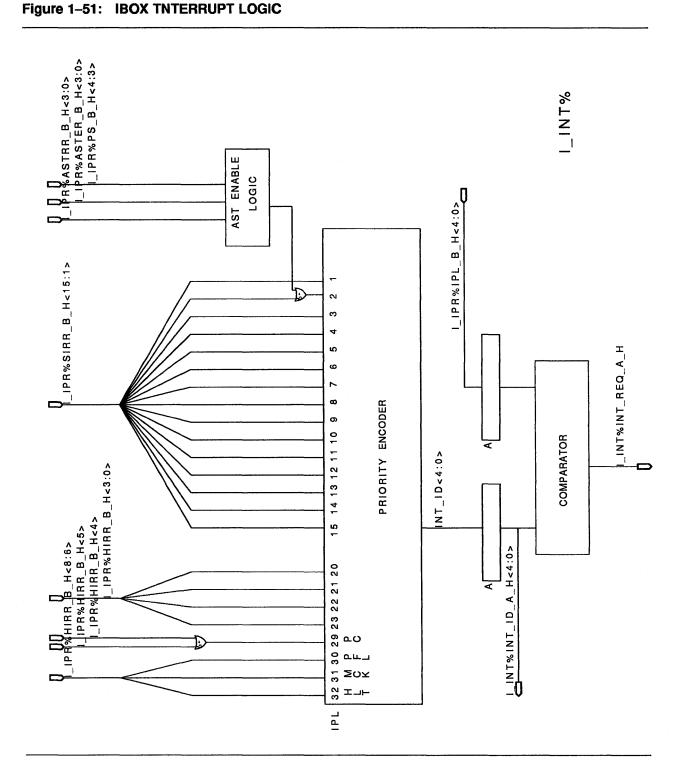

|           | 1.2.11  | Traps and Interrupts1.2.11.1Trap Prioritization and cross-products • 1–831.2.11.1Asynchronous traps • 1–841.2.11.2Aborting Ibox pipe stages on traps • 1–851.2.11.3Aborting Mbox pipe stages on traps • 1–851.2.11.4Generating Restart addresses • 1–851.2.11.5INTERRUPTS • 1–861.2.11.5.1Interrupt Generation Logic • 1–86 | 1–81            |

|           |         | 1.2.11.6 ERRORS • 1–89                                                                                                                                                                                                                                                                                                      |                 |

| 1.3       | RESET A |                                                                                                                                                                                                                                                                                                                             | 189             |

| 1.4       | ERROR I | HANDLING AND RECORDING                                                                                                                                                                                                                                                                                                      | 189             |

| 1.5       | TEST AS | PECTS                                                                                                                                                                                                                                                                                                                       | 1–89            |

| 1.6       | PERFOR  | MANCE MONITORING FEATURES                                                                                                                                                                                                                                                                                                   | 1–89            |

| 1.7       | ISSUES  |                                                                                                                                                                                                                                                                                                                             | 1–89            |

| 1.8       | REVISIO | N HISTORY                                                                                                                                                                                                                                                                                                                   | 1–89            |

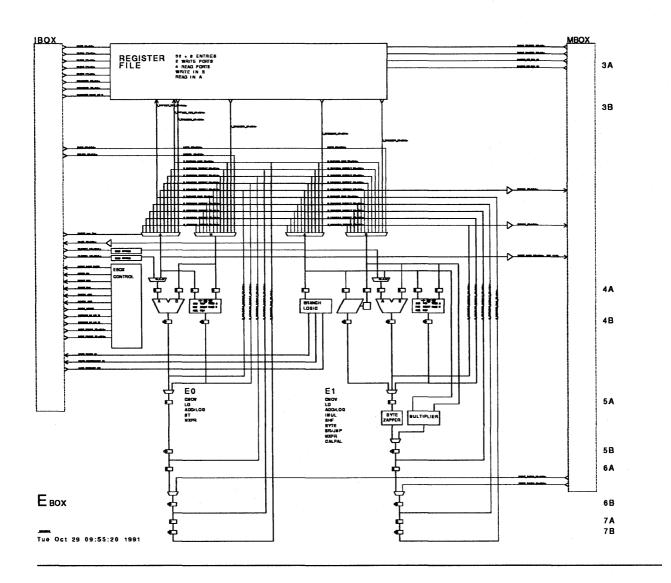

| CHAPTER 2 | THE EBC | X                                                                                                                                                                                                                                                                                                                           | 2–1             |

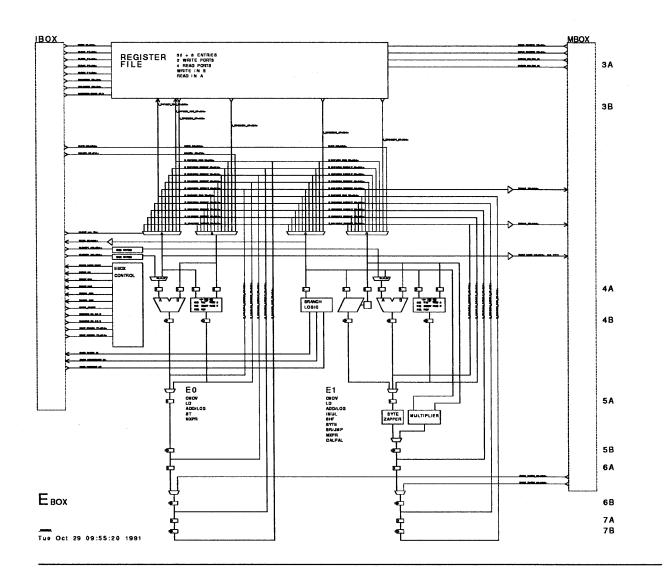

| 2.1       | OVERVIE | EW-BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                            | 2–1             |

| 2.2       | FUNCTIO | DNAL DESCRIPTION                                                                                                                                                                                                                                                                                                            | 2–5             |

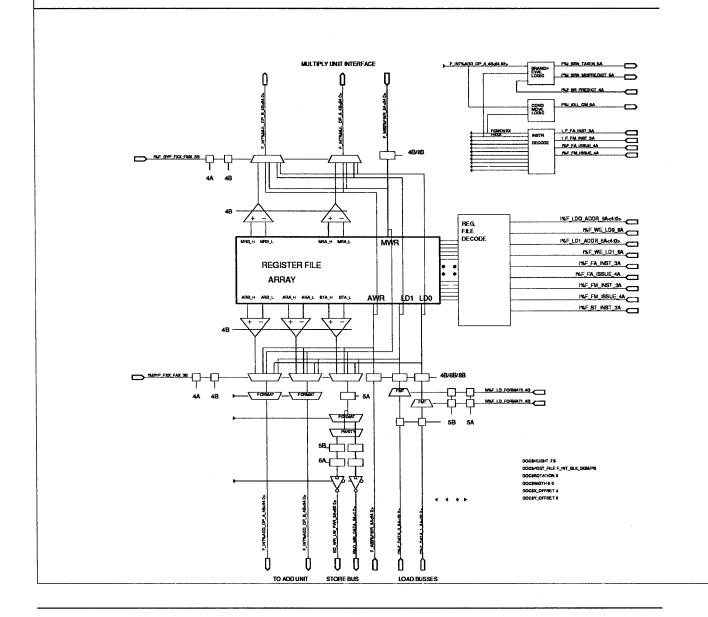

|           | 2.2.1   | Register File                                                                                                                                                                                                                                                                                                               | 2–5             |

|           | 2.2.2   | Bypass Logic                                                                                                                                                                                                                                                                                                                | 2–5             |

|           | 2.2.3   | Adder                                                                                                                                                                                                                                                                                                                       | 25              |

|           | 2.2.4   | Logic Unit                                                                                                                                                                                                                                                                                                                  | 2–8             |

|           | 2.2.5   | Shifter                                                                                                                                                                                                                                                                                                                     | <b>2–</b> 9     |

|           | 2.2.6   | Byte Zapper                                                                                                                                                                                                                                                                                                                 | 2–9             |

|           | 2.2.7   | Multiplier                                                                                                                                                                                                                                                                                                                  | 2– <del>9</del> |

|           | 2.2.8   | Branch Condition Logic                                                                                                                                                                                                                                                                                                      | 2–10            |

| 2.3       |         | CTION FLOWS                                                                                                                                                                                                                                                                                                                 | 2–10            |

|           | 2.3.1   | Compare (CMPEQ, CMPLT, CMPLE)                                                                                                                                                                                                                                                                                               | 2–10            |

|           | 2.3.2   | Compare Unsigned (CMPULT, CMPULE)                                                                                                                                                                                                                                                                                           | 2–11            |

|           | 2.3.3   | Compare Byte (CMPBGE)                                                                                                                                                                                                                                                                                                       | 2–12            |

|           | 2.3.4   | Logical Functions (AND, BIS, XOR, BIC, ORNOT, EQV)                                                                                                                                                                                                                                                                          | 2–12            |

|           | 2.3.5   | Conditional Move (CMOVEQ, CMOVNE, CMOVLT, CMOVLE, CMOVGT, CMOVGE, CMOVLBC, CMOVLBS)                                                                                                                                                                                                                                         | 2–13            |

|           | 2.3.6   | Add Longword (ADDL)                                                                                                                                                                                                                                                                                                         | 2-13            |

|           | 2.3.7   | Scaled Add Longword (S4ADDL, S8ADDL)                                                                                                                                                                                                                                                                                        | 2–14            |

|           | 2.3.8   | Add Quadword (ADDQ)                                                                                                                                                                                                                                                                                                         | 2–14            |

|           | 2.3.9   | Scaled Add Quadword (S4ADDQ, S8ADDQ)                                                                                                                                                                                                                                                                                        | 2–14            |

|           | 2.3.10  | Subtract Longword (SUBL)                                                                                                                                                                                                                                                                                                    | 2-14            |

|           | 2.3.11  | Scaled Subtract Longword (S4SUBL, S8SUBL)                                                                                                                                                                                                                                                                                   | 2-15            |

|           | 2.3.12  | Subtract Quadword (SUBQ)                                                                                                                                                                                                                                                                                                    | 2-15            |

|           | 2.3.13  | Scaled Subtract Quadword (S4SUBQ, S8SUBQ)                                                                                                                                                                                                                                                                                   | 2-15            |

|           | 2.3.14  | Multiply Longword (MULL)                                                                                                                                                                                                                                                                                                    | 2–16            |

|           |         |                                                                                                                                                                                                                                                                                                                             |                 |

|      |       | 2.3.15 Multiply Quadword (MULQ)                                                                 | 2–16 |

|------|-------|-------------------------------------------------------------------------------------------------|------|

|      |       | 2.3.16 Multiply Unsigned Quadword High (UMULH)                                                  | 2–16 |

|      |       | 2.3.17 Shift (SLL, SRL, SRA)                                                                    | 2-17 |

|      |       | 2.3.18 Extract Byte (EXTBL, EXTWL, EXTLL, EXTQL, EXTWH, EXTLH, EXTQH)                           | 2–17 |

|      |       | 2.3.19 Insert Byte (INSBL, INSWL, INSLL, INSQL, INSWH, INSLH, INSQH)                            | 2-18 |

|      |       | 2.3.20 Mask Byte (MSKBL, MSKWL, MSKLL, MSKQL, MSKWH, MSKLH,                                     |      |

|      |       | MSKQH)                                                                                          | 2–20 |

|      |       | 2.3.21 Zap Byte (ZAP, ZAPNOT)                                                                   | 2–22 |

|      |       | 2.3.22 Load Address (LDA, LDAH)                                                                 | 2-22 |

|      |       | 2.3.23 Load (LDL, LDQ)                                                                          | 2–23 |

|      |       | 2.3.24 Load Unaligned (LDQ_U)                                                                   | 2–23 |

|      |       | 2.3.25 Load Locked (LDL_L, LDQ_L)                                                               | 2–24 |

|      |       | 2.3.26 Store Conditional (STL_C, STQ_C)                                                         | 2–24 |

|      |       | 2.3.27 Store (STL, STQ)                                                                         | 2–24 |

|      |       | 2.3.28 Store Unaligned (STQ_U)                                                                  | 2–25 |

|      |       | 2.3.29 Hardware Load (HW_LD)                                                                    | 2–25 |

|      |       | 2.3.30 Hardware Store (HW_ST)                                                                   | 2–26 |

|      |       | 2.3.31 Hardware Move From Processor Register (HW_MFPR)                                          | 2–26 |

|      |       | 2.3.32 Hardware Move To Processor Register (HW_MTPR)                                            | 226  |

|      |       | 2.3.33 Conditional Branch (BEQ, BNE, BLT, BLE, BGT, BGE, BLBC, BLBS)                            | 2–27 |

|      |       | 2.3.34 Unconditional Branch (BR, BSR)                                                           | 2–27 |

|      |       | 2.3.35 Jump (JMP, JSR, RET, JSR_COROUTINE)                                                      | 2–28 |

|      |       | 2.3.36 Fetch (FETCH, FETCH_M)                                                                   | 2–28 |

|      |       | 2.3.37 Read Cycle Counter / VAX Compatibility (RPCC, RC, RS)                                    | 2–28 |

|      |       | 2.3.38 Other Instructions                                                                       | 2–28 |

|      | 2.4   | EBOX INTERFACES                                                                                 | 2–29 |

|      |       | 2.4.1 Ibox Interface                                                                            | 2–29 |

|      |       | 2.4.2 Mbox Interface                                                                            | 233  |

|      | 2.5   | EXCEPTIONS, TRAPS, & STALLS                                                                     | 234  |

|      | 2.6   | RESET AND INITIALIZATION                                                                        | 2–34 |

|      | 2.7   | REVISION HISTORY                                                                                | 2–35 |

| CHAP | TER 3 | THE FBOX                                                                                        | 3–1  |

|      | 3.1   | OVERVIEW-BLOCK DIAGRAM                                                                          | 31   |

|      | 3.2   | FUNCTIONAL DESCRIPTION                                                                          | 3–1  |

|      | 3.3   | FBOX INTERFACE                                                                                  | 3–1  |

|      |       | 3.3.1 Interface Overview                                                                        | 3–3  |

|      |       | 3.3.1.1 External Interface • 3–3                                                                |      |

|      |       | 3.3.1.1.1 Floating Point Instruction Issue • 3–3                                                |      |

|      |       | 3.3.1.1.2 Floating Point Instruction Retirement • 3–3                                           |      |

|      |       | 3.3.1.1.3 Floating Point LOAD/STORE Issue and Retirement • 3–4                                  |      |

|      |       | 3.3.1.1.4 Operand Bypasses • 3–5<br>3.3.1.1.5 Floating Point Branch Evaluation • 3–5            |      |

|      |       | 3.3.1.1.5 Floating Point Branch Evaluation • 3–5<br>3.3.1.1.6 Conditional Move Evaluation • 3–5 |      |

|      |       | 3.3.1.1.7 Pipeline Stalls • 3–5                                                                 |      |

|      |       | 3.3.1.1.8 Pipeline Aborts • 3–6                                                                 |      |

|      |       |                                                                                                 |      |

|       |                  |          | 3.3.1.1.9            | Exceptions • 3–6                                          |      |

|-------|------------------|----------|----------------------|-----------------------------------------------------------|------|

|       |                  |          |                      | Internal Interface • 3-6                                  |      |

|       |                  |          | 3.3.1.2.1            | Stage 1 Interface • 3-6                                   |      |

|       |                  |          | 3.3.1.2.2            | Stage 3 Interface • 3-8                                   |      |

|       |                  | 3.3.2    | interface in         | struction Flows                                           | 3–8  |

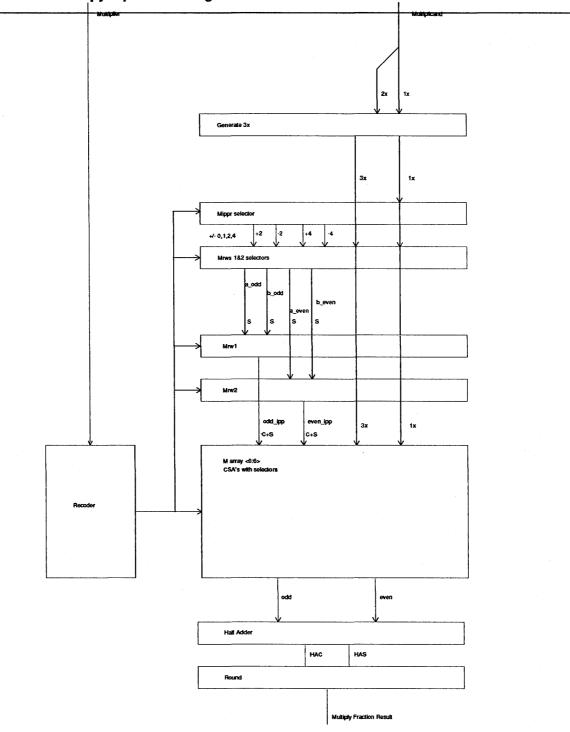

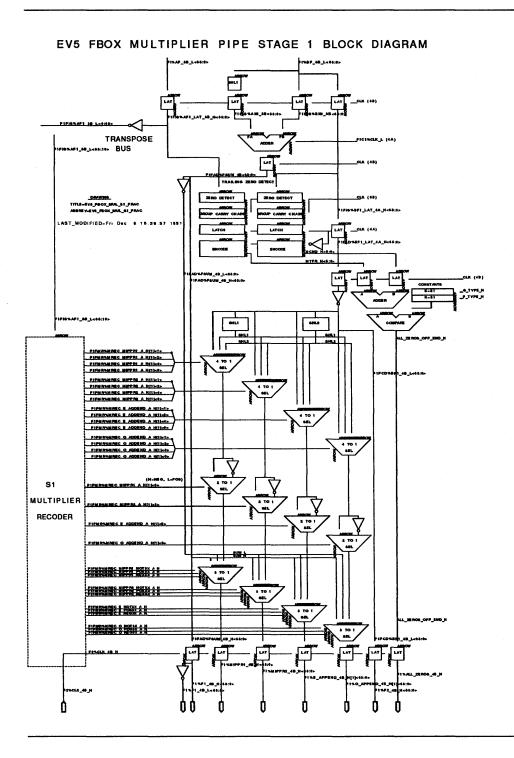

|       | 3.4              | FBOX MU  | LTIPLIER PIF         |                                                           | 3–13 |

|       |                  | 3.4.1    | INTRODUC             |                                                           | 3–13 |

|       |                  | 3.4.2    |                      | be Overview                                               | 313  |

|       |                  |          |                      | Interface • 3–14                                          |      |

|       |                  |          |                      | MUL data path • 3–14<br>Nomenclature • 3–15               |      |

|       |                  | 3.4.3    | INSTRUCTI            |                                                           | 3–15 |

|       |                  | J.4.J    |                      | Floating Point Multiply • 3–15                            | J-1J |

|       |                  | 3.4.4    | Mul Pipe Si          |                                                           | 3–18 |

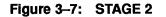

|       |                  | 3.4.5    | Mul Pipe Si          | -                                                         | 3–18 |

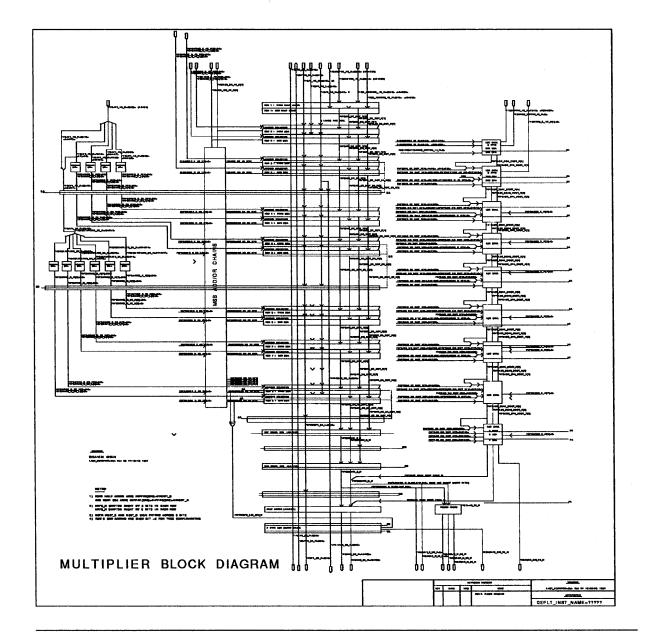

|       |                  | 3.4.6    | Mul Pipe Si          | tage 3                                                    | 3–21 |

|       |                  | 3.4.7    | Copy Sign            |                                                           | 3–21 |

|       |                  |          |                      | Copy Sign - STAGE 1 • 3-21                                |      |

|       |                  |          |                      | Copy Sign - STAGE 2 • 3–21                                |      |

|       |                  |          |                      | Copy Sign - STAGE 3 • 3–23                                | 0.00 |

|       |                  | 3.4.8    | Rounding             |                                                           | 3–23 |

|       | 3.5              |          | ND INITIALIZ         |                                                           | 3–24 |

|       | 3.6              |          |                      | ND RECORDING                                              | 3–24 |

|       | 3.7 TEST ASPECTS |          |                      | 3–24                                                      |      |

|       | 3.8              | PERFORM  | MANCE MON            | ITORING FEATURES                                          | 3–25 |

|       | 3.9              | ISSUES   |                      |                                                           | 3–25 |

|       | 3.10             | REVISION | <b>HISTORY</b>       |                                                           | 3–25 |

| CHAP1 | TER 4            | THE MBC  | X                    |                                                           | 4–1  |

|       | 4.1              | FUNCTIO  | NAL DESCR            | PTION                                                     | 4–1  |

|       |                  | 4.1.1    |                      | Descriptions                                              | 4–3  |

|       |                  |          |                      | LDx - (LDL, LDQ, LDF, LDG, LDS, LDT) • 4-4                |      |

|       |                  |          | 4.1.1.1.1            | Dcache FILLs • 4–5                                        |      |

|       |                  |          |                      |                                                           | ,    |

|       |                  |          | 4.1.1.3<br>4.1.1.4   | STx - (STL, STQ, STF, STG, STS, STT) • 4–7<br>STQ U • 4–8 |      |

|       |                  |          | 4.1.1.5              | MB • 4–8                                                  |      |

|       |                  |          | 4.1.1.6              | WMB • 4–9                                                 |      |

|       |                  |          | 4.1.1.7              | RPCC • 4–9                                                |      |

|       |                  |          | 4.1.1.8              | LDx_L - (LDL_L , LDQ_L) • 4–9                             |      |

|       |                  |          | 4.1.1.9              | STx_C - (STL_C, STQ_C) • 4–10                             |      |

|       |                  |          | 4.1.1.10             | HW_MFPR • 4–11<br>HW MTPR • 4–11                          |      |

|       |                  |          | 4.1.1.11<br>4.1.1.12 | FETCHx - (FETCH , FETCH_M) • 4–11                         |      |

|       |                  |          | 4.1.1.12             | HW LD • 4–11                                              |      |

|       |                  |          | 4.1.1.14             | HW_ST • 4–13                                              |      |

|       |                  | 4.1.2    | Memory M             | anagement                                                 | 414  |

|       |                  |          | 4.1.2.1              | Data Translation Buffer • 4-14                            |      |

vii

| 4.1.3 | Traps            |                                                            | 4–16 |

|-------|------------------|------------------------------------------------------------|------|

|       | 4.1.3.0.1        | Memory Management Traps • 4–18                             |      |

|       | 4.1.3.0.2        | Miss Address File Full and Conflict Traps • 4–19           |      |

|       | 4.1.3.0.3        | Dcache Parity Errors • 4–19                                |      |

|       | 4.1.3.0.4        | Traps from the IBOX • 4–19                                 |      |

|       | 4.1.3.0.5        | CBOX fill errors • 4–20                                    |      |

|       | 4.1.3.0.6        | Multiple Traps • 4–21                                      |      |

| 4.1.4 | Processor        | r Cycle Counter                                            | 4-23 |

| 4.1.5 | <b>Big Endia</b> | n Support                                                  | 424  |

| 4.1.6 | -                | requirements with FBOX, EBOX, IBOX for Dstream Instruction |      |

|       | Execution        | •                                                          | 4-24 |

|       | 4.1.6.1          | Instruction Opcode • 4–24                                  |      |

|       | 4.1.6.2          | Restarting the IBOX After MB, LDx_L and STx_C              |      |

|       |                  | Instructions • 4–25                                        |      |

|       | 4.1.6.3          | Virtual Address from EBOX • 4-25                           |      |

|       | 4.1.6.4          | LD bus • 4–25                                              |      |

|       | 4.1.6.5          | ST Bus Sources and Destinations • 4–26                     |      |

|       | 4.1.6.6          | Register Numbers and Controls to FBOX and IBOX for         |      |

|       |                  | Dstream FILLs and LDs • 4-26                               |      |

| 4.1.7 | Dcache H         | it and Load Miss Conditions                                | 427  |

| 4.1.8 | Dcache In        |                                                            | 4-28 |

|       | 4.1.8.1          | Dcache LDs • 4–30                                          | - 20 |

|       | 4.1.8.2          | Dcache STs • 4–30                                          |      |

|       | 4.1.8.3          | Dcache FILLs • 4–31                                        |      |

|       | 4.1.8.4          | Dcache Invalidates • 4–32                                  |      |

|       | 4.1.8.5          | Parity Generation and Checking • 4–32                      |      |

|       | 4.1.8.6          | Operation Modes for the Dcaches • 4–33                     |      |

|       | 4.1.8.6.1        | Dcache Force Bad Parity and Disable Parity • 4–33          |      |

|       | 4.1.8.6.2        | Dcache Enable and Force Hit Modes • 4–33                   |      |

|       | 4.1.8.6.3        | Dcache Flush • 4–34                                        |      |

|       | 4.1.8.7          | Reading/writing Dcache Tags for Testability • 4-34         |      |

| 4.1.9 | Miss Add         | • • • •                                                    | 434  |

|       | 4.1.9.1          | Overview • 4–34                                            |      |

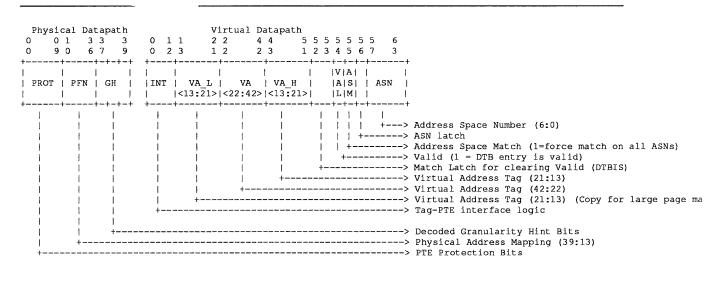

|       | 4.1.9.2          | Basic Timing • 4–35                                        |      |

|       | 4.1.9.3          | CBOX Interface • 4–36                                      |      |

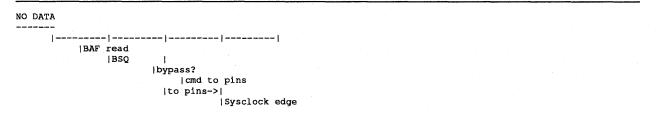

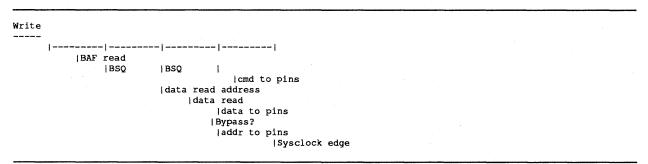

|       | 4.1.9.3.1        | Command/Address Issue Interface • 4–36                     |      |

|       | 4.1.9.3.2        | Write Buffer Interface • 4-38                              |      |

|       | 4.1.9.3.3        | Return Status • 4–38                                       |      |

|       | 4.1.9.3.4        | Invalidates - CBOX Guarantee • 4–39                        |      |

|       | 4.1.9.4          | Icache Interface • 4–40                                    |      |

|       | 4.1.9.5          | Loading the MAF • 4–40                                     |      |

|       | 4.1.9.5.1        | Dcache Read Misses • 4–41                                  |      |

|       | 4.1.9.5.2        | Dstream Writes WMB, FETCHx • 4-44                          |      |

|       | 4.1.9.5.3        | Memory Barriers (MB) • 4-46                                |      |

|       | 4.1.9.5.4        | Write Memory Barriers (WMB) • 4-47                         |      |

|       | 4.1.9.5.5        | Icache Read Misses • 4–47                                  |      |

|       | 4.1.9.6          | MAF Issue to Scache • 4-47                                 |      |

|       | 4.1.9.6.1        | Reissuing WB addresses • 4-48                              |      |

|       | 4.1.9.6.2        | Replaying an Address • 449                                 |      |

|       | 4.1.9.7          | Retiring MAF entries • 4–49                                |      |

|       | 4.1.9.8          | Loads from IO SPACE • 4-50                                 |      |

|       | 4.1.9.9          | Mbox Unavailable Traps • 4–50                              |      |

|       | 4.1.9.10         | MAF Boundary Conditions • 4-50                             |      |

|       | 4.1.9.10.1       | · · · · · · · · · · · · · · · · · · ·                      |      |

|       |                  |                                                            |      |

|         |          | 4.1.9.10.2   | WB Merge Cutoff Point • 4–51                         |      |

|---------|----------|--------------|------------------------------------------------------|------|

|         | 4.1.10   | Mbox and     | Dcache IPR's                                         | 4–51 |

|         |          | 4.1.10.1     | DTB_ASN, Dstream TB Address Space Number • 4-51      |      |

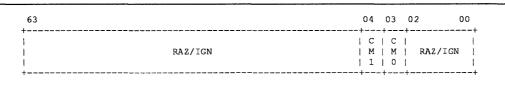

|         |          | 4.1.10.2     | DTB_CM, Dstream TB Current Mode • 4-51               |      |

|         |          | 4.1.10.3     | DTB_TAG, Dstream TB TAG • 4–52                       |      |

|         |          | 4.1.10.4     | Dstream TB PTE, DTB_PTE • 4–52                       |      |

|         |          | 4.1.10.5     | DTB_PTE_TEMP • 4–53                                  |      |

|         |          | 4.1.10.6     | MM_STAT, Dstream MM Fault Status Register • 4-54     |      |

|         |          | 4.1.10.7     | VA, Faulting Virtual Address • 4–55                  |      |

|         |          | 4.1.10.8     | VA_FORM, Formatted Virtual Address • 4–55            |      |

|         |          | 4.1.10.9     | MVPTBR, Mbox Virtual Page Table Base Register • 4-56 |      |

|         |          | 4.1.10.10    |                                                      |      |

|         |          | 4.1.10.11    | Dstream TB Invalidate All Process, DTBIAP • 4-57     |      |

|         |          | 4.1.10.12    | -                                                    |      |

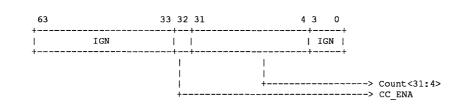

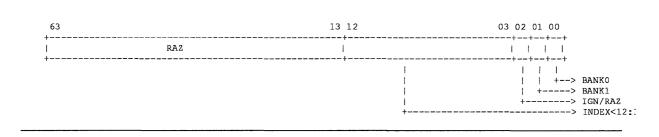

|         |          |              | DTBIS, Dstream TB Invalidate Single • 4–57           |      |

|         |          | 4.1.10.14    |                                                      |      |

|         |          | 4.1.10.15    |                                                      |      |

|         |          | 4.1.10.16    |                                                      |      |

|         |          | 4.1.10.17    |                                                      |      |

|         |          |              | ALT_MODE, Alternate mode • 4-62                      |      |

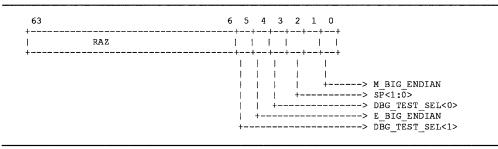

|         |          |              | CC, Cycle Counter • 4–62                             |      |

|         |          |              | CC_CTL, Cycle Counter Control • 4–63                 |      |

|         |          | 4.1.10.21    |                                                      |      |

|         |          | 4.1.10.22    |                                                      |      |

|         |          | 4.1.10.23    |                                                      |      |

|         |          |              | Register • 4–65                                      |      |

| 4.2     | RESET    | AND INITIALI | ΖΑΤΙΟΝ                                               | 4-66 |

| 4.3     | ERROR    | HANDLING A   | ND RECORDING                                         | 467  |

| 4.4     | TEST A   | SPECTS       |                                                      | 467  |

| 4.5     | PERFO    | RMANCE MON   | NITORING FEATURES                                    | 467  |

| 4.6     | ISSUES   |              |                                                      | 468  |

| 4.7     | REVISIO  | ON HISTORY   |                                                      | 468  |

| CHAPTER | 5 THE CB | OX           |                                                      | 51   |

| 5.1     | OVERVI   | IEW & BLOCK  | DIAGRAMS                                             | 51   |

| 5.2     | FUNCT    | ONAL DESCR   |                                                      | 5–3  |

| 5.2     | 5.2.1    | Scache A     |                                                      | 53   |

|         | J.Z. I   | 5.2.1.1      | Mbox Requests • 5–4                                  | 5-5  |

|         |          | 5.2.1.1.1    | Requests from Mbox • 5–6                             |      |

|         |          | 5.2.1.1.1.1  | •                                                    |      |

|         |          | 5.2.1.1.1.2  | ,                                                    |      |

|         |          | 5.2.1.1.1.3  |                                                      |      |

|         |          | 5.2.1.1.1.4  |                                                      |      |

|         |          | 5.2.1.1.1.5  |                                                      |      |

|         |          | 5.2.1.1.1.6  |                                                      |      |

|         |          | 5.2.1.1.2    | Invalidates to DCache • 5–9                          |      |

|         |          | 5.2.1.1.3    | Retries and Merging of Mbox requests • 5–9           |      |

|         |          | 5.2.1.1.4    | Read/Write Ordering from Mbox • 5–11                 |      |

|         |          | 5.2.1.2      | TROLLing of Scache Access Requests • 5-12            |      |

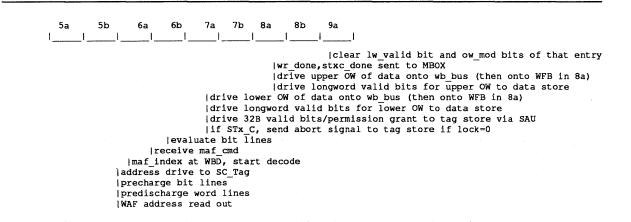

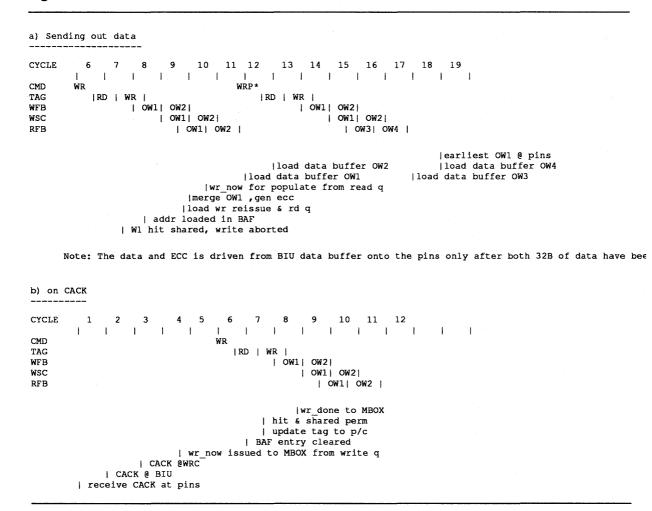

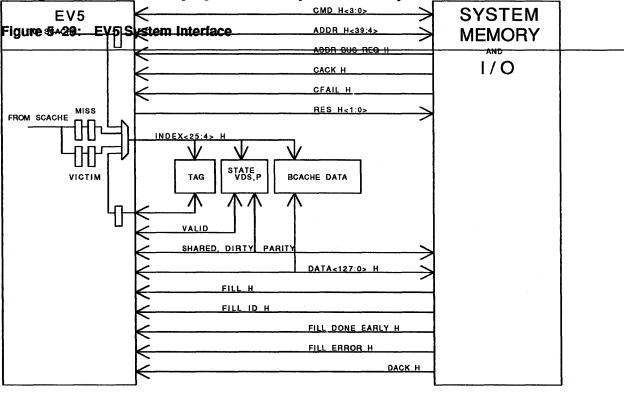

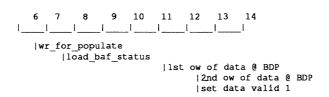

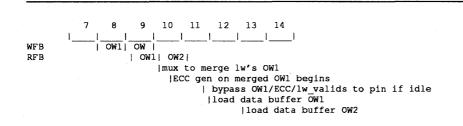

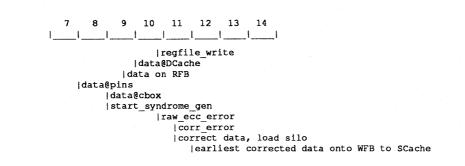

5.2.1.3 BIU requests • 5-13 BIU request Prioritization at SAU • 5-13 5.2.1.3.1 5.2.1.4 SCache Set Allocation • 5-14 Bcache Index Match • 5-15 5.2.1.4.1 Fills from Scache to I/DCache • 5-16 5.2.1.4.2 5.2.2 Write Buffer Unit 5-21 Write Buffer Data Store: WBD • 5-21 5.2.2.1 5.2.2.2 Storing Data in write buffer • 5-21 Issue of Writes • 5-22 5.2.2.3 5.2.2.4 Write Buffer Completion Control:WCC • 5-23 Write Reissue Queue and Control : WRQ,WRC • 5-25 5.2.2.5 5.2.2.5.1 Stopping Writes • 5-26 5.2.2.5.2 Stopping Reads • 5-27 Write flows • 5-28 5.2.2.6 5.2.2.6.1 Private & Dirty • 5-28 5.2.2.6.2 Private & Clean • 5-28 5.2.2.6.3 Shared & Clean • 5-29 Shared & Dirty • 5-31 5.2.2.6.4 5.2.2.6.5 Write misses/Invalid • 5-31 5.2.2.6.6 I/O writes & non-cacheable writes • 5-32 General considerations for writes • 5-33 5.2.2.7 STx C • 5-33 5.2.2.8 5.2.3 **Bus Interface Unit** 5-35 5.2.3.1 BIU Functions • 5-35 Lock Register • 5-36 5.2.3.2 5.2.3.3 Scache Requests • 5-36 5.2.3.3.1 Loading the BAF and VAF • 5-36 5.2.3.3.2 Loading the BAF and VAF • 5-38 5.2.3.3.3 Victims • 5-39 5.2.3.4 System Probe Address Requests • 5-42 5.2.3.5 System Data Requests • 5-47 5.2.3.5.1 BIU Sequencer • 5-48 Bcache Data Cycle Timer • 5-51 5.2.3.5.2 Bcache Data Valid • 5-51 5.2.3.5.3 5.2.3.6 Data Datapath:ECC generation/check • 5-51 Outgoing Data section • 5-52 5.2.3.6.1 5.2.3.6.2 Data buffer section • 5-52 5.2.3.6.3 Incoming Data section & Error Signals • 5-52 5.2.3.7 IPR's • 5-55 SC\_STAT • 5-56 5.2.3.7.1 5.2.3.7.2 SC ADDR • 5-56 5.2.3.7.3 SC CTL • 5-56 FILL SYNDROME • 5-56 5.2.3.7.4 5.2.3.7.5 EI STAT • 5-56 EI\_ADDR • 5-56 5.2.3.7.6 BC TAG ADDR • 5-57 5.2.3.7.7 BC\_CTL • 5-57 5.2.3.7.8 5.2.3.7.9 BC CONFIG • 5-57 LOCK • 5-57 5.2.3.7.10 **RESET AND INITIALIZATION** 5-57 **ERROR HANDLING AND RECORDING** 5--57 **TEST ASPECTS** 5-57

5.3

5.4

5.5

| 5.6       | PERFOR  | MANCE MON            | IITORING FEATURES                                                                                    | 557        |

|-----------|---------|----------------------|------------------------------------------------------------------------------------------------------|------------|

| 5.7       | ISSUES  |                      |                                                                                                      | 5–57       |

| 5.8       | REVISIO | N HISTORY            |                                                                                                      | 557        |

| CHAPTER 6 | THE CAC | HES                  |                                                                                                      | 6–1        |

| 6.1       | OVERVIE | W                    |                                                                                                      | 6–1        |

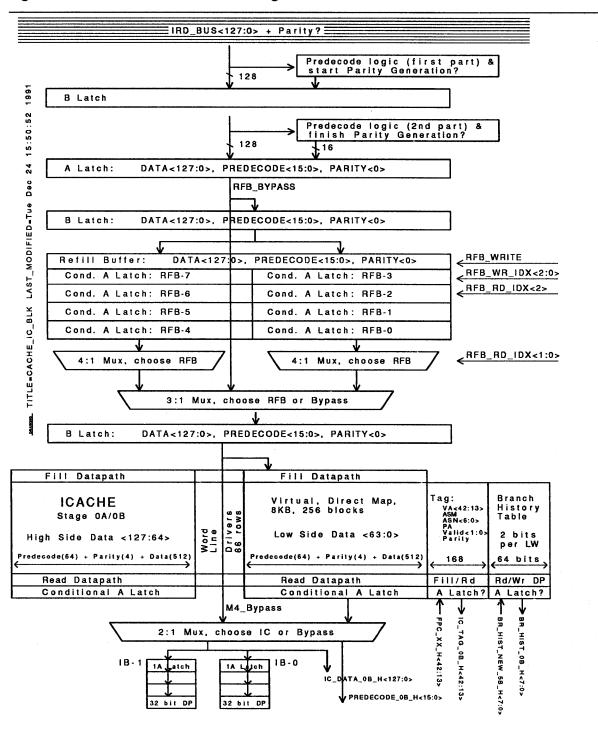

| 6.2       | ICACHE  |                      | BUFFER FUNCTIONAL DESCRIPTION                                                                        | 6–3        |

| 0.2       | 6.2.1   | Icache De            |                                                                                                      | 6-5        |

|           | 0.2.1   | 6.2.1.1              | Icache SROM Interface • 6–6                                                                          | U          |

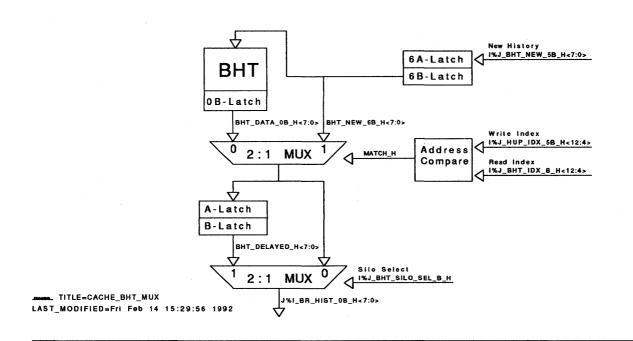

|           | 6.2.2   | +                    | story Table                                                                                          | 66         |

|           | 6.2.3   |                      | d Refill Buffer Initialization and Test                                                              | 6–7        |

|           | 6.2.4   |                      | Refill Buffer Transactions                                                                           | 6-7        |

|           | U.L.T   | 6.2.4.1<br>6.2.4.1.1 | Icache & Refill Buffer Fill Operations • 6–8<br>Writing the Icache and Branch History Table with the | 01         |

|           |         |                      | SROM • 6–9                                                                                           |            |

|           |         | 6.2.4.2              | Icache & Refill Buffer Read Operations • 6–9                                                         |            |

|           |         | 6.2.4.3              | Branch History Table Reads and Writes • 6-10                                                         |            |

|           | 6.2.5   | Icache Tes           | st Operations                                                                                        | 6–11       |

|           | 6.2.6   | Icache Sta           | ates Resulting in UNPREDICTABLE operation                                                            | 6–11       |

|           | 6.2.7   | Icache Re            | dundancy Logic                                                                                       | 6–12       |

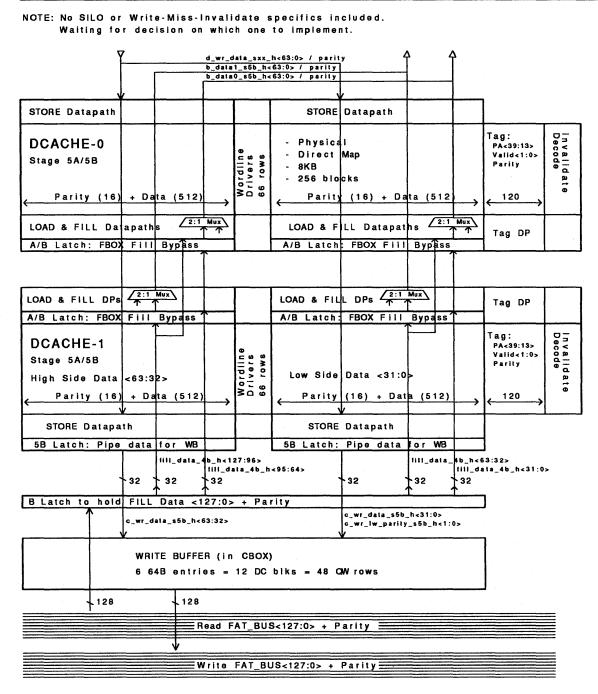

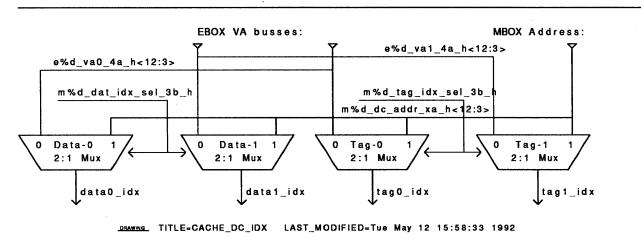

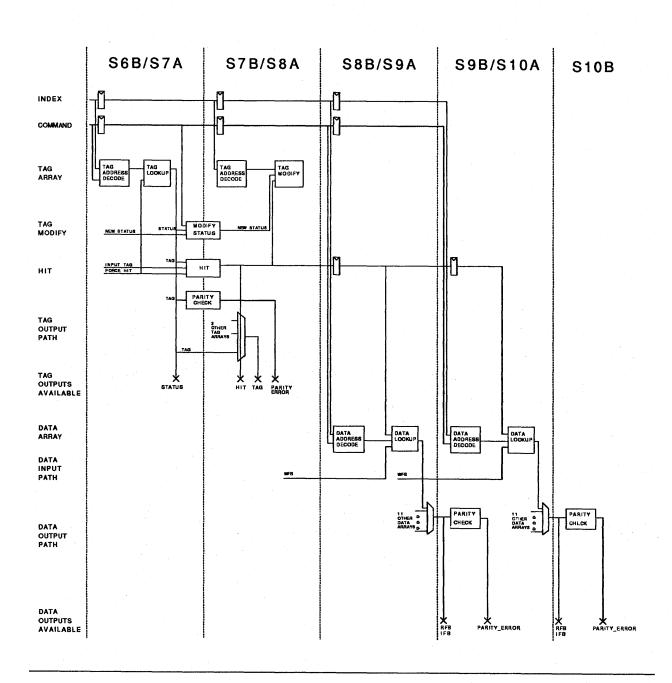

| 6.3       | DCACHE  | E FUNCTION/          | AL DESCRIPTION                                                                                       | 6–12       |

|           | 6.3.1   | Dcache In            | itialization and Test                                                                                | 6–15       |

|           | 6.3.2   | Dcache Tr            | ansactions                                                                                           | 6–16       |

|           |         | 6.3.2.1              | Dcache Load Operation • 6–17                                                                         |            |

|           |         | 6.3.2.2              | Dcache Store Operation • 6–17                                                                        |            |

|           |         | 6.3.2.3              | Dcache Fill Operation • 6–19                                                                         |            |

|           |         | 6.3.2.4              | Dcache Invalidate Operation • 6-20                                                                   |            |

|           |         | 6.3.2.5              | Dcache Test Operations • 6–20                                                                        |            |

|           | 6.3.3   | Dcache R             | edundancy Logic                                                                                      | 6–21       |

| 6.4       | SCACHE  | E FUNCTION/          | AL DESCRIPTION                                                                                       | 6–21       |

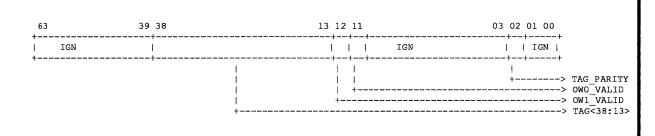

|           | 6.4.1   | SCache Ta            |                                                                                                      | 6–23       |

|           |         | 6.4.1.1              | Block Size • 6-23                                                                                    |            |

|           |         | 6.4.1.2              | Physical Organization • 6-23                                                                         |            |

|           |         | 6.4.1.3              | Force Hit/Force Miss Conditions • 6–25<br>Status Bits • 6–25                                         |            |

|           |         | 6.4.1.4<br>6.4.1.5   | Aborting an SCache Reference • 6–27                                                                  |            |

|           |         | 6.4.1.5<br>6.4.1.6   | Parity Checking • 6–27                                                                               |            |

|           | 6.4.2   | SCache D             |                                                                                                      | 6–27       |

|           | 6.4.3   | Pipeline             | ala Anay                                                                                             | 6-29       |

|           | 6.4.4   | Transactio           |                                                                                                      | 029<br>630 |

|           | 0.4.4   | 6.4.4.1              | SC READ • 6–30                                                                                       | 0-30       |

|           |         | 6.4.4.2              | SC WRITE • 6–31                                                                                      |            |

|           |         | 6.4.4.3              | SC_INVAL • 6–31                                                                                      |            |

|           |         | 6.4.4.4              | SC_READ_DIRTY • 6-32                                                                                 |            |

|           |         | 6.4.4.5              | SC_FILL • 6-32                                                                                       |            |

|           |         | 6.4.4.6              | SC_SET_SHARED • 6-33                                                                                 |            |

|           | 6.4.5   | SCache R             | edundancy Logic                                                                                      | 6–33       |

|           | 6.4.6   | Cbox Inte            |                                                                                                      | 6–34       |

|           | 6.4.7   | Ibox Inter           | face                                                                                                 | 6–35       |

|           |         |                      |                                                                                                      |            |

Xİ

## Contents

|                   | 6.5             | RESET AND INITIALIZATION                               | 6–35                         |

|-------------------|-----------------|--------------------------------------------------------|------------------------------|

|                   | 6.6             | ERROR HANDLING AND RECORDING                           | 635                          |

|                   | 6.7             | TEST ASPECTS6.7.1BiST6.7.2IPR access6.7.3Scan Chains   | 6–35<br>6–35<br>6–35<br>6–35 |

|                   | 6.8             | PERFORMANCE MONITORING FEATURES                        | 6-42                         |

|                   | 6. <del>9</del> | ISSUES<br>6.9.1 ICache<br>6.9.2 DCache<br>6.9.3 SCache | 6–42<br>6–42<br>6–43<br>6–43 |

|                   | 6.10            | REVISION HISTORY                                       | 643                          |

| CHAP <sup>-</sup> | TER 7           | THE CLOCKS                                             | 7-1                          |

|                   | 7.1             | OVERVIEW-BLOCK DIAGRAM                                 | 7-1                          |

|                   | 7.2             | FUNCTIONAL DESCRIPTION                                 | 7–3                          |

|                   | 7.3             | RESET AND INITIALIZATION                               | 7–3                          |

|                   | 7.4             | ERROR HANDLING AND RECORDING                           | 7–3                          |

|                   | 7.5             | TEST ASPECTS                                           | 7–3                          |

|                   | 7.6             | PERFORMANCE MONITORING FEATURES                        | 7–3                          |

|                   | 7.7             | ISSUES                                                 | 73                           |

|                   | 7.8             | REVISION HISTORY                                       | 7–3                          |

| CHAP              | TER 8           | TEST INTERNALS                                         | 8–1                          |

|                   | 8.1             | OVERVIEW                                               | 8-1                          |

|                   | 8.2             | THE TESTABILITY STRATEGY                               | 8–1                          |

|                   | 8.3             | TEST PORT                                              | 8-1                          |

|                   | 8.4             | PARALLEL DEBUG PORT                                    | 82                           |

|                   | 8.5             | SROM PORT                                              | 8–3                          |

|                   | 8.6             | IEEE 1149.1 (JTAG) PORT<br>8.6.1 Instruction Register  | 8–3<br>8–4                   |

|                   | 8.7             | MISCELLANEOUS TEST PINS<br>8.7.1 DISABLE_OUT_L         | 8–5<br>8–5                   |

|                   | 8.8             | CACHE BIST                                             | 85                           |

|                   | 8.9             | INTERNAL SCAN REGISTERS                                | 85                           |

|                   | 8.10            | INTERNAL LFSRS                                         | 86                           |

|                   | 8.11            | MISCELLANEOUS TESTABILITY FEATURES                     | 86                           |

|                   |                 |                                                        |                              |

| 8.12      | ISSUES                                          | 8–6  |

|-----------|-------------------------------------------------|------|

| 8.13      | REVISION HISTORY                                | 8-6  |

| CHAPTER 9 | THE INTERCONNECT                                | 9–1  |

| 9.1       | EV5CIP.H - THE ONLY GLOBAL INTERCONNECT .H FILE | 9–1  |

| 9.2       | REVISION HISTORY                                | 9–23 |

## FIGURES

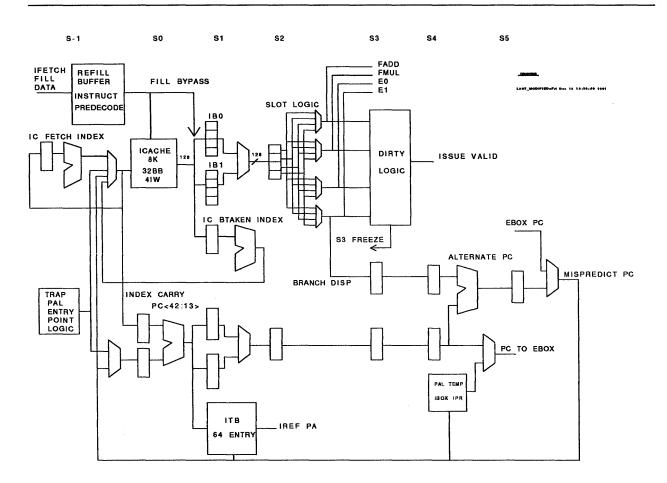

| 11   | Simple Block Diagram                                       | 1–2  |

|------|------------------------------------------------------------|------|

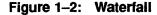

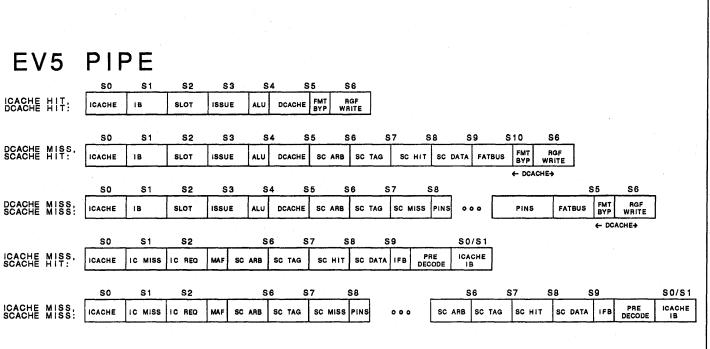

| 1-2  | Waterfall                                                  | 1–3  |

| 1–3  | Fetch Index Mux Selects for Trap, Exception, Replay(4A,6A) | 1–9  |

| 1-4  | IC_Index and RFB_Index on IC_Miss and RFB_Hit              | 1–9  |

| 15   | Ibox requests to MBOX                                      | 1–10 |

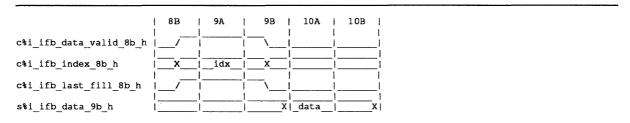

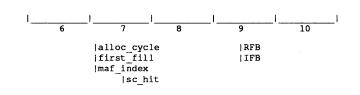

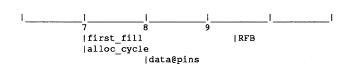

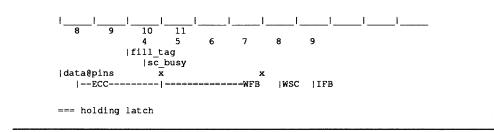

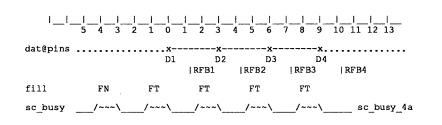

| 1–6  | Signal Protocall for Fills                                 | 1–11 |

| 17   | IFB Fills with RFB Hits                                    | 1–11 |

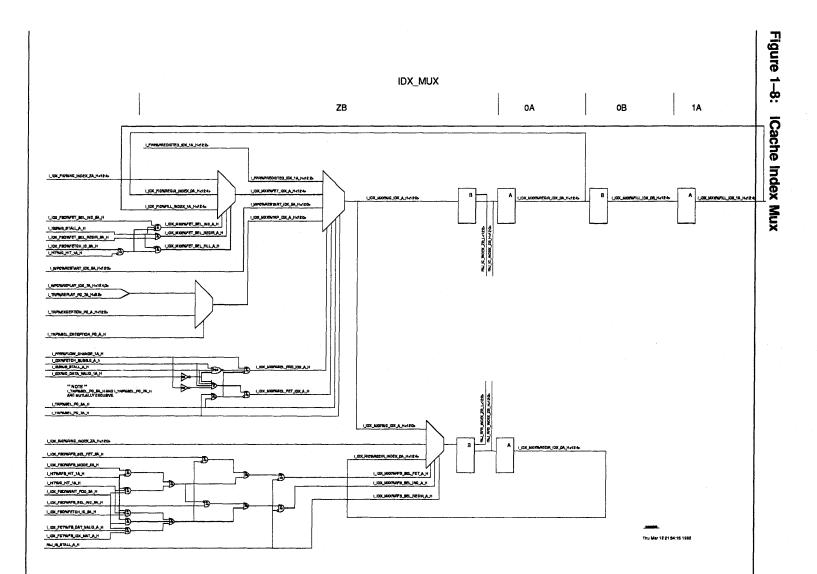

| 18   | ICache Index Mux                                           | 1–14 |

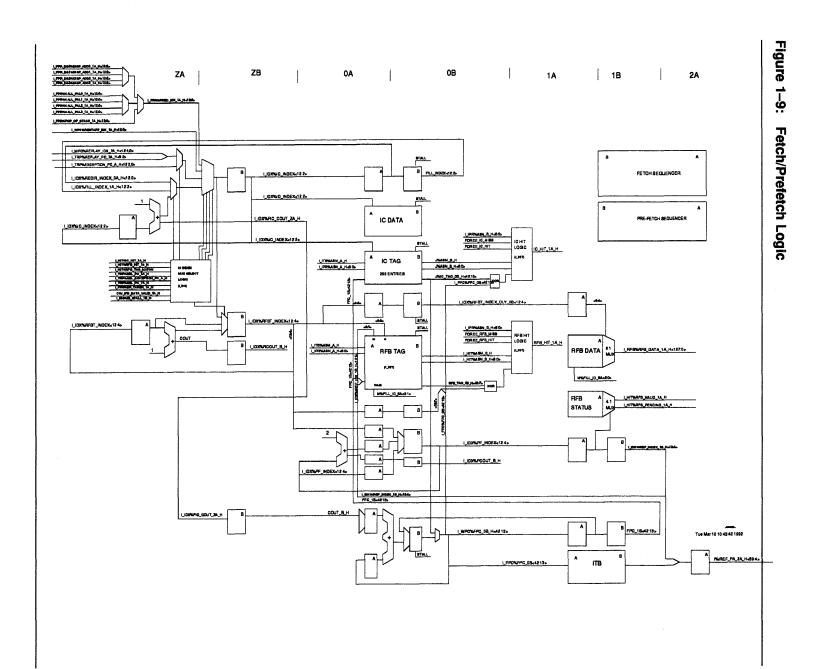

| 1–9  | Fetch/Prefetch Logic                                       | 1–15 |

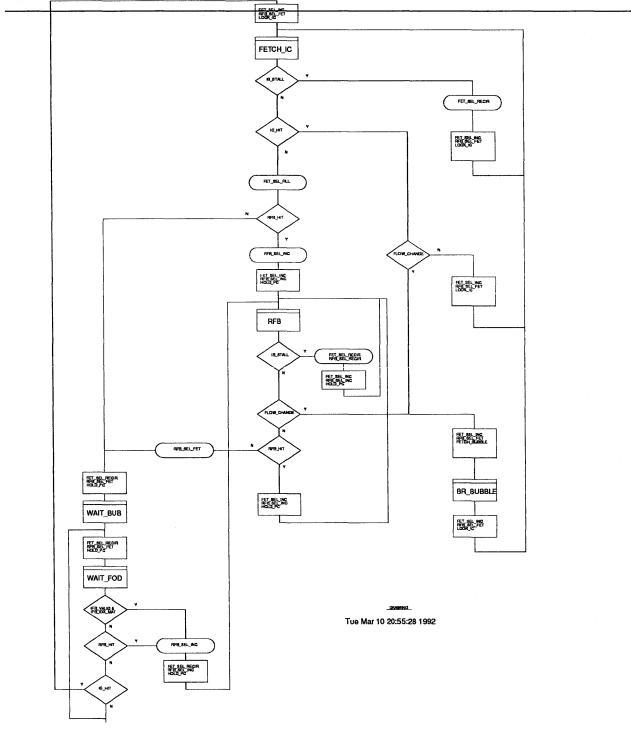

| 1–10 | IBOX FETCHER SEQUENCER                                     | 1–16 |

| 111  | IBOX HIT Logic                                             | 1–17 |

| 1–12 | Superpage                                                  | 1–18 |

| 1–13 | ITB Block                                                  | 1–21 |

| 1–14 | Branch History Logic                                       | 1–24 |

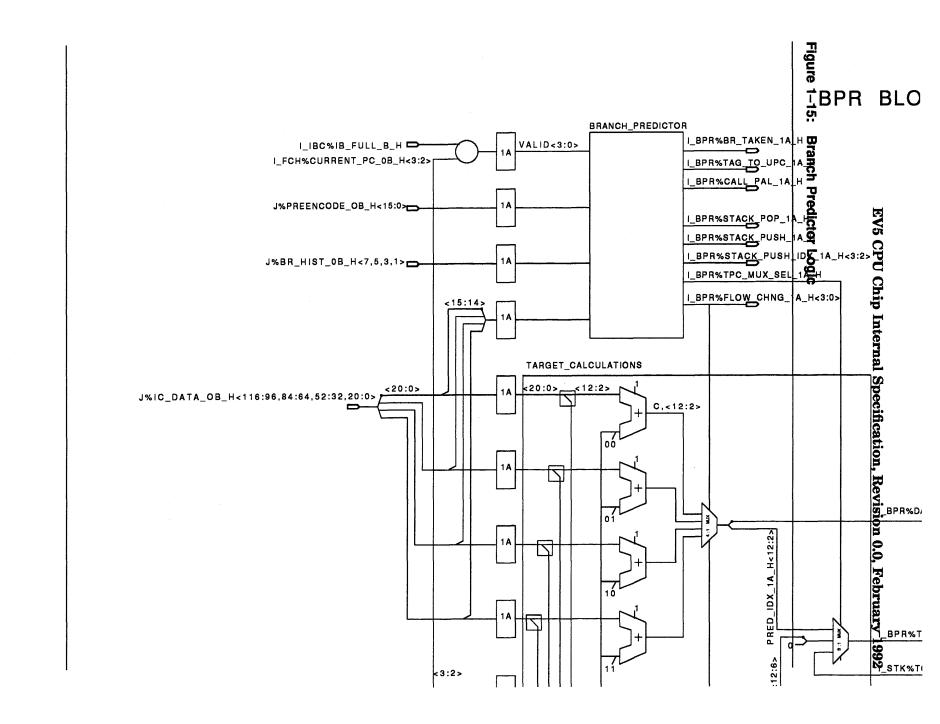

| 1–15 | Branch Predictor Logic                                     | 1–27 |

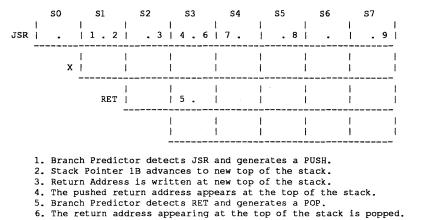

| 116  | Return Stack Operation                                     | 1–29 |

| 1–17 | Return Prediction Stack                                    | 1–30 |

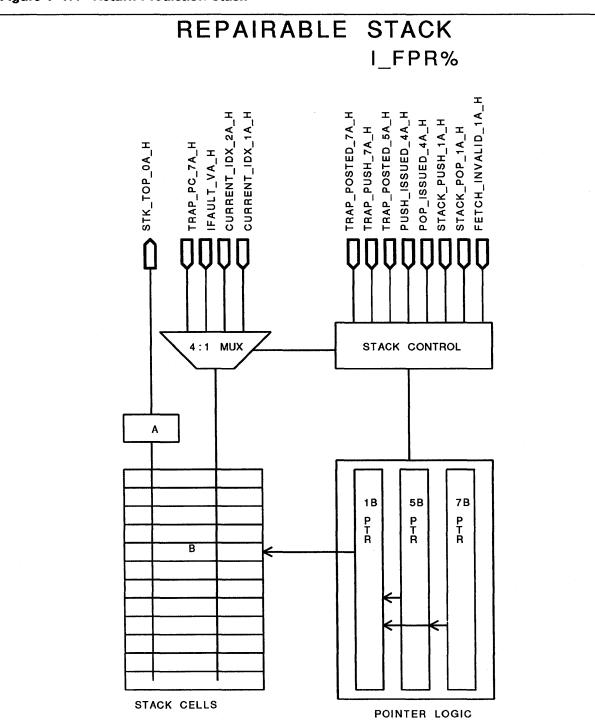

| 1–18 | Fetch PC                                                   | 1–33 |

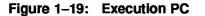

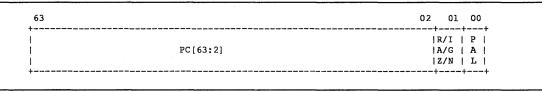

| 1–19 | Execution PC                                               | 1–36 |

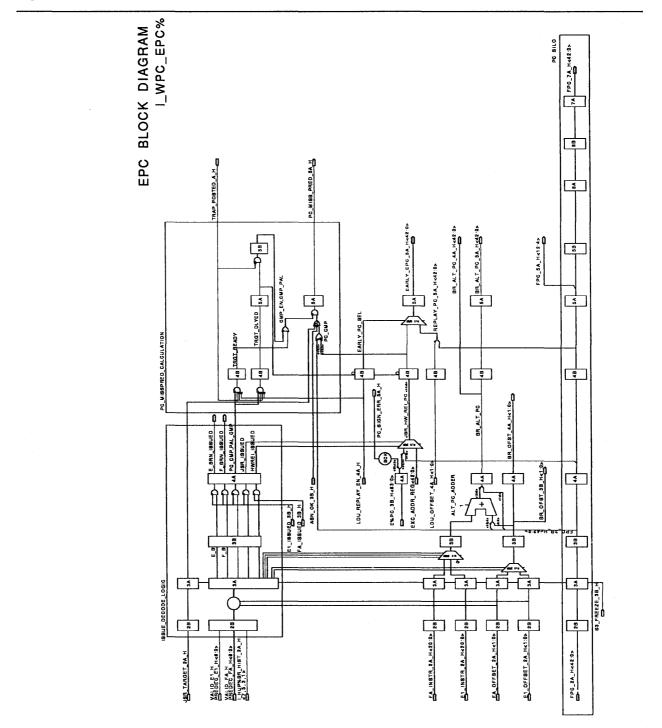

| 1–20 | IB Slot Logic                                              | 1–39 |

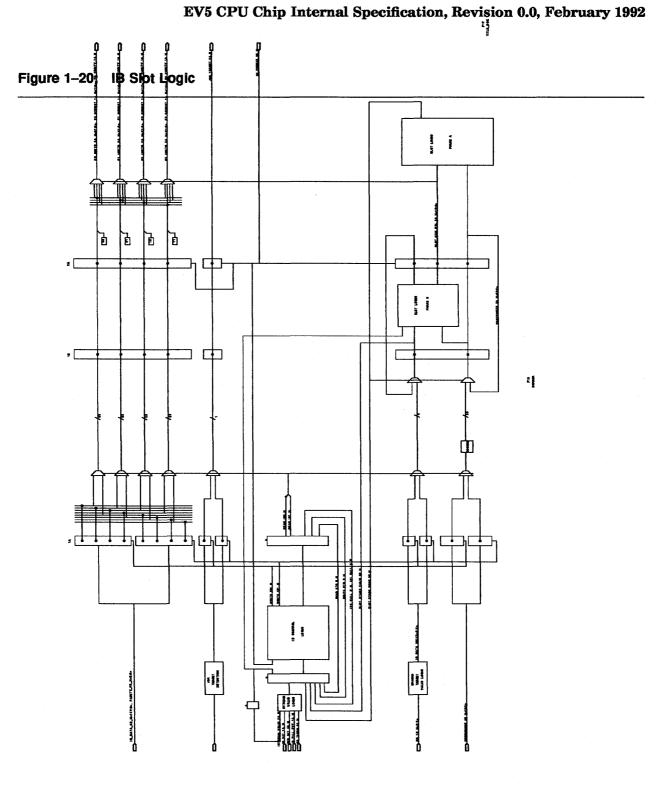

| 1-21 | Instruction Slotting                                       | 1-42 |

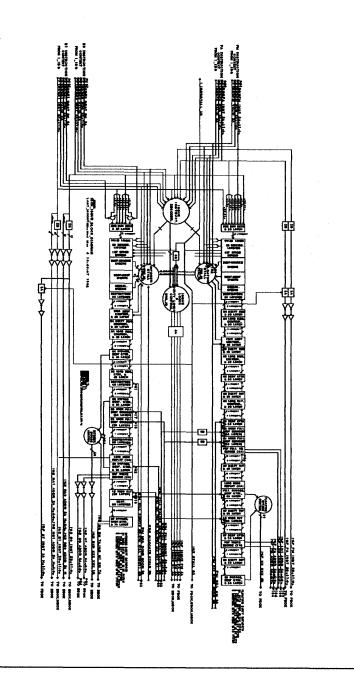

| 1–22 | Instruction Issue-Block Diagram                            | 1-49 |

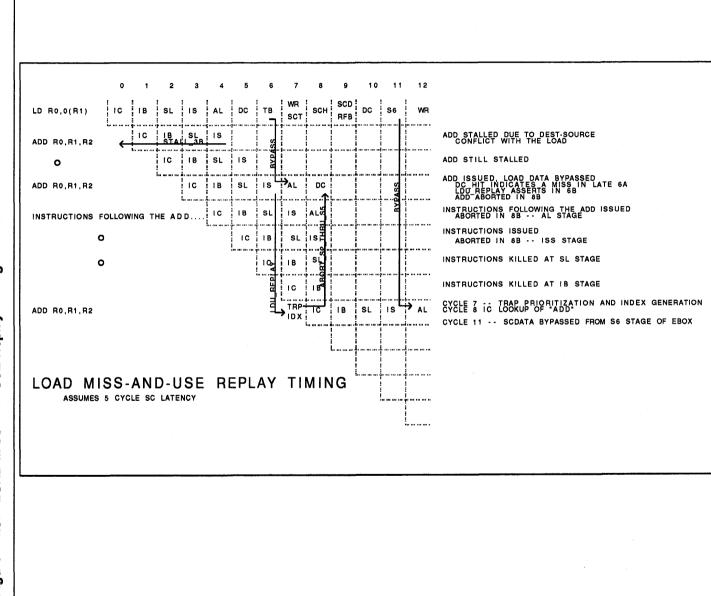

| 1–23 | LOAD MISS-AND-USE Replay Timing                            | 167  |

| 1–24 | Istream TB Tag, ITB_TAG                                    | 1–70 |

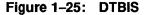

| 1–25 | Istream TB PTE Write Format, ITB_PTE                       | 1–70 |

| 126  | Istream TB PTE Read Format, ITB_PTE                        | 1–70 |

| 1–27 | Address Space Number Read/Write Format, ITB_ASN            | 1–71 |

| 1–28 | Istream TB PTE Temp Read Format, ITB_PTE_TEMP              | 1–71 |

| 1–29 | ITB_IS                                                     | 1–72 |

| 1–30 | IFAULT_VA_FORM in non NT mode                              | 1–72 |

| 1–31 | IFAULT_VA_FORM in NT mode                                  | 1–72 |

| 1–32 | IVPTBR in non NT mode                                      | 1–73 |

| 1–33 | IVPTBR in NT mode                                          | 1–73 |

| 1–34 | ICPERR_STAT Read format                                    | 1–73 |

## Contents

| 1–35        | EXC_ADDR Read/Write format                             | 1–74         |

|-------------|--------------------------------------------------------|--------------|

| 136         | Exception Summary register Read Format, EXC_SUM        | 1–74         |

| 137         | Exception Mask register Read Format, EXC_MASK          | 175          |

| 1–38        | PAL_BASE                                               | 1 <b>—76</b> |

| 1–39        | Processor Status, PS                                   | 1 <b>76</b>  |

| 1-40        | Ibox Control/Status Register ICSR                      | 1–76         |

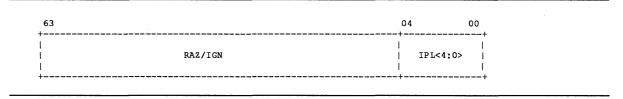

| 141         | Interrupt Priority Level Register, IPL                 | 1–77         |

| 1-42        | Interrupt Id Register, INTID                           | 1 <b>78</b>  |

| 1-43        | Asynchronous System Trap Request Register, ASTRR       | 1 <b>78</b>  |

| 1-44        | Asynchronous System Trap Enable Register, ASTER format | 1 <b>–78</b> |

| 1-45        | Software Interrupt Request Register, SIRR write format | 1 <b>–79</b> |

| 146         | Hardware Interrupt Clear Register, HWINT_CLR           | 1 <b>79</b>  |

| 1–47        | Interrupt Summary Register, ISR read format            | 1 <b>80</b>  |

| 148         | Serial line transmit Register, SL_XMIT                 | 181          |

| 149         | Serial line receive Register, SL_RCV                   | 181          |

| 1 <b>50</b> | PAL_ENTRY                                              | 1–85         |

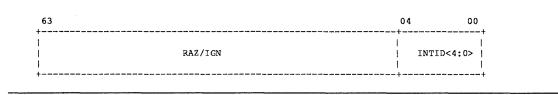

| 151         | IBOX TNTERRUPT LOGIC                                   | 1–88         |

| 2—1         | Ebox Block Diagram                                     | 2–4          |

| 2–2         | Summary of Adder Control                               | 2–7          |

| 2–3         | Conditional Move Conditions                            | 2–13         |

| 24          | Branch Conditions                                      | 2–27         |

| 3–1         | Fbox Interface Block Diagram                           | 3–2          |

| 3–2         | ADD Pipe Fraction Datapath Alignment/Format            | 3–7          |

| 3–3         | STAGE 1 INPUT BYPASS/FORMAT/RESOURCE TABLE             | <b>3–</b> 9  |

| 34          | Register File Data Format                              | 3–14         |

| 3–5         | Multipy Pipe Block Diagram                             | 3–16         |

| 36          | STAGE 1                                                | 3–19         |

| 3–7         | STAGE 2                                                | 3–20         |

| 38          | STAGE 3                                                | 3–22         |

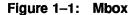

| 41          | Mbox                                                   | 4–2          |

| 42          | MBOX Pipe                                              | 4–3          |

| 43          | HW_LD instruction                                      | 4–12         |

| 44          | HW_ST instruction                                      | 4–13         |

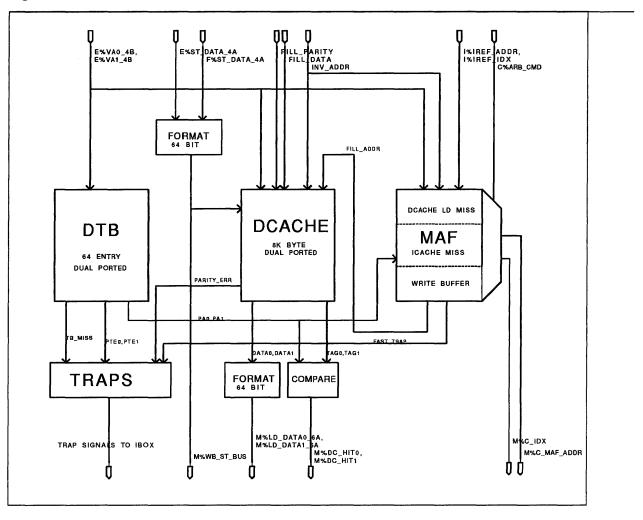

| 45          | DTB Bit Fields                                         | 4–15         |

| 46          | MAF Timing Definition                                  | 436          |

| 47          | Pending Queue Bit Fields                               | 440          |

| 48          | Dread Address Datapath                                 | 4-42         |

| 49          | Dread Register Formatting Bits                         | 442          |

| 4–10        | Dread Control Bits                                     | 4–43         |

| 4-11        | WB PA Datapath                                         | 4-45         |

| 4-12        | WB Control Bits                                        | 4–45         |

| 4–13        | IREF PA Datapath                                       | 4-47         |

| 4–14        | DTB_ASN                                                | 451          |

| 4–15           | DTB_CM                                                       | 452  |

|----------------|--------------------------------------------------------------|------|

| 4-16           | DTB_TAG, Dstream TB Tag                                      | 4–52 |

| 417            | DTB_PTE, Dstream TB PTE                                      | 4–53 |

| 4–18           | DTB_PTE_TEMP                                                 | 4-54 |

| 4–19           | MM_STAT, Dstream MM Fault Register                           | 4–54 |

| 420            | VA, Faulting VA Register                                     | 4–55 |

| 421            | VA_FORM, Formatted VA Register for NT_Mode=0                 | 455  |

| 4–22           | VA_FORM, Formatted VA Register, NT_Mode=1                    | 456  |

| 4–23           | MVPTBR                                                       | 4–56 |

| 424            | DC_PERR_STAT, Dcache Parity Error Status                     | 4–57 |

| 4–25           | DTBIS                                                        | 4–58 |

| 4–26           | MCSR, Mbox Control Register                                  | 4–58 |

| 4–27           | DC_MODE, Dcache Mode Register                                | 4–59 |

| 4–28           | MAF_MODE, MAF Mode Register                                  | 4–61 |

| 4–29           | ALT_MODE                                                     | 4–62 |

| 4–30           | CC, Cycle Counter Register                                   | 4–63 |

| 4–31           | CC_CTL, Cycle Counter Control Register                       | 4–63 |

| 4–32           | DC_TEST_CTL, Dcache Test TAG Control Register                | 4–64 |

| 4–33           | DC_TEST_TAG, Dcache Test TAG Register                        | 4–65 |

| 4–34           | DC_TEST_TAG_TEMP, Dcache Test TAG Temp Register              | 4–66 |

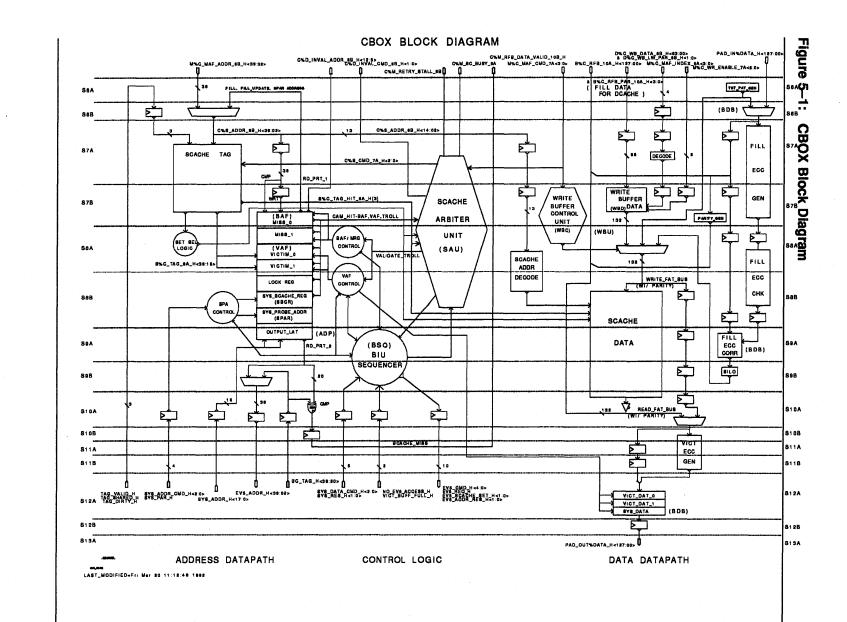

| 5-1            | CBOX Block Diagram                                           | 5–2  |

| 52             | SAU Pipe Stages                                              | 5–3  |

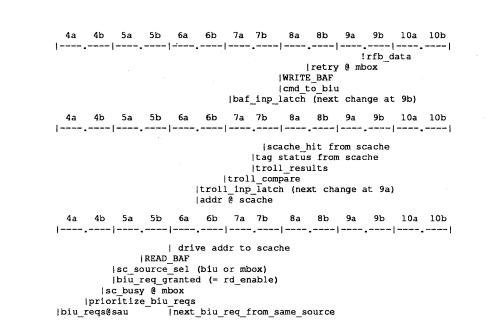

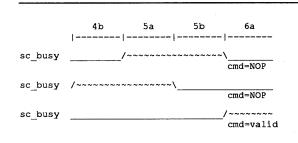

| 53             | SC_BUSY and Mbox Command Issue                               | 54   |

| 5-4            | Possible FIRST_FILL/LAST_FILL sequences from Cbox to Mbox    | 5-5  |

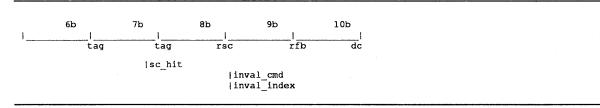

| 55             | Invalidate Timing                                            | 5–9  |

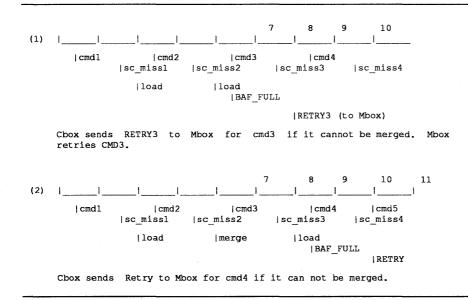

| 56             | Mbox Retry on Miss                                           | 5–11 |

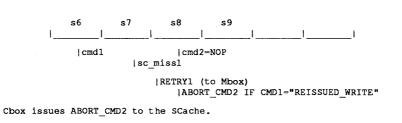

| 5–7            | Retry on BIU resources full                                  | 5–11 |

| 5–8            | Set Allocation Algorithm                                     | 5–14 |

| 5 <del>9</del> | Bcache index match                                           | 5–15 |

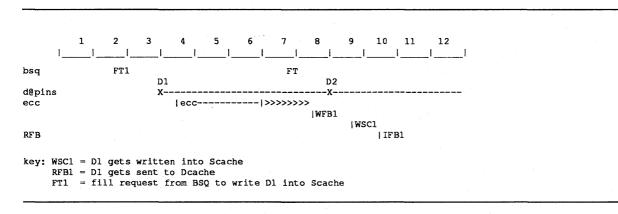

| 510            | I/DREAD hits in the SCache                                   | 5–16 |

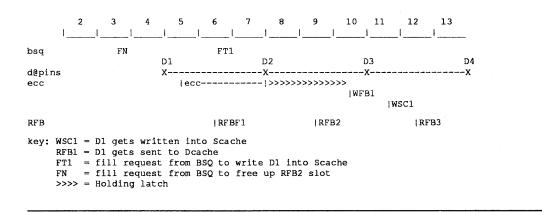

| 5-11           | DREAD fills from external memory (Non-error mode)            | 5–16 |

| 5–12           | IREAD fills from external memory                             | 5–16 |

| 5–13           | SCache Arbitration under fills                               | 5–17 |

| 5–14           | SCache Dstream (non-error mode) Fill Flow (3 cycle sysclock) | 5–17 |

| 5–15           | SCache Dstream (non-error mode) Fill Flow (4 cycle sysclock) | 5–17 |

| 5–16           | SCache Dstream (non-error mode) Fill Flow (5 cycle sysclock) | 5–18 |

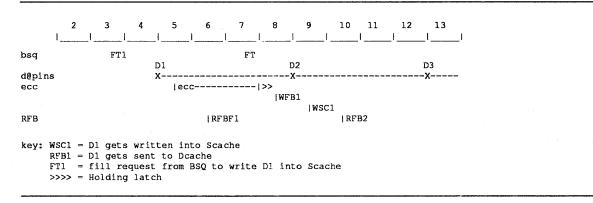

| 5–17           | SCache Dstream (Error mode) Fill Flow (5 cycle sysclock)     | 5–18 |

| 5-18           | SCache Istream (non-error mode) Fill Flow (5 cycle sysclock) | 5–19 |

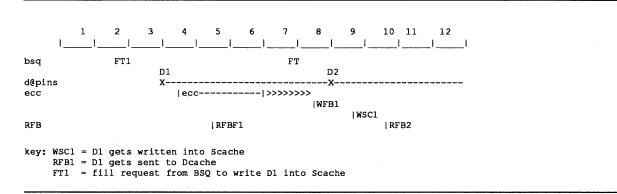

| 519            | Scache Read Hits Under Fills (3 cycle sysclock)              | 5–19 |

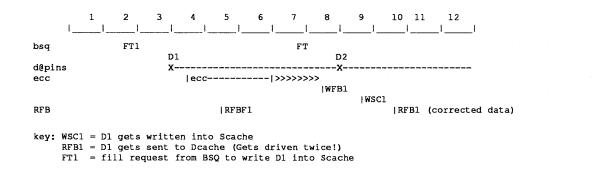

| 5–20           | Scache Write Hits Under Fills (3 cycle sysclock)             | 5–20 |

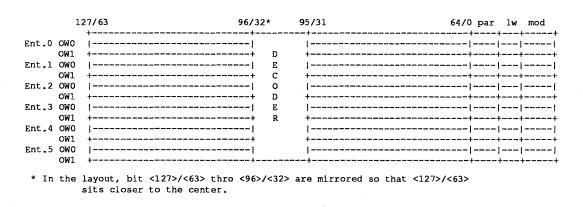

| 5–21           | Write Buffer Data Store                                      | 5–21 |

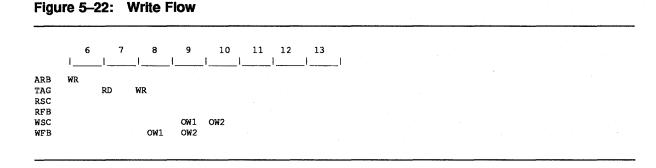

| 5–22           | Write Flow                                                   | 5–23 |

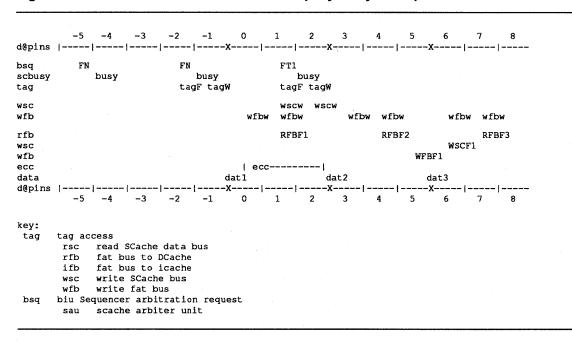

| 5–23           | Write buffer data write timing diagram                       | 5–23 |

| 5–24 | Write buffer data issue timing diagram                              | 5–24 |

|------|---------------------------------------------------------------------|------|

| 525  | Write hit private/dirty                                             | 5–28 |

| 526  | Write hit private/clean                                             | 5–29 |

| 5–27 | Write broadcast                                                     | 5–30 |

| 5–28 | Write miss                                                          | 5–32 |

| 529  | EV5 System Interface                                                | 5–35 |

| 5–30 | BAF full timing                                                     | 5–37 |

| 5-31 | Victim data flow                                                    | 5-41 |

| 532  | Data collection of first subblock in VAF                            | 5-42 |

| 533  | Data collection of second subblock in VAF                           | 5-42 |