## 21464 Internal Design Specification

Available Internally from: HTTP://segsrv.hlo.dec.com/arana

This document specifies the internal design for the Alpha microprocessor that is also known as EV8 and Araña.

**Revision/Update Information:**

Revision 1.1k, January, 2001

COMPAQ

Compaq Computer Corporation Shrewsbury, Massachusetts

#### January 2001

The information in this publication is subject to change without notice.

COMPAQ COMPUTER CORPORATION SHALL NOT BE LIABLE FOR TECHNICAL OR EDITORIAL ERRORS OR OMISSIONS CONTAINED HEREIN, NOR FOR INCIDENTAL OR CONSEQUENTIAL DAM-AGES RESULTING FROM THE FURNISHING, PERFORMANCE, OR USE OF THIS MATERIAL. THIS INFORMATION IS PROVIDED "AS IS" AND COMPAQ COMPUTER CORPORATION DISCLAIMS ANY WARRANTIES, EXPRESS, IMPLIED OR STATUTORY AND EXPRESSLY DISCLAIMS THE IMPLIED WAR-RANTIES OF MERCHANTABILITY, FITNESS FOR PARTICULAR PURPOSE, GOOD TITLE AND AGAINST INFRINGEMENT.

This publication contains information protected by copyright. No part of this publication may be photocopied or reproduced in any form without prior written consent from Compaq Computer Corporation.

© Compaq Computer Corporation 2001.

All rights reserved. Printed in the U.S.A. COMPAQ, the Compaq logo, the Digital logo, and VAX Registered in United States Patent and Trademark Office.

Pentium is a registered trademark of Intel Corporation.

Other product names mentioned herein may be trademarks and/or registered trademarks of their respective companies.

## Contents

## Preface

•

| 1 | 1 Introduction |                              |     |

|---|----------------|------------------------------|-----|

|   | 1.1            | Terminology and Conventions. | 1–1 |

| 2 | Arch           | itecture Overview            |     |

| 2.1      | New Features                                         | 2–1  |

|----------|------------------------------------------------------|------|

| 2.1.1    | Processor Features                                   | 2–1  |

| 2.1.2    | Memory Features                                      | 2–3  |

| 2.1.3    | Multiprocessor Features                              | 2–3  |

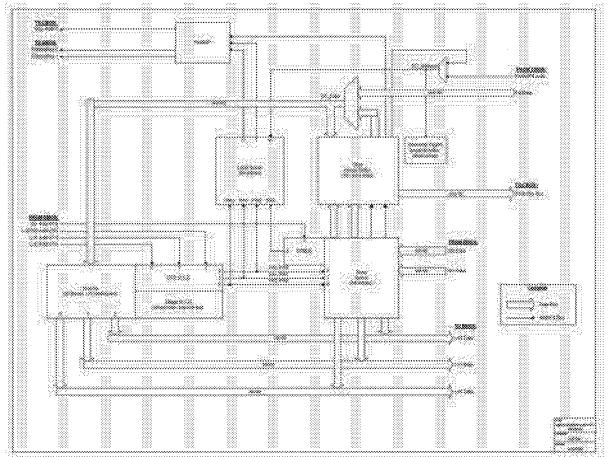

| 2.2      | Microarchitecture Diagram                            | 2–4  |

| 2.3      | Simultaneous Multithreading (SMT)                    | 2–5  |

| 2.4      | Instruction Unit                                     | 2–7  |

| 2.4.1    | Instruction Fetch Unit — the Ibox                    | 2–7  |

| 2.4.2    | Dependency Mapper Unit — the Pbox                    | 28   |

| 2.4.3    | Instruction Issue and Retire Unit — the Qbox         | 2–9  |

| 2.5      | Execution Unit                                       | 2-11 |

| 2.5.1    | Register File                                        | 2–11 |

| 2.5.2    | Integer Instruction Execution Unit — the Ebox        | 2-11 |

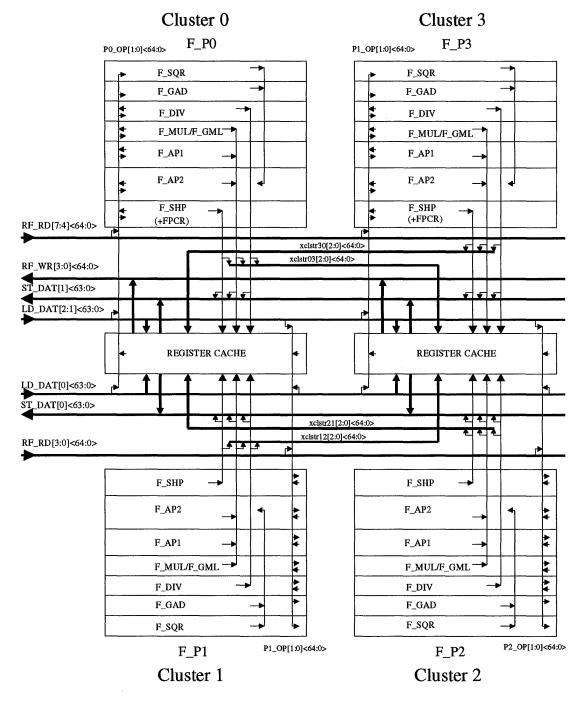

| 2.5.3    | Floating-Point Instruction Execution Unit — the Fbox | 2–14 |

| 2.5.3.1  | Functional Units                                     | 2–15 |

| 2.6      | Memory Controller Unit — the Mbox                    | 2-16 |

| 2.7      | External Interface                                   | 2-17 |

| 2.7.1    | Scache Controller — the Cbox.                        | 2-17 |

| 2.7.2    | Router — the Rbox                                    | 2-18 |

| 2.7.3    | Rambus Interface — the Zbox                          | 2-18 |

| 2.7.4    | Cache Coherency Protocol                             | 2-18 |

| 2.7.4.1  | Introduction to the Protocol.                        | 2-18 |

| 2.7.4.2  | Structures that Maintain the Cache Coherence         | 2-19 |

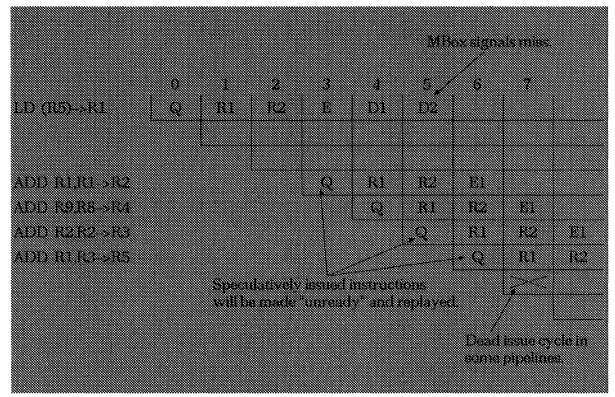

| 2.8      | Pipeline Organization                                | 2-19 |

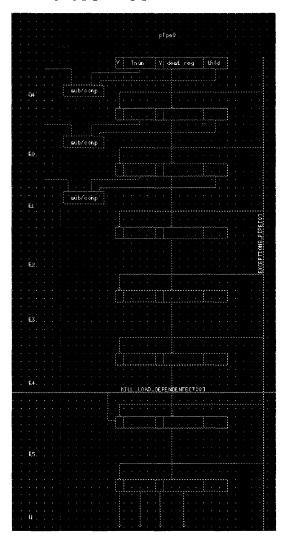

| 2.8.1    | Pipeline Diagram                                     | 2-20 |

| 2.8.2    | Conversion Between Negative Integer and Alphabet     | 2-21 |

| 2.8.3    | Basic Pipeline Stage Conversion Equations            | 2-21 |

| 2.8.4    | Conversion Table.                                    | 2-21 |

| 2.0.4    | Instruction Execution Pipelines and Latency.         | 2-22 |

| 2.10     | Instruction Issue and Retire Rules                   | 2-27 |

| 2.10.1   |                                                      | 2-27 |

| 2.10.1   |                                                      | 2-27 |

| 2.10.1.1 | Retirement Rules                                     | 2-29 |

| 2.10.2   |                                                      | 2-29 |

| 2.10.2.1 | Implementation-Specific Architecture Features.       | 2-29 |

| 2.11     | New Instructions.                                    | 2-29 |

| 2.11.1   |                                                      | 2-29 |

|          | ······································               | 2-29 |

| 2.11.1.2 | · · · · · · · · · · · · · · · · · · ·                |      |

| 2.11.2   | CMOV Instruction Processing                          | 2-32 |

| 2.11.2.1 |                                                      | 2-32 |

| 2.11.2.2 |                                                      | 2-33 |

| 2.11.2.3 |                                                      | 2-33 |

| 2.11.2.4 | Native FCMOV                                         | 2–34 |

| 2.11.2.5 | Implementation                                      | 2–34 |

|----------|-----------------------------------------------------|------|

| 2.11.2.5 | .1 Native CMOV                                      | 2–34 |

| 2.11.2.5 | .2 Legacy CMOV                                      | 2–34 |

| 2.11.3   | Mapper Alignment                                    | 2–35 |

| 2.12     | Interrupts                                          | 2–35 |

| 2.12.1   | IPR Access Mechanism                                | 2-36 |

| 2.12.1.1 |                                                     |      |

| 2.13     | AMASK and IMPLVER Instruction Processing and Values | 2–36 |

| 2.14     | Performance Monitoring                              | 2–36 |

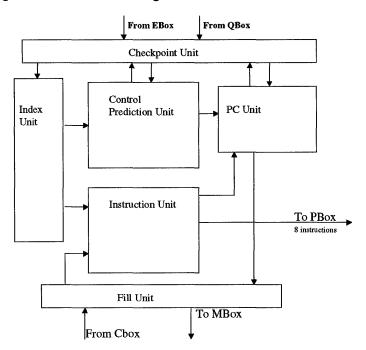

#### 3 Instruction Fetch Unit — the Ibox

| 3.1 Features                                                                                                      | -1 |

|-------------------------------------------------------------------------------------------------------------------|----|

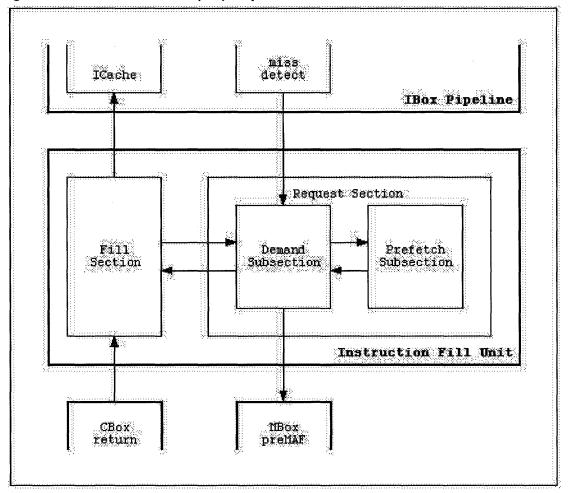

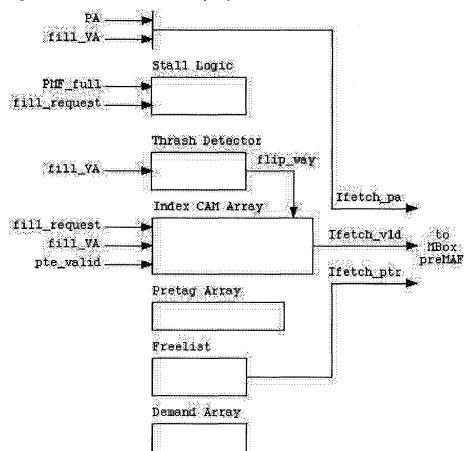

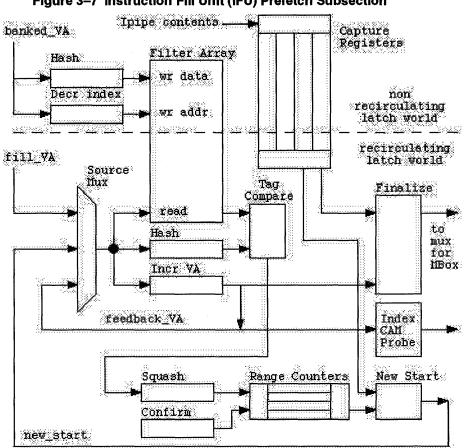

| 3.2 Major Sections                                                                                                | -2 |

| 3.3 Forward Path Pipeline 3                                                                                       | -4 |

|                                                                                                                   | -4 |

| 3.4.1 Fetch TPU Chooser                                                                                           | -4 |

| 3.4.2 Line Predictor                                                                                              | -5 |

|                                                                                                                   | -7 |

|                                                                                                                   | -7 |

|                                                                                                                   | 7  |

|                                                                                                                   | -8 |

|                                                                                                                   | -9 |

|                                                                                                                   | -9 |

| 3.4.4 Thread Training Latches                                                                                     | 10 |

| 3.5 Instruction Processing Unit                                                                                   |    |

| 3.5.1 Icache Data Array 3–                                                                                        |    |

| 3.5.2 Icache Tag Array 3–                                                                                         |    |

| 3.5.3 Store-Sets Based Memory Dependence Predictor                                                                |    |

| 3.5.4 Collapsing Buffer 3–                                                                                        |    |

| 3.5.4.1 Instruction Buffer                                                                                        |    |

| 3.5.4.1.1 Data Path 3–                                                                                            |    |

| 3.5.4.1.2 Control Path                                                                                            |    |

| 3.5.4.2 Collapser                                                                                                 |    |

| 3.5.4.2 Collapsel                                                                                                 |    |

| 3.5.4.2.2 Start/End Buffer                                                                                        |    |

| 3.5.4.2.3 New Start Calculation                                                                                   |    |

| 3.5.4.2.4 CMov                                                                                                    |    |

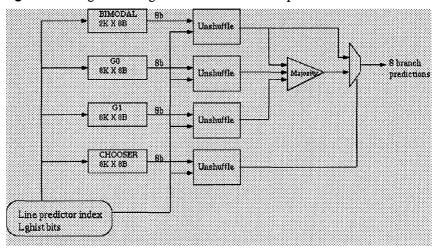

| 3.6         Control Flow Prediction Unit         3-           3.6         Control Flow Prediction Unit         3- |    |

|                                                                                                                   |    |

|                                                                                                                   |    |

| 3.6.1.1 Branch Prediction Components                                                                              |    |

| 3.6.1.1.1 Branch History (LGHist)                                                                                 |    |

| 3.6.1.1.2 Prediction Tables                                                                                       |    |

| 3.6.1.1.3 Bank Selection                                                                                          |    |

| 3.6.1.1.4 Unshuffle Network                                                                                       |    |

| 3.6.1.1.5 Backend logic and checkpoint information                                                                |    |

| 3.6.1.2 Branch Training 3–                                                                                        |    |

| 3.6.1.2.1 Predictor Training                                                                                      |    |

| 3.6.1.2.2 Hysteresis Training                                                                                     |    |

| 3.6.1.3 PAL mode                                                                                                  |    |

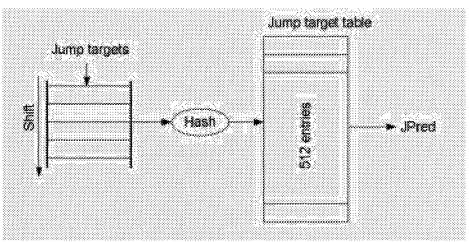

| 3.6.2 Jump Target Predictor 3–                                                                                    |    |

| 3.6.3 Return Address Stack 3–                                                                                     |    |

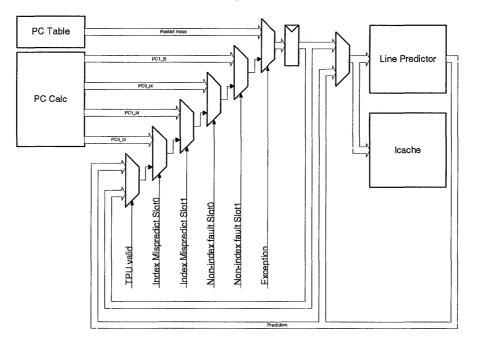

| 3.7 PC Unit                                                                                                       |    |

| 3.7.1 PC Calculation                                                                                              | 28 |

| 3.7.2 PC Compare                                                                                                  |    |

| 3.7.2.1 Index Mispredicts 3–                                                                                      | 33 |

| 3.7.2.2 Icache Hit Determination                                                                                  | 33 |

| 3.7.2.3 Icache Access Violation:                                | 3-34         |

|-----------------------------------------------------------------|--------------|

|                                                                 | 3-35         |

|                                                                 | 3–35<br>3–35 |

|                                                                 | 3-35<br>3-36 |

|                                                                 | 3-30<br>3-36 |

|                                                                 | 3-30<br>3-37 |

|                                                                 | 3-37<br>3-40 |

|                                                                 |              |

|                                                                 | 3-40         |

|                                                                 | 3-40         |

|                                                                 | 3-41         |

|                                                                 | 3–41         |

|                                                                 | 3-41         |

|                                                                 | 3–42         |

|                                                                 | 3-43         |

|                                                                 | 3-44         |

|                                                                 | 3–44         |

|                                                                 | 3–45         |

| <b>y</b>                                                        | 3–45         |

|                                                                 | 3–46         |

|                                                                 | 3–47         |

|                                                                 | 3–47         |

|                                                                 | 3–47         |

| 3.8.2.2.5 Prefetch cases: badpath indication during prefetching | 3–48         |

| 3.8.2.3 Fill                                                    | 3-48         |

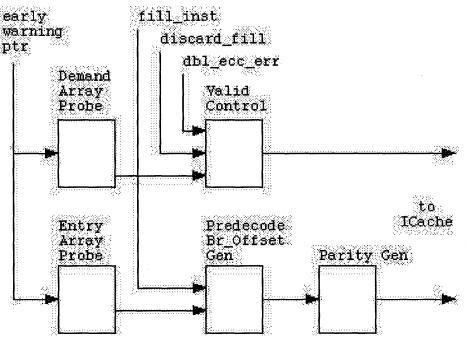

| 3.8.2.3.1 Predecode Bit Generation                              | 3–49         |

|                                                                 | 3–53         |

|                                                                 | 3–55         |

|                                                                 | 3-55         |

|                                                                 | 3–56         |

|                                                                 | 3–59         |

| ·                                                               | 3–60         |

|                                                                 | 3-61         |

|                                                                 | 3-62         |

| 5                                                               | 3-62         |

|                                                                 | 3-62         |

|                                                                 | 3-62         |

|                                                                 | 3-62         |

|                                                                 | 3-62         |

|                                                                 | 3-62         |

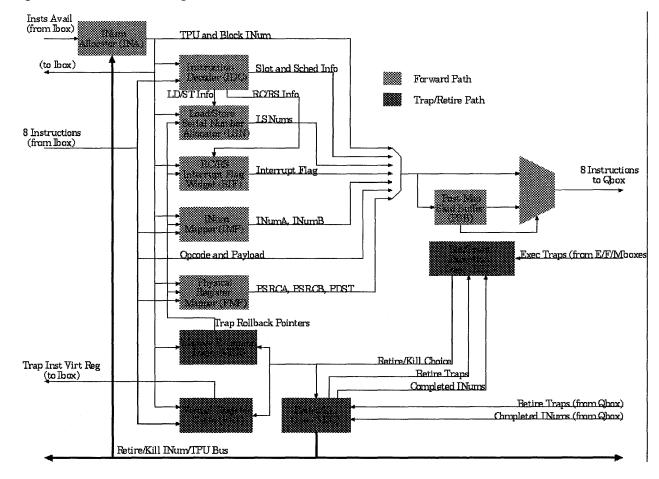

## 4 Dependency Mapper Unit — the Pbox

| 4.1     | Dependency Analysis: General Concepts | 4–2  |

|---------|---------------------------------------|------|

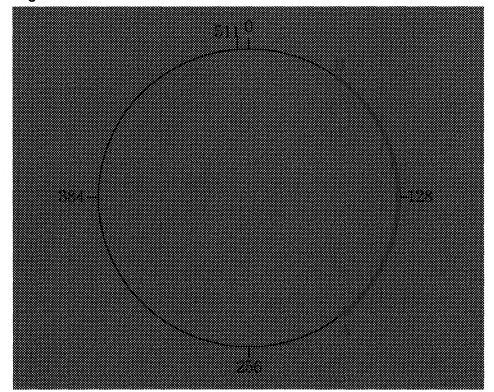

| 4.2     | INum Space                            | 44   |

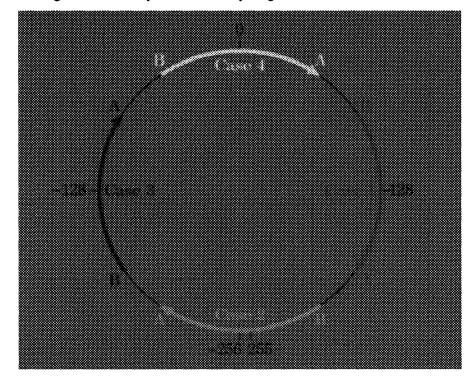

| 4.2.1   | INum Age Comparison                   | 4-5  |

| 4.3     | Component Details                     | 4-7  |

| 4.3.1   | INum Mapper (IMP)                     | 4–7  |

| 4.3.1.1 | Design considerations                 | 4–7  |

| 4.3.1.2 | Design Architecture                   | 4–7  |

| 4.3.1.3 | Map Predecode Bits from the Ibox      | 4–9  |

| 4.3.2   | Physical Register Map (PMP)           | 4–10 |

| 4.3.2.1 | Design Considerations                 | 4–10 |

| 4.3.2.2 | Design Architecture                   | 4-11 |

| 4.3.3   | INum Allocator (INA)                  | 4–13 |

| 4.3.3.1 | Design Considerations                 | 4–13 |

| 4.3.3.2 | Design Architecture                   | 4–13 |

| 4.3.3.3 | Map Thread Chooser (MTC)              | 4–14 |

| 4.3.4    | Mapper Exception Logic (MEX)             | 4–15 |

|----------|------------------------------------------|------|

| 4.3.4.1  | Design Considerations                    | 415  |

| 4.3.4.2  | Design Architecture                      | 4–15 |

| 4.3.5    | Memory Queue Allocation Unit (MQA)       | 4–15 |

| 4.3.5.1  | Allocation                               | 4–15 |

| 4.3.5.2  | Background and Terminology               | 4–16 |

| 4.3.5.3  | Basic Allocation Loop                    | 4–16 |

| 4.3.5.4  | Reset                                    | 4-17 |

| 4.3.5.5  | Deallocation                             | 4-17 |

| 4.3.5.6  | Kills                                    | 4–17 |

| 4.3.5.7  | Retires                                  | 4–18 |

| 4.3.5.8  | Quiesce                                  | 4–19 |

| 4.3.5.9  | Merge Buffer Purging                     | 4–19 |

| 4.3.6    | Instruction Decoder (IDC)                | 4–19 |

| 4.3.6.1  | Design Considerations                    | 4–19 |

| 4.3.6.2  | Design Architecture                      | 4–19 |

| 4.3.7    | Load/Store Serial Number Allocator (LSN) | 4–20 |

| 4.3.7.1  | Design Considerations                    | 4–20 |

| 4.3.7.2  | Design Architecture                      | 4–20 |

| 4.3.8    | Post-Map Skid Buffer (PSB)               | 4–22 |

| 4.3.8.1  | Design Considerations                    | 4–22 |

| 4.3.8.2  | Design Architecture                      | 4–22 |

| 4.3.9    | RC/RS Interrupt Flag Widget (RIF)        | 4–23 |

| 4.3.9.1  | Design Considerations                    | 4–23 |

| 4.3.9.2  | Design Architecture                      | 4–23 |

| 4.3.10   | Bid/Grant Exception Logic (BEL)          | 4–24 |

| 4.3.10.1 | Design Considerations                    | 4–24 |

| 4.3.10.2 | Design Architecture                      | 4–24 |

| 4.3.11   | Retire/Kill Unit (RKU)                   | 4–25 |

| 4.3.11.1 | Design Considerations                    | 4–25 |

| 4.3.11.2 | Design Architecture                      | 4–25 |

#### 5 Instruction Issue and Retire Unit — the Qbox

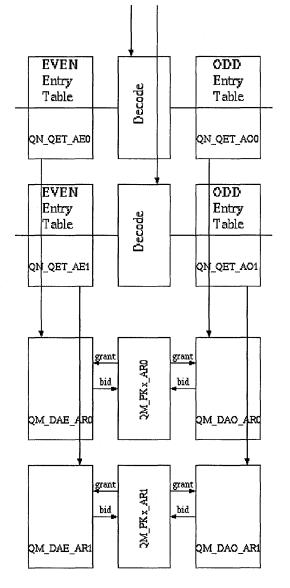

| 5.1      | Scheduling Decisions — General Concepts              | 5–2  |

|----------|------------------------------------------------------|------|

| 5.2      | Component Details                                    | 5–3  |

| 5.2.1    | Instruction Queue (IQ) Generalities                  | 5–3  |

| 5.2.1.1  | Design Considerations                                | 5–3  |

| 5.2.1.2  | Design Architecture                                  | 5–3  |

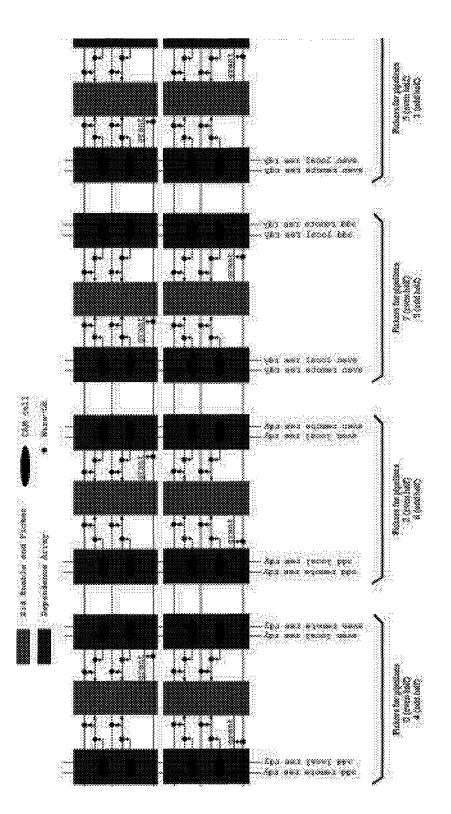

| 5.2.2    | Queue Entry Table (QET) and Reallocation Logic (RAL) | 5–9  |

| 5.2.2.1  | Design Considerations                                | 5–9  |

| 5.2.2.2  | Design Architecture                                  | 5–9  |

| 5.2.2.2. |                                                      | 5–9  |

| 5.2.2.3  | Physical Organization                                | 5–11 |

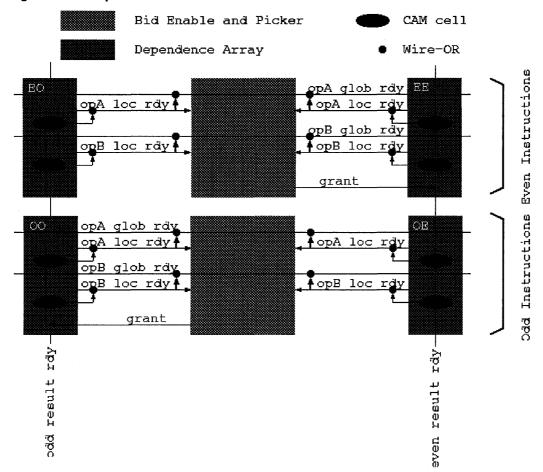

| 5.2.3    | Dependency Arrays (DAs)                              | 5–12 |

| 5.2.3.1  | Design Considerations                                | 5–12 |

| 5.2.3.2  | Design Architecture                                  | 5–12 |

| 5.2.3.3  | Physical Organization                                | 5–13 |

| 5.2.4    | Picker Arrays (PKs)                                  | 5–13 |

| 5.2.4.1  | Design Considerations                                | 5–13 |

| 5.2.4.2  | Design Architecture                                  | 5–13 |

| 5.2.5    | Bid Enable Logic (BID)                               | 5–14 |

| 5.2.5.1  | Design Considerations                                | 5–14 |

| 5.2.5.2  | Design Architecture                                  | 5–14 |

| 5.2.5.3  | Physical Organization                                | 5–14 |

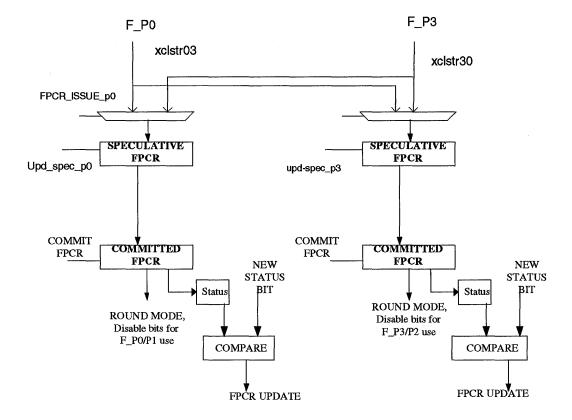

| 5.2.6    | FPCR Control Unit (FCR).                             | 5–14 |

| 5.2.7    | Profile-Me Data Collection (PRM)                     | 5–14 |

| 5.2.8      | Source Register Number Arrays (SRNs)      | 5–15 |

|------------|-------------------------------------------|------|

| 5.2.8.1    | Design Considerations                     | 5–15 |

| 5.2.8.2    | Design Architecture                       | 5–15 |

| 5.2.9      | Destination Register Number Array (DRN)   | 5–15 |

| 5.2.9.1    | Design Considerations                     | 5–15 |

| 5.2.9.2    | Design Architecture                       | 5–15 |

| 5.2.10     | Load/Store Number High-Water Marker (HWM) | 5–16 |

| 5.2.10.1   | Design Considerations                     | 5–16 |

| 5.2.10.2   | Design Architecture                       | 5–16 |

| 5.2.11     | Load/Poison Re-Arm Widget (LPR)           | 5–18 |

| 5.2.11.1   | Design Considerations                     | 5–18 |

| 5.2.11.2   | Design Architecture                       | 519  |

| 5.2.12     | Post-Issue Logic (PIL)                    | 5-20 |

| 5.2.12.1   | Design Considerations                     | 5-20 |

| 5.2.12.2   | Design Architecture                       | 5–20 |

| 5.2.13     | Oldest CBR Selector (OCS)                 | 5–21 |

| 5.2.13.1   | Design Considerations                     | 5–21 |

| 5.2.13.2   | Design Architecture                       | 5–21 |

| 5.2.14     | Queue Chunk Allocator/Deallocator (ALC)   | 5–22 |

| 5.2.14.1   | Design Considerations                     | 5–22 |

| 5.2.14.2   | Design Architecture                       | 5–22 |

| 5.2.15     | in-Flight Table (IFx)                     | 5–23 |

| 5.2.15.1   | Design Considerations                     | 5–23 |

| 5.2.15.2   | Design Architecture                       | 5–23 |

| 5.2.16     | Completion Unit (CMP)                     | 5–24 |

| 5.2.16.1   | Design Considerations                     | 5–24 |

| 5.2.16.2   | Design Architecture                       | 5–25 |

| 5.2.16.2.1 | Completion                                | 5–25 |

| 5.2.16.2.2 | Kills                                     | 5–25 |

| 5.2.16.2.3 | Retirement                                | 5–25 |

| 5.2.16.2.4 | Mbox Interface                            | 5–26 |

| 5.2.17     | Payload Array (PAY)                       | 5–26 |

| 5.2.17.1   | Design Considerations                     | 5–26 |

| 5.2.17.2   | Design Architecture                       | 5–26 |

| 5.2.18     | Exception Kill Logic (EKC)                | 5–27 |

| 5.2.18.1   | Design Considerations                     | 5–27 |

| 5.2.18.2   | Design Architecture                       | 5–27 |

## 6 Integer Execution Unit — the Ebox

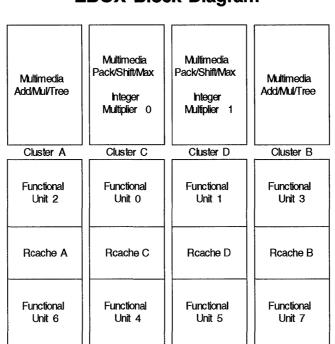

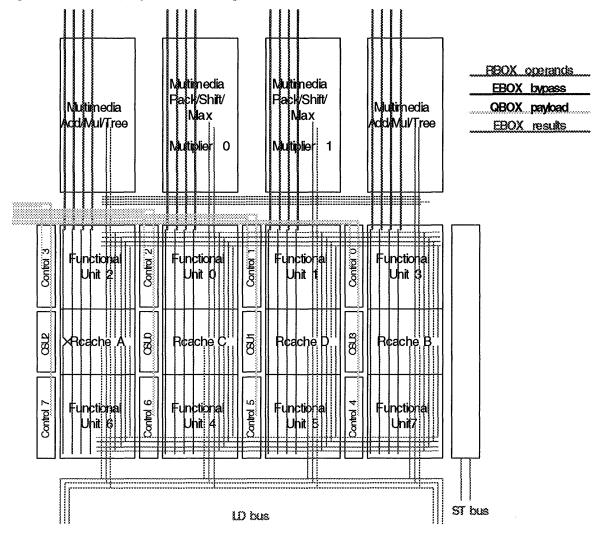

| 6.1   | Major Components                | 6–1  |

|-------|---------------------------------|------|

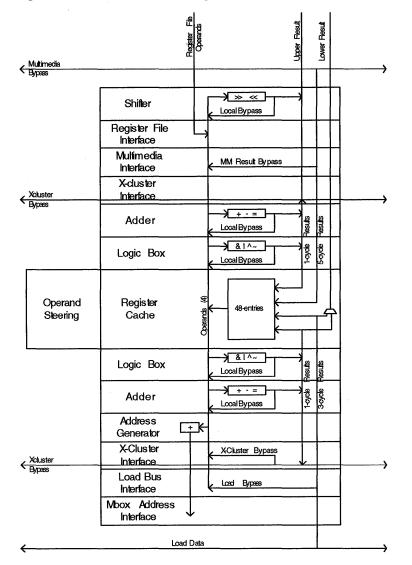

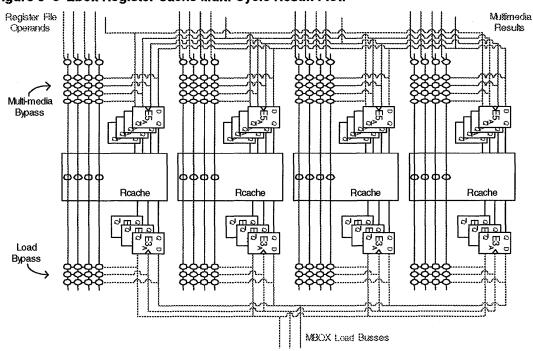

| 6.1.1 | Datapath                        | 6–2  |

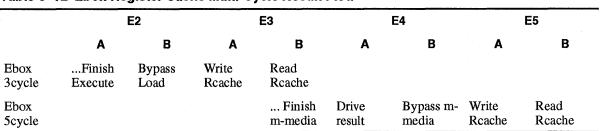

| 6.1.2 | Timing                          | 6–3  |

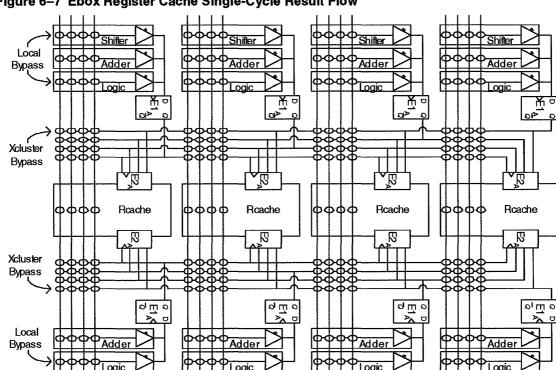

| 6.2   | Integer Clusters                | 6–4  |

| 6.2.1 | Adder                           | 6–6  |

| 6.2.2 | Shifter                         | 6–7  |

| 6.2.3 | Logic Box                       | 6–8  |

| 6.2.4 | Register File Operand Interface | 68   |

| 6.2.5 | Virtual Address Generator       | 6–9  |

| 6.2.6 | Load Data Interface             | 6–10 |

| 6.2.7 | Multimedia Interface            | 6–10 |

| 6.2.8 | Global Control                  | 6–11 |

| 6.2.9 | Store Data Interface            | 6–11 |

| 6.3   | Operand Steering                | 6–12 |

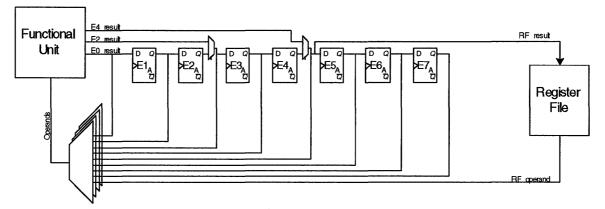

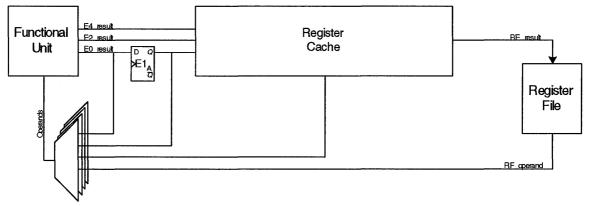

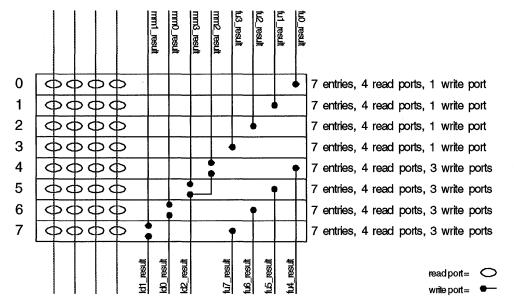

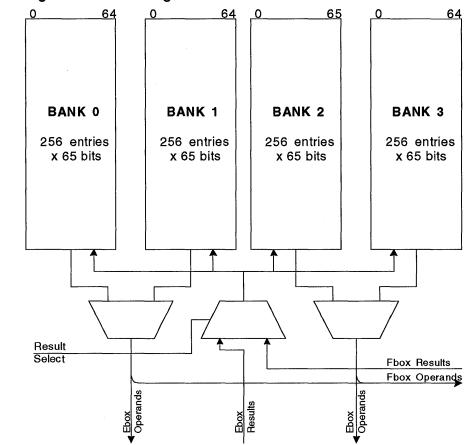

| 6.4   | Register Caches                 | 6–12 |

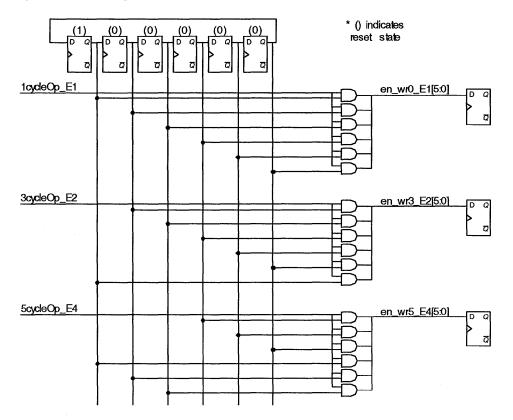

| 6.4.1 | Writing the Rcache              | 6–16 |

| 6.4.2 | Reading the Rcache              | 6–17 |

|       |                                 |      |

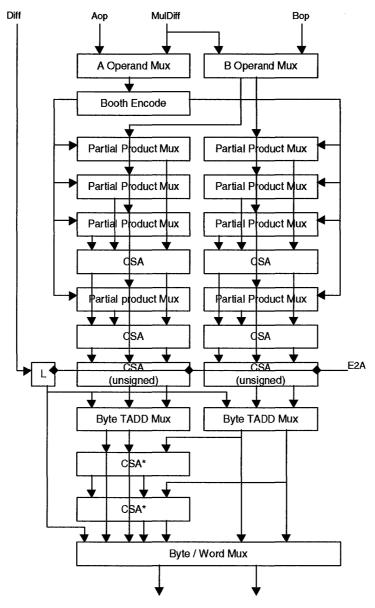

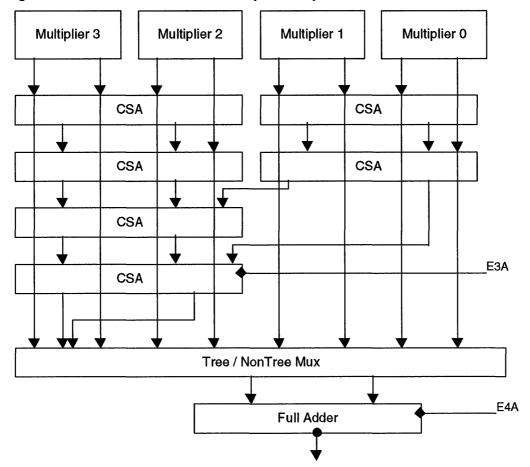

| 6.5     | Multimedia Unit                                                  | 6–18 |

|---------|------------------------------------------------------------------|------|

| 6.5.1   | Inputs and Outputs                                               | 6–18 |

| 6.5.2   | Signal Nomenclature                                              | 6–18 |

| 6.5.3   | Timing                                                           | 6–18 |

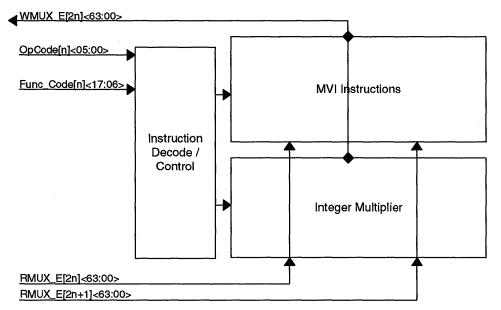

| 6.5.4   | Instruction Decode/Control Section                               | 6–19 |

| 6.5.5   | MVI Section                                                      | 6–19 |

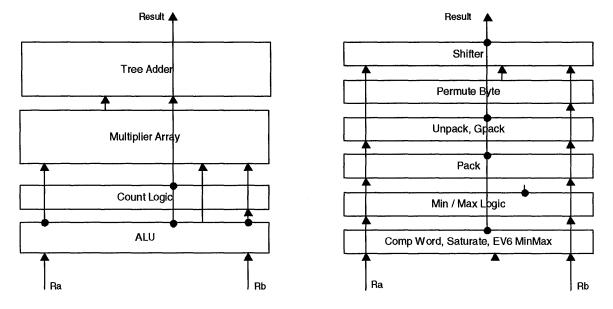

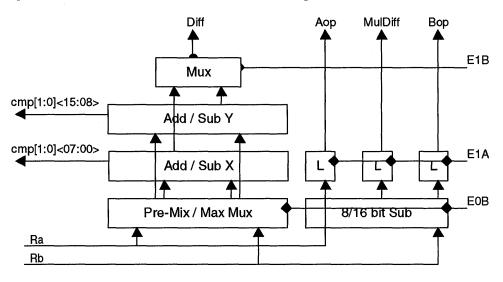

| 6.5.6   | ALU                                                              | 6–20 |

| 6.5.6.1 | TADD, TSUB PADD, PSUB, CMPWGE, MIN, MAX Instructions             | 6–21 |

| 6.5.6.2 | TABSERR Instruction                                              | 6–21 |

| 6.5.6.3 | TSQERR Instruction                                               | 6–21 |

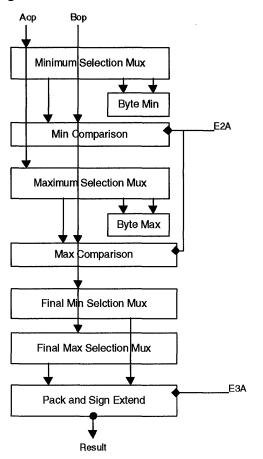

| 6.5.6.4 | Min/Max Instruction                                              | 6–21 |

| 6.5.7   | Multiplier Array                                                 | 6–22 |

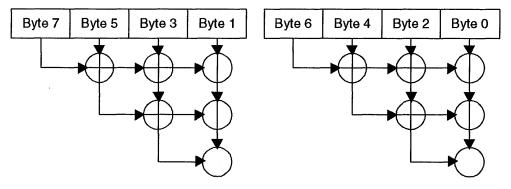

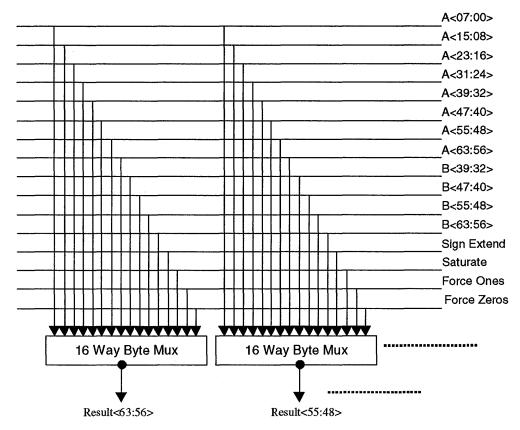

| 6.5.8   | Count Logic                                                      | 6–24 |

| 6.5.9   | Compare Word, Saturation, and the 21264 Min Max                  | 6–25 |

| 6.5.10  | MinMax Logic                                                     | 6–25 |

| 6.5.11  | Pack, Unpack, Permute Byte                                       | 6–26 |

| 6.5.12  | Shifter                                                          | 6–26 |

| 6.5.13  | Delay                                                            | 6–27 |

| 6.5.14  | Integer Multiplier                                               | 6-27 |

| 6.6     | Debug Features                                                   | 6–29 |

| 6.7     | Testability Features                                             | 6–30 |

| 6.8     | External Interfaces: Ibox, Qbox, Pbox, Mbox, Register File, Fbox | 6–30 |

| 6.8.1   | lbox                                                             | 6–30 |

| 6.8.2   | Qbox                                                             | 6–31 |

| 6.8.3   | Pbox                                                             | 6–32 |

| 6.8.4   | Mbox                                                             | 6–32 |

| 6.8.5   | Register File                                                    | 6–33 |

| 6.8.6   | Fbox                                                             | 6–33 |

| 6.8.7   | Global                                                           | 6–33 |

| 6.9     | IPRs                                                             | 6–34 |

| 6.10    | Exceptions                                                       | 6–34 |

| 6.11    | Poisoned Data                                                    | 6–35 |

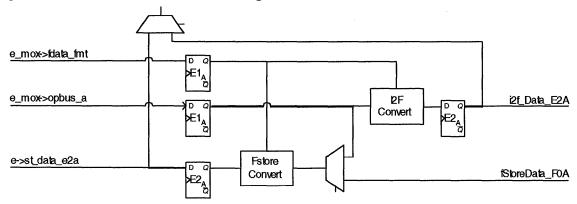

| 6.12    | Format Conversions                                               | 6–36 |

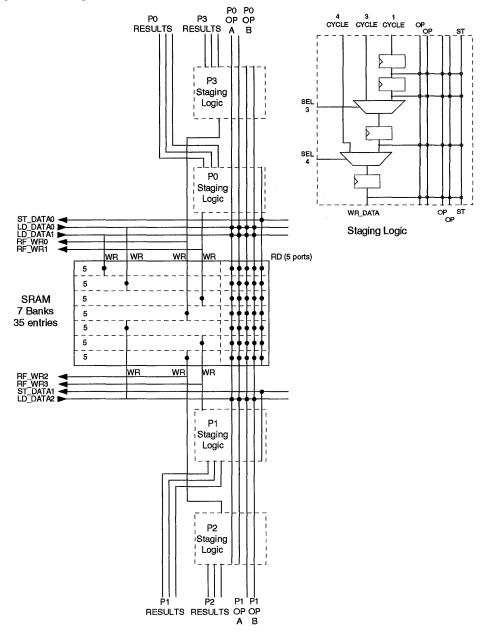

## 7 Register File

| 7.1   | Test Structures                 | 7-2 |

|-------|---------------------------------|-----|

| 7.1.1 | Timing                          | 7–2 |

| 7.1.2 | Read Timing                     | 7–3 |

| 7.1.3 | Write/Read Timing               | 7-3 |

| 7.2   | External Interfaces             | 7–3 |

| 7.2.1 | Qbox to Register File Interface | 7–3 |

| 7.2.2 | Ebox to Register File Interface | 7-4 |

| 7.2.3 | Fbox to Register File Interface | 7-4 |

| 7.2.4 | Global Register File Interface  | 7–4 |

## 8 Floating-Point Execution Units — the Fbox

| 8.1   | Major Sections            |

|-------|---------------------------|

| 8.2   | Interface Section         |

| 8.2.1 | External Interface        |

| 8.2.2 | Qbox Timing to Fbox       |

| 8.2.3 | Fbox Pipeline Timing      |

| 8.2.4 | Register File/Operand Bus |

| 8.2.5 | Loads/Stores to/from Fbox |

| 8.2.6 | Register Cache (F_RGC)    |

| 8.2.7              | The Operand Steering Unit (F_OSU)                    | 8–8          |

|--------------------|------------------------------------------------------|--------------|

| 8.2.8              | Interface Control (F_INT)                            | 8–10         |

| 8.2.9              | Divide and SQRT – Qbox interface                     | 8–10         |

| 8.2.10             | Fbox Exceptions                                      | 8–11         |

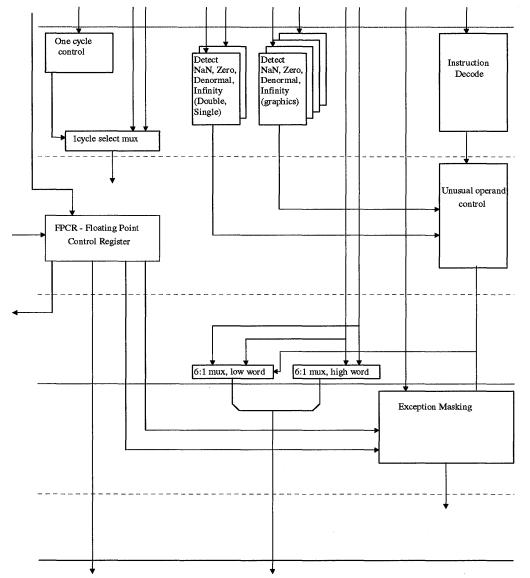

| 8.3                | Fbox Floating-Point Control Register (FPCR)          | 8–14         |

| 8.3.1              | FPCR Format.                                         | 8–14         |

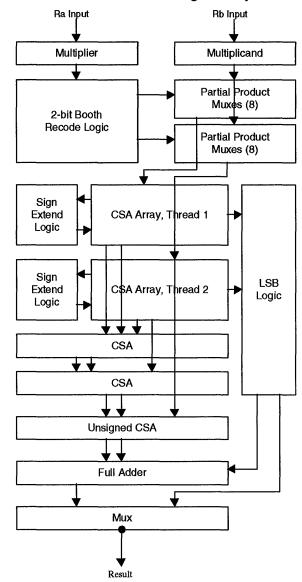

| 8.4                | Fbox Multiplier Unit F_MUL and F_GML                 | 8–16         |

| 8.4.1              | FMUL Operation.                                      | 8–16         |

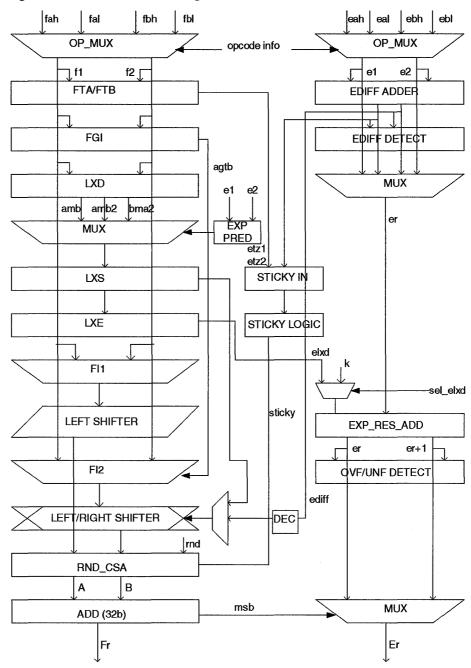

| 8.5                | Fbox Add Pipeline                                    | 8–18         |

| 8.6                | Fbox Add Pipe1 — F_AP1                               | 8–19         |

| 8.6.1              | Operation                                            | 8–21         |

| 8.6.1.0.           | 1 Phase F0A                                          | 8–21         |

| 8.6.1.0.           | 2 Phase F0B                                          | 8–22         |

| 8.6.1.0.           | 3 Phase F1A                                          | 8–23         |

| 8.6.1.0.           | 4 Phase F1B                                          | 8–23         |

| 8.6.1.0.           | 5 Phase F2A                                          | 8–25         |

| 8.6.1.0.           |                                                      | 8–26         |

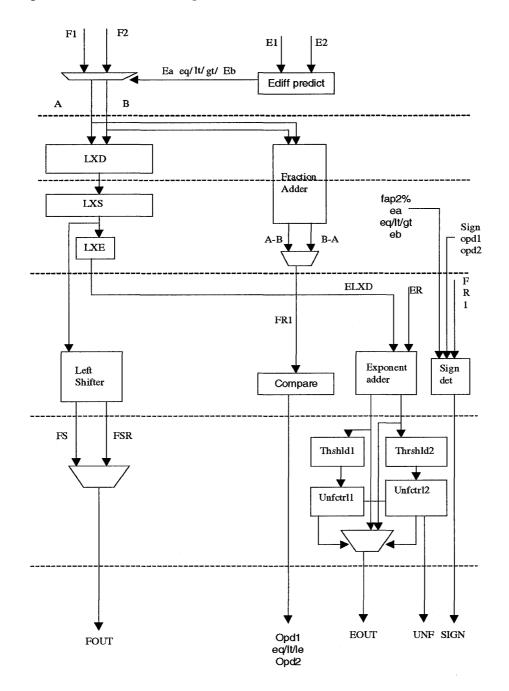

| 8.7                | Fbox Add Pipe2 — F_AP2                               | 8–26         |

| 8.7.1              | Cycle 1 Operation                                    | 8–26         |

| 8.7.1.1            | Fraction:                                            | 8–26         |

| 8.7.1.2            | Exponent                                             | 8–28         |

| 8.7.1.3            | Control                                              | 8–28         |

| 8.7.2              | Cycle 2 Operation                                    | 8–29         |

| 8.7.2.1            | Fraction                                             | 8–29         |

| 8.7.2.2            | Exponent/Control                                     | 8–29         |

| 8.7.3              | Cycle 3 Operation                                    | 8–30         |

| 8.7.3.1            | Fraction                                             | 830          |

| 8.7.3.2            | Exponent/Control                                     | 8–30         |

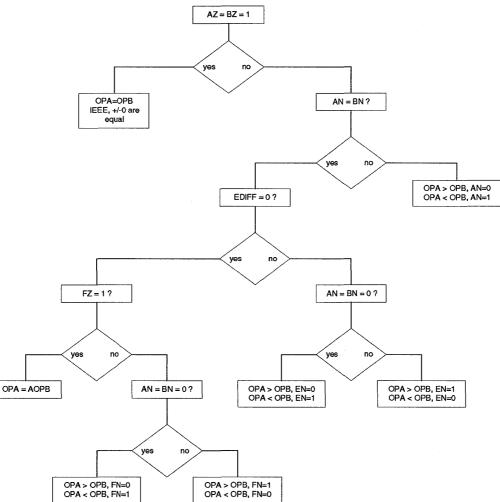

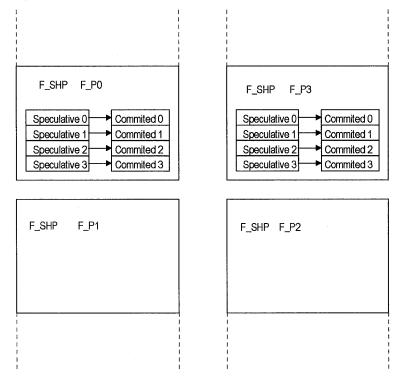

| 8.8                | Fbox Short Pipe — F_SHP                              | 8–31         |

| 8.8.1              | Short Instructions                                   | 8–32         |

| 8.8.1.1            | CPYS, CPYSN, CPYSE                                   | 8–32         |

| 8.8.1.2            | FCMOVEQ, FCMOVGE, FCMOVGT, FCMOVLE, FCMOVLT, FCMOVNE | 8–32         |

| 8.8.2              | Unusual Input Operands                               | 8–32         |

| 8.8.2.1            | Unusual Cases                                        | 8-33         |

| 8.8.2.2            |                                                      | 8-34         |

| 8.8.2.2.           |                                                      | 8-34         |

| 8.8.2.2.           | •                                                    | 8-34         |

| 8.8.2.2.           |                                                      | 8-34         |

| 8.8.2.2.           | •                                                    | 8-35         |

| 8.8.2.2.           | ,                                                    | 8-35         |

| 8.8.3              | Floating-Point Control Register (FPCR)               | 8–35<br>8–36 |

| 8.8.3.1<br>8.8.3.2 |                                                      |              |

| 8.8.3.2            | Dynamic Rounding                                     | 8–36<br>8–37 |

| 8.9                | Exceptions                                           | 8–37<br>8–39 |

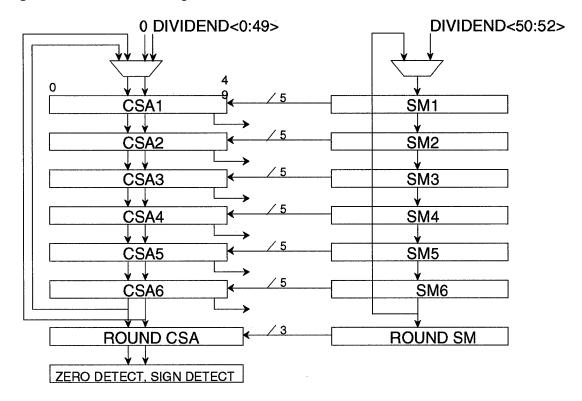

| 8.9<br>8.9.1       | Divider Description                                  | 8-39         |

| 8.9.1<br>8.9.2     | The Divider in Detail.                               | 8-39         |

| 8.9.3              | Over-Redundant Digits to Binary and Rounding         | 8–39<br>8–41 |

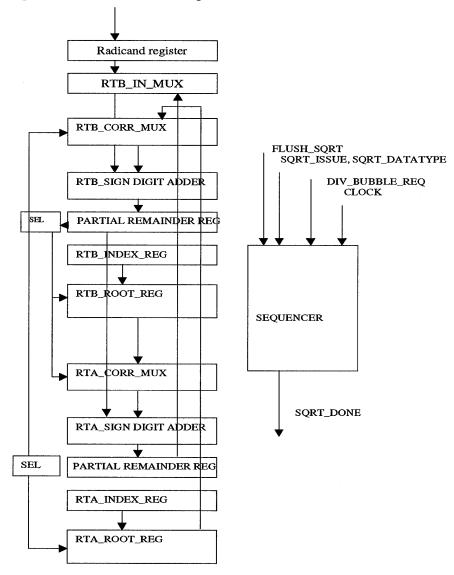

| 8.10               | Fbox Square-Root Unit — F_SQR                        | 8-44         |

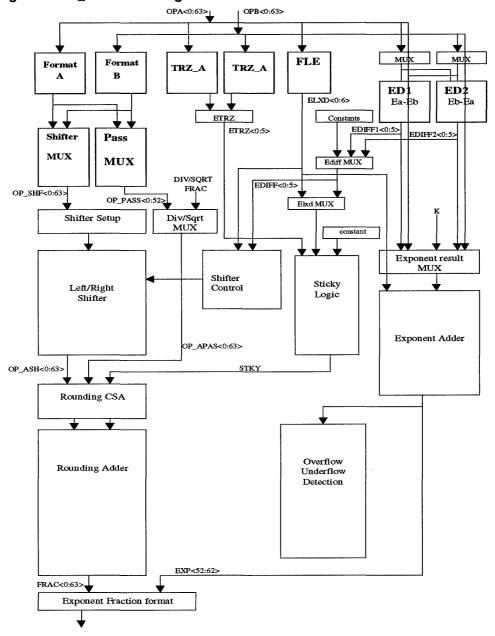

| 8.11               | Fbox Graphics Pipeline                               | 8–45         |

| 8.11.1             | Paired SP Floating-point Operate Instruction Format  | 8-46         |

| 8.11.2             | Register and Memory Formats.                         | 8-46         |

| 8.11.3             | Rounding Modes                                       | 8-46<br>8-46 |

| 8.11.3             | Exceptions                                           | 8–40<br>8–46 |

| 8.11.5             | Paired Single-Precision Instructions                 | 8–40<br>8–47 |

| 8.11.5.1           |                                                      | 8-50         |

| 8.11.5.2           |                                                      | 8-51         |

| 8.11.5.2           |                                                      | 8–51         |

| 8.11.5.2           |                                                      | 8-51         |

|                    |                                                      | 1            |

| 8.11.5.2 | 3 FGT                                    | 8-52 |

|----------|------------------------------------------|------|

| 8.11.5.2 |                                          | 8-52 |

| •••••    |                                          |      |

| 8.11.5.2 | .5 LXS and LXE                           | 8–52 |

| 8.11.5.2 | .6 FI1/FI2 MUX and the LEFT/LR Shifters. | 8–52 |

| 8.11.5.2 | .7 RND CSA and ADDER                     | 8–53 |

| 8.11.5.3 | Exponent Data Path                       | 8–54 |

| 8.11.5.3 | .1 EDIFF ADDER                           | 8–54 |

| 8.11.5.3 | .2 EDIFF DETECT                          | 8–54 |

| 8.11.5.3 | 3 ER MUX                                 | 8–54 |

| 8.11.5.3 | .4 EXP_RES_ADD                           | 8–54 |

| 8.12     | G_AD Control                             | 8–55 |

| 8.12.1   | Fraction Data Path                       | 8–55 |

| 8.13     | Sticky Bit Calculation                   | 8–56 |

## 9 Memory Instruction Execution Unit — the Mbox

| 9.1.1       Inputs       9-2         9.1.2       Outputs       9-2         9.2       Dcache       9-2         9.3       Dtags       9-3         9.4       Load Queue       9-3         9.5       Merge Buffer       9-4         9.6       Pre-MAF       9-5         9.7       Store Queue (SQA and SQD)       9-5         9.8       Translation Buffers       9-5         9.9       Back End Bus       9-6         9.10       Operations       9-6         9.10.1       Read Requests       9-6         9.10.2       Prefetches       9-6         9.10.3       Write Requests       9-7 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.2       Dcache       9–2         9.3       Dtags.       9–3         9.4       Load Queue.       9–3         9.5       Merge Buffer       9–4         9.6       Pre-MAF       9–5         9.7       Store Queue (SQA and SQD)       9–5         9.8       Translation Buffers       9–5         9.9       Back End Bus       9–6         9.10       Operations.       9–6         9.10.1       Read Requests       9–6         9.10.2       Prefetches       9–6         9.10.3       Write Requests.       9–7                                                                        |

| 9.3       Dtags.       9–3         9.4       Load Queue.       9–3         9.5       Merge Buffer .       9–4         9.6       Pre-MAF       9–5         9.7       Store Queue (SQA and SQD)       9–5         9.8       Translation Buffers       9–5         9.9       Back End Bus       9–6         9.10       Operations       9–6         9.10.1       Read Requests       9–6         9.10.2       Prefetches       9–6         9.10.3       Write Requests       9–7                                                                                                           |

| 9.4       Load Queue.       9–3         9.5       Merge Buffer       9–4         9.6       Pre-MAF       9–5         9.7       Store Queue (SQA and SQD)       9–5         9.8       Translation Buffers       9–5         9.9       Back End Bus       9–6         9.10       Operations       9–6         9.10.1       Read Requests       9–6         9.10.2       Prefetches       9–6         9.10.3       Write Requests       9–7                                                                                                                                                |

| 9.5       Merge Buffer       9–4         9.6       Pre-MAF       9–5         9.7       Store Queue (SQA and SQD)       9–5         9.8       Translation Buffers       9–5         9.9       Back End Bus       9–6         9.10       Operations       9–6         9.10.1       Read Requests       9–6         9.10.2       Prefetches       9–6         9.10.3       Write Requests       9–7                                                                                                                                                                                        |

| 9.6       Pre-MAF       9–5         9.7       Store Queue (SQA and SQD)       9–5         9.8       Translation Buffers       9–5         9.9       Back End Bus       9–6         9.10       Operations       9–6         9.10.1       Read Requests       9–6         9.10.2       Prefetches       9–6         9.10.3       Write Requests       9–7                                                                                                                                                                                                                                 |

| 9.7       Store Queue (SQA and SQD).       9–5         9.8       Translation Buffers.       9–5         9.9       Back End Bus       9–6         9.10       Operations.       9–6         9.10.1       Read Requests       9–6         9.10.2       Prefetches       9–6         9.10.3       Write Requests.       9–7                                                                                                                                                                                                                                                                 |

| 9.8         Translation Buffers         9–5           9.9         Back End Bus         9–6           9.10         Operations         9–6           9.10.1         Read Requests         9–6           9.10.2         Prefetches         9–6           9.10.3         Write Requests         9–7                                                                                                                                                                                                                                                                                         |

| 9.8         Translation Buffers         9–5           9.9         Back End Bus         9–6           9.10         Operations         9–6           9.10.1         Read Requests         9–6           9.10.2         Prefetches         9–6           9.10.3         Write Requests         9–7                                                                                                                                                                                                                                                                                         |

| 9.10         Operations.         9–6           9.10.1         Read Requests         9–6           9.10.2         Prefetches         9–6           9.10.3         Write Requests.         9–7                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.10.1         Read Requests         9–6           9.10.2         Prefetches         9–6           9.10.3         Write Requests         9–7                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.10.2         Prefetches         9–6           9.10.3         Write Requests         9–7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9.10.3 Write Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9.10.4 Retries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.10.5 Dcache Misses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.10.6 Load Locked/Store Conditional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.10.7 Traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.10.8 Invalidates/Probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9.10.9 Memory Barriers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.10.10 Multi-threading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9.11 Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9.11.1 Pipeline Legend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.12 Data address Translation buffer (DTB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9.12.1 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9.12.2 What Data are Compared on a DTB Lookup?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.12.2.1 The TPU Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.12.2.2 Granularity Hints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9.12.3 64K Pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9.12.4 Hit Determination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9.12.5 Returned Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.12.6 Effects of a DTB Miss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.12.6.1 Speculative and Duplicate DTB entries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.12.7 Data Storage in the PTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.12.8 IPRs That Affect the Contents or Behavior of the DTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9.12.9 Superpages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9.12.10 Possible Support for Generic Superpages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9.12.10.1 Page Table Array(PTA) Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.12.10.2 Virtual Address Array(VAA) Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9.12.11 Replacement Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9.12.12   | DTB Size                                                        |

|-----------|-----------------------------------------------------------------|

| 9.12.13   | ITB Usage                                                       |

| 9.12.14   | Reset and Testability                                           |

| 9.12.15   | lssues                                                          |

|           | 9–2                                                             |

| 9.13.1    | Overview                                                        |

| 9.13.2    | Store Issue Flow                                                |

| 9.13.3    | Load Issue Flow                                                 |

| 9.13.4    | Store Copy-Out Flow                                             |

| 9.13.5    | Block Allocate Flow (TBD)                                       |

| 9.13.6    | Things Not Done         9–2                                     |

|           | rge Buffer                                                      |

| 9.14.1    | Overview                                                        |

| 9.14.2    | Merge Buffer Allocation                                         |

| 9.14.2.1  | Boundary Case                                                   |

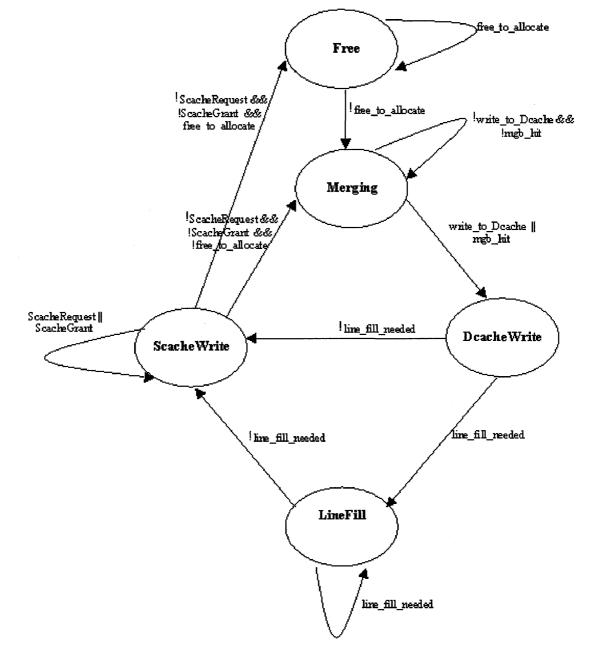

| 9.14.3    | Merge Buffer Writes to Dcache                                   |

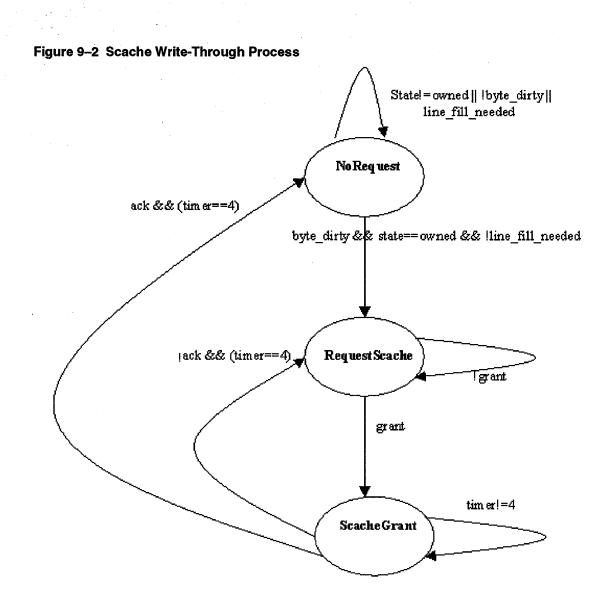

| 9.14.4    | Scache Writes                                                   |

| 9.14.5    | Probe handling in the Merge Buffer                              |

| 9.14.6    | Line fill and Merge Buffer                                      |

| 9.14.7    | IO Stores                                                       |

| 9.14.8    | Store Conditional Support                                       |

| 9.14.9    | MB and WMB Processing                                           |

| 9.14.10   | MAF request                                                     |

| 9.14.11   | Cache Movement ops (WH64, Evict)                                |

| 9.14.12   | Merge Buffer States                                             |

| 9.14.13   | Data Array                                                      |

| 9.14.14   | Address Array                                                   |

| 9.14.15   | Control Section                                                 |

|           | ad Queue                                                        |

| 9.15.1    | Load Queue Allocation                                           |

| 9.15.2    | (Age) Young Vector generation                                   |

| 9.15.3    | Load Queue Limit and Block Allocation                           |

| 9.15.4    | Thread Choosing         9–3                                     |

| 9.15.5    | Block Assignment                                                |

| 9.15.6    | Load Issue                                                      |

| 9.15.7    | Load Retries                                                    |

| 9.15.8    | Dcache Miss                                                     |

| 9.15.8.1  | MAF Pick                                                        |

| 9.15.8.2  | Load Queue Pick                                                 |

| 9.15.9    | Scache Line Miss                                                |

| 9.15.10   | Load Queue retry - Bank Conflict                                |

| 9.15.11   | Retry at retirement                                             |

| 9.15.12   | Retry Block                                                     |

| 9.15.12.1 | Pick Oldest Retry                                               |

| 9.15.12.2 | Oldest and Next Oldest Retry Chooser                            |

| 9.15.12.3 | Thread Chooser                                                  |

| 9.15.13   | Prefetches                                                      |

| 9.16 Loa  | ad Traps                                                        |

| 9.16.1    | DTB trap                                                        |

| 9.16.1.1  | Load/store Order Trap                                           |

| 9.16.1.2  | Inval Trap (Traps Due to Probe-invalidates)                     |

| 9.16.1.3  | MGB Trap (Traps Due To Merge Buffer Dispatches On Back End Bus) |

| 9.16.1.4  | Trap Summary                                                    |

| 9.16.2    | Trap Resolution                                                 |

| 9.16.3    | Thread chooser                                                  |

| 9.16.4    | Kill Bus                                                        |

| 9.16.5    | Litmus 1 Handling                                               |

| 9.17 Dca  | ache Tags                                                       |

| 9.17.1    | Front End Tags                                                  |

|           |                                                                 |

| 9.17.1.1 | Timing                       | 9–43             |

|----------|------------------------------|------------------|

| 9.17.1.2 | Tag Operations               | 9–43             |

| 9.17.2   | Back End Tag                 | 9–43             |

| 9.17.2.0 | 0.1 Tag Operations           | 9–43             |

| 9.17.3   | IPRs                         | 9-44             |

| 9.18     | Dcache Array                 | 9–44             |

| 9.18.1   | Read Dcache                  | <del>9–</del> 45 |

| 9.18.2   | Write Dcache                 | 9–45             |

| 9.18.3   | Bypass Fill Data             | 9–45             |

| 9.18.4   | Structure                    | <del>9–</del> 45 |

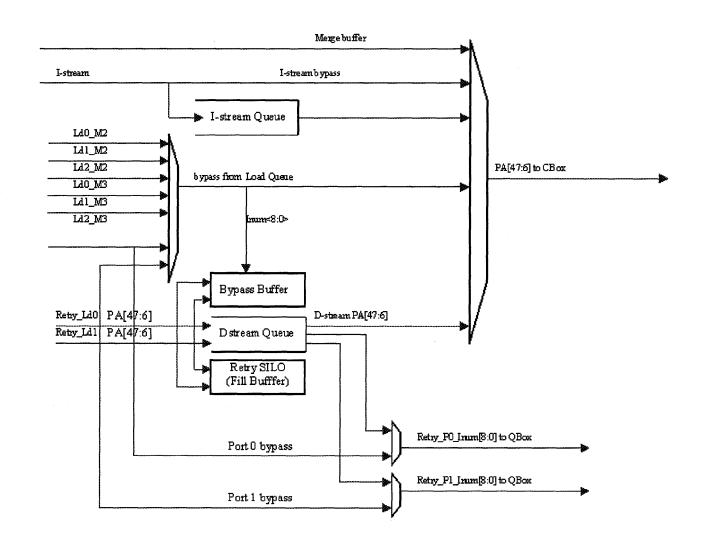

| 9.19     | Pre-MAF                      | 9–45             |

| 9.19.1   | Merge Buffer Requests        | 9–47             |

| 9.19.2   | D-stream Queue               | 9–47             |

| 9.19.3   | Killing Retries              | 9–48             |

| 9.19.4   | I-stream Queue               | 9–48             |

| 9.20     | Mbox Back End Bus            | <del>9</del> –48 |

| 9.21     | Internal Processor Registers | 9–48             |

| 9.21.1   | Implicitly Written IPRs      | 9–49             |

#### 10 Internal Ring Bus

## 11 Second-Level Cache and Controller (Cbox)

| 11.1 Cb    | ox Overview                                                  |

|------------|--------------------------------------------------------------|

| 11.2 Sb    | ox Overview                                                  |

| 11.3 Sc    | ache Control — the CS Partition                              |

| 11.3.1     | Overall Pipeline Flow                                        |

| 11.3.2     | Miss Address File — the MAF 11-                              |

| 11.3.2.1   | Overview                                                     |

| 11.3.2.2   | Principle of Operation                                       |

| 11.3.2.2.1 | Requests from the Core                                       |

| 11.3.2.2.2 | Fills/Responses from the System                              |

| 11.3.2.2.3 | Probes From Other Processors 11-                             |

| 11.3.2.3   | MAF Pipeline Timing Diagram and Pipeline Overview            |

| 11.3.2.3.1 | CZ, C0: MAF Arbitration Logic 11-                            |

| 11.3.2.3.2 | C1: MAF Bank Conflict Detection Logic / MAF CAM / MAF RD 11- |

| 11.3.2.3.3 | Exceptions                                                   |

| 11.3.2.3.4 | C1: MAF CAM / MAF RD                                         |

| 11.3.2.3.5 | c2: MAF logic                                                |

| 11.3.2.3.6 | C3–C6: Scache Tag Access 11–1                                |

| 11.3.2.3.7 | C7: Fill Pipe Control 11–1                                   |

| 11.3.2.4   | Contents of MAF Entries 11–1                                 |

| 11.3.2.5   | MAF Allocation/Merge/Retry 11–1                              |

| 11.3.2.6   | MAF Deallocation                                             |

| 11.3.3     | RSQ 11–1                                                     |

| 11.3.4     | Internal Probe Queue — the IPQ 11-1                          |

| 11.3.5     | Probe Queue — the PRQ 11–1                                   |

| 11.3.5.0.1 | Principle of Operation                                       |

| 11.3.5.1   | Probe Address File (MAF) Contents per Entry 11–1             |

| 11.3.6     | Victim Address File — the VAF 11–1                           |

| 11.3.6.1   | Victim Address File (VAF) Contents per Entry 11–1            |

| 11.3.6.2   | Principle of Operation                                       |

| 11.3.6.3   | Secondary VAF Flows                                          |

| 11.3.6.4   | Reserved VAF Entries                                         |

| 11.3.7     | System Interface (SYS) 11-2                                  |

| 11.3.7.1   | Principle of Operation:                                      |

| 11.3.7.1.1 | Response FIFO Entry Fields                                         | 1121  |

|------------|--------------------------------------------------------------------|-------|

| 11.3.7.1.2 | Request FIFO Entry Fields                                          | 11-22 |

| 11.3.8     | System Request Queue (SRQ)                                         | 11-22 |

| 11.3.8.1   | Principle of Operation .                                           | 11-22 |

|            |                                                                    |       |

| 11.3.9     | Retry Queue (RTQ)                                                  | 11–23 |

| 11.3.9.1   | Principle of Operation                                             | 11–23 |

| 11.3.10    | TTQ                                                                | 11–24 |

| 11.4 Fill  | Datapath — the CF Partition                                        | 11-24 |

| 11.4.1     | FBE                                                                | 11-24 |

| 11.4.2     |                                                                    |       |

|            | VDB                                                                | 11–24 |

| 11.4.3     | FDB                                                                | 11–24 |

| 11.4.4     | DBM                                                                | 11–25 |

| 11.4.5     | RBI                                                                | 11-25 |

| 11.4.6     | RBO                                                                | 11-25 |

|            |                                                                    |       |

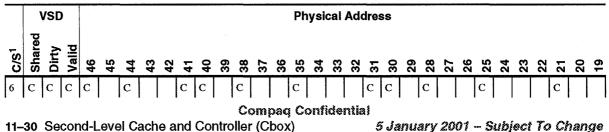

|            | ache Tag Array — the ST Partition                                  | 11–25 |

| 11.5.0.1   | Principle of Operation                                             | 11–25 |

| 11.5.0.2   | Pipeline Stages                                                    | 11–26 |

| 11.5.0.3   | State Transition                                                   | 11–26 |

| 11.5.0.4   | Stale Fill Table                                                   | 11-28 |

| 11.5.0.5   | The 21464 Scache Least Recently Used (LRU) Scheme                  | 11-28 |

|            |                                                                    |       |

| 11.5.0.6   | Scache Tag ECC Code                                                | 11–30 |

| 11.6 Sca   | ache Data Array — the SG Partition                                 | 11–32 |

| 11.7 Flo   | ws                                                                 | 11-32 |

| 11.7.1     | Overall Pipeline Flow                                              | 11-32 |

| 11.7.1.1   |                                                                    | 11-32 |

|            | Pipe Operation                                                     |       |

| 11.7.1.2   | Pipeline Timing Diagrams                                           | 11–37 |

| 11.7.1.2.1 | Scache Control Pipeline Stages                                     | 11–37 |

| 11.7.1.3   | Resource Conflict                                                  | 11–39 |

| 11.7.1.4   | Scache Bank Conflict Check.                                        | 11–40 |

| 11.7.2     | Fill and LRU Evict Flow                                            | 11-42 |

|            |                                                                    |       |

| 11.7.2.1   | Hiccup Flow                                                        | 11–42 |

| 11.7.3     | Probe Flow                                                         | 11–42 |

| 11.7.4     | Mbox Request Flow                                                  | 11–42 |

| 11.7.5     | Victim Flow                                                        | 11-43 |

| 11.7.6     | Retry Flow                                                         | 11-46 |

|            |                                                                    |       |

|            | ecial Support                                                      | 11-46 |

| 11.8.1     | Input – Output                                                     | 11–46 |

| 11.8.1.1   | I/O Request Ordering and Merging                                   | 11–46 |

| 11.8.1.2   | I/O System Request                                                 | 11-47 |

| 11.8.1.3   | Others                                                             | 11-47 |

| 11.8.1.4   | I/O Request Flow                                                   | 11-47 |

|            |                                                                    |       |

| 11.8.1.5   | I/O Specific Structures/Operations                                 | 11–49 |

| 11.8.1.6   | I/O System Request Timing                                          | 11–49 |

| 11.8.1.7   | I/O Request Packet Format                                          | 1150  |

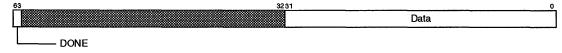

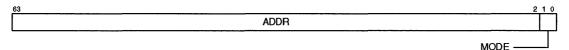

| 11.8.1.7.1 | Read I/O (RDIO)                                                    | 11–50 |

| 11.8.1.7.2 | Write I/O (WRIO)                                                   | 11-51 |

|            |                                                                    | 11-51 |

| 11.8.2     | Memory Barriers — the MB Instruction                               |       |

| 11.8.3     | Load-Locked Store-Conditional (LDx_L/STx_C) Instruction Processing | 11–51 |

| 11.8.3.1   | Lock Register for Each Thread                                      | 11–53 |

| 11.8.3.2   | Stx_C Issuing                                                      | 11–53 |

| 11.8.4     | Prefetch/Modify                                                    | 11-53 |

|            |                                                                    |       |

|            | Rs, CSRs, and Error Handling                                       | 11-53 |

| 11.9.1     | Required IPRs and CSRs                                             | 11–53 |

| 11.9.2     | Error Handling                                                     | 11–55 |

| 11.9.3     | Cbox Deadlock Avoidance Mechanisms                                 | 11–55 |

|            | filing Support                                                     | 11-55 |

|            |                                                                    |       |

|            | ff From Original Cbox Spec Not in Outline                          | 11-55 |

| 11.11.1    | Scache Index (paddr<18:6>) Conflict                                | 11–55 |

| 11.11.2    | ShrToDirty[STC]Req                                                 | 11–56 |

|            |                                                                    |       |

| 11.11.3 | Scache Tag Launch Pipe                      | 1157  |

|---------|---------------------------------------------|-------|

| 11.11.4 | Probe Processing in Cbox                    | 11–60 |

| 11.11.5 | Order Dependency                            | 11–61 |

| 11.11.6 | Possible Race Conditions and Other Concerns | 11–62 |

| 11.11.7 | CBox mechanisms                             | 11–62 |

#### 12 Cache Coherence Protocol Processing

| 12.1     | Introduction to the Protocol                                 | 12-1  |

|----------|--------------------------------------------------------------|-------|

| 12.2     | Structures that Maintain the Cache Coherence                 | 12-2  |

| 12.2.1   | Miss Address File (MAF)                                      | 12–3  |

| 12.2.2   | System Request Queue (SRQ)                                   | 12–3  |

| 12.2.3   | Victim Buffer                                                | 12–3  |

| 12.2.4   | Probe Queue (PRQ)                                            | 12–4  |

| 12.2.5   | DIFT                                                         | 12–5  |

| 12.3     | Overview of the Cache Coherency Protocols                    | 12–5  |

| 12.3.1   | Comparison Between 21363 and 21464 Cache Coherence Protocols | 12–5  |

| 12.3.2   | Onchip Directory Cache                                       | 12–6  |

| 12.3.3   | Coherence Messages are Split into Three Types                | 12–6  |

| 12.4     | Protocol Races                                               | 12–7  |

| 12.5     | Probe Processing                                             | 12–8  |

| 12.6     | Coherence State                                              | 12–10 |

| 12.7     | MAF Address CAM                                              | 12–11 |

| 12.8     | Scache Hit                                                   | 12–14 |

| 12.9     | VAF Address CAM                                              | 12–17 |

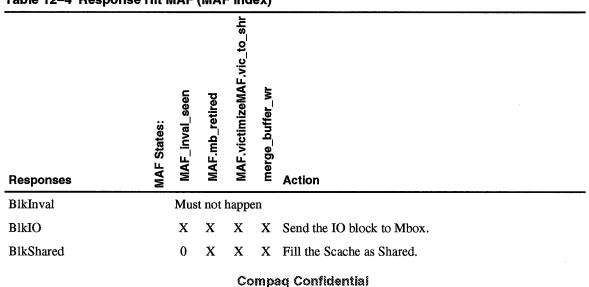

| 12.10    | Directory Responses                                          | 12–18 |

| 12.11    | System Command Opcodes                                       | 12–20 |

| 12.12    | Protocol Message Descriptions                                | 12–21 |

| 12.12.1  | IO CHANNEL Message Details                                   | 12-21 |

| 12.12.1. |                                                              | 12–21 |

| 12.12.1. | — , , , , , , , , , , , , , , , , , , ,                      | 12–22 |

| 12.12.2  | REQUEST CHANNEL Message Details                              | 12–24 |

| 12.12.2. |                                                              | 12–24 |