# Digital Alpha VME 4/224 and 4/288 Single-Board Computers

# User Guide and Technical Description

Order Number: EK-DAVME-TD. B01

This manual describes the Digital Alpha VME 4 module. It provides configuration and installation procedures and describes the module's built-in features, including the console code and diagnostics.

Revision/Update Information: This manual supersedes the *Digital*

Alpha VME 4/224 and 4/288 Single-Board Computers User Guide and Technical Description,

EK-DAVME-TD. A01.

#### First Printing, July 1996 Revised, September 1996

Printed in U.S.A.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

#### **FCC Notice:**

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

#### Warning!

This is a Class A product. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.

#### Achtung!

Dieses ist ein Gerät der Funkstörgrenzwertklasse A. In Wohnbereichen können bei Betrieb dieses Gerätes Rundfunkstörungen auftreten, in welchen Fällen der Benutzer für entsprechende Gegenmaßnahmen verantwortlich ist.

#### Attention!

Ceci est un produit de Classe A. Dans un environment domestique, ce produit risque de créer des interférences radioélectriques, il appartiendra alors à l'utilisateur de prendre les mesures spécifiques appropriées.

#### **Canadian EMC Notice:**

"This Class [A] Digital apparatus meets all requirements of the Canadian Interference-Causing Equipment Regulations."

"Cet appareil numerique de la class [A] respecte toutes les exigences du Reglement sur le materiel broilleur du Canada."

© Digital Equipment Corporation 1996.

All Rights Reserved.

The following are trademarks of Digital Equipment Corporation: Alpha AXP, DECchip, DECnet, DECpc, Digital, OpenVMS, ThinWire, ULTRIX, VAX, and the DIGITAL logo.

The following are third-party trademarks:

DALLAS is a registered trademark of Dallas Systems Corporation. Futurebus/Plus is a registered trademark of Force Computers GMBH, Germany. IBM is a registered trademark of International Business Machines Corporation. Intel is a trademark of Intel Corporation.

NCR is a registered trademark of National Cash Register Company.

OSF and OSF/1 are registered trademarks of Open Software Foundation, Inc. UNIX is a registered trademark licensed exclusively by X/Open Company Ltd. VIC64 is a trademark of Cypress Semiconductor Corporation.

VxWorks is a registered trademark of Wind River Systems, Inc.

All other trademarks and registered trademarks are the property of their respective holders.

# Contents

| Pı | Preface  |                                           | xxi  |

|----|----------|-------------------------------------------|------|

| 1  | Produc   | et Overview                               |      |

|    | 1.1      | Product Description                       | 1–1  |

|    | 1.2      | Functional Specifications                 | 1–1  |

|    | 1.3      | Physical and Environmental Requirements   | 1–4  |

| 2  | Installa | ation Procedures                          |      |

|    | 2.1      | Unpacking                                 | 2–1  |

|    | 2.2      | Installation                              | 2–6  |

|    | 2.2.1    | Installing the PMC I/O Companion Card     | 2-23 |

|    | 2.3      | Diagnostics                               | 2-27 |

|    | 2.4      | Troubleshooting                           | 2-29 |

|    | 2.5      | Repair and Warranty Information           | 2-32 |

|    | 2.5.1    | Return to Digital Hardware Maintenance    | 2-32 |

|    | 2.5.2    | Hardware Warranty                         | 2-32 |

|    | 2.5.2.1  | Availability                              | 2-32 |

|    | 2.5.2.2  | Return-to-Digital Process                 | 2-33 |

|    | 2.5.2.3  | Response Time                             | 2-33 |

|    | 2.5.2.4  | Eligible Parts                            | 2-33 |

|    | 2.5.2.5  | Purchaser Responsibility                  | 2-33 |

|    | 2.5.2.6  | Pre-Call Checklist                        | 2-34 |

|    | 2.5.3    | Software Maintenance                      | 2-34 |

|    | 2.5.4    | Field Replaceable Units and Order Numbers | 2-35 |

|    |          | •                                         |      |

| 3 | Opera                                             | ting the Digital Alpha VME 4 Computer                                                                                                               |                                        |

|---|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   | 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>3.4<br>3.5 | Controls and Indicators Console Mode Entering Console Mode Exiting Console Mode Environment Variables Booting an Operating System Updating Firmware | 3–1<br>3–3<br>3–3<br>3–3<br>3–3<br>3–7 |

| 4 | Diagno                                            | ostics                                                                                                                                              |                                        |

|   | 4.1                                               | Overview                                                                                                                                            | 4–1                                    |

|   | 4.2                                               | Operating Environments                                                                                                                              | 4–1                                    |

|   | 4.2.1                                             | POST Diagnostics                                                                                                                                    | 4–1                                    |

|   | 4.2.2                                             | Console Prompt Diagnostics                                                                                                                          | 4–2                                    |

|   | 4.3<br>4.3.1                                      | Diagnostic Test Descriptions                                                                                                                        | 4–2<br>4–2                             |

|   | 4.3.1                                             | Available Console Diagnostics                                                                                                                       | 4–2<br>4–4                             |

|   | 4.3.2                                             | Console POST Descriptions                                                                                                                           | 4 <del>-4</del><br>4-5                 |

|   | 1.0.0                                             | POST Non-Volatile RAM Diagnostic                                                                                                                    | 4–6                                    |

|   |                                                   | POST Memory Diagnostic                                                                                                                              | 4–7                                    |

|   | 4.3.4                                             | Console Diagnostic Test Descriptions                                                                                                                | 4–7<br>4–8                             |

|   | 1.0. 1                                            | Heartbeat Timer Test                                                                                                                                | 4–9                                    |

|   |                                                   | Interval Timer Tests                                                                                                                                | 4–10                                   |

|   |                                                   | DECchip 21040 Ethernet Controller Tests                                                                                                             | 4–16                                   |

|   |                                                   | DALLAS DS1386 RAMified Watchdog Timekeeper                                                                                                          | 7 10                                   |

|   |                                                   | Tests                                                                                                                                               | 4–18                                   |

|   |                                                   | Local Area Network Address ROM Test                                                                                                                 | 4–22                                   |

|   |                                                   | NCR 53C810 PCI-SCSI I/O Processor Tests                                                                                                             | 4–24                                   |

|   |                                                   | Watchdog Timer Interrupt Test                                                                                                                       | 4-24                                   |

|   |                                                   | VME Interface Tests                                                                                                                                 | 4-27                                   |

|   | 4.4                                               | Initialization Sequence                                                                                                                             | 4–28<br>4–30                           |

|   | 7.7                                               | initianzation bequeite                                                                                                                              | <del>-1</del> -30                      |

| 5 | Systen       | n Address Mapping                                                          |            |

|---|--------------|----------------------------------------------------------------------------|------------|

|   | 5.1<br>5.1.1 | CPU Address Mapping to PCI Space                                           | 5–1        |

|   | 5.1.2        | 0x0FFFFFFFF)                                                               | 5–4        |

|   |              | 0x17FFFFFF)                                                                | 5–4        |

|   | 5.1.3        | DECchip 21071-CA CSR Space (0x180000000 to 0x19FFFFFFF)                    | 5–4        |

|   | 5.1.4        | DECchip 21071-DA CSR Space (0x1A0000000 to 0x1AFFFFFFF)                    | 5–5        |

|   | 5.1.5        | PCI Interrupt Acknowledge/Special Cycle Space (0x1B0000000 to 0x1BFFFFFFF) | 5–5        |

|   | 5.1.6        | PCI Sparse I/O Space (0x1C0000000 to                                       |            |

|   | 5.1.7        | 0x1DFFFFFFF)                                                               | 5–5        |

|   | 5.1.7.1      | 0x1FFFFFFFF)                                                               | 5–8        |

|   | 5.1.7.2      | Targets                                                                    | 5–9        |

|   |              | Targets                                                                    | 5–10       |

|   | 5.1.8        | PCI Sparse Memory Space (0x200000000 to 0x2FFFFFFFF)                       | 5–11       |

|   | 5.1.9        | PCI Dense Memory Space (0x300000000 to 0x3FFFFFFFF)                        | 5–14       |

|   | 5.2          | PCI-to-Physical Memory Addressing                                          | 5–15       |

| 6 | Cache        | and Memory Subsystem                                                       |            |

|   | 6.1          | System Bus Interface                                                       | 6–4        |

|   | 6.1.1        | Arbitration on the System Bus                                              | 6–4        |

|   | 6.1.2        | System Bus Controller                                                      | 6–4        |

|   | 6.1.3        | Decoding Addresses                                                         | 6–4        |

|   | 6.2          | Bcache Control                                                             | 6–5        |

|   | 6.3          | Memory Controller                                                          | 6–5        |

|   | 6.3.1        | Memory Organization                                                        | 6–6        |

|   | 6.3.2        | Memory Address Generation                                                  | 6–7        |

|   | 6.3.3        | Support for Memory Page Mode                                               | 6–7        |

|   | 6.3.4        | Minimizing Read Latency                                                    | 6–7        |

|   | 6.3.5        | Transaction Scheduler                                                      | 6–7        |

|   | 6.3.6        | Programmable Memory Timing                                                 | 6–7        |

|   | 6.3.7<br>6.4 | Presence Detect Logic                                                      | 6–8<br>6–8 |

|   |              |                                                                            |            |

|   | 6.5     | Address Space of Control/Status Registers       | 6–8  |

|---|---------|-------------------------------------------------|------|

|   | 6.6     | Description of CSRs                             | 6–11 |

|   | 6.6.1   | General Control Register                        | 6–11 |

|   | 6.6.2   | Error and Diagnostic Status Register            | 6–13 |

|   | 6.6.3   | Tag Enable Register                             | 6–16 |

|   | 6.6.4   | Error Low Address Register                      | 6–18 |

|   | 6.6.5   | Error High Address Register                     | 6–19 |

|   | 6.6.6   | LDx_L Low Address Register                      | 6–19 |

|   | 6.6.7   | LDx_L High Address Register                     | 6-20 |

|   | 6.6.8   | Memory Control Registers                        | 6-20 |

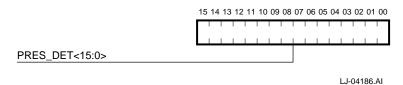

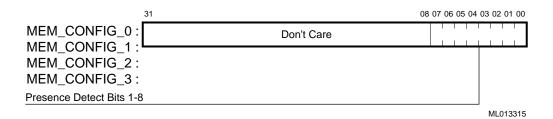

|   | 6.6.8.1 | Presence Detect Low-Data Register               | 6-20 |

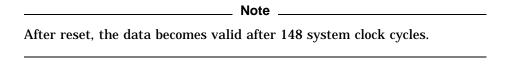

|   | 6.6.8.2 | Presence Detect High-Data Register              | 6–21 |

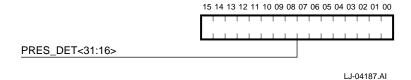

|   | 6.6.8.3 | Base Address Registers                          | 6–21 |

|   | 6.6.8.4 | Configuration Registers                         | 6–22 |

|   | 6.6.8.5 | Bank Set Timing Registers                       | 6-24 |

|   | 6.6.8.6 | Global Timing Register                          | 6–27 |

|   | 6.6.8.7 | Refresh Timing Register                         | 6–28 |

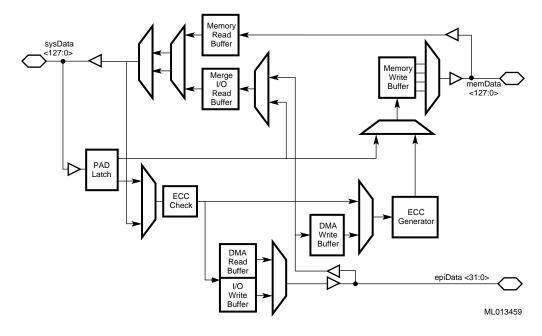

|   | 6.7     | Data Path                                       | 6-30 |

|   | 6.7.1   | Memory Read Buffer                              | 6-31 |

|   | 6.7.2   | I/O Read Buffer and Merge Buffer                | 6–31 |

|   | 6.7.3   | I/O Write and DMA Read Buffer                   | 6–31 |

|   | 6.7.4   | DMA Write Buffer                                | 6–31 |

|   | 6.7.5   | Memory Write Buffer                             | 6-32 |

|   | 6.7.6   | Error Handling                                  | 6–32 |

| 7 | PCI Ho  | st Bridge                                       |      |

|   | 7.1     | Interface to the System Bus                     | 7–2  |

|   | 7.1.1   | Decoding Physical Addresses                     | 7–2  |

|   | 7.1.2   | Buffering System Bus Transactions               | 7–3  |

|   | 7.1.3   | Burst Length and Prefetching for the System Bus | 7–3  |

|   | 7.2     | Interface to the PCI bus                        | 7–3  |

|   | 7.2.1   | Decoding PCI Addresses                          | 7–3  |

|   | 7.2.2   | Buffering PCI Transactions                      | 7–3  |

|   | 7.2.3   | Burst Length and Prefetching for PCI bus        | 7–4  |

|   | 7.3     | Features                                        | 7–4  |

|   | 7.3.1   | Burst Order                                     | 7–4  |

|   | 7.3.2   | Parity Support                                  | 7–4  |

|   | 7.3.3   | Data Coherency                                  | 7–5  |

|   | 7.3.4   | Interrupts                                      | 7–6  |

|   | 7.3.5   | Exclusive Access                                | 7–6  |

|   | 7.3.6   | Bus Parking                                     | 7–6  |

|   | 7.3.7   | Retry Timeout                                   | 7–7  |

|   |         |                                                 |      |

|   | 7.3.8                                                                                                                        | PCI Master Timeout                                                                                                                                                                                                                                                                                                                                 | 7–7                                                                                             |

|---|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|   | 7.3.9                                                                                                                        | Address Stepping in Configuration Cycles                                                                                                                                                                                                                                                                                                           | 7–7                                                                                             |

|   | 7.4                                                                                                                          | Address Space of Control/Status Registers                                                                                                                                                                                                                                                                                                          | 7–7                                                                                             |

|   | 7.5                                                                                                                          | Description of CSRs                                                                                                                                                                                                                                                                                                                                | 7–9                                                                                             |

|   | 7.5.1                                                                                                                        | Diagnostic Control/Status Register                                                                                                                                                                                                                                                                                                                 | 7–9                                                                                             |

|   | 7.5.2                                                                                                                        | PCI Error Address Register                                                                                                                                                                                                                                                                                                                         | 7–13                                                                                            |

|   | 7.5.3                                                                                                                        | System Bus Error Address Register                                                                                                                                                                                                                                                                                                                  | 7–14                                                                                            |

|   | 7.5.4                                                                                                                        | Dummy Registers 1 Through 3                                                                                                                                                                                                                                                                                                                        | 7–15                                                                                            |

|   | 7.5.5                                                                                                                        | Translated Base Registers 1 and 2                                                                                                                                                                                                                                                                                                                  | 7–15                                                                                            |

|   | 7.5.6                                                                                                                        | PCI Base Registers 1 and 2                                                                                                                                                                                                                                                                                                                         | 7–16                                                                                            |

|   | 7.5.7                                                                                                                        | PCI Mask Registers 1 and 2                                                                                                                                                                                                                                                                                                                         | 7–17                                                                                            |

|   | 7.5.8                                                                                                                        | Host Address Extension Register 0                                                                                                                                                                                                                                                                                                                  | 7–18                                                                                            |

|   | 7.5.9                                                                                                                        | Host Address Extension Register 1                                                                                                                                                                                                                                                                                                                  | 7–18                                                                                            |

|   | 7.5.10                                                                                                                       | Host Address Extension Register 2                                                                                                                                                                                                                                                                                                                  | 7–19                                                                                            |

|   | 7.5.11                                                                                                                       | PCI Master Latency Timer Register                                                                                                                                                                                                                                                                                                                  | 7–20                                                                                            |

|   | 7.5.12                                                                                                                       | TLB Tag Registers 0 Through 7                                                                                                                                                                                                                                                                                                                      | 7–20                                                                                            |

|   | 7.5.13                                                                                                                       | TLB Data Registers 0 Through 7                                                                                                                                                                                                                                                                                                                     | 7–21                                                                                            |

|   | 7.5.14                                                                                                                       | Translation Buffer Invalidate All Register:                                                                                                                                                                                                                                                                                                        |                                                                                                 |

|   |                                                                                                                              | 0x1A0000400                                                                                                                                                                                                                                                                                                                                        | 7–22                                                                                            |

| 8 | PCI bu                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                 |

|   |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                 |

|   | 8.1                                                                                                                          | Ethernet Controller                                                                                                                                                                                                                                                                                                                                | 8–3                                                                                             |

|   | 8.1.1                                                                                                                        | PCI Configuration Registers                                                                                                                                                                                                                                                                                                                        | 8–3                                                                                             |

|   | 8.1.1<br>8.1.2                                                                                                               | PCI Configuration Registers Ethernet Controller CSRs                                                                                                                                                                                                                                                                                               | 8–3<br>8–4                                                                                      |

|   | 8.1.1<br>8.1.2<br>8.1.3                                                                                                      | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles                                                                                                                                                                                                                                                                                    | 8–3<br>8–4<br>8–5                                                                               |

|   | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4                                                                                             | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address                                                                                                                                                                                                                                                                   | 8–3<br>8–4<br>8–5<br>8–6                                                                        |

|   | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2                                                                                      | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address SCSI Controller                                                                                                                                                                                                                                                   | 8–3<br>8–4<br>8–5<br>8–6                                                                        |

|   | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1                                                                             | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address SCSI Controller Connection and Termination                                                                                                                                                                                                                        | 8–3<br>8–4<br>8–5<br>8–6<br>8–6                                                                 |

|   | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2                                                                    | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address SCSI Controller Connection and Termination SCSI ID                                                                                                                                                                                                                | 8–3<br>8–4<br>8–5<br>8–6<br>8–6<br>8–6                                                          |

|   | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3                                                           | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address  SCSI Controller Connection and Termination SCSI ID Programming                                                                                                                                                                                                   | 8–3<br>8–4<br>8–5<br>8–6<br>8–6<br>8–7<br>8–7                                                   |

|   | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4                                                  | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address  SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers                                                                                                                                                                       | 8-3<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7                                            |

|   | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5                                         | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address  SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers SCSI Control Status Registers                                                                                                                                         | 8-3<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7<br>8-8                                     |

|   | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4                                                  | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address  SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers                                                                                                                                                                       | 8-3<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7                                            |

| 9 | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5                                         | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address  SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers SCSI Control Status Registers                                                                                                                                         | 8–3<br>8–4<br>8–5<br>8–6<br>8–6<br>8–7<br>8–7<br>8–7<br>8–7                                     |

| 9 | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.3                                  | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers SCSI Control Status Registers PCI I/O Companion Card  Nbus Address Space                                                                                               | 8–3<br>8–4<br>8–5<br>8–6<br>8–6<br>8–7<br>8–7<br>8–7<br>8–7                                     |

| 9 | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.3                                  | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers SCSI Control Status Registers PCI I/O Companion Card  Nbus Address Space                                                                                               | 8-3<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7<br>8-7<br>8-8<br>8-11                      |

| 9 | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.3                                  | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers SCSI Control Status Registers PCI I/O Companion Card                                                                                                                   | 8-3<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7<br>8-7<br>8-8<br>8-11                      |

| 9 | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.3<br><b>Nbus</b> 9.1 9.1.1         | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address  SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers SCSI Control Status Registers PCI I/O Companion Card  Nbus Address Space SIO Chip PCI Configuration Space                                                             | 8-3<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7<br>8-7<br>8-11                             |

| 9 | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.3<br><b>Nbus</b> 9.1 9.1.1         | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address  SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers SCSI Control Status Registers PCI I/O Companion Card  Nbus Address Space SIO Chip PCI Configuration Space PCI Control Register                                        | 8-3<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7<br>8-7<br>8-11<br>9-1<br>9-2<br>9-3        |

| 9 | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.3<br><b>Nbus</b> 9.1 9.1.1 9.1.1.1 | PCI Configuration Registers Ethernet Controller CSRs PCI Cycles Ethernet Address  SCSI Controller Connection and Termination SCSI ID Programming PCI Configuration Registers SCSI Control Status Registers PCI I/O Companion Card  Nbus Address Space SIO Chip PCI Configuration Space PCI Control Register ISA Controller Recovery Timer Register | 8-3<br>8-4<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7<br>8-8<br>8-11<br>9-1<br>9-2<br>9-3<br>9-4 |

|    | 9.2.1<br>9.2.2<br>9.2.3<br>9.2.4 | Module Display Control Register                      | 9–5<br>9–6<br>9–8            |

|----|----------------------------------|------------------------------------------------------|------------------------------|

|    | 9.2.5<br>9.2.6                   | Identification Register       Reset Reason Registers | 9–8<br>9–12<br>9–14          |

|    | 9.2.7                            | Heartbeat Register                                   | 9–14                         |

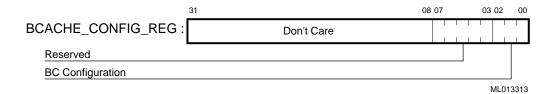

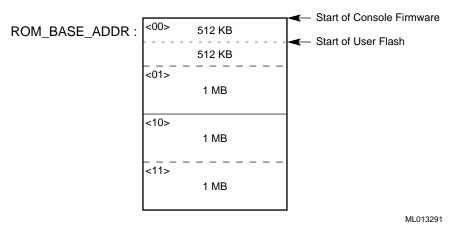

|    | 9.2.8<br>9.3                     | Bcache Configuration Register                        | 9–16<br>9–17                 |

|    | 9.4<br>9.4.1<br>9.4.2            | Super I/O Chip                                       | 9–18<br>9–18<br>9–19         |

|    | 9.5<br>9.6                       | Keyboard and Mouse Controller                        | 9–21<br>9–22                 |

|    | 9.6.1<br>9.6.2                   | TOY Clock Timekeeping Registers                      | 9–23<br>9–24                 |

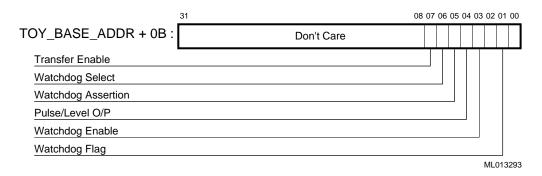

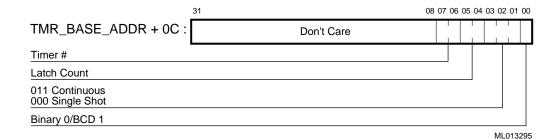

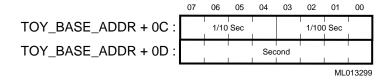

|    | 9.7<br>9.7.1<br>9.7.2            | Interval Timing Registers                            | 9–25<br>9–26<br>9–28         |

|    | 9.7.3<br>9.7.4                   | Timer Modes                                          | 9–29<br>9–31                 |

|    | 9.7.5<br>9.8                     | Timer Interrupt Status Registers                     | 9–32<br>9–33                 |

| 10 | 9.9                              | Nonvolatile RAM                                      | 9–36                         |

| ıu | 10.1                             | VMEbus Master                                        | 10–2                         |

|    | 10.1.1<br>10.1.1.                | Outbound Scatter-Gather Mapping                      | 10–4<br>10–6                 |

|    | 10.1.1.<br>10.1.2<br>10.1.2.     | Data Transfers                                       | 10–6<br>10–7<br>10–7         |

|    | 10.1.2.<br>10.1.3<br>10.2        |                                                      | 10–7<br>10–7<br>10–9<br>10–9 |

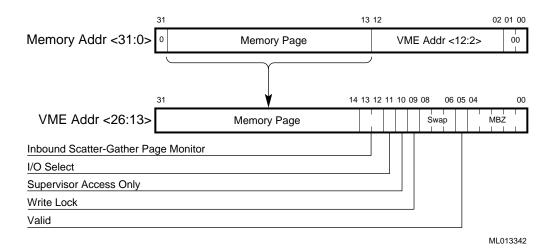

|    | 10.2.1<br>10.2.2                 | Decoding Addresses Inbound Scatter-Gather Entries    | 10–10<br>10–12               |

|    |                                  |                                                      |                              |

|     | 10.2.3.1 | Interprocessor Communication Registers              | 10–14 |

|-----|----------|-----------------------------------------------------|-------|

|     | 10.2.3.2 | Interprocessor Communication Global Switches        | 10–14 |

|     | 10.2.3.3 | Interprocessor Communication Module                 |       |

|     |          | Switches                                            | 10–15 |

|     | 10.3 Sy  | stem Controller Operation                           | 10–17 |

|     | 10.3.1   | Arbitrating the VMEbus                              | 10–18 |

|     | 10.3.1.1 | Requesting the VMEbus                               | 10–18 |

|     | 10.3.1.2 | Releasing the VMEbus                                | 10–19 |

|     | 10.3.2   | System Clock Output                                 | 10–21 |

|     | 10.3.3   | Timeout Timers                                      | 10–21 |

|     | 10.3.3.1 | Arbitration Timers                                  | 10–21 |

|     | 10.3.3.2 | VMEbus Transfer Timers                              | 10-22 |

|     | 10.3.3.3 | Local Bus Transfer Timer                            | 10-23 |

|     | 10.3.4   | VMEbus Interrupt Handling                           | 10-23 |

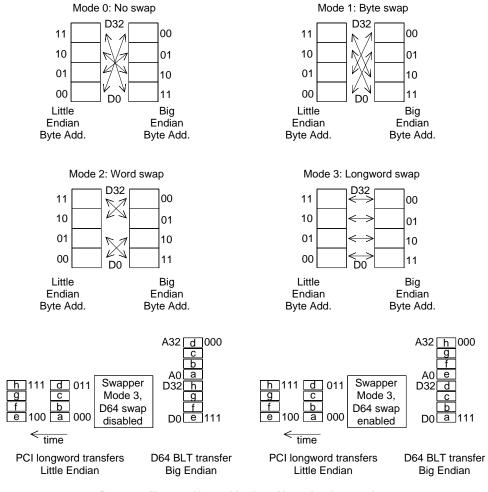

|     | 10.4 By  | rte Swapping                                        | 10-26 |

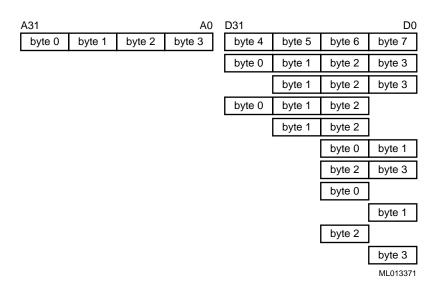

|     | 10.4.1   | DC7407 Byte Swapping                                | 10-26 |

|     | 10.4.2   | VIC64 Byte Swapping                                 | 10-27 |

|     | 10.5 In  | itializing the VME Interface                        | 10-30 |

|     | 10.5.1   | VME PCI Configuration Registers                     | 10-30 |

|     | 10.5.2   | Programming Scatter-Gather RAM                      | 10-31 |

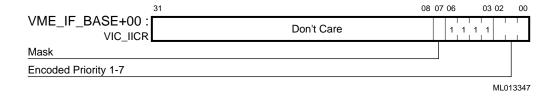

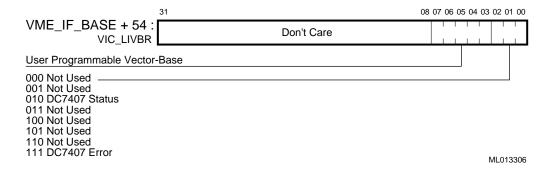

|     | 10.5.3   | Configuring the VIC64                               | 10-32 |

|     | 10.6 Su  | Immary of VME Interface Registers                   | 10-37 |

|     | 10.7 VN  | ME Subsystem Restrictions (as of 03-Jun-94)         | 10-40 |

|     | 10.7.1   | Collision of VIC64 Master Write Posting with Master |       |

|     |          | Block Transfers                                     | 10-40 |

|     | 10.7.2   | VIC64 Errata: A16 Master Cycles During              |       |

|     |          | Interleave                                          | 10-40 |

|     |          |                                                     |       |

| 11  | System   | Interrupts                                          |       |

| • • | System   | interrupts                                          |       |

|     |          | stem Interrupts                                     | 11–1  |

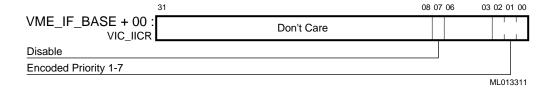

|     | 11.1.1   | Xilinx Interrupt Controller                         | 11–2  |

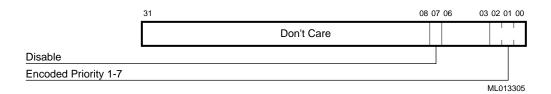

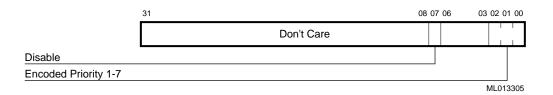

|     | 11.1.2   | VIC64 Chip System Interrupt Controller              | 11–4  |

|     | 11.1.2.1 | Basic Operation                                     | 11–5  |

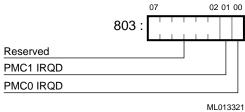

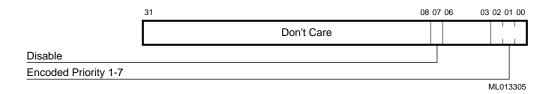

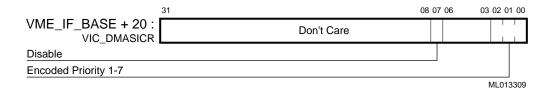

|     | 11.1.3   | VIC64 Chip Interrupt Sources                        | 11–6  |

|     | 11.1.3.1 | Local Device Interrupts                             | 11–6  |

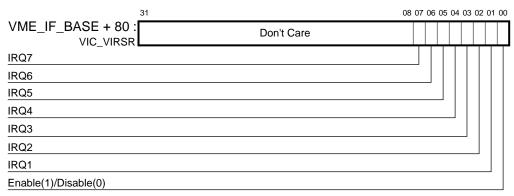

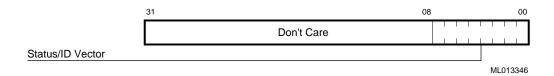

|     | 11.1.3.2 | VMEbus Interrupt Requests                           | 11–7  |

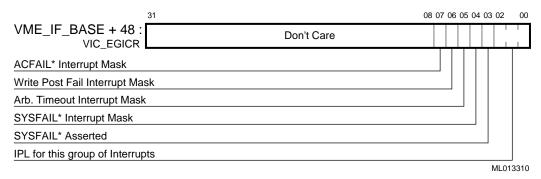

|     | 11.1.3.3 | Status/Error Interrupts                             | 11–8  |

|     | 11.1.4   | SIO Chip Programmable Interrupt Controller          | 11–11 |

|     | 11.1.4.1 | Nonmaskable System Events                           | 11–11 |

|     | 11.1.4.2 | NMI Status and Control Register                     | 11–12 |

|     | 11.1.4.3 | EPIC Interrupt                                      | 11–13 |

|     |          | •                                                   |       |

Interprocessor Communication.....

10.2.3

10–14

|    | 11.2                                                                         | Module Reset                                                                                                                                                                                                              | 11–13                                                                                               |

|----|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 12 | Cons                                                                         | ole Primer                                                                                                                                                                                                                |                                                                                                     |

|    | 12.1<br>12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>12.2<br>12.3<br>12.4         | About the Console Console Features Command Overview Shell Operators Using Flow Control Getting Information About the System Getting Help Examining and Depositing to Memory or System Registers                           | 12–1<br>12–1<br>12–2<br>12–3<br>12–4<br>12–5                                                        |

|    | 12.4.1<br>12.4.2<br>12.5<br>12.6<br>12.7<br>12.7.1<br>12.7.2<br>12.8<br>12.9 | Accessing Memory Examining Registers Using Pipes and grep to Filter Output Using I/O Redirection (>) Running Commands in Background Monitoring Status Killing a Process Creating Scripts Copying Scripts Over the Network | 12–7<br>12–9<br>12–10<br>12–12<br>12–13<br>12–13<br>12–14<br>12–14<br>12–15                         |

| 13 | Cons                                                                         | ole Commands                                                                                                                                                                                                              |                                                                                                     |

|    | 13.1<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4                                 | Console Commands Special Keys Command Line Characteristics Radix Control Console Command Dictionary alloc boot break cat chmod chown clear clear_log date deposit dynamic                                                 | 13–1<br>13–2<br>13–2<br>13–3<br>13–4<br>13–14<br>13–15<br>13–16<br>13–18<br>13–20<br>13–21<br>13–21 |

| echo            | 13-30 |

|-----------------|-------|

|                 |       |

| eval            | 13–32 |

| examine         | 13–34 |

| exer            | 13–40 |

| exit            | 13–49 |

| false           | 13–50 |

| free            | 13–51 |

| grep            | 13–52 |

| hd              | 13–55 |

| help            | 13–57 |

| init_ev         | 13–59 |

| initialize      | 13–60 |

| kill            | 13–61 |

| line            | 13–62 |

| ls              | 13–63 |

| memexer         | 13-64 |

| memtest         | 13–65 |

| net             | 13–72 |

| ps              | 13–75 |

| pwrup           | 13–76 |

| rm              | 13–77 |

| sa              | 13–78 |

| semaphore       | 13-79 |

| set             | 13-80 |

| set led         | 13-83 |

| set reboot srom | 13-84 |

| set toy sleep   | 13-85 |

| sh              | 13-86 |

| show            | 13–88 |

| show config     | 13-90 |

| show device     | 13–91 |

| show hwrpb      | 13–93 |

| show led        | 13–94 |

| show map        | 13–95 |

| show_log        | 13–96 |

| sleep           | 13–98 |

| sort            | 13–99 |

|                 |       |

|     |                                                                       | spstartstop                                                                                                                                                                                                                                                                                                                                                                                 | 13–100<br>13–101<br>13–102                                         |

|-----|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|     |                                                                       | update                                                                                                                                                                                                                                                                                                                                                                                      | 13–103                                                             |

| Α   | Modul                                                                 | e Connector Pinouts                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

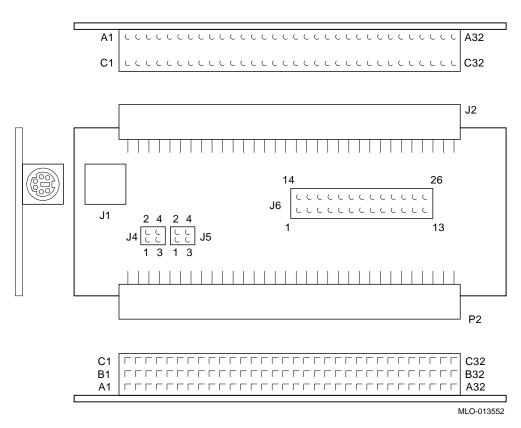

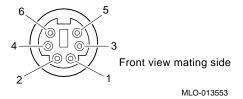

|     | A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.3<br>A.4<br>A.4.1<br>A.4.2 | CPU Connector Pinouts  I/O Type 1 Card Connector Pinouts  VMEbus (J1) Connector Pinouts  Console (J6) and Serial (J7) Connector Pinouts  Ethernet (J9) Connector Pinouts  Primary Breakout Module Connector Pinouts  Secondary Breakout Module Connector Pinouts  Keyboard and Mouse (J1) Connector Pinouts  Parallel Port (J6) Connector Pinouts  PMC I/O Companion Card Connector Pinouts | A-1<br>A-1<br>A-2<br>A-3<br>A-4<br>A-4<br>A-6<br>A-7<br>A-8<br>A-9 |

|     | dex                                                                   |                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

| Fiç | gures                                                                 |                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

|     | 1–1                                                                   | Digital Alpha VME 4 Block Diagram                                                                                                                                                                                                                                                                                                                                                           | 1–3                                                                |

|     | 2–1                                                                   | Digital Alpha VME 4 Module Components                                                                                                                                                                                                                                                                                                                                                       | 2–2                                                                |

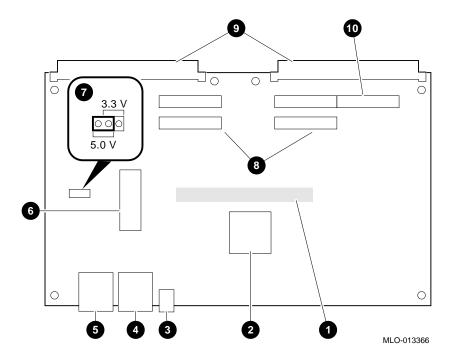

|     | 2–2                                                                   | Digital Alpha VME 4 Module Layout                                                                                                                                                                                                                                                                                                                                                           | 2–7                                                                |

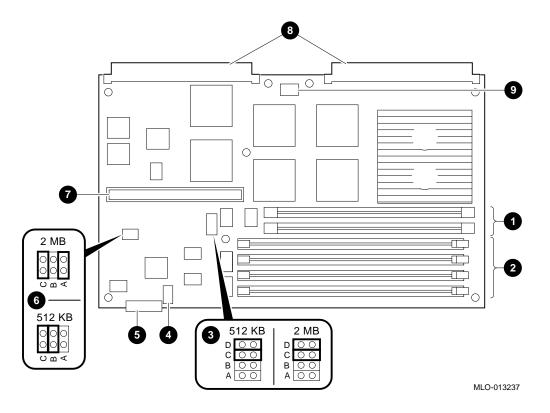

|     | 2–3                                                                   | I/O Module Layout                                                                                                                                                                                                                                                                                                                                                                           | 2–8                                                                |

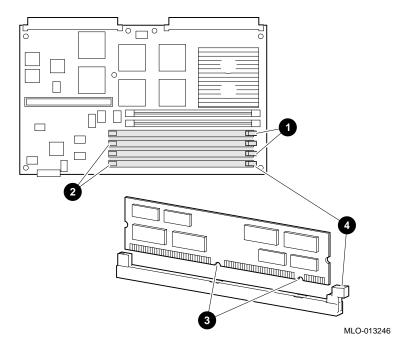

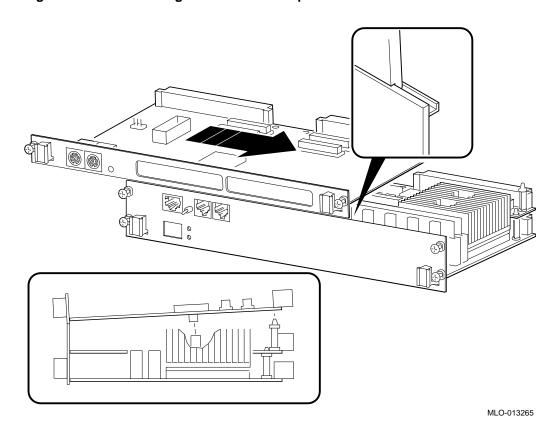

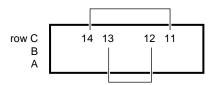

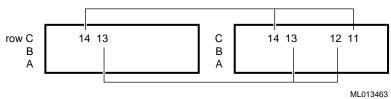

|     | 2–4                                                                   | Installing the Main Memory Modules                                                                                                                                                                                                                                                                                                                                                          | 2–11                                                               |

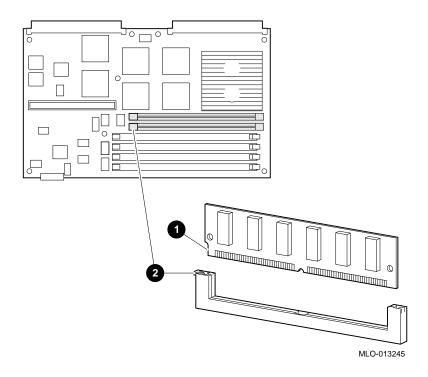

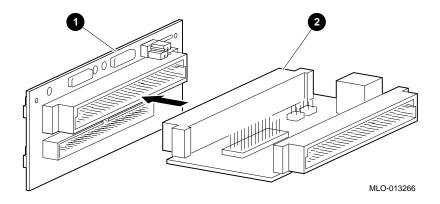

|     | 2–5                                                                   | Cache Memory Modules                                                                                                                                                                                                                                                                                                                                                                        | 2–13                                                               |

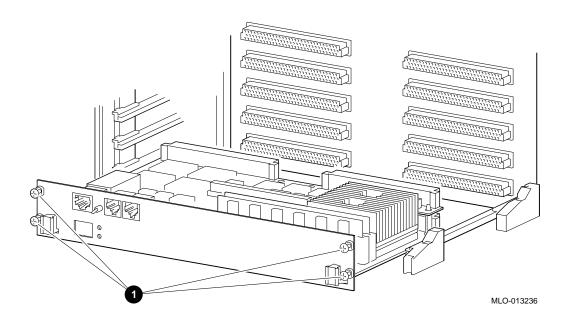

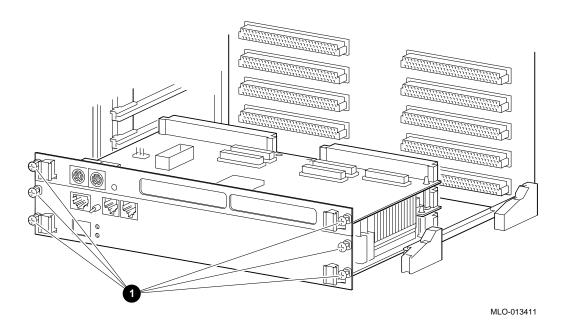

|     | 2–6                                                                   | Installing the Digital Alpha VME 4 Module                                                                                                                                                                                                                                                                                                                                                   | 2–15                                                               |

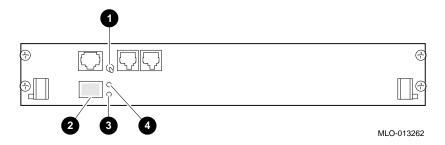

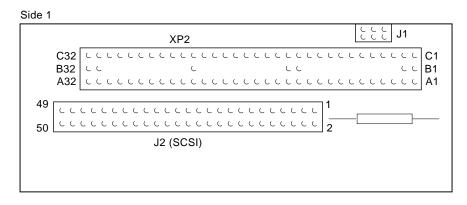

|     | 2–7                                                                   | Alpha VME 4 Primary Breakout Module                                                                                                                                                                                                                                                                                                                                                         | 2–16                                                               |

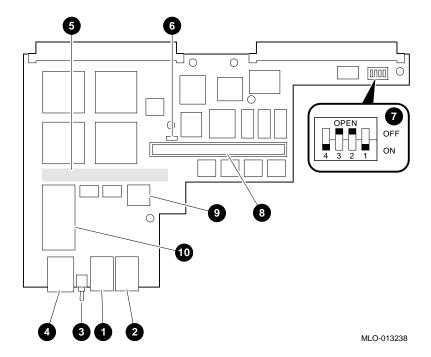

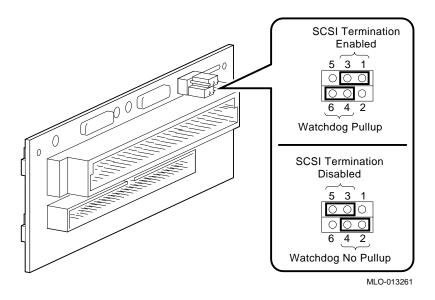

|     | 2–8                                                                   | Primary Breakout Module Jumpers                                                                                                                                                                                                                                                                                                                                                             | 2–17                                                               |

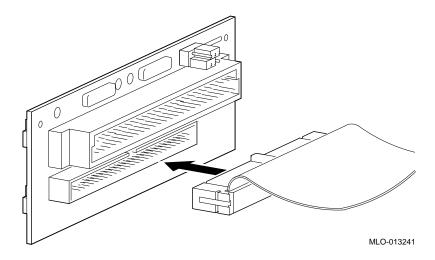

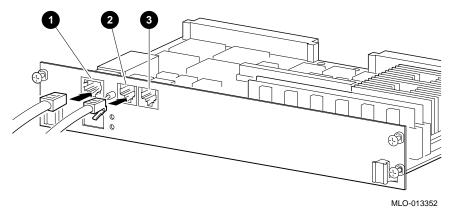

|     | 2–9                                                                   | Connecting the SCSI Cable to the Primary Breakout Module                                                                                                                                                                                                                                                                                                                                    | 2–18                                                               |

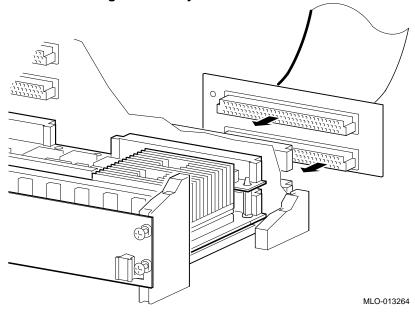

|     | 2–10                                                                  | Installing the Primary Breakout Module                                                                                                                                                                                                                                                                                                                                                      | 2–19                                                               |

|     | 2–11                                                                  | Secondary Breakout Module Jumpers                                                                                                                                                                                                                                                                                                                                                           | 2–20                                                               |

|     | 2–12                                                                  | Connecting the Secondary Breakout Module to the                                                                                                                                                                                                                                                                                                                                             |                                                                    |

|     |                                                                       | Primary Breakout Module                                                                                                                                                                                                                                                                                                                                                                     | 2–21                                                               |

|     | 2-13                                                                  | Connecting Network and Console Terminal Cables                                                                                                                                                                                                                                                                                                                                              | 2–22                                                               |

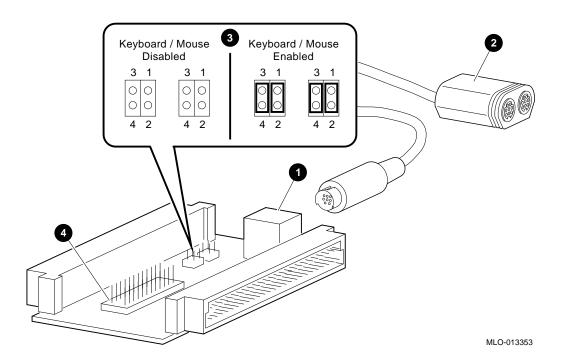

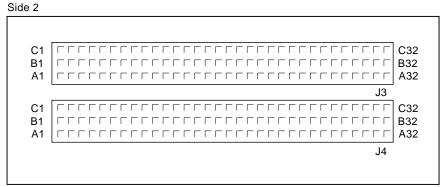

|     | 2–14                                                                  | PMC I/O Companion Card Layout                                                                                                                                                                                                                                                                                                                                                               | 2-23                                                               |

| 2–15 | Connecting the PMC I/O Companion Card                | 2–26 |

|------|------------------------------------------------------|------|

| 2–16 | Installing the PMC I/O Companion Card                | 2–27 |

| 3–1  | Controls and Indicators                              | 3–2  |

| 4–1  | Loopback Descriptions for Interval Timer Test 3 and  |      |

|      | 4                                                    | 4–15 |

| 4–2  | LAN Address ROM Format                               | 4–23 |

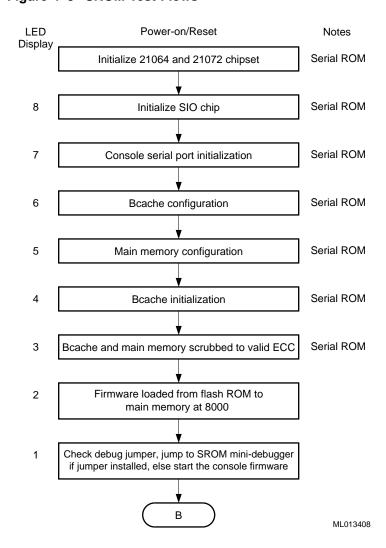

| 4–3  | SROM Test Flows                                      | 4-30 |

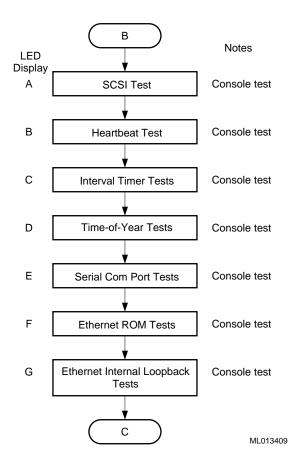

| 4–4  | Console POST Flows                                   | 4–31 |

| 4–5  | Console POST Flows                                   | 4-32 |

| 5–1  | System Bus Address Map                               | 5–2  |

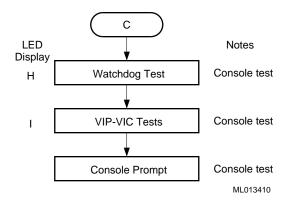

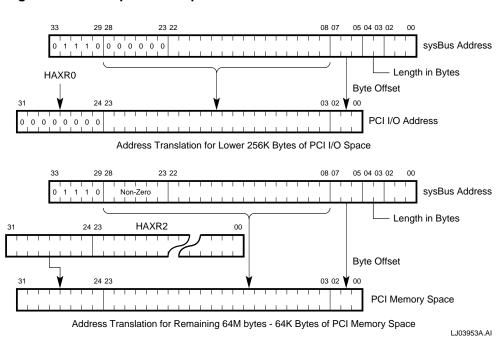

| 5–2  | PCI Sparse I/O Space Address Translation             | 5–6  |

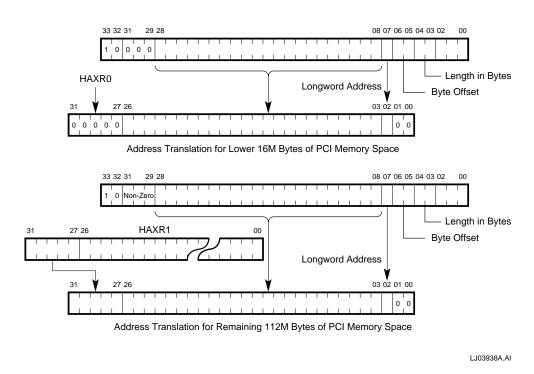

| 5–3  | PCI Memory Space Address Translation                 | 5–12 |

| 5–4  | PCI Target Window Compare Scheme                     | 5–17 |

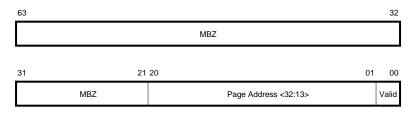

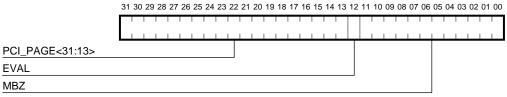

| 5–5  | Scatter-Gather Map Page Table Entry in Memory        | 5–19 |

| 5–6  | Scatter-Gather Map Translation of PCI Bus Address to |      |

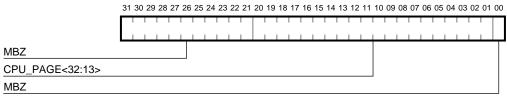

|      | System Bus Address                                   | 5–21 |

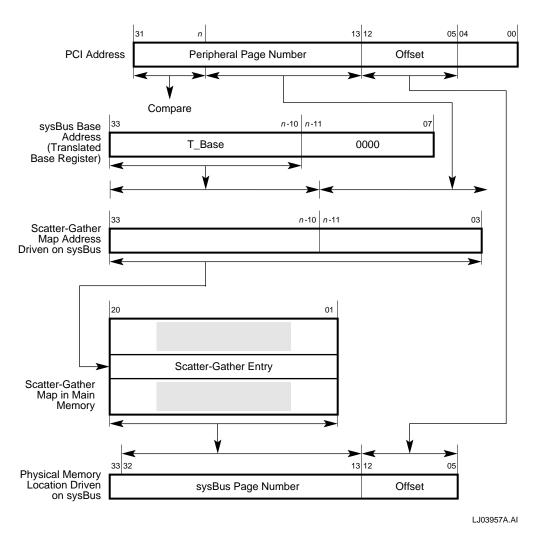

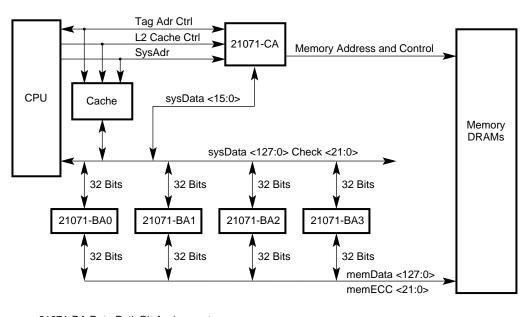

| 6–1  | Cache and Memory Subsystem                           | 6–1  |

| 6–2  | Address and Data Paths of Cache and Memory           | 6–2  |

| 6–3  | 21071-CA Block Diagram                               | 6–3  |

| 6–4  | Cache Subsystem for a 2 MB Cache                     | 6–5  |

| 6–5  | Maximum and Minimum DIMM Bank Layouts                | 6–6  |

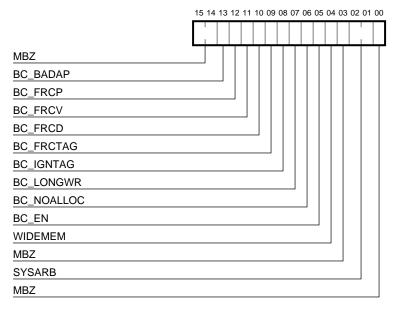

| 6–6  | General Control Register: 0x180000000                | 6–11 |

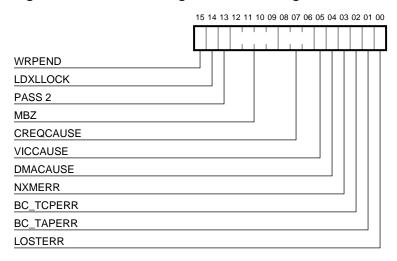

| 6–7  | Error and Diagnostic Status Register:                |      |

|      | 0x180000020                                          | 6–14 |

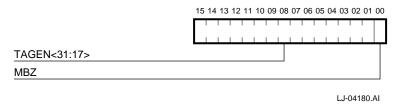

| 6–8  | Tag Enable Register: 0x180000060                     | 6–16 |

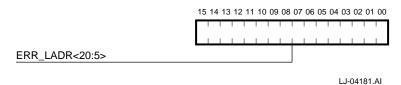

| 6–9  | Error Low Address Register: 0x180000080              | 6–19 |

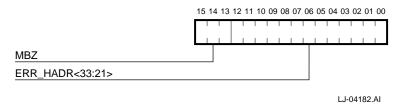

| 6–10 | Error High Address Register: 0x1800000A0             | 6–19 |

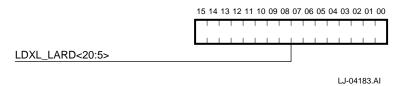

| 6–11 | LDx_L Low Address Register: 0x1800000C0              | 6–20 |

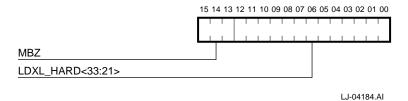

| 6–12 | LDx_L High Address Register: 0x1800000E0             | 6–20 |

| 6–13 | Presence Detect Low-Data Register: 0x180000280       | 6–21 |

| 6–14 | Presence Detect High-Data Register: 0x180000260      | 6–21 |

| 6–15 | Bank 0 Base Address Register: 0x180000800            | 6–22 |

| 6–16 | Configuration Registers for Bank Set 0:              |      |

|      | 0x180000A00                                          | 6–22 |

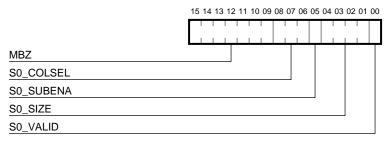

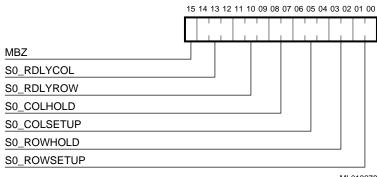

| 6–17 | Bank Set 0 Timing Register A: 0x180000C00            | 6–25 |

| 6–18 | Bank Set 0 Timing Register B: 0x180000E00            | 6–26 |

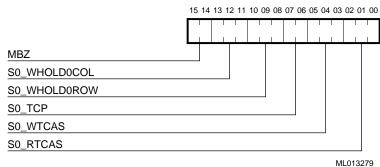

| 6–19 | Global Timing Register: 0x180000200                  | 6–28 |

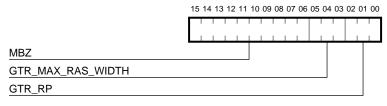

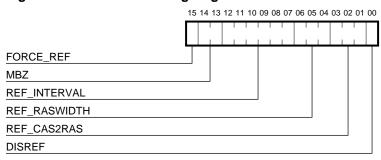

| 6-20 | Refresh Timing Register: 0x180000220                       | 6–29 |

|------|------------------------------------------------------------|------|

| 6–21 | Block Diagram of the DECchip 21071-BA                      | 6–30 |

| 7–1  | PCI Host Bridge                                            | 7–1  |

| 7–2  | DECchip 21071-DA Block Diagram                             | 7–2  |

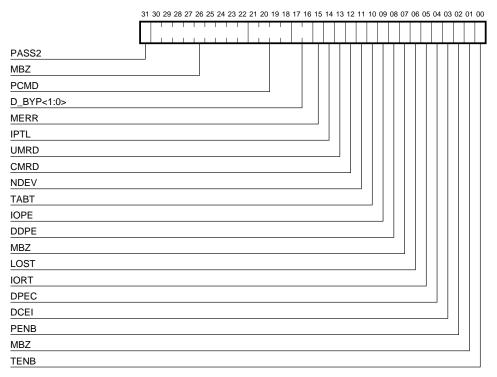

| 7–3  | Diagnostic Control/Status Register: 0x1A0000000            | 7–10 |

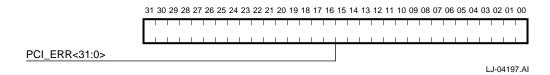

| 7–4  | PCI Error Address Register: 0x1A0000020                    | 7–14 |

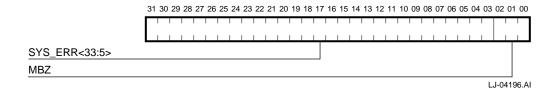

| 7–5  | System Bus Error Address Register: 0x1A0000040             | 7–14 |

| 7–6  | Translated Base Registers 1, 2: 0x1A00000C0,               |      |

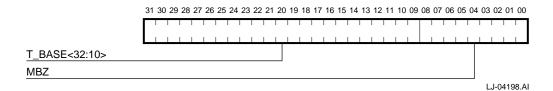

|      | 0x1A00000E0                                                | 7–15 |

| 7–7  | PCI Base Registers 1 and 2: 0x1A0000100,                   |      |

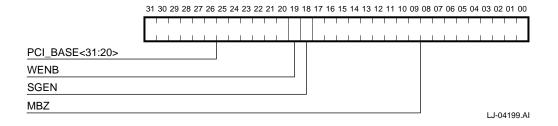

|      | 0x1A0000120                                                | 7–16 |

| 7–8  | PCI Mask Registers 1 and 2: 0x1A0000140,                   | 7 47 |

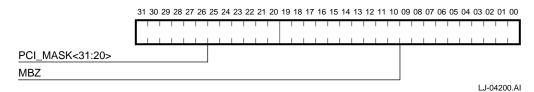

|      | 0x1A0000160                                                | 7–17 |

| 7–9  | Host Address Extension Register 0: 0x1A0000180             | 7–18 |

| 7–10 | Host Address Extension Register 1: 0x1A00001A0             | 7–18 |

| 7–11 | Host Address Extension Register 2: 0x1A00001C0             | 7–19 |

| 7–12 | PCI Master Latency Timer Register: 0x1A00001E0             | 7–20 |

| 7–13 | TLB Tag Registers 0 Through 7: 0x1A0000200 to 0x1A00002E0  | 7–21 |

| 7–14 | TLB Data Registers 0 Through 7: 0x1A0000300 to 0x1A00003E0 | 7–21 |

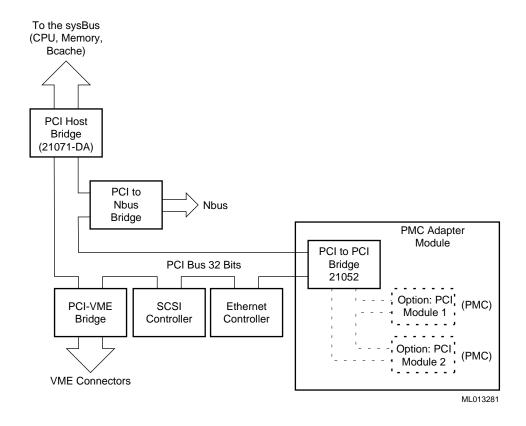

| 8–1  | PCI Bus and Interfaces to the I/O Subsystem                | 8–2  |

| 8–2  | PCI Configuration Registers                                | 8–4  |

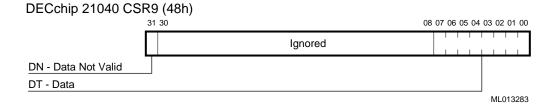

| 8–3  | DECchip 21040-AA CSR9 (ENET ROM Register)                  | 8–6  |

| 8–4  | PCI Configuration Block                                    | 8–8  |

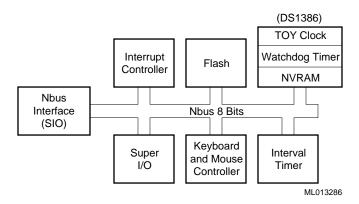

| 9–1  | Nbus and Nbus Resources                                    | 9–1  |

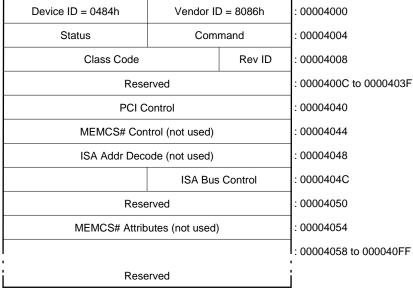

| 9–2  | SIO Configuration Block                                    | 9–3  |

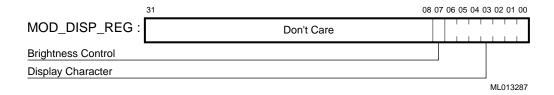

| 9–3  | Module Display Control Register                            | 9–6  |

| 9–4  | Display Character Set                                      | 9–6  |

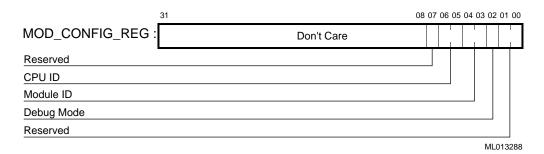

| 9–5  | Module Configuration Register                              | 9–7  |

| 9–6  | Memory Configuration Registers 0-3                         | 9–9  |

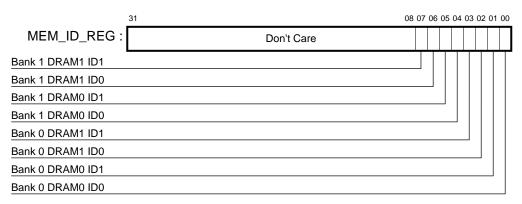

| 9–7  | Memory Identification Register                             | 9–10 |

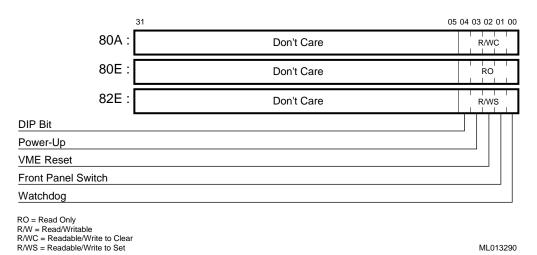

| 9–8  | Reset Reason Registers                                     | 9–13 |

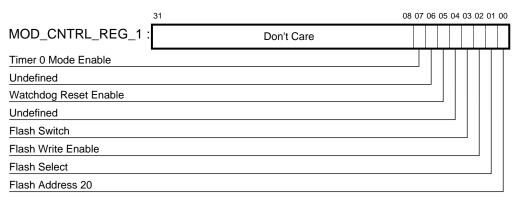

| 9–9  | Module Control Register 1                                  | 9–15 |

| 9–10 | Bcache Configuration Register                              | 9–16 |

| 9–11 | Flash ROM Layout/Addressing                                | 9–18 |

| 9–12 | TOY Clock Command Register                                 | 9–24 |

| 9–13 | 82C54 Control Byte                                         | 9–26 |

| -    | <b>,</b>                                                   |      |

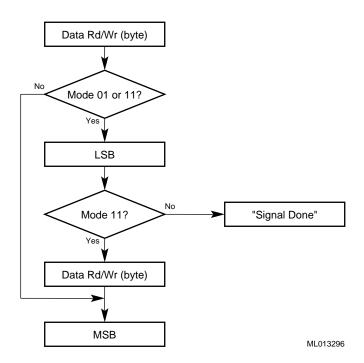

| 9–14  | 82C54 Timer Data Access                       | 9–28  |

|-------|-----------------------------------------------|-------|

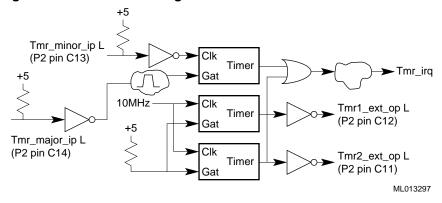

| 9–15  | Timer Clocking                                | 9–31  |

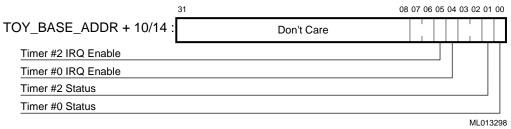

| 9–16  | Timer Interrupt Status Register               | 9–32  |

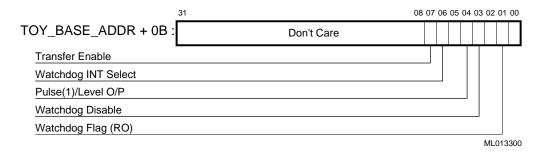

| 9–17  | Watchdog Timer Registers                      | 9-34  |

| 9–18  | Watchdog Timer TOY Clock Command Register     | 9–34  |

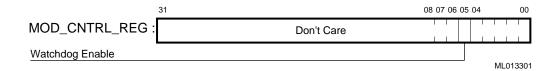

| 9–19  | Watchdog Timer Module Control Register        | 9–35  |

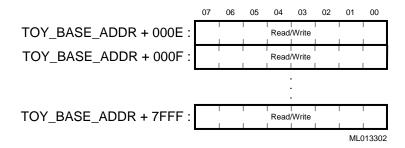

| 9–20  | NVRAM Access                                  | 9–36  |

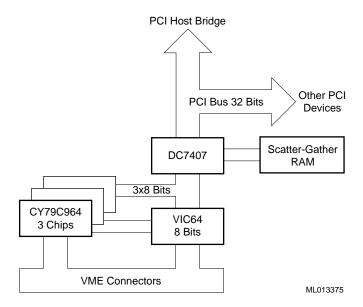

| 10–1  | VME Interface Block Diagram                   | 10–1  |

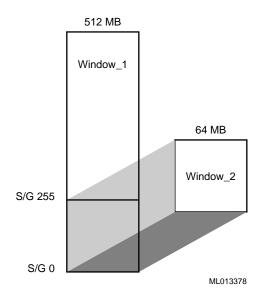

| 10–2  | Mapping Window_1 and Window_2                 | 10–3  |

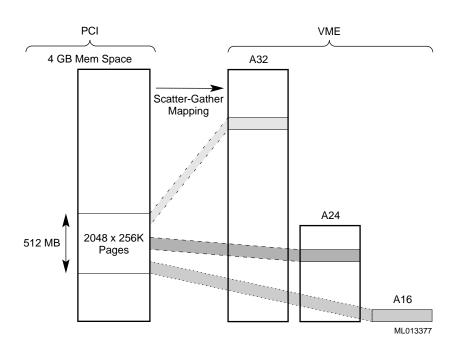

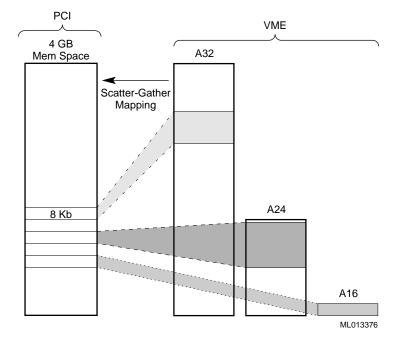

| 10–3  | Mapping Pages From PCI to VME                 | 10–4  |

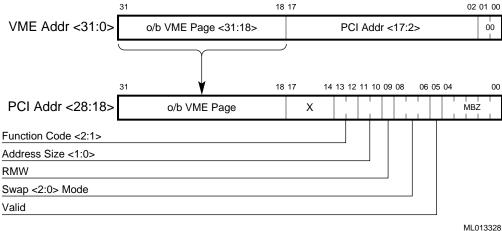

| 10–4  | Outbound Scatter-Gather Entry                 | 10–5  |

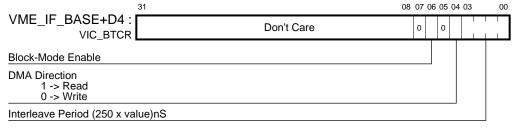

| 10–5  | VIC Block Transfer Control Register           | 10–8  |

| 10–6  | Mapping Pages of Memory from VMEbus to PCI    |       |

|       | Bus                                           | 10–10 |

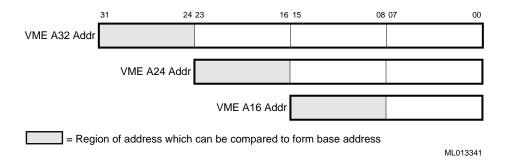

| 10–7  | Address Decoding                              | 10–11 |

| 10–8  | Base and Mask Register                        | 10–11 |

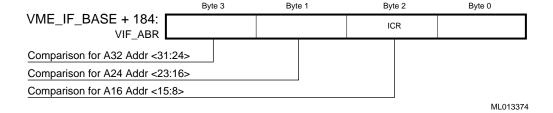

| 10–9  | Inbound Scatter-Gather Entry With A32 Address |       |

|       | Mapping                                       | 10–12 |

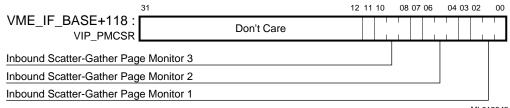

| 10–10 | VME Interface Processor Page Monitor CSR      | 10–13 |

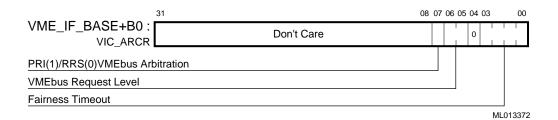

| 10–11 | VIC Arbiter/Requester Configuration Register  | 10–18 |

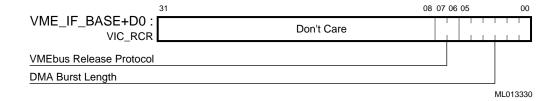

| 10–12 | VIC Release Control Register                  | 10–20 |

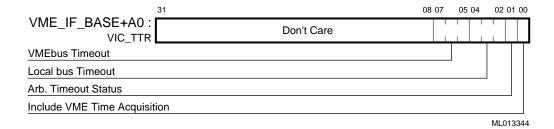

| 10–13 | VMEbus Transfer Timeout Register              | 10–22 |

| 10–14 | VIC Interrupt Request/Status Register         | 10–24 |

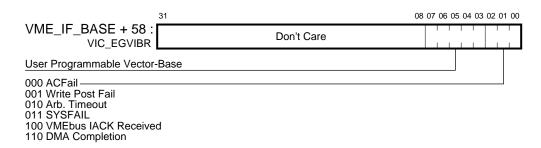

| 10–15 | VMEbus Interrupt Vector Base Registers        | 10–25 |

| 10–16 | VMEbus Interrupter Interrupt Control Register | 10–25 |

| 10–17 | Swap Modes                                    | 10–27 |

| 10–18 | Big Endian VME Byte Lane Formats              | 10–28 |

| 11–1  | Block Diagram of the Interrupt Logic          | 11–2  |

| 11–2  | Interrupt/Mask Register #1                    | 11–3  |

| 11–3  | Interrupt/Mask Register #2                    | 11–3  |

| 11–4  | Interrupt/Mask Register #3                    | 11–4  |

| 11–5  | Interrupt/Mask Register #4                    | 11–4  |

| 11–6  | Generic ICR                                   | 11–5  |

| 11–7  | Device ICRs                                   | 11–7  |

| 11–8  | VIC Local Interrupt Vector Base Register      | 11–7  |

| 11–9  | VME IRQ* ICRs                                 | 11–8  |

| 11–10 | DMA Status ICR                                | 11–9  |

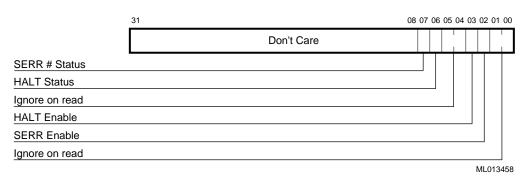

| 11–11  | VIC Error Group ICR                                            | 11–10 |

|--------|----------------------------------------------------------------|-------|

| 11–12  | VMEbus Interrupter ICR                                         | 11–10 |

| 11–13  | VIC Error Group Interrupt Vector Base Register                 | 11–11 |

| 11–14  | NMI Status and Control Register                                | 11–12 |

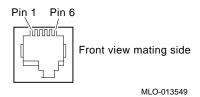

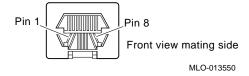

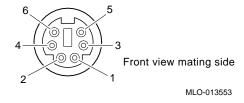

| A-1    | Console (J6) and Serial (J7) Connector Pinouts                 | A-3   |

| A-2    | Ethernet (J9) Connector Pinouts                                | A-4   |

| A-3    | Primary Breakout Module Connector Pinouts                      | A-6   |

| A-4    | Secondary Breakout Module Connector Pinouts                    | A-7   |

| A-5    | Keyboard and Mouse (J1) Pinouts                                | A-8   |

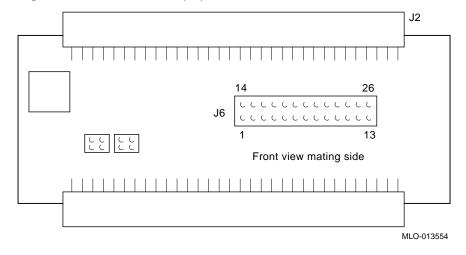

| A-6    | Parallel Port (J6) Connector Pinouts                           | A-9   |

| A-7    | PMC I/O Companion Card Mouse (J2) and Keyboard                 |       |

|        | (J3) Connector Pinouts                                         | A-10  |

| Tables |                                                                |       |

| 1–1    | Digital Alpha VME 4 Functional Specifications                  | 1–2   |

| 1–2    | Physical and Environmental Specifications                      | 1–4   |

| 1–3    | Typical Peak Power Supply Current and Module Power Dissipation | 1–5   |

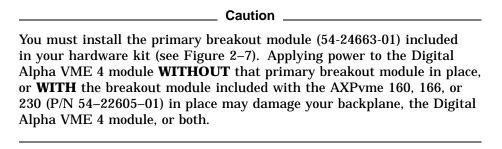

| 2–1    | Digital Alpha VME 4 Hardware Kit Items                         | 2–3   |

| 2–2    | Digital Alpha VME 4 Memory Modules                             | 2–4   |

| 2–3    | Digital Alpha VME 4 Cache Memory Modules                       | 2–4   |

| 2–4    | Additional Hardware Installation Items                         | 2–5   |

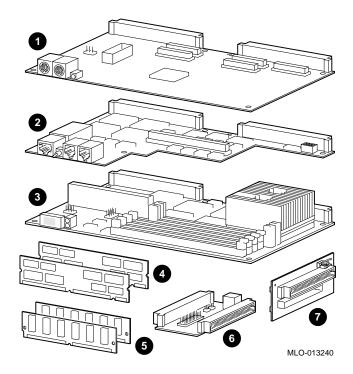

| 2–5    | Digital Alpha VME 4 Module Configuration Switches              | 2–9   |

| 2–6    | Supported Switch Settings for Digital Alpha VME 4              | 2–9   |

| 2 0    | Modules in Slot 1 (System Controller)                          | 2–9   |

| 2–7    | Supported Switch Settings for Digital Alpha VME                |       |

|        | 4 Modules in Other Than Slot 1 (Nonsystem                      |       |

|        | Controller)                                                    | 2–10  |

| 2–8    | Digital Alpha VME 4 Memory Configurations                      | 2–12  |

| 2–9    | J9 Cache Jumper Settings                                       | 2–13  |

| 2–10   | J10 Cache Jumper Settings                                      | 2–14  |

| 2–11   | SROM Test Numbers and Descriptions                             | 2–28  |

| 2–12   | Console Code Test Letters and Names                            | 2–29  |

| 2–13   | Troubleshooting                                                | 2–31  |

| 2–14   | Products With a 1 Year Return to Digital Warranty              | 2-32  |

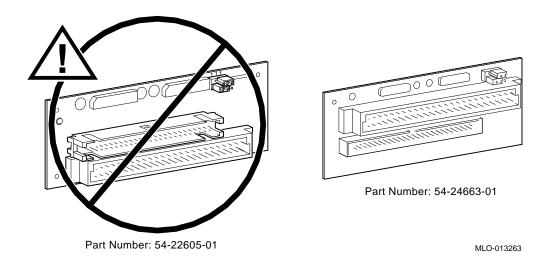

| 2-15   | Field Replaceable Units and Order Numbers                      | 2-35  |

| 3–1  | Controls and Indicators                            | 3–2  |

|------|----------------------------------------------------|------|

| 3–2  | Environment Variable Summary                       | 3–4  |

| 4–1  | Console Diagnostic Tests                           | 4–3  |

| 5–1  | System Bus Address Space Description               | 5–3  |

| 5–2  | PCI Sparse I/O Space Byte Enable Generation        | 5–7  |

| 5–3  | PCI Configuration Space Definition                 | 5–8  |

| 5–4  | PCI Address Decoding for Primary Bus Configuration |      |

|      | Accesses                                           | 5–9  |

| 5–5  | PCI Sparse Memory Space Byte Enable Generation     | 5–13 |

| 5–6  | PCI Target Window Enables                          | 5–16 |

| 5–7  | PCI Target Address Translation—Direct Mapped       | 5–18 |

| 5–8  | Scatter-Gather Map Address                         | 5–20 |

| 6–1  | CSR Register Addresses for DECchip 21071-CA        | 6–9  |

| 6–2  | General Control Register                           | 6–12 |

| 6–3  | Error and Diagnostic Status Register               | 6–14 |

| 6–4  | Cache Size Tag Enable Values                       | 6–17 |

| 6–5  | Maximum Memory Tag Enable Values                   | 6–18 |

| 6–6  | Configuration Register for Banks 0 and 1           | 6-23 |

| 6–7  | Timing Register A                                  | 6-25 |

| 6–8  | Timing Register B                                  | 6–27 |

| 6–9  | Global Timing Register                             | 6–28 |

| 6–10 | Refresh Timing Register                            | 6–29 |

| 7–1  | DECchip 21071-DA CSR Addresses                     | 7–7  |

| 7–2  | Diagnostic Control/Status Register                 | 7–10 |

| 7–3  | PCI Error Address Register                         | 7–14 |

| 7–4  | System Bus Error Address Register                  | 7–15 |

| 7–5  | Translated Base Registers 1 and 2                  | 7–16 |

| 7–6  | PCI Base Registers 1 and 2                         | 7–16 |

| 7–7  | PCI Mask Registers 1 and 2                         | 7–18 |

| 7–8  | Host Address Extension Register 1                  | 7–19 |

| 7–9  | Host Address Extension Register 2                  | 7–19 |

| 7–10 | PCI Master Latency Timer Register                  | 7–20 |

| 7–11 | TLB Tag Registers 0 Through 7                      | 7–21 |

| 7–12 | TLB Data Registers 0 Through 7                     | 7–22 |

| 8–1  | Ethernet Controller CSRs                           | 8–5  |

| 8–2  | SCSI Controller CSRs                               | 8–9  |