# Alpha Architecture Reference Manual

# RICHARD L. SITES

Alpha Architecture Reference Manual

# Alpha Architecture Reference Manual

**Contributing Authors**

Richard Witek Alpha co-architect

and Ellen M. Batbouta **Richard A. Brunner** Wayne M. Cardoza Daniel W. Dobberpuhl Robert A. Giggi Henry N. Grieb Richard B. Grove Robert H. Halstead, Jr. Michael S. Harvey Nancy P. Kronenberg Raymond J. Lanza Stephen J. Morris William B. Novce Charles G. Nylander Mary H. Payne Audrey R. Reith Robert M. Supnik Benjamin J. Thomas Catharine Van Ingen

Edited by Richard L. Sites Alpha co-architect

digital

DIGITAL PRESS

Copyright © 1992 by Digital Equipment Corporation

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without prior written permission of the publisher.

Printed in the United States of America.

9876543

Order number EY-L520E-DP ISBN 1-55558-098-X

Technical Writer: Charles Greenman Production Editor: Kathe Rhoades Technical Illustrator: Lynne Kenison Cover Design: Marshall Henrichs

The following are trademarks of Digital Equipment Corporation: Alpha AXP, AXP, the AXP logo, DEC, the Digital logo, OpenVMS, PALcode, PDP-11, VAX, VMS, and ULTRIX. Cray is a registered trademark of Cray Research, Inc. IBM is a registered trademark of International Business Machines Corporation. OSF/1 is a registered trademark of Open Software Foundation, Inc. UNIX is a registered trademark of UNIX System Laboratories, Inc.

Digital believes the information in this book is accurate as of its publication date; such information is subject to change without notice. Digital is not responsible for any inadvertent errors.

# Contents

Foreword Preface

# Part I / Common Architecture

- 1 Introduction

- 2 Basic Architecture

- **3** Instruction Formats

- 4 Instruction Descriptions

- 5 System Architecture and Programming Implications

- 6 Common PALcode Architecture

- 7 Console Subsystem Overview

- 8 Input/Output

# Part II / OpenVMS Alpha Software

- 1 Introduction to OpenVMS Alpha

- 2 OpenVMS PALcode Instruction Descriptions

- 3 OpenVMS Memory Management

- 4 OpenVMS Process Structure

- 5 OpenVMS Internal Processor Registers

- 6 OpenVMS Exceptions, Interrupts, and Machine Checks

# Part III / DEC OSF/1 Alpha Software

- 1 Introduction to DEC OSF/1 Alpha

- 2 OSF/1 PALcode Instruction Descriptions

- 3 OSF/1 Memory Management

- 4 OSF/1 Process Structure

- 5 OSF/1 Exceptions and Interrupts

# **Appendixes**

- A Software Considerations

- **B** IEEE Floating-Point Conformance

- C Instruction Encodings

Index

NOTE

The final name of the architecture had not been formalized at the first printing of the *Alpha Architecture Reference Manual*. The final name has now been determined and it is Alpha AXP. Therefore, all references in this manual to the Alpha architecture mean the Alpha AXP architecture.

Further, the formalization of the of the architecture name is now reflected in the operating system names, which are now OpenVMS AXP and DEC OSF/1 AXP.

In the foreword to the VAX Architecture Reference Manual, Sam Fuller, Digital's Vice President for Research and Architecture, wrote, "Computer design continues to be a dynamic field; I expect we will see more rather than less change and innovation in the decades ahead." The Alpha Architecture Reference Manual demonstrates the accuracy of that prediction.

Alpha follows VAX by about fifteen years. Those fifteen years have witnessed a torrent of change in computer technology, one that shows no sign of abating:

- More than a 1000-fold increase in the performance of microprocessors

- More than a 1000-fold increase in the density of semiconductor memories

- More than a 500-fold increase in the density of magnetic storage devices

- More than a 100-fold increase in the speed of network connections

During the same period, the internal organization of computer systems has changed as well, based on developments such as RISC architecture, symmetric multiprocessing, and coherent distributed systems. Moreover, the fundamental paradigms of computing have changed not once, but several times, with the introduction of personal computers, graphics workstations, local area networks, and client/server computing.

These developments present an enormous challenge for computing in the 21st century. Future computers will be called upon to solve problems of great scale and complexity, worldwide, in a distributed manner. They will have to provide unprecedented performance, flexibility, reliability, and scalability in order to implement a global infrastructure of information, and to give users an untrammeled window on the world.

Alpha is Digital's response to the challenges of 21st-century computing. It represents the culmination of the company's knowledge and belief about how the next generations of computers should be built. Alpha is based on a decade's experimental and engineering work in RISC architecture, high-speed implementation, software compatibility and migration, and system serviceability. It provides the foundation for implementations ranging from mobile computing units to massively parallel supercomputers.

Alpha is designed to handle the largest computing problems of today and tomorrow. When the Alpha architecture is compared to its predecessor, the VAX architecture, two differences stand out immediately. First, Alpha is a 64-bit architecture; VAX is a 32-bit architecture. This means that Alpha's virtual address extends to a 64-bit linear range of bytes in memory. Supporting this extended virtual address space are an extended maximum physical address range (up to 48 bits) and larger pages (8KB to 64KB). Alpha's extended virtual address range allows direct manipulation of the gigabytes and terabytes of data produced in electrical and mechanical design, database and transaction processing, and imaging.

Second, Alpha is a RISC architecture; VAX is a CISC architecture. RISC stands for Reduced Instruction Set Computer, CISC for Complex Instruction Set Computer. RISC architectures are characterized by simple, fixed-length instruction formats; a small number of addressing modes; large register files; a load-store instruction set model; and direct hardware execution of instructions. CISC architectures are characterized by variable-length instruction formats; a large number of addressing modes; small-to-medium-sized register files; a full set of register-to-memory (or even memory-to-memory) instructions; and microcoded execution of instructions. Alpha's streamlined organization facilitates high-speed implementation in a variety of technologies, while providing strong compatibility with today's programs and data.

The following tabulation contrasts the architectural differences between VAX and Alpha:

|                               | VAX                                                                         | Alpha               |

|-------------------------------|-----------------------------------------------------------------------------|---------------------|

| Architecture                  | CISC                                                                        | RISC                |

| Virtual address range         | 32 bits                                                                     | Up to 64 bits       |

| Physical address range        | Up to 32 bits                                                               | Up to 48 bits       |

| Page size                     | 512 bytes                                                                   | 8KB64KB             |

| Instruction lengths           | 1–51 bytes                                                                  | 4 bytes             |

| General registers             | $16 \times 32$ bits                                                         | $64 \times 64$ bits |

| Addressing modes              | 21                                                                          | 3                   |

| Instruction set architecture  | General                                                                     | Load-store          |

| Directly supported data types | Integer, floating, bit<br>field, queue, character<br>string, decimal string | Integer, floating   |

This book is the culmination of an effort begun three years ago. In that time, Alpha has grown from a paper specification to a cohesive set of chips, systems, and software, spanning the computer spectrum. This achievement is due to the efforts of many hundreds of people in Engineering, Marketing, Sales, Service, and Manufacturing. This book is documentation of, and a tribute to, the outstanding work they have done.

Bob Supnik Corporate Consultant, Vice President The Alpha architecture is a RISC architecture that was designed for high performance and longevity. Following Amdahl, Blaauw, and Brooks,<sup>1</sup> we distinguish between architecture and implementation:

- Computer architecture is defined as the attributes of a computer seen by a machinelanguage programmer. This definition includes the instruction set, instruction formats, operation codes, addressing modes, and all registers and memory locations that may be directly manipulated by a machine-language programmer.

- Implementation is defined as the actual hardware structure, logic design, and datapath organization.

This architecture book describes the required behavior of all Alpha implementations, as seen by the machine-language programmer. The architecture does not speak to implementation considerations such has how fast a program runs, what specific bit pattern is left in a hardware register after an unpredictable operation, how to schedule code for a particular chip, or how to wire up a given chip; those considerations are described in implementation-specific documents.

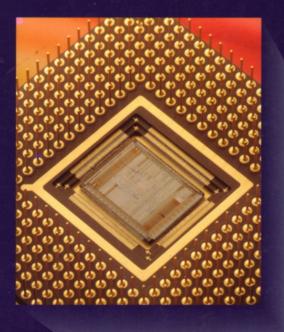

Various Alpha implementations are expected over the coming years, starting with the Digital 21064 chip.

#### Goals

When we started the Alpha project in the fall of 1988, we had a small number of goals:

- 1. High performance

- 2. Longevity

- 3. Run VMS and UNIX

- 4. Easy migration from VAX (and soon-to-be MIPS) customer base

As principal architects, Rich Witek and I made design decisions that were driven directly by these goals.

We assumed that high performance was needed to make a new architecture attractive in the marketplace, and to keep Digital competitive.

We set a 15-25 year design horizon (longevity) and tried to avoid any design elements that we thought would become limitations during this time. The design horizon led directly to the conclusion that Alpha could not be a 32-bit architecture: 32bit addresses will be too small within 10 years. We thus adopted a full 64-bit

<sup>1.</sup> Amdahl, G.M., G.A. Blaauw, and F.P. Brooks, Jr. "Architecture of the IBM System/360." *IBM Journal of Research and Development*, vol. 8, no. 2 (April 1964): 87-101.

architecture, with a minimal number of 32-bit operations for backward compatibility. Wherever possible, 32-bit operands are put in registers in a 64-bit canonical form and operated upon with 64-bit operations.

The longevity goal also caused us to examine how the performance of implementations would scale up over 25 years. Over the past 25 years, computers have become about 1000 times faster. This suggested to us that Alpha implementations would need to do the same, or we would have to bet that the industry would fall off the historical performance curve. We were unwilling to bet against the industry, and were unwilling to ignore the issue, so we seriously examined the consequences of longevity.

We thought that it would be realistic for implementors to improve clock speeds by a factor of 10 over 25 years, but not by a factor of 100 or 1000. (Clock speeds have improved by about a factor of 100 over the past 25 years, but physical limits are now slowing down the rate of increase.)

We concluded that the remaining factor of 100 would have to come from other design dimensions. If you cannot make the clock faster, the next dimension is to do more work per clock cycle. So the Alpha architecture is focused on allowing implementations that issue many instructions every clock cycle. We thought that it would be realistic for implementors to achieve about a factor of 10 over 25 years by using multiple instruction issue, but not a factor of 100. Even a factor of 10 will require perhaps a decade of compiler research.

We concluded that the remaining factor of 10 would have to come from some other design dimension. If you cannot make the clock faster, and cannot do more work per clock, the next dimension is to have multiple clocked instruction streams, that is, multiple processors. So the Alpha architecture is focused on allowing implementations that apply multiple processors to a single problem. We thought that it would be realistic for implementors to achieve the remaining factor of 10 over 25 years by using multiple processors.

Overall, the factor-of-1000 increase in performance looked reasonable, but required factor-of-10 increases in three different dimensions. These three dimensions therefore formed part of our design framework:

- Gracefully allow fast cycle-time implementations

- Gracefully allow multiple-instruction-issue implementations

- Gracefully allow multiple-processor implementations

The cycle-time goal encouraged us to keep the instruction definitions very simple, and to keep the interactions between instructions very simple. The multiple-instructionissue goal encouraged us to eliminate specialized registers, architected delay slots, precise arithmetic traps, and byte writes (with their embedded read-modify-write bottleneck). The multiple-processor goal encouraged us to consider the memory model and atomic-update primitives carefully. We adopted load-locked/store-conditional sequences as the atomic-update primitive, and eliminated strict read-write ordering between processors.

All of the above design decisions were driven directly by the performance and

longevity goals. The lack of byte writes, precise arithmetic traps, and multiprocessor read/write ordering have been the most controversial decisions, so far.

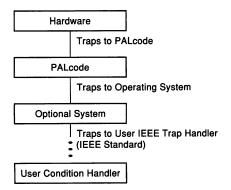

#### **Clean Sheet of Paper**

To run both OpenVMS and UNIX without burdening the hardware implementations with elaborate (and sometimes conflicting) operating system underpinnings, we adopted an idea from a previous Digital RISC design. Alpha places the underpinnings for interrupt delivery and return, exceptions, context switching, memory management, and error handling in a set of privileged software subroutines called PALcode (privileged architecture library code). PALcode subroutines have controlled entries, run with interrupts turned off, and have access to real hardware (implementation) registers. By having different sets of PALcode for different operating systems, the architecture itself is not biased toward a specific operating system or computing style.

PALcode allowed us to design an architecture that could run OpenVMS gracefully without elaborate hardware and without massively rewriting the VMS synchronization and protection mechanisms. PALcode lets the Alpha architecture support some complex VAX primitives (such as the interlocked queue instructions) that are heavily used by OpenVMS, without burdening a UNIX implementation in any way.

Finally, we also considered how to move VAX and MIPS code to Alpha. We rejected various forms of "compatibility mode" hardware, because they would have severely compromised the performance and time-to-market of the first implementation. After some experimentation, we adopted the strategy of running existing binary code by building software translators. One translator converts OpenVMS VAX images to functionally identical OpenVMS Alpha images. A second translator converts MIPS ULTRIX images to functionally identical DEC OSF/1 Alpha images.

Fundamentally, PALcode gave us a migration path for existing operating systems, and the translators (and native compilers) gave us a migration path for existing user-mode code. PALcode and the translators provided a clean sheet of design paper for the bulk of the Alpha architecture. Other than an extra set of VAX floating-point formats (included for good business reasons, but subsettable later), no specific VAX or MIPS features are carried directly into the Alpha architecture for compatibility reasons.

These considerations substantially shaped the architecture described in the rest of this book.

#### Organization

The first part of this book describes the instruction-set architecture, and is largely self-contained for readers who are involved with compilers or with assembly language programming. The second and third parts describe the supporting PALcode routines for each operating system—the specific operating system PALcode architecture.

#### Acknowledgments

My collaboration with Rich Witek over the past few years has been extremely rewarding, both personally and professionally. By combining our backgrounds and viewpoints, we have produced an architecture that is substantially better than either of us could have produced alone. Thank you, Rich. A work of this magnitude cannot be done on a shoestring or in isolation. Rich and I were blessed with a rich environment of dozens and later hundreds of bright, thoughtful, and outspoken professional peers. I thank the management of Digital Equipment Corporation for providing that rich environment, and those peers for making the architecture so much more robust and well-considered.

Three people have especially influenced my views of computer architecture, through personal interaction and landmark machine design: Fred Brooks, John Cocke, and Seymour Cray. This work is built directly upon theirs, and could not exist without them.

The organization, editing, and production of this text in final form is largely the work of Charlie Greenman, whose clear writing is much appreciated.

Richard L. Sites May 1992

# A Note on the Structure of This Book

The Alpha Architecture Reference Manual is divided into three parts, three appendixes, and an index. Each part describes a major portion of the Alpha architecture. Each contains its own table of contents.

The following tabulation outlines the book's contents:

| Name       | Contents                                                                                                                                                                                                 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part I     | Common Architecture                                                                                                                                                                                      |

|            | This part describes the instruction-set architecture that is common to<br>and required by all implementations.                                                                                           |

| Part II    | OpenVMS Alpha Software                                                                                                                                                                                   |

|            | This part describes how the OpenVMS operating system relates to the Alpha architecture.                                                                                                                  |

| Part III   | DEC OSF/1 Alpha Software                                                                                                                                                                                 |

|            | This part describes how the DEC OSF/1 operating system relates to the Alpha architecture.                                                                                                                |

| Appendixes | The appendixes describe implementation considerations, IEEE floating-<br>point conformance, and instruction encodings.                                                                                   |

| Index      | Index entries are called out by the symbol (I), (II), or (III). Each symbol is associated with the corresponding Part. Index entries for the appendixes are called out by appendix name and page number. |

# Part I Common Architecture

This part describes the common Alpha architecture and contains the following chapters:

- 1. Introduction

- 2. Basic Architecture

- **3. Instruction Formats**

- 4. Instruction Descriptions

- 5. System Architecture and Programming Implications

- 6. Common PALcode Architecture

- 7. Console Subsystem Overview

- 8. Input/Output

# Common Architecture (I)

# Chapter 1 Introduction (I)

| 1.1    | The Alpha Approach to RISC Architecture | 1–1 |

|--------|-----------------------------------------|-----|

| 1.2    | Data Format Overview                    | 1–3 |

| 1.3    | Instruction Format Overview             | 1–4 |

| 1.4    | Instruction Overview                    | 1–5 |

| 1.5    | Instruction Set Characteristics         | 1–6 |

| 1.6    | Terminology and Conventions             | 1–7 |

| 1.6.1  | Numbering                               | 1–7 |

| 1.6.2  | Security Holes                          | 1–7 |

| 1.6.3  | UNPREDICTABLE and UNDEFINED             | 1–7 |

| 1.6.4  | Ranges and Extents                      | 18  |

| 1.6.5  | ALIGNED and UNALIGNED                   | 1–8 |

| 1.6.6  | Must Be Zero (MBZ)                      | 1–9 |

| 1.6.7  | Read As Zero (RAZ)                      | 1–9 |

| 1.6.8  | Should Be Zero (SBZ)                    | 1–9 |

| 1.6.9  | Ignore (IGN)                            | 1–9 |

| 1.6.10 |                                         | 1–9 |

| 1.6.11 |                                         | 1–9 |

| 1.6.12 | Macro Code Example Conventions          | 1–9 |

|        |                                         |     |

# Chapter 2 Basic Architecture (I)

| 2–1<br>2–1<br>2–1<br>2–2 |

|--------------------------|

| 2–1                      |

|                          |

| 0 0                      |

| 4-4                      |

| 2–2                      |

| 2–3                      |

| 2–3                      |

| 2–5                      |

| 26                       |

| 2–7                      |

| 28                       |

| 2–10                     |

|                          |

,

| 2.2.7 | Longword Integer Format in Floating-Point Unit | 2–11 |

|-------|------------------------------------------------|------|

| 2.2.8 | Quadword Integer Format in Floating-Point Unit | 2–12 |

| 2.2.9 | Data Types with No Hardware Support            | 2–13 |

# Chapter 3 Instruction Formats (I)

| 3.1     | Alpha Registers                                 | 3–1  |

|---------|-------------------------------------------------|------|

| 3.1.1   | Program Counter                                 | 3–1  |

| 3.1.2   | Integer Registers                               | 3–1  |

| 3.1.3   | Floating-Point Registers                        | 3–2  |

| 3.1.4   | Lock Registers                                  | 3–2  |

| 3.1.5   | Optional Registers                              | 3–2  |

| 3.1.5.1 | Memory Prefetch Registers                       | 3–2  |

| 3.1.5.2 | 2 VAX Compatibility Register                    | 3–2  |

| 3.2     | Notation                                        | 3–2  |

| 3.2.1   | Operand Notation                                | 3–3  |

| 3.2.2   | Instruction Operand Notation                    | 3–4  |

| 3.2.3   | Operators                                       | 3–5  |

| 3.2.4   | Notation Conventions                            | 3–8  |

| 3.3     | Instruction Formats                             | 3–8  |

| 3.3.1   | Memory Instruction Format                       | 3–9  |

| 3.3.1.1 | Memory Format Instructions with a Function Code | 3–9  |

| 3.3.1.2 | 2 Memory Format Jump Instructions               | 3–10 |

| 3.3.2   | Branch Instruction Format                       | 3–10 |

| 3.3.3   | Operate Instruction Format                      | 3–10 |

| 3.3.4   | Floating-Point Operate Instruction Format       | 3–12 |

| 3.3.4.1 | Floating-Point Convert Instructions             | 3–12 |

| 3.3.5   | PALcode Instruction Format                      | 3–13 |

# Chapter 4 Instruction Descriptions (I)

| 4.1 Inst | ruction Set Overview                               | 4–1  |

|----------|----------------------------------------------------|------|

| 4.1.1 S  | ubsetting Rules                                    | 4–2  |

| 4.1.1.1  | Floating-Point Subsets                             | 4–2  |

| 4.1.2 S  | oftware Emulation Rules                            | 4–2  |

| 4.1.3 0  | Opcode Qualifiers                                  | 4–3  |

| 4.2 Me   | nory Integer Load/Store Instructions               | 4-4  |

| 4.2.1 I  | oad Address                                        | 4–5  |

| 4.2.2 I  | oad Memory Data into Integer Register              | 46   |

| 4.2.3 I  | oad Unaligned Memory Data into Integer Register    | 4–7  |

| 4.2.4 I  | oad Memory Data into Integer Register Locked       | 48   |

| 4.2.5 S  | tore Integer Register Data into Memory Conditional | 4–11 |

| 4.2.6 \$ | tore Integer Register Data into Memory             | 4–13 |

| 4.2.7 \$ | tore Unaligned Integer Register Data into Memory   | 4–14 |

| 4.3 Cor  | trol Instructions                                  | 4–15 |

|   | 4.3.1   | Conditional Branch                         | 4–17 |

|---|---------|--------------------------------------------|------|

|   | 4.3.2   | Unconditional Branch                       | 4–19 |

|   | 4.3.3   | Jumps                                      | 4–20 |

|   | 4.4 In  | nteger Arithmetic Instructions             | 4–22 |

|   | 4.4.1   | Longword Add                               | 4-23 |

|   | 4.4.2   | Scaled Longword Add                        | 4–24 |

|   | 4.4.3   | Quadword Add                               | 4-25 |

|   | 4.4.4   | Scaled Quadword Add                        | 4-26 |

|   | 4.4.5   | Integer Signed Compare                     | 4-27 |

|   | 4.4.6   | Integer Unsigned Compare                   | 4–28 |

|   | 4.4.7   | Longword Multiply                          | 4–29 |

|   | 4.4.8   | Quadword Multiply                          | 430  |

|   | 4.4.9   | Unsigned Quadword Multiply High            | 4-31 |

|   | 4.4.10  | Longword Subtract                          | 4-32 |

|   | 4.4.11  | Scaled Longword Subtract                   | 4-33 |

|   | 4.4.12  | Quadword Subtract                          | 4-34 |

|   | 4.4.13  | Scaled Quadword Subtract                   | 4-35 |

|   | 4.5 L   | ogical and Shift Instructions              | 436  |

|   | 4.5.1   | Logical Functions                          | 4-37 |

|   | 4.5.2   | Conditional Move Integer                   | 4-38 |

|   | 4.5.3   | Shift Logical                              | 440  |

|   | 4.5.4   | Shift Arithmetic                           | 4-41 |

|   | 4.6 B   | yte-Manipulation Instructions              | 4-42 |

|   | 4.6.1   | Compare Byte                               | 444  |

|   | 4.6.2   | Extract Byte                               | 4-46 |

|   | 4.6.3   | Byte Insert                                | 4-50 |

|   | 4.6.4   | Byte Mask                                  | 4-52 |

|   | 4.6.5   | Zero Bytes                                 | 4-55 |

|   | 4.7 F   | loating-Point Instructions                 | 4-56 |

| ' | 4.7.1   | Floating Subsets and Floating Faults       | 456  |

|   | 4.7.2   | Definitions                                | 4-57 |

|   | 4.7.3   | Encodings                                  | 4-58 |

|   | 4.7.4   | Floating-Point Rounding Modes              | 459  |

|   | 4.7.5   | Floating-Point Trapping Modes              | 4-60 |

|   | 4.7.5.1 | Imprecise /Software Completion Trap Modes  | 4-62 |

|   | 4.7.5.2 | Invalid Operation Arithmetic Trap          |      |

|   | 4.7.5.3 | Division by Zero Arithmetic Trap           | 4-63 |

|   | 4.7.5.4 | Overflow Arithmetic Trap                   | 4-63 |

|   | 4.7.5.5 | Underflow Arithmetic Trap                  | 463  |

|   | 4.7.5.6 | Inexact Result Arithmetic Trap             | 4-64 |

|   | 4.7.5.7 | Integer Overflow Arithmetic Trap           | 4-64 |

|   | 4.7.6   | Floating-Point Single-Precision Operations | 464  |

|   | 4.7.7   | FPCR Register and Dynamic Rounding Mode    | 4-64 |

|   | 4.7.7.1 | Accessing the FPCR                         | 4-66 |

|   | 4.7.7.2 | Default Values of the FPCR                 | 4-67 |

| 4.7.7.3 | Saving and Restoring the FPCR                | 4–67  |

|---------|----------------------------------------------|-------|

| 4.7.8   | IEEE Standard                                | 4–67  |

| 4.8 M   | emory Format Floating-Point Instructions     | 4–68  |

| 4.8.1   | Load F_floating                              | 4–69  |

| 4.8.2   | Load G_floating                              | 4–70  |

| 4.8.3   | Load S_floating                              | 4–71  |

| 4.8.4   | Load T_floating                              | 4–72  |

| 4.8.5   | Store F_floating                             | 4–73  |

| 4.8.6   | Store G_floating                             | 4-74  |

| 4.8.7   | Store S_floating                             | 4–75  |

| 4.8.8   | Store T_floating                             | 4–76  |

| 4.9 B   | ranch Format Floating-Point Instructions     | 4–77  |

| 4.9.1   | Conditional Branch                           | 4–78  |

| 4.10 F  | loating-Point Operate Format Instructions    | 4–80  |

| 4.10.1  | Copy Sign                                    | 4-83  |

| 4.10.2  | Convert Integer to Integer                   | 4–84  |

| 4.10.3  | Floating-Point Conditional Move              | 4-85  |

| 4.10.4  | Move from/to Floating-Point Control Register | 4-87  |

| 4.10.5  | VAX Floating Add                             | 4-88  |

| 4.10.6  | IEEE Floating Add                            | 4-89  |

| 4.10.7  | VAX Floating Compare                         | 4–91  |

| 4.10.8  | IEEE Floating Compare                        | 4–92  |

| 4.10.9  | Convert VAX Floating to Integer              | 4–94  |

| 4.10.10 | Convert Integer to VAX Floating              | 4–95  |

| 4.10.11 | Convert VAX Floating to VAX Floating         | 4–96  |

| 4.10.12 | Convert IEEE Floating to Integer             | 4-98  |

| 4.10.13 | Convert Integer to IEEE Floating             | 4–99  |

| 4.10.14 | Convert IEEE Floating to IEEE Floating       | 4–100 |

| 4.10.15 | VAX Floating Divide                          | 4–102 |

| 4.10.16 | IEEE Floating Divide                         | 4–104 |

| 4.10.17 | VAX Floating Multiply                        | 4–106 |

| 4.10.18 | IEEE Floating Multiply                       | 4–107 |

| 4.10.19 | VAX Floating Subtract                        | 4–109 |

| 4.10.20 | IEEE Floating Subtract                       | 4–111 |

| 4.11 M  | liscellaneous Instructions                   | 4–113 |

| 4.11.1  | Call Privileged Architecture Library         | 4–114 |

| 4.11.2  | Prefetch Data                                | 4–115 |

| 4.11.3  | Memory Barrier                               | 4–117 |

| 4.11.4  | Read Process Cycle Counter                   | 4–118 |

| 4.11.5  | Trap Barrier                                 |       |

| 4.12 V  | AX Compatibility Instructions                |       |

| 4.12.1  | VAX Compatibility Instructions               | 4–122 |

# Chapter 5 System Architecture and Programming Implications (I)

| 5.1     | Introduction                                       | 5–1  |

|---------|----------------------------------------------------|------|

| 5.2     | Physical Memory Behavior                           | 5–1  |

| 5.2.1   | Coherency of Memory Access                         | 5–1  |

| 5.2.2   | Granularity of Memory Access                       | 5–2  |

| 5.2.3   | Width of Memory Access                             | 5–2  |

| 5.2.4   | Memory-Like Behavior                               | 5–3  |

| 5.3     | Translation Buffers and Virtual Caches             | 5–3  |

| 5.4     | Caches and Write Buffers                           | 5–4  |

| 5.5     | Data Sharing                                       | 5–5  |

| 5.5.1   | Atomic Change of a Single Datum                    | 5–5  |

| 5.5.2   | Atomic Update of a Single Datum                    | 5–6  |

| 5.5.3   | Atomic Update of Data Structures                   | 5-6  |

| 5.5.4   | Ordering Considerations for Shared Data Structures | 5–8  |

| 5.6     | Read/Write Ordering                                | 5–9  |

| 5.6.1   | Alpha Shared Memory Model                          | 5–9  |

| 5.6.1.  |                                                    | 5–10 |

| 5.6.1.  |                                                    | 5–11 |

| 5.6.1.3 |                                                    | 5–11 |

| 5.6.1.4 |                                                    | 5-11 |

| 5.6.1.  |                                                    | 5–12 |

| 5.6.1.  |                                                    | 5-12 |

| 5.6.1.  | -                                                  | 5-12 |

| 5.6.1.  |                                                    | 5-13 |

| 5.6.1.  |                                                    | 5-13 |

| 5.6.2   | Litmus Tests                                       | 5-13 |

| 5.6.2.  |                                                    | 5-13 |

| 5.6.2.  |                                                    | 5-13 |

| 5.6.2.3 |                                                    | 5–14 |

| 5.6.2.4 |                                                    | 5-14 |

| 5.6.2.  |                                                    | 5-14 |

| 5.6.2.  |                                                    | 5-14 |

| 5.6.2.  |                                                    | 5-15 |

| 5.6.2.  |                                                    | 5-15 |

| 5.6.2.  |                                                    | 5-15 |

| 5.6.3   | Implied Barriers                                   | 5-16 |

| 5.6.4   | Implications for Software                          | 5-16 |

| 5.6.4.  |                                                    | 5-16 |

| 5.6.4.  |                                                    | 5-16 |

| 5.6.4.  |                                                    | 5-16 |

| 5.6.4.  |                                                    |      |

| 5.6.4.  |                                                    | 5-17 |

| 5.6.4.  |                                                    | 5-20 |

| 5.6.5   | Implications for Hardware                          | 5-20 |

| 5.7 | Arithmetic Traps |  |  |  |  |  | 5–21 |

|-----|------------------|--|--|--|--|--|------|

|-----|------------------|--|--|--|--|--|------|

# Chapter 6 Common PALcode Architecture (I)

| 6.1   | PALcode                                | 6–1 |

|-------|----------------------------------------|-----|

| 6.2   | PALcode Instructions and Functions     | 6–1 |

| 6.3   | PALcode Environment                    | 6–2 |

| 6.4   | Special Functions Required for PALcode | 6–2 |

| 6.5   | PALcode Effects on System Code         | 6–3 |

| 6.6   | PALcode Replacement                    | 6–3 |

| 6.7   | Required PALcode Instructions          | 6-4 |

| 6.7.1 | Drain Aborts                           | 6–5 |

| 6.7.2 | Halt                                   | 6–6 |

| 6.7.3 | Instruction Memory Barrier             | 6–7 |

# Chapter 7 Console Subsystem Overview (I)

# Chapter 8 Input/Output (I)

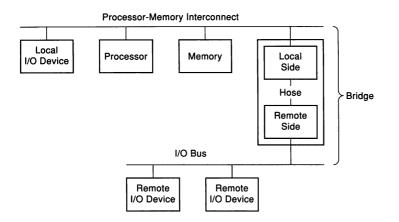

| 8.1   | Introduction                        | 8–1  |

|-------|-------------------------------------|------|

| 8.2   | Local I/O Space Access              | 8–2  |

| 8.2.1 | Read/Write Ordering                 | 8–2  |

| 8.3   | Remote I/O Space Access             | 8–2  |

| 8.3.1 | Mailbox Posting                     | 8–3  |

| 8.3.2 | Mailbox Pointer Register (MBPR)     | 8-4  |

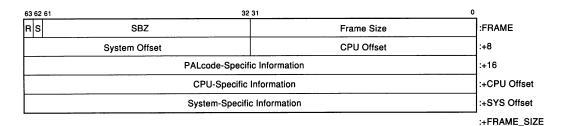

| 8.3.3 | Mailbox Structure                   | 85   |

| 8.3.4 | Mailbox Access Synchronization      | 8–6  |

| 8.3.5 | Mailbox Read/Write Ordering         | 8–7  |

| 8.3.6 | Remote I/O Space Access Granularity | 8–7  |

| 8.3.7 | Remote I/O Space Read Accesses      | 8–8  |

| 8.3.8 | Remote I/O Space Write Accesses     | 8–9  |

| 8.4   | Direct Memory Accesss (DMA)         | 8–10 |

| 8.4.1 | Access Granularity                  | 8–10 |

| 8.4.2 | Read/Write Ordering                 | 8–11 |

| 8.4.3 | Device Address Translation          | 8–12 |

| 8.5   | Interrupts                          | 8–12 |

| 8.6   | I/O Bus-Specific Mailbox Usage      | 8–12 |

| 8.6.1 | Mailbox Field Checking              | 8–12 |

| 8.6.2 | CMD Field                           | 8-13 |

| 8.6.3 | Special Commands                    | 8–13 |

# Figures

| 11   | Instruction Format Overview                   | 1-4  |

|------|-----------------------------------------------|------|

| 2–1  | Byte Format                                   | 2–1  |

| 2–2  | Word Format                                   | 2-2  |

| 2–3  | Longword Format                               | 2–2  |

| 2–4  | Quadword Format                               | 2–3  |

| 2–5  | F_floating Datum                              | 2–3  |

| 2–6  | F_floating Register Format                    | 2–4  |

| 2–7  | G_floating Datum                              | 2–5  |

| 2–8  | G_floating Format                             | 2–5  |

| 2–9  | D_floating Datum                              | 2–6  |

| 2–10 | D_floating Register Format                    | 2–6  |

| 2–11 | S_floating Datum                              | 2–8  |

| 2–12 | S_floating Register Format                    | 2–8  |

| 2-13 | T_floating Datum                              | 2–10 |

|      | T_floating Register Format                    | 2–10 |

| 2–15 | Longword Integer Datum                        | 2–11 |

| 2–16 | Longword Integer Floating-Register Format     | 2–11 |

| 2–17 | Quadword Integer Datum                        | 2–12 |

| 2–18 | Quadword Integer Floating-Register Format     | 2–12 |

| 3–1  | Memory Instruction Format                     | 3–9  |

| 3–2  | Memory Instruction with Function Code Format  | 3–9  |

| 3–3  | Branch Instruction Format                     | 3–10 |

| 3–4  | Operate Instruction Format                    | 3–11 |

| 3–5  | Floating-Point Operate Instruction Format     | 3–12 |

| 3–6  | PALcode Instruction Format                    | 3–13 |

| 4–1  | Floating-Point Control Register (FPCR) Format | 4–65 |

| 8–1  | Alpha System Overview                         | 8–1  |

| 8–2  | Mailbox Pointer Register Format               | 8-4  |

| 8–3  | Mailbox Data Structure Format                 | 8–5  |

# Tables

| 2–1 | F_floating Load Exponent Mapping        | 2–4  |

|-----|-----------------------------------------|------|

| 2–2 | S_floating Load Exponent Mapping        | 2–9  |

| 3–1 | Operand Notation                        | 3–3  |

| 3–2 | Operand Value Notation                  | 3–3  |

| 3–3 | Expression Operand Notation             | 3–3  |

| 3–4 | Operators                               | 3–5  |

| 4–1 | Opcode Qualifiers                       | 43   |

| 4–2 | Memory Integer Load/Store Instructions  | 4-4  |

| 4–3 | Control Instructions Summary            | 4–16 |

| 4–4 | Jump Instructions Branch Prediction     | 4–21 |

| 4–5 | Integer Arithmetic Instructions Summary | 4–22 |

| 46  | Logical and Shift Instructions Summary  | 436  |

|     |                                         |      |

| 4–7  | Byte-Manipulation Instructions Summary                  | 4-42  |

|------|---------------------------------------------------------|-------|

| 4–8  | Floating-Point Control Register (FPCR) Bit Descriptions | 4–65  |

| 4–9  | Memory Format Floating-Point Instructions Summary       | 4–68  |

| 4–10 | Floating-Point Branch Instructions Summary              | 4-77  |

| 4–11 | Floating-Point Operate Instructions Summary             | 4–80  |

| 4–12 | Miscellaneous Instructions Summary                      | 4–113 |

| 4–13 | VAX Compatibility Instructions Summary                  | 4–121 |

| 5–1  | Processor Issue Order                                   | 5–11  |

| 5–2  | Location Access Order                                   | 5–12  |

| 6–1  | PALcode Instructions that Require Recognition           | 6–4   |

| 6–2  | Required PALcode Instructions                           | 6–4   |

| 8–1  | Mailbox Pointer Register Format                         | 8–4   |

| 8–2  | Mailbox Data Structure Format                           | 8–5   |

.

# Chapter 1 Introduction (I)

Alpha is a 64-bit load/store RISC architecture that is designed with particular emphasis on the three elements that most affect performance: clock speed, multiple instruction issue, and multiple processors.

The Alpha architects examined and analyzed current and theoretical RISC architecture design elements and developed high-performance alternatives for the Alpha architecture. The architects adopted only those design elements that appeared valuable for a projected 25-year design horizon. Thus, Alpha becomes the first 21st century computer architecture.

The Alpha architecture is designed to avoid bias toward any particular operating system or programming language. Alpha initially supports the OpenVMS Alpha and DEC OSF/1 operating systems, and supports simple software migration from applications that run on those operating systems.

This manual describes in detail how Alpha is designed to be the leadership 64-bit architecture of the computer industry.

# **1.1 The Alpha Approach to RISC Architecture**

#### Alpha Is a True 64-Bit Architecture

Alpha was designed as a 64-bit architecture. All registers are 64 bits in length and all operations are performed between 64-bit registers. It is not a 32-bit architecture that was later expanded to 64 bits.

#### Alpha Is Designed for Very High-Speed Implementations

The instructions are very simple. All instructions are 32 bits in length. Memory operations are either loads or stores. All data manipulation is done between registers.

The Alpha architecture facilitates pipelining multiple instances of the same operations because there are no special registers and no condition codes.

The instructions interact with each other only by one instruction writing a register or memory and another instruction reading from the same place. That makes it particularly easy to build implementations that issue multiple instructions every CPU cycle. (The first implementation issues two instructions per cycle.)

Alpha makes it easy to maintain binary compatibility across multiple implementations and easy to maintain full speed on multiple-issue implementations. For example, there are no implementation-specific pipeline timing hazards, no loaddelay slots, and no branch-delay slots.

## Alpha's Approach to Byte Manipulation

The Alpha architecture does byte shifting and masking with normal 64-bit registerto-register instructions, crafted to keep instruction sequences short.

Alpha does not include single-byte store instructions. This has several advantages:

- Cache and memory implementations need not include byte shift-and-mask logic, and sequencer logic need not perform read-modify-write on memory locations. Such logic is awkward for high-speed implementation and tends to slow down cache access to normal 32-bit or 64-bit aligned quantities.

- Alpha's approach to byte manipulation makes it easier to build a high-speed error-correcting write-back cache, which is often needed to keep a very fast RISC implementation busy.

- Alpha's approach can make it easier to pipeline multiple byte operations.

#### Alpha's Approach to Arithmetic Traps

Alpha lets the software implementor determine the precision of arithmetic traps. With the Alpha architecture, arithmetic traps (such as overflow and underflow) are imprecise—they can be delivered an arbitrary number of instructions after the instruction that triggered the trap. Also, traps from many different instructions can be reported at once. That makes implementations that use pipelining and multiple issue substantially easier to build.

However, if precise arithmetic exceptions are desired, trap barrier instructions can be explicitly inserted in the program to force traps to be delivered at specific points.

#### Alpha's Approach to Multiprocessor Shared Memory

As viewed from a second processor (including an I/O device), a sequence of reads and writes issued by one processor may be arbitrarily reordered by an implementation. This allows implementations to use multibank caches, bypassed write buffers, write merging, pipelined writes with retry on error, and so forth. If strict ordering between two accesses must be maintained, explicit memory barrier instructions can be inserted in the program.

The basic multiprocessor interlocking primitive is a RISC-style load\_locked, modify, store\_conditional sequence. If the sequence runs without interrupt, exception, or an interfering write from another processor, then the conditional store succeeds. Otherwise, the store fails and the program eventually must branch back and retry the sequence. This style of interlocking scales well with very fast caches, and makes Alpha an especially attractive architecture for building multiple-processor systems.

#### Alpha Instructions Include Hints for Achieving Higher Speed

A number of Alpha instructions include hints for implementations, all aimed at achieving higher speed.

- Calculated jump instructions have a target hint that can allow much faster subroutine calls and returns.

- There are prefetching hints for the memory system that can allow much higher cache hit rates.

• There are granularity hints for the virtual-address mapping that can allow much more effective use of translation lookaside buffers for large contiguous structures.

#### PALcode—Alpha's Very Flexible Privileged Software Library

A Privileged Architecture Library (PALcode) is a set of subroutines that are specific to a particular Alpha operating system implementation. These subroutines provide operating-system primitives for context switching, interrupts, exceptions, and memory management. PALcode is similar to the BIOS libraries that are provided in personal computers.

PALcode subroutines are invoked by implementation hardware or by software CALL\_PAL instructions.

PALcode is written in standard machine code with some implementation-specific extensions to provide access to low-level hardware.

One version of PALcode lets Alpha implementations run the full OpenVMS operating system by mirroring many of the OpenVMS VAX features. The OpenVMS PALcode instructions let Alpha run OpenVMS with little more hardware than that found on a conventional RISC machine: the PAL mode bit itself, plus 4 extra protection bits in each Translation Buffer entry.

Another version of PALcode lets Alpha implementations run the OSF/1 operating system by mirroring many of the RISC ULTRIX features. Other versions of PALcode can be developed for real-time, teaching, and other applications.

PALcode makes Alpha an especially attractive architecture for multiple operating systems.

#### Alpha and Programming Languages

Alpha is an attractive architecture for compiling a large variety of programming languages. Alpha has been carefully designed to avoid bias toward one or two programming languages. For example:

- Alpha does not contain a subroutine call instruction that moves a register window by a fixed amount. Thus, Alpha is a good match for programming languages with many parameters and programming languages with no parameters.

- Alpha does not contain a global integer overflow enable bit. Such a bit would need to be changed at every subroutine boundary when a FORTRAN program calls a C program.

# **1.2 Data Format Overview**

Alpha is a load/store RISC architecture with the following data characteristics:

- All operations are done between 64-bit registers.

- Memory is accessed via 64-bit virtual little-endian byte addresses.

- There are 32 integer registers and 32 floating-point registers.

- Longword (32-bit) and quadword (64-bit) integers are supported.

- Four floating-point data types are supported:

- VAX F\_floating (32-bit)

- VAX G\_floating (64-bit)

- IEEE single (32-bit)

- IEEE double (64-bit)

# **1.3 Instruction Format Overview**

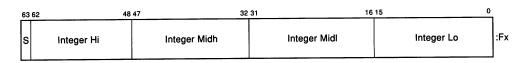

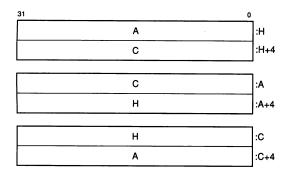

As shown in Figure 1–1, Alpha instructions are all 32 bits in length. As represented in Figure 1–1, there are four major instruction format classes that contain 0, 1, 2, or 3 register fields. All formats have a 6-bit opcode.

| Figure 1–1: | Instruction | Format | Overview |

|-------------|-------------|--------|----------|

|-------------|-------------|--------|----------|

| 31 26  | 25 21 | 20 16 | 15       | 54 | 0  |                |

|--------|-------|-------|----------|----|----|----------------|

| Opcode |       |       | Number   |    |    | PALcode Format |

| Opcode | RA    |       | Disp     |    |    | Branch Format  |

| Opcode | RA    | RB    | Dis      | р  |    | Memory Format  |

| Opcode | RA    | RB    | Function |    | RC | Operate Format |

- **PALcode instructions** specify, in the function code field, one of a few dozen complex operations to be performed.

- Conditional branch instructions test register Ra and specify a signed 21bit PC-relative longword target displacement. Subroutine calls put the return address in register Ra.

- Load and store instructions move longwords or quadwords between register Ra and memory, using Rb plus a signed 16-bit displacement as the memory address.

- **Operate instructions** for floating-point and integer operations are both represented in Figure 1–1 by the operate format illustration and are as follows:

- Floating-point operations use Ra and Rb as source registers, and write the result in register Rc. There is an 11-bit extended opcode in the function field.

- Integer operations use Ra and Rb or an 8-bit literal as the source operand, and write the result in register Rc.

Integer operate instructions can use the Rb field and part of the function field to specify an 8-bit literal. There is a 7-bit extended opcode in the function field.

# **1.4 Instruction Overview**

#### **PALcode Instructions**

As described above, a Privileged Architecture Library (PALcode) is a set of subroutines that is specific to a particular Alpha operating-system implementation. These subroutines can be invoked by hardware or by software CALL\_PAL instructions, which use the function field to vector to the specified subroutine.

#### **Branch Instructions**

Conditional branch instructions can test a register for positive/negative or for zero /nonzero. They can also test integer registers for even/odd.

Unconditional branch instructions can write a return address into a register.

There is also a calculated jump instruction that branches to an arbitrary 64-bit address in a register.

#### Load/Store Instructions

Load and store instructions move either 32-bit or 64-bit aligned quantities from and to memory. Memory addresses are flat 64-bit virtual addresses, with no segmentation.

The VAX floating-point load/store instructions swap words to give a consistent register format for floating-point operations.

A 32-bit integer datum is placed in a register in a canonical form that makes 33 copies of the high bit of the datum. A 32-bit floating-point datum is placed in a register in a canonical form that extends the exponent by 3 bits and extends the fraction with 29 low-order zeros. The 32-bit operates preserve these canonical forms.

There are facilities for doing byte manipulation in registers, eliminating the need for 8-bit or 16-bit load/store instructions.

Compilers, as directed by user declarations, can generate any mixture of 32-bit and 64-bit operations. The Alpha architecture has no 32/64 mode bit.

#### **Integer Operate Instructions**

The integer operate instructions manipulate full 64-bit values, and include the usual assortment of arithmetic, compare, logical, and shift instructions.

There are just three 32-bit integer operates: add, subtract, and multiply. They differ from their 64-bit counterparts only in overflow detection and in producing 32-bit canonical results.

There is no integer divide instruction.

The Alpha architecture also supports the following additional operations:

- Scaled add/subtract instructions for quick subscript calculation

- 128-bit multiply for division by a constant, and multiprecision arithmetic

- Conditional move instructions for avoiding branch instructions

• An extensive set of in-register byte and word manipulation instructions

Integer overflow trap enable is encoded in the function field of each instruction, rather than kept in a global state bit. Thus, for example, both ADDQ/V and ADDQ opcodes exist for specifying 64-bit ADD with and without overflow checking. That makes it easier to pipeline implementations.

#### **Floating-Point Operate Instructions**

The floating-point operate instructions include four complete sets of VAX and IEEE arithmetic instructions, plus instructions for performing conversions between floating-point and integer quantities.

In addition to the operations found in conventional RISC architectures, Alpha includes conditional move instructions for avoiding branches and merge sign /exponent instructions for simple field manipulation.

The arithmetic trap enables and rounding mode are encoded in the function field of each instruction, rather then kept in global state bits. That makes it easier to pipeline implementations.

# **1.5 Instruction Set Characteristics**

Alpha instruction set characteristics are as follows:

- All instructions are 32 bits long and have a regular format.

- There are 32 integer registers (R0 through R31), each 64 bits wide. R31 reads as zero, and writes to R31 are ignored.

- There are 32 floating-point registers (F0 through F31), each 64 bits wide. F31 reads as zero, and writes to F31 are ignored.

- All integer data manipulation is between integer registers, with up to two variable register source operands (one may be an 8-bit literal), and one register destination operand.

- All floating-point data manipulation is between floating-point registers, with up to two register source operands and one register destination operand.

- All memory reference instructions are of the load/store type that move data between registers and memory.

- There are no branch condition codes. Branch instructions test an integer or floating-point register value, which may be the result of a previous compare.

- Integer and logical instructions operate on quadwords.

- Floating-point instructions operate on G\_floating, F\_floating, IEEE double, and IEEE single operands. D\_floating "format compatibility," in which binary files of D\_floating numbers may be processed, but without the last 3 bits of fraction precision, is also provided.

- A minimal number of VAX compatibility instructions are included.

# **1.6 Terminology and Conventions**

The following sections describe the terminology and conventions used in this book.

# 1.6.1 Numbering

All numbers are decimal unless otherwise indicated. Where there is ambiguity, numbers other than decimal are indicated with the name of the base in subscript form, for example,  $10_{16}$ .

## 1.6.2 Security Holes

A security hole is an error of commission, omission, or oversight in a system that allows protection mechanisms to be bypassed.

Security holes exist when unprivileged software (that is, software running outside of kernel mode) can:

- Affect the operation of another process without authorization from the operating system;

- Amplify its privilege without authorization from the operating system; or

- Communicate with another process, either overtly or covertly, without authorization from the operating system.

The Alpha architecture has been designed to contain no architectural security holes. Hardware (processors, buses, controllers, and so on) and software should likewise be designed to avoid security holes.

# **1.6.3 UNPREDICTABLE and UNDEFINED**

The terms UNPREDICTABLE and UNDEFINED are used throughout this book. Their meanings are quite different and must be carefully distinguished.

In particular, only privileged software (software running in kernel mode) can trigger UNDEFINED operations. Unprivileged software cannot trigger UNDEFINED operations. However, either privileged or unprivileged software can trigger UNPREDICTABLE results or occurences.

UNPREDICTABLE results or occurences do not disrupt the basic operation of the processor; it continues to execute instructions in its normal manner. In contrast, UNDEFINED operation can halt the processor or cause it to lose information.

The terms UNPREDICTABLE and UNDEFINED can be further described as follows:

#### UNPREDICTABLE

- Results or occurrences specified as UNPREDICTABLE may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. Software can never depend on results specified as UNPREDICTABLE.

- An UNPREDICTABLE result may acquire an arbitrary value subject to a few constraints. Such a result may be an arbitrary function of the input operands

or of any state information that is accessible to the process in its current access mode. UNPREDICTABLE results may be unchanged from their previous values.

Operations that produce UNPREDICTABLE results may also produce exceptions.

• An occurrence specified as UNPREDICTABLE may happen or not based on an arbitrary choice function. The choice function is subject to the same constraints as are UNPREDICTABLE results and, in particular, must not constitute a security hole.

Specifically, UNPREDICTABLE results must not depend upon, or be a function of, the contents of memory locations or registers which are inaccessible to the current process in the current access mode.

Also, operations that may produce UNPREDICTABLE results must not:

- Write or modify the contents of memory locations or registers to which the current process in the current access mode does not have access, or

- Halt or hang the system or any of its components.

For example, a security hole would exist if some UNPREDICTABLE result depended on the value of a register in another process, on the contents of processor temporary registers left behind by some previously running process, or on a sequence of actions of different processes.

#### UNDEFINED

- Operations specified as UNDEFINED may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. The operation may vary in effect from nothing, to stopping system operation.

- UNDEFINED operations may halt the processor or cause it to lose information. However, UNDEFINED operations must not cause the processor to hang, that is, reach an unhalted state from which there is no transition to a normal state in which the machine executes instructions.

# 1.6.4 Ranges and Extents

Ranges are specified by a pair of numbers separated by a ".." and are inclusive. For example, a range of integers 0..4 includes the integers 0, 1, 2, 3, and 4.

Extents are specified by a pair of numbers in angle brackets separated by a colon and are inclusive. For example, bits <7:3> specify an extent of bits including bits 7, 6, 5, 4, and 3.

# 1.6.5 ALIGNED and UNALIGNED

In this document the terms ALIGNED and NATURALLY ALIGNED are used interchangeably to refer to data objects that are powers of two in size. An aligned datum of size  $2^{**}N$  is stored in memory at a byte address that is a multiple of  $2^{**}N$ , that is, one that has N low-order zeros. Thus, an aligned 64-byte stack frame has a memory address that is a multiple of 64. If a datum of size  $2^{**}N$  is stored at a byte address that is not a multiple of  $2^{**}N$ , it is called UNALIGNED.

## 1.6.6 Must Be Zero (MBZ)

Fields specified as Must be Zero (MBZ) must never be filled by software with a nonzero value. These fields may be used at some future time. If the processor encounters a non-zero value in a field specified as MBZ, an Illegal Operand exception occurs.

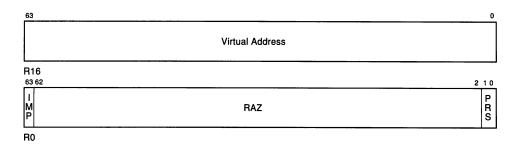

# 1.6.7 Read As Zero (RAZ)

Fields specified as Read as Zero (RAZ) return a zero when read.

## 1.6.8 Should Be Zero (SBZ)

Fields specified as Should be Zero (SBZ) should be filled by software with a zero value. Non-zero values in SBZ fields produce UNPREDICTABLE results and may produce extraneous instruction-issue delays.

## 1.6.9 Ignore (IGN)

Fields specified as Ignore (IGN) are ignored when written.

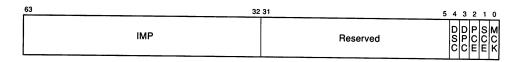

## 1.6.10 Implementation Dependent (IMP)

Fields specified as Implementation Dependent (IMP) may be used for implementationspecific purposes. Each implementation must document fully the behavior of all fields marked as IMP by the Alpha specification.

### **1.6.11 Figure Drawing Conventions**

Figures that depict registers or memory follow the convention that increasing addresses run right to left and top to bottom.

### 1.6.12 Macro Code Example Conventions

All instructions in macro code examples are either listed in Chapter 4 or OpenVMS Section, Chapter 2, or are stylized code forms found in Appendix A.

.

# 2.1 Addressing

The basic addressable unit in Alpha is the 8-bit byte. Virtual addresses are 64 bits long. An implementation may support a smaller virtual address space. The minimum virtual address size is 43 bits.

Virtual addresses as seen by the program are translated into physical memory addresses by the memory management mechanism.

# 2.2 Data Types

Following are descriptions of the Alpha architecture data types.

### 2.2.1 Byte

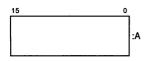

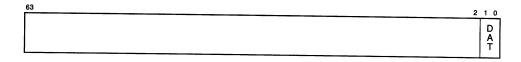

A byte is 8 contiguous bits starting on an addressable byte boundary. The bits are numbered from right to left, 0 through 7, as shown in Figure 2-1.

#### Figure 2–1: Byte Format

A byte is specified by its address A. A byte is an 8-bit value. The byte is only supported in Alpha by the extract, mask, insert, and zap instructions.

### 2.2.2 Word

A word is 2 contiguous bytes starting on an arbitrary byte boundary. The bits are numbered from right to left, 0 through 15, as shown in Figure 2–2.

#### Figure 2–2: Word Format

A word is specified by its address, the address of the byte containing bit 0.

A word is a 16-bit value. The word is only supported in Alpha by the extract, mask, and insert instructions.

### 2.2.3 Longword

A longword is 4 contiguous bytes starting on an arbitrary byte boundary. The bits are numbered from right to left, 0 through 31, as shown in Figure 2–3.

#### Figure 2–3: Longword Format

A longword is specified by its address A, the address of the byte containing bit 0. A longword is a 32-bit value.

When interpreted arithmetically, a longword is a two's-complement integer with bits of increasing significance from 0 through 30. Bit 31 is the sign bit. The longword is only supported in Alpha by sign-extended load and store instructions and by longword arithmetic instructions.

### NOTE

Alpha implementations will impose a significant performance penalty when accessing longword operands that are not naturally aligned. (A naturally aligned longword has zero as the low-order two bits of its address.)

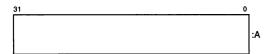

### 2.2.4 Quadword

A quadword is 8 contiguous bytes starting on an arbitrary byte boundary. The bits are numbered from right to left, 0 through 63, as shown in Figure 2–4.

Figure 2–4: Quadword Format

63

A quadword is specified by its address A, the address of the byte containing bit 0. A quadword is a 64-bit value. When interpreted arithmetically, a quadword is either a two's-complement integer with bits of increasing significance from 0 through 62 and bit 63 as the sign bit, or an unsigned integer with bits of increasing significance from 0 through 63.

#### NOTE

Alpha implementations will impose a significant performance penalty when accessing quadword operands that are not naturally aligned. (A naturally aligned quadword has zero as the low-order three bits of its address.)

### 2.2.5 VAX Floating-Point Formats

VAX floating-point numbers are stored in one set of formats in memory and in a second set of formats in registers. The floating-point load and store instructions convert between these formats purely by rearranging bits; no rounding or range-checking is done by the load and store instructions.

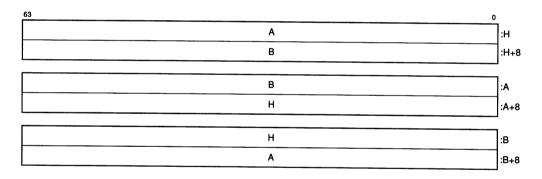

#### 2.2.5.1 F\_floating

An F\_floating datum is 4 contiguous bytes in memory starting on an arbitrary byte boundary. The bits are labeled from right to left, 0 through 31, as shown in Figure 2-5.

#### Figure 2–5: F\_floating Datum

| 15          | 14 |      | 7 | 6       | 0  | _  |

|-------------|----|------|---|---------|----|----|

| s           |    | Exp. |   | Frac. H | li | :A |

| Fraction Lo |    |      |   | :A+2    |    |    |

An F\_floating operand occupies 64 bits in a floating register, left-justified in the 64-bit register, as shown in Figure 2–6.

0

:A

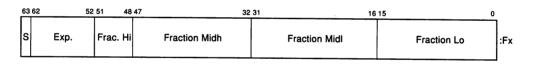

### Figure 2–6: F\_floating Register Format

| 63 62 | 52   | 51 45    | 44 29       | 28 | 0   |

|-------|------|----------|-------------|----|-----|

| S E   | Exp. | Frac. Hi | Fraction Lo | 0  | :Fx |

The F\_floating load instruction reorders bits on the way in from memory, expands the exponent from 8 to 11 bits, and sets the low-order fraction bits to zero. This produces in the register an equivalent G\_floating number suitable for either F\_floating or G\_floating operations. The mapping from 8-bit memory-format exponents to 11-bit register-format exponents is shown in Table 2–1.

Table 2–1: F\_floating Load Exponent Mapping

| Register <62:52 |                                                 |

|-----------------|-------------------------------------------------|

| 1 000 1111111   |                                                 |

| 1 000 xxxxxxx   | (xxxxxxx not all 1's)                           |

| 0 111 xxxxxxx   | (xxxxxxx not all 0's)                           |

| 0 000 000000    |                                                 |

|                 | 1 000 1111111<br>1 000 xxxxxxx<br>0 111 xxxxxxx |

This mapping preserves both normal values and exceptional values.

The F\_floating store instruction reorders register bits on the way to memory and does no checking of the low-order fraction bits. Register bits <61:59> and <28:0> are ignored by the store instruction.

An F\_floating datum is specified by its address A, the address of the byte containing bit 0. The memory form of an F\_floating datum is sign magnitude with bit 15 the sign bit, bits <14:7> an excess-128 binary exponent, and bits <6:0> and <31:16> a normalized 24-bit fraction with the redundant most significant fraction bit not represented. Within the fraction, bits of increasing significance are from 16 through 31 and 0 through 6. The 8-bit exponent field encodes the values 0 through 255. An exponent value of 0, together with a sign bit of 0, is taken to indicate that the F floating datum has a value of 0.

If the result of a VAX floating-point format instruction has a value of zero, the instruction always produces a datum with a sign bit of 0, an exponent of 0, and all fraction bits of 0. Exponent values of 1..255 indicate true binary exponents of -127..127. An exponent value of 0, together with a sign bit of 1, is taken as a reserved operand. Floating-point instructions processing a reserved operand take an arithmetic exception. The value of an F\_floating datum is in the approximate range  $0.29*10^{**}-38..1.7*10^{**}38$ . The precision of an F\_floating datum is approximately one part in  $2^{**}23$ , typically 7 decimal digits.

Alpha implementations will impose a significant performance penalty when accessing  $F_{floating}$  operands that are not naturally aligned. (A naturally aligned  $F_{floating}$ floating datum has zero as the low-order two bits of its address.)

#### 2.2.5.2 G\_floating

A G\_floating datum in memory is 8 contiguous bytes starting on an arbitrary byte boundary. The bits are labeled from right to left, 0 through 63, as shown in Figure 2-7.

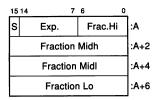

#### Figure 2–7: G\_floating Datum

| 15 | 14            | 43   | 0      |  |

|----|---------------|------|--------|--|

| s  | Exp.          | Frac | .Hi :A |  |

|    | Fraction Midh |      |        |  |

|    | Fraction Midl |      |        |  |

|    | Fraction Lo   |      |        |  |

A G\_floating operand occupies 64 bits in a floating register, arranged as shown in Figure 2–8.

#### Figure 2–8: G\_floating Format

A G\_floating datum is specified by its address A, the address of the byte containing bit 0. The form of a G\_floating datum is sign magnitude with bit 15 the sign bit, bits <14:4> an excess-1024 binary exponent, and bits <3:0> and <63:16> a normalized 53-bit fraction with the redundant most significant fraction bit not represented. Within the fraction, bits of increasing significance are from 48 through 63, 32 through 47, 16 through 31, and 0 through 3. The 11-bit exponent field encodes the values 0 through 2047. An exponent value of 0, together with a sign bit of 0, is taken to indicate that the G\_floating datum has a value of 0.

If the result of a floating-point instruction has a value of zero, the instruction always produces a datum with a sign bit of 0, an exponent of 0, and all fraction bits of 0. Exponent values of 1..2047 indicate true binary exponents of

#### NOTE

-1023..1023. An exponent value of 0, together with a sign bit of 1, is taken as a reserved operand. Floating-point instructions processing a reserved operand take a user-visible arithmetic exception. The value of a G\_floating datum is in the approximate range  $0.56*10^{**}-308..0.9*10^{**}308$ . The precision of a G\_floating datum is approximately one part in  $2^{**}52$ , typically 15 decimal digits.

#### NOTE

Alpha implementations will impose a significant performance penalty when accessing  $G_{floating}$  operands that are not naturally aligned. (A naturally aligned  $G_{floating}$ floating datum has zero as the low-order three bits of its address.)

#### 2.2.5.3 D\_floating

A D\_floating datum in memory is 8 contiguous bytes starting on an arbitrary byte boundary. The bits are labeled from right to left, 0 through 63, as shown in Figure 2-9.

#### Figure 2–9: D\_floating Datum

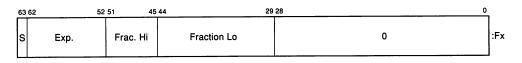

A D\_floating operand occupies 64 bits in a floating register, arranged as shown in Figure 2–10.

#### Figure 2–10: D\_floating Register Format

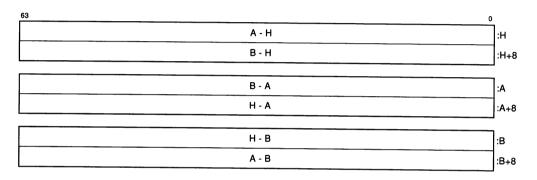

| 63 62  | 55 54 48 | 47 32         | 31 16         | 15 0        | -   |

|--------|----------|---------------|---------------|-------------|-----|

| S Exp. | Frac. Hi | Fraction Midh | Fraction Midl | Fraction Lo | :Fx |

The reordering of bits required for a D\_floating load or store are identical to those required for a G\_floating load or store. The G\_floating load and store instructions are therefore used for loading or storing D\_floating data.

A D\_floating datum is specified by its address A, the address of the byte containing bit 0. The memory form of a D\_floating datum is identical to an F\_floating datum except for 32 additional low significance fraction bits. Within the fraction, bits of increasing significance are from 48 through 63, 32 through 47, 16 through 31, and 0 through 6. The exponent conventions and approximate range of values is the same for D\_floating as F\_floating. The precision of a D\_floating datum is approximately one part in  $2^{**55}$ , typically 16 decimal digits.

#### NOTE

D\_floating is not a fully supported data type; no D\_floating arithmetic operations are provided in the architecture. For backward compatibility, exact D\_ floating arithmetic may be provided via software emulation. D\_floating "format compatibility" in which binary files of D\_floating numbers may be processed, but without the last 3 bits of fraction precision, can be obtained via conversions to G\_floating, G arithmetic operations, then conversion back to D\_floating.

#### NOTE

Alpha implementations will impose a significant performance penalty on access to D\_floating operands that are not naturally aligned. (A naturally aligned D\_ floating datum has zero as the low-order three bits of its address.)

## 2.2.6 IEEE Floating-Point Formats

The IEEE standard for binary floating-point arithmetic, ANSI/IEEE 754-1985, defines four floating-point formats in two groups, basic and extended, each having two widths, single and double. The Alpha architecture supports the basic single and double formats, with the basic double format serving as the extended single format. The values representable within a format are specified by using three integer parameters:

- 1. P-the number of fraction bits

- 2. Emax—the maximum exponent

- 3. Emin—the minimum exponent

Within each format, only the following entities are permitted:

- 1. Numbers of the form (-1)\*\*S x 2\*\*E x b(0).b(1)b(2)..b(P-1) where:

- a. S = 0 or 1

- b. E = any integer between Emin and Emax, inclusive

- c. b(n) = 0 or 1

- 2. Two infinities—positive and negative

- 3. At least one Signaling NaN

- 4. At least one Quiet NaN

NaN is an acronym for Not-a-Number. A NaN is an IEEE floating-point bit pattern that represents something other than a number. NaNs come in two forms: Signaling NaNs and Quiet NaNs. Signaling NaNs are used to provide values for uninitialized variables and for arithmetic enhancements. Quiet NaNs provide retrospective diagnostic information regarding previous invalid or unavailable data and results. Signaling NaNs signal an invalid operation when they are an operand to an arithmetic instruction, and may generate an arithmetic exception. Quiet NaNs propagate through almost every operation without generating an arithmetic exception.

Arithmetic with the infinities is handled as if the operands were of arbitrarily large magnitude. Negative infinity is less than every finite number; positive infinity is greater than every finite number.

### 2.2.6.1 S\_Floating

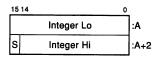

An IEEE single-precision, or S\_floating, datum occupies 4 contiguous bytes in memory starting on an arbitrary byte boundary. The bits are labeled from right to left, 0 through 31, as shown in Figure 2–11.

### Figure 2–11: S\_floating Datum

| 15 14 | 7     | 6      | 0       |

|-------|-------|--------|---------|

|       | Fract | ion Lo | :A      |

| s     | Exp.  | Frac.  | Hi :A+2 |

An S\_floating operand occupies 64 bits in a floating register, left-justified in the 64-bit register, as shown in Figure 2–12.

### Figure 2–12: S\_floating Register Format

The S\_floating load instruction reorders bits on the way in from memory, expanding the exponent from 8 to 11 bits, and sets the low-order fraction bits to zero. This produces in the register an equivalent T\_floating number, suitable for either S\_ floating or T\_floating operations. The mapping from 8-bit memory-format exponents to 11-bit register-format exponents is shown in Table 2–2.

Memory <30:23>

Register <62:52>

1 1111111

1 111 1111111

1 xxxxxxx

1 000 xxxxxxx (xxxxxx not all 1's)

0 xxxxxxx

0 111 xxxxxxx (xxxxxx not all 0's)

0 0000000

0 000 0000000

Table 2–2: S\_floating Load Exponent Mapping

This mapping preserves both normal values and exceptional values. Note that the mapping for all 1's differs from that of F\_floating load, since for S\_floating all 1's is an exceptional value and for F\_floating all 1's is a normal value.

The S\_floating store instruction reorders register bits on the way to memory and does no checking of the low-order fraction bits. Register bits <61:59> and <28:0> are ignored by the store instruction. The S\_floating load instruction does no checking of the input.

The S\_floating store instruction does no checking of the data; the preceding operation should have specified an S\_floating result.