# **TABLE OF CONTENTS**

| Section |                    |                                     | Page   |

|---------|--------------------|-------------------------------------|--------|

| 1       | GENER              | AL INFORMATION                      | 1-1    |

|         | 1.1                | INTRODUCTION                        | 1-1    |

|         | 1.1.1              | Product Definition                  | 1-1    |

|         | 1.1.2              | Manual Purpose and Intended Use     | 1-3    |

|         | 1.1.3              | Drive Functions and Applications    |        |

|         | 1.1.4              | Disc Pack                           |        |

|         | 1.1.5              | Hardware Orientation                | 1-8    |

|         | 1.1.6              | Basic Drive Operations              |        |

|         | 1.2                | DRIVE SPECIFICATIONS                |        |

|         | 1.2.1              | Drive General Specifications        |        |

|         | 1.2.2              | Error Rates                         |        |

|         | 1.2.3              | PM Time and MTBF                    |        |

|         | 1.2.4              | Response to Brownouts               |        |

|         | 1.3                | INTERFACE SPECIFICATIONS            |        |

|         | 1.3.1              | Electrical Interface Specifications |        |

|         | 1.3.1.1            | Command Summary                     |        |

|         | 1.3.1.2            | DCL to Drive Lines                  |        |

|         | 1.3.1.3            | Drive to DCL Lines                  |        |

|         | 1.3.1.4            | Sequencing                          |        |

|         | 1.3.1.5            | Line Drivers and Receivers          |        |

|         | 1.3.1.6            | AC Power                            |        |

|         | 1.3.1.7            | Grounding                           |        |

|         | 1.3.1.8            | Termination Requirement             |        |

|         | 1.3.2              | Mechanical Interface Specifications |        |

|         | 1.3.2.1            | Connector Locations                 |        |

|         | 1.3.2.2            | AC Power Connections                |        |

|         | 1.3.2.3            | Signal Connections                  |        |

|         | 1.3.2.4<br>1.3.2.5 | Ground Connection                   |        |

|         | 1.3.2.6            |                                     |        |

|         | 1.3.2.0            | Controls and Indicators             | . 1-37 |

| 2       | INSTAL             | LATION AND OPERATION                | 2-1    |

|         | 2.1                | SCOPE AND INTENDED USE              | 2-1    |

|         | 2.2                | SPECIAL TOOLS AND TEST EQUIPMENT    | 2-1    |

|         | 2.3                | INSTALLATION                        | 2-1    |

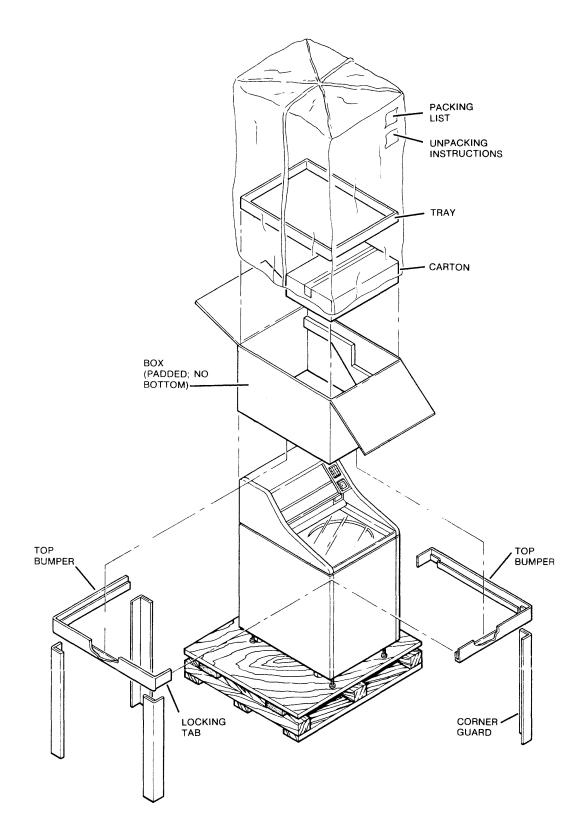

|         | 2.3.1              | Unloading and Moving                | 2-1    |

|         | 2.3.2              | Unpacking                           | 2-3    |

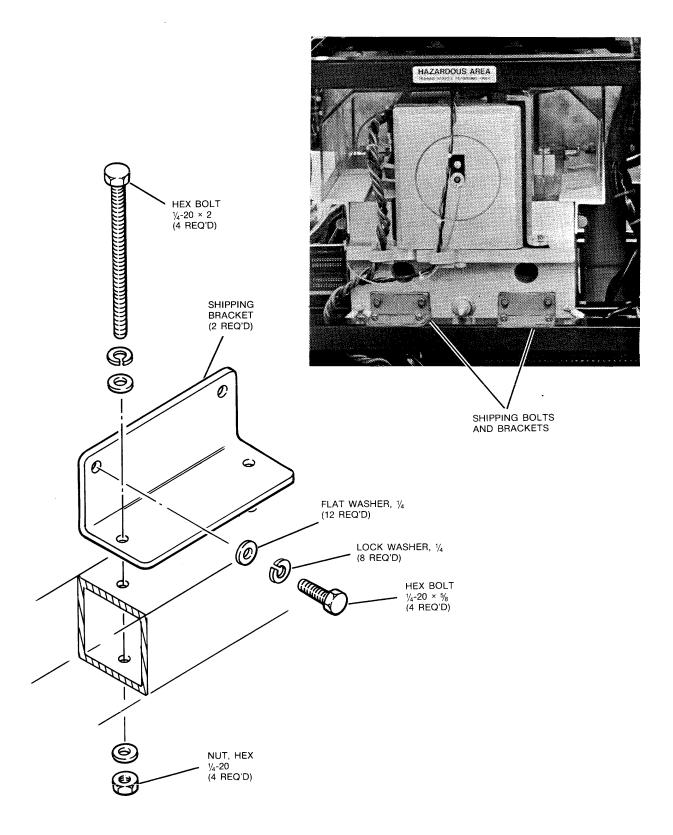

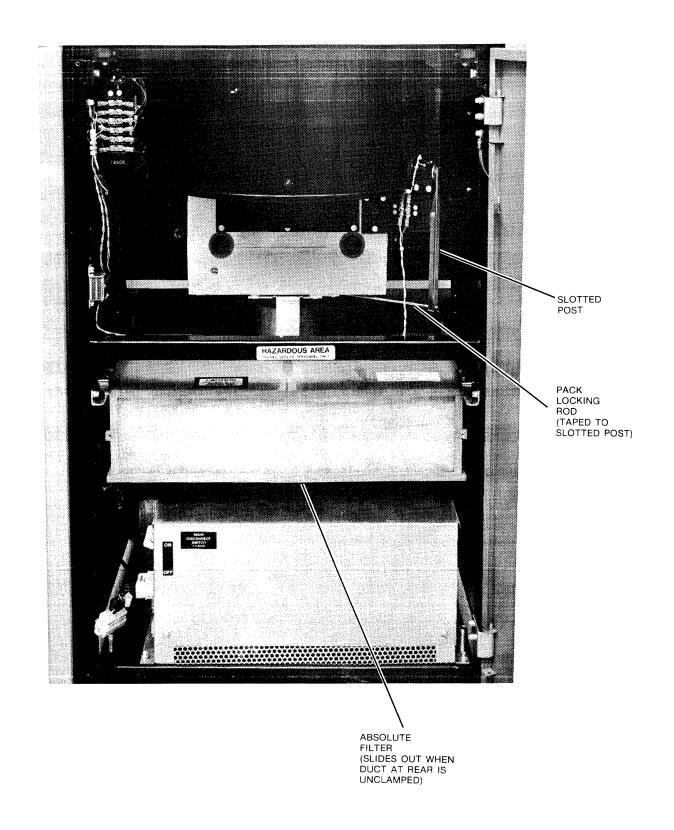

|         | 2.3.3              | Mechanical Preparation              | 2-3    |

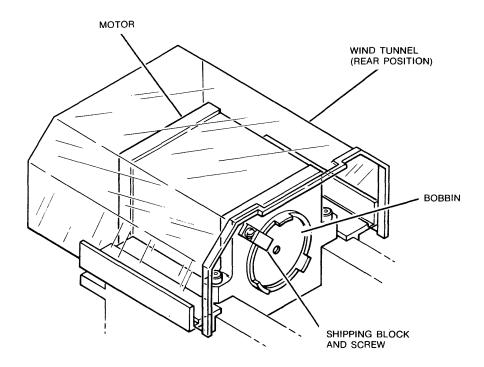

|         | 2.3.4              | Shipping Hardware Removal           |        |

|         | 2.3.5              | Terminal Board Checks               |        |

|         | 2.3.6              | Power Configuration Check           | 2-8    |

|         | 2.3.7              | Grounding Check                     |        |

|         | 2.3.8              | Prepower Checks                     | . 2-10 |

| Section |                            |                                                        | Page  |

|---------|----------------------------|--------------------------------------------------------|-------|

| 2       | INSTALL                    | ATION AND OPERATION (Continued)                        |       |

|         | 2.3.9                      | Power On Checks                                        | 2-10  |

|         | 2.3.10                     | Readiness Tests                                        | 2-12  |

|         | 2.3.11                     | Leveling                                               | 2-12  |

|         | 2.3.12                     | Covers and Kickplates                                  | 2-12  |

|         | 2.4                        | OPERATION                                              | 2-12  |

|         | 2.4.1                      | User Information                                       | 2-12  |

|         | 2.4.2                      | Operator Controls                                      | 2-13  |

|         | 2.4.3                      | Operator Displays                                      | 2-14  |

|         | 2.4.4                      | Normal Operating Procedures                            | 2-14  |

|         | 2.4.4.1                    | Handling the Disc Pack                                 | 2-14  |

|         | 2.4.4.2                    | Disc Pack Installation and Removal                     | 2-15  |

|         | 2.4.4.3                    | Drive Address Assignment                               | 2-16  |

|         | 2.4.4.4                    | Spindle Motor Start/Stop                               | 2-16  |

|         | 2.4.5                      | User Responses to Abnormal Conditions                  | 2-17  |

|         | 2.4.5.1                    | Clearing an Unsafe Condition                           | 2-17  |

|         | 2.4.5.2                    | Removing a Pack with No Drive Power                    | 2-17  |

|         | 2.4.5.3                    | Detecting Head-to-Disc Interference                    | 2-17  |

|         | 2.5                        | REMOVAL                                                | 2-18  |

|         | 2.5.1                      | Preparation                                            | 2-18  |

|         | 2.5.2                      | Shipping Hardware Installation                         | 2-18  |

| 3       | PRINCIP                    | PLES OF OPERATION                                      | . 3-1 |

|         | 3.1                        | CONTENTS AND INTENDED USE                              | 3-1   |

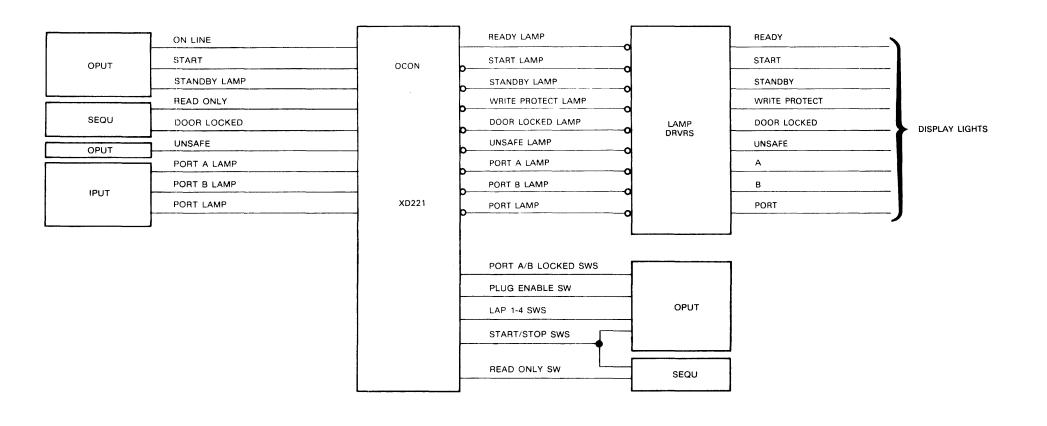

|         | 3.2                        | OPERATOR CONTROL SYSTEM                                |       |

|         | 3.2.1                      | System Description                                     |       |

|         | 3.2.2                      | Operator Control PCB                                   |       |

|         | 3.2.2.1                    | LAP Plug Enabling                                      |       |

|         | 3.2.2.2                    | Generating Port A and Port B                           |       |

|         | 3.2.2.3                    | Transmitting Display Commands                          |       |

|         | 3.2.3                      | Lamp Matrix PCB                                        |       |

|         | 3.2.4                      | System Performance Requirements                        |       |

|         | 3.2.4.1                    | Addressing                                             |       |

|         | 3.3                        | DCL SUPPORT SYSTEM                                     |       |

|         | 3.3.1                      | System Description                                     |       |

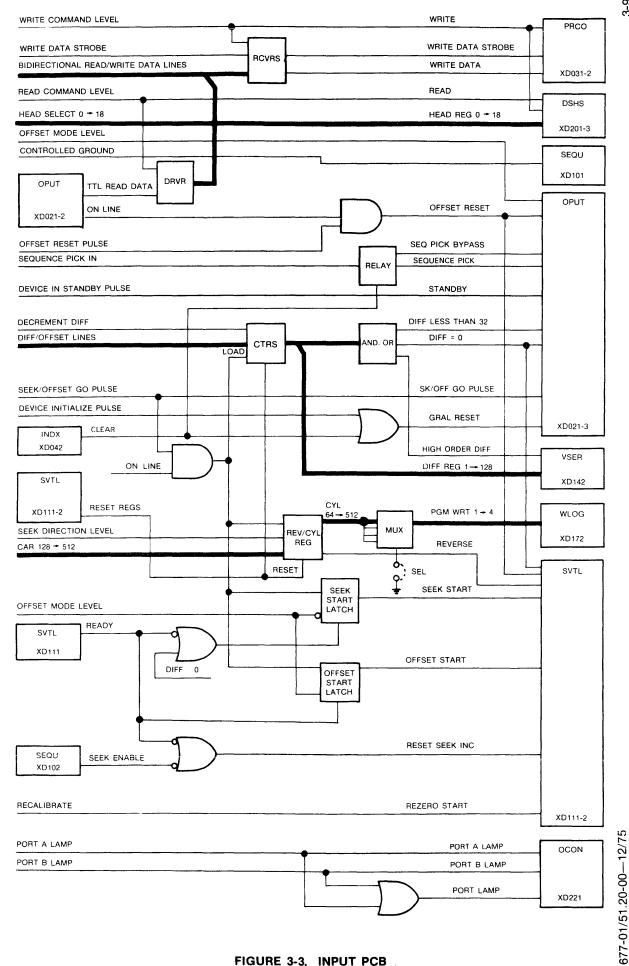

|         | 3.3.2                      | Input PCB                                              |       |

|         | 3.3.2.1                    | Providing Seek Go Instructions                         |       |

|         | 3.3.2.2                    | Providing Seek Offset Instructions                     |       |

|         | 3.3.2.3                    | Providing Write Operation Instructions                 |       |

|         | 3.3.2.4                    | Transmitting Read Data                                 | 3-10  |

|         | 3.3.2.5                    | Transmitting Recalibrate Command                       | 3-10  |

|         | 3.3.2.6                    | Initializing the Drive                                 | 3-10  |

|         | 3.3.2.7                    | Placing Drive in Standby Mode                          |       |

|         | 3.3.2. <i>1</i><br>3.3.2.8 | Resetting an Offset Operation                          | 3-10  |

|         | 3.3.2.6<br>3.3.2.9         |                                                        |       |

|         | 3.3.2.9                    | Port Enabling  Providing Power Sequencing Instructions |       |

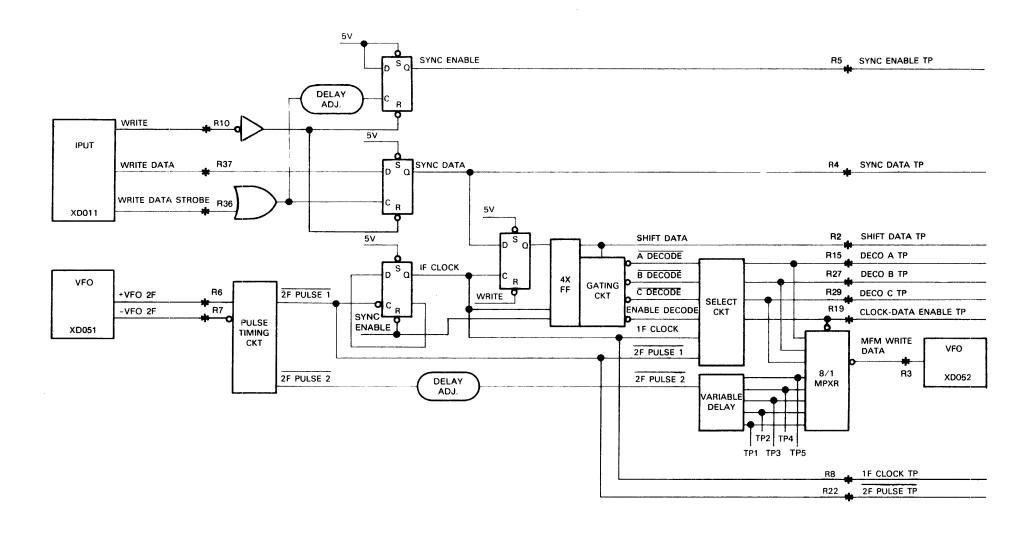

|         | 3.3.2.10                   | Precompensation PCB                                    |       |

|         | 0.0.0                      | I FECULIDENSAUDH FUD                                   | 0 10  |

| Section |                    |                                                                                           | Page         |

|---------|--------------------|-------------------------------------------------------------------------------------------|--------------|

| 3       | PRINCIP            | LES OF OPERATION (Continued)                                                              |              |

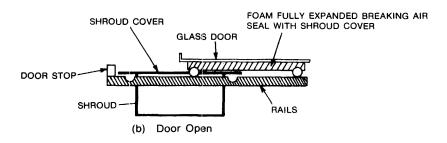

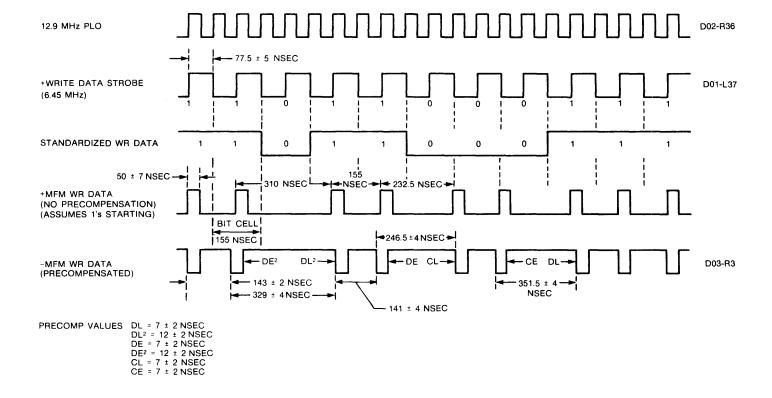

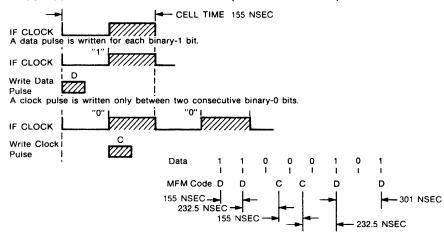

|         | 3.3.3.1            | Encoding and Precompensating Data                                                         | 3-10         |

|         | 3.3.3.2            | Write Precompensation Requirements                                                        | 3-12         |

|         | 3.3.3.3            | Signal Input Requirements                                                                 | 3-14         |

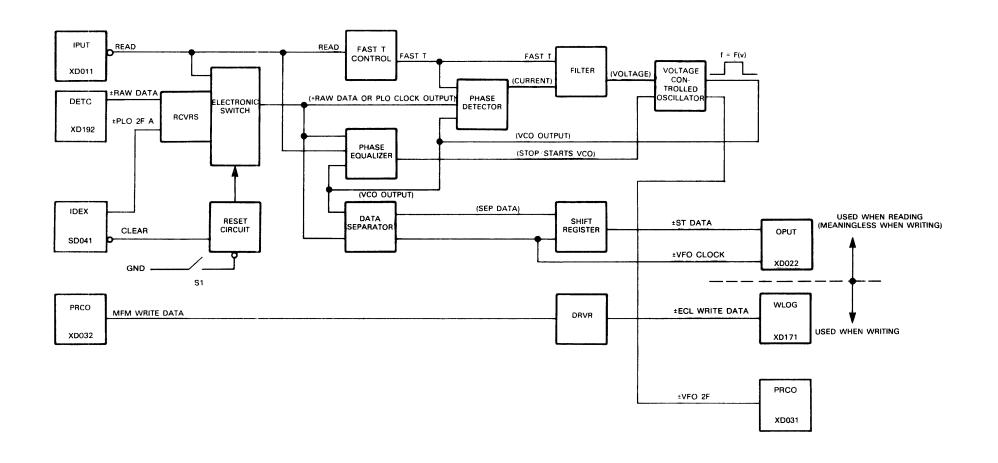

|         | 3.3.4              | Variable Frequency Oscillator PCB                                                         | 3-15         |

|         | 3.3.4.1            | Decoding Raw Data and Generating VFO Clock.                                               | 3-15         |

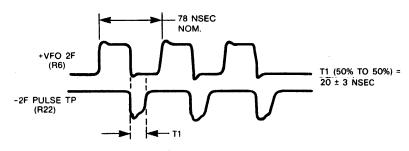

|         | 3.3.4.2            | Converting Write Data and Generating VFO 2F                                               | 3-17         |

|         | 3.3.4.3            | VFO Performance Requirements                                                              | 3-17         |

|         | 3.3.5              | Related Circuitry                                                                         | 3-20         |

|         | 3.3.5.1            | Generating PLO Clock Outputs                                                              | 3-20         |

|         | 3.3.5.2            | Monitoring Regulated Power Supplies                                                       | 3-20         |

|         | 3.3.5.3            | PLO Performance Requirements                                                              | 3-20         |

|         | 3.3.6              | Output PCB                                                                                | 3-23         |

|         | 3.3.6.1            | Responding to DCL Commands                                                                | 3-23         |

|         | 3.3.6.2            | Transmitting Read Data                                                                    | 3-23         |

|         | 3.3.6.3            | Indicating an Unsafe Drive                                                                | 3-23         |

|         | 3.3.6.4            | Providing Start, Standby,                                                                 |              |

|         |                    | and Unsafe Lamp Indications                                                               | 3-23         |

|         | 3.3.6.5            | Generating On Line                                                                        | 3-23         |

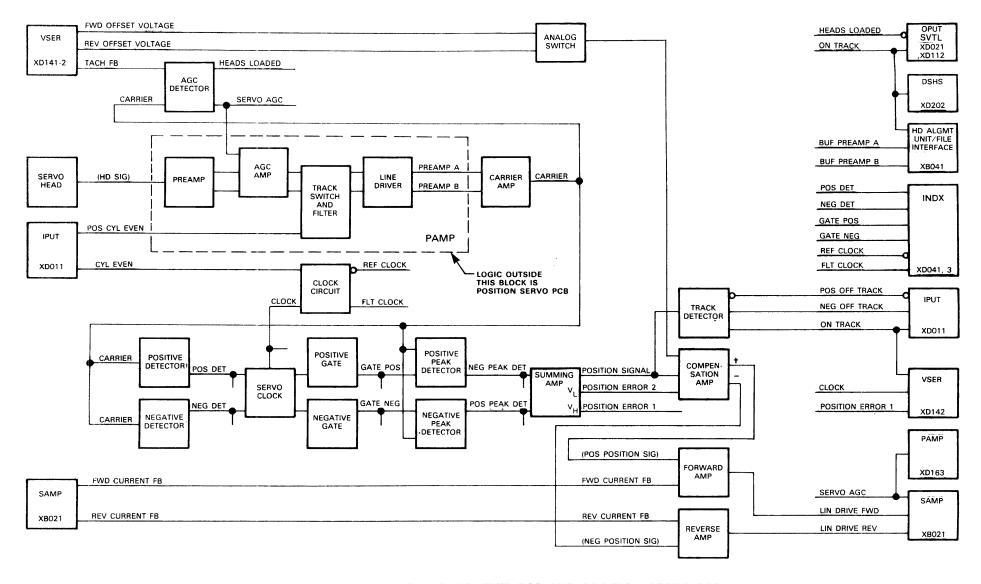

|         | 3.4                | SERVO SYSTEM                                                                              | 3-27         |

|         | 3.4.1              | System Description                                                                        | 3-27         |

|         | 3.4.2              | Servo Operating Modes                                                                     | 3-30         |

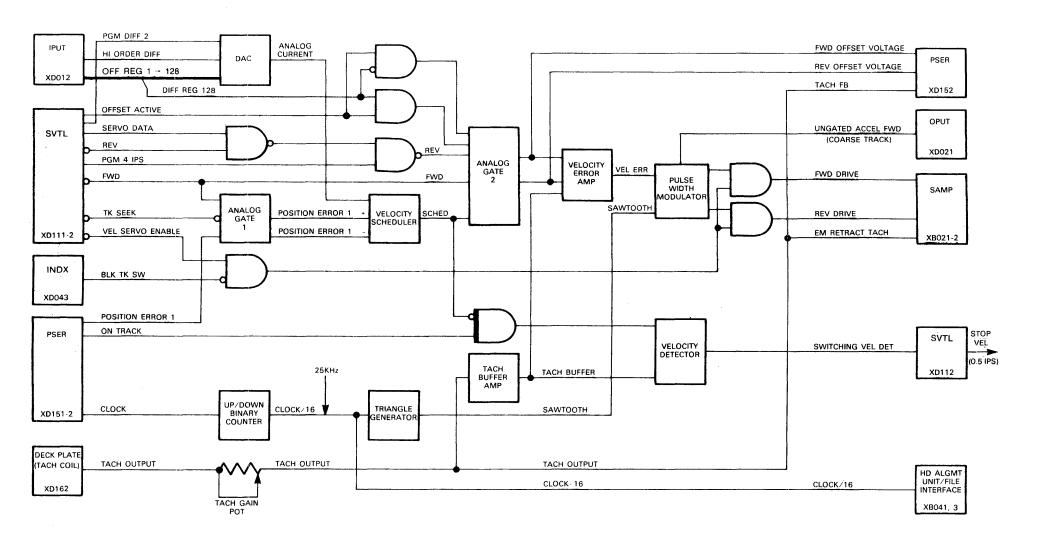

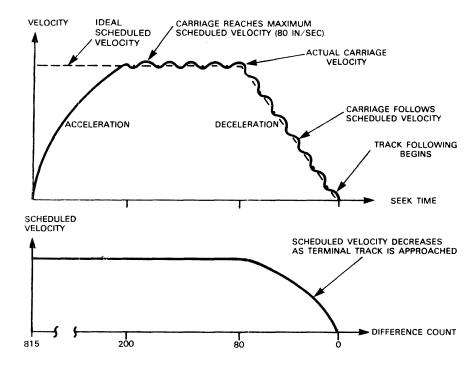

|         | 3.4.2.1            | Velocity Control Mode                                                                     | 3-30         |

|         | 3.4.2.2            | Position Control Mode                                                                     | 3-31         |

|         | 3.4.2.3            | Emergency Retract Mode                                                                    | 3-32         |

|         | 3.4.3              | Access Mechanism                                                                          | 3-32         |

|         | 3.4.4              | Servo Surface                                                                             | 3-33         |

|         | 3.4.5              | Servo Head                                                                                | 3-33         |

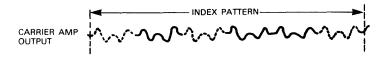

|         | 3.4.5.1            | Servo Carrier                                                                             | 3-33         |

|         | 3.4.5.2            | Carrier Amplitude                                                                         | 3-35         |

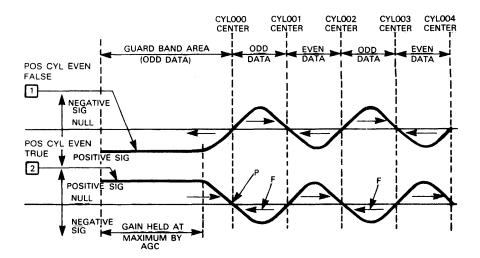

|         | 3.4.5.3            | Head Position Error                                                                       | 3-35         |

|         | 3.4.5.4            | Error Correction                                                                          | 3-36         |

|         | 3.4.6              | Servo Circuits                                                                            | 3-36<br>3-37 |

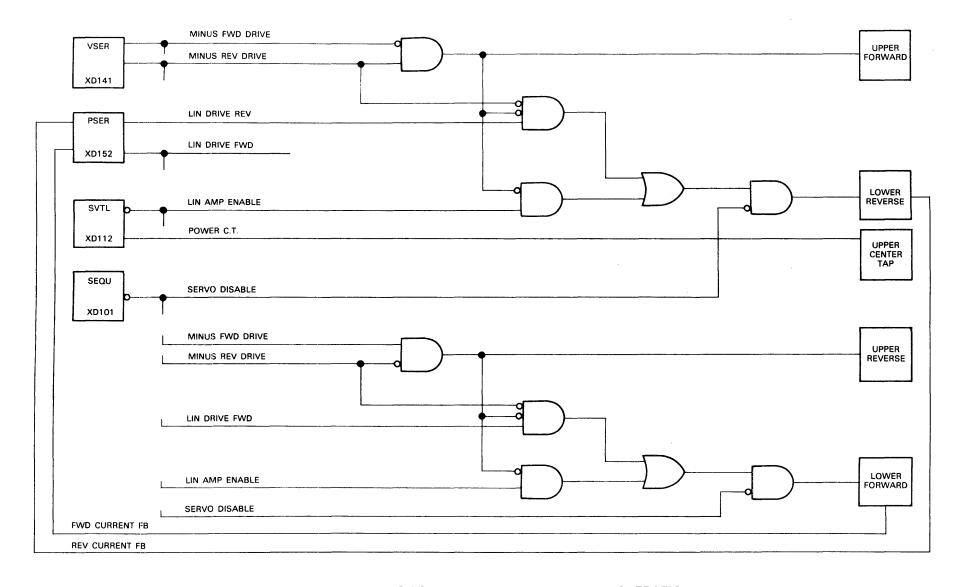

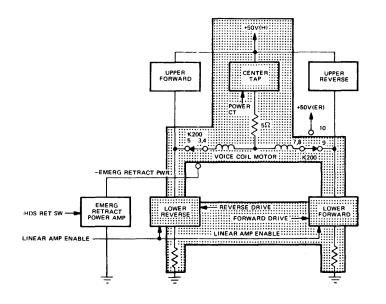

|         | 3.4.7              | Servo Power Amplifier PCB                                                                 |              |

|         | 3.4.7.1<br>3.4.7.2 | Operating in Position Control Mode                                                        | 3-37<br>3-37 |

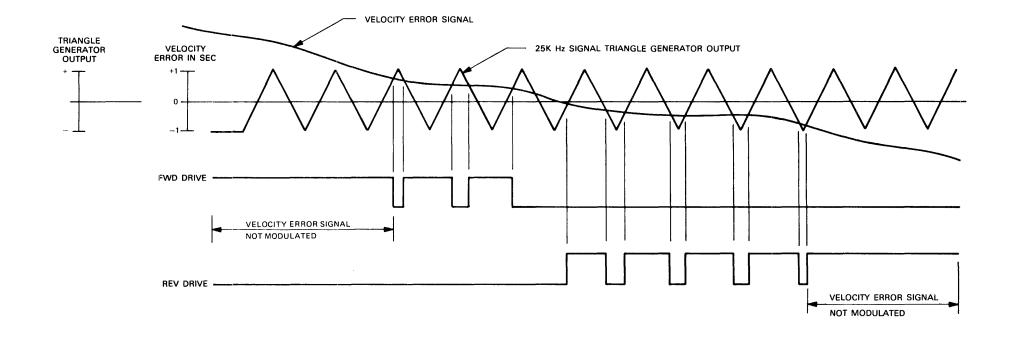

|         | 3.4.7.2            | Operating in Velocity Control Mode                                                        | 3-3 <i>1</i> |

|         | 3.4.7.3<br>3.4.8   | Operating in Emergency Retract Mode                                                       | 3-44         |

|         | 3.4.8.1            | Servo Preamplifier PCB                                                                    | 3-44         |

|         | 3.4.8.2            | Reading Servo Head Signal and Adjusting Gain .  Inverting or Noninverting the Head Signal | 3-44         |

|         | 3.4.6.2<br>3.4.9   |                                                                                           | 3-44         |

|         | 3.4.9<br>3.4.9.1   | Position Servo PCB                                                                        | 3-44         |

|         | 3.4.9.1            | Offset Track Following                                                                    | 3-44         |

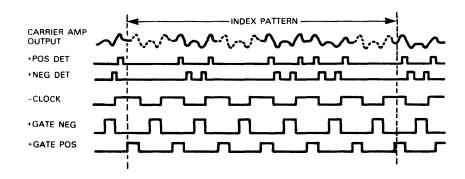

|         | 3.4.9.2<br>3.4.9.3 | Developing Index and Supporting Data Timing                                               | 3-47         |

|         | 3.4.9.4            | Supporting Velocity Control                                                               | 3-48         |

|         | 3.4.9.5            | PSER Performance Requirements                                                             | 3-48         |

|         | 3.4.10             | Velocity Servo PCB                                                                        | 3-48         |

|         | 3.4.10.1           | Scheduling of Seek Velocity                                                               | 3-48         |

| Section |          |                                                | Page |

|---------|----------|------------------------------------------------|------|

| 3       | PRINCIP  | PLES OF OPERATION (Continued)                  |      |

|         | 3.4.10.2 | Providing Linear Power Control                 | 3-50 |

|         | 3.4.10.3 | Terminating Velocity Control                   | 3-50 |

|         | 3.4.10.4 | Transmitting Offset Value                      | 3-50 |

|         | 3.4.10.5 | Responding to a DCL Command                    | 3-50 |

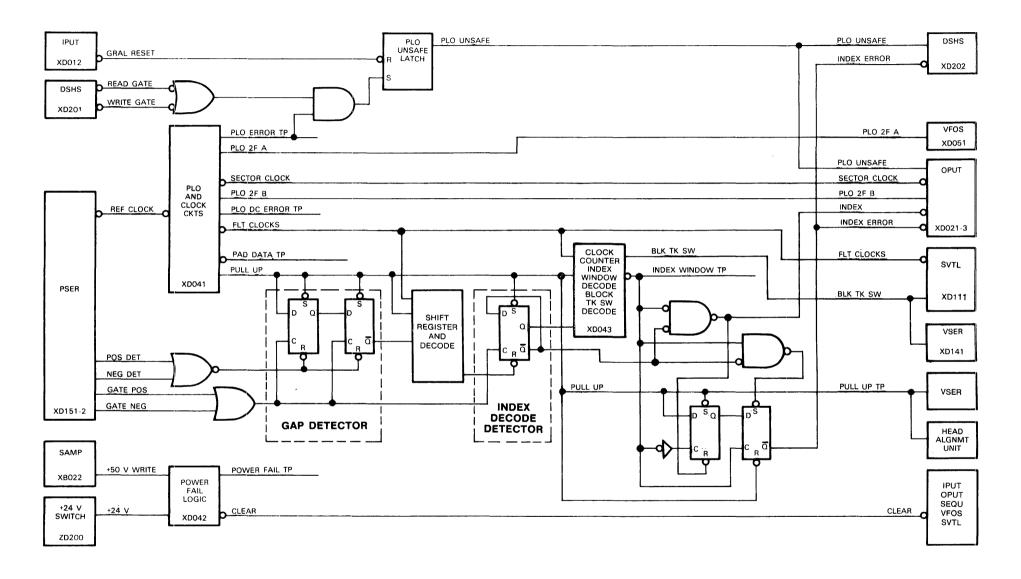

|         | 3.4.11   | Index PCB                                      | 3-52 |

|         | 3.4.11.1 | Detecting Index                                | 3-52 |

|         | 3.4.11.2 | Blocking Servo Operation                       | 3-52 |

|         | 3.4.11.3 | Generating PLO Outputs                         | 3-52 |

|         | 3.4.11.4 | Checking for Power Failure                     | 3-52 |

|         | 3.4.11.5 | INDX Performance Requirements                  | 3-52 |

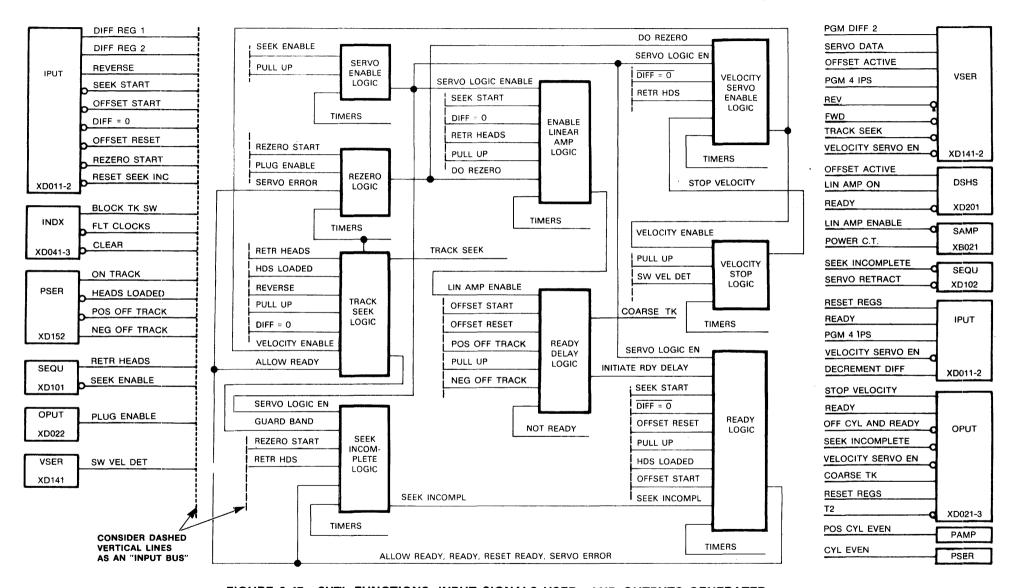

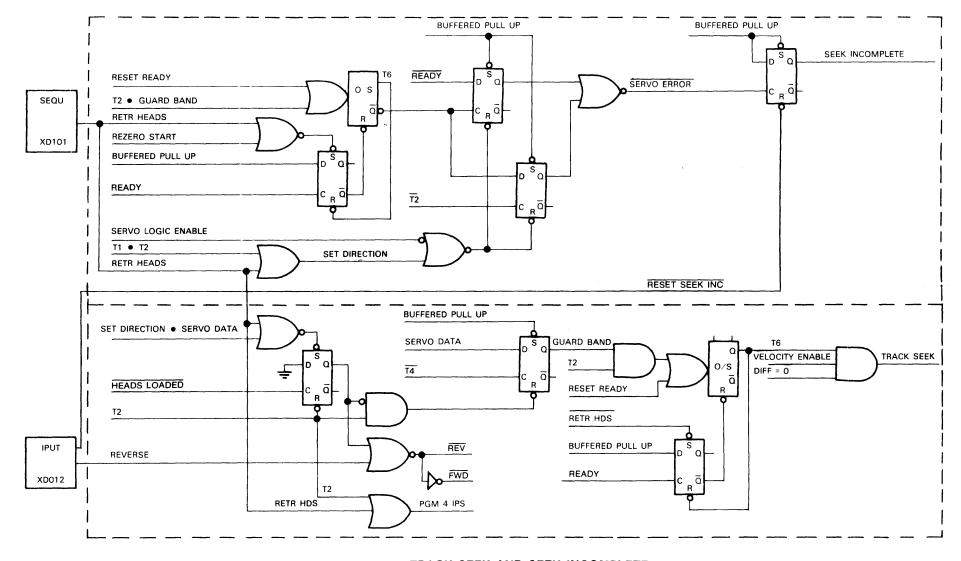

|         | 3.4.12   | Servo Control PCB                              | 3-54 |

|         | 3.4.12.1 | Enabling Servo Logic                           | 3-54 |

|         | 3.4.12.2 | Enabling Rezeroing                             | 3-54 |

|         | 3.4.12.3 | Enabling Velocity Control                      | 3-54 |

|         | 3.4.12.4 | Stopping Velocity Control                      | 3-54 |

|         | 3.4.12.5 | Enabling Power Amp                             | 3-58 |

|         | 3.4.12.6 | Delaying Ready                                 | 3-58 |

|         | 3.4.12.7 | Allowing Ready                                 | 3-58 |

|         | 3.4.12.8 | Enabling a Seek                                | 3-58 |

|         | 3.4.12.9 | Detecting an Incomplete Seek                   | 3-58 |

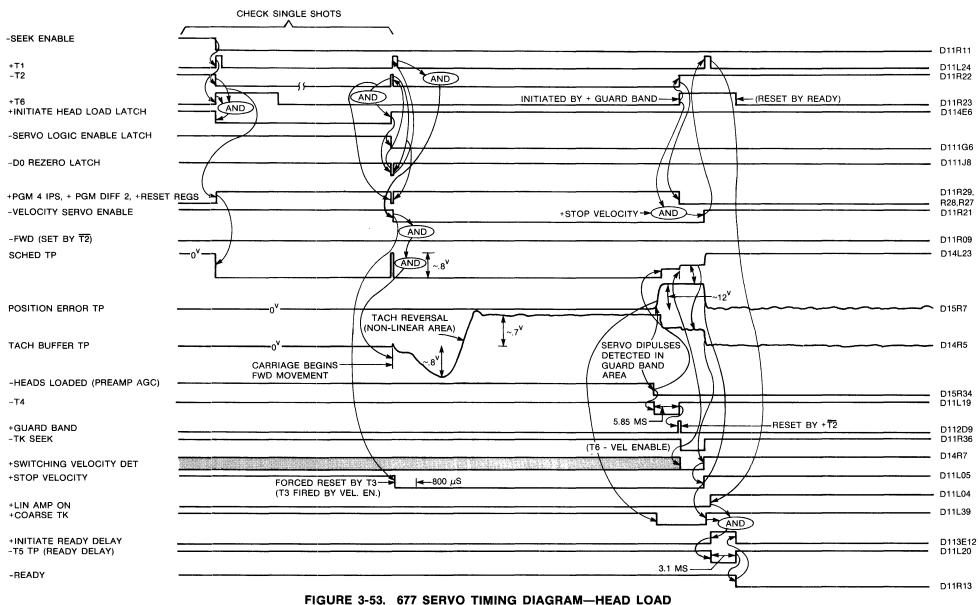

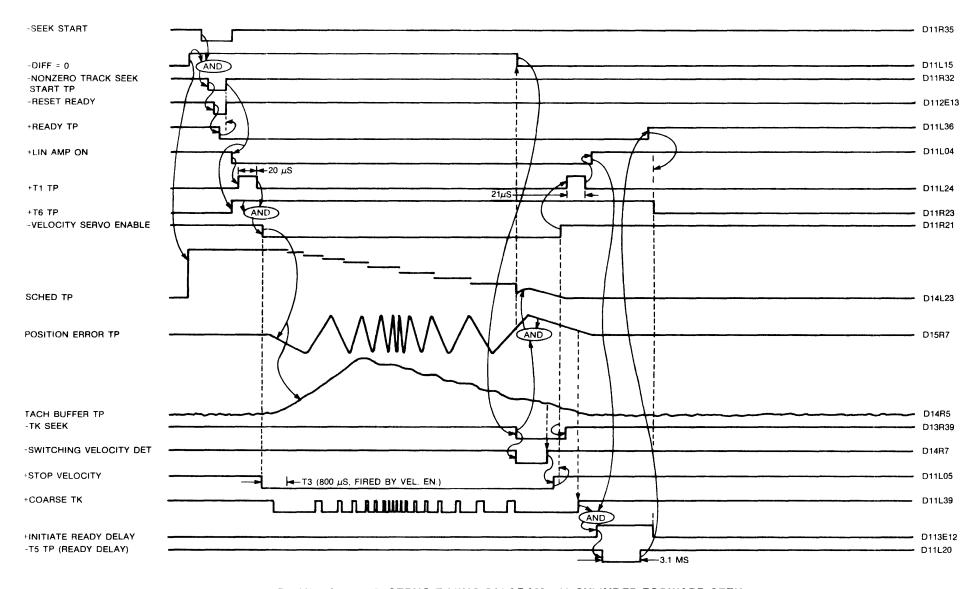

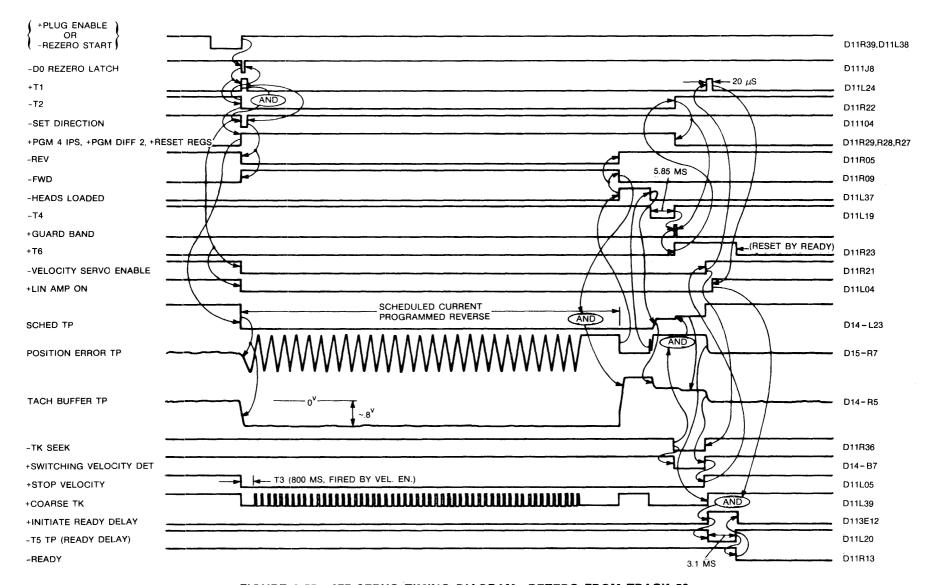

|         | 3.4.13   | Timing Diagrams and Waveforms                  | 3-58 |

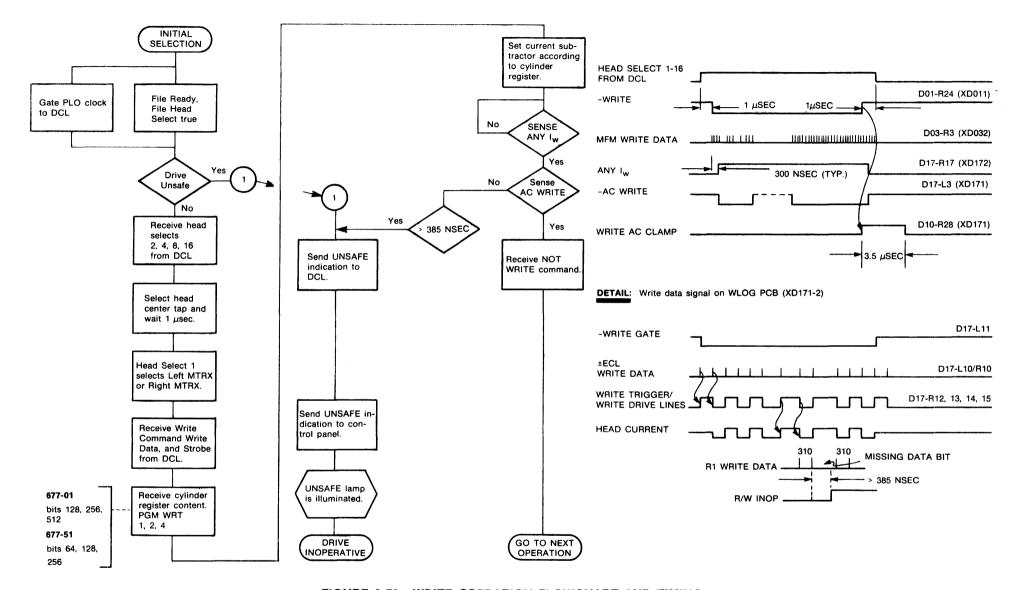

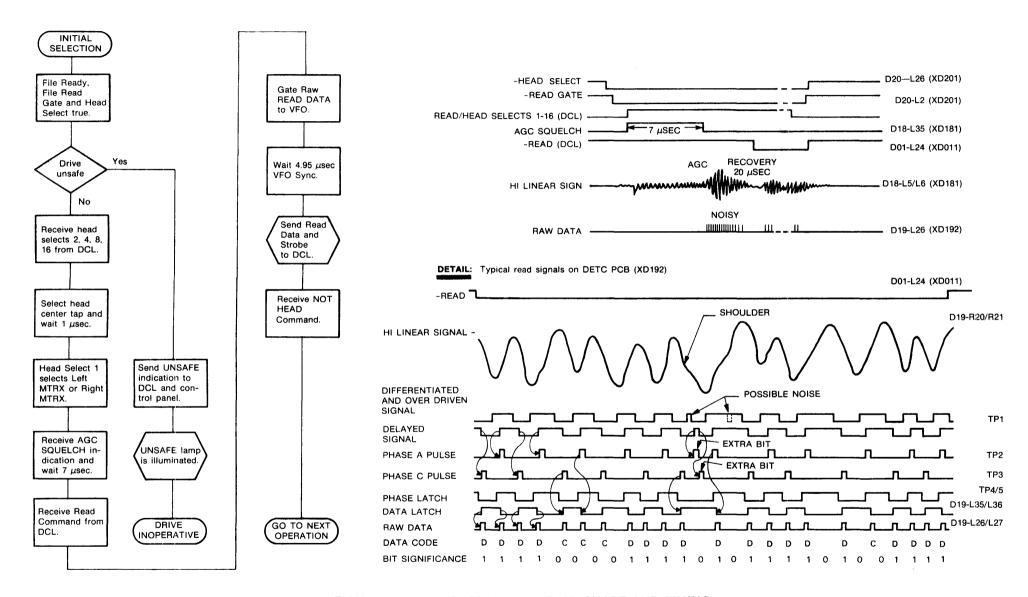

|         | 3.5      | READ/WRITE SYSTEM                              | 3-72 |

|         | 3.5.1    | System Description                             | 3-72 |

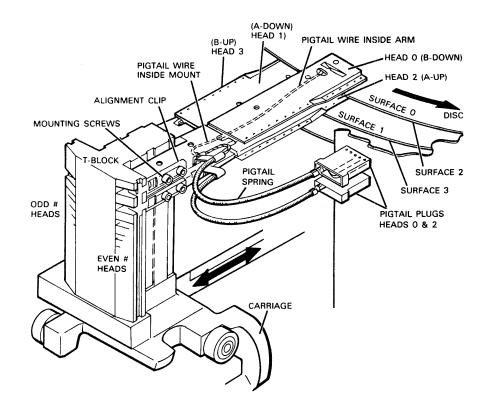

|         | 3.5.1.1  | Head Numbering and Containment                 | 3-72 |

|         | 3.5.1.2  | Head/Arm Assembly Components                   | 3-72 |

|         | 3.5.1.3  | Head Communication with Read/Write Circuits    | 3-72 |

|         | 3.5.1.4  | Selection of Read or Write Operation           | 3-72 |

|         | 3.5.1.5  | Identification of Servo Head                   | 3-73 |

|         | 3.5.1.6  | Identification of 100 MB Versus 200 MB Heads . | 3-73 |

|         | 3.5.1.7  | Head Adjustments                               | 3-73 |

|         | 3.5.1.8  | Data Transfer Synchronization                  | 3-73 |

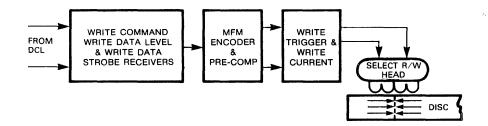

|         | 3.5.1.9  | Channel Write Operation                        | 3-73 |

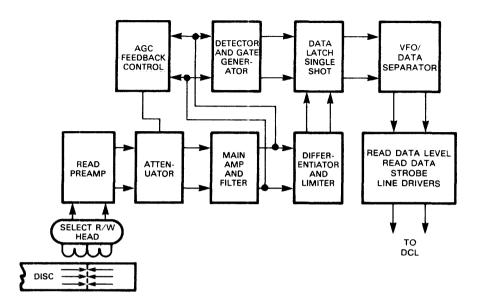

|         | 3.5.1.10 | Channel Read Operation                         | 3-73 |

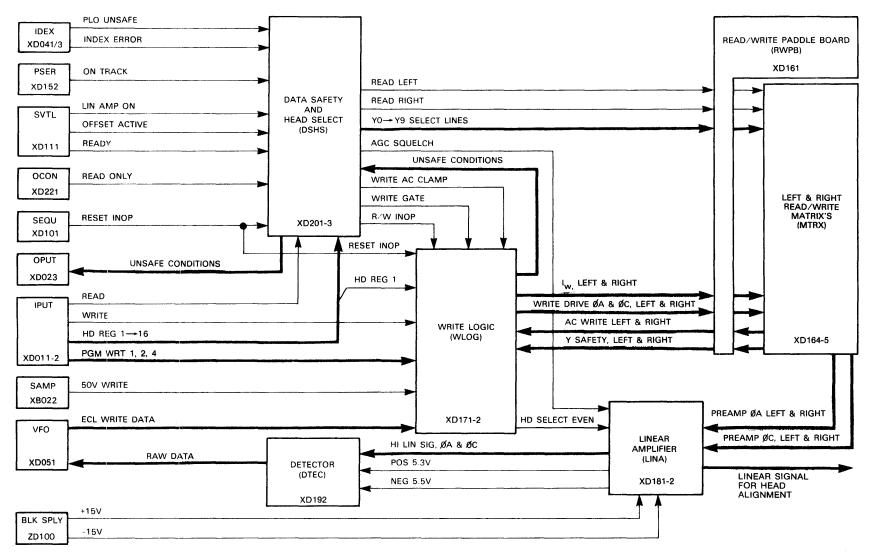

|         | 3.5.2    | Read/Write Circuits                            | 3-74 |

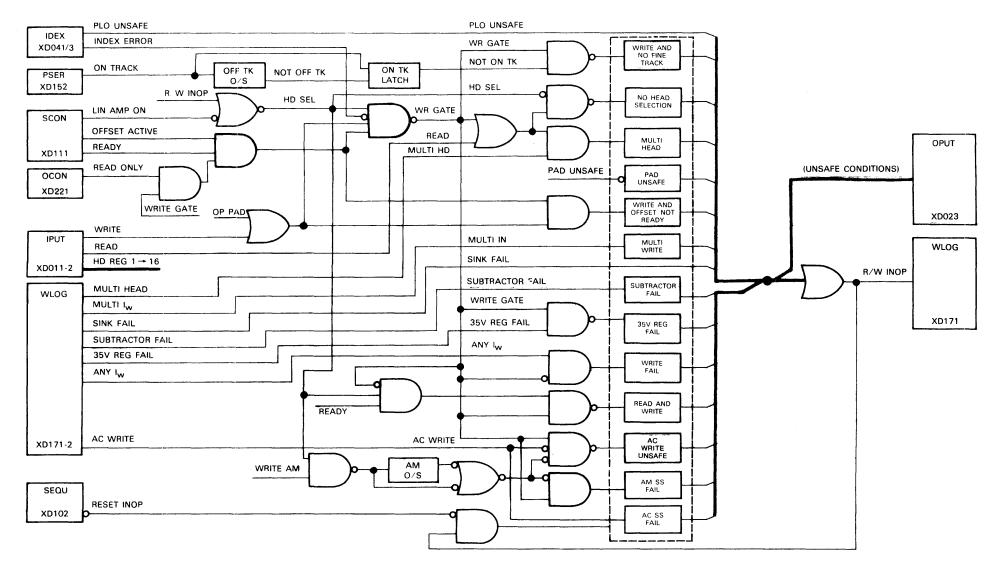

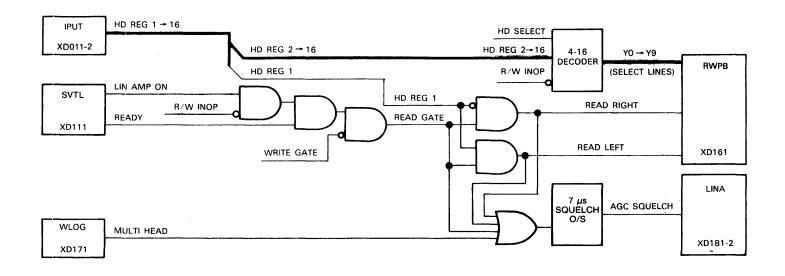

|         | 3.5.3    | Data Safety and Head Select PCB                | 3-74 |

|         | 3.5.3.1  | Read/Write Inoperate Circuits                  | 3-76 |

|         | 3.5.3.2  | Activating Head Select Line                    | 3-78 |

|         | 3.5.3.3  | Activating Read Matrix                         | 3-78 |

|         | 3.5.3.4  | Suppressing AGC Control                        | 3-78 |

|         | 3.5.3.5  | Performance Requirements                       | 3-78 |

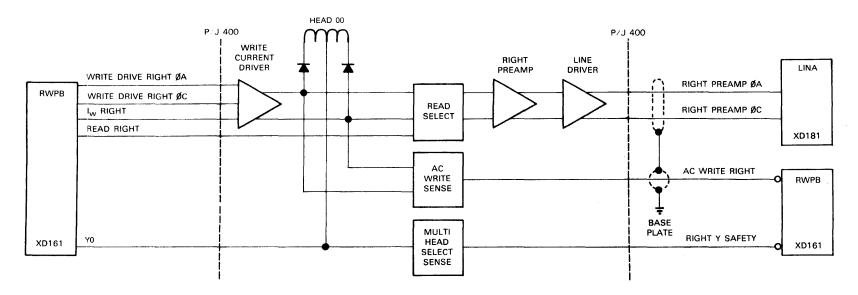

|         | 3.5.4    | Left and Right Read/Write Matrix PCBs          | 3-80 |

|         | 3.5.4.1  | Grounding Head Center Tap                      | 3-80 |

|         | 3.5.4.2  | Connecting Head to Preamp                      | 3-80 |

|         | 3.5.4.3  | Switching Current to Head                      | 3-80 |

|         | 3.5.4.4  | Failure Monitoring                             | 3-80 |

|         | 3.5.5    | Linear Amplifier PCB                           | 3-80 |

|         | 2551     | I INA Circuitra                                | 3-80 |

| Section |         |                                          | Page   |

|---------|---------|------------------------------------------|--------|

| 3       | PRINCI  | PLES OF OPERATION (Continued)            |        |

|         | 3.5.5.2 | Performance Requirements                 | . 3-82 |

|         | 3.5.6   | Detector PCB                             |        |

|         | 3.5.6.1 | Detector Circuitry                       | . 3-84 |

|         | 3.5.6.2 | Performance Requirements                 | . 3-86 |

|         | 3.5.7   | Write Logic PCB                          |        |

|         | 3.5.7.1 | Supplying Head Switching Current         | . 3-88 |

|         | 3.5.7.2 | Supplying Write Data                     |        |

|         | 3.5.7.3 | Failure Monitoring                       |        |

|         | 3.5.7.4 | Connecting Preamp to Main Amp            | . 3-91 |

|         | 3.5.7.5 | Performance Requirements                 | . 3-91 |

|         | 3.5.8   | Operation Flowcharts and Timing Diagrams | . 3-91 |

|         | 3.6     | SPINDLE CONTROL SYSTEM                   | . 3-94 |

|         | 3.6.    | System Description                       |        |

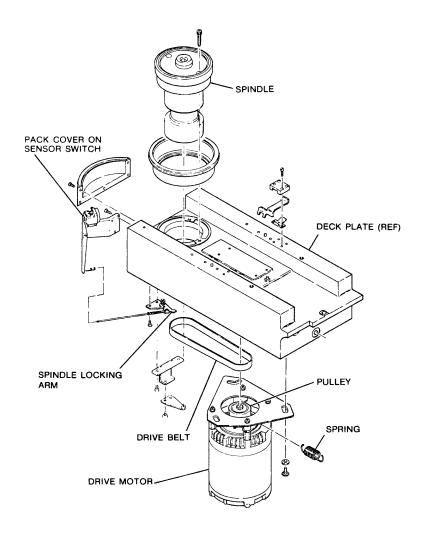

|         | 3.6.1.1 | Pack Drive Assembly                      | . 3-94 |

|         | 3.6.1.2 | Control Circuitry                        | . 3-95 |

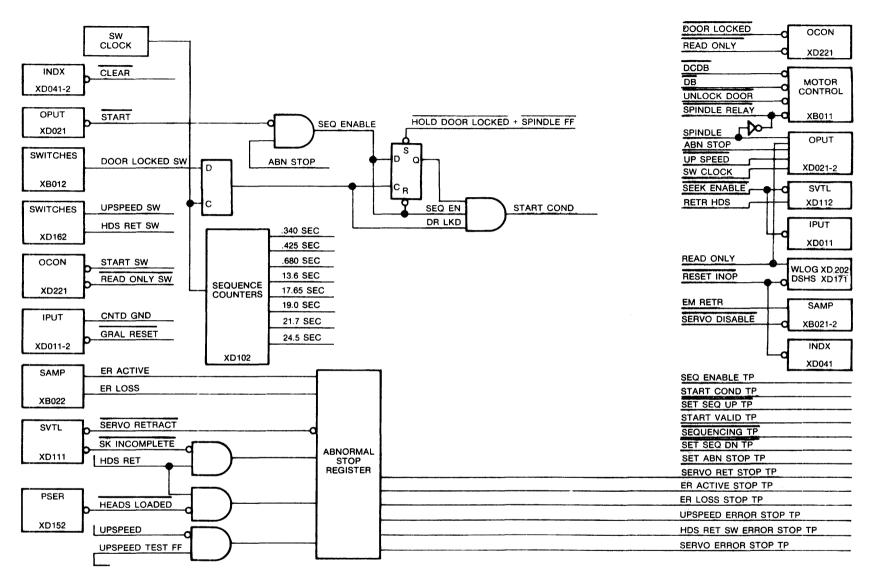

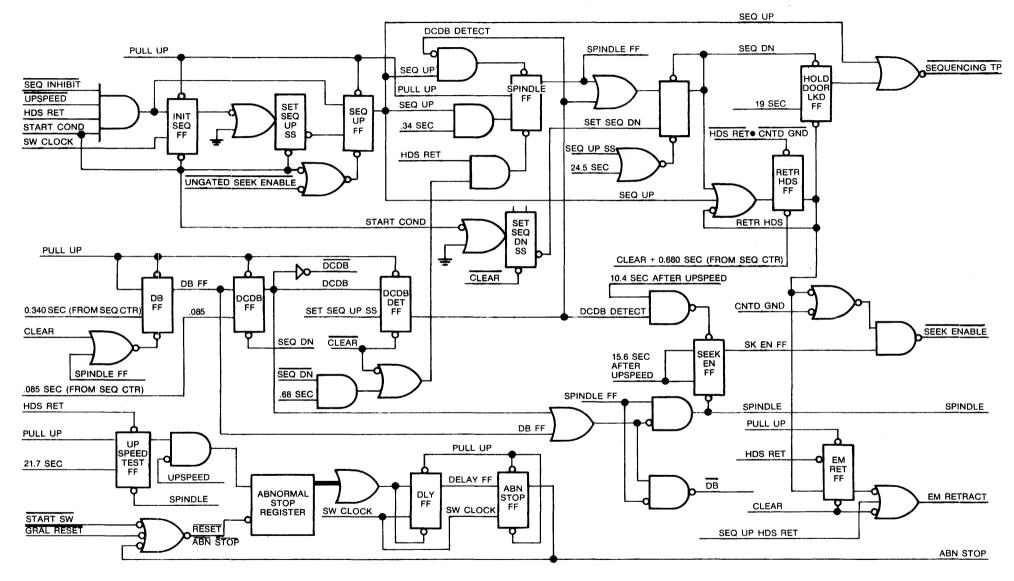

|         | 3.6.2   | Sequence PCB                             | . 3-95 |

|         | 3.6.2.1 | Starting Sequencing                      |        |

|         | 3.6.2.2 | Up Sequencing                            |        |

|         | 3.6.2.3 | Down Sequencing                          |        |

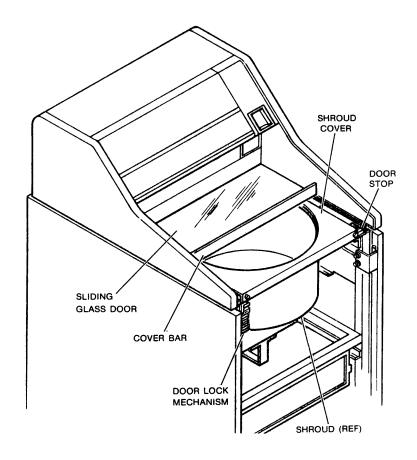

|         | 3.7     | PACK ACCESS SYSTEM                       | . 3-98 |

|         | 3.7.1   | System Description                       |        |

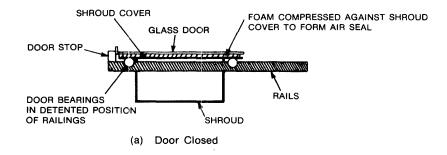

|         | 3.7.2   | Door Assembly and Locking Mechanism      |        |

|         | 3.7.3   | Air Seal                                 |        |

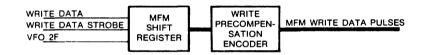

|         | 3.8     | AIRFLOW AND FILTRATION SYSTEM            |        |

|         | 3.8.1   | System Description                       |        |

|         | 3.8.2   | Mechanism for Upper Air Circulation      | 3-100  |

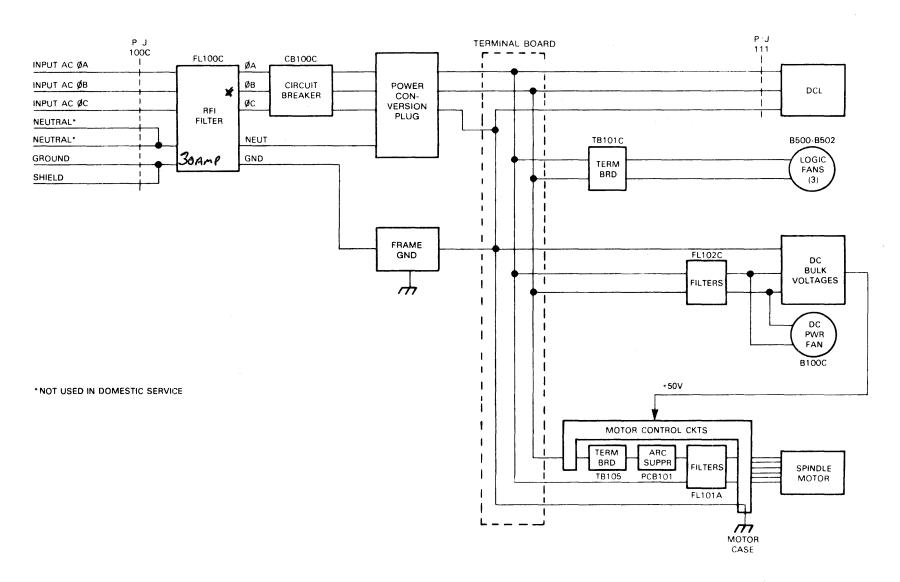

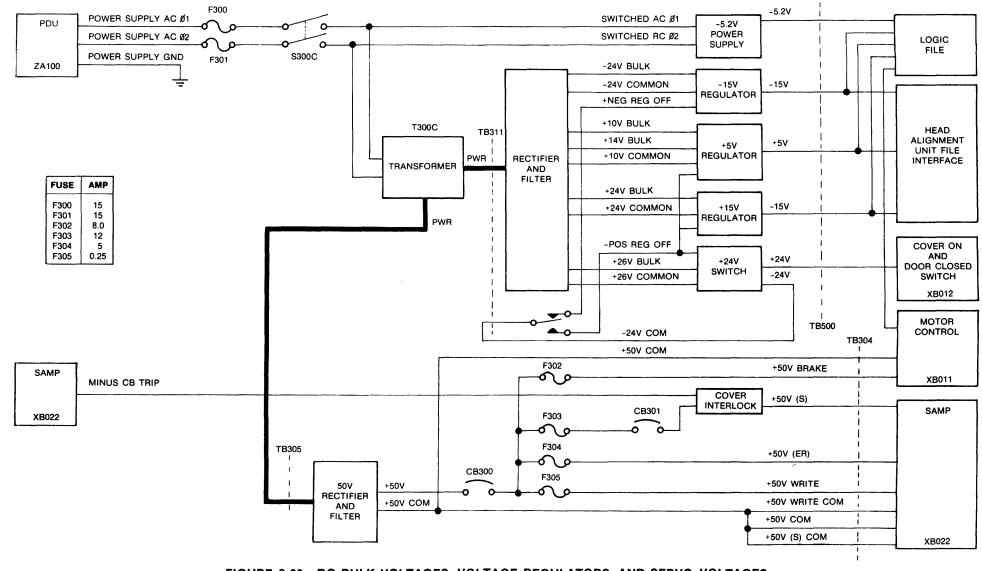

|         | 3.9     | POWER SYSTEM                             | 3-100  |

|         | 3.9.1   | System Description                       | 3-100  |

|         | 3.9.2   | Power Distribution Unit                  | 3-100  |

|         | 3.9.3   | Power Supply                             | 3-101  |

|         | 3.9.3.1 | Performance Requirements                 | 3-101  |

| 4       | MAINTE  | ENANCE                                   | 4-1    |

|         | 4.1     | INTRODUCTION                             | 4-1    |

|         | 4.2     | SAFETY PRACTICES AND GENERAL PRECAUTION  | . 4-1  |

|         | 4.2.1   | Personnel Safety                         | . 4-1  |

|         | 4.2.2   | Equipment Safety                         |        |

|         | 4.2.3   | Housekeeping                             |        |

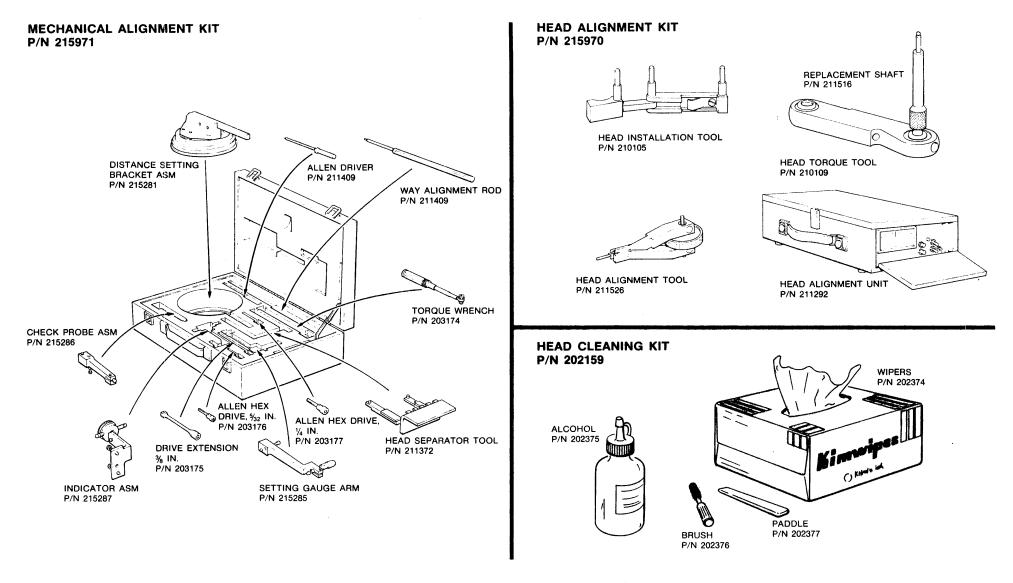

|         | 4.3     | SPECIAL TOOLS                            | 4-2    |

|         | 4.4     | TESTER HOOKUP, ROUTINES, AND RUN OPTIONS | 4-3    |

|         | 4.5     | SCHEDULED MAINTENANCE                    |        |

|         | 4.6     | UNSCHEDULED MAINTENANCE                  |        |

|         | 4.6.1   | Head Inspection and Cleaning             | 4-9    |

|         | 4.6.1.1 | Tools Required                           |        |

|         | 4.6.1.2 | Cleaning and Handling Precautions        |        |

|         | 4613    | Inspecting Heads                         | . 4-9  |

Section Page

| 4 | MAINTENAN | CE (Continued) |

|---|-----------|----------------|

|---|-----------|----------------|

| 4.6.1.4  | Cleaning Heads in Machine           | 4-9  |

|----------|-------------------------------------|------|

| 4.6.1.5  | Cleaning Heads Out of Machine       | 4-10 |

| 4.6.2    | Head Replacement                    | 4-11 |

| 4.6.2.1  | Tools Required                      | 4-11 |

| 4.6.2.2  | Removing a Head                     | 4-11 |

| 4.6.2.3  | Installing a Head                   | 4-12 |

| 4.6.3    | Head Adjustment                     | 4-13 |

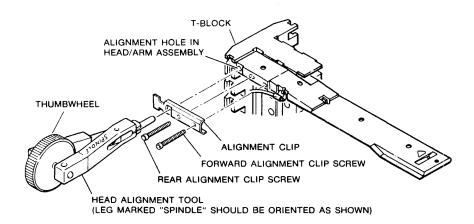

| 4.6.3.1  | Tools Required                      | 4-13 |

| 4.6.3.2  | Checking Alignment                  | 4-13 |

| 4.6.3.3  | Adjusting Alignment                 | 4-14 |

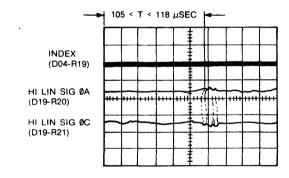

| 4.6.3.4  | Circumferential Alignment           | 4-16 |

| 4.6.4    | Filtration and Cooling Components   | 4-16 |

| 4.6.4.1  | Replacing Absolute Filter           | 4-17 |

| 4.6.4.2  | Replacing Logic Fan                 | 4-17 |

| 4.6.4.3  | Replacing Baffle                    | 4-17 |

| 4.6.4.4  | Replacing Upspeed Switch            | 4-18 |

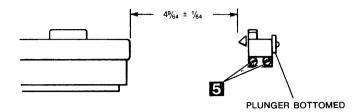

| 4.6.4.5  | Adjusting Upspeed Switch            | 4-18 |

| 4.6.5    | Shroud and Pack Access Door         | 4-18 |

| 4.6.5.1  | Replacing Pack Access Door          | 4-18 |

| 4.6.5.2  | Replacing Shroud                    | 4-18 |

| 4.6.6    | Drive Mechanism                     | 4-18 |

| 4.6.6.1  | Tools Required                      | 4-18 |

| 4.6.6.2  | Replacing Drive Motor               | 4-19 |

| 4.6.6.3  | Adjusting Drive Belt Tension        | 4-19 |

| 4.6.6.4  | Replacing Drive Belt                | 4-19 |

| 4.6.6.5  | Replacing Spindle Lock Shaft        | 4-20 |

| 4.6.6.6  | Replacing Spindle                   | 4-20 |

| 4.6.6.7  | Adjusting Pack Cover Sensor         | 4-21 |

| 4.6.6.8  | Adjusting Spindle Lock              | 4-21 |

| 4.6.7    | Actuator Mechanism                  | 4-22 |

| 4.6.7.1  | Tools Required                      | 4-22 |

| 4.6.7.2  | Replacing Linear Motor              | 4-22 |

| 4.6.7.3  | Aligning Linear Motor               | 4-23 |

| 4.6.7.4  | Replacing Bobbin                    | 4-24 |

| 4.6.7.5  | Replacing Heads Retracted Switch    | 4-24 |

| 4.6.7.6  | Replacing Carriage T-Block Assembly | 4-24 |

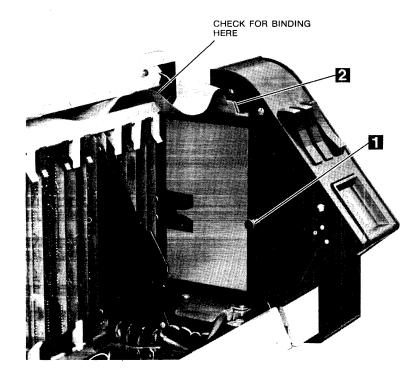

| 4.6.7.7  | Adjusting Carriage Tilt Limit       | 4-25 |

| 4.6.7.8  | Replacing Carriage Way              | 4-25 |

| 4.6.7.9  | Cleaning Carriage Way               | 4-26 |

| 4.6.7.10 | Adjusting Carriage Way              | 4-26 |

| 4.6.7.11 | Replacing Cams                      | 4-28 |

| 4.6.7.12 | Replacing Cam Tower                 | 4-28 |

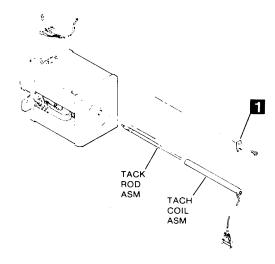

| 4.6.7.13 | Replacing Tachometer Rod            | 4-29 |

| 4.6.7.14 | Replacing Tachometer                | 4-29 |

| 4.6.7.15 | Adjusting Tachometer Gain           | 4-29 |

| 4.6.8    | Miscellaneous Electrical Assemblies | 4-30 |

| 4.6.8.1  | Replacing Operator Control Panel    | 4-30 |

|    | Section   |         |                                          | Page  |

|----|-----------|---------|------------------------------------------|-------|

|    | 4         | MAINTE  | NANCE (Continued)                        |       |

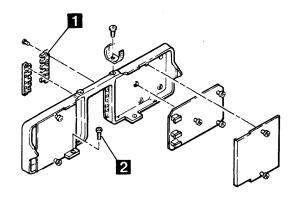

|    |           | 4.6.8.2 | Replacing Lamp Matrix PCB                | 4-30  |

|    |           | 4.6.8.3 | Replacing Logic Assembly Motherboard PCB | 4-30  |

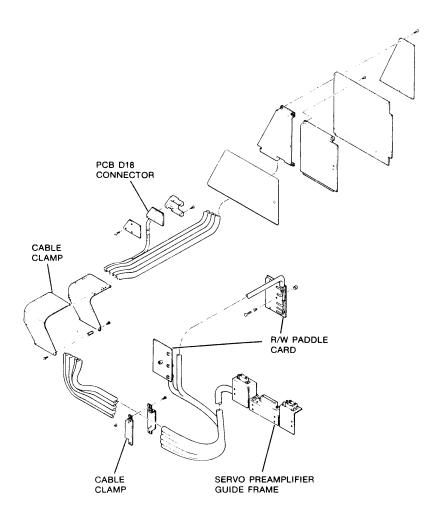

|    |           | 4.6.8.4 | Replacing Read/Write Preamplifier        | 4-31  |

|    |           | 4.6.8.5 | Replacing Servo Power Amplifier          | 4-31  |

|    |           | 4.6.8.6 | Replacing Servo Preamplifier             | 4-31  |

|    |           | 4.6.8.7 | Replacing Read/Write Preamplifier Cable  | 4-31  |

|    |           | 4.6.9   | Power Conversion                         | 4-33  |

|    |           | 4.6.9.1 | 50 Hz to 60 Hz Conversion                | 4-33  |

|    |           | 4.6.9.2 | 60 Hz to 50 Hz Conversion                | 4-33  |

| AF | PPENDIX A | TROUBL  | ESHOOTING AIDS                           | . A-1 |

# LIST OF ILLUSTRATIONS

| Figure       |                                           | Page |

|--------------|-------------------------------------------|------|

| 1-1          | MEMOREX 677-01/51 DEC DISC STORAGE DRIVE  | 1-2  |

| 1-2          | EXAMPLE OF A DATA PROCESSING SYSTEM       | 1-5  |

| 1-3          | MEMOREX 800 DISC STORAGE SUBSYSTEM TESTER |      |

| 1-4          | TYPICAL DRIVE EXTERNAL CABLING            | 1-7  |

| 1-5          | MEMOREX MARK X OR MARK XI DISC PACK       | 1-9  |

| 1-6          | DRIVE FRONT VIEW                          | 1-10 |

| 1-7          | DRIVE REAR VIEW                           |      |

| 1-8          | DECK PLATE                                |      |

| 1-9          | POWER DISTRIBUTION UNIT                   |      |

| 1-10         | POWER SUPPLY                              |      |

| 1-11         | SERVO DATA FORMAT                         |      |

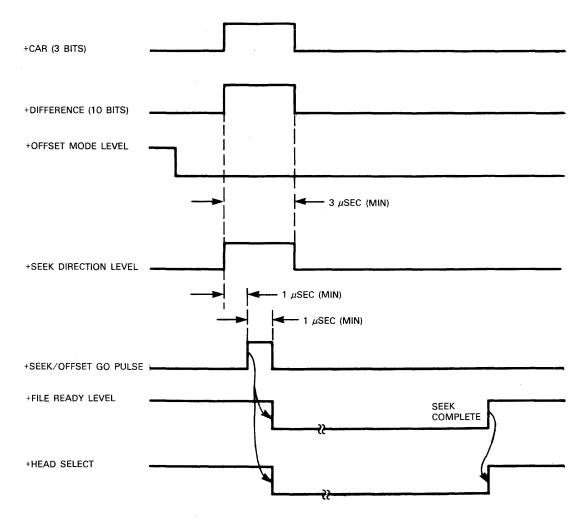

| 1-12         | SEEK TIMING                               |      |

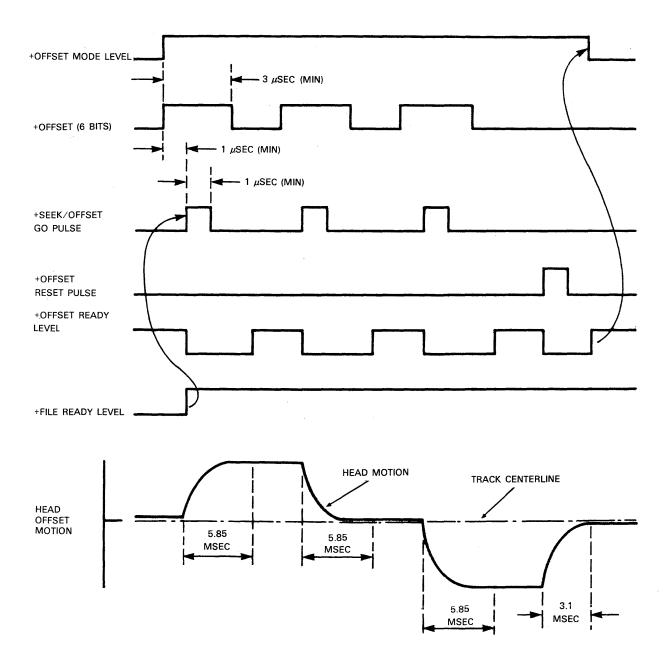

| 1-13         | OFFSET TIMING                             |      |

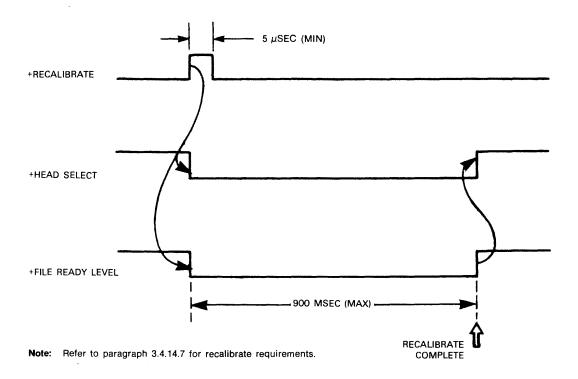

| 1-14         | RECALIBRATE TIMING                        |      |

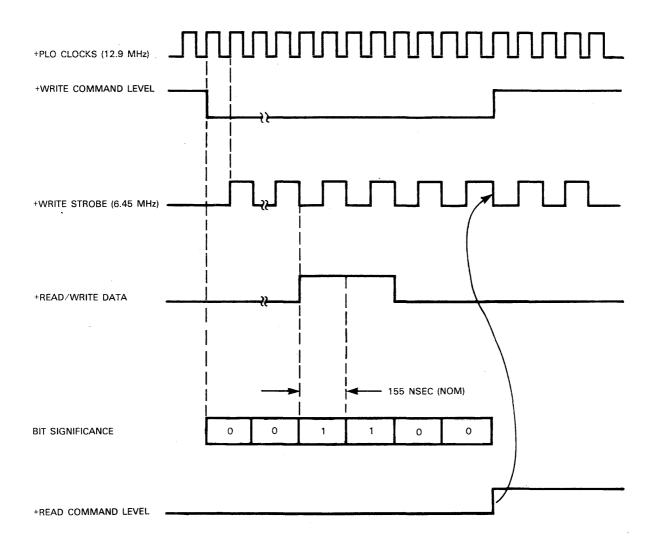

| . 1-15       | WRITE DATA TIMING                         |      |

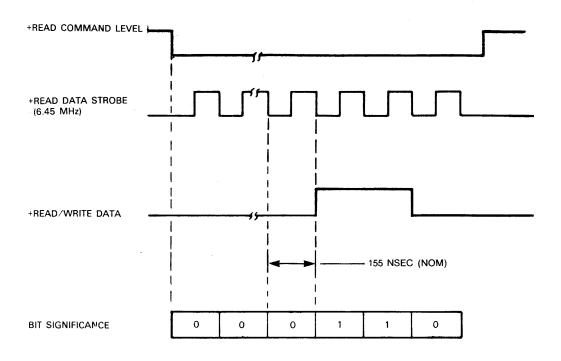

| 1-16         | READ DATA TIMING                          |      |

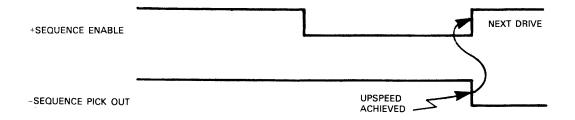

| 1-17         | POWER SEQUENCE TIMING                     |      |

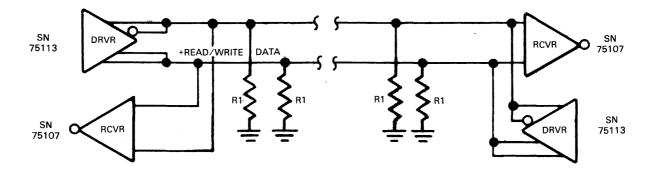

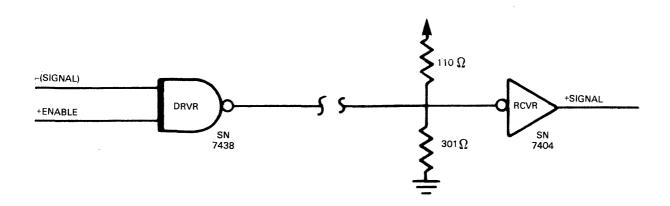

| 1-18         | DIFFERENTIAL LINE DRIVERS AND RECEIVERS   |      |

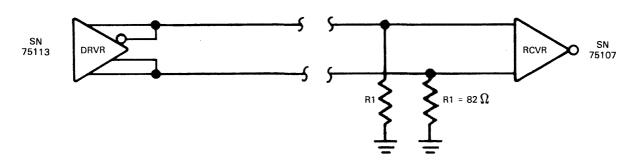

| 1-19<br>1-20 | SINGLE ENDED LINE DRIVERS AND RECEIVERS   |      |

| 1-20         | AC POWER DISTRIBUTION                     |      |

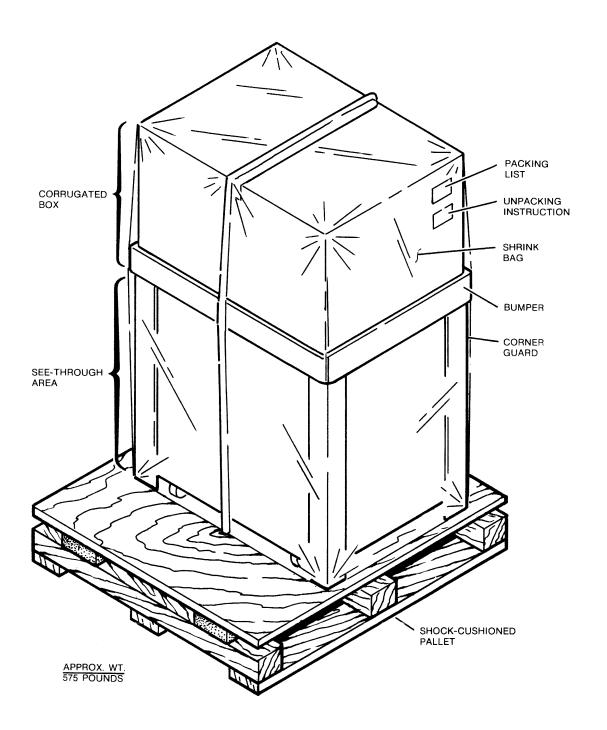

| 2-1          | SHIPPING CONTAINER                        |      |

| 2-1          | SHIPPING CONTAINER DESIGN                 |      |

| 2-2          | SHIPPING BRACKETS                         |      |

| 2-3          | ABSOLUTE FILTER AND PACK LOCKING ROD      |      |

| 2-5          | SHIPPING SPACERS AND SUPPORT BAR          |      |

| 2-6          | LINEAR MOTOR SHIPPING BLOCK               |      |

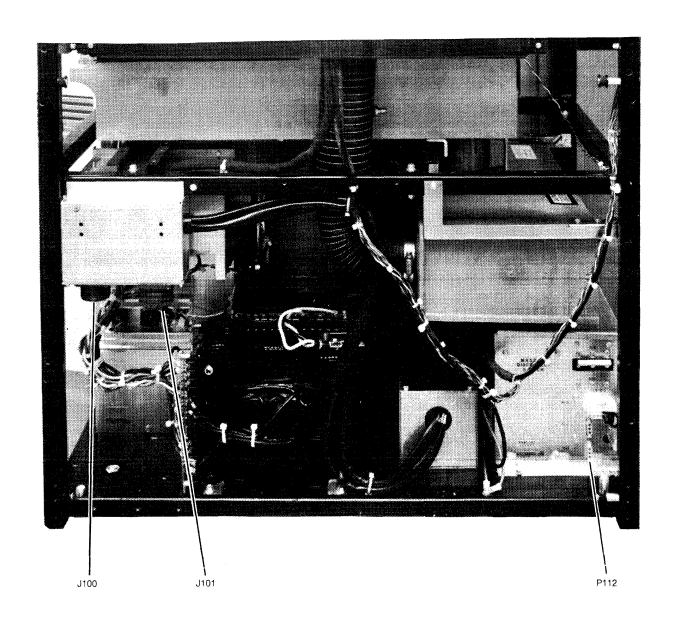

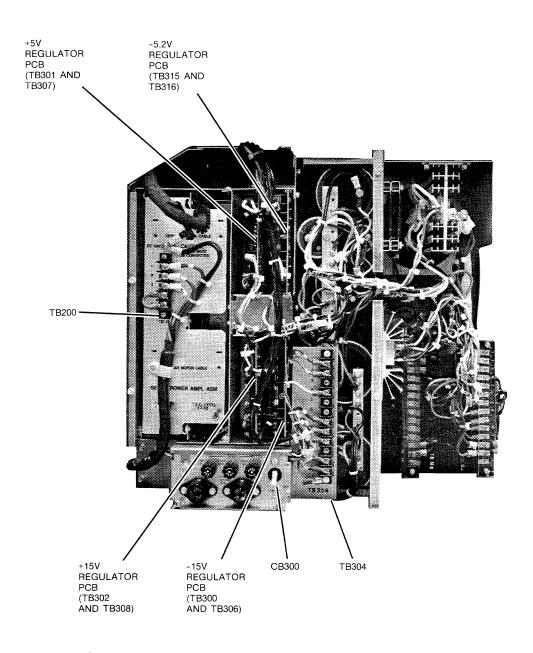

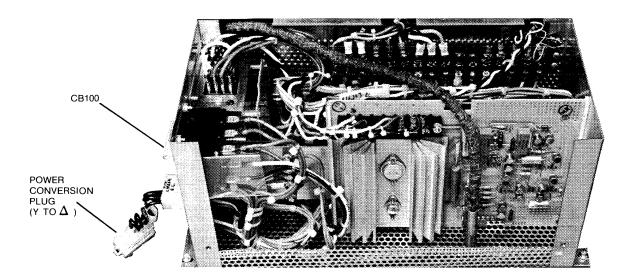

| 2-7          | REAR VIEW, POWER SUPPLY COVER OFF         |      |

| 2-8          | FRONT VIEW, PDU COVER OFF                 |      |

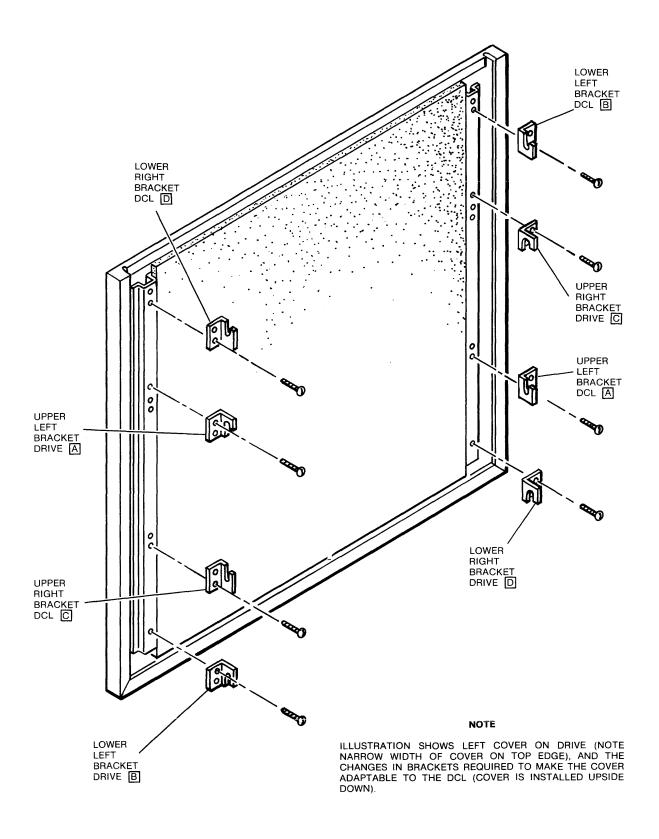

| 2-9          | CONVERTING DRIVE COVER TO DCL COVER       |      |

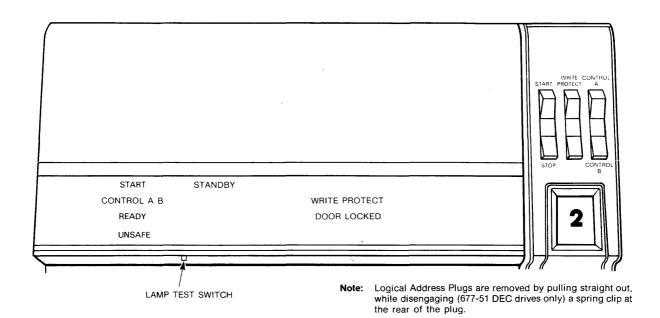

| 2-10         | OPERATOR PANEL                            |      |

| 2-11         | MARK X OR XI DISC PACK                    |      |

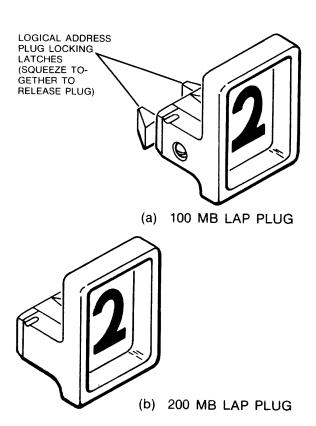

| 2-12         | LOGICAL ADDRESS PLUG                      |      |

| 2-13         | DOOR LOCK OVERRIDE MECHANISM              |      |

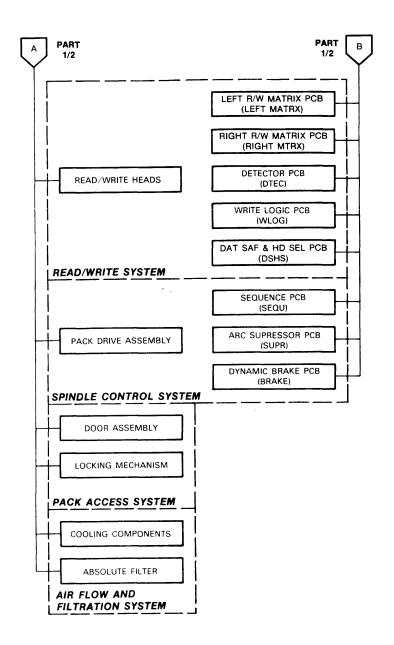

| 3-1          | BREAKDOWN INTO SYSTEMS (2 parts)          |      |

| 3-2          | OPERATOR CONTROL AND LAMP MATRIX PCBs     |      |

| 3-3          | INPUT PCB                                 | 3-9  |

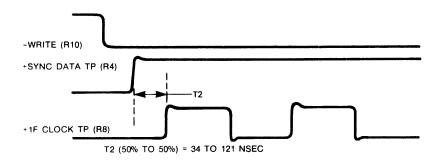

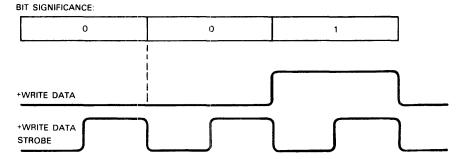

| 3-4          | WRITE DATA TIMING                         |      |

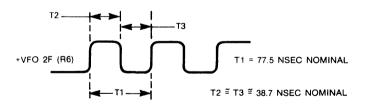

| 3-5          | 2F PULSE TIMING                           |      |

| 3-6          | 1F CLOCK TIMING                           |      |

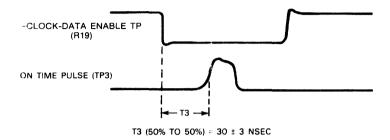

| 3-7          | PRECOMPENSATION PCB                       |      |

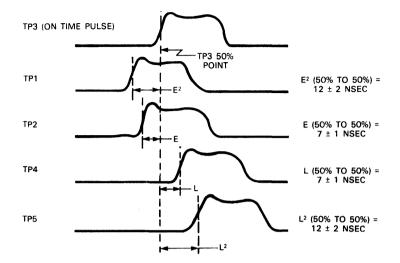

| 3-8          | ON TIME PULSE TIMING                      |      |

| 3-9          | DELAY LINE TIMING                         |      |

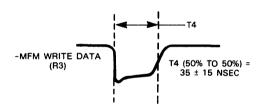

| 3-10         | MFM WRITE DATA TIMING                     |      |

| 3-11         | PLO CLOCKS TIMING                         | 3-14 |

| Figure |                                                  | Page |

|--------|--------------------------------------------------|------|

| 3-12   | CHANGING STATES OF WRITE DATA                    | 3-15 |

| 3-13   | VARIABLE FREQUENCY OSCILLATOR PCB                | 3-16 |

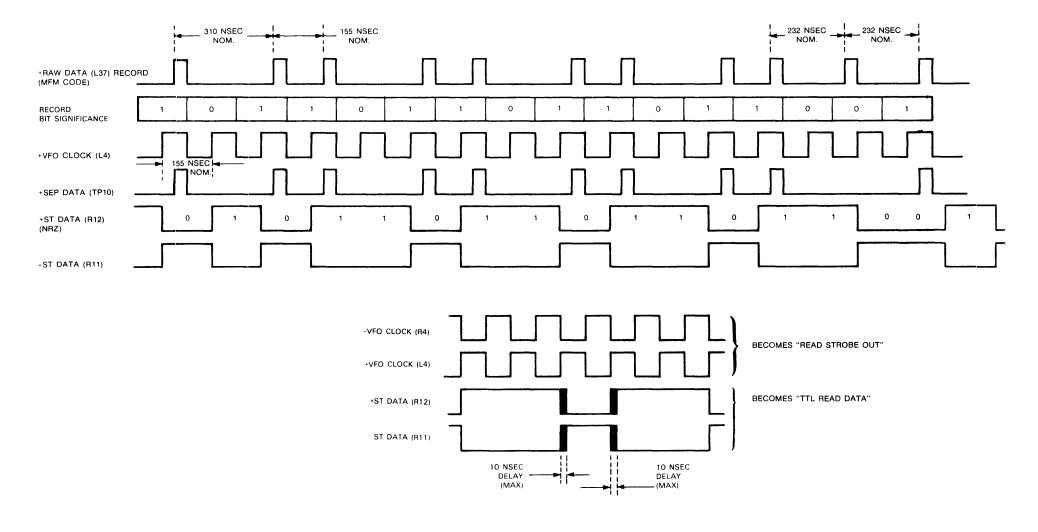

| 3-14   | DATA SEPARATOR RESPONSE                          | 3-17 |

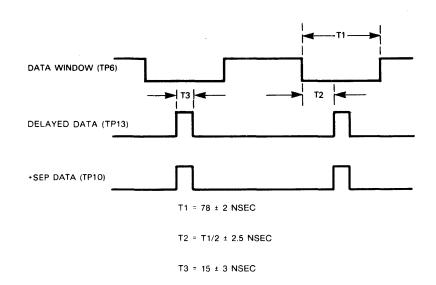

| 3-15   | VFO OUTPUTS                                      | 3-19 |

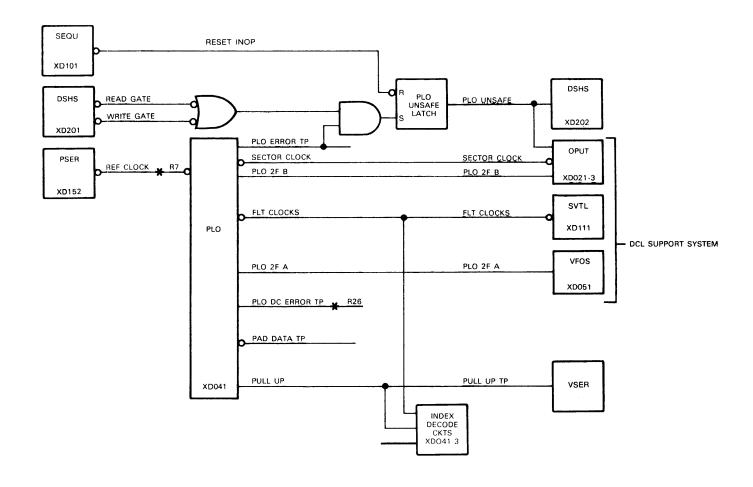

| 3-16   | PLO INPUTS AND OUTPUTS                           | 3-21 |

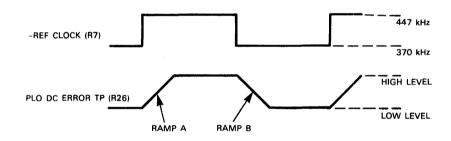

| 3-17   | PLO DC ERROR RESPONSE                            | 3-20 |

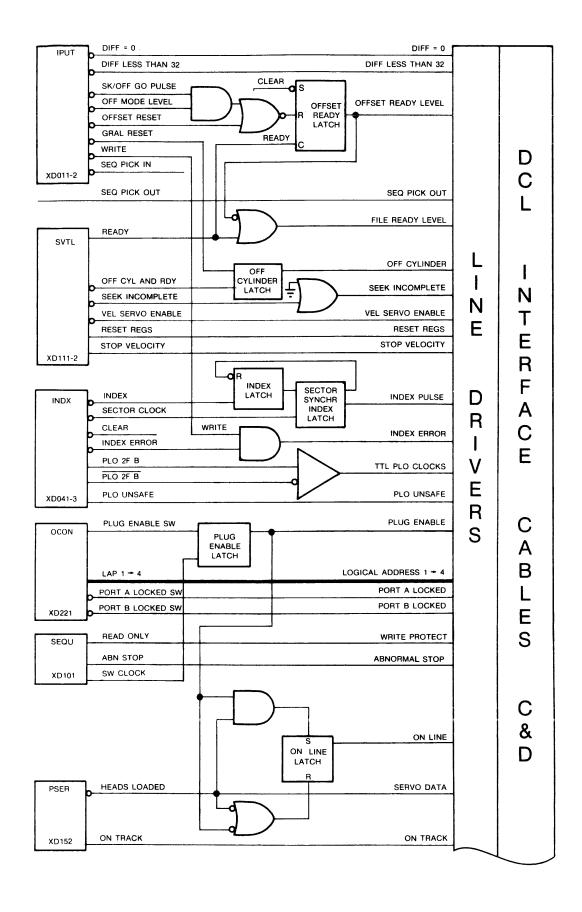

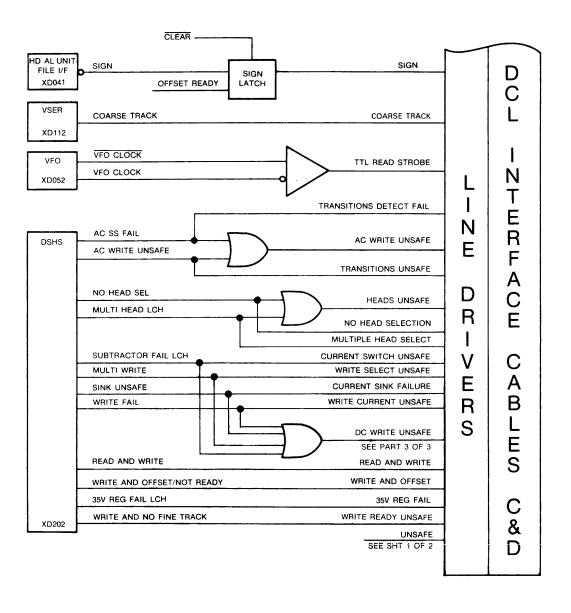

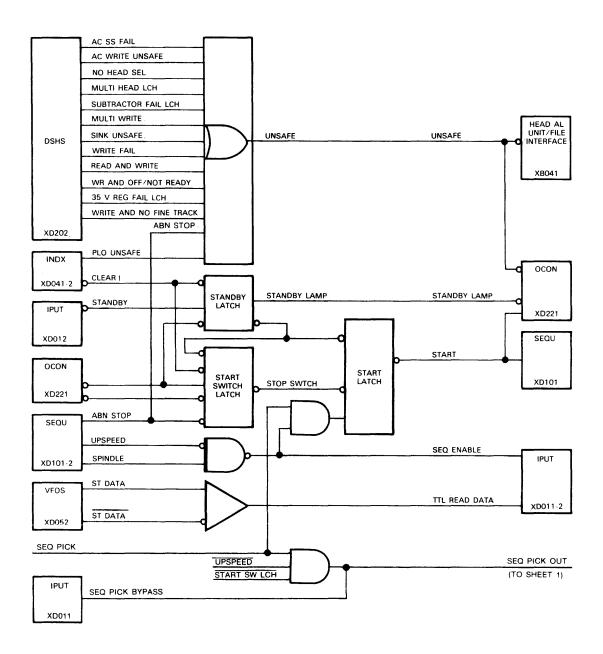

| 3-18   | OUTPUT PCB (3 parts)                             | 3-24 |

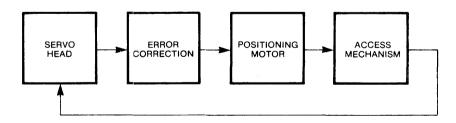

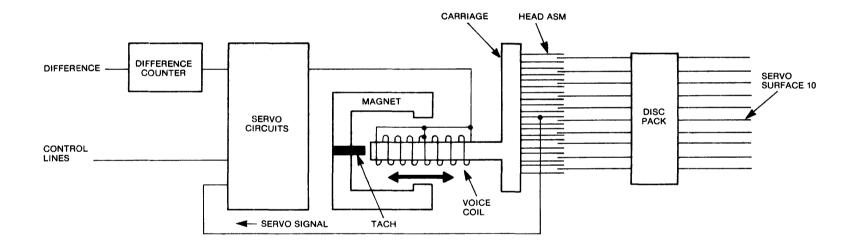

| 3-19   | CLOSED-LOOP SERVO SYSTEM PHILOSOPHY              |      |

| 3-20   | SERVO SYSTEM BASIC ELEMENTS                      |      |

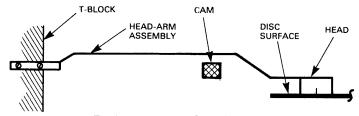

| 3-21   | LOADED HEADS                                     |      |

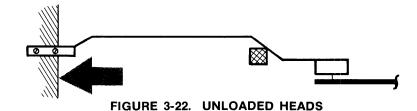

| 3-22   | UNLOADED HEADS                                   |      |

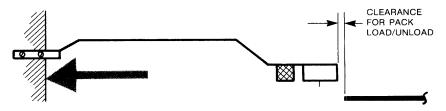

| 3-23   | RETRACTED HEADS                                  |      |

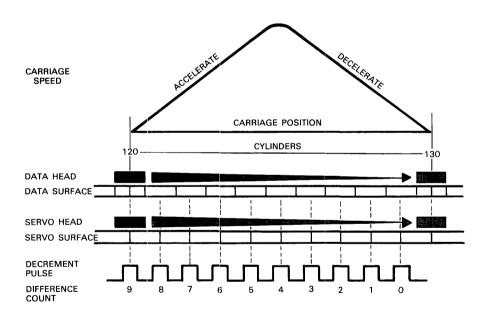

| 3-24   | SIMPLIFIED SEEK OPERATION                        |      |

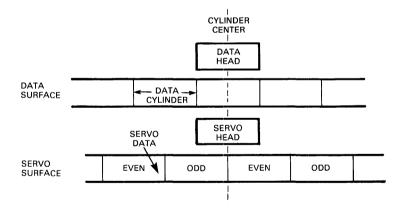

| 3-25   | DEFINITION OF CYLINDER CENTER                    |      |

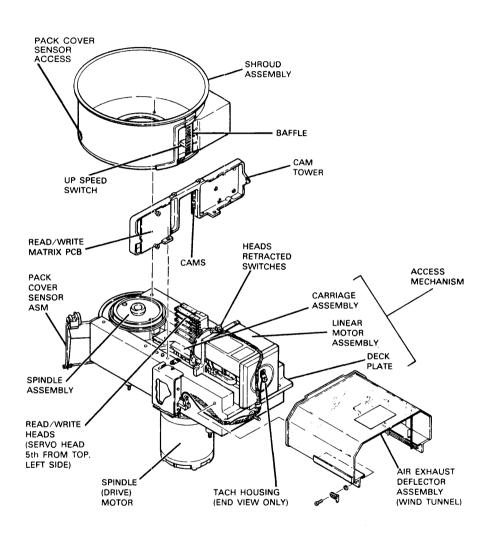

| 3-26   | MAJOR COMPONENTS OF DECK PLATE                   |      |

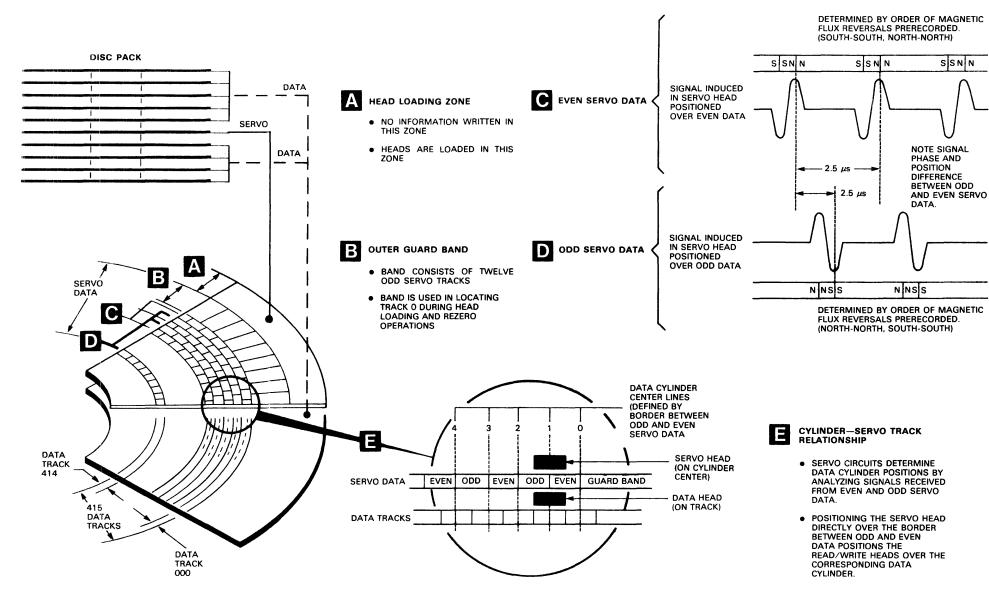

| 3-27   | SERVO SURFACE FORMAT                             |      |

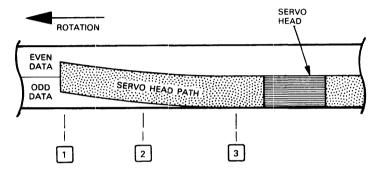

| 3-28   | EXAMPLE SERVO HEAD PATH                          |      |

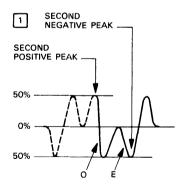

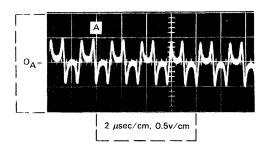

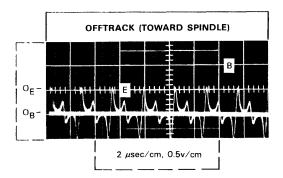

| 3-29   | SIGNAL FROM CENTERED SERVO HEAD                  |      |

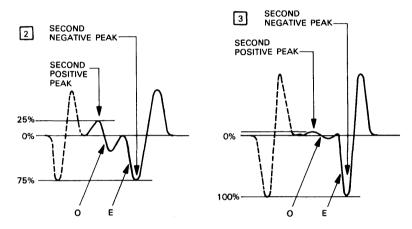

| 3-30   | SIGNAL FROM OFFSET SERVO HEAD                    |      |

| 3-31   | HEAD POSITION ERROR CORRECTION                   |      |

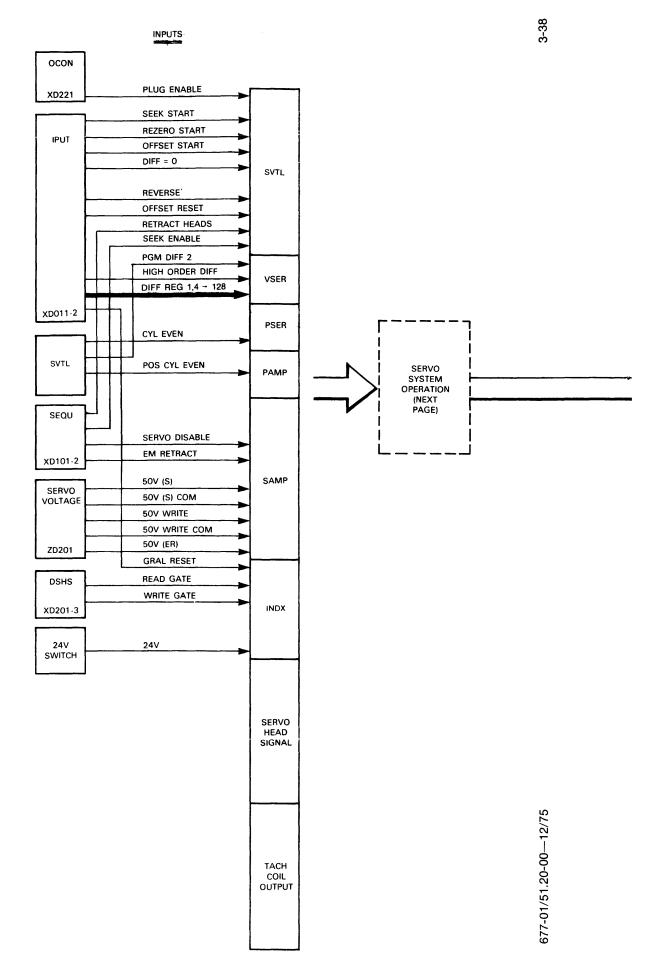

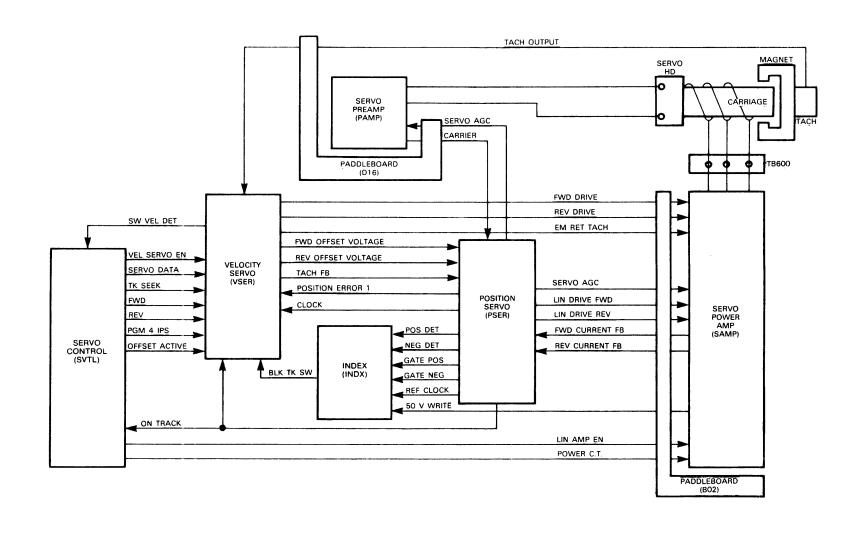

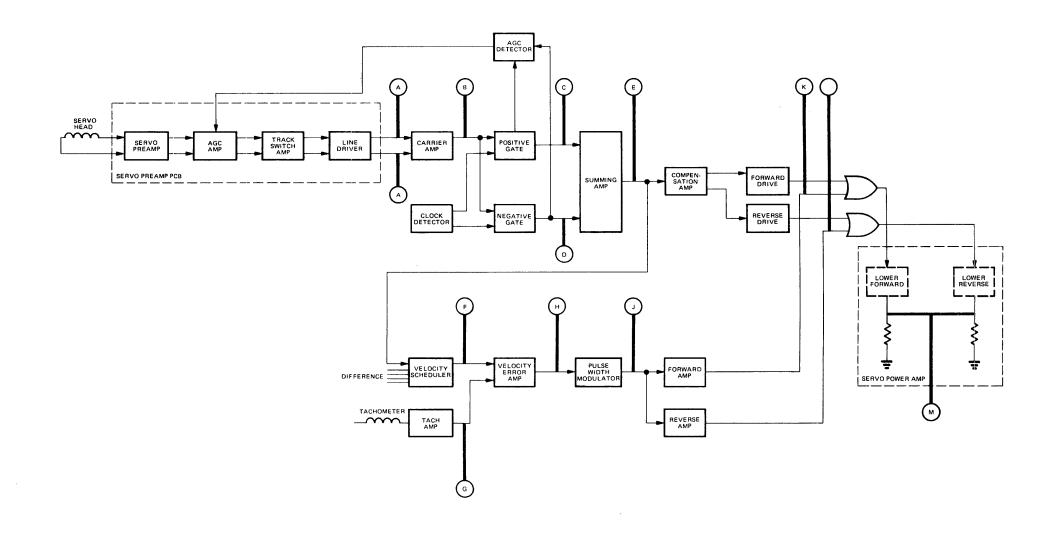

| 3-32   | SERVO SYSTEM INPUTS AND OUTPUTS (2 parts)        |      |

| 3-33   | SERVO SYSTEM INTERNAL OPERATION                  |      |

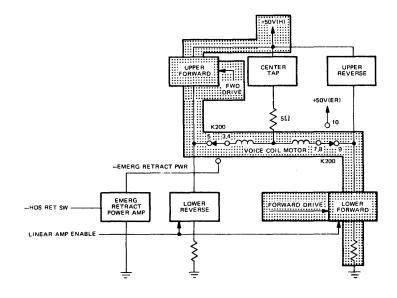

| 3-34   | SERVO POWER AMP PCB, NORMAL OPERATION            |      |

| 3-35   | POWER AMP IN POSITION CONTROL MODE               |      |

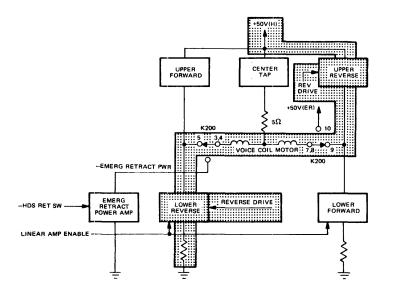

| 3-36   | POWER AMP IN VELOCITY CONTROL MODE, FORWARD      |      |

| 3-37   | POWER AMP IN VELOCITY CONTROL MODE, REVERSE      |      |

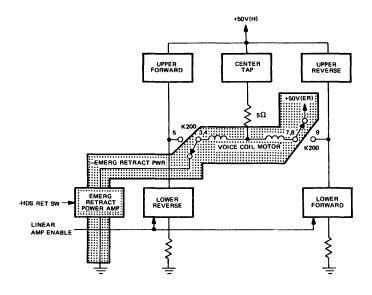

| 3-38   | POWER AMP IN EMERGENCY RETRACT MODE              | 3-43 |

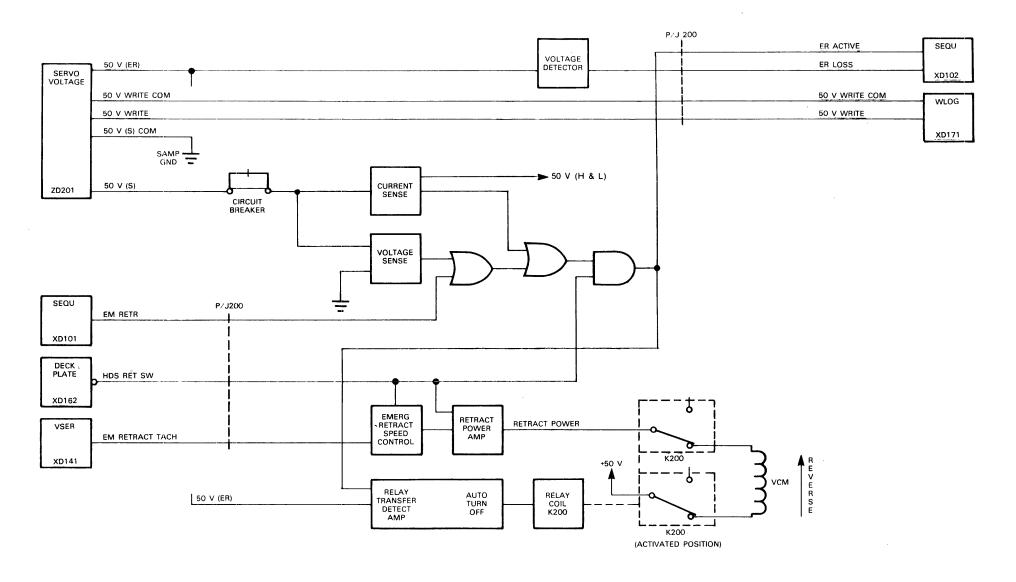

| 3-39   | SERVO POWER AMP PCB, EMERGENCY RETRACT OPERATION | 0 45 |

| 3-40   | SERVO PREAMP PCB AND POSITION SERVO PCB          |      |

| 3-40   | INDEX PATTERN                                    |      |

| 3-42   | VELOCITY SERVO PCB                               |      |

| 3-42   | SCHEDULING SEEK VELOCITY                         |      |

| 3-44   | PULSE WIDTH MODULATION                           |      |

| 3-45   | SERVO CLOCKING FOR INDEX                         |      |

| 3-46   | INDEX PCB                                        |      |

| 3-47   | SVTL FUNCTIONS, INPUT SIGNALS USED,              | 0 00 |

| 0 11   | AND OUTPUTS GENERATED                            | 3-55 |

| 3-48   | SVTL ONE SHOTS                                   |      |

| 3-49   | SERVO LOGIC ENABLE AND DO REZERO                 | 3-57 |

| 3-50   | VELOCITY ENABLE AND STOP VELOCITY                |      |

| 3-51   | AMP ENABLE, READY DELAY, ALLOW READY, AND READY  | 3-59 |

| 3-52   | TRACK SEEK AND SEEK INCOMPLETE                   | 3-60 |

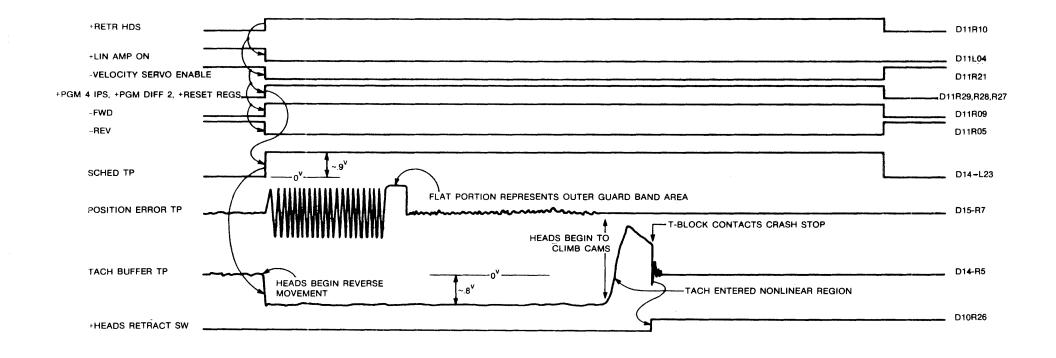

| 3-53   | 677 SERVO TIMING DIAGRAM, HEAD LOAD              |      |

| 3-54   | 677 SERVO TIMING DIAGRAM, 18 CYLINDER FORWARD    | 3-62 |

| 3-55   | 677 SERVO TIMING DIAGRAM, REZERO FROM TRACK 53   | 3-63 |

| 3-56   | 677 SERVO TIMING DIAGRAM, RETRACT FROM TRACK 42  |      |

| 3-57   | SERVO SYSTEM TEST POINTS                         |      |

| 3-58   | SERVO SYSTEM WAVEFORMS (6 parts)                 |      |

| 3-59   | HEAD DETAILS                                     |      |

| Figure |                                               | Page  |

|--------|-----------------------------------------------|-------|

| 3-60   | SIMPLIFIED WRITE OPERATION                    | 3-73  |

| 3-61   | SIMPLIFIED READ OPERATION                     | 3-74  |

| 3-62   | READ/WRITE SYSTEM                             |       |

| 3-63   | DATA SAFETY AND HEAD SELECT PCB (2 parts)     | 3-77  |

| 3-64   | RIGHT READ/WRITE MATRIX PCB                   |       |

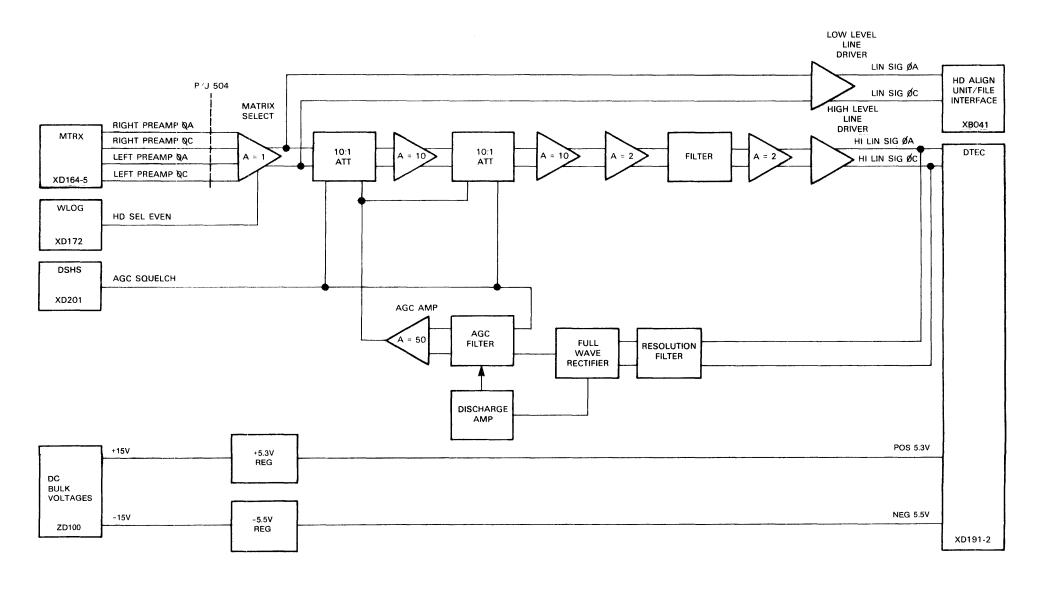

| 3-65   | LINEAR AMP PCB                                |       |

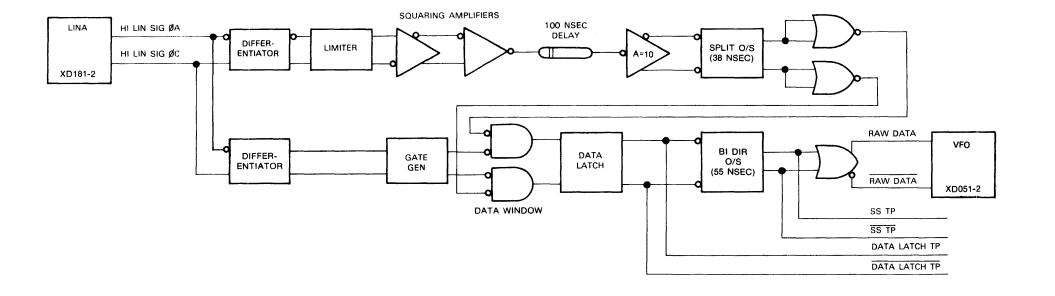

| 3-66   | DETECTOR PCB                                  |       |

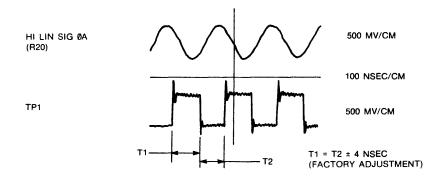

| 3-67   | DIFFERENTIATOR SYMMETRY                       |       |

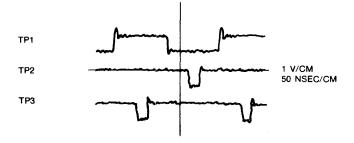

| 3-68   | SPLIT ONE SHOT                                |       |

| 3-69   | GATE GENERATOR                                |       |

| 3-70   | BIDIRECTIONAL ONE SHOT, DATA LATCH            |       |

| 3-71   | BIDIRECTIONAL ONE SHOT                        |       |

| 3-72   | WRITE LOGIC PCB                               |       |

| 3-73   | WRITE OPERATION FLOWCHART AND TIMING          |       |

| 3-74   | READ OPERATION FLOWCHART AND TIMING           |       |

| 3-75   | PACK DRIVE ASSEMBLY                           |       |

| 3-76   | SEQUENCE PCB (2 parts)                        |       |

| 3-77   | PACK ACCESS DOOR ASSEMBLY                     |       |

| 3-78   | OPERATION OF DOOR AIR SEAL                    |       |

| 3-79   | AIRFLOW AND FILTRATION SYSTEM                 |       |

| 3-80   | DC BULK VOLTAGES, VOLTAGE REGULATORS,         |       |

|        | AND SERVO VOLTAGES                            | 3-102 |

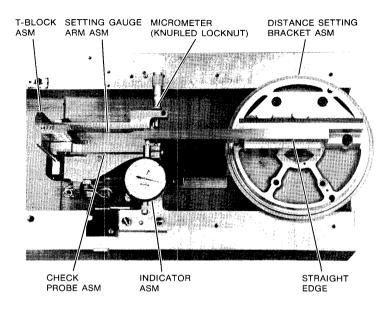

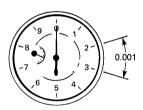

| 4-1    | SPECIAL TOOLS (2 parts)                       |       |

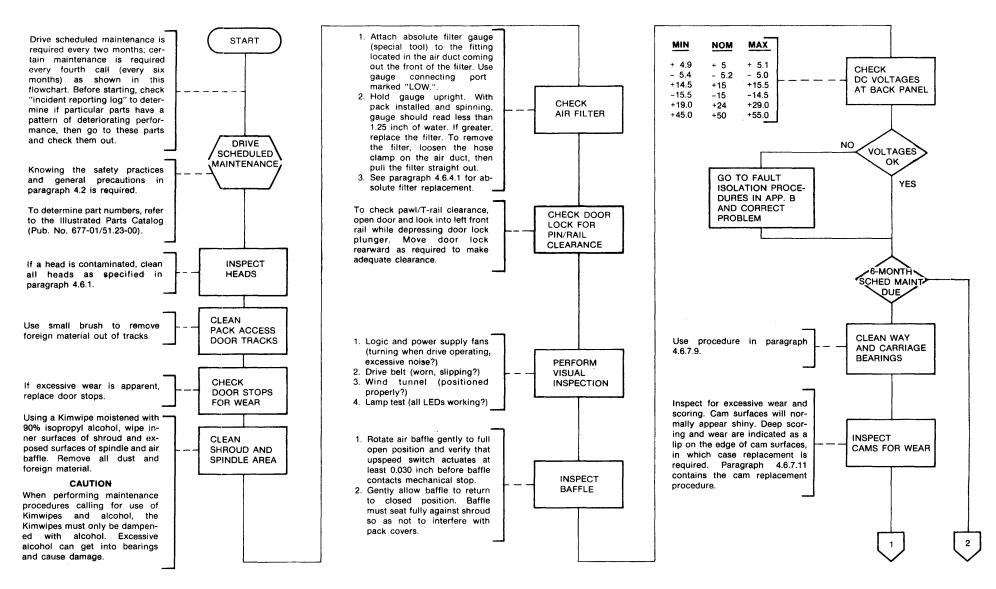

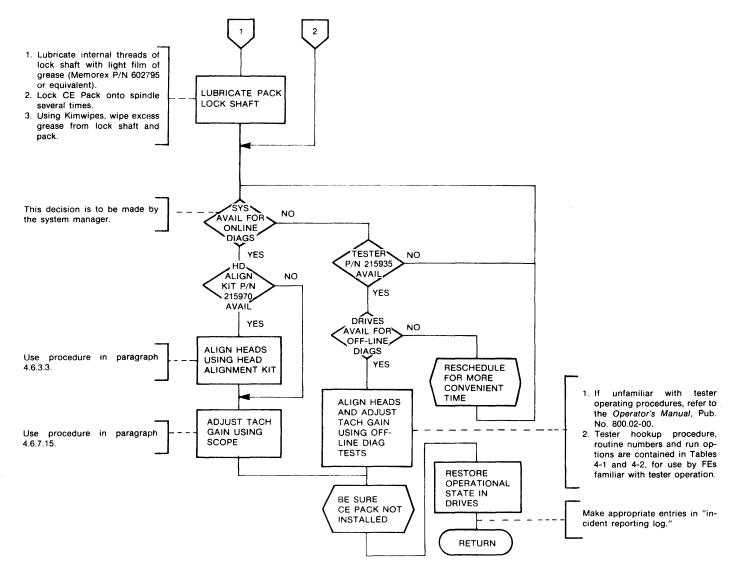

| 4-2    | SCHEDULED MAINTENANCE FLOWCHART (2 parts)     |       |

| 4-3    | CLEANING HEADS IN DRIVE                       |       |

| 4-4    | CLEANING HEADS OUT OF DRIVE                   |       |

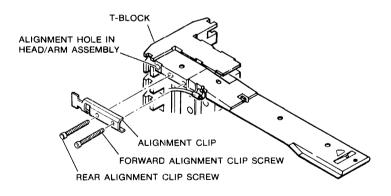

| 4-5    | HEAD ALIGNMENT CLIP AND SCREWS                |       |

| 4-6    | T-BLOCK, VIEWED FROM LINEAR MOTOR             |       |

| 4-7    | HEAD INSTALLATION TOOL IN 'A' TYPE HEAD       |       |

| 4-8    | HEAD INSTALLATION TOOL IN 'B' TYPE HEAD       |       |

| 4-9    | USING HEAD TORQUE TOOL                        |       |

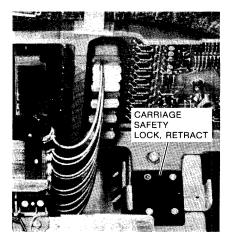

| 4-10   | CARRIAGE SAFETY LOCK                          |       |

| 4-11   | ORIENTATION OF ALIGNMENT TOOL TO HEAD         |       |

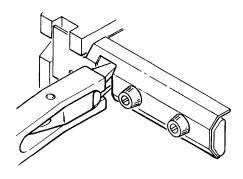

| 4-12   | ALIGNMENT TOOL IN HEAD                        |       |

| 4-13   | CIRCUMFERENTIAL ALIGNMENT TIMING              |       |

| 4-14   | AIRFLOW AND FILTRATION SYSTEM                 |       |

| 4-15   | RECOMMENDED DRIVE MOTOR REPLACEMENT TOOL      |       |

| 4-16   | DRIVE MECHANISM                               |       |

| 4-17   | ACTUATOR MCHANISM                             |       |

| 4-18   | BOBBIN AND LINEAR MOTOR                       |       |

| 4-19   | CARRIAGE T-BLOCK ASSEMBLY AND WAY             |       |

| 4-20   | WAY ADJUSTMENT TOOLS ON FULLY RETRACTED WAY . |       |

| 4-21   | WAY ADJUSTMENT TOOLS ON FULLY EXTENDED WAY    |       |

| 4-22   | RETAINING SCREWS, CAMS AND CAM TOWER          |       |

| 4-23   | TACH RETAINING SCREW AND CLIP                 |       |

| 4-24   | OPERATOR CONTROL PANEL, HALF WAY OUT          |       |

| 4-25   | R/W PREAMP CABLE ROUTING                      |       |

|        |                                               |       |

| Р                                         | age         |

|-------------------------------------------|-------------|

| APPENDIX A:                               |             |

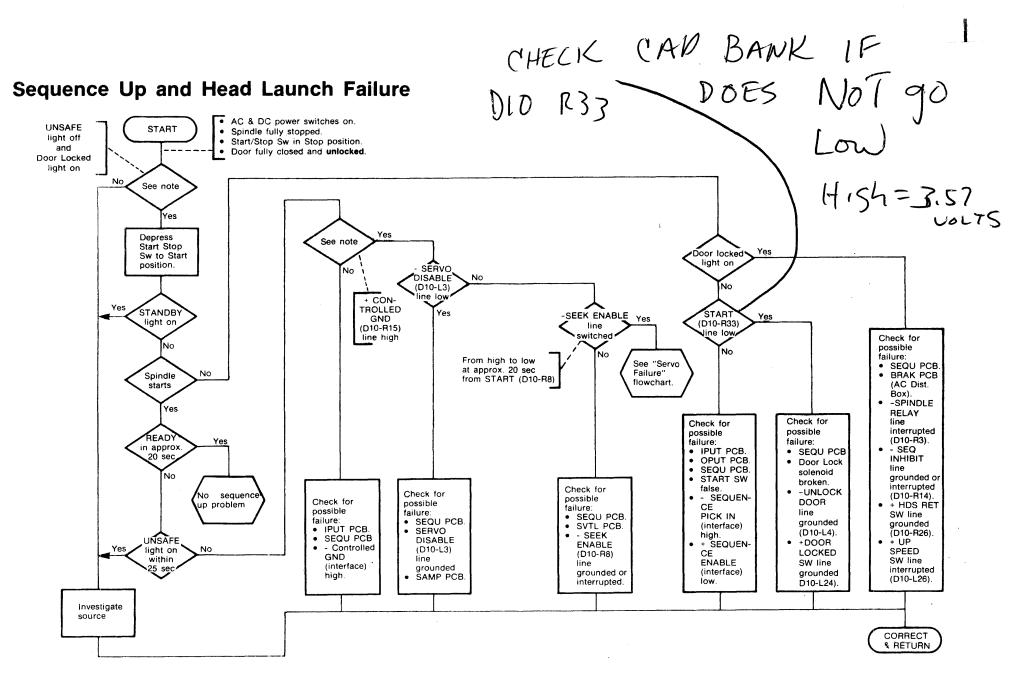

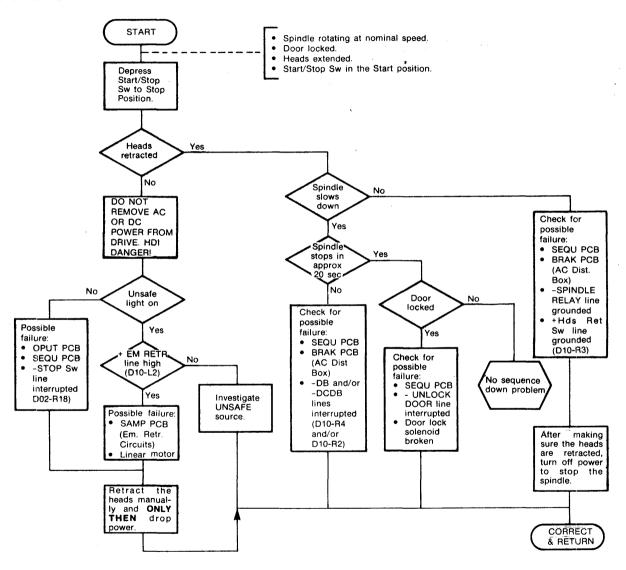

| SEQUENCE UP AND HEAD LAUNCH FAILURE       | <b>A-</b> 2 |

| SEQUENCE DOWN FAILURE                     | A-3         |

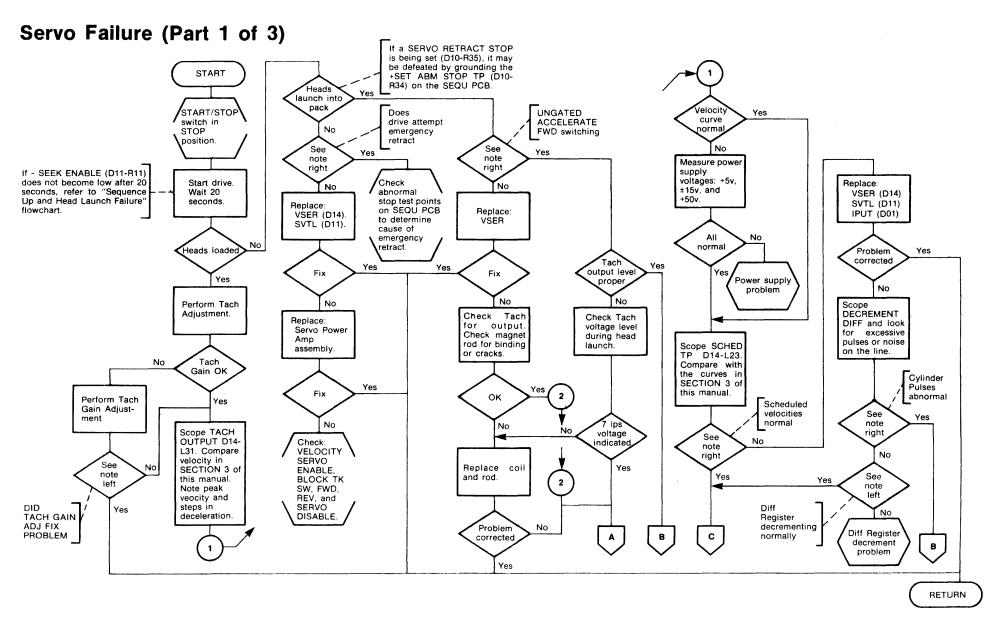

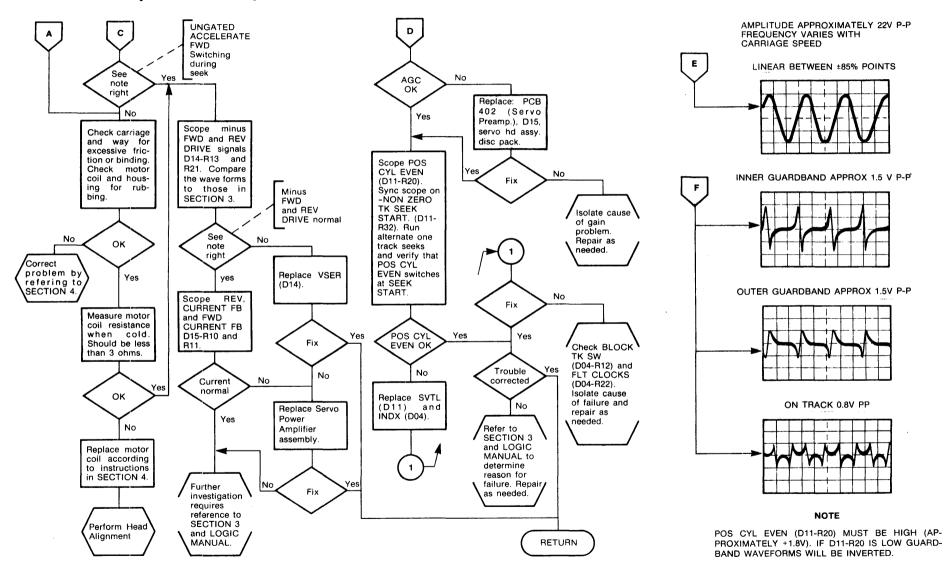

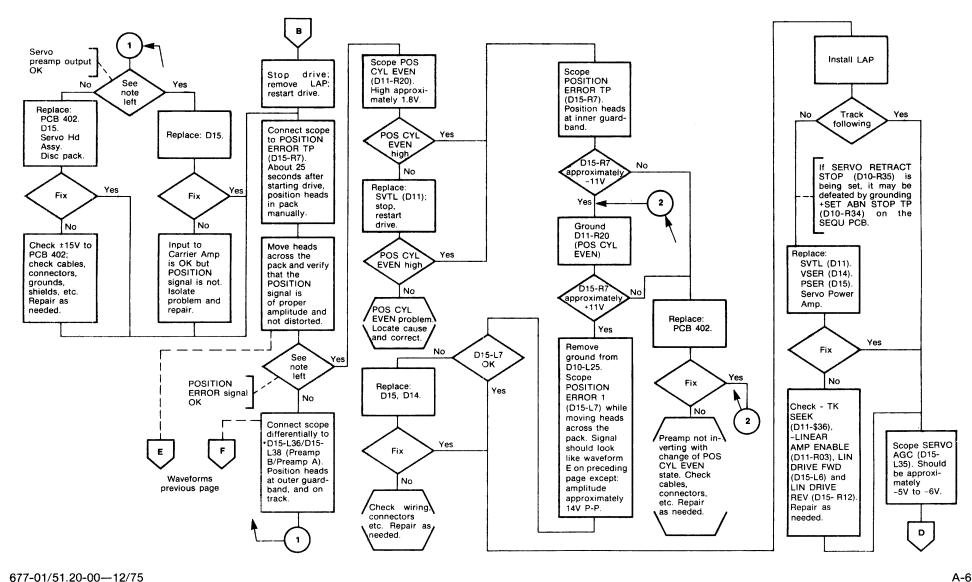

| SERVO FAILURE (3 parts)                   | A-4         |

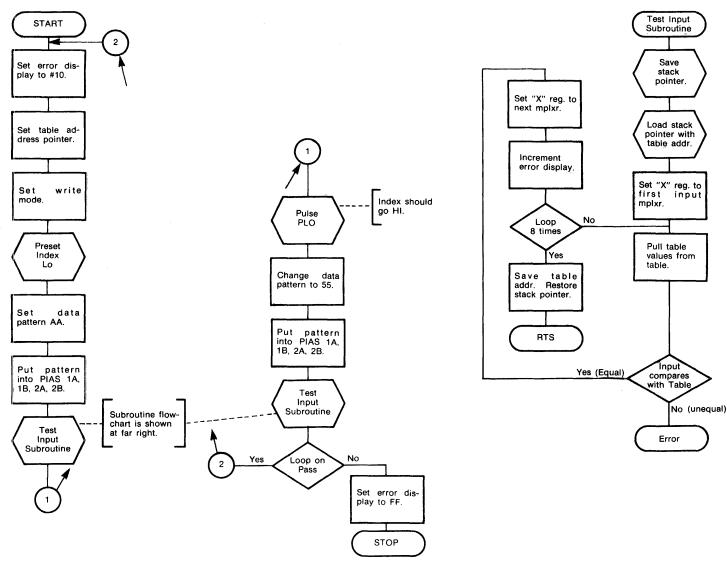

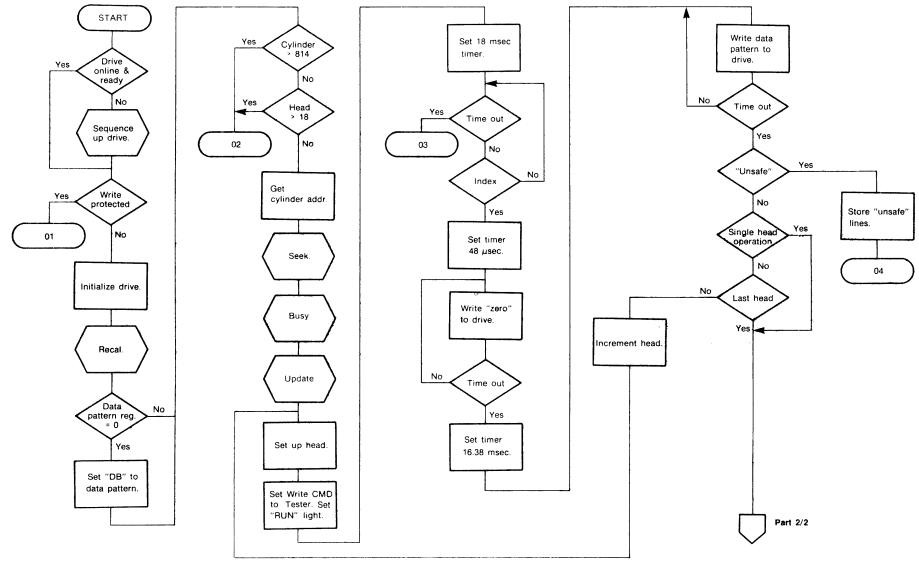

| WRAP TEST, ROUTINE 00 A                   |             |

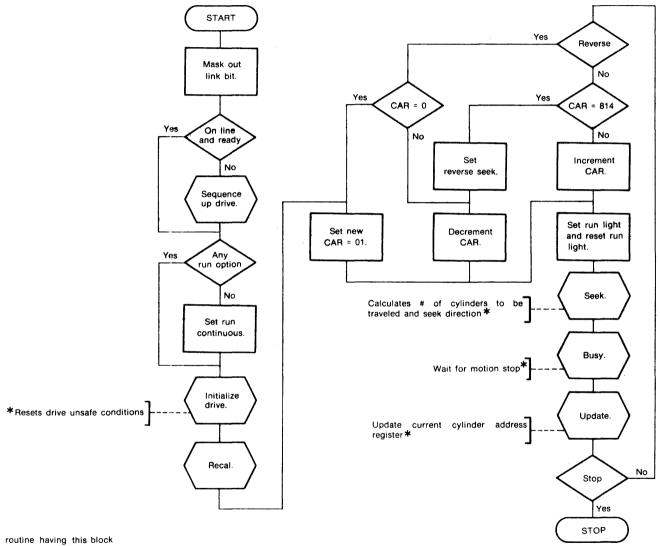

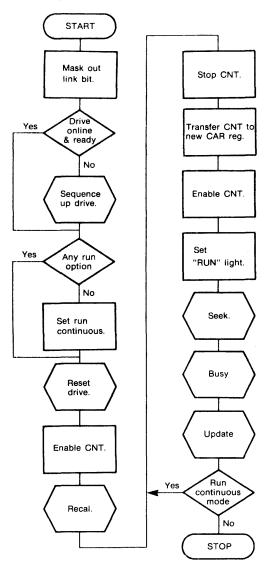

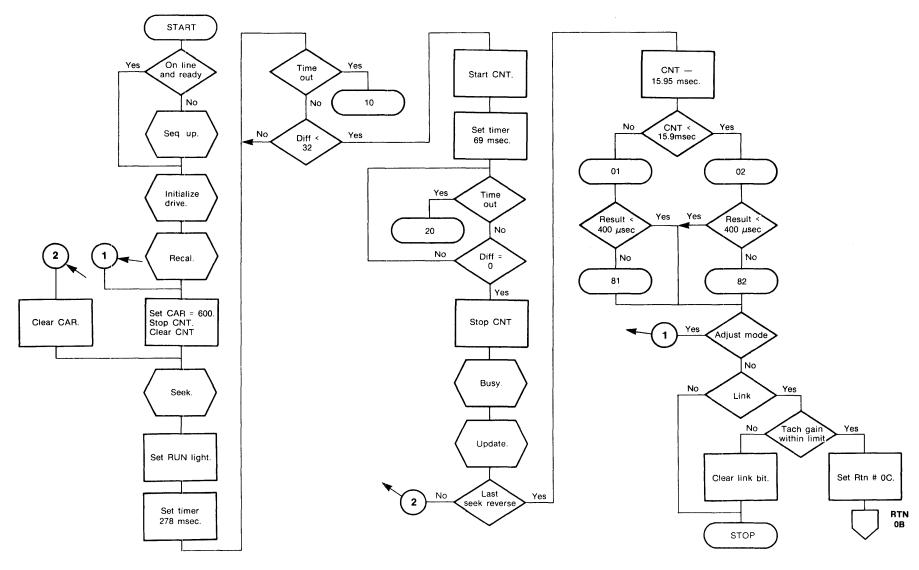

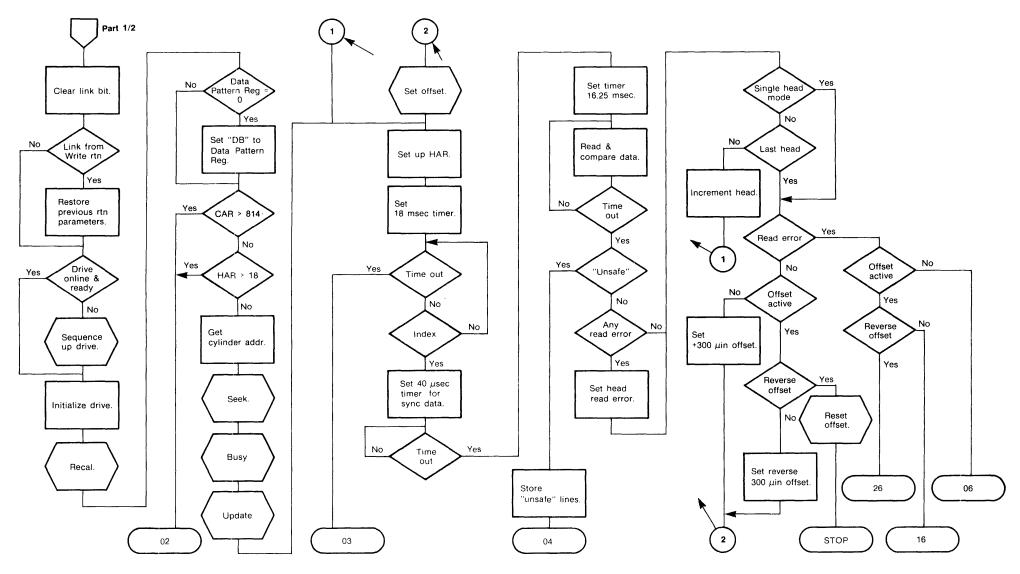

| INCREMENTAL SEEK, ROUTINE 01 A            | \-32        |

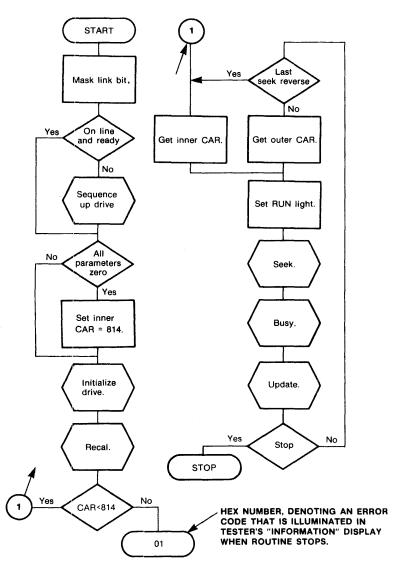

| ALTERNATE SEEK, ROUTINE 02 A              |             |

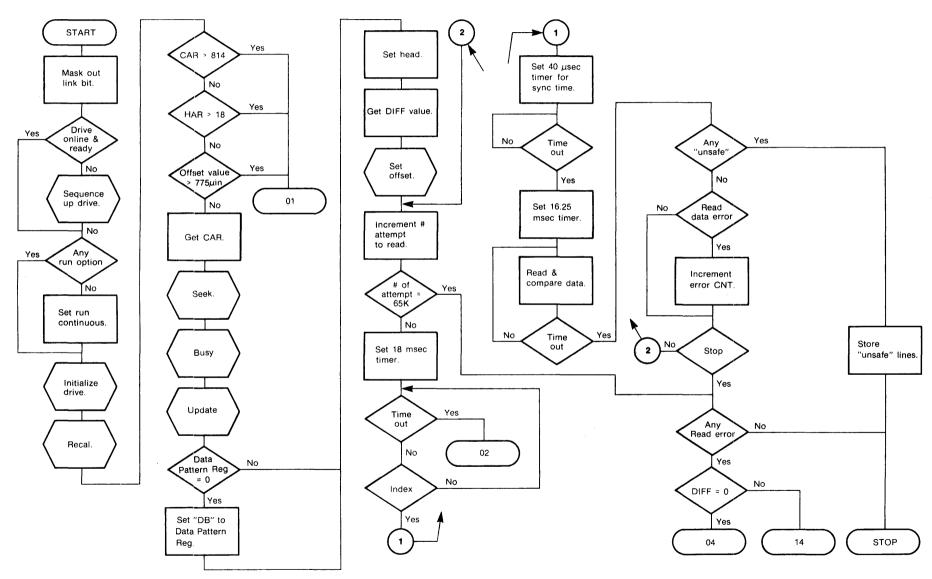

| RANDOM SEEK, ROUTINE 03 A                 |             |

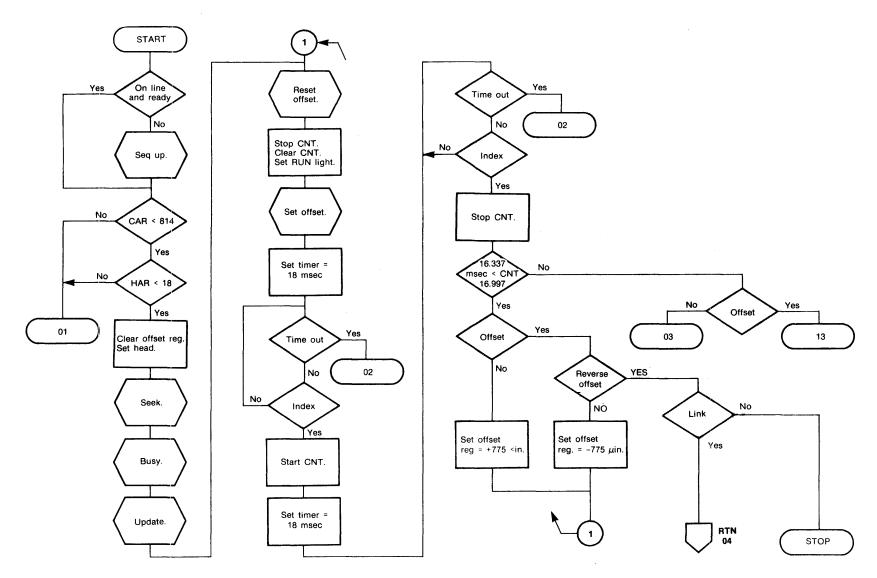

| TACHOMETER GAIN ADJUSTMENT, ROUTINE 04 A  |             |

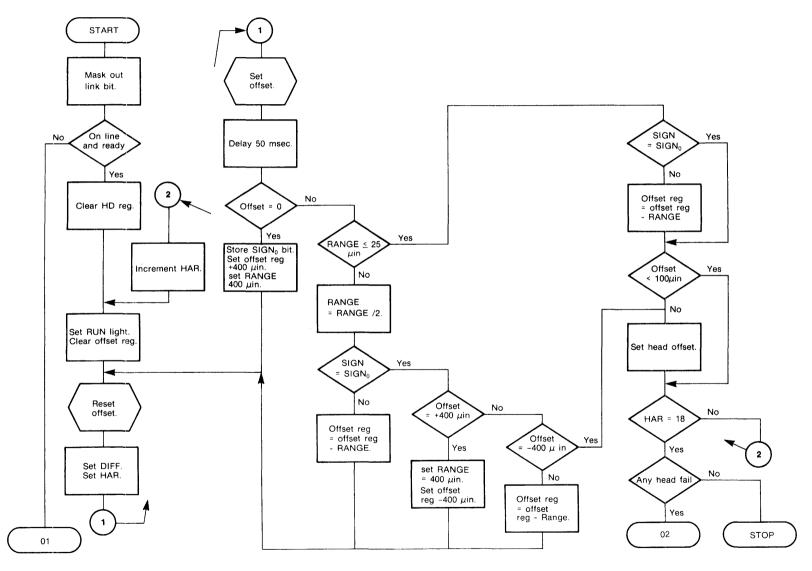

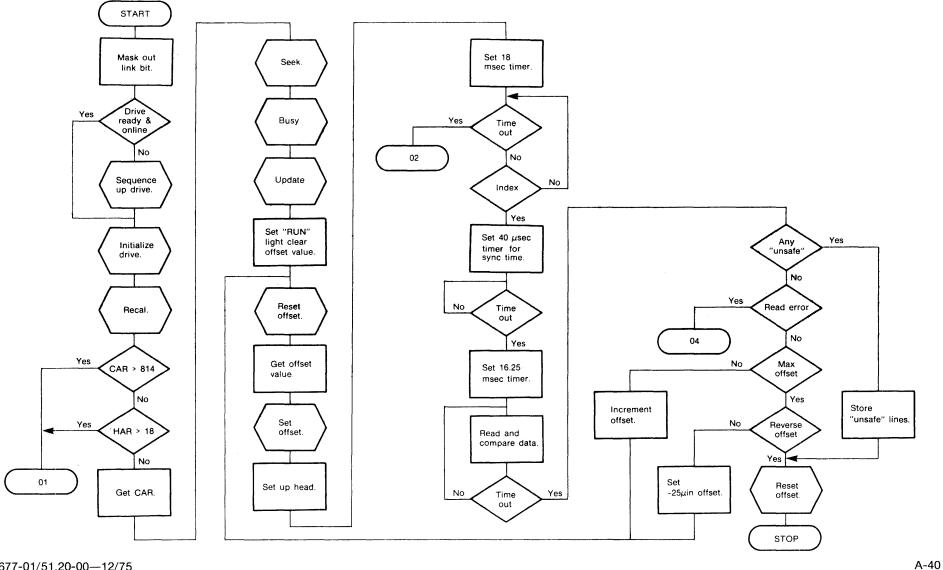

| HEAD ALIGNMENT, ROUTINE 05 A              |             |

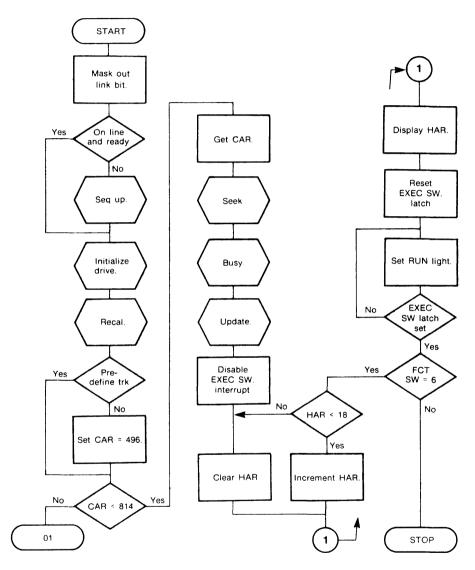

| HEAD VERIFICATION, ROUTINE 06 A           |             |

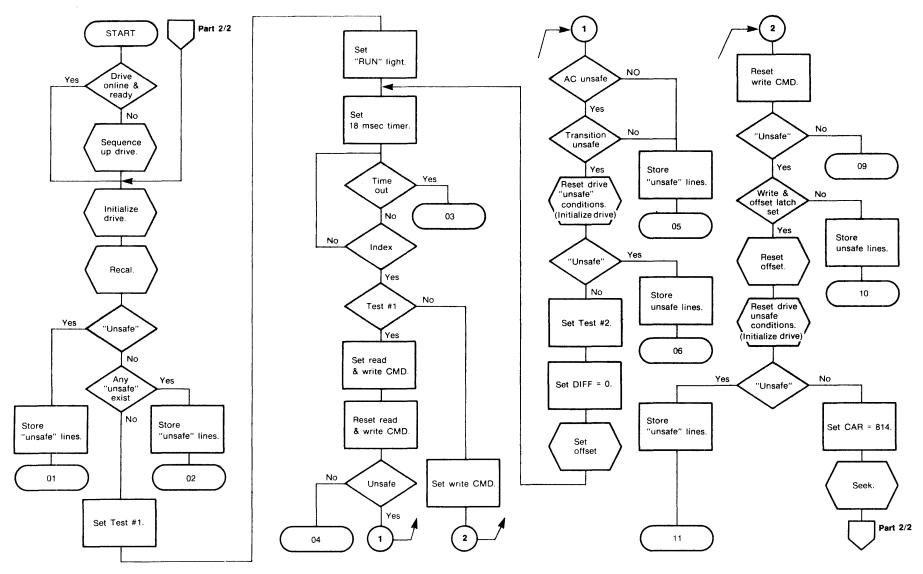

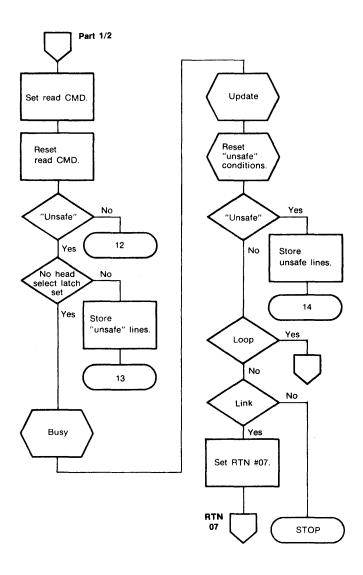

| WRITE VERIFY READ, ROUTINE 07 (2 parts) A |             |

| INCREMENTAL OFFSET READ, ROUTINE 09 A     |             |

| READ 65K TIMES, ROUTINE 0A A              |             |

| READ/WRITE SAFETY, ROUTINE 0B (2 parts) A | ١-42        |

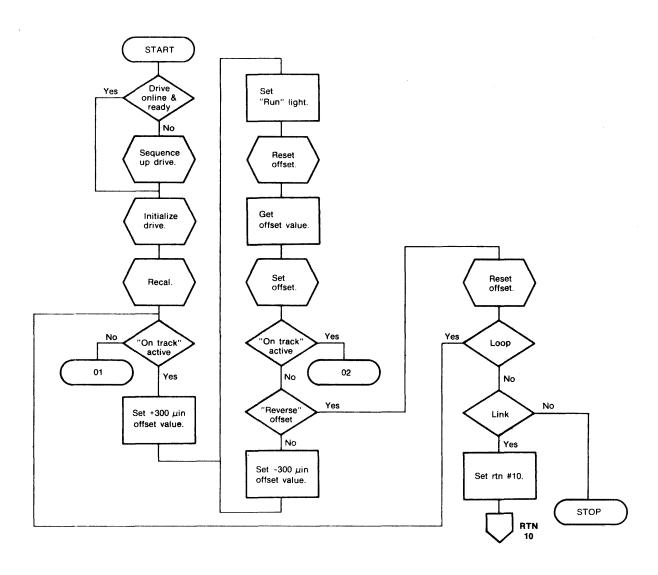

| OFFSET, ROUTINE 0D A                      |             |

| INDEX, ROUTINE 10 A                       | ۱-45        |

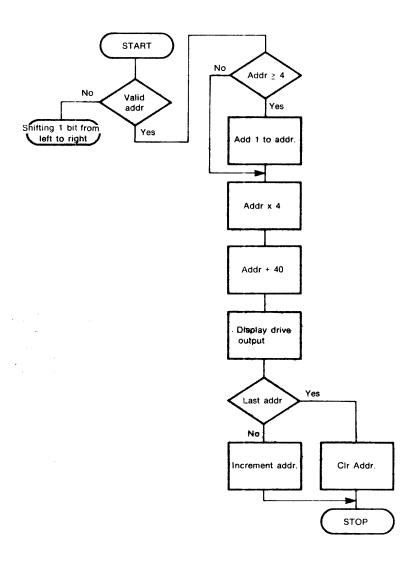

| DISPLAY DRIVE OUTPUT BYTE, ROUTINE 11 A   |             |

| RECALIBRATE, ROUTINE 12 A                 | 47-47       |

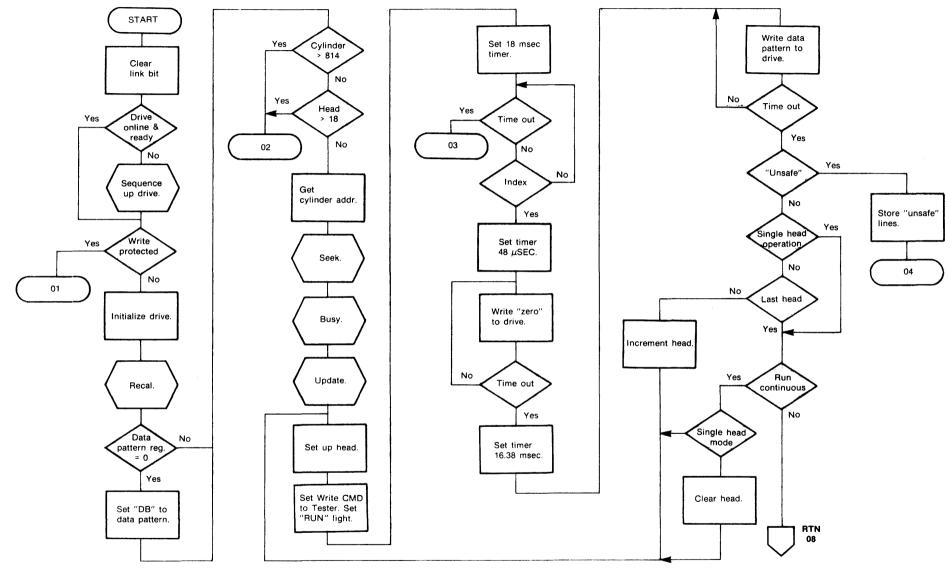

| WRITE, ROUTINE 13 A                       | 48-۸        |

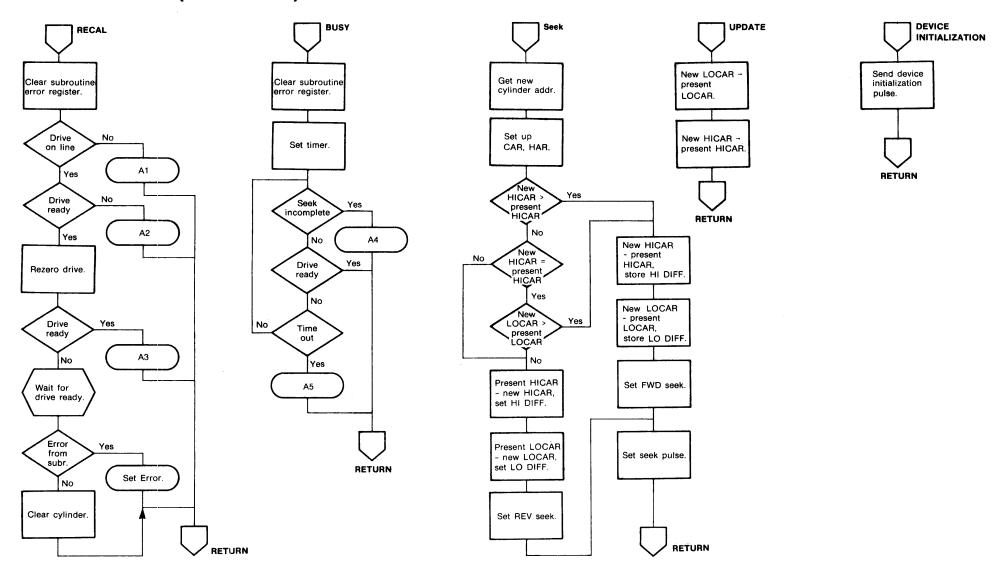

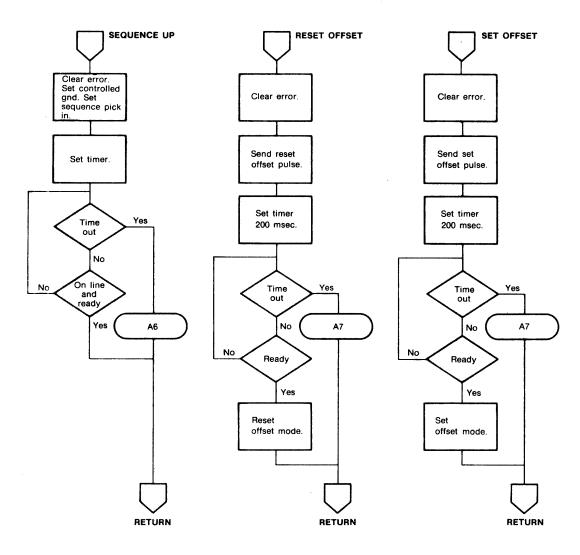

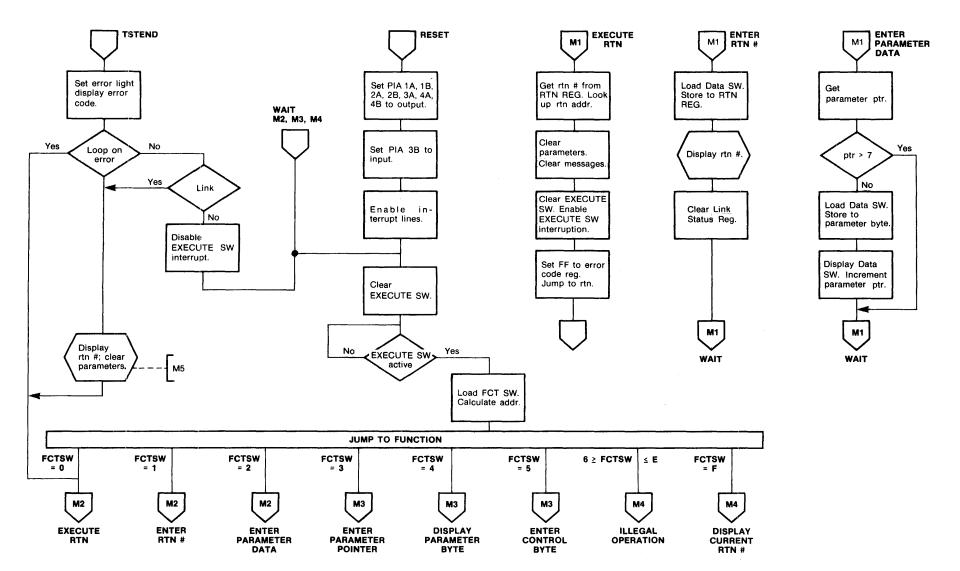

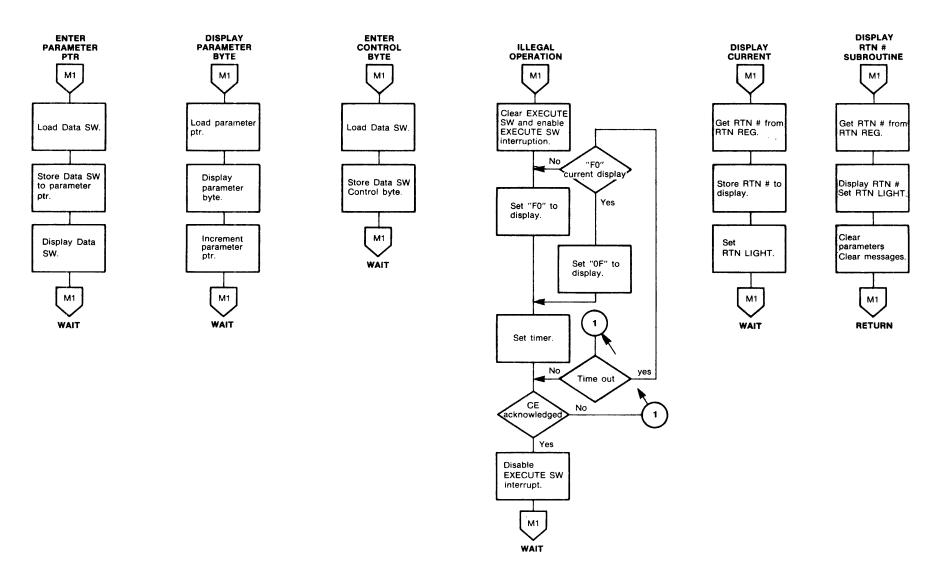

| SUBROUTINES (2 parts) A                   | ۱-49        |

| MONITOR (2 parts) A                       |             |

## LIST OF TABLES

| Table                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                                           |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>3-1               | GENERAL SPECIFICATIONS INPUT INTERFACE LINES OUTPUT INTERFACE LINES LINE CURRENT REQUIREMENTS AC CONNECTOR PIN ASSIGNMENTS DCL SUPPORT SYSTEM INPUT SOURCES AND                                                                                                                                                                                                                                                                                                                                                                 | 1-20<br>1-27<br>1-34<br>1-37                                                                                   |

| 3-2<br>3-3<br>3-4<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5 | OUTPUT DESTINATIONS POWER MONITOR SPECIFICATIONS HEAD AND Y-SELECT EQUIVALENCE WRITE CURRENT AMPLITUDE TESTER HOOKUP TESTER ROUTINE NUMBERS AND RUN OPTIONS HARDWARE VERSUS APPLICABLE PARAGRAPH ALIGNMENT SPECIFICATIONS WAY ALIGNMENT EXAMPLE CASES                                                                                                                                                                                                                                                                           | 3-20<br>3-78<br>3-88<br>. 4-3<br>. 4-3<br>. 4-9<br>4-16                                                        |

|                                                      | APPENDIX A:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

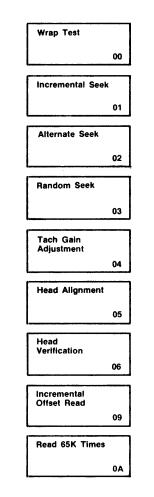

|                                                      | ROUTINE INDEX WRAP TEST, ROUTINE 00 INCREMENTAL SEEK, ROUTINE 01 ALTERNATE SEEK, ROUTINE 02 RANDOM SEEK, ROUTINE 03 TACHOMETER GAIN ADJUSTMENT, ROUTINE 04 HEAD ALIGNMENT, ROUTINE 05 HEAD VERIFICATION, ROUTINE 06 WRITE VERIFY READ, ROUTINE 07 (3 parts) INCREMENTAL OFFSET READ, ROUTINE 09 (2 parts) READ 65K TIMES, ROUTINE 0A (2 parts) READ/WRITE SAFETY, ROUTINE 0B (2 parts) OFFSET, ROUTINE 0D INDEX, ROUTINE 10 (2 parts) DISPLAY DRIVE OUTPUT BYTE, ROUTINE 11 (2 parts) RECALIBRATE, ROUTINE 12 WRITE, ROUTINE 13 | . A-8<br>. A-9<br>A-10<br>A-11<br>A-12<br>A-13<br>A-14<br>A-15<br>A-18<br>A-20<br>A-22<br>A-24<br>A-25<br>A-27 |

# SECTION 1 GENERAL INFORMATION

### 1.1 INTRODUCTION

Memorex 677 Series Disc Storage Drives are high-capacity, direct-access data storage devices featuring fast access and simplicity in design and packaging, proven to provide high reliability and ease of maintenance. Particular 677 Series drives are customized to fill the needs of original equipment manufacturers. Two such drives, supplied to Digital Equipment Corporation (DEC), are addressed in this manual. They are:

### 1.1.1 Product Definition

The 677-51 DEC and 677-01 DEC are derivatives of the 670 and 675, Memorex's third and fourth generation drives, respectively. Major components in either DEC drive are the same as those in the 670, with refinements as incorporated since the first 670 was delivered in October of 1972. Components in the 677-01 DEC drive which are sensitive to a doubling of data capacity to 200 megabytes are the same as those in the 675, with

| Memorex Designation                                                                   | DEC Designation      | Approximate Data Capacity | Average<br>Access Time |

|---------------------------------------------------------------------------------------|----------------------|---------------------------|------------------------|

| <ul><li>677-01 DEC Disc Storage Drive</li><li>677-51 DEC Disc Storage Drive</li></ul> | RP06 Disc Pack Drive | 200 megabytes             | 28.5 msec              |

|                                                                                       | RP05 Disc Pack Drive | 100 megabytes             | 28.5 msec              |

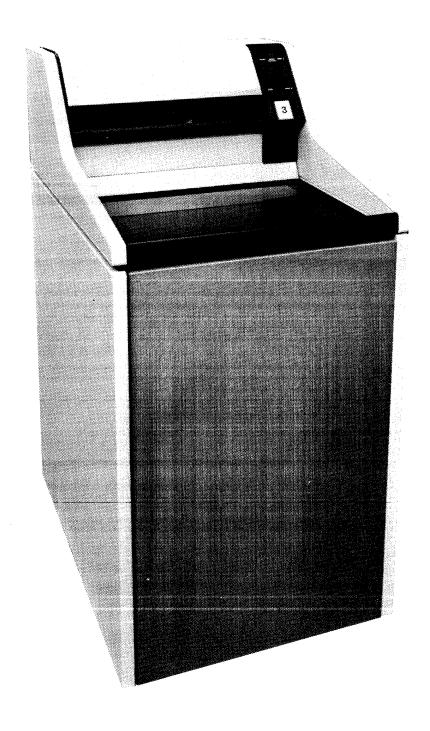

The two drives above are packaged as one spindle per drive. The data storage media used is the 200-megabyte Memorex Mark XI Disc Pack (equivalent to IBM 336-11) or the 100-megabyte Memorex Mark X Disc Pack (equivalent to IBM 3336). Except for DEC logo identifications, the two drives above look alike (Figure 1-1).

Each drive is supplied in one of two power configurations. Model A configurations (677-01A DEC and 677-51A DEC) operate from domestic power sources. Model B configurations operate from other power sources. Power conversion at the user site is possible.

Field conversion to double the approximate data capacity (going from a -51 DEC drive to a -01 DEC drive) is possible.

Control logic for either DEC drive is contained in an external attachment. It is designated the Device Control Logic (DCL) and is supplied and integrated with a drive by the user.

Each DEC drive (excluding DCL) is a recognized component of Underwriters Laboratories.

refinements as incorporated since the first 675 was delivered in October of 1974.

Any 677-XY ("X" designates maximum data capacity, "Y" designates a particular OEM) consists of customized features, integrated with a residual core of hardware and logic which provide fundamental drive capabilities. The "residual core" consists of major components in the drive's servo system, read/write system, spindle control system, and power system. The approach used in structuring any 677-XY drive has two principal objectives:

- To maximize the latitude provided OEM's for customization, to insure drive compliance with OEM system compatibility, performance, and operating requirements.

- 2. To insure drive compliance with Memorex standards for high reliability, proven maintainability, and effective physical design—all as derived from manufacturing experience (18,000 drives) and operating experience (90 million online hours) with the core of hardware and logic which are common to all state-of-the-art Memorex drives.

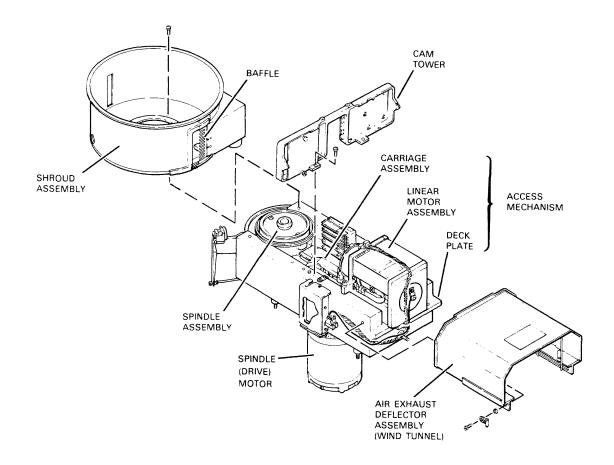

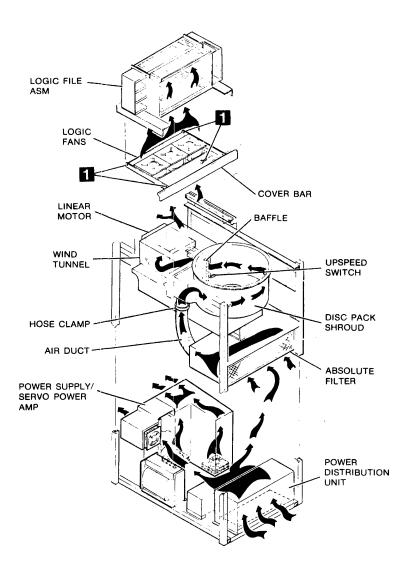

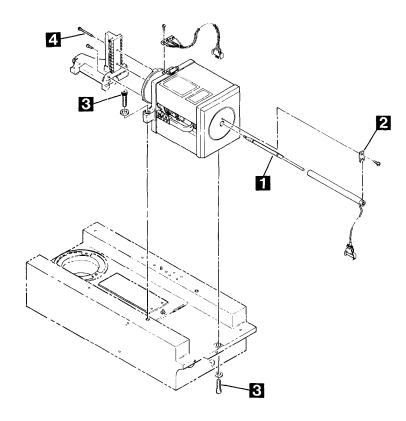

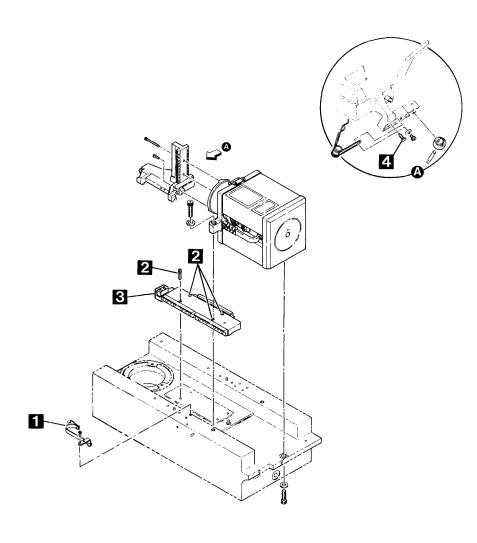

FIGURE 1-1. MEMOREX 677-01/51 DEC DISC STORAGE DRIVE

The customized features in any 677-XY address:

- Either one or two spindles per drive

- Overall performance (either column below):

Approx. data capacity per spindle:

200 megabytes

100 megabytes

Average access time:

28.5 msec

28.5 msec

Data transfer rate:

806 kilobytes/sec

806 kilobytes/sec

Media compatibility (same column below):

Memorex media:

Mark XI Disc Pack

Mark X Disc Pack

IBM media:

3336-11 Disc Pack

3336 Disc Pack

- Interface lines

- Receiver and driver circuits

- Dual port capability

- Logical address plugs

- Console indicators and diagnostic display

- Automatic restart after ac power drop

- Dynamic braking of pack rotation

- 50 Hz power

- Rotational position sensing

- Address mark

- · Pad to index after write address mark

- VFO/precompensated data conditioning

- 1 to 128 programmable sector divider

- · Reading of registers

- Multiplex interface

- External cables and configuration

- Appearance group (covers and company logo)

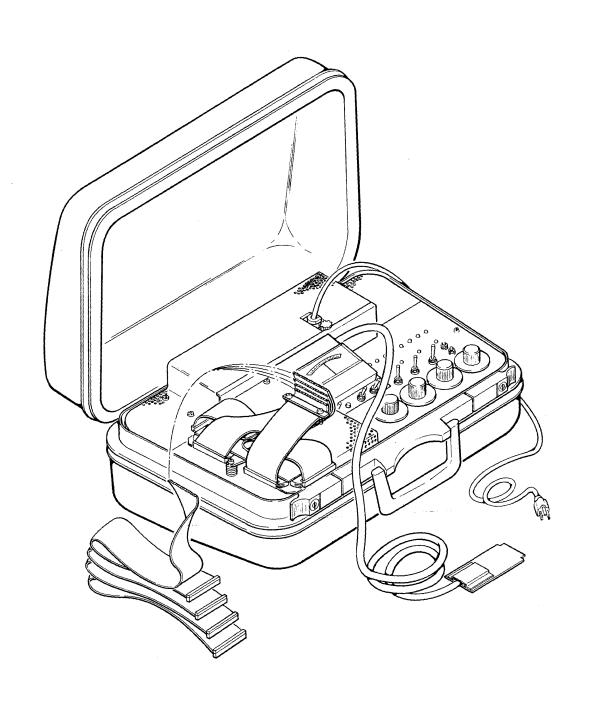

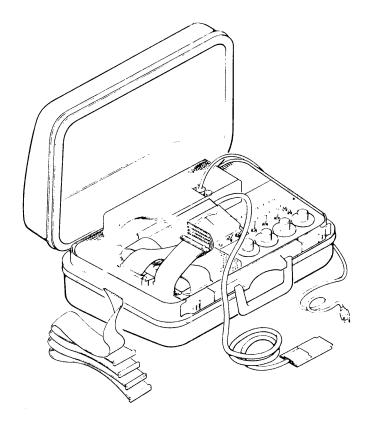

In addition to customizing the drive itself as indicated above, the Memorex 800 Disc Storage Subsystem Tester can be customized to execute OEM diagnostic programs for testing 677-XY offline, and this has been accomplished for the 677-01 DEC and 677-51 DEC.

Special maintenance tools, in addition to the tester mentioned above, and conversion kits (power and data capacity) are also available.

# 1.1.2 Manual Purpose and Intended Use

This manual is the single authoritative reference for technical information on the 677-01 and 677-51 DEC drives that are provided by Memorex, with one exception: the *Illustrated Parts Catalog* is provided separately as Publication No. 677-01.23-00

#### **NOTE**

This manual, in its entirety, is applicable only to 677-01 DEC and 677-51 DEC. Applicability of particular paragraphs to any 677-XY (existing or planned) can be ascertained by applying the information in paragraph 1.1.1, recognizing at the outset that no other distinction is made in succeeding paragraphs between customized and standardized features.

Information in this manual is intended for use by Digital Equipment Corporation, in preparing documentation for installing, operating, servicing, and troubleshooting customer EDP systems which contain Memorex drives. Within the general framework of providing drive inputs to this system documentation, scope of coverage in this manual is unlimited. The format used is described as follows (refer to Table of Contents):

- Information is presented in a way that recognizes drive involvement with the rest of the system, thereby easing the transition from "drive inputs" to "system documentation." For example, drive installation procedures contain indications of when the drive is ready for DCL attachment, cabling, or system verification testing.

- Different audiences are recognized. For example, paragraph 2.4 is dedicated to operator information. Searching through other paragraphs for drive inputs to a "system operator's guide" is probably unnecessary.

- As the required number of drives are produced, nonfunctional refinements may be incorporated; this possibility is recognized in the manual. To lessen the probable impact on system documentation due to engineering changes in the drive, operating principles and

theory are described in functional terms. The result is a decreased probability of issuing manual updates, and consequently of changing system documentation to reflect the updates.

Performance requirements are presented to support and extend the descriptions of system operating principles and theory—and also to make available, for possible customer use, a basis for designing tests of the drive at either the system or component level. Of course, performance testing of the drive after delivery is totally customer discretionary, but the requirements themselves relate directly to what systems do for the drive, and this is vital to understanding the operating principles and theory applied.

# 1.1.3 Drive Functions and Applications

The 677-01 DEC or 677-51 DEC drive is used as an input/output device in the data processing system shown in Figure 1-2. The system is configured using OEM control units and drive attachments to process sequential and randomly organized files using disc storage. Data is either read from a recording surface on the disc pack and sent to the system, or written on a disc surface for retrieval at a later time. The pack serves as permanent or temporary information storage media which can be written on by one drive, removed and stored, and then installed on the same or another drive with no degradation in data recovery or loss of pack compatibility. The drive rotates the pack at 3600 rpm, selects one of 19 read/write heads for an operation, positions the heads to the selected track on the disc surface, and allows the system to synchronize the data transfer. The data transfer between drive and system occurs under control of an OEM device packaged as an external attachment to the drive. The mechanical and electrical characteristics of the drive are customized to satisfy OEM interface specifications. Once the drive is installed into the system, routine operation of the drive is fully automated, requiring Operator intervention simply for an exchange of disc packs.

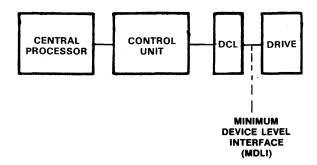

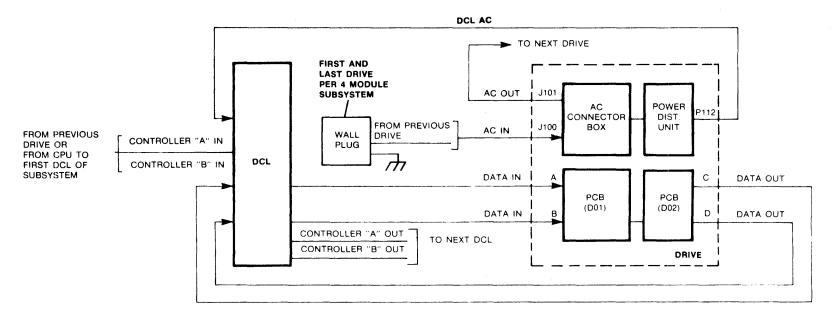

The name designated by DEC for the interface control attachment is **Device Control Logic (DCL)**. A DCL is physically attachable to a drive, and is attached to serve as the drive's port of com-

munication with the system. It is supplied by DEC, which also supplies information needed for DCL installation and servicing.

The sketch below defines the MDLI used as a reference point in discussing the system.

As indicated above, a drive transfers data to the system through the MDLI to its attached DCL.

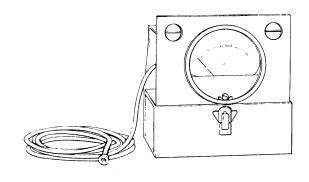

The 800 Disc Storage Subsystem Tester (Figure 1-3) permits drive testing concurrently with system operation. The Tester attaches to the MDLI to perform microdiagnostics testing the key functional areas within a drive. The routines programmed into this tester are described in Appendix A.

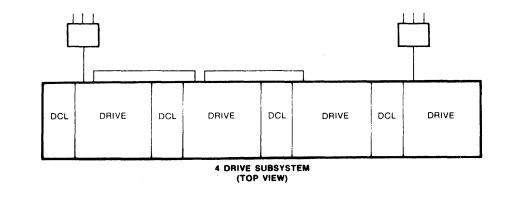

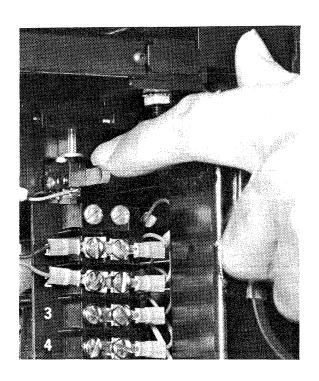

Figure 1-4 illustrates drive external cabling for the example case of a system having four drives. All drive signal inputs and outputs are transmitted in dedicated lines, contained in Cables A and B (DCL commands of the drive) and Cables C and D (drive responses to commands). Regarding ac power connections, wall power is supplied to one drive in a grouping of three drives. For four to six attached drives, two wall power connections are required.

Two models of each drive, accommodating 60 Hz and 50 Hz operation at specified voltages, are supplied. Conversion between models in the field is straightforward (replacement of spindle motor assembly and belts and moving connections only).

FIGURE 1-2. EXAMPLE OF A DATA PROCESSING SYSTEM

FIGURE 1-3. MEMOREX 800 DISC STORAGE SUBSYSTEM TESTER

| QTY*                                 | NAME                                                                      | CONNECTION                                                                                                           |

|--------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 4<br>2<br>2<br>4<br>4<br>4<br>4<br>3 | DCL AC AC IN AC OUT CABLE A CABLE B CABLE C CABLE D CONTROLLER CONTROLLER | DRIVE TO DCL" WALL TO DRIVE DRIVE TO DRIVE DCL TO DRIVE DCL TO DRIVE DRIVE TO DCL DRIVE TO DCL CPU TO DCL DCL TO DCL |

<sup>\*</sup>FOR A 4-DRIVE SYSTEM

<sup>\*\*\*2</sup> FOR CONTROLERS "A" AND "B" ACTIVE

FIGURE 1-4. TYPICAL DRIVE EXTERNAL CABLNG

<sup>&</sup>quot;MEMOREX SUPPLIED

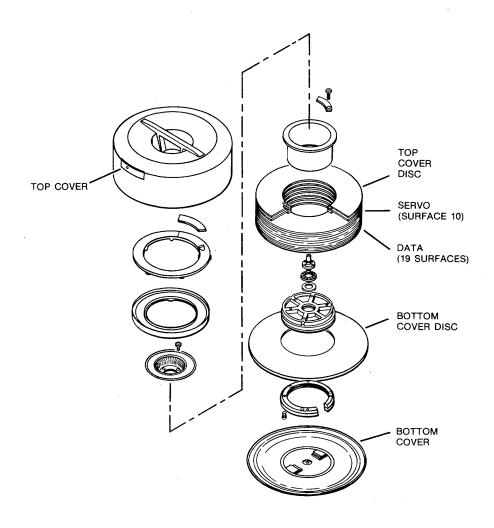

### 1.1.4 Disc Pack

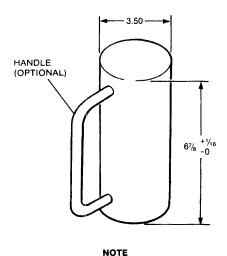

The Memorex Mark X or XI Disc Pack (Figure 1-5) is a compact disc assembly weighing 20 pounds. Protective discs are located at the top and bottom of the disc array to minimize possible physical damage that might result from handling. A two-piece cover has a shock absorbing bumper strip for additional pack protection. Specifications for the Memorex packs equal or exceed those for equivalent capacity IBM packs.

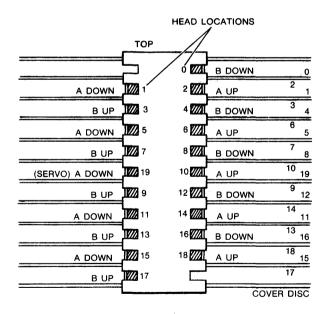

The assembly contains 10 recording discs. A total of 19 surfaces are recording surfaces; the 20th surface contains prerecorded track-following (servo) and sector-timing data.

Installation of the disc pack is accomplished by simply sliding the drive's glass access door with a slight lifting action toward the rear of the drive, mounting the pack on the spindle in the conventional manner, and closing the access door.

### 1.1.5 Hardware Orientation

Major assemblies of the drive are shown in Figures 1-6 to 1-10.

The drive can be divided into a number of hardware groups. They are:

- Operator Control System, containing the specified controls and indicators for routine operation of the drive by nontechnical personnel.

- DCL (Device Control Logic) Support System, which receives a specified set of commands and data to be recorded on the disc pack, and sends specified responses to these commands and data retrieved from the pack to the DCL.

- Pack Access System, providing access to the pack area for loading and unloading disc packs.

It consists of a sliding access door assembly and a door lock mechanism.

- Servo System, consisting of servo electronics, linear positioning motor assembly, and carriage assembly. Access to a data cylinder in the disc pack is achieved by the positioning motor; it controls motion of the carriage on which the read/write heads and servo head are attached. The servo electronics position and lock the carriage on the desired cylinder by reading

information prerecorded on the disc pack at the factory. This information is read by the servo head. Once the desired cylinder has been reached and the Servo System has locked on the servo track, any read/write head may be electronically selected and the data recorded or retrieved from the pack.

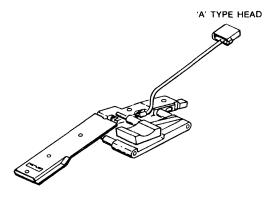

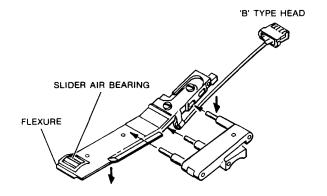

- Read/Write System, consisting of read/write circuitry and read/write heads. The system accepts decoded control signals to provide the head select, read, and write functions. Including the servo head, there are a total of 20 heads, 10 mounted on each side of the T-block. Each head is contained in a head/arm assembly which fits into precision slots in the T-block and is held in place by screws.

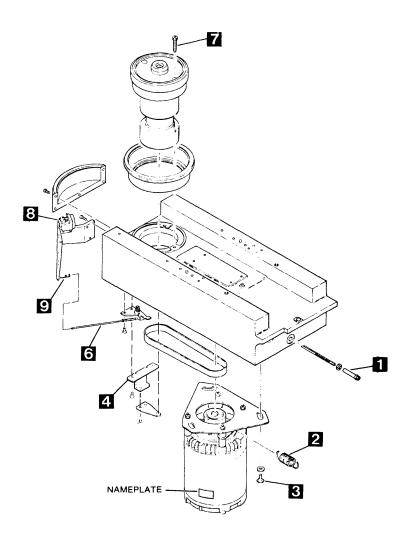

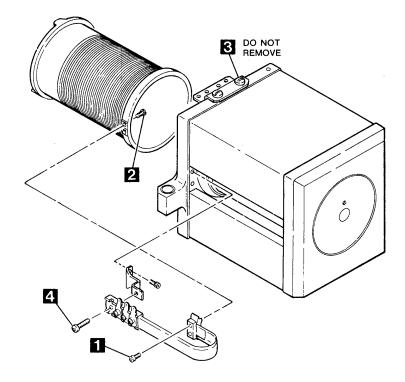

- Spindle Control System, consisting of motor control circuitry, drive motor, and spindle. The disc pack attaches to the precision ball-bearing spindle assembly that is belt driven by the one-HP drive motor at 3600 rpm. The drive motor assembly is spring loaded with sufficient belt tension to achieve start and stop requirements. Fast stopping times are achieved by a dynamic braking system that utilizes the electromagnetic properties of the motor. The spindle assembly has a static brake mechanism which senses correct positioning of the disc pack and inhibits drive operation if the pack is not correctly positioned. The motor control circuits provide up- and down-sequencing control.

- Airflow and Filtration System, which is a patented absolute-filter system, moves filtered air throughout the shroud assembly and carriage way, and cools the linear positioning motor assembly. The spinning disc pack itself is used to pump filtered air through the drive. A wind tunnel guides the cooling air around and through the linear positioning motor assembly, and then out of the drive through the rear cover. It slides towards the rear to provide easy access to the heads for servicing. The fundamental design of the system allows for more effective air sealing, greatly reducing the chances of contamination.

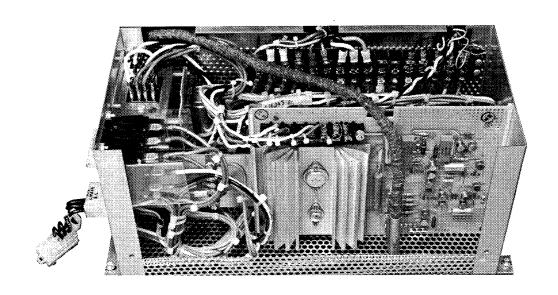

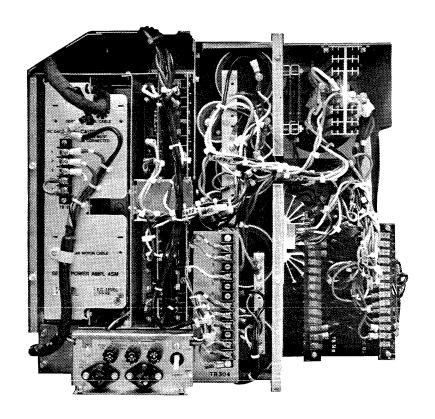

- Power System, consisting of the power distribution unit and dc power supply. The power distribution unit distributes filtered ac power to the drive and dc power supply. The dc power supply provides all dc voltages needed for drive operation.

FIGURE 1-5. MARK X OR MARK XI DISC PACK

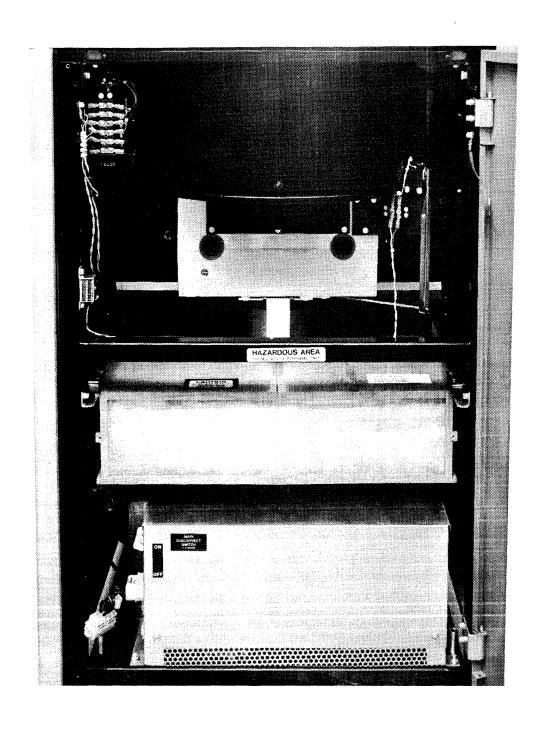

FIGURE 1-6. DRIVE FRONT VIEW

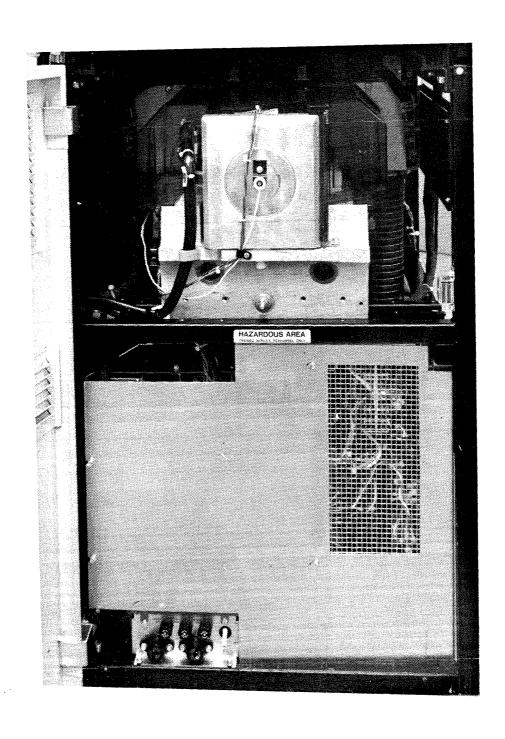

FIGURE 1-7. DRIVE REAR VIEW

FIGURE 1-8. DECK PLATE

FIGURE 1-9. POWER DISTRIBUTION UNIT

FIGURE 1-10. POWER SUPPLY

## 1.1.6 Basic Drive Operations

The basic drive operations are head position, read, and write. Head position operations are head load, recalibrate, seek, offset seek, retract, and emergency retract.

Head Load. When the START switch on the drive's operator panel is depressed (assuming that the drive is installed in the system and power is applied), power is supplied to the spindle and the pack begins rotating. When the pack is up to speed (3600 rpm), the heads are positioned to Cylinder 000 in a head load sequence and the drive sends a signal to the system indicating it is ready. The ready state occurs approximately 20 seconds after the START switch is depressed, and is indicated to the drive user by lighting READY on the drive's display panel. At this time the drive is ready to receive a command to seek a specified cylinder, select a specified head, and read or write.

**Recalibrate.** A recalibrate operation causes the heads to be positioned at Cylinder 000. A recalibrate can be initiated by a system command, an operator inserting the logical address plug, or a seek incomplete condition (see paragraph below).

**Seek.** A seek operation causes the heads to be positioned at the desired cylinder and is initiated by a system command. If the heads fail to position at the proper cylinder, a seek incomplete status is sent to the system and a recalibrate operation is initiated.

Offset Seek. An offset seek operation is initiated by a system command and causes the heads to move a nominal distance away from the data track centerline to aid in recovering data after a read error has been made.

**Retract.** A retract operation is initiated when the drive is stopped, and causes the heads to be lifted from their flying position immediately above the disc surface and to be retracted from the pack to allow pack removal.

**Emergency Retract.** An emergency retract operation is used to remove the heads from the pack if the retract operation fails, or if there is a power or power supply failure.

Write. Writing is performed by a magnetic recording head which flies over a rotating disc in the prescribed cylinder location. The control unit

sends a serial stream of data to the drive to be MFM-encoded into clock or data pulses and recorded on a data track as magnetic flux reversals. The data remains on the disc surface where it can be read at any time until recorded over by new data. The disc pack containing this data can be removed from the drive and stored, and then installed in the same or another drive for reading or additional writing of data.

Read. The same head is used to write the data as used to read it. The magnetic flux changes recorded on the disc surface cause current reversals in the head's coils. The current reversals are converted to an output signal which is fed into the data separator (VFO). The VFO separates clock from data, generates serial data to the control unit, and provides a clock pulse to strobe the data.

### 1.2 DRIVE SPECIFICATIONS

### 1.2.1 General Drive Specifications

Table 1-1 summarizes general specifications for the 677-01A and B and 677-51A and B. This table provides, primarily, a single reference source of the major performance and operating features of the drive (both models), its physical characteristics, the numbering conventions adopted (heads, cylinders, surfaces), and the power and environmental requirements of the user site.

Referring to each specification for access time in Table 1-1 (first paragraph), access time is defined as the time interval between true transitions of SEEK START and READY.

The CONTROL A/B switch (Table 1-1) in the operator control panel is a three-position switch. When switched to the center position, drive communication with the DCL is disabled completely. When switched up or down, communication in one port is enabled and the other is disabled.

### 1.2.2 Error Rates

A seek error, defined as an incomplete seek or a seek to a wrong cylinder, occurs less than one in 10° random seeks (average).

#### TABLE 1-1. GENERAL SPECIFICATIONS

## DATA RETRIEVAL TIMES Average Latency Time ...... 8.33 msec Maximum Access Time, Track-toTrack\*...... 6 msec Maximum Access Time, Track 000 to Track 814\* ...... 53 msec DISC PACK CHARACTERISTICS Surface Numbering Scheme, Uppermost to Lowermost Surface ..... Surface 00 to 19 Servo Surface ...... Surface 10 Servo Format...... Ref: Figure 1-11 Encoding Scheme ...... MFM Coating Material (Memorex Mark X or XI) ...... Oriented pfizer iron oxide **HEADS** Nominal Track Spacing Center-to-Center (677-01) ............. 2.7 mils Nominal Track Spacing Center-to-Center (677-51) ............. 5.2 mils INFORMATION STORAGE CAPACITIES Cylinder Capacity (bytes available to a single access) ...... 255,360 bytes Disc Pack Capacity (including alternate cylinders) ...... 208,118,400 bytes (677-01 drive) 104,952,960 bytes (677-51 drive) **DIMENSIONS AND WEIGHT** Weight ...... 550 lbs.

<sup>\*</sup>This figure does not include average latency time of 8.33 msec due to rotation.

<sup>\*\*</sup>Average access time = time excluding latency to do all possible combinations of seeks

number of seek combinations possible

## TABLE 1-1. GENERAL SPECIFICATIONS (Continued)

| SERVICE CLEARANCE                                                                                      |                                                                                                    |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Front Rear Sides                                                                                       | 45 inches                                                                                          |

| OPERATOR CONTROLS                                                                                      |                                                                                                    |

| Switches                                                                                               | START/STOP<br>WRITE PROTECT/READ WRITE<br>CONTROL A/CONTROL B<br>Logical Address Plug<br>Lamp Test |

| Indicators                                                                                             | START CONTROL A/B READY UNSAFE STANDBY WRITE PROTECT DOOR LOCKED                                   |

| START/STOP TIME                                                                                        | 20 sec                                                                                             |

| POWER REQUIREMENTS                                                                                     |                                                                                                    |

| Model A: Frequency Voltage Phase and Configuration Model B:                                            | 208/230/240 Vac ± 10%                                                                              |

| Frequency Voltage Phase and Configuration, 220 Vac Phase and Configuration, 380/398/416 Vac Model A/B: | 220/380/398/416 Vac ± 10%<br>3-phase + ground, Delta                                               |

| Maximum Run Current (excluding DCL)                                                                    | 30 amps/phase                                                                                      |

| Number of Drives on One AC Cable String                                                                | 70% Self contained Self contained                                                                  |

| MAXIMUM HEAT DISSIPATION                                                                               | 4450 Btu/hour                                                                                      |

| INTERNAL AIR FLOW                                                                                      | 550 CFM                                                                                            |

| OPERATING ENVIRONMENTAL CONDITIONS                                                                     |                                                                                                    |

| Temperature: Range Optimum Allowed Variation                                                           | 75° F                                                                                              |

### TABLE 1-1. GENERAL SPECIFICATIONS (Continued)

Relative Humidity:

Maximum Wet Bulb ...... 78°F

(continued operation while writing)

### NONOPERATING ENVIRONMENTAL CONDITIONS

Temperature:

Range ...... 50° to 110° F

Relative Humidity:

### SHIPPING ENVIRONMENTAL CONDITIONS

Temperature:

Relative Humidity:

D-999-63T

One drive performance parameter is specified by the Read Error Rate, which depends on whether the error is correctable or uncorrectable. The specification for read errors follows.

- a. The Read Error Rate is determined for interchanged written media using Memorex Mark XI Disc Packs and drives aligned with Memorex CE Disc Packs.

- b. Error detection and correction capabilities external to the drive must be capable of detecting and correcting burst errors of 11 bits or less in length within the record being read.

c. When a data error occurs, the customer's control unit must reorient on the failing record and retry the read operation up to 16 times. If the error persists, after 16 retries at nominal head position, the control unit must attempt to recover the data by offset operation and error correction. The retry sequence must be two retrys, each at offsets of:

| 677-01           | <u>677-51</u>                       |

|------------------|-------------------------------------|

| +200 microinches | + 400 microinches                   |

| -200 microinches | <ul> <li>400 microinches</li> </ul> |

| +400 microinches | + 800 microinches                   |

| -400 microinches | <ul> <li>800 microinches</li> </ul> |

| +600 microinches | +1200 microinches                   |

| -600 microinches | -1200 microinches                   |

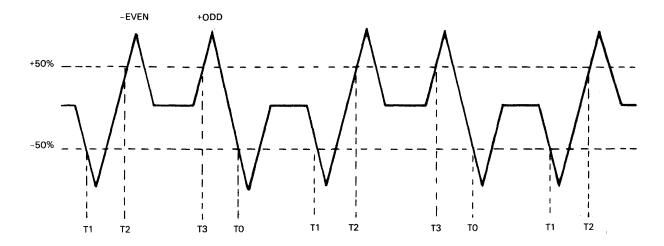

| INTERVAL | TIME (NSEC)      |

|----------|------------------|

| T0 to T0 | 2480             |

| T0 to T2 | 1240             |

| T1 to T1 | 2480             |

| T1 to T2 | 360 (Track 404)* |

|          | 360 (Track 808)  |

| T1 to T2 | 250 (Track 000)  |

| T3 to T0 | 360 (Track 404)* |

| 1        | 360 (Track 808)  |

| T3 to T0 | 250 (Track 000)  |

|          | 1                |

<sup>\*100</sup> Megabyte Drives

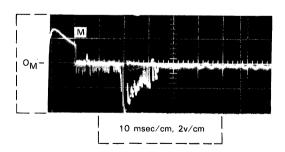

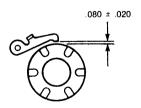

FIGURE 1-11. SERVO DATA FORMAT

- d. Correctable errors per items (a,b,c) do not occur at a rate greater than once in every 10<sup>9</sup> bits transferred.

- e. Uncorrectable/unrecoverable errors per items (a,b,c) do not occur at a rate greater than once in every 10<sup>12</sup> bits transferred.

- f. Error rates specified in items (d,e) exclude errors due to defects in a disc pack.

## 1.2.3 PM Time and MTBF

Actual maintenance time spent by trained field engineers in performing the recommended preventive maintenance (PM) on a population of drives is estimated at 1 manhour per 200 operating hours per spindle. Following an initial test/debug period of 90 days, and before the period at which the drive approaches its end of life, the average Mean Time Between Failure (MTBF) of a population of 18 drives or more, distributed over 5 or more customer sites, is 2500 power-on hours. This statistical MTBF is based on performance of all recommended PM procedures as scheduled. Each drive must operate a minimum time period equal to the stated MTBF for the statistic to be meaningful.

### 1.2.4 Response to Brownouts

Redundant power monitoring circuits in the drive detect a loss of ac power (such as brownouts). If it occurs, heads are retracted from the pack at a controlled velocity with a clearance adequate to retain their sensitive calibrations and alignments with respect to the disc surfaces. The drive will withstand up to 10 msec ac supply dropout without loss of any recorded data or interruption to normal operation.

### 1.3 INTERFACE SPECIFICATIONS

Interface specifications are presented in paragraphs 1.3.1 (electrical) and 1.3.2 (mechanical). They address the principle items of drive customization for the OEM. Field engineers can skip over these paragraphs, and return to them as referenced in succeeding paragraphs.

The term "interface specifications" is generally used, but its specific meaning for this manual should be discussed to assure a common understanding. A discussion follows:

- The "interface" referred to is the internal/external interface relative to the drive. Three distinct interfaces are involved: between drive and DCL, drive and operator (human interface), and drive and user site. Their commonality is OEM customization, most extensive (relative to the drive) for the first interface mentioned and least for the last mentioned.

- The "specifications" referred to are drive design requirements and conventions which establish compatibility between both sides of each interface. Specifications containing data of special significance to technical readers are provided in this manual.

- Many "interface specifications" significance when installing, operating, and servicing the drive. Regarding a particular interface specification, who needs to know (site planners, operators, instructors, and/or field engineers), when it is applied in the field (for installation, operation, and/or servicing), and what functional unit of the drive is being addressed (servo system, power system, etc.) have several appropriate combinations, depending on the item specified. For this reason, the interface specifications which follow are organized into general categories of electrical and mechanical types. This organization avoids repetition of information relating to specific subjects as addressed in later sections-and which, by referencing, will return field engineers here.

# 1.3.1 Electrical Interface Specification

### 1.3.1.1 Command Summary

The drive contains logic to execute the following system commands:

Seek Go, which specifies the start of seek motion, head to be used, cylinder difference, and direction

- Seek Offset, which specifies the start of offset motion, offset value, and direction

- · Write, which specifies a write operation

- Read, which specifies a read operation

- Recalibrate, which specifies repositioning the heads to Cylinder 000

- Device Initialize, which specifies resetting of all safety latches

- Device in Standby, which specifies standby sequencing

- Offset Reset, which specifies resetting an offset operation by repositioning the heads over track centers.

#### 1.3.1.2 DCL to Drive Lines

Commands are provided via dedicated input lines contained in interface Cables A and B, connecting the DCL with the drive's Input PCB (logic gate position D01). Table 1-2 tabulates the names given to signals in these lines and their pin assignments. Each signal is described in the following paragraphs.

- SEEK DIRECTION LEVEL indicates the direction of the seek. The signal being true specifies a reverse seek (motion away from spindle). A false condition specifies a forward seek (motion towards spindle).

- Cylinder Difference/Offset Lines (10) indicate, for a seek operation, the number of cylinders to be traversed. The seek direction is given by the condition of SEEK DIRECTION LEVEL. For an offset operation, these lines indicate the amount and direction of head offset. The condition of OFFSET MODE LEVEL determines whether the operation is a seek or offset operation. Definitions of the 10 lines are:

| Bit  | Seek<br>Operation | Offset<br>Operation |

|------|-------------------|---------------------|

| 1    | DIFF=1            | 25 MICROINCHES      |

| 2    | DIFF=2            | 50 MICROINCHES      |

| 4    | DIFF=4            | 100 MICROINCHES     |

| 8    | DIFF=8            | 200 MICROINCHES     |

| 16   | DIFF=16           | 400 MICROINCHES     |

| 32   | DIFF=32           | 800 MICROINCHES*    |

| 64   | DIFF=64           | (not used)          |

| 128  | DIFF=128          | REVERSE DIRECTION   |

| 256  | DIFF=256          | (not used)          |

| 512* | DIFF=512*         | (not used)          |

<sup>\*</sup>Not used in 100 MB drive.

### TABLE 1-2. INPUT INTERFACE LINES

Input Lines (36), MDLI to Drive PCB D01

|                                 | —Pin Number and Signal—                                                                                                     |                                 | —Pin Number and Signal—                              |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------|

| B40<br>A24                      | -SEEK DIRECTION LEVEL<br>-DIFF 1/OFFSET 25 µIN                                                                              | A19<br>B18                      | -CÁR 256<br>-CAR 512                                 |

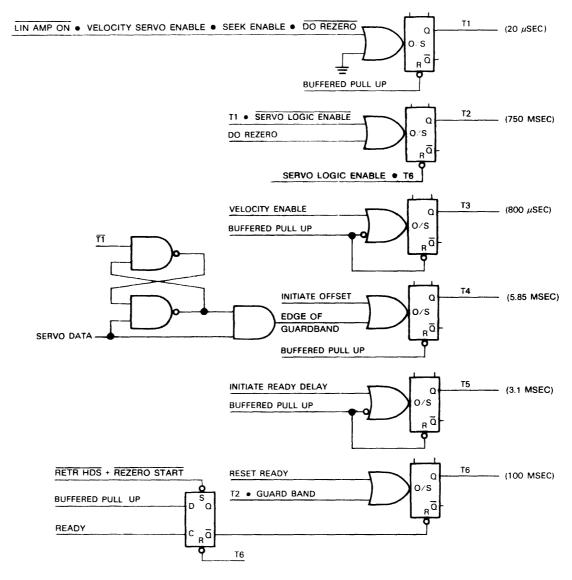

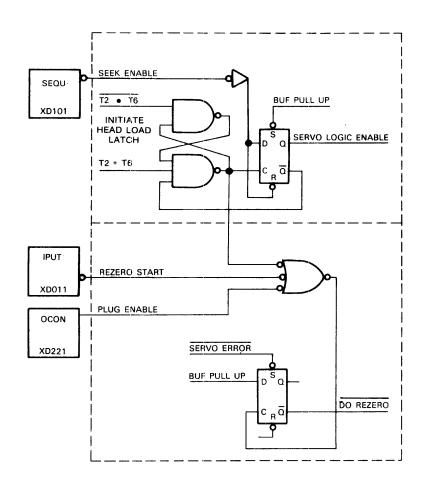

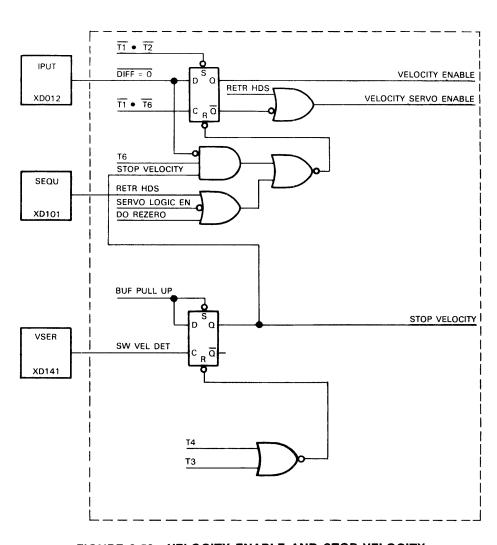

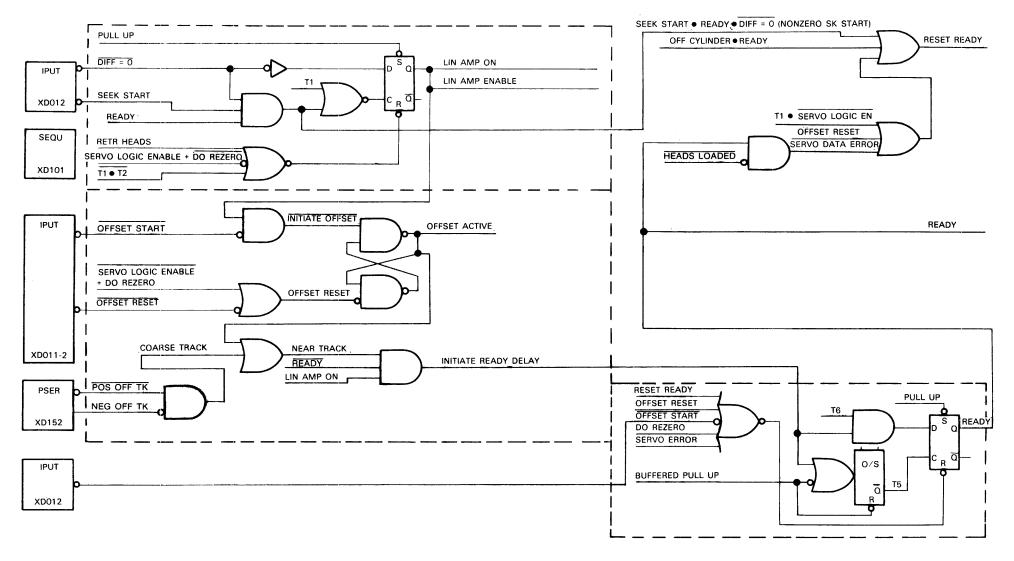

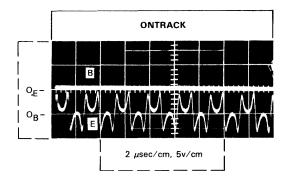

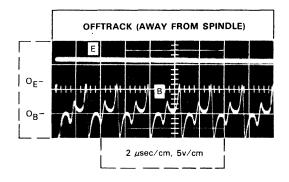

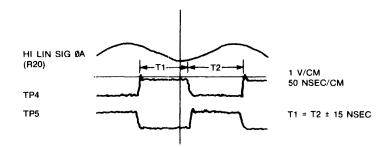

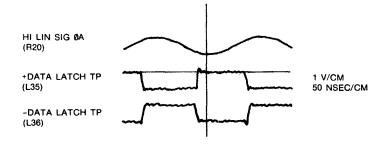

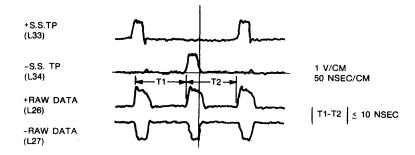

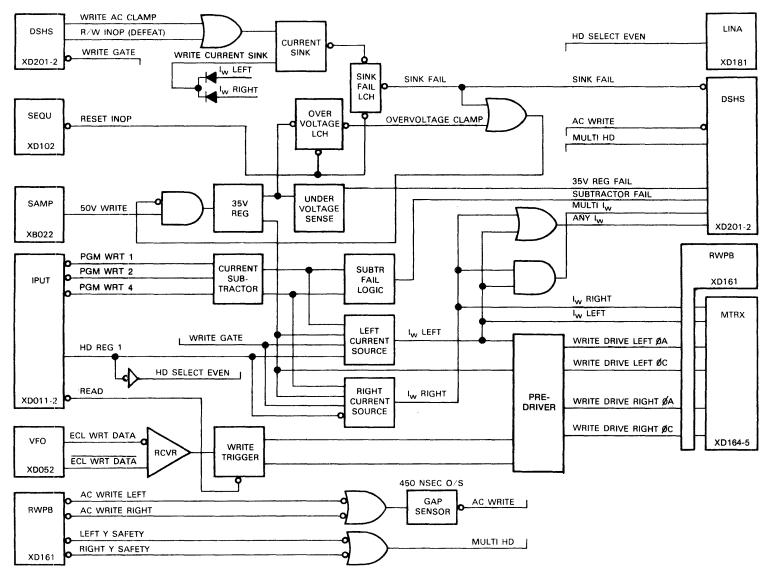

| A26<br>A28<br>A30<br>A32<br>A34 | -DIFF 2/OFFSET 50 μIN -DIFF 4/OFFSET 100μIN -DIFF 8/OFFSET 200 μIN -DIFF 16/OFFSET 400 μIN -DIFF 32 /OFFSET 800 μIN (00 MB) | A01<br>A03<br>A05<br>A07<br>A09 | -HEAD 1<br>-HEAD 2<br>-HEAD 4<br>-HEAD 8<br>-HEAD 16 |