# **COMPARISON OF IBM AND Digital STORAGE ARCHITECTURES** (including Vail)

29-March-1990

TR-9021, Storage Performance Engineering - MLDS/CXO

Abstract:

This report provides information on historical IBM storage achievements and compares the current architectures between IBM and Digital.

# **Revision/Update Information:**

**IBM 3390** VAX9000 **RA70** RA92 Aspen

Robert Bauman & Dennis Haugh-Authors

# Digital Equipment Corporation

# Preface

This document provides a description and identifies the differences in the IBM and Digital I/O subsystems from an architectural perspective. Since architectures provide a framework, the limitations of each can be validly discussed. However, actual implementations must be analyzed for valid comparison. The details within this report attempt to isolate the effects of the architecture upon the implementation.

The target audience includes Digital internal personnel only. The level of detail is intended for marketing as well as engineering.

#### ACKNOWLEDGMENTS

Special thanks is given to Tom Kinlaw and Bernie Goldstein for their assistance in the KDM70 model. Don Matthews provided the illustrations and information for the Vail model. Kathy Woodard and Bernie Goldstein editted numerous flaws in grammar and spelling.

#### INTENDED AUDIENCE

The audience is: Digital product engineering - primarily SIMG, HPS, MSB, VMS, and UL-TRIX; Digital product management and marketing; and sales support personnel. This document is for internal Digital use only; it is not intended for customers or third party product vendors.

All rights reserved.

# CONTENTS

| Preface                                                                                                          | v            |

|------------------------------------------------------------------------------------------------------------------|--------------|

| 1 EXECUTIVE SUMMARY                                                                                              | 1<br>1       |

| 1.2 Summary                                                                                                      | 1            |

| Chapter 1 IBM I/O ARCHITECTURE - SYSTEM 360 TO SYSTEM 370/ESA                                                    |              |

|                                                                                                                  | 1–1          |

| 1.1 Introduction                                                                                                 | 1–1          |

| 1.2 A Short History of IBM's I/O Architecture         1.2.1 Storage Organizations and Early Channel Architecture | 1–2<br>1–2   |

| 1.2.1.1 1954 - Drum Memories                                                                                     | 1-2<br>1-3   |

| 1.2.1.3 1957 Data Synchronizers                                                                                  | 1-3          |

| 1.2.2 System 360                                                                                                 | 1-4          |

| 1.2.2.1 Channel Developments                                                                                     | 1-4<br>1-6   |

| 1.2.2.3 I/O Interface Improvements                                                                               | 1-7          |

| 1.2.2.4 Channel Programming                                                                                      | 1–7          |

| 1.2.2.5 Count Key-Data                                                                                           | 1-8          |

| 1.2.3 System 370                                                                                                 | 1-9<br>1-9   |

| 1.2.3.1 Access Methods                                                                                           | 1-9          |

| 1.2.3.3 Channel Structure                                                                                        | 1–11         |

| 1.2.3.4 Input/Output                                                                                             | 1–12         |

| 1.3 System 370/XA                                                                                                | 1–14         |

| 1.3.1 System 370/XA - I/O Architecture                                                                           | 1–14         |

| 1.3.2 What 370/XA did for IBM's I/O Architecture         1.3.3 Input/Output                                      | 1–14<br>1–16 |

| 1.3.4 Monitoring                                                                                                 | 1-10         |

| 1.3.5 24 & 31 Bit Channel Commands                                                                               | 1–17         |

| 1.3.6 Dynamic Reconnection                                                                                       | 1–18         |

| 1.3.7 System 370/XA - Developments in Channel Path Selection                                                     | 1–19         |

| 1.3.8 Application Affects                                                                                        | 1-20         |

| 1.3.9 More On Interruption Processing                                                                            | 1–21         |

| 1.4 ESA/370 - Architecture for Modern Times                                                                      | 1–21         |

| 1.5 Disk Storage                                                                                                 | 1–22         |

| Chapter 2 DIGITAL I/O ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-1                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2–1                                    |

| 2.2 VAX Computer Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2–1                                    |

| 2.3 DSA concepts         2.3.1 System Communications Architecture         2.3.1.1 Computer Interconnect         2.3.1.2 Ethernet         2.3.1.3 Digital Storage Systems Interconnect         2.3.2 Standard Device Interfaces         2.3.3 Device Data Formats                                                                                                                                                                                                                              | 2-3<br>2-4<br>2-5<br>2-6<br>2-8<br>2-9 |

| 2.4 DSA Implementations         2.4.1 DSA controllers         2.4.1.1 Board Level Controllers         2.4.1.2 HSC         2.4.2 DSA Devices                                                                                                                                                                                                                                                                                                                                                   | 2-9<br>2-9<br>2-10<br>2-11<br>2-14     |

| 2.5 VAIL Concepts       2.5.1 Storage Element Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

| 2.6 Cache Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-17                                   |

| Chapter 3 IBM VERSUS DIGITAL I/O ARCHITECTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-1                                    |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3–1                                    |

| 3.2 Physical I/O Functional Comparison      3.2.1 Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3–1                                    |

| 3.2.2 Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3–2<br>3–2                             |

| <ul> <li>3.2.2 Analysis</li> <li>3.3 Anatomy of an I/O</li> <li>3.3.1 Host Initiation</li> <li>3.3.2 Seek</li> <li>3.3.3 Rotational Positioning and Data Transfer</li> <li>3.3.3.1 Non-realtime Transfer</li> <li>3.3.3.2 RPS Miss Quantification</li> <li>3.3.3.2.1 IBM model</li> <li>3.3.3.2.2 Digital models</li> <li>3.3.3.2.2.1 HSC</li> <li>3.3.3.2.2.3 Vail</li> <li>3.3.3.3 Cumulative Delays</li> <li>3.3.3.2 KDM70</li> <li>3.3.3.3 Vail</li> <li>3.3.4 Post Processing</li> </ul> |                                        |

| 3.4              | .1 Request Rate versus Data Rate      | 3-19         |

|------------------|---------------------------------------|--------------|

| 3                | 4.1.1 Bandwidth                       | 3-20         |

|                  | .2 Disk Data Format                   | 3-20         |

| 3.4              | .3 Caching                            | 3-20         |

| 3.4              | .4 Expanded Storage                   | 3-20         |

| 3.5 (            | Caching                               | 3-21         |

|                  | .1 Principles                         | 3-21         |

|                  | 5.1.1 Read Policies                   |              |

|                  | 5.1.2 Write Policies                  | 3-21         |

|                  | 5.1.3 Replacement                     | 3–22         |

| 3.5              | .2 IBM                                | 3-22         |

| 3.               | 5.2.1 Controller Cache                | 3–22         |

| 3.5              | .3 Digital                            | 3-23         |

|                  | 5.3.1 Host Software Cache             |              |

| 3.               | 5.3.2 HSC cache                       | 3-23         |

| 3.               | 5.3.3 Vail Cache                      | 3-23         |

| 3.6 (            | Conclusions                           | 3-23         |

|                  | .1 Digital I/O Competitive Weaknesses |              |

|                  |                                       |              |

| Append           | dix A RPS QUANTIFICATION              | A-1          |

|                  |                                       |              |

| Append           | dix B CUMULATIVE DELAY QUANTIFICATION | B-1          |

| <b>A m m m m</b> |                                       | <b>C</b> 1   |

| Append           | dix C SYSTEM TOPOLOGY                 | C-1          |

|                  | Monolithic Processing                 | C-1          |

|                  | Coupling                              | C-1          |

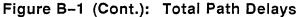

|                  | 2.1 Tight Coupling                    | C-1          |

|                  | .2.1.1 Attached Multiprocessing       | C-2          |

|                  | .2.1.2 Symmetric Multiprocessing      | C-2<br>C-3   |

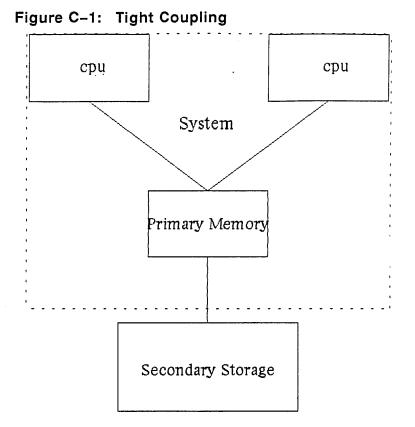

| C.2              | 2.2 Loose Coupling                    | C-3          |

| BIBLIO           | GRAPHY                                |              |

|                  |                                       |              |

| GLOSS            | ARY Gloss                             | ary-1        |

|                  |                                       |              |

| EXAMP            |                                       | 2.0          |

| 3-1              | DLSE Four 3380 Strings                |              |

| 3–2<br>3–3       | HSC RPS miss                          | 3-10<br>3-11 |

| 3-3<br>3-4       | HSC RPS with RA70                     | 3-11         |

| 3–4<br>3–5       | KDM70 RPS                             | 3-13         |

| 3-5              | SEBB Contention                       | 3-13         |

| 3-0              | HSC Cumulative Delay                  |              |

| 3-8              | KDM70 Cumulative Delay                |              |

| 0-0              |                                       | 5 10         |

|                  |                                       | v            |

|                  |                                       | v            |

|                  |                                       |              |

| 3–9     | Vail Cumulative Delay            | 3-17 |

|---------|----------------------------------|------|

|         |                                  |      |

| FIGURES |                                  |      |

| 1–1     | System/360 Channel Architecture  | 1-4  |

| 1–2     | Count, Key and Data Areas        | 1–8  |

| 1–3     | System/370 Channel Architecture  | 1-11 |

| 1-4     | 370-XA Channel Architecture      | 1–15 |

| 1–5     | 370 Channel Command Word Format  | 1–18 |

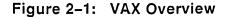

| 2-1     | VAX Overview                     | 2–2  |

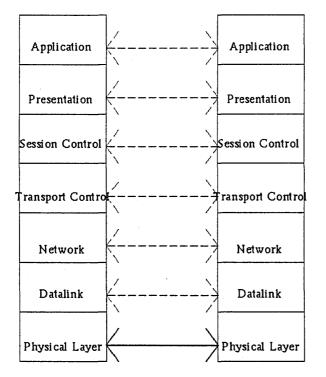

| 2–2     | ISO model                        | 2-3  |

| 2-3     | DSA Overview                     | 2-4  |

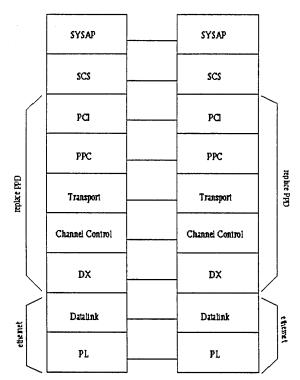

| 2-4     | SCA with Ethernet                | 2–5  |

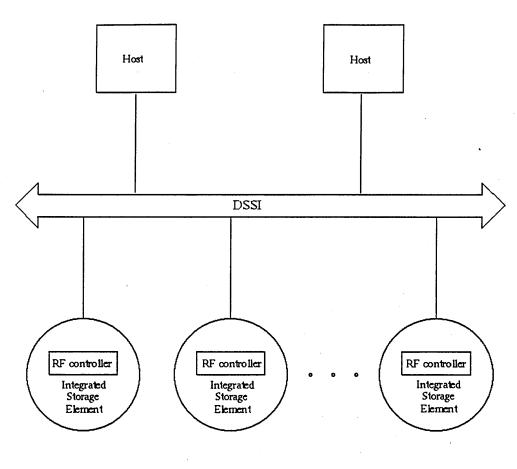

| 2-5     | DSSI Topology                    | 2–7  |

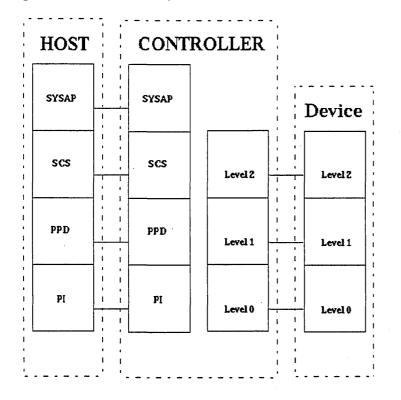

| 2-6     | SCA with DSSI                    | 2-8  |

| 2–7     | KDM70 Overview                   | 2–11 |

| 2-8     | HSC Without Disk/Tape Requestors | 2–13 |

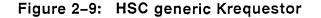

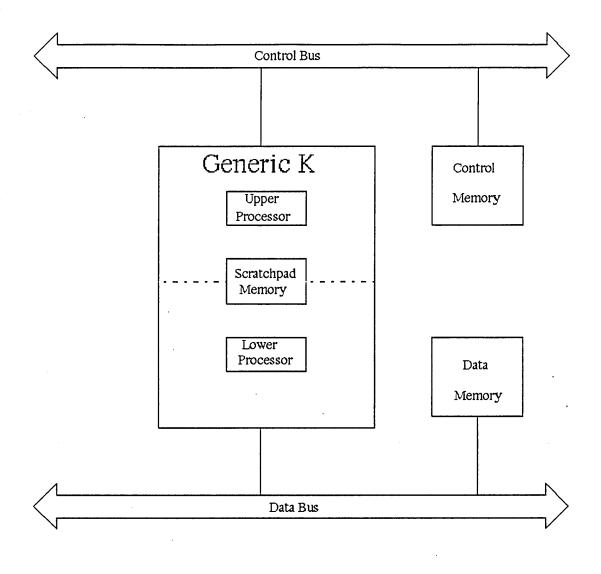

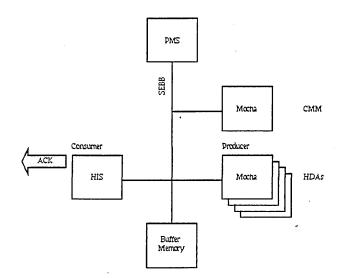

| 2–9     | HSC generic Krequestor           | 2–14 |

| 2-10    | Storage Element Overview         | 2–16 |

| 2–11    | Storage Element                  | 2–17 |

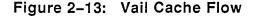

| 2-12    | HSC cache read hit               | 2–19 |

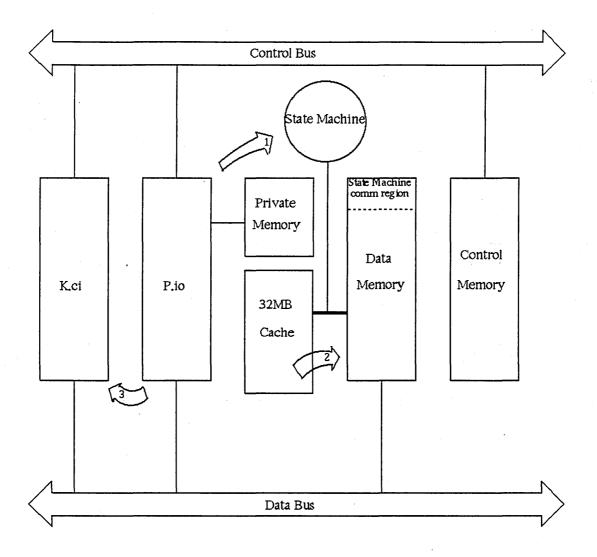

| 2-13    | Vail Cache Flow                  | 2–20 |

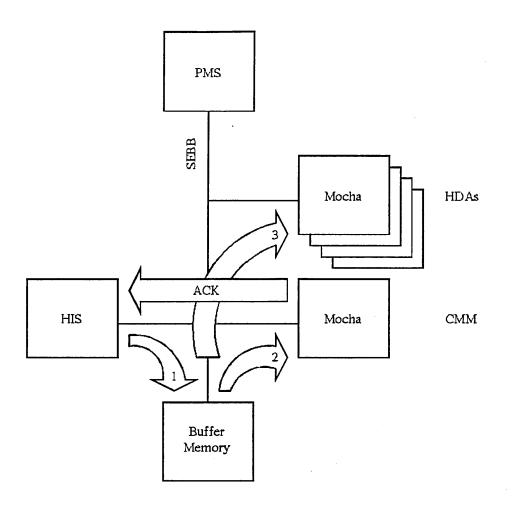

| 3-1     | DLSE vs. HSC                     | 3–3  |

| 3–2     | DLSE Controller                  | 3-4  |

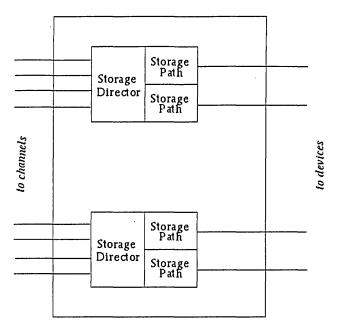

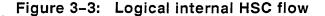

| 3-3     | Logical internal HSC flow        | 3–5  |

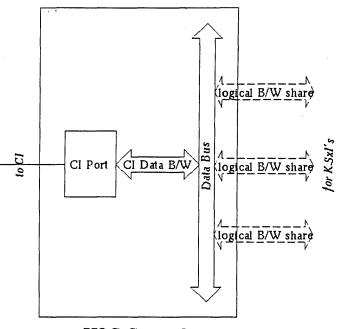

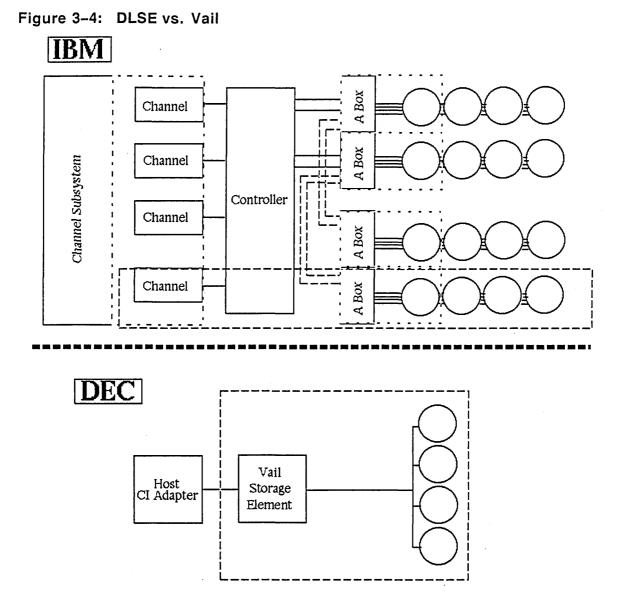

| 3-4     | DLSE vs. Vail                    | 3-6  |

| A-1     | RPS Miss                         | A-1  |

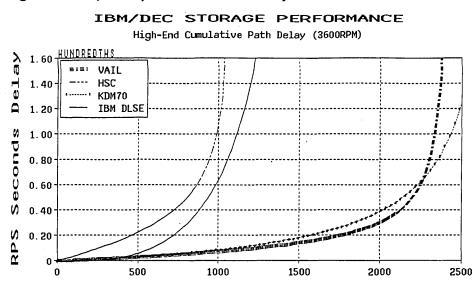

| B-1     | Total Path Delays                | B-1  |

| C-1     | Tight Coupling                   | C-2  |

| C-2     | Loose Coupling                   | C-3  |

# TABLES

| 2–1 | DSA controllers and statistics | 2–10 |

|-----|--------------------------------|------|

| 2–2 | HSC Naming Conventions         | 2–12 |

| 2-3 | DSA disk devices               | 2–15 |

| 2-4 | DSA tape devices               | 2–15 |

#### **EXECUTIVE SUMMARY** 1

#### 1.1 Scope

The purpose of this document is to educate the reader in the development of IBM's I/O architecture and to develop the ability to intelligently compare Digital to IBM I/O subsystem configurations and performance. The first two chapters of this report introduce the respective I/O architectures of each vendor. Chapter 1 describes the evolution of the IBM I/O architecture from the initial S/360 subsystem to the current 370/XA architecture. Chapter 2 introduces the various current designs of the Digital Storage Architecture (DSA).

In Chapter 3, the IBM and Digital I/O subsystems are compared at an architectural level. Device specifics are eliminated as much as possible. The delays quantified do not include seek time, rotational latency, or the queueing times produced directly by device characteristics. What remains are the delays inherent in the implementations of each architecture.

The comparative analysis is based on a set of 32 devices for the following reasons:

- IBM's DLSE groups strings such that 32 actuators are common to a set of four paths.

- Digital HSC70 can support up to 32 devices.

- Digital KDM70 can support up to 8 devices, hence 4 KDM70s are required.

- Digital VAIL model is based upon eight storage elements, each with four ASPEN actuators.

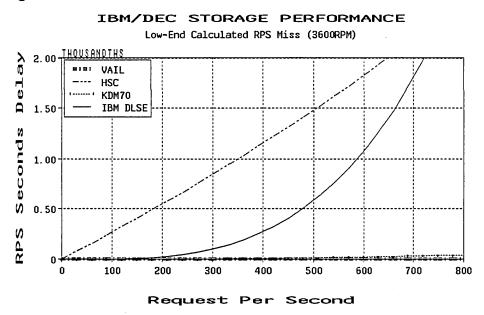

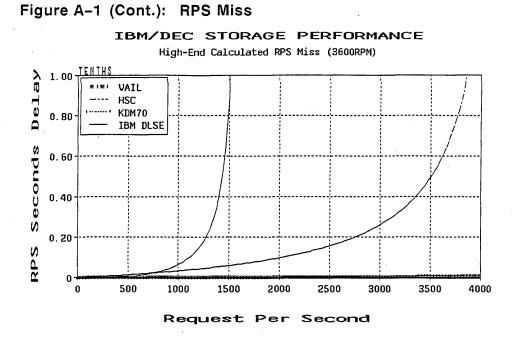

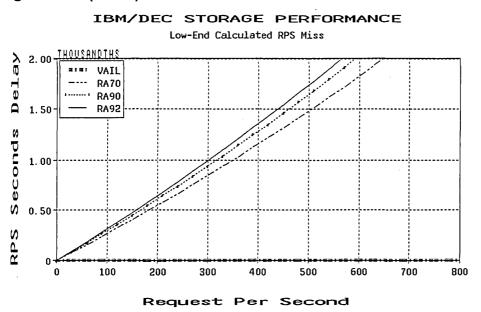

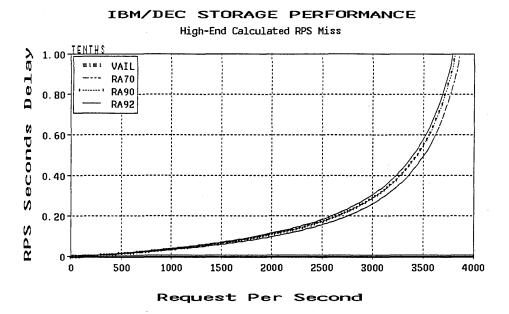

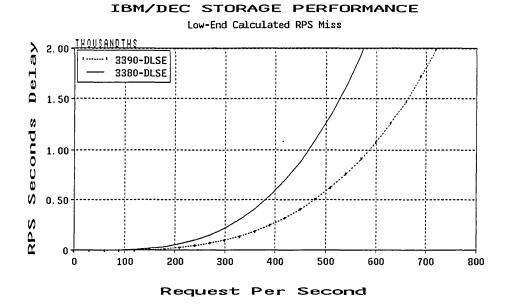

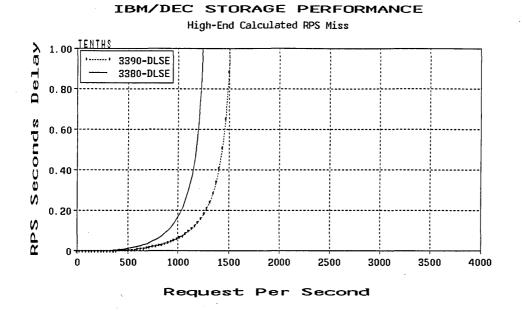

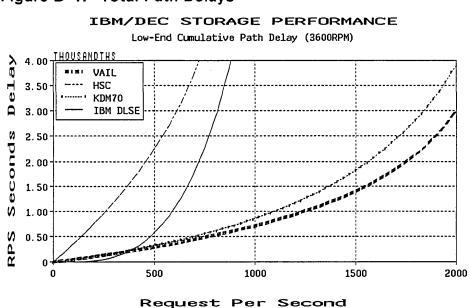

Appendix A details the effects of "RPS miss" under both architectures. RPS miss is the additional delay induced when no path to memory is available at the time the desired data is ready to transfer. Although this delay accounts for virtually all of the delays encountered in IBM's architecture, it provides only a portion of the delays in Digital implementations. Appendix B provides an assessment of the aggregrate delay for the Digital architecture. This topic is introduced in Chapter 3.

#### 1.2 Summary

The current Digital and IBM I/O architectures are built upon opposite premises. Digital has built its DSA I/O architecture as a special case of communications. IBM views communications to be a special case of I/O. In practice, both have evolved to offload the host CPU of the I/O function by use of microprocessing within the I/O subsystem. Another significant disparity between the two architectures is that IBM's primary storage performance measurement is the largest amount of data delivered in the least amount of time (throughput to response time ratio). Digital's concentration, to date, has been focused on designing subsystems which are capable of delivering the maximum number of I/O requests per second.

In the Digital I/O architecture, a single CI has become too limited. Mixing a CI subsystem with other interconnects, such as XMI in the case of KDM70, allows a more "open-ended" architecture capable of competing with IBM in the single system space. The introduction of multiple host CI ports (VAX9000) is another solution. A single CI now appears topologically similar to an IBM channel. VMS software will address the routing to and from the multiple CI ports. IBM is still ahead in that the DLSE "channel subsystem" offloads routing overhead from the host.

The lack of caching in the Digital I/O subsystem is a serious implementation deficiency; however, it is not an architectural problem. The performance of a cache can be projected by reducing the request rate for a workload to the percentage of cache misses and adding the appropriate cache overhead for hits. Host-based software cache reduces the CI utilization and improves the head-on competitive position significantly. With IBM's introduction of "fast write" neither VAXcluster Cache (VCC) nor the HSC cache are sufficient—especially for workloads with a high percentage of writes (like transaction processing). The pending SDI extension to effect "fast write" should prevent the same competitive disavantage experienced from the long absence of caching. The VAIL strategy has the added performance advantage of having a nonvolatile RAM, instead of utilizing an adhoc technique with rotating media like the SDI extensions.

IBM's expanded storage is a serious hint at IBM's future directions. Although current 3090 implementations are limited to 2 Gigabytes, the Enterprise Systems Architecture (ESA) limit is 16 Terabytes. Synchronous access to expanded storage affords the opportunity to greatly reduce overall access time delays to rotating media. Single stream performance can be greatly enhanced by a significant reduction in paging times. The use of VAX host memory with VMS global sections currently provides a competitive answer, but the architectural capacity of expanded storage could allow for loading of entire databases as well as executable images.

# CHAPTER 1

# IBM I/O ARCHITECTURE - SYSTEM 360 TO SYSTEM 370/ESA

#### 1.1 Introduction

This chapter describes IBM's I/O architecture which is defined as the features and functions of a system as seen by a programmer. This architecture will be shown to be evolutionary in nature. Looking back in time this evolution could be seen as a series of new developments for circumventing the limitations of previous generations. More accurately, it is the development of a method for performing I/O to processor external devices. This method has evolved in response to the demands placed on it by customers with growing businesses who required an architecture which could keep pace.

This chapter does not describe specific wire signals or component command streams necessary to perform I/Os. Control program (operating system) dependencies are omitted since these are outside the scope of the underlying I/O architecture. See the detailed reference materials listed in appendix (*POp1 through POp5*) for discussions on these topics. What will be covered is the historical foundation and the current 370 developments in IBM's I/O architecture.

For the last approximately 30 years IBM has continued to improve it's I/O architecture by gradually externalizing I/O management. Two versions of the architecture are implemented in the operating systems and hardware platforms marketed by IBM: System/370 and 370-XA. The fundamental structure of these architectures were initially conceived in the 1950s & 1960s and one of the objectives of this section is to explain those early developments, as well as, the 'why' of how those methods affect todays architecture. Current implementations of these architectures are:

- 937x

- AS400

- 438x

- 3090

Operating systems for these systems are:

- SAA

- VM

- DOS/VSE

- MVS

Both the AS400 and 9370 use emulator, or translator, boards to perform conversions from their internal I/O instructions to those required by the external storage devices sold with the systems. Both are basically 370 machines but the AS400 takes the layering a step further by separating applications from the underlying hardware and control program. This is accomplished by translating the generated applications into processor executable instructions at the

time of task initiation. This departure, from the typical dependency of operating systems and applications on the underlying processor architecture, allows IBM to incorporate new technology into the system package without impacting the users. In fact, IBM could place a 3090 into the core of the AS400, and the customer would be required to change nothing.

IBM's I/O architecture is general enough to handle terminal, tape, disk and forms I/O. In the case of disk, these devices are connected to and rely upon disk controllers, a physical and functional part of the Head-of-String. Disk controllers are attached to one or more Storage Control Units which direct the flow of data through storage paths. Storage Control Units are connected to channels, by way of transmission cables, which are connected to the processor. Controllers are function dependent which means that disk controllers manage disk drives, communications controllers manage their respective devices, etc. The components composing connecting I/O devices to the processor are defined in the following table:

| Device               | Function                                                                                                                                                                                                                                                                       |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| IBM Channel          | A card-on-board processor which accepts and executes Channel Programs build by applications or a component of the control program running in the CPU. Channel Programs reside in central storage. The result of a Channel Program processing is a Order for the control units. |  |  |  |  |

| Тад                  | One of two separate transmission cables which connects the channel to the control unit.<br>Maintains channel synch signalling with the CPU.                                                                                                                                    |  |  |  |  |

| Bus                  | The other transmission cable; connects the channel to the control unit and carries inter-<br>leaved byte or interleaved block data.                                                                                                                                            |  |  |  |  |

| Storage Control Unit | Receives and executes orders from channels such as 'Seek Sector 00125 on device 0125'.                                                                                                                                                                                         |  |  |  |  |

| Head-of-String       | Contains the Read and Write control logic for attached disk storage devices.                                                                                                                                                                                                   |  |  |  |  |

# 1.2 A Short History of IBM's I/O Architecture

# 1.2.1 Storage Organizations and Early Channel Architecture

Storage is and always has been a component, or subordinate of the memory system that serves the processor. Central, Expanded, Disk and other storage medias functions by inexpensively storing information which will be used to keep the processor busy. The expense is relative to how long the information will be stored and how quickly it will be needed once requested by the processor. When data is requested it is requested using some addressing scheme designed to expedite the retrieval of information. When accessing main memory a read or write instruction is directed to a specific location within the central storage complex. Accesses to disk involve an address which corresponds to a record, sector, track or cylinder assigned for data recording.

# 1.2.1.1 1954 - Drum Memories

Prior to the introduction of magnetic cores, magnetic drums were used as central storage. These drums are analogous to disk but had one head per track and rotated at about four times the speed of todays disks (*Ham1*). The IBM 650, introduced in 1954, used a magnetic drum for it's main memory. After the introduction of core memories these drums were delegated to the role of secondary storage device.

#### 1.2.1.2 1956 - Disk Storage

IBMs first disk system, the 350 introduced in 1956, organized the stored data in much the same way as it was in memory. The data was stored in fixed length words of 100 characters. Each of these words had an unalterable address associated with it which was stored just prior to the data area. When an area of the storage media was needed for data transfer the hardware performed repeated read and compare operations (Search operations) until the address was found. The processor remained disconnected during this search because the disk control unit served as the search initiator/controller. Once the address was found the data was either read or written sequentially with the controller acting as speed matching buffer by collecting the characters into a block for transfer across the channel. Speed matching buffers are used when there is a disparity between the device transfer speed and the system it's attached to.

#### 1.2.1.3 1957 - Data Synchronizers

In 1957 I/O channels were introduced with the IBM 709 processor and permitted the concurrent execution of I/O and CPU operations (*IBM1*). The channels, termed data synchronizers, acted as I/O processors with specialized I/O instruction and allowed up to six I/O devices to access the processors memory buffers. Memory access was independent of the program running in the CPU and permitted each channel to store and retrieve data directly. Instructions, executed by the CPU, coordinated functions to eliminate conflicts between the processor and channels. For each data synchronizer attached to the 709, a proportionate number of I/O devices could operate. The reason for this is that the path between the synchronizer and the storage device was busy throughout the entire operation, including seek, rotational delay and transfer.

The 709 was also the platform on which IBM's first I/O supervisory program was introduced. This I/O Control System (IOCS) eliminated the need to re-design the synchronization and control procedures when new applications were developed. In other words, previously these procedures were written into the applications using instructions built into the CPUs architecture. I/O completion was tested for by repeatedly executing loops of code which tested the data synchronizers state. With the 7090 processor (1958) IBM implemented I/O interrupts which caused the CPU to branch to an instruction sequence designed to process the interrupt. Interrupts occurred at the completion of an I/O or as the result of some unexpected condition in the storage subsystem. The importance of this development is that it eliminated the 'loops of code' which further promoted the asynchronize execution of I/Os.

Another complexity in these early systems was with the organization of data on disk devices. The disk themselves were organized into a series of fixed length sectors each with a unique address. The programmer wishing to save data on a disk drive was required to hard code the physical address of the record locations in the form of cylinder/track/record. There was no volume index or volume table of contents to protect one programmers data from being over-written by another.

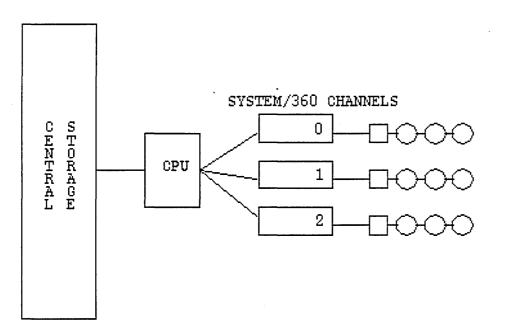

# 1.2.2 System 360

The introduction of System/360 in 1964 embodied a corporate strategy that specified that architectures and implementations would be separate. This architecture provided a general purpose structure to support varied processing demands and to work with current and future I/O equipment. System/360 standardized the aspects of I/O attachment and control by introducing a common interface, a comprehensive interruption system, storage protection, and uniform program control. The common interface prescribed the procedure and specification for attaching I/O devices and was published in an I/O architecture principles of operation (*POp5*). The following logical diagram depicts the typical System/360 organization:

Figure 1–1: System/360 Channel Architecture

This System/360 standard was the foundation for future platform and device implementations. These implementations would introduce new disk storage control units, microcode controls, disk storage devices, device allocation and storage management software. A channel subsystem, originating with the 709s data synchronizer, was designed into the system to promote concurrence with I/O and CPU operations. I/O interrupts were also taken from the 709s architecture. The System/360 I/O architecture would allow up to 256 channels, each with up to 256 devices attached.

# 1.2.2.1 Channel Developments

System/360s specification stated a reliance on DASD for storing operating system, job control routines, and data. Customer acceptance of this media as a reliable and expedient retrieval mechanism was greatly underestimated. Users soon exceeded the capabilities of the subsystem architecture to meet the throughput and response time demands. One of the limitation of System/360 channels is that they were dedicated during the execution of I/O operations. In the original implementation of the architecture to perform a read, or write, three separate operations were required: seek, search, and data transfer. During the search operation, the channel, interface, and control unit were held open while the search argument was repeatedly

passed from the channel to control unit. While performing the read/write, the System/360 could not connect through the channel to control unit path.

Another problem in early implementations of the architecture was a relative inefficiency with the Input/Output Supervisor (IOS). IOS was run in the central processor and initiated and terminated I/O operations. The IOS disabled interruptions while handling specific functions which impaired I/O. For multiplexer channels, a queue of interruptions built up as I/Os reached completion. Selector channels, which were data streaming single path pipelines, were held open and incapable of performing new operations while waiting for IOS to handle an outstanding interruption which would make the channel available again.

The following ideas were suggested to resolving the I/O problem:

- To use a large record buffer in the control unit that would hold data transferred from the device until the channel became available and then move the data to the host across a selector channel. This would result in a reduction of RPS miss accumulation and provide earlier drive availability.

- To use an I/O Processor with its own instruction set in which IOS would run and have a direct link with main storage, were the programs, data, and channel control information would reside. The functions performed by this IOP would include record blocking/deblocking, error recovery, and address translation. An IOP would also relocate the interrupt lock-out problem.

- To use a block multiplexer channel, which would offer high data rates and block interleaving along with new functionallity for the storage controllers.

The block multiplexer channel was chosen for its performance under the scrutiny of simulators and its cost of development and implementation. New functionallity for control units introduced sector addressing, which allowed the control unit to monitor DASD for a selected sector before beginning the search for the requested record. This replaced the current addressing method of cylinder and track and allowed the control unit to disconnect from the channel while waiting for the appropriate sector to become available. Reconnect then took place and the requested record was transferred to/from the channel.

The block multiplexer channel proposal required a new channel design and a new control unit. The proposed channel would posses a high data rate, and allowed a degree of multiplexing. Logical disconnection of the device from the channel would be permitted between blocks and occurs only if a significant delay is anticipated before another operation can be executed by the device.

The IBM 2880 Block Multiplexer Channel was architected to transfer data at 3.0 Megabytes per second (limited by signal and interface circuitry) while interleaving blocks of data from multiple subchannels. Subchannels are subordinate entities to the channel which act like an independently operating processor that can sustain its own channel program. Subchannels are virtual components of channels and analogously fills the role of an address space in a virtual processor. Each attached I/O device would be activated and managed by a corresponding subchannel.

The System/360 Models 85 and 195 were the first to incorporate the 2880 block multiplexer channel as a common method of attaching and programming all I/O devices. The channel was particularly suited for rotation position sensing devices. The block multiplexer channel was used with rotation position sensing, it permitted a subchannel to be assigned and a channel program to be established for each access arm, with each program monopolizing the channel

for the duration of data transfer. Channel facilities were released during arm movement and during the rotation delay associated with locating the designated record. This channel introduced a third type of channel. Each type would permit different levels of concurrence among channel programs. The following table lists the various types of System/360 channels:

| Channel           | Description                                                           |

|-------------------|-----------------------------------------------------------------------|

| Selector          | 1 Subchannel that permits one high-speed transfer of streaming blocks |

| Byte Multiplexer  | 256 Subchannels for low-speed transfers of interleaved blocks         |

| Block Multiplexer | 256 subchannels for high-speed transfers of interleaved blocks        |

### 1.2.2.2 RPS, Request Queueing & Other Channel Exploitations

RPS storage was exploited with System/360. RPS storage had to be divided into sectors. The number of sectors per track had to be fixed for each device but could vary among models. During an operation, the 1-byte sector number was sent to the DASD by a new command called SET SECTOR. When it received the sector number, the control unit logically disconnected from the channel until the desired angular position was reached or was about to be reached. Reconnection was then attempted. Monitoring was performed by the disk device with the control unit communicating the disks status with the requesting channel. During disconnection the channel was free to initiate request of attached devices and the control unit was available to accept request from the channel, hence multiplexing. The sector number could be obtained in two ways: When the records on the track are of a fixed length and format, the sector can be derived from the track capacity and the sectors per track. Alternatively, when a record is read, written, or searched, its sector can be derived by a READ SECTOR command.

During SEEK operations similar events took place. After the device was instructed to position the read/write heads the control unit would disconnect from the channel. The I/O channel was then free act upon work for other devices and the control unit became available to handle work for other attached disks.

The request queueing facility of the IBM 2305 used the block multiplexer channel and the rotational position sensing concept by allowing up to eight operations to simultaneously process for a single device. The device was assigned eight device addresses to which operations could be arbitrarily directed. The control unit for the 2305 effectively sorted these operations so that they were handled in the order their respective sectors became ready.

IBM also introduced the dynamic channel selection facility on the System/360 Model 67. The Model 67 was a two processor CPU complex which required that specific channels be dedicated to specific CPUs or that the channels could float. Operating in an extended problem state this system could access all channels and accept I/O interruptions on either of the two system processors. Sounding remarkably like components of the 370-XA architectural specification these facilities were not promoted in System/370.

#### 1.2.2.3 I/O Interface Improvements

The I/O interface also required improvements to support the demands of the block multiplexer channel. The I/O interface connects a channel and an I/O control unit and it provides physical and electrical specifications. The original System/360 I/O interface specification was adequate for data rates up to about 1Mbyte/sec for a 100-foot cable. For 20-foot cables the IBM 2301 Drum Storage, with a rate of 1.2 M Bytes per second could be accommodated. Fully interlocked signalling allowed one channel cable connection to sustain data transfer over a range of rates, with both channels and devices controlling the timing of each byte transferred. It did, however, require an electrical signal to be propagated between the channel and the control unit four times for each byte transferred.

Block multiplexer channels, in order to meet the required through-put, required 2 bytes more data transfer capacity and a tightening of the electrical specification for signalling. These improvements were introduced in June, 1970 with the first implementation of the System/370 in the models 155 and 165.

#### 1.2.2.4 Channel Programming

Early I/O devices were accessed and controlled by the CPU (*BUC1*). The CPU instruction set contained specific operation codes for operating and controlling the device. The System/360 and System/370 architectures took these instructions out of the CPU and gave them to smaller special purpose processors - channels. Channels have their own set of instructions, known as channel commands, which are stored in central storage and are fetched, decoded and executed by the channel in association with the target I/O device. The CPU starts the I/O operation by issuing an instruction which gives the first address of the first channel command. Since the specialized I/O commands had been moved off the CPU then only one instruction was required for all I/O operations. The op code of the instruction specifies that the channel should asynchronously Start I/O (SIO).

This method of I/O control is known as channel programming and involves the set-up of a sequence of commands for a channel to execute. The Start I/O (SIO) CPU instruction initiated the channel to find the list of channel commands (CCWs) to execute. These commands direct the channel to the result required by the application; such as read a record. Three key fields are involved:

- Channel Address Word (CAW)

- Channel Status Word (CSW)

- Channel Command Word (CCW)

System/360 removed the I/O subroutine address from the instruction and placed it into a fixed memory location termed the Channel Address Word. This word had to be loaded with the correct subroutine address prior to the execution of the Start I/O operation. What this accomplished was that it allowed I/O devices, their instructions, and the channels controlling the devices to change without affecting the CPUs architecture. The CSW was used to contain channel status information. Execution of an SIO led to an "initial interrupt" where the CSW was queried to ensure the channel was accessible. The CSW also was used to contain the completion status for an I/O operation. The CCW provided both the commands—like read and write—and the data pointers for the channel to process. Execution was sequential from the initial CCW pointed to by the CAW unless a Transfer In Channel (TIC) command was encountered to effect a branch.

# 1.2.2.5 Count-Key-Data

Another introduction with System/360 was the disk allocation methodology known as Count-Key-Data. CKD organization was introduced with IBM first microcode based storage control unit the 2841. The 2841 control unit provided device dependent interpretation of channel commands and would adapt to the disk record format specified in the 360 architecture. CKD is the method employed by IBM to implement Store Addressing Information (*MAT1*) which permits record level granularity when accessing data.

For example, a physical track can hold as much as 56KBytes of data, but most application records are significantly smaller. In order to directly access these smaller records some greater degree of granularity is required. To implement the finer addressing at the disk level requires that the algorithm be incorporated into both the I/O architecture and the systems access methods. Store Addressing Information is simply a defined address stored on the disk in predefined areas designated by gaps that contain special codes. Logic circuitry into the controllers sense the gap codes and repeated compares can be done until the specified record is located. Since the Store Addressing Information can be in any of the various gaps, between physical sectors, the track can be logically divided into fixed or variable length records each of which contains addressing information in it's header. A significant difference between CKD formatting and FBA is that the former permits the physical record length to be determined by the application allocating the space for storage.

With CKD formatting each record contains a count, key and data areas. The count area holds the physical cylinder, head and track relative record number along with the length of both key and data areas. The optional key area can contain a record index and is used by the control unit to automatically locate the record during SEARCH operations. The data area contains a record limited in size by the data capacity of the track. The following illustration outlines CKD formatting:

| FLAG | Cyl i Nder<br>Numb | HEAD<br>NUMB |   | data<br>Length | CHECK | KEY AREA<br>0-256 bytes | GAP | DATA AREA<br>0-47476 bytes |

|------|--------------------|--------------|---|----------------|-------|-------------------------|-----|----------------------------|

|      |                    | ID           | ] |                |       | KEY                     |     | DATA                       |

Figure 1-2: Count, Key and Data Areas

COUNT AREA

# 1.2.3 System 370

From the standpoint of I/O, if one thing could be said about the System/370 permutation of the architecture it would be that it was an extension. System/370 added to and improved upon the initial conception of what the I/O design should contain. In 1962, IBM knew that the interruption mechanism and the I/O control formats did not have the required extensibility needed for an evolving architecture. However, costs and performance consequences prevented them from improving the System/360 platform. With the improvements in hardware technology during the late 60s, these facilities became feasible. System/370 was an evolutionary extension of the System/360 architecture for a new set of models and for new releases of programming systems. The objectives of the architecture were:

- Eliminate bottlenecks

- Improve efficiency

- Attach to and operate System/360 I/O devices

The architecture would accomplish this by incorporating the following extensions to System/360s foundation:

- Block Multiplexing

- Command retry

- High-Speed data transfer

Bottlenecks existed in the data request facilities and in the ability of the I/O subsystem to deliver that data expediently. These problems would be addressed by incorporating additional data access methods in the system design. Channels and I/O interfaces posed difficulties; processor speeds were outpacing the ability of the storage to deliver data. New controllers were needed to fully exploit the benefits of microcode-controlled storage directors and the inherit efficiency of Count-Key-Data. In essence the new architecture would bring the complex components back into balance with each other while protecting existing customers investments in subsystems hardware.

# 1.2.3.1 Access Methods

Even though this is a departure from the prescription of outlining architectural developments the subject of access methods is important because they eliminate dependency on the design specification. System/360 introduced a series of facilities which allowed users to eliminate the hardcoding of stored data addresses (cylinder, track and relative record) from their access routines. System/370s involvement in this was to standardize by incorporating them into the architecture and to remove the requirement that programmers understand the physical geometry of the storage devices. This information is still used, the programmer is simply insulated from it. The access methods introduced with System/360 were (*CLA1*):

| Acronym | Definition                       |  |

|---------|----------------------------------|--|

| BDAM    | Basic Direct Access Method       |  |

| BPAM    | Basic Partitioned Access Method  |  |

| SAM     | Sequential Access Method         |  |

| ISAM    | Indexed Sequential Access Method |  |

Both the Basic Partitioned and Indexed Sequential Access Methods were new while the others were improvements on hard coded access routines already available. BPAM was designed to eliminate the CKD allocation inefficiencies of small record length datasets; multiple files of 80 byte records could be organized under a single file structure. ISAM was designed to utilize the Index area of the CKD. Both BPAM and ISAM handled the translation of the logical record identifier to a physical address (Cylinder, Track, Record) on disk.

These access methods replaced macro functions in IBMs initial I/O supervisor (IOS). The IOS had disk management functions which were basically an extension of those used for tape (SAM). It did provide for the management of buffers and the blocking of logical records to physical tracks. BDAM allowed for direct access but required that the application provide the physical address of the record(s) by transformation of the logical record identifier to the physical device address before calling IOCS (*BUC2*).

# 1.2.3.2 I/O Interface

The original System/360 I/O interface specification was adequate for data rates up to about 1 Mbyte/Sec. In special cases for disk devices and for very short cable lengths, a rate up to 1.25 Mbytes/Sec could be supported. Storage technologies employing higher recording densities and buffered devices required higher rates. This required an electrical signal to be propagated between the channel and the control unit four times for each byte transferred. 360 changed the width of the interface and the interface signalling to assist in the expansion of these data rates. Fully interlocked signalling on the I/O interface allowed one channel cable connection to transfer data at a range of rates; both the channel and device controlled the timing of each byte transfer (*AD01*).

The 2880 Block Multiplexer Channel introduced with the System/360 Models 85 and 195 implemented these signalling improvements. The System/370 I/O interface introduced two additional tag wires (*3601*) to provide the same level of transfer interlocks with only two propagation times per byte transferred. Depending on the control unit this facility allowed for the migration of System/360 I/O devices to System 370 processors. Control units implemented to operate with the System/360 interface can be attached to System/370 channels. On some System/370 channels and control units the bus cable width could be extended optionally to two bytes, doubling the data transfer capacity. As a result of these two additions, the System/370 I/O interface could sustain a data transfer rate of over 1.5 Mbytes/Sec in the 1-byte version and over 3Mbyte/Sec in the 2-byte version, over a 100-foot cable (*DTB1*). Longer cables had to sacrifice transfer speed.

The cable modification added two wires to the tag interface to provide the same level of transfer interlocks at the expense of only two propagation times per byte transferred. The facility used depends on the control unit, so that control units implemented to operate with the System/360 interface can be attached to System/370 channels. The basic bus interface is 1 byte wide comprising 8 data bits and 1 parity bit. On some System/370 models, the bus width can be extended optionally to 2 bytes, thus doubling its data transfer capacity.

The data streaming mode, introduced with the IBM 3380 Disk Storage, further eliminated the interlocks between the request and response signals during data transfer. Data, with the appropriate tag signals, were sent in the form of fixed length pulses. (3601). Thus, the data rate no longer depended on cable. The IBM 3380 specifications provided a transfer rate of 3M bytes per second over 400 feet with the 1 byte interface.

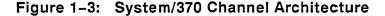

#### 1.2.3.3 Channel Structure

In System/370, a single physical path usually exists between a channel and the attached control units. The IBM 2870 channel is an exception with five paths to attached control units. The physical path is referred to (and still is in 370-XA) as the System/360 and System/370 I/O interface. In System/370, communication between the channel and I/O device occurs by using a subchannel, the physical path, and the control unit. Communication between another channel and the I/O device requires a different subchannel, physical path, and control unit (or the same control unit when a two-channel switch is used). The need for separately identifying the physical path is unnecessary; therefore the term channel also implies the physical path. A channel is distinguishable from another channel by three characteristics: a unique address, a separate set of subchannels for attaching up to 256 I/O devices, and a connected CPU.

In System/370, the channel-to-CPU interface is uniprocessor oriented. Channels are provided in sets attached to a CPU. A System/370 channel can be addressed only by the CPU to which it is connected. Also, a System/370 channel can interrupt only that CPU to which it is connected. In a System/370 multi-processor (MP) system, each CPU has its own set of channels. Thus, the operating system in an MP system must ensure that the correct CPU performs I/O operations with I/O devices that are not attached to channels on each CPU. When a program initiates an I/O operation, the path over which the operation is to take place is specified as part of the START I/O or START I/O FAST RELEASE instruction. The I/O operation either is initiated on that path or is not initiated. If the operation is not initiated, the program is notified, and the program may initiate the operation on a different path to the device, if one is available. The following diagram illustrates the layout of 370 I/O:

The channel-to-I/O device interface is single path oriented in another way. Once a chain of I/O operations is initiated with a device, all data, status, and commands for the chain of operations must use the physical channel path over which the first command was initiated (*IBM1*). In particular, if a device disconnects from the channel path during a chain of commands, as when block multiplexing occurs, the device must reconnect to the same path to continue

executing that chain of commands. If the path to which the device must reconnect is in use when the device is ready to reconnect, the device must wait until the path is free before it can reconnect to continue execution.

# 1.2.3.4 *Input/Output*

System/370 architecture adds several facilities and functions to input/output (I/O) operations to improve channel utilization, to make control operations more efficient and flexible, and to increase the maximum data rate on the I/O (channel-to-control-unit) interface. This section discusses some of the more important additions.

The System/360 architecture provided for two channel types: a selector channel, and a byte multiplexer channel. The development of the block multiplexer channel for the System/360 Model 85 and 195 and its subsequent standardization in the System/370 architecture added both a high data rate and multiple-device capabilities.

The block multiplexer channel is similar to the byte multiplexer channel in it has a number of subchannels, each associated with an I/O device or a group of I/O devices. The subchannel is the logical entity that controls an I/O operation and contains the addresses, count, and control bits associated with the operation. The channel provides the data paths and controls for communicating with the CPU, main storage, and I/O control units and for associating the proper subchannel with each communications sequence. The difference between the block and byte multiplexer channels is in the level of multiplexing. The byte multiplexer channel can interleave the transfer of individual bytes for different subchannels. However, the block multiplexer channel, designed for high data rates, is limited to interleaving complete blocks of data.

The block multiplexing capability is advantageous when used with rotational position sensing on rotating storage devices, such as disks and drums. The device disconnects from the channel during rotational delay, thereby releasing the channel. When the addressed sector is approached on the track, reconnection is attempted for the transfer of data. If the connection cannot be established when the sector is reached, another attempt is made after a delay of one rotation time. Rotation position sensing is available, for example, on the IBM 2305 fixed head file server (*3602*). The control unit for this file can appear to have 16 devices, each associated with its own subchannel which can sustain an I/O operation.

Without the block multiplexing capability, I/O facilities required separate START I/O instructions to specify the position of the arm on the disk and the subsequent reading and writing. On the block multiplexer channel, these commands are chained. Thus, the CPU is not interrupted when positioning is complete and the number of instructions is reduced.

Because the block multiplexer channel transfers blocks of data during CPU operation, a new interruption, the channel available interruption, was required to indicate when the channel was free to process a new request. The block multiplexer channel generates this signal when the busy condition no longer exists. The signal is sent to the originating CPU.

A HALT DEVICE instruction also is introduced largely because of the block multiplexer channel. It is similar to the previously available HALT I/O except that, when the channel is busy, only the operation on the addressed subchannel is affected. HALT I/O terminated the current burst operation on the channel and ignored the device address. The new CLEAR I/O instruction permits freeing the subchannel associated with the addressed device while I/O operations take place at the device. This function is useful for situations involving machine error or reconfiguration of I/O devices and control units.

Finally, an extension is provided to reduce the CPU time to start an I/O operation. When START I/O (SIO) is issued, the channel signals the device to check if the device can execute the command. This involves a number of signal sequences and the associated propagation delays and logic delays in the channel and the control unit (*POp5*). According to the I/O interface specification the portion of the total delay introduced by the circuitry in the control unit can be as high as 32 microseconds. Additional delays may be introduced by the channel. On a CPU that can perform a few million average instructions per second, the delay from communications with the device can equal a hundred or more instruction executions.

The new instruction START I/O FAST RELEASE (SIOF) (*POp2*) allows the acceptance to be signalled and the CPU to be released as soon as the channel has fetched the channel address word from main storage. The channel subsequently initiates the operation at the device and verifies the command information. Exceptions are signalled by interruptions. Normally such exceptions are infrequent and overall little time is spent processing the interruptions. Some channels, available with early 370 processors and on current 9370 processors, implement the early release on SIOF and instead execute SIOF as SIO. Such implementations are compatible and permit the same program to run with either channel developments.

Most System/370 channels provide the command-retry facility, whereby the channel, in response to a signal from the device, re-executes a channel command. This re-execution is usually invoked when the device or control unit detects a malfunction.

# 1.3 System 370/XA

# 1.3.1 System 370/XA - I/O Architecture

The first IBM processor product to implement the 370/XA architecture was the 3081. The 3081 Processor increased the I/O channel capability with two central processors. Each processor accessed channels and central storage by a single system controller. This direct path to central storage permitted dynamic reconnection and eliminated the need for channels to reconnect to the CPU to which they were attached. The system controller moved data between the channel subsystem and central storage, and into the 32K-byte buffer associated with each central processor (*RNG1*).

The 3081 supported up to 24 channels, which were either byte multiplexer or block multiplexer type. A maximum of four byte multiplexer channels could be configured within the 3081 processor complex, each having an aggregate data rate of up to 500K bytes per second with a burst size of 32 bytes. All block multiplexers had data streaming capability that permitted data rates up to 3M bytes per second per channel. Channels were assigned in two channel sets, one for each central processor, with a maximum of 16 channels per set.

Channels were controlled by the external data controller, an integrated I/O processor within the 3081 processor unit. The external data controller consists of two types of microcode controlled elements.

- The channel processor element (CPE) is a special processor which controls I/O instructions and interrupts. It supports a queued interface with the central processor for START I/O FAST RELEASE operations and for I/O interrupts, and handled command/data chaining and all external data controller recovery operations. The channel processor element is driven by vertical microcode having a 2-byte microword and an addressing capability of 32K microwords. A 2K-microword write-able static array contains the most frequently used microwords. A second 256-microword array contains 4 blocks of 64 microwords each. The array is dynamically loaded on demand from a hardware system area located in a portion of central storage. The processor has a 2-byte data path structure and is packaged in one thermal conductor module (TCM) (*RNG1*).

- The data server element (DSE) handles the control sequencing and data buffering for eight channels. It is packaged on a single TCM, and a maximum of three Data Server Elements can be attached to the CPE. The Data Server Element contains 256 bytes of data buffering per channel. It supports 2-byte transfers with the interface adapters and 64-byte transfers with central storage. The DSE is controlled by horizontal microcode having a 54-bit microword in a 750-microword array. The eight channels are controlled by DSE microcode that is time-shared on an equal round-robin basis. Outboard of the DSE, packaged in a card-on-board technology, each channel has an interface adapter element which drives the I/O interface and contains eight bytes of data buffering.

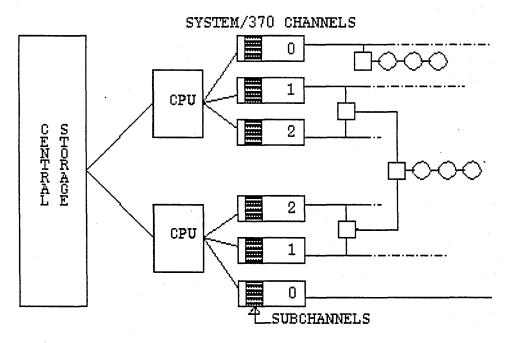

# 1.3.2 What 370/XA did for IBM's I/O Architecture

370-XA replaced the System/370 I/O functions with a structure that moved I/O management out of the CPU with a completely queued interface between the CPU and the channel subsystem. The 370-XA architecture increased the performance of the large scale systems and structured the I/O architecture to take full advantage of the 3081 and subsequent tightly coupled multi-processors. The 370-XA channel subsystem allows CPUs the same access capability for all devices attached to the system. The subsystem became a separate component of the processor complex. I/O devices were attached to the Subsystem, rather than to the CPU, as in System/370. This removed the limitation of CPU's initiating I/O functions and accepting interrupts, only to those devices to which they were physically connected. The new architecture allowed any I/O function to be initiated with any I/O device, regardless of the CPU executing the I/O instruction or the physical attachment of the I/O device to the channel subsystem. The channel subsystem was not identified by an address, and permitted attachment of enough I/O devices to correspond with 256 System/370 channels. However, all of the I/O devices attached to the channel subsystem were represented by a single set of subchannels. These characteristics present the appearance of a collection of channels, or what is termed a "channel subsystem." The following illustration shows the 370-XA structure:

The separation of the channels from direct CPU control allowed the following prominent features:

- The channel subsystem architecture allowed devices, like the 3380-AA4, to dynamically reconnect to a free path.

- In 370-XA all I/O busy conditions were handled by the channel subsystem rather than by the CPU program, as in System/370.

- In 370-XA, alternate path are scheduled by the channel subsystem rather than by the CPU program.

- In System/370, channels must be handled by type; that is, there are differences in program action depending on whether a device is attached to a selector channel or a multiplexer channel. In 370-XA, the type of channel path used is not apparent to the CPU program.

- In 370-XA, eight different physical paths can be used when communications takes place between a single subchannel and an I/O device.

• In 370-XA, any CPU in the system enabled for I/O interruption can accept an interruption from any subchannel.

#### 1.3.3 Input/Output

Communication between the control program and the channel subsystem regarding an I/O device depends upon the use of a subchannel number. The channel subsystem and the I/O device communicate by using a device address. The subchannel number identifies the target subchannel during the execution of I/O instructions and during the handling of I/O interruptions. The device number is assigned during installation of the I/O device and bears no relationship to the physical attachment of that I/O device. Compatibility of addressing between the channel subsystem and the I/O device has been maintained from System/370 to 370-XA since the device number is still used in 370-XA for administrative or operator communication purposes. Separating device number and device address allowed customers complete freedom when assigning device numbers.

In 370/XA, each I/O device is assigned to a different subchannel. Architecturally the device number has no relationship to the device address used in the communication path between the channel subsystem and the I/O device or the channel path to which the I/O device is physically attached. Consequently, physical addressing changes can be made between the channel subsystem and the attached I/O device, without impacting the control program. Subchannel numbers must be assigned in contiguous ascending order, starting with zero. This presents a problem in multiple system installations with shared DASD because it removes what might otherwise be a convenient system unique identifier.

The channel subsystem, during initiation of an I/O function, tests the availability of channel paths to the associated I/O device. The testing result reports one or more available channel paths. One of these paths is selected during initiation of an I/O function. If a busy condition occurs, an alternate path, from the set, is chosen. If another busy condition occurs, another path is selected if one is available. This function is performed without the involvement of the control program.

I/O interruption requests from individual I/O devices can be assigned to any one of eight maskable interruption subclasses. In effect this created interruption subclasses assigned to I/O devices. Masking of these subclasses is provided by use of a control register in each CPU. Subclass assignments are made to each subchannel during the execution of MODIFY SUBCHANNEL. Under System 370, a similar feature was designed into the channel sub-system. However, all of the attached I/O devices (to 256) were likewise being masked. In 370-XA, assignment of subclasses to subchannels provides greater flexibility in controlling I/O interruptions from I/O devices. For example, a software-controlled priority-interruption methodology can be employed where only the lowest priority programs are executed with all subclasses enabled, and successively higher-priority programs are executed with fewer subclasses enabled. As a result, low-priority programs can be interrupted by all I/O devices, but high-priority programs can be interrupted by only a few devices (*POp3*).

#### 1.3.4 Monitoring

The monitoring of the channel subsystem provides I/O resource usage data in the form of measured information maintained in central storage. This information is available to the Resource Management Facility (RMF), which assists in managing the performance of the system. The RMF also performed this function in System/370; however, most of the information was obtained through sampling techniques that examined the delays or busy conditions encountered by the control program while attempting to initiate I/O operations. A monitoring facility in 370-XA was added because of the changes to the internal interfaces of the control program and because the I/O queue management and busy-handling functions were moved into the channel subsystem. The monitoring facility provides measured elapsed time parameters in main storage that described the extent of I/O resource usage, delay time, and I/O contentions encountered during execution of I/O operations. The data is accumulated on a subchannel basis and made available as each operation completes.

The instruction SET CHANNEL MONIFOR places the channel subsystem in the monitoring mode and identifies the starting location, in main storage, where the measured data is accumulated. Control bits provided by the control program and placed in the subchannel during execution of the MODIFY SUBCHANNEL command selectively enable or disable a subchannel for monitoring.

#### 1.3.5 24 & 31 Bit Channel Commands

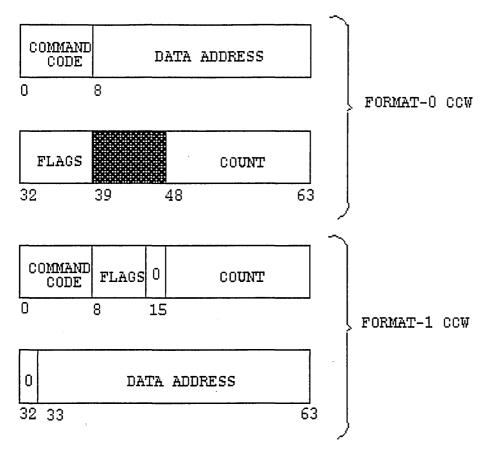

A 31-bit data address in a new CCW format allows for the direct use of 31-bit addresses in channel programs. In System/370, 31-bit addressing of I/O data can only be accomplished by use of the Indirect Data Address Word (IDAW), and all CCWs and IDAWs must reside in the first 16M bytes of storage. In 370-XA, two modes of operation are provided: a compatible 24-bit addressing mode for executing old CCWs (Format-0 CCW) and a 31-bit address mode for executing the new format CCWs (Format-1 CCW). When Format-1 CCWs are specified, the CCWs and IDAWs may reside anywhere in storage. The mode is controlled by a bit passed to the channel subsystem during the execution of the START SUBCHANNEL instruction. In 370-XA, depending upon the setting of the control bit, direct addressing in either the 24-bit or 31-bit mode applies for the entire channel program being executed. Mixed CCW formats within a channel program are not allowed. The two CCW formats are illustrated as follows:

Figure 1–5: 370 Channel Command Word Format

The indirect-data-address word (IDAW) was extended to 31-bits when 26-bit real addressing was introduced in the system/processor architecture prior to XA. At the time this was the only way the channel could access data beyond the 16-Mbyte limit. The 31-bit format IDAW is now also used in 370-XA for application compatibility. 370-XA also introduced a new channel command word format called Format-1, with a 31-bit data address field. The address formats used in I/O operations are subject to and subordinate to the addressing mode specified in the address space PSW.

The 370-XA channel subsystem architecture executes CCWs that were defined for System/370, as well as the new Format-1 CCWs. Regardless of the format of the CCWs, the same channel and control unit operations can be executed. The portions of the architecture dealing with the initiation of I/O operations and with the I/O interruption mechanism were changed extensively from those implemented in System/370.

# 1.3.6 Dynamic Reconnection

The dynamic reconnection facility allows an I/O device to reconnect to any available path to continue execution of a chain of commands in a channel program. The instruction MODIFY SUBCHANNEL (MSCH) describes to the subchannel, by means of mask bytes, the set of available channel paths. This facility is controlled by a mode setting (multipath mode) in each subchannel. The MSCH instruction is also used to enable and disable the dynamic reconnection ability. The control program IOS reports the set of available channel paths for which reconnection is permitted to the I/O device. This capability, together with the channel

path management capability, allows the channel subsystem and I/O devices to chose the first available path to initiate or resume execution of a chain of I/O operations.

### 1.3.7 System 370/XA - Developments in Channel Path Selection

In System/370, I/O operations are initiated by the START I/O instruction, which identifies the channel and the device address on the specified channel. START I/O causes the channel to fetch the channel-address-word (CAW) from a fixed location in real storage. The CAW contains the subchannel key and designates the location in storage from which the channel subsequently fetches the first CCW. If the specified channel is busy at the time START I/O is executed, the operation is not initiated and the program is notified. If the specified channel is available, the CPU is delayed while the channel attempts to initiate the operation at the device. The length of time required is determined by the I/O device and, in some cases, may be more than 100 microseconds. While attempting to initiate the operation at the I/O device, the channel may receive a control-unit-busy indication, in which case the operation are connected to the device, the program can repeat the procedure, specifying a different channel in the instruction. In this instance, multiple control-unit-busy indications are possible, with a resulting CPU delay.

The START I/O FAST RELEASE function was introduced with System/370 to reduce CPU delay in initiating the operation at the device. This function allows the CPU to execute the next instruction as soon as the channel is available. Thus, processing continues while the channel, in parallel with the CPU, attempts to initiate the operation at the device. On encountering a control-unit-busy condition, the channel notifies the program with an I/O interruption so that operation initiation can be attempted on an alternate path. In some configurations, the additional processing to handle the interruptions reporting control-unit-busy more than offset the gain from the START I/O FAST RELEASE function. As a result, the function was modified to cause the CPU to wait until the control unit was engaged before the CPU could execute the next instruction. Since the time required to determine a control-unit-busy condition is less than the time to initiate an I/O operation, the START I/O FAST RELEASE function.

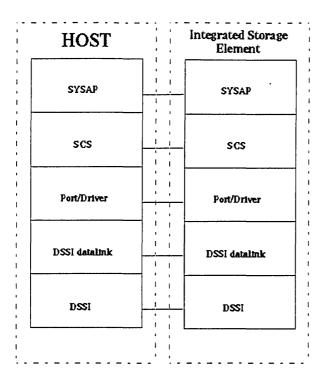

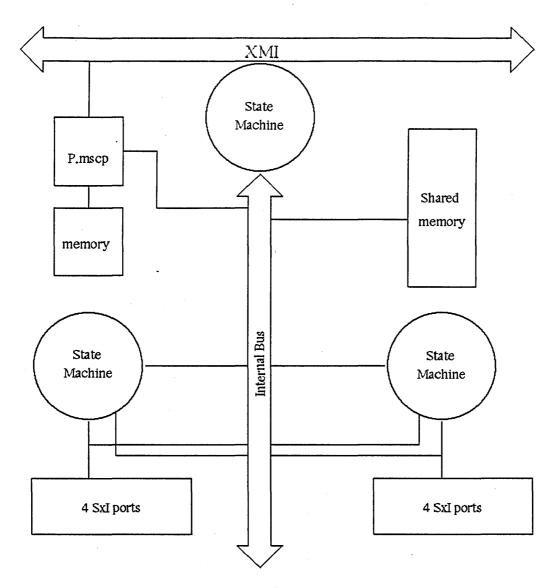

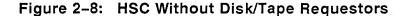

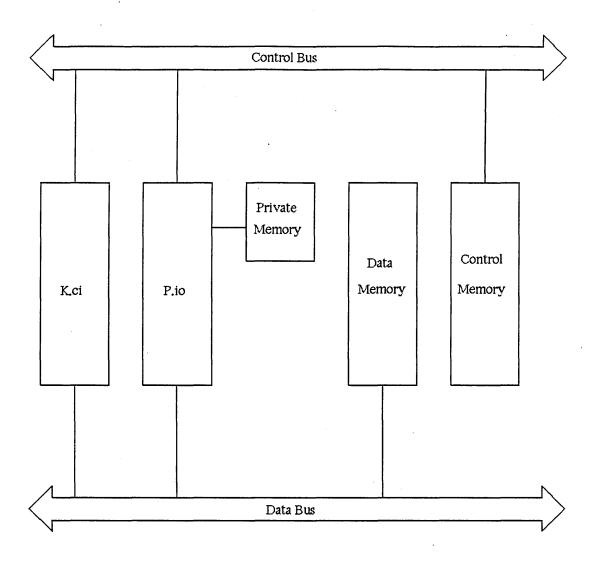

START I/O FAST queueing was introduced for System/370 as a result of the control-unitbusy problem. With this function, the channel would return (send back) an I/O request to the program only if the desired subchannel was busy executing an operation. If any other busy condition was encountered, the channel waited for the busy condition to clear and then initiated the operation. This approach offered performance improvement in some cases. However, an I/O request could be queued in one channel because of a busy condition while other channels with paths to the desired device are idle.