Digital's Storage Systems Interconnect

ECO Controlled Version 1.0.0

RELEASE VERSION

27 March 1990

T

Send inquiries and comments to SSAG::SSAG.

#### Abstract

This document defines the Digital Storage Systems Interconnect (DSSI). DSSI is based on the higher layer protocols of the CI (DEC STD 161) using a different data-link and physical interconnect.

DIGITAL EQUIPMENT CORPORATION CONFIDENTIAL AND PROPRIETARY

This document is an unpublished work and contains valuable trade secrets which are confidential and proprietary to Digital Equipment Corporation, and may only be disclosed to individuals who have entered into a confidentiality agreement with Digital, and may not be copied or reproduced in whole or in part.

Copyright (c) Digital Equipment Corporation 1990. All Rights Reserved.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0CONTENTSPage ii

27 March 1990

#### CONTENTS

|         | 1                                       | Preface To Version 1.0.0 viii                                    |

|---------|-----------------------------------------|------------------------------------------------------------------|

| CHAPTER | 1                                       | INTRODUCTION                                                     |

|         | 1.1<br>1.2<br>1.3<br>1.4<br>1.5         | SCA Overview                                                     |

| CHAPTER | 2                                       | TERMINOLOGY AND NOTATIONAL CONVENTIONS                           |

|         | 2.1<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4 | Time Unit Abbreviations                                          |

| CHAPTER | 3                                       | PORT ADDITIONS AND/OR CLARIFICATIONS                             |

|         | 3.1<br>3.2<br>3.3<br>3.4<br>3.5         | Port Additions And/or Clarifications 3-1<br>Unrecognized Packets |

#### CHAPTER 4 THE DSSI DATALINK

3.6

3.7

| 4.1   | The DSSI Datalink 4-1                      |  |

|-------|--------------------------------------------|--|

| 4.2   | Overview Of A DSSI Data Transfer 4-1       |  |

| 4.3   | DSSI Datalink Logical Description 4-3      |  |

| 4.4   | Channel Control Services 4-6               |  |

| 4.5   | Data Transmit And Error Recovery Layer 4-7 |  |

| 4.5.1 | Error Recovery Procedure 4-8               |  |

| 4.5.2 | Example Of Random Number Generator 4-9     |  |

| 4.6   | Interface To The CI Port Layer 4-11        |  |

\*\*\* R E L E A S E V E R S I O N \*\*\* Digital Equipment Corporation Confidential And Proprietary Digital's Storage System Interconnect Version 1.0.0 CONTENTS Page iii 27 March 1990

CHAPTER 5 THE DSSI PHYSICAL BUS PROTOCOL

| 5.1            | The DSSI Physical Bus Protocol 5-1           |

|----------------|----------------------------------------------|

| 5.2            | Logical Description Of The DSSI 5-2          |

| 5.3            | Signal Definitions                           |

| 5.4            | DSSI Bus Timing [1]                          |

| 5.4.1          | Arbitration Delay [ 2.4us ]         5-4      |

| 5.4.2          |                                              |

|                |                                              |

| 5.4.3          | Bus Clear Delay [ 800ns ] 5-4                |

| 5.4.4          | Bus Free Delay [ 800ns ] 5-5                 |

| 5.4.5          | Bus Set Delay [ 1.8us ] 5-5                  |

| 5.4.6          | Bus Settle Delay [ 400ns ] 5-5               |

| 5.4.7          | Cable Skew Delay [ 10ns ] 5-5                |

| 5.4.8          | Data Release Delay [ 400ns ] 5-5             |

| 5.4.9          | Deskew Delay [ 45ns ] 5-5                    |

| 5.4.10         | Hold Time [ 45ns ] 5-5                       |

| 5.4.11         | Negation Period [ 90ns ] 5-5                 |

| 5.4.12         | Negation Period [ 90ns ]                     |

| 5.4.13         | Transfer Period [ 180ns ] 5-6                |

| 5.5            | Bus Protocol 5-6                             |

| 5.5.1          | General Requirements 5-8                     |

| 5.5.1.1        | Implicit Signal State 5-8                    |

| 5.5.1.2        | Definition Of Initiator And Target Nodes 5-8 |

| 5.5.1.3        | Use Of And Reaction To Bus Reset (RST) 5-8   |

| 5.5.1.4        | Watchdog Timers                              |

| 5.5.2          | DSSI Bus Phases And Signal Sources 5-10      |

| 5.5.3          | BUS FREE Phase                               |

| 5.5.4          | ARBITRATION Phase                            |

| 5.5.5          | Fair ( Round-Robin ) Arbitration 5-12        |

| 5.5.5.1        |                                              |

|                | Algorithm                                    |

| 5.5.5.2        | Rules For Enabled Nodes                      |

| 5.5.5.3        | Rules For Disabled Nodes                     |

| 5.5.5.4        | Rules For Manipulating The                   |

| 0101011        | Enabled/Disabled Flag 5-16                   |

| 5.5.5.5        | ARBITRATION Phase Transitions 5-17           |

| 5.5.6          | SELECTION Phase                              |

| 5.5.6.1        | SELECTION Phase Transitions                  |

| 5.5.7          | Information Transfer Phases                  |

| 5.5.7.1        |                                              |

| 5.5.7.2        | Synchronous Data Transfer                    |

| 5.5.7.2        | •                                            |

| 5.5.7.3        |                                              |

| <b>E E 7</b> 4 | Phases                                       |

| 5.5.7.4        |                                              |

| 5.5.7.5        |                                              |

| 5.5.7.6        | Command Out Descriptor Validation            |

|                | Precedence                                   |

|                |                                              |

\*\*\* R E L E A S E V E R S I O N \*\*\* Digital Equipment Corporation Confidential And Proprietary Digital's Storage System Interconnect Version 1.0.0 CONTENTS Page iv 27 March 1990

| 5.5.7.6 | .1 Reserved Field Validation 5-32        |

|---------|------------------------------------------|

| 5.5.7.6 | .2 COMMAND OUT Phase Transitions 5-32    |

| 5.5.8   | The DATA OUT Phase 5-34                  |

| 5.5.8.1 | Data Block Length 5-35                   |

| 5.5.8.2 | DATA OUT Phase Transitions 5-35          |

| 5.5.8.3 | The STATUS IN Phase 5-37                 |

| 5.5.8.4 | STATUS IN Phase Transitions 5-37         |

|         | Performance And Diagnostic Counters 5-39 |

| 5.6.1   | Counter Descriptions 5-39                |

# CHAPTER 6 DSSI BUS ELECTRICAL AND PHYSICAL SPECIFICATION

| 6.1 II    | ntroduction 6-                             |    |

|-----------|--------------------------------------------|----|

| 6.2 E     | lectrical Description 6-                   | 1  |

| 6.2.1     | Required Signal Termination 6-             | 1  |

| 6.2.2     | Terminator Package 6-                      | 2  |

| 6.2.3     | DSSI Driver 6-                             | 3  |

| 6.2.4     | Electrical Characteristics 6-              |    |

| 6.2.4.1   | Output Characteristics 6-                  | -  |

| 6.2.4.2   | Input Characteristics 6-                   | 5  |

| 6.2.5     | Terminator Power Characteristics 6-        |    |

| 6.2.5.1   | Terminator Power Dissipation 6-            |    |

| 6.2.5.2   | Noise Margin 6-                            | 8  |

| 6.3 PI    | HYSICAL CHARĂCTERISTICS 6-                 |    |

| 6.3.1     | Maximum Length 6-                          | 9  |

| 6.3.2     | STUB LENGTH 6-1                            |    |

| 6.3.3     | STUB SEPARATION 6-1                        | .0 |

| 6.3.4     | MODULE ETCH REQUIREMENTS 6-1               | .0 |

| 6.3.5     | INTERNAL CONNECTOR REQUIREMENTS 6-1        |    |

| 6.3.5.1   |                                            |    |

| 6.3.5.1.1 |                                            |    |

| 6.3.5.1.2 |                                            |    |

| 6.3.6     | INTERNAL CABLE REQUIREMENTS 6-1            | .1 |

| 6.3.7     | EXTERNAL CONNECTOR REQUIREMENTS 6-1        |    |

| 6.3.8     | EXTERNAL CABLE REQUIREMENTS 6-1            | .1 |

| 6.3.9     | Connecting And Disconnecting A Device From |    |

|           | The DSSI Bus 6-1                           |    |

| 6.3.9.1   | Hot Swap Prohibited 6-1                    | .2 |

| 6.3.9.2   | Power Supply Requirements 6-1              |    |

| 6.3.9.3   | Mechanical Requirements 6-1                | .3 |

| 6.3.9.3.1 |                                            |    |

|           | Layout Rules 6-1                           | .3 |

| 6.3.9.3.2 |                                            |    |

| 6.3.9.3.3 | Pin Sequencing 6-1                         | .3 |

\*\*\* R E L E A S E V E R S I O N \*\*\* Digital Equipment Corporation Confidential And Proprietary Digital's Storage System Interconnect Version 1.0.0 CONTENTS Page v 27 March 1990

- APPENDIX A FAIR ARBITRATION ALGORITHM TIMING PARAMETERS

- APPENDIX B SII

- APPENDIX C DSSI PARAMETER VALUES

#### APPENDIX D IMPLEMENTATION FUNCTIONALITY

| D.1   | Section 5.5.8.1 "Data Block Length"          | D-1 |

|-------|----------------------------------------------|-----|

| D.1.1 | SWIFT And SII                                | D-1 |

| D.1.2 | SHAC And DASH                                | D-2 |

| D.2   | Table E 2 "Summary Of Chappel Control Layor  |     |

| D.Z   | Table 5-2, "Summary Of Channel Control Layer |     |

| D.2   | Status Values"                               | D-2 |

#### APPENDIX E USE OF CREDITS IN SCA/MSCP SPECIFICATIONS

#### E.1 DSSI Device Credit Management . . . . . . E-4

#### APPENDIX F SCA AND MSCP CLARIFICATIONS

| F.1 SCA Additior | ns And/or Clarifications F-1         |  |

|------------------|--------------------------------------|--|

| F.2 Format Of Bu | Iffer Descriptors And Use In         |  |

| SNTDAT/DATRE     | Qn Packets                           |  |

|                  | Concepts                             |  |

| F.3.1 Example Po | ort State Diagram In DSSI Drives F-2 |  |

| F.3.1.1 Uninitia | alzed State F-2                      |  |

| F.3.1.2 Uninitia | alized/Maint State F-2               |  |

| F.3.1.3 Enabled/ | Maint State F-3                      |  |

| F.4 Generation ( | )f Unique Node Parameters F-3        |  |

| F.4.1 SCA And MS | SCP Parameters F-3                   |  |

| F.4.1.1 SCA Syst | cem Name                             |  |

| F.4.1.2 SCS SYST | FEMID                                |  |

| F.5 SCA Packet F | Format Clarification F-5             |  |

#### APPENDIX G REVISION HISTORY

\*\*\* R E L E A S E V E R S I O N \*\*\* Digital Equipment Corporation Confidential And Proprietary Digital's Storage System Interconnect Version 1.0.0 CONTENTS Page vi 27 March 1990

APPENDIX H EXCEPTIONS H.1 Policy . . . . . . . . . . . . . . . . H-1 H.2 Exceptions For Products Using The SII Bus Interface Chip . . . . . . . . . . . . . . . . H-1 H.2.1 SII Fixed Priority Arbitration Scheme . . H-2 H.3 Exceptions For SHAC/DASH . . . . . . . . . . H-3 H.3.1 Target Timeout Enforcement . . . . . . . . H-3

# APPENDIX J TERMINATOR SELECTION

#### FIGURES

| 1-1  | The SCA Model 1-2                                 |

|------|---------------------------------------------------|

| 1-2  | CI PPD Architectural Layers 1-4                   |

| 1-3  | Comparison of CI and DSSI features 1-7            |

| 4-1  | Simplified DSSI Atomic Bus Sequence 4-2           |

| 4-2  | DSSI Datalink Model 4-4                           |

| 4-3  | Format of Unique Initial Seed 4-10                |

| 5-1  | Datalink Channel Control Layer 5-1                |

| 5-2  | ARBITRATION Phase Transitions 5-17                |

| 5-3  | SELECTION Phase Transitions 5-21                  |

| 5-4  | Format of DSSI Command Out Descriptor Block 5-29  |

| 5-5  | COMMAND OUT Phase Transitions 5-33                |

| 5-6  | DSSI Data Format 5-34                             |

| 5-7  | DATA OUT Phase Transitions 5-36                   |

| 5-8  | DSSI STATUS IN Data Formats 5-37                  |

| 5-9  | STATUS IN Phase Transitions 5-38                  |

| 6-1  | DSSI Bus Electrical Configuration 6-1             |

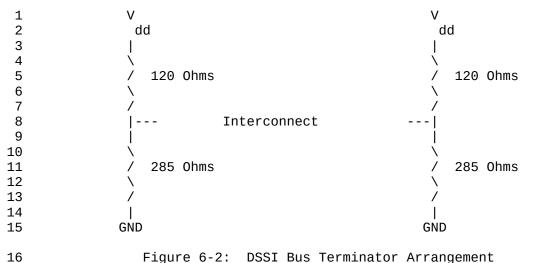

| 6-2  | DSSI Bus Terminator Arrangement 6-2               |

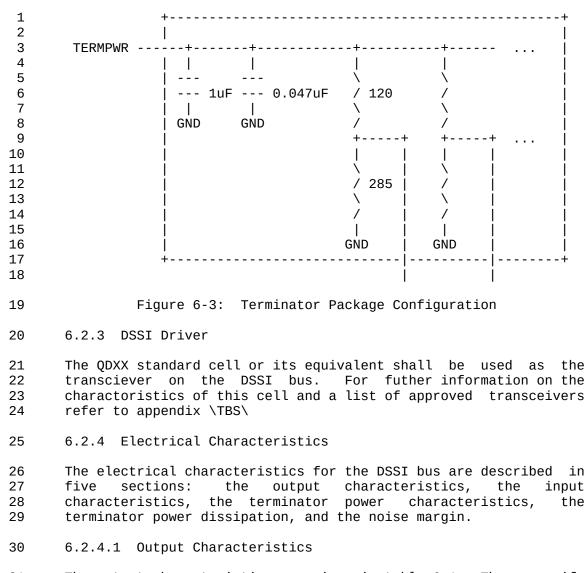

| 6-3  | Terminator Package Configuration 6-3              |

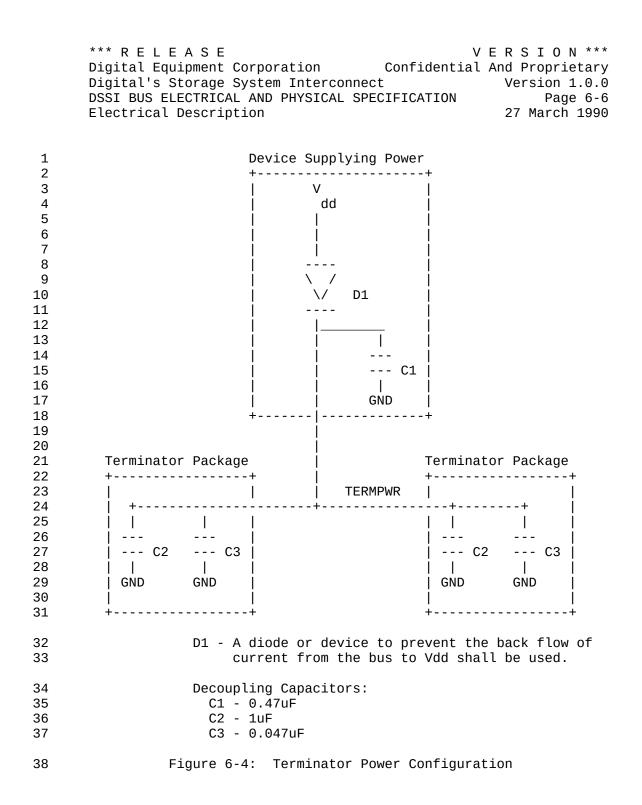

| 6-4  | Terminator Power Configuration 6-6                |

| 6-5  | DSSI Noise Margin Definition 6-9                  |

| F-1  | Minimum Port State Diagram in DSSI Drives . F-2   |

| F-2  | Format of PPD START Datagram F-6                  |

| F-3  | Detail of PPD START Datagram F-6                  |

| F-4  | PPD Start Datagram Packet                         |

| F-5  | SCA Message Packet containing MSCP Command . F-8  |

| F-6  | Format of VAX CI Port Packet F-11                 |

| F-7  | Format of CI Packet                               |

| F-8  | DSSI Packet Format                                |

| F-9  | SCS Application Message in VAX CI Port            |

|      | Packet                                            |

| F-10 | SCS Application Message in DSSI Data Block . F-15 |

\*\*\* R E L E A S E V E R S I O N \*\*\* Digital Equipment Corporation Confidential And Proprietary Digital's Storage System Interconnect Version 1.0.0 CONTENTS Page vii 27 March 1990

# TABLES

| 5-1 | DSSI Bus Timing Values 5-4                 |

|-----|--------------------------------------------|

| 5-2 | Summary of Channel Control Layer Status    |

|     | Values                                     |

| 5-3 | DSSI Signal Sources 5-11                   |

| 5-4 | Information Transfer Phases 5-23           |

| 6-1 | DSSI Electrical Output Characteristics 6-4 |

| 6-2 | DSSI Electrical Input Characteristics 6-5  |

| 6-3 | Terminator Power Characteristics 6-7       |

| 6-4 | Terminator Power Dissipation 6-8           |

| 6-5 | DSSI Noise Margins 6-9                     |

| 6-6 | DSSI Signal Assignments 6-12               |

| C-1 | DSSI General Parameters C-1                |

| C-2 | Selected DSSI Timing Parameters C-1        |

| D-1 | SHAC/DASH Differences in Channel Control   |

|     | Layer Status D-3                           |

| D-2 | CI Port Maintenance I/Ds D-3               |

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0PrefacePage viiiPreface To Version 1.0.027 March 1990

1 Preface To Version 1.0.0

This release of the specification is the final form version approved by the DSSI Review Committee on 27 March 1990. All further changes to the document shall be made by ECO.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0INTRODUCTIONPage 1-1OT March 1000Page 1-1

27 March 1990

# 1 CHAPTER 1 2 INTRODUCTION 3 This specification defines the architecture for the Digital 4 Storage Systems Interconnect (DSSI). The DSSI, supporting the 5 needs of low-end and mid-range systems, is one in a family of 6 high-performance computer-to-computer interconnects (CI's ) that 7 combine a common host interface and port layer with an

9 1.1 SCA Overview

8

CI-class interconnects provide the transmission services required

by Digital's Systems Communication Architecture - a four-tiered

set of protocols and interfaces as shown in figure 1-1.

implementation-specific datalink and physical interconnect.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0INTRODUCTIONPage 1-2SCA Overview27 March 1990

| 1<br>2      |           | Node<br>+                  | L                  | Node<br>++                   |

|-------------|-----------|----------------------------|--------------------|------------------------------|

| 2<br>3<br>4 |           | System                     | SYSAP              | System                       |

| 5<br>6      |           | ( SYSAP )                  | Protocol           | ( SYSAP )                    |

| 0<br>7<br>8 |           | System<br>  Communications | SCS                | System  <br>  Communications |

| 9<br>10     |           | Services<br>  ( SCS )      | Protocol           | Services  <br>  ( SCS )      |

| 11<br>12    |           | +<br>  Port/Port           | + PPD +            | ++                           |

| 12          |           | Driver                     | <> <br>  Protocol  | Driver                       |

| 14          |           | Layer<br>+                 |                    | Layer                        |

| 15          |           | +                          | + +                | ++                           |

| 16          |           |                            | , ,                | I                            |

| 17          |           |                            | //                 |                              |

| 18          |           | Pr                         | nysical Interconne | ect                          |

| 19          |           | Figure 1                   | -1: The SCA Mode   | L                            |

| 20          | This arch | nitecture consists o       | of the following 1 | layers:                      |

| 21          | 0         |                            |                    | ocess whose services         |

| 22          |           | and protocol are           | specific to a giv  | ven application. The         |

| 23          |           | disk class driver :        | is an example of s | such a process. It's         |

| 24          |           | protocol is the Mas        | ss Storage Control | l Protocol ( MSCP ).         |

| 25          | 0         | Systems Communicat         | tions Services     | (SCS) - Provides             |

| 26          |           | facilities for             |                    | and maintaining              |

| 27          |           | communications betw        | ween two Sysaps.   |                              |

| 28          | 0         | Port/Port Driver La        | ayer (PPD) - A con | nbination of hardware        |

| 29          |           | and software th            | nat provides t     | the host with a              |

| 30          |           | device-independant         | . packet-orient    | ed interface for             |

| 31          |           | node-to-node data 1        | transfers.         |                              |

| 32          | 0         | Physical Intercon          | nect - The ph      | nysical media and            |

| 33          |           | signalling protoco         | ols used to tra    | ansmit the raw bit           |

| 34          |           | stream.                    |                    |                              |

| 35          |           |                            |                    | elivery of packets to        |

| 36          |           |                            |                    | able errors. The PPD         |

| 37          | provides  | the following serve        | ices:              |                              |

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0INTRODUCTIONPage 1-3SCA Overview27 March 1990

- o Datagram service The delivery of independant packets 1 2 to another node with high probability of success. 3 Datagrams may be discarded if buffers to accommodate them are not available in the receiving node. 4 5 o Virtual Circuit Services - The transfer of data between nodes without duplication or loss. Virtual circuits are 6 7 established between node pairs and support the following 8 classes of service: 9 Message Service - The delivery in correct sequence 1. of one or more packets comprising a message. 10 2. Buffered Data Service - The efficient transfer of 11

- 121313141516171717141414141414141414

15 A CI implementation consists of the physical interconnect, 16 combined with hardware and software within the PPD layer, that 17 implements SCA packet tranmission services. The following 18 section presents an overview of this layer.

19 1.2 CI PPD Layer

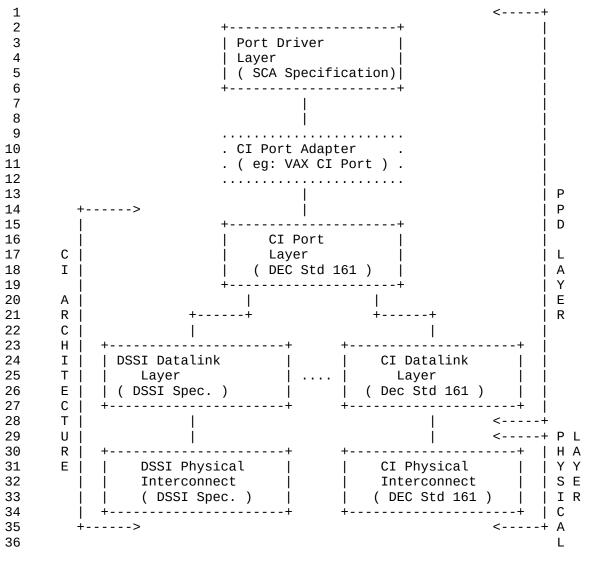

Figure 1-2 illustrates the layers of a PPD implementation built on a CI-class interconnect. The specifications controlling each functional element are listed in section 1.5.

| *** R E L E A S E |                     | V E R S I O N ***            |

|-------------------|---------------------|------------------------------|

| Digital Equipment | Corporation         | Confidential And Proprietary |

| Digital's Storage | System Interconnect | Version 1.0.0                |

| INTRODUCTION      |                     | Page 1-4                     |

| CI PPD Layer      |                     | 27 March 1990                |

#### 37

#### Figure 1-2: CI PPD Architectural Layers

38 The topmost layer, the port driver, provides a device-independant 39 interface to the data transfer services provided by lower layers. 40 It is also responsible for managing the startup and orderly 41 shutdown of virtual circuits.

The CI port adapter is the hardware interface that performs the

physical transfer of packets between host memory and the CI port.

The architecture of such hardware interfaces is outside the scope

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0INTRODUCTIONPage 1-5CI PPD Layer27 March 1990

1 of SCA. In some implementations, this function is performed by 2 host software.

The port implements the protocols that provide the datagram, block data and message services defined by the architecture. It is responsible for error recovery, the detection of lost packets within a message or block data transfer and the sequential delivery of message packets.

- 8 The Datalink layer is responsible for:

- 9 1. Channel control including channel access arbitration.

- 102. The transformation of outgoing packets into bit streams11for transmission over the physical medium through the12addition of addressing data, framing information and13error-detection codes.

14 3. Recovery from transmission errors.

The conversion of incoming data streams into packets in memory free of detectable errors. This includes the detection and removal of framing information, address detection, error detection and receipt acknowledgment.

19 The Physical Interconnect layer consists of the line drivers, 20 wires, bus arbitration and electrical signalling rules that 21 control the physical transfer of data over the bus.

As indicated in the diagram, the CI architecture consists of a common port protocol, defined in DEC standard 161, coupled with unique datalink and physical channel layers.

25 1.3 Overview Of The DSSI Bus

This section presents an overview of the DSSI bus and its design goals in comparision to the CI.

The DSSI is designed to support low-end and mid-range systems, including VAX clusters, where an application can tolerate a reduction in availability and performance in exchange for reduced cost. The main features of DSSI are:

32 o Multidrop electrical topology

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0INTRODUCTIONPage 1-6Overview Of The DSSI Bus27 March 1990

- 1 o 8-bit parallel data bus.

- 2 o DC coupling between nodes

- 3 O Use of low-cost, single-ended drivers and receivers.

| 4 | 0 | Restricted length ( 6 meters maximum ) suitable f | or |

|---|---|---------------------------------------------------|----|

| 5 |   | one-, two-, or three-box systems.                 |    |

6 o Single electrical path.

7 In contrast, the CI is designed to support the needs of high-end

8 systems where availability and performance are the primary goals.

9 The main features of the CI are:

- 10o "Star" electrical topology to isolate the bus from11single-point node failures,

- 12 o Passive star coupler for reliability

- o Active, redundant-element star coupler for large arrays

of intelligent subsystems

- o Bit-serial signalling to simplify star coupler design

and facilitate inter-system isolation.

- 17 o Dual-path for redundancy

- 18 o End-to-end length suitable for interconnecting large 19 systems in a 'computer room' environment.

- 20 The following table summarizes the characteristics of each 21 interconnect:

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0INTRODUCTIONPage 1-7Overview Of The DSSI Bus27 March 1990

- CI DSSI 1 2 - -- - - -3 Format of Bit-serial, embedded 8-bit parallel, transmitted clock. 'synchronous burst' 4 5 Data: 6 Data Bandwidth: 70Mbits/sec 4Mbytes/sec 7 (unformatted) ( ~32Mbits/sec ) 8 Maximum Number 16 ( Passive Hub ) 8 of Nodes per 9 224 ( Active Exchange ) 10 Datalink: Data Format: Packets, 7 - 4100 bytes Packets, 2 - 4114 11 12 ( excluding bit synch, bytes 13 header and trailer ) 6 meters end-to-end 14 Distance: 45 meters max from 15 center of hub, 90 meters node-to-node. 16 17 Medium: 2 send-receive Single, 50-conductor 18 coaxial cable pairs cable with multiple 19 taps.

- 20ElectricalTransformer-coupledDC-coupled, single-21Interface:line drivers for highended line drivers.22dc isolation.ended line drivers.

- 23 Figure 1-3: Comparison of CI and DSSI features

- 24 1.4 Scope Of This Document

This document is the functional specification of the DSSI bus. Its purpose is to specify the interconnect to the level of detail necessary to build a DSSI node and configure a series of nodes into an operational system.

- 29 The following elements are specified:

- 30

1. The DSSI Data Link Protocol.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0INTRODUCTIONPage 1-8Scope Of This Document27 March 1990

The physical bus protocol including signal definitions 1 2. 2 and timing. 3 The bus the 3. electrical requirements including specification for line drivers and receivers and rules 4 5 for signal integrity. 6 4. The mechanical requirements, including the definition of connectors, cables and mounting rules. 7 The electrical and mechanical rules for configuring a 8 5. system of DSSI nodes. 9 10 1.5 References The following documents may be useful in fully understanding DSSI 11 and its relationship with Digital's Storage Architecture (DSA) 12 and other I/O architectures. 13 14 1. Mass Storage Control Protocol (MSCP); Revision 2.1.1 ( 15 13 March 1988 ) 16 2. Tape Mass Storage Control Protocol (TMSCP); Revision 2.0.2 ( 8 November 1987 ) 17 Diagnostics and Utilities Protocol (DUP); Revision 1.0 18 3. 19 (May 15, 1984) 20 4. Systems Communications Architecture (SCA); Revision 7 21 (August 8, 1985) 22 5. Computer Interconnect Specification (DEC STD 161);Revision A (November 24, 1986) 23 24 6. VAX-11 CI Port Architecture (CIPORT); Revision 5.0 (August 17, 1987) 25 26 7. Storage Systems Port; Revision 3.1.0 (November 9, 1989 ) 27

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0TERMINOLOGY AND NOTATIONAL CONVENTIONSPage 2-127 March 1990

| 1 |             | CHAPTER 2                              |

|---|-------------|----------------------------------------|

| 2 |             | TERMINOLOGY AND NOTATIONAL CONVENTIONS |

|   |             |                                        |

| 3 | Active Node |                                        |

4 During an atomic bus sequence, the node that controls the bus 5 and drives bus-level commands. Either the initiator or 6 target will assume the role of active node. See 'Passive 7 Node'.

- 8 Asynchronous Mode

- 9 A mode of DSSI data transfer that requires an explicit 10 send/receive handshake for each byte transferred.

- 11 Atomic Bus Sequence

12 The sequence of DSSI bus phases associated with the 13 transmission of one data block from an initiator to a target 14 device. The sequence is performed atomically with respect to 15 other nodes on the bus in that bus ownership and control 16 remain with the target-initiator pair until the sequence 17 completes.

18 Bus Phase

19The sequence of bus states comprising one step in an Atomic20Bus Sequence. The ARBITRATION phase, through which a node21bids for ownership of the bus, is one such phase.

#### 22 Command Descriptor Block

| 23 | Six bytes of control information ( plus checksum )           |

|----|--------------------------------------------------------------|

| 24 | transmitted to the target during the DSSI COMMAND OUT phase. |

| 25 | This block contains parameters used to control the           |

| 26 | transmission of information during the DATA OUT phase.       |

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0TERMINOLOGY AND NOTATIONAL CONVENTIONSPage 2-227 March 1990

1 Data Block

2 The block of information (with checksum ) transmitted from 3 the initiator to the target during the DATA OUT phase of a 4 DSSI bus transaction.

- 5 DSSI Node

- 6 The site of a DSSI datalink. The terms 'node' and 'DSSI 7 node' are used synonymously in this specification.

- 8 DSSI Packet

- 9 The Command Out descriptor block and Data block transmitted 10 by the initiator during an atomic bus sequence.

- 11 Hot-swap

- 12 The act of physically connecting or disconnectiong a node 13 from the bus while the node is powered on.

- 14 Initiator

- 15 A DSSI node that has arbitrated for the bus with the 16 intention of sending a data packet.

- 17 May

Denotes a lack of prohibition when used as a directive. It

is used to indicate an option or options architecturally

permissible for an implementation. No bias for or against

the option is implied. "May not" denotes strict prohibition

when used as a directive.

- 23 Node

- 24 See 'DSSI node'.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0TERMINOLOGY AND NOTATIONAL CONVENTIONSPage 2-327 March 1990

1 Nugatory

2

- Of little or no consequence: Trifling, Inconsequential.

- 3 Passive Node

During a bus phase, the DSSI node that reacts to bus-level

commands. For each phase of an atomic bus sequence either

the initiator or target will assume the role of passive node.

See 'Active Node'.

8 Physical Bus Protocol

9 The electrical signalling rules and timing required for a 10 DSSI node to properly transmit control signals and data over 11 the DSSI physical interconnect.

12 Shall

Denotes an architectural requirement. It is used as a

directive to express what is mandatory for an implementation.

"Shall not" denotes strict prohibition.

16 Should

Denotes an emphatic recommendation when used as a directive.

It is used where "shall" might be too strong because of the

possibility of technical, implementation-specific obstacles

or other overriding considerations.

- 21 Synchronous Mode

- 22 Synonymous with "synchronous burst mode".

- 23 Synchronous Burst Mode

A mode of data transmission over the DSSI bus in which data bytes are transmitted in bursts, without waiting for an explicit send/receive "handshake" after each byte. This mode requires that each DSSI implementation have a dedicated

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0TERMINOLOGY AND NOTATIONAL CONVENTIONSPage 2-427 March 1990

- 1 hardware buffer ( FIFO ) that is tightly coupled to the bus.

- 2 Target

- A DSSI node that has been signalled by an initiator, via the physical bus protocol, that it is to receive a packet.

- 5 Warm-swap

- 6 The act of physically disconnectiong or connecting a node to 7 the bus while node power is off.

\*\*\* R E L E A S E VERSION\*\*\* Digital Equipment Corporation Confidential And Proprietary Digital's Storage System Interconnect Version 1.0.0 TERMINOLOGY AND NOTATIONAL CONVENTIONS Page 2-5 Notational Conventions 27 March 1990 2.1 Notational Conventions 1 2 2.1.1 Numeric Notation 3 All numbers are decimal unless otherwise specified. Hexadecimal numbers are noted by a suffix of "h", for example, 1Ah. 4 2.1.2 Time Unit Abbreviations 5 6 The following time unit abbreviations are used: 7 1. ms - Milliseconds 2. us - Microseconds 8 9 3. ns - Nanoseconds 2.1.3 Bit Field Notation 10 A string of contiguous bits is described by the notation: 11 12 field name< m:n > 13 where: "field\_name" is an ascii string describing the function or 14 15 field 16 "m" is the bit position of the left-most ( highest order ) 17 bit in the field. 18 "n" is the bit position of the right-most ( lowest order ) 19 bit in the field. 20 2.1.4 Naming Conventions For Variables Throughout this specification, variable names designating 21 22 parameters and function values, are constructed in the form: 23 <xx>\_<value\_mnemonic> 24 Where: 25 "<xx>" is a two-character abbreviation for the layer or 26 function that establishes the variable's value and "<value\_mnemonic>" is a string suggestive of the parameter or 27

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0TERMINOLOGY AND NOTATIONAL CONVENTIONSPage 2-6Notational Conventions27 March 1990

1 condition represented.

2 Variables associated with the physical bus always have a null3 prefix string.

So, for example, the name "CC\_NAK" represents a value returned by

the datalink Channel Control layer, whereas "NAK" represents a

value returned over the DSSI bus during the STATUS IN phase.

| 1                                                        | CHAPTER 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                        | PORT ADDITIONS AND/OR CLARIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3                                                        | 3.1 Port Additions And/or Clarifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4<br>5<br>6<br>7                                         | This section clarifies or adds to the Port section of DEC STD<br>161. These changes are due to past experience with the CI, or<br>due to different requirements of the underlying DSSI Physical<br>Channel.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8                                                        | 3.2 Unrecognized Packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9<br>10<br>11                                            | When an unrecognized packet (unrecognized port layer opcode, or invalid packet length) is received by a DSSI node, it should close the virtual circuit to the corresponding node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12                                                       | 3.3 Self Directed Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22 | All DSSI adapters other than KFQSA should support the self<br>directed commands (CI Port commands with Port Field the same as<br>their own node number). Two SYSAP processes within a system may<br>communicate with each other through self directed commands. They<br>should be supported with all variations of the specific commands<br>(such as R bit set or clear) like all other non-self directed<br>commands. It is further recommended that they should be<br>implemented to use the same code paths (to the extent possible)<br>as non-self directed commands. Such an approach will provide a<br>loop back mechanism and help diagnosis. |

| 23                                                       | 3.4 Loop Back Packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 24<br>25<br>26<br>27<br>28<br>29<br>30                   | CI Port Architecture and DEC STD 161 support loop back packets on<br>the CI wires. The SNDLB command (Sec 7.8, Ref [6]) requires that<br>the packet should be transmitted and received on the wires at the<br>same time. CI data link supports such a feature. However DSSI<br>(more specifically the SII) does not support such feature.<br>However DSSI adapters other than KFQSA should treat the SNDLB<br>commands similar to the self directed commands.                                                                                                                                                                                        |

| 31                                                       | 3.5 Multibit Sequence Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 32<br>33                                                 | CI port layer uses single bit sequenced numbers in all the sequenced message packets (refer to section 4.1 in DEC STD 161).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                          | *** RELEASE VERSION ***                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

\*\*\* RESTRICTED DISTRIBUTION \*\*\*

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0PORT ADDITIONS AND/OR CLARIFICATIONSPage 3-2Multibit Sequence Numbers27 March 1990

Single bit sequence numbers have the problem that if a single NAK 1 2 status turns into an ACK, (i.e., the receiver sent a NAK and the 3 sender received the status as ACK due to 8 bit errors in 9 bit DSSI status), two sequenced message packets will be discarded at 4 5 the receiver and both nodes will be unaware of the lost packets. 6 To overcome the above problem DSSI uses 3 bit sequence numbers. All references to NS and NR in DEC STD 161 and CI Port 7 8 Architecture should be treated as 3 bit fields. The sequence 9 number field, NS, is located in bits <3:1> of the FLAGS byte.

- 10 When a frame is received, a DSSI node should use the following 11 rule for validating sequence numbers:

- 12 1. If NS = NR, the node should accept the frame and 13 increment NR.

- If NS = NR-1, the node should discard the frame, and should not increment NR.

- With any other combination of NS and NR, the node should

break VC, and report a sequence number mismatch error to

higher layers.

- 19 3.6 CI ID Response Packet Fields

Sec 7.9.3 of CI Port Architecture (Ref[6]), describes ID Response

packet format. The fields relevant to DSSI are in this section.

22 The only sub-field of PORT\_FCN\_EXT that is currently meaningful 23 for DSSI devices is MAX\_BODY\_LEN, which is the low 13 bits of the 24 high order word of the PORT\_FCN\_EXT longword. The contents of 25 this field are the maximum number of bytes in a packet BODY 26 supported by the sending node. The packet body comprises the data bytes passed during the DSSI data phase --- the packet 27 28 opcode byte, flags byte, and other data bytes, but not the 29 checksum.

30 It should be noted that the MAX\_BODY\_LEN value reported by a DSSI 31 node must reflect the size of the buffers on the SII receive 32 queue (target queue).

33 Nodes that do not have internal data buffers (SHAC) must always 34 report the maximum size, (4114).

| *** R E L E A S E                     | V E R S I O N ***            |

|---------------------------------------|------------------------------|

| Digital Equipment Corporation         | Confidential And Proprietary |

| Digital's Storage System Interconnect | t Version 1.0.0              |

| PORT ADDITIONS AND/OR CLARIFICATIONS  | Page 3-3                     |

| CI ID Response Packet Fields          | 27 March 1990                |

Block data transfer packets include 18 bytes of overhead in addition to data --- packet opcode (1), flags (1), transaction ID (8), buffer name (4), and offset (4). Thus transferring 4K bytes of data per packet requires that MAX\_BODY\_LEN be 4114 (4096+18) or larger.

DSSI nodes should return zero in all other currently defined

sub-fields of PORT\_FCN\_EXT. XNR, AARB, XPRE, and AST report CI

data link parameters that are inapplicable to DSSI. A CSZ

(cluster size) value of zero means 16 nodes, which is the closest

value available to the 8 nodes supported by DSSI.

11 DSSI nodes must ignore all the inapplicable fields of the 12 PORTFCNTEXT field (as well as other fields of the ID response 13 packet). They should ignore whatever values they receive in the 14 XNR, AARB, XPRE, AST and MBZ (Must Be Zero) fields. They should 15 also ignore the CSZ (cluster size) field.

DSSI nodes should use the contents of the MAX\_BODY\_LEN to

determine the maximum size of a block data transfer.

Specifically, DSSI disk and tape drives should do the following:

- 19 1. The drive has its own MAX\_BODY\_LEN that corresponds to 20 its native or preferred data transfer size --- that is, to the size of its data buffers. While it is strongly 21 22 recommended that this be 4114 (4K data bytes per 23 packet), smaller values can be justified so long as 24 their effect on system performance (not just device cost 25 or performance) is considered and verified (through 26 simulation, performance testing, etc.).

- The drive determines the host's MAX\_BODY\_LEN from the configuration polling process.

- For each host, the drive determines an effective

MAX\_BODY\_LEN equal to the minimum of the drive's

MAX\_BODY\_LEN and the host's MAX\_BODY\_LEN.

- 32 4. DSSI drives may only initiate data byte transfers with

33 base packet size of 512 bytes (P=0).

- 345. The drive determines the packet multiple (M value) to35use for the block data transfers that the drive36initiates on each host as follows:

- 37 if (effective MAX\_BODY\_LEN < 530) then begin

| *** R E L E A S E                     | V E R S I O N ***            |

|---------------------------------------|------------------------------|

| Digital Equipment Corporation         | Confidential And Proprietary |

| Digital's Storage System Interconnect | t Version 1.0.0              |

| PORT ADDITIONS AND/OR CLARIFICATIONS  | Page 3-4                     |

| CI ID Response Packet Fields          | 27 March 1990                |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | <pre>{ host either does not implement the CI ID response ECO, } { in which case MAX_BODY_LEN is zero, or the host returned } { a MAX_BODY_LEN value smaller than one 512 byte block. } { In either case use M=0, or one 512 byte block per packet.} M := 0; end else begin M := (effective MAX_BODY_LEN - 18) div 512 - 1; { div means integer division with truncation towards zero. } if M &lt; 0 then M := 0; if M &gt; 7 then M := 7; end;</pre> |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12                                                    | The drive supplies this M value in all DATREQn packets and uses                                                                                                                                                                                                                                                                                                                                                                                      |

| 13<br>14                                              | it to limit the size of all SNTDAT packets. It should be noted<br>that the drive determines a separate value of M for each host.                                                                                                                                                                                                                                                                                                                     |

15 DSSI host nodes should do the following:

# 161. All native DSSI host nodes (all host ports that attach17to a DSSI cable or bus) should return a MAX\_BODY\_LEN18value of 4114 in ID response packets.

- 19DSSI host nodes should also support packets with body20lengths up to 4114 bytes.

- All DSSI host nodes shall support 512 byte block packets

(P=0).

| 23 | 3. | DSSI nodes are not required to support 576 byte block    |

|----|----|----------------------------------------------------------|

| 24 |    | packets. Any such node that does not support 576 byte    |

| 25 |    | block packets should verify that P=0 in received DATREQn |

| 26 |    | packets, and treat the packet as invalid (and close the  |

| 27 |    | virtual circuit) if P=1.                                 |

- 28 3.7 Only Single Path In DSSI.

- 29 Unlike the CI, DSSI has only a single `path'.

- 30 Section 4.3 of DEC STD 161 which specifies path selections is not 31 applicable to DSSI. All senders in DSSI must set the path 32 field(s) so that it appears that path zero (0) is being used for 33 all communication. Receivers may ignore path fields.

\*\*\* R E L E A S E V E R S I O N \*\*\* Digital Equipment Corporation Confidential And Proprietary Digital's Storage System Interconnect Version 1.0.0 THE DSSI DATALINK Page 4-1 27 March 1990

| 1  | CHAPTER 4                                                                   |

|----|-----------------------------------------------------------------------------|

| 2  | THE DSSI DATALINK                                                           |

| 3  | 4.1 The DSSI Datalink                                                       |

| 4  | The datalink layer, the next to lowest tier of DSSI, is                     |

| 5  | responsible for the reliable delivery of single frames of                   |

| 6  | information over the physical channel. To meet the requirements             |

| 7  | of the port layer the datalink must:                                        |

| 8  | 1. deliver sequential, error free text from one DSSI node                   |

| 9  | to another (duplication can occur), and                                     |

| 10 | <ol> <li>perform error recovery by retransmission, only notifying</li></ol> |

| 11 | the Port Layer of failures.                                                 |

| 12 | Datalink functions are separated into two areas, higher-level               |

| 13 | mechanisms for error recovery and packet exchange with the Port             |

| 14 | layer and a low level Channel Control layer that manages the                |

| 15 | exchange of packets with the remote node over the physical                  |

| 16 | interconnect.                                                               |

| 17 | An overview of the datalink layer and a detailed description of             |

| 18 | these higher level mechanisms is presented in this chapter. A               |

| 19 | complete description of the Channel Control layer is given in               |

| 20 | chapter 5.                                                                  |

| 21 | 4.2 Overview Of A DSSI Data Transfer                                        |

| 22 | The transfer of data packets from one node to another is                    |

| 23 | accomplished by the Channel Control layer through a series of bus           |

| 24 | phases defined as the DSSI atomic bus sequence. Since bus                   |

| 25 | ownership and control remain with the sending and receiving node            |

| 26 | pair until the transfer completes, the sequence is atomic                   |

| 27 | relative to other nodes on the bus.                                         |

A simplified diagram of this sequence, omitting exception paths,

is shown below (figure 4-1).

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0THE DSSI DATALINKPage 4-2Overview Of A DSSI Data Transfer27 March 1990

| 1<br>2 |             | ++<br> Bus Free <+            |

|--------|-------------|-------------------------------|

| 2      |             |                               |

| 3<br>4 |             | · · · · · · · · · · · · · · · |

| 5      |             |                               |

| 6      |             | ++                            |

| 7      |             | Arbitration                   |

| 8      |             | ++                            |

| 9      |             |                               |

| 10     |             | V I                           |

| 11     |             | ++                            |

| 12     |             | Selection                     |

| 13     |             | ++                            |

| 14     |             |                               |

| 15     |             | +> V                          |

| 16     |             | ++                            |

| 17     |             | Cmd Out                       |

| 18     |             | ++                            |

| 19     |             |                               |

| 20     | Information | V                             |

| 21     | Transfer    | ++                            |

| 22     | Phases      | Data Out                      |

| 23     |             | ++                            |

| 24     |             |                               |

| 25     |             | V I                           |

| 26     |             | ++                            |

| 27     |             | Status In  +                  |

| 28     |             | ++                            |

| 29     |             | +>                            |

30

# Figure 4-1: Simplified DSSI Atomic Bus Sequence

After detecting the bus free phase, a node wishing to start a transfer must successfully arbitrate for exclusive bus access. The node winning arbitration, referred to as the initiator, then attempts to select a receiving node. When a response to selection is detected, the initiator passes bus ownership to the selected node, or target, who controls the remaining information transfer phases.

The transfer of a data packet requires a three-step exchange of information between initiator and target.

| 40 | 1. | During | the  | Comman | d 0 | ut phase, | , the | targ | jet solici | ts from |

|----|----|--------|------|--------|-----|-----------|-------|------|------------|---------|

| 41 |    | the    | inti | tiator | а   | 6-byte    | Comma | and  | Descriptor | Block,  |

| 42 |    | contai | ning | parame | ter | s require | ed by | the  | target's   | Channel |

\*\*\* R E L E A S E VERSION\*\*\* Digital Equipment Corporation Confidential And Proprietary Digital's Storage System Interconnect Version 1.0.0 THE DSSI DATALINK Page 4-3 Overview Of A DSSI Data Transfer 27 March 1990

- Control Layer for the Data Out phase 1 2

- 2. During the Data Out phase, the target receives and buffers a Data block containing the actual port layer 3 data packet.

- 5 3. During the Status In phase, the target returns a single 6 byte of status to the initiator. One of two values is 7 returned:

- o ACK Indicates that the data packet was received 8 and buffered successfully, 9

- 10 o NAK - Indicates a receive failure and requests retransmission. 11

- All data is transmitted via an 8-bit, parity-protected data path. 12 In addition, vertical checksums are appended to the Command 13 14 Descriptor and Data blocks.

15 Should an error occur, the initiator's datalink will attempt to 16 recover by resending the packet. If this fails, the initiator's port layer will be notified of an unrecoverable error. 17

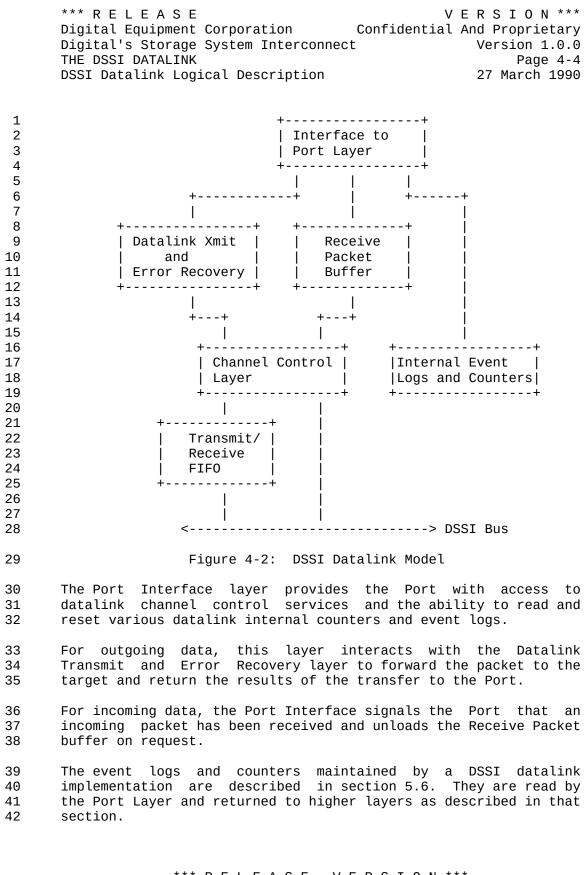

4.3 DSSI Datalink Logical Description 18

4

19 Figure 4-2 is schematic of datalink layer functions. The purpose 20 of this model is to facilitate the description of essential datalink functions. It is not meant to represent or suggest 21 22 actual implementations.

| *** R E L E A S E                     | V E R S I O N ***            |

|---------------------------------------|------------------------------|

| Digital Equipment Corporation         | Confidential And Proprietary |

| Digital's Storage System Interconnect | Version 1.0.0                |

| THE DSSI DATALINK                     | Page 4-5                     |

| DSSI Datalink Logical Description     | 27 March 1990                |

The Receive Packet Buffer represents a generic delivery site for

incoming data from the Channel Control Layer. The potential for

congestion exists when the arrival rate for incoming packets

exceeds the rate at which such packets are consumed by higher

layers.

6 The function of the Datalink Transmit and Error Recovery Layer is 7 the reliable delivery of outgoing packets to the target. It 8 initiates error recovery by retransmission according to the 9 policy described in section 4.5, notifying the port layer only 10 when an unrecoverable transmission error occurs.

As viewed by higher layers, the Channel Control Layer provides the following services:

131. Transmits outbound packets over the physical14interconnect and reports delivery status. Error-free15delivery is not guaranteed.

Buffers incoming packets, returning delivery status to

the remote node and notifying higher layers when an

error-free packet has been received.

- At the physical interconnect, this layer is responsible for the following

- 21 1. Bus arbitration,

- 22 2. Initiating and responding to target selection,

- Receipt of incoming data, including the detection of

checksum and parity errors

- Packetization of outgoing data through the addition of

parity and checksum information.

- 27 5. Detection of bus protocol errors and exceptions

- 28 6. Returning delivery status to the remote node.

The Channel Control layer provides two data transfer modes: asynchronous mode, characterized by the transfer of single bytes directly to or from the bus, and synchronous burst mode, which moves data by way of the Transmit/Receive FIFO. The less efficient asynchronous mode requires an explicit bus handshake

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0THE DSSI DATALINKPage 4-6DSSI Datalink Logical Description27 March 1990

1 for each byte transferred and thus has a throughput of 2 approximately 1.5Mb/sec. This mode is used to transmit the 3 Command Descriptor block and the Status In byte.

Synchronous burst mode is used to efficiently transfer large

blocks of data during the DATA OUT phase by pipelining requests

for data. Using this mode, a data transfer rate of 4Mb/sec can

be achieved.

- 8 4.4 Channel Control Services

- 9 The Channel Control layer provides the following services to 10 higher layers:

- 11 o Transmit a data packet and return status to higher 12 layers,

13 o Receive and buffer a data packet.

After transmitting a packet, the initiator's Channel Control Layer shall return one of the following status values to higher datalink layers:

- 17oCC\_ACK The packet was successfully transmitted. A18value of ACK was received from the target during the19STATUS IN phase.

- 20 o CC\_NAK - The Channel Control layer has detected a 'short 21 term' error, probably correctable through 22 retransmission. Such errors usually result from 23 congestion in the target node due to lack of receive 24 buffers.

25oCC\_NORSP - The Channel Control Layer has detected what26isprobably a persistent error. Such errors are27frequently caused by polling traffic addressed to28non-existent nodes.

Implementations may differ in the ability to discriminate between various error conditions. An implementation may, as a minimum, return CC\_NAK whenever a transmit request terminates with NAK status from the target, reporting all other errors with status CC\_NORSP.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0THE DSSI DATALINKPage 4-7Channel Control Services27 March 1990

When receiving a packet, the target's Channel Control Layer shall only notify higher layers, and return a STATUS IN value of ACK to the initiator, when the packet is received and buffered without error.

5 4.5 Data Transmit And Error Recovery Layer

6 This layer performs only one function: The reliable transmission 7 of a single data packet. Any failure status returned to higher 8 layers indicates a non-recoverable error.

9 In DSSI, the procedure for error recovery is to retry the failing 10 transmission. The goals of an efficient retry procedure are recovery from errors in the shortest possible time using the 11 12 fewest retransmissions. For that reason, DSSI transmission 13 failures are divided into two types: short-term, transient failures - likely to last for only a few milliseconds - and 14 persistent, long-term errors. For transient failures, caused by 15 bus errors or short-term receiver congestion, the initiator 16 17 recovers by generating a burst of retransmissions within a short 18 For persistent failures, usually caused by polling a time. 19 non-existent node, such retries are widely spaced and extend over 20 a much longer time.

- To reduce or prevent bus congestion caused by recovery traffic,

DSSI nodes use a random coin-toss to control retries during

long-term recovery.

- 24 The retry procedure consists of the following steps:

- When a transmission fails, the recovery procedure uses

the transmit status returned by the Channel Control

layer to infer whether the condition is of short- or

long-term duration.

- 2. If a transient problem is indicated, the procedure

performs up to 8 retries within approximately 2.0ms as

described in section 4.5.1.

- 32 3. If a persistent error occurs or immediate recovery

33 fails, a series of 'delayed' retry events is scheduled

34 at 10ms intervals. At each interval, the decision to

35 retransmit is made by 'coin-toss'.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0THE DSSI DATALINKPage 4-8Data Transmit And Error Recovery Layer27 March 1990

In the procedure described below, certain steps are contingent on 1 2 the existence of the target node. For DSSI implementations, the 3 probable existence of a node is determined at a protocol layer above the Datalink. To avoid knowlege of packet contents and higher layer protocols, it is assumed that the higher layer passes an appropriate 'existence' flag ( see the PL\_EXIST 4 5 6 parameter in section 4.6 ). with each outgoing data packet. For 7 8 the CI port protocol, this flag shall be set - unless the 9 following conditions are true:

- 101. The virtual circuit to the addressed port is 'closed'11and

- 12 2. The CI port data packet is 'IDREQ'

- 13 4.5.1 Error Recovery Procedure

- After a failed transmission attempt with CC\_NAK status, the sender shall perform immediate retries as described below. Otherwise the delayed retry procedure shall be executed starting at step 5.

- 182. Immediate retries shall consist of up to 8 evenly spaced19retry attempts over an interval of 2.0ms the immediate20retry duration. This represents an average of 1 retry21every 250us.

- 3. The initiator shall guarantee that immediate retries

conform to the following constraints:

- 24a. The first retransmission shall be delayed by at25least 250us from the initial attempt.

- 26b. The immediate retry duration shall be at least 2.0ms27for 90% of all immediate retries that perform 828attempts. The sender should attempt to achieve this29minimum duration for all retry sequences. If the30immediate retry limit is ever changed, the minimum31immediate retry duration shall scale linearly with32the retry limit.

- 33c. The sender may interleave immediate retries with34transmissions to other nodes. A node having several35immediate retries in progress shall limit the36aggregate rate of retries to an average of no more

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's StorageSystem InterconnectVersion 1.0.0THE DSSI DATALINKPage 4-9Data Transmit And Error Recovery Layer27 March 1990

than 1 attempt every 250us. 1 2 Immediate retries shall continue until the immediate 4. 3 retry limit is reached or a status other than NAK is 4 received after a retransmission. If immediate retries 5 fail, the sender shall perform delayed retries. Delayed retry events are scheduled at 10ms intervals. 6 5. 7 When the interval elapses, the sender shall randomly determine, by means of a 'coin-toss', whether or not a 8 retransmission is required. The sender shall retransmit 9 the failed packet according to the coin-toss result or 10 if 10 delayed retry events in a row have occurred with 11 12 no retransmission attempt. 13 The random coin-toss algorithm shall generate a sequence of 'heads' and 'tails' that is unique to each node on 14 the bus. See section 4.5.2 for an example of such an 15 16 algorithm. 17 6. If the 'existence' flag is asserted, as described above, delayed retries shall terminate when a CC\_ACK is 18 received from the Channel Control later or after 256 19 20 delayed retransmissions have occurred. 21 7. When the 'existence' flag is deasserted only a single 22 delayed retransmission shall be performed. 23 NOTE 24 While delayed retries are in progress, the sender 25 shall interleave such retries with transmissions 26 to other nodes. 27 4.5.2 Example Of Random Number Generator

The following pseudo-code is an example of a coin tossing routine that generates a random number using a seed that is unique to each node on the bus. The value returned is TAILS if the result is less than zero and HEADS otherwise.

\*\*\* R E L E A S E VERSION\*\*\* Digital Equipment Corporation Confidential And Proprietary Digital's Storage System Interconnect Version 1.0.0 THE DSSI DATALINK Page 4-10 Data Transmit And Error Recovery Layer 27 March 1990 The procedure for random number generation is derived from VMS 1 2 library routine MTH\$RANDOM. 3 The initial seed is a 32-bit integer, derived by concantenating the first three characters of the SCS system I/D and the node 4 5 number as shown in figure 4-3: 6 31 24|23 16|15 8|7 0 7 +---+ 8 | Node | Char | Char | Char | | Number| 2 | 1 | 0 9 10 +----+ Figure 4-3: Format of Unique Initial Seed 11 12 procedure coin\_toss() 13 } { All variables are 32-bit integers. 14 15 } 16 { Multiply operations generate 64-bits. The low order } 17 { 32 bits are assigned to the specified variable. The } } { high-order portion is discarded. 18 19 } 20 BEGIN 21 { Variables current\_seed and cold\_start are assigned to } 22 { static storage to preserve their values across calls. } 23 o allocate current seed in static storage. 24 o allocate cold\_start in static storage with an initial value 25 of O 26 if ( cold\_start is 0 ) then 27 BEGIN 28 o cold\_start := 1 29 o current\_seed := initial\_seed 30 END o current\_seed := ( current\_seed \* 69069 ) + 1 31 if ( current\_seed is less that 0 ) then 32 33 return ( TAILS )

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's StorageSystem InterconnectVersion 1.0.0THE DSSI DATALINKPage 4-11Data Transmit And Error Recovery Layer27 March 1990

- 1 else

- 2 return ( HEADS )

- 3 END

- 4 4.6 Interface To The CI Port Layer

5 The interface to the CI Port Layer is the highest Datalink layer. 6 As noted earlier, this layer is responsible for delivering 7 incoming data blocks to the CI Port Layer, forwarding outgoing 8 packets to the Data Transmit layer and returning transmit status.

- 9 Parameters passed to or from the Port layer with each Port layer10 packet are:

- 111. PL\_EXIST -- existence flag. For outgoing packets, set12to a non-zero value by the Port layer if the target node13is believed to exist. The rules for setting or clearing14this flag are given in section 4.5.

- DL\_DST -- for outgoing packets, the DSSI I/D of the node

to receive the packet; for incoming packets, the DSSI

I/D of this node.

- 183. DL\_SRC -- for outgoing packets, the DSSI I/D of this19node; for incoming packets, the DSSI I/D of the node20that sent the packet.

- DL\_LEN -- The length of the packet in bytes (excludes the checksum appended by the Channel Control layer).

- DL\_STATUS -- packet status passed with each packet

received or transmitted.

- 25 Possible received packet status values are:

26 - DL\_OK -- Packet successfully received in its entirety.

DL\_OVERSIZE -- Packet was successfully received into the

Datalink Receve buffer but was too large to deliver in

its entirety to the Port layer buffer. The packet is

truncated to fit into the Port layer buffer.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0THE DSSI DATALINKPage 4-12Interface To The CI Port Layer27 March 1990

- Possible transmit packet status values (after attempted error recovery) are:

- DL\_ACK -- Successful transmission. A value of ACK was

received from the target during the STATUS IN phase.

- 5 DL\_NAK -- The target exists but was unable to 6 succesfully receive the packet, most likely due to lack 7 of a Receive Packet buffer.

- DL\_NORSP -- transmission was attempted to a possibly

non-existent target node.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0THE DSSI PHYSICAL BUS PROTOCOLPage 5-127 March 1990

| 1  | CHAPTER 5                                                      |

|----|----------------------------------------------------------------|

| 2  | THE DSSI PHYSICAL BUS PROTOCOL                                 |

| 3  | 5.1 The DSSI Physical Bus Protocol                             |

| 4  | The following figure ( figure 5-1 ) shows the datalink Channel |

| 5  | Control layer, with its interfaces to the DSSI bus and higher  |

| 6  | datalink layers.                                               |

| 7  | Transmit Transmit Received                                     |

| 8  | Data Status Data                                               |

| 9  | ^ ^ ^                                                          |

| 10 | v                                                              |

| 11 | ++                                                             |

| 12 | Channel Control                                                |

| 13 | Layer                                                          |

| 14 | ++                                                             |

| 15 | ^                                                              |

| 16 | Physical Bus                                                   |

| 17 | v Protocol                                                     |

| 18 | <>                                                             |

| 19 | DSSI Bus                                                       |

20

Figure 5-1: Datalink Channel Control Layer

As indicated in the diagram, the DSSI physical bus protocol defines the interface between the Channel Control Layer and the DSSI bus. This signalling protocol, used to exchange data packets between an initiator and target over the interconnect, supports the following Channel Control services:

- Transmit a data packet, returning status to a higher

layer,

- Receive a packet, notifying higher layers only when the

packet is delivered without error.

\*\*\* R E L E A S EV E R S I O N \*\*\*Digital Equipment CorporationConfidential And ProprietaryDigital's Storage System InterconnectVersion 1.0.0THE DSSI PHYSICAL BUS PROTOCOLPage 5-2The DSSI Physical Bus Protocol27 March 1990

1 The following sections specify the logical behavior of the 2 interconnect when servicing a transmit request, including data 3 formats, bus signals, bus phases, timing, error detection and 4 conditions reported to higher datalink layers.

- 5 The electrical and physical bus requirements are specified in 6 chapter 6.

- 7 5.2 Logical Description Of The DSSI

8 The DSSI is a daisy-chained bus, connecting up to 8 nodes, that 9 uses low-cost, open-collector drivers and receivers for data 10 transfer and control. The physical bus contains 16 active 11 signals, 9 of which comprise an 8-bit, parity protected data bus.

12 The bus protocol is designed for the transfer of data in packets 13 between an initiator and target node. Other nodes are excluded 14 from the bus while such a transfer is in progress. All nodes on 15 the bus are capable of acting as either an initiator or target.

16 5.3 Signal Definitions

Signals on the bus are defined as TRUE (asserted) when low.