# digital

### equipment international

# TECHNICIAN'S HANDBOOK

1974

compiled by

Training Department

Digital Equipment International Ballybrit Galway Ireland

First Edition February 1974 Second Printing May 1974 Third Printing August 1974 Fourth Printing April 1975 Fifth Printing March 1977 Copyright © 1974, 1975, 1977 Digital Equipment International

3/77-15

# CONTENTS

| 1 | CALENDAR 1974/1975 |  |

|---|--------------------|--|

| 2 | TROUBLE SHOOTING   |  |

| 3 | GENERAL NOTES      |  |

| 4 | 8 FAMILY NOTES     |  |

| 5 | 11 FAMILY NOTES    |  |

| 6 | I.C. INDEX         |  |

| 7 | SAFETY             |  |

### FOREWORD

The content of this book is draft information which has been compiled at short notice. Please inform your Training Department of any errors, ambiguities or omissions you find.

Any comments or suggestions concerning the format, content or scope of the book would be welcomed by the Training Department.

# []

## CALENDAR 1974/1975

| NAME : |      |  |

|--------|------|--|

| AREA : | <br> |  |

|        |      |  |

|        |      |  |

Fiscal Calendar

Page

|       | 1974 FISCAL CALENDAR     |                           |                           |                           |                           |                           |                          |                |                           |                           |                           |                           |                           |                           |                          |

|-------|--------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|----------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

|       | FIR                      | ST                        | QU                        | IAR                       | TER                       | )                         |                          | THIRD QUARTER  |                           |                           |                           |                           |                           |                           |                          |

| MONTH | S                        | м                         | τ                         | w                         | τ                         | F                         | s                        | MONTH          | S                         | м                         | τ                         | W                         | τ                         | F                         | S                        |

| JUL   | 1<br>8<br>15<br>22       | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25       | 5<br>12<br>19<br>26       | 6<br>13<br>20<br>27       | 7<br>14<br>21<br>28      | JAN            | 30<br>6<br>13<br>20       | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25       | 5<br>12<br>19<br>26      |

| AUG   | 29<br>5<br>12<br>19      | 30<br>6<br>13<br>20       | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25      | FEB            | 27<br>3<br>10<br>17       | 28<br>4<br>11<br>18       | 29<br>5<br>12<br>19       | 30<br>6<br>13<br>20       | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23       |

| SEP   | 26<br>2<br>9<br>16<br>23 | 27<br>3<br>10<br>17<br>24 | 28<br>4<br>11<br>18<br>25 | 29<br>5<br>12<br>19<br>26 | 30<br>6<br>13<br>20<br>27 | 31<br>7<br>14<br>21<br>28 | 1<br>8<br>15<br>22<br>29 | MAR            | 24<br>3<br>10<br>17<br>24 | 25<br>4<br>11<br>18<br>25 | 26<br>5<br>12<br>19<br>26 | 27<br>6<br>13<br>20<br>27 | 28<br>7<br>14<br>21<br>28 | 1<br>8<br>15<br>22<br>29  | 2<br>9<br>16<br>23<br>30 |

|       | SEC                      | :ON                       | D                         | JUA                       | RTE                       | R                         |                          | FOURTH QUARTER |                           |                           |                           |                           |                           |                           |                          |

| MONTH | s                        | м                         | τ                         | w                         | τ                         | F                         | s                        | MONTH          | s                         | M                         | T                         | w                         | τ                         | F                         | s                        |

| ост   | 30<br>7<br>14<br>21      | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25       | 5<br>12<br>19<br>26       | 6<br>13<br>20<br>27      | APR            | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25       | 5<br>12<br>19<br>26       | 6<br>13<br>20<br>27      |

| NOV   | 28<br>4<br>11<br>18      | 29<br>5<br>12<br>19       | 30<br>6<br>13<br>20       | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24      | MAY            | 28<br>5<br>12<br>19       | 29<br>6<br>13<br>20       | 30<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25      |

| DEC   | 25<br>2<br>9<br>16<br>23 | 26<br>3<br>10<br>17<br>24 | 27<br>4<br>11<br>18<br>25 | 28<br>5<br>12<br>19<br>26 | 29<br>6<br>13<br>20<br>27 | 30<br>7<br>14<br>21<br>28 | 1<br>8<br>15<br>22<br>29 | JUN            | 26<br>2<br>9<br>16<br>23  | 27<br>3<br>10<br>17<br>24 | 28<br>4<br>11<br>18<br>25 | 29<br>5<br>12<br>19<br>26 | 30<br>6<br>13<br>20<br>27 | 31<br>7<br>14<br>21<br>28 | 1<br>8<br>15<br>22<br>29 |

|               | 19                       | 75                       | 5                         | FI.                       | SC                        | A                         | L                         | CAL            | ΕΛ                       | ID                        | A                         | R                         |                           |                           |                           |

|---------------|--------------------------|--------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|----------------|--------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| FIRST QUARTER |                          |                          |                           |                           |                           | THIRD QUARTER             |                           |                |                          |                           |                           |                           |                           |                           |                           |

| MONTH         | s                        | м                        | τ                         | w                         | τ                         | F                         | s                         | MONTH          | s                        | м                         | т                         | w                         | τ                         | F                         | s                         |

| JUL           | 30<br>7<br>14<br>21      | 1<br>8<br>15<br>22       | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25       | 5<br>12<br>19<br>26       | 6<br>13<br>20<br>27       | JAN            | 29<br>5<br>12<br>19      | 30<br>6<br>13<br>20       | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25       |

| AUG           | 28<br>4<br>11<br>18      | 29<br>5<br>12<br>19      | 30<br>6<br>13<br>20       | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | FEB            | 26<br>2<br>9<br>16       | 27<br>3<br>10<br>17       | 28<br>4<br>11<br>18       | 29<br>5<br>12<br>19       | 30<br>6<br>13<br>20       | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        |

| SEP           | 25<br>1<br>8<br>15<br>22 | 26<br>2<br>9<br>16<br>23 | 27<br>3<br>10<br>17<br>24 | 28<br>4<br>11<br>18<br>25 | 29<br>5<br>12<br>19<br>26 | 30<br>6<br>13<br>20<br>27 | 31<br>7<br>14<br>21<br>28 | MAR            | 23<br>2<br>9<br>16<br>23 | 24<br>3<br>10<br>17<br>24 | 25<br>4<br>11<br>18<br>25 | 26<br>5<br>12<br>19<br>26 | 27<br>6<br>13<br>20<br>27 | 28<br>7<br>14<br>21<br>28 | 1<br>8<br>15<br>22<br>29  |

|               | SEC                      | CON                      | DC                        | UA.                       | RTE                       | R                         |                           | FOURTH QUARTER |                          |                           |                           |                           |                           |                           |                           |

| MONTH         | s                        | м                        | т                         | w                         | Т                         | F                         | s                         | MONTH          | s                        | м                         | τ                         | w                         | т                         | F                         | s                         |

| ост           | 29<br>6<br>13<br>20      | 30<br>7<br>14<br>21      | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25       | 5<br>12<br>19<br>26       | APR            | 30<br>6<br>13<br>20      | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       | 4<br>11<br>18<br>25       | 5<br>12<br>19<br>26       |

| NOV           | 27<br>3<br>10<br>17      | 28<br>4<br>11<br>18      | 29<br>5<br>12<br>19       | 30<br>6<br>13<br>20       | 31<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | МАҮ            | 27<br>4<br>11<br>18      | 28<br>5<br>12<br>19       | 29<br>6<br>13<br>20       | 30<br>7<br>14<br>21       | 1<br>8<br>15<br>22        | 2<br>9<br>16<br>23        | 3<br>10<br>17<br>24       |

| DEC           | 24<br>1<br>8<br>15<br>22 | 25<br>2<br>9<br>16<br>23 | 26<br>3<br>10<br>17<br>24 | 27<br>4<br>11<br>18<br>25 | 28<br>5<br>12<br>19<br>26 | 29<br>6<br>13<br>20<br>27 | 30<br>7<br>14<br>21<br>28 | JUN            | 25<br>1<br>8<br>15<br>22 | 26<br>2<br>9<br>16<br>23  | 27<br>3<br>10<br>17<br>24 | 28<br>4<br>11<br>18<br>25 | 29<br>5<br>12<br>19<br>26 | 30<br>6<br>13<br>20<br>27 | 31<br>7<br>14<br>21<br>28 |

### TROUBLE SHOOTING

| MAINTENANCE      |       | 2.3  |

|------------------|-------|------|

| Reliability      |       | 2.4  |

| Component Failu  | ires  | 2.5  |

| Production Erro  | ors   | 2.8  |

|                  |       |      |

| TROUBLE SHOOTING |       | 2.9  |

| Fault Detection  | 1     | 2.9  |

| Fault Location   |       | 2.10 |

| Fault Rectifica  | ation | 2.15 |

| Tools            |       | 2.15 |

| Soldering        |       | 2.16 |

| IC Removal       |       | 2.18 |

.

#### MAINTENANCE

The work of the computer technician in the manufacturing environment is part of a much wider subject maintenance. Maintenance divides into two parts and our work contributes to each:

#### (a) Preventive Maintenance:

aimed at preventing unserviceability. The production of a reliable and high quality product is the foundation of the preventive maintenance programme at the customers site. The initial adjustments made during manufacture are to secure reliable as well as optimum performance.

#### (b) Corrective Maintenance:

fixing a piece of equipment which is not working properly or not working at all. In our environment there is a peculiarity - the equipment with which we deal will probably never have worked before.

Maintenance is closely related to another subject - RELIABILITY - which has a close bearing on both aspects of our work.

#### RELIABILITY

It is easy to understand that a piece of machinery must have a degree of reliability. No machine is perfectly reliable - the wear between moving parts takes care of that - but, on the other hand, few machines are totally unreliable, if we exclude those that are nearly worn out.

The reliability of a mechanism is related to its complexity and its quality and is measured as a Failure Rate (failures per "n" hours or "n" operations) or as a MEAN TIME BETWEEN FAILURES (MTBF).

Now consider a piece of electronic equipment. One might expect to encounter 100% reliability because of the lack of moving parts. Unfortunately the cycling of the components between their ON and OFF temperatures produces expansions and contractions that fatigue metal and plastics and give rise to electrical failures. Nevertheless the reliability of electronic devices is far greater than that of mechanical or electromechanical devices.

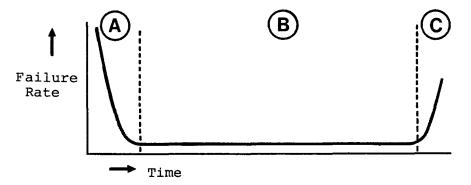

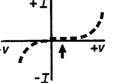

If we draw a graph of reliability against time for the working life of a batch of devices or components, the curve always comes out like this:

and three zones are easily discernible.

#### Burn-In:

where initial failures occur: when the first contact with work weeds out delicate parts and exposes weaknesses.

#### Useful Life:

with a relatively low rate of random failures.

#### Wear Out:

when old age and wear and tear combine to produce a rising failure rate.

Of these three aspects of reliability our work is governed by the first - Burn-In, because our trouble shooting and testing procedures eliminate the weak and delicate components and represent a significant fraction of the Burn-In period of the systems we ship.

In trouble shooting newly manufactured modules, assemblies and sub-assemblies, the technician has to deal with faults stemming from two main sources:

- (a) Component Failures

- (b) Production Errors

#### COMPONENT FAILURES

Table 1 summarises the commonest faults associated with components. The components are given in order of failure rates. Although the typical rates quoted are for the Useful Life part of their reliability curves, the relative order of failure rates is approximately the same during Burn-in.

| TABLE 1                      |                                                          |                                                                                                               |                                 |  |  |  |  |  |  |

|------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|

| COMPONENT                    | COMMON<br>FAULT                                          | TYPICAL CAUSES                                                                                                | % FAILURES<br>PER 1000<br>HOURS |  |  |  |  |  |  |

| Lamps                        | Open Circuit                                             | Fatigue from thermal<br>and magnetic motion<br>at ON/OFF                                                      | 1.2                             |  |  |  |  |  |  |

| Capacitors<br>(electrolytic) | Open Circuit<br>Short Circuit                            | Stressed and broken<br>connections<br>Dielectric breakdown<br>or leakage                                      | 0.2                             |  |  |  |  |  |  |

| Transistors<br>(Si-power)    | Performance<br>Change<br>Open Circuit<br>Short Circuit   | Seal or chip defect<br>Broken bond or conn-<br>ection<br>Crystalline break-<br>down - connection<br>clearance | 0.08                            |  |  |  |  |  |  |

| Capacitors<br>(paper)        | Open Circuit<br>Short Circuit                            | Stressed and broken<br>connections<br>Dielectric failure                                                      | 0.05                            |  |  |  |  |  |  |

| Transistors<br>(Ge-power)    |                                                          | See Si Power<br>Transistors                                                                                   | 0.05                            |  |  |  |  |  |  |

| Capacitors<br>Glass/Mica     |                                                          | See Paper Capacitors                                                                                          | 0.03                            |  |  |  |  |  |  |

| Relays                       | Contact<br>Failure<br>Action<br>Failure                  | Arcing - corrosion -<br>fatigue<br>Mechanical stress                                                          | 0.03                            |  |  |  |  |  |  |

| Resistors<br>(variable)      | Change in<br>value<br>Open Circuit                       | Track wear - substrat<br>cracks - turn shorts<br>Wiper or connection<br>failure                               | ce<br>0.03                      |  |  |  |  |  |  |

| I.C's.<br>(linear)           | Performance<br>Change<br>Short Circuits<br>Open Circuits | Chip and package<br>defects - stresses<br>Fouled connections<br>Broken bonds and<br>connections               | 0.03                            |  |  |  |  |  |  |

| COMPONENT                     | COMMON<br>FAULT                                | TYPICAL CAUSES                                    | <pre>% FAILURES PER 1000 HOURS</pre> |

|-------------------------------|------------------------------------------------|---------------------------------------------------|--------------------------------------|

| Zener Diodes                  | Performance<br>Change                          | Chip and package<br>defects                       |                                      |

|                               | Short Circuits                                 | Crystal failures                                  | 0.01                                 |

|                               | Open circuits<br>& intermittent<br>connections | Bond and connection failure                       |                                      |

| Switches                      |                                                | See Relays                                        | 0.01                                 |

| Transformers                  | Short Circuits                                 | Insulation failure<br>or connector clear-<br>ance | 0.01                                 |

|                               | Open Circuits                                  | rcuits Connector or wind-<br>ing failure          |                                      |

| Transistors<br>(Ge -low pwr.) |                                                | See Si-power<br>Transistors                       | 0.01                                 |

| I.C's.<br>Digital             |                                                | See I.C's linear                                  | 0.01                                 |

| Resistors<br>(WW)             | Value change                                   | shorted turns                                     | 0.01                                 |

| ()))                          | Open Circuit                                   | rcuit Fatigued winding or connector               |                                      |

| Transistors<br>(Si Low Pwr.)  |                                                | See Transistors<br>(Si-power)                     | 0.008                                |

| Multiway<br>Connectors        | High R                                         | Galvanic corrosion                                |                                      |

| connectors                    | Open Circuit                                   | Broken Pin                                        | 0.005                                |

|                               | Short Circuit                                  | Bent Pin                                          |                                      |

| Diodes                        | Performance<br>Change                          | Crystal defects                                   |                                      |

|                               | Short circuit                                  | Crystal failure                                   | 0.005                                |

|                               | Open Circuit                                   | Bond failure                                      |                                      |

| Resistors<br>(film & comp)    | Value Change                                   | Substrate cracks -<br>composition aging           | 0.005                                |

|                               | Open Circuit                                   | Cracking, connector<br>failure                    | 0.005                                |

| COMPONENT               | COMMON<br>FAULT | TYPICAL CAUSES | <pre>% FAILURES PER 1000 HOURS</pre> |

|-------------------------|-----------------|----------------|--------------------------------------|

| Connection<br>(solder)  | Open            | Fatigue        | 0.001                                |

| Connection<br>(wrapped) | Open            | Fatigue        | 0.0001                               |

#### PRODUCTION ERRORS

No matter how rigorous the inspection procedure of the production areas a percentage of errors escape detection. Some of the more common errors are listed below.

| COMPONENT  | ERRORS                                                                                                                                                                                                                                 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I.C's.     | <ol> <li>Reversed</li> <li>Wrong type</li> <li>Legs not inserted (bent under by<br/>insertion machine)</li> </ol>                                                                                                                      |

| Resistors  | <ol> <li>Wrong Value</li> <li>Wrong Place</li> <li>One connector in wrong hole</li> <li>Missing</li> <li>Additional - inserted in space<br/>intended to be vacant</li> <li>Diode or capacitor instead</li> </ol>                       |

| Diodes     | <ol> <li>Wrong type 7. Reversed</li> <li>Wrong place</li> <li>One connector in wrong hole</li> <li>Missing</li> <li>Additional - inserted in space<br/>intended to be vacant</li> <li>Resistor or capacitor instead</li> </ol>         |

| Capacitors | <ol> <li>Wrong type</li> <li>Wrong value</li> <li>Wrong place</li> <li>Connector in wrong hole</li> <li>Wrong polarity</li> <li>Diode or resistor instead</li> <li>Additional - inserted in space<br/>intended to be vacant</li> </ol> |

| COMPONENT | ERRORS                                                                                                                                                                                                                                                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Etch      | <ol> <li>Cracked tracks (sometimes two or<br/>more at same site.</li> <li>Break in track(s)</li> <li>Lifted track</li> <li>Missing etch - lifted or guillo-<br/>tined off on one or more edges</li> <li>Solder shorts</li> <li>Open circuit plated through holes</li> <li>Note - all defects may be concealed<br/>by components or handles.</li> </ol> |

| Joints    | <ol> <li>Dry</li> <li>Unsoldered</li> <li>Excess solder shorting components<br/>or tracks.</li> <li>Open circuit - apparently soldered.</li> </ol>                                                                                                                                                                                                     |

#### TROUBLE SHOOTING

The process of trouble shooting divides into three stages:

- 1. Detection of the fault

- 2. Location of the fault

- 3. Repair of the fault

#### FAULT DETECTION

This merely implies "becoming aware" of the existence of a fault. Because, in our case, the technician is the first user of the equipment this stage holds few complications. This is not true in other environments where the technician has to unravel the ideas and actions of the user - where "faulty readers" need switching on and "dead videos" need the brightness turned up.

#### FAULT LOCATION

The technician can use a number of different methods to locate a fault. He can:

- (a) Start at the output end of a system and search back towards the input until he finds the point at which the "signal" stops.

- (b) Start at the input end of the system and search forward to locate the point at which the "signal" is lost.

- (c) Start half-way between input and output and move forward to a new half-way point if the "signal" is present, or backward if not.

- (d) Cast about at random until he discovers the fault.

- (e) Gather all available information and use his power of reasoning and his theoretical knowledge to deduce which components have failed.

These methods have names. They are known respectively as:

- (a) Output to input.

- (b) Input to output

- (c) Half split

- (d) Random or non-systematic

- (e) Theoretical analysis or non-sequential.

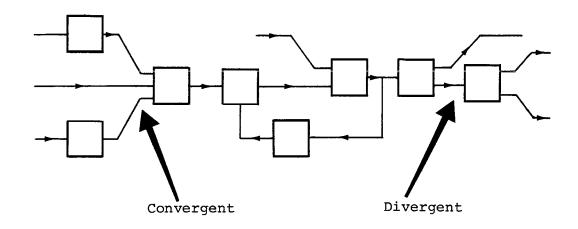

If we consider these methods applied to this functional diagram.

- (a) Output-to-input is of most use in the convergent area (a lot of combinational logic falls into this category).

- (b) Input-to-output is of most use in the divergent area.

- (c) Half split is the fastest way to identify the faulty area of the system but is applicable to a system with a long serial aspect and which, like the diagram, can be considered in "functional" blocks.

- (d) Random is difficult to justify.

- (e) Theoretical analysis, for ordinary mortals, is likely to be a technique to support either a, b, or c.

Generally speaking, a reasonable plan would be to use the half split method to localise the area of the fault and then to use output-to-input or input-to-output according to the nature of the circuitry in that area. To support the methods of fault location there are certain 'tools' at the disposal of the technician. Some of these, alone or in combination, are powerful enough to obviate the need for a formal method of fault location but this is only true when the system or fault is relatively uncomplicated. Usually these "tools" are included as techniques or aids in the location sequence. They are listed below in the order in which they should be of use when tracing an obscure fault in a large system to component level:

- a) Logical Approach Work deliberately, eliminating the irrelevant as you go so that each decision has only to be made once. Untidy thinking often sends us round the same loop of deduction several times - with varying results for each cycle.

- b) <u>Pencil and Paper</u> An invaluable aid to the previous item allowing us to work out and record the most logical approach to the fault. When having second thoughts later on we have a record of the sequence of reasoning - complete with its errors.

- c) <u>Knowledge</u> If you don't know how the thing works then you are reduced to the RANDOM method of fault location with the added disadvantage of not knowing what you are looking for. If you have only a partial knowledge then every deduction you make will be suspect and surrounded with alternatives.

- d) Experience As time passes the technician accumulates a mental file of faults which eventually separates into groups of related faults. The diary section of this book is intended to help this process.

- e) <u>Symptoms</u> Make sure that you use all of the data that the hardware offers: all lamp and register indications and switch settings. Note the effect of, and response to, manual operation. If the correct output is not obtained from a system then the incorrect output, if any, may be significant.

- f) <u>Diagnostics</u>. This is an extension of the previous item, but the power of repetitive selftesting is realised against intermittent and partial failures. Too often the reserve of diagnostic programmes is inadequately used. Make sure that the programmes and listings are up to date.

- g) <u>Programming</u>. Vital to the selection, understanding and interpretation of diagnostics and vital for the generation of your own test programmes - another neglected technique.

- h) <u>Documentation</u>. Manuals, Handbooks, Prints, Timing diagrams and Flow-charts - OF THE CORRECT REVISION. The flow-charts and timing diagrams are generally underestimated. They are the only source of dynamic information - the data is presented with the provisos of relative timing included.

- j) <u>Substitutions</u>. The location of a fault within a particular module or assembly can be confirmed by substituting an identical item that is known to be serviceable. The occasional substitution of a good module also checks the continued serviceability of the other parts of the system which may have suffered during the troubleshooting process.

- k) <u>Inspection</u>. A close examination for production errors at the suspected site can often reveal the cause of the fault.

- <u>Test Equipment</u>. The intelligent use of testequipment which is well kept and properly calibrated includes the frequent checking of its performance - 'scope probes need frequent checking.

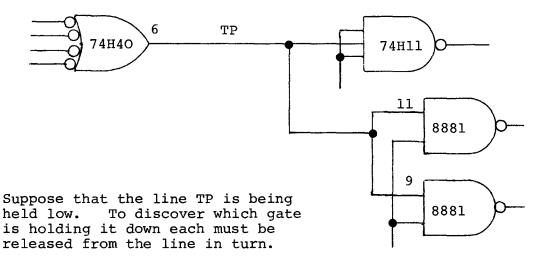

- m) <u>Hand Tools</u>. Generally associated with the repair of faults but often useful in the final stages of fault location. In this situation, for instance:

By sucking away the solder from, say - pin 6 of the 74H4O and checking that it is isolated from the etch with a multi-meter the line is disconnected from the gate (without damaging the IC) and its state can be checked.

At this final stage it is sometimes possible to combine the rectification of the fault with the last stage of fault location. If, in the example above, the two 8881's were in the same IC and one of them were known to be at fault the obvious course of action would be to change the IC.

The way in which a technician works varies from fault to fault but in each case the sequence of events will include some of the methods and techniques mentioned here. The order in which they are used is again a function of circumstances and can differ widely from the order suggested here. For instance - the half-split method may be found to be useless for identifying the faulty function at system level but ideal for pin-pointing the faulty component in a sub-assembly.

#### FAULT RECTIFICATION

The action taken to remove a fault from a system will usually involve making an adjustment or replacing a component. In both cases you will need hand tools.

#### TOOLS

Keep your tools safe and in good condition. They will stay in good condition longer if you don't lend them. Several Tools need special attention:

- a) Soldering Iron Keep at least two bits one fine point and one long chisel. The fine point serves (for technicians dealing with modules) as a general purpose bit but having such a small surface area for its volume it gets very hot and is hard to keep in good condition. It also tends to develop a pronounced hook at the tip when used for heavier work and this can lead to damage in delicate work. For heavier jobs change to a chisel bit. The occasional bit change removes the oxide dust from the element body and helps to keep the iron efficient. Bit changing can be carried out when the iron is hot by manipulating the retaining collar and hot parts with pliers. Bits should be cleaned frequently and for this reason the sponge must be moistened often. If ever the flex of the iron gets damaged or burnt have it replaced.

- b) Cutters Keep a fine pair for working on  $\overline{IC's}$ . A narrow point is needed to clip the pins cleanly. When trimming pins or leads make sure the clippings are aimed in a safe direction.

- c) <u>Solder Sucker</u> Do not modify the action of a solder sucker by tampering with the spring. The intensity of its action can be adjusted at the point of work by tilting the nozzle to allow extra air to enter. Do not use

oily or greasy lubricants in the bore of the sucker - they will destroy the internal washers. To maintain an efficient action the cylinder should be cleared of debris frequently.

#### SOLDERING

The object of a soldered joint is to join two pieces of metal for electrical continuity with a degree of mechanical strength. In the electronics industry the two pieces of metal will almost always be copper because:

- a) It is a good conductor of electricity

- b) It is relatively cheap in comparison to silver

- c) It is flexible and withstands wear

- d) It is a good conductor of heat

If an attempt is made to solder together two pieces of bare copper wire with the aid of a dry iron and some bar solder it will be impossible to produce a soldered joint. To produce a successful joint the solder must be able to flow freely into the pores of the metal: this freedom to flow is prevented by the presence of copper oxide on the surface of the metal and also by sundry other contaminants.

To remove the oxide and contamination a fairly savage flux would be needed - a substance like 'killed spirit' which would be too corrosive for our use. So, in practice we dont attack copper oxide with severe fluxes: we prevent the copper from oxidising by plating it with a thin layer of another metal which does not oxidise so readily and which solders easily ( tin and tin-lead coatings are common). The plating oxidises, of course but this oxide is easy to deal with and a mild flux is adequate. For our purposes the solder is made as a fine tube and the flux is put in the tube. Solder manufactured in the form of wire with the flux inside is known as cored solder. The flux is usually resin which is comparatively mild but strong enough to deal with ordinary surface contamination.

There are two jargon words associated with soldering:

- Wetting. When a surface of metal has a coating of bright molten solder adhering to it the surface is said to be wetted. The flowing on of the molten solder is called wetting.

- Tinned. When the wetted surface has cooled it is known as a tinned surface. A soldering iron is tinned by cleaning the bit and applying a coating of bright molten solder - in other words, by wetting the bit with solder.

To make a soldered joint:

- a) Tin the bit of the iron and wipe or shake off surplus solder.

- b) Heat the joint by applying the tip of the bit so that the joint is between you and the bit -

- c) At the same time apply the tip of the solder to the joint from the front.

- d) At the moment the joint 'wets' remove the solder and then the iron.

- e) Keep the joint perfectly still until the solder is seen to set.

The amount of solder applied to the joint is a matter of timing at the instant of wetting. The aim is to produce a joint with a concave fillet of solder -the upper photographs on page 4-62 of the Workmanship Standards Manual illustrate the required effect. Surplus solder at the joint can run through a platedthrough hole and cause solder shorts beneath components on the other side of a board. On the other hand, an attempt to make the joint with insufficient solder causes overheating and the formation of dusty oxides which the flux cannot remove.

Above all - any movement of a joint before it has set must be avoided. Movement of a setting joint produces a dry joint with a typical dull grainy appearance. Dry joints have little or no mechanical strength and electrical properties which can vary from open circuit to semi-conductor rectification.

#### I C REMOVAL

The following sequence assumes that the IC is not to be saved for re-use:

- a) Cut the legs of the IC at the top where they enter the body of the device using a pair of miniature side-cutters. Remove the body of the IC.

- b) Remove each leg by applying heat and gently withdrawing it from side 1 using a pair of fine-nosed pliers. If a leg is reluctant to move, leave it.

- c) Turn the board over and heat each hole individually, removing solder with a de-soldering tool. If any remaining leg is retained by a bend at the tip it can be straightened and the removal completed from side 1. Where no obstruction is apparent the addition of a little extra solder may facilitate removal.

- d) Clean both sides of the area with solvent and inspect for damage.

NOTES

### **GENERAL NOTES**

| OPERATIONAL AMPLIFIERS                                                                              | 3.3                                          |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------|

| Feedback<br>The Differential Amplifier<br>Virtual Earth                                             | 3.3<br>3.6<br>3.8                            |

| FLIP FLOPS                                                                                          |                                              |

| J-K Flip Flop<br>D-Type Flip Flop<br>Redefined D-Type Flip Flop<br>Set/Reset Flip Flop              | 3.10<br>3.10<br>3.11<br>3.12                 |

| MAGNETIC DATA RECORDING                                                                             | 3.13                                         |

| Pulse Recording<br>Return to Zero<br>Non-Return to Zero<br>NRZI<br>System Limitations<br>Manchester | 3.13<br>3.14<br>3.15<br>3.16<br>3.16<br>3.18 |

| THE TTL NAND GATE                                                                                   | 3.19                                         |

| Totem Pole Output                                                                                   | 3.21                                         |

| FORMULAE                                                                                            | 3.22                                         |

| LOCATION OF I.C's.                                                                                  | 3.25                                         |

| INFORMATION DIRECTORY                                                                               | 3.26                                         |

.

#### **OPERATIONAL AMPLIFIERS**

The idea of the amplifier as a 'component' to be inserted into a piece of equipment and adjusted for the required performance seems to have originated in the late 1940's. This idea became a reality in the 1960's with the arrival of the integrated circuit.

The underlying principle of such a versatile amplifier is that the parameters of an amplifier can be set by adjusting the amount of FEEDBACK between its input and output terminals.

For an 'op-amp' to be truly versatile it would need to have:

- (a) Infinite gain

- (b) Infinitely High input impedance

- (c) Zero output impedance

- (d) Infinite bandwidth

We could, of course, add small physical size and minute power consumption.

In practice the op-amp is a very high gain, wide band, direct-coupled amplifier with a performance that can be pre-set over a wide range by selecting a suitable feedback arrangement.

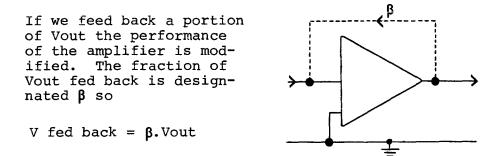

#### FEEDBACK

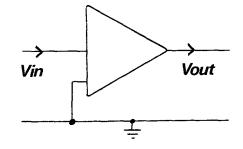

In a simple amplifier, having a gain of A

Vout =  $A \times Vin$

So, with Feedback, Vin becomes Vin +  $\beta$ .Vout and since Vout = A.Vin

$$Vin = Vin + \beta.A.Vin$$

Now Gain =  $\frac{\text{Vout}}{\text{Vin}}$

So gain with feedback,  $A' = \frac{A.Vin}{Vin + \beta.A.Vin}$

$$A' = \frac{A}{1 + A\beta}$$

Let's try an example:

Suppose we have an amplifier with a gain of 50 If Vin = 1V $\therefore$  Vout = 50VNow suppose we feedback 1% of this, i.e.  $\beta = 0.01$ Now Vin = 1 Volt + (0.01 x 50) = 1V + 0.5V= ? Remember, Vin and Vout are a.c. signals so 1V + 0.5V is a matter of relative phase. Let us exclude all but IN-PHASE and ANTI-PHASE.

If  $\beta$  is in-phase 1V + 0.5V = 1.5V so now Vin is bigger, Vout gets bigger.  $\beta$ Vout gets bigger so Vin gets bigger again ..... This is a POSITIVE FEEDBACK and gives us impressive gain figures, instability and oscillators.

Let us concentrate on the ANTI-PHASE condition:

So Vout drops to 25V and  $\beta$  drops to 0.25V.....

It is quicker to use the "gain with feedback" formulae.

$$A' = \frac{A}{1 + A\beta} = \frac{50}{1 + (50 \times 0.01)}$$

$$=\frac{50}{1.5}$$

= 33.33

So Vout settles at 33  $\frac{1}{3}$  V.

In practical op-amps, gain is very high. If we feedback a large portion of Vout

so Gain =

$$\frac{A}{1 + A\beta}$$

=  $\frac{A}{\beta A}$  =  $\frac{1}{\beta}$

So the feedback fraction sets the gain and since  $\beta$  is determined by the feedback components, the gain of an op-amp is selectable for any particular application (within reason).

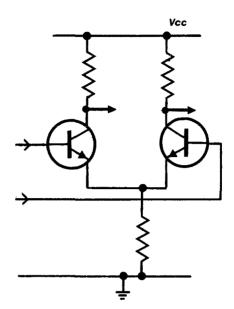

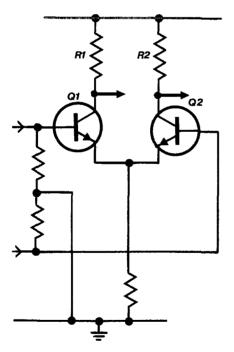

#### THE DIFFERENTIAL AMPLIFIER

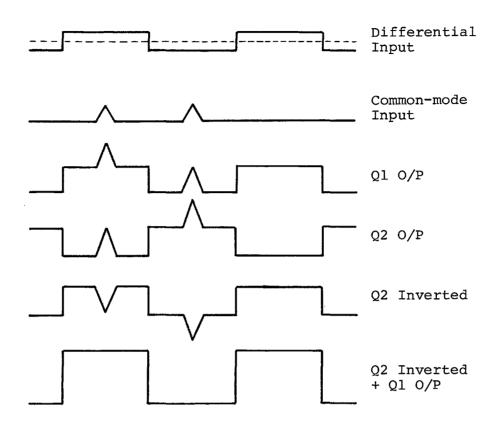

Several circuits are suitable for use as direct-coupled amplifiers but, of these, the differential amplifier has superior stability and interference rejection qualities. The dual input arrangement of this circuit gives the op-amp much of its versatility.

If Q1 and Q2 are matched and if Rl = R2 then in the quiescent state the two collectors will be at the same potential. If we apply a differential signal to the input terminals, (inputs are driven with opposite polarities) one collector potential will rise and the other will fall - in other words antiphase outputs will result. But if a signal affects both inputs equally, in the same sense (noise, for example) then both collectors will respond in phase. This in-phase response to commonmode inputs can be used to cancel interference.

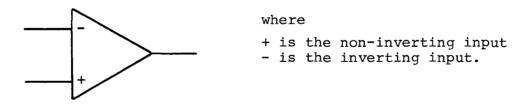

Because the differential amplifier forms the first stage of an op-amp the symbol is:

This allows the selection of either positive or negative feedback.

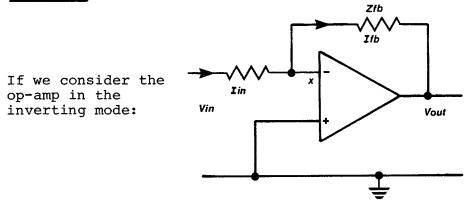

VIRTUAL EARTH

Because the gain is extremely high then the current into the amplifier at point X must be virtually zero; and if this is so then the voltage at point X must also be virtually zero. In fact, point X is a virtual Earth - approximately at ground without actually being grounded - under all operating conditions.

We must now account for Vin and Iin. Vin must be dropped across Zin and Iin can only flow through Zfb, as Ifb. So if Iin = Ifb and point X is at ground (virtual) then

| Vin  | = | _ | Vout |          |

|------|---|---|------|----------|

| Zin  |   |   | Zfb  |          |

| Vout | = | _ | Zfb  | <br>Gain |

| Vin  |   |   | Zin  |          |

This is a re-statement of the earlier argument but in a more practical context. It is also an elaboration of Fig. 2, Page 272 of the 1973-74 LOGIC HANDBOOK - part of an article on op-amps to which the reader is referred for terminology and configuration details.

#### FLIP FLOPS

If we think of flip-flops as logic elements, and not as sophisticated bistable circuits, it is surprising how little there is to know about them. Since we spend so much of our time dealing with flip-flops we must be clear about their operation.

There are certain factors common to all types of flipflop:

a) Complementary Outputs:

Every flip-flop has two outputs which we know as the 1 and  $\emptyset$  outputs. They are also called Q and Q, true and false, ON and OFF, and SET and RESET. These two outputs are usually opposite in state - if one is Hi then the other is Lo and vice-versa.

When 1 is Hi and  $\emptyset$  is Lo the flip-flop is said to be SET.

When 1 is Lo and  $\emptyset$  is Hi the flip-flop is said to be RESET.

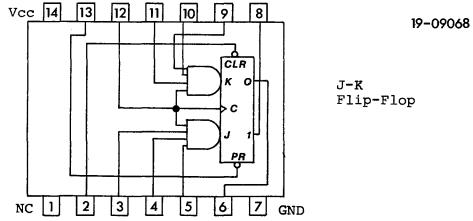

b) SET and/or RESET Inputs:

Most flip-flops have inputs which can force the outputs to a particular state. These inputs are enabled Lo. If held high they have no effect on the operation of the device. The input which forces the set condition is called SET (sometimes PRE for PRESET) and the other, which forces Reset is known as RESET.

Note: If both inputs are made Lo at the same time both outputs go Hi - normally an undesirable state.

#### c) Clock Input:

Most flip-flops have a clock input that controls the insertion of binary data. The clock pulse usually causes the flip-flop to record the input state prevailing before the pulse.

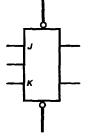

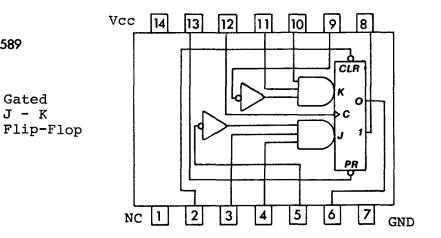

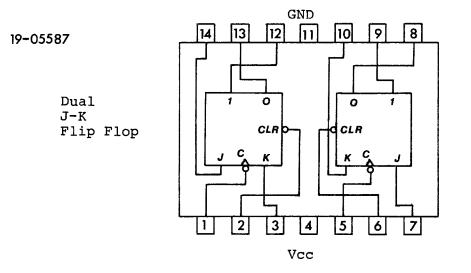

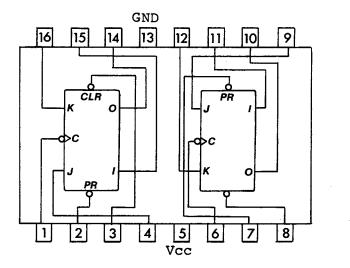

J-K FLIP FLOP

The J-K has two data inputs, designated J and K. Data applied to these inputs will not affect the outputs

UNTIL THE CLOCK PULSE ENDS. The effect the inputs have on the outputs is quite definite. On the trailing edge of the clock pulse the outputs:

Do not change if J and K are both Lo.

Complement if both J and K are Hi.

Otherwise they copy the inputs.

| Inputs |    | Outputs when Clock<br>Pulse Ends |    |

|--------|----|----------------------------------|----|

| J      | K  | 1                                | 0  |

| Lo     | Lo | No Change                        |    |

| Lo     | Hi | Lo                               | Hi |

| Hi     | Lo | Hi                               | Lo |

| Hi     | Hi | Changes                          |    |

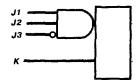

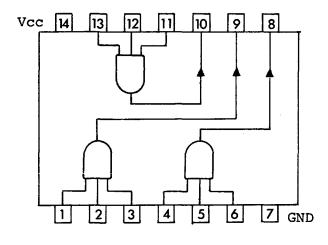

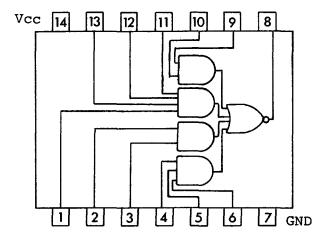

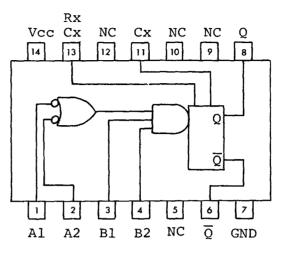

Sometimes the J or K or both inputs have combinational gating included within the device. For example:

Here the J input is determined by Jl, J2, and J3 where

$J = J1. J2. \overline{J3}$

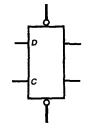

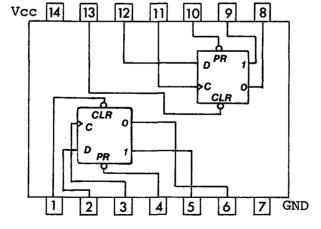

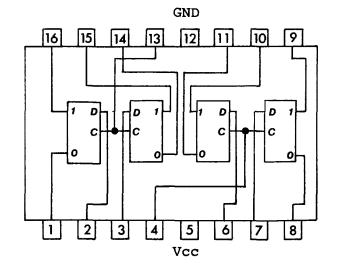

D-TYPE FLIP FLOP

The D-type has a single information input, D. The output responds to the state of the D input

AT THE START OF THE CLOCK PULSE.

It will not respond to a change of input taking place during or after the pulse. The behaviour of the D-type at the leading edge of the clock pulse is simply:

- a) If D is Lo it RESETS (or stays Reset).

- b) If D is Hi it SETS (or stays Set).

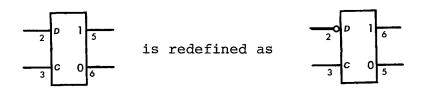

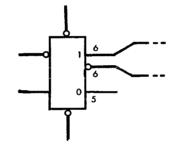

## REDEFINED D-TYPE FLIP FLOP

In modern logic circuitry many signals are true (asserted) when Lo. This means that the D-type often has its "active" condition as RESET - a state associated with "inactive". This situation is remedied by re-drawing the device with the  $\emptyset$  output in the l position and vice-versa. In other words, the pin numbers for the outputs are reversed; so for the 7474:

Notice that the sense of the D input is inverted to signify the change.

We now have a flip-flop that looks SET when responding to a Lo assertion. All that is needed now is to change the Set and Reset input titles so that their effects match the new arrangement:

This gives the final redefinition as:

One final complication. Sometimes outputs are shown twice on the same flip-flop - one for each sense of the output. In other words an output is drawn for the circuits it affects when Hi and again for those it affects when Lo.

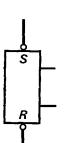

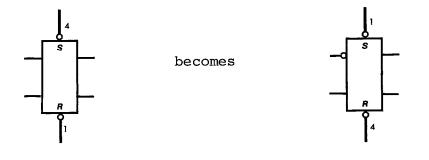

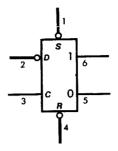

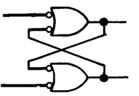

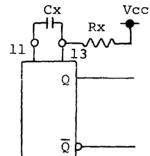

SET / RESET FLIP FLOP

This flip-flop has no clock input.

If a Lo is applied:

- (a) to the Set input the flip-flop SETS (or stays set)

- (b) to the Reset input the flip-flop RESETS (or stays Reset)

- (c) to both inputs both outputs go Hi, but on removal of the inputs the output state is unpredictable.

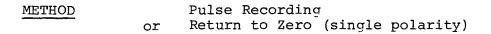

## MAGNETIC DATA RECORDING

These elementary notes summarise the methods of magnetic recording available to the engineer. Some methods not in current use are included to indicate the advantages of those that are.

The bit cell boundaries, pulse directions and field polarities have been chosen arbitrarily as innumerable variations will be encountered in practice. Alternative titles are given where a recording technique is known by more than one name.

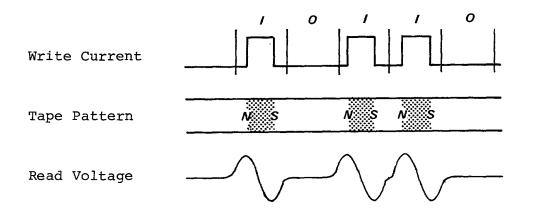

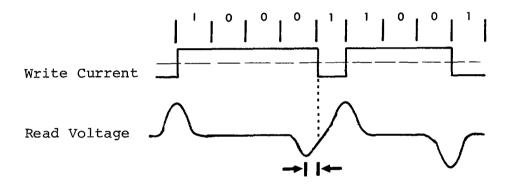

Pulses of Write Current are applied for 'ones'. Zeros are signified by absence of pulse.

Disadvantage: Since zero bit cells contain no event the data is not self-clocking.

When the tape or surface has been pre-magnetised (saturated by a D.C. erase) this method is known as Return to Saturation or Return to Bias.

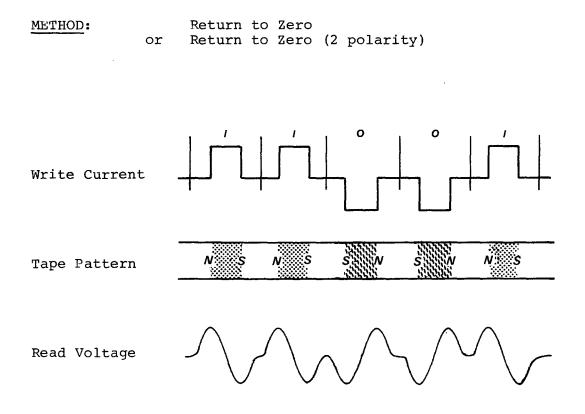

A development of the previous method with zeros written by current pulses in the opposite direction. As there is an event in each bit cell the data can be selfclocking. The greater signal range gives an improved signal to noise ratio.

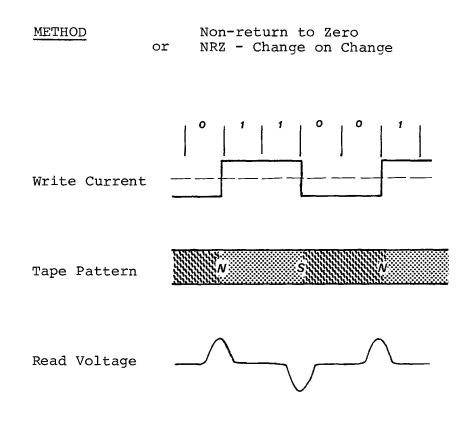

The write current reverses only on bit changes, i.e.  $\varnothing$  to 1 or 1 to  $\varnothing.$

Note that write current always flows and that data is not self-clocking as some bits are not marked by an event.

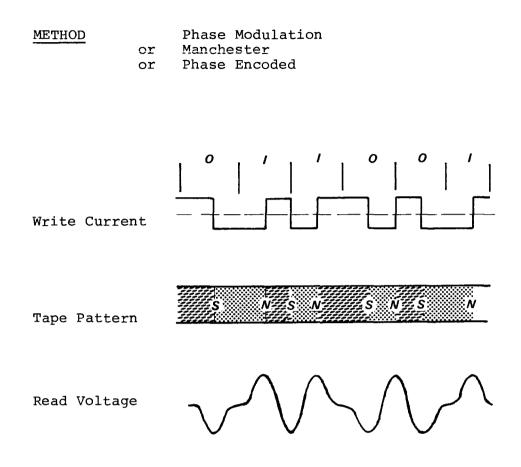

### METHOD NRZI known variously as:

| i)   | Non-return | to | Zero  | Inverted    |

|------|------------|----|-------|-------------|

| ii)  | Non-return | to | Zero  | Inhibited   |

| iii) | Non-return | to | Zero  | Incremented |

| iv)  | NRZ change | on | ones. |             |

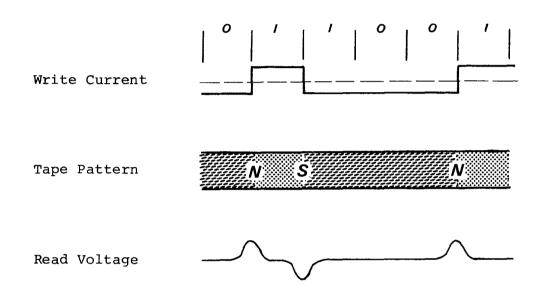

Write current reverses to indicate a 1. No reversal for a  $\ensuremath{\varnothing}$  .

Not self clocking. Preferred to NRZ as any error affects only one bit whereas an error in NRZ propagates i.e. affects all subsequent bits in the read cycle.

Used in several D.E.C. products including TU1Ø, TU2O, DF32, and RSØ8.

#### SYSTEM LIMITATIONS

The recovery of data which has been recorded using the techniques described above simply involves an amplitude detection system (and suitable clocking arrangements to mark the data times for the NRZ systems).

Noise pulses caused by tape imperfections do not usually have sufficient magnitude to be interpreted as data but any large pulse would also have to coincide with data-time in the NRZ systems.

So - error rates can be insignificant when signals have to meet both amplitude and timing standards. Unfortunately, these standards limit the amount of data we can record on a given length of surface since compression of the data produces wide variations in amplitude and timing. For example, if we raise the data rate in NRZI

certain pulses degrade both in amplitude and timing: for two reversals close together the detected voltage for the first is just getting established when the field of the next reversal influences it causing an early peak of reduced amplitude.

It is possible to overcome this deficiency of NRZI by detecting the zero-crossings instead of the peaks of the read waveform. This modified form of NRZI is used in the RK05.

NRZI used with zero-crossing (more accurately, zeroapproaching) detection gives low error rates and high data density. There remains the one major disadvantage - the data is not self-clocking - which means that in multi-track systems head skew, both static and dynamic, can interfere with the relationship between the clock and data tracks. Also, in single track systems clock information must be combined with data.

For these reasons use is often made of phase and frequency modulation techniques, the commonest of which is described overleaf.

A l is indicated by a flux reversal in one direction and a  $\emptyset$  by a reversal in the other direction. Information is retrieved by merely detecting the polarity of the output pulses.

However, some intermediate flux reversals are necessary to enable transitions of the correct polarity to be made and thus frequencies of up to twice the bit rate are encountered.

This form of recording is used in the TU60 and Dectape.

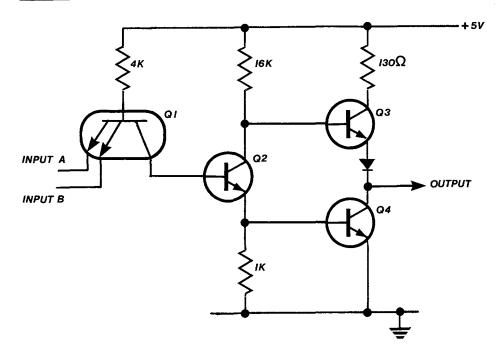

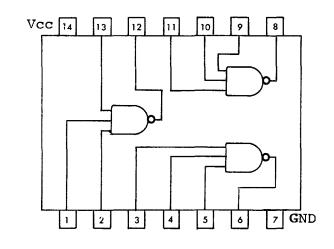

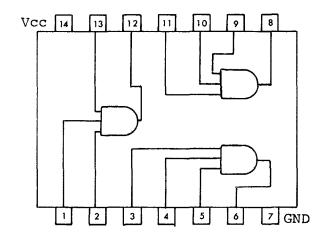

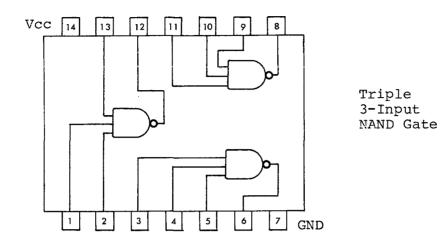

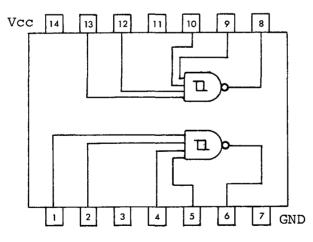

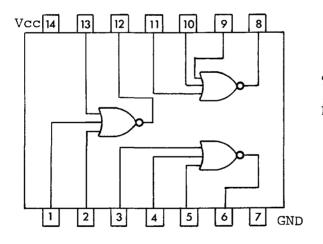

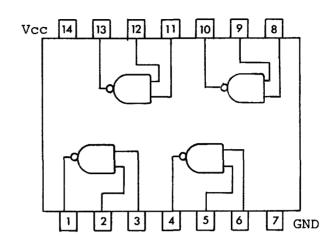

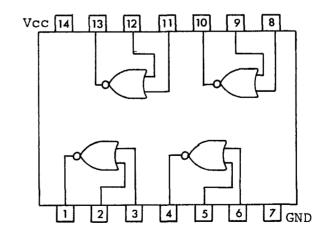

## THE TTL NAND GATE

This circuit is fundamental to the system of TTL logic and yet the conventional analytical approach to its operation is not easy to grasp, especially for the technician encountering logic for the first time.

An N-P-N transistor consists essentially of two blocks of N type semi-conductor separated by a thin layer of P-type.

We usually think of the transistor as its symbol is drawn, with the base controlling the flow of electron current from emitter to collector. But, when a transistor is used as a switch it will still work if the collector and emitter

are interchanged: both are N-type and even in discrete transistors where emitter and collector dopings are markedly different, the device will still function upside-down.

C

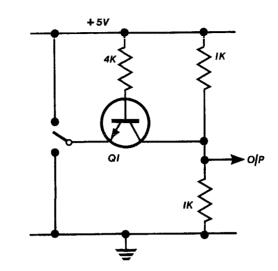

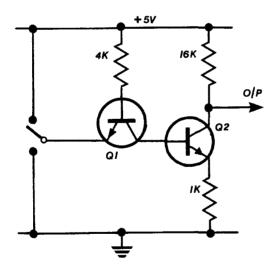

Consider this circuit:-

The emitter of the transistor can be switched to either  $\emptyset$  V or +5V. If it is taken to  $\emptyset$  V then, because the base is high it will switch the transistor on and connect the output point to  $\emptyset$  V. (O/P goes to "about"  $\emptyset$  V - in fact 0.4V = Vce (sat) for any transistor).

When the switch is taken to +5V the transistor works upside-down; the emitter behaves as a collector and the collector as an emitter. Now the transistor is on (still with its base high) but this time the output point is connected to +5V via an "ON" transistor so output goes to about +5V.

If the collector of Ql is taken to the base of a second transistor Q2, then Q2 will be cut off when the switch is to ground (because Q2 base is taken to about Ø V via Ql) and the output will rise to +5V. When the switch is at +5V, the base of Q2 is high: Q2 conducts heavily and the divider effect of the 16k and 1k resistors combined with Vce (Sat) gives an output of about 0.7V.

To provide multiple inputs Q1 is given a number of emitters. If one or more of these is taken LOW the transistor works as a normal N-P-N and Q2 is off. However, if all the emaitters are HIGH then Q1 operates in its inverted mode and turns on Q2. This gives a NAND function.

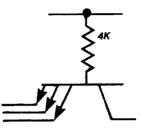

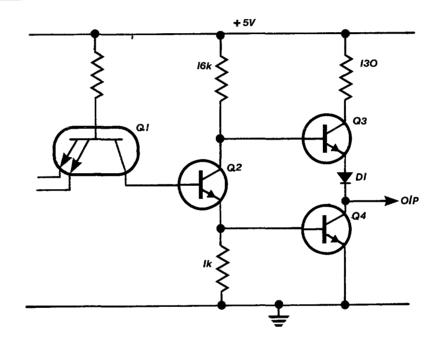

TOTEM POLE OUTPUT

Q2 is used as a phase splitter and drives a cascade pair Q3 and Q4. When Q2 is cut off its emitter is at ground and Q4 must also be off. Q2 collector is at +5V - so is Q3 base. Q3 is therefore on and the output is High.

When Q2 is conducting its emitter is a fraction of a volt above ground - enough to turn on Q4 and switch the output to ground. Q3 base is slightly higher in potential than Q4 base and Q3 would like to conduct but diode Dl has to operate in the flat part of its characteristic, just above ØV,

and limits the current to a negligible value.

| Resistors                     | $R = R_1 + R_2$                               | in series                               |

|-------------------------------|-----------------------------------------------|-----------------------------------------|

|                               | $1/R = 1/R_1 + 1/R_2$                         | in parallel                             |

|                               | $R = \frac{R_1  R_2}{R_1  +  R_2}$            | 2 in parallel                           |

| Ohms<br>Law                   | $I = \frac{E}{R} R = \frac{E}{I} E = IR$      |                                         |

| Power                         | $P = VI P = I^2 R P = \frac{E^2}{R}$          |                                         |

| Charge in<br>Capacitor        | Q = VC                                        | Q in Couls<br>C in Farads<br>V in Volts |

| Capacitors                    | $\frac{1}{C} = \frac{1}{C_1} + \frac{1}{C_2}$ | in series                               |

|                               | $C = \frac{C_1 C_2}{C_1 + C_2}$               | 2 in series                             |

|                               | $C = C_1 + C_2$                               | in parallel                             |

| Capacitive<br>Reactance       | $X_{c} = \frac{1}{2  \Pi  fc}$                | f in Hz                                 |

| Charge/<br>Discharge<br>of CR | T = 5CR                                       | T = time to<br>99.7% change             |

| CR Time -<br>constant         | T = CR                                        | T in Secs                               |

| Capacitor<br>Charge<br>State  | $V = V_s e^{-\left(\frac{t}{cr}\right)}$      | V = aiming volt<br>e = 2.7182           |

| Inductors                              | $L = L_1 + L_2$                             | in series                                         |

|----------------------------------------|---------------------------------------------|---------------------------------------------------|

|                                        | $1_{L} = 1_{L_{1}} + 1_{L_{2}}$             | in parallel                                       |

|                                        | $L = \frac{L_1  L_2}{L_1  +  L_2}$          | 2 in parallel                                     |

|                                        | $L = L_1 + L_2 + 2M$                        | series with mutua<br>inductance                   |

|                                        | $L = \frac{L_1  L_2 - M^2}{L_1 + L_2 + 2M}$ | parallel with<br>mutual inductance                |

| LR Time<br>constant                    | $T = \frac{L}{R}$                           | T in secs.<br>L in Henries.                       |

| Cha <b>rge</b> /<br>Discharge<br>of LR | $T = 5 \frac{L}{R}$                         | T = time for<br>99.7% change                      |

| Inductor<br>Charge State               | $I = I_s e^{-\left(\frac{tL}{R}\right)}$    | I in Amps<br>e = 2.7182<br>$I_s = aiming current$ |

| Inductive<br>Reactance                 | $X_L = 2 \pi fL$                            | f in Hz                                           |

| Q of Coil                              | $Q = \frac{X_L}{P}$                         |                                                   |

| Resonant<br>Frequency                  | $f = \frac{1}{2  \Pi \sqrt{LC}}$            |                                                   |

| Impedance                              | Z = R                                       | series resonance                                  |

|                                        | $Z = \frac{L}{CR}$                          | Parallel resonance                                |

|                                        | $Z = \sqrt{X^2 + R^2}$                      | X and R in series                                 |

|                                        | $Z = \frac{R}{\sqrt{R^2 + X^2}}$            | X and R in paralle                                |

|                                        | $Z = R^{\pm} jX$                            | combined impedance                                |

| Conductance | $G = \frac{1}{R}$                                                         | G in mhos                           |

|-------------|---------------------------------------------------------------------------|-------------------------------------|

| Susceptance | $B = \frac{1}{X}$                                                         | B in mhos                           |

| Admittance  | $Y = \frac{1}{Z}$                                                         | Y in mhos                           |

| Transistor  | $\text{Hfb} = \frac{\Delta I_c}{\Delta I_e}$                              |                                     |

|             | Hfe = $\frac{\text{Hfb}}{1 - \text{Hfb}} = \frac{\Delta I_c}{\Delta I_b}$ |                                     |

| Gain        | $A = \frac{Vout}{V \text{ in}}$                                           |                                     |

|             | $A' = \frac{\beta}{1 - \beta}$                                            | with feedback $\beta$ = Fb fraction |

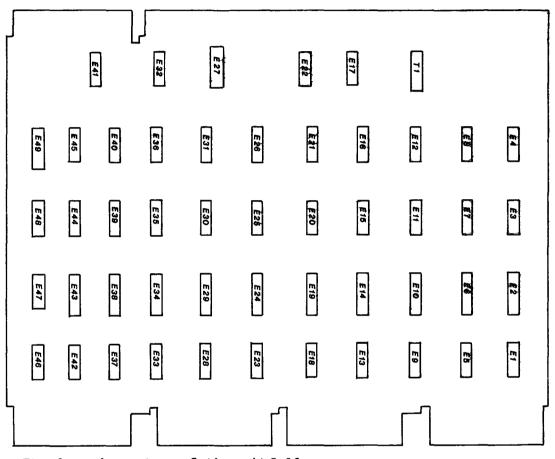

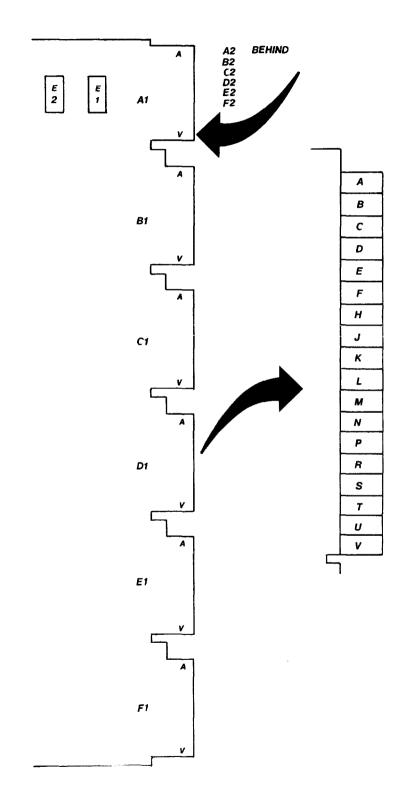

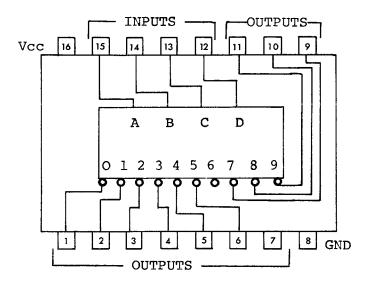

### LOCATION OF I.C's.

With the module component side up the I.C's are numbered starting beside the Al contact set. This plan of the M8330 shows the system:

It also shows two of the pitfalls:

- (a) Note that after El2 comes Tl which looks like an I.C. and could easily be included in the count. (In fact, transformers are given E numbers in some modules - G227 for example.)

- (b) I.C's. falling out of line are counted as single I.C. rows. Here E32 could be taken as part of row E33-36 and again cause misidentification.

- IF IN DOUBT CONSULT THE PRINT.

## INFORMATION DIRECTORY

In this list the abbreviations used indicate the book in which the information will be found.

| LSDH  | - | Logic System Design Handbook           |

|-------|---|----------------------------------------|

| WSM   | - | Workmanship Standards Manual           |

| LH    | - | Logic Handbook                         |

| CLW   | ~ | Computer Lab Workbook                  |

| ITDDL | - | Introduction to DEC Drawing<br>& Logic |

| SCH   | - | Small Computer Handbook                |

| ITP   | - | Introduction to Programming            |

| ITEM                                                            | REF.              | CHAPTER/PAGE            |

|-----------------------------------------------------------------|-------------------|-------------------------|

| Cable<br>characteristics<br>connections                         | LSDH<br>WSM       | Ch. 4<br>Ch. 1<br>Ch. 6 |

| types<br>Component Identifier                                   | LH<br>WSM         | 393<br>Ch. 8            |

| Decimal to Binary Conversion                                    | CLW<br>ITP        | App.F<br>Ch. 1          |

| Flip Flops<br>timing<br>signal names                            | LH<br>LH<br>ITDDL | 11<br>18<br>2.20        |

| Flow Charting<br>Flow Chart Symbols                             | SCH<br>ITP        | 3.3<br>App.C            |

| Gates<br>timing considerations<br>unused inputs<br>truth tables | LH<br>LH<br>ITDDL | 16<br>16                |

| Information Directory (cont'd)              |                     |                |                     |

|---------------------------------------------|---------------------|----------------|---------------------|

| Logic<br>levels<br>noise margins<br>symbols | LH<br>ITDDL<br>SCH  | App.A          | 9<br>2.5            |

| Noise<br>logic noise margins<br>lines       | LH<br>LSDH          |                | 9<br>81             |

| Powers of<br>eight<br>two                   | WSM<br>CLW<br>SCH   | App.G          | 8.14<br>A.35        |

| Prefixes (milli, micro, etc)                | WSM                 |                | 8.8                 |

| Resistor Codes                              | WSM                 |                | 8.3                 |

| Signal Names<br>Soldering Standards         | ITDDL<br>WSM<br>WSM |                | 2.19<br>4.43<br>7.3 |

| Wire Wrapping<br>Wire Terminations          | WSM<br>WSM          | Ch. 3<br>Ch. 7 |                     |

Information Directory (cont'd)

# 8 FAMILY NOTES

| Basic Instructions                   | 4.2  |

|--------------------------------------|------|

| Group 1 Operate Microinstructions    | 4.2  |

| Group 2 Operate Microinstructions    | 4.2  |

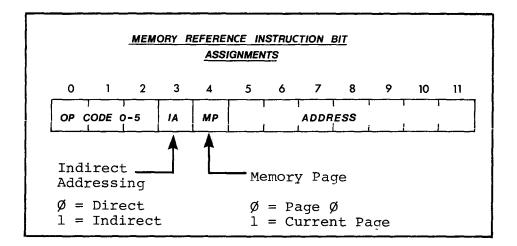

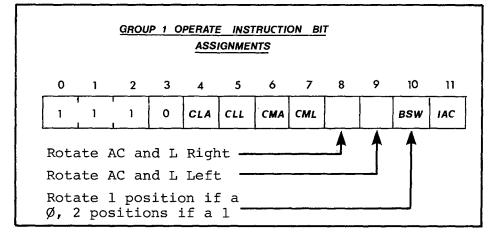

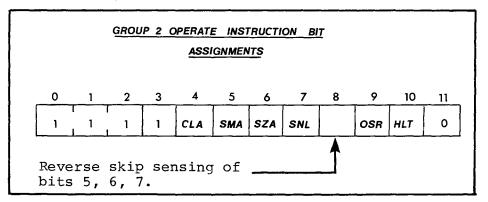

| Instruction Bit Assignments          | 4.3  |

| Rim Loaders                          | 4.4  |

| MQ Microinstruction Bit Assignments  | 4.4  |

| Memory Extension & Time Share MC8-E  |      |

| Combined Operate Microinstructions   | 4.5  |

| MQ Microinstructions                 | 4.5  |

| Internal IOT Microinstructions       |      |

| Program Interrupt and Flag           | 4.6  |

| Loading Constants into the AC        | 4.6  |

| Extended Arithmetic Element KE8-E    |      |

| Teletype Keyboard Reader             | 4.7  |

| Teletype Teleprinter Punch           | 4.8  |

| PC8-E Reader Punch                   | 4.8  |

| LE-8 Line Printer                    | 4.8  |

| TCO8-P Dectape Control               | 4.9  |

| TD8-E Dectape Control                | 4.9  |

| TA8-E DECcassette IOT Instructions   | 4.10 |

| RKO8-P Control & TKOl Disk Drive &   |      |

| Control                              | 4.10 |

| VT8-E Instructions                   | 4.11 |

| RFO8 Disk File                       | 4.12 |

| DF32-D Disk File & Control           | 4.12 |

| VC8-E CRT Display Control            | 4.12 |

| CR8-E Card Reader & Control or CM8-E |      |

| Optical Mark Card Reader & Control   |      |

| XY8-E Incremental Plotter Control    | 4.13 |

| TM8-E/F Magtape Control              | 4.14 |

| Data Transfer Signals                | 4.14 |

| ASCII Code                           | 4.15 |

| Omnibus Pin Assignments              | 4.16 |

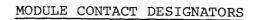

| Module Contact Designators           | 4.17 |

| Information Directory                | 4.18 |

|                                      |      |

| Mnemonic | Code | Operation                   | Time (µsec.) |

|----------|------|-----------------------------|--------------|

|          |      | BASIC INSTRUCTIONS          |              |

| AND      | 0000 | logical AND                 | 2.6          |

| TAD      | 1000 | 2's complement add          | 2.6          |

| ISZ      | 2000 | increment, and skip if zero | 2.6          |

| DCA      | 3000 | deposit and clear AC        | 2.6          |

| JMS      | 4000 | jump to subroutine          | 2.6          |

| JMP      | 5000 | jump                        | 1.2          |

| IOT      | 6000 | in/out transfer             | -            |

| OPR      | 7000 | operate                     | 1.2          |

|     |      | GROUP I OPERATE MICROINSTRUCTIONS (1.2) |          |

|-----|------|-----------------------------------------|----------|

|     |      |                                         | Sequence |

| NOP | 7000 | no operation                            | -        |

| CLA |      | clear AC                                | 1        |

| CLL | 7100 | clear link                              | 1        |

| CMA | 7040 | complement AC                           | 2        |

| CML | 7020 | complement link                         | 2        |

| RAR | 7010 | rotate AC and link right one            | 4        |

| RAL | 7004 | rotate AC and link left one             | 4        |

| RTR | 7012 | rotate AC and link right two            | 4        |

| RTL | 7006 | rotate AC and link left two             | 4        |

| IAC | 7001 | increment AC                            | 3        |

| BSW | 7002 | Swap Bytes in AC                        | 4        |

|     | GROUP 2 OPERATE MICROINSTRUCTIONS (1.2) |                               |          |  |

|-----|-----------------------------------------|-------------------------------|----------|--|

|     |                                         |                               | Sequence |  |

| SMA | 7500                                    | skip on minus AC              | 1        |  |

| SZA |                                         | skip on zero AC               | 1        |  |

| SPA |                                         | skip on plus AC               | 1        |  |

| SNA |                                         | skip on non zero AC           | 1        |  |

| SNL | 7420                                    | skip on non-zero link         | 1        |  |

| SZL | 7430                                    | skip on zero-link             | 1        |  |

| SKP | 7410                                    | skip unconditionally          | 1        |  |

| OSR | 7404                                    | inclusive OR, switch register |          |  |

|     |                                         | with AC                       | 3        |  |

| HLT | 7402                                    | halts the program             | 3        |  |

| CLA | 7600                                    | clear AC                      | 2        |  |

|                                                                                                                   |                                                                                                      | RIM_LOAL | DERS                                                                                                                                |                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| (Low                                                                                                              | Speed)                                                                                               |          | (High                                                                                                                               | Speed)                                                                                               |

| 7756/<br>7757/<br>7760/<br>7761/<br>7762/<br>7763/<br>7764/<br>7765/<br>7766/<br>7766/<br>7767/<br>7770/<br>7771/ | 6032<br>6031<br>5357<br>6036<br>7106<br>7006<br>7510<br>5357<br>7006<br>6031<br>5367<br>6034<br>7420 |          | 7756/<br>7757/<br>7760/<br>7761/<br>7762/<br>7763/<br>7764/<br>7765/<br>7766/<br>7766/<br>7770/<br>7770/<br>7771/<br>7772/<br>7773/ | 6014<br>6011<br>5357<br>6016<br>7106<br>7006<br>7510<br>5374<br>7006<br>6011<br>5367<br>6016<br>7420 |

| 7774/<br>7775/                                                                                                    | 3376<br>5356                                                                                         |          | 7774/<br>7775/                                                                                                                      |                                                                                                      |

|   |   |     | 01451 | nocric |     | 4051 | GNMENT | - |   |    |   |

|---|---|-----|-------|--------|-----|------|--------|---|---|----|---|

| 0 | ł | 2   | 3     | 4      | 5   | 6    | 7      | 8 | 9 | 10 | 1 |

| 1 | 1 | , 1 | 1     | CLA    | MQA |      | MQL    |   |   |    | 1 |

|                    | MEMORY E             | XTENSION & TIME SHARING TYPE MC8-E |                   |

|--------------------|----------------------|------------------------------------|-------------------|

| CDF<br>CIF         | 62n1<br>62n2         | Change to Instruction Field n      | 1.2<br>1.2        |

| CDI<br>CINT        | 62n3<br>6204         | Instruction Field n                | 1.2               |

| RDF                | 6204<br>6214<br>6224 | Read Data Field                    | 1.2<br>1.2<br>1.2 |

| RIB<br>RMF         | 6234<br>6244         |                                    | 1.2               |

| SINT<br>CUF<br>SUF | 6254<br>6264<br>6274 | <u>-</u>                           | 1.2<br>1.2<br>1.2 |

.

|              |                                           | and the second secon |

|--------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|              | COMBINED OPERATE MICROMISTRUCTIONS        |                                                                                                                 |

|              |                                           | Sequence                                                                                                        |

| CIA 7041     | complement and increment AC               | 2, 3                                                                                                            |

| LAS 7604     | load AC with switch register              | 2, 3                                                                                                            |

| STL 7120     | set link (to 1)                           | 1, 2                                                                                                            |

| GLK 7204     | get link (put link in AC bit 11)          | 1, 4                                                                                                            |

| CLA CLL 7300 | clear AC and link                         | 1                                                                                                               |

| CLA IAC 7201 | set $AC = 1$                              | 1, 3                                                                                                            |

| CLA CMA 7240 | set $AC = -1$                             | 1, 2                                                                                                            |

| CLL RAR 7110 | shift positive number one right           | 1, 4                                                                                                            |

| CLL RAL 7104 | shift positive number one left            | 1, 4                                                                                                            |

| CLL RTL 7106 | clear link, rotate 2 left                 | 1, 4                                                                                                            |

| CLL RTR 7112 | clear link, rotate 2 right                | 1, 4                                                                                                            |

| SZA CLA 7640 | skip if $AC = 0$ , then clear $AC$        | 1, 2                                                                                                            |

| SZA SNL 7460 | skip if $AC = 0$ or link is 1, or         |                                                                                                                 |

|              | both                                      | 1                                                                                                               |

| SNA CLA 7650 | skip if AC $\neq$ 0, then clear AC        | 1, 2                                                                                                            |

| SMA CLA 7700 | skip if $AC < O$ , then clear AC          | 1, 2                                                                                                            |

| SMA SZA 7540 | skip if AC $\leq$ 0                       | 1,                                                                                                              |

| SMA SNL 7520 | skip if $AC < O$ or link is 1, or         |                                                                                                                 |

|              | both                                      | 1                                                                                                               |

| SPA SNA 7550 |                                           | 1                                                                                                               |

| SPA SZL 7530 | skip if AC $\geqslant$ O, and if the link |                                                                                                                 |

|              | is O                                      | 1                                                                                                               |

|              | skip if AC $\geqslant$ O, then clear AC   | 1, 2                                                                                                            |

| SNA SZL 7470 | skip if AC $\neq$ 0 and link = 0          | 1                                                                                                               |

|          |      | MQ MICROINSTRUCTION             | · · · · · · · · · · · · · · · · · · · |

|----------|------|---------------------------------|---------------------------------------|

|          |      | Time                            | (µsec.)                               |

| NOP      | 7401 | No operation                    | 1.2                                   |

| CLA      | 7601 | Clear AC                        | 1.2                                   |

| MQL      | 7421 | Load MQ from AC then Clear AC   | 1.2                                   |

| MQA      | 7501 | Inclusive OR the MQ with the AC | 1.2                                   |

| CAM      | 7621 | Clear AC and MQ                 | 1.2                                   |

| SWP      | 7521 | Swap AC and MQ                  | 1.2                                   |

| ACL      | 7701 | Load MQ into AC                 | 1.2                                   |

| CLA, SWP | 7721 | Load AC from MQ then Clear MQ   | 1.2                                   |

|      |              | INTERNAL IOT MICROINSTRUCTIONS<br>PROGRAM INTERRUPT AND FLAG |              |

|------|--------------|--------------------------------------------------------------|--------------|

|      |              |                                                              | Time (µsec.) |