# DECstation 3100 Desktop Workstation Functional Specification

**Revision 1.3**

Workstation Systems Engineering Digital Equipment Corporation 100 Hamilton Avenue Palo Alto, CA 94301

August 28, 1990

## August 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibilty for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

Digital Equipment Coporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by Digital or its affiliated companies.

© Digital Equipment Corporation 1990. All Rights reserved Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

| DEC        | DECnet   | DECstation | DECsystem    | DECUS      |

|------------|----------|------------|--------------|------------|

| MicroVAX   | MicroVMS | PDP        | TURBOchannel | ULTRIX     |

| ULTRIX-32  | UNIBUS   | VAX        | VAXBI        | VAXcluster |

| VAXstation | VMS      | VT         |              |            |

--

Blank Page

# **Table of Contents**

# 1. DECstation 2100/3100 Desktop Workstation

## 2. External Interface

# 3. Power Requirements

# 4. Address Map

# 5. Interrupts

# 6. Subsystems

| 6.1. Processor                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 6.2. Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                  |

| 6.3. ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                  |

| 6.4. Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                  |

| 6.4.1. Control And Status Register 6.4.2. Receiver Buffer Register                                                                                                                                                                                                                                                                                                                                                                                         | 6<br>8<br>9                                        |

| 6.4.3. Line Parameter Register 6.4.4. Transmit Control Register                                                                                                                                                                                                                                                                                                                                                                                            | 11                                                 |

| 6.4.5. Modem Status Register 6.4.6. Transmit Data Register                                                                                                                                                                                                                                                                                                                                                                                                 | 11<br>12                                           |

| 6.5. SCSI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13                                                 |

| 6.5.1. SII Registers                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14                                                 |

| 6.5.1.1. SII_SDB - SCSI Data Bus 6.5.1.2. SII_SC1 - SCSI Control Signals One 6.5.1.3. SII_SC2 - SCSI Control Signals Two 6.5.1.4. SII_CSR - Control/Status Register 6.5.1.5. SII_ID - Bus ID Register 6.5.1.6. SII_SLCSR - Selector Control And Status Register 6.5.1.7. SII_DESTAT - Selection Detector Status Register 6.5.1.8. SII_DATA - Data Register 6.5.1.9. SII_DMCTRL - DMA Control Register 6.5.1.0. SII_DMCTRL - DMA Length Of Transfer Counter | 15<br>15<br>16<br>16<br>17<br>17<br>18<br>18<br>18 |

| 6.5.1.10. SII_DMLOTC - DMA Length Of Transfer Counter                                                                                                                                                                                                                                                                                                                                                                                                      | 19                                                 |

6.5.1.11. SII\_DMADDR - DMA Address Registers ..... 19 6.5.1.12. SII\_DMABYTE - DMA Initial Byte Register ...... 6.5.1.13. SII\_CSTAT - Connection Status Register ..... 20 6.5.1.14. SII DSTAT - Data Transfer Status Register ..... 22 6.5.1.15. SII COMM - Command Register ..... 22 6.5.1.16. SII\_DICTRL - Diagnostic Control Register ..... 24 6.5.2. Commands ..... 24 6.5.2.1. Immediate Commands 6.5.2.1.1. Chip Reset ..... 24 6.5.2.1.2. Disconnect 25 6.5.2.2. Complex Commands 25 6.5.2.2.1. Request Data ..... 25 6.5.2.2.2. Select 25 6.5.2.2.3. Information Transfer Command 26 6.5.3. SCSI Operations 27 6.5.3.1. Initiator Selection Of A Target ..... 27 6.5.3.2. Initiator Selection With ATN Of A Target ...... 28 6.5.3.3. Target Reselection Of An Initiator 28 6.5.3.4. Information Transfers 29 6.5.3.4.1. Initiator DMA Information Transfers 6.5.3.4.2. Initiator Programmed I/O Transfers ..... 30 6.5.3.4.3. Target DMA Information Transfers ..... 31 6.5.3.4.4. Target Programmed I/O Transfers ..... 32 6.5.3.5. Initiator Setting ATN 33 6.5.3.6. SII Setting RST 33 6.5.3.7. Command Chaining 33 6.6. Network Interface 36 6.6.1. LANCE Chip Overview 36 6.6.2. Programming of the LANCE 37 6.6.2.1. Register Address Port (LANCE\_RAP) 37 6.6.2.2. Register Data Port (LANCE RDP) 38 6.6.2.3. Control and Status Register 0 (LANCE CSR0) 6.6.2.4. Control and Status Register 1 (LANCE\_CSR1) ..... 41 6.6.2.5. Control and Status Register 2 (LANCE\_CSR2) 42 6.6.2.6. Control and Status Register 3 (LANCE\_CSR3) 42 6.6.3. Interrupts 43 6.6.4. DMA Operation ..... 43 6.6.5. Initialization Block 43 6.6.5.1. Initialization Block MODE Word (NIB\_MODE) ..... 44 6.6.5.2. Network Physical Address (NIB\_PADR) 46 6.6.5.3. Multicast Address Filter Mask (NIB LADRF) 47 6.6.5.4. Receive 6.6.5.5. Transmit Descriptor Ring Pointer (NIB\_TDRP) 48

| 6.10.2. Updating the Overlay Map | 74 |

|----------------------------------|----|

| 6.10.3. Grey-scale Displays      | 74 |

| 6.11. Color Plane Mask           | 74 |

| 6.12. Monochrome Frame Buffer    | 74 |

| 6.13. Color Frame Buffer         | 75 |

| 6.14. Video Timing               | 75 |

| 6.15. Reset Switch               | 76 |

-

# **Revision History**

| Date      | Version | Content/Changes                              |

|-----------|---------|----------------------------------------------|

| 22 Aug 88 | 1.0     | First release                                |

| 3 Nov 88  | 1.1     | Added parity disable bit to system CSR       |

|           |         | Specified VDAC output comparator resolution  |

| 24 Mar 89 | 1.2     | Updated power supply requirements            |

|           |         | Updated reliability data                     |

|           |         | Added video timing                           |

|           |         | Changed to company confidential distribution |

| 23 Aug 89 | 1.3     | Changed name to DS3100                       |

|           |         | Added references to DS2100                   |

|           |         | Eliminated reliability data                  |

|           |         | Changed to general distribution              |

<del>--</del>

Blank Page

#### 1. DECstation 2100/3100 Desktop Workstation

\_\_\_\_\_

This is the functional specification for the DECstation 3100/2100 desktop workstations. The DS3100 has a processor with slightly more than 11 times the performance of a VAX 11/780, up to 24 Mbytes of memory, and integral disk, network, serial and monochrome or color bitmap graphics interfaces. The DS2100 is identical to the DS3100, except for running at 12MHz, only differing by the lower cost processor and cache chips the slower clock speed allows, with a performance slightly greater than eight times a VAX 11/780. Elsewhere in this document, DS3100 will be used to refer to either machines. This specification describes the workstation subsystems, and describes the software interface of VLSI devices on the module.

The DS3100 desktop workstation is designed for use in a diskless networked environment, in a networked environment with local SCSI peripherals, or as a stand-alone workstation. DS2100/3100 contains the following subsystems on the KN01 system module:

- R2000/R2010/R2020 12.0 or 16.67 MHz CPU/FPU/WB

- 64 KByte instruction cache

- 64 KByte data cache

- 4 to 24 Mbytes of parity protected memory in 4 MByte increments

- 256 KByte boot ROM

- Serial lines for keyboard, mouse, modem, and printer

- Disk/tape interface for SCSI peripherals

- Network interface for ThickWire Ethernet

- Integral ThinWire Ethernet transceiver

- System clock

- 50-byte battery-backed-up (BBU) RAM

- VFB01 1024-by-864 pixel, 1-plane, monochrome frame-buffer option

- VFB02 1024-by-864 pixel, 8-plane, color frame-buffer option

- 16 by 16 pixel, 2-plane graphics cursor

- 8-plane write mask for color frame buffer

- System control and status register

- Reset switch

The KN01 system module accepts up to 12 MS01 memory option modules, with two modules required per 4 MByte memory bank. The KN01 also accepts either a VFB01 monochrome frame buffer or a VFB02 color frame buffer option module. The monochrome option is compatible with the VR150 15-inch monochrome monitor or the VR262 19-inch monochrome monitor. The color option is compatible with the VR297 16-inch color monitor or the VR299 19-inch color monitor. The system module is designed for use with the LK201 or LK401 keyboard, and the VSXXX-AA mouse. The SCSI interface supports up to seven SCSI peripherals such as the RZ23 3.5-inch disk drive or the RZ55 5.25-inch disk drive. The KN01 is compatible with the VAXstation 3100 system enclosure.

The following sections describe the KN01 system module configured with MS01 memory options and VFB01/VFB02 frame buffer options. Further discussion of external peripherals or packaging options is beyond the scope of this document.

The memory SIM connectors are specified for a maximum of 25 insertion/removal cycles. Limiting insertion/removal cycles to 5 is recommended.

2. External Interface

The rear bulkhead has the following external interfaces:

- AC power switch

- AC line receptacle

- AC convenience receptacle for video monitor

- 8 red status LEDs

- Modem MMJ-6 female connector with DTR, TX, RX, and DSR DEC423/EIA-232-D compatible signals

- Printer MMJ-6 female connector with TX and RX DEC423/EIA-232-D compatible signals

- Video DB15 male connector with RS343A/RS170 compatible signals

- Mouse DIN7 female connector with TX and RX EIA-232-D compatible signals, +12 Volts at 300 mAmps, +5 Volts at 150 mAmps, and -12 Volts at 20 mAmps

- Keyboard MMJ-4 female connector with TX and RX EIA-232-D compatible signals and +12 Volts at 300 mAmps

- Momentary push-button reset switch

- ThinWire Ethernet BNC female connector to internal ThinWire transceiver

- ThinWire-selected green status LED

- Latching push-button selector switch for Thin/Thick Ethernet interface

- ThickWire-selected green status LED

- ThickWire Ethernet DB15 female connector for external ThickWire transceiver

- SCSI HONDA68 male connector

#### 3. Power Requirements

DECstation 2100/3100 electronics has a theoretical maximum power dissipation of 81 Watts. Table 3-1 lists the theoretical worst case power supply requirements for a 24 MByte, color, diskless DECstation 3100. The worst case supply requirements include power provided to external LK201 keyboard, VSXXX-AA mouse, external ThickWire transceiver, and external SCSI terminator. The typical supply currents include power for a keyboard and mouse. All currents are for steady state conditions.

Table 3-1: Supply Requirements

| Supply (Volts) | <b>Maximum Current (Amps)</b> | <b>Typical Current (Amps)</b> |

|----------------|-------------------------------|-------------------------------|

| +5 +/-5%       | 15.6                          | 10.0                          |

| +12 +/-5%      | 0.89                          | 0.07                          |

| -12 +/-5%      | 0.11                          | 0.04                          |

| -9 +/-5%       | 0.18                          | 0.13                          |

#### 4. Address Map

The R2000 CPU has a 4 GByte virtual address space consisting of four regions. Table 4-1 lists these regions. Note that the KSEG0, KSEG1, and KSEG2 regions are only accessible while the R2000 is in kernel mode. Refer to the R2000 Processor Architecture for a detailed discussion of its virtual address space.

Table 4-1: R2000 Virtual Address Space

| Address Range        | Size (GBytes) | Region | Properties            |

|----------------------|---------------|--------|-----------------------|

| 0x000000000x7FFFFFF  | 2.0           | KUSEG  | Mapped and cached     |

| 0x800000000x9FFFFFF  | 0.5           | KSEG0  | Unmapped and cached   |

| 0xA00000000xBFFFFFFF | 0.5           | KSEG1  | Unmapped and uncached |

| 0xC00000000xFFFFFFF  | 1.0           | KSEG2  | Mapped and cached     |

The DS3100 workstation has a 512 MByte physical address space. Physical addresses beyond this range are reserved and must not be referenced. The first 256 MBytes of the physical address space are considered memory space. The second 256 MBytes of physical address space are considered I/O space with I/O subsystems decoded on 16 MByte boundaries. Table 4-2 summarizes the primary address space decoding of the workstation. Note that memory and the frame buffer are listed at both their KSEG0 and KSEG1 addresses. These are aliases of the same physical storage locations and cache data inconsistencies may result if they are referenced through both of the KSEG0 and KSEG1 regions.

Table 4-2: System Address Map

| Address Range        | Subsystem                                   |

|----------------------|---------------------------------------------|

| 0x000000000x7FFFFFF  | KUSEG                                       |

| 0x800000000x817FFFF  | Memory                                      |

| 0x818000000x8FBFFFFF | Reserved                                    |

| 0x8FC000000x8FCFFFFF | Frame buffer                                |

| 0x8FD000000x9FFFFFFF | Reserved                                    |

| 0xA00000000xA17FFFFF | Memory (uncached)                           |

| 0xA18000000xAFBFFFFF | Reserved                                    |

| 0xAFC000000xAFCFFFFF | Frame buffer (uncache)                      |

| 0xAFD000000xAFFFFFF  | Reserved                                    |

| 0xB00000000xB0FFFFF  | Color plane mask                            |

| 0xB10000000xB1FFFFF  | Cursor (PCC)                                |

| 0xB20000000xB2FFFFFF | Color map (VDAC)                            |

| 0xB30000000xB6FFFFFF | Reserved                                    |

| 0xB70000000xB7FFFFF  | Write error address                         |

| 0xB80000000xB8FFFFFF | Network interface (LANCE)                   |

| 0xB90000000xB9FFFFF  | Network buffer (64 KBytes)                  |

| 0xBA0000000xBAFFFFF  | SCSI interface (SII)                        |

| 0xBB0000000xBBFFFFFF | SCSI buffer (128 KBytes)                    |

| 0xBC0000000xBCFFFFFF | Serial interface (DZ)                       |

| 0xBD0000000xBDFFFFF  | Real-time-clock/battery-backed-up-RAM (RTC) |

| 0xBE0000000xBEFFFFF  | Control/status register (SYS_CSR)           |

| 0xBF0000000xBFFFFFF  | Self-test/bootstrap ROM                     |

| 0xC00000000xFFFFFFF  | KSEG2                                       |

I/O subsystems generally do not occupy their entire 16 MByte region. References to portions of I/O subsystem address space not explicitly defined in the following sections should not be issued. DS3100 contains a bus timer that aborts I/O space transactions that do not complete within 128 cycles (7.68 microseconds). Aborted read transactions result in a bus error exception. Aborted write transactions result in a memory error (MEMERR) interrupt.

Memory, the frame buffer, and the ROM are non-volatile (in the programming sense) and may be cached. The network buffer, SCSI buffer, color plane mask, cursor, color map, write error address, LANCE, SII, DZ, RTC, and SYS\_CSR are volatile and must never be cached.

The R2000 CPU is configured for little-endian byte order. All address space descriptions in this

document are correspondingly little-endian.

## 5. Interrupts

Table 5-1 lists the I/O device connections to the R2000 interrupt inputs. The state of the interrupt signals is continually reflected in the R2000 CAUSE register at the bit position shown in the table. Note that a given interrupt signal only generates an R2000 exception if it is enabled in the STATUS register interrupt mask field, and interrupts are enabled by the STATUS<0> register bit. Note also that the interrupt signals are visible in the CAUSE register regardless of the state of the STATUS interrupt mask. That is, the operating system interrupt dispatcher must explicitly check that a given interrupt level, which is asserted in the CAUSE register, is enabled before activating that interrupt level's handler.

Table 5-1: I/O Interrupt Levels

| Level | CAUSE/STATUS | I/O Device     |

|-------|--------------|----------------|

| 5     | 15           | FPU            |

| 4     | 14           | VINT or MEMERR |

| 3     | 13           | RTC            |

| 2     | 12           | DZ             |

| 1     | 11           | LANCE          |

| 0     | 10           | SII            |

#### 6. Subsystems

#### 6.1. Processor

The DS3100 processor is composed of the R2000 scalar processor, R2010 floating point coprocessor, and R2020 write buffers. The R2000 chipset operates at 16.67 MHz resulting in average processing performance of 12 million instructions per second (MIPS) over a range of applications.

The R2000 CPU implements the instruction set, processor registers, virtual memory, and interrupt system as defined by the R2000 architecture. The CPU maintains the direct-mapped instruction cache and the direct-mapped, write-through data cache. Each cache is 64 KBytes in capacity with a 4-byte line size. The tag and data stores of each cache are byte-parity protected, with cache parity errors transparently generating cache misses to reload the cache from memory. Operating system software should poll the CPU STATUS<PE> bit in its clock-interrupt handler to detect excessive rates of cache parity errors.

The R2010 FPU implements the IEEE arithmetic functions and coprocessor registers as defined by the R2000 architecture. The FPU is coprocessor 1 to the CPU. The FPU interrupts at level 5, which is visible in the R2000 CAUSE<15> register bit.

The R2020 WB implements a 4-stage write buffer for the CPU. The WB functions as part of coprocessor 0 to the CPU. Software may determine whether or not the WB is empty by conditionally branching on the coprocessor 0 condition (BC0F branches if WB is non-empty). If the CPU issues an I/O read immediately after a write, the I/O read will be completed before the write due to pipeline latency in the WB. Consequently, operating system device drivers must explicitly wait for the WB to drain after modifying I/O buffers or device registers, before reading device registers which have volatile state affected by the write. Note that this restriction does not apply to memory locations as the hardware automatically detects and corrects such conflicts.

In the event of a bus timeout on a memory write, the WB latches the write address, asserts the SYS\_CSR<MEMERR> bit, and generates a level 4 interrupt, which is visible in the R2000 CAUSE<14>

register bit. The write error address may be read at address 0xB7000000. Note that in the event of multiple write errors, the WB error address latch records the address of the last error which occurred.

If a bus timeout occurs on an I/O read, or a parity error occurs on a memory read, then a bus-error exception results. Processor state is preserved and exception processing initiated as defined by the R2000 architecture. In the case of a memory parity error caused by a soft error, there is no direct record of which byte(s) of the word caused the parity error. To localize the error, the operating system handler may selectively rewrite bytes in the indicated word, and then reread the location until parity errors no longer occur.

Hard memory bit errors may be isolated by disabling parity checking via the system CSR<PARDIS> bit and memory test patterns.

#### 6.2. Memory

The DS3100 system module supports 4 to 24 MBytes of byte-parity protected DRAM in 4 MByte increments. The memory system includes both the DRAM-based memory array and the VRAM-based video frame buffer. The frame buffer has the same memory access characteristics as memory, and may be cached if desired. The memory system supports byte (8-bit), half-word (16-bit), word (32-bit) writes, and word reads as per the R2000 instruction set.

The memory array starts at address 0x80000000 (in KSEG0) through the size of the array. The frame buffer starts at address 0xAFC00000 (in KSEG1) through the size of the frame buffer. Note that memory is only decoded with 32 MByte resolution, consequently the array is aliased eight times through the 256 MByte physical memory space. The memory array and frame buffer should only be referenced at the addresses defined above for future compatibility.

The memory subsystem serves only the processor, there is no I/O device DMA support. Operating system device drivers must explicitly copy network and SCSI data between buffers and user memory. Since there is no I/O DMA, the caches never need to be flushed.

The memory system control logic is optimized for minimum memory read latency, at a slight cost in memory write latency. On a memory read, the CPU incurs a 5 cycle stall in the absence of memory refresh contention. The memory system can sustain 5 cycle reads resulting in a peak read bandwidth of 13.3 MBytes/second.

Memory writes to an empty WB complete in 8 cycles, but do not stall the CPU. Successive memory writes complete at the rate of 6 cycles, with the CPU stalled whenever the write buffer is full. The memory system can sustain 6 cycle writes resulting in a peak write bandwidth of 11.1 MBytes/second.

Memory refresh occurs once each 18.5 microseconds and reloads the VRAM shift registers and runs two RAS-only DRAM refresh cycles. CPU memory access during refresh can result in up to 16 cycles of additional latency; a 5% overhead.

The DRAM memory array is implemented with MS01 single-inline memory modules (SIMMs), each implementing 1-M-by-18 bits of memory. Two SIMMs are required for a 4 MByte bank of memory. The system modules supports from 1 to 6 banks. The mono or color frame buffer is also implemented with a VFB01 or VBF02 SIMM.

If a soft error occurs in a text segment, the operating system should mark the page as swapped-out and reload from backing store. If a soft error occurs in a data or stack segment, the operating system should terminate the affected process.

Parity checking on memory reads is normally enabled. Consequently, after a restart exception, all

memory should be written before it is read to initialize the parity bits. For diagnostic isolation of memory errors, parity checking may be disabled by asserting the PARDIS bit in the system control and status register.

#### 6.3. ROM

Workstation self-test and bootstrap software is resident in 256 KBytes of ROM starting at address 0xBFC00000. Reads to the ROM stall the CPU for 8 cycles. The ROM is in sockets.

Since the ROM does not contain parity, it is recommended that power-up-self-test software calculate and verify a checksum on the ROM contents.

#### **6.4.** Serial Interface

The quad asynchronous serial interface, based upon the DC7085 gate array, presents a DZ software interface and a DEC423/EIA-232-D electrical interface. The serial transmitters are double buffered, while the receivers share a 64-entry FIFO. The baud rate of each serial line is independently programmable to 50 through 9600 bits per second.

The keyboard, mouse, and printer lines are data leads only, while the modem line also supports DTR/DSR control signals. The keyboard line is available via a 4-pin MMJ connector. The mouse line is available via a 7-pin DIN connector. The printer and modem lines are available via 6-pin modular connectors. The keyboard and mouse connectors supply power (through current limit devices) to the external devices. Table 6-1 lists the binding of devices to serial lines.

Table 6-1: Serial Device DZ Line Numbers

| DZ Line | Serial Device |

|---------|---------------|

| 0       | Keyboard      |

| 1       | Mouse         |

| 2       | Modem         |

| 3       | Printer       |

The DZ interrupts the CPU at level 2, which is visible in the R2000 CAUSE<12> register bit.

The DC7085 only supports half-word reads and writes. The DC7085 registers are 8-byte-aligned in the processor address space. Reads to the DZ nominally stall the CPU for 14 cycles. Writes to the DZ nominally complete in 19 cycles. Table 6-2 lists the addresses of the DZ registers.

Table 6-2: DZ Register Addresses

| Address    | Access | Name    | Function            |

|------------|--------|---------|---------------------|

| 0xBC000000 | R/W    | DZ_CSR  | Control and status  |

| 0xBC000008 | R      | DZ_RBUF | Receiver buffer     |

| 0xBC000008 | W      | DZ_LPR  | Line parameters     |

| 0xBC000010 | R/W    | DZ_TCR  | Transmitter control |

| 0xBC000018 | R      | DZ_MSR  | Modem status        |

| 0xBC000018 | W      | DZ_TDR  | Transmit data       |

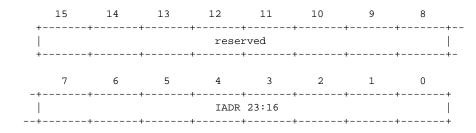

6.4.1. Control And Status Register

| +     |           | +      | +   | +     |          | +            | +               |

|-------|-----------|--------|-----|-------|----------|--------------|-----------------|

| TRDY  | 14<br>TIE | 13<br> | 12  | 11    | 10       | 09<br>TLINEB | 08  <br> TLINEA |

| RO    | RW        |        | •   |       |          |              | RO              |

| +     |           | +      | +   | +     | <b>.</b> | +            |                 |

| 07    |           |        |     |       |          |              |                 |

| RDONE | RIE       | MSE    | CLR | MAINT |          |              |                 |

| +     | +         | +      | •   | +     | +        | +            | ++              |

| RO    | RW        | RW     | RW  | RW    |          |              |                 |

All bits in the DZ\_CSR register are cleared by device reset or by asserting *master clear* (DZ\_CSR<CLR>).

#### DZ\_CSR<15> Transmitter Ready (TRDY)

This read-only bit is set when the transmitter scanner stops on a line whose transmit buffer may be loaded with another character and whose related DZ\_TCR<LNENBX> bit is set. If the DZ\_CSR<TIE> bit is also set, an interrupt request will be generated. When DZ\_CSR<TRDY> is set, and at no other time, the *transmitter line number* (bits DZ\_CSR<TLINEB:TLINEA>) is valid.

This bit is cleared when data is loaded into the transmitter for the line number indicated in DZ\_CSR<TLINEB:TLINEA>. If additional transmit lines need service, DZ\_CSR<TRDY> appears again within 1.4 microseconds of the completion of the transmitter data load operation. Note that since DZ\_CSR<TRDY> requires 1.4 microseconds to update, software must not examine this bit during that period of time or it may erroneously interpret slow deassertion of the bit as a transmitter ready condition.

This bit is also cleared when *master scan enable* (DZ\_CSR<MSE>) is cleared, or when the related DZ TCR<LNENBX> bit is cleared.

## DZ\_CSR<14> Transmitter Interrupt Enable (TIE)

When this read/write bit is set, the setting of DZ\_CSR<TRDY> will generate an interrupt request.

#### DZ\_CSR<13:10> MBZ

#### DZ\_CSR<09:08> Transmitter Line Number (TLINEB, TLINEA)

These read-only bits indicate the line number whose transmit buffer needs servicing. These bits are valid only when *transmitter ready* (DZ\_CSR<TRDY)>) is set, and are cleared when *master scan enable* (DZ\_CSR<MSE>) is cleared. Bit DZ\_CSR<08> is the least significant bit.

## DZ\_CSR<07> Receiver Done (RDONE)

This is a read-only bit that is set when a character appears at the output of the silo. If the *receiver interrupt enable* (DZ\_CSR<RIE>) is set, an interrupt request will be generated. If DZ\_CSR<RIE> is clear, no interrupt request is generated, and the program may poll this bit to detect available characters.

This bit is cleared when the receiver buffer register (DZ\_RBUF) is read. If another character is available in the silo, this bit will be cleared for a period between 100 nanoseconds and 1 microsecond, and will then be re-asserted.

This bit is also cleared when master scan enable (DZ\_CSR<MSE>) is cleared.

DZ\_CSR<06> Receiver Interrupt Enable (RIE)

This read/write bit permits the generation of an interrupt request when DZ\_CSR<RDONE> is set.

DZ\_CSR<05> Master Scan Enable (MSE)

This read/write bit must be set to permit the receiver and transmitter control sections to start the flag scanning process. When this bit is clear, *transmitter ready* (DZ\_CSR<TRDY>) is inhibited from setting and the receiver silo is cleared.

DZ CSR<04> Master Clear (CLR)

When written to a 1, this bit generates *initialize* within the chip. A read-back of this register with this bit set indicates that initialization is still in progress. This bit is self-clearing. All registers, silos, and UART functions are cleared with the following exceptions:

- 1. Only DZ\_RBUF<DVAL> is cleared; the other bits are not

- 2. The modem control output bits are not cleared

- 3. The modem status register is not cleared

## DZ\_CSR<03> Maintenance (MAINT)

This is a read/write bit which, when set, loops the serial output connections of the transmitters to the corresponding serial input connections of the receivers. This feature is used only for maintenance.

Note that while in maintenance mode, the transmitter outputs are still active. To avoid sending internal loopback data to external serial devices, the EIA drivers may be disabled by asserting the system control and status register TXDIS bit during the loopback test.

DZ\_CSR<02:00> MBZ

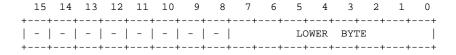

## 6.4.2. Receiver Buffer Register

|        | OERR   | FERR   | PERR   |        |        | RLINEB | RLINEA |

|--------|--------|--------|--------|--------|--------|--------|--------|

|        | RO     |        |        |        |        | RO     |        |

| +      | ·      | +      | ·      | +      | ·      | ·      | ++     |

| 07     | 06     | 05     | 04     | 03     | 02     | 01     | 00     |

| RBUF07 | RBUF06 | RBUF05 | RBUF04 | RBUF03 | RBUF02 | RBUF01 | RBUF00 |

| +      | +      | +      | +      | +      | +      | ·      | ++     |

| RO     |

The receiver buffer register (DZ\_RBUF) is a 16-bit read-only register that contains the received character as the output of the 64-location silo buffer. A read of the register causes the character entry to be removed from the buffer, and all other entries shift down to the lowest location that is not occupied. Only the *data valid bit* (DZ\_RBUF<15>) is cleared by *master clear* (DZ\_CSR<CLR>) or device reset. The other bits have **unpredictable** values.

DZ\_RBUF<15> Data Valid (DVAL)

This bit, when set, indicates that the data in bits DZ\_RBUF<14:00> is valid. This permits an interrupt handling program to read the silo repeatedly and test each entry (after it has been moved out of the silo) until the program finds an entry for which this bit is zero, indicating that the silo is now empty.

DZ RBUF<14> Overrun Error (OERR)

This bit becomes set when a received character is overwritten in the UART buffer by a following character before it has been transferred to the silo by the scanner. This condition indicates that the program is not removing characters from the silo sufficiently quickly, resulting in silo full conditions.

DZ\_RBUF<13> Framing Error (FERR)

This bit is set if the received character did not have a stop bit present at the correct time. This bit is usually interpreted as indicating that a BREAK has been received.

DZ\_RBUF<12> Parity Error (PERR)

This bit is set if the sense of the parity of the received character does not agree with the parity defined for that line.

DZ RBUF<11:10> RAZ

DZ\_RBUF<09:08> Received Line Number (RLINEB, RLINEA)

These bits contain the line number upon which the received character arrived. Bit DZ RBUF<08> is the least significant.

DZ\_RBUF<07:00> Received Character (DZ\_RBUF7 - DZ\_RBUF0)

These bits contain the received character. Characters of less than eight bits in length are right justified with unused bit positions shown as zeroes. The least significant bit is bit DZ\_RBUF<00>. The parity bit is not shown.

## **6.4.3.** Line Parameter Register

|              | 14<br> |            | RXENAB         | SC D | SC C |               | 08  <br>  SC A  |

|--------------|--------|------------|----------------|------|------|---------------|-----------------|

| +            | +      |            | #<br>WO        | #    | WO   | WO            | WO              |

| 07<br>ODDPAR |        | 05<br>STOP | 04<br>  CHAR B | 03   | 02   | 01<br> LINE B | 00  <br> LINE A |

| WO           | WO     | WO         | WO             | WO   |      | WO            | WO              |

The line parameter register (DZ\_LPR) controls the operating parameters related to each line in the chip. The DZ\_LPR must be addressed with a word address and is a write-only register. The line parameters for each line must be loaded again after the setting of *master clear* (DZ\_CSR<CLR>) or the assertion of the device reset pin. This register should not be modified while data transmission or reception is in progress on the associated line.

DZ LPR<15:13> MBZ

## DZ\_LPR<12> Receiver Enable (RXENAB)

This bit must be set before the UART receiver logic for this line can assemble characters from the serial input line.

#### DZ LPR<11:08> Speed Code (SC D, SC C, SC B, SC A)

The state of these bits determines the operating speed for the transmitter and receiver of the selected line. Note that the non-standard 19800 baud rate is not supported.

| 11 | 1    | LO | 0  | 9 | 0  | 8 | Speed |     |  |

|----|------|----|----|---|----|---|-------|-----|--|

| SC | D SC | С  | SC | В | SC | A |       |     |  |

| 0  |      | 0  |    | 0 |    | 0 | 5     | 0   |  |

| 0  |      | 0  |    | 0 |    | 1 | 7     | 5   |  |

| 0  |      | 0  |    | 1 |    | 0 | 11    | 0   |  |

| 0  |      | 0  |    | 1 |    | 1 | 13    | 4.5 |  |

| 0  |      | 1  |    | 0 |    | 0 | 15    | 0   |  |

| 0  |      | 1  |    | 0 |    | 1 | 30    | 0   |  |

| 0  |      | 1  |    | 1 |    | 0 | 60    | 0   |  |

| 0  |      | 1  |    | 1 |    | 1 | 120   | 0   |  |

| 1  |      | 0  |    | 0 |    | 0 | 180   | 0   |  |

| 1  |      | 0  |    | 0 |    | 1 | 200   | 0   |  |

| 1  |      | 0  |    | 1 |    | 0 | 240   | 0   |  |

| 1  |      | 0  |    | 1 |    | 1 | 360   | 0   |  |

| 1  |      | 1  |    | 0 |    | 0 | 480   | 0   |  |

| 1  |      | 1  |    | 0 |    | 1 | 720   | 0   |  |

| 1  |      | 1  |    | 1 |    | 0 | 9600  |     |  |

| 1  |      | 1  |    | 1 |    | 1 | 1980  | 0   |  |

## DZ\_LPR<07> Odd Parity (ODDPAR)

If this bit is set (and DZ\_LPR<PARENB> is set), characters of odd parity are generated on the line and incoming characters are expected to have odd parity. If this bit is not set (and DZ\_LPR<PARENB> is set), characters of even parity are generated and incoming characters are expected to have even parity. If DZ\_LPR<PARENB> is not set, the state of this bit is immaterial.

## DZ\_LPR<06> Parity Enable (PARENB)

If this bit is set, characters transmitted on the line have an appropriate parity bit added, and characters received on the line have their parity checked.

## DZ\_LPR<05> Stop Code (STOP)

This bit sets the stop code length; 0 = 1 unit stop, 1 = 2 unit stop (or 1.5 unit stop if 5-bit character length is selected).

DZ\_LPR<04:03> Character Length (CHAR B, CHAR A)

The bits control the length of the characters generated by the transmitter and expected by the receiver according to the table below:

| 04     | 03     |   | Chara | cter | Length |

|--------|--------|---|-------|------|--------|

| CHAR B | CHAR . | Α |       |      |        |

|        |        |   |       |      |        |

| 0      | 0      |   | 5     | bits | 3      |

| 0      | 1      |   | 6     | bits | 3      |

| 1      | 0      |   | 7     | bits | 3      |

| 1      | 1      |   | 8     | bits | 3      |

|        |        |   |       |      |        |

DZ\_LPR<02>

MBZ

DZ LPR<01:00> Parameter Line Number (LINE B, LINE A)

These bits specify the line number for which the parameter information bits <12:03> is to apply. Bit DZ LPR<00> is the least significant bit.

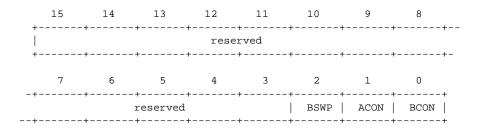

## 6.4.4. Transmit Control Register

| - | + | +      |    | +  | +              | +      |               | ++              |

|---|---|--------|----|----|----------------|--------|---------------|-----------------|

|   |   | 14<br> |    |    |                | DTR 2  |               |                 |

| - |   |        |    |    |                | RW     |               |                 |

|   | j | 06     | 05 | 04 | 03<br>  LNENB3 | LNENB2 | 01<br> LNENB1 | 00  <br> LNENB0 |

|   | + | +      |    | +  | RW             | RW     |               | RW              |

DZ\_TCR<15:11> MBZ

## DZ\_TCR<10> Modem Control (DTR2)

This read/write bit controls the assertion of the DTR modem control signal for line 2. This bit is **not** cleared by the setting of *master clear* (DZ\_CSR<CLR>). It is cleared by a device reset.

DZ\_TCR<09:04> MBZ

## DZ\_TCR<03:00> Transmitter Line Enable (LNENB3, LNENB2, LNENB1, LNENB0)

These read/write bits enable the transmitter logic for lines 3, 2, 1, and 0 respectively. Setting one of these bits causes the transmitter scanner to stop if the UART for that line has a transmitter buffer empty condition. An interrupt is then generated if transmitter interrupts are enabled. The scanner restarts when either the transmit data register (DZ\_TDR) is loaded with a character or when the DZ\_TCR<LNENBX> bit is cleared for the line upon which the scanner stopped. DZ\_TCR<LNENBX> bits should only be cleared while the scanner is not running, i.e. when *transmitter ready* (DZ\_CSR<TRDY>) is set, or *master scan enable* (DZ\_CSR<MSE>) is clear.

These bits are cleared by setting *master clear* (DZ\_CSR<CLR>) or by asserting the device reset pin.

6.4.5. Modem Status Register

| 15     | 14 | 13 | 12 | 11 | 10 | 09<br>DSR 2 | ++<br>  08  <br> |

|--------|----|----|----|----|----|-------------|------------------|

|        |    |    |    |    |    | RO          |                  |

| 07<br> | 06 | 05 | 04 | 03 | 02 | 01          | 00               |

The modem status register (DZ\_MSR) is a 16-bit read-only register. A read of this register gives the status of the DSR modem control signal. The ON condition of a modem control signal is interpreted as a logical one.

DZ MSR<15:10>RAZ

DZ\_MSR<09> Data Set Read (DSR)

This bit reflects the state of the *data set ready* signal from the modem on line 2.

DZ\_MSR<08:00>RAZ

## 6.4.6. Transmit Data Register

| 15              | 14            | 13           | 12            | 11<br> BRK 3 | 10<br> BRK 2 | 09<br> BRK 1   | BRK 0           |

|-----------------|---------------|--------------|---------------|--------------|--------------|----------------|-----------------|

| +               |               | +            | r             | WO           |              | WO             |                 |

| 07  <br> TBUF07 | 06<br> TBUF06 | 05<br>TBUF05 | 04<br> TBUF04 |              | 02<br>TBUF02 | 01<br>  TBUF01 | 00  <br> TBUF00 |

| WO              | WO            | WO           | WO            | WO           | WO           | WO             | WO              |

DZ\_TDR<15:12> MBZ

DZ\_TDR<11:08> Break Control (BRK 3, BRK 2, BRK 1, BRK 0)

These bits control the assertion of BREAK on lines 3, 2, 1, and 0 respectively. Setting a break bit IMMEDIATELY forces the output of that line to space.

DZ\_TDR<07:00> Transmitter Buffer

Characters for transmission are loaded into these bits.  $DZ\_TDR<00>$  is the least significant bit. Loading of a character should occur only when *transmitter ready* ( $DZ\_CSR<15>$ ) is set. The character that is loaded into this register is routed to the line defined in  $DZ\_CSR<TLINEB:TLINEA>$ .

This register is cleared by setting *master clear* (DZ\_CSR<CLR>) or by asserting the device reset pin. This register can be used regardless of the state of the *maintenance* bit (DZ\_CSR<MAINT>).

6.5. SCSI Interface

The SCSI interface is based upon the DC7061 SII gate array and a 64 K by 16-bit (128 KBytes) SCSI buffer. The SII manages the SCSI bus via selection, DMA data transfer, and disconnect commands. The SII supports command disconnect/reconnect and synchronous data transfers at 4.0 Mbytes/second on the SCSI bus; this is the highest performance mode of operation for the SCSI bus. The buffer is time-multiplexed between the SII and the processor. The SII can only access its buffer during DMA transfers; it has no access to memory.

An 83C11 transceiver drives the SCSI cable in the single-ended configuration that support a total cable length of up to six meters. The SCSI cable is always terminated on the DS3100 system module, which supplies termination power (through a current limit device) to the remote-end terminator. Up to seven SCSI peripherals may be connected to the cable.

The SII interrupts the CPU at level 0, which is visible in the R2000 CAUSE<10> register bit.

The SII only supports half-word reads and writes. The SII registers are word-aligned. Reads of the SII nominally stall the CPU for 21 cycles. Writes to the SII nominally complete in 20 cycles. The SCSI buffer only supports half-word reads and writes. The SCSI buffer is word-aligned in the processor address space. Reads of the buffer nominally stall the CPU for 12 cycles when the SII is idle; a peak read bandwidth of 2.8 MBytes/second. Writes to the buffer nominally complete in 14 cycles when the SII is idle; a peak write bandwidth of 2.4 MBytes/second. Buffer access during SII activity may increase the access latency by up to 5 additional cycles. Table 6-3 lists the SII register and SCSI buffer addresses.

Table 6-3: SII Register and SCSI Buffer Addresses

| Address    | Name        | Register                        |

|------------|-------------|---------------------------------|

| 0xBA000000 | SII_SDB     | SCSI data bus and parity        |

| 0xBA000004 | SII_SC1     | SCSI control signals 1          |

| 0xBA000008 | SII_SC2     | SCSI control signals 2          |

| 0xBA00000C | SII_CSR     | Control and status register     |

| 0xBA000010 | SII_ID      | ID register                     |

| 0xBA000014 | SII_SLCSR   | Selector control and status     |

| 0xBA000018 | SII_DESTAT  | Selection detector status       |

| 0xBA00001C | SII_DSTMO   | <unsupported></unsupported>     |

| 0xBA000020 | SII_DATA    | Data register                   |

| 0xBA000024 | SII_DMCTRL  | DMA control                     |

| 0xBA000028 | SII_DMLOTC  | DMA length of transfer          |

| 0xBA00002C | SII_DMADDRL | DMA address pointer (low half)  |

| 0xBA000030 | SII_DMADDRH | DMA address pointer (high half) |

| 0xBA000034 | SII_DMABYTE | DMA initial byte                |

| 0xBA000038 | SII_STLP    | <unsupported></unsupported>     |

| 0xBA00003C | SII_LTLP    | <unsupported></unsupported>     |

| 0xBA000040 | SII_ILP     | <unsupported></unsupported>     |

| 0xBA000044 | SII_DSCTRL  | <unsupported></unsupported>     |

| 0xBA000048 | SII_CSTAT   | Connection interrupt control    |

| 0xBA00004C | SII_DSTAT   | Data interrupt control          |

| 0xBA000050 | SII_COMM    | Command register                |

| 0xBA000054 | SII_DICTRL  | Diagnostic control register     |

| 0xBB000000 | Buffer base | SCSI buffer                     |

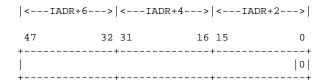

Since the buffer is word-aligned to the CPU, all addresses specified to the SII must be left-shifted by one when referencing the buffer. That is, from the CPU successive half-words of the buffer are at

0xBB000000, 0xBB000004, 0xBB000008, etc., while they are at 0x0000, 0x0002, 0x0004, etc., to the SII.

#### **6.5.1.** SII Registers

The registers of the SII can be divided into two categories according to usage. These categories can be described as:

- Diagnostic those registers which are used ONLY to diagnose the functionality of the chip and nearby circuitry. Typically, these registers are accessed only during power-up testing.

- SCSI those registers which are used when the SII is operating in SCSI mode.

Most registers in the SII are standard read/write registers. Some, however, do not fall into this class. These other classes are:

- R/W1TC read/write 1 to clear. Several status registers contain bits which require that once a status bit has been set, it can only be cleared by writing a 1 to that bit position.

- R/O read only. Several status registers contain only status and writing to them has no effect.

- R/W\* these registers are not true read/write in that under certain conditions they will not read back the value last written to them. These conditions will be noted in the description of the register.

--

Figure 6-1 shows the classification of each register.

| NAME        | USAGE      | CLASS  |

|-------------|------------|--------|

| SII_SDB     | DIAGNOSTIC | R/W*   |

| SII_SC1     | DIAGNOSTIC | R/W*   |

| SII_SC2     | DIAGNOSTIC | R/W*   |

| SII_CSR     | SCSI       | R/W    |

| SII_ID      | SCSI       | R/W*   |

| SII_SLCSR   | SCSI       | R/W    |

| SII_DESTAT  | SCSI       | R/O    |

| SII_DATA    | SCSI       | R/W*   |

| SII_DMCTRL  | SCSI       | R/W    |

| SII_DMLOTC  | SCSI       | R/W    |

| SII_DMADDRL | SCSI       | R/W    |

| SII_DMADDRH | SCSI       | R/W    |

| SII_DMABYTE | SCSI       | R/W    |

| SII_CSTAT   | SCSI       | R/W1TC |

| SII_DSTAT   | SCSI       | R/W1TC |

| SII_COMM    | SCSI       | R/W    |

| SII_DICTRL  | DIAGNOSTIC | R/W    |

|             |            |        |

## Figure 6-1: SII Register Classification

In the following register descriptions, all undefined bits will read as zero (0). Writing to any of these bits will have no effect.

## 6.5.1.1. SII\_SDB - SCSI Data Bus

The SII\_SDB register is used only in diagnostic mode (see SII\_DICTRL description) in conjunction with a loop back connector to test the SCSI port. It is also used in diagnostic internal loopback mode to effectively act like the SCSI bus. The fields in this register directly reflect the SCSI data bus ASSERTED HIGH. This register should NOT be used during normal operations. It should be noted that care must be taken to test this portion of the chip without any disturbance to the SCSI bus.

SII\_SDB (0) -- READ/WRITE

## 6.5.1.2. SII\_SC1 - SCSI Control Signals One

This register is used in diagnostic mode (see SII\_DICTRL description) in conjunction with a loop back connector to test the SCSI port or to effectively act as the SCSI bus in internal loopback mode. The bits in this register directly reflect some of the SCSI control lines ASSERTED HIGH. It should be noted that data written to this register may differ from that read back since only certain bits are driven while in the target or initiator mode.

|    | SII_SC1 (2) READ/WRITE |   |   |   |    |       |       |       |     |         |     |           |     |     |     |

|----|------------------------|---|---|---|----|-------|-------|-------|-----|---------|-----|-----------|-----|-----|-----|

| 15 |                        |   |   |   | 10 |       |       |       |     |         |     |           |     |     |     |

| -  | -                      | - | - | - | -  | -   E | BSY S | SEL F | RST | ACK   F | REQ | ATN   NTA | MSG | C/D | I/0 |

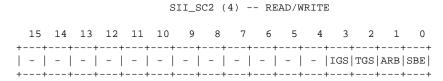

#### 6.5.1.3. SII\_SC2 - SCSI Control Signals Two

The SII\_SC2 register is used only in diagnostic mode (see SII\_DICTRL description) in conjunction with a loop back connector to test the SCSI port. These signals directly drive the four control signals on the NCR83C11 receiver/driver chip. Special care should be taken when writing this register to avoid disturbing the SCSI bus during power-up diagnostics. This register should only be accessed if an external loop-back connector is in place. It should not be used during normal operations.

IGS is set (1) to steer the SCSI drivers for the initiator role. READ/WRITE.

TGS is set (1) to steer the SCSI drivers for the target role. READ/WRITE.

ARB is set (1) to enable the SCSI drivers for arbitration. READ/WRITE.

SBE is set (1) to drive the SCSI data bus and parity lines. READ/WRITE.

6.5.1.4. SII\_CSR - Control/Status Register

This register contains control and status information about the general operation of the SII in regard to the SCSI bus, including various enable bits.

SII\_CSR (6) -- READ/WRITE

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4     | 3  | 2        | 1 | 0  |

|----|----|----|----|----|----|---|---|---|---|---|-------|----|----------|---|----|

|    |    |    |    |    |    |   |   |   |   |   |       |    | +        |   |    |

| -  | -  | -  | -  | -  | -  | - | - | - | - | - | HPM R | SE | SLE   PC | E | ΙE |

|    |    |    |    |    |    |   |   |   |   |   |       |    |          |   |    |

The fields in the SII CSR are defined as follows:

- HPM set to one (1) if the SII is operating on an arbitrated bus. In this mode, the SII will handle the arbitration. HP\_RDY is used as a BUS\_REQ, the SII returns HP\_BUSGRANT to indicate that the external device has control of the bus. When clear(0), HP\_RDY acts as an indicator that the current data transfer can be terminated and HP\_BUSGRANT is not used. HPM must always be set to 1.

- RSE set to one (1) if the SII is to respond to reselections. Clear (0) (default on reset) otherwise.

- SLE set to one (1) if the SII is to respond to selections. Clear (0) (default on reset) otherwise.

- PCE set to one (1) if the SII is to check parity and report parity errors. When clear (0), the SII will continue to check parity but will not report any errors. In either case, the SII will continue to generate parity. The default value is zero (0).

- IE set to one (1) if interrupts are to be enabled. Clear (0) (the default on reset) otherwise. If clear, all interrupts are disabled.

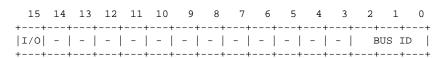

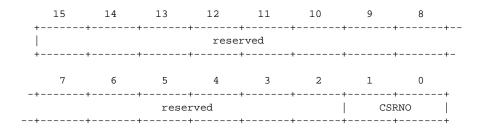

#### 6.5.1.5. SII\_ID - Bus ID Register

This register contains the three bit ID number of this SII on the SCSI bus. This value is needed for selection and selection detection.

SII\_ID (8) -- READ/WRITE

The bits is this register are defined as follows:

I/O when set to one, indicates that the 3 ID pins of the SII are outputs and the values presented in the SII\_ID register are reflected (complemented) at these pins. It is expected that this register be written before the SII is enabled. When clear, the ID pins are inputs. The logical inversion of these pins will appear in the SII\_ID register. Note that if this bit is cleared, writing this register has no effect. I/O must be set to 1.

**BUS ID**

the ID of the SII.

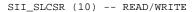

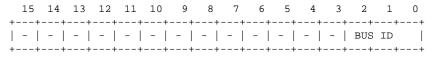

6.5.1.6. SII\_SLCSR - Selector Control And Status Register

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4  | 3  | 2   | 1   | 0 |

|----|----|----|----|----|----|---|---|---|---|---|----|----|-----|-----|---|

| ++ | +  | +  | +  | +  | +  | + | + | + | + | + | +- | +- | +   | -+- | + |

| -  | -  | -  | -  | -  | -  | - | - | - | - | - | -  | -  | BUS | ID  |   |

| ++ | +  | +  | +  |    |    |   |   |   |   |   |    |    |     |     |   |

The bits in this register are defined as follows:

**BUS ID**

the ID of the device to be selected or reselected (destination ID). This must be loaded before a SELECT command is issued.

6.5.1.7. SII DESTAT - Selection Detector Status Register

This register contains the bus ID of the device which has selected the SII. It is typically read after an interrupt is received to dispatch to the ID-dependent code.

The bits in this register are defined as follows:

**BUS ID**

the number of the device which selected the SII (source ID). This register is only updated by the SII after being selected.

6.5.1.8. SII\_DATA - Data Register

This register is used to load data to be sent out on the SCSI bus. It can also be used to read incoming information. Typically, it would be used for message and status phases. For all programmed I/O operations, only the lower byte is used. This register cannot be used for synchronous data transfers. This register will not reflect the data written to it.

6.5.1.9. SII\_DMCTRL - DMA Control Register

This register contains mode information concerning the current DMA activity. This consists of the req/ack offset used for synchronous data transfers. Note that this register must be written following detection of a selection or reselection to insure proper operation during synchronous data transfers.

These bits are defined as follows:

## REQ/ACK OFFSET

the desired request/acknowledge offset for any synchronous data transfers occurring during this connection. A maximum of three (3) is implemented for data phase transfers. A zero (0) value implies SCSI asynchronous data transfers. This offset is only for data phase transfers; other information phases must be done asynchronously. It should be noted that there is no special command for synchronous data transfer. A non-zero value for the REQ/ACK offset implies all data transfers are done in synchronous mode.

## 6.5.1.10. SII\_DMLOTC - DMA Length Of Transfer Counter

This register contains the number of BYTES which are to be DMA'ed into/out of memory. This register will auto-decrement after each transaction and will reflect the number of bytes left to transfer. It will be implemented as a 13 bit counter. This register will contain the number of bytes sent across the SCSI bus during a read and the number of bytes deposited into RAM on a write. This is a true count and bytes currently in the FIFO are not considered transferred.

Note that data transfers in excess of 8 KBytes are possible by simply reloading the SII\_DMADDR and SII\_DMLOTC registers as appropriate for the next data fragment, and issuing a new DMA command transfer command after a DNE interrupt is received from the current transfer.

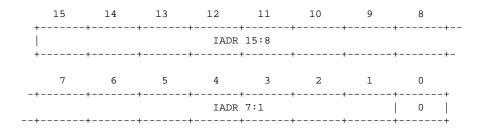

#### 6.5.1.11. SII\_DMADDR - DMA Address Registers

This register contains the memory byte address from which the DMA operation will begin. Note that a "1" in the least significant bit position means that the first cycle will be done with an initial byte offset.

$6.5.1.12.\ SII\_DMABYTE$  - DMA Initial Byte Register

This register is used to load data to be sent to the memory bus. Typically, it would be used in the following scenario:

- The SII is operating as an initiator

- The target is sending data to this SII.

- The target changes phase on an odd boundary and requests the pointers be saved.

- The SII interrupts the processor indicating a phase change has occurred and the DMA transfer ended on an odd byte boundary.

- At some later time, the target reconnects to complete the transfer.

- The processor will load the "odd" byte from the previous transfer into this register.

- After receiving the next byte, the SII will transfer the whole word into memory.

SII\_DMABYTE (26) -- READ/WRITE

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4     | 3   | 2  | 1  | 0 |

|----|----|----|----|----|----|----|----|----|----|----|-------|-----|----|----|---|

| ++ | +  | +  | +  | +  | +- | +- | +- | +- | +- | +  | +-    | +-  | +- | +- | + |

| -  | -  | -  | -  | -  | -  | -  | -  |    |    | IN | ITIAL | BYT | ΓE |    |   |

|    |    |    |    |    |    |    |    |    |    |    |       |     |    |    |   |

## 6.5.1.13. SII\_CSTAT - Connection Status Register

This register contains interrupt status related to SII connections.

SII\_CSTAT (36) -- READ/SELECTIVE WRITE 1

|    | 15    | 14 | 13  | 12  | 11  | 10 | 9   | 8   | 7          | 6       | 5   | 4       | 3       | 2     | 1   | 0 |

|----|-------|----|-----|-----|-----|----|-----|-----|------------|---------|-----|---------|---------|-------|-----|---|

| C  | !I  I | DI | RST | BER | OBC | TZ | BUF | LDN | +<br>SCH ( | CON   I | DST | TGT   S | SWA   S | SIP I | LST | 0 |

| +- | +-    |    |     |     |     |    | +   |     | +-         | +-      | +   | +-      | +-      | +-    | +-  | + |

These bits are defined as follows:

- CI SII\_CSTAT Interrupt composite error bit for the SII\_CSTAT register. It is the logical 'or' of bits 13 through 11 and 9 through 7. Those bits marked by '\*' will interrupt the processor when set.

- DI SII\_DSTAT Interrupt composite error bit for the SII\_DSTAT register.

- RST RST asserted set to one (1) if the RSTIN signal is asserted on the SCSI bus. The SII will automatically disconnect itself from the bus and interrupt the processor. This bit is write one (1) to clear.

- BER Bus Error this bit is set on any of the following conditions:

- 1. Fifo Overflow

- 2. Req/Ack Offset exceeded

- 3. Illegal Phase change

While this bit is asserted, the SII will not receive or transmit data in either DMA or programmed I/O mode. This bit is write one (1) to clear.

- OBC Not used; ignore this bit.

- TZ Not used; ignore this bit.

- BUF Not used; ignore this bit.

- LDN Not used; ignore this bit.

- SCH State Change this bit is set to one (1) if the state of the SII has changed. A change is considered to be any of the following:

- 1. Selected

- 2. Reselected

- 3. Disconnected

- 4. RST has occurred on the SCSI bus

Write one (1) to clear this bit.

- CON Connected this bit is set to one (1) if the SII is connected to another device. It is clear while the SII is idle. (Read only)

- DST Destination this bit is set to one (1) if the SII was the destination of the current transfer. In other words, this bit is set if the SII was selected or reselected by another device. (Read only)

- TGT Target this bit is set to one (1) if the SII is operating as a target during the current transfer. (Read only)

- SWA Selected With ATN this bit is set to one if the SII was selected with attention. Write one (1) to clear this bit.

- SIP Selection In Progress this bit is set if the SII is currently in a selection process. This is useful in determining if the desired destination is unavailable. (Read only)

- LST Lost this bit is set when the SII loses arbitration. It is cleared by the SII when it begins a

selection process. (Read only)

## 6.5.1.14. SII\_DSTAT - Data Transfer Status Register

This register contains interrupt status related to data transfers.

SII\_DSTAT (38) -- READ/SELECTIVE WRITE 1

| 15 | 5 14 | 13  | 12 | 11 | 10 | 9 | 8  | 7 | 6 | 5 | 5 4 | 3 | 2  | 1  | 0  |

|----|------|-----|----|----|----|---|----|---|---|---|-----|---|----|----|----|

|    | •    | DNE |    |    |    |   |    |   |   | • | •   | - |    |    |    |

|    |      | *   |    |    |    |   | ++ |   |   |   |     | + | ++ | ++ | ++ |

These bits are defined as follows:

- CI SII\_CSTAT Interrupt composite error bit for the SII\_CSTAT register.

- DI SII\_DSTAT Interrupt composite error bit for the SII\_DSTAT register. It is the logical 'or' of bits 13,11,10 and 4. Those bits marked with \* will interrupt the processor when set.

- DNE Xfer Done this bit is set to one (1) when the DMA operation is completed (successfully or not). This bit is write one (1) to clear.

- TCZ Transfer Counter Zero this bit is set when the transfer counter has a value of zero. Cleared otherwise.

- TBE Transmit Buffer Empty This bit is set to one (1) if the attached target requests data from the SII while there is no command pending for the datamover (i.e. an Info Xfer command is not in progress). This bit is cleared when an Info Xfer command is started (either DMA or programmed I/O).

- IBF Input Buffer Full this bit is set to one (1) if the SII has received a byte while there is no command pending for the datamover (i.e. an Info Xfer command is not in progress). This bit is cleared when an Info Xfer command is started (either DMA or programmed I/O).

- IPE Incoming Parity Error this bit is set to one (1) if there was a parity error on the incoming data. It remains asserted until the next DMA operation begins.

- OBB Odd Byte Boundary this bit is set if the current transfer has ended on an odd byte boundary. It is automatically reset by the SII when the next DMA operation begins. This can be used in conjunction with the previous register to solve "odd byte disconnects".

- MIS Phase Mismatch this bit is set to one (1) if the phase currently on the bus does not match the expected phase (as described in the SII\_COMM register) and a REQ has been issued by the target. This bit should only be asserted while acting in the initiator role. This bit is cleared by resolving the difference in phase by modifying the SII\_COMM register.

- ATN this bit is set to one (1) if, while the SII was in the target role, the initiator asserted ATN. Write one (1) to clear this bit.

- C/D set to one (1) if the current bus state has the C/D signal asserted. This bit is read only.

- MSG set to one (1) if the current bus state has the MSG signal asserted. This bit is read only.

- I/O set to one (1) if the current bus state has the I/O signal asserted. This bit is read only.

6.5.1.15. SII\_COMM - Command Register

The SII uses this register to determine its actions while operating in SCSI mode. This register also contains information concerning use of DMA in the present command.

SII\_COMM (40) -- READ/WRITE

| 15  | 14  | 13 | 12  | 11 | 10  | 9     | 8  | 7  | 6  | 5  | 4              | 3     | 2     | 1   | 0   |

|-----|-----|----|-----|----|-----|-------|----|----|----|----|----------------|-------|-------|-----|-----|

| ++  | +   | +  | +   | +  | +-  | +-    | +- | +- | +- | +- | +-             | +-    | +-    | +   | +   |

| DMA | RST | 0  | RSL |    | CON | INANI | )  | 0  | ON | RI | rgt   <i>i</i> | I NTA | MSG C | Z/D | 1/0 |

| ++  | +   | +  | +   | +  | +-  | +-    | +- | +- | +- | +- | +-             | +-    | +-    | +   | +   |

The bits in this register are defined as follows:

- DMA when asserted, data will be transferred to and from the memory area. When clear, data will be sent and received via the processor through the SII\_DATA register.

- RST when written to one (1), the SII will assert RST on the SCSI bus for 25 microseconds. This bit always reads zero.

- RSL when asserted (1) along with a SELECT command, the SII will attempt to reselect the desired device. When clear (0), the SII will attempt a selection.

#### COMMAND<4:0>

these bits, collectively, control the actions of the SII. The roles in which these commands are valid are listed parenthetically.

- I initiator role

- T target role

- D disconnected

These bits are defined in the following manner:

- 00001 Chip Reset (I,T,D) This command resets the entire chip in the same manner as a "hard" reset.

- 00010 Disconnect (I,T,D) This command forces the SII to release all signals it is driving on the SCSI bus (as a target). It is also used to "gracefully" abort a selection/reselection attempt.

The disconnect bit should not be written to one (1) if the SII is already disconnected. The command will remain in the COMM register and cause the SII to disconnect immediately following the next time it is selected.

- 00100 Request Data (T) This command forces the SII to issue a REQ on the SCSI bus. This command must be used only while a target receiving data. In order for this command to be executed, bits <6:3> of the SII\_COMM register must match bits <6:3> of the SII\_CSTAT and bits <2:0> of the SII\_COMM register must match bits <2:0> of the SII DSTAT register.

- O1000 Select (D) This command allows the SII to attempt to select or reselect another device on the bus.

- 10000 Information Transfer (I,T) This command allows the SII to transfer information to and from another device. This command is only valid while connected to another device. In order for this command to be executed, bits <6:3> of the SII\_COMM register must match bits <6:3> of the SII\_CSTAT and bits <2:0> of the SII\_COMM register must match bits <2:0> of the SII\_DSTAT register.

The information transfer bit is only cleared by clearing the command or a DONE interrupt. It is not cleared when the SII becomes disconnected from the bus or when RSTIN is asserted.

State lines

(D,I,T) - These three bits make up the expected state of the chip. These bits must match those in the SII\_CSTAT register for a data transfer to take place. These bits are:

CON Connected

**DST** Destination

TGT Target

#### Control lines

(I,T) - This is used to directly drive several of the bus signals. While in SCSI mode and acting as a target, the values written to C/D,I/O, and MSG are driven onto the SCSI bus. While acting as an initiator, ATN is driven onto the SCSI bus. In either mode, the bits constitute the "expected phase". The three phase bits must match those on the SCSI bus or MIS is set in the SII\_DSTAT register (following receipt of a REQ from the target).

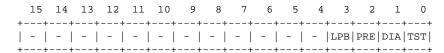

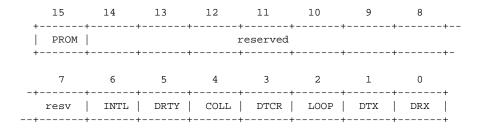

#### 6.5.1.16. SII DICTRL - Diagnostic Control Register

This register contains the various control bits used in diagnostic mode.

SII\_DICTRL (42) -- READ/WRITE

The bits is this register are defined as follows:

- LPB set to one (1) if the values written to the diagnostic registers are to be looped back into the chip. This will enable the processor to insert test vectors into the chip during power-up diagnostics if desired. Note that the DIA bit must be deasserted for this test to be meaningful. Clear (0) (default on reset) otherwise.

- PRE port enable. Set to one (1) to enable the off-chip drivers to the SCSI port. After a reset, the SII will be disconnected from the bus (this bit will be zero). The primary purpose of this bit is to allow chip diagnostics to run without affecting the rest of the SCSI bus.

- DIA When this bit is asserted, the SII is in external loop-back mode. In this mode, the diagnostic registers directly control the SCSI data and control lines, as well as the bus steering signals. After a RESET condition, this bit is zero (0).

TST is set to one (1), when the chip is in test mode. This bit must always be zero.

#### 6.5.2. Commands

The following is a description of the command set for the SII chip. Included will be operation of the chip during each command along with the various results due to execution. Registers used by the chip during the execution of the command will also be mentioned. Also included is a summary of the interrupts which may occur following the issuance of each command.

Commands will be divided into two groups, immediate and complex. All immediate commands are executed immediately, and return no status information. Complex commands are executed as soon as possible and interrupt the processor when the command has been completed. In addition, most will return status information regarding the execution of the operation.

6.5.2.1. Immediate Commands

## 6.5.2.1.1. Chip Reset

This command will stop any operation presently executing, and reset the chip. The registers will return to their default values and the chip will be left disconnected from the SCSI bus. This command may be executed in any mode (disconnected, initiator, or target), although it is recommended that the chip is disconnected from the SCSI bus when this command is issued. Following the issuance of this command the following interrupts may occur:

<none>

the SII will reset its registers and IE will be disabled (as will selection and reselection attempts). This precludes interrupts from occurring.

#### **6.5.2.1.2.** Disconnect

This command will cause the SII chip to immediately release all signals on the SCSI bus. As the target, this is typically used to end a transfer. As an initiator, this is used in the case of a firmware timeout during a selection. A disconnect command, in this case, will cause the SII to abort the selection in the way described by the SCSI specification. When disconnected already, this command will cause the SII to disconnect following the next time it is selected. Only the SII\_CSTAT register is affected by this command. Following the issuance of this command the following interrupts may occur:

SCH acknowledgment of the disconnect or a device has selected or reselected the SII. The state bits can be used to determine what has happened.

RST a device has issued RST on the bus.

#### **6.5.2.2.** Complex Commands

#### **6.5.2.2.1.** Request Data

This command is only valid when in the target role. During a transfer directed towards the target (programmed I/O), the data must be requested first. The expected chip state written in the SII\_COMM register must match the state of the chip for this command to be executed. Following the issuance of this command the following interrupts may occur:

IBF the initiator has sent a byte to the target. The following status bit may be set:

IPE the byte just received contained a parity error.

RST a device has asserted Reset on the SCSI bus.

#### 6.5.2.2.2. Select

This command instructs the SII to arbitrate for the SCSI bus and select a SCSI device. The ID of the device to be selected must be placed in the SII\_SLCSR register. See SII\_SLCSR definition for more detail. The SII chip will interrupt the processor for one of the following reasons:

SCH a state change has occurred for one of the following reasons.

• The selection has been accomplished. Some of the transfer status bits (SII\_DSTAT) may be set:

BER the target violated SCSI protocol

MIS the target has issued a REQ in a phase other than that currently in the SII\_COMM register.

IBF the target has sent a byte to the SII.

TBE the target has requested a byte from the SII.

- The SII has lost the arbitration and has been selected by another device. In this case, the ATN status bit may also be asserted.

- The SII has lost the arbitration and has been reselected by another device. In this case, the following bits may also be set:

BER the target violated SCSI protocol

MIS the target has issued a REQ in a phase other than that currently in the SII\_COMM register.

IBF the target has sent a byte to the SII.

TBE the target has requested a byte from the SII.

RST A device has asserted RST on the bus.

#### 6.5.2.2.3. Information Transfer Command

This command allows the transfer of information to or from this SII. The direction of the transfer is contained in the bus phase, which can also be found in the SII\_COMM register. The state of the chip must match the expected state written to the SII\_COMM register. This command can be aborted by clearing bit <11> in the SII\_COMM register. This command is not cleared when the SII disconnects from the bus, or when RSTIN is asserted. The SII will interrupt the processor for the following reasons:

- DNE The transfer was completed. The transfer status bits can be used to determine if completed successfully. The following transfer status bits may be set:

- TCZ The transfer counter has a zero count. In DMA mode, all bytes were received or transferred.

- IPE The SII received a byte with a parity error. In the target role, the SII\_DMLOTC register contains the number of bytes not sent (or received). In the initiator role, the SII must continue to accept data. However, the chip will automatically assert ATN on the bus.

- OBB The DMA transfer has ended on an odd byte boundary. The SII\_DSTAT will also indicate if the initiator has asserted ATN during the transfer.

- IBF The SII has received a byte while the DataMover was idle (SII was in programmed I/O mode or the DMA was completed and more data arrived.)

- TBE A byte has been requested from the SII while the DataMover was idle (SII was in programmed I/O mode or the DMA was completed and more data was requested.)

- SCH When connected as an initiator, the attached target disconnects.

- MIS When connected as an initiator, the target changes the phase and sends a REQ.

- RST Reset is asserted on the SCSI bus.

- BER A bus error occurs during the operation.

#### **6.5.3.** SCSI Operations

While the SII is operating in SCSI mode, it behaves quite similar to most industry-standard SCSI protocol controller chips.

The following is a detailed description explaining the procedure needed to execute many SCSI-type functions.

6.5.3.1. Initiator Selection Of A Target

- Begin by loading the ID of the device to be selected into the SII SLCSR register.

- 2. Bits <11:7> of the SII\_COMM register should be set to 01000B. This will instruct the SII to attempt to select the desired device. Bit 15 should be cleared since no DMA is involved. Bit 12 should be cleared since this is not a reselection. Should this SII win arbitration, IGS will be asserted. ATN and RST will both remain deasserted. The command code for selection would be 0400H. At this time, it is advisable to begin a firmware timer.

- 3. At the next detection of a bus free phase, the SII will arbitrate for the SCSI bus. Several actions may result from this:

- The SII loses the arbitration and, before the software timeout, is selected by another

device. In this case, the SII interrupts with the SCH bit set in the SII\_CSTAT register. Since the SII is now connected to another device, the SELECT command is forgotten.