# DEC OSF/1

## Writing EISA Bus Device Drivers

Part Number: AA-Q0R6A-TE

## **DEC OSF/1**

## Writing EISA Bus Device Drivers

Order Number: AA-Q0R6A-TE

February 1994

Product Version:

DEC OSF/1 Version 2.0 or higher

This guide contains information systems engineers need to write device drivers that operate on the EISA bus. The guide describes EISA busspecific topics, including EISA bus architecture and the data structures that EISA bus drivers use.

digital equipment corporation Maynard, Massachusetts Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii).

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

Possession, use, or copying of the software described in this publication is authorized only pursuant to a valid written license from Digital or an authorized sublicensor.

© Digital Equipment Corporation 1994 All rights reserved.

The following are trademarks of Digital Equipment Corporation:

ALL–IN–1, Alpha AXP, AXP, Bookreader, CDA, DDIS, DEC, DEC FUSE, DECnet, DECstation, DECsystem, DECUS, DECwindows, DTIF, MASSBUS, MicroVAX, Q-bus, ULTRIX, ULTRIX Mail Connection, ULTRIX Worksystem Software, UNIBUS, VAX, VAXstation, VMS, XUI, and the DIGITAL logo.

UNIX is a registered trademark licensed exclusively by X/Open Company Limited. Open Software Foundation, OSF, OSF/1, OSF/Motif, and Motif are trademarks of the Open Software Foundation, Inc. MIPS is a trademark of MIPS Computer Systems, Inc.

All other trademarks and registered trademarks are the property of their respective holders.

## **About This Book**

| Audience                                 | ix   |

|------------------------------------------|------|

| Scope of the Book                        | ix   |

| Organization                             | x    |

| Related Documentation                    | xi   |

| Hardware Documentation                   | xii  |

| Bus-Specific Device Driver Documentation | xii  |

| Programming Tools Documentation          |      |

| System Management Documentation          | xiii |

| Porting Documentation                    | xiv  |

| Reference Pages                          | xiv  |

| Reader's Comments                        | xv   |

| Conventions                              | xv   |

## 1 Review of Device Driver Concepts

| 1.1 | Gathering Information                        | 1-1 |

|-----|----------------------------------------------|-----|

| 1.2 | Designing a Device Driver                    | 1-1 |

| 1.3 | Allocating Data Structures                   | 1–2 |

| 1.4 | Writing Portable Device Drivers              | 1–3 |

| 1.5 | Reviewing Device Driver Configuration Models | 1–3 |

## 2 EISA Bus Architectures

| 2.1 | EISA Bus Hardware Architecture                                                                  | 2-1               |

|-----|-------------------------------------------------------------------------------------------------|-------------------|

|     | <ul> <li>2.1.1 Address Spaces</li> <li>2.1.2 Data Sizes</li> <li>2.1.3 Puta Ordering</li> </ul> | 2-1<br>2-2<br>2-2 |

| 2.2 | 2.1.3 Byte Ordering         EISA Bus Software Architecture                                      | 2-2<br>2-2        |

## 3 Structure of an EISA Bus Device Driver

| 3.1 | Incluc | de Files Section               | 3–3 |

|-----|--------|--------------------------------|-----|

| 3.2 | Autoc  | configuration Support Section  | 3–3 |

|     | 3.2.1  | Setting Up the Probe Interface | 3–4 |

|     | 3.2.2  | Setting Up the Slave Interface | 3–6 |

## 4 Data Structures That EISA Bus Device Drivers Use

| 4.1 | controller Structure Members as Specified on the EISA Bus |                                                                                 | 4–1        |  |

|-----|-----------------------------------------------------------|---------------------------------------------------------------------------------|------------|--|

|     | 4.1.1<br>4.1.2                                            | slot Member                                                                     | 4–2<br>4–3 |  |

| 4.2 | EISA                                                      | Bus Structures                                                                  | 4–4        |  |

|     |                                                           | Members of the eisa_option Structure<br>Contents of the eisa_option_data.c File | 4–4<br>4–5 |  |

## 5 Device Autoconfiguration on the EISA Bus

| 5.1 | Audiences Involved in Delivering an EISA Bus Product | 5-1 |

|-----|------------------------------------------------------|-----|

| 5.2 | Configuration for Devices Connected to the EISA Bus  | 5–3 |

|     | 5.2.1 Creating an Expansion Board Configuration File | 5–4 |

|     | 5.2.2 Creating a Device Configuration File           | 5–4 |

|     | 5.2.3 Running the EISA Configuration Utility         | 5–4 |

|     | 5.2.4 Reading the Information Generated by the ECU   | 5–4 |

## 6 EISA Bus Device Driver Example

| 6.1  | Overview of the /dev/envram Device Driver                |                                                                                                                                                               |                      |  |  |

|------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| 6.2  | envram_reg.h Header File                                 |                                                                                                                                                               |                      |  |  |

| 6.3  | envram_data.c File                                       |                                                                                                                                                               |                      |  |  |

| 6.4  | Includ                                                   | e Files Section for the /dev/envram Device Driver                                                                                                             | 6–13                 |  |  |

| 6.5  | Declar                                                   | ations Section for the /dev/envram Device Driver                                                                                                              | 6–15                 |  |  |

| 6.6  | Autoco                                                   | onfiguration Support Section for the /dev/envram Device Driver.                                                                                               | 6–18                 |  |  |

|      | 6.6.1<br>6.6.2<br>6.6.3                                  | Implementing the envram_probe InterfaceImplementing the envram_attach InterfaceImplementing the envram_ssn Interface                                          | 6–19<br>6–27<br>6–31 |  |  |

| 6.7  | Status                                                   | Section for the /dev/envram Device Driver                                                                                                                     | 6–33                 |  |  |

| 6.8  | Battery Status Section for the /dev/envram Device Driver |                                                                                                                                                               |                      |  |  |

|      | 6.8.1<br>6.8.2<br>6.8.3                                  | Implementing the eisa_nvram_battery_status InterfaceImplementing the eisa_nvram_battery_enable InterfaceImplementing the eisa_nvram_battery_disable Interface | 6–35<br>6–37<br>6–39 |  |  |

| 6.9  | Read a                                                   | and Write Device Section for the /dev/envram Device Driver                                                                                                    | 6-41                 |  |  |

|      | 6.9.1<br>6.9.2                                           | Implementing the envram_read InterfaceImplementing the envram_write Interface                                                                                 | 6–42<br>6–44         |  |  |

| 6.10 | Zero                                                     | NVRAM Section                                                                                                                                                 | 6–50                 |  |  |

| 7    | EISA I                                                   | Bus Device Driver Configuration                                                                                                                               |                      |  |  |

| 7.1  | Using                                                    | an eisa_data File with the mkeisadata Utility                                                                                                                 | 7–1                  |  |  |

| A    | EISA                                                     | Bus-Specific Reference Information                                                                                                                            |                      |  |  |

| A.1  | Conve                                                    | entions for Device Driver-Related Reference (Man) Pages                                                                                                       | A-1                  |  |  |

|      | A.1.1<br>A.1.2                                           | Conventions for Header Files                                                                                                                                  | A-1<br>A-2           |  |  |

|     | A.1.3                                      | Conventions for Device Driver Interfaces                                                                                                                        | A3  |  |

|-----|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| A.2 | A.2 Reference (Man) Pages for the EISA Bus |                                                                                                                                                                 |     |  |

|     | A.2.2                                      | Header File Specific to EISA Bus Device Drivers<br>Data Structures Specific to EISA Bus Device Drivers<br>Device Driver Interfaces That EISA Device Drivers Use | A–7 |  |

## B EISA Bus Device Driver Source Listing

## Glossary

## Index

## Figures

| 3-1: | Sections of a Character Device Driver and a Block Device Driver | 3–2 |

|------|-----------------------------------------------------------------|-----|

| 5-1: | Audiences Associated with an EISA Bus Product                   | 5–2 |

| 6-1: | Relationship of the /dev/envram and /dev/presto Device Drivers  | 6–3 |

## Tables

| 4-1: | controller Structure                                                                                     | 4-1  |

|------|----------------------------------------------------------------------------------------------------------|------|

| 4-2: | eisa_option Structure Members and Associated Data Types                                                  | 4-4  |

| 6-1: | Parts of the /dev/envram Device Driver                                                                   | 6–1  |

| 6-2: | Autoconfiguration Support Section                                                                        | 6–18 |

| 6-3: | Interfaces Implemented as Part of the Battery Status Section for the /dev/envram Device Driver           | 6–34 |

| 6-4: | Interfaces Implemented as Part of the Read and Write Device Section<br>for the /dev/envram Device Driver | 6–41 |

| A-1: | Summary Description of Header File Specific to EISA Bus Device<br>Drivers                                | A-5  |

| A-2: | Summary Description of Data Structures Specific to EISA Bus<br>Device Drivers                            | A–7  |

| A-3: | Summary | Description of Driver Interfaces that EISA Device Drivers |      |

|------|---------|-----------------------------------------------------------|------|

|      | Use     |                                                           | A-22 |

.

This book discusses topics associated with writing device drivers that operate on the Extended Industry Standard Architecture (EISA) bus.

## Audience

This book is intended for systems engineers who:

- Use standard library interfaces to develop programs in the C language

- Know the Bourne or some other UNIX-based shell

- Understand basic DEC OSF/1 concepts such as kernel, shell, process, configuration, and autoconfiguration

- Understand how to use the DEC OSF/1 programming tools, compilers, and debuggers

- Develop programs in an environment involving dynamic memory allocation, linked list data structures, and multitasking

- Understand the hardware device for which the driver is being written

- Understand the basics of the CPU hardware architecture, including interrupts, direct memory access (DMA) operations, and I/O

This book assumes you have a strong background in operating systems based on the UNIX operating system. It also assumes you have a strong background in systems and C programming, and that you are familiar with topics presented in *Writing Device Drivers, Volume 1: Tutorial*. In addition, the book assumes that you have no source code licenses.

## Scope of the Book

The book is directed towards DEC OSF/1 on computer systems developed by Digital Equipment Corporation. The book builds on the concepts and topics presented in *Writing Device Drivers, Volume 1: Tutorial*, the core book for developing device drivers on DEC OSF/1. This book introduces driver writers to topics specific to the EISA bus and that are beyond the scope of the core tutorial. The book presents an example driver that operates on the EISA bus.

The book does not emphasize any specific types of device drivers. However, mastering the concepts and examples presented in this book is useful preparation for writing a variety of device drivers that operate on the EISA bus.

## Organization

The book contains the following chapters and appendixes:

| The book contains the following endptois and appendition |                                                                                                                                                                                                                |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Chapter 1                                                | Review of Device Driver Concepts                                                                                                                                                                               |  |  |

|                                                          | Reviews general device driver concepts that are discussed<br>in detail in <i>Writing Device Drivers, Volume 1: Tutorial.</i>                                                                                   |  |  |

| Chapter 2                                                | EISA Bus Architectures                                                                                                                                                                                         |  |  |

|                                                          | Discusses aspects of the EISA bus hardware and software architectures with which you must be familiar.                                                                                                         |  |  |

| Chapter 3                                                | Structure of an EISA Bus Device Driver                                                                                                                                                                         |  |  |

|                                                          | Describes the sections that make up an EISA bus device driver.                                                                                                                                                 |  |  |

| Chapter 4                                                | Data Structures That EISA Bus Device Drivers Use                                                                                                                                                               |  |  |

|                                                          | Discusses the data structures developed for use with EISA bus device drivers.                                                                                                                                  |  |  |

| Chapter 5                                                | Device Autoconfiguration on the EISA Bus                                                                                                                                                                       |  |  |

|                                                          | Discusses the sequence of events that occurs during the autoconfiguration of devices that operate on the EISA bus.                                                                                             |  |  |

| Chapter 6                                                | EISA Bus Device Driver Example                                                                                                                                                                                 |  |  |

|                                                          | Describes the /dev/envram device driver, which operates on the EISA bus.                                                                                                                                       |  |  |

| Chapter 7                                                | EISA Bus Device Driver Configuration                                                                                                                                                                           |  |  |

|                                                          | Reviews the device driver configuration models presented<br>in <i>Writing Device Drivers, Volume 1: Tutorial</i> and<br>discusses some driver configuration topics associated with<br>EISA bus device drivers. |  |  |

| Appendix A                                               | EISA Bus-Specific Reference Information                                                                                                                                                                        |  |  |

|                                                          | Describes, in reference (man) page style, the header file,<br>data structures, kernel support interfaces, and device driver<br>interfaces that are specific to the EISA bus.                                   |  |  |

| Appendix B                                               | EISA Bus Device Driver Source Listing                                                                                                                                                                          |  |  |

|                                                          | Contains the source code listing for the /dev/envram example driver.                                                                                                                                           |  |  |

Glossary

Provides definitions of terms related to the EISA bus.

## **Related Documentation**

The printed version of the DEC OSF/1 documentation set is color coded to help specific audiences quickly find the books that meet their needs. (You can order the printed documentation from Digital.) This color coding is reinforced with the use of an icon on the spines of books. The following list describes this convention:

| Audience               | lcon | Color Code |

|------------------------|------|------------|

| General Users          | G    | Teal       |

| System Administrators  | S    | Red        |

| Network Administrators | Ν    | Yellow     |

| Programmers            | Р    | Blue       |

| Reference Page Users   | R    | Black      |

Glossary

Some books in the documentation set help meet the needs of several audiences. For example, the information in some system books is also used by programmers. Keep this in mind when searching for information on specific topics.

The *Documentation Overview* provides information on all of the books in the DEC OSF/1 documentation set.

Writing device drivers is a complex task; driver writers require knowledge in a variety of areas. One way to acquire this knowledge is to have at least the following categories of documentation available:

- Hardware documentation

- Bus-specific device driver documentation

- Programming tools documentation

- System management documentation

- Porting documentation

- Reference pages

The following sections list the documentation associated with each of these categories. EISA bus device driver writers should also be familiar with the *Extended Industry Standard Architecture Revision 3.10* specification. This specification defines a high-performance, open-architecture bus available to personal computer (PC) manufacturers, expansion board vendors, software

developers, and semiconductor suppliers.

#### **Hardware Documentation**

You should have available the hardware manual associated with the device for which you are writing the device driver. Also, you should have access to the manual that describes the architecture associated with the CPU that the driver operates on, for example, the *Alpha Architecture Reference Manual*.

#### **Bus-Specific Device Driver Documentation**

Writing Device Drivers, Volume 1: Tutorial is the core book for developing device drivers on DEC OSF/1. It contains information needed for developing drivers on any bus that operates on Digital platforms. Writing Device Drivers, Volume 2: Reference is a companion volume to the tutorial and describes, in reference (man) page style, the header files, kernel interfaces, data structures, and other interfaces used by device drivers. The following books provide information about writing device drivers for a specific bus that is beyond the scope of the core tutorial and reference:

• Writing Device Drivers for the SCSI/CAM Architecture Interfaces

This manual provides information for systems engineers who write device drivers for the SCSI/CAM Architecture interfaces.

The manual provides an overview of the DEC OSF/1 SCSI/CAM Architecture and describes User Agent routines, data structures, common and generic routines and macros, error handling and debugging routines. The manual includes information on configuration and installation. Examples show how programmers can define SCSI/CAM device drivers and write to the SCSI/CAM special I/O interface supplied by Digital to process special SCSI I/O commands.

The manual also describes the SCSI/CAM Utility (SCU) used for maintenance and diagnostics of SCSI peripheral devices and the CAM subsystem.

• Writing TURBOchannel Device Drivers

This manual provides information for systems engineers who write device drivers for the TURBOchannel. The manual describes TURBOchannelspecific topics, including TURBOchannel architecture and kernel interfaces used by TURBOchannel drivers.

#### **Programming Tools Documentation**

To create your device drivers, you use a number of programming development tools and should have on hand the manuals that describe how to use these tools. The following manuals provide information related to programming tools used in the DEC OSF/1 operating system environment:

• Kernel Debugging

This manual provides information on debugging a kernel and analyzing a crash dump of a DEC OSF/1 operating system. The manual provides an overview of kernel debugging and crash dump analysis and describes the tools used to perform these tasks. The manual includes examples with commentary that show how to analyze a running kernel or crash dump. The manual also describes how to write a kdbx utility extension and how to use the various utilities for exercising disk, tape, memory, and communications devices.

This manual is for system administrators responsible for managing the operating system and for systems programmers writing applications and device drivers for the operating system.

• Programming Support Tools

This manual describes several commands and utilities in the DEC OSF/1 system, including facilities for text manipulation, macro and program generation, source file management, and software kit installation and creation.

The commands and utilities described in this manual are intended primarily for programmers, but some of them (such as grep, awk, sed, and the Source Code Control System (SCCS)) are useful for other users. This manual assumes that you are a moderately experienced user of UNIX systems.

• Programmer's Guide

This manual describes the programming environment of the DEC OSF/1 operating system, with an emphasis on the C programming language.

This manual is for all programmers who use the DEC OSF/1 operating system to create or maintain programs in any supported language.

#### **System Management Documentation**

Refer to the *System Administration* book for information about building a kernel and for general information on system administration. This manual describes how to configure, use, and maintain the DEC OSF/1 operating system. It includes information on general day-to-day activities and tasks, changing your system configuration, and locating and eliminating sources of trouble.

This manual is for the system administrators responsible for managing the operating system. It assumes a knowledge of operating system concepts, commands, and configurations.

### **Porting Documentation**

Refer to the *DEC OSF/1 Migration Guide* for a discussion of the differences between the DEC OSF/1 and ULTRIX operating systems. This manual compares the DEC OSF/1 operating system to the ULTRIX operating system by describing the differences between the two systems.

This manual has three audiences, as follows:

- General users can read this manual to determine what differences exist between using an ULTRIX system and using the DEC OSF/1 system.

- System and network administrators can read this manual to determine what differences exist between ULTRIX and DEC OSF/1 system administration.

- Programmers can read this manual to determine differences in the DEC OSF/1 programming environment and the ULTRIX programming environment.

This manual assumes you are familiar with the ULTRIX operating system.

#### **Reference Pages**

The following provide reference (man) pages that are of interest to device driver writers:

• Reference Pages Section 2

This section defines system calls (entries into the DEC OSF/1 kernel) that programmers use. The introduction to Section 2, intro(2), lists error numbers with brief descriptions of their meanings. The introduction also defines many of the terms used in this section. This section is for programmers.

• Reference Pages Section 3

This section describes the routines available in DEC OSF/1 programming libraries, including the C library, Motif library, and X library. This section is for programmers. In printed format, this section is divided into volumes.

- Reference Pages Sections 4, 5, and 7

- Section 4 describes the format of system files and how the files are used. The files described include assembler and link editor output, system accounting, and file system formats. This section is for programmers and system administrators.

- Section 5 contains miscellaneous information, including ASCII character codes, mail-addressing formats, text-formatting macros, and a description of the root file system. This section is for programmers and system administrators.

- Section 7 describes special files, related device driver functions, databases, and network support. This section is for programmers and system administrators.

- Reference Pages Section 8

This section describes commands for system operation and maintenance. It is for system administrators.

## **Reader's Comments**

Digital welcomes your comments on this or any other DEC OSF/1 manual. You can send your comments in the following ways:

- Internet electronic mail: readers comment@ravine.zk3.dec.com

- Fax: 603-881-0120 Attn: USG Documentation, ZK03-3/Y32

- A completed Reader's Comments form (postage paid, if mailed in the United States). Two Reader's Comments forms are located at the back of each printed DEC OSF/1 manual.

If you have suggestions for improving particular sections or find any errors, please indicate the title, order number, and section numbers. Digital also welcomes general comments.

## Conventions

This book uses the following conventions:

| •<br>•   | A vertical ellipsis indicates that a portion of an example that<br>would normally be present is not shown.                                                                                                                                                                                                                                                        |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •••      | In syntax definitions, a horizontal ellipsis indicates that the preceding item can be repeated one or more times.                                                                                                                                                                                                                                                 |

| filename | In examples, syntax descriptions, and function definitions, this typeface indicates variable values.                                                                                                                                                                                                                                                              |

| buf      | In function definitions and syntax definitions used in driver<br>configuration, this typeface is used to indicate names that you<br>must type exactly as shown.                                                                                                                                                                                                   |

| []       | In formal parameter declarations in function definitions and<br>in structure declarations, brackets indicate arrays. Brackets<br>are also used to specify ranges for device minor numbers and<br>device special files in file fragments. However, for the<br>syntax definitions used in driver configuration, these brackets<br>indicate items that are optional. |

Vertical bars separating items that appear in the syntax definitions used in driver configuration indicate that you choose one item from among those listed.

This book uses the word kernel "interface" instead of kernel "routine" or kernel "macro" because, from the driver writer's point of view, it does not matter whether the interface is a routine or a macro.

I.

Before writing a driver for an Extended Industry Standard Architecture (EISA) device, you must be familiar with general driver concepts as well as specific tasks you need to perform to successfully code the driver. This book presumes you understand the following concepts:

- The purpose of a device driver

- The types of device drivers

- Static versus loadable device drivers

- When a device driver is called

- The place of a device driver in DEC OSF/1

The following sections review the tasks associated with writing device drivers. These tasks are discussed in detail in *Writing Device Drivers*, *Volume 1: Tutorial*.

## **1.1 Gathering Information**

The first task in writing a device driver is to gather pertinent information about the host system and the device for which you are writing the driver. For example, you need to:

- Specify information about the host system

- Identify the standards used in writing the driver

- Specify the characteristics and describe the usage of the device

- Provide a description of the device registers

- Identify support in writing the driver

## 1.2 Designing a Device Driver

After you gather information about the host system and the device, you are ready to design and develop the device driver. You need to specify the driver type and whether the driver you write links into the kernel dynamically at run time (loadable) or requires a reboot (static). During the design of the driver, you also identify device driver entry points and describe the driver states.

#### Note

Loadable device drivers are not supported on the EISA bus. The /dev/envram example driver discussed in Chapter 6 does not implement the loadable device driver-specific code. If you are interested in learning about loadable device drivers in anticipation of future support, see *Writing Device Drivers, Volume 1: Tutorial.*

## 1.3 Allocating Data Structures

Data structures are the mechanism used to pass information between the kernel and device driver interfaces. The following table summarizes data structures that are described in detail in *Writing Device Drivers, Volume 1: Tutorial*:

| buf and uio | Used in I/O operations.                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| controller  | Contains members that store information about<br>hardware resources and store data for communication<br>between the kernel and the device driver.                              |

| device      | Contains information that identifies the device. There is<br>one device data structure for each device connected to<br>the controller.                                         |

| driver      | Specifies information such as pointers to the probe,<br>slave, and attach interfaces used in the device<br>driver. You initialize this data structure in the device<br>driver. |

| bus         | Represents an instance of a bus entity to which other buses or controllers are logically attached.                                                                             |

| cdevsw      | Defines a device driver's entry points in the character device switch table.                                                                                                   |

| bdevsw      | Defines a device driver's entry points in the block device switch table.                                                                                                       |

Chapter 4 describes the data structures that EISA bus device drivers use.

When designing your device driver, you must decide on the technique you will use for allocating data structures. Generally, there are two techniques you can use: static allocation and dynamic allocation. Dynamic allocation is the recommended method for all new drivers; some existing drivers allocate data structures statically. If you do not plan to implement loadable drivers now or in the future, the static allocation method will suffice. Otherwise (or if you know that the maximum number of devices is greater than five or that

the driver uses numerous data structures), plan to use the dynamic allocation method.

The /dev/envram example driver uses the dynamic allocation technique discussed in Writing Device Drivers, Volume 1: Tutorial.

## **1.4 Writing Portable Device Drivers**

Whenever possible, design your device driver so that it can accommodate peripheral devices that operate on more than one CPU architecture and more than one CPU type within the same architecture. The following list notes some of the issues you need to consider to make your drivers portable:

- Control status register (CSR) access issues

- Input/Output (I/O) copy operation issues

- Direct memory access (DMA) operation issues

- Memory mapping issues

- 64-bit versus 32-bit issues

## **1.5 Reviewing Device Driver Configuration Models**

When you are ready to write your driver, you may want to study the device driver configuration models and create an appropriate device driver development environment. If you plan to ship a device driver product to customers, you also need to create a device driver kit development environment. *Writing Device Drivers, Volume 1: Tutorial* describes the configuration models and provides example development environments. The tutorial discusses how to write device drivers for computer systems running the DEC OSF/1 operating system.

The Extended Industry Standard Architecture (EISA) bus is an industrystandard high-performance bus that is a superset of the 8- and 16-bit Industry Standard Architecture (ISA). This chapter presents an overview of the EISA bus hardware and software architectures. Specifically, the chapter discusses the following:

- EISA bus hardware architecture

- EISA bus software architecture

For detailed information on EISA bus architectures, see the *Extended Industry Standard Architecture Revision 3.10*.

## 2.1 EISA Bus Hardware Architecture

The EISA bus is a 32-bit address and 32-bit data bus with support for 8-, 16-, 24, and 32-bit bus cycles. (A bus cycle refers to the action that occurs on the bus to transfer the data.) Support for different bus cycle sizes provides backward compatibility with the Industry Standard Architecture (ISA) bus options. The ISA bus is used in computer systems that adhere to the ISA. The ISA bus supplies the signals for performing the following basic functions of the computer system: memory, I/O, and direct memory access (DMA). There are two types of ISA options: one type supports only 8-bit bus cycles (PC and XT) and one type supports 8- and 16-bit bus cycles (AT).

The EISA bus also supports DMA and bus mastering. Although the EISA bus supports a maximum of 15 slots, most computer systems support a maximum of eight. The rest of this section describes the following EISA bus hardware architecture topics relevant to the device driver writer:

- Address spaces

- Data sizes

- Byte ordering

#### 2.1.1 Address Spaces

The EISA bus defines two address spaces:

• I/O address space

The EISA bus supports a 64-kilobyte (KB) I/O address space. This I/O address space contains 16 slots, each of which is 4 KB in size. This I/O address space is referred to as slot-specific I/O space. The system board and the ISA-compatible I/O address space share slot zero (0).

• Memory address space

The EISA bus supports a 4-gigabyte (GB) memory address space. This memory address space is available to any device on the bus. Assignment of the memory address space is done with the EISA configuration utility (ECU).

#### 2.1.2 Data Sizes

The EISA bus supports 8-bit (D16), 16-bit (D16), 24-bit (D24), and 32-bit (D32) data sizes.

#### 2.1.3 Byte Ordering

While the EISA bus does not specify any particular byte ordering, most devices use the Intel model, which is little endian. The Digital model is also little endian.

## 2.2 EISA Bus Software Architecture

The EISA bus supports a 4-gigabyte (GB) address space and a 64-kilobyte (KB) I/O space.

The sections that make up a DEC OSF/1 device driver differ, depending on whether the driver is a block, character, or network driver. Figure 3-1 shows the sections that a character device driver can contain and the possible sections that a block device driver can contain. Device drivers do not have to use all of the sections shown in the figure, and more complex drivers can use additional sections. Both character and block device drivers can contain:

- An include files section

- A declarations section

- An autoconfiguration support section

- A configure section (only for loadable drivers)

- An open and close device section

- An ioctl section

- An interrupt section

The block device driver can also contain a strategy section, a psize section, and a dump section.

The character device driver contains the following sections not contained in a block device driver:

- A read and write device section

- A reset section

- A stop section

- A select section

Writing Device Drivers, Volume 1: Tutorial discusses each of the driver sections. The remainder of this chapter describes the differences in the following driver sections as they relate to EISA bus device drivers: include file and autoconfiguration support (specifically, the xxprobe and xxslave interfaces).

#### Figure 3-1: Sections of a Character Device Driver and a Block **Device Driver**

| Character Device Driver                 | BIOCK Device Driver                                                               |

|-----------------------------------------|-----------------------------------------------------------------------------------|

| /* Include Files Section */             | /* Include Files Section */<br>·                                                  |

| /* Declarations Section */              | . /* Declarations Section */ .                                                    |

| /* Autoconfiguration Support Section */ | <ul> <li>.</li> <li>/* Autoconfiguration Support Section */</li> <li>.</li> </ul> |

| /* Configure Section */                 | /* Configure Section */                                                           |

| /* Open and Close Device Section */     | /* Open and Close Device Section */                                               |

| /* ioctl Section */                     | •<br>/* ioctl Section */<br>•                                                     |

| ·<br>/* Interrupt Section */<br>·       | /* Interrupt Section */                                                           |

| /* Read and Write Device Section */     | /* Strategy Section */                                                            |

| /* Reset Section */                     | /* psize Section */                                                               |

| ·<br>/* Stop Section */<br>·            | ·<br>·<br>/* Dump Section */<br>·                                                 |

| /* Select Section */                    | :                                                                                 |

| -                                       |                                                                                   |

Character Device Driver Block Device Driver

ZK--0875U--R

## 3.1 Include Files Section

Data structures and constant values are defined in header files that you include in the include files section of the driver source code. The number and types of header files you specify in the include files section vary, depending on such things as what structures, constants, and kernel interfaces your device driver references. You need to be familiar with:

- The device driver header file

- The common driver header files

- The loadable driver header files

- The device register header file

- The name data.c file

These files are described in *Writing Device Drivers, Volume 1: Tutorial.* EISA bus device drivers use the following file in addition to the previously mentioned files:

#include <io/dec/eisa/eisa.h>

The eisa.h file contains definitions specific to the EISA bus.

Another file of interest to EISA bus device driver writers is /usr/sys/data/eisa\_option\_data.c. The eisa\_option\_data.c file contains the array (table) of eisa\_option structures, which store information about a specific EISA option. Each structure contains such information as the option board's product ID and the name of the controlling device driver. Digital initilizes the array of eisa\_option structures with its own EISA bus option product information. Third-party device driver writers can directly edit the eisa\_option array with their EISA bus option product information; or, they can use the mkeisadata utility to automatically add product entries to a copy of the eisa\_option array. Chapter 7 discusses the mkeisadata utility.

## 3.2 Autoconfiguration Support Section

When DEC OSF/1 boots, the kernel determines what EISA bus devices are connected to the computer. After finding an EISA bus device, the EISA bus configuration code initializes it based on the data supplied in the device's configuration file. The probe interface determines if a particular EISA bus device is present and the attach interface initializes the device. If the device is a disk controller, the slave interface determines if the device is present. The autoconfiguration support section of an EISA bus device driver contains the code that implements these interfaces and the section applies to both character and block device drivers. The section can contain:

- A probe interface

- A slave interface

- An attach interface

Writing Device Drivers, Volume 1: Tutorial discusses each of these interfaces.

The following sections describe the xxprobe and xxslave interfaces as they apply to EISA bus device drivers. For convenience in referring to the names for the driver interfaces, the chapter uses the prefix xx. For example, xxprobe refers to a probe interface for some XX device.

### 3.2.1 Setting Up the Probe Interface

An EISA bus device driver's xxprobe interface performs the tasks necessary to determine if the device exists and is functional on a given system. At boot time, the EISA bus configuration code reads the configuration information saved by the EISA configuration utility (ECU) and performs checks to determine if the device is present before calling xxprobe for statically configured drivers. The EISA bus configuration code calls the xxprobe interface for each device that is defined according to specific rules discussed in Chapter 5. The xxprobe interface typically checks some device control status register (CSR) to determine whether the physical device is present. If the device is not present, the device is not initialized and not available for use. For static device drivers, the device interrupt handlers are defined in the system configuration file or the stanza.static file fragment and registered by the config program at system configuration time.

The *xxprobe* interface returns a nonzero value if the probe operation was successful. It returns the value zero (0) to indicate that the driver did not complete the probe operation.

The arguments you pass to the probe interface differ according to the bus on which the driver operates. The following code fragment shows you how to set up a probe interface for a driver that operates on an EISA bus:

```

xxprobe(bus_io_handle, ctlr)

io_handle_t bus_io_handle; 1

struct controller *ctlr; 2

{

/* Variable and structure declarations */

.

.

.

.

```

/\* Code to perform necessary checks \*/

.

.

.

Specifies an I/O handle that you can use to reference a device register located in the EISA bus address space. This I/O handle is for the base of the device's slot-specific I/O address space. The EISA bus configuration code passes this I/O handle to the driver's xxprobe interface during device autoconfiguration. You can perform standard C mathematical operations on the I/O handle. For example, you can add an offset to or subtract an offset from the I/O handle.

Device drivers pass the I/O handle to the following categories of interfaces, which are discussed in *Writing Device Drivers, Volume 1: Tutorial*. These interfaces can process the I/O handle to access the desired bus address space.

CSR I/O access interfaces

The CSR I/O access interfaces are read\_io\_port and write\_io\_port. These are generic interfaces that allow device drivers to read from and write to device registers. Using these interfaces to read data from and write data to a device register makes the device driver more portable across different bus architectures, different CPU architectures, and different CPU types within the same CPU architecture.

- I/O copy interfaces

The I/O copy interfaces are io\_copyin, io\_copyio, io\_copyout, and io\_zero. These are generic interfaces that allow device drivers to perform I/O copy operations. Using these interfaces to perform the copy operation makes the device driver more portable across different CPU architectures and different CPU types within the same architecture.

Section 6.3 shows how the /dev/envram device driver uses the read\_io\_port and write\_io\_port interfaces to construct driverspecific interfaces to accomplish the tasks of reading from and writing to the device registers of an EISA bus nonvolatile random access memory (NVRAM) memory expansion board.

The /dev/envram device driver example described in Chapter 6 uses the io\_copyin, io\_copyout, and io\_zero interfaces.

2 Specifies a pointer to the controller structure associated with this device. The bus configuration code passes this pointer to the driver's *xxprobe* interface. The device driver can reference hardware resource and other information contained in the controller structure pointer.

Section 6.6.1 shows the probe interface for the /dev/envram device driver.

#### 3.2.2 Setting Up the Slave Interface

A device driver's xxslave interface is called only for a controller that has slave devices connected to it. This interface is called once for each slave attached to the controller. You (or the system manager) specify the attachments of these slave devices for static device drivers in the system configuration file or stanza.static file fragment. The following code fragment shows you how to set up a slave interface for a driver that operates on an EISA bus:

```

xxslave(device, bus_io_handle)

struct device *device; 1

io_handle_t bus_io_handle; 2

{

/* Variable and structure declarations */

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

```

- 1 Specifies a pointer to a device structure for this device. The bus configuration code passes this pointer to the driver's xxslave interface. The device driver can reference such information as the logical unit number of the device, whether the device is functional, and the bus number the device resides on.

- 2 Specifies an I/O handle that you can use to reference a device register located in the EISA bus address space. This I/O handle is for the base of the device's slot-specific I/O address space. The EISA bus configuration code passes this I/O handle to the driver's xxslave interface during device autoconfiguration. You can perform standard C mathematical operations on the I/O handle. For example, you can add an offset to or subtract an offset from the I/O handle.

Device drivers pass the I/O handle to the following categories of interfaces, which are discussed in *Writing Device Drivers, Volume 1: Tutorial*. These interfaces can process the I/O handle to access the desired bus address space.

- CSR I/O access interfaces

The CSR I/O access interfaces are read\_io\_port and write\_io\_port. These are generic interfaces that allow device drivers to read from and write to device registers. Using these interfaces to read data from and write data to a device register makes the device driver more portable across different bus architectures, different CPU architectures, and different CPU types within the same CPU architecture.

– I/O copy interfaces

The I/O copy interfaces are io\_copyin, io\_copyio, io\_copyout, and io\_zero. These are generic interfaces that allow device drivers to perform I/O copy operations. Using these interfaces to perform the copy operation makes the device driver more portable across different CPU architectures and different CPU types within the same architecture.

.

Data structures are the mechanism used to pass information between the DEC OSF/1 kernel and device driver interfaces. EISA bus device driver writers must understand the data structures described in *Writing Device Drivers, Volume 1: Tutorial.* To write EISA bus device drivers, driver writers must also understand the following categories of data structures:

- controller structure members as specified on the EISA bus

- EISA bus structures

The following sections describe the structures associated with each category. For reference (man) page-style descriptions of these data structures, see Section A.2.2.

## 4.1 controller Structure Members as Specified on the EISA Bus

The controller structure represents an instance of a controller entity, one that connects logically to a bus. A controller can control devices that are directly connected or can perform some other controlling operation, such as a network interface or terminal controller operation.

Table 4-1 lists those members of the controller structure that have specific meanings on the EISA bus along with their associated data types. Following the table are descriptions of these members as they apply to the EISA bus.

| Member Name | Data Type |

|-------------|-----------|

| slot        | int       |

| physaddr    | caddr_t   |

#### Table 4-1: controller Structure

#### 4.1.1 slot Member

The slot member specifies the bus slot or node number. As it applies to the EISA bus, the slot member specifies the slot number that the EISA bus board is plugged into. The slot number ranges from 1-n, where nrepresents the maximum number of slots. This value corresponds to the one that you (the device driver writer) specified in the system configuration file or the stanza.static file fragment. In the system configuration file, you precede the slot number for the slot that the EISA bus board is plugged into with the slot keyword, as follows:

slot 1

The autoconfiguration software uses the syntax following the slot keyword in the system configuration file or the stanza.static file fragment to obtain this value. The bus configuration code obtains this value from the autoconfiguration software and uses it to initialize the slot member of the controller structure associated with this EISA bus device.

The following code fragment shows that the /dev/envram device driver saves the slot number in a softc structure pointer:

## 4.1.2 physaddr Member

The physaddr member specifies the physical address that corresponds to the virtual address set in the addr member. As it applies to the EISA bus, the physaddr member specifies an I/O handle that you can use to reference a device register located in the EISA bus address space. This I/O handle is for the base of the device's slot-specific I/O address space.

The following code fragment shows that the /dev/envram device driver saves the base physical address of the device's slot-specific I/O address space in the driver's softc structure pointer. The code fragment also shows that /dev/envram uses this address in the construction of a read and write device register interface.

```

* The ENVRAM READIO- and ENVRAM WRITE IO-related

* macros are defined in envram data.c. They use

* the read io port and write io port interfaces and

* OR the offset with the sc->regbase value. The

* sc->regbase value is the peroption physical base *

* address of the EISA NVRAM I/O registers

#define ENVRAM READIO D8(a) read io port(sc->regbase | a, 1, BUS IO)

٠

#define ENVRAM WRITEIO D8(a,d) write io port(sc->reqbase | a, 1, BUS IO, d)

struct envram softc {

٠

vm offset t regbase; /* Base address for device registers */

};

envram_probe(bus io handle, ctlr)

io handle t bus io handle; /* I/O handle */

struct controller *ctlr; /* Pointer to controller structure */

register struct envram softc *sc; /* Pointer to softc structure */

```

## 4.2 EISA Bus Structures

In addition to the structures described in the Writing Device Drivers, Volume 1: Tutorial, device driver writers must understand the eisa\_option data structure. The eisa\_option structure contains EISA bus option information such as the bus option board's product ID and the name of the controlling device driver. An array of eisa\_option structures is declared in the file /usr/sys/data/eisa\_option\_data.c. You must be familiar with:

- The members of the eisa option structure

- The contents of the eisa option data.c file

#### 4.2.1 Members of the eisa\_option Structure

Table 4-2 lists the members of the eisa\_option structure along with their associated data types.

# Table 4-2: eisa\_option Structure Members and Associated Data Types Types

| Member Name     | Data Type                        |  |

|-----------------|----------------------------------|--|

| board_id        | char [EISA_IDNAMELEN + 1]        |  |

| function        | char [EISA_FUNCLEN + 1]          |  |

| driver_name     | char [EISA_NAMELEN + 1]          |  |

| intr_b4_probe   | int                              |  |

| intr_aft_attach | int                              |  |

| type            | char                             |  |

| adpt_config     | <pre>int (*adpt_config) ()</pre> |  |

The board\_id member specifies the EISA bus option expansion board's product ID name. You set board\_id to the character string that represents the option board's product ID name. The ID name consists of a 3-character manufacturer code, a 3-character product identifier, and a 1-character revision number. For example, the string ADP0002 identifies this as a second

revision of an Adaptec ADP1742A SCSI option board.

The function member specifies the text that identifies the product up to a maximum of 79 characters. This text can include part numbers. The default is the null string (""). You set function to the character string that represents the product. For example, the string AHA1740 identifies this as the product name for a Digital ADP1742A SCSI option board.

The driver\_name member specifies the name of the controlling device driver. You set driver\_name to the character string that represents the name of the controlling device driver up to a maximum of 8 characters. This same character string also specifies the name of the controlling device driver in the system configuration file. For example, the string aha identifies this as the controlling device driver for the device connected to an ADP1742A SCSI option board.

The intr\_b4\_probe member specifies whether the device needs interrupts enabled before the bus configuration code calls the driver's xxprobe interface. You can set intr\_b4\_probe to the value zero (0) or the value 1. A zero (0) value indicates that the device does not need interrupts enabled; this is the default value. A value of 1 indicates that the device needs interrupts enabled.

The intr\_aft\_attach member specifies whether the device needs interrupts enabled after the driver's xxprobe and xxcattach or xxdattach interfaces complete execution. You can set intr\_aft\_attach to the value zero (0) or the value 1. A zero (0) value indicates that the device does not need interrupts enabled; this is the default value. A value of 1 indicates that the device needs interrupts enabled.

The type member specifies the type of device. You can set type to the string C (the device is a controller) or A (the device is a bus or an adapter). The default value is C.

The adpt\_config member specifies the name of the bus (or adapter) configuration interface to call. You set adpt\_config to the string that identifies the bus configuration interface, if type was set to A (the device is a bus or an adapter). Otherwise, do not set adpt\_config to any value.

## 4.2.2 Contents of the eisa\_option\_data.c File

Digital initilizes the array of eisa\_option structures with its own EISA bus option product information. Third-party device driver writers can directly edit the eisa\_option array with their EISA bus option product information; or, they can use the mkeisadata utility to automatically add product entries to a copy of the eisa\_option array. Chapter 7 discusses the mkeisadata utility.

struct eisa option eisa option[] = /\* board function driver intr\_b4 itr\_aft adpt \*/ /\* id name name probe attach type config \*/ /\* \_\_\_\_\_ ----- \*/ { "CPQ3011", "", "vga", 0, 1, 'C', 0}, /\* QVISION \*/

{ "DEC4220", "NET,ETH", "ln", 0, 1, 'C', 0}, /\* DEC\_LANCE \*/

{ "ADP0002", "AHA1740", "aha", 0, 1, 'C', 0}, /\* ADP1742A \*/ /\* SCSI \*/ { "ADP0002", "MSD, FPYCTL", "fdi", 0, 1, 'C', 0}, /\* ADP1742A \*/ /\* FLPY \*/ { "DEC3001", "", "fta", 0, 1, 'C', 0}, /\* DEC\_FDDI \*/

{ "DEC3002", "", "fta", 0, 1, 'C', 0}, /\* DEC\_FDDI \*/

{ "DEC2500", "", "envram", 0, 0, 'C', 0}, /\* EISA NVRAM \*/

{ "ISA1010", "COM,1", "ace", 0, 1, 'C', 0}, /\* COMM POR TS \*/

{ "ISA1010", "COM,2", "ace", 0, 1, 'C', 0}, /\* COMM POR TS \*/

{ "ISA1010", "PAR", "ace", 0, 1, 'C', 0}, /\* COMM PORTS \*/ /\* \* Do not delete any table entries above this line or your system \* will not configure properly. \* Add any new controllers or devices here. \* Remember, the module name must be blank padded to 7 bytes. \*/ /\* %%%Used by mkeisadata as placemarker for automatic installation \*/ /\* \* Do not delete this null entry, which terminates the table or your \* system will not configure properly. \*/ ""**,** { "" } /\* Null terminator in the table \*/ };

The following shows the Digital-provided eisa option data.c file:

## Device Autoconfiguration on the EISA Bus 5

Autoconfiguration is a process that determines what hardware actually exists during the current instance of the running kernel. *Writing Device Drivers, Volume 1: Tutorial* discusses the events that occur during device autoconfiguration, using the TURBOchannel bus as an example. This chapter describes device configuration on the EISA bus, which consists of the following topics:

- Audiences involved in delivering an EISA bus product

- Autoconfiguration for devices connected to the EISA bus

## 5.1 Audiences Involved in Delivering an EISA Bus Product

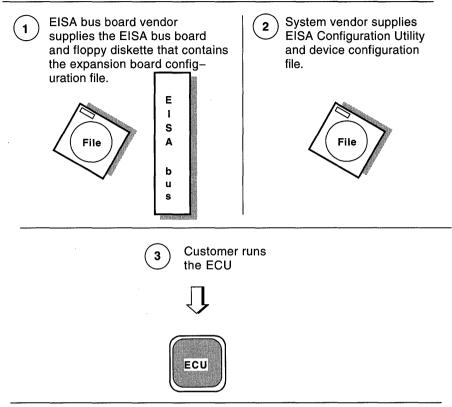

Figure 5-1 shows the audiences involved in delivering an EISA bus product. The figure shows at least three different audiences:

• An EISA bus expansion board manufacturer

The manufacturer of the EISA bus expansion board supplies the board and its configuration requirements in a configuration file. An EISA bus expansion board does not provide for onboard configuration space. An expansion board configuration file provides information on the resources and register values required to program the EISA bus expansion board. Some of the resources supplied in this file are the board ID, manufacturer of the board, the interrupt line, DMA channel, and board memory. Do not confuse the expansion board configuration file with the DEC OSF/1 system configuration file, which is an ASCII text file that defines the hardware and software components of the system. Expansion board configuration files, unlike system configuration files, have CFG extensions. The figure shows that the manufacturer distributes the expansion board configuration file on a diskette.

#### Figure 5-1: Audiences Associated with an EISA Bus Product

ZK-0904U-R

#### • A system vendor

A system vendor builds the CPU on which the EISA bus connects. For example, as a system vendor Digital builds the Alpha AXP CPUs and implements the software that allows an EISA bus device to connect to the CPU. The system vendor supplies the EISA configuration utility and device configuration file for its system. The EISA configuration utility (ECU) is a program that reads the expansion board and device configuration files and, for each option in the system, generates a conflict-free configuration. The ECU runs on top of the firmware, not the operating system. A device configuration file provides information on the resources required to program the EISA bus device. Some of the resources supplied in this file are dma channel, interrupt channel, and memory space information. Do not confuse the device configuration file with the DEC OSF/1 system configuration file, which is an ASCII text file that defines the hardware and software components of the system. Device configuration files, unlike system configuration files, have CFG extensions.

After generating a conflict-free configuration, the ECU writes it to nonvolatile random-access memory (NVRAM) for future use by the firmware and the DEC OSF/1 operating system.

• A customer

A customer purchases the EISA expansion board from the board manufacturer, the CPU from a system vendor like Digital, and the associated peripheral devices from a system vendor like Digital. The system vendor might also provide the device driver for the peripheral device. The customer loads the diskette that contains the expansion board configuration file, the device configuration file, and the ECU. The customer runs the ECU.

The ECU powers up the CPU and the firmware compares the options present on the system with the configuration information stored in NVRAM. If the information matches, the powerup continues. If the information does not match, the powerup is discontinued and the user is instructed to run the ECU. As powerup continues, the firmware uses the configuration information in NVRAM to configure and initialize each option on the system. After initializing an option, the firmware enables the option through the EISA bus control register.

A customer must run the ECU any time a new EISA expansion board is added to the system.

## 5.2 Configuration for Devices Connected to the EISA Bus

This section summarizes device autoconfiguration for EISA bus devices, focusing on the interaction of the expansion board configuration file, the device configuration file, the EISA configuration utility (ECU), and the DEC OSF/1 operating system. The following list summarizes the tasks associated with device autoconfiguration for EISA bus devices:

- Creating an expansion board configuration file

- Creating a device configuration file

- Running the EISA configuration utility (ECU)

- Reading the information generated by the ECU

- Guidelines for specifying entries in the device configuration file

The following sections describe these tasks.

#### 5.2.1 Creating an Expansion Board Configuration File

As stated in Section 5.1, the EISA expansion board manufacturer creates an expansion board configuration file that contains such resources as the board ID, manufacturer identification, the interrupt line, DMA channel, and board memory. The *Extended Industry Standard Architecture Revision 3.10* specification describes the syntax for specifying the resources in the expansion board configuration file. The board manufacturer copies the expansion board configuration file to a diskette.

#### 5.2.2 Creating a Device Configuration File

As stated in Section 5.1, the system vendor creates a device configuration file that contains such device resources as the DMA channel, interrupt channel, and memory space. The *Extended Industry Standard Architecture Revision* 3.10 specification describes the syntax for specifying the device resources and indicating a selection of choices for each resource in the device configuration file. For example, a device configuration file might specify that a device requires an interrupt channel and that the device can use channels 9, 11, 14, or 15. The system vendor copies the device configuration file to a diskette (either the diskette that contains the expansion board configuration file or a separate diskette).

The system vendor also supplies the ECU. The *Extended Industry Standard Architecture Revision 3.10* specification provides guidelines on how to write the ECU.

#### 5.2.3 Running the EISA Configuration Utility

The customer runs the ECU whenever the configuration changes. The ECU reads the board configuration file and device configuration file for each device in the system and assigns resources based on the information in the device configuration file. The ECU resolves any conflicts. The ECU saves the configuration information in nonvolatile random access memory (NVRAM).

#### 5.2.4 Reading the Information Generated by the ECU

When the customer boots the CPU, the EISA bus configuration code reads the configuration information from NVRAM and does the following for each device in the configuration:

• Looks for a device entry in the eisa\_option table. If there is no entry in the table, goes to the next device (and does not probe the device whose entry is missing from the table). After finding a valid entry in the table, continues.

- Looks for the device in the controller table. If found, continues. If not found, stops and goes to the next device (and does not probe the device whose entry is missing from the controller table).

- Configures the device based on the information saved by the ECU in NVRAM. Typically, this activity consists of writing a set of device registers to tell the device the resources assigned to it.

- Calls the device driver's xxprobe interface.

- If the probe operation succeeds, calls the driver's xxcattach or xxdattach interface.

In summary, for the EISA bus configuration code to call the driver's *xxprobe* interface the following must occur:

- 1. The system vendor creates a configuration file for the device and copies it to the system configuration diskette or a separate diskette that the ECU can read. The system configuration diskette, supplied by the board manufacturer, contains a configuration file for the expansion board. The diskette is in FAT format.

- 2. The device driver writer creates an entry for the device in the eisa option table located in the eisa option data.c file.

- 3. The device driver writer creates an entry (or entries if there are multiple instances of the device) in the system configuration file.

- 4. The customer runs the ECU.

This chapter provides you with an opportunity to study an EISA bus device driver called /dev/envram. You can use the /dev/envram device driver as the basis for writing your own working EISA bus device drivers. The /dev/envram device driver operates on an EISA bus and implements many of the device driver interfaces shown in Chapter 3. It also implements other sections needed by the EISA bus NVRAM memory expansion board. The chapter begins with a section that gives you an overview of the tasks performed by the /dev/envram device driver. Following this overview are sections that describe each piece of the /dev/envram device driver. Table 6-1 lists the parts of the /dev/envram device driver and the sections of the chapter where each is described.

| Part                                                                | Section<br>Section 6.2 |  |

|---------------------------------------------------------------------|------------------------|--|

| envram_reg.h Header File                                            |                        |  |

| envram_data.c File                                                  | Section 6.3            |  |

| Include Files Section for the /dev/envram Device Driver             | Section 6.4            |  |

| Declarations Section for the /dev/envram Device Driver              | Section 6.5            |  |

| Autoconfiguration Support Section for the /dev/envram Device Driver | Section 6.6            |  |

| Status Section for the /dev/envram Device Driver                    | Section 6.7            |  |

| Battery Status Section for the /dev/envram Device Driver            | Section 6.8            |  |

| Read and Write Device Section for the /dev/envram Device Driver     | Section 6.9            |  |

| Zero NVRAM Section                                                  | Section 6.10           |  |

#### Table 6-1: Parts of the /dev/envram Device Driver

The source code uses the following convention:

#define ENVRAM\_MAPPED 1 1

1 Numbers appear after some line or lines of code in the /dev/envram device driver example. Following the example, a corresponding number appears that contains an explanation for the associated line or lines. The source code does not contain any inline comments. If you prefer to read the /dev/envram driver source code in its entirety with the inline comments, see Appendix B.

#### 6.1 Overview of the /dev/envram Device Driver

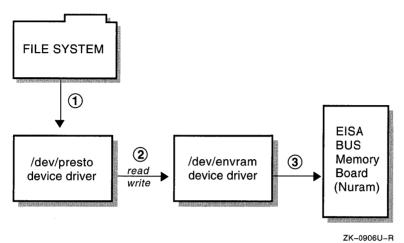

The /dev/envram device driver is a character device driver that provides read and write services to the /dev/presto device driver. The /dev/presto device driver is a disk driver that uses nonvolatile memory as a cache. It works as a layer between other drivers and the rest of the DEC OSF/1 kernel.

The /dev/presto device driver's interfaces appear as the entry points in the cdevsw and bdevsw switch tables, instead of the interfaces of the other drivers (including the /dev/envram driver) it works with. Whenever /dev/presto needs to perform actual I/O operations (for example, when the cache needs filling or draining), it calls the layered driver's entry points (strategy, close, read, and write).

Figure 6-1 shows the relationship between the /dev/envram and /dev/presto device drivers. The figure shows the flow of data between the different layers.

- 1. The file system makes a read or write request.

- 2. The /dev/presto device driver interprets the request as an actual I/O operation. It calls the /dev/envram device driver.

- 3. The /dev/envram device driver performs the actual work of reading from and writing data to the EISA bus NVRAM memory expansion board. In addition to providing services to the /dev/presto driver, the /dev/envram device driver also:

- Manages the EISA bus NVRAM memory expansion board

- Hides hardware idiosyncrasies from the /dev/presto driver

- Allows the EISA bus NVRAM memory expansion board to communicate with some SCSI device

Figure 6-1: Relationship of the /dev/envram and /dev/presto Device Drivers

### 6.2 envram\_reg.h Header File