Digital Equipment Corporation Maynard, Massachusetts

## PDP-15 Systems Programmer's Reference Manual

# FP15 Floating Point Processor

DEC-15-HQEA-D

94-003/084/36

## PDP-15 SYSTEMS FP15 FLOATING POINT PROCESSOR PROGRAMMER'S REFERENCE MANUAL

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

#### Copyright © 1971 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

#### CONTENTS

#### CHAPTER 1 INTRODUCTION

| 1.1   | General                                    | 1-1 |

|-------|--------------------------------------------|-----|

| 1.2   | Floating-Point Arithmetic                  | 1-1 |

| 1.2.1 | Floating–Point Addition and Subtraction    | 1-2 |

| 1.2.2 | Floating–Point Multiplication and Division | 1-2 |

#### CHAPTER 2 FP15 FUNCTIONAL DESCRIPTION

| 2.1 | Introduction                                              | 2-1 |

|-----|-----------------------------------------------------------|-----|

| 2.2 | FP15 Simplified Block Diagram Discussion                  | 2-1 |

| 2.3 | Instruction and Address Formats                           | 2-3 |

| 2.4 | Data Formats                                              | 2-5 |

| 2.5 | Data Transfer to FP15 from Memory – Integer Format        | 2-5 |

| 2.6 | Data Transfer to FP15 from Memory – Floating–Point Format | 2-5 |

#### CHAPTER 3 FP15 ARITHMETIC

| 3.2 Guard Bit and Rounding | 3-1 |

|----------------------------|-----|

| 3.3 Interrupt Handling     | 3-2 |

| 3.3.1 Memory Protect Trap  | 3-3 |

#### CHAPTER 4 INSTRUCTION SET

| 4.1    | Introduction                    | 4-1  |

|--------|---------------------------------|------|

| 4.2    | FPU Instruction Set             | 4-6  |

| 4.2.1  | Integer Subtract                | 4-6  |

| 4.2.2  | Floating–Point Subtract         | 4-7  |

| 4.2.3  | Integer Reverse Subtract        | 4-8  |

| 4.2.4  | Floating Point Reverse Subtract | 4-8  |

| 4.2.5  | Integer Multiply                | 4-9  |

| 4.2.6  | Floating Point Multiply         | 4-10 |

| 4.2.7  | Integer Divide                  | 4-11 |

| 4.2.8  | Floating Point Divide           | 4-11 |

| 4.2.9  | Integer Reverse Divide          | 4-12 |

| 4.2.10 | Floating Point Reverse Divide   | 4-12 |

#### CONTENTS (Cont)

Page

4-13 4.2.11 Integer Load 4.2.12 Floating Point Load 4-13 4.2.13 4-14 Integer Store 4.2.14 4-14 **Floating Point Store** 4-16 4.2.15 Load and Float 4-16 4.2.16 Float (FMA) 4.2.17 Load and Fix 4-17 4-17 4.2.18 Fix EPA (FMA) 4.2.19 4-18 Load FMQ (Integer) 4.2.2<sup>0</sup> Load FMQ (Floating Point) 4-18 4.2.21 Swap FMA and FMQ 4-19 4.2.22 Load JEA (Jump Exit Address) 4-19 4.2.23 4-20 Store JEA (Jump Exit Address) 4.2.24 4-20 Integer Add 4.2.25 4-20 Floating Point Add 4.2.26 Branch 4-21 4.2.27 Modify FMA 4-22 4.2.28 4-23 **Floating Point Test** 4.3 Worst-Case Timing 4-23

#### CHAPTER 5 DIAGNOSTIC INSTRUCTIONS

| 5.1   | Introduction                            | 5-1         |

|-------|-----------------------------------------|-------------|

| 5.2   | Debreak                                 | 5-1         |

| 5.3   | Diagnostic Mode On, Diagnostic Mode Off | 5-1         |

| 5.4   | Diagnostic Read, Step and Read          | 5 <b>-2</b> |

| 5.4.1 | Diagnostic Read                         | 5-2         |

| 5.4.2 | Diagnostic Step and Read                | 5-3         |

#### CHAPTER 6 FP15 PROGRAMMING EXAMPLES

| 6.1 | Introduction                                 | 6-1 |

|-----|----------------------------------------------|-----|

| 6.2 | Single-Precision Integer                     | 6-1 |

| 6.3 | Double-Precision Integer Programming Example | 6-2 |

| 6.4 | Single-Precision Floating Point              | 6-3 |

| 6.5 | Double-Precision Floating Point              | 6-4 |

#### ILLUSTRATIONS

| Figure No. | Title                                           | Art No. | Page |

|------------|-------------------------------------------------|---------|------|

| 1-1        | Floating-Point Representation                   | 15-0560 | 1-1  |

| 2-1        | FP15 Simplified Diagram                         | 15-0550 | 2-2  |

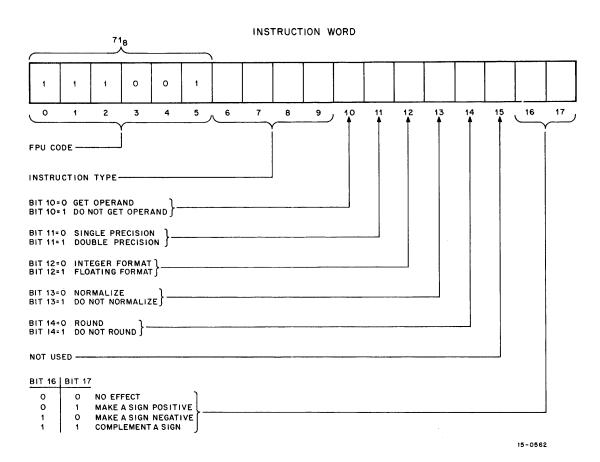

| 2-2        | Floating-Point Instruction Format               | 15-0562 | 2-4  |

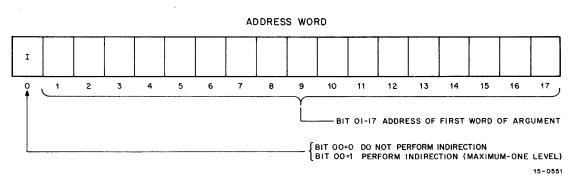

| 2-3        | Floating-Point Address Format                   | 15-0551 | 2-4  |

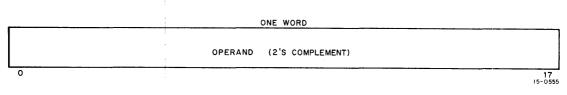

| 2-4        | Single-Precision Integer Format                 | 15-0555 | 2-5  |

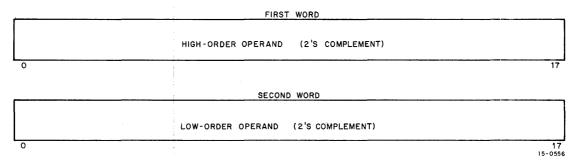

| 2-5        | Extended Integer Format                         | 15-0556 | 2-5  |

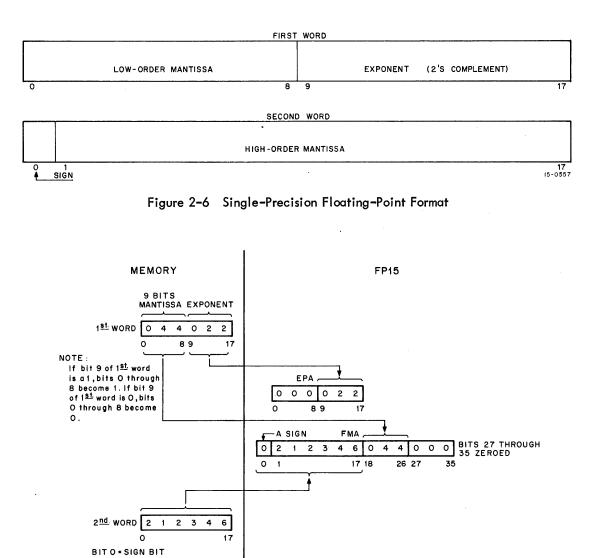

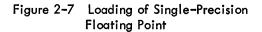

| 2-6        | Single-Precision Floating-Point Format          | 15-0557 | 2-6  |

| 2-7        | Loading of Single–Precision Floating<br>Point   | 15-0552 | 2-6  |

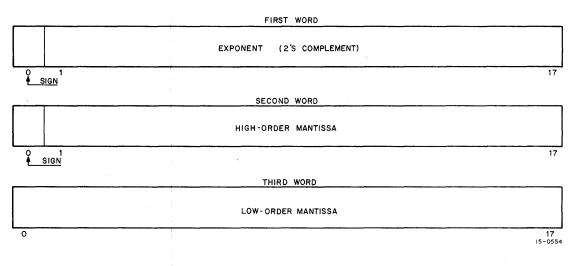

| 2-8        | Double-Precision Floating-Point Format          | 15-0554 | 2-7  |

| 3-1        | Handling of Negative Integers                   | 15-0559 | 3-1  |

| 3-2        | Handling of Guard Bit During Round Re-<br>quest | 15-0561 | 3-2  |

#### TABLES

| Table No. | 1 | Title                    | Page |

|-----------|---|--------------------------|------|

| 4-1       | - | FP15 Instruction Summary | 4-2  |

### CHAPTER 1 INTRODUCTION

#### 1.1 GENERAL

The FP15 Floating-Point Processor (FPU) is a hardware option used with the PDP-15/20, /30, and /40 Central Processors; the FP15 enables the PDP-15 to perform arithmetic and logic operations using floating-point arithmetic. The prime advantage is increased speed without the necessity of writing complex floating-point software routines. The FP15 has single-precision and extended-integer capability, as well as single- and double-precision floating point. Prior to describing the FP15 Floating-Point Processor, several fundamentals of floating-point arithmetic are reviewed in this chapter.

#### 1.2 FLOATING-POINT ARITHMETIC

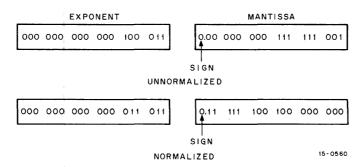

Floating-point representation of a binary number consists of two parts, an exponent and a mantissa. The mantissa is a fraction with the binary point positioned between the sign bit and the most significant bit. If the mantissa is normalized, all leading 0s are eliminated from the binary representation; the most significant bit is thus a logical 1. Leading 0s are removed by shifting the mantissa left; however, each left shift of the mantissa must be followed by a decrement of the exponent value to maintain the true value of the number. The exponent value represents the power of 2, by which the mantissa is multiplied to obtain the value to be used. Figure 1-1 shows an unnormalized number in floating-point notation, and then the same number after it has been normalized. Note in the example that the mantissa is shifted eight places to the left, and the exponent has been decreased by eight to maintain the equivalent value.

Figure 1-1 Floating-Point Representation

#### 1.2.1 Floating-Point Addition and Subtraction

For floating-point addition and subtraction operations, the exponents must be aligned or equal; if they are not aligned, the mantissa with the smaller exponent is shifted right until they are. Each shift to the right is accompanied by an increment of the exponent value. When the exponents are aligned or equal, the mantissa can be added or subtracted, whichever the case may be. The exponent value indicates the number of places the binary point is to be moved to obtain the actual representation of the number.

The example below shows the number  $7_{10}$  added to the number  $40_{10}$ , as is done in floating-point representation. Note that the exponents are first aligned and then the mantissas are added; the exponent value dictates the final location of the binary point.

Example:

$$0.10 \underbrace{\frac{5}{7}}_{100} \underbrace{100}_{000} \underbrace{000}_{000} \underbrace{000}_{000} \underbrace{000}_{000} \times 2^{6} = 50_{8} = 40_{10}$$

$$0.11 \underbrace{100}_{000} \underbrace{000}_{000} \underbrace{000}_{000} \times 2^{3} = 7_{8} = 7_{10}$$

To align exponents, shift mantissa with smaller exponent three places to α. the right, and increment exponent by 3.

|      | 5   |       |     |     |     | ·                                                      |

|------|-----|-------|-----|-----|-----|--------------------------------------------------------|

| 0.10 | 100 | _ 000 | 000 | 000 | 000 | $\times 2^{6} = 50_{8} = 40_{10}$                      |

| 0.00 | 011 | 100   | 000 | 000 | 000 | $2^{6} = 50_{8} = 40_{10}$<br>$2^{6} = 7_{8} = 7_{10}$ |

| 0.10 | 111 | 100   | 000 | 000 | 000 | $\times 2^6 = 57_8 = 47_{10}$                          |

b. Move binary point six places to the right.

$$0.10^{5}111^{7}1.00$$

000 000 000

#### 1.2.2 Floating-Point Multiplication and Division

For floating-point multiplication, the mantissas are multiplied and the exponents are added. For floating-point division, one mantissa is divided by the other and the exponents are subtracted. There is no requirement to align the binary point in multiplication or division.

The following example shows the number  $7_{10}$  multiplied by the number  $5_{10}$ . A 9-bit register is assumed for simplicity.

|    |     |      | 0.11 | 100 | 000   | $\times 2^3 = 7_8 = 7_{10}$          |

|----|-----|------|------|-----|-------|--------------------------------------|

|    |     |      | 0.10 | 100 | 000   | $x 2^3 = 5_8 = 5_{10}$               |

|    | 1   | 110  | 000  | 000 | 000   |                                      |

|    | 111 | 000  | 00   |     |       |                                      |

| .1 | 000 | 11.0 | 000  | 000 | 000 = | = 43 <sub>8</sub> = 35 <sub>10</sub> |

Move binary point six places to the right =  $35_{10} = 43_8$ .

## CHAPTER 2 FP15 FUNCTIONAL DESCRIPTION

#### 2.1 INTRODUCTION

This chapter describes the simplified block diagram of the FP15, and its associated addresses and word formats.

#### 2.2 FP15 SIMPLIFIED BLOCK DIAGRAM DISCUSSION

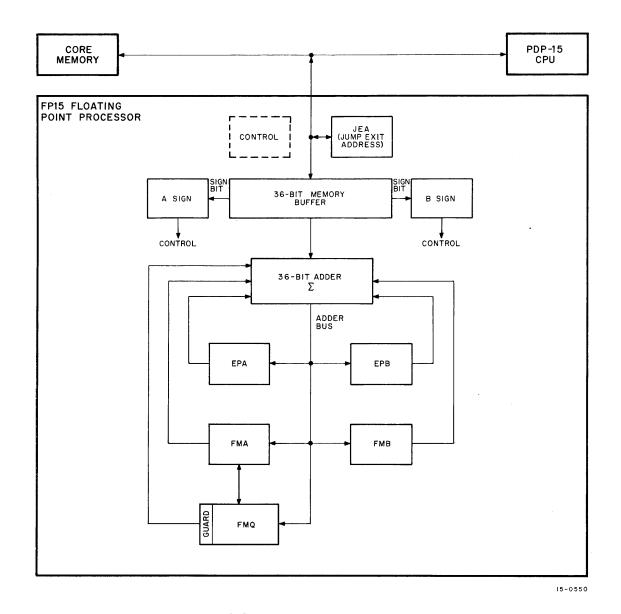

Figure 2-1 shows a simplified block diagram of the FP15 Floating-Point Processor. The FP15 is in para-Ilel with the CPU on the memory bus, and monitors each instruction fetched by the CPU from core. If bits 00 through 05 of the instruction are equal to 71<sub>8</sub>, it is recognized as a floating-point instruction; the CPU treats the instruction as an NOP. The FP15 takes control of memory, inhibits the CPU, and then simulates the CPU by completing the normal interface between CPU and memory. After the floatingpoint instruction has been executed, the CPU is enabled and both the CPU and FP15 are free to monitor the next instruction.

Functionally, the FP15 contains a memory buffer register and two operand registers. The memory buffer register provides temporary storage for all words transferred to the FP15. One operand register consists of an 18-bit exponent register (EPA), a 35-bit mantissa register (FMA), and a 1-bit sign register (A SIGN). This operand register is referred to as the floating-point accumulator. An additional 35-bit register designated the FMQ serves as an extension to the floating-point accumulator.

A second operand register consists of an 18-bit exponent register (EPB), a 35-bit mantissa register (FMB), and a 1-bit sign register (B SIGN). This second operand register, EPB/B SIGN/FMB, serves as a temporary accumulator to hold the argument fetched from core.

The exponent registers store the exponents associated with floating-point numbers and are not used during integer operations. Basically, if two numbers (integer or floating-point) are to be manipulated, one number is loaded in the floating-point accumulator by a Load type instruction. The second number is usually loaded in the temporary accumulator [EPB (B SIGN) FMB] by an instruction specifying an arithmetic operation. Both numbers are gated into a 36-bit adder, where the arithmetic operation is

Figure 2-1 FP15 Simplified Diagram

performed. The result is then transferred to the floating-point accumulator. The major registers are described below:

Memory Buffer Register - A 36-bit register which provides the FP15/memory interface. All data transferred into the FP pass through this register.

Adder - A 36-bit arithmetic logic unit (ALU) which serves as the central point in the FP15 and performs all arithmetic and logic operations. The output of the adder is connected to all major registers via an adder bus.

A SIGN - A 1-bit register used to store the polarity of the associated operand (A mantissa).

EPA - An 18-bit register used to store the 2's complement of the exponent associated with the mantissa loaded in the FMA. The most significant bit of the EPA represents the sign of the exponent; in single-precision floating arithmetic, the most significant bit of the exponent is bit 09. It is, therefore, necessary to extend the value of this bit from bits 00 through 08. If bit 09 is a 1, bits 00 through 08 in the EPA are forced to 1s, and if bit 09 is a 0, bits 00 through 08 in the EPA are forced to 0s. The EPA and FMA serve as the floating-point accumulator.

FMA – A 35-bit register used to store the integer in integer arithmetic, or the mantissa in floating-point arithmetic. The binary point is located between bit 00 and bit 01 of the FMA.

FMQ – A 35-bit extension of the FMA register used during multiplication and division operations.

B SIGN – A 1-bit register used to store the polarity of the associated operand (B mantissa).

EPB - An 18-bit register used to store the exponent associated with the mantissa in the FMB. The most significant bit of the EPB represents the sign of the exponent. In singleprecision arithmetic, where the most significant bit in the EPB is bit 09, the value of this bit is extended to bits 00 through 08 (refer to EPA register). The EPB and FMB serve as a temporary accumulator to store the argument fetched from core. The EPB is a dynamic register, and is therefore not directly accessible by software.

FMB - A 35-bit register used to store the integer in integer arithmetic or the mantissa argument in floating-point arithmetic. The binary point is located between the most significant bit (bit 00) and bit 01 of the FMB. The FMB is a dynamic register and is therefore not directly accessible by software.

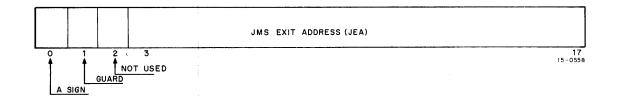

JEA (JMS Exit Address) - A 17-bit register used to store two status bits and a 15-bit base exit address for floating-point interrupts. When an interrupt condition (overflow, underflow, abnormal division, or memory protect violation) occurs in the FP15, the base exit address (a unique address for each type of interrupt) is returned. This indicates a service routine associated with the interrupt. The guard bit is used in rounding operations; for a more detailed description, refer to Paragraph 3.3 (Interrupt Handling).

#### 2.3 INSTRUCTION AND ADDRESS FORMATS

Floating-point instructions consist of two 18-bit words: an instruction word with a 71 code (see Figure 2-2), followed by an address word (see Figure 2-3). The instruction word specifies type of operation, type of precision, and data format. The address word specifies direct or indirect addressing and contains the address of the memory operand, if direct, or the address of a word containing the address of the memory operand, if indirect. Each instruction received from memory is monitored by both the FP15 and

Figure 2-2 Floating-Point Instruction Format

Figure 2-3 Floating-Point Address Format

#### 2.4 DATA FORMATS

The single- and double-precision floating point and single-precision integer data formats are identical to those in the existing PDP-15 floating-point software. Extended (double-precision) integer format is not presently supported by the PDP-15 software. The above formats are shown in Figures 2-4, 2-5, 2-6, and 2-7.

#### 2.5 DATA TRANSFER TO FP15 FROM MEMORY - INTEGER FORMAT

For single-precision integer words, the 18-bit 2's complement operand is loaded from memory into bits 18 through 35 of the FMA. The value of bit 18 (sign bit) is loaded into the remaining bit positions (bits 17 through 00) to extend the sign bit.

Figure 2-4 Single-Precision Integer Format

For extended integer words, the high-order operand from memory is loaded into bits 00 through 17 of the FMA, and the low-order operand is loaded into bits 18 through 35.

All integers loaded into the floating-point processor are converted to 36-bit sign and magnitude numbers.

Figure 2-5 Extended Integer Format

#### 2.6 DATA TRANSFER TO FP15 FROM MEMORY - FLOATING-POINT FORMAT

For single-precision floating-point words, the first word from memory consists of nine bits of low-order mantissa and nine bits of exponent. The nine bits of mantissa are loaded into bits 18 through 26 of the FMA, and bits 27 through 35 are zeroed. The nine bits of exponent in 2's complement form are loaded

into bits 09 through 17 of the EPA, with bit 09 representing the sign bit. The unloaded portion of the EPA register (bits 00 through 08) is loaded with the value of bit 09. If this bit is a 1, 1s are placed in bit positions 00 through 08, and if the bit is a 0, 0s are placed in bit positions 00 through 08. This extends the sign bit to bit positions 00 (the bit normally reserved for sign of the exponent value). The second word from memory is loaded into bits 00 through 17 of the FMA and represents the 18 bits of high-order mantissa. Figure 2-7 shows the loading of single-precision floating-point words from memory. The first word is 044022, and the second is 212346.

Note that the EPA and bits 18 through 26 of the FMA are loaded by the first word, and bits 00 through 17 of the FMA are loaded with the second word.

For double-precision floating-point words, the 18-bit 2's complement exponent is first loaded into the EPA, the 18-bit high-order mantissa is loaded into A SIGN and bits 01 through 17 of the FMA, and the low-order mantissa is loaded into bits 18 through 35 of the FMA. All 36 bits of the FMA are loaded at one time.

## CHAPTER 3 FP15 ARITHMETIC

#### 3.1 INTRODUCTION

Negative integers are stored in memory as 2's complement numbers. Such operands are converted to sign and magnitude format when transferred to the FMA or FMB in the FP15. Load and reverse arithmetic instructions transfer operands to the FMA, while arithmetic instructions transfer operands to the FMA. Positive integers and floating-point numbers stored in memory require no conversion, as they are already in sign and magnitude format.

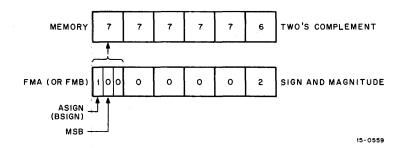

As an example of how negative integers are handled, consider the integer designated as negative 2. This number is stored in memory as  $777776_8$ . When transferred to the FMA, for example, the number is converted to  $000002_8$  with a negative sign (1), as shown in Figure 3-1.

Figure 3-1 Handling of Negative Integers

Negative integers in sign and magnitude format in the FP15 are converted to two's complement format prior to being stored in memory by a STORE instruction.

#### 3.2 GUARD BIT AND ROUNDING

The FP15 has an internal guard bit that is used under certain conditions to determine whether the FMA is to be rounded. The guard bit is set independent of any request for rounding. When set, and rounding is requested, it adds +1 to the least significant bit of the FMA. The guard bit is cleared at the beginning of all instructions except Floating-Point Test, Load JEA, Store JEA, and Branch.

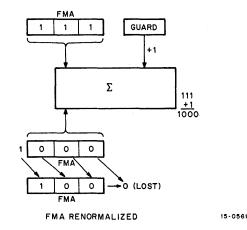

During alignment of the mantissas in floating-point addition and subtraction, bits shifted out of the FMA or FMB are shifted into the FMQ. If rounding is requested, and FMQ 01 is a 1, the mantissa that is being aligned is rounded. Further, if the addition or subtraction produced a carry out of the most significant stage of the adder, the adder is right-shifted and the exponent is incremented. This returns the true number to the FMA (see Figure 3-2). The least significant bit shifted out of the FMA is not shifted into the FMQ, but is shifted into a guard bit. If rounding is requested, and the guard bit is set, +1 is added to the least significant bit of the FMA.

For floating-point multiplication and division operations, the guard bit is set if FMQ 01 is on a 1. If rounding is requested, and the guard bit is set, +1 is added to the least significant bit of the FMA.

For a Fix instruction, the bits in the FMA and FMQ are right-shifted. If, upon completion of the shifting process, FMQ 01 is on a 1, the guard bit is set. If rounding is requested, and the guard bit is set, +1 is added to the least significant bit of the FMA.

Figure 3-2 Handling of Guard Bit During Round Request

In single precision floating-point arithmetic, after numbers are loaded into the FP15 they are handled as double-precision numbers - 18-bits of exponent and 35-bits of mantissa. Due to this, +1 is added to bit 35 of the floating-point accumulator during arithmetic operations when rounding is performed. When rounding takes place in the single-precision floating STORE instruction, however, +1 is added to bit 26 of the FMA if bit 27 is a one. Bits 27-35 are then cleared.

#### 3.3 INTERRUPT HANDLING

The FP15 can cause an interrupt under the following conditions:

Overflow – Occurs when the final magnitude of an arithmetic operation exceeds the maximum number that can be represented by the FP15. Overflow can occur with both integer and floating-point numbers.

Underflow - Occurs when the final magnitude of an arithmetic operation is less than the minimum number which can be represented by the FP15. Underflow applies to floating-point numbers only.

Abnormal Divide – Occurs when division by an unnormalized operand is attempted on either integer or floating-point numbers (0 represents a special case of the unnormalized operand).

Memory Protect Trap - Occurs when the system is in user mode and a memory protect violation or non-existent memory reference has been made by the FPU.

Prior to starting FP15 floating-point operation, the 15-bit JEA register is loaded with an address representing a core location to which the FP15 can exit when a particular error condition (overflow, underflow, abnormal divide, or memory protect trap) is detected. When one of these conditions is detected, the FP15 forces the CPU to execute a JMS to a location specified by the JEA plus a fixed constant, N. This location is the entry point to a specific routine associated with the error condition. If the interrupt exception is overflow, the CPU will execute a JMS to the JEA address; if the exception is underflow, the CPU will execute a JMS to the JEA address +2; if abnormal divide, the CPU will execute a JMS to the JEA +4; and if memory protect trap, the CPU will execute a JMS to the JEA address +6. The JEA is a 15-bit register which holds the exit address as follows:

| EXIT ADDRESS | 0        |                         |

|--------------|----------|-------------------------|

| +1           | JMP OVR  | /GO TO OVERFLOW         |

| +2           | 0        |                         |

| +3           | JMP UND  | /go to underflow        |

| +4           | 0        |                         |

| +5           | JMP DIV  | /go to divide           |

| +6           | 0        |                         |

| +7           | JMP TRAP | /GO TO MEMORY VIOLATION |

#### NOTE

To determine the data mode on an interrupt exception, it is necessary to examine the instruction that was being executed. The address which was stored, due to the JMS instruction, is equal to the location of the original instruction +3.

#### 3.3.1 Memory Protect Trap

When a memory protect violation occurs during a floating-point instruction, the FP15 forces the CPU to execute a JMS to the location specified by JEA +6 (as previously described), no trap will occur, user mode will remain on, and no modification of core above or below the boundary will occur.

An example of this is shown below, where, upon occurrence of a memory protect violation, a JMS to location JEA +6 occurs and the PC points to A+3.

Example:

|     | 1000 DAC | LOC (JEA+6) | 1004           |

|-----|----------|-------------|----------------|

| А   | 1001 DAD | +7          | JMP MP Service |

| A+1 | 1002 400 |             |                |

| A+2 | 1003     |             |                |

| A+3 | 1004     |             |                |

An exception to the above occurs if the JEA points to an address above or below the protect boundaries and a floating-point memory violation occurs. In this case, the CPU will trap and service the attempted boundary violation, and the PC will point to A+3.

## CHAPTER 4 INSTRUCTION SET

#### 4.1 INTRODUCTION

Table 4-1 is a summary of all FP15 Floating-Point instructions by categories. Following this table is a description of the FP15 instruction set. The mnemonic, instruction type, execution time, and octal code are provided for each instruction, followed by a general description of its operation. The instructions which can cause interrupt exceptions (underflow, overflow, abnormal division, or memory trap) are specified. Section 4.3 discusses worst-case timing.

The XCT of any FP15 instruction is permissible, and the address associated with the FP15 instruction is contained in the location following the XCT. The EXEC switch will not execute a FP15 instruction; an NOP will occur. SING TIME, SING STEP, or SING INST switches will not stop the execution of a FP15 instruction.

The instruction modifiers, formats, and operations of the FP15 instruction set are designated by the following characters:

#### MODIFIERS

UR – unrounded UN – unnormalized UU – unrounded and unnormalized

FORMATS

I - single precision integer

E - extended (double-precision) integer

F - single-precision floating point

D - double-precision floating point

#### **OPERATIONS**

AD - Add

SB - Subtract

**RS** – Reverse Subtract

- MP Multiply

- DV Divide

- RD Reverse Divide

ST - Store

LF - Load and Float

LD – Load

OPERATIONS (Cont) FL - Float LX - Load and Fix FX - Fix LQ - Load FMQ SWQ - Swap

Generally, the FP15 instructions are in the following format:

For example, if an unrounded, unnormalized, double-precision floating point Add instruction is specified, the mnemonic is specified as UUDAD; where the UU is the modifier, D is the format, and AD is the operation. Modify FMA instructions, branch instructions, and diagnostic instructions do not follow this general pattern.

All the FP15 instructions (except Floating-Point Test, Branch, Load or Store JEA, and diagnostic instructions) can be microprogrammed with bits 16 and 17 of the instruction word as described below:

| Bit 16 | Bit 17 |                      |                                 |

|--------|--------|----------------------|---------------------------------|

| 0      | 0      | No effect            |                                 |

| 0      | 1      | Make A SIGN positive | Not used in FP test, Load or    |

| 1      | 0      | Make A SIGN negative | Store JEA, Branch on condition, |

| 1      | 1      | Complement A SIGN    | and diagnostic instructions.    |

For example, the instruction 710540 specifies double-precision floating-point subtraction. If desired to make A SIGN negative, the instruction would be specified as 710542.

| Mnemonic | Instruction Type                                         | Octal Code |

|----------|----------------------------------------------------------|------------|

| FPT      | Floating-Point Test                                      | 710314     |

| ISB      | Single Integer Subtract                                  | 710400     |

| ESB      | Extended Integer Subtract                                | 710500     |

| FSB      | Single–Precision Float Subtract                          | 710440     |

| URFSB    | Unrounded, Single-Precision Float Subtract               | 710450     |

| UNFSB    | Unnormalized, Single-Precision Float Subtract            | 710460     |

| UUFSB    | Unrounded, Unnormalized, Single-Precision Float Subtract | 710470     |

|      | Table 4-1   |         |

|------|-------------|---------|

| FP15 | Instruction | Summary |

| Т    | able 4–1 (C | Cont)   |

|------|-------------|---------|

| FP15 | Instruction | Summary |

| Mnemonic | Instruction Type                                                    | Octal Code |

|----------|---------------------------------------------------------------------|------------|

| DSB      | Double-Precision Float Subtract                                     | 710540     |

| URDSB    | Unrounded, Double–Precision, Float Subtract                         | 710550     |

| UNDSB    | Unnormalized, Double-Precision Float Subtract                       | 710560     |

| UUDSB    | Unrounded, Unnormalized, Double-Precision Float Subtract            | 710570     |

| IRS      | Single Integer Reverse Subtract                                     | 711000     |

| ERS      | Extended Integer Reverse Subtract                                   | 711100     |

| FRS      | Single-Precision Float Reverse Subtract                             | 711040     |

| URFRS    | Unrounded, Single–Precision Float Reverse Subtract                  | 711050     |

| UNFRS    | Unnormalized, Single-Precision Float Reverse Subtract               | 711060     |

| UUFRS    | Unrounded, Unnormalized, Single–Precision Float Reverse<br>Subtract | 711070     |

| DRS      | Double-Precision Float Reverse Subtract                             | 711140     |

| URDRS    | Unrounded, Double–Precision Float Reverse Subtract                  | 711150     |

| UNDRS    | Unnormalized, Double-Precision Float Reverse Subtract               | 711160     |

| UUDRS    | Unrounded, Unnormalized, Double–Precision Float Reverse<br>Subtract | 711170     |

| IMP      | Single Integer Multiply                                             | 711400     |

| EMP      | Extended Integer Multiply                                           | 711500     |

| FMP      | Single–Precision Float Multiply                                     | 711440     |

| URFMP    | Unrounded, Single–Precision Float Multiply                          | 711450     |

| UNFMP    | Unnormalized, Single-Precision Float Multiply                       | 711460     |

| UUFMP    | Unrounded, Unnormalized, Single–Precision Float Multiply            | 711470     |

| DMP      | Double-Precision Float Multiply                                     | 711540     |

| URDMP    | Unrounded, Double-Precision Float Multiply                          | 711550     |

| UNDMP    | Unnormalized, Double-Precision Float Multiply                       | 711560     |

| UUDMP    | Unrounded, Unnormalized, Double–Precision Float Multiply            | 711570     |

| IDV      | Single-Precision Integer Divide                                     | 712000     |

| EDV      | Extended Integer Divide                                             | 712100     |

| FDV      | Single-Precision Float Divide                                       | 712040     |

| URFDV    | Unrounded, Single–Precision Float Divide                            | 712050     |

| DDV      | Double-Precision Float Divide                                       | 712140     |

| URDDV    | Unrounded, Double–Precision Float Divide                            | 712150     |

| IRD      | Single-Precision Integer Reverse Divide                             | 712400     |

| ERDExtended Integer Reverse DivideFRDSingle-Precision Float Reverse DivideURFRDUnrounded, Single-Precision Float Reverse DivideDRDDouble-Precision Float Reverse DivideURDRDUnrounded, Double-Precision Float Reverse DivideILDSingle-Precision Integer LoadELDExtended Integer LoadFLDSingle-Precision Float LoadUNFLDUnnormalized, Single-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadISTSingle-Precision Float StoreESTExtended Integer StoreFSTSingle-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNFSTUnnormalized, Double-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreUNDSTUnnormalized, Single-Precision Float StoreUNDSTUnnormalized, Single-Precision Float StoreUNILFUnnormalized, Single-Precision Float Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 712500<br>712440<br>712450<br>712540<br>712550<br>713000<br>713100<br>713050<br>713070<br>713150<br>713170 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| FRDSingle-Precision Float Reverse DivideURFRDUnrounded, Single-Precision Float Reverse DivideDRDDouble-Precision Float Reverse DivideURDRDUnrounded, Double-Precision Float Reverse DivideILDSingle-Precision Integer LoadELDExtended Integer LoadFLDSingle-Precision Float LoadUNFLDUnnormalized, Single-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNDLDUnnormalized, Single-Precision Float LoadUNDLDUnnormalized, Single-Precision Float LoadUNDLDUnnormalized, Single-Precision Float StoreESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreDSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 712440<br>712450<br>712540<br>712550<br>713000<br>713100<br>713050<br>713070<br>713150                     |

| URFRDUnrounded, Single-Precision Float Reverse DivideDRDDouble-Precision Float Reverse DivideURDRDUnrounded, Double-Precision Float Reverse DivideILDSingle-Precision Integer LoadELDExtended Integer LoadFLDSingle-Precision Float LoadUNFLDUnnormalized, Single-Precision Float LoadDLDDouble-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNFLTSingle-Precision Float StoreESTExtended Integer StoreFSTSingle-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNFSTUnnormalized, Double-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 712450<br>712540<br>712550<br>713000<br>713100<br>713050<br>713070<br>713150                               |

| DRDDouble-Precision Float Reverse DivideURDRDUnrounded, Double-Precision Float Reverse DivideILDSingle-Precision Integer LoadELDExtended Integer LoadFLDSingle-Precision Float LoadUNFLDUnnormalized, Single-Precision Float LoadDLDDouble-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadUNDLDUnnormalized, StoreESTExtended Integer StoreFSTSingle-Precision Float StoreUNFSTUnrounded, Single-Precision Float StoreUNFSTUnrounded, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Float Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 712540<br>712550<br>713000<br>713100<br>713050<br>713070<br>713150                                         |

| URDRDUnrounded, Double-Precision Float Reverse DivideILDSingle-Precision Integer LoadELDExtended Integer LoadFLDSingle-Precision Float LoadUNFLDUnnormalized, Single-Precision Float LoadDLDDouble-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadISTSingle-Precision Integer StoreESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Float Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 712550<br>713000<br>713100<br>713050<br>713070<br>713150                                                   |

| ILDSingle-Precision Integer LoadELDExtended Integer LoadFLDSingle-Precision Float LoadUNFLDUnnormalized, Single-Precision Float LoadDLDDouble-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadISTSingle-Precision Integer StoreESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreUNFSTUnrounded, Unnormalized, Single-Precision Float StoreUNFSTUnrounded, Unnormalized, Single-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 713000<br>713100<br>713050<br>713070<br>713150                                                             |

| ELDExtended Integer LoadFLDSingle-Precision Float LoadUNFLDUnnormalized, Single-Precision Float LoadDLDDouble-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadISTSingle-Precision Integer StoreESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Single-Precision Float StoreUUFSTUnrounded, Onnormalized, Single-Precision Float StoreUSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 713100<br>713050<br>713070<br>713150                                                                       |

| FLDSingle-Precision Float LoadUNFLDUnnormalized, Single-Precision Float LoadDLDDouble-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadISTSingle-Precision Integer StoreESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreDSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 713050<br>713070<br>713150                                                                                 |

| UNFLDUnnormalized, Single-Precision Float LoadDLDDouble-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadISTSingle-Precision Integer StoreESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUNFSTUnrounded, Unnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreDSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 713070<br>713150                                                                                           |

| DLDDouble-Precision Float LoadUNDLDUnnormalized, Double-Precision Float LoadISTSingle-Precision Integer StoreESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreUSTDouble-Precision Float StoreUIFSTUnrounded, Unnormalized, Single-Precision Float StoreIUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 713150                                                                                                     |

| UNDLDUnnormalized, Double-Precision Float LoadISTSingle-Precision Integer StoreESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreDSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                            |

| ISTSingle-Precision Integer StoreESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreDSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                            |

| ESTExtended Integer StoreFSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreDSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 713600                                                                                                     |

| FSTSingle-Precision Float StoreURFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreDSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 713700                                                                                                     |

| URFSTUnrounded, Single-Precision Float StoreUNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreDSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 713640                                                                                                     |

| UNFSTUnnormalized, Single-Precision Float StoreUUFSTUnrounded, Unnormalized, Single-Precision Float StoreDSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 713650                                                                                                     |

| DSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 713660                                                                                                     |

| DSTDouble-Precision Float StoreUNDSTUnnormalized, Double-Precision Float StoreILFSingle-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 713670                                                                                                     |

| ILF Single-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 713750                                                                                                     |

| ILF Single-Precision Integer Load and Float                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 713770                                                                                                     |