DEC-08-HZDC-D

UDC8 universal digital control subsystem maintenance manual

digital equipment corporation · maynard. massachusetts

1st Printing April 1971 2nd Printing (Rev) December 1971 3rd Printing (Rev) May 1972

# Copyright © 1971, 1972 by Digital Equipment Corporation

,

•

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

# CONTENTS

| CHAPTER 1 | GENERAL INFORMATION                                  | н<br>1       |

|-----------|------------------------------------------------------|--------------|

| 1.1       | General                                              | 1-1          |

| 1.2       | Purpose                                              | 1-1          |

| 1.3       | Functional Description                               | 1-1          |

| 1.4       | Physical Description                                 | 1-5          |

| 1,4.1     | System Organization                                  | 1-5          |

| 1.4.2     | Logic and Screw Terminal Cabinet H964AA/AB           | 1-5          |

| 1.4.3     | Logic and Screw Terminal Cabinets H964CA, CB, CC, CD | 1-5          |

| 1.4.3.1   | 849A Power Control Panel                             | 1-11         |

| 1.4.3.2   | H740D Power Supply                                   | 1-11         |

| 1.4.4     | UDC8-N or -P Master File                             | 1-11         |

| 1.4.4.1   | Master Control DD01                                  | 1-11         |

| 1.4.4.2   | File Unit DD02                                       | 1-11         |

| 1.4.5     | UDC8 Expander File                                   | 1-11         |

| 1.4.6     | Functional Modules and Signal-Conditioning Modules   | 1-11         |

| 1.4.7     | Screw Terminal Cable Assembly BC40C                  | 1-13         |

| 1.5       | Specifications                                       | 1-14         |

| 1.5.1     | General                                              | 1-14         |

| 1.5.2     | System Performance                                   | 1-15         |

| 1.6       | Reference Documents                                  | 1-15         |

| CHAPTER 2 | PROGRAMMING                                          |              |

| 2.1       | IOT Format and Instructions                          | 2-1          |

| 2.2       | Address Format and Generic Code                      | 2-2          |

| 2.3       | Interrupt Structure                                  | 2-2          |

| 2.4       | Data Format                                          | 2-4          |

| 2.5       | Application Programs                                 | 2-4          |

| 2.6       | Sample Programs                                      | 2-4          |

| CHAPTER 3 | PRINCIPLES OF OPERATION                              |              |

| 3.1       | General                                              | 3-1          |

| 3.2       | Block Diagram Analysis                               | 3-1          |

| 3.3       | Detailed Circuit Analysis                            | 3-3          |

| 3.3.1     | General                                              | 3-3          |

| 3.3.2     | Device Selector and IOT Decoder                      | 3-3          |

| 3.3.3     | Addressing                                           | 3-3          |

| 3.3.4     | Interrupt and Skip Logic                             | 3-13         |

| 3.3.5     |                                                      |              |

|           | Data Gating                                          | 3-13         |

| 3.3.6     | Data Gating<br>Determining Change-of-State (COS)     | 3-13<br>3-14 |

# **CONTENTS** (Cont)

| CHAPTER 4 | NSTALLATION                                     |      |

|-----------|-------------------------------------------------|------|

| 4.1       | Site Preparation                                | 4-1  |

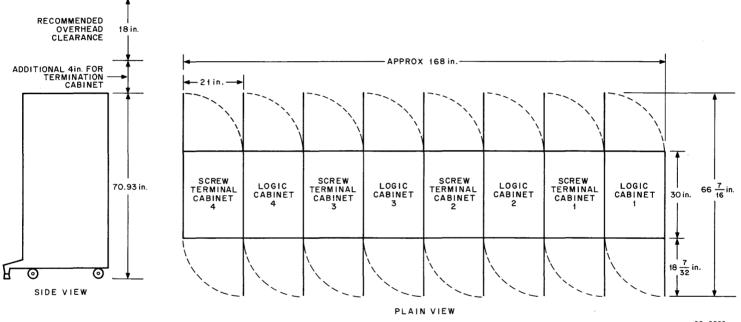

| 4.1.1     | Space Requirements                              | 4-2  |

| 4.1.2     | Environmental Conditions                        | 4-2  |

| 4.1.2.1   | Humidity and Temperature                        | 4-2  |

| 4.1.2.2   | Cleanliness                                     | 4-2  |

| 4.1.2.3   | Static Electricity                              | 4-2  |

| 4.2       | Power Requirements                              | 4-2  |

| 4.2.1     | Logic Power                                     | 4-4  |

| 4.2.2     | Primary Power Requirements                      | 4-4  |

| 4.2.3     | Primary Power Receptacles                       | 4-5  |

| 4.3       | Installation Checkout                           | 4-5  |

| 4.3.1     | Unpacking and Visual Inspection                 | 4-5  |

| 4.3.2     | I/O Bus Connections                             | 4-5  |

| 4.3.3     | UDC Bus and Connections                         | 4-6  |

| 4.3.4     | External Cabling                                | 4-6  |

| 4.3.5     | Electrical AC Power Cabling                     | 4-6  |

| 4.3.6     | DC Voltage Checks                               | 4-7  |

| 4.3.7     | UDC Functional Checkout                         | 4-7  |

| 4.3.8     | System Pre-Use Requirements                     | 4-7  |

| 4.3.9     | UDC Add On Expansion                            | 4-7  |

| 4.4       | UDC System Configuration                        | 4-8  |

| 4.4.1     | Bi-Level Interrupt Identification               | 4-8  |

| 4.4.1.1   | Module Interrupt Selection                      | 4-10 |

| 4.4.2     | System Interrupt Response                       | 4-10 |

| 4.4.3     | Generic Codes                                   | 4-10 |

| 4.4.4     | Status and Control                              | 4-11 |

| 4.4.5     | User Identification Functional I/O Modules      | 4-11 |

| 4.4.6     | Address Assignments                             | 4-11 |

| 4.5       | Functional I/O Module Setup                     | 4-17 |

|           | W730 Contact Sense Relay Input Module           | 4-19 |

|           | W732 Contact Interrupt Relay Input Module       | 4-21 |

|           | W740 Contact Sense Solid-State Input Module     | 4-25 |

|           | W742 Contact Interrupt Solid-State Input Module | 4-27 |

|           | M684 Flip-Flop Driver Output Module             | 4-31 |

|           | M686 Single-Shot Driver Output Module           | 4-33 |

|           | M802 Latching Relay Output Module               | 4-35 |

|           | M804 Flip-Flop Relay Output Module              | 4-37 |

|           | M806 Single-Shot Relay Output Module            | 4-39 |

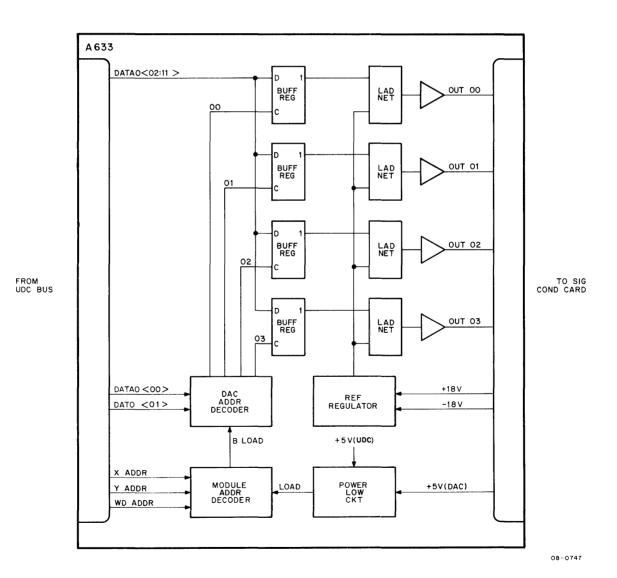

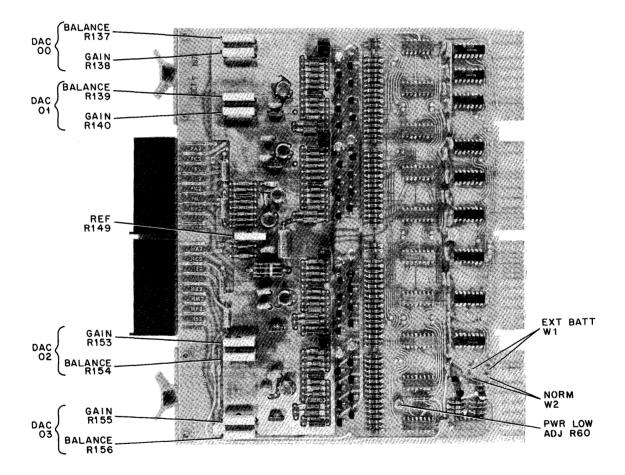

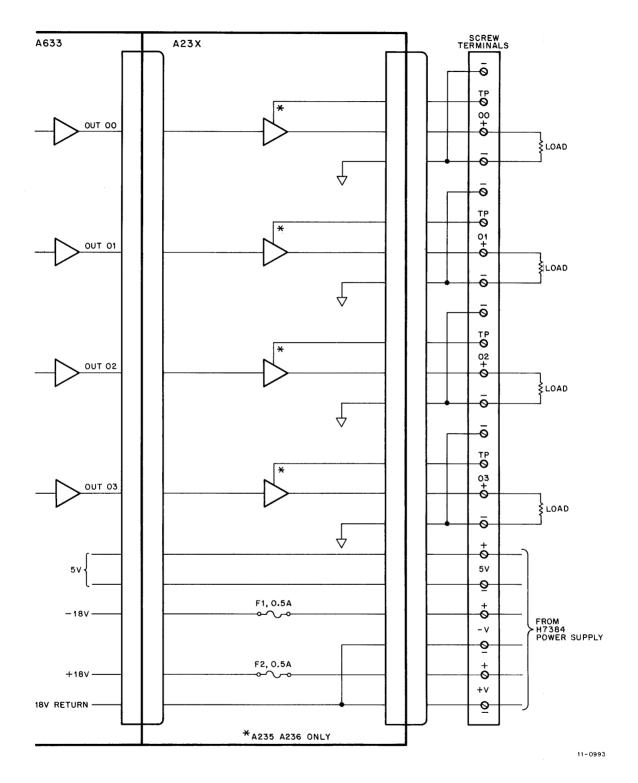

|           | A633 D/A Converter Output Module                | 4-41 |

|           | W734 I/O Counter Module                         | 4-45 |

| 4.6       | Signal Conditioning                             | 4-53 |

| 4.6.1     | Field Power                                     | 4-53 |

# **CONTENTS** (Cont)

|           |                                                          | Page |

|-----------|----------------------------------------------------------|------|

| 4.6.1.1   | Common Power                                             | 4-53 |

| 4.6.1.2   | Isolated Power                                           | 4-53 |

| 4.6.1.3   | Driver Output                                            | 4-53 |

| 4.6.2     | Input Module Signal Conditioning for Contact Sensing     | 4-53 |

| 4.6.3     | Input Module Signal-Conditioning for Logic Level Sensing | 4-53 |

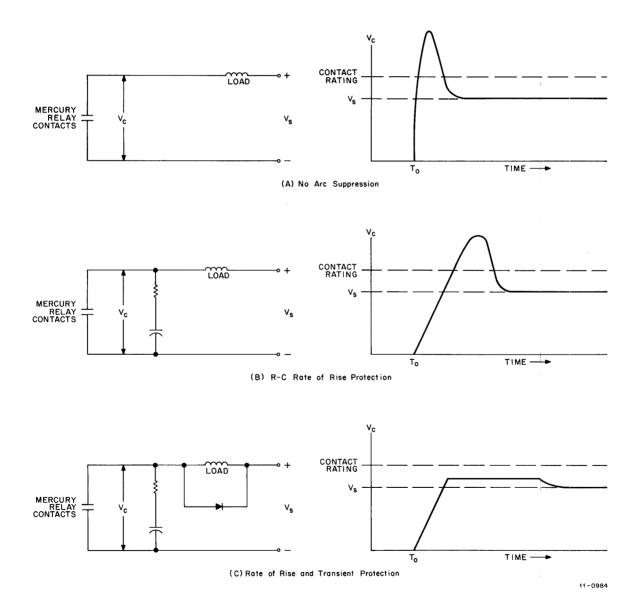

| 4.6.4     | Mercury-Wetted Relay Contact Signal Conditioning         | 4-57 |

| 4.6.4.1   | Location of the Arc Suppression Network                  | 4-57 |

| 4.6.4.2   | Determination of RC                                      | 4-57 |

| 4.6.4.3   | Load Consideration                                       | 4-57 |

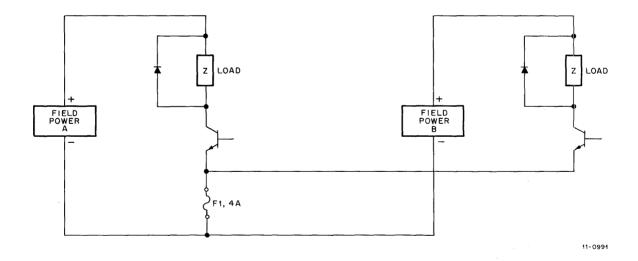

| 4.6.5     | Driver Output Signal Conditioning                        | 4-61 |

| 4.6.6     | DAC Module Signal Conditioning                           | 4-61 |

| 4.6.7     | Counter Module Signal Conditioning                       | 4-61 |

| 4.6.8     | Signal-Conditioning Module                               | 4-64 |

|           | W400 Isolated Power Signal-Conditioning Module           | 4-69 |

|           | W402 Common Power Signal-Conditioning Module             | 4-71 |

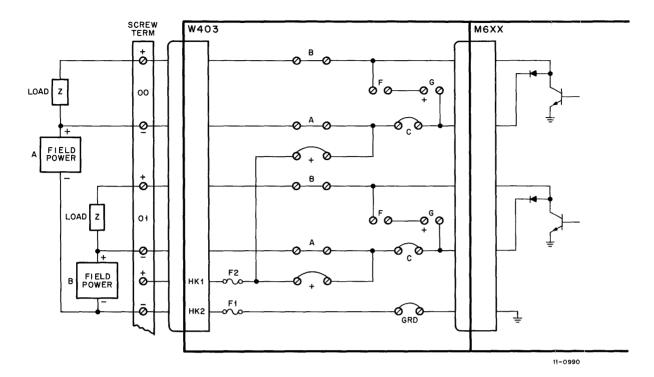

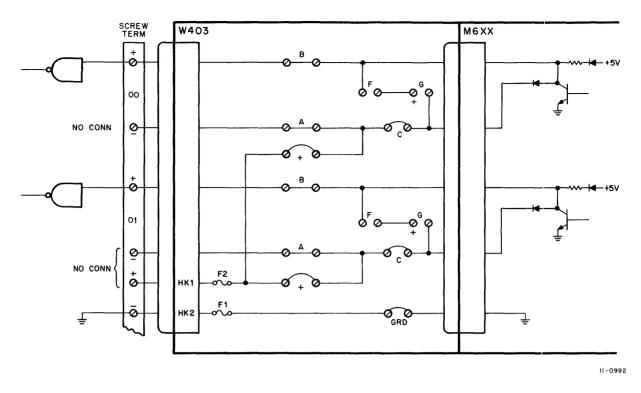

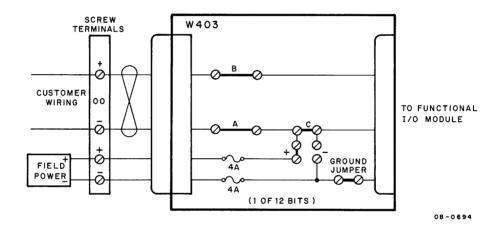

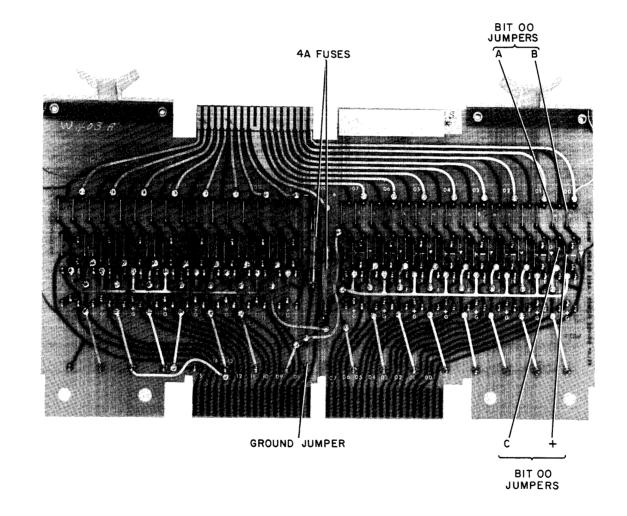

|           | W403 Solid-State Driver Signal-Conditioning Module       | 4-73 |

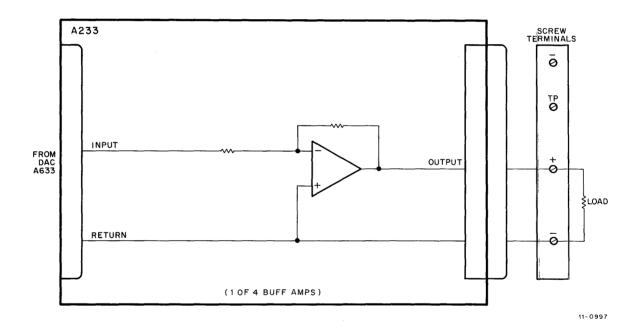

|           | A233 Buffered Voltage Signal-Conditioning Module         | 4-75 |

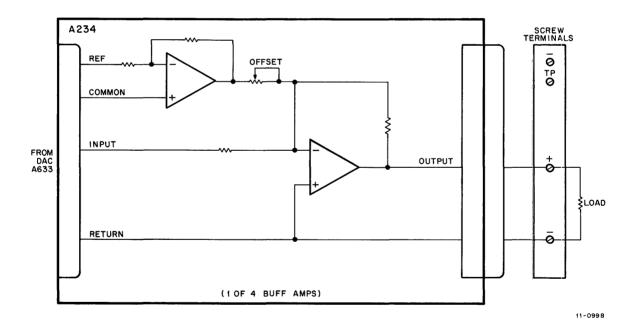

|           | A234 Buffered Voltage Signal-Conditioning Module         | 4-77 |

|           | A235 Buffered Current Signal-Conditioning Module         | 4-79 |

|           | A236 Buffered Current Signal-Conditioning Module         | 4-81 |

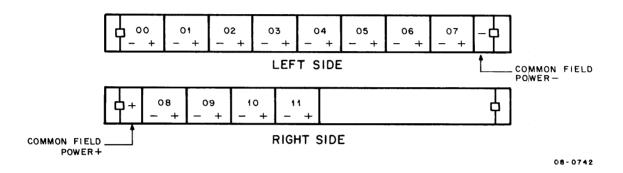

| 4.7       | Field Wiring                                             | 4-83 |

| 4.7.1     | Wire Specifications                                      | 4-83 |

| 4.7.1.1   | Analog Output Wiring                                     | 4-83 |

| 4.7.1.2   | Digital Input Wiring                                     | 4-83 |

| 4.7.1.3   | Digital Output Wiring                                    | 4-84 |

| 4.7.1.4   | Grounding                                                | 4-84 |

| 4.7.2     | Installation                                             | 4-84 |

| 4.7.2.1   | Top Entry                                                | 4-84 |

| 4.7.2.2   | Bottom Entry                                             | 4-84 |

| 4.7.2.3   | Cable Routing Lengths                                    | 4-84 |

| 4.7.2.4   | Breakouts                                                | 4-84 |

| 4.7.2.5   | Rear Terminal Assemblies                                 | 4-84 |

| 4.7.3     | Screw-Terminal Markers                                   | 4-85 |

| CHAPTER 5 | MAINTENANCE                                              | •    |

| 5.1       | General                                                  | 5-1  |

| 5.2       | Preventive Maintenance                                   | 5-1  |

| 5.3       | Corrective Maintenance                                   | 5-1  |

| 5.3.1     | General                                                  | 5-1  |

| 5.3.2     | Test Equipment Required                                  | 5-2  |

| 5.3.3     | H740D Power Supply Adjustment                            | 5-2  |

| 5.3.4     | Scanner Clock Adjustment                                 | 5-3  |

| 5.3.5     | Bus Clock Signal Adjustments                             | 5-4  |

|           |                                                          |      |

# CONTENTS (Cont)

# Page

.

# CHAPTER 6 ENGINEERING DRAWINGS

6.1 General 6-1

# ILLUSTRATIONS

| Figure No. | Title                                                       | Page |

|------------|-------------------------------------------------------------|------|

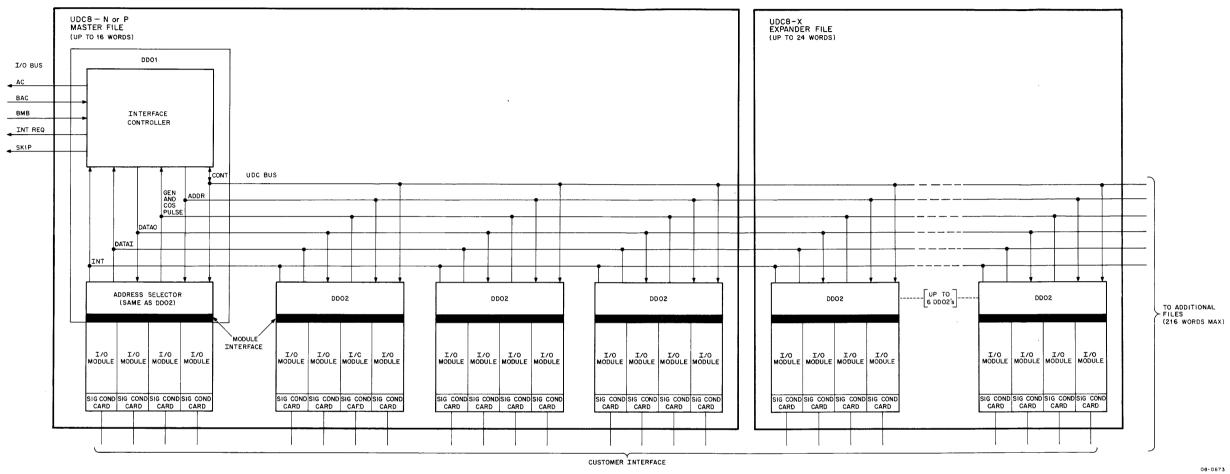

| 1-1        | UDC8 Overall Block Diagram                                  | 1-3  |

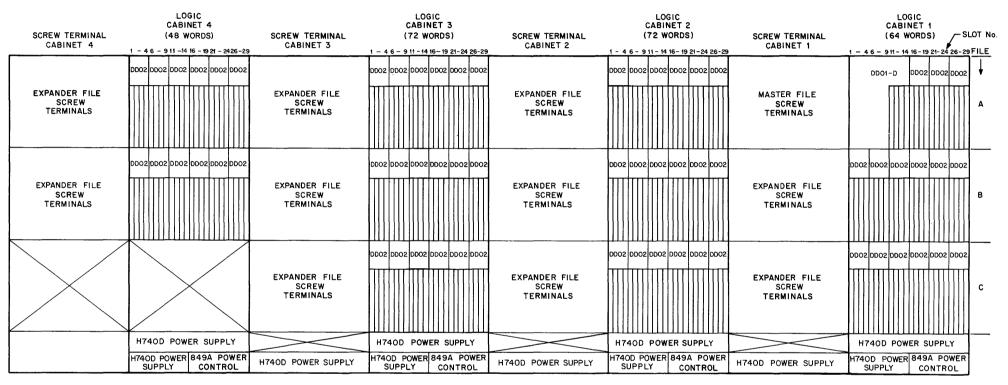

| 1-2        | UDC8 Maximum Configuration Diagram                          | 1-9  |

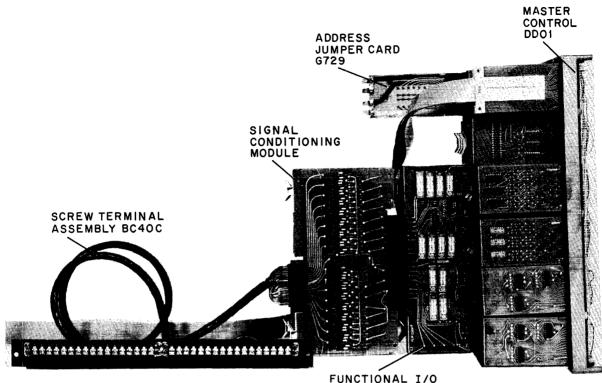

| 1-3        | DD01 and DD02 Configuration Diagram                         | 1-12 |

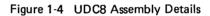

| 1-4        | UDC8 Assembly Details                                       | 1-14 |

| 2-1        | IOT Format                                                  | 2-1  |

| 2-2        | Address Format                                              | 2-3  |

| 2-3        | Status and Control Word Format                              | 2-3  |

| 2-4        | General Application Program, Flow Chart                     | 2-5  |

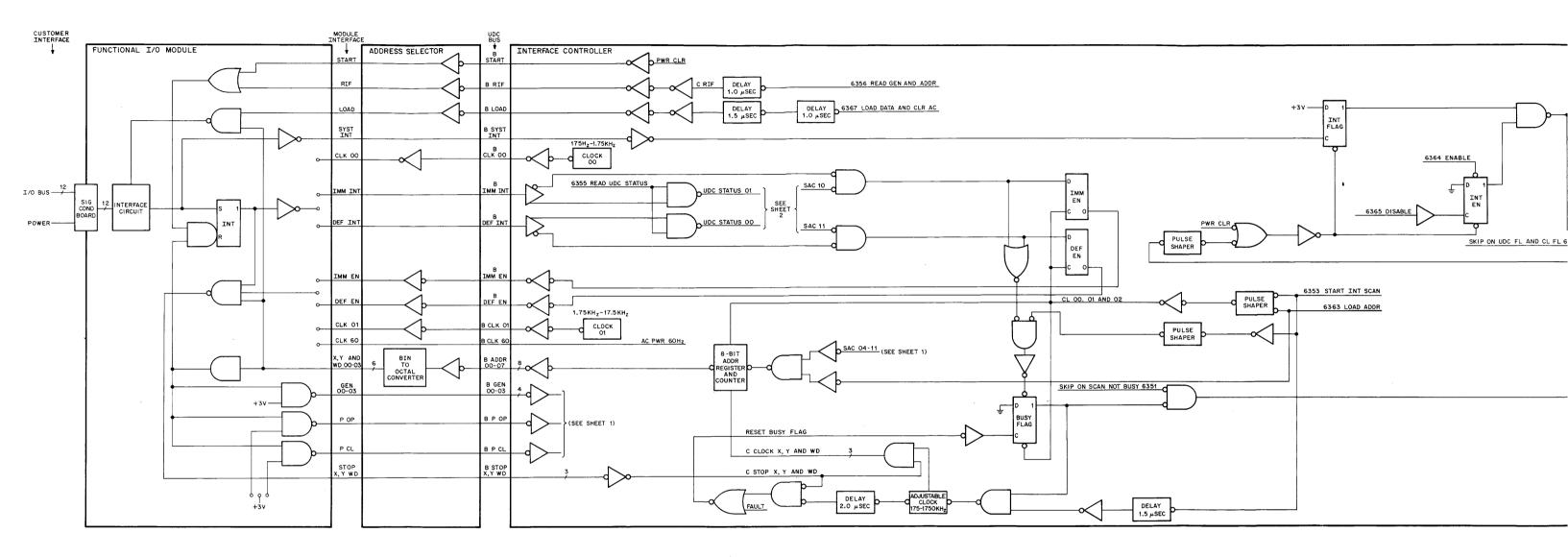

| 3-1        | UDC8 Detailed Block Diagram                                 | 3-2  |

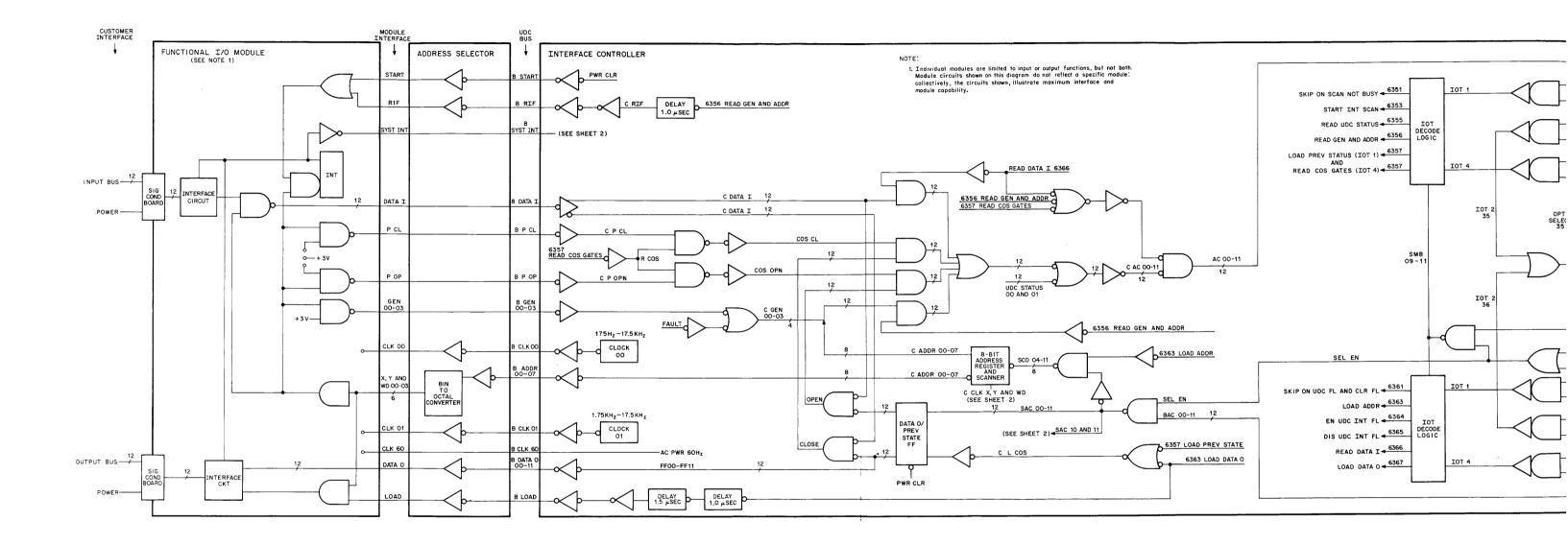

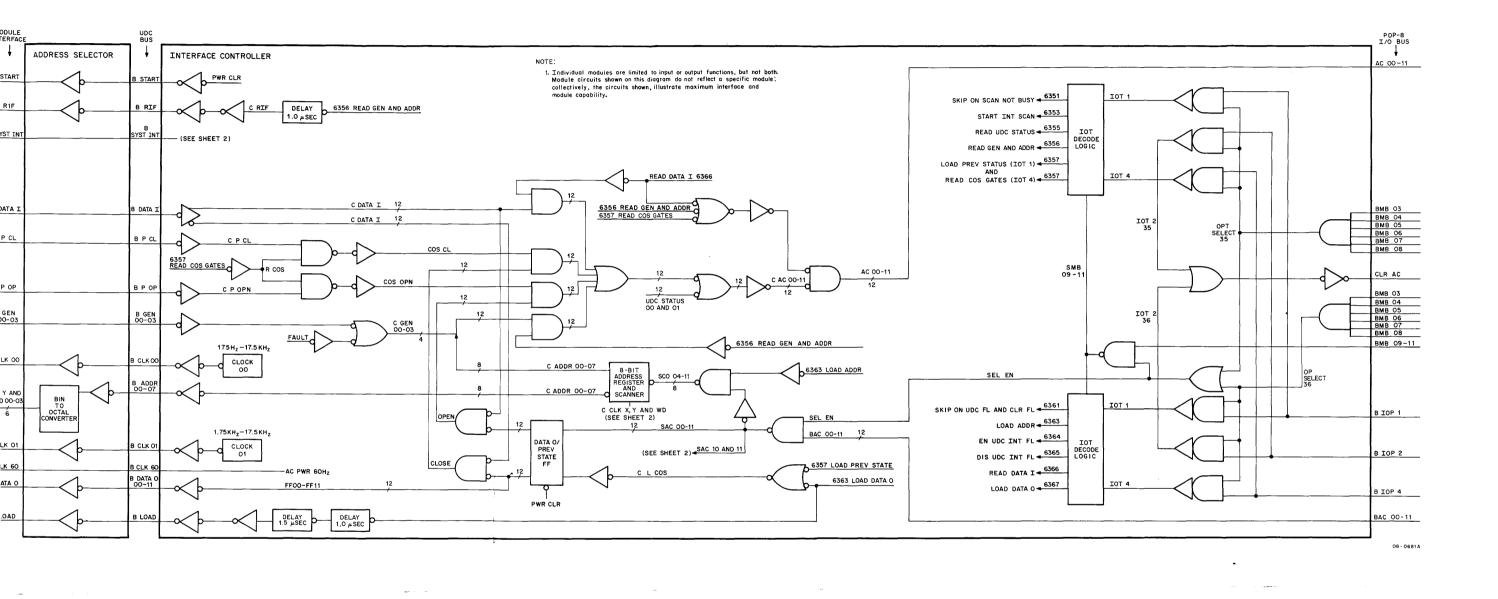

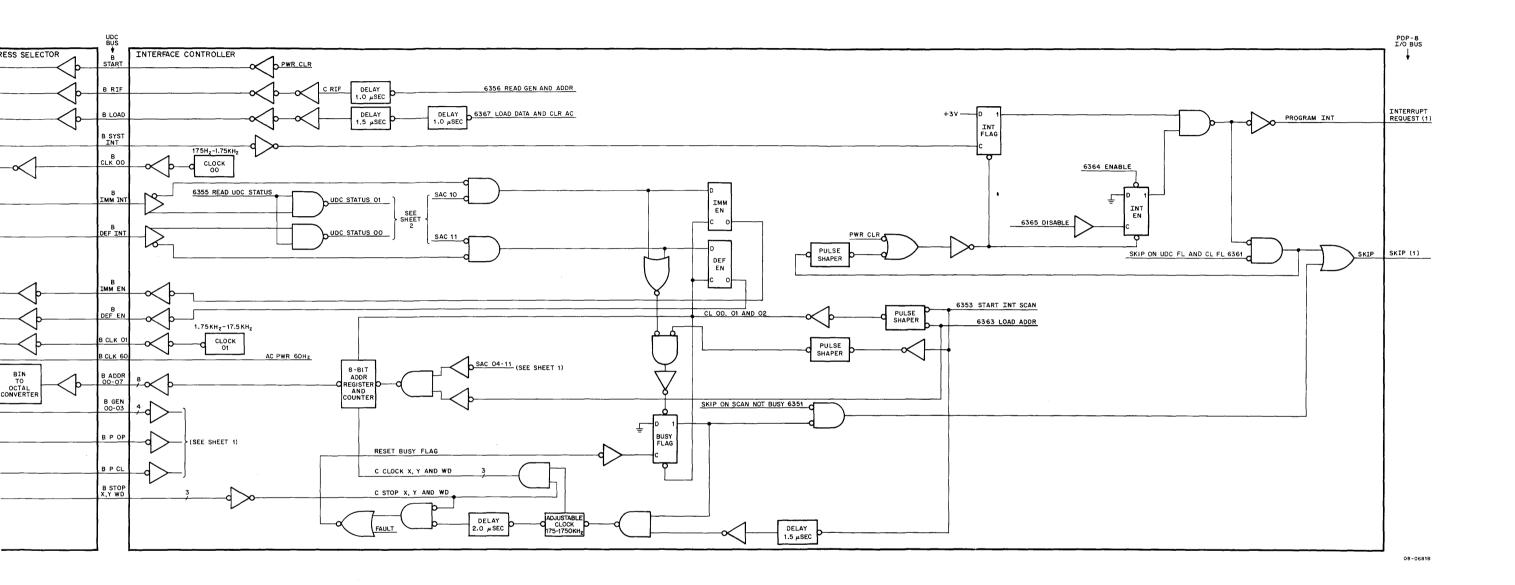

| 3-2        | UDC8 Logic Diagram                                          | 3-5  |

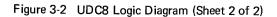

| 3-3        | IOT Decoder and Truth Table                                 | 3-9  |

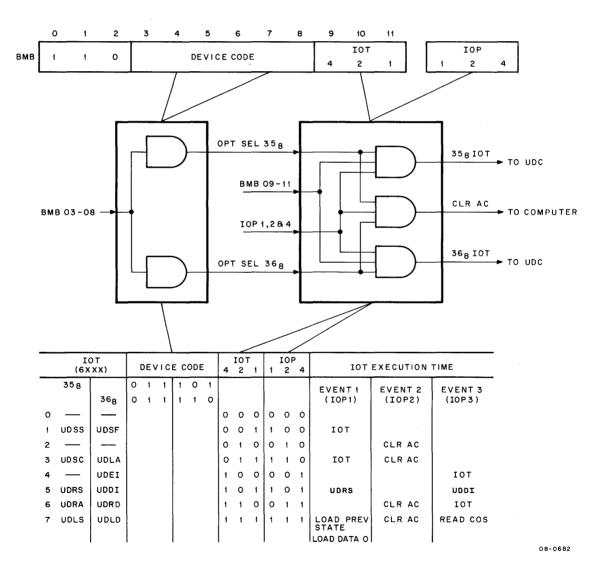

| 3-4        | Address Scanner Logic                                       | 3-11 |

| 3-5        | COS Logic                                                   | 3-15 |

| 4-1        | Space Requirements for UDC8                                 | 4-3  |

| 4-2        | UDC8 Logic Cabinet Power Distribution Block Diagram         | 4-5  |

| 4-3        | Interrupt Class Example                                     | 4-8  |

| 4-4        | Functional Module I/O Chart                                 | 4-11 |

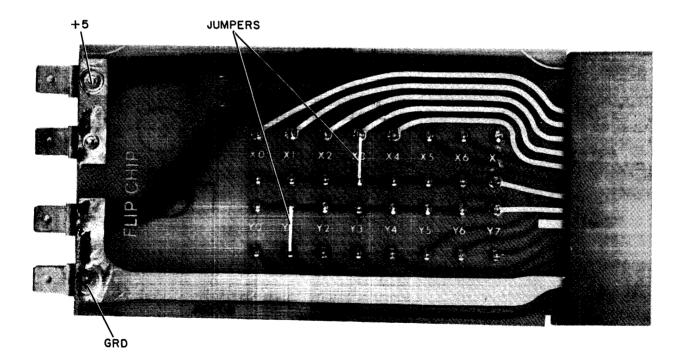

| 4-5        | Functional Module I/O Page                                  | 4-12 |

| 4-6        | G729 Address Jumper Module                                  | 4-12 |

| 4-7        | Channel Address Scheme                                      | 4-13 |

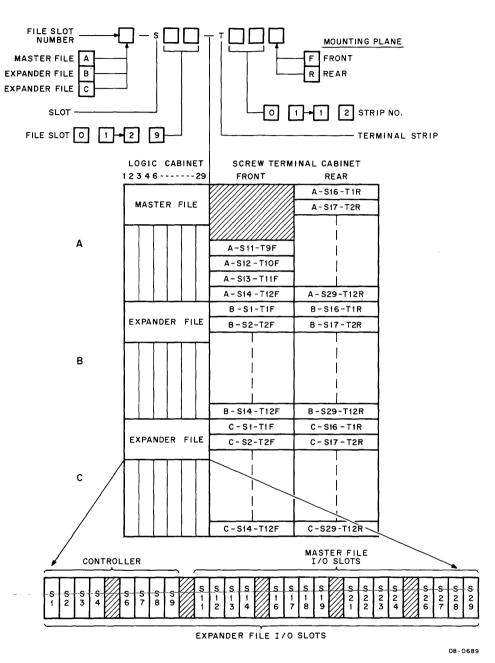

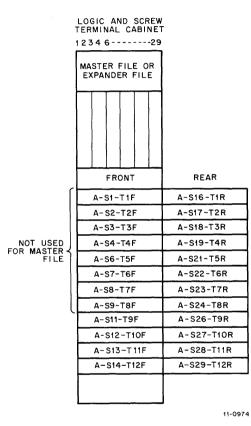

| 4-8        | Slot and Screw-Terminal Numbering Scheme                    | 4-15 |

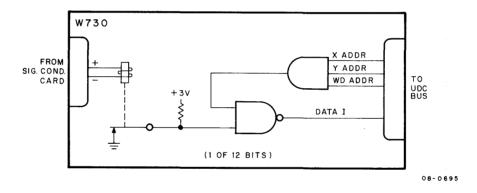

| 4-9        | Simplified Schematic Diagram (W730)                         | 4-19 |

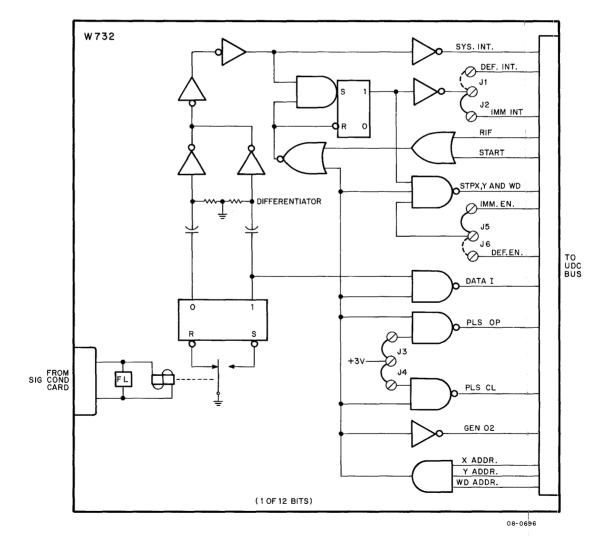

| 4-10       | Simplified Schematic Diagram (W732)                         | 4-21 |

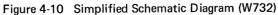

| 4-11       | Location of Jumpers (W732)                                  | 4-23 |

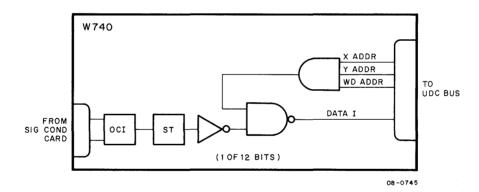

| 4-12       | Simplified Schematic Diagram (W740)                         | 4-25 |

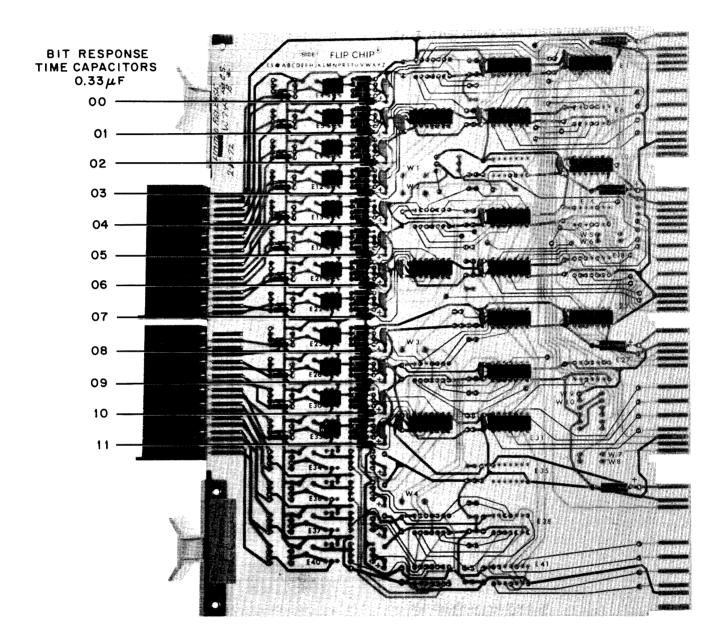

| 4-13       | Location of Bit Response Time Capacitors (W740)             | 4-26 |

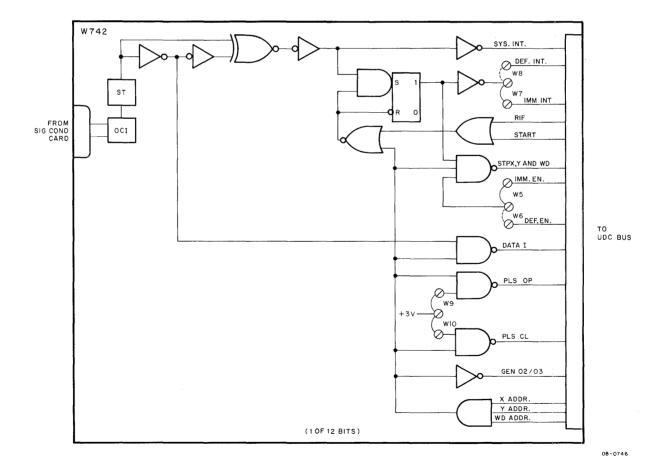

| 4-14       | Simplified Schematic Diagram (W742)                         | 4-27 |

| 4-15       | Location of Jumpers and Bit Response Time Capacitors (W742) | 4-29 |

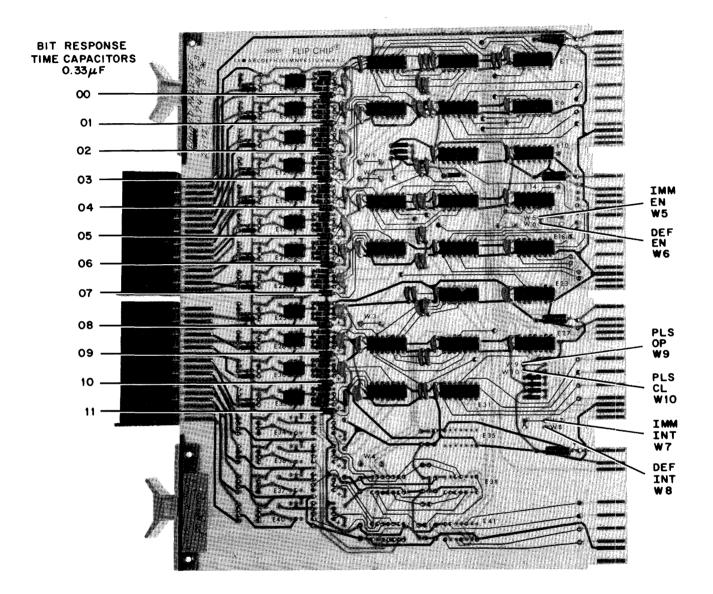

| 4-16       | Simplified Schematic Diagram (M684)                         | 4-31 |

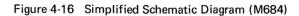

| 4-17       | Simplified Schematic Diagram (M686)                         | 4-33 |

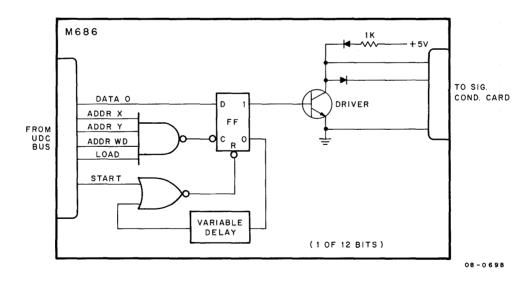

| 4-18       | Location of Bit Timeout Potentiometers and Jumpers (M686)   | 4-34 |

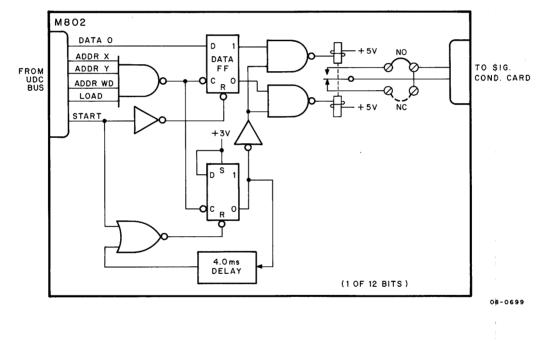

| 4-19       | Simplified Schematic Diagram (M802)                         | 4-35 |

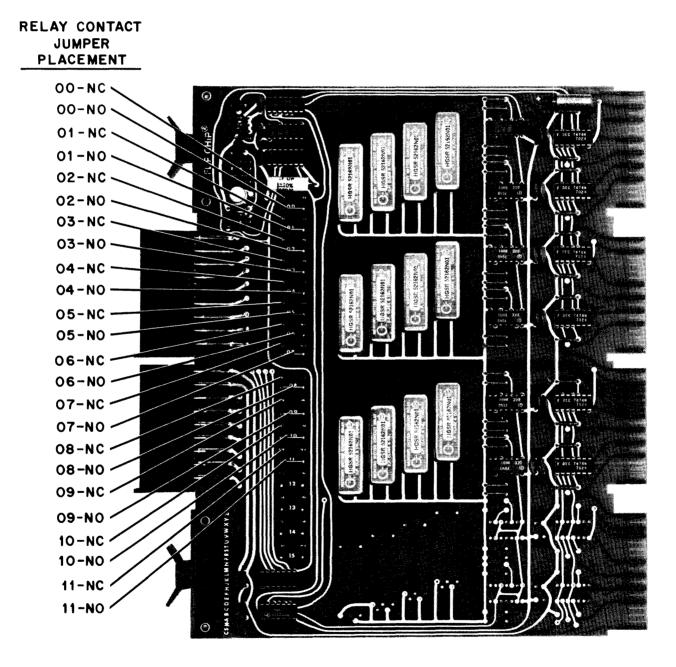

| 4-20       | Location of Bit Relay Contact Jumpers (M802)                | 4-36 |

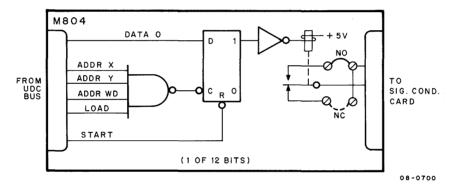

| 4-21       | Simplified Schematic Diagram (M804)                         | 4-37 |

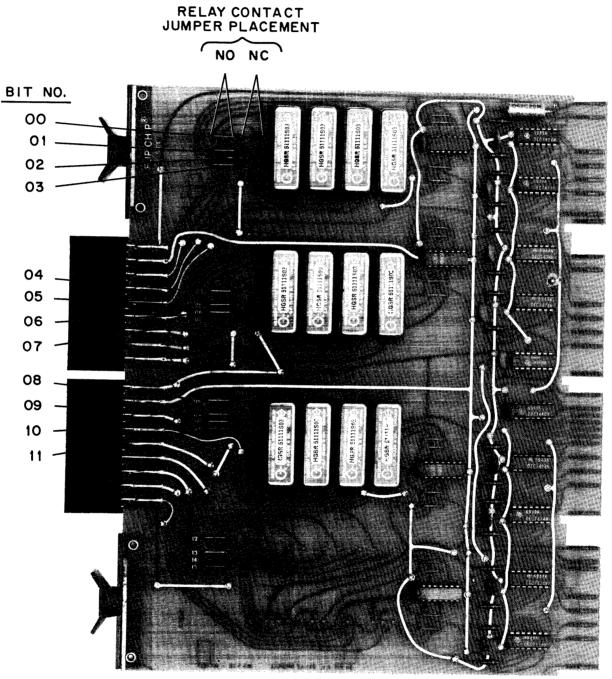

| 4-22       | Location of Bit Relay Contact Jumpers (M804)                | 4-38 |

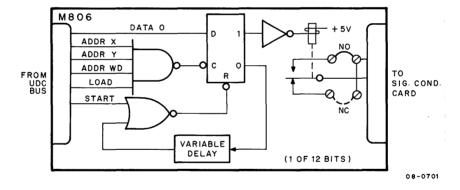

| 4-23       | Simplified Schematic Diagram (M806)                         | 4-39 |

# ILLUSTRATIONS (Cont)

|            | ILLUSTRATIONS (Cont)                                         | -    |

|------------|--------------------------------------------------------------|------|

| Figure No. | Title                                                        | Page |

| 4-24       | Location of Bit Timeout Potentiometers and Jumpers and Relay |      |

|            | Contact Jumpers (M806)                                       | 4-40 |

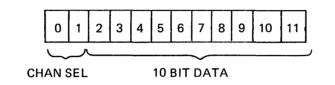

| 4-25       | Simplified Schematic Diagram (A633)                          | 4-42 |

| 4-26       | Location of Adjustments and Jumpers (A633)                   | 4-43 |

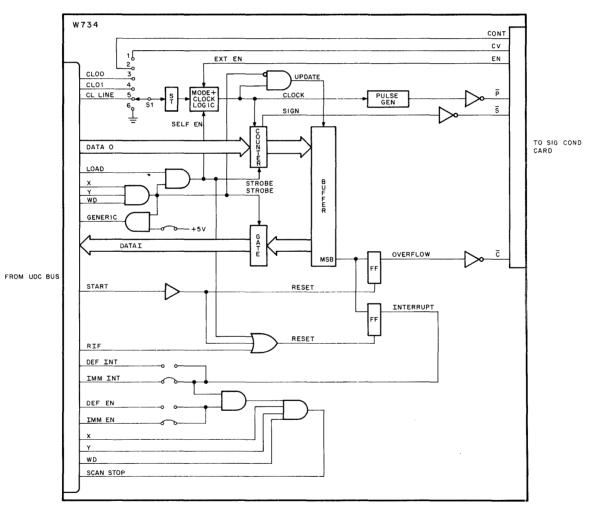

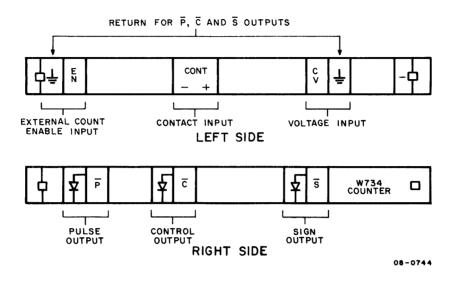

| 4-27       | Simplified Schematic Diagram (W734)                          | 4-46 |

| 4-28       | Location of Jumpers and Input Switch (W734)                  | 4-51 |

| 4-29       | Common Power for Load Switching, Wiring Diagram              | 4-54 |

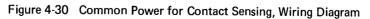

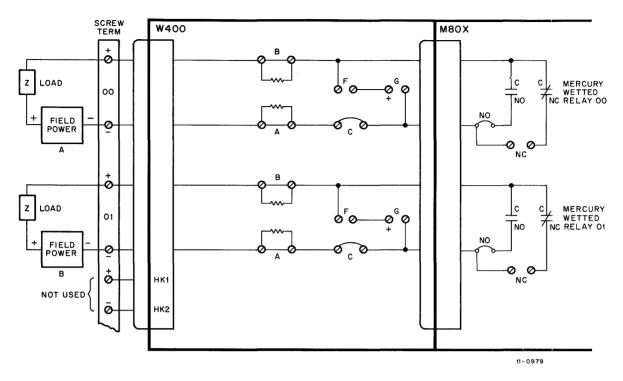

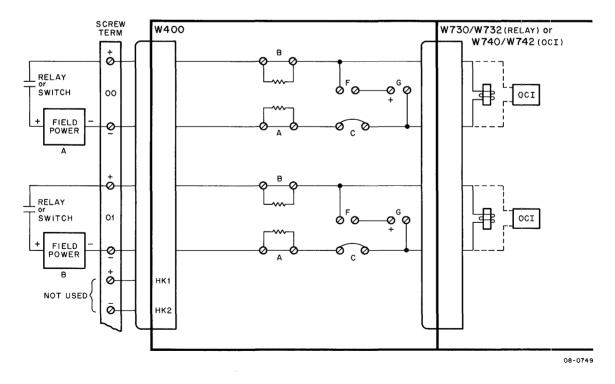

| 4-30       | Common Power for Contact Sensing, Wiring Diagram             | 4-54 |

| 4-31       | Isolated Power for Load Switching, Wiring Diagram            | 4-55 |

| 4-32       | Isolated Power for Contact Sensing, Wiring Diagram           | 4-55 |

| 4-33       | Logic Level (TTL) Input, Wiring Diagram                      | 4-56 |

| 4-34       | Logic Level (RTL) Input, Wiring Diagram                      | 4-56 |

| 4-35       | Logic Level (DTL) Input, Wiring Diagram                      | 4-57 |

| 4-36       | Contact Protection Network Nomograph                         | 4-58 |

| 4-37       | Arc Suppression Circuit Characteristics                      | 4-59 |

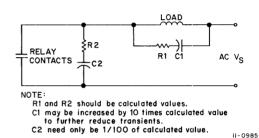

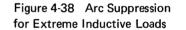

| 4-38       | Arc Suppression for Extreme Inductive Loads                  | 4-60 |

| 4-39       | Alternate Arc Suppression for Extreme Inductive Loads        | 4-60 |

| 4-40       | Arc Suppression for Capacitive Loads                         | 4-60 |

| 4-41       | Common Power for Driver Output, Wiring Diagram               | 4-62 |

| 4-42       | Common Power for Driver Output, Schematic Diagram            | 4-62 |

| 4-43       | Isolated Power for Driver Output, Wiring Diagram             | 4-63 |

| 4-44       | Isolated Power for Driver Output, Schematic Diagram          | 4-63 |

| 4-45       | Logic Level Output, Wiring Diagram                           | 4-64 |

| 4-46       | DAC Wiring Diagram                                           | 4-65 |

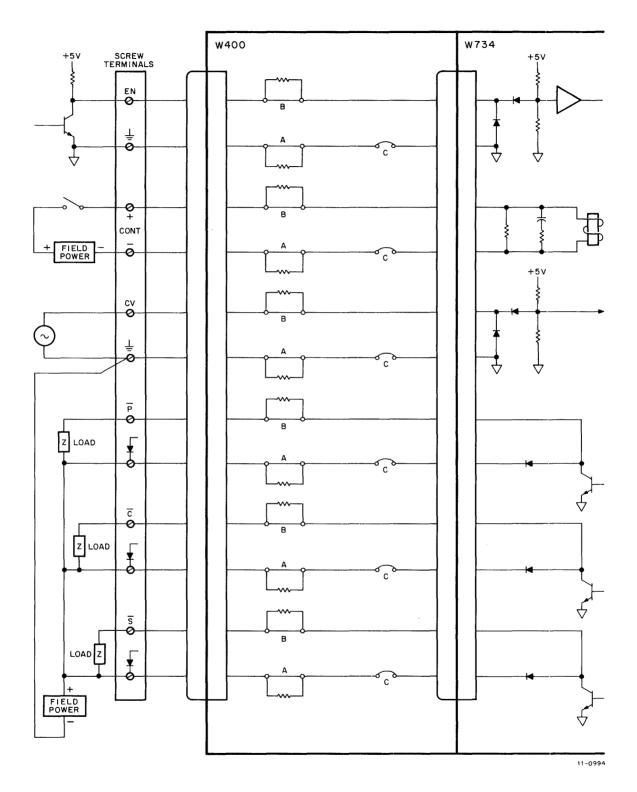

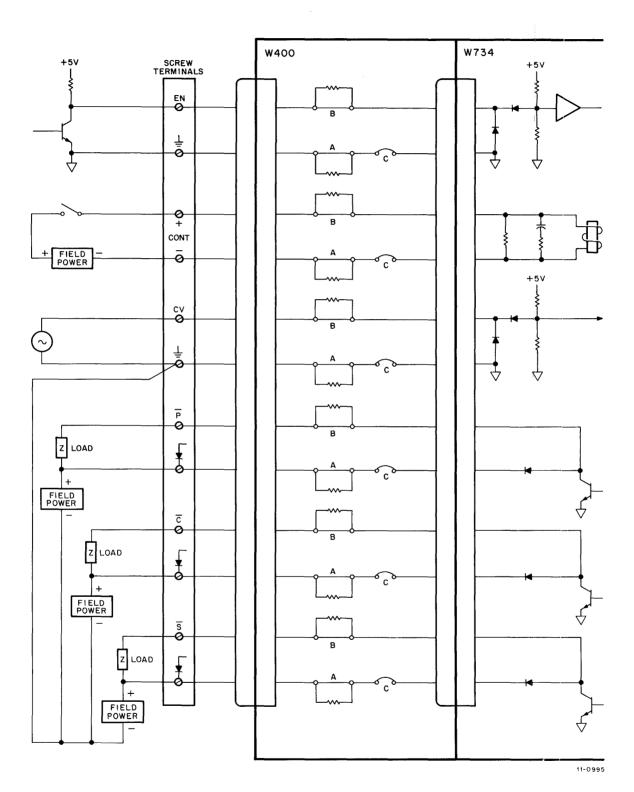

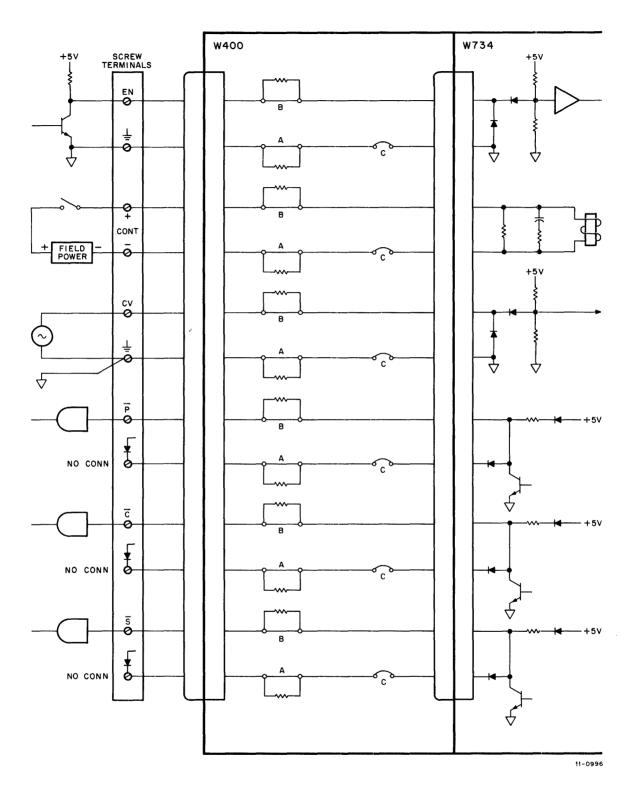

| 4-47       | Counter Input and Output (Common Power), Wiring Diagram      | 4-66 |

| 4-48       | Counter Input and Output (Isolated Power), Wiring Diagram    | 4-67 |

| 4-49       | Counter Input and Output (Logic Level), Wiring Diagram       | 4-68 |

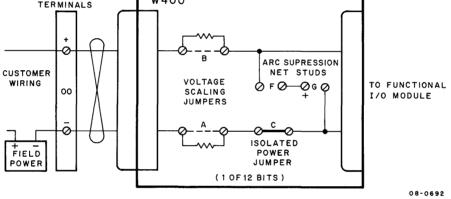

| 4-50       | Simplified Schematic Diagram (W400)                          | 4-69 |

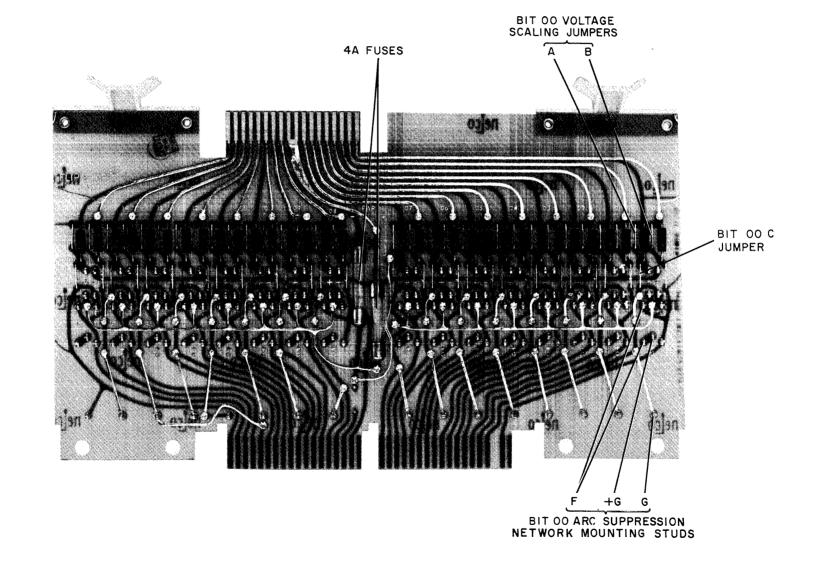

| 4-51       | Location of Jumpers and Component-Mounting Studs (W400)      | 4-70 |

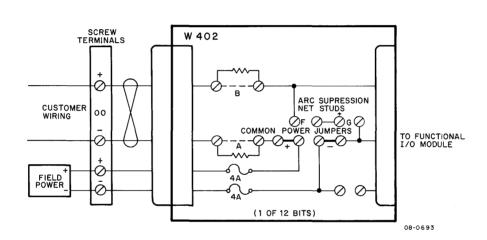

| 4-52       | Simplified Schematic Diagram (W402)                          | 4-71 |

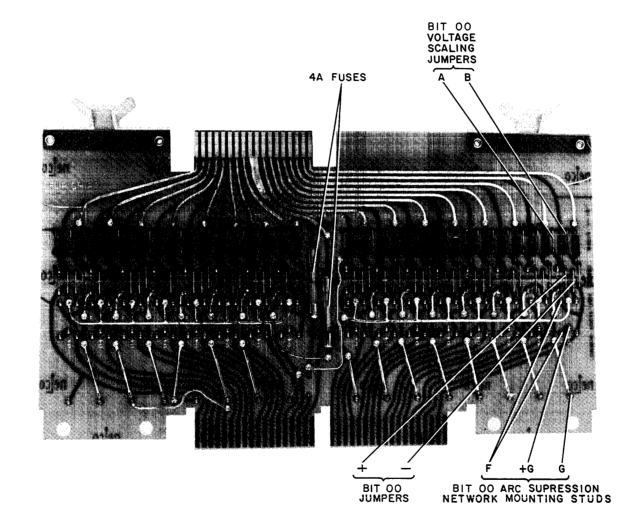

| 4-53       | Location of Jumpers and Component-Mounting Studs (W402)      | 4-72 |

| 4-54       | Simplified Schematic Diagram (W403)                          | 4-73 |

| 4-55       | Location of Jumpers (W403)                                   | 4-74 |

| 4-56       | Simplified Schematic Diagram (A233)                          | 4-75 |

| 4-57       | Simplified Schematic Diagram (A234)                          | 4-77 |

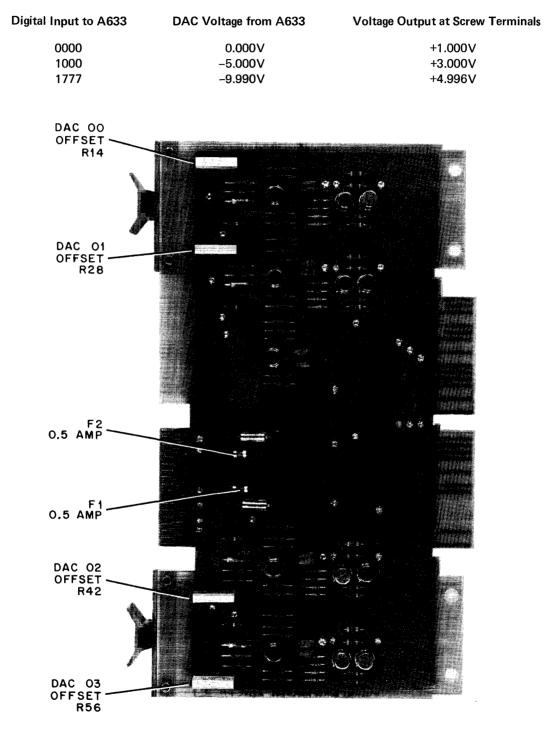

| 4-58       | Location of Adjustments and Fuses (A234)                     | 4-78 |

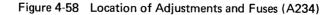

| 4-59       | Simplified Schematic Diagram (A235)                          | 4-79 |

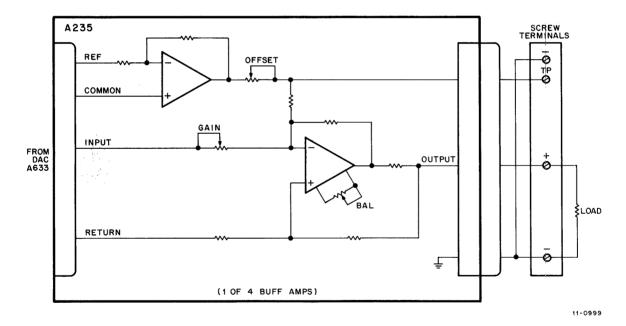

| 4-60       | Location of Adjustments and Fuses (A235)                     | 4-80 |

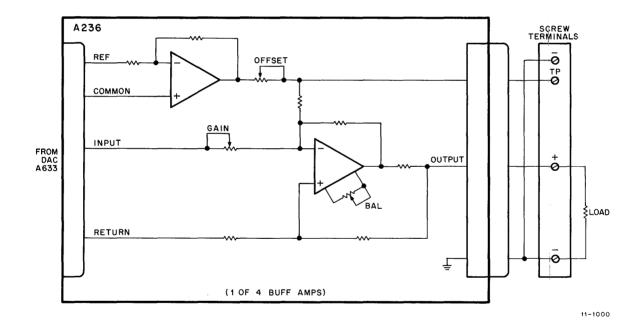

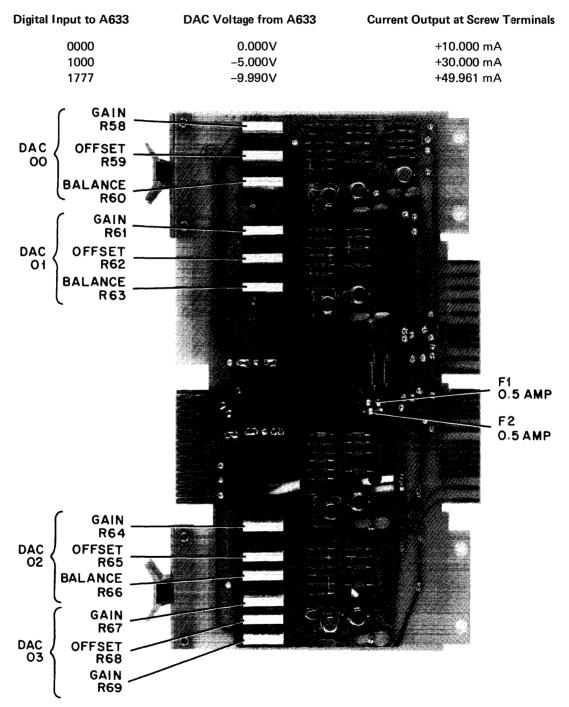

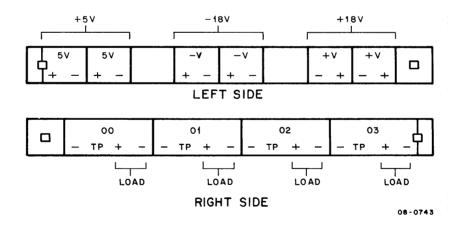

| 4-61       | Simplified Schematic Diagram (A236)                          | 4-81 |

| 4-62       | Location of Adjustments and Fuses (A236)                     | 4-82 |

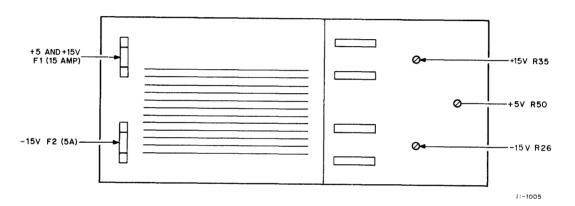

| 5-1        | H740D Power Supply Fuses and Adjustment Controls             | 5-4  |

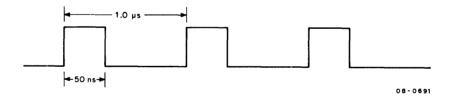

| 5-2        | Scanner Clock Waveform                                       | 5-4  |

|            |                                                              |      |

# TABLES

| Table No. | Page                                 |      |

|-----------|--------------------------------------|------|

| 1-1       | System Organization                  | 1-6  |

| 1-2       | DD01 Module Complement               | 1-13 |

| 1-3       | DD02 Module Complement               | 1-13 |

| 2-1       | UDC8 Instruction Set                 | 2-1  |

| 2-2       | UDC8 Generic Code                    | 2-3  |

| 3-1       | COS Definition Table                 | 3-14 |

| 4-1       | UDC8 Power Requirements              | 4-4  |

| 4-2       | Hubbell Wall Receptacle Part Numbers | 4-5  |

| 4-3       | Scanner Counting Characteristics     | 4-9  |

| 4-4       | Jumper Options (W732)                | 4-22 |

| 4-5       | Jumper Options (W742)                | 4-28 |

| 4-6       | Jumper Options (W734)                | 4-50 |

| 4-7       | Voltage Scaling Options              | 4-53 |

| 5-1       | H740D Voltage Tolerances             | 5-1  |

| 5-2       | Recommended Module Spares            | 5-2  |

| 5-3       | Recommended Component Spares         | 5-3  |

| 5-4       | Test Equipment Required              | 5-4  |

| 6-1       | UDC8 Engineering Drawings            | 6-1  |

# CHAPTER 1 GENERAL INFORMATION

#### 1.1 GENERAL

The UDC8 Universal Digital Controller I/O Subsystem, manufactured by Digital Equipment Corporation, is a peripheral device to be used with PDP-8 Computer Systems in industrial data acquisition and control applications. This device can be used with both the positive and the negative bus PDP-8 computers (refer to the *PDP-8 Maintenance Manual* for information on the computers and I/O bus structures).

#### **1.2 PURPOSE**

The UDC8 operates under computer program control as a highly flexible digital input/output device capable of interrogating digital inputs and driving digital outputs connected to functional modules. Up to 256 digital sense and control functional modules, each handling up to 12 individual digital points, can be directly accessed by the UDC8. I/O functions that can be handled by the existing complement of modules include driver output, relay output, contact sense, contact interrupt, and D/A converters. This complement of functional modules provides the means for controlling and monitoring most devices found in an industrial and process control environment. Selection and inclusion of appropriate functional input and output modules in the UDC8 tailors the subsystem to a specific application.

#### **1.3 FUNCTIONAL DESCRIPTION**

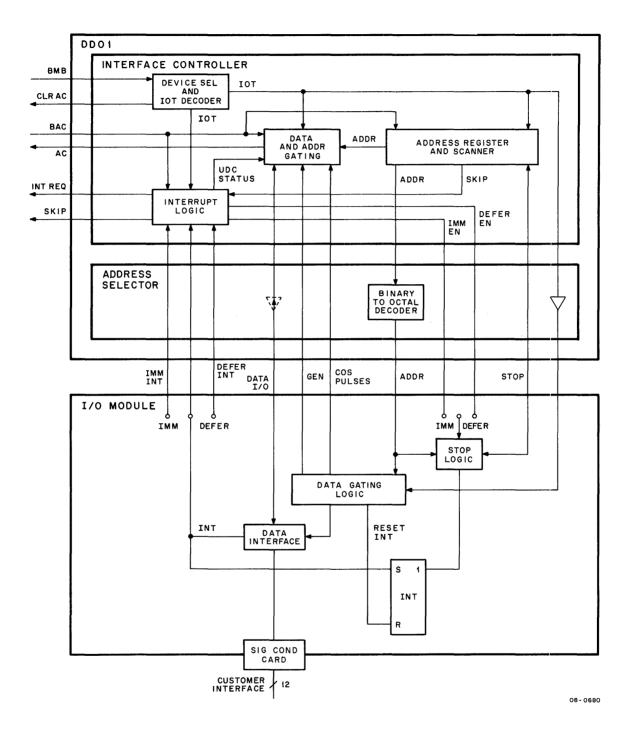

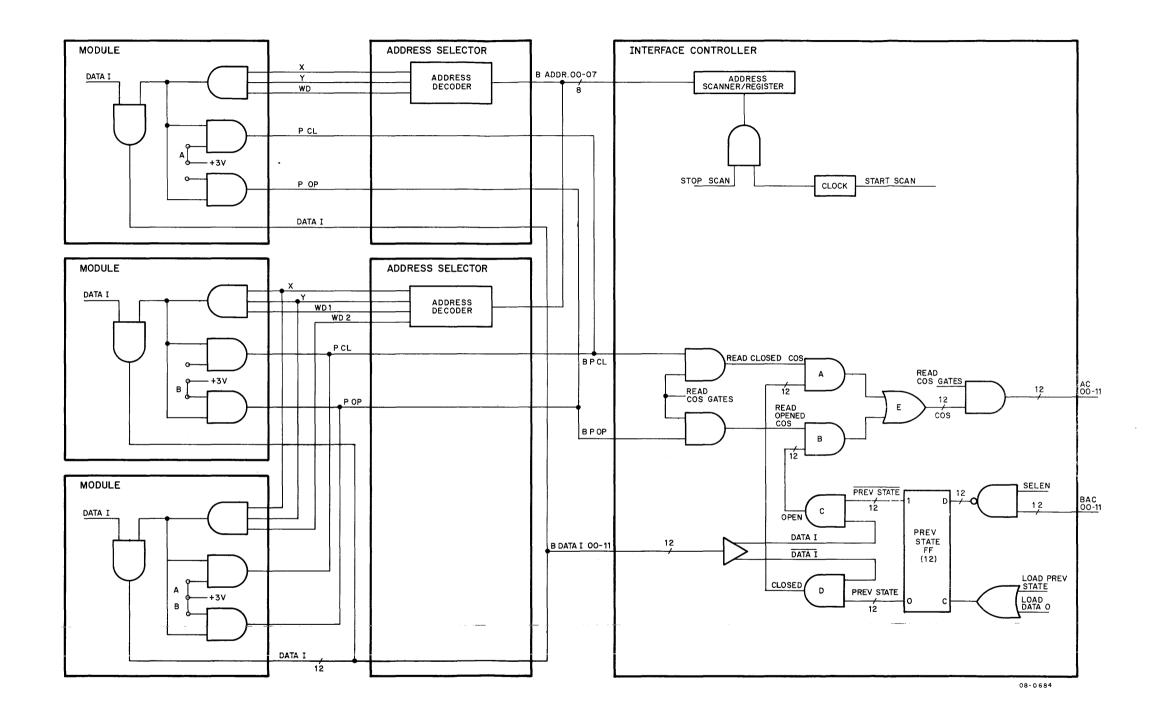

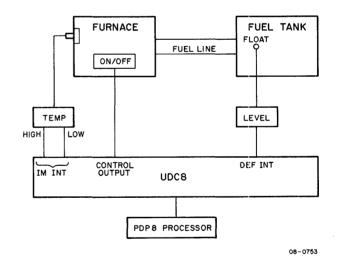

The UDC8 consists of one *master file*, up to 63 *file units* (DD02) and up to 256 *functional modules* (Figure 1-1). The *interface controller* (DD01) of the master file coordinates all activities within the UDC8 in response to programmed IOT instructions, address, and data from the computer. Each I/O file unit is set up to respond to a unique 2-digit octal address (6 binary bits), and each module slot in this unit responds to a unique 2-bit binary address.

Thus, each module can be accessed directly, using an 8-bit address. Once accessed, data (DATAO) can be loaded into the module for output control, or data (DATAI) can be read into the computer from a module to be sensed. In addition to the direct access feature, the UDC8 contains an interrupt structure, which may be enabled or disabled under program control, and an automatic scan feature to determine the address of an interrupting module. Only those functional modules that require fast program intervention are equipped with and connect to the interrupt structure. A third feature of the UDC8 is a hardware gating scheme for determining when an input contact has changed state, and the direction of that change. Both the interrupt structure and the hardware gating scheme significantly reduce computer processing overhead.

. . .....

.

Figure 1-1 UDC8 Overall Block Diagram

#### 1.4 PHYSICAL DESCRIPTION

#### 1.4.1 System Organization

The UDC8 System is completely modular for ease of system configuration and expansion (Table 1-1). For applications requiring 16 digital words (192 digital points) or less, the system is available in a *single-cabinet* configuration. Systems requiring greater than 16 digital words but less than 64 digital words are housed in a *dual-cabinet* configuration — one cabinet to mount the electronics, and one for the screw terminal connectors. Four dual-cabinet configurations are required to implement a maximum system of 256 digital words (3072 digital points).

The system's electronics cabinets are organized in files. The first file in the system is a master file which contains the computer interface, system timing and control, address/scan register, COS gating, and address decoding hardware for selection of up to four digital words. The master file can also contain three additional file units, each providing address decoding for up to four digital words. The hardware for each 4-word group is implemented by adding up to four functional I/O signal-conditioning modules and the required screw terminal cable assemblies — one for each module. Fully implemented, the master file contains 16 digital words.

Expansion beyond 16 words is accomplished by the addition of expander files. Each expander file contains provision for a total of 24 words (288 digital points) in six file units.

Industrial packaging and modular design permit the UDC8 to be configured and modified according to application needs. The UDC8 is available with screw terminals which provide a conveninet means for connecting customer field wiring to the UDC functional modules. The screw terminals can be housed in the logic cabinet or in a separate cabinet located adjacent to the logic cabinet. The logic for a maximum UDC8 configuration of 256 words (functional modules) is housed in four industrial-type cabinets. Figure 1-2 illustrates the maximum configuration, including screw terminal cabinets, and locates the major units and functional modules of the UDC8. The major units and modules are described in the following paragraphs.

#### 1.4.2 Logic and Screw Terminal Cabinet H964AA/AB

The H964AA/AB Cabinet is a 19 in. industrial-type cabinet which contains the 849A Power Control, H740D Power Supply, two top-mounted forced-air-cooling fans, air filters, and full front and rear doors. It will house one UDC8 file and, with H964MA mounting hardware, the necessary screw terminals for connection of field wiring. The UDC8 file is mounted at the top, the screw terminals just underneath, and the power elements at the bottom. Cabinet cooling is accomplished by blowing air down from the top of the cabinet and using the hole in the bottom of the cabinet for exhaust. Bottom entry of field wiring is standard, although top, rear entry is available as an option. See Figure 4-1 for cabinet dimensions.

#### 1.4.3 Logic and Screw Terminal Cabinets H964CA, CB, CC, CD

The H964CA, CB, CC, and CD Cabinets consist of a pair of 19 in. industrial-type cabinets secured to each other. The right-hand cabinet (as viewed from the wirewrap side) houses the UDC logic, while the left-hand cabinet contains the necessary screw terminals. The logic cabinet is capable of housing up to three UDC8 files. In addition to the UDC8 files, the logic cabinet contains the 849A Power Control, one H740D Power Supply for each file implemented, two top-mounted forced-air-cooling fans, air filters, and full front and rear doors. The screw terminal cabinet contains the necessary screw terminals for connection of field wiring. The screw terminals are secured to the cabinet with H964MA mounting hardware. Bottom entry of field wiring is standard, although top, rear entry is available as an option.

| Table 1-1           |

|---------------------|

| System Organization |

| ltem            | Description                                                                                                                                                                                                                                                                                                                                                                                              | Model                                                                                                                                                                                                                                                         | Prerequisite                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| System Cabinets | Single cabinet for UDC System up to 16 digital words<br>(192 digital points). Contains logic power supply,<br>cooling fans, and filters. Screw terminals that mount<br>in the same cabinet requires separate mechanical as-<br>sembly (Model H964MA).                                                                                                                                                    | H964A (bottom entry only of field<br>cables).<br>A-115V power supply<br>B-230V power supply                                                                                                                                                                   |                                                                   |

|                 | Mechanical assembly for mounting screw terminals in single cabinets.                                                                                                                                                                                                                                                                                                                                     | H964MA                                                                                                                                                                                                                                                        | H964AA or H964AE                                                  |

|                 | EXAMPLE: Model H964AA designates a single cab with 115V power supply).                                                                                                                                                                                                                                                                                                                                   | ninet (bottom entry only of field cables,                                                                                                                                                                                                                     |                                                                   |

|                 | Dual cabinet for UDC8 System. One cabinet houses<br>system electronics and logic (contains logic power sup-<br>plies, cooling fans, and filters). Second cabinet for<br>termination of input field wiring on screw terminals.                                                                                                                                                                            | H964C<br>A-top or bottom entry of field<br>cables. 115V power supply<br>B-bottom entry only of field<br>cables. 115V power supply<br>C-top or bottom entry of field<br>cables. 230V power supply<br>D-bottom entry only of field<br>cables. 230V power supply | · · · · · · · · · · · · · · · · · · ·                             |

| Master File     | Basic UDC8 system file contains interface and control,<br>address/scan register, change-of-state (COS) gating, and<br>provision for installing four functional I/O modules<br>(48 digital points) and I/O cable. Master file may be<br>expanded to 16 digital words (192 digital points) by<br>adding three DD02 File Units and appropriate number<br>of functional I/O and signal-conditioning modules. | UDC8 N-negative bus interface<br>P-positive bus interface                                                                                                                                                                                                     | H964A or H964C<br>PDP-8/I<br>H964A or H964C<br>PDP-8/L or PDP-8/E |

(continued on next page)

| Item                              | Description                                                                                                                                                                                                                                                                                                                                                |         | Model                                                                                                        | Prerequisite                                                                   |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Expander File                     | Provides expansion capability. Expander file contains<br>mounting hardware, file I/O cable, and provision for<br>installing four digital words and up to five DD02 File<br>Units, each capable of containing four digital words.<br>(Fully implemented expander file contains 24 func-<br>tional I/O modules – 24 digital words or 288 digital<br>points.) | UDC8-X  | A-second or third file in<br>electronics cabinets<br>B-first file in each additional<br>electronics cabinets | UDC8 Master File<br>plus H964C Dual<br>Cabinet<br>Second H964C Dual<br>Cabinet |

| File Units                        | Provides address decoding, control logic, and DD02 ca-<br>pacity for mounting up to four functional I/O and sig-<br>nal-conditioning modules (four digital words or 48<br>digital points).                                                                                                                                                                 |         |                                                                                                              | UDC8 Master File,<br>Expander Files                                            |

| Functional I/O                    | Contact Sense (relay)                                                                                                                                                                                                                                                                                                                                      | W730    |                                                                                                              | Master File,                                                                   |

| Modules                           | Contact Interrupt (relay)                                                                                                                                                                                                                                                                                                                                  | W732    |                                                                                                              | Expander Files,                                                                |

|                                   | Contact Sense (Solid State)                                                                                                                                                                                                                                                                                                                                | W740    |                                                                                                              | DD02 File Units                                                                |

|                                   | Contact Interrupt (Solid State)                                                                                                                                                                                                                                                                                                                            | W742    |                                                                                                              |                                                                                |

|                                   | Single-shot Driver                                                                                                                                                                                                                                                                                                                                         | M686    |                                                                                                              |                                                                                |

|                                   | Single-shot Relay                                                                                                                                                                                                                                                                                                                                          | M806    |                                                                                                              |                                                                                |

|                                   | Flip-flop Driver                                                                                                                                                                                                                                                                                                                                           | M684    |                                                                                                              |                                                                                |

|                                   | Flip-flop Relay                                                                                                                                                                                                                                                                                                                                            | M804    |                                                                                                              |                                                                                |

|                                   | Latching Relay                                                                                                                                                                                                                                                                                                                                             | M802    |                                                                                                              |                                                                                |

|                                   | DAC                                                                                                                                                                                                                                                                                                                                                        | A633    |                                                                                                              |                                                                                |

|                                   | I/O Counter                                                                                                                                                                                                                                                                                                                                                | W734    |                                                                                                              |                                                                                |

| Signal-Conditioning               | Common Power                                                                                                                                                                                                                                                                                                                                               | W400    |                                                                                                              | Functional I/O                                                                 |

| Modules                           | Isolated Power                                                                                                                                                                                                                                                                                                                                             | W402    |                                                                                                              | Module                                                                         |

|                                   | Solid State Driver                                                                                                                                                                                                                                                                                                                                         | W403    |                                                                                                              |                                                                                |

|                                   | Buffer – 0V to +10V                                                                                                                                                                                                                                                                                                                                        | A233    |                                                                                                              |                                                                                |

|                                   | Buffer – +1V to +5V                                                                                                                                                                                                                                                                                                                                        | A234    |                                                                                                              |                                                                                |

|                                   | Buffer – 4 mA to 20 mA                                                                                                                                                                                                                                                                                                                                     | A235    |                                                                                                              |                                                                                |

|                                   | Buffer – 10 mA to 50 mA                                                                                                                                                                                                                                                                                                                                    | A236    |                                                                                                              |                                                                                |

| Screw Terminal/<br>Cable Assembly | Provides screw terminal connection for one word.<br>Connects to signal-conditioning module.                                                                                                                                                                                                                                                                | BC40C-4 |                                                                                                              | Signal-Conditioning<br>Module                                                  |

# Table 1-1 (Cont) System Organization

•

.

08-0674

.....

## Figure 1-2 UDC8 Maximum Configuration Diagram

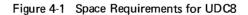

**1.4.3.1 849A Power Control Panel** — The power control panel located in the front of the logic cabinet controls the application and removal of system primary power. The power control contains a LOCAL/REMOTE switch, a power ON indicator, a primary power contactor, and a circuit breaker. When the LOCAL/REMOTE switch is placed in REMOTE, application and removal of primary power can be controlled from the computer. For the LOCAL position, primary power is controlled by using the front panel 30A circuit breaker.

**1.4.3.2** H740D Power Supply – The H740D Power Supplies are located as shown in Figure 1-2. They produce regulated +5V (20A) and -15V potentials for the file logic circuits and I/O modules. The +5V and power ground outputs are made available at an output connector on the rear of the supply. These outputs are routed to each of the files by separate wire runs. Ground and +5V are connected from file unit to file unit, using jumpers on the rear of the G729 Modules. The -15V potential is used only for level conversions involved with a negative I/O bus interface, and is therefore routed only to the master file. The supply contains a 15A fuse for +5V, and a 5A fuse for -15V.

#### 1.4.4 UDC8-N or -P Master File

The master file contains one DD01 Master Control, space for up to three DD02 File Units, power supply harness, I/O bus cables, and bus terminators.

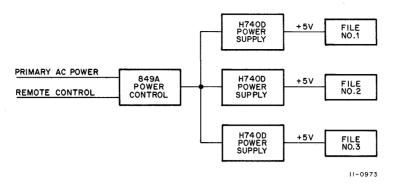

**1.4.4.1** Master Control DD01 – The DD01 Master Control (Figure 1-3) occupies three file unit slots in a UDC8 Master File, and offers four insertion slots for functional modules. Only one master control is required for full utilization of the UDC8. Two types of master controls are available. One type is required to interface with the PDP-8 family of computers having a positive I/O bus, and another for the PDP-8 family of computers having a negative bus. The only difference in the two types of master controls is the module complement as listed in Table 1-2.

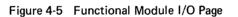

**1.4.4.2** File Unit DD02 – The DD02 File Unit occupies one of six available locations in a file and contains four slots for functional modules. Although 63 file units are required for full utilization of the UDC8, any number of file units (up to 63) can be serviced by one master control. The module complement of the DD02 is listed in Table 1-3. The DD02 is an expander assembly which contains 24 slots arranged in four vertical rows of six slots. The upper two slots in each row constitute an extension of the UDC bus. The lower four slots in each row constitute a unique address within the address field, into which any of the functional modules may be inserted. The M851 Address Decoder and G729 Address Jumper Module occupy the second pair of slots in the bus section (AB2) and serve the four I/O slots below.

#### 1.4.5 UDC8 Expander File

The expander file is a housing which contains a DD02 File Unit and may contain up to five additional DD02 File Units, a BC41A Bus Extender, and one M935 Bus Connector per DD02.

#### 1.4.6 Functional Modules and Signal-Conditioning Modules

There are several types of functional modules available for the UDC8. Some serve as input modules for receiving sensory or control data from customer devices; others perform output functions for controlling customer devices. A detailed description, a simplified schematic, and a photograph of each module currently available are provided in Chapter 4. The functional modules are plugged into slots provided by the master file, expander files, and DD02 File Units (Figure 1-4). Each functional module requires a signal-conditioning module for normalizing input voltages, fusing, arc suppression, and for connection to field wiring. These modules are also described in Chapter 4. The 12 data bits and field power connections on the signal-conditioning module are brought to the screw-terminal cabinet via a cable consisting of 18 twisted pairs.

|   | 1    | 2    | 3    | 4    | 5              | 6    | 7    | 8    | 9    | 10             | 11   | 12              | 13 | 14   | 1    | 2               | 3 | 4    |

|---|------|------|------|------|----------------|------|------|------|------|----------------|------|-----------------|----|------|------|-----------------|---|------|

| А | M903 | M903 | M903 | G772 |                | M113 | M112 | M624 | M623 | $ \ /$         | M942 | M851<br>G729    |    | M935 | M935 | M851<br>G729    |   | M935 |

| В |      |      |      | *    | $\backslash /$ | *    | M510 | M510 | M510 | $\backslash$ / |      | **              |    | ***  | ***  | **              |   | ***  |

| С | *    | M169 | M169 | M169 | V              | *    | M302 | M206 | M206 | V              |      | Four            |    |      |      | Four            |   |      |

| D | *    | M111 | M111 | M115 | $\Lambda$      | M115 | M113 | M112 | M206 | $\land$        |      | Function        |    |      |      | Function        |   |      |

| E | M206 | M112 | M113 | M602 | /              | M111 | M302 | M307 | M401 | $/ \setminus$  |      | Module<br>Slots |    |      |      | Module<br>Slots |   |      |

| F | M206 | M112 | M112 | M602 | \              | M304 | M401 | M401 |      | $  \rangle$    |      | 51010           |    |      |      |                 |   |      |

\*Modules in these slots are as follows

Positive Bus

DD01 (P)

B4

- M101

B6 and C6

- M103

C1 and D1

- M623

Negative Bus

DD01 (N)

B4

- M100

B6 and C6

- M102

C1 and D1

- M633

\*\*Module G729 plugs into rear of Module M851.

\*\*\*Flat Mylar Cable BC41A-5 is used to interconnect files within a cabinet from slot AB4 of the last DD02 of a file to slot AB1 of the first DD02 of the next file. A BC41A-10 Cable is required when extending the UDC bus to the first DD02 in a new cabinet. Module M942 plugs into slot AB4 of the last DD02.

Figure 1-3 DD01 and DD02 Configuration Diagram

| UDC8-N<br>Negative Bus | UDC8-P<br>Positive Bus | Name                         | Quantity | Location                   |  |  |  |

|------------------------|------------------------|------------------------------|----------|----------------------------|--|--|--|

| M100                   | M101                   | Bus Data Interface           | 1        | B4                         |  |  |  |

| M102                   | M103                   | Device Selector              | 2        | B6 and C6                  |  |  |  |

| M111                   | M111                   | Inverters                    | 3        | D2, D3, and E6             |  |  |  |

| M112                   | M112                   | NOR Gates                    | 5        | A7, D8, E2, F2, and F3     |  |  |  |

| M113                   | M113                   | NAND Gates                   | 3        | A6, D7, and E3             |  |  |  |

| M115                   | M115                   | NAND Gates                   | 2        | D4 and D6                  |  |  |  |

| M169                   | M169                   | Gating Module                | 3        | C2, C3, and C4             |  |  |  |

| M206                   | M206                   | General-Purpose Flip-Flops   | 5        | C8, C9, D9, E1, F1, and F4 |  |  |  |

| M302                   | M302                   | Dual Delay Multivibrator     | 3        | C7, E7                     |  |  |  |

| M304                   | M304                   | Pulse Shaper                 | 1        | F6                         |  |  |  |

| M307                   | M307                   | Dual Integrating One-Shot    | 1        | E8                         |  |  |  |

| M401                   | M401                   | Variable Clock               | 3        | E9, F7, and F8             |  |  |  |

| M510                   | M510                   | I/O Bus Receiver             | 3        | B7, B8, and B9             |  |  |  |

| M602                   | M602                   | Pulse Amplifier              | 2        | E4 and F1                  |  |  |  |

| M633                   | M633                   | Bus Driver                   | 2        | C1 and D1                  |  |  |  |

| M623                   | M623                   | Bus Driver                   | 1        | A9                         |  |  |  |

| M624                   | M624                   | Bus Driver                   | 1        | A8                         |  |  |  |

| M851                   | M851                   | Address Decoder/Bus Receiver | 1        | AB12                       |  |  |  |

| M903                   | M903                   | Flat Mylar Connector         | 3        | AB1, AB2, and AB3          |  |  |  |

| M942                   | M942                   | Terminator Module            | 2        | AB11 and AB14              |  |  |  |

| G729                   | G729                   | Address Jumper Module        | 1        | AB12 (Piggy-back on M851)  |  |  |  |

| G772                   | G772                   | Power Connector              | 1        | A4                         |  |  |  |

Table 1-2 DD01 Module Complement

Table 1-3 DD02 Module Complement

| Type/Part No. | Name                         | Quantity | Location                 |  |

|---------------|------------------------------|----------|--------------------------|--|

| M935          | UDC Bus Extender             | 1        | AB1*                     |  |

| M851          | Address Decoder/Bus Receiver | 1        | AB2                      |  |

| G729          | Address Jumper Module        | 1        | AB2 (Piggy-back on M851) |  |

\*See Paragraph 4.3.2 for bus extension details.

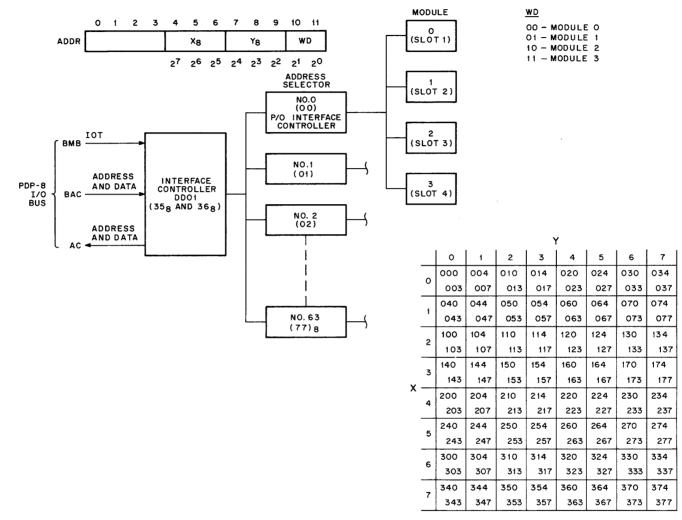

#### 1.4.7 Screw Terminal Cable Assembly BC40C

Field wiring is connected to screw terminal assemblies (BC40C-4) which make the necessary connections between the signal-conditioning modules and the field-wiring terminations. Each BC40C Assembly makes connections available through 16 of the 18 twisted pairs for control wiring. The two remaining pairs provide paralleled conductors for bringing in external excitation power when using common power signal conditioning. Only 12 control pairs are used with UDC8 Functional Modules. Each circuit is completed through a twisted pair of No. 26 AWG stranded color-coded wires connected to a pair of screw terminals. The terminals will accommodate No. 14 AWG wire, and are arranged in two strips of 17 terminals, each supported in line by a common steel angle support.

FUNCTIONAL I/O MODULE

## 1.5 SPECIFICATIONS

| 1.5.1 | General                                                    |                                                                                                                                                                                                                                                            |                                      |  |

|-------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

|       | Operating temperature:                                     | 0° to 50°C                                                                                                                                                                                                                                                 |                                      |  |

|       | Humidity:                                                  | Up to 95% without condens                                                                                                                                                                                                                                  | sation                               |  |

|       | Cooling and filtering:                                     | and filtering: Dust filters and blower fans in each logic cabinet<br>bottom exhaust                                                                                                                                                                        |                                      |  |

|       | Input cabling:                                             | Top or bottom entry to supplied screw terminals.<br>Screw terminals will accommodate No. 14 AWG wires.<br>However, customer wiring should be limited to No. 18<br>AWG (max) 2-wire twisted pair per digital point for a<br>fully-wired cabinet (72 words). |                                      |  |

|       | Cabinet dimensions:                                        | Single Cabinet                                                                                                                                                                                                                                             | Dual Cabinet                         |  |

|       | Height:<br>Bottom entry:<br>Top entry:<br>Width:<br>Depth: | 72 in.<br>75 in.<br>21 in.<br>30 in.                                                                                                                                                                                                                       | 72 in.<br>75 in.<br>42 in.<br>30 in. |  |

|       | Power:                                    | 115/230V, 50 to 60 Hz, single-phase, 500 VA (max)<br>for logic. Possible additional 700W for 48V field exci-<br>tation in 72 12-bit words of signal conditioning.                                                    |  |  |

|-------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       | Heat dissipation:                         | 1800 Btu/hr for logic power. Possible additional 2500<br>Btu/hr for 72 12-bit words of signal conditioning.                                                                                                          |  |  |

| 1.5.2 | System Performance                        |                                                                                                                                                                                                                      |  |  |

|       | Modes of operation:                       | <ul> <li>a. Programmed digital output</li> <li>b. Programmed analog output</li> <li>c. Programmed digital input</li> <li>d. Interrupt controlled input</li> <li>e. Interrupt controlled counting function</li> </ul> |  |  |

|       | Data Format:                              | (Paragraph 2.4)                                                                                                                                                                                                      |  |  |

|       | Number of digital inputs and outputs:     | 256 12-bit words (3072 digital points) maximum                                                                                                                                                                       |  |  |

|       | Type of input and output:                 | See functional modules described in Chapter 4                                                                                                                                                                        |  |  |

|       | Input and output word (module) selection: | Directly addressable                                                                                                                                                                                                 |  |  |

|       | Interrupt module identification:          | 4-bit module generic code and an 8-bit address                                                                                                                                                                       |  |  |

|       | Interrupt scan:                           | Locates address and module type in a minimum of 5 $\mu s$ (20 $\mu s$ worst case)                                                                                                                                    |  |  |

|       | I/O data rate:                            | 1 x 10 <sup>5</sup> 12-bit words/sec                                                                                                                                                                                 |  |  |

|       | Computer interface:                       | Direct interface to positive or negative bus PDP-8<br>Computers                                                                                                                                                      |  |  |

|       | System clock rates:                       | <ul> <li>Three clocks are available to each I/O word:</li> <li>a. 0.63V rms at line frequency</li> <li>b. 175 Hz - 1.75 kHz adjustable</li> <li>c. 1.75 kHz - 17.5 kHz adjustable</li> </ul>                         |  |  |

For functional and signal-conditioning module specifications, see Chapter 4.

For controller module replacement schematics, see Volume II.

## **1.6 REFERENCE DOCUMENTS**

The following documents are essential in gaining an understanding of the PDP-8 Computer System:

Small Computer Reference Manual PDP-8 Maintenance Manual PDP-8 User Guide

The following diagnostic program is essential in establishing the performance of the UDC8 subsystem:

UDC8 System Function Exerciser UDC-8EX (MainDEC-08-D8YB-D)

.

# CHAPTER 2 PROGRAMMING

## 2.1 IOT FORMAT AND INSTRUCTIONS

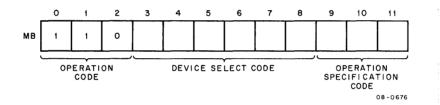

The UDC8 responds to eleven unique IOT instructions employing device select codes  $35_8$  and  $36_8$ . These eleven instructions, along with other computer instructions, are used to develop the program for controlling the operation of the UDC8. The IOT instruction format is illustrated by Figure 2-1; each instruction is listed and described in Table 2-1.

Figure 2-1 IOT Format

| Mnemonic | Instruction Code<br>(Octal) | Operation                                                                                                                                                                                  |

|----------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UDSF     | 6361                        | Skip on UDC Flag and Clear Flag — If the UDC flag<br>is set this instruction will generate a skip pulse, caus-<br>ing the computer to skip the next instruction and<br>clear the UDC flag. |

| UDEI     | 6364                        | Enable UDC Interrupt Flag                                                                                                                                                                  |

| UDDI     | 6365                        | Disable UDC Interrupt Flag                                                                                                                                                                 |

| UDLA     | 6363                        | Load Address — An 8-bit address (AC 04 through 11)<br>is loaded into the address/scanner register of the<br>UDC8 for accessing a specific module, after which<br>accumulator is cleared.   |

Table 2-1 UDC8 Instruction Set

(continued on next page)

## Table 2-1 (Cont) UDC8 Instruction Set

| Mnemonic | Instruction Code<br>(Octal) | Operation                                                                                                                                                                                                                                                                                                               |

|----------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UDRD     | 6366                        | Read Data – Clears the accumulator and reads data from whichever module has its address stored in the address/scanner register.                                                                                                                                                                                         |

| UDLD     | 6367                        | Load Data — Loads contents of accumulator into which-<br>ever module has its address stored in the UDC address/<br>scanner register, after which accumulator is cleared.                                                                                                                                                |

| UDSS     | 6351                        | Skip On Scan Not Busy — This instruction will cause<br>the computer to skip the next instruction when the<br>scanner register has located the interrupting module<br>(used only after 6353).                                                                                                                            |

| UDSC     | 6353                        | Start Address Scan – Initiates address scan and clears accumulator. Bit 10 enables scan for immediate in-<br>terrupts; bit 11 enables scan for deferred interrupts.                                                                                                                                                     |

| UDRA     | 6356                        | Read Address and Generic Type – The accumulator<br>is cleared. The contents of the address scanner regis-<br>ter and the module type code (generic) of the module<br>in that address are loaded into the accumulator as a<br>12-bit word.                                                                               |

| UDLS     | 6357                        | Load Previous Status and Read Change of State (COS)<br>Gates — This instruction loads the contents of the<br>accumulator (previous status of the interrupting mod-<br>ule) into the COS register of the UDC, clears the accu-<br>mulator, and reads the exclusive OR function of the<br>COS gates into the accumulator. |

| UDRS     | 6355                        | Read UDC Status – Read UDC status (immediate AC bit 10, or deferred AC bit 11).                                                                                                                                                                                                                                         |

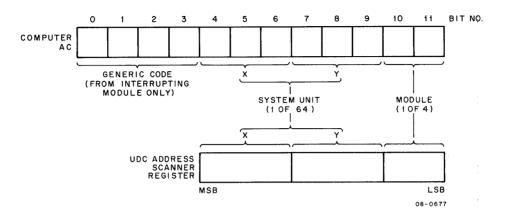

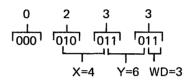

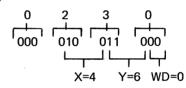

### 2.2 ADDRESS FORMAT AND GENERIC CODE

The address/scanner register in the UDC serves a dual purpose. It serves as a buffer register when the UDC is directly addressed by the computer, and as a scanner register upon command to find the address of an interrupting module. The address format and the bit values of the address in the accumulator and the scanner/register are illustrated in Figure 2-2. The generic codes, used only to identify which type of module generated an interrupt, are listed and defined in Table 2-2. These codes may be used in directing the program to jump to unique servicing routines.

## 2.3 INTERRUPT STRUCTURE

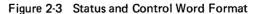

The interrupt structure of the UDC can be enabled or disabled under program control. If enabled and a module issues an interrupt, the interrupt structure can be interrogated under program control to determine whether the module requires immediate service or whether services can be deferred. When interrogated, the UDC issues a

status word. The status word format is illustrated in Figure 2-3. Subject to the result of the interrogation, the automatic scan may be started to search selectively for the address of the deferred or the immediate interrupt module. In multiple interrupts, the lowest channel address is always found.

Figure 2-2 Address Format

Table 2-2

| UDC8 Generic Codes                                                   |  |  |  |  |

|----------------------------------------------------------------------|--|--|--|--|

| Type of Module                                                       |  |  |  |  |

| No interrupts present<br>Fault condition                             |  |  |  |  |

| Contact interrupt W733<br>Contact interrupt W743<br>I/O counter W734 |  |  |  |  |

| I/O counter W734<br>I/O counter W734<br>I/O counter W734             |  |  |  |  |

|                                                                      |  |  |  |  |

0 7 10 2 3 5 8 9 11 6 NOT USED STATUS BITS BIT 10 BIT 11 TYPE OF INTERRUPT 0 0 1 NO INTERRUPT 0 DEFERRED INTERRUPT IMMEDIATE INTERRUPT 1 Ó DEFERRED AND IMMEDIATE INTERRUPT 08-0678

The search is selective because the processor issues a control word when the scan is started to enable one or both types of interrupt modules for the search. The format of the control word is identical to the status word. After locating and servicing an interrupt, it must be determined that no further interrupts await servicing. This may be done either by reading UDC status (6355), or by issuing another start scan (6353) instruction. A return of generic code 0000 indicates no further interrupts are set.

#### 2.4 DATA FORMAT

The data transferred between the computer and the UDC modules is an unstructured 12-bit word. The 12 bits may be unrelated, as in the case of driving or sensing individual digital points, or may represent a 12-bit number for presetting or reading a counter or a 2-bit channel code and a 10-bit number for driving a digital-to-analog converter. Bit 0 on the module corresponds to bit 0 in the accumulator.

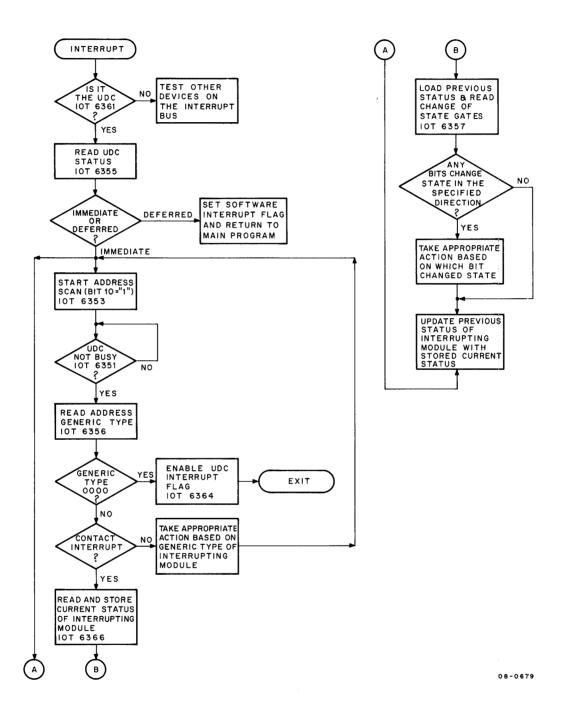

### 2.5 APPLICATION PROGRAMS

Application programs for the UDC8 will vary from one application to the next. However, to provide some insight into the use of the UDC IOT instructions, a flow chart presenting some operational characteristics of the UDC relative to the IOTs is presented in Figure 2-4.

#### 2.6 SAMPLE PROGRAMS

Program No. 1

This sample routine reads the contents of the switch register, then outputs the information to the selected address.

| BEGIN, | 200<br>201 | 7300<br>1211 | CLA,CLL<br>TAD ADDRESS |                                   |

|--------|------------|--------------|------------------------|-----------------------------------|

|        | 202        | 6363         | UDLA                   | /LOAD ADDRESS TO UDC              |

|        | 203        | 7604         | LAS                    |                                   |

|        | 204        | 6367         | UDLD                   | /OUTPUT DATA TO SELECTED          |

|        | 205        | 2210         | ISZ DELAY              | ADDRESS THEN                      |

|        | 206        | 5205         | JMP1                   | /DELAY FOR TIME SPECIFIED         |

|        | 207        | 5200         | JMP BEGIN              |                                   |

|        | 210        | 0000         | DELAY, 0000            |                                   |

|        | 211        | 0000         | ADDRESS,0000           | /DEPOSIT ADDRESS IN THIS LOCATION |

#### Program No. 2

This sample program selects the address, then reads the data into the AC register from the input module.

| BEGIN | 200<br>201 | 7300<br>1207 | CLA,CLL<br>TAD ADDRESS |                                   |

|-------|------------|--------------|------------------------|-----------------------------------|

|       | 201        | 1201         | IND ADDRESS            |                                   |

|       | 202        | 6363         | UDLA                   | /LOAD ADDRESS                     |

|       | 203        | 6366         | UDRD                   | /THEN READ DATA IN                |

|       | 204        | 2210         | ISZ                    | /AND DELAY FOR TIME               |

|       | 205        | 5204         | JMP1                   | /SPECIFIED                        |

|       | 206        | 5200         | JMP BEGIN              |                                   |

|       | 207        | 0000         | ADDRESS,0000           | /DEPOSIT ADDRESS IN THIS LOCATION |

|       | 210        | 0000         | DELAY,0000             |                                   |

Figure 2-4 General Application Program, Flow Chart

~

## Program No. 3

This sample program is a routine to handle interrupts coming from Contact Interrupt (W732) Modules. First the interrupt circuitry is enabled, then, when an interrupt occurs, the scanner is activated to find the address of the interrupting module. When the address is found, it and the generic code are read, the COS is determined, and the data are read in. After each HALT check the data, then press CONTINUE.

| BEGIN | 200                                                  | 7300                                                         | CLA,CLL                                                                                                        | <pre>/ENABLE THE INTERRUPT CIRCUIT</pre>                                                                                                                     |

|-------|------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 201                                                  | 6364                                                         | UDEI                                                                                                           | /AND SKIP ON INTERRUPT FLAG                                                                                                                                  |

|       | 202                                                  | 6361                                                         | UDSF                                                                                                           | /JUMP BACK AND SENSE FLAG AGAIN                                                                                                                              |

|       | 203                                                  | 5203                                                         | JMP1                                                                                                           | /READ UDC STATUS AND                                                                                                                                         |

|       | 204                                                  | 6355                                                         | UDRS                                                                                                           | /START UDC SCANNER                                                                                                                                           |

|       | 205                                                  | 6353                                                         | UDSC                                                                                                           | /SKIP ON FLAG NOT BUSY                                                                                                                                       |

|       | 206                                                  | 6351                                                         | UDSS                                                                                                           | /JUMP BACK AND SENSE FLAG AGAIN                                                                                                                              |

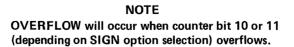

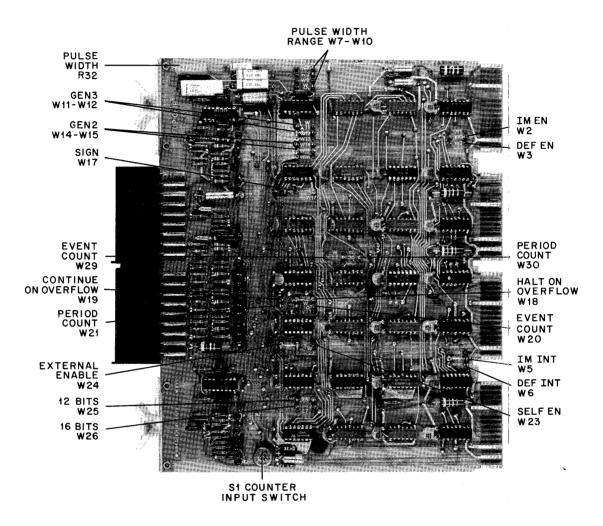

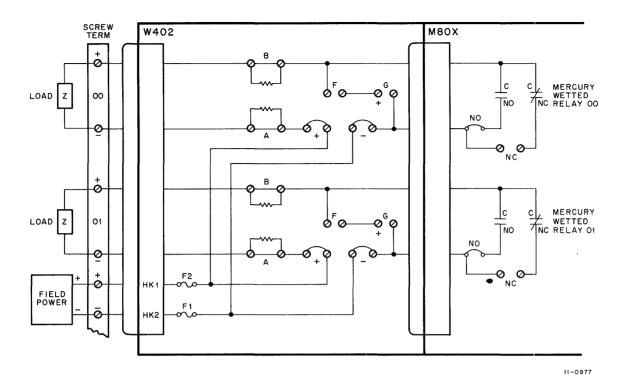

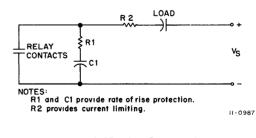

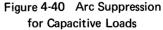

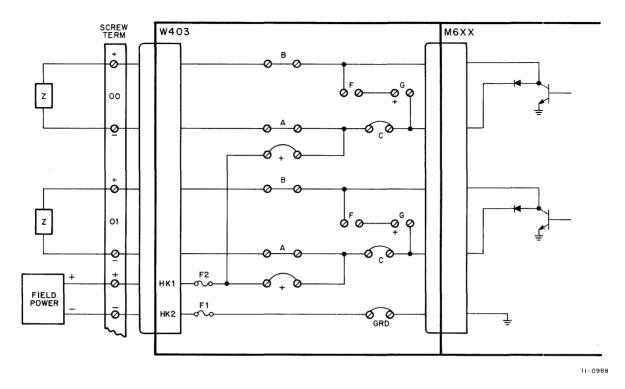

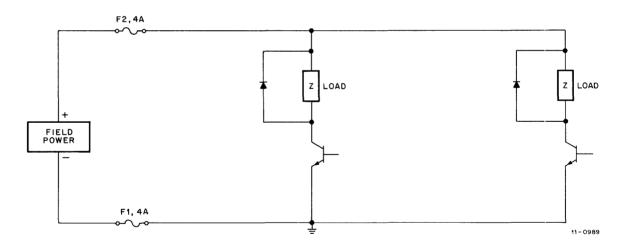

|       | 207                                                  | 5206                                                         | JMP1                                                                                                           | /READ THE ADDRESS AND GENERIC                                                                                                                                |