# TS03/TM8-E DECmagtape system maintenance manual

EK-T3TM8-MM-001

Copyright © 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECtape | PDP              |

|--------------|---------|------------------|

| DECCOMM      | DECUS   | RSTS             |

| DECsystem-10 | DIGITAL | <b>TYPESET-8</b> |

| DECSYSTEM-20 | MASSBUS | TYPESET-11       |

|              |         | UNIBUS           |

#### CONTENTS

#### PART I SYSTEM INFORMATION

| CHAPTER 1 | INTRODUCTION                                   |

|-----------|------------------------------------------------|

| 1.1       | INTRODUCTION                                   |

| 1.2       | SYSTEM CONFIGURATION 1-1                       |

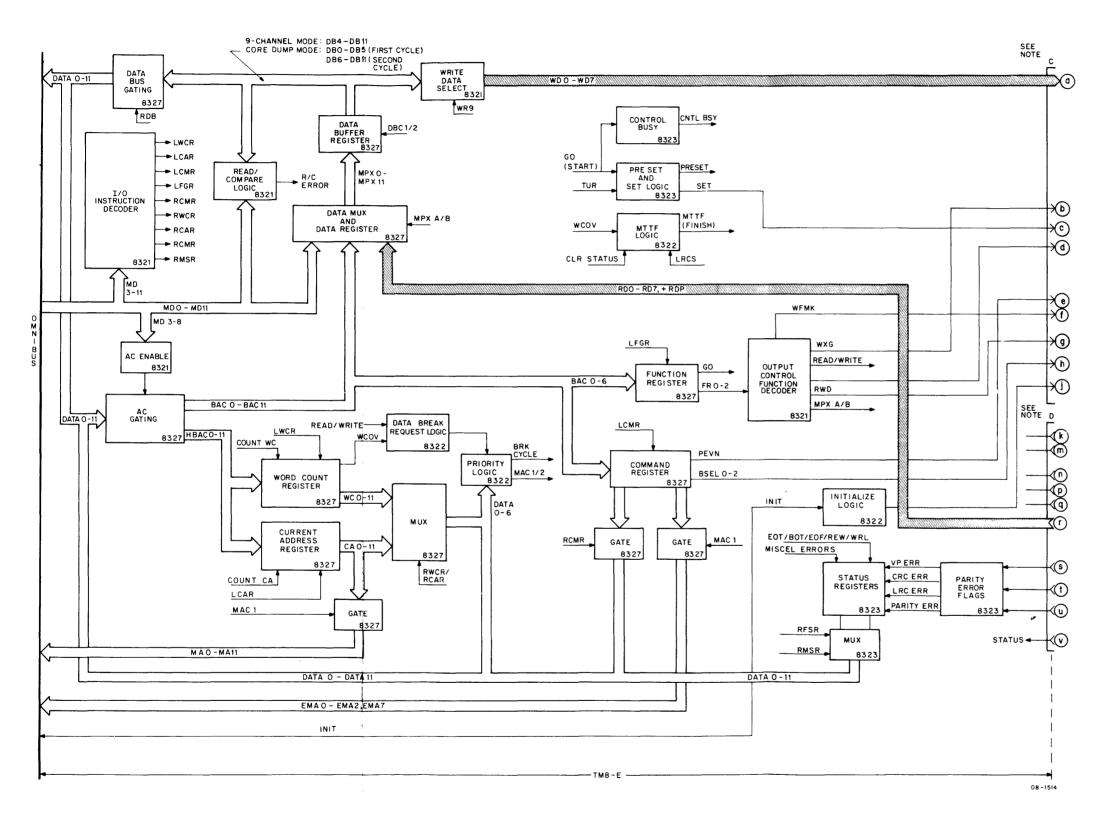

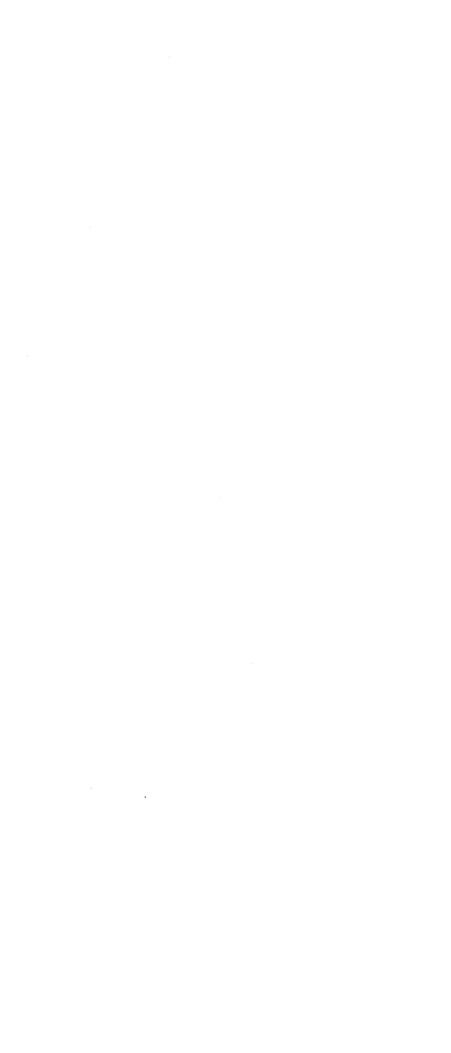

| 1.3       | TM8-M FUNCTIONAL BLOCK DIAGRAM DESCRIPTION 1-3 |

| 1.4       | APPLICABLE DOCUMENTS 1-6                       |

| 1.5       | MAGNETIC TAPE FUNDAMENTALS – DEFINITIONS       |

| 1.6       | RECORDING METHODS AND DECmagtape FORMATS 1-8   |

| 1.6.1     | NRZI Recording Method                          |

| 1.6.2     | Tape Format                                    |

| 1.6.3     | Cyclic Redundancy Check (CRC) Characters       |

| 1.6.4     | Longitudinal Redundancy Check (LRC) Character  |

| 1.6.5     | Data Files                                     |

| 1.6.6     | Track Assignments                              |

| 1.7       | SPECIFICATIONS                                 |

|           |                                                |

| CHAPTER 2 | INSTALLATION                                   |

| 2.1       | SITE PLANNING AND CONSIDERATIONS 2-1           |

| 2.1.1     | Space Requirements                             |

| 2.1.2     | Power Requirements                             |

| 2.1.3     | Environmental Requirements                     |

| 2.2       | UNPACKING                                      |

| 2.2.1     | Cabinet Unpacking Instructions 2-1             |

| 2.2.2     | Device Unpacking Instructions 2-2              |

| 2.3       | INSPECTION                                     |

| 2.4       | INSTALLATION                                   |

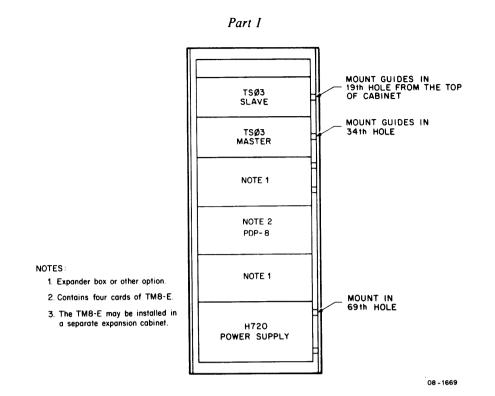

| 2.4.1     | Cabinet Installation                           |

| 2.4.2     | Device Installation                            |

| 2.4.2.1   | TS03 Mounting Instructions                     |

| 2.4.2.2   | TM8-E Controller Mounting Instructions         |

| 2.4.2.3   | H720 Power Supply Mounting Instructions        |

| 2.4.3     | I/O Signal Cable Connections 2-5               |

| 2.4.4     | Power Connections                              |

| 2.5       | ACCEPTANCE TESTING                             |

| CHAPTER 3 | SYSTEM OPERATING INSTRUCTIONS                  |

| 3.1       | SCOPE                                          |

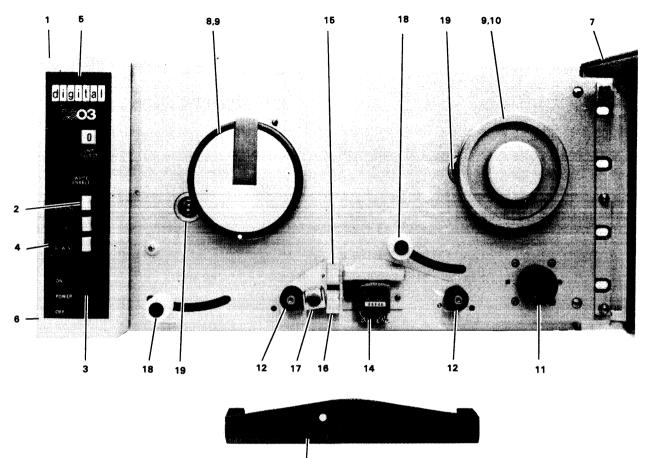

| 3.2       | CONTROLS AND INDICATORS                        |

| 3.3       | OPERATING PROCEDURES                           |

| 3.3.1     | Tape Threading    3-1                          |

| 3.3.2     | Tape Loading         3-1                       |

| 3.3.3     | Placing Tape Unit On-Line                      |

| 3.3.4     | Tape Unloading and Rewind    3-3               |

| 3.3.5     | Power Shutdown                                 |

|           |                                                |

#### CONTENTS (Cont)

| CHAPTER 4 | CUSTOMER EQUIPMENT CARE AND OPERATION   |

|-----------|-----------------------------------------|

| 4.1       | SCOPE                                   |

| 4.2       | REQUIREMENTS                            |

| 4.3       | CARE OF MAGNETIC TAPE                   |

| 4.4       | CARE OF TS03 TAPE TRANSPORT             |

| 4.4.1     | General                                 |

| 4.4.2     | Preventive Maintenance                  |

| 4.4.3     | Materials Required                      |

| 7.4.5     |                                         |

| CHAPTER 5 | SYSTEM MAINTENANCE                      |

| 5.1       | SCOPE                                   |

| 5.2       | MAINTENANCE PHILOSOPHY                  |

| 5.3       | <b>TEST EQUIPMENT</b>                   |

| 5.3.1     | Standard Test Equipment 5-1             |

| 5.3.2     | Special Test Equipment 5-2              |

| 5.4       | PREVENTIVE MAINTENANCE                  |

| 5.5       | ADJUSTMENTS                             |

| 5.5.1     | General                                 |

| 5.5.2     | Test Box                                |

| 5.5.2.1   | Functions of Test Box 5-3               |

| 5.5.2.2   | Test Box Operation                      |

| 5.5.3     | Adjustment Procedures                   |

| 5.5.3.1   | Voltage Check                           |

| 5.5.3.2   | Tape Path Alignment    5-9              |

| 5.5.3.3   | Capstan Creep Adjustment                |

| 5.5.3.4   | Mag Pot Adjustment                      |

| 5.5.3.5   | Write Lock Adjustment                   |

| 5.5.3.6   | Head Shield Adjustment                  |

| 5.5.3.7   | Tape Cleaner Adjustment                 |

| 5.5.3.8   | Capstan Perpendicularity Adjustment     |

| 5.5.3.9   | Photo Sensor Adjustment                 |

| 5.5.3.10  | Tape Speed Adjustment                   |

| 5.5.3.11  | Read Skew Adjustment                    |

| 5.5.3.12  | Read Level Adjustment                   |

| 5.5.3.13  | Write Skew Adjustment                   |

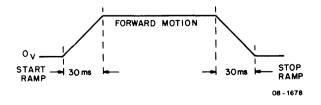

| 5.5.3.14  | Ramp Time Adjustments                   |

| 5.6       | CORRECTIVE MAINTENANCE                  |

| 5.6.1     | TM8-M Diagnostics                       |

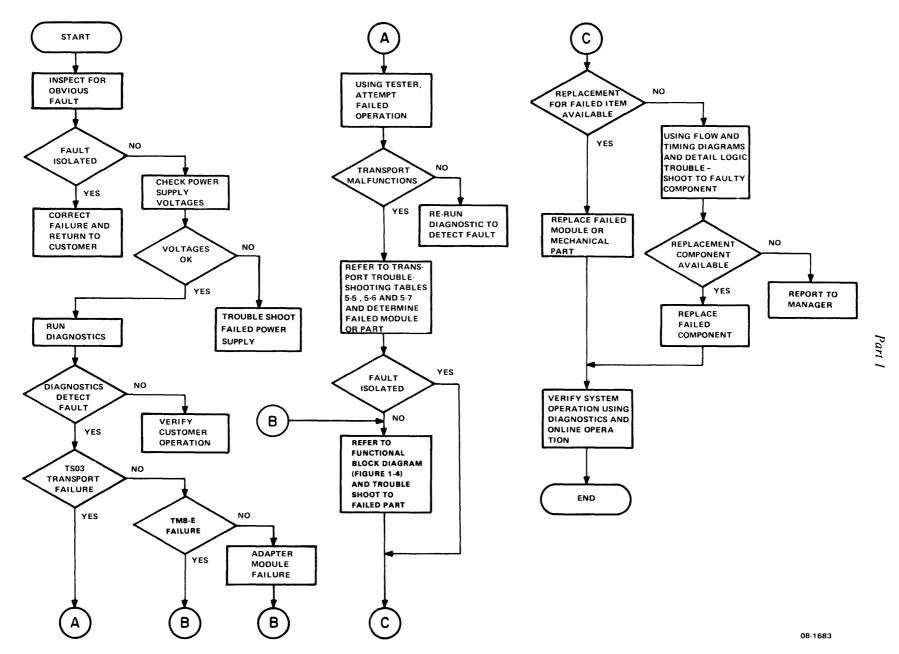

| 5.6.2     | Corrective Action Flow Diagram          |

| 5.6.3     | Functional Block Diagram                |

| 5.6.4     | TM8-E Controller Troubleshooting Hints  |

| 5.6.5     | TS03 Transport Troubleshooting Hints    |

| 5.6.6     | TS03 Transport Troubleshooting Tables   |

| 5.6.7     | Troubleshooting Procedure               |

| 5.7       | PARTS REPLACEMENT                       |

| 5.7.1     | Roller Guide Replacement                |

| 5.7.2     | Tape Tension Arm Replacement       5.34 |

| 5.7.3     | Reel Motor or Belt Replacement          |

# **CONTENTS** (Cont)

APPENDIX E TM8-E/TS03 UTILITY DRIVER

# ILLUSTRATIONS

# Figure No.

#### Title

#### Page

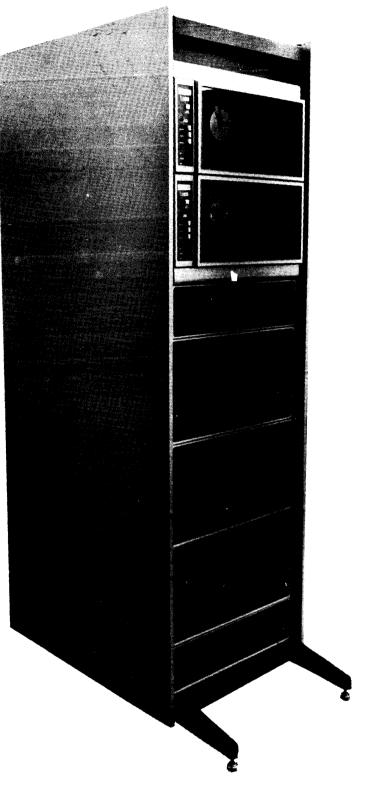

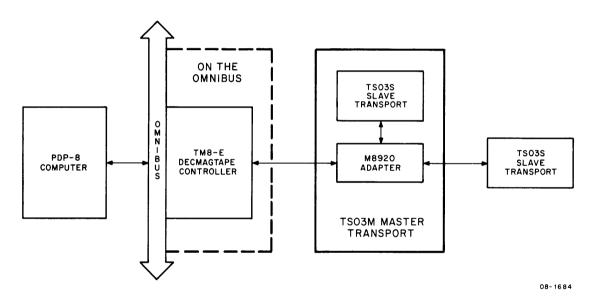

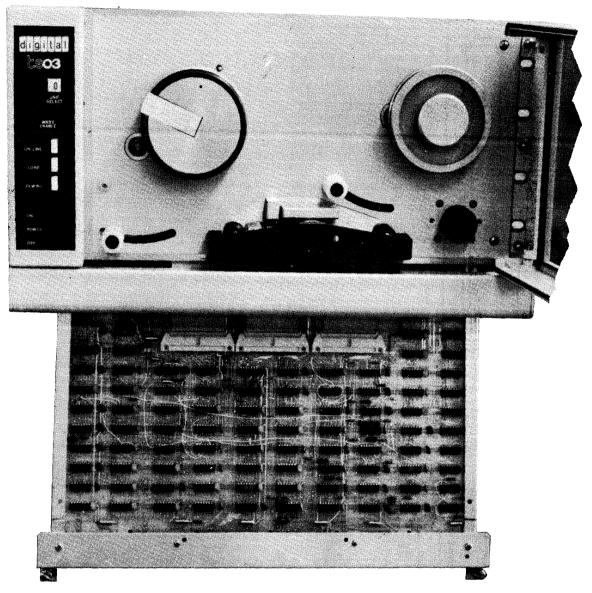

| 1-3       TM8-E Controller       1-3         1-4       TM8-M Functional Block Diagram       1-4         1-5       Reference Edge of Tape       1-7         1-6       Track-Bit Weight Relationship for Nine-Channel Transport       1-7         1-7       Data Recording Scheme       1-9         1-8       Tape Format       1-10         2-1       Space and Service Clearance, Top View       2-2         2-2       Cabinet Installation       2-4         2-3       TM8-E Module Orientation       2-5         2-4       Paddle Board Jumpers on Side 2 of Cable Assembly 7011571       2-6         2-5       TM8-E Controller Cabling       2-7         2-6       7011571 Cable Assembly       2-7         2-7       M8920 Cabling to TM8-E       2-8         2-8       Securing TM8-M Cables       2-9         2-9       I/O Cable Connection Diagram       2-9         2-10       Power Connection Diagram       3-1         3-2       Controls and Indicators       3-2         4-1       Opening Head Shield       4-3         5-1       TS03 Test Box       5-4         5-2       Test Box Installation       5-5         5-3       TS03 Adjustment Flowchar | 1-1  | TM8-M System Configuration 1-1                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------|

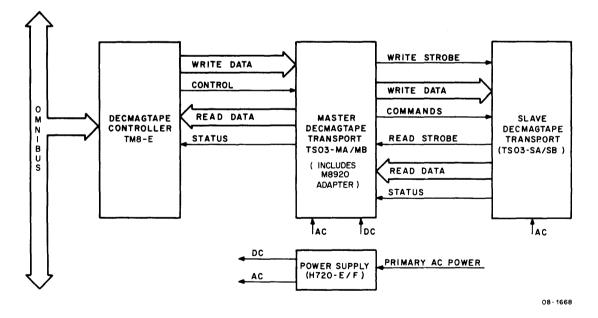

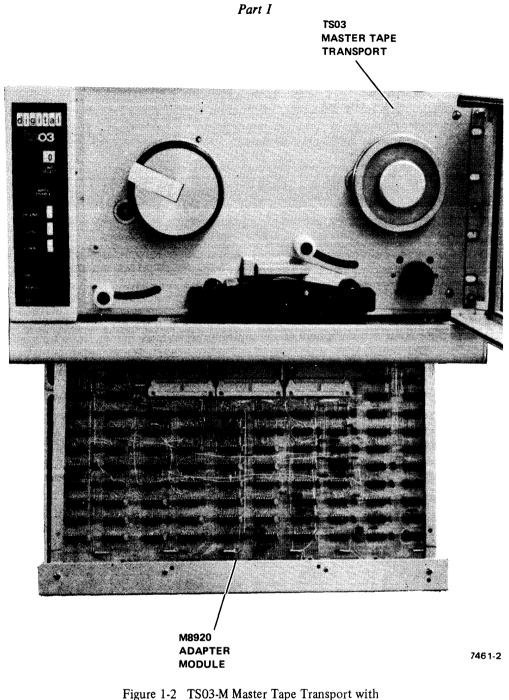

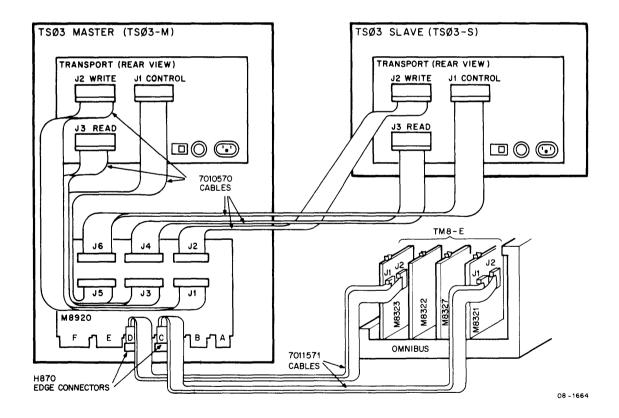

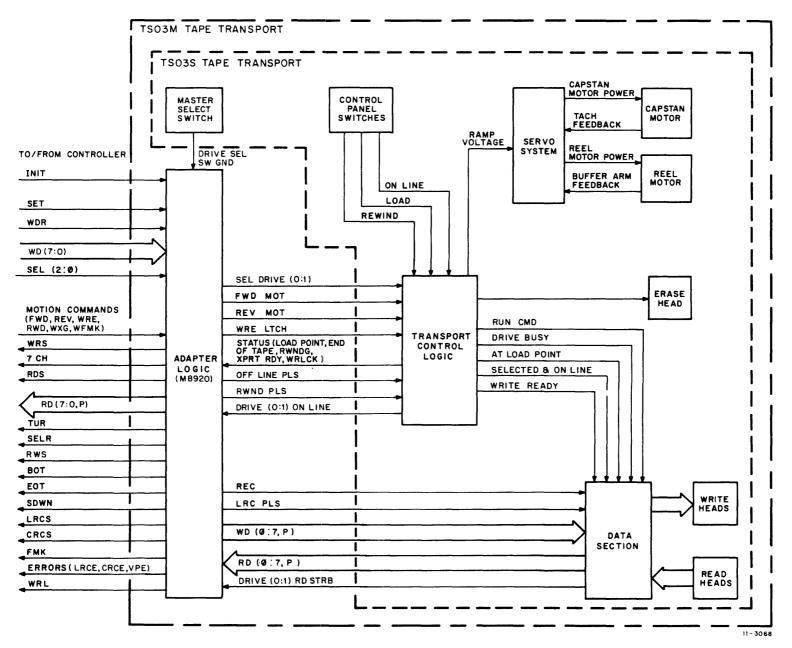

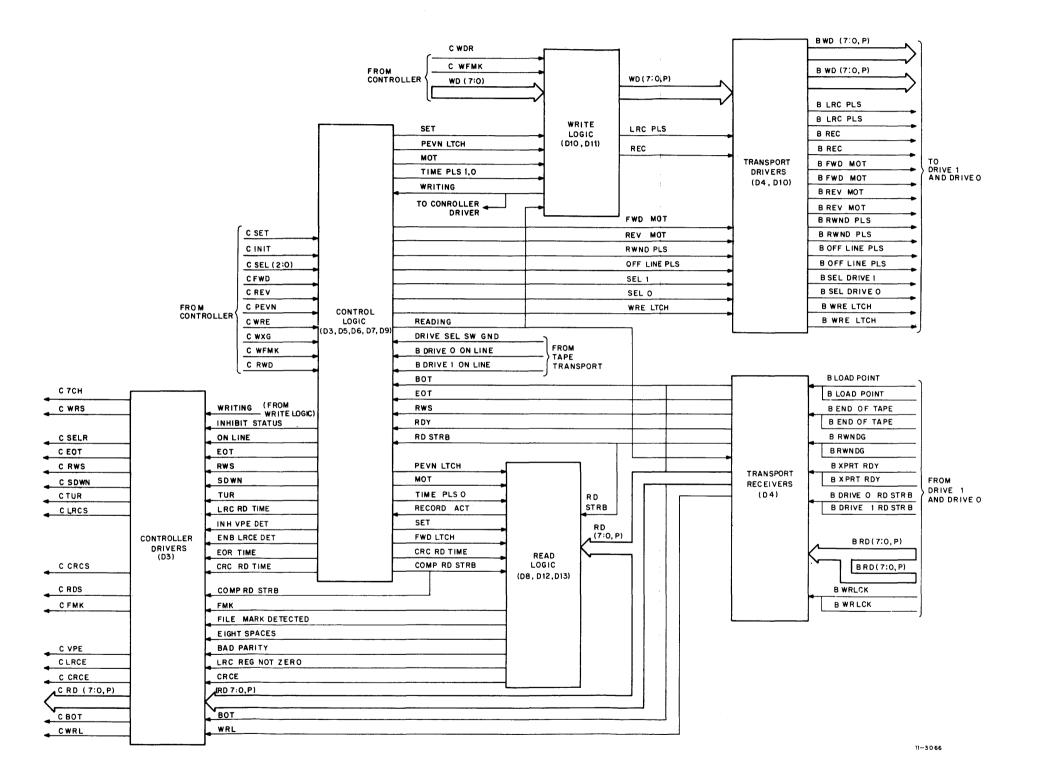

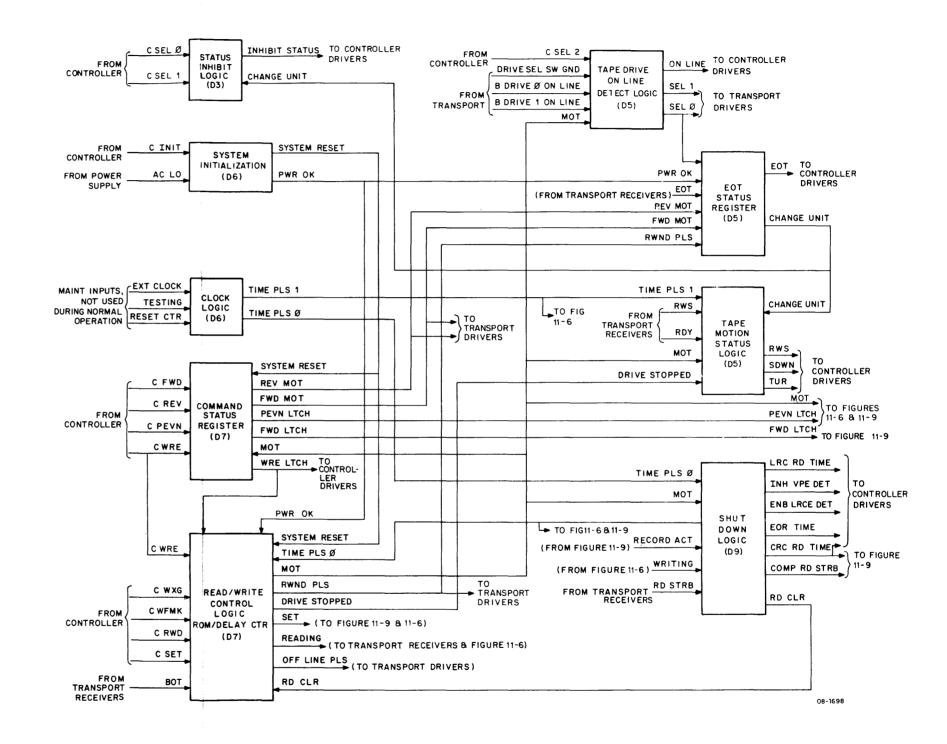

| 1-4       TM8-M Functional Block Diagram       1-4         1-5       Reference Edge of Tape       1-7         1-6       Track-Bit Weight Relationship for Nine-Channel Transport       1-7         1-7       Data Recording Scheme       1-9         1-8       Tape Format       1-10         2-1       Space and Service Clearance, Top View       2-2         2-2       Cabinet Installation       2-4         2-3       TM8-E Module Orientation       2-4         2-4       Paddle Board Jumpers on Side 2 of Cable Assembly 7011571       2-6         2-5       TM8-E Controller Cabling       2-7         2-6       7011571 Cable Assembly       2-7         2-7       M8920 Cabling to TM8-E       2-8         2-8       Securing TM8-M Cables       2-9         2-9       I/O Cable Connection Diagram       2-9         2-10       Power Connection Diagram       3-1         3-1       Tape Threading Diagram       3-1         3-2       Controls and Indicators       3-2         4-1       Opening Head Shield       4-3         5-1       TS03 Test Box       5-5         5-3       TS03 Adjustment Flowchart       5-5         5-4       Plug-In Module | 1-2  | TS03-M Master Tape Transport with M8920 Adapter Module 1-2   |

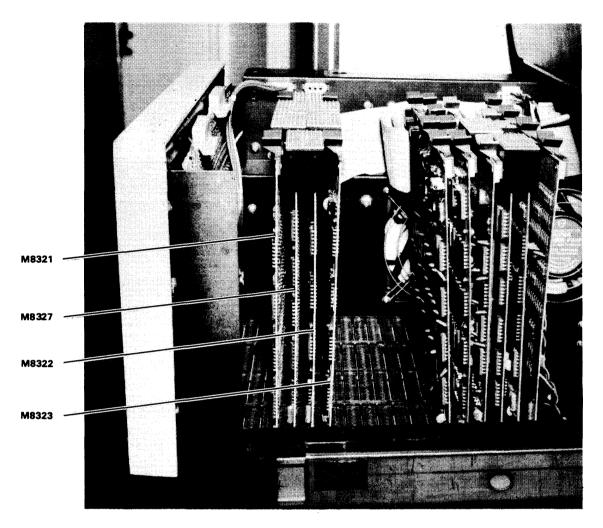

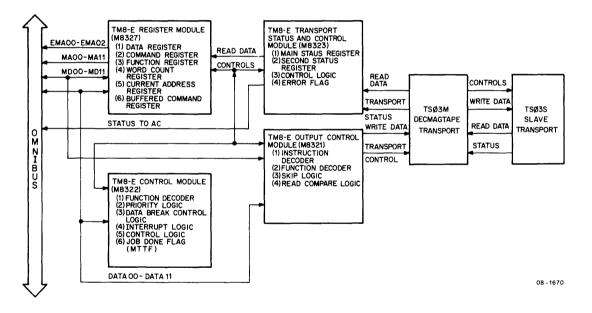

| 1-5       Reference Edge of Tape       1-7         1-6       Track-Bit Weight Relationship for Nine-Channel Transport       1-7         1-7       Data Recording Scheme       1-9         1-8       Tape Format       1-10         2-1       Space and Service Clearance, Top View       2-2         2-2       Cabinet Installation       2-4         2-3       TM8-E Module Orientation       2-5         2-4       Paddle Board Jumpers on Side 2 of Cable Assembly 7011571       2-6         2-5       TM8-E Controller Cabling       2-7         2-6       7011571 Cable Assembly       2-7         2-7       M8920 Cabling to TM8-E       2-8         2-8       Securing TM8-M Cables       2-9         2-9       I/O Cable Connection Diagram       2-9         2-10       Power Connection Diagram       2-10         3-1       Tape Threading Diagram       3-1         3-2       Controls and Indicators       3-2         4-1       Opening Head Shield       4-3         5-1       TS03 Test Box       5-4         5-2       Test Box Installation       5-5         5-3       TS03 Adjustment Flowchart       5-6         5-4       Plug-In Modules and Te | 1-3  | TM8-E Controller                                             |

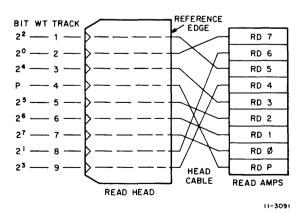

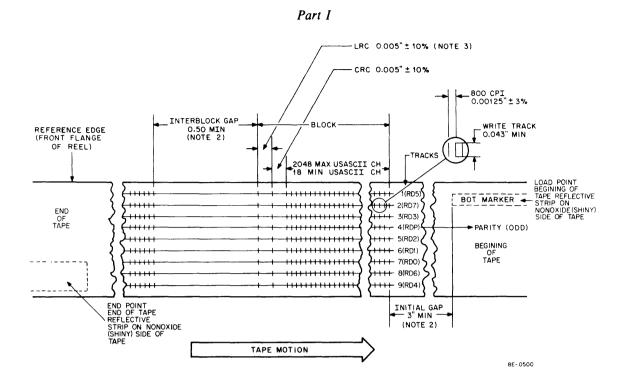

| 1-6Track-Bit Weight Relationship for Nine-Channel Transport1-71-7Data Recording Scheme1-91-8Tape Format1-102-1Space and Service Clearance, Top View2-22-2Cabinet Installation2-42-3TM8-E Module Orientation2-52-4Paddle Board Jumpers on Side 2 of Cable Assembly 70115712-62-5TM8-E Controller Cabling2-72-67011571 Cable Assembly2-72-7M8920 Cabling to TM8-E2-82-8Securing TM8-M Cables2-92-9I/O Cable Connection Diagram2-92-10Power Connection Diagram3-13-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-3TS03 Adjustment Flowchart5-65-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-4  | TM8-M Functional Block Diagram 1-4                           |

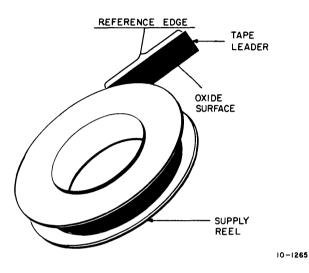

| 1-7Data Recording Scheme1-91-8Tape Format1-102-1Space and Service Clearance, Top View2-22-2Cabinet Installation2-42-3TM8-E Module Orientation2-42-3TM8-E Module Orientation2-52-4Paddle Board Jumpers on Side 2 of Cable Assembly 70115712-62-5TM8-E Controller Cabling2-72-67011571 Cable Assembly2-72-7M8920 Cabling to TM8-E2-82-8Securing TM8-M Cables2-92-9I/O Cable Connection Diagram2-92-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-3TS03 Adjustment Flowchart5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-5  | Reference Edge of Tape 1-7                                   |

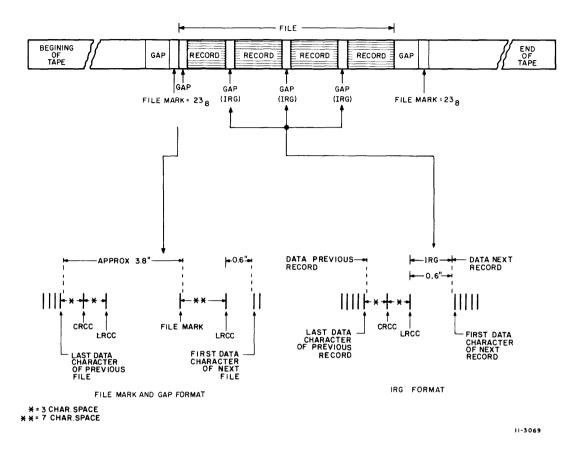

| 1-8       Tape Format       1-10         2-1       Space and Service Clearance, Top View       2-2         2-2       Cabinet Installation       2-4         2-3       TM8-E Module Orientation       2-4         2-4       Paddle Board Jumpers on Side 2 of Cable Assembly 7011571       2-6         2-5       TM8-E Controller Cabling       2-7         2-6       7011571 Cable Assembly       2-7         2-7       M8920 Cabling to TM8-E       2-8         2-8       Securing TM8-M Cables       2-9         2-9       I/O Cable Connection Diagram       2-9         2-10       Power Connection Diagram       2-10         3-1       Tape Threading Diagram       3-1         3-2       Controls and Indicators       3-2         4-1       Opening Head Shield       4-3         5-1       TS03 Test Box       5-4         5-2       Test Box Installation       5-5         5-3       TS03 Adjustment Flowchart       5-6         5-4       Plug-In Modules and Test Point Locations       5-8                                                                                                                                                               | 1-6  | Track-Bit Weight Relationship for Nine-Channel Transport     |

| 2-1       Space and Service Clearance, Top View       2-2         2-2       Cabinet Installation       2-4         2-3       TM8-E Module Orientation       2-5         2-4       Paddle Board Jumpers on Side 2 of Cable Assembly 7011571       2-6         2-5       TM8-E Controller Cabling       2-7         2-6       7011571 Cable Assembly       2-7         2-7       M8920 Cabling to TM8-E       2-8         2-8       Securing TM8-M Cables       2-9         2-9       I/O Cable Connection Diagram       2-9         2-10       Power Connection Diagram       2-10         3-1       Tape Threading Diagram       3-1         3-2       Controls and Indicators       3-2         2-1       Opening Head Shield       4-3         5-1       TS03 Test Box       5-4         5-2       Test Box Installation       5-5         5-3       TS03 Adjustment Flowchart       5-6         5-4       Plug-In Modules and Test Point Locations       5-8                                                                                                                                                                                                        | 1-7  | Data Recording Scheme                                        |

| 2-2Cabinet Installation2-42-3TM8-E Module Orientation2-52-4Paddle Board Jumpers on Side 2 of Cable Assembly 70115712-62-5TM8-E Controller Cabling2-72-67011571 Cable Assembly2-72-7M8920 Cabling to TM8-E2-82-8Securing TM8-M Cables2-92-9I/O Cable Connection Diagram2-92-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-3TS03 Adjustment Flowchart5-65-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-8  | Tape Format                                                  |

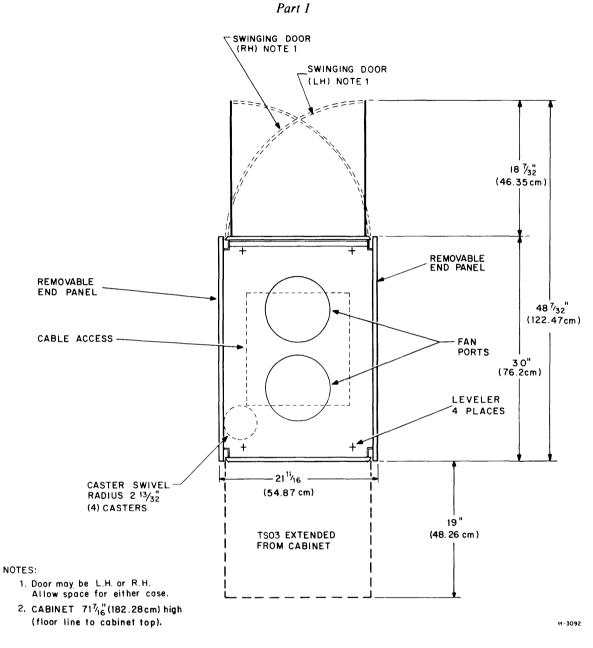

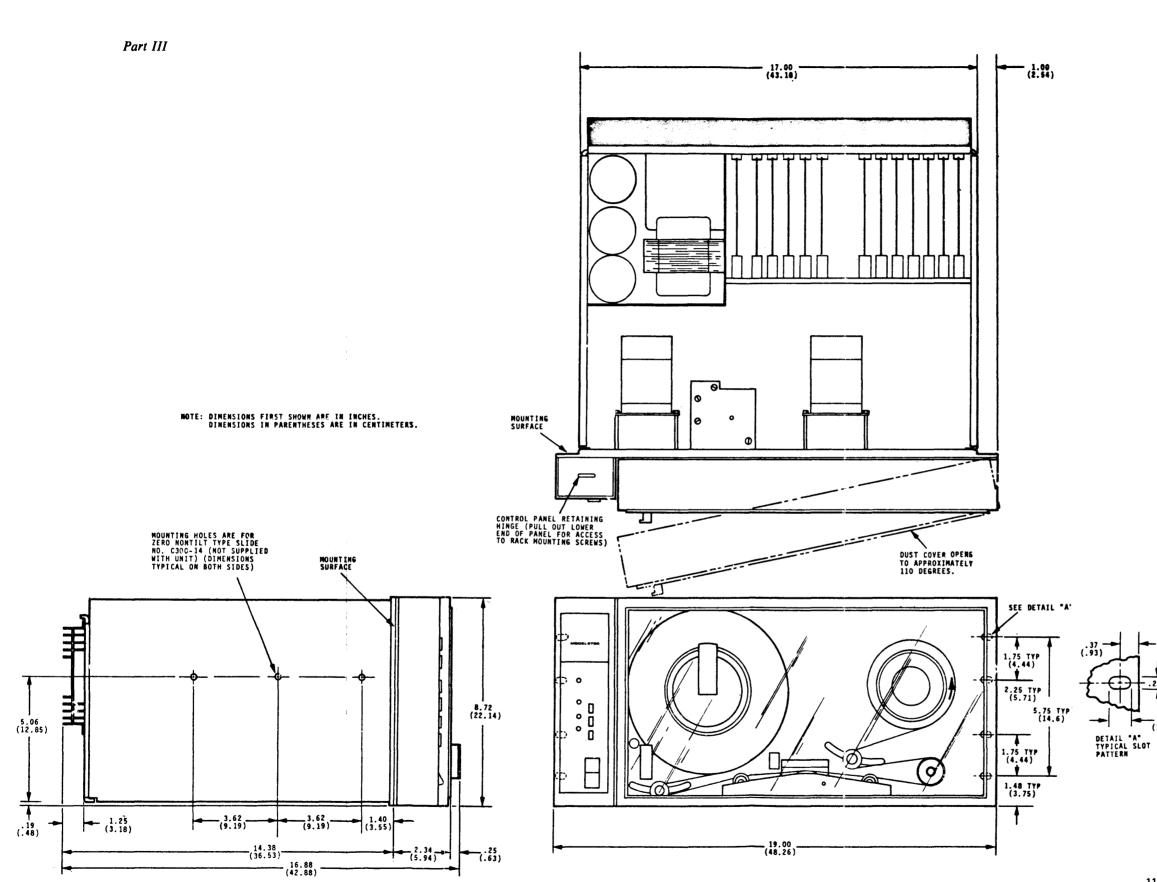

| 2-3TM8-E Module Orientation2-52-4Paddle Board Jumpers on Side 2 of Cable Assembly 70115712-62-5TM8-E Controller Cabling2-72-67011571 Cable Assembly2-72-7M8920 Cabling to TM8-E2-82-8Securing TM8-M Cables2-92-9I/O Cable Connection Diagram2-92-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-3TS03 Adjustment Flowchart5-65-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-1  | Space and Service Clearance, Top View 2-2                    |

| 2-4Paddle Board Jumpers on Side 2 of Cable Assembly 70115712-62-5TM8-E Controller Cabling2-72-67011571 Cable Assembly2-72-7M8920 Cabling to TM8-E2-82-8Securing TM8-M Cables2-92-9I/O Cable Connection Diagram2-92-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-3TS03 Adjustment Flowchart5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-2  | Cabinet Installation                                         |

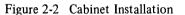

| 2-5TM8-E Controller Cabling2-72-67011571 Cable Assembly2-72-7M8920 Cabling to TM8-E2-82-8Securing TM8-M Cables2-92-9I/O Cable Connection Diagram2-92-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-3TS03 Adjustment Flowchart5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-3  | TM8-E Module Orientation         2-5                         |

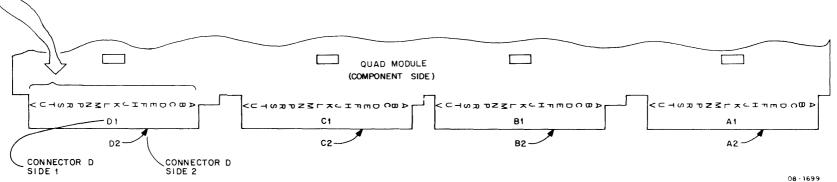

| 2-67011571 Cable Assembly2-72-7M8920 Cabling to TM8-E2-82-8Securing TM8-M Cables2-92-9I/O Cable Connection Diagram2-92-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-3TS03 Adjustment Flowchart5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-4  | Paddle Board Jumpers on Side 2 of Cable Assembly 7011571 2-6 |

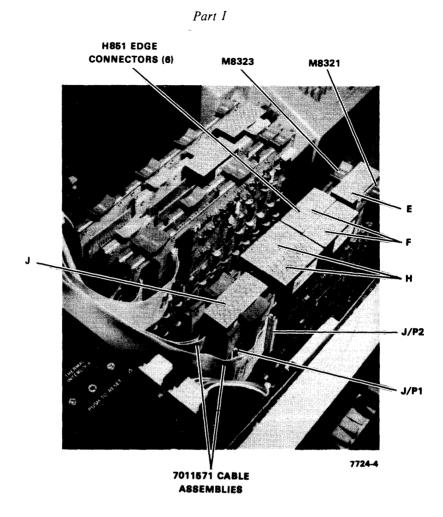

| 2-7M8920 Cabling to TM8-E2-82-8Securing TM8-M Cables2-92-9I/O Cable Connection Diagram2-92-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-2Test Box Installation5-55-3TS03 Adjustment Flowchart5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-5  | TM8-E Controller Cabling         2-7                         |

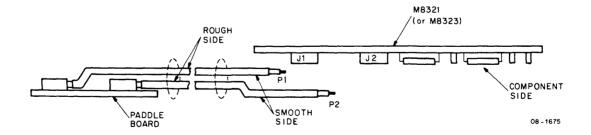

| 2-8Securing TM8-M Cables2-92-9I/O Cable Connection Diagram2-92-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-2Test Box Installation5-55-3TS03 Adjustment Flowchart5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-6  | 7011571 Cable Assembly 2-7                                   |

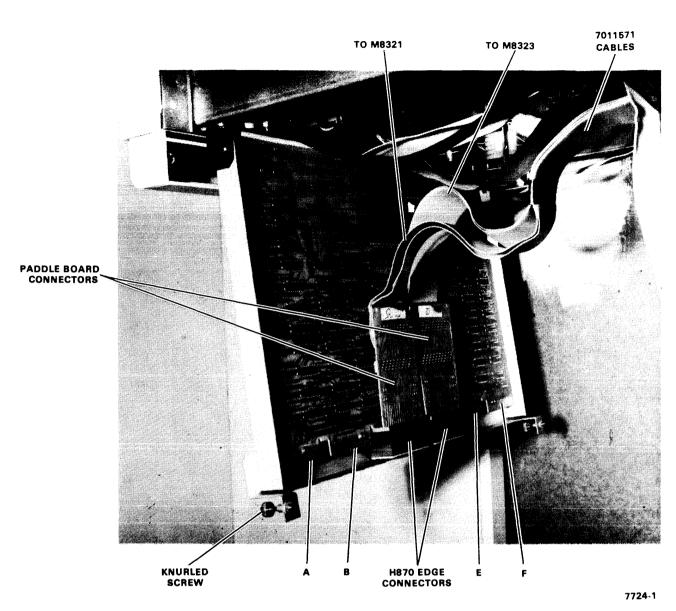

| 2-9I/O Cable Connection Diagram2-92-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-2Test Box Installation5-55-3TS03 Adjustment Flowchart5-65-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-7  | M8920 Cabling to TM8-E 2-8                                   |

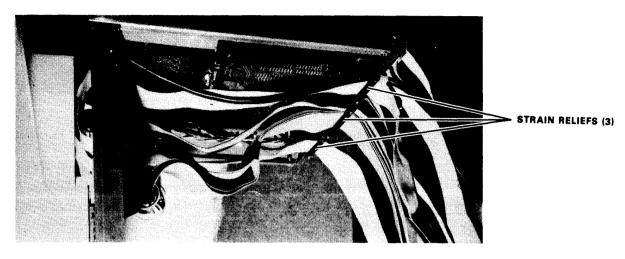

| 2-10Power Connection Diagram2-103-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-2Test Box Installation5-55-3TS03 Adjustment Flowchart5-85-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-8  | Securing TM8-M Cables                                        |

| 3-1Tape Threading Diagram3-13-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-2Test Box Installation5-55-3TS03 Adjustment Flowchart5-65-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-9  | I/O Cable Connection Diagram 2-9                             |

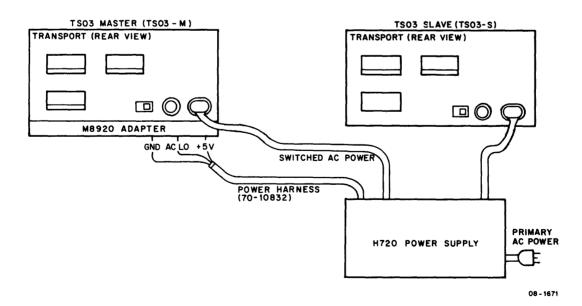

| 3-2Controls and Indicators3-24-1Opening Head Shield4-35-1TS03 Test Box5-45-2Test Box Installation5-55-3TS03 Adjustment Flowchart5-65-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-10 | Power Connection Diagram                                     |

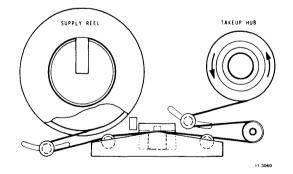

| 4-1Opening Head Shield4-35-1TS03 Test Box5-45-2Test Box Installation5-55-3TS03 Adjustment Flowchart5-65-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-1  | Tape Threading Diagram    3-1                                |

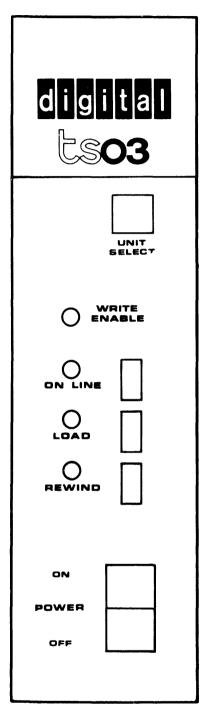

| 5-1       TS03 Test Box       5-4         5-2       Test Box Installation       5-5         5-3       TS03 Adjustment Flowchart       5-6         5-4       Plug-In Modules and Test Point Locations       5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-2  | Controls and Indicators                                      |

| 5-2Test Box Installation5-55-3TS03 Adjustment Flowchart5-65-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-1  | Opening Head Shield                                          |

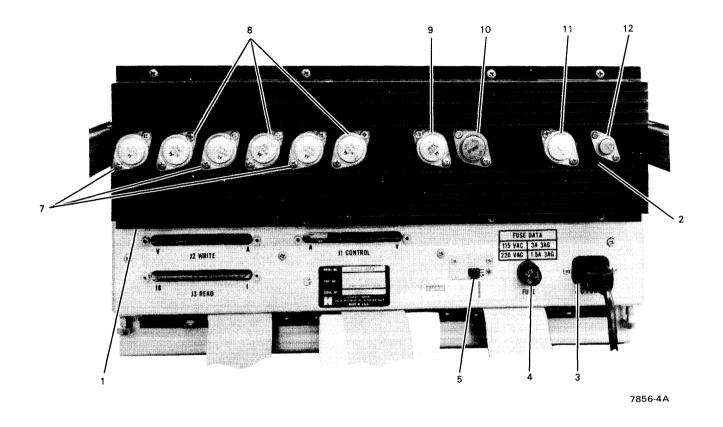

| 5-3TS03 Adjustment Flowchart5-65-4Plug-In Modules and Test Point Locations5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1  | TS03 Test Box                                                |

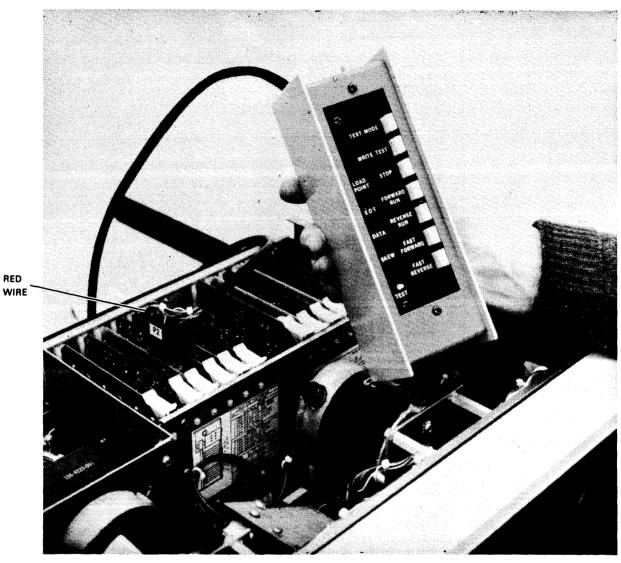

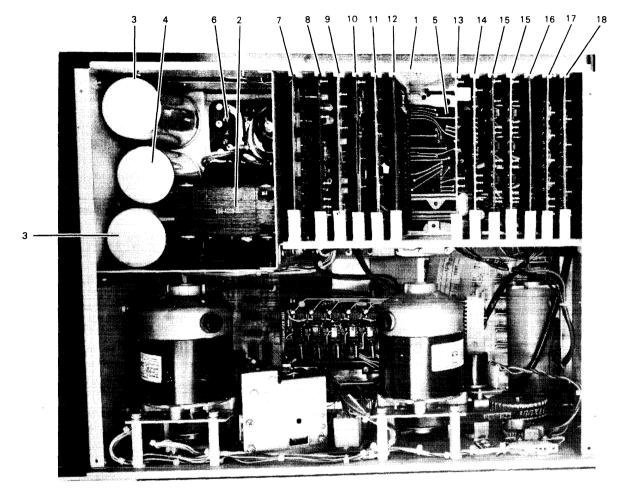

| 5-4 Plug-In Modules and Test Point Locations 5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-2  | Test Box Installation                                        |

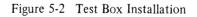

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-3  | TS03 Adjustment Flowchart 5-6                                |

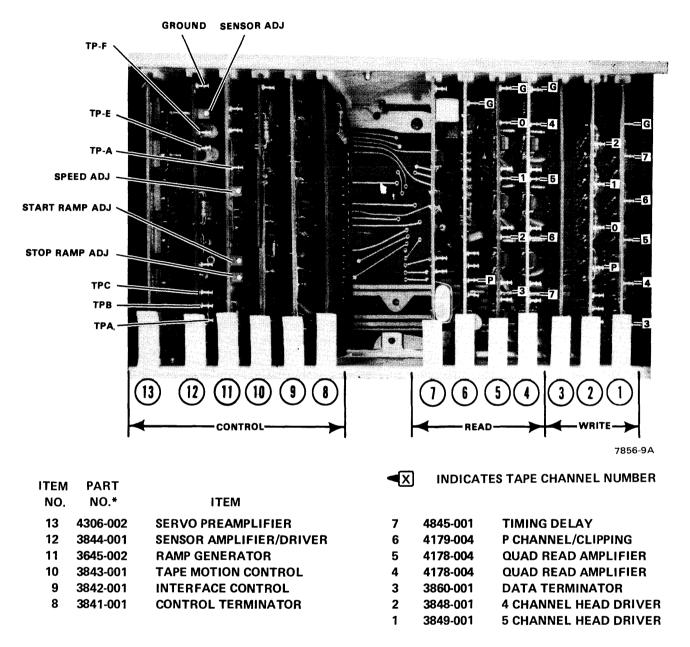

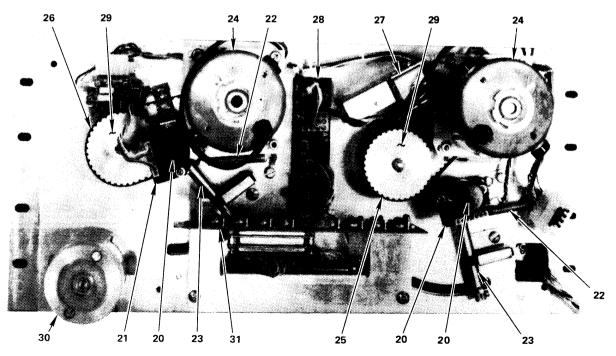

| 5-5 TS03 Tape Transport, Rear View 5-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-4  | Plug-In Modules and Test Point Locations 5-8                 |

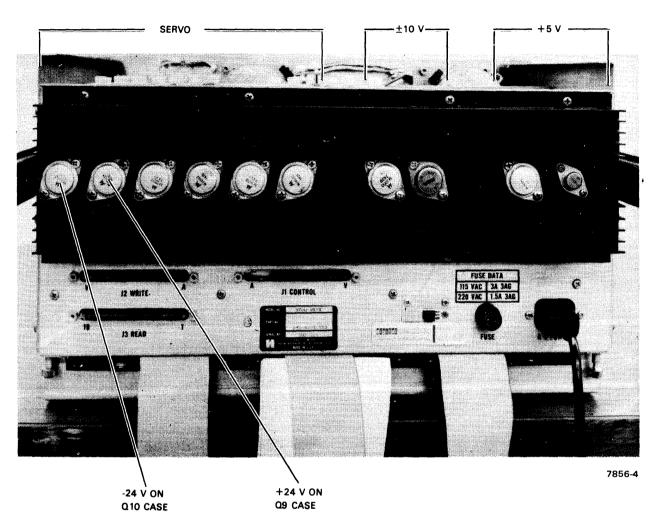

| • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-5  | TS03 Tape Transport, Rear View 5-9                           |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                                                    | Page |

|------------|------------------------------------------------------------------------------------------|------|

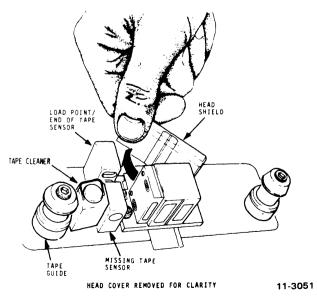

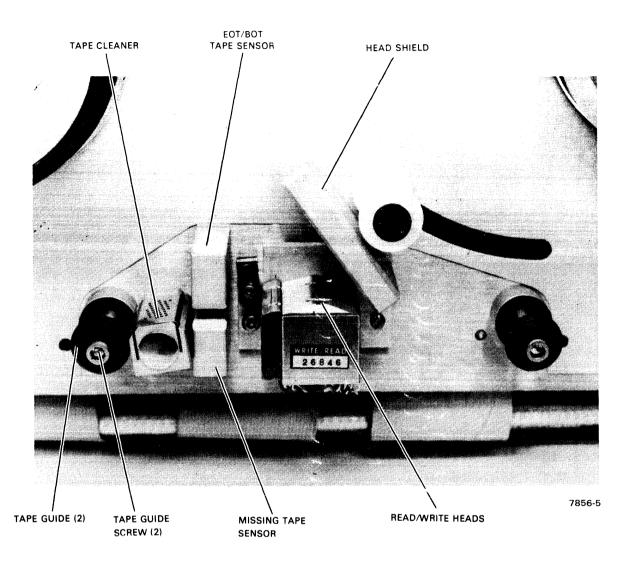

| 5-6        | Head Assembly with Tape Guides                                                           | 5-10 |

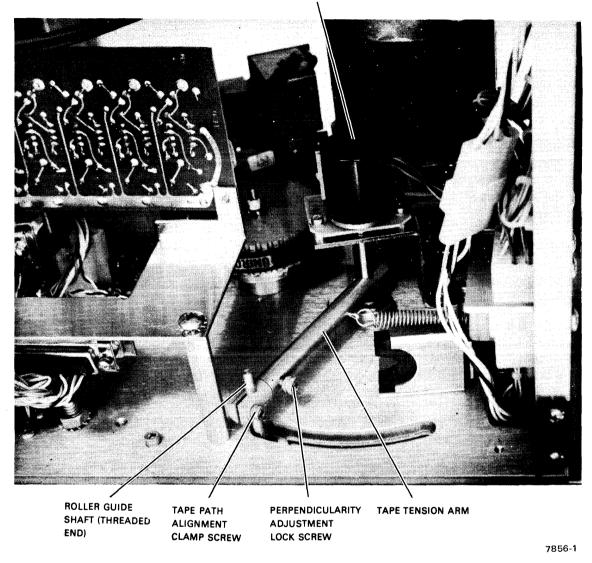

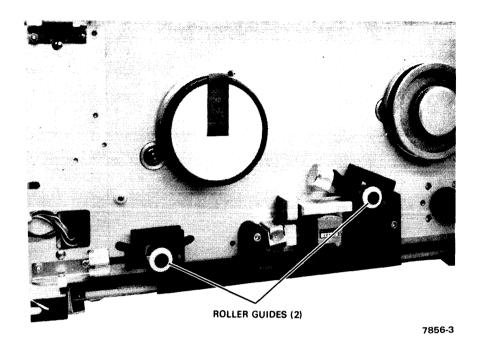

| 5-7        | Roller Guide/Tape Tension Arm Connection, Bottom View                                    | 5-11 |

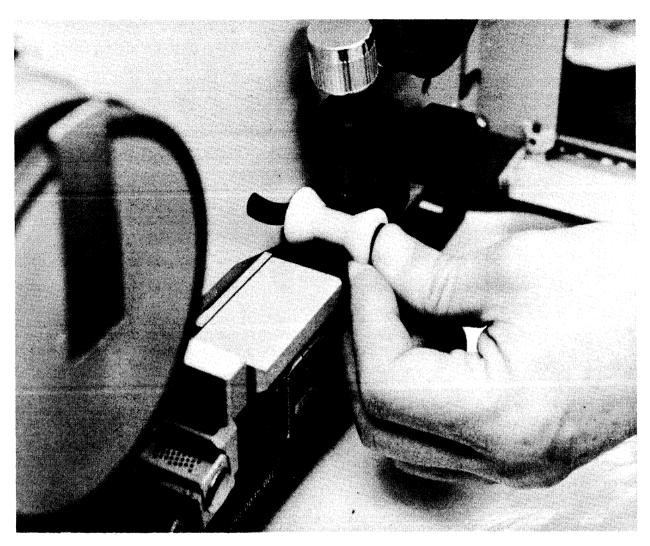

| 5-8        | Use of Alignment Tool                                                                    | 5-12 |

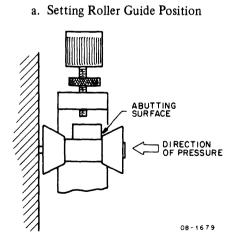

| 5-9        | Tape Path Alignment                                                                      | 5-13 |

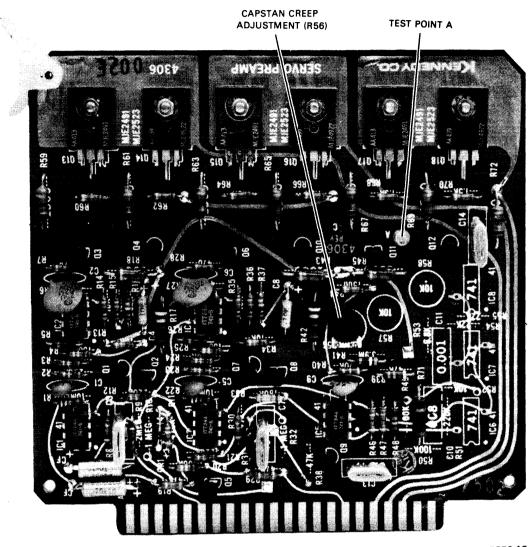

| 5-10       | Servo Pre-Amp, Card No. 13                                                               | 5-15 |

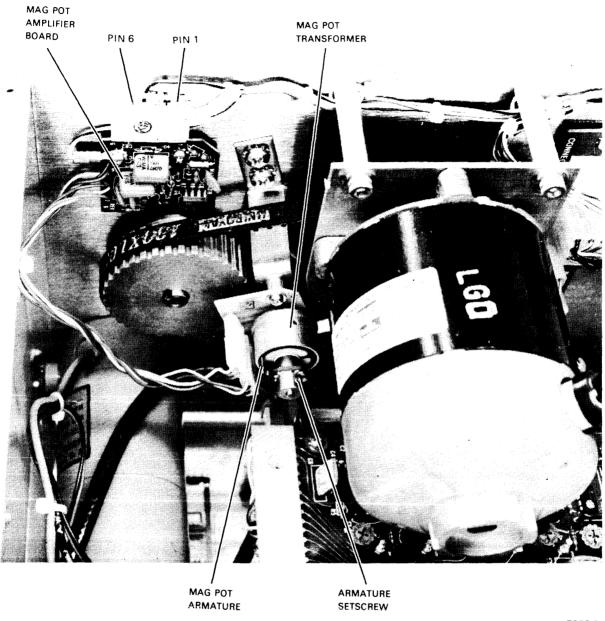

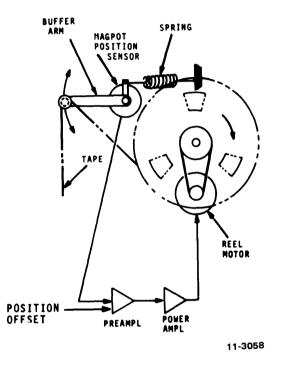

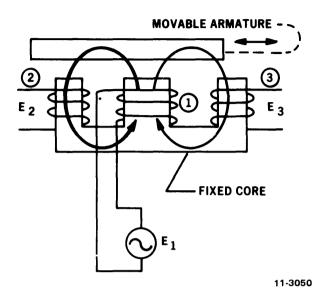

| 5-11       | Mag Pot Position Sensor Assembly, Plastic Cover Removed                                  | 5-16 |

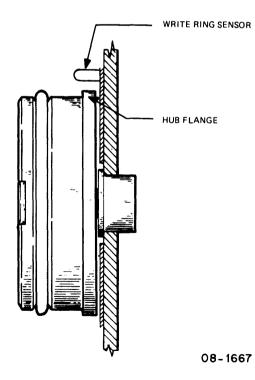

| 5-12       | Supply Reel, Side View                                                                   | 5-17 |

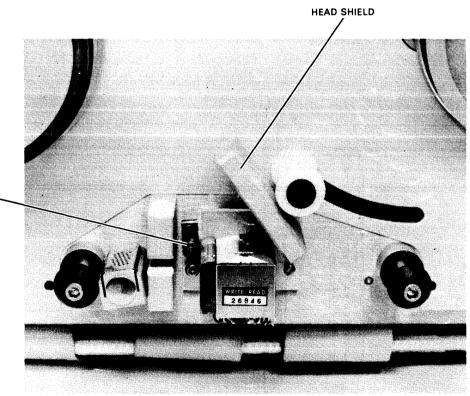

| 5-13       | Head Shield Adjustment                                                                   | 5-18 |

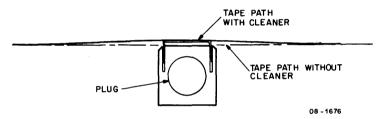

| 5-14       | Tape Cleaner Adjustment                                                                  | 5-19 |

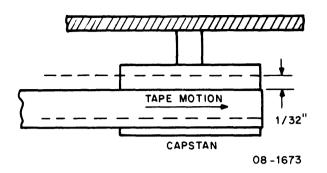

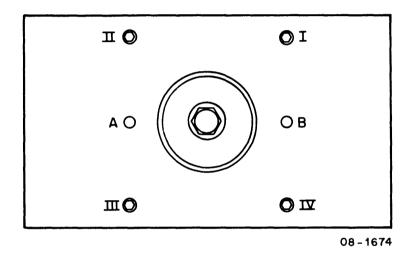

| 5-15       | Capstan Perpendicularity Check                                                           | 5-20 |

| 5-16       | Capstan Motor Mounting Screws                                                            | 5-20 |

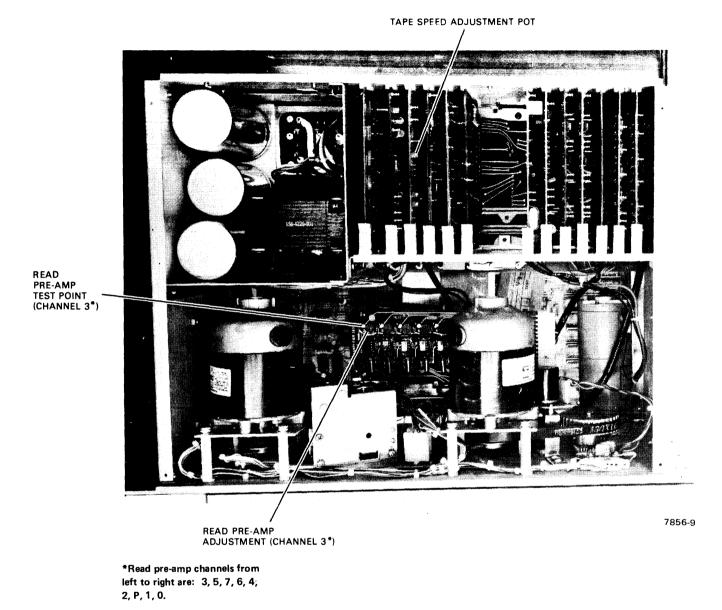

| 5-17       | Tape Speed and Read Pre-Amp Adjustment                                                   | 5-22 |

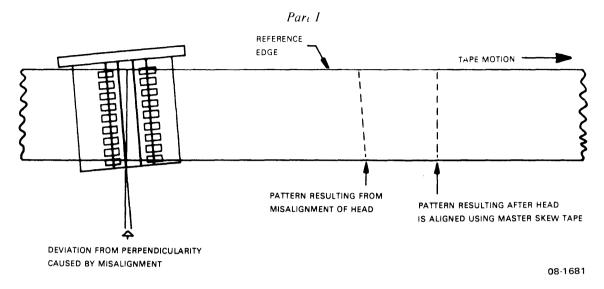

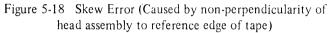

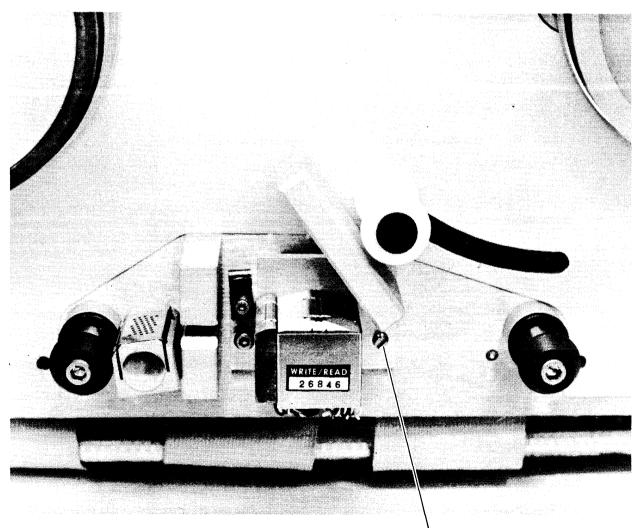

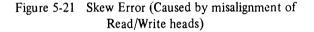

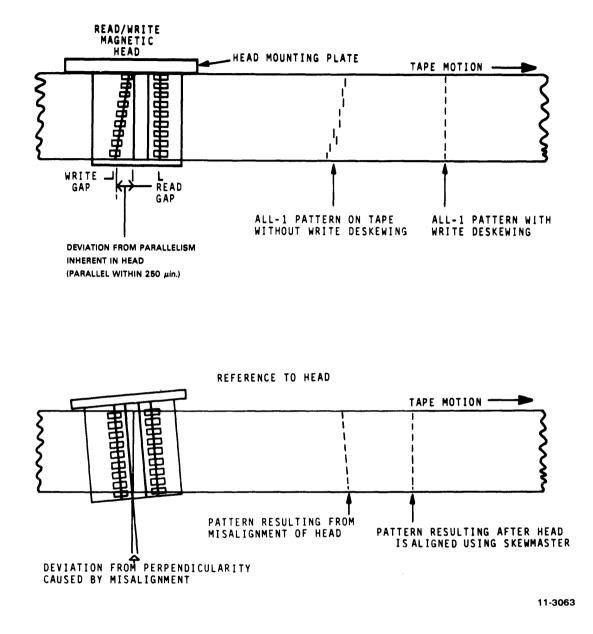

| 5-18       | Skew Error (Caused by non-perpendicularity of head assembly to reference edge of tape) . | 5-23 |

| 5-19       | Location of Skew Adjustment                                                              | 5-23 |

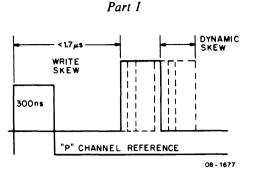

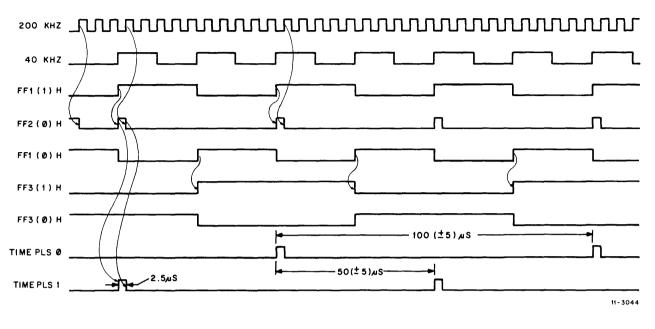

| 5-20       | Read Skew Adjustment Waveform                                                            | 5-24 |

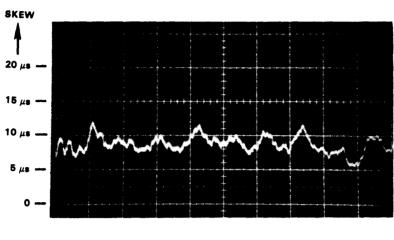

| 5-21       | Skew Error (Caused by misalignment of Read/Write heads)                                  | 5-25 |

| 5-22       | Write Skew Adjustment                                                                    | 5-26 |

| 5-23       | Ramp Time Adjustments                                                                    | 5-26 |

| 5-24       | TM8-M Corrective Action Flow Diagram                                                     |      |

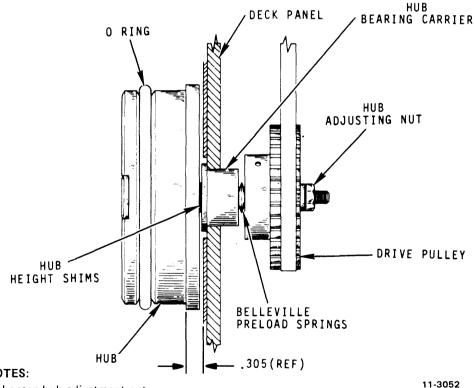

| 5-25       | Reel Hub Adjustment                                                                      |      |

### TABLES

# Table No.

# Title

# Page

| 1-1 | Applicable Documents                            |

|-----|-------------------------------------------------|

| 1-2 | Five-Character Record                           |

| 1-3 | CRCC In Register When Writing                   |

| 1-4 | TS03 Track Assignments for Data and Parity      |

| 2-1 | 7010570 Cable Connections                       |

| 2-2 | Power Harness Color Coding                      |

| 4-1 | Customer Equipment Care Operations              |

| 5-1 | Standard Test Equipment Required 5-2            |

| 5-2 | Diagnostic Descriptions                         |

| 5-3 | Special Test Equipment and Tools 5-3            |

| 5-4 | TM8-M Diagnostics                               |

| 5-5 | TS03 DECmagtape Transport Troubleshooting Hints |

| 5-6 | High Error Rate Troubleshooting                 |

| 5-7 | Control Malfunctions Troubleshooting            |

# CONTENTS

# PART II TM8-E CONTROLLER

| 6.2       PHYSICAL DESCRIPTION       6-2         CHAPTER 7       BLOCK DIAGRAM DESCRIPTION       7-1         7.1       INTRODUCTION       7-1         7.2       M8321 OUTPUT CONTROL MODULE       7-1         7.2.1       IOT Instruction Decoder       7-2         7.2.2       Function Decoder       7-2         7.2.3       Cating Logic       7-2         7.2.4       Read/Compare Erro Detection Logic       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3.1       Multiplexer and Data Register       7-2         7.3.2       Command Register       7-2         7.3.3       Function Register       7-2         7.3.4       Current Address Register       7-3         7.3.4       Current Address Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.3       Eror Flag       7-6         7.4.4       Ilegal Function Decoder       7-7         7.5       M8322 CONTROL AND DATA BREAK       7-7         7.5.1       Data Break Control Logic       7-7                                                                             | CHAPTER 6 | INTRODUCTION              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------|

| 6.2       PHYSICAL DESCRIPTION       6-2         CHAPTER 7       BLOCK DIAGRAM DESCRIPTION       7.1         7.1       INTRODUCTION       7.1         7.2       M321 OUTPUT CONTROL MODULE       7.1         7.2.1       IOT Instruction Decoder       7.1         7.2.2       Function Decoder       7.2         7.2.3       Cating Logic       7.2         7.2.4       Read/Compare Erro Detection Logic       7.2         7.2.5       Skip Logic       7.2         7.3       M327 REGISTERS MODULE       7.2         7.3.1       Multipker and Data Register       7.2         7.3.2       Command Register       7.3         7.3.3       Function Register       7.3         7.3.4       Current Address Register       7.5         7.3.4       Current Register       7.5         7.4       M8232 TRANSPORT STATUS AND CONTROL MODULE       7.5         7.4.1       Main Status Register       7.5         7.4.2       Second Status Register       7.5         7.4.3       Error Flag       7.6         7.4.4       Illegal Function Detection       7.6         7.4.5       PRESET and SET Pulas Generator       7.7 <td< td=""><td>6.1</td><td>GENERAL DESCRIPTION</td></td<>                                     | 6.1       | GENERAL DESCRIPTION       |

| 7.1       INTRODUCTION       7-1         7.2       M8321 OUTPUT CONTROL MODULE       7-1         7.2.1       IOT Instruction Decoder       7-1         7.2.2       Function Decoder       7-2         7.2.3       Cating Logic       7-2         7.2.4       Read/Compare Error Detection Logic       7-2         7.2.5       Skip Logic       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3.1       Multiplexer and Data Register       7-2         7.3.2       Command Register       7-3         7.3.2.1       Buffered Command Register (BCM)       7-3         7.3.3       Function Register       7-5         7.3.4       Current Address Register       7-5         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7                                                                    | 6.2       |                           |

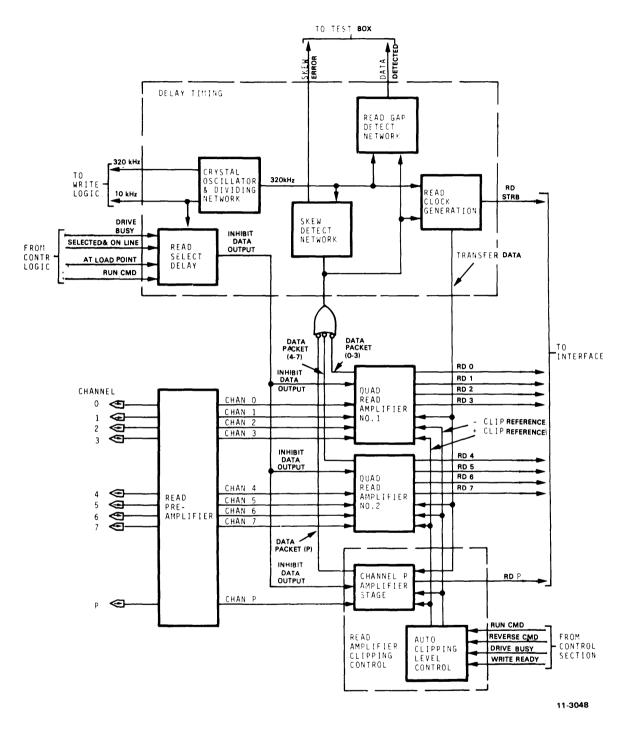

| 7.2       M8321 OUTPUT CONTROL MODULE       7-1         7.2.1       IOT Instruction Decoder       7-1         7.2.2       Function Decoder       7-2         7.2.3       Cating Logic       7-2         7.2.4       Read/Compare Error Detection Logic       7-2         7.2.5       Skip Logic       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3.1       Multiplexer and Data Register       7-3         7.3.2       Command Register       7-3         7.3.1       Buffered Command Register (BCM)       7-3         7.3.2       Command Register       7-3         7.3.3       Function Register       7-5         7.3.4       Current Address Register       7-5         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5       M322 CONTROL AND CONTROL MODULE <th>CHAPTER 7</th> <th>BLOCK DIAGRAM DESCRIPTION</th> | CHAPTER 7 | BLOCK DIAGRAM DESCRIPTION |

| 7.2       M8321 OUTPUT CONTROL MODULE       7-1         7.2.1       IOT Instruction Decoder       7-1         7.2.2       Function Decoder       7-2         7.2.3       Cating Logic       7-2         7.2.4       Read/Compare Error Detection Logic       7-2         7.2.5       Skip Logic       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3.1       Multiplexer and Data Register       7-3         7.3.2       Command Register       7-3         7.3.1       Buffered Command Register (BCM)       7-3         7.3.2       Command Register       7-3         7.3.3       Function Register       7-5         7.3.4       Current Address Register       7-5         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5       M322 CONTROL AND CONTROL MODULE <td>7.1</td> <td>INTRODUCTION</td>                    | 7.1       | INTRODUCTION              |

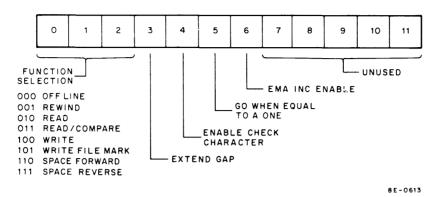

| 7.2.1       IOT Instruction Decoder       7-1         7.2.2       Function Decoder       7-2         7.2.3       Cating Logic       7-2         7.2.4       Read/Compare Error Detection Logic       7-2         7.2.5       Skip Logic       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3.1       Multiplexer and Data Register       7-2         7.3.2       Command Register       7-3         7.3.3       Function Register       7-3         7.3.4       Current Address Register       7-3         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.4       Main Status Register       7-6         7.4.5       Second Status Register       7-6         7.4.4       Illegal Function Detection       7-7         7.5       M322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       SINGLE CYCLE DATA BREAK MODULE       7-7         7.5.3       INTRODUCTION       8-1         8.1       INTRODUCTION       8-1                                                                                     | 7.2       |                           |

| 7.2.2       Function Decoder       7-2         7.2.3       Cating Logic       7-2         7.2.4       Read/Compare Error Detection Logic       7-2         7.2.5       Skip Logic       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3.1       Multiplexer and Data Register       7-2         7.3.2       Command Register       7-3         7.3.2.1       Buffered Command Register (BCM)       7-3         7.3.3       Function Register       7-3         7.3.4       Current Address Register       7-5         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.4       Main Status Register       7-5         7.4.2       Second Status Register       7-6         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.5.6       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7                                                                     | 7.2.1     |                           |

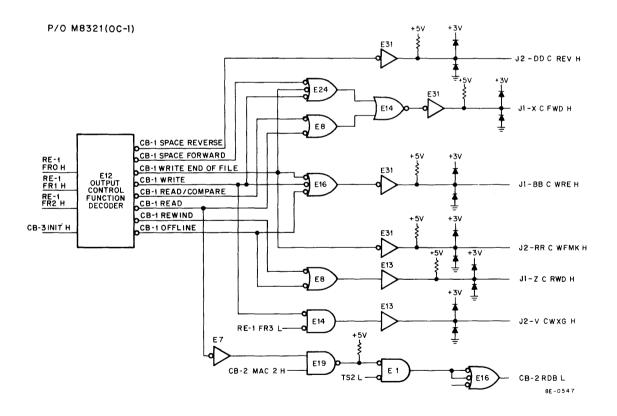

| 7.2.3       Cating Logic       7-2         7.2.4       Read/Compare Error Detection Logic       7-2         7.2.5       Skip Logic       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3       Multiplexer and Data Register       7-2         7.3.1       Multiplexer and Data Register       7-3         7.3.2.1       Buffered Command Register (BCM)       7-3         7.3.3       Function Register       7-3         7.3.4       Current Address Register       7-5         7.3.5       Word Court Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-6         7.4.3       Error Flag       7-6         7.4.4       Ilegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.4.6       Control Busy (CNTL BSY)       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder                                                           | 7.2.2     |                           |

| 7.2.4       Read/Compare Error Detection Logic       7-2         7.2.5       Skip Logic       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3.1       Multiplexer and Data Register       7-2         7.3.2       Command Register       7-3         7.3.3       Function Register       7-3         7.3.4       Current Address Register       7-3         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-7         7.4.5       PRESET and SET Pulse Generator       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         7.5.4       Signal Conve                                                    | 7.2.3     |                           |

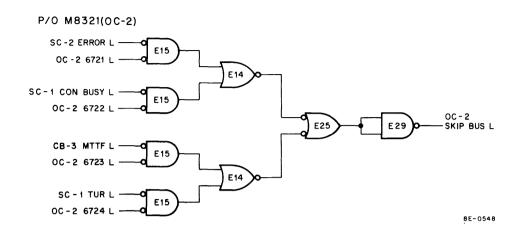

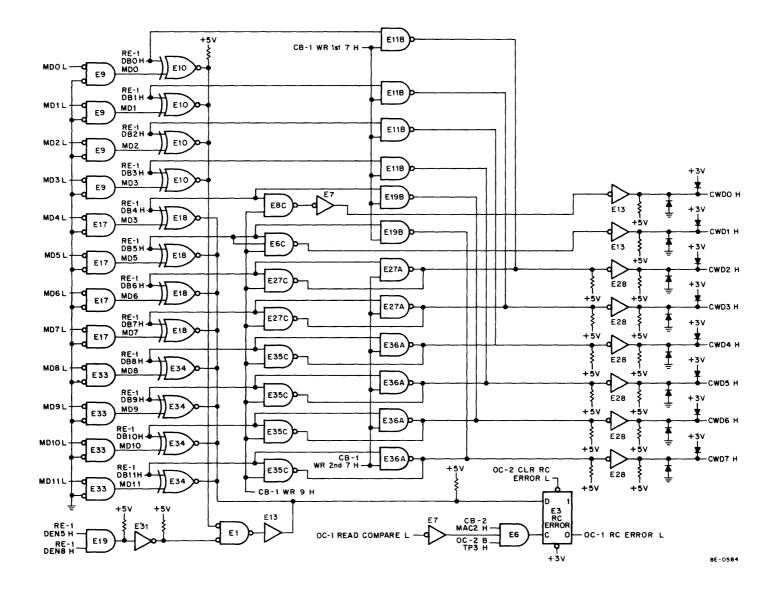

| 7.2.5       Skip Logic       7-2         7.3       M8327 REGISTERS MODULE       7-2         7.3.1       Multiplexer and Data Register       7-2         7.3.2       Command Register       7-3         7.3.2.1       Buffered Command Register (BCM)       7-3         7.3.3       Function Register       7-3         7.3.4       Current Address Register       7-5         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-6         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         7.5.4       PROGRAMMING INFORMATION       8-1         8.1       INTRODUCTION       8-1 <t< td=""><td>7.2.4</td><td>0 0</td></t<>                                                    | 7.2.4     | 0 0                       |

| 7.3       M8327 REGISTERS MODULE       7-2         7.3.1       Multiplexer and Data Register       7-2         7.3.2       Command Register       7-3         7.3.2.1       Buffered Command Register (BCM)       7-3         7.3.3       Function Register       7-3         7.3.4       Current Address Register       7-3         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-6         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic                    | 7.2.5     |                           |

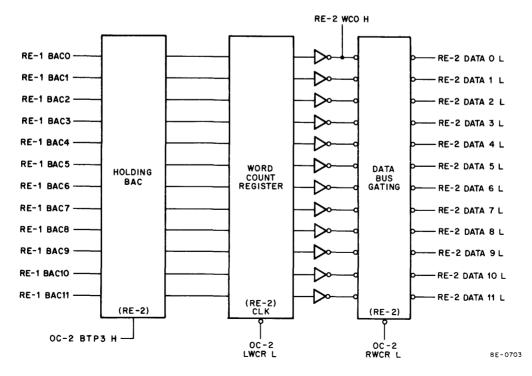

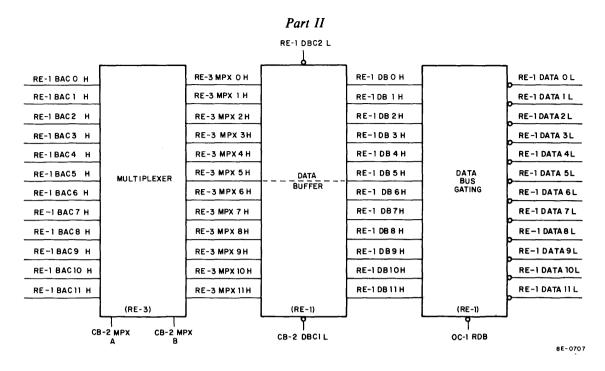

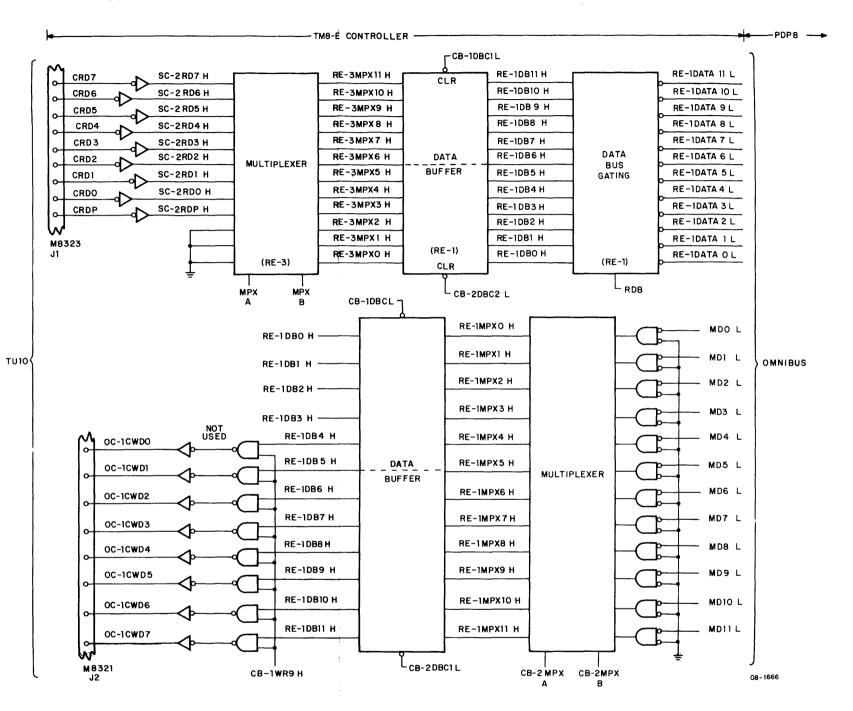

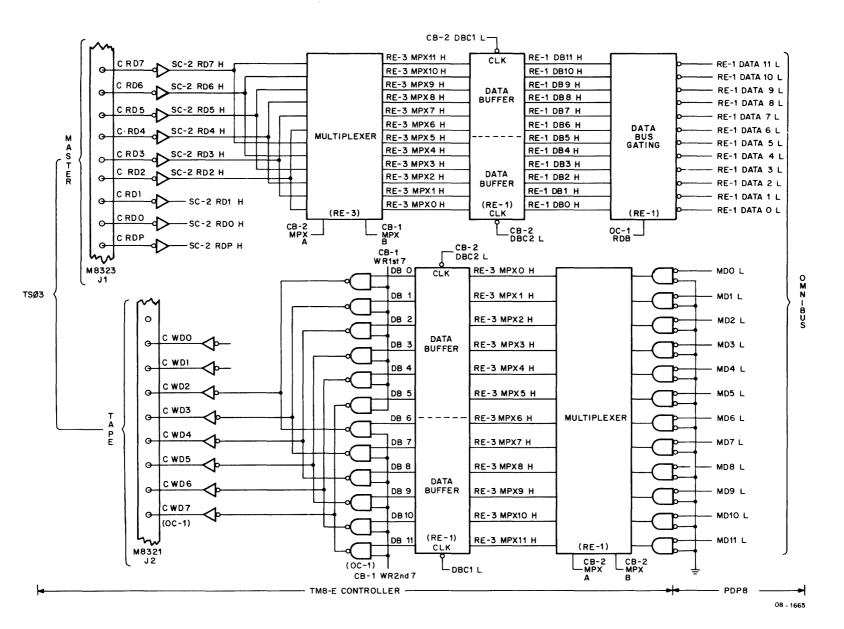

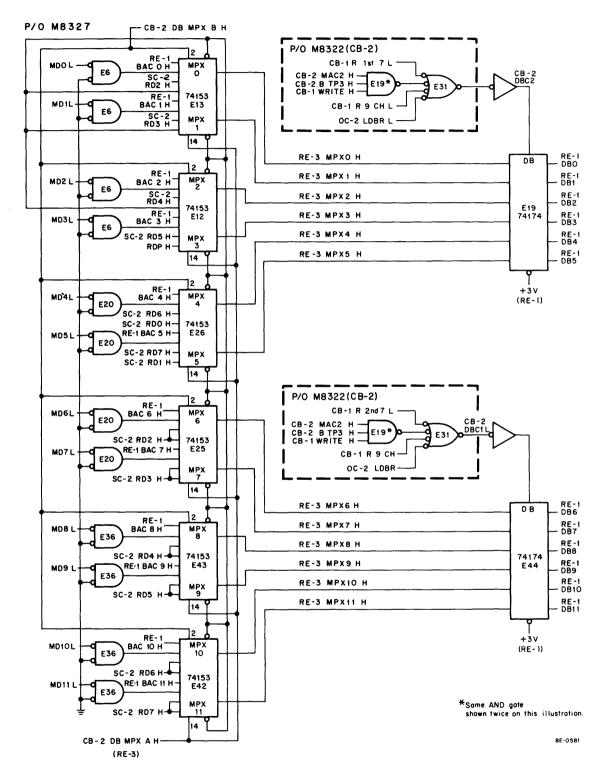

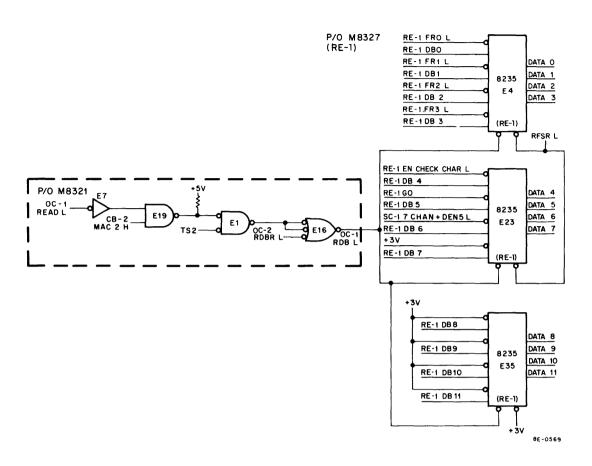

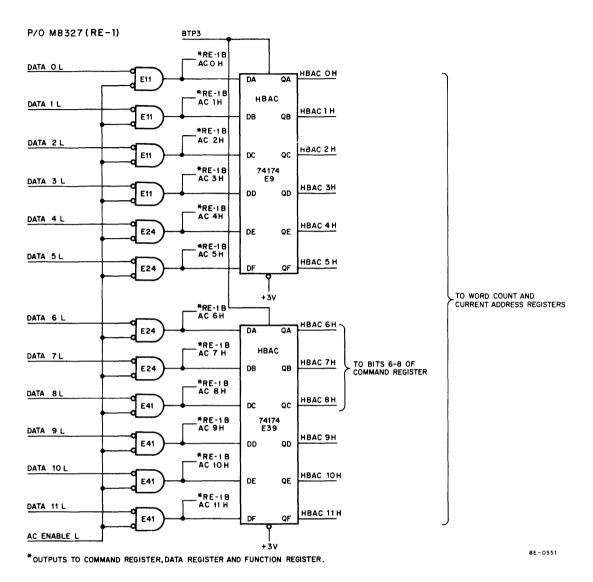

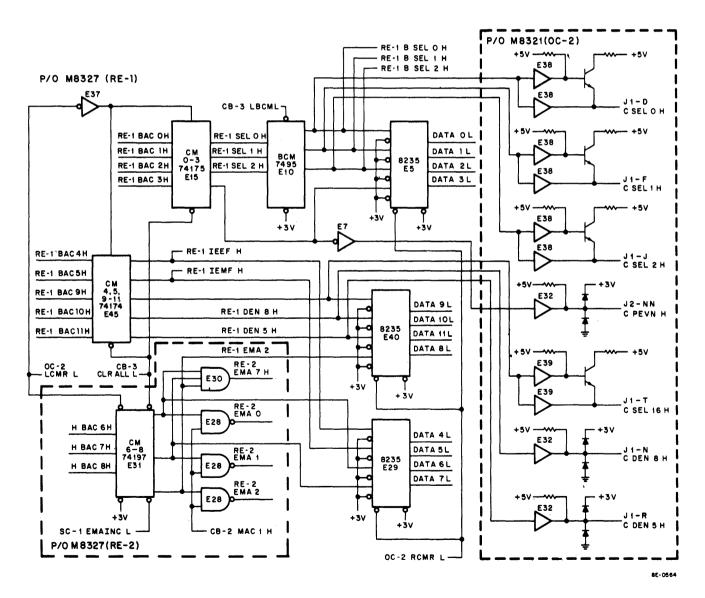

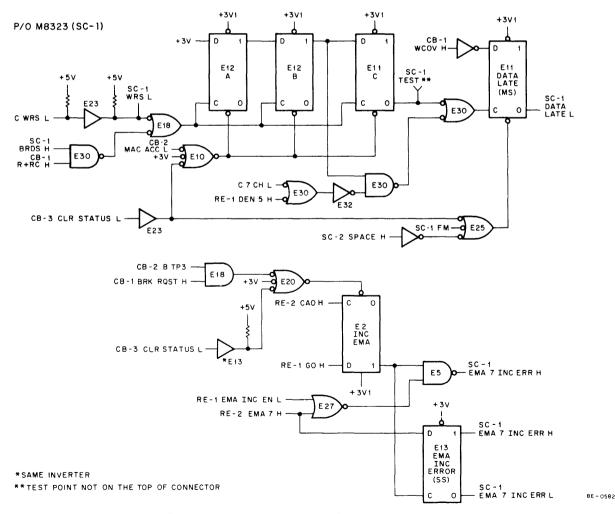

| 7.3.1       Multiplexer and Data Register       7-2         7.3.2       Command Register       7-3         7.3.2.1       Buffered Command Register (BCM)       7-3         7.3.3       Function Register       7-3         7.3.4       Current Address Register       7-5         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.4.6       Control Busy (CNTL BSY)       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         7.5.4       PROGRAMMING INFORMATION       8-11         8.1       INTROUCTION AND REGISTER BITS       8-18         8.3.1       Signal Conventions       8-13         8.3.3       Read Data       8-                                                             | 7.3       |                           |

| 7.3.2       Command Register       7.3         7.3.2.1       Buffered Command Register (BCM)       7.3         7.3.3       Function Register       7.3         7.3.4       Current Address Register       7.5         7.3.5       Word Count Register       7.5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7.5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7.5         7.4.1       Main Status Register       7.5         7.4.2       Second Status Register       7.6         7.4.3       Error Flag       7.6         7.4.4       Illegal Function Detection       7.6         7.4.5       PRESET and SET Pulse Generator       7.7         7.4.6       Control Busy (CNTL BSY)       7.7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7.7         7.5.1       Data Break Control Logic       7.7         7.5.2       Function Decoder       7.7         7.5.3       Interrupt Logic       7.7         7.5.4       PROGRAMMING INFORMATION       8-1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-13         8.3.3       SINGLE CYCLE DATA BREAK <td>7.3.1</td> <td></td>                              | 7.3.1     |                           |

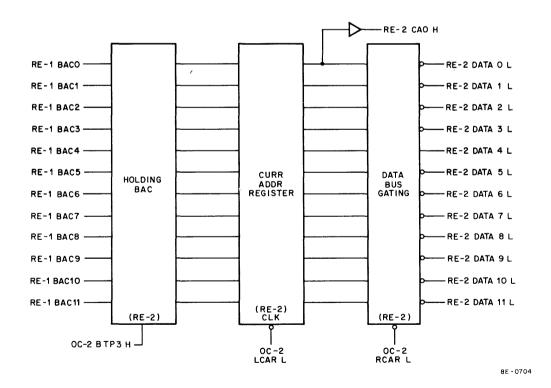

| 7.3.2.1       Buffered Command Register (BCM)       7.3         7.3.3       Function Register       7.3         7.3.4       Current Address Register       7.5         7.3.5       Word Count Register       7.5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7.5         7.4.1       Main Status Register       7.5         7.4.2       Second Status Register       7.5         7.4.3       Error Flag       7.6         7.4.4       Illegal Function Detection       7.6         7.4.5       PRESET and SET Pulse Generator       7.7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7.7         7.5.1       Data Break Control Logic       7.7         7.5.2       Function Decoder       7.7         7.5.3       Interrupt Logic       7.7         7.5.3       Interrupt Logic       7.7         7.5.4       BROGRAMMING INFORMATION       \$-11                                           | 7.3.2     | 1 6                       |

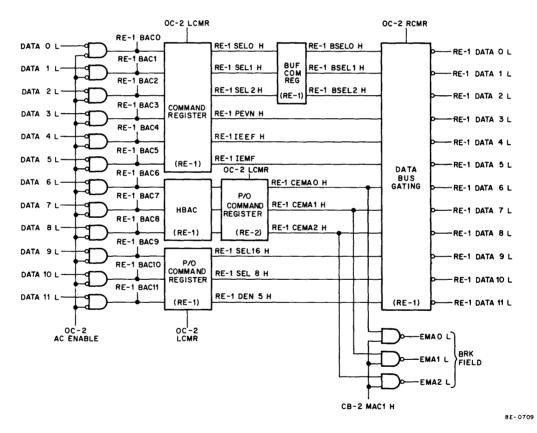

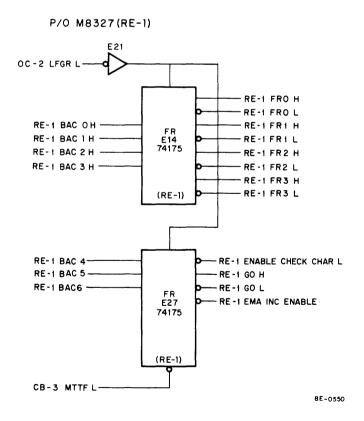

| 7.3.3       Function Register       7.3         7.3.4       Current Address Register       7.5         7.3.5       Word Count Register       7.5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7.5         7.4.1       Main Status Register       7.5         7.4.2       Second Status Register       7.5         7.4.3       Error Flag       7.6         7.4.4       Illegal Function Detection       7.6         7.4.5       PRESET and SET Pulse Generator       7.7         7.4.6       Control Busy (CNTL BSY)       7.7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7.7         7.5.1       Data Break Control Logic       7.7         7.5.2       Function Decoder       7.7         7.5.3       Interrupt Logic       7.7         7.5.4       PROGRAMMING INFORMATION       8.1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-13         8.3.2       Write Data       8-22         8.3.3       Read Data       8-22 <td< td=""><td></td><td></td></td<>                                                           |           |                           |

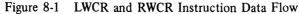

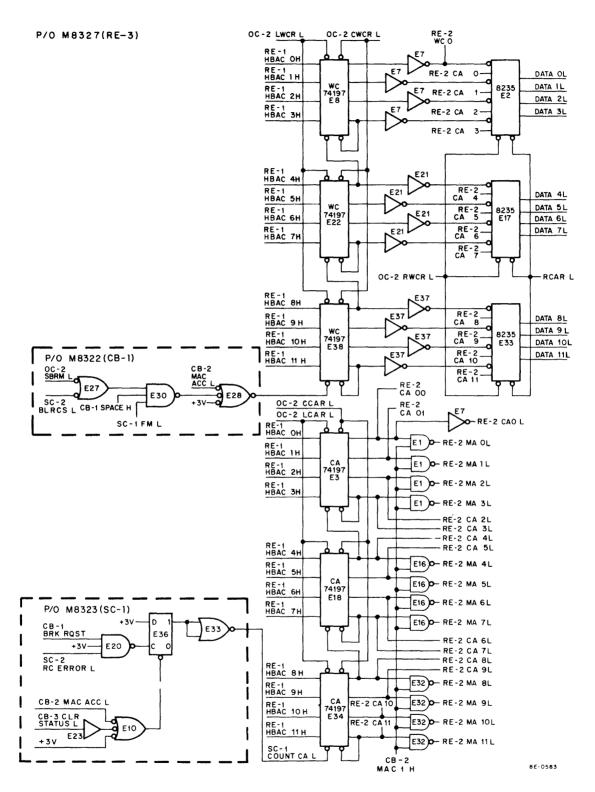

| 7.3.4       Current Address Register       7-5         7.3.5       Word Count Register       7-5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-6         7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.4       M322 CONTROL AND DATA BREAK MODULE       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         7.5.4       PROGRAMMING INFORMATION       8-1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-16         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22 <td></td> <td></td>                                                       |           |                           |

| 7.3.5       Word Count Register       7.5         7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7.5         7.4.1       Main Status Register       7.5         7.4.2       Second Status Register       7.5         7.4.3       Error Flag       7.5         7.4.4       Illegal Function Detection       7.6         7.4.5       PRESET and SET Pulse Generator       7.7         7.4.6       Control Busy (CNTL BSY)       7.7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7.7         7.5.1       Data Break Control Logic       7.7         7.5.2       Function Decoder       7.7         7.5.3       Interrupt Logic       7.7         7.5.4       INTRODUCTION       8-1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       Signal Conventions       8-13         8.3.2       Write Data       8-12         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7       Space Forw                                                                                                |           |                           |

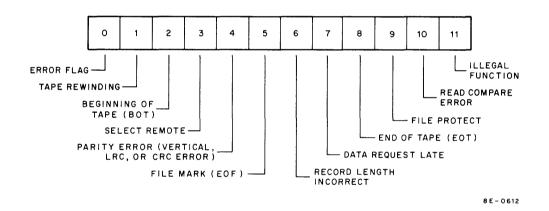

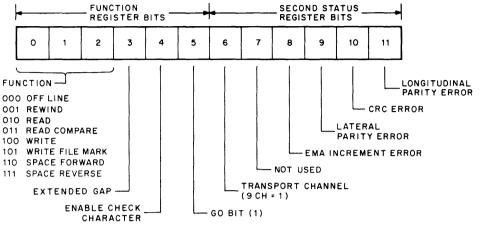

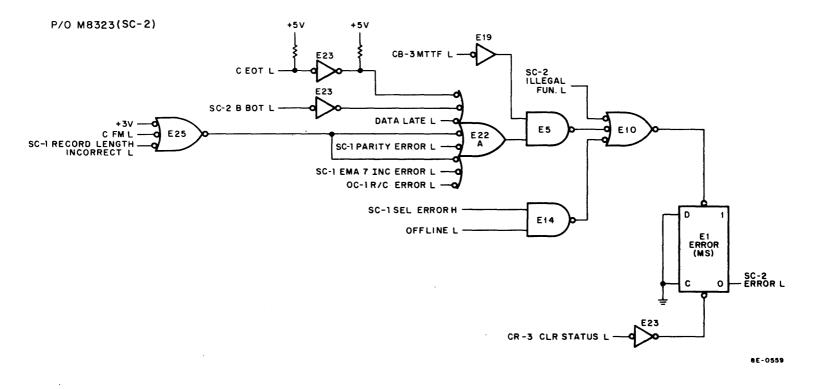

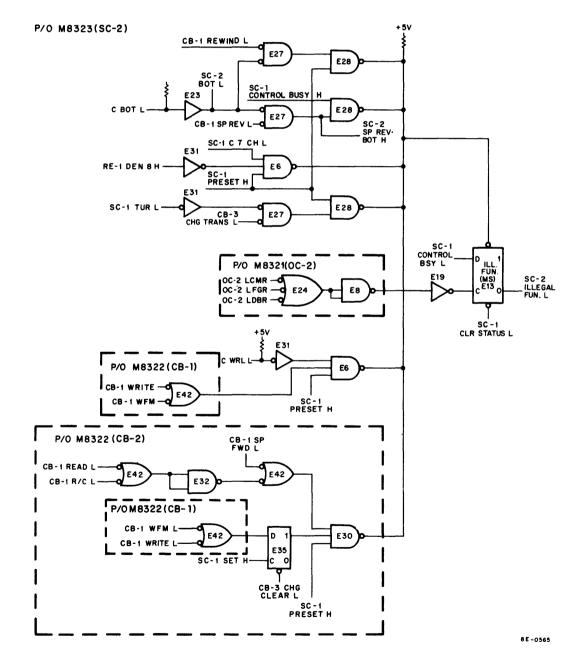

| 7.4       M8323 TRANSPORT STATUS AND CONTROL MODULE       7-5         7.4.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-6         7.4.6       Control Busy (CNTL BSY)       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         7.5.4       PROGRAMMING INFORMATION       8-1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-13         8.3.2       Write Data       8-22         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7                                                                                                 |           |                           |

| 74.1       Main Status Register       7-5         7.4.2       Second Status Register       7-5         7.4.3       Error Flag       7-6         7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.4       Control Busy (CNTL BSY)       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         CHAPTER 8       PROGRAMMING INFORMATION       8-1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-13         8.3.2       Write Data       8-22         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7 <td< td=""><td></td><td>0</td></td<>                                                                 |           | 0                         |

| 7.4.2       Second Status Register       7.5         7.4.3       Error Flag       7.6         7.4.4       Illegal Function Detection       7.6         7.4.5       PRESET and SET Pulse Generator       7.7         7.4.6       Control Busy (CNTL BSY)       7.7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7.7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7.7         7.5.1       Data Break Control Logic       7.7         7.5.2       Function Decoder       7.7         7.5.3       Interrupt Logic       7.7         7.5.4       PROGRAMMING INFORMATION       8.1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-13         8.3.2       Write Data       8-22         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7       Space Forward       8-22         8.3.8       Space                                                                                                 |           |                           |

| 7.4.3       Error Flag       7.6         7.4.4       Illegal Function Detection       7.6         7.4.5       PRESET and SET Pulse Generator       7.7         7.4.6       Control Busy (CNTL BSY)       7.7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7.7         7.5.1       Data Break Control Logic       7.7         7.5.2       Function Decoder       7.7         7.5.3       Interrupt Logic       7.7         7.5.4       PROGRAMMING INFORMATION       8-1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-13         8.3.2       Write Data       8-10         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7       Space Forward       8-22         8.3.8       Space Forward       8-23         8.3.9       Rewind       8-23 <td></td> <td>0</td>                                                                                                                                        |           | 0                         |

| 7.4.4       Illegal Function Detection       7-6         7.4.5       PRESET and SET Pulse Generator       7-7         7.4.6       Control Busy (CNTL BSY)       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         7.5.3       Interrupt Logic       7-7         CHAPTER 8       PROGRAMMING INFORMATION       8-1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       Single Conventions       8-1         8.3.1       Signal Conventions       8-16         8.3.2       Write Data       8-16         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7       Space Forward       8-23         8.3.9                                                                                               |           |                           |

| 7.4.5       PRESET and SET Pulse Generator       7-7         7.4.6       Control Busy (CNTL BSY)       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         CHAPTER 8         PROGRAMMING INFORMATION       8-1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-13         8.3.2       Write Data       8-22         8.3.3       Read Data       8-22         8.3.4       Read Data       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7       Space Forward       8-22         8.3.8       Space Forward       8-23         8.3.9       Rewind       8-23                                                                                                                                                                                            |           |                           |

| 74.6       Control Busy (CNTL BSY)       7-7         7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         CHAPTER 8       PROGRAMMING INFORMATION       8-1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-13         8.3.2       Write Data       8-22         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7       Space Forward       8-22         8.3.8       Space Reverse       8-23         8.3.9       Rewind       8-23                                                                                                                                                                                                                                                                                                                         |           |                           |

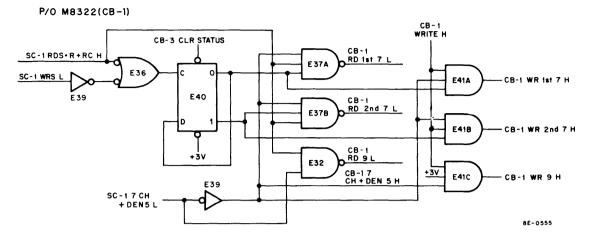

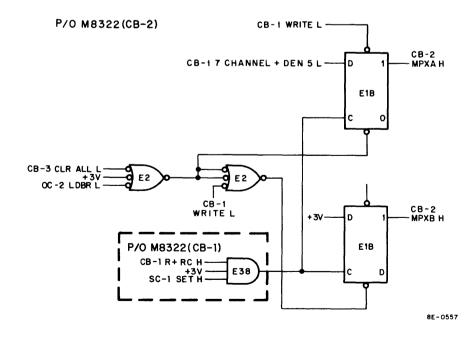

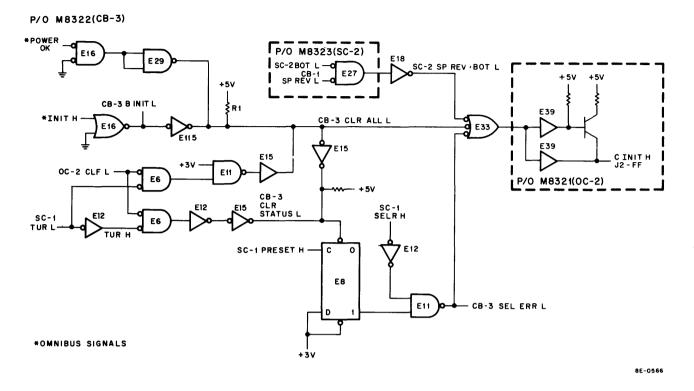

| 7.5       M8322 CONTROL AND DATA BREAK MODULE       7-7         7.5.1       Data Break Control Logic       7-7         7.5.2       Function Decoder       7-7         7.5.3       Interrupt Logic       7-7         CHAPTER 8       PROGRAMMING INFORMATION         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-13         8.3.2       Write Data       8-16         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7       Space Forward       8-22         8.3.8       Space Reverse       8-23         8.3.9       Rewind       8-23                                                                                                                                                                                                                                                                                                                                                                                        |           |                           |

| 7.5.1Data Break Control Logic7-77.5.2Function Decoder7-77.5.3Interrupt Logic7-7CHAPTER 8PROGRAMMING INFORMATION8.1INTRODUCTION8-18.2INSTRUCTIONS AND REGISTER BITS8-18.3SINGLE CYCLE DATA BREAK8-118.3.1Signal Conventions8-138.3.2Write Data8-168.3.3Read Data8-228.3.4Read/Compare8-228.3.5Extended Gap8-228.3.6Write End-of-File8-228.3.7Space Forward8-238.3.9Rewind8-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                           |

| 7.5.2       Function Decoder       7.7         7.5.3       Interrupt Logic       7.7         CHAPTER 8       PROGRAMMING INFORMATION       8.1         8.1       INTRODUCTION       8-1         8.2       INSTRUCTIONS AND REGISTER BITS       8-1         8.3       SINGLE CYCLE DATA BREAK       8-11         8.3.1       Signal Conventions       8-13         8.3.2       Write Data       8-16         8.3.3       Read Data       8-22         8.3.4       Read/Compare       8-22         8.3.5       Extended Gap       8-22         8.3.6       Write End-of-File       8-22         8.3.7       Space Forward       8-22         8.3.8       Space Reverse       8-23         8.3.9       Rewind       8-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                           |

| 7.5.3Interrupt Logic7-7CHAPTER 8PROGRAMMING INFORMATION8.1INTRODUCTION8.2INSTRUCTIONS AND REGISTER BITS8.3SINGLE CYCLE DATA BREAK8.3.1Signal Conventions8.3.2Write Data8.3.3Read Data8.3.4Read/Compare8.3.5Extended Gap8.3.6Write End-of-File8.3.7Space Forward8.3.8Space Reverse8.3.9Rewind                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | 6                         |

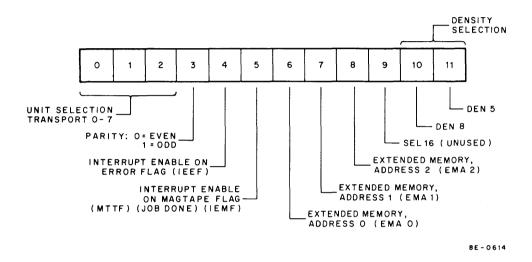

| CHAPTER 8PROGRAMMING INFORMATION8.1INTRODUCTION8-18.2INSTRUCTIONS AND REGISTER BITS8-18.3SINGLE CYCLE DATA BREAK8-118.3.1Signal Conventions8-138.3.2Write Data8-168.3.3Read Data8-228.3.4Read/Compare8-228.3.5Extended Gap8-228.3.6Write End-of-File8-228.3.7Space Forward8-228.3.8Space Reverse8-238.3.9Rewind8-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                           |