# digital

# Microcomputer Products Handbook

Microcomputer Products Handbook

Ł

n santa Angelan angelan

# digital

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

Digital believes the information in this publication is accurate as of its publication date; such information is subject to change without notice. Digital is not responsible for any inadvertent errors.

| DATATRIEVE        | Letterwriter 100  | RSX          |

|-------------------|-------------------|--------------|

| DEC               | LSI               | RSX-11       |

| DECnet            | MicroPDP-11       | RSX-11M-PLUS |

| DECProm           | MicroPower/Pascal | RX02         |

| DECservice        | Micro/RSTS        | RX50         |

| DECtape           | Micro/RSX         | RT-11        |

| DIBOL             | Packetnet         | SB11         |

| the Digital logo  | PDP               | SBC-11/21    |

| DSM-11            | Professional      | ULTRIX       |

| FMS               | Q-bus             | UNIBUS       |

| FORTRAN IV        | Rainbow           | VAX          |

| IAS               | ReGIS             | VAXELN       |

| Internet          | RSTS              | VMS          |

| J-11              | RSTS/E            | VT           |

| Letterprinter 100 |                   |              |

The following are trademarks of Digital Equipment Corporation:

Copyright © 1985 Digital Equipment Corporation. All Rights Reserved.

# Contents

#### Part I • Introduction

## Chapter 1 - The Q-bus and Q-bus Modules

| The Q-bus                           | ••••    | <br> | ••• |       | <br> |       |  | <br>. 1-1 |

|-------------------------------------|---------|------|-----|-------|------|-------|--|-----------|

| Master/Slave Relationship           |         |      |     |       |      |       |  |           |

| Device Registers and Addresses      | • • • • | <br> |     |       | <br> |       |  | <br>. 1-1 |

| Interrupts and Device Priority      |         | <br> |     |       |      |       |  | <br>. 1-2 |

| Q-bus Addressing                    |         |      |     |       |      |       |  |           |

| Q-bus Signal and Pin Identification |         |      |     |       |      |       |  |           |

| Specifications                      |         | <br> |     | <br>• | <br> | <br>• |  | <br>1-13  |

| Cabling and Cabinet Kits            |         |      |     |       |      |       |  |           |

#### Part II • Microcomputers

#### Chapter 2 - Introduction to Microcomputers

## Chapter 3 • KDF11-AA LSI-11/23 Microcomputer

#### Chapter 4 • KDF11-B LSI-11/23-PLUS Microcomputer

| Specifications                                  | -2 |

|-------------------------------------------------|----|

| Related Documentation 4                         | -2 |

| Configuration                                   | -3 |

| Jumper and Switch Configuration 4               | -3 |

| Manufacturing Test Jumpers 4                    |    |

| CPU Option Jumpers 4                            | -5 |

| Powerup Mode Selection 4                        | -5 |

| Halt/Trap Option–J16 4                          |    |

| Onboard Device Selection Jumpers 4              | -7 |

| Console SLU Switch and Jumper Configurations 4  | -9 |

| Break/Halt Jumpers 4-2                          | 10 |

| Second SLU Switch and Jumper Configurations 4-1 | 11 |

| Boot/Diagnostic Switches and Jumpers 4-1        | 12 |

| Q-bus Backplane Jumpers 4-2                     |    |

| Cabinet Kits                                    | 19 |

## Chapter 5 • KDJ11-A LSI-11/73 Microcomputer

| S | rifications       |

|---|-------------------|

| R | ted Documentation |

| C | figuration        |

|   | owerup Options    |

|   | alt Option        |

|   | oot Address       |

|   | /akeup Disable    |

|   | EVNT Recognition  |

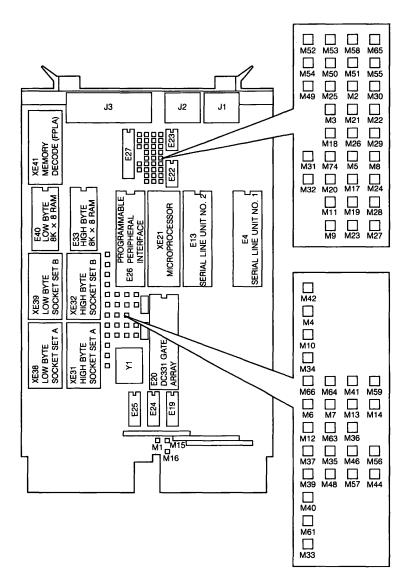

#### Chapter 6 • KXT11-AB FALCON-PLUS SBC-11/21-PLUS Microcomputer

| pecifications                           |

|-----------------------------------------|

| elated Documentation 6-1                |

| onfiguration                            |

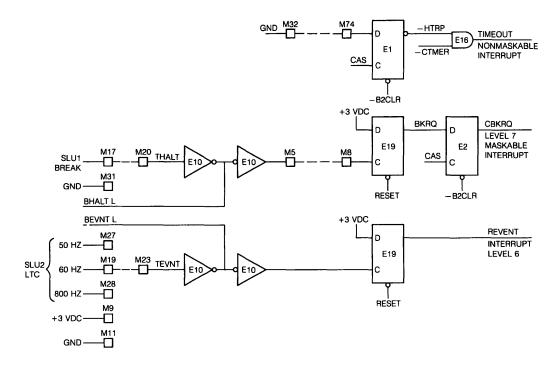

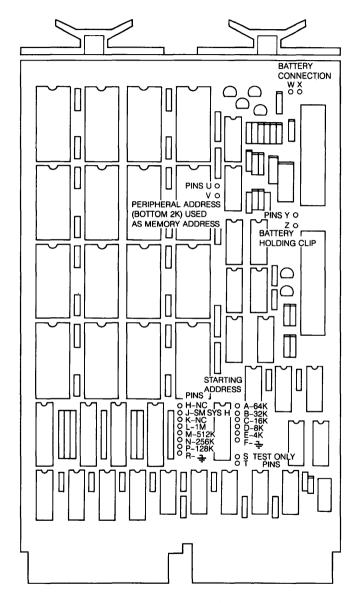

| Battery Backup                          |

| Wakeup Circuit                          |

| Starting Address                        |

| Interrupts                              |

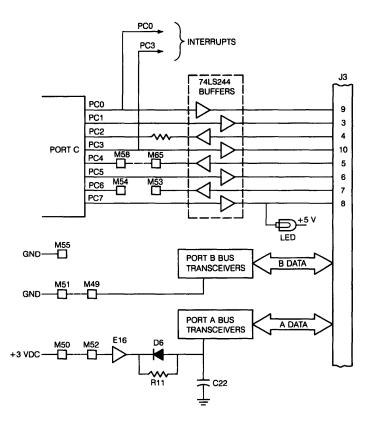

| Parallel I/O                            |

| Serial I/O                              |

| Memories                                |

| ables and Connectors 6-22               |

| Parallel I/O Interface                  |

| Serial Line Interfaces (J1 and J2) 6-23 |

## Chapter 7 = KXT11-CA Single-Board Computer

| Specifications                         | 7-1  |

|----------------------------------------|------|

| Related Documentation                  | 7-1  |

| Configuration                          | 7-2  |

| User EPROM, EEPROM, and ROM            | 7-5  |

| Battery Backup                         | 7-6  |

| User Socket + 5V Power                 |      |

| Memory Maps                            |      |

| Boot/Self-test Option                  |      |

| Base Address                           |      |

| Realtime Clock Interrupt               |      |

| Break Enable                           |      |

| SLU1 Transmitter                       |      |

| SLU1 Receiver                          | 7-11 |

| SLU1 Baud Rate                         | 7-11 |

| DMA Requests                           |      |

| SLU2 Channel A Receiver                |      |

| SLU2 Channel B Operation               |      |

| SLU2 Channel B Receiver                |      |

| SLU2 Channel B Transmitter             |      |

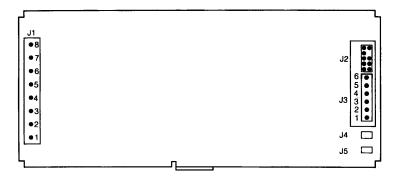

| Cables and Connectors                  |      |

| Parallel I/O Interface (J4)            |      |

| Serial I/O Interfaces (J1, J2, and J3) |      |

| Loopback Connectors                    |      |

| •                                      |      |

## Part III • Memories

#### Chapter 8 - Introduction to Memories

| arity Operation              | 8-1 |

|------------------------------|-----|

| Vindow Mapping               |     |

| Refresh Circuitry            | 8-2 |

| Battery Backup               |     |

| bootstrap                    |     |

| /O Page                      |     |

| Control and Status Registers |     |

## Chapter 9 • MCV11-D CMOS Read/Write Memory with Battery Backup

| . 9-1 |

|-------|

| . 9-3 |

| . 9-3 |

| . 9-5 |

| . 9-7 |

| . 9-7 |

| . 9-8 |

|       |

#### Chapter 10 • MRV11-C Read-Only Memory Module

| Specifications                |       |    |       | <br>    | <br>••• |     |     | <br> |     | ••• | . 10-1  |

|-------------------------------|-------|----|-------|---------|---------|-----|-----|------|-----|-----|---------|

| Related Documentation         |       |    | • • • | <br>    | <br>    |     |     | <br> | •   | ••• | . 10-2  |

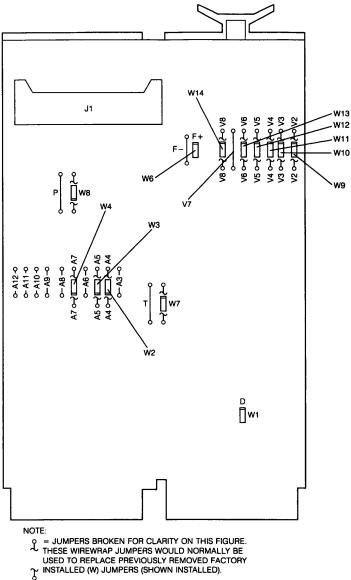

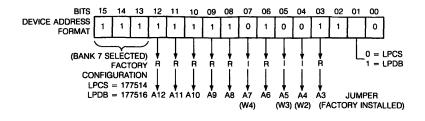

| Configuration                 |       |    | •••   | <br>    | <br>    |     |     | <br> |     |     | . 10-2  |

| Direct Addressing Mode        |       |    |       | <br>••  | <br>    |     |     | <br> | ••  | ••  | . 10-5  |

| Window-mapping Mode           |       |    |       | <br>    | <br>    |     |     | <br> | • • | ••  | . 10-9  |

| Bootstrap                     |       |    |       | <br>    | <br>    |     | • • | <br> | ••  |     | . 10-13 |

| Use of Multiple MRV11-C Board | s     | •• |       | <br>••• | <br>    |     |     | <br> |     | ••• | . 10-16 |

| ROM Chips                     |       |    | •••   | <br>••  | <br>    |     |     | <br> | • • |     | . 10-17 |

| Chip Access Time              |       |    |       | <br>    | <br>    |     |     | <br> | • • | ••• | . 10-20 |

| DATIO Bus Cycle Inhibit       |       |    | •••   | <br>    | <br>    |     |     | <br> | •   | ••• | 10-20   |

| Wirewrap Pin Identification   | • • • |    |       | <br>    | <br>    | • • |     | <br> | •   |     | . 10-20 |

|                               |       |    |       |         |         |     |     |      |     |     |         |

#### Chapter 11 • MRV11-D Universal Programmable Read-Only Memory

| Specifications              |   |     | <br>• | . 11-1 |

|-----------------------------|---|-----|-------|--------|

| Relation Documentation      |   |     |       | . 11-2 |

| Configuration               | • |     | <br>• | . 11-2 |

| Memory Array                | • |     | <br>• | . 11-3 |

| Addressing Modes            |   |     |       | 11-10  |

| Bootstrap                   |   | • • |       | 11-13  |

| Battery Backup Shunt        | • |     |       | 11-13  |

| System Size Jumpers         | • |     |       | 11-14  |

| DATO Bus Cycle              | • |     |       | 11-14  |

| Read Timing                 |   |     |       |        |

| Installing the MXV11-B2 ROM | • |     |       | 11-14  |

|                             |   |     |       |        |

#### Chapter 12 • MSV11-D, -E Dynamic MOS Read/Write Memory

| Specifications          |     |

|-------------------------|-----|

| Related Documentation 1 | 2-3 |

| Configuration           | 2-3 |

| Address Selection 1     | 2-3 |

| Battery Backup Power 1  | 2-4 |

| Parity 1                | 2-4 |

| Memory Size 1           | 2-5 |

## Chapter 13 • MSV11-L MOS Random-Access Memory

| Specifications                | 13 | -1 |

|-------------------------------|----|----|

| Related Documentation         | 13 | -2 |

| Configuration                 |    |    |

| Module Starting Address (MSA) | 13 | -3 |

| CSR Address Selection         | 13 | -3 |

| Battery Backup                | 13 | -3 |

#### Chapter 14 • MSV11-P MOS Random-Access Memory

| Specifications                               | 4-1 |

|----------------------------------------------|-----|

| Related Documentation 14                     | 4-2 |

| Configuration 14                             | 4-3 |

| Module Starting Address (MSA) 14             | 4-3 |

| Control and Status Register (CSR) Jumpers 14 | 4-7 |

| Power Jumpers                                | 1-8 |

| Bus Grant Continuity Jumpers 14              | 4-9 |

| Miscellaneous Jumpers                        | 1-9 |

| System Size Jumpers 14                       | 4-9 |

|                                              |     |

#### Chapter 15 • MSV11-Q MOS Random-Access Memory

| Specifications                                 | -1 |

|------------------------------------------------|----|

| Related Documentation                          |    |

| Configuration of the MSV11-QA (Etch Rev A) 15- | 3  |

| Memory Starting and Ending Addresses 15-       | 5  |

| Control and Status Register Address 15-        | 8  |

| Miscellaneous Jumpers 15-                      | 8  |

| Configuration of the MSV11-Q 15-               | .9 |

| Memory Starting and Ending Addresses 15-1      | 0  |

| Control and Status Register Address 15-1       | 3  |

| Battery Backup 15-1                            | 4  |

| Miscellaneous Jumpers                          | 5  |

#### Part IV - Multifunction Modules

#### Chapter 16 • Introduction to Multifunction Modules

#### Chapter 17 • MXV11-A Memory and Asynchronous Serial Line Interface

| Model Options                          | 7-1          |

|----------------------------------------|--------------|

| Specifications 1                       |              |

| Related Documentation 1                | .7 <b>-2</b> |

| Configuration                          | .7 <b>-2</b> |

| Configuring the RAM 17                 |              |

| Configuring the ROM 17                 |              |

| Serial Line Register Address Selection |              |

| Interrupt Vector Selection             |              |

| Serial Line Parameter Jumpers 17       |              |

| Bootstrap Jumpers                      |              |

| Baud Rate Jumpers                      |              |

| Halt/Reboot on Break                   |              |

| 60-Hz Clock                            |              |

| Cables and Connectors                  |              |

## Chapter 18 • MXV11-B Multifunction Option Module

| Specifications                    |  | • • |    | <br>• • | <br> | 18-1  |

|-----------------------------------|--|-----|----|---------|------|-------|

| Related Documentation             |  | •   |    | <br>    | <br> | 18-2  |

| Configuration                     |  |     |    | <br>    | <br> | 18-2  |

| Configuring the RAM               |  |     |    | <br>    | <br> | 18-4  |

| ROM Configurations                |  |     |    | <br>    | <br> | 18-7  |

| Configuring the Serial Line Units |  | • • | Ċ. | <br>• • |      | 18-11 |

| Linetime Clock                    |  |     |    |         |      |       |

| Master Clock                      |  |     |    | <br>• • |      | 18-17 |

| MSV11-B2 ROM Set                  |  |     |    | <br>    |      | 18-17 |

| Cables and Connectors             |  |     |    | <br>    |      | 18-18 |

|                                   |  |     |    |         |      |       |

## Part V = Asynchronous Communications Interfaces

#### Chapter 19 • Introduction to Asynchronous Communications Interfaces

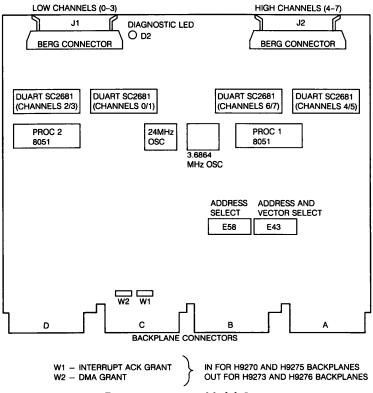

#### Chapter 20 = DHV11 Asynchronous Multiplexer

| Specifications                     |         | <br> |       | <br>20-1 |

|------------------------------------|---------|------|-------|----------|

| Related Documentation              |         | <br> |       | <br>20-2 |

| Configuration                      |         | <br> |       | <br>20-2 |

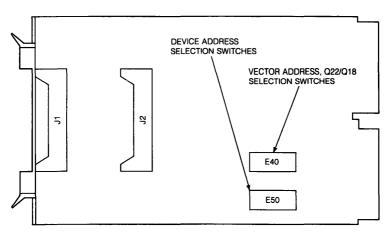

| Address Switches                   |         | <br> |       | <br>20-3 |

| Vector Switches                    |         | <br> | • • • | <br>20-3 |

| Bus Grant Continuity Jumpers       |         |      |       |          |

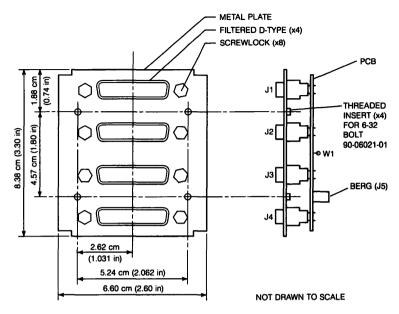

| Cables and Cabinet Kits            |         | <br> |       | <br>20-4 |

| Null Modem Cables                  |         |      |       |          |

| Full Modem Cables                  |         | <br> |       | <br>20-7 |

| Data Rate to Cable Length Relation | onships | <br> |       | <br>20-8 |

| Cabinet Kits                       |         | <br> |       | <br>20-8 |

|                                    |         |      |       |          |

## Chapter 21 • DLV11 Asynchronous Serial Line Unit

| Specifications              | <br>-1 |

|-----------------------------|--------|

| Related Documentation       | <br>-1 |

| Configuration               | <br>-1 |

| Register Addresses          | <br>-4 |

| Vector Addresses            | <br>-5 |

| UART Operation              | <br>-5 |

| Baud Rate Selection         | <br>-6 |

| EIA Interface               | <br>-6 |

| 20mA Current Loop Interface | <br>-6 |

| Cables                      | <br>-7 |

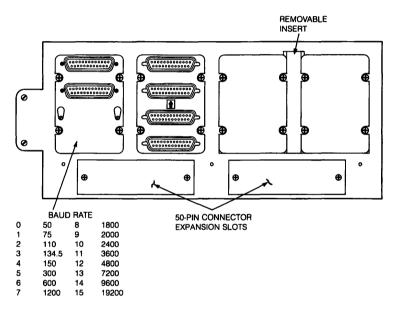

#### Chapter 22 • DLVE1 Asynchronous Line Interface

| pecifications              | -1        |

|----------------------------|-----------|

| Related Documentation 22   | !-1       |

| Configuration              | !-1       |

| Register Addresses 22      | 2-5       |

| Interrupt Vectors          | !-7       |

| Baud Rate Selection 22     | !-7       |

| Data Bit Selection         | !-7       |

| Cables and Cabinet Kits 22 | <u>-9</u> |

## Chapter 23 • DLVJ1 Four-Channel Asynchronous Serial Interface

| Specifications                     | 23-   |

|------------------------------------|-------|

| Related Documentation              |       |

| Configuration                      |       |

| Device Registers                   |       |

| Interrupt Vectors                  | 23-   |

| Character Formats                  | 23-   |

| Baud Rates                         | 23-1  |

| Console Device Selection           | 23-1  |

| Break Response                     | 23-1  |

| Peripheral Interface Configuration | 23-12 |

| Cables and Cabinet Kits            |       |

## Chapter 24 • DZQ11 Asynchronous Multiplexer

| Specifications                       | <br> | 24-1 |

|--------------------------------------|------|------|

| Related Documentation                | <br> | 24-1 |

| Configuration                        | <br> | 24-1 |

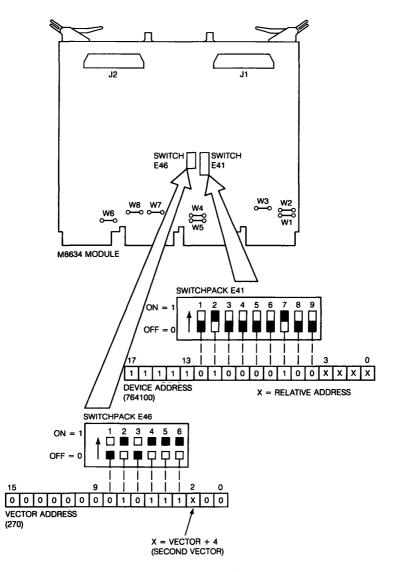

| Device Address                       | <br> | 24-3 |

| Vector Address                       | <br> | 24-4 |

| Test Switch (E13-8)                  | <br> | 24-5 |

| Break Character Response             |      |      |

| Modem Control                        | <br> | 24-6 |

| Baud Rate Jumpers                    |      |      |

| Cables, Connectors, and Cabinet Kits | <br> | 24-7 |

|                                      |      |      |

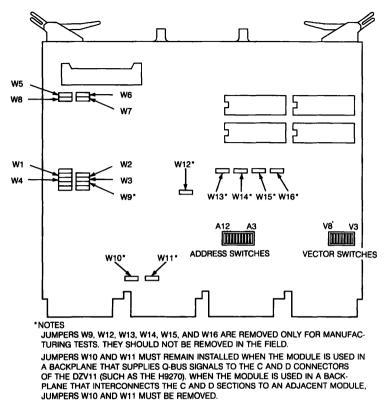

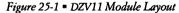

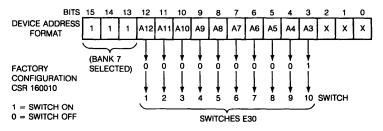

#### Chapter 25 = DZV11 Asynchronous Multiplexer

| Specifications                       | <br> | 25-1 |

|--------------------------------------|------|------|

| Related Documentation                | <br> | 25-1 |

| Configuration                        | <br> | 25-1 |

| Device Address Selection             |      |      |

| Interrupt Vector Selection           | <br> | 25-3 |

| Cables, Connectors, and Cabinet Kits | <br> | 25-5 |

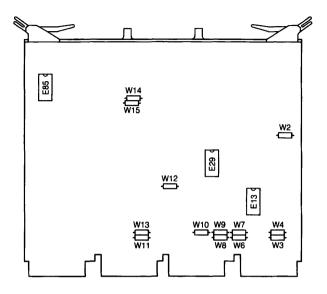

#### Chapter 26 - KMV11-A Programmable Communications Controller

| Specifications                    | 1 |

|-----------------------------------|---|

| Related Documentation             | 1 |

| Configuration                     | 1 |

| Device Address Switches           | 3 |

| Interrupt Vector Address Switches | 4 |

| Self-test Switches                |   |

| Extended Address Jumpers 26-      | 5 |

| BDCOK Jumper                      | 5 |

| Bus Continuity Jumpers 26-        |   |

| Factory Test Jumpers              | 5 |

| Modem Signal Switches and Jumpers |   |

| Cables and Connectors             |   |

|                                   |   |

#### Part VI • Synchronous Communications Interfaces

#### Chapter 27 • Introduction to Synchronous Communications Interfaces

| DEQNA Ethernet Q-bus Network Controller        | 27-1 |

|------------------------------------------------|------|

| DMV11 Synchronous Controller                   | 27-1 |

| DPV11 Serial Syncrhonous Line Interface        |      |

| DUV11 Synchronous Line Interface               | 27-2 |

| KMV11-A Programmable Communications Controller | 27-2 |

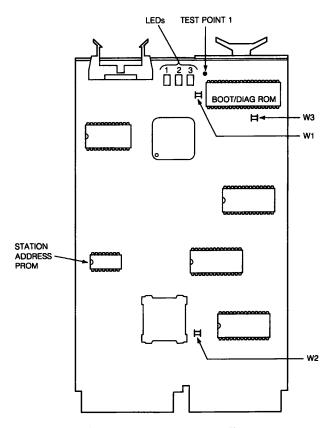

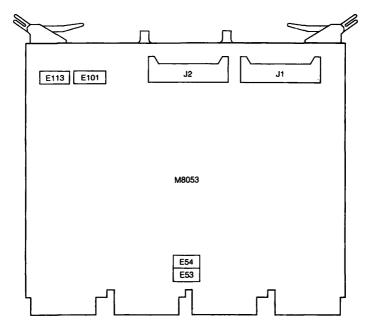

## Chapter 28 • DEQNA Ethernet Q-bus Network Adapter

| Specifications                  | <br>28-1 |

|---------------------------------|----------|

| Related Documentation           | <br>28-1 |

| Configuration                   | <br>28-2 |

| Device Address Assignment (W1)  | <br>28-4 |

| Bus Request Hold-off Timer (W2) | <br>28-4 |

| Sanity Timer (W3)               | <br>28-4 |

| Cables and Cabinet Kits         | <br>28-4 |

|                                 |          |

## Chapter 29 = DMV11 Synchronous Controller

| Specifications             | 29 | -1 |

|----------------------------|----|----|

| Related Documentation      | 29 | -2 |

| Configuration              | 29 | -2 |

| Device Address             | 29 | -3 |

| Interrupt Vector Address   | 29 | -4 |

| Tributary Address          |    | -5 |

| Switch-Selectable Features |    |    |

| Cables and Cabinet Kits    | 29 | -8 |

#### Chapter 30 • DPV11 Serial Synchronous Line Interface

| Specifications                   | -1 |

|----------------------------------|----|

| Related Documentation            | .2 |

| Configuration                    | .2 |

| Device Address                   | 4  |

| Interrupt Vector Address         | .4 |

| Drive Attentuation Jumper 30-    | .5 |

| Interface Selection Jumpers 30-  | .5 |

| Receiver Termination Jumpers 30- | .6 |

| Clock Jumpers 30-                | .6 |

| Data Set Jumpers 30-             | .6 |

| Cables and Cabinet Kits 30-      | .7 |

#### Chapter 31 • DUV11 Line Interface

| Specifications           | 31-1 |

|--------------------------|------|

| Related Documentation    |      |

| Configuration            |      |

| Device Address           | 31-2 |

| Interrupt Vector Address |      |

| Option Switches          | 31-4 |

| Cables                   | 31-5 |

## Part VII • Analog Interfaces

## Chapter 32 - Introduction to Analog Interfaces

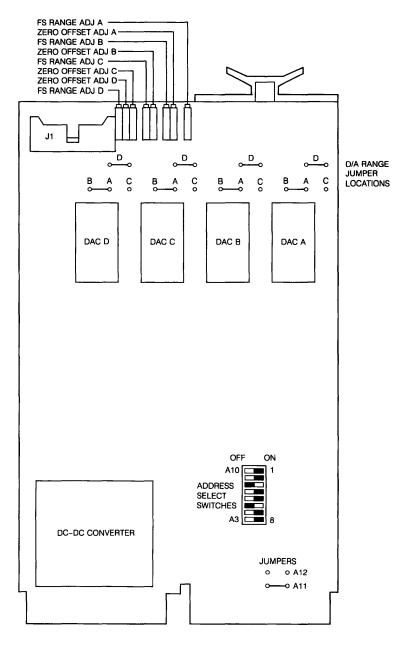

#### Chapter 33 = AAV11-C Analog Output Board

| Specifications                   | <br> | <br> | <br> | 33-1 |

|----------------------------------|------|------|------|------|

| Related Documentation            |      |      |      |      |

| Configuration                    | <br> | <br> | <br> | 33-2 |

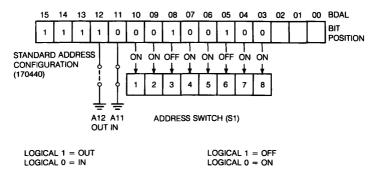

| Device Address                   | <br> | <br> | <br> | 33-2 |

| Output Voltage Range Selection . | <br> | <br> | <br> | 33-4 |

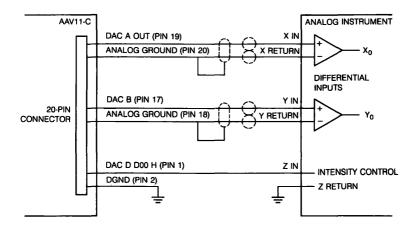

| Interfacing to the AAV11-C       | <br> | <br> | <br> | 33-5 |

#### Chapter 34 ADV11-C Analog-to-Digital Converter

| Specifications                         | 34-1 |

|----------------------------------------|------|

| Related Documentation                  |      |

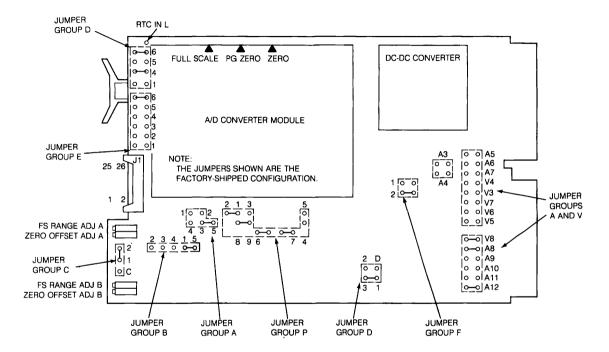

| Configuration                          | 34-2 |

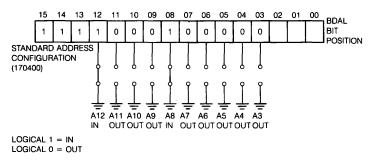

| Device Address                         |      |

| Interrupt Vector Address               | 34-5 |

| Analog Input Range, Type, and Polarity | 34-5 |

| A/D Output Data Notation               |      |

| External Trigger Source                | 34-6 |

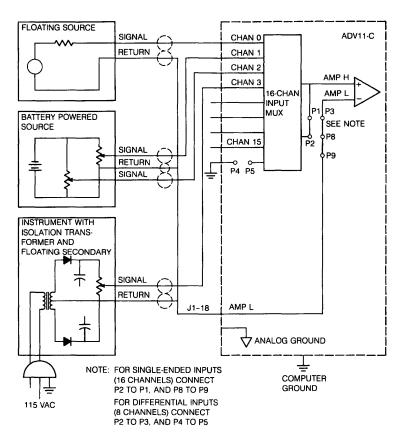

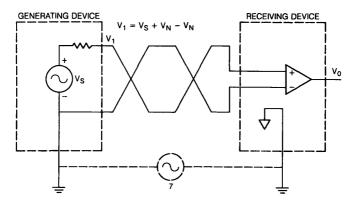

| Interfacing to the ADV11-C               | 34-7 |

|------------------------------------------|------|

| Single-Ended Inputs (16 Channels)        |      |

| Pseudo-Differential Inputs (16 Channels) | 34-8 |

| Differential Inputs (8 Channels)         | 34-9 |

## Chapter 35 • AXV11-C Analog Input/Output Board

| Specifications                         | 35-1 |

|----------------------------------------|------|

| Related Documentation 3                | 35-3 |

| Configuration                          | 35-3 |

| Device Address                         |      |

| Interrupt Vector Address 3             | 35-6 |

| Analog Input Range, Type, and Polarity | 35-6 |

| A/D Output Data Notation 3             | 35-7 |

| External Trigger Source 3              | 35-7 |

| D/A Configuration                      | 35-8 |

| Interfacing to the AXV11-C 3           | 35-9 |

## Chapter 36 • KWV11-C Programmable Realtime Clock

| Specifications                              | 36-1 |

|---------------------------------------------|------|

| Related Documentation                       | 36-2 |

| Configuration                               | 36-3 |

| Device Address                              | 36-5 |

| Interrupt Vector Address                    | 36-5 |

| Schmitt Trigger Reference Levels and Slopes |      |

| External Control of Schmitt Triggers        | 36-7 |

| Interfacing to the KWV11-C                  | 36-7 |

## Part VIII • Parallel Interfaces

## Chapter 37 = Introduction to Parallel Interfaces

| DRV11 Parallel Line Unit                  | 37-1 |

|-------------------------------------------|------|

| DRV11-J High-Density Parallel Interface   | 37-1 |

| DRV11-WA General Purpose DMA Interface    | 37-1 |

| IBV11-A Instrument Bus Interface          | 37-1 |

| IEQ11-A DMA IEC/IEEE Bus Interface Option | 37-2 |

#### Chapter 38 • DRV11 Parallel Line Unit

| Specifications               | <br> |  | • | <br>    |  | • |  |  |   | • |       |   | <br>• |   |   | <br> | <br>38- | 1 |

|------------------------------|------|--|---|---------|--|---|--|--|---|---|-------|---|-------|---|---|------|---------|---|

| <b>Related</b> Documentation | <br> |  | • | <br>• • |  | • |  |  | • | • | <br>• | • | <br>• | • | • | <br> | <br>38- | 1 |

| Configuration                                        | 38-1 |

|------------------------------------------------------|------|

| Device Address                                       | 38-3 |

| Interrupt Vector Address                             |      |

| NEW DATA RDY and DATA TRANS Pulse Width Modification | 38-4 |

| Cables and Cabinet Kits                              | 38-4 |

## Chapter 39 = DRV11-J High-Density Parallel Interface

| Specifications           | 39-1 |

|--------------------------|------|

| Related Documentation    |      |

| Configuration            | 39-2 |

| Device Address           | 39-4 |

| Interrupt Vector Address |      |

| Cables and Cabinet Kits  | 39-6 |

## Chapter 40 • DRV11-WA General Purpose DMA Interface

| Specifications             | 40-1             |

|----------------------------|------------------|

| Related Documentation      | <del>1</del> 0-2 |

| Configuration              | <del>1</del> 0-2 |

| Device Address 4           | 10-2             |

| Interrupt Vector Address 4 | 10-3             |

| Addressing Mode 4          | 10-4             |

| Cables and Cabinet Kits    |                  |

#### Chapter 41 • IBV11-A Instrument Bus Interface

| Specifications        |   | ••• |    |     | 41-1 |

|-----------------------|---|-----|----|-----|------|

| Related Documentation |   |     |    |     | 41-1 |

| Configuration         |   |     |    |     | 41-1 |

| Device Address        |   | •   |    |     | 41-3 |

| Interrupt Vectors     |   |     | •• |     | 41-4 |

| Cables and Connectors | • | • • |    |     | 41-5 |

| Optional Cables       | • | • • | •• | • • | 41-7 |

# Chapter 42 • IEQ11-A DMA Interface Option

•

| Specifications                   | <br>42 | 2-1 |

|----------------------------------|--------|-----|

| Related Documentation            | <br>42 | 2-2 |

| Configuration                    | <br>42 | 2-2 |

| Device Address                   | <br>   | 2-4 |

| Interrupt Vector Address         | <br>42 | 2-4 |

| Backplane and Continuity Jumpers | <br>   | 2-4 |

| Interrupt Priority Level         | <br>42 | 2-5 |

| Cables                           | <br>42 | 2-6 |

|                                  |        |     |

#### Part IX • Peripheral Interfaces

## Chapter 43 • Introduction to Peripheral Interfaces

| LPV11 Printer Option                 | 43-1 |

|--------------------------------------|------|

| RLV12 Disk Controller                | 43-1 |

| RQC25 Disk Controller                | 43-1 |

| RQDX1 Disk Controller                | 43-1 |

| RXV21 Floppy Disk Option             | 43-2 |

| TQK25 Streaming Tape Drive Interface | 43-2 |

| TSV05 Tape Transport Subsystem       | 43-2 |

| TU58 Cartridge Tape Drive            | 43-2 |

## Chapter 44 - LPV11 Printer Option

| Specifications        | 44-1 |

|-----------------------|------|

| Related Documentation |      |

| Configuration         | 44-2 |

| Device Address        | 44-5 |

| Interrupt Vector      | 44-5 |

| Bus Reply Timing      | 44-6 |

| Uppercase Only        | 44-6 |

| Parity                | 44-6 |

| Error Filter          |      |

| Cables                | 44-7 |

## Chapter 45 = RLV12 Disk Controller

| Specifications                    | Ð-1  |

|-----------------------------------|------|

| Related Documentation             | 15-2 |

| Configuration                     | 45-2 |

| Device Address Selection          |      |

| Bus Selection                     | 15-7 |

| Interrupt Vector                  | 15-7 |

| Interrupt Request Level           | 15-8 |

| Memory Parity Error Abort Feature |      |

| Jumpers That Remain Installed     | 15-8 |

| Cables and Cabinet Kits           | 15-9 |

## Chapter 46 = RQC25 Adapter Module

| Specifications        | 46-1 |

|-----------------------|------|

| Related Documentation | 46-2 |

| Configuration         | 46-2 |

.

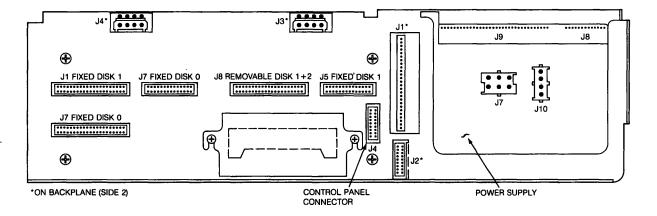

# Chapter 47 • RQDX1 Disk Drive Controller

| Specifications                 |      |

|--------------------------------|------|

| Related Documentation          |      |

| Configuration                  |      |

| Device Address Selection       | 47-5 |

| Logical Unit Number Selection  |      |

| Interrupt Vector               |      |

| RQDX1-E Extender Module Option |      |

| Configuration                  |      |

| Cables and Cabinet Kits        |      |

## Chapter 48 = RXV21 Floppy Disk Option

| Specifications          |      |

|-------------------------|------|

| Related Documentation   |      |

| Configuration           |      |

| Cables and Cabinet Kits | 48-6 |

# Chapter 49 = TQK25 Tape Drive Adapter Module

| Specifications           |     | •   | <br> |   |     |   |     |     |     | 49-1 |

|--------------------------|-----|-----|------|---|-----|---|-----|-----|-----|------|

| Related Documentation    |     |     | <br> | • |     |   | •   |     |     | 49-1 |

| Configuration            |     | •   | <br> |   |     |   |     |     |     | 49-1 |

| Device Address           |     | •   | <br> | • |     | • | • • |     |     | 49-4 |

| Interrupt Vector Address |     | •   | <br> |   |     |   | • • |     |     | 49-5 |

| Block Mode DMA           |     |     | <br> |   |     |   |     |     |     | 49-5 |

| Q-bus Address Mode       | ••• | •   | <br> |   |     | • |     | •   |     | 49-5 |

| Interrupt Priority Level | • • |     | <br> |   |     |   | •   |     |     | 49-6 |

| Cables and Cabinet Kits  | • • | ••• | <br> |   | • • | • | ••• | • • | • • | 49-6 |

## Chapter 50 • TSV05 Tape Transport Subsystem

| Specifications                      | 50-1 |

|-------------------------------------|------|

| Related Documentation               | 50-3 |

| Configuration                       | 50-3 |

| Device and Vector Address Selection | 50-5 |

| Selecting Extended Features         | 50-5 |

| Selecting Record Buffering          |      |

| Selecting Interrupt Priority        |      |

| Bus Grant Continuity Jumpers        |      |

| SCLOCK Enable Jumper                |      |

| Cables and Cabinet Kits             |      |

|                                     |      |

## Chapter 51 • TU58 Cartridge Tape Drive

| Specifications        | 51-1 |

|-----------------------|------|

| Related Documentation | 51-3 |

| Configuration         | 51-3 |

#### Part X • Backplanes, Enclosures, and Expansion Cables

#### Chapter 52 • Introduction to Backplanes, Enclosures, and Expansion

| Backplanes         | 52-1         |

|--------------------|--------------|

| Enclosures 5       |              |

| Bus Termination    |              |

| Expansion Cables 5 | <i>i</i> 2-4 |

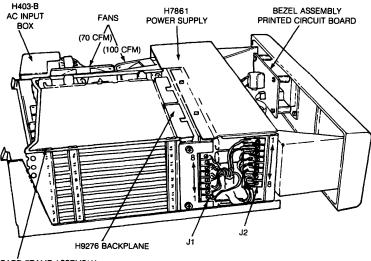

#### Chapter 53 BA11-M Enclosure

| Specifications        | 53-1 |

|-----------------------|------|

| Related Documentaiton | 53-2 |

| Description           | 53-2 |

| Cables                | 53-4 |

# Chapter 54 = BA11-N Enclosure

| Specifications                | 54-1 |

|-------------------------------|------|

| Related Documentation         | 54-2 |

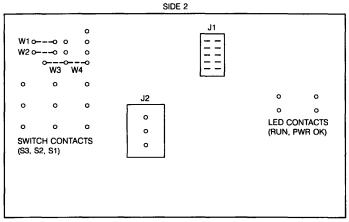

| Description and Configuration | 54-3 |

| Backplane Configuration       | 54-4 |

| Bezel Assembly Jumpers        |      |

# Chapter 55 • BA11-S Enclosure

| Specifications        | 55-1 |

|-----------------------|------|

| Related Documentation | 55-3 |

| Configuration         | 55-3 |

## Chapter 56 = BA23-A Enclosure

| <b>i</b> 6-1        |

|---------------------|

| <del>.</del><br>6-2 |

| 6-2                 |

| i6-5                |

| i6-5                |

| 6-7                 |

|                     |

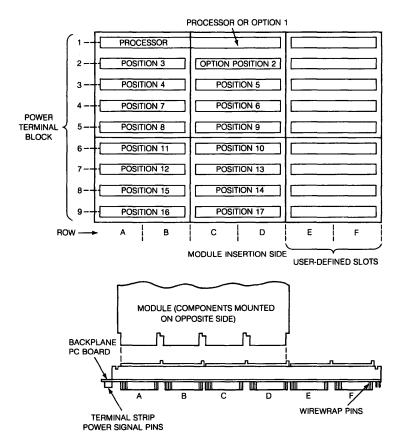

## Chapter 57 • DDV11-B Backplane

| Description and Specifications        | 57-1 |

|---------------------------------------|------|

| Related Documentation                 |      |

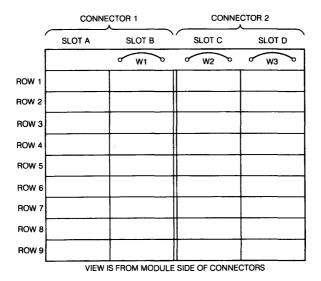

| Configuration                         | 57-2 |

| Module Slot Assignments               |      |

| dc Power and Power Signal Connections |      |

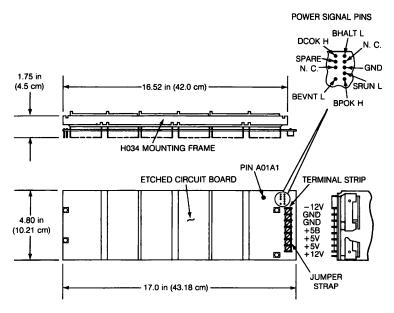

## Chapter 58 = H780 Power Supply

| Specifications                        | 58-1 |

|---------------------------------------|------|

| Notes Relating to Specifications      | 58-3 |

| Related Documentation                 | 58-3 |

| Description                           | 58-4 |

| Console Controls and Indicators       | 58-4 |

| + 12 V and + 5 V Adjustment Procedure | 58-4 |

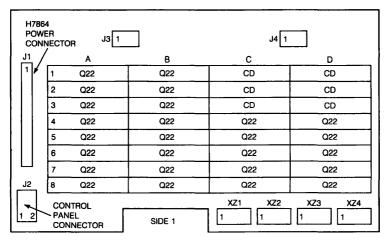

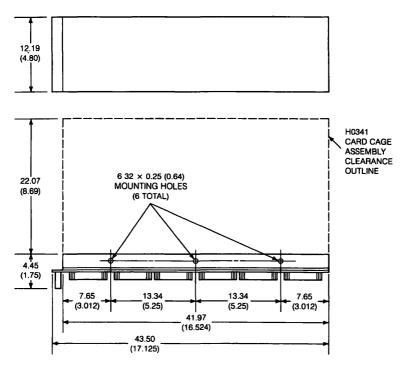

#### Chapter 59 • H9270-Q Backplane

| Specifications         | 59-1 |

|------------------------|------|

| Configuration          | 59-2 |

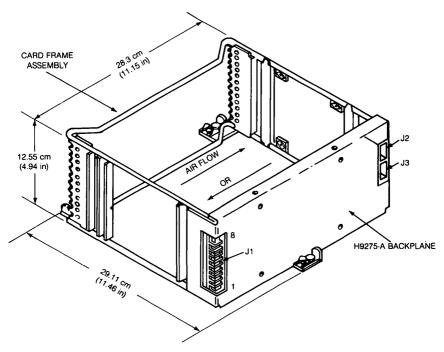

| Mounting the Backplane | 59-3 |

| dc Power Connections   | 59-5 |

#### Chapter 60 = H9273-A Backplane

| Specifications        | 60-1 |

|-----------------------|------|

| Related Documentation | 60-1 |

| Configuration         | 60-1 |

#### Chapter 61 = H9275-A Backplane

| Specifications                 | <br>61-1 |

|--------------------------------|----------|

| Related Documentation          | <br>61-2 |

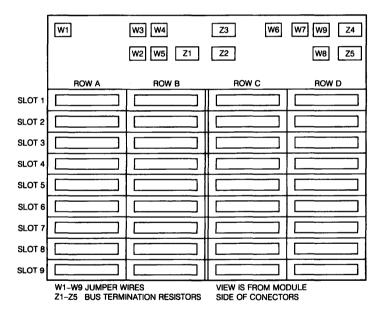

| Configuration                  | <br>61-2 |

| Connecting System Power        | <br>61-3 |

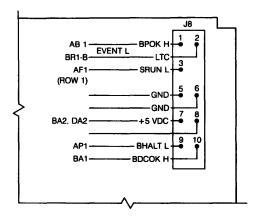

| Connecting Control Bus Signals | <br>61-4 |

| Bus Priority                   | <br>61-5 |

| Bus Termination                | <br>61-6 |

| Bus Restrictions               | <br>61-6 |

|                                |          |

# Chapter 62 = H9281-Q Backplane

| Specifications                              | 62-1 |

|---------------------------------------------|------|

| Configuration                               | 62-2 |

| Connecting System Power                     |      |

| Connecting Externally Generated Bus Signals | 62-5 |

| Device Priority           | 62-6 |

|---------------------------|------|

| Bus Terminations          | 62-6 |

| 16- and 18-Bit Addressing | 62-6 |

#### Chapter 63 = TEV11 Terminator

| Specifications        | <br> | <br>63-1 |

|-----------------------|------|----------|

| Related Documentation |      |          |

| Description           | <br> | <br>63-1 |

# Appendix A • Chip Kits

| DC003 Interrupt Chip              | A-2 |

|-----------------------------------|-----|

| DC004 Protocol Chip               |     |

| DC005 Transceiver Chip            |     |

| DC006 Word Count/Bus Address Chip | A-3 |

| DC010 Direct Memory Access Chip   | A-4 |

| Related Documentation             | A-4 |

## Appendix B = System Configuration Concepts

| Configuration Steps                    | . <b>B-1</b> |

|----------------------------------------|--------------|

| Configuration Rules                    | . <b>B-2</b> |

| Configuring Single Backplane Systems   | . B-3        |

| Configuring Multiple Backplane Systems |              |

| Example                                | . B-3        |

| Problem Statement                      |              |

| Block Diagram                          | . B-4        |

| Processing and Software Requirements   | . B-4        |

| Hardware Product Selection             |              |

| Backplane and Power Supply             | . B-6        |

| Cables and Cabinet Kits                | . B-7        |

|                                        |              |

# Appendix C - Mature Q-bus Products

| Maintenance Products                    | <br>. C-1 |

|-----------------------------------------|-----------|

| BDV11 Diagnostic, Bootstrap, Terminator | <br>. C-1 |

| Specifications                          | <br>. C-1 |

| Related Documentation                   | <br>. C-2 |

| Configuration                           | <br>. C-2 |

| DLV11-F Asynchronous Line Interface     | <br>. C-9 |

| Specifications                          | <br>. C-9 |

| Related Documentation                   | <br>. C-9 |

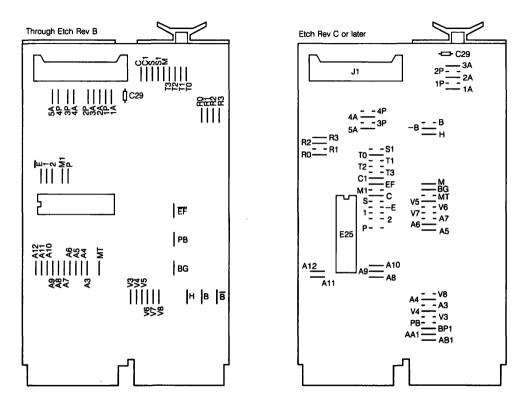

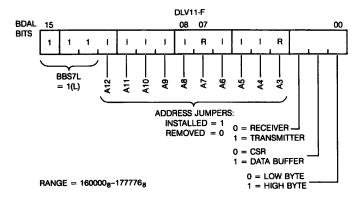

| Configuration                           | <br>. C-9 |

| Cables                                  | <br>C-16  |

| KD11-HA LSI-11/2 Microcomputer                   | C-17 |

|--------------------------------------------------|------|

| Specifications                                   | C-17 |

| Related Documentation                            | C-17 |

| Configuration                                    |      |

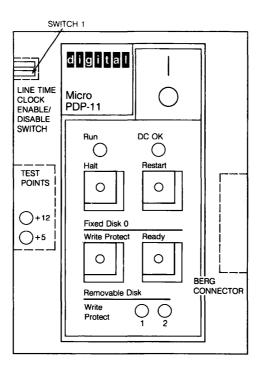

| VT103 LSI-11 Video Terminal                      | C-19 |

| Specifications                                   |      |

| Related Documentation                            | C-21 |

| Configuration                                    | C-21 |

| Cables and Connectors                            |      |

| Obsolete or Replaced Products                    |      |

| AAV11-A Digital-to-Analog Converter              | C-22 |

| Related Documentation                            | C-22 |

| ADV11-A Analog-to-Digital Converter              | C-22 |

| Related Documentation                            | C-23 |

| DRV11-B Direct Memory Access Interface           | C-23 |

| Related Documentation                            |      |

| KD11-F LSI-11 Microcomputer                      |      |

| Related Documentation                            |      |

| KPV11 Powerfail/Linetime Clock/Terminator Option | C-24 |

| Related Documentation                            | C-24 |

| KWV11-A Programmable Realtime Clock              | C-24 |

| Related Documentation                            |      |

| KXT11-AA Falcon SBC-11/21 Microcomputer          |      |

| Related Documentation                            |      |

| LAV11 Printer Option                             |      |

| Related Documentation                            | C-25 |

| MRV11-AA Read-Only Memory Module                 |      |

| Related Documentation                            | C-25 |

| MRV11-BA UV PROM-RAM Memory Module               | C-26 |

| Related Documentation                            | C-26 |

| REV11-A DMA Refresh/Bootstrap/Terminator         | C-26 |

| Related Documentation                            | C-26 |

| RKV11-D Disk Drive Controller                    | C-26 |

| Related Documentation                            |      |

| RLV11 Disk Controller                            | C-27 |

| Related Documentation                            |      |

| RXV11 Floppy Disk Interface                      |      |

| Related Documentation                            | C-27 |

| VK170-CA Serial Video Module                     | C-27 |

| Related Documentation                            |      |

| VSV11 Graphics Display                           |      |

| Related Documentation                            | C-28 |

•

1. .

k

# Foreword

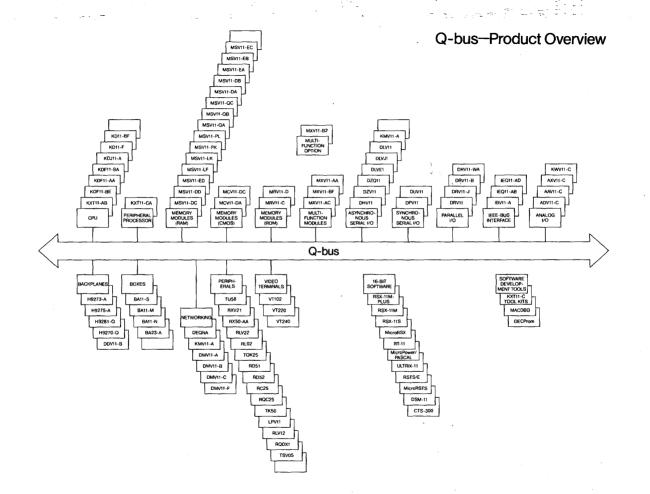

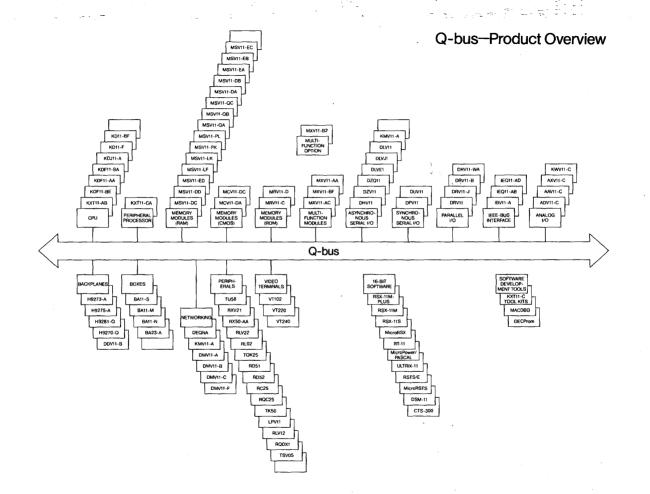

This handbook is a reference guide for board-level microcomputers, memories, interfaces, and peripheral options that can be installed on the Q-bus. The book is divided into ten parts (listed below) and three appendixes.

- Part I: Introduction

- Part II: Microcomputers

- Part III: Memories

- Part IV: Multifunction Modules

- Part V: Asynchronous Communications Interfaces

- Part VI: Synchronous Communications Interfaces

- Part VII: Analog Interfaces

- Part VIII: Parallel Interfaces

- Part IX: Peripheral Interfaces

- Part X: Backplanes, Enclosures, and Expansion Cables

Within Parts II through IX each module is discussed separately in an individual chapter. Following a brief description of the module, each chapter includes specification, configuration, and (where appropriate) cabling and cabinet kit information. The appendixes provide related information on configuration of a Q-bus system, on modules that are no longer marketed, and on chip kits.

For more information on configuring Q-bus systems including summary charts on all Q-bus module products and configuration rules, refer to the *Microcomputer Products Configuration Guide* (order number EB-27318-68).

# Part I • Introduction

# Chapter 1 • The Q-bus and Q-bus Modules

## • The Q-bus

System components, including the processor, memory, and peripherals, are interconnected and communicate with each other via the Q-bus. The form of communication is the same for all devices on the bus; instructions that communicate with memory can communicate with peripheral devices. Each device, including memory locations and peripheral device registers, is assigned an individual byte or word address on the bus.

#### Master/Slave Relationship

Communication between devices on the bus is asynchronous. A master/slave relationship exists throughout each bus transaction. At any time, there is one device that has control of the bus. This controlling device is known as the bus master. The master device controls the bus while communicating with another device, known as the slave. The bus master (typically the processor or a direct memory access [DMA] device) initiates a bus transaction. The slave device responds by acknowledging the transaction in progress and by receiving data from, or transmitting data to, the bus master. Q-bus control signals transmitted or received by the bus master or slave device must complete the sequence according to bus protocol. Table 1-1 lists signals.

The processor controls bus arbitration, determining which device becomes bus master at any given time. A typical example of this relationship is the processor, as master, fetching an instruction from memory, which is always a slave. Communication on the Q-bus is interlocked so that for certain control signals issued by the master device, there must be a response from the slave in order to complete the transfer. It is this master/slave signal protocol that makes the Q-bus asynchronous. The asynchronous operation precludes the need for synchronizing with, and waiting for, clock pulses.

#### **Device Registers and Addresses**

The Q-bus reserves the top 4 Kwords of its address space for I/O and peripheral devices. This area is known as the I/O page. Digital implements some controllers at fixed addresses within this space; other controller addresses "float," based on a particular system's configuration.

Peripheral device addresses within the I/O page are decoded by each device itself. Each peripheral includes one or more device registers, accessible under program control in exactly the same manner as memory locations. These registers (generally known as control and status registers, or CSRs) contain all the necessary information to establish communications with the device. Additional data buffer registers (DBRs) are used for temporary storage of data to be transferred into and out of the processor.

## Interrupts and Device Priority

The interrupt capability of the Q-bus allows any I/O device to temporarily suspend (or interrupt) current program execution and divert processor operation to service the requesting device. Interrupts can be caused by devices connected to the Q-bus or by actions within the CPU itself. Those interrupts that originate within the CPU are called traps and are caused by programming errors, hardware errors, special instructions, or maintenance features.

When an interrupt request is received from the bus, the processor completes execution of the present instruction, saves the program counter (PC) and processor status (PS) words on the stack and acknowledges the interrupt. The highest priority device requesting interrupt service responds by inputting its interrupt vector address to the processor. The processor uses this vector address as a pointer to two memory locations containing the starting address (PC) and processor status (PS) of the device's interrupt service routine. Program control is transferred to the service routine. Once the service routine has completed execution, control is either returned to the previously interrupted program or transferred to the service routine of the next device requesting interrupt service.

The Q-bus supports the following two methods of establishing device priority:

- Distributed arbitration priority levels are implemented on the hardware.

When devices of an equal priority level request an interrupt, priority is given to the device electrically closest to the processor.

- Position-defined arbitration priority is determined solely by electrical position on the bus. The closer a device is to the processor, the higher its priority.

## **Q-bus Addressing**

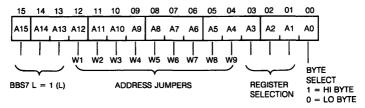

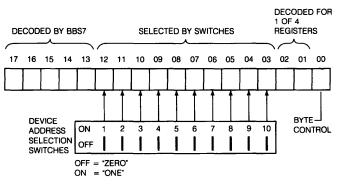

The Q-bus supports 16-, 18-, or 22-bit addresses. However, processors and peripherals having 22-bit addressing capabilities are completely PDP-11 softwareand hardware-compatible within the 18-bit or 16-bit limitation. Similarly, 18-bit addressing devices are compatible within the 16-bit limitation. This is true because of the manner in which peripheral devices are addressed within a Q-bus system. As mentioned above, all peripheral device addresses are located within the I/O page, regardless of the addressing mode of the bus. When the I/O page is addressed, the processor must assert the "bank 7 select" (BBS7) bus signal. All peripheral devices use this signal line during addressing rather than decoding the upper address bits. An asserted BBS7 signal always indicates an address in the I/O page, thereby enabling peripheral device addressing.

It should be noted, however, that memories or L/O devices that are not capable of 22-bit addressing can generate or decode erroneous addresses if they are used in systems that implement 22-bit addressing. Such devices can be used in a 22-bit system only if the size of the system is restricted to the address range of the device.

For more detailed information on the Q-bus, refer to the PDP-11 Architecture Handbook.

#### **Q-bus Signal and Pin Identification**

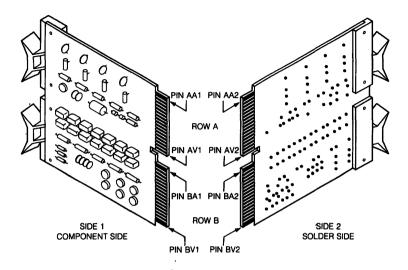

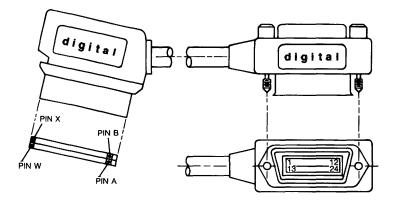

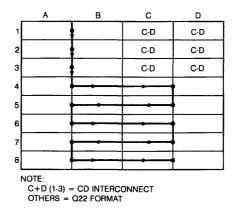

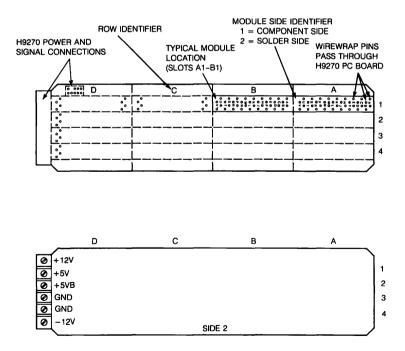

The Q-bus is based on the use of dual-height modules that plug into a 2-slot bus connector. Each slot contains 36 lines — 18 each on the component and solder sides of the circuit board — making a total of 72 contact pins carrying 72 individual signals. These contact pins are identified in the following fashion:

- The two slots are designated A or B— matching rows A and B on the module (as shown in Figure 1-1).

- The component side of the module is designated side 1 and the solder side is designated side 2.

- The 18 pins on each side of each slot (or row) are identified using letters A through V (excluding G, I, O, and Q).

An actual pin identifier has the format "slot/pin/side." For example, pin AA1 is the first pin of slot A, side 1; pin BE2 is the fifth pin of slot B, side 2; and pin BV1 is the eighteenth pin of slot B, side 1.

Table 1-1 lists the bus pins, along with the mnemonic and description of their associated signals.

Figure 1-1 • Dual-Height Module Contact Pin Identification

| Table 1-1 • Q-bus Signal and Pin Identifiers |          |                                                                                                             |

|----------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------|

| Pin                                          | Mnemonic | Description                                                                                                 |

| AA1                                          | BIRQ5    | Interrupt Request Priority Level 5                                                                          |

| AB1                                          | BIRQ6    | Interrupt Request Priority Level 6                                                                          |

| AC1                                          | BDAL16   | Extended address bit during addressing<br>protocol; memory error data line during<br>data transfer protocol |

| AD1                                          | BDAL17   | Extended address bit during addressing protocol; memory error logic enable during data transfer protocol    |

| Pin        | Mnemonic                             | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AE1        | SSPARE1<br>(Alternate +5B)           | Special Spare — not assigned or bused<br>in Digital cable or backplane assem-<br>blies; available for user connection.<br>Optionally, this pin can be used for +5<br>V battery (+5B) backup power to keep<br>critical circuits alive during power fail-<br>ures. A jumper is required on Q-bus<br>options to open (disconnect) the +5B<br>circuit in systems that use this line as<br>SSPARE1. |

| AF1        | SSPARE2                              | Special Spare — not assigned or bused<br>in Digital cable or backplane assem-<br>blies; available for user connection. In<br>the highest-priority device slot, the<br>processor can use this pin for a signal to<br>indicate its RUN state.                                                                                                                                                    |

| AH1        | SSPARE3 and SRUN<br>(simultaneously) | Special Spare — not assigned or bused<br>in Digital cable or backplane assem-<br>blies; available for user connection. An<br>alternate SRUN signal can be connected<br>in the highest-priority slot.                                                                                                                                                                                           |

| AJ1        | GND                                  | Ground – System signal ground and dc<br>return                                                                                                                                                                                                                                                                                                                                                 |

| AK1<br>AL1 | MSPAREA<br>MSPAREB                   | Maintenance Spares – normally con-<br>nected together on the backplane at<br>each option location (not a bused con-<br>nection)                                                                                                                                                                                                                                                                |

| AM1        | GND                                  | Ground – System signal ground and dc return                                                                                                                                                                                                                                                                                                                                                    |

,

Table 1-1 • Q-bus Signal and Pin Identifiers (Cont.)

| Pin | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN1 | BDMR     | Direct Memory Access (DMA) Request<br>— A device asserts this signal to request<br>bus mastership. The processor arbi-<br>trates bus mastership between itself and<br>all DMA devices on the bus. If the<br>processor is not bus master (it has com-<br>pleted a bus cycle and BSYNC is not<br>being asserted by the processor), it<br>grants bus mastership to the requesting<br>device by asserting BDMGO. The device<br>responds by negating BDMR and<br>asserting BSACK.                   |

| AP1 | BHALT    | Processor Halt — When BHALT is<br>asserted for at least 25 microseconds,<br>the processor services the halt interrupt<br>and responds by halting normal pro-<br>gram execution. External interrupts are<br>ignored but memory refresh interrupts<br>in the LSI-11 are enabled if W4 on the<br>M7264 and M7264-YA processor mod-<br>ules is removed and DMA request/grant<br>sequences are enabled. The processor<br>executes the ODT microcode and the<br>console device operation is invoked. |

| AR1 | BREF     | Memory Refresh — Asserted by a DMA<br>device. This signal forces all dynamic<br>MOS memory units requiring bus<br>refresh signals to be activated for each<br>BSYNC/BDIN bus transaction. It is also<br>used as a control signal for block mode<br>DMA.                                                                                                                                                                                                                                        |

|     |          | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 1-1 • O-bus Signal and Pin Identifiers (Cont.)

The user must avoid multiple DMA data transfers (burst or "hog" mode) that could delay refresh operation if using DMA refresh. Complete refresh cycles must occur once every 1.6 milliseconds if required.

|                          | Table 1-1         Q-bus Signal and Pin Identifiers (Cont.)           |                                                                                                                                                                                                                                                                                                                                        |  |

|--------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                      | Mnemonic                                                             | Description                                                                                                                                                                                                                                                                                                                            |  |

| AS1                      | + 12B or +5B                                                         | + 12 Vdc or + 5 V Battery Backup<br>Power to keep critical circuits alive dur-<br>ing power failures. This signal is not<br>bused to BS1 in all Digital backplanes.<br>A jumper is required on all Q-bus<br>options to open (disconnect) the<br>backup circuit from the bus in systems<br>that use this line at the alternate voltage. |  |

| AT1                      | GND                                                                  | Ground – System signal ground and dc<br>return                                                                                                                                                                                                                                                                                         |  |

| AU1                      | PSPARE1                                                              | Spare — not assigned; customer usage<br>not recommended. Prevents damage<br>when modules are inserted upside<br>down.                                                                                                                                                                                                                  |  |

| AV1                      | +5B                                                                  | +5 V Battery Power — Secondary +5<br>V power connection. Battery power can<br>be used with certain devices.                                                                                                                                                                                                                            |  |

| BA1                      | BDCOK                                                                | dc Power OK – Power supply-generated<br>signal that is asserted when there is suf-<br>ficient dc voltage available to sustain<br>reliable system operation.                                                                                                                                                                            |  |

| BB1                      | ВРОК                                                                 | Power OK — Asserted by the power sup-<br>ply 70 milliseconds after BDCOK is<br>negated when ac power drops below<br>the value required to sustain power<br>(approximately 75 percent of nominal).<br>When BPOK is negated during proces-<br>sor operation, a powerfail trap sequence<br>is initiated.                                  |  |

| BC1<br>BD1<br>BE1<br>BF1 | SSPARE4/BDAL18<br>SSPARE5/BDAL19<br>SSPARE6/BDAL20<br>SSPARE7/BDAL21 | Special Spares (in 18-bit Q-bus) – Not<br>assigned. Bused in 22-bit cable and<br>backplane assemblies; available for user<br>connection. (Caution: These pins may<br>be used as test points by Digital in some<br>options.)                                                                                                            |  |

|                          |                                                                      | Address Lines <21:18> (in 22-bit Q-<br>bus). Currently not used during data<br>transfers.                                                                                                                                                                                                                                              |  |

| Table 1-1 • Q-bus Signal and Pin Identifiers (Cont.) |                    |                                                                                                                                                                                                                              |

|------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                                                  | Mnemonic           | Description                                                                                                                                                                                                                  |

| BH1                                                  | SSPARE8            | Special Spare – Not assigned or bused<br>in Digital cable and backplane assem-<br>blies; available for user connection.                                                                                                      |

| BJ1                                                  | GND                | Ground – System signal ground and dc return                                                                                                                                                                                  |

| BK1<br>BL1                                           | MSPAREB<br>MSPAREB | Maintenance Spares – Normally con-<br>nected together on the backplane at<br>each option location (not a bused con-<br>nection).                                                                                             |

| BM1                                                  | GND                | Ground – System signal ground and dc return                                                                                                                                                                                  |

| BN1                                                  | BSACK              | This signal is asserted by a DMA device<br>in response to the processor's BDMGO<br>signal, indicating that the DMA is bus<br>master.                                                                                         |

| BP1                                                  | BIRQ7              | Interrupt Request Priority Level 7                                                                                                                                                                                           |

| BR1                                                  | BEVNT              | External Event Interrupt Request —<br>When this signal is asserted, the proces-<br>sor responds by entering a service rou-<br>tine via vector address 100. A typical<br>use of this signal is a linetime clock<br>interrupt. |

| BS1                                                  | + 12B              | + 12 Vdc Battery Backup Power—not<br>bused to AS1 in all Digital backplanes                                                                                                                                                  |

| BT1                                                  | GND                | Ground – System signal ground and dc return                                                                                                                                                                                  |

| BU1                                                  | PSPARE2            | Spare — Not assigned; customer usage is<br>not recommended. If a module is using<br>- 12 V (on pin AB2) and if the module<br>is accidentally inserted upside down in<br>the backplane, - 12 Vdc appears on<br>this pin.      |

| BV1                                                  | +5V                | + 5 V Power – Normal + 5 Vdc system                                                                                                                                                                                          |

|                                                      |                    | power                                                                                                                                                                                                                        |

| AA2                                                  | +5V                | + 5 V Power – Normal + 5 Vdc system<br>power                                                                                                                                                                                 |

|                                                      |                    |                                                                                                                                                                                                                              |

| Table 1-1         Q-bus Signal and Pin Identifiers (Cont.) |          |                                                                              |  |

|------------------------------------------------------------|----------|------------------------------------------------------------------------------|--|

| Pin                                                        | Mnemonic | Description                                                                  |  |

| AB2                                                        | – 12V    | – 12 V Power – Optional – 12 Vdc<br>power for devices requiring this voltage |  |

Note

LSI-11 modules that require negative voltages contain an inverter circuit (on the module) which generates the required voltages. Hence, -12 V power is not required with Digital-supplied options.

| GND   | Ground – System signal ground and dc return                                                                                                                                                                                                                                                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| + 12V | + 12 V Power – 12 Vdc system power                                                                                                                                                                                                                                                                                                      |

| BDOUT | Data Output — When asserted, BDOUT<br>implies that valid data is available on<br>BDAL <0:15> and that an output<br>transfer, from the bus master device, is<br>taking place. BDOUT is deskewed with<br>respect to data on the bus. The slave<br>device responding to the BDOUT signal<br>must assert BRPLY to complete the<br>transfer. |

| BRPLY | Reply – BRPLY is asserted in response to<br>BDIN or BDOUT and during IAK trans-<br>actions. It is generated by a slave device<br>to indicate that it has placed its data on<br>the BDAL bus or that it has accepted<br>output data from the bus.                                                                                        |

| BDIN  | Data Input – Used for two types of bus operations.                                                                                                                                                                                                                                                                                      |

|       | When asserted at the same time as<br>BSYNC, BDIN signals an input transfer<br>to the current bus master and requires a<br>response (BRPLY). The master device<br>must deskew input data from BRPLY.                                                                                                                                     |

|       | When asserted without BSYNC, BDIN signals an interrupt operation.                                                                                                                                                                                                                                                                       |

|       | + 12V<br>BDOUT<br>BRPLY                                                                                                                                                                                                                                                                                                                 |

| Table 1-1 • Q-bus Signal and Pin Identifiers (Cont.) |                |                                                                                                                                                                                                                                                                                                                        |  |

|------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                                                  | Mnemonic       | Description                                                                                                                                                                                                                                                                                                            |  |

| AJ2                                                  | BSYNC          | Synchronize — BSYNC is asserted by the<br>bus master device to indicate that it has<br>placed an address on BDAL<0: 17>.<br>The transfer continues until BSYNC is<br>negated.                                                                                                                                          |  |

| AK2                                                  | BWTBT          | Write/Byte—BWTBT is used in two<br>ways to control a bus cycle:                                                                                                                                                                                                                                                        |  |

|                                                      |                | It is asserted at the leading edge of<br>BSYNC to indicate that an output<br>sequence (rather than an input<br>sequence) is to follow.                                                                                                                                                                                 |  |

|                                                      |                | It is asserted during BDOUT (in a DATOB bus cycle) for byte addressing.                                                                                                                                                                                                                                                |  |

| AL2                                                  | BIRQ4          | Interrupt Request Priority Level 4 – A<br>level 4 device asserts this signal when its<br>interrupt enable and interrupt request<br>flip-flops are set. If PS<7> is 0, the<br>processor acknowledges the request by<br>asserting BDIN and BIAKO.                                                                        |  |

| AM2<br>AN2                                           | BIAKI<br>BIAKO | Interrupt Acknowledge — In accor-<br>dance with interrupt protocol, the<br>processor asserts BIAKO to acknowl-<br>edge receipt of an interrupt. The bus<br>transmits this to BIAKI of the device<br>electrically closest to the processor. This<br>device accepts the interrupt acknowl-<br>edge under two conditions: |  |

|                                                      |                | (1) The device requested the bus by asserting BIRQx, and (2) the device has the highest-priority interrupt request on the bus at that time.                                                                                                                                                                            |  |

|                                                      |                | If these conditions are not met, the<br>device asserts BIAKO to the next device<br>on the bus. This process continues in a<br>daisychain fashion until the device with<br>the highest interrupt priority receives<br>the interrupt acknowledge signal.                                                                 |  |

Table 1-1 • O-bus Signal and Pin Identifiers (Cont.)

|                        | Table 1-1 • Q-bus | s Signal and Pin Identifiers (Cont.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                    | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AP2                    | BBS7              | Bank 7 Select — The bus master asserts<br>this signal to reference the I/O page<br>(including that portion of the I/O page<br>reserved for nonexistent memory). The<br>address in BDAL <0:12> is the address<br>within the I/O page.                                                                                                                                                                                                                                                                                                                            |

| AR2 BDMGI<br>AS2 BDMGO |                   | Direct Memory Access Grant — The<br>bus arbitrator asserts this signal to grant<br>bus mastership to a requesting device,<br>according to bus mastership protocol.<br>The signal is passed from the arbitrator<br>(as BDMGO), through the bus, to<br>BDMGI of the device electrically closest<br>to the processor. This device accepts the<br>grant only if it requested the bus by<br>asserting BDMR. If not, the device<br>passes the grant to the next device on<br>the bus. The process continues until the<br>requesting device acknowledges the<br>grant. |

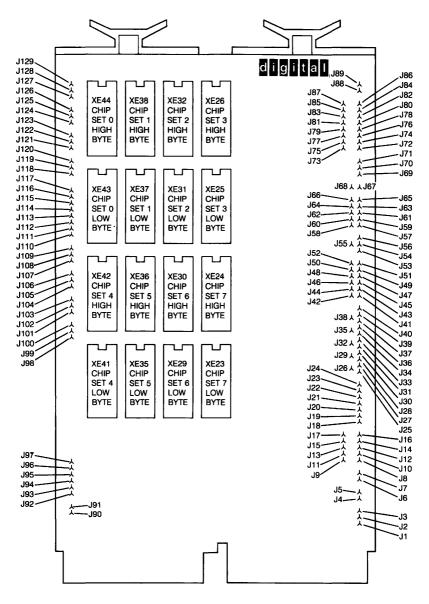

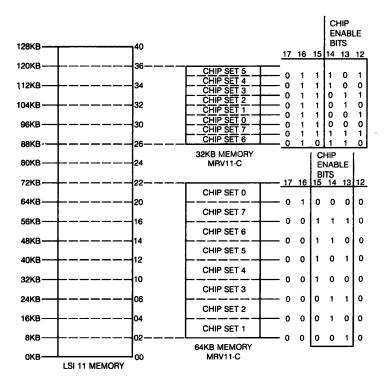

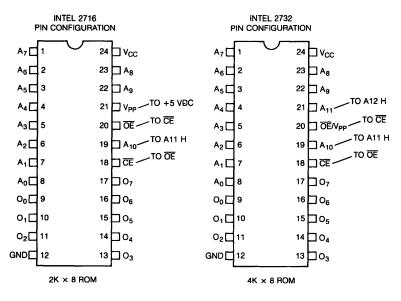

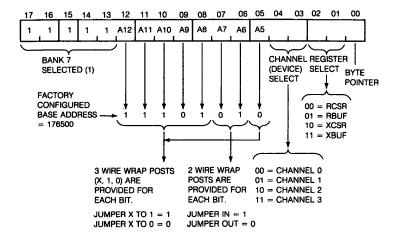

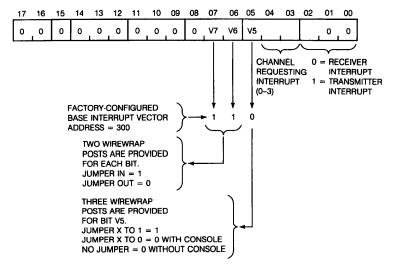

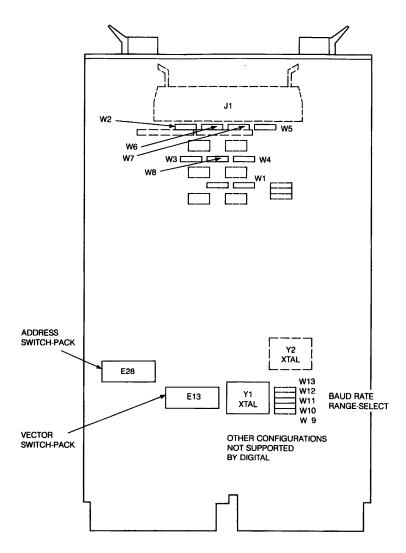

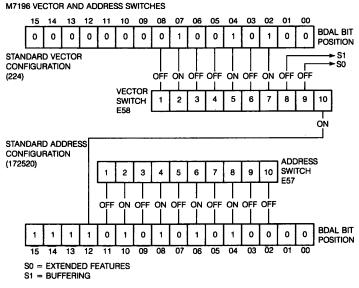

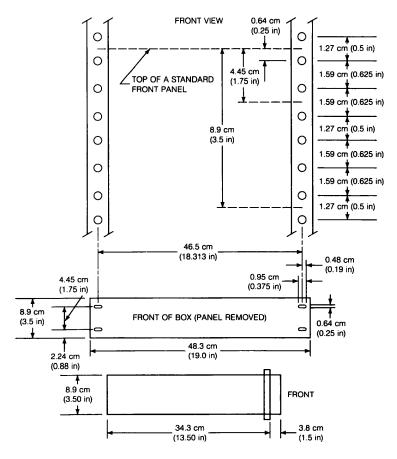

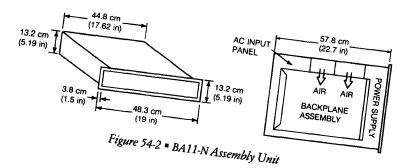

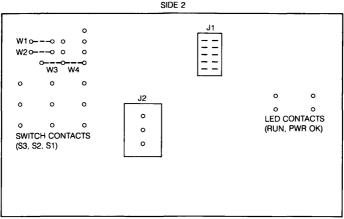

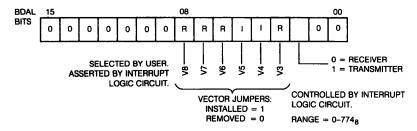

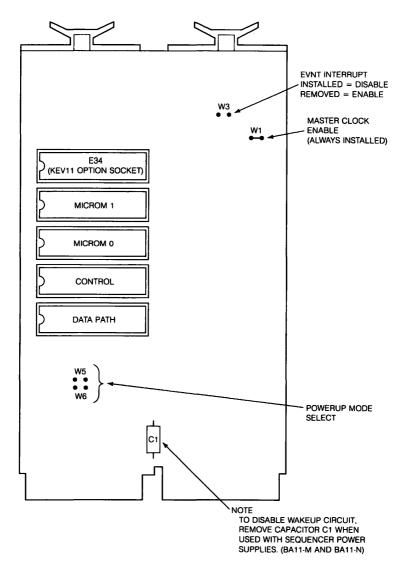

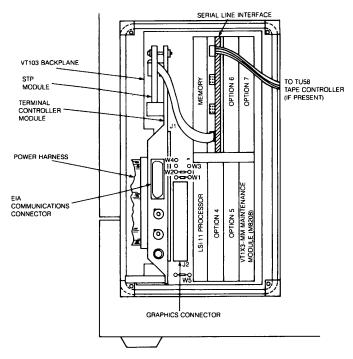

| AT2                    | BINIT             | Initialize — This signal is used for system<br>reset. When BINIT is asserted, all<br>devices on the bus are required to<br>return to a known, initial state (i.e., all<br>registers and logic are set to zero). Any<br>exceptions should be completely docu-<br>mented in programming and engineer-<br>ing specifications for the device.                                                                                                                                                                                                                       |