EK-MRV1D-UG-001

# MRV11-D Universal PROM Module

**User Guide**

EK-MRV1D-UG-001

# MRV11-D Universal PROM Module

**User Guide**

Prepared by Educational Services of Digital Equipment Corporation

First Edition, May 1983

Copyright <sup>©</sup> 1983 by Digital Equipment Corporation. All Rights Reserved. Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts 01754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

UniPak is a trademark of Data I/O Corporation.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| ******  | •         |              |                |

|---------|-----------|--------------|----------------|

| digital | DECwriter | P/OS         | RT             |

| DEC     | DIGITAL   | Professional | UNIBUS         |

| DECmate | LA        | Rainbow      | VAX            |

| DECnet  | LSI       | RSTS         | VMS            |

| DECUS   | MASSBUS   | RSX          | VT             |

|         | PDP       |              | Work Processor |

# CONTENTS

# CHAPTER 1 SYSTEM DESCRIPTION

| 1.1   | General                                   | 1 |

|-------|-------------------------------------------|---|

| 1.2   | Features                                  | 2 |

| 1.3   | Configuration                             | 2 |

| 1.4   |                                           | 4 |

| 1.4.1 |                                           | 4 |

| 1.4.2 | Page Mode Addressing                      | 5 |

| 1.4.3 |                                           | 5 |

| 1.5   | Physical and Environmental Specifications | 7 |

| 1.5.1 | Physical Specifications                   | 7 |

| 1.5.2 | Temperature                               | 8 |

| 1.5.3 | Relative Humidity                         | 9 |

| 1.5.4 | Altitude                                  | 9 |

| 1.5.5 | Sea Level Operating Airflow               | 9 |

| 1.5.6 |                                           | 9 |

| 1.6   | Electrical Specifications                 | 9 |

| 1.6.1 | Power                                     | 9 |

| 1.6.2 | Technology 1                              | 0 |

|       |                                           |   |

# CHAPTER 2 FUNCTIONAL DESCRIPTION

| 2.1 | Introduction   | 11 |

|-----|----------------|----|

| 2.2 | Direct Mode    |    |

| 2.3 | Page Mode      | 14 |

| 2.4 | Bootstrap Mode | 16 |

# CHAPTER 3 JUMPER CONFIGURATIONS

| 3.1   | Introduction 21                       |

|-------|---------------------------------------|

| 3.2   | Configuration 22                      |

| 3.2.1 | Installing MXV11-B2 ROM on MRV11-D 22 |

| 3.3   | PROM Sizes and Pinouts 37             |

# CHAPTER 4 PROGRAMMING

| 4.1 | Introduction                                      | 39 |

|-----|---------------------------------------------------|----|

| 4.2 | Executing Windowed Programs                       | 39 |

| 4.3 | Transferring Application Programs from ROM to RAM | 41 |

# CHAPTER 5 PROGRAMMING THE ARRAY DECODER

| 5.1 | Introduction                 | 43 |

|-----|------------------------------|----|

| 5.2 | Decoder Programming Hardware | 43 |

| 5.3 | Array Decoder                | 44 |

| 5.4 | Guidelines and Restrictions  | 47 |

| 5.5 | Designing an Array Decoder   | 47 |

# CHAPTER 6 MAINTENANCE

| 6.1 | Introduction    | 57 |

|-----|-----------------|----|

| 6.2 | Troubleshooting | 57 |

| 6.3 | Console ODT     | 58 |

# APPENDIX A MODULE CONFIGURATION

# FIGURES

| 1-1 | Page Mode Addressing                                 | . 6  |

|-----|------------------------------------------------------|------|

| 1-2 | Page Mode Bootstrap                                  | . 8  |

| 2-1 | Direct Mode Block Diagram                            | . 11 |

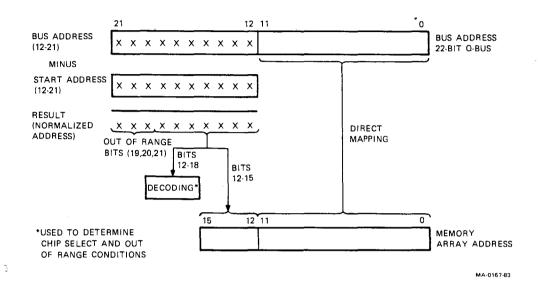

| 2-2 | Direct Mode Addressing                               | . 13 |

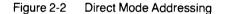

| 2-3 | Chip Select and Out-of-Range Functions (Direct Mode) | . 13 |

| 2-4 | Page Mode Block Diagram                              | . 15 |

| 2-5 | Bootstrap Mode Block Diagram                         | . 17 |

| 2-6 | Bootstrap Access to Window 0 (I/O Page)              | . 18 |

| 2-7 | Bootstrap Access to Window 1 (I/O Page)              | . 19 |

| 3-1 | MRV11-D Chip Set Locations                           | . 21 |

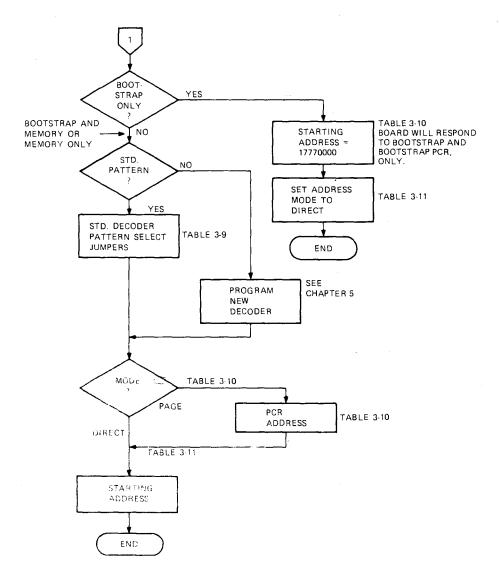

| 3-2 | Jumper Configuration Flowchart                       | . 23 |

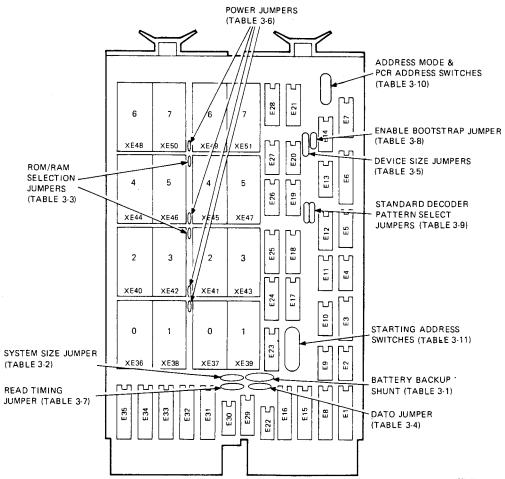

| 3-3 | Jumper and Switch Locations                          | . 25 |

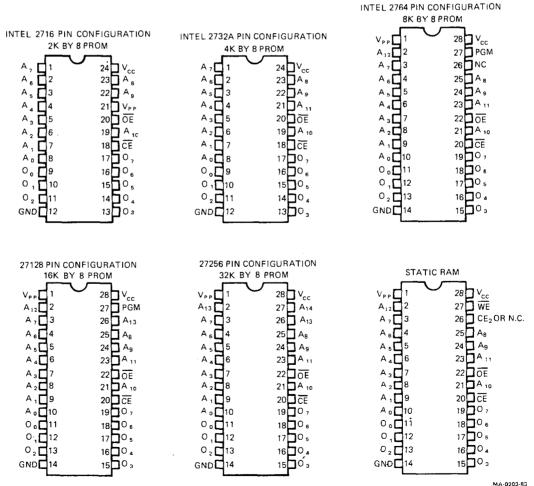

| 3-4 | PROM Sizes and Types                                 | . 37 |

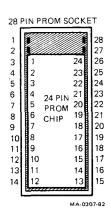

| 3-5 | Insertion of 24-Pin PROM Chips                       | . 38 |

| 4-1 | JSR and JMP Control Routines for Window Mapping      | . 40 |

| 4-2 | Bootstrap Loader for Standalone Programs in RT-11    |      |

|     | .SAV Format                                          | . 41 |

| 5-1 | 2K Array Decoder                                     | . 45 |

| 5-2 | Pattern Select                                       | . 45 |

| 5-3 | Pin Designations for Array Decoder                   | . 45 |

| 5-4 | Direct Mode Format for Array Decoder                 | . 49 |

| 5-5 | Page Mode Format for Array Decoder                   |      |

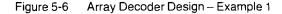

| 5-6 | Array Decoder Design – Example 1                     | . 51 |

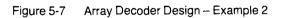

| 5-7 | Array Decoder Design - Example 2                     | . 53 |

| 5-8 | Array Decoder Design – Example 3                     |      |

| A-1 | Module Configuration                                 | . 64 |

# CONTENTS v

# TABLES

| 1-1  | Storage Capacity Per ROM Chip Size and Number            |

|------|----------------------------------------------------------|

|      | of Chips 3                                               |

| 1-2  | Typical EPROMS 4                                         |

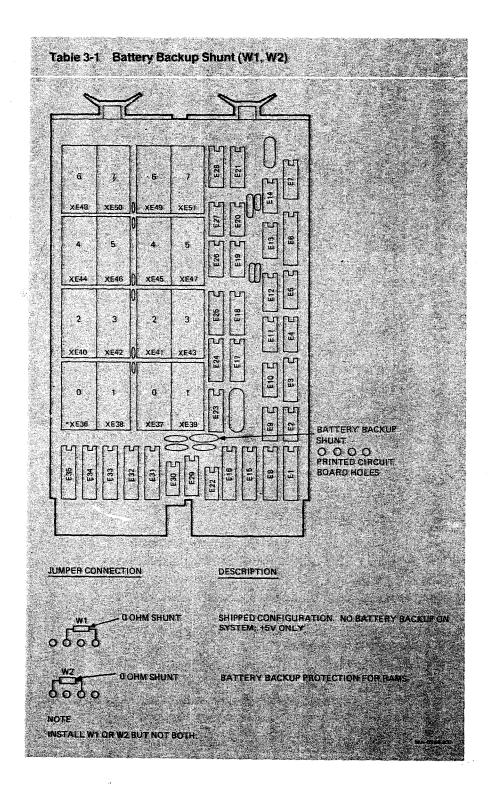

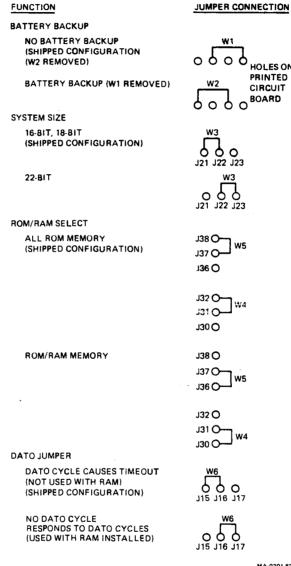

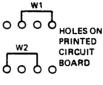

| 3-1  | Battery Backup Shunt (W1, W2) 26                         |

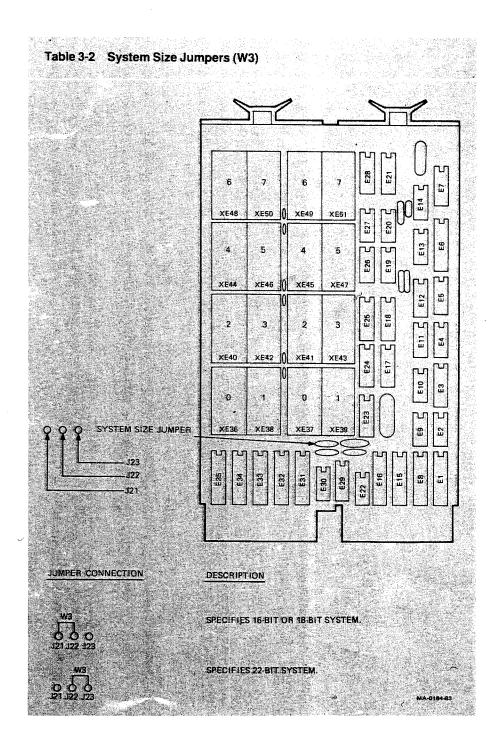

| 3-2  | System Size Jumpers (W3) 27                              |

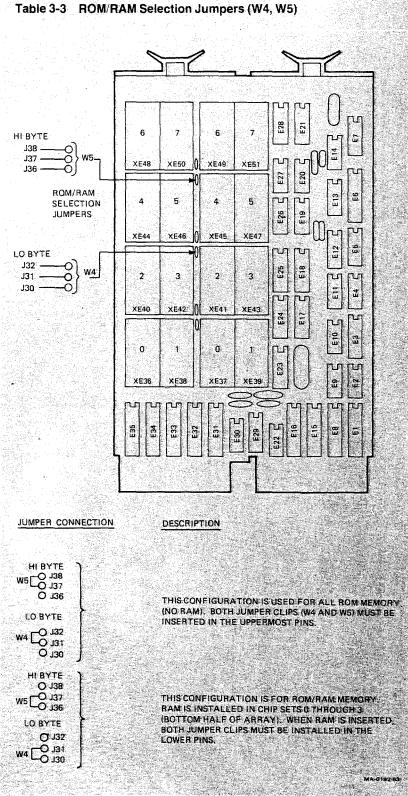

| 3-3  | ROM/RAM Selection Jumpers (W4, W5) 28                    |

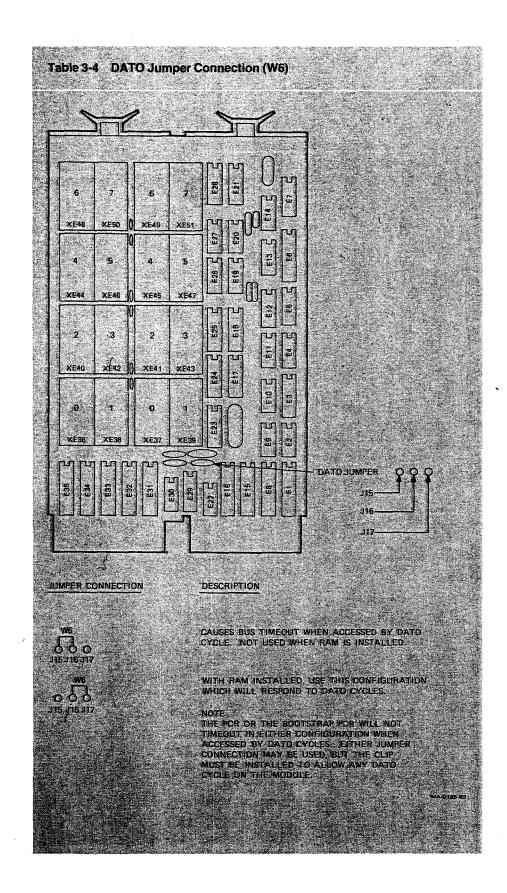

| 3-4  | DATO Jumper Connection (W6) 29                           |

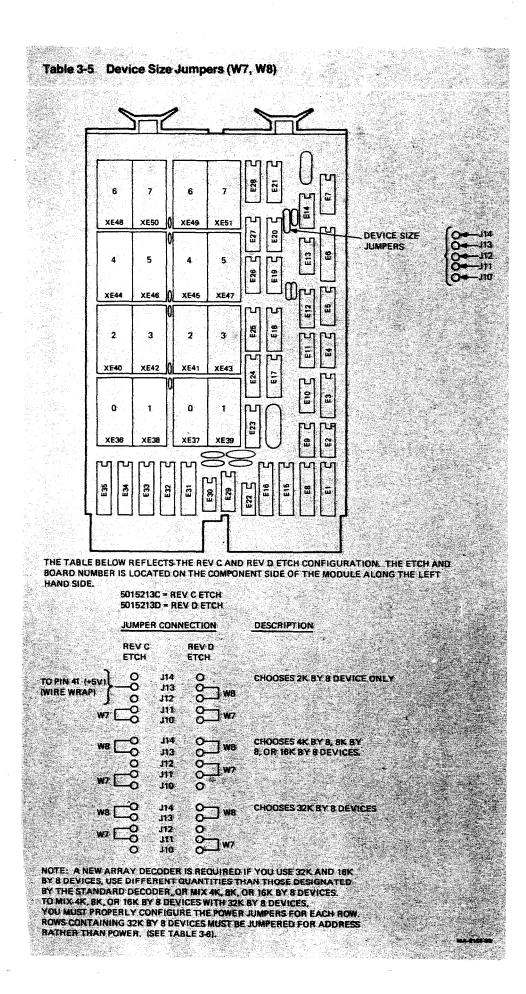

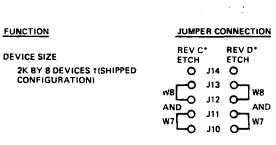

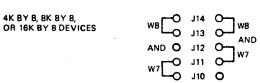

| 3-5  | Device Size Jumpers (W7, W8) 30                          |

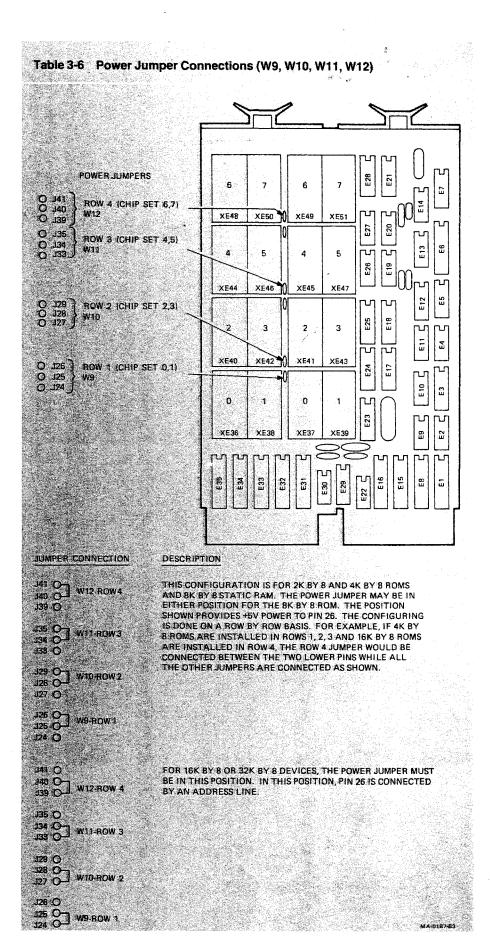

| 3-6  | Power Jumper Connections (W9, W10, W11, W12) 31          |

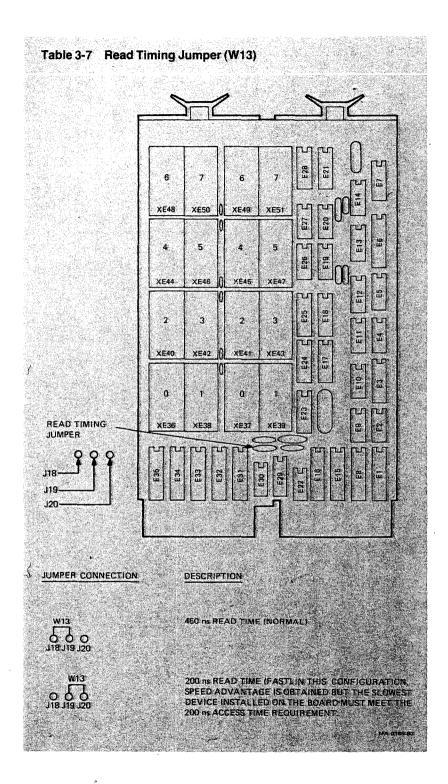

| 3-7  | Read Timing Jumper (W13) 32                              |

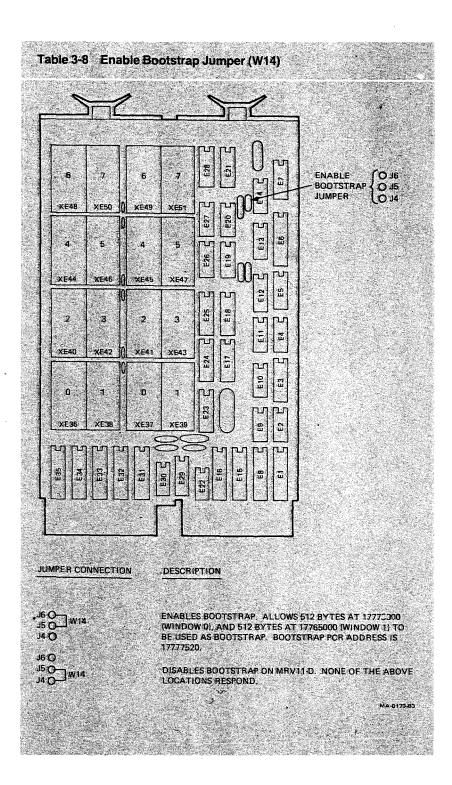

| 3-8  | Enable Bootstrap Jumper (W14) 33                         |

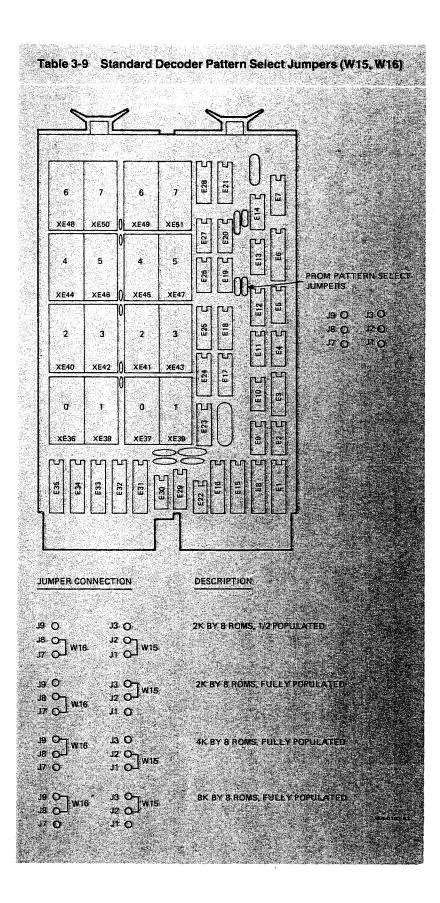

| 3-9  | Standard Decoder Pattern Select Jumpers                  |

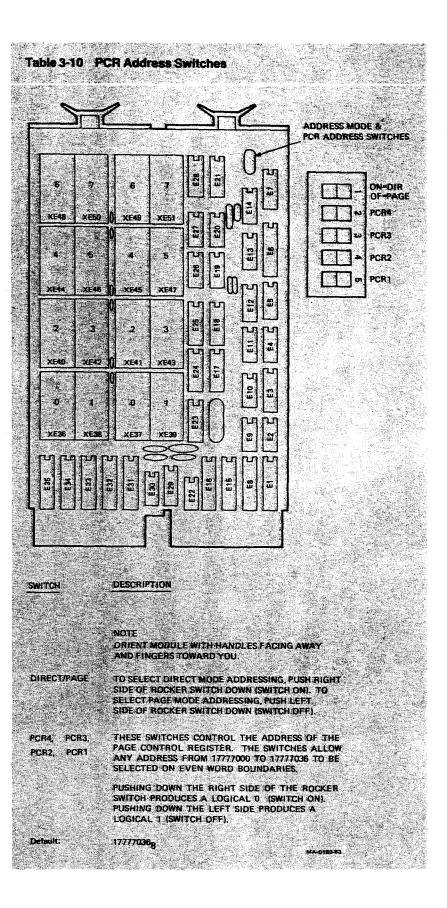

| 3-10 | PCR Address Switches 35                                  |

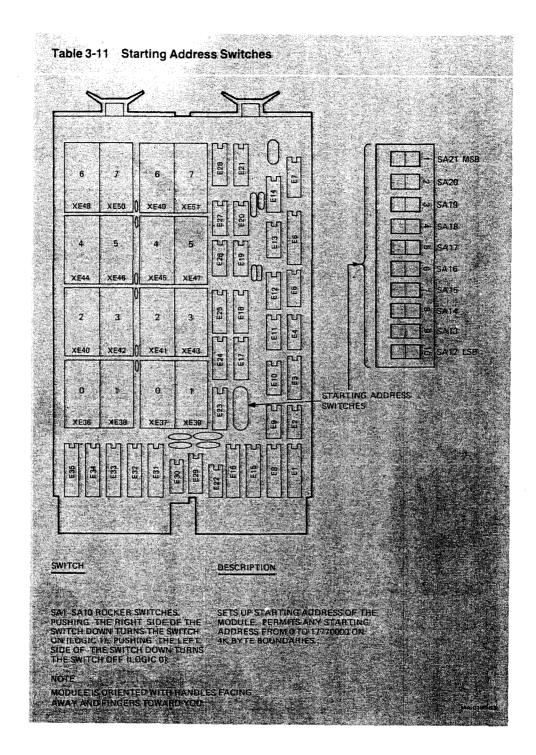

| 3-11 | Starting Address Switches 36                             |

| 5-1  | Array Decoder Programming Hardware                       |

| 5-2  | Chip Select and Range Bits for Fully Populated Module 46 |

| 6-1  | Console ODT Commands 58                                  |

| 6-2  | Console ODT States and Valid Input Characters 59         |

# SYSTEM DESCRIPTION

#### 1.1 GENERAL

The MRV11-D is a universal, programmable read only memory (PROM) module. It is a flexible, high-density, dual-size module for 16-, 18-, or 22-bit Q-bus systems. The MRV11-D can be used in PDP-11/02, PDP-11/03, SBC-11/21 single board computer, PDP-11/23A, or PDP-11/23B systems. The module contains sixteen 28-pin sockets that accept static random access memory (RAM) and a variety of user-supplied ROMs, such as fusible link PROMs, ultraviolet erasable (UV E)PROMs, and masked ROMs. It accepts several device densities up to and including 32K by 8. With sixteen 32K devices, memory capacity is 512 kilobytes.

The contents of the module can be accessed in one of two modes, direct mode addressing or page mode addressing, which employs a window-mapping technique.

Direct mode addressing provides immediate access to all memory locations on the module. Page mode addressing, or window mapping, provides two 2-kilobyte windows in bus address space that map a 2-kilobyte page each of the memory array. The page that is viewed or accessed through each window (2 kilobytes per window) can be varied under program control through a page control register (PCR). The PCR must be written with the desired page number before the access. A bootstrap feature allows 64 kilobytes of bootstrap code.

1

#### 2 SYSTEM DESCRIPTION

### 1.2 FEATURES

The MRV11-D has the following features.

- Full 22-bit Q-bus addressing capability as well as 16- or 18-bit Q-bus addressing

- Four-kilobyte starting address boundaries

- Direct mode or page mode addressing

- MXV11-B2 bootstrap PROM option

- Sixteen different page control register locations

- Bootstrap page control register

- Standard bootstrap

- Bootstrap disable

- ROM sockets that house 2K, 4K, 8K, 16K, or 32K by 8 ROMs as well as static RAM

- Normal or optional high-performance timing

- Optional battery backup for static RAM

- Capacity of 0 to 0.5 megabytes

## **1.3 CONFIGURATION**

The MRV11-D contains 41 jumper posts, 2 switch packs, and 16 memory chip sockets. The user can configure desired features by connecting the jumper posts with the 13 jumper clips that are supplied with the module. The module is shipped from the factory with all jumper clips installed.

The following features can be configured by means of the jumper clips or by the two switch packs on the module.

Page/direct mode addressing Location of PCR Bootstrap enable/disable Use of multiple MRV11-D modules Normal/high-performance timing Switch-selectable starting address Allow/inhibit DATO bus cycle Memory array size and response pattern Small system/large system Static RAM The size of the memory array is determined by the size of the memory devices installed. The MRV11-D is shipped with no memory devices installed, so the user must provide and install them.

Digital Equipment Corporation supplies a standard array decoder on the module that is a preprogrammed fusible link PROM. In the basic configuration with this array decoder installed, all memory chips must be the same size (2K by 8, 4K by 8, or 8K by 8). The pin configuration of the chips must conform to the Joint Electron Device Engineering Council (JEDEC) standard pinout for byte-wide devices. The following four patterns are available with the standard array decoder supplied by Digital.

2K by 8 half-populated (socket sets 0–3) 2K by 8 fully populated 4K by 8 fully populated 8K by 8 fully populated

The user can populate the module with many other combinations of devices by programming his own array decoder. (See Chapter 5.) There are certain device mixtures that are restricted. Chapters 3 and 5 describe these restrictions.

The user can also configure a system with more than one MRV11-D. Table 1-1 shows the storage capacity per module as a function of device size and number of device chips. This table lists the capacities for configurations with similar device sizes. It does not account for the configurations with mixed device sizes that can be used if the customer programs his own array decoder.

Table 1-2 lists typical UV PROMs and PROMs that can be installed on the MRV11-D. Other UV PROMs or PROMs that conform to the JEDEC pinout can also be used.

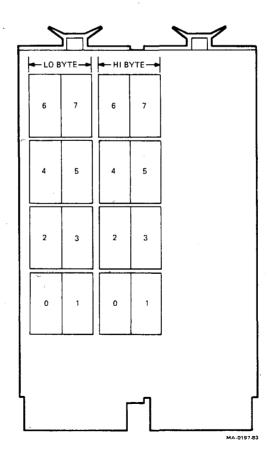

Chapter 3 describes how to configure the MRV11-D. Figure 3-1 shows the physical location of the 16 memory chip sockets. They are divided into eight chip sets, chip set 0 through chip set 7. Each chip set is composed of a low byte and a high byte.

|           |           |             | 29 C. A. A. | area Tres dae | Contract of the second |

|-----------|-----------|-------------|-------------|---------------|------------------------|

| Number of | (Capacity | Measured in | KIIODYTES)  |               |                        |

| Chips     |           |             |             |               |                        |

| Installed | 2K Dy 8   | 🌙 4K by 8   | 8K by 8     | 16K by 8      | 32K by 8               |

|           |           |             |             |               |                        |

| 2         | - 4       | 8           | 16          | 32            | 64                     |

| 4         | 8         | 16          | 32          | 64            | 128                    |

| 6         | 12        | 24          | 48          | .96           | 192                    |

| 8         | 16        | 32          | 64          | 128           | 256                    |

| 10        | 20        | 40          | 80          | 160           | 320                    |

| 12        | 24        | 48          | 96          | 192           | 384                    |

| 14        | 28        | 56          | 112         | 224 -         | 448                    |

| 16        | 32        | 64          | 128         | 256           | 512                    |

| Table 1-2 Typical EPROMs |                    |                              |           |

|--------------------------|--------------------|------------------------------|-----------|

| ŪV PROMs                 | Chip Array<br>Size | Maximum Memory<br>Array Size |           |

| Intel 2716               | 2K by 8            | , 32 kilobytes               |           |

| Intel 2732               | 4K by 8            | 64 kilobytes                 | - 12 A- 5 |

| Intel 2764               | 8K by 8            | 128 kilobytes                |           |

| Intel 27128              | 16K by 8           | 256 kilobytes                |           |

| Masked ROMS              |                    |                              |           |

| Mostek MK3700            | 8K by 8            | 128 kilobytes                |           |

| NCFI23128                | 16K by 8           | 256 kilobytes                |           |

| NEC 23256                | 32K by 8           | 512 kilobytes                |           |

| National 52364           | 8K.by8             | 128 kilobytes                |           |

| Signetics 23128          | 16K by 8           | 256 kilobytes                |           |

| Synertek 2365            | 8K by 8            | 128 kilaöytes                |           |

| Synertek 2365A           | 8K by 8            | 128 kilobytes                |           |

| Synertek 2316B           | 2K by 8            | 32 kilobytes                 |           |

| Synertek 2333-3          | 4K by 8            | 64 kilobytes                 |           |

### 1.4 ADDRESSING MODES

The MRV11-D can be configured to operate in one of two addressing modes, page mode and direct mode. Configuration is accomplished by setting a hardware switch on the module and is not variable under program control.

# 1.4.1 Direct Address Mode

In direct address mode, each memory location on the MRV11-D has a corresponding location on the system bus. The number of system bus address locations allocated to the module is equal to the module's configured capacity. For example, an MRV11-D that is fully populated (16 devices) with 4K by 8 PROMs (64 kilobytes) corresponds to 64 kilobytes of the system bus. The starting address of the module and the array decoder pattern determine the boundaries of the module's address range.

The starting address of the MRV11-D can be placed on any 4-kilobyte boundary from address  $0_8$  to 17770000<sub>8</sub>. However, the module's main memory does not respond to any I/O page accesses, even if the address range overlaps the I/O page. Only the bootstrap areas and the bootstrap PCR, if enabled, respond in the I/O page under direct mode addressing.

### 1.4.2 Page Mode Addressing

Page mode addressing is a virtual addressing scheme that extends the addressing capability of the system bus. A 4-kilobyte segment of the system bus and an I/O register called the page control register (PCR) are assigned to the MRV11-D. The MRV11-D's starting address determines the beginning of the module's portion of the system bus. The user configures the PCR address to 1 of 16 locations in the I/O section of the system bus.

The MRV11-D's portion of the system bus is further divided into two sections called windows. Each window is 2 kilobytes long and can contain any 2-kilobyte page of data on the module. The two pages of data that are currently available to the system have their page numbers stored, one in each byte of the PCR. To move a different page into the window, simply change the contents of the corresponding PCR byte to the number of the desired page.

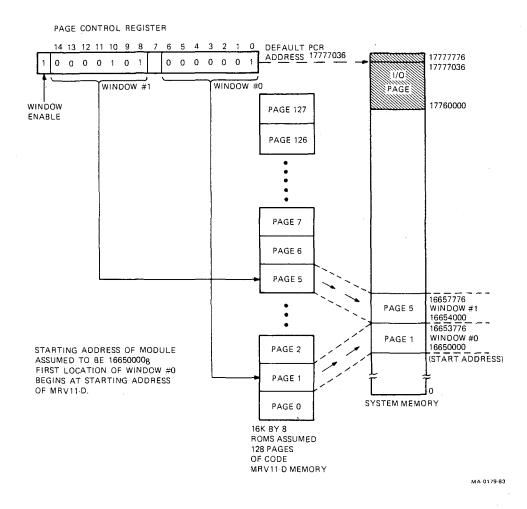

Figure 1-1 displays the page mode function. The MRV11-D has been assigned to the bus addresses from 166500008 through 166577768. Its PCR is at 177770368. In this example page 1 appears in window 0 and page 5 appears in window 1. Notice that the low byte of the PCR contains a 1 and the high byte contains a 5, controlling windows 0 and 1 respectively.

Bits 7 and 15 are not part of the page numbers. Bit 7 is unused and bit 15 is the window control bit. When bit 15 is asserted (1), the windows are open and the pages in the windows can be accessed. When bit 15 is not asserted (0), the windows are closed and attempted accesses through the windows produce a bus timeout.

Upon power-up and restart, the PCR bits are cleared to 0. Both windows contain the data from page 0, but they are closed because bit 15 of the PCR is also 0. Bit 15 must be set to open the windows.

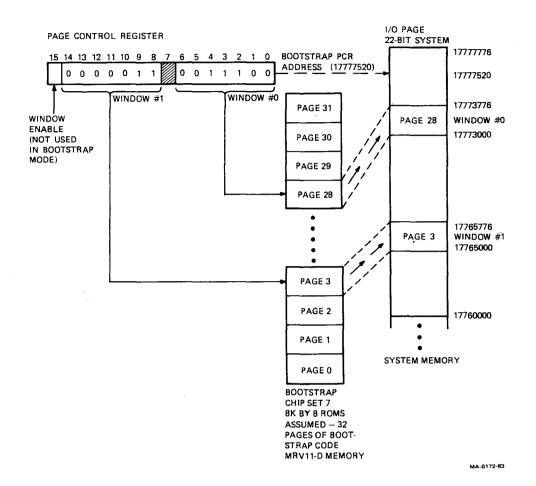

#### 1.4.3 Bootstrap

The MRV11-D bootstrap operation is similar to page mode addressing. It is independent of the address mode chosen for the module. The bootstrap windows are split. Window 0 begins at  $17773000_8$  and runs through  $17773776_8$ . Window 1 begins at  $17765000_8$  and runs through  $17765776_8$ . The bootstrap PCR is located at  $17777520_8$ . There are, however, the following important differences between page mode and bootstrap.

- 1. The bootstrap windows and pages are 512 bytes long. In page mode, the windows and pages are 2 kilobytes long.

- 2. Bit 15 of the bootstrap PCR is not a control bit. The windows are always open. In page mode, the windows are open only when bit 15 is a 1.

- 3. The bootstrap PCR address is fixed at 17777520<sub>8</sub>. The page mode PCR address is configured by the user between 17777000<sub>8</sub> and 17777036<sub>8</sub>.

Figure 1-1 Page Mode Addressing

The bootstrap memory device must be physically installed in chip set 7. (See Chapter 3.) The device may be any of the JEDEC standard pinout PROMs or ROMs that meet the requirements listed in Chapter 3. The module must be properly configured to accept the devices.

The bootstrap program size is limited by the size of the memory devices installed. A pair of 8K by 8 devices can contain a 16-kilobyte bootstrap program. Note, however, that like page mode addressing, only two 512-byte pages are available to the system at a time. The program must be specially written to turn its own pages. The MXV11-B2 bootstrap PROM set is written this way and will function if installed and properly configured on an MRV11-D. (See Chapter 3.)

If the bootstrap program is smaller than 512 bytes, it can be written on one page, avoiding the need to change pages. In this case, the program should be in the first 512 bytes of the bootstrap devices. Since the bootstrap PCR clears on power-up and restart, both windows contain page 0 of the bootstrap devices.

Nothing defines the last page of the bootstrap device. If a page number that is larger than the maximum page number for the bootstrap device is placed in the bootstrap PCR, the device in chip set 7 responds with data from the page that is given by the following formula.

(requested page number) modulo (pages on device) = actual page number

For example, a pair of 4K by 8 bootstrap devices contain 16 pages of bootstrap program. An access to page 18 is actually an access to page 2.

$18 \mod 16 = 2$

Similarly, an access to page 34 or 50 using 4K by 8 bootstrap devices is an access to page 2. With 8K by 8 bootstrap devices (32 pages), an access to page 33 is actually an access to page 1 (33 modulo 32).

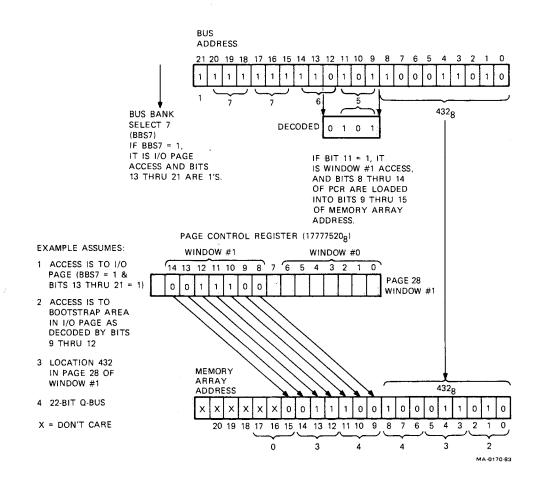

Figure 1-2 represents the bootstrap function. Window 1 holds the data from page 3. The page number (3 or  $3_8$ ) is stored in the high byte of the PCR. Window 0 holds the data from page 28. The page number (28 or  $34_8$ ) is stored in the low byte of the PCR.

If the MRV11-D that contains the bootstrap is also used as a page mode module on the system bus, the page mode PCR is in an undefined state after the bootstrap operation. Initialize the page mode PCR before attempting to access the module.

NOTE: When using the MRV11-D to bootstrap the RSX11-M operating system, a line time clock register (17777546<sub>8</sub>) must exist on another module to ensure proper operation.

#### 1.5 PHYSICAL AND ENVIRONMENTAL SPECIFICATIONS

The MRV11-D is a class C module conforming to the specifications described in the following paragraphs.

#### 1.5.1 Physical Specifications

| Height | 13.17 cm (5.187 in), double                             |

|--------|---------------------------------------------------------|

| Width  | 1.27 cm (0.500 in), single                              |

| Length | 22.70 cm (8.940 in), bottom of fingers to top of handle |

## 1.5.2 Temperature

```

Storage temperature -40° C to 66° C (-40° F to 151° F)

range

```

The module must stabilize at operating temperature for 5 minutes before operation.

Operating temperature 5° C to 60° C (41° F to 140° F) range

Derate the maximum operating temperature by 1.8 °C (3.24°F) for each 1000 m (3280 ft) above sea level.

# 1.5.3 Relative Humidity

| Storage   | 10% to 95%                                 |

|-----------|--------------------------------------------|

|           | Maximum wet bulb temperature 32° C (90° F) |

|           | Minimum dew point 2° C (36° F)             |

| Operating | 10% to 95%                                 |

|           | Maximum wet bulb temperature 32° C (90° F) |

|           | Minimum dew point 2° C (36° F)             |

# 1.5.4 Altitude

ŗ

| Storage   | Up to 9.1 km (5.65 mi)                    |

|-----------|-------------------------------------------|

| Operating | 2.4 km (1.5 mi) maximum (paragraph 1.5.2) |

# 1.5.5 Sea Level Operating Airflow

| Operating temperature | 0° C to 55° C (32° F to 131° F) |

|-----------------------|---------------------------------|

| range                 |                                 |

Adequate airflow must be provided to limit the temperature rise across the MRV11-D to 10° C (18° F).

| Operating temperature | 55° C to 60° C (131° F to 140° F) |

|-----------------------|-----------------------------------|

| range                 |                                   |

Adequate airflow must be provided to limit the temperature rise across the MRV11-D to 5° C (9° F).

#### 1.5.6 Mechanical Shock

The packaged product shall withstand half-sine shock pulses of 40 g peak for a duration of  $30 \pm 10$  ms.

# **1.6 ELECTRICAL SPECIFICATIONS**

This section provides the electrical specifications for the MRV11-D.

#### 1.6.1 Power

The following values are measured for an unpopulated MRV11-D. Add operating current for each device installed. Note only one pair of devices operates at any given time; the rest are in standby mode.

| Voltage | Tolerance | Current | Pins          |

|---------|-----------|---------|---------------|

| + 5 Vdc | ±0.25 V   | 1.6 A   | AA2, BA2, BV1 |

#### **Battery Backup Installed**

| + 5 VB  | ±0.25 V | 280 mA | AV1           |

|---------|---------|--------|---------------|

| + 5 Vdc | ±0.25 V | 1.3 A  | AA2, BA2, BV1 |

# 1.6.2 Technology

# Printed Circuit Board

Board type Etch Dual-sized, 4-layer board 0.012/0.013-inch technology

## Electronics

Latest MSI (medium scale integration) and PAL (programmable array logic) technologies

# Software

Window mapping virtual addressing

# FUNCTIONAL DESCRIPTION

# 2.1 INTRODUCTION

This chapter describes the functional operation of the MRV11-D universal PROM module. The description divides operation into direct mode, page mode, and bootstrap mode.

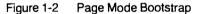

For purposes of explanation, the discussion refers to a 22-bit Q-bus system. The bus master asserts a 22-bit address on the Q-bus and then asserts the SYNC line to gain control of the bus. The address is latched into the MRV11-D by the bus interface. Decoding begins as soon as the address stabilizes rather than at the assertion of the SYNC line.

# 2.2 DIRECT MODE

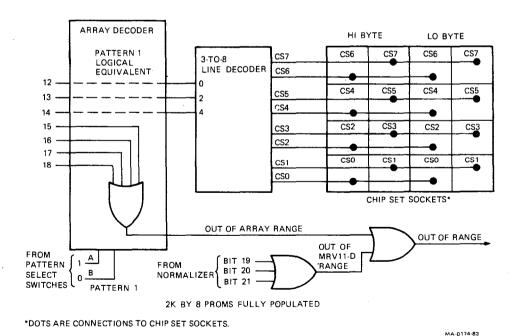

Direct mode addressing is implemented by configuring the PAGE/DIR switch as DIR. Figure 2-1 is a block diagram showing the address decoding for direct mode.

Figure 2-1 Direct Mode Block Diagram

The bus interface blocks receive address and control signals from the Q-bus and latch the address when the bus master asserts SYNC. If the bus address corresponds to an address configured for the MRV11-D, then the module responds to the access per the Q-bus protocol. If not, the module does not respond and does not transmit information on the bus.

The range of the MRV11-D is determined by the starting address (lower boundary) and the decoder PROM (upper boundary). The normalized address (bus address minus starting address) measures the distance between the bus address and start address. If this number is negative, the bus address is below the lower boundary of the module. If the number is positive, but greater than the configured capacity, the bus address is beyond the module's range. The module responds only when the bus address is greater than the module starting address and less than the configured array size.

Bits 0 through 11 of the bus address are directly mapped to bits 0 through 11 of the memory array address. Bits 12 through 18 from the normalizer are applied to the direct input of the PAGE/DIR multiplexer, which is set to DIR. These bits are then a plied to the array decoder, which determines chip select and out-of-range condition. Additional out-of-range conditions occur if either bits 19, 20, 21, or any combination are asserted. If this happens, the access detector does not issue a valid access signal to the timing circuit and the RPLY signal is blocked.

If the bus address is within range of the module, the access detector issues a valid access signal, which causes RPLY to be asserted on the bus. If a read cycle was initiated, the timing circuit drives the data onto the bus. If a write cycle was initiated, the module accepts data from the bus.

If bits 12 through 21 are all 1s, BUS BANK SELECT 7 (BBS7) is asserted to indicate that the access is not to the memory array but to the I/O page. Accesses to the PCR, bootstrap PCR (BPCR), and bootstrap areas are through the I/O page.

Note that bits 0 through 11 of the bus address are directly applied to the memory array and bits 12 through 21 of the bus address are applied to the normalizer with bits 12 through 21 from the starting address switches. The starting address set in the switches is subtracted from the bus address (Figure 2-2). This operation establishes the starting address as the lower boundary of the array. Normalized bits 12 through 15 are applied directly to the memory array to be decoded by array devices larger than 2K by 8. Bits 12 through 15 are also applied to the array decoder along with bits 16 through 18. Bits 12 through 18 perform different functions, depending on the size of the memories, number of memories utilized in the array, and the configuration.

For example, with a fully populated array of 2K by 8 PROMs, bits 0 through 11 define a particular byte within each 4 kilobyte boundary. Bits 12, 13, and 14 determine the chip set socket selected while bits 15 through 18 are used as out-of-range bits (Figure 2-3). If any of these bits are asserted, the address is above the upper boundary.

Figure 2-3 Chip Select and Out-of-Range Functions (Direct Mode)

Bits 19, 20, or 21 from the normalizer determine an out-of-range condition where the maximum capacity of the MRV11-D has been exceeded. Bits 15 through 18 are applied to the array decoder to determine an unselected condition when a chip set socket is configured for no device, or when a small array's capacity has been exceeded. Bits 19 through 21 and bits 15 through 18 are combined to determine an out-of-range condition when either of the above described situations occur.

A pair of 2K by 8 PROMs look at 12 address bits (0 through 11) to specify one byte in a 4-kilobyte block. Therefore, the next three bits (12, 13, 14) are used by the array decoder to select the desired pair of devices. This is accomplished by programming the array decoder for the desired configuration.

The standard array decoder has four selectable patterns as described in Chapter 1. Select these patterns with the pattern select jumpers as shown below.

| Device                         | Pattern Select<br>Jumpers |

|--------------------------------|---------------------------|

| 2K by 8 PROMs, half-populated  | 00                        |

| 2K by 8 PROMs, fully populated | 01                        |

| 4K by 8 PROMs, fully populated | 10                        |

| 8K by 8 PROMs, fully populated | 11                        |

If 4K by 8 PROMs are used instead of the 2K by 8 PROMs, 13 address bits (0 through 12) are required by the devices. In the fully populated case, bits 13, 14, and 15 determine the chip set sockets where the devices are to be inserted and bits 16, 17, and 18 are out-of-range bits. Similarly, for 8K by 8 PROMs, 14 address bits (0 through 13) are required. Consequently, bits 14, 15, and 16 determine the chip set socket where each device is to be inserted and bits 17 and 18 are out-of-range bits.

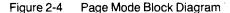

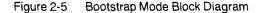

## 2.3 PAGE MODE

For page mode operation, the PAGE/DIR switch must be configured in the PAGE position. The page number is stored in the PCR during a previous bus cycle. This page number supplies the more significant address bits of the array address. For all window accesses, bit 15 of the PCR must be set to open the window areas. Figure 2-4 is a functional block diagram showing the page mode data paths.

Bits 0 through 10 of the bus address are directly mapped to bits 0 through 10 of the memory array address. Bit 11 of the bus address marks the boundary between window 0 and window 1 of the bus. If bit 11 equals 1, the page of code in window 1 is accessed. If bit 11 equals 0, the page of code in window 0 is accessed.

The starting address is subtracted from the bus address in the normalizer block and the result is checked against the upper boundary. (In page mode, the upper boundary equals the starting address plus 4 kilobytes.) If any combination of normalized bits 12 through 21 are asserted, the address is greater than the upper boundary of the module – out of its range. In this instance, the access detector gets an out-of-range signal and never issues a valid access signal to the timing chain. Consequently, the MRV11-D ignores that bus cycle.

#### FUNCTIONAL DESCRIPTION 15

The page numbers in the PCR are multiplexed and controlled by bus address bit 11. Therefore, the appropriate page number for the accessed window is used to construct the memory array address. This address is applied to the array and array decoder as in the direct mode example. Note that the PCR window contains 7 bits and these bits replace normalized bits 11 through 17. These bits are used by the array decoder for chip select decoding and/or out-of-range conditions.

For a half-populated array of 2K by 8 PROMs, the PROM sets look at 12 address bits (bits 0 through 11) because this pattern specifies 4 kilobytes for each set. The next two bits (12 and 13) are used by the array decoder to select one of the four chip sets. This is accomplished by setting the pattern select jumpers for the installed device configuration as shown below.

Pattern Select

| Device                                                           | Jumpers  |

|------------------------------------------------------------------|----------|

| 2K by 8 PROMs, half-populated<br>2K by 8 PROMs, fully populated  | 00       |

| 4K by 8 PROMs, fully populated<br>8K by 8 PROMs, fully populated | 10<br>11 |

If a fully populated array of 2K by 8 PROMs is used instead of the half-populated 2K by 8 PROMs, 12 address bits (0 through 11) are required (Figure 2-3). In this case then, bits 12, 13, and 14 determine the chip set socket where each device pair is inserted and bits 15 through 18 are out-of-range bits. Similarly, for 4K by 8 PROMs, 13 address bits (0 through 12) are required. Bits 13, 14, and 15 determine the chip set socket where each device is to be inserted and bits 16 through 18 are out-of-range bits. For 8K by 8 PROMs, 14 address bits (bits 0 through 13) are required. Bits 14, 15, and 16 are chip select bits and bits 17 and 18 are out-of-range bits.

The array address is derived as follows (Figure 2-4). Bus address bits 0 through 10 are directly mapped to memory array address bits 0 through 10. Bus address bit 11 chooses the byte of the PCR that serves as array address bits 11 through 17. The low byte contains the page number for window 0 (bit 7 is unused): The high byte contains the page number for window 1 (bit 15 is a window enable bit). Since a page mode address is limited to 18 bits, the page mode array capacity is limited to 256 kilobytes. Bus address bits 12 through 21 are used solely to determine that the access is between the base of window 0 (starting address) and the top of window 1 (starting address plus 4 kilobytes).

Bits 11 through 17 of the memory array address are supplied from the PCR (PCR bits 0 through 6 for window 0 or PCR bits 8 through 14 for window 1). As previously mentioned, bits 11 through 17 perform different functions depending on the PROM devices used and the number of PROMs installed.

Bits 12 through 21 from the normalizer determine an out-of-range condition (4 kilobytes greater than starting address) where the range of the MRV11-D memory array has been exceeded. Bits 15 through 18 applied to the array decoder determine an out-of-range condition when a chip set socket with no device configured has been addressed or the page limit has been exceeded. Bits 12 through 21 from the normalizer and bits 15 through 18 from the array decoder are combined to detect an out-of-range condition if either of the above described situations occur.

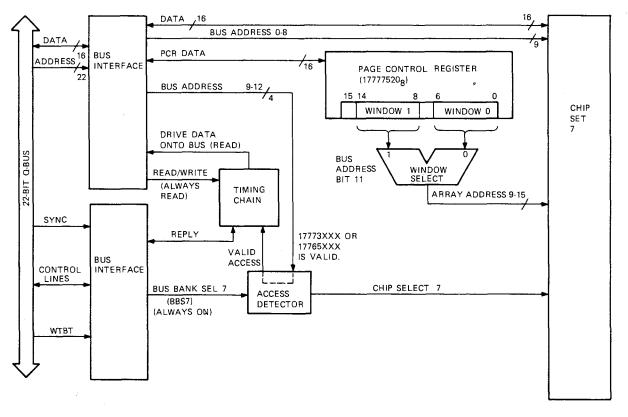

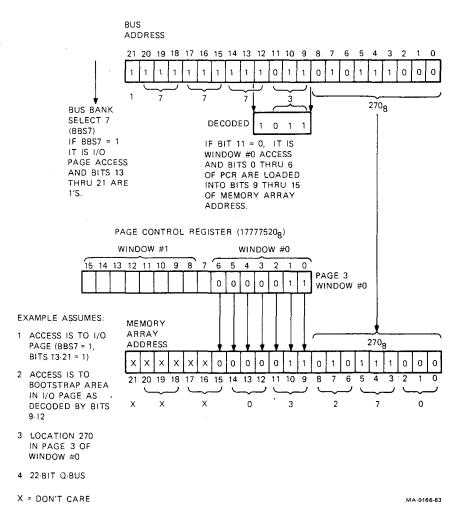

#### 2.4 BOOTSTRAP MODE

Figure 2-5 is a functional block diagram of the MRV11-D in bootstrap mode. Bus address bits 0 through 8 are directly mapped to memory array address bits 0 through 8 to define one byte within each 512-byte boundary. Bus address bits 9 through 21 must be either 17773<sub>8</sub> or 17765<sub>8</sub> for a valid bootstrap access. As a result of bits 13 through 21 being asserted, BBS7 is also asserted to indicate an I/O page access. Bits 9 through 12 are decoded as follows.

| 21–15  | 14 13 12      | 11 10 9               | <b>8 7 6</b> - | 543 | 210 |

|--------|---------------|-----------------------|----------------|-----|-----|

| All 1s | $\frac{1}{1}$ | $\frac{0 \ 1 \ 1}{3}$ | ×              |     |     |

| 177    | /             | 3                     | ~              | ~   | ^   |

| or     |               |                       |                |     |     |

| 21–15  | 14 13 12      | i 11 10 9             | 876            | 543 | 210 |

| All 1s | 1 1 0         | 1 0 1                 |                |     |     |

| 177    | 6             | 5                     | X              | X   | ×   |

FUNCTIONAL DESCRIPTION 17

MA-0180-83

The state of bit 11 chooses the byte of the bootstrap PCR that serves as array address bits 9 through 15. The 17773XXX represents an access to window 0 (BPCR low byte). The 17765XXX represents an access to window 1 (BPCR high byte). The bootstrap PCR is located at 177775208.

If an I/O address other than the above addresses is detected, the MRV11-D does not respond.

In bootstrap mode, chip select 7 is always asserted during a bootstrap access. Consequently, the bootstrap code must always reside in chip set 7.

Figure 2-6 shows how the bus address is mapped for the bootstrap using window 0 (location 17773270<sub>8</sub>, page 3). Bits 0 through 8 of the bus address map directly to memory array address bits 0 through 8. Bits 12 through 9 of the bus address are respectively decoded as 1011. When bit 11 equals 0, the low byte of the PCR is appended to bits 0 through 8 to form the memory array address. The state of bus address bits 9 through 21 (all asserted) indicate an access to the bootstrap area in the I/O page.

The page number, loaded in bits 0 through 6 of the PCR, is mapped into bits 9 through 15 of the memory array address. Chip select 7 is always asserted on bootstrap access, so the array address (3270<sub>8</sub>) is applied to the PROMs in chip set 7.

Figure 2-6 Bootstrap Access to Window 0 (I/O Page)

Figure 2-7 shows a bootstrap access to window 1, location 177654328. Bits 0 through 8 of the bus address map directly to memory array address bits 0 through 8. Bits 12 through 9 of the bus address are respectively decoded as 0101 with bit 11 equal to 1. Since bit 11 equals 1, the page number for window 1 is selected from the PCR. BBS7 is asserted since bits 13 through 21 are all asserted, indicating an access to the I/O page.

To address the I/O page, BBS7 and bus address bits 13 through 21 must be asserted.

The page address  $(34_8)$  in window 1 of the PCR is mapped into bits 9 through 15 of the memory array address. The address  $34432_8$  is applied to chip set 7.

Figure 2-7 Bootstrap Access to Window 1 (I/O Page)

.

## 3.1 INTRODUCTION

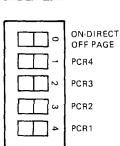

This chapter describes how to configure the MRV11-D to function properly for your application. Configuration is accomplished by setting a bank of PCR switches, setting a bank of starting address switches, and connecting a series of jumper posts. The required jumper posts are connected by means of jumper clips designated as W3 through W16. These jumper clips allow two adjacent jumper posts to be connected. Nonfunctional holder posts are provided in many jumper groups to avoid the loss of jumper clips when not used. There are 16 memory sockets on the module that house 8 possible chip sets. (Each chip set has a high byte device and a low byte device.) This arrangement is shown in Figure 3-1.

21

# 3.2 CONFIGURATION

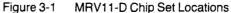

To configure the MRV11-D properly for a specific application, use the flowchart in Figure 3-2. The tables referenced in this figure provide additional information on the jumper and switch selections.

Figure 3-3 shows the location of the jumpers and switches on the module. The figure contains a reference to a table for each jumper and switch bank. Refer to the appropriate table to determine the actual jumper connections or switch settings. For example, Figure 3-3 shows the location of the DATO jumper and references Table 3-4. Table 3-4 shows the actual jumper posts and describes the possible connections.

NOTE: The MRV11-D can be remotely enabled and disabled by asserting the spare bus signal SSPARE3 (bus pin AN1). This signal is not bussed in Digital backplanes, but may be connected in other backplanes supplied by other manufacturers.

# 3.2.1 Installing MXV11-B2 ROM on MRV11-D

Perform the following steps to install an MXV11-B2 PROM set on the MRV11-D.

- 1. Enable the bootstrap function (Table 3-8).

- 2. Set the row 4 jumper (power jumper) for an 8K by 8 device (Table 3-6).

- 3. Set the device size jumper to 8K by 8 (Table 3-5).

NOTES: MXV11-B2 bootstrap ROMs cannot be used if the device size jumper is set for 2K by 8 or if the power jumper connection for row 4 is set for 16K by 8 or 32K by 8 devices.

For additional information on the MXV11-B2 ROM, refer to the MXV11-B2 ROM Set User Guide (EK-MXVB2-UG).

Figure 3-2 Jumper Configuration Flowchart (Part 1)

Figure 3-2 Jumper Configuration Flowchart (Part 2)

•

÷

MA-0277N-82

#### Figure 3-3 Jumper and Switch Locations

÷

35

### 3.3 PROM SIZES AND PINOUTS

The MRV11-D contains sixteen 28-pin sockets to house the various PROMs and static RAM devices that can be used in the module. The sockets can house 2K by 8, 4K by 8, 8K by 8, 16K by 8, and 32K by 8 PROMs. In addition, the bottom half of the socket array (chip sets 0 through 3) can accommodate static RAM. The 2K by 8 and 4K by 8 PROMs contain 24 pins while the others contain 28 pins.

Figure 3-4 shows the pin assignments for the 24- and 28-pin memories using the JEDEC standard pinout. The 2K by 8 PROM is represented by the 2716 and the 4K by 8 PROM is represented by the 2732. The other PROM types (8K by 8, 16K by 8, and 32K by 8) are represented by the 2764, 27128, and 27256 respectively. The 8K by 8 static RAM is also shown. The basic differences on the 2764, 27128, 27256, and static RAM are in the functions of pins 26 and/or 27. Figure 3-4 shows these differences. For example, on the 16K by 8 PROM (27128), pin 26 is used as an address pin (A13). On the 32K by 8 PROM (27256), pins 26 and 27 are used as address pins (A13 and A14, respectively).

MA-0203-8

When installing a 24-pin PROM (2K by 8, 4K by 8) in a 28-pin socket, install it with the notch on top and bottom justified. Pin 1 of the PROM inserts into pin 3 of the socket (Figure 3-5). On 28-pin devices, pin 28 is the power.pin. For 24-pin devices, pin 28 of the socket must be strapped to pin 26 of the socket to provide power to the device. The power jumpers strap these pins together (Table 3-6).

NOTE: If you are using 24-pin devices such as the 2716 (2K by 8 PROM) on a revision C etch board, you must wirewrap J13 (Vpp) to J40 (pin 26 of row 4). It is also necessary to jumper J40 to J41 (+5 V). However, you cannot use the jumper clip because a wirewrap exists on J40. Therefore, you must wirewrap, rather than jumper, J40 to J41. This procedure ensures proper read mode operation (Table 3-5). On a revision D etch board, you can install 2K by 8 PROMs without wirewrap (Table 3-5).

Insertion of 24-Pin PROM Chips

# 4

4.1 INTRODUCTION

The window-mapped mode can be used in two ways in LSI-11 application programs. One way is to code the application program to execute directly from the windows. The other is to use the window-mapped board to transfer a standalone application program from ROM into RAM memory at system start-up. This chapter provides an example of each type.

PROGRAMMING

### 4.2 EXECUTING WINDOWED PROGRAMS

Executing directly from MRV11-D windows allows large programs of up to 56 kilobytes of RAM on LSI-11/2 systems. However, software executed in this mode must be specially designed and written in assembly language.

An application designed for window mode execution must have a mechanism for calling a subroutine or transferring control to another routine that is in a presently unmapped section of the windowed ROM board. You must use a technique different from the standard JSR or JMP instructions. This technique is illustated in Figure 4-1.

The routine that processes subroutine calls and jumps to other pages must, of course, be in a section of memory that is not window mapped. To call a subroutine using these capabilities, write CALLWO *label* instead of JSR PC *label*. CALLWO *label* causes the desired subroutine to map into window 0. It also causes the call to execute. Upon subroutine return, which is done with a normal RTS PC instruction, the original mapping is restored and control returns to the calling program. To invoke a subroutine and have it mapped in window 1, write CALLW1 *label*.

Note that the mechanism shown in Figure 4-1 preserves condition codes from the called routine back to the caller. That is, routines can return status in the condition codes. Instead of the unconditional jump instruction, write JMPW0 *label* to jump to a routine, and map it into window 0. Write JMPW1 *label* to transfer control to a routine that should be mapped into window 1.

```

;ADRS IS RELATIVE TO BEGINNING OF MRV11-D

WOBASE = 150000;<<STARTING ADDRESS OF MRV11-D

W1BASE = 154000

JMPW = 1

JSRW = 0

W1 = 2

WO = O

MRVPCR = 177000

+MACRO

CALLWO ADRS

TRAP

JSRW + WO + <<ADRS/1000> & 774>

WOBASE + <ADRS & 3777>

,WORD

+ ENDM

CALLWO

+ MACRO

JMPWO ADRS

TRAP

JMPW + WO + <<ADRS/1000> & 774>

+ WORD

WOBASE + <ADRS & 3777>

+ ENDM

JMPWO

, MACRO

CALLW1 ADRS

TRAP

JSRW + W1 <<ADDRS/1000> & 774>

,WORD

W1BASE + < ADRS & 3777>

+ ENDM

JMPW1

+MACRO

JMPW1 ADRS

TRAP

JMPW + W1 + << ADRS/1000> & 774>

+ WORD

WIBASE + <ADRS & 3777>

+ ENDM

JMPW1

TRPHAN: MOV @#MRVCSR,-(SP)

Save previous mapping

TST

- (SP)

Reserve space for adrs

MOV

R0→ -(SP)

Save caller's register

MOV

6 (SP), RO

;And set RO to address of

;TRAP + 2

ADD

#2, 6(SP)

Update return PC beyond adrs

MOV

(R0), 2(SP)

Move adrs (follows TRAP

;instructions)

MOV

-(RO), RO

FRO TRAP instruction itself

BIC

#177600, RO

Fextract page #, window #,

;JMP/JSR

ASR

RO

Move JMP/JSR to C bit

ROR

RO

Place window # in C,

JMP/JSR in bit 15

MOV

#MRVPCR→ -(SP)

Set address of window O in

imap bits

ADC

@SP

#And update based on window #

MOVB RO, @(SP)

Map new page in selected

iwindow

BIS

#100000,@(SP)+

#Enable windows

ROL

RO

JMP/JSR back to C bit

MOV

(SP)+, RO

Restore caller's resister

BCS

if JMP, branch to 1$

1$

JSR

PC, @(SP)+

Else JSR to desired routine

MFPS 4(SP)

Store returned condition codes

in old PS

MOV

(SP)+3@#MRVPCR

Restore original mapping

RTI

SAnd return after TRAP

jand adrs

$

MOV

(SP)+, @SP.

ilf JMP, move adrs

MOV

(SP)+, @SP

iUP over old (caller's) PC

RTI

;And so to new location

```

Figure 4-1 JSR and JMP Control Routines for Window Mapping To use this mechanism, the program should be assembled with .ENABL AMA to force absolute addressing in the assembly. At start-up, a bootstrap routine must be executed from the MRV11-D bootstrap window or elsewhere. This routine copies the trap handler routine to RAM memory, if necessary. It initializes the trap vector to contain the address of the trap handling routine and a new status word of all 0s.

With this type of application, take care not to cross page boundaries without remapping to the next page. If you encounter a page boundary, use the JMPW0 or JMPW1 pseudo instructions to move to the beginning of the next page.

### 4.3 TRANSFERRING APPLICATION PROGRAMS FROM ROM TO RAM

In window-mapped mode, the MRV11-D can also be used as a low-cost, program load device for standalone applications. This use allows application programs that cannot be easily segmented into ROM and RAM sections to be loaded from a ROM environment into RAM for execution. To use the MRV11-D in this mode, write a bootstrap loader program to copy the contents of the ROM board into the RAM area at power-up. Figure 4-2 demonstrates such a program. The program is designed to load standalone images created by the RT-11 LINK utility. It is also possible to load an RSX-11S system image from one or more MRV11-D boards into RAM for execution.

| MRVPCR =<br>MRVWIN =<br>ONEKW = | 150000                                                |                                                                                              |

|---------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------|

| LOADER:                         | MDV #100000,@#MRVPCR<br>MDV @#MRVWIN+50, R5<br>CLR R4 | Finable & map low 1K words<br>FR5=RT-11 SAV file high limit<br>Start copying into location O |

| 1\$                             | MOV "#MRVWIN; R3                                      | Reset to base of first window                                                                |

| 2\$                             | MOV (R3)+, (R4)+                                      | COPY one word into RAM                                                                       |

|                                 | ·CMP R4 + R5                                          | Moved highest word in program?                                                               |

|                                 | BHIS 3\$                                              | ilf HIS, yes                                                                                 |

|                                 | BIT #ONEKW, R3                                        | ¡Have reached next 1 Kw boundary?                                                            |

|                                 | BNE 2\$                                               | ;if NE→ no                                                                                   |

|                                 | INC @#MRVPCR                                          | ;Else map next 1K in window O                                                                |

|                                 | BR 1\$                                                | ;And continue copying                                                                        |

| 3\$                             | MOV @#40, PC                                          | ;Start at user's transfer address                                                            |

Figure 4-2

Bootstrap Loader for Standalone Programs in RT-11 SAV Format

### 5.1 INTRODUCTION

This chapter is for users who want specific applications on the MRV11-D. As previously specified, the module is shipped with a standard array decoder supplied by Digital. It provides four predefined patterns.

2K by 8 PROMs, half-populated 2K by 8 PROMs, fully populated 4K by 8 PROMs, fully populated 8K by 8 PROMs, fully populated

Users whose needs are satisfied by this configuration may omit this chapter with no loss of continuity.

### 5.2 DECODER PROGRAMMING HARDWARE

Programming the array decoder requires specific hardware. The basic hardware is the model 19 or model 29 programmer from the Data I/O Corporation or the PB11 PROM programming option for the LSI-11 from Digital. Table 5-1 lists the 512 by 4 array decoders, vendors, card sets/socket adapters, and UniPak fixtures. Either the card set and adapter or the UniPak fixture are required in addition to the basic hardware.

|                                          |                   |          |      |                    | Alternate          | Hardwar      | e           |

|------------------------------------------|-------------------|----------|------|--------------------|--------------------|--------------|-------------|

| 512 by 4<br>Array Decoder<br>Part Number | PROM_,.<br>Vendor | Card Set | Rev. | Socket<br>Adapter* | UniPak<br>Revision | Fam.<br>Code | Pin<br>Code |

| 27S13/29771                              | AMP               | 1286-1   | G    | 1408-2             | A                  | 16           | 03          |

| 93446                                    | Fairchild         | 1063-2   | H    | 1035-2             | А                  | 01           | -03         |

| 7621                                     | Harris            | 1473-002 | A    | 1035-2             | Α .                | 05           | 03          |

| 5306/6306                                | MM                | 1226-1   | M    | 1035-2             | D                  | 11           | 03          |

| 54/74\$571                               | National          | 1473-003 | A    | 1035-2             | Ā                  | 08           | . 03        |

A brief description of each column in Table 5-1 follows.

| 512 by 4<br>Array Decoder<br>Part Number | Vendor's part number of the PROM                                                                                                                                                                         |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROM<br>Vendor                           | Manufacturer of the PROM                                                                                                                                                                                 |

| Card Set                                 | Programming card set from the Data I/O<br>Corporation that is used to program the PROM                                                                                                                   |

| Rev.                                     | Required revision of the card set                                                                                                                                                                        |

| Socket Adapter                           | Part number of socket adapter used with the card set                                                                                                                                                     |

| UniPak Revision                          | The UniPak fixture plugs into Data I/O<br>Corporation's programmer in place of the card<br>set. The programmer and UniPak can program                                                                    |

|                                          | MOS and bipolar PROMs. This column lists the<br>required revision level. For the 5306/6306<br>MMI PROM, UniPak revision D or later can be<br>used. For the others, revision A or later is<br>applicable. |

| Fam. Code                                | required revision level. For the 5306/6306<br>MMI PROM, UniPak revision D or later can be<br>used. For the others, revision A or later is                                                                |

### 5.3 ARRAY DECODER

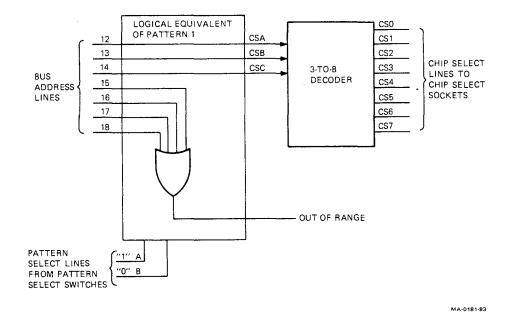

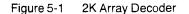

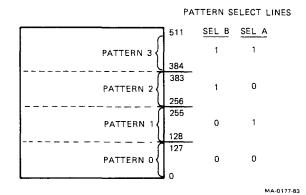

Each array decoder location controls a 4-kilobyte segment of array memory. For example, in a 512 by 4 array decoder, there are 512 locations and each location controls 4 kilobytes of memory. Two pattern select lines (Figure 5-1) allow one of four patterns to be selected. Each pattern contains 128 locations (512 divided by 4). The pattern select lines are connected to the pattern select jumpers, which select the desired pattern.

The first location (location 0) of each pattern responds at the starting address of the module. Location 1 responds at the next address and so on up to location 127. These 128 locations comprise the first pattern (pattern 0), which is indicated by both pattern select lines being 0. The next 128 locations comprise pattern 1, the next 128 locations comprise pattern 2, and the final 128 locations comprise pattern 3 (Figure 5-2).

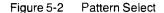

NOTE: Figure 5-3 shows the pin designations of the array decoder. Refer to them when you design the array decoder for a special application.

Three chip select lines from the array decoder are applied to a 3-to-8 line decoder (Figure 5-1). The 3-to-8 decoder asserts one of eight chip select lines. One line is associated with each pair of chip sets. The chip select number and the in-range signal must be asserted to turn on a chip set. Under these conditions, the chip set is enabled and all other chip sets are turned off.

For the 2K by 8 decoder pattern, each PROM pair monitors bits 0 through 11. These bits specify a byte within each 4-kilobyte block. Bits 12 through 14 are chip select lines. Bits 15 through 18 are bits that determine if the address is in the range of the MRV11-D. A 4K by 8 PROM pair monitors bits 0 through 12. Table 5-2 shows the chip select bits and range bits for fully populated arrays using other size PROMs. For each PROM size, bit 0 specifies high byte or low byte. As an example, a 4K by 8 PROM requires 13 address bits. They are address bits 0 through 12, where bit 0 merely specifies which byte of the chip set is specified.

The least significant bit (LSB) into the array decoder can resolve between 4-kilobyte blocks. For example, in the 2K by 8 PROMs, bit 12 controls the first 4-kilobyte boundary and is the LSB applied to the array decoder. The remaining address bits control the memory boundaries as follows.

| Bit | Controls                |

|-----|-------------------------|

| 13  | 8-kilobyte boundaries   |

| 14  | 16-kilobyte boundaries  |

| 15  | 32-kilobyte boundaries  |

| 16  | 64-kilobyte boundaries  |

| 17  | 128-kilobyte boundaries |

| 18  | 256-kilobyte boundaries |

An 8K by 8 PROM pair requires 14 address bits (0 through 13). In this case, bits 14, 15, and 16 are chip select bits and bits 17 and 18 are out-of-range bits.

|               |                                                                                                                                                                                                                                                                                | den en e |                        |           |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------|-----------|--|

| Table 5       | i-2 Chip Sele                                                                                                                                                                                                                                                                  | ct and Range B                            | its for Fully Populate | ed Module |  |

|               | 동안 200 - 190 - 1910 - 1910 - 1910 - 1910<br>1920 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 -<br>1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - 1910 - |                                           |                        |           |  |

|               | PROM                                                                                                                                                                                                                                                                           |                                           |                        |           |  |

| PROM          | Monitors                                                                                                                                                                                                                                                                       | Chip Select                               | Out-of-Range           |           |  |

| Size          | Bits                                                                                                                                                                                                                                                                           | Bits                                      | Bits                   |           |  |

|               |                                                                                                                                                                                                                                                                                |                                           | . 전철은 가능하는 것같          |           |  |

| 4K            | 0-12                                                                                                                                                                                                                                                                           | 13, 14, 15                                | 16, 17, 18             |           |  |

| 8K            | 0–13                                                                                                                                                                                                                                                                           | 14, 15, 16                                | 17, 18                 |           |  |

| - 16K         | 0-14                                                                                                                                                                                                                                                                           | 15, 16, 17                                | 18                     |           |  |

| 32K           | 0-15                                                                                                                                                                                                                                                                           | 16, 17, 18                                |                        |           |  |

| 200 C 12 C 10 |                                                                                                                                                                                                                                                                                |                                           | 는 사망했지만 방법에 걸었어? 그 놈   | 的可能就是認識的  |  |

### 5.4 GUIDELINES AND RESTRICTIONS

When programming your own array decoder, you should follow certain guidelines and restrictions. This section describes them.

- Use only 2K by 8 devices or larger.

- Devices must be in pairs and there must be no mixing within pairs of devices. For example, you cannot have a 2K by 8 PROM in the high byte of chip set socket 0 and a 4K by 8 PROM in the low byte of chip set socket 0.

- If you are installing a static RAM, you must install it in the lower half of the array. A 4K by 8 PROM can be mixed with static RAM in the same row, or it can be placed elsewhere in the array. The 8K by 8, 16K by 8, or 32K by 8 PROMs cannot be mixed with RAM in the same row and must be installed in the upper half.

- If you are creating a pattern that includes bootstrap code, the bootstrap code must reside in chip set 7. The code should not be included in your pattern. Otherwise, the bootstrap code will appear erroneously.

- Do not mix 2K by 8 devices with any other device sizes on the module.

- You can mix 8K by 8 devices with 4K by 8 devices in the same row or with 16K by 8 devices in the same row.

- If 32K by 8 devices are installed in a chip set, no other device sizes can be installed in the row incorporating that chip set. For example, if 32K by 8 devices are installed in chip set 0, chip set 1 can contain only 32K by 8 devices.

- When developing an array decoder pattern to handle a mixture of device sizes, enable the largest device to be read first. Otherwise, blocks in the array will be offset because the larger devices sample higher order address lines.

For example, you have an 8K by 8 RAM pair that must be installed in the lower half of the array and you want to install a 16K by 8 PROM pair. You must install the 16K by 8 PROM pair in the upper half. In this case, you should enable the 16K by 8 PROM to be read first, even though RAM is in the lower half of the array and 16K by 8 PROM is in the upper half of the array.

### 5.5 DESIGNING AN ARRAY DECODER

This section briefly describes the procedure for designing a decoder PROM for a specific application. Before proceeding, become familiar with the guidelines and restrictions described in the preceding section.

The first step is to convert the bus address to the array address. In direct mode, select a starting address and subtract it from the bus address. To obtain the array address in page mode, bits 11 through 21 of the bus address are stripped off. Bits 11 through 17 of the bus address are replaced by bits from the PCR that represent the page number for the corresponding window.

Next, determine the pattern selection and the decoder PROM address. The pattern select jumpers determine the pattern select lines. The decoder PROM address is obtained by appending the pattern select bits to bits 12 through 18 of the array. address.

Finally, determine which device is to be read for each 4-kilobyte block of bus addresses. Once the chip set number for each block is determined, it is programmed into the array decoder as out-of-range and chip select C, B, and A.

Refer to Figures 5-4 and 5-5 for help in designing the array decoder. Use the form in Figure 5-4 when you are using direct mode addressing. Use the form in Figure 5-5 when you are using page mode addressing.

This section provides examples that show how to use these forms. The following points are common to the examples. Keep them in mind when you review the examples.

- Because of space considerations, the bus address and array address in the examples are shown in octal format. The decoder address is shown in binary format. The binary format for the decoder address is used so you can see the effect of bit.12 and higher order bits changing individually throughout the pattern.

- The pattern select bits (appended to bit 18 of the decoder address) take the value set in the pattern select jumpers.

- The decoder address, bus address, and array address increase sequentially through a given pattern.

- Bit 12 defines 4-kilobyte boundaries, so each row represents a 4-kilobyte increase. The bus address and array address increase by 10000<sub>8</sub> in each row. This increase is equivalent to the 4-kilobyte increase of the decoder address.

- The decoder data is the data that is programmed into the device at the specified address. This data consists of the out-of-range line and three chip select lines labeled C, B, and A. The three select lines are supplied to a 3-to-8 line decoder with each of the eight output lines connected to a different chip set.

- When the pattern is programmed, all other locations remaining in the pattern represent an out-of-range condition. The out-of-range condition is denoted by the out-of-range line going to a logic 1. When this occurs, C, B, and A select lines are marked with Xs indicating a "don't care" condition.

| ٩. | DECODER DATA<br>(BINARY) |                   |                 |     | DECODER ADDRESS (BINARY) |               |    |    |    |    |   | ARRAY ADDRESS (OCTAL) |    |  |  | BUS ADDRESS (OCTAL) |          |    |   |      |     |  |  |   |         |     |   |              |

|----|--------------------------|-------------------|-----------------|-----|--------------------------|---------------|----|----|----|----|---|-----------------------|----|--|--|---------------------|----------|----|---|------|-----|--|--|---|---------|-----|---|--------------|

| ,  | 8                        | с                 | OUT OF<br>RANGE | 12  | 13                       | 14            | 15 | 16 | 17 | 18 |   | B                     | •0 |  |  | 2                   | 1, 13, 1 | 14 | , | 21 - | • 0 |  |  | 2 | , 13, 1 | _14 | • | 4            |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     | [        |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 | , i |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   | Τ            |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   | 2            |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     | ]                        |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    | _ |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      | •   |  |  |   |         |     |   |              |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

|    |                          | $ \rightarrow $   |                 |     |                          | $\rightarrow$ |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   | 4            |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   | $\downarrow$ |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   | 4            |

|    |                          | $\longrightarrow$ |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   | 4            |

|    |                          | $ \rightarrow $   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   | $\downarrow$ |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   | 4            |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     | ]        |    |   |      |     |  |  |   |         |     |   | 4            |

|    | $ \rightarrow $          | $ \rightarrow $   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   | _            |

|    |                          |                   |                 |     |                          |               |    |    |    |    |   |                       |    |  |  |                     |          |    |   |      |     |  |  |   |         |     |   |              |

Figure 5-4 Direct Mode Format for Array Decoder

PROGRAMMING THE ARRAY DECODER 49

|    | PAGE     | NUN | IBER     | (BIN     | ARY)     | <b>,</b> |      |      | ECOL | DERA                                           | DDR      | ESS (   | BINA     | RY) |          | DECO<br>(B       | DER      | DATA<br>Y) | `       |

|----|----------|-----|----------|----------|----------|----------|------|------|------|------------------------------------------------|----------|---------|----------|-----|----------|------------------|----------|------------|---------|

|    |          |     |          | 10       |          |          | SELI | مسسم |      |                                                |          |         |          |     |          | OUT-OF-<br>RANGE | с        |            |         |

| 17 | 16       | 15  | 14       | 13       | 12       | 11       | В    | A    | 18   | 17                                             | 16       | 15      | 14       | 13  | 12       |                  | <u>ر</u> | в          | A       |

|    | <u> </u> |     |          | <u> </u> | ļ        |          |      |      |      | <u> </u>                                       | ļ        | ļ       |          |     |          |                  |          |            |         |

|    | ļ        |     |          |          |          |          |      |      |      | <u> </u>                                       | <b> </b> |         | <b> </b> |     | <u> </u> |                  |          |            | <b></b> |

|    | <u> </u> |     |          | L        | ļ        |          |      |      |      |                                                |          | ļ       |          |     |          |                  |          |            | L       |