EK-MSV1Q-UG-002

### MSV11-Q MOS Memory

User's Guide

٩

1st Edition, March 1985 2nd Edition, May 1985

Copyright © May 1985 by Digital Equipment Corporation. All Rights Reserved. Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts 01754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| digital <sup>™</sup> | DECwriter | P/OS         | UNIBUS         |

|----------------------|-----------|--------------|----------------|

| DEC                  | DIGITAL   | Professional | VAX            |

| DECmate              | LA        | Rainbow      | VMS            |

| DECnet               | MASSBUS   | RSTS         | VT             |

| DECUS                | PDP       | RSX          | Work Processor |

#### CONTENTS

#### CHAPTER 1 CHARACTERISTICS AND SPECIFICATIONS

| 1.1     | Introduction 1                  |

|---------|---------------------------------|

| 1.2     | General Description 3           |

| 1.3     | Specifications 4                |

| 1.3.1   | Functional Specifications 5     |

| 1.3.2   | Electrical Specifications 7     |

| 1.3.2.1 | Voltages 7                      |

| 1.3.2.2 | Power Requirements 7            |

| 1.3.3   | Environmental Specifications 11 |

| 1.3.3.1 | Temperature 11                  |

| 1.3.3.2 | Relative Humidity 12            |

| 1.3.3.3 | Operating Airflow 12            |

| 1.3.3.4 | Altitude 12                     |

| 1.3.4   | Refresh 12                      |

| 1.3.5   | Diagnostics 12                  |

| 1.3.6   | Backplane Pin Utilization 12    |

| 1.3.7   | Electrical Specifications 15    |

| 1.3.7.1 | Power Supply Requirements       |

| 1.3.8   | Bus Loading 15                  |

| 1.4     | Related Documents 15            |

|         |                                 |

#### CHAPTER 2 CONFIGURATION (MSV11-QA, ETCH REVISION A)

| 2.1   | General                                     | 17 |

|-------|---------------------------------------------|----|

| 2.2   | Configuring the MSV11-QA (Etch Revision A)  | 17 |

| 2.2.1 | Test Jumper (W5, W6)                        | 19 |

| 2.2.2 | CSR Register Selection (R, P, N, M) Jumpers | 19 |

| 2.2.3 | Enable/Disable CSR Selection Jumper         | 21 |

|       |                                             |    |

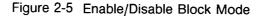

| 2.2.4 | Enable/Disable Block Mode Jumper                |

|-------|-------------------------------------------------|

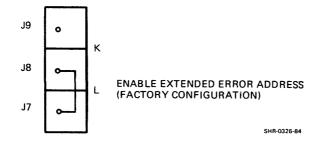

| 2.2.5 | Enable/Disable Extended Error Address Jumper 22 |

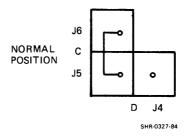

| 2.2.6 | Test Jumper C, D 22                             |

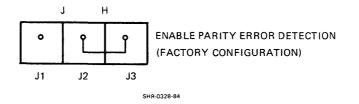

| 2.2.7 | Enable Parity Error Detection Jumper            |

| 2.2.8 | Battery Backup 23                               |

| 2.2.9 | Address Switches 24                             |

#### CHAPTER 3 (MSV11-QA ETCH REVISION C OR LATER, MSV11-QB AND MSV11-QC)

| 3.1   | General                                           | 27 |

|-------|---------------------------------------------------|----|

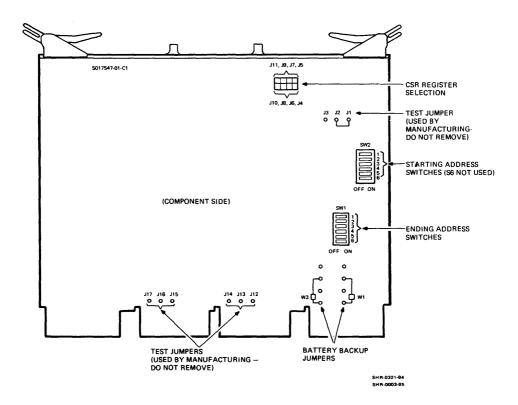

| 3.2   | Configuring the MSV11-Q 2                         | 27 |

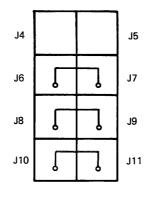

| 3.2.1 | CSR Register Selection (Jumpers J4 through J11) 2 | 29 |

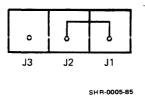

| 3.2.2 | Test Jumpers J1 through J3 3                      | 30 |

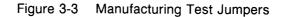

| 3.2.3 | Battery Backup 3                                  | 31 |

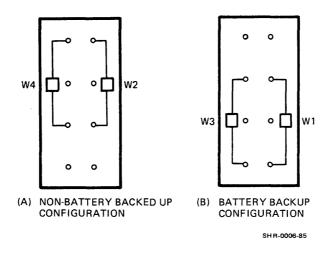

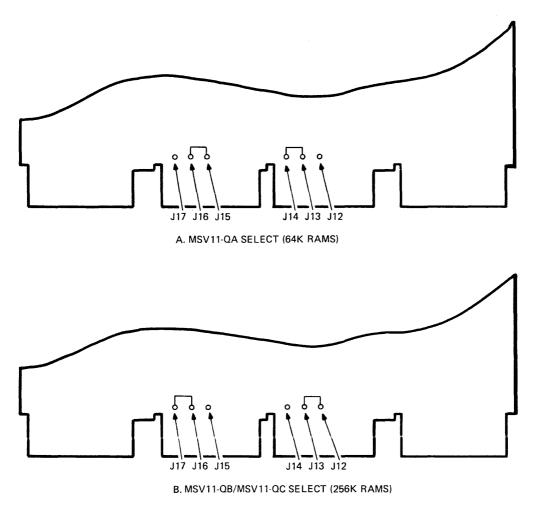

| 3.2.4 | Chip Select Jumpers 3                             | 31 |

| 3.2.5 | Address Switches 3                                |    |

|       |                                                   |    |

#### CHAPTER 4 UNPACKING AND INSTALLATION

| 4.1   | General                    | 5 |

|-------|----------------------------|---|

| 4.1.1 | Unpacking and Inspection 3 | 5 |

| 4.1.2 | Pre-installation 3         | 6 |

| 4.1.3 | Installation               | 7 |

| 4.1.4 | Module Checkout 3          | 7 |

#### CHAPTER 5 FUNCTIONAL DESCRIPTION

| 5.1   | Introduction                                       | 9 |

|-------|----------------------------------------------------|---|

| 5.2   | LSI-11 Bus Signals and Definitions 4               | 0 |

| 5.2.1 | LSI-11 Bus Dialogues 5                             |   |

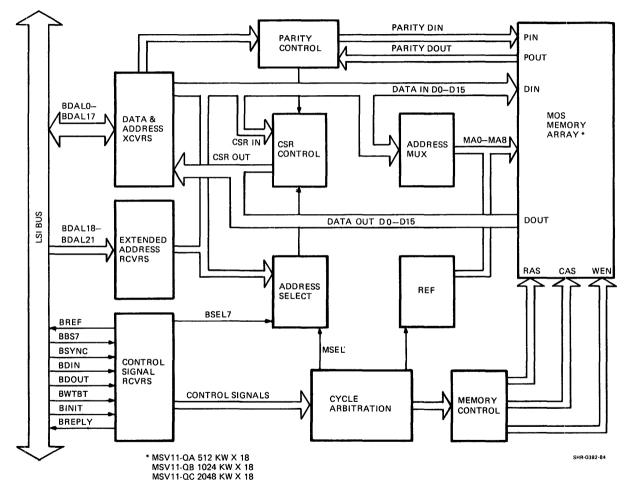

| 5.3   | Functional Description of Memory Module            | 8 |

| 5.3.1 | Xcvrs (Transmit - Receive) 5                       | 8 |

| 5.3.2 | Address Logic 5                                    | 8 |

| 5.3.3 | Control Signal Xcvrs 5                             | 8 |

| 5.3.4 | Address Select Logic 5                             | 8 |

| 5.3.5 | Cycle Arbitration 6                                | 0 |

| 5.3.6 | Memory Access 6                                    | 0 |

| 5.3.7 | Parity 6                                           | 1 |

| 5.4   | Control and Status Register (CSR) Bit Assignment 6 | 2 |

|       |                                                    |   |

#### CHAPTER 6 MAINTENANCE

| 6.1      | General 6                             | 35 |

|----------|---------------------------------------|----|

| 6.2      | Preventive Maintenance 6              | 6  |

| 6.2.1    | Visual Inspection 6                   | 6  |

| 6.2.2    | Power Voltage Check 6                 | 6  |

| 6.3      | Diagnostic Testing 6                  | 6  |

| 6.3.1    | MicroVAX Memory Diagnostic I (EHXMS)6 | 6  |

| 6.3.1.1  | Bootstrapping Procedure               | 57 |

| 6.3.1.2  | Operation 6                           | 57 |

| 6.3.1.3  | Command Syntax 6                      | 57 |

| 6.3.1.4  | Using the Commands 6                  | ;9 |

| 6.3.1.5  | Test Procedure 7                      | 1  |

| 6.3.1.6  | Error Messages 7                      | ΄3 |

| 6.3.2    | MSV11-Q Diagnostic (LSI-11 Bus)7      | '5 |

| 6.3.2.1  | Hardware Requirements7                | '5 |

| 6.3.2.2  | Software Requirements7                | '6 |

| 6.3.2.3  | Hardware Restrictions7                | ΄6 |

| 6.3.2.4  | Related Documents and Standards       | '6 |

| 6.3.2.5  | Diagnostic Hierarchy Prerequisites    | 6` |

| 6.3.2.6  | Assumptions 7                         | '6 |

| 6.3.2.7  | Loading the Program 7                 | 7  |

| 6.3.2.8  | Special Environments 7                | 7  |

| 6.3.2.9  | Program Options 7                     | 7  |

| 6.3.2.10 | Execution Times 7                     | 7  |

| 6.3.2.11 | Error Reporting 7                     | '8 |

| 6.3.2.12 | Error Halts 7                         | 8` |

| 6.3.2.13 | Sub-test Summaries 7                  | '9 |

| 6.3.2.14 | Toggle-In-Program 1 8                 | 51 |

| 6.3.2.15 | Toggle-In-Program 2 8                 | 32 |

| 6.4      | Digital's Services 8                  | 33 |

| 6.4.1    | Digital Repair Service 8              | 3  |

INDEX

#### FIGURES

| Module Identification                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jumper and Switch Locations MSV11-QA        | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Jumper Block Example                        | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Jumper Settings for CSR Address of 17772100 | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Enable/Disable CSR Selection                | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Enable/Disable Block Mode                   | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Enable/Disable Extended Error Address       | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Test Jumper                                 | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Enable/Disable Parity Error Detection       | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Battery Backup                              | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MSV11-Q Jumpers and Switches                | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Jumper Settings for CSR Address of 17772102 | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Manufacturing Test Jumpers                  | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Battery Backup                              | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Chip Select Jumpers                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

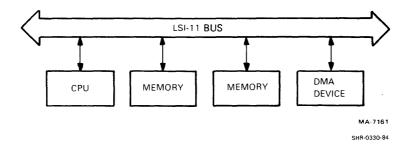

| Typical System                              | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

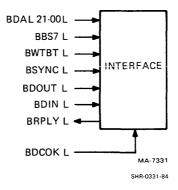

| MSV11-Q Memory Interface                    | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

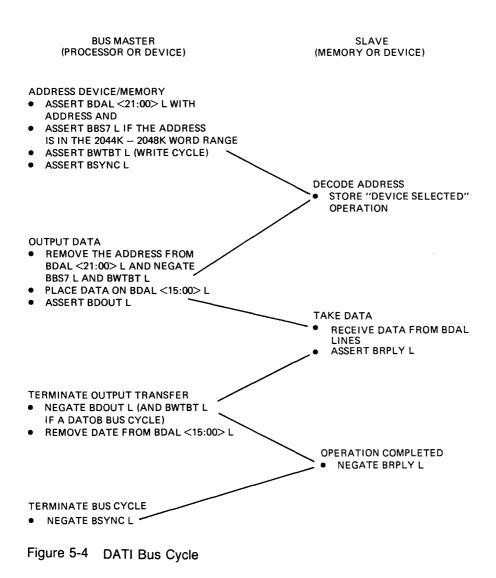

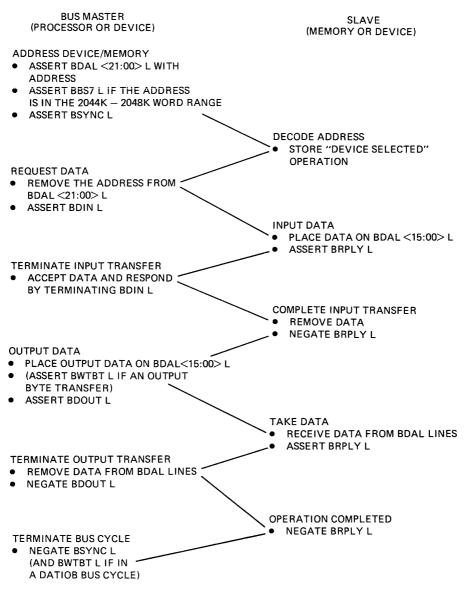

| DATO or DATOB Bus Cycle                     | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

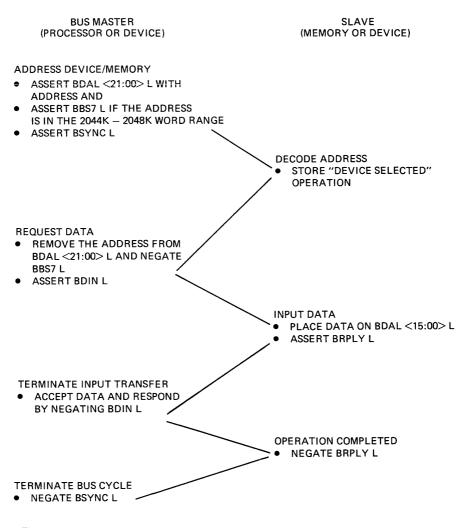

| DATI Bus Cycle                              | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DATIO or DATIOB Bus Cycle                   | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

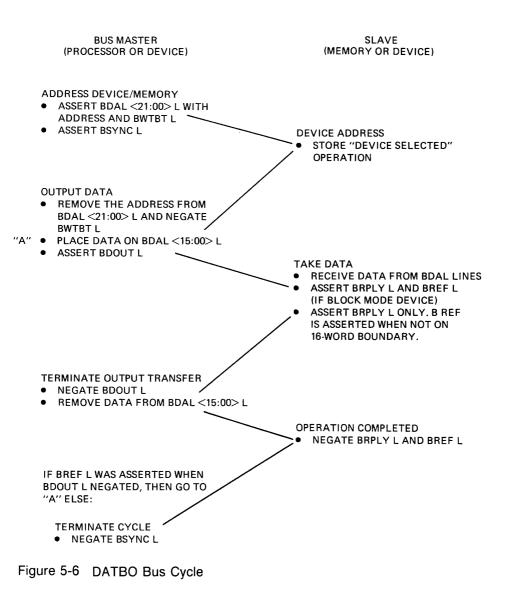

| DATBO Bus Cycle                             | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

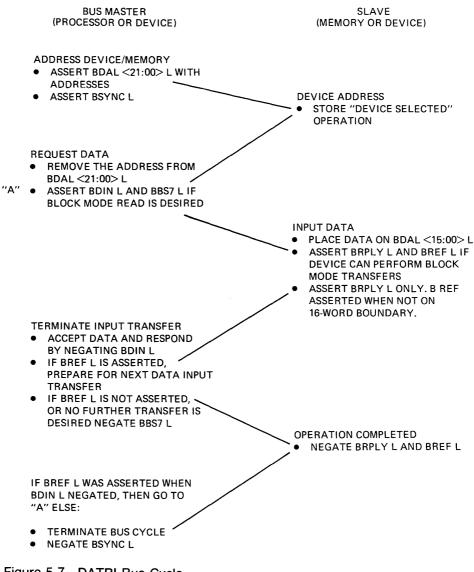

| DATBI Bus Cycle                             | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MSV11-Q Functional Block Diagram            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CSR Bit Allocation                          | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

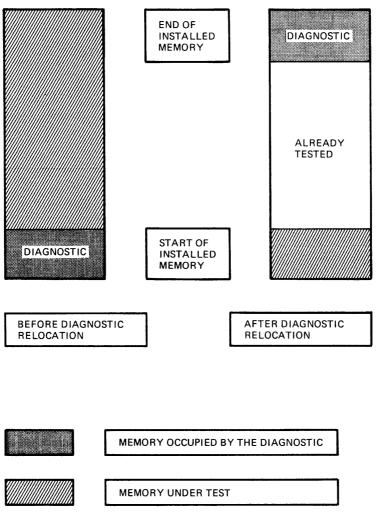

| Memory Diagnostic Relocation                | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sample Diagnostic Run for MSV11-QA/MSV-11P  | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                             | Jumper and Switch Locations MSV11-QA<br>Jumper Block Example<br>Jumper Settings for CSR Address of 17772100<br>Enable/Disable CSR Selection<br>Enable/Disable Block Mode<br>Enable/Disable Block Mode<br>Enable/Disable Extended Error Address<br>Test Jumper<br>Enable/Disable Parity Error Detection<br>Battery Backup<br>MSV11-Q Jumpers and Switches<br>Jumper Settings for CSR Address of 17772102<br>Manufacturing Test Jumpers<br>Battery Backup<br>Chip Select Jumpers<br>Battery Backup<br>MSV11-Q Memory Interface<br>DATO or DATOB Bus Cycle<br>DATI Bus Cycle<br>DATIO or DATIOB Bus Cycle<br>DATBO Bus Cycle<br>DATBI Bus Cycle<br>MSV11-Q Functional Block Diagram<br>CSR Bit Allocation<br>Memory Diagnostic Relocation |

#### TABLES

| 1-1   | MSV11-QA Access and Cycle Times                 | 5  |

|-------|-------------------------------------------------|----|

| 1-2   | MSV11-QA, MSV11-QB, and MSV11-QC Access and     |    |

|       | Cycle Times                                     | 6  |

| 1-3   | Voltage Pins (MSV11-QA)                         | 8  |

| 1-4   | Voltage Pins [MSV11-QA, MSV11-QB, and MSV11-QC] | 8  |

| 1-5   | MSV11-QA Power                                  | 9  |

| 1-6   | MSV11-QB Power 1                                | 10 |

| 1-7   | MSV11-QC Power 1                                | 11 |

| 1-8   | Backplane Pin Utilization (MSV11-QA) 1          | 13 |

| 1-9   | Backplane Pin Utilization (MSV11-QA, MSV11-QB,  |    |

|       | MSV11-QC) 1                                     | 14 |

| 2-1   | CSR Register Selection 2                        | 20 |

| 2-2   | Starting and Ending Address Selection           | 24 |

| 3-1   | CSR Register Selection                          | 30 |

| 3-2   | Starting and Ending Address Selection           | 33 |

| 5-1   | Summary of Bus Cycles 4                         | 40 |

| 5-2   | Bus Signals                                     | 41 |

| 5-3   | Dialogues to Perform Memory Data Transfers      | 52 |

| 6-1   | Control Keys 6                                  | 38 |

| 6-2   | Command Summary 6                               | 38 |

| 6.3.1 | MicroVAX Memory Diagnostic 1 (EHXMS)6           | 36 |

| 6.3.2 | MSV11-Q Diagnostic (LSI-11 Bus)7                | '5 |

|       |                                                 |    |

### CHARACTERISTICS AND SPECIFICATIONS

#### **1.1 INTRODUCTION**

This manual describes the MSV11-Q memory module. The module contains metal oxide semiconducters (MOS) random access memory (RAM). It is used with the LSI-11 bus and provides 1024K byte to 4096K byte storage for 18-bit words (16 data bits and 2 parity bits). It also contains parity control circuitry and a control and status register (CSR).

There are four variations of the MSV11-Q module.

- MSV11-QA (etch revision A) 64K RAMs fully populated; cannot be configured for battery backup

- MSV11-QA (etch revision C or later) 64K RAMs fully populated; can be configured for battery backup

- MSV11-QB 256K RAMs half populated; can be configured for battery backup

- MSV11-QC 256K RAMs fully populated; can be configured for battery backup

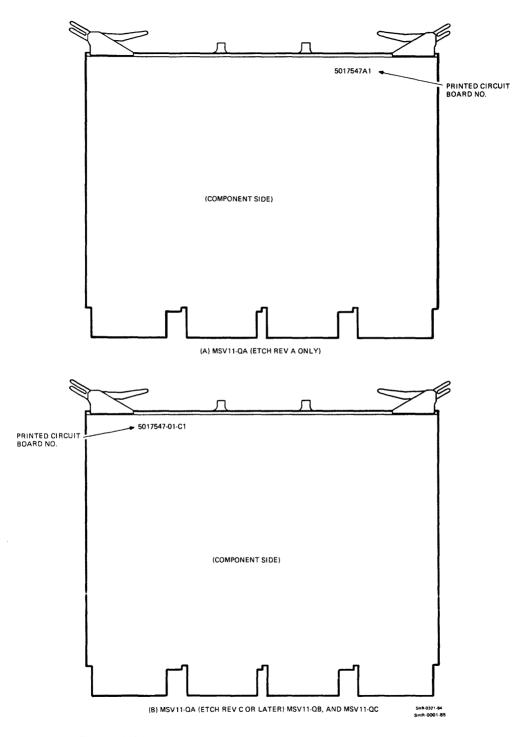

The MSV11-QA (etch revision A) is indicated as shown in Figure 1-1A. Differences between the MSV11-QA, etch revision A, and the other variations will be pointed out as they occur.

The MSV11-QA (etch revision C), MSV11-QB, and MSV11-QC all use the same etch (refer to Figure 1-1B).

Figure 1-1 Module Identification

The major features of the MSV11-Q are:

- 1 megabyte of MOS memory on a single quad module (MSV11-QA).

2 megabyte of MOS memory on a single quad module (MSV11-QB).

4 megabyte of MOS memory on a single quad module (MSV11-QC).

- 22-bit addressing standard.

- Parity is generated and checked for each byte for data integrity.

- Self-contained Control and Status Register (CSR) for full parity implementation.

- Full parity control enables the CPU to trap on a parity error with LED display for parity status.

- Completely LSI hardware and software compatible.

- Switch selectable starting address in 128K byte increments.

- 16 jumper selectable CSR addresses (17772100 through 17772136).

- Single +5 V power. MSV11-QA (etch revision A) does not support battery backup.

- Supports Block-Mode for efficient multiple DMA transfer.

#### **1.2 GENERAL DESCRIPTION**

The MSV11-Q memory module consists of a single, quad-height module (M7551) that contains the LSI-11 bus interface, timing and control logic, refresh circuitry, and a MOS storage array. The module also contains circuitry to generate and check parity, and a control and status register. The MSV11-Q memory uses +5 V from the backplane.

The memory module's starting address can be set on any 128 KB boundary within the 4096 KB LSI-11 address space or 256 KB LSI-11 address space. The MSV11-Q allows the top 4K of the LSI-11 address space to be reserved for the I/O peripheral page. There is no address interleaving with the MSV11-Q.

The memory storage elements for the MSV11-QA are 65,536 by 1 bit MOS dynamic RAM devices. The storage elements for the MSV11-QB and MSV11-QC are 262,144 by 1 bit MOS dynamic RAM devices. The MOS storage array for the MSV11-QA and MSV11-QC has 8 rows with each row containing 18 devices for a total of 1024K bytes on the MSV11-QA and 4 megabytes on the MSV11-QC. The MSV11-QB is half populated and therefore contains 4 rows for a total of 2 megabytes of memory. The read operation for MOS storage devices is non-destructive. The MOS storage devices must be refreshed every 12.0  $\mu$ s so that the data remains valid.

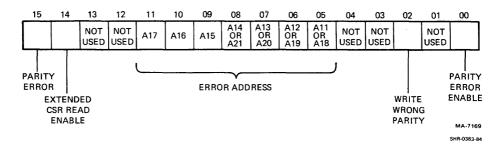

The control and status register in the MSV11-Q contains bits used to store the parity error address bits. You can force wrong parity by setting a bit in the CSR. This is a useful diagnostic tool for checking out the parity logic. The CSR has its own address in the top 4K of memory. Bus masters can read or write to the CSR.

The parity control circuitry in the MSV11-Q generates parity bits based on data being written into memory during a DATO or DATOB bus cycle. One parity bit is assigned to each data byte and is stored with the data in the MOS storage array. When data is retrieved from memory during DATI or DATIO bus cycles, the parity of the data is determined. If parity is good, the data is assumed correct. If the parity bits do not correspond, the data is assumed unreliable and memory initiates the following action.

1. If a parity error occurs, CSR bit 15 is set and a red LED on the module lights.

In the case of MSV11-QA (etch revision C or later), MSV11-QB and MSV11-QC, the memory asserts BDAL 16 and 17 if bit 0 in the CSR is set. This warns the processor that a parity error has occurred. For this to occur in the MSV11-QA (etch revision A), jumper H must be connected (refer to Paragraph 2.2.7).

2. Part of the address of the faulty data is recorded in the CSR.

#### 1.3 SPECIFICATIONS

This section gives functional, electrical, and environmental specifications and backplane pin utilization information. The specifications in this section are applicable to all variations of the MSV11-Q memory except where differences are noted.

#### 1.3.1 Functional Specifications

Table 1-1 provides access and cycle time specifications for the MSV11-QA (etch revision A) memory. Table 1-2 provides access and cycle times for the other MSV11-Q variations.

|                             |                       | T <sub>acc(ns</sub>   | )                       | <sup>T</sup> cyc(ns) |                    |                         |  |  |

|-----------------------------|-----------------------|-----------------------|-------------------------|----------------------|--------------------|-------------------------|--|--|

|                             | Meas<br>Typ           | Max                   | Notes                   | Meas<br>Typ          | Мах                | Notes                   |  |  |

| Parity-CSR Col              | nfigurations (        | (Notes 1,8            | 8,9)                    |                      |                    |                         |  |  |

| DATI<br>DATO(B)<br>DATIO(B) | 320<br>350<br>1000    | 358<br>376<br>1045    | 2<br>2<br>3             | 520<br>550<br>1220   | 578<br>597<br>1255 | 4<br>5<br>6             |  |  |

| DATBI                       | 320<br>20<br>320<br>- | 358<br>31<br>376<br>- | 2<br>10<br>11,12<br>N/A | -<br>-<br>-<br>520   | -<br>-<br>-<br>569 | N/A<br>N/A<br>N/A<br>15 |  |  |

| DATBO                       | 350<br>20<br>280<br>- | 387<br>31<br>668<br>- | 2<br>10<br>13,14<br>N/A | -<br>-<br>500        | -<br>-<br>547      | N/A<br>N/A<br>N/A<br>16 |  |  |

| Table 1-1 | MSV11-QA | (etch | revision | A) | Access | and | Cycle | Times |

|-----------|----------|-------|----------|----|--------|-----|-------|-------|

|-----------|----------|-------|----------|----|--------|-----|-------|-------|

|               | Meas         | T <sub>acc(ns</sub> | 5)    | <sup>T</sup> cyc( | ns)  |               |

|---------------|--------------|---------------------|-------|-------------------|------|---------------|

|               | Тур          | Мах                 | Notes | Тур               | Max  | Meas<br>Notes |

| Parity-CSR Co | nfigurations | (Notes 1,           | 8,9)  |                   |      |               |

| DATI          | 320          | 358                 | 2     | 510               | 563  | 4             |

| DATO(B)       | 160          | 18 <del>9</del>     | 2     | 550               | 592  | 5             |

| DATIO(B)      | 780          | 847                 | 3     | 1220              | 1250 | 6             |

| DATBI         | 320          | 358                 | 2     | _                 | _    | N/A           |

|               | 20           | 31                  | 10    | _                 | -    | N/A           |

|               | 340          | 363                 | 11,12 | -                 |      | N/A           |

|               | -            | -                   | N/A   | 518               | 569  | 15            |

| DATBO         | 160          | 189                 | 2     | _                 | -    | N/A           |

|               | 20           | 31                  | 10    | _                 | _    | N/A           |

|               | 250          | 292                 | 13,14 | -                 | _    | N/A           |

|               | -            | -                   | N/A   | 655               | 695  | 16            |

### Table 1-2MSV11-QA (Etch Revision C or Later), MSV11-QB, and<br/>MSV11-QC Access and Cycle Times

The following notes (1 through 16) refer to Tables 1-1 and 1-2.

Notes for DATI, DATO(B), DATIO(B) Cycles:

- 1. Assuming memory not busy and no arbitration.

- 2. SYNCH to RPLYH with minimum times (25/50 ns) from SYNCH to (DINH/DOUTH). The DATO(B) access and cycle times assume a minimum of 50 ns from SYNCH to DOUTH inside memory receivers. For actual LSI-11 bus measurements, a constant (K-50 ns) where K = 200 ns should be added to DATI(B) times, i.e. acc (Typ) = 100 + (200 - 50) = 250 ns.

- 3. SYNCH to RPLYH DATIO(B), with minimum time (25 ns) from SYNCH to DINH and minimum 350 ns from RPLYH (DATI) asserted to DOUT asserted.

- 4. SYNCH to MBSY L negated.

- 5. SYNCH to MBSY L negated with minimum time (50 ns) from SYNCH to DOUTH.

- 6. SYNCH to MBSY L (DATIO(B)) with minimum times (25 ns) from SYNCH to DINH and minimum 350 ns from RPLYH (DATI) asserted to DOUT asserted.

- 7. REF REQ L to MBSY L negated.

- 8. The MSV11-Q Module does not lose any time due to refresh arbitration.

- 9. REFRESH conflict adds 250 ns Typical and 542 ns maximum to access and cycle time.

Notes for DATBI AND DATBO Cycles:

- 10. DIN/DOUT negation to MRPLY negation

- 11. DIN negation to TRPLY assertion

- 12. DIN remains asserted for 200 ns minimum after TRPLY with 150 ns minimum from TRPLY negation to assertion of next DIN.

- 13. DOUT remains asserted for 150 ns minimum after TRPLY with 150 ns minimum from TRPLY negation to assertion of next DOUT.

- 14. DOUT assertion to TRPLY assertion.

- 15. DIN negation to MBSY L negation after first DIN cycle. Use DATI cycle time for first DIN/TRPLY cycle in block mode ready cycle.

- 16. DOUT assertion to MBSY L negation after first DOUT cycle. Use DATO(B) cycle time for first DOUT/TRPLY cycle in block mode write cycle.

#### **1.3.2 Electrical Specifications**

The electrical specifications state the voltage and power requirements for the MSV11-Q.

**1.3.2.1 Voltages –** Single voltage MOS RAMs require only +5 V. Voltage margins for +5 V are  $\pm 5$  percent (Tables 1-3 and 1-4).

**1.3.2.2 Power Requirements** – Power requirements are provided in Tables 1-5, 1-6 and 1-7.

#### 8 CHARACTERISTICS AND SPECIFICATIONS

| Table 1-3 Voltage Pins (MSV11-QA, Etch Revision A | Table 1-3 | Voltage Pin | is (MSV11-QA, | Etch | <b>Revision A</b> | ) |

|---------------------------------------------------|-----------|-------------|---------------|------|-------------------|---|

|---------------------------------------------------|-----------|-------------|---------------|------|-------------------|---|

| Voltage | Pins                    | Service                     |  |

|---------|-------------------------|-----------------------------|--|

| +5 V    | AA2, BA2, BV1, CA2, DA2 | Single voltage<br>MOS RAMs* |  |

| Table 1-4 | Voltage Pins [MSV11-QA (Etch Revision QB, and MSV11-QC] | on C or Later,) MSV11-     |

|-----------|---------------------------------------------------------|----------------------------|

| Voltage   | Backplane Pins                                          |                            |

| +5 V      | AA2,BA2,BV1,CA2, and DA2                                | Single voltage<br>MOS RAMs |

| +5 V BBU  | AV1, and AE1*                                           |                            |

|           |                                                         |                            |

\* Check backplane voltages to ensure proper configurations.

|                              | Curre<br>Standby | nt (Amps     | active          |              |  |  |  |  |

|------------------------------|------------------|--------------|-----------------|--------------|--|--|--|--|

|                              | Typ<br>Measured  | Max          | Typ<br>Measured | Мах          |  |  |  |  |

| +5 V total<br>+5 V BBU total | 1.0<br>1.28      | 1.32<br>2.33 | 1.0<br>1.4      | 1.32<br>2.67 |  |  |  |  |

| Module total                 | 2.28             | 3.65         | 2.4             | 3.99         |  |  |  |  |

#### Table 1-5 MSV11-QA Power (All Etch Revisions)

|                              | Pov<br>Standby  |               |                 |               |

|------------------------------|-----------------|---------------|-----------------|---------------|

|                              | Typ<br>Measured | Max           | Typ<br>Measured | Max           |

| +5 V total<br>+5 V BBU total | 5.0<br>6.4      | 6.93<br>12.23 | 5.0<br>7.0      | 6.93<br>14.02 |

| Module total                 | 11.4            | 19.16         | 12.0            | 20.95         |

#### MSV11-QA With 64K RAMs Fully Populated

#### Table 1-6 MSV11-QB Power

|                              | Currer<br>Standby | nt (Amps)    | Active          |               |

|------------------------------|-------------------|--------------|-----------------|---------------|

|                              | Typ<br>Measured   | Max          | Typ<br>Measured | Мах           |

| +5 V total<br>+5 V BBU total | 1.0<br>1.18       | 1.32<br>1.66 | 1.00<br>1.30    | 1.32<br>2.27  |

| Module total                 | 2.18              | 2.98         | 2.30            | 3.59          |

|                              | Power<br>Standby  | r (Watts)    | Active          |               |

|                              | Typ<br>Measured   | Max          | Typ<br>Measured | Max           |

| +5 V total<br>+5 V BBU total | 5.0<br>5.90       | 6.93<br>8.72 | 5.0<br>6.50     | 6.93<br>11.92 |

| Module total                 | 10.90             | 15.65        | 11.50           | 18.85         |

|                              | Currer<br>Standby | nt (Amps)     | Active          |               |  |

|------------------------------|-------------------|---------------|-----------------|---------------|--|

|                              | Typ<br>Measured   | Max           | Typ<br>Measured | Max           |  |

| +5 V total<br>+5 V BBU total | 1.0<br>1.34       | 1.32<br>2.37  | 1.0<br>1.50     | 1.32<br>2.98  |  |

| Module total                 | 2.34              | 3.69          | 2.50            | 4.30          |  |

|                              | Power<br>Standby  | r (Watts)     | Active          | <u>,,</u>     |  |

|                              | Typ<br>Measured   | Мах           | Typ<br>Measured | Мах           |  |

| +5 V total<br>+5 V BBU total | 5.00<br>6.70      | 6.93<br>12.44 | 5.00<br>7.50    | 6.93<br>15.65 |  |

| Module total                 | 11.70             | 19.37         | 12.50           | 22.58         |  |

#### Table 1-7 MSV11-QC Power

MSV11-QC With 256K BAMs Fully Populated

#### **1.3.3 Environmental Specifications**

Environmental specifications cover storage and operating temperature, relative humidity, altitude, and air flow specifications.

**1.3.3.1 Temperature** – Temperature is separated into the following two groups.

1. Operating Temperature Range – The operating temperature range is +5°C to +60°C. Lower the maximum operating temperature by 1°C for every 1000 feet of altitude above 8000 feet.

Storage Temperature Range – The storage temperature range is -40°C to +66°C. Do not operate a module that has been stored outside the operating temperature range before bringing the module to an environment within the operating range and allowing at least five minutes for the module to stabilize.

**1.3.3.2 Relative Humidity** – The relative humidity for the MSV11-QA memory modules must be 10% to 90 percent noncondensing for storage or operating conditions.

**1.3.3.3 Operating Airflow** – Adequate airflow must be provided to limit the inlet to outlet temperature rise across the module to  $5^{\circ}$ C when the inlet temperature is +60°C. For operation below +55°C, airflow must be provided to limit the inlet to outlet temperature rise across the module to  $10^{\circ}$ C maximum.

**1.3.3.4** Altitude – The module resists mechanical or electrical damage at altitudes up to 50,000 feet (90 MM mercury) under storage or operating conditions.

*NOTE:* Lower the maximum operating temperature by 1°C for every 1000 feet of altitude above 8000 feet.

#### 1.3.4 Refresh

The MSV11-Q memory module uses a self-contained refresh oscillator, with rate that is typically 535 ns every 12,000 ns. The refresh overhead maximum is 542 ns/12,500 ns or 4.3 percent.

#### 1.3.5 Diagnostics

The diagnostics are CVMSAA for 22-bit systems and EHXMS for MicroVAX.

#### 1.3.6 Backplane Pin Utilization

Backplane pin utilization for the MSV11-QA (etch revision A) is shown in Table 1-8. Backplane pin utilization for the MSV11-QA (etch revision C or later), MSV11-QB and MSV11-QC is shown in Table 1-9. Blank spaces indicate pins not used.

|     | A Connector B Connecto |          | B Connector | C Connector |        |         | D Connector |        |

|-----|------------------------|----------|-------------|-------------|--------|---------|-------------|--------|

| Pin | Side 1                 | Side 2   | Side 1      | Side 2      | Side 1 | Side 2  | Side 1      | Side 2 |

| A   |                        | +5 V     | BDCOK H     | +5 V        |        | +5 V    | <u></u>     | +5 V   |

| в   | —                      |          | _           |             |        |         |             | —      |

| С   | BDAL 16L               | GND      | BDAL 18L    | GND         |        | GND     |             | GND    |

| D   | BDAL 17L               |          | BDAL 19L    | —           |        |         |             |        |

| *E  | +5 V BB                | BDOUT L  | BDAL 20L    | BDAL 02L    |        |         |             |        |

| F   |                        | BRPLY L  | BDAL 21L    | BDAL 03L    |        |         |             |        |

| Н   |                        | BDIN L   |             | BDAL 04L    | В      |         | В           | В      |

| J   | GND                    | BSYNC L  | GND         | BDAL 05L    | L      |         | L           | L      |

| К   | REFKILL                | BWTBT L  |             | BDAL 06L    | А      |         | А           | А      |

| L   |                        |          | —           | BDAL 07L    | N      |         | N           | N      |

| М   | GND                    | *BIAKIL  | GND         | BDAL 08L    | к      | *BIAKIL | к           | К      |

| Ν   | _                      | *BIAKOL  |             | BDAL 09L    |        | *BIAKOL |             |        |

| Р   | _                      | BBS7L    |             | BDAL 10L    |        | _       |             |        |

| R   | BREF L                 | *BDMGIL  |             | BDAL 11L    |        | *BDMGIL |             |        |

| S   | —                      | *BDMGOL  |             | BDAL 12L    |        | *BDMGOL |             |        |

| т   | GND                    | BINIT L  | GND         | BDAL 13L    | GND    |         | GND         |        |

| U   |                        | BDALOO L |             | BDAL 14L    |        |         |             |        |

| *V  | +5 V BB                | BDALO1 L | +5 V        | BDAL 15L    |        | _       |             |        |

Table 1-8

Backplane Pin Utilization (MSV11-QA, Etch Revision A)

\* Hardwired via etch on module. If a system uses the pin for anything but power, user must cut gold finger AE1 on the board.

|     | A Connector |          | B Connector |          | C Connector |         | D Connector |        |

|-----|-------------|----------|-------------|----------|-------------|---------|-------------|--------|

| Pin | Side 1      | Side 2   | Side 1      | Side 2   | Side 1      | Side 2  | Side 1      | Side 2 |

| A   |             | +5 V     | BDCOK H     | +5 V     |             | +5 V    |             | +5 V   |

| В   |             |          | —           | —        |             |         |             |        |

| С   | BDAL 16L    | GND      | BDAL 18L    | GND      |             | GND     |             | GND    |

| D   | BDAL 17L    |          | BDAL 19L    |          |             | _       |             |        |

| Е   | +5 V BB     | BDOUT L  | BDAL 20L    | BDAL 02L |             |         |             |        |

| F   |             | BRPLY L  | BDAL 21L    | BDAL 03L |             | _       |             |        |

| Н   |             | BDIN L   |             | BDAL 04L | В           |         | В           | В      |

| J   | GND         | BSYNC L  | GND         | BDAL 05L | L           |         | L           | L      |

| к   | REFKILL     | BWTBT L  |             | BDAL 06L | А           |         | Α           | А      |

| L   |             |          |             | BDAL 07L | Ν           |         | N           | N      |

| М   | GND         | *BIAKIL  | GND         | BDAL 08L | к           | *BIAKIL | к           | к      |

| Ν   |             | *BIAKOL  |             | BDAL 09L |             | *BIAKOL |             |        |

| Р   |             | BBS7L    | _           | BDAL 10L |             | _       |             |        |

| R   | BREF L      | *BDMGIL  |             | BDAL 11L |             | *BDMGIL |             |        |

| S   | _           | *BDMGOL  |             | BDAL 12L |             | *BDMGOL |             |        |

| т   | GND         | BINIT L  | GND         | BDAL 13L | GND         |         | GND         |        |

| U   |             | BDALOO L |             | BDAL 14L |             |         | _           |        |

| V   | +5 V BB     | BDALO1 L | +5 V        | BDAL 15L | —           |         |             |        |

Table 1-9 Backplane Pin Utilization (MSV11-QA, Etch Revision C or Later, MSV11-QB, MSV11-QC)

\* Hardwired via etch on module.

NOTE: If you are using AE1 (sspare 1) for anything other than battery backup voltage (+5 V BB), jumper W1 must not be installed. However, Digital Equipment Corporation recommends backpanel pin <AE1> be used as +5.0 V battery backup power in this application. Refer to Paragraph 3.2.3 for additional information.

#### **1.3.7 Electrical Specifications**

#### 1.3.7.1 Power Supply Requirements – The module operates on +5 V only.

#### 1.3.8 Bus Loading

MSV11-QA (etch revision A)

AC load units = 1.9DC load units = 0.5

MSV11-QA (etch revision C)

AC load units = 2.4DC load units = 0.5

#### 1.4 RELATED DOCUMENTS

Refer to the following documents for more information.

- MSV11-QA, MSV11-QB, and MSV11-QC (all etch revisions) Field Maintenance Printset (MP01931)

- Microcomputer and Memory Handbook (EB-18451-20)

- Microcomputer Interface Handbook (EB-20175-20)

- LSI-11 System Service Manual (EK-LSI-FS-SV)\*

- MicroVAX I Owner's Manual (EK-KD32A-OM) (For Diagnostics Section)

These documents can be ordered from:

Digital Equipment Corporation 444 Whitney Street Northboro, MA 01532

ATTN: Communications Services (NR2/M15) Customer Services Section

<sup>\*</sup> Field Service Use Only

## $\underset{(\text{MSV11-QA, ETCH REVISION A)}{\text{CONFIGURATION}}{2}$

#### 2.1 GENERAL

This chapter contains information for configuring the MSV11-QA memory module (etch revision A). Jumper and address switch settings are included.

NOTE: Configuration and installation for the MSV11-QA (etch revision C or later), and the MSV11-QB and MSV11-QC are provided in Chapter 3.

#### 2.2 CONFIGURING THE MSV11-QA (Etch Revision A)

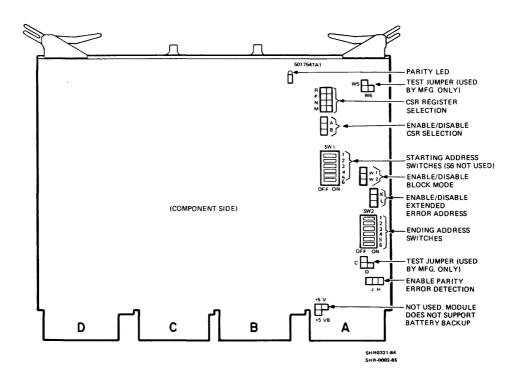

The MSV11-QA (etch revision A) has one red LED to indicate parity errors. The module contains the following jumpers (Figure 2-1).

- Test jumper (W5, W6)

- CSR register selection jumpers (R, P, N, M)

- Enable/disable CSR selection jumper (A, B)

- Enable/disable block mode jumper (W1, W2)

- Enable extended error address jumper (K, L)

- Test jumper (C, D)

- Enable parity error detection jumper (J, H)

- +5 V/+5 VB

The MSV11-QA has two DIP (dual in-line package) switch packs. Each DIP switch pack consists of six switches. The two DIP switch packs are used to set:

- Starting address.

- Ending address.

Figure 2-1 Jumper and Switch Locations MSV11-QA (Etch Revision A)

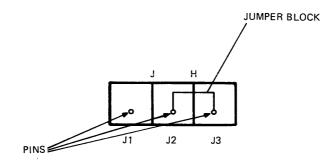

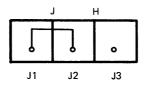

Figure 2-1 shows the physical location of the jumpers and switches. The jumpers and switches are described in the following paragraphs. To jumper two pins, a 0 ohm connector block is used. For example, to enable parity error detection, jumper H (Figure 2-2) is connected (pin J2 to J3) and to disable parity error detection, jumper J is connected (pin J1 to J2). Factory configuration has parity error detection enabled.

a. PARITY ERROR DETECTION ENABLED

b. PARITY ERROR DETECTION DISABLED

SHR-0322-84

Figure 2-2 Jumper Block Example

#### 2.2.1 Test Jumper (W5, W6)

This test jumper is used by manufacturing and should not be changed. W6 should be jumpered and W5 should be open.

#### 2.2.2 CSR Register Selection (R, P, N, M) Jumpers

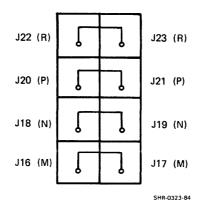

The MSV11-QA can provide up to 16 CSR register address selections when the user installs or removes appropriate jumper blocks (Figure 2-2). For example, in Figure 2-2, the parity error detection jumper block is shown. Table 2-1 shows the jumper positions and the corresponding CSR register addresses. Figure 2-3 shows the jumper settings for a CSR register address of 17772100.

| Jumper Position |                                                                                                    |                                                                                                                                                                                                                                            |                                                                                                                                                 |                                                                                                                                                                                                                 |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R               | Ρ                                                                                                  | Ν                                                                                                                                                                                                                                          | М                                                                                                                                               | CSR Register Address                                                                                                                                                                                            |  |  |  |

| in              | in                                                                                                 | in                                                                                                                                                                                                                                         | in                                                                                                                                              | 17772100                                                                                                                                                                                                        |  |  |  |

| out             | in                                                                                                 | in                                                                                                                                                                                                                                         | in                                                                                                                                              | 17772102                                                                                                                                                                                                        |  |  |  |

| in              | out                                                                                                | in                                                                                                                                                                                                                                         | in                                                                                                                                              | 17772104                                                                                                                                                                                                        |  |  |  |

| out             | out                                                                                                | in                                                                                                                                                                                                                                         | in                                                                                                                                              | 17772106                                                                                                                                                                                                        |  |  |  |

| in              | in                                                                                                 | out                                                                                                                                                                                                                                        | in                                                                                                                                              | 17772110                                                                                                                                                                                                        |  |  |  |

| out             | in                                                                                                 | out                                                                                                                                                                                                                                        | in                                                                                                                                              | 17772112                                                                                                                                                                                                        |  |  |  |

| in              | out                                                                                                | out                                                                                                                                                                                                                                        | in                                                                                                                                              | 17772114                                                                                                                                                                                                        |  |  |  |

| out             | out                                                                                                | out                                                                                                                                                                                                                                        | in                                                                                                                                              | 17772116                                                                                                                                                                                                        |  |  |  |

| in              | in                                                                                                 | in                                                                                                                                                                                                                                         | out                                                                                                                                             | 17772120                                                                                                                                                                                                        |  |  |  |

| out             | in                                                                                                 | in                                                                                                                                                                                                                                         | out                                                                                                                                             | 17772122                                                                                                                                                                                                        |  |  |  |

| in              | out                                                                                                | in                                                                                                                                                                                                                                         | out                                                                                                                                             | 17772124                                                                                                                                                                                                        |  |  |  |

| out             | out                                                                                                |                                                                                                                                                                                                                                            |                                                                                                                                                 | 17772126                                                                                                                                                                                                        |  |  |  |

| in              | in                                                                                                 |                                                                                                                                                                                                                                            |                                                                                                                                                 | 17772130                                                                                                                                                                                                        |  |  |  |

|                 |                                                                                                    |                                                                                                                                                                                                                                            |                                                                                                                                                 | 17772132                                                                                                                                                                                                        |  |  |  |

|                 |                                                                                                    |                                                                                                                                                                                                                                            |                                                                                                                                                 | 17772134                                                                                                                                                                                                        |  |  |  |

| out             | out                                                                                                | out                                                                                                                                                                                                                                        | out                                                                                                                                             | 17772136                                                                                                                                                                                                        |  |  |  |

|                 | R<br>in<br>out<br>in<br>out<br>in<br>out<br>in<br>out<br>in<br>out<br>in<br>out<br>in<br>out<br>in | R P<br>in in<br>out in<br>in out<br>out out<br>in in<br>out in<br>in out<br>out out<br>in in<br>out out<br>in in<br>out out<br>in in<br>out out<br>in<br>in<br>out out<br>in<br>in<br>out<br>out<br>out<br>out<br>out<br>out<br>out<br>out | RPNinininoutinininoutininoutinoutoutinininoutoutinoutoutinoutoutinoutoutinininoutoutoutinininoutininoutininoutininoutoutininoutinoutoutinoutout | RPNMinininininoutinininininoutinininoutoutinininoutoutinoutinininoutoutinoutinoutoutinoutinoutoutinoutoutoutoutininoutininoutoutoutinoutoutinoutinoutoutininoutoutoutinoutoutoutoutinoutoutoutoutinoutoutoutout |  |  |  |

#### Table 2-1 CSR Register Selection

If more than one CSR parity type of memory is installed in the system, use care to ensure that no two modules have the same address.

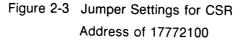

#### 2.2.3 Enable/Disable CSR Selection Jumper (Figure 2-4)

This jumper disables CSR selection when non-parity memory is used. Since the MSV11-QA is a parity memory, this jumper should be set for "enable CSR selection" (jumper B connected).

Figure 2-4 Enable/Disable CSR Selection

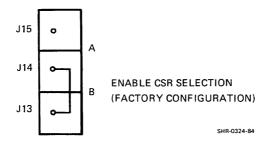

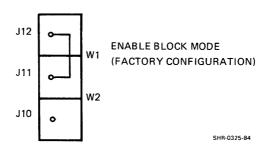

#### 2.2.4 Enable/Disable Block Mode Jumper (Figure 2-5)

This jumper enables or disables block mode operation. The jumper should be set for ''enable block mode'' (jumper W1 connected).

#### 2.2.5 Enable/Disable Extended Error Address Jumper (Figure 2-6)

This jumper selects 18- or 22-bit addressing. The jumper should be set for "enable extended error address" (jumper L connected).

Figure 2-6 Enable/Disable Extended Error Address

#### 2.2.6 Test Jumper C, D (Figure 2-7)

This jumper is a test jumper for use by manufacturing. Jumper C should be connected and jumper D should be open.

Figure 2-7 Test Jumper

#### 2.2.7 Enable Parity Error Detection Jumper (Figure 2-8)

This jumper enables or disables parity error detection. The jumper should be set for "enable parity error detection" (jumper H connected).

Figure 2-8 Enable/Disable Parity Error Detection

#### 2.2.8 Battery Backup (Figure 2-9)

Not used or supported in etch revision A of MSV11-QA.

Figure 2-9 Battery Backup

#### 2.2.9 Address Switches

There are two DIP (dual-in-line package) switch packs on the MSV11-QA module. DIP switch pack SW1, containing six switches, selects the starting address. DIP switch pack SW2, containing six switches, selects the ending address. The starting address is set first and then the ending address is set to a number greater than the starting address. Table 2-2 shows the switch settings for the starting addresses and ending addresses. Switch 6 of SW1 is not used. Switch 6 of SW2 is turned on or enabled (0) for a starting address of all 0's and is turned off or disabled (1) for all other starting addresses.

| Desired<br>Starting<br>Address | SW 1<br>Switch<br>Position | SW 2<br>Switch<br>Position | Desired<br>Ending<br>Address | SW 2<br>Switch<br>Position |

|--------------------------------|----------------------------|----------------------------|------------------------------|----------------------------|

| In Kbyte                       | 12345                      | 6                          | In Kbyte                     | 12345                      |

| 0                              | 00000                      | 0                          | 128                          | 11111                      |

| 128                            | 11111                      | 1                          | 256                          | 01111                      |

| 256                            | 01111                      | 1                          | 384                          | 10111                      |

| 384                            | 10111                      | 1                          | 512                          | 00111                      |

| 512                            | 00111                      | 1                          | 640                          | 11011                      |

| 640                            | 11011                      | 1                          | 768                          | 01011                      |

| 768                            | 01011                      | 1                          | 896                          | 10011                      |

| 896                            | 10011                      | 1                          | 1024 (1 MB)                  | 00011                      |

| 1024 (1 MB)                    | 00011                      | 1                          | 1152 `                       | 11101                      |

| 1152                           | 11101                      | 1                          | 1280                         | 01101                      |

| 1280                           | 01101                      | 1                          | 1408                         | 10101                      |

| 1408                           | 10101                      | 1                          | 1536                         | 00101                      |

| 1536                           | 00101                      | 1                          | 1664                         | 11001                      |

| 1664                           | 11001                      | 1                          | 1792                         | 01001                      |

| 1792                           | 01001                      | 1                          | 1920                         | 10001                      |

| 1920                           | 10001                      | 1                          | 2048 (2 MB)                  | 00001                      |

| 2048 (2 MB)                    | 00001                      | 1                          | 2176                         | 11110                      |

| 2176                           | 11110                      | 1                          | 2304                         | 01110                      |

| 2304                           | 01110                      | 1                          | 2432                         | 10110                      |

| 2432                           | 10110                      | 1                          | 2560                         | 00110                      |

#### Table 2-2 Starting and Ending Address Selection

|                                | -                          | -                          | •                            | •                          |

|--------------------------------|----------------------------|----------------------------|------------------------------|----------------------------|

| Desired<br>Starting<br>Address | SW 1<br>Switch<br>Position | SW 2<br>Switch<br>Position | Desired<br>Ending<br>Address | SW 2<br>Switch<br>Position |

| In Kbyte                       | 12345                      | 6                          | In Kbyte                     | 12345                      |

| 2560                           | 00110                      | 1                          | 2688                         | 11010                      |

| 2688                           | 11010                      | 1                          | 2816                         | 01010                      |

| 2816                           | 01010                      | 1                          | 2944                         | 10010                      |

| 2944                           | 10010                      | 1                          | 3072 (3 MB)                  | 00010                      |

| 3072 (3 MB)                    | 00010                      | 1                          | 3200                         | 11100                      |

| 3200                           | 11100                      | 1                          | 3328                         | 01100                      |

| 3328                           | 01100                      | 1                          | 3456                         | 10100                      |

| 3456                           | 10100                      | 1                          | 3584                         | 00100                      |

| 3584                           | 00100                      | 1                          | 3712                         | 11000                      |

| 3712                           | 11000                      | 1                          | 3840                         | 01000                      |