# **u note Reprints**

It took the minicomputer company to make micros this easy.

# TABLE OF CONTENTS

# PAGE NO.

| 001  | Battery Backup                                                    | 1          |

|------|-------------------------------------------------------------------|------------|

| 005  | IEEE BUS SUB-SPECS                                                | 4          |

| 009  | Hex and Quad Hold-Down Bracket for LSI-11<br>Systems              | 5          |

| 010A | Power Supply for H909C                                            | 6          |

| 011  | LSI-11 HALTING DURING INTERRUPT CYCLE                             | 8          |

| 012  | LSI-11 Bus Theory of Operation                                    | 10         |

| 013  | Installing APL-11 on 11V03 and 11T03                              | 19         |

| 014  | Correct Input Parameters for the QJV11 PROM<br>Formatting Program | 20         |

| 015  | Power Sequcencing for the KD11-HA Module                          | 22         |

| 017  | LSI-11/2 Processor Clock                                          | 25         |

| 018  | DR11-C vs. DRV11                                                  | 26         |

| 019  | EIA RS-422 and RS-423                                             | 30         |

| 020  | 9 X 6 Slot Backplane Documentation Error                          | 34         |

| 021  | Comparison of Data Transmission Techniques                        | 35         |

| 023  | USING THE MSV11-D 30K OPTION                                      | 40         |

| 024A | Async., Serial Line Unit Comparisons                              | 41         |

| 025  | Configuring Memory Systems with MSV11-D<br>RAM & PROM             | 46         |

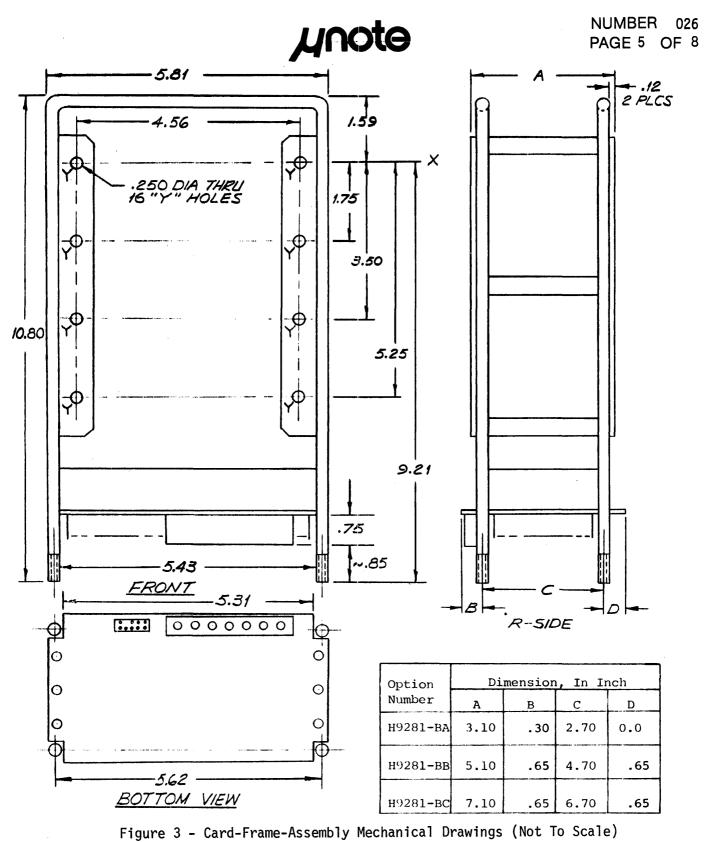

| 026  | Micro Backplane Mechanical Mounting<br>Guidelines                 | 48         |

| 027A | PROM CHIPS AVAILABLE UNDER PART # MRV11-AC                        | 56         |

| 028  | Extended Memory for the LSI-11                                    | 5 <b>7</b> |

| 029  | Using the MRV11-AA for a Bootstrap ROM                            | 69         |

| 030  | SRUN SIGNAL                                                       | 71         |

| 032  | Extended Bus Time-Out Logic                                       | 73         |

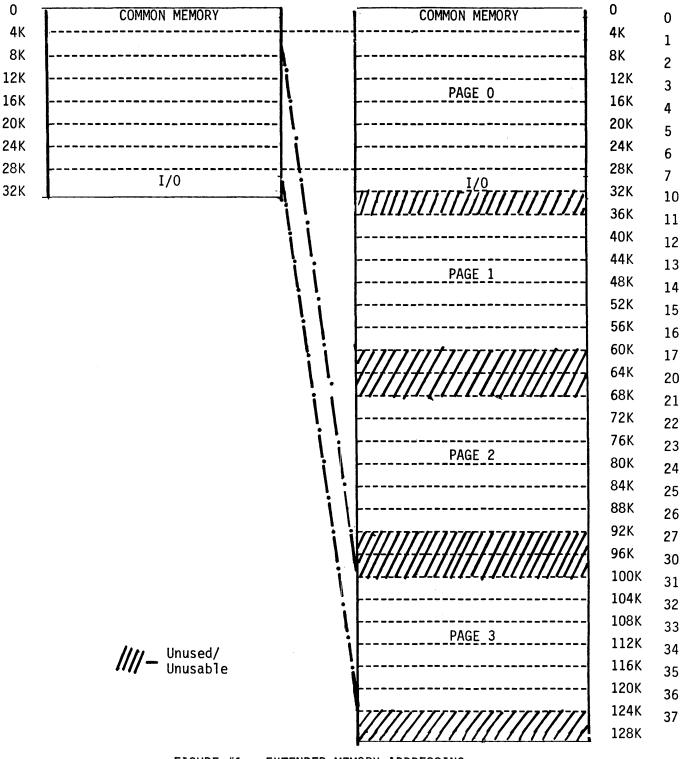

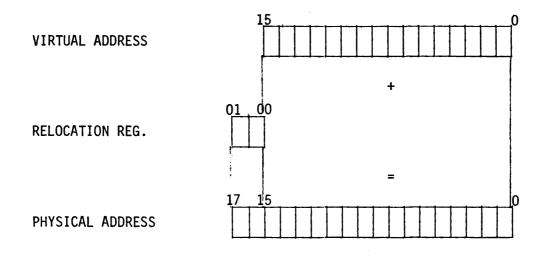

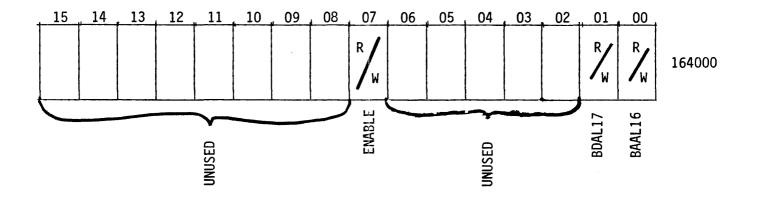

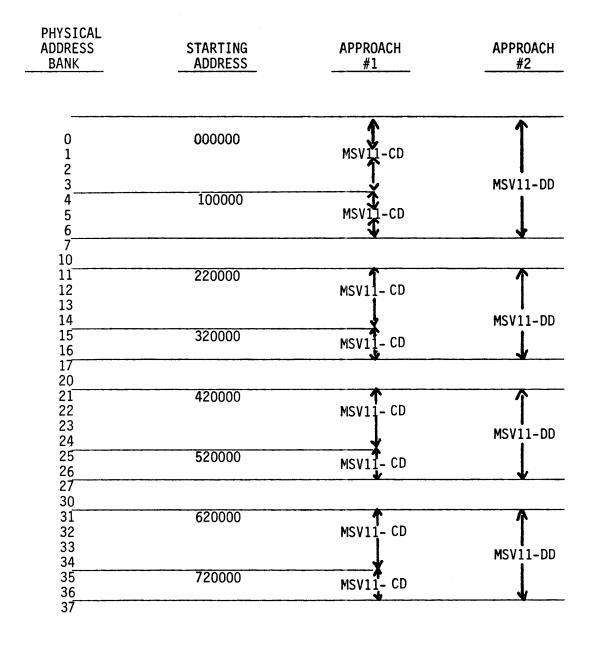

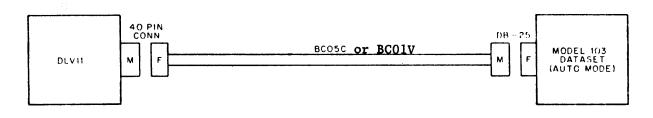

| 033  | Cables for DLV11, DLV11-E, DLV11-F                                | 76         |

| 034  | Configuring a 3-Box 11/03 System                                  | 78          |

|------|-------------------------------------------------------------------|-------------|

| 035  | PROM Programming                                                  | 80          |

| 036  | Core Memory in 11/03-L Backplane                                  | 81          |

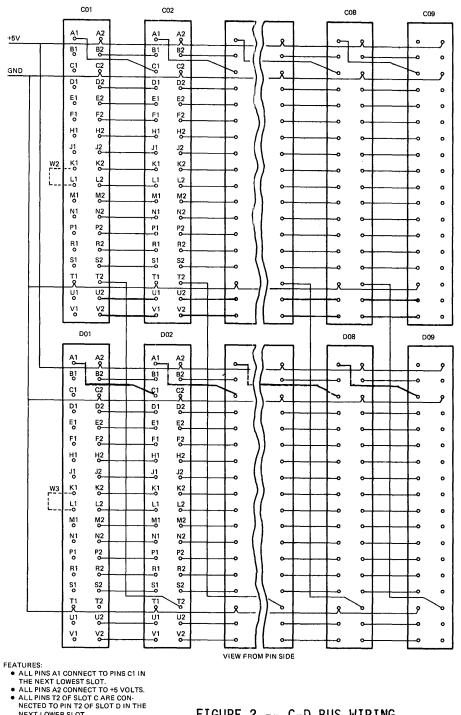

| 037  | C-D Interconnect Scheme                                           | 82          |

| 038  | DIAGNOSTICS FOR 30K MEMORIES ON LSI-11'S                          | 85          |

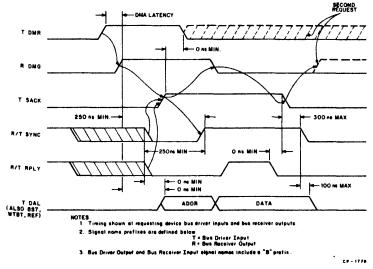

| 039  | DMA Request/Grant Timing                                          | 86          |

| 040  | Patches for BASIC/PTS on LSI-11                                   | 88          |

| 041  | New Functionality for BDV11-AA Boot                               | 90          |

| 042  | Removing Modules from "Live" Backplanes                           | 91          |

| 043  | BACKPLANES FOR THE RLV11 (RLO1)                                   | 93          |

| 044  | Console ODT "L" Command on 30K Systems                            | 95          |

| 046A | DLV11-F Replacement for the DLV11                                 | 96          |

| 047  | INCOMPATIBILITY BETWEEN THE REV11 AND THE LSI-11/23               | 99          |

| 048  | LSI-11/23 INSTRUCTION TIMING (PRELIMINARY)                        | 101         |

| 049  | System Differences - LSI-11 vs. LSI-11/23                         | 111         |

| 050  | MICRO ODT DIFFERENCES - LSI-11 vs. LSI-11/23                      | 113         |

| 051  | DIGITAL SUPPORTED PROM'S                                          | 116         |

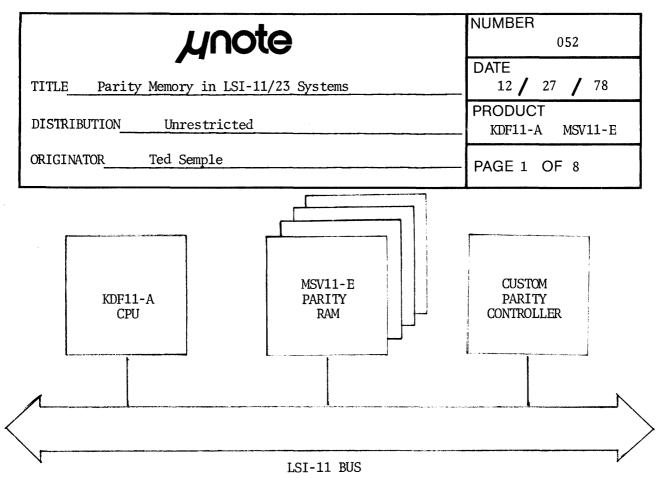

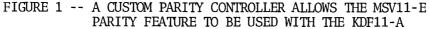

| 052  | Parity Memory in LSI-11/23 Systems                                | 117         |

| 053  | PDP-11 FAMILY DIFFERENCES                                         | 125         |

| 054  | MXV11 Configuration                                               | 136         |

| 055  | LSI-11 vs. LSI-11/23 Bus Timing                                   | 141         |

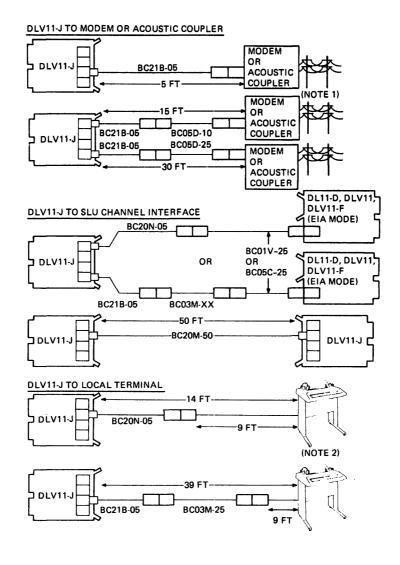

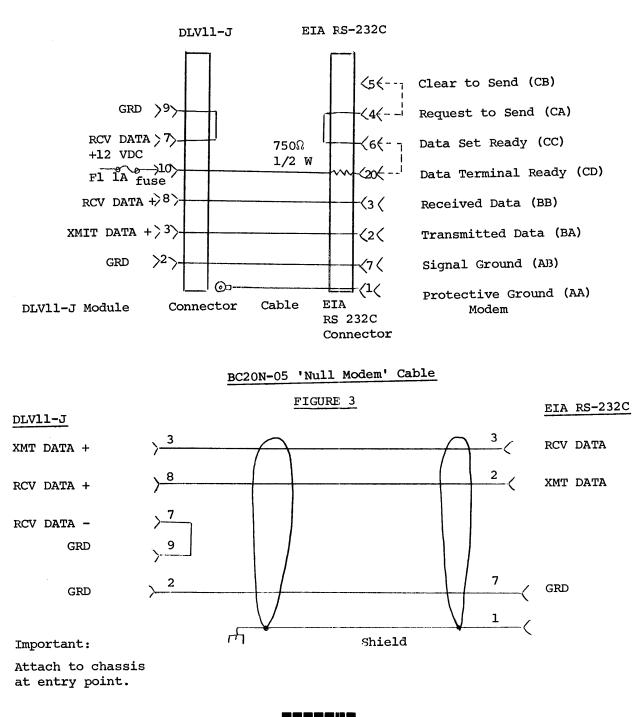

| 056  | DLV11-J CABLING                                                   | 143         |

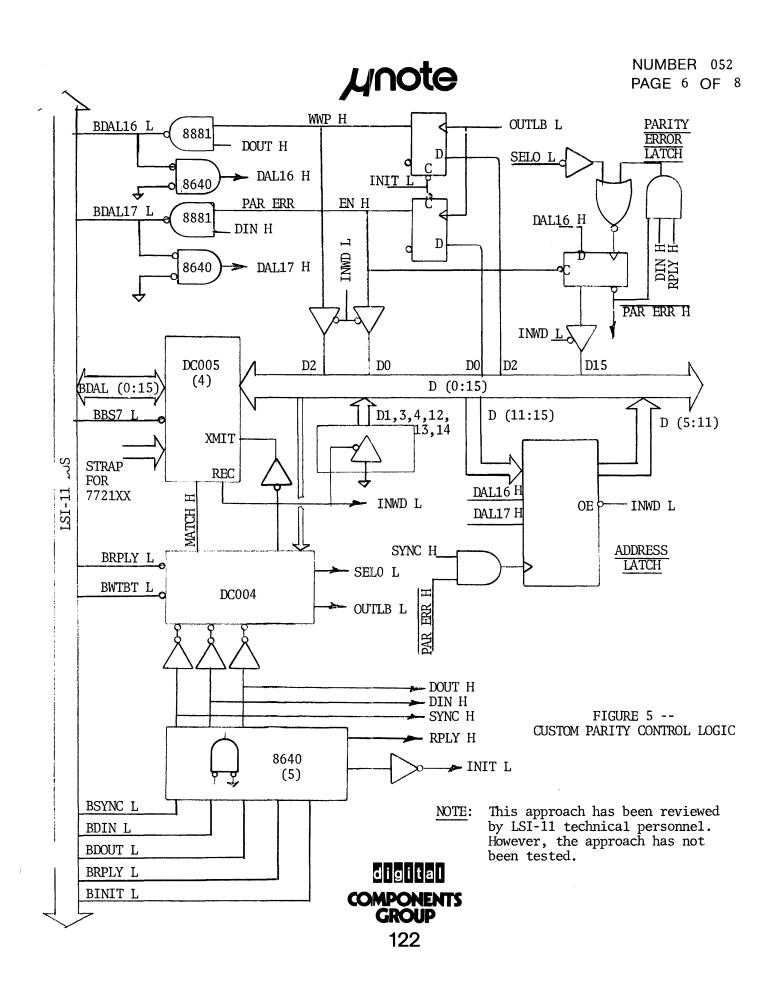

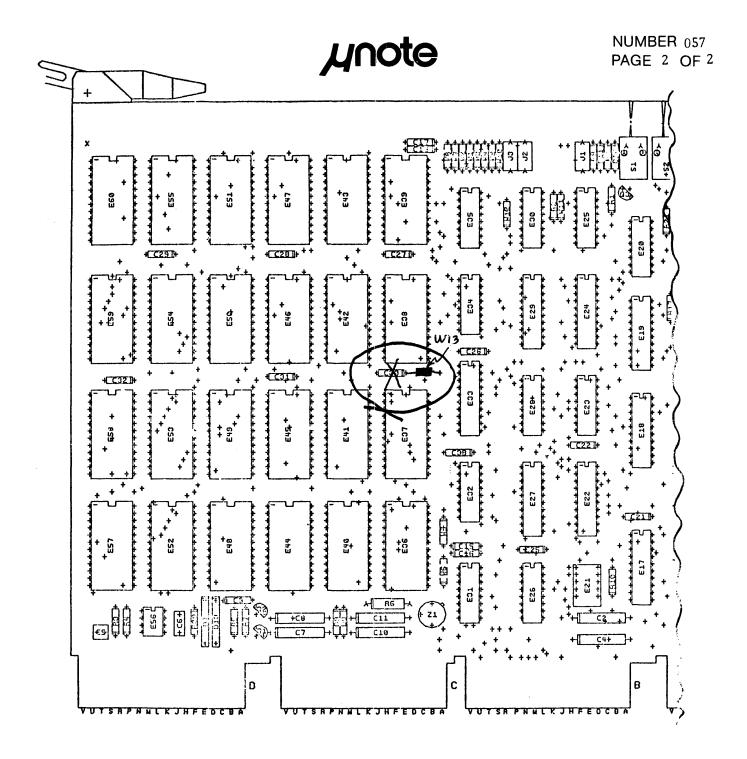

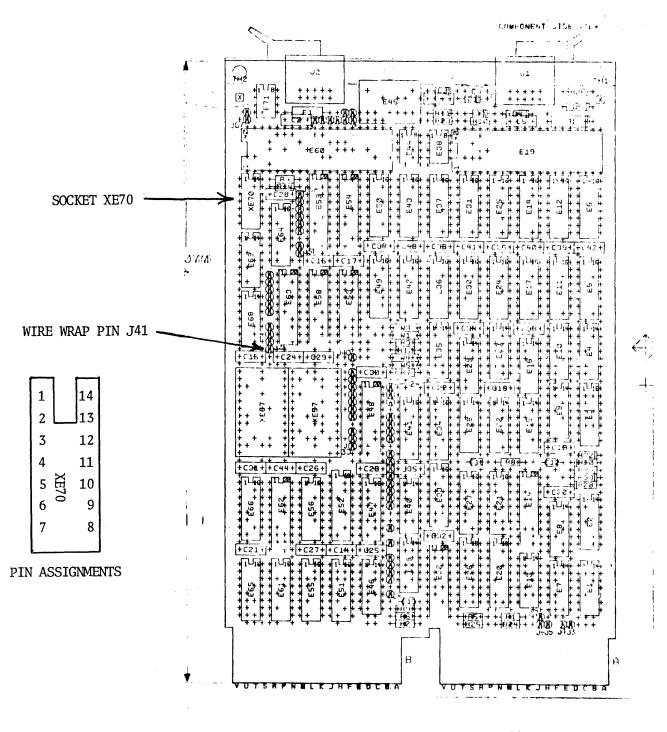

| 057  | Location of W13 on the BDV11                                      | <u>1</u> 47 |

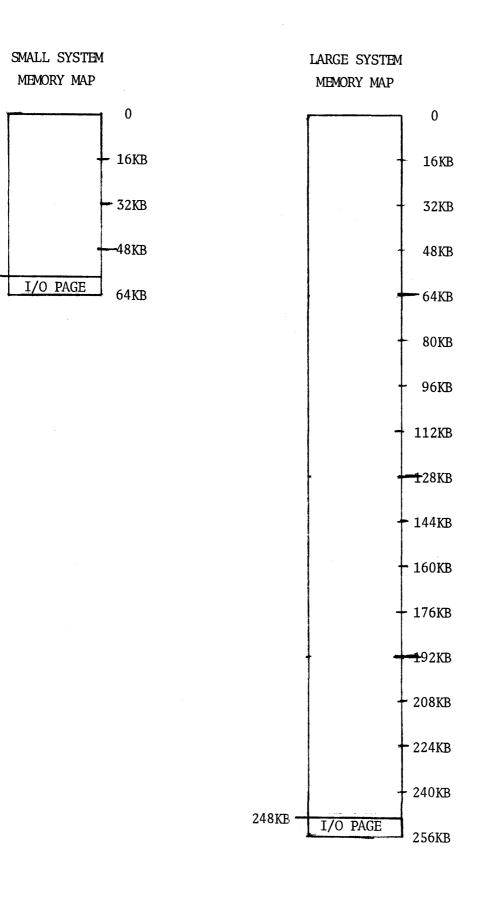

| 058  | Configuring Memory for LSI-11 Systems<br>with More than 64K Bytes | 149         |

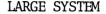

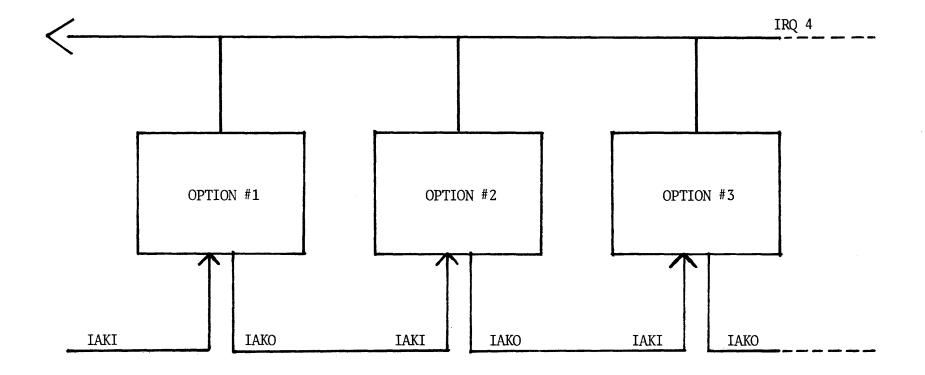

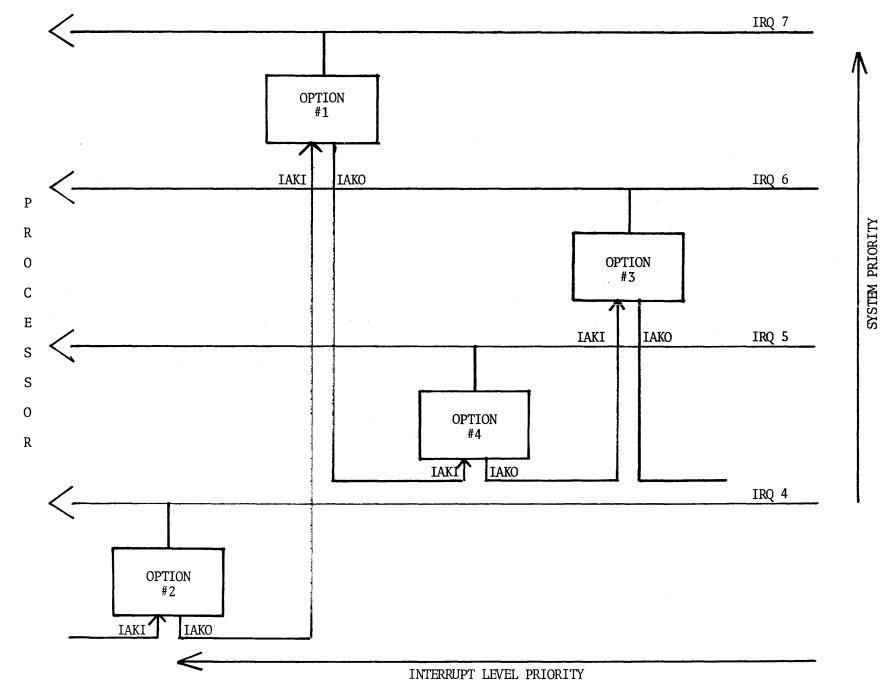

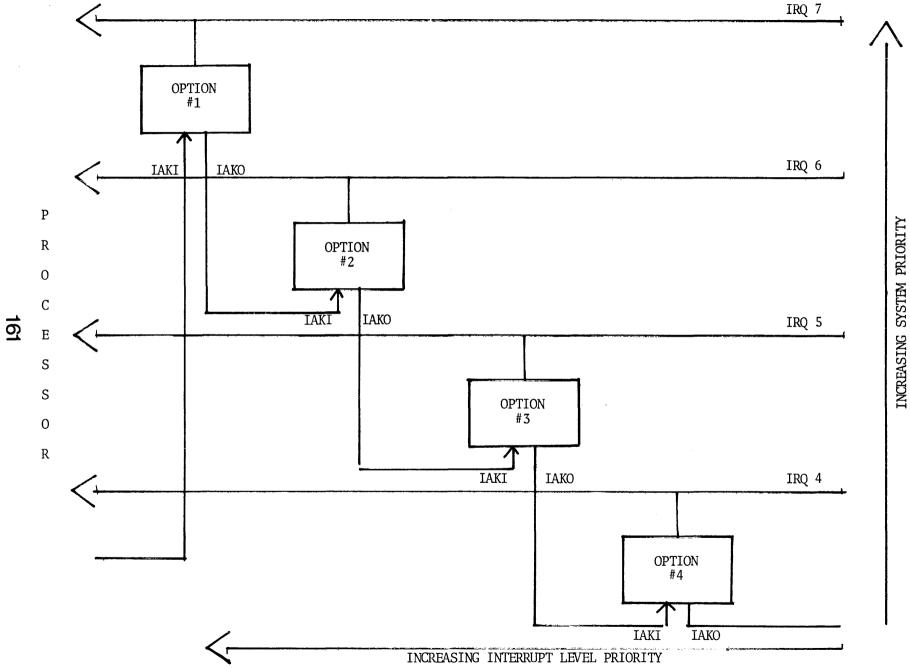

| 059  | LSI-11/23 Four-Level Interrupts                                   | 155         |

| 060  | MAXIMUM CONFIGURATION OF DLV11-J MODULES                          | 162         |

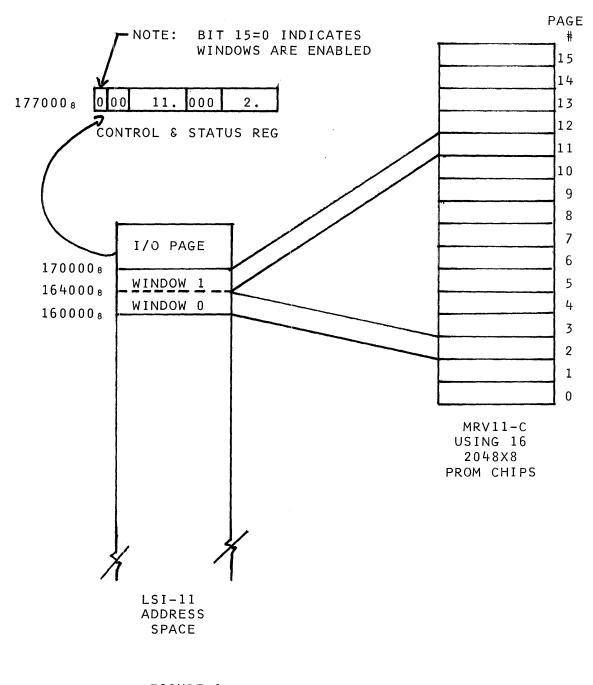

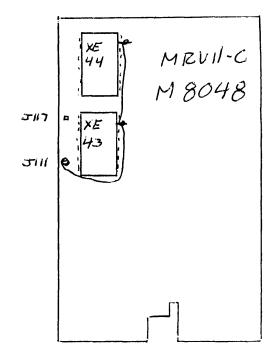

| 061  | Programming the MRV11-C                              | 164 |

|------|------------------------------------------------------|-----|

| 062  | Bootstraps for TU58, RL01, RK05, RX02, RX01          | 173 |

| 063  | RLO1 Type-In Bootstrap                               | 204 |

| 064  | DLV11-J I/O Page Address Problem Report              | 205 |

| 065  | BOOTSTRAP FOR RX02                                   | 207 |

| 066  | 11/23 FLOATING POINT COMPATIBILITY                   | 210 |

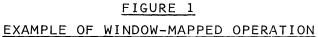

| 067A | DLV11-J RECEIVER CHIP PROBLEM                        | 211 |

| 068  | Microcomputer Module Environmental<br>Considerations | 213 |

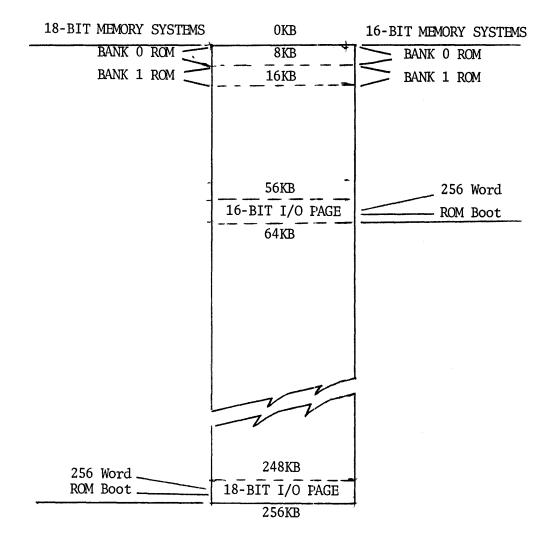

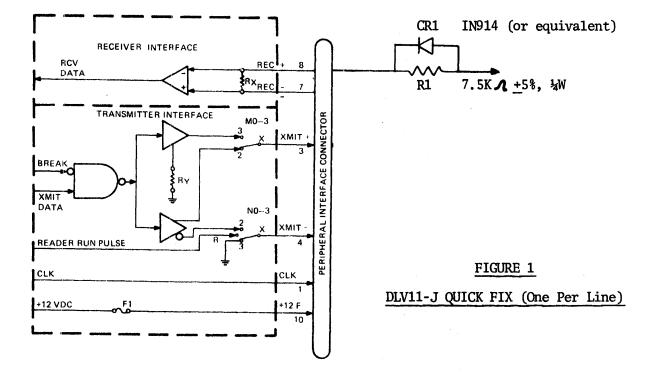

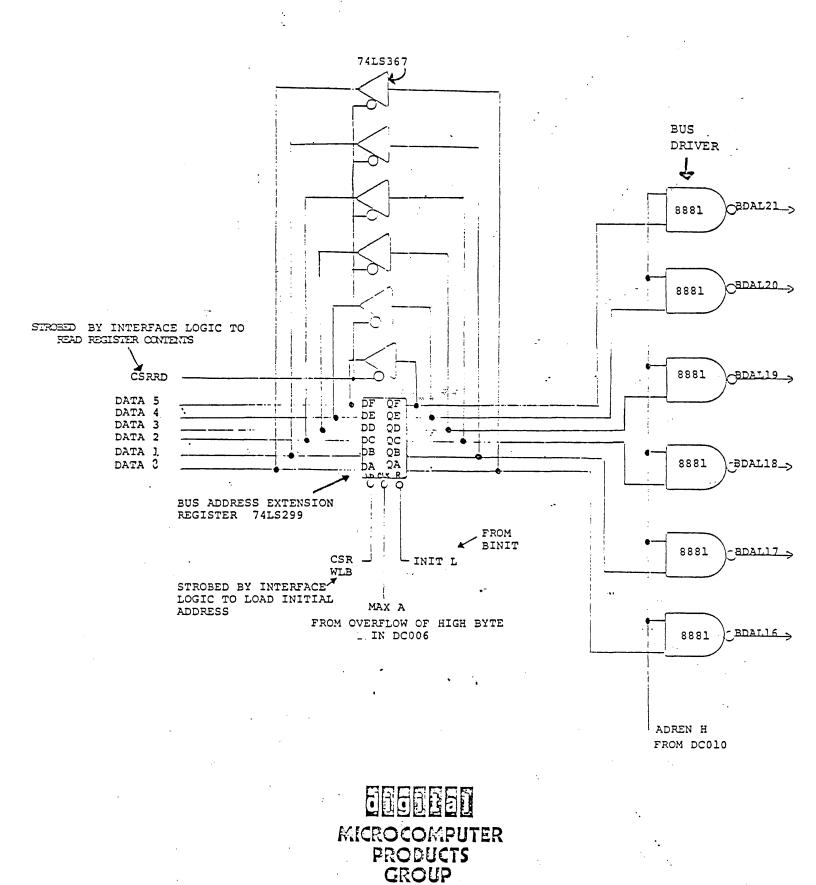

| 069  | 18-BIT DMA WITH CHIPKITS                             | 214 |

| 070  | LSI-11 vs. LSI-11/23 TRANSACTION DIFFERENCES         | 216 |

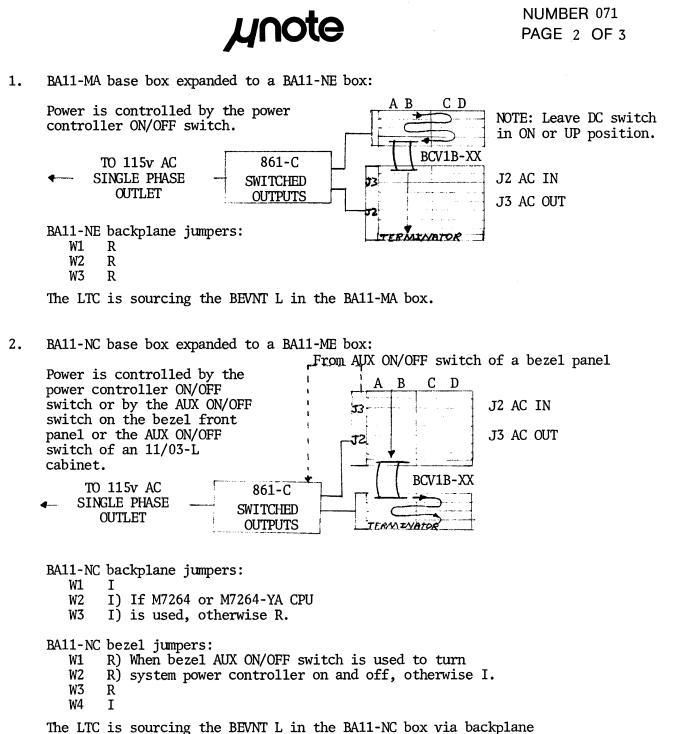

| 071  | Expanding BA11-MA and BA11-NC Based Systems          | 218 |

| 072  | Peripheral Compatibility with 11/23 Systems          | 221 |

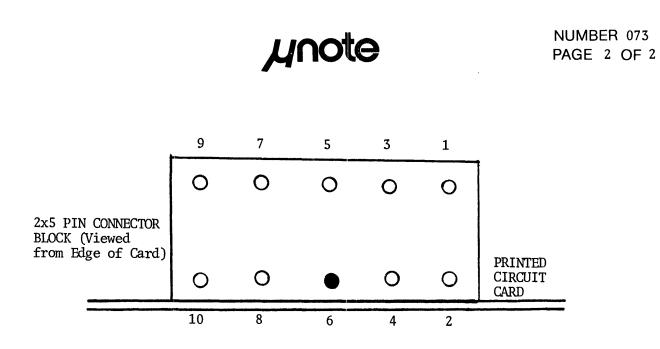

| 073  | TU58 Cabling                                         | 223 |

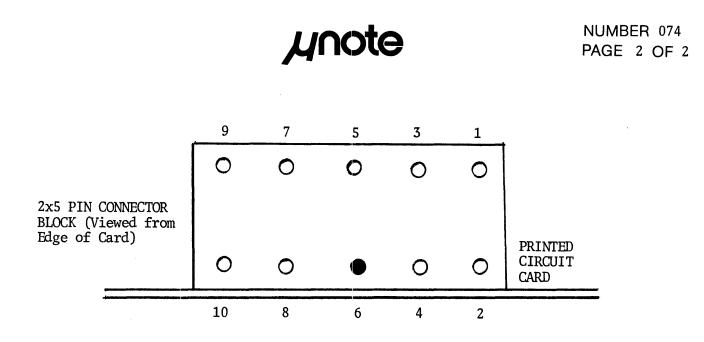

| 074  | MXV11-AA, -AC CABLING                                | 225 |

| 075  | MXV11-A2 Bootstrap Error Halts                       | 227 |

| 077  | Summary of Bootstrap Sources                         | 230 |

| 078  | LSI-11/23 PROCESSOR DIFFERENCES                      | 231 |

| 079  | The LSI-11/23 and the LSI-11/2 Buses are the Same    | 233 |

| 080A | LSI-11/23 I/O Page Addressing                        | 234 |

| 081  | Use of Recommended Diskettes                         | 236 |

| 082  | Handlers for Serial Line Printers                    | 237 |

| 083  | Alternate Clock Frequencies for the MXV11            | 248 |

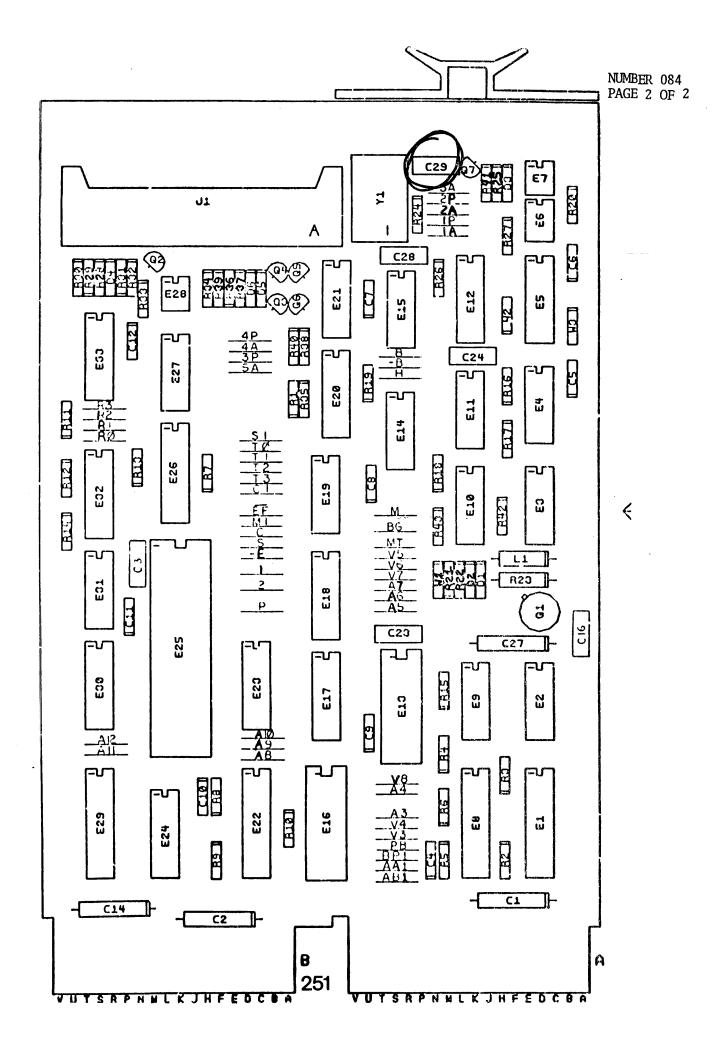

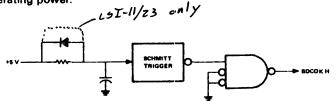

| 084  | Improved DLV11-F                                     | 250 |

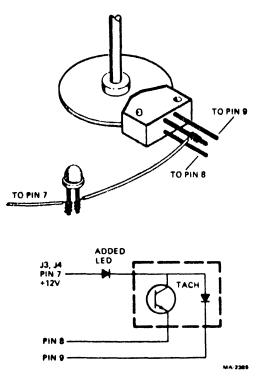

| 085  | WAKE-UP CIRCUIT IMPLEMENTATIONS                      | 252 |

|      |                                                      |     |

| <i>H</i> note             | NUMBER<br>001     |

|---------------------------|-------------------|

| TITLE BATTERY BACKUP      | DATE<br>4 / 1 /77 |

| DISTRIBUTION UNRESTRICTED | PRODUCT           |

| ORIGINATOR JOE AUSTIN     | MSV11-C (M7955)   |

|                           | PAGE 1 OF 3       |

#### SCOPE

The function of this note is to furnish the information necessary to provide battery backup for the MSV11-C 16K MOS RAM module. Specific recommendations for the battery, charger, and DC-DC converters will not be covered at this time.

Additional information on the MSV11-C is contained in the "MSV11-C Users Manual", document number EK-MSV11-OP.

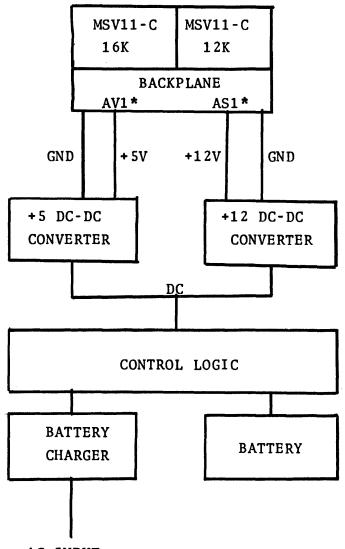

#### SYSTEM DESCRIPTION

A block diagram showing two MSV11-C modules providing 28K words of memory is shown in Figure 2. Each 16K module is plugged into a standard backplane with the battery power connected to pins AV1 (+5V) and AS1 (+12V) as shown. These two voltages are sourced by DC-DC converters/regulators which are connected directly to the battery. A charger is provided which is connected to the battery and converters by control logic. The function of the control logic is to disconnect the charger when AC power is lost, to disconnect the battery from the converters when it discharges too low, and to switch to a trickle-charge once the battery has been fully charged.

## FUNCTIONAL REQUIREMENTS

To properly implement this system, the following conditions must be met:

1. The battery power required to back up the two modules is:

| +5V <u>+</u> 3\$ | 1.6 A type (2.8A max)  |

|------------------|------------------------|

| +12V <u>+</u> 3% | 0.32 A type (0.4A max) |

These voltages must remain within +3% of the voltages for the LSI-11 at all times, and must not change by more than +3% during the transition for the battery.

Hunote

NUMBER 001 PAGE 2 OF 3

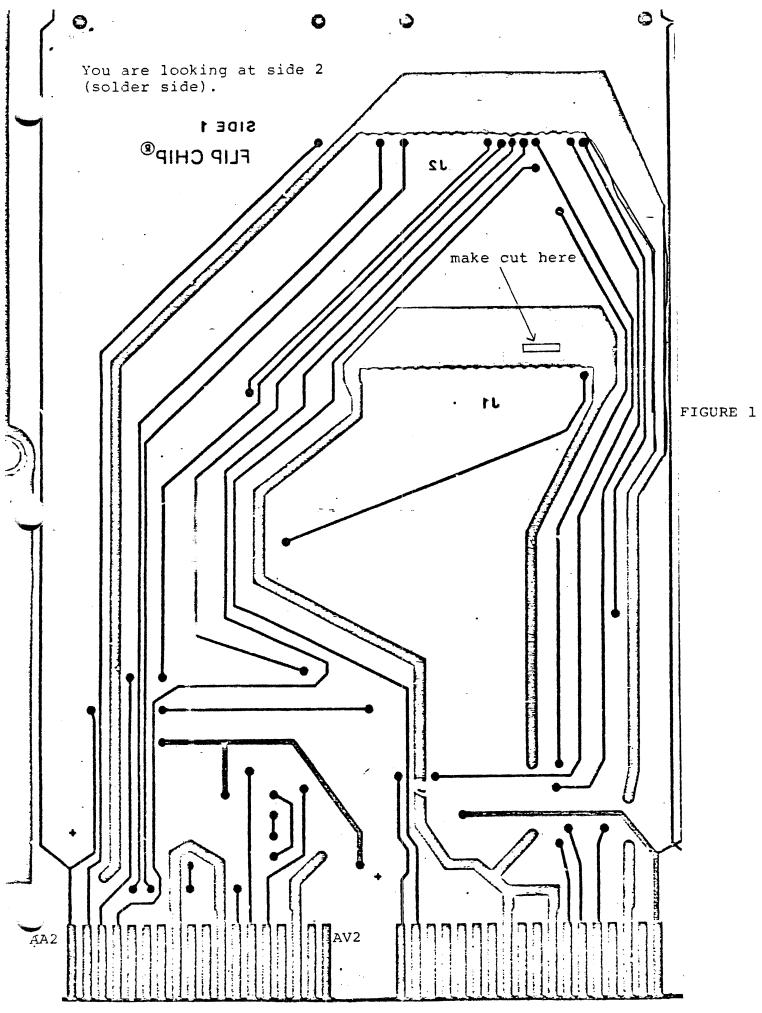

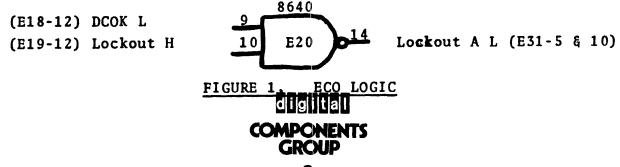

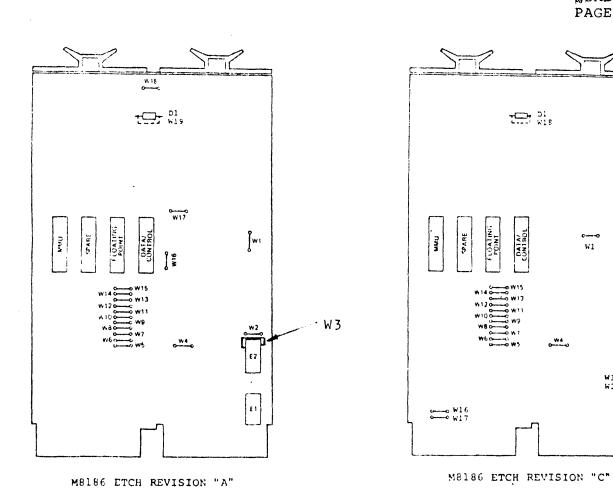

- 2. All MSV11-C modules using battery backup must be at etch Rev. D. Those modules at etch Rev. C must have ECO No. 1 for module M7955 installed. This ECO adds the circuit shown in Figure 1 in the following manner:

- cut the etch to free pins E31-5 and E31-10

- add wires from E18-12 to E20-9 E19-12 to E20-10 E20-14 to E31-5 § 10

- 3. The following jumpers should be configured as shown:

- W1, W5 Remove to separate the battery power from the bussed system power.

- W2, W3 Insert to connect the battery power to the refresh logic.

- W6, W7 Insert to enable internal refresh and to prevent the module from asserting BRPLY during refresh.

- 4. The heat generated by the refresh logic on each MSV11-C is 8 watts. Alternate cooling must be provided to dissipate this heat if the AC fans are off for more than two minutes.

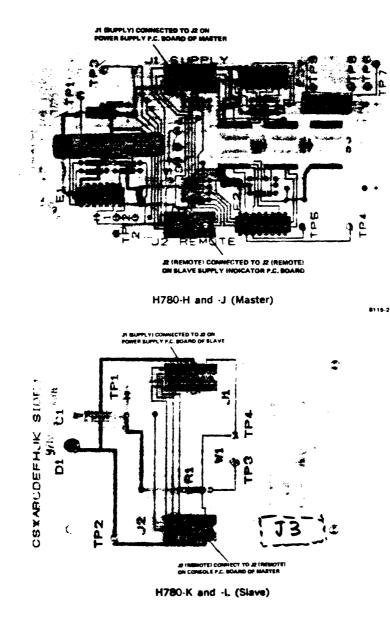

- 5. Certain precautions should be taken in the design of the power sequencing logic and other special modules. Signal BSYNC must be driven by a source that has a high impedance when power is removed from the rest of the system. Signals BDCOK and BPOK must be driven by a low impedance source (less than 8 ohms) under the same condition and should have no bounce (no relay). A J-FET is recommended since it also provides the necessary rise and fall times. These precautions have been taken in those systems using the H780-H or J power supply as provided by PDP-11/03 or PDP-11V03 systems.

- 6. All master (DMA) modules must finish gracefully when BPOK indicates an AC power failure. Any cycles in process must be allowed to finish, should be off the bus within two microseconds, and must not hang up signal BSYNC.

- 7. The software must finish its power-down procedure and issue a HALT instruction within two milliseconds from the time signal BPOK indicates an AC power failure.

Hunote

## FIGURE 2. TYPICAL BATTERY BACKUP SYSTEM

AC INPUT

digiiai components group

| <i>µ</i> note                | NUMBER<br>005              |

|------------------------------|----------------------------|

| TITLE IEEE BUS SUB-SPECS     | DATE<br>s / 2 /77          |

| DISTRIBUTION IBV11 CUSTOMERS | PRODUCT<br>18v11-A (M7954) |

| ORIGINATOR JOE AUSTIN        | PAGE OF                    |

The IBV11-A, when connected to the LSI-11, will meet the following subsets of IEEE Standard 488-1975:

| SH1  | SR1 | <b>C1</b> |

|------|-----|-----------|

| AH1  | RL1 | C2        |

| T5   | PP2 | C3        |

| TE 5 | DC1 | C4        |

| L3   | DT1 | C5        |

| LE3  |     |           |

This module is designed to be the only controller on the IEEE bus. Therefore, it will not respond to another controller on the bus that issues either a parallel poll configure command or a parallel poll control signal (subset PP2).

| <i>µ</i> note                            | NUMBER<br>009                         |

|------------------------------------------|---------------------------------------|

| TITLE HEX AND QUAD HOLD-DOWN BRACKET FOR | DATE<br>6 / 6 / 77                    |

|                                          | PRODUCT<br>LSI-11<br>DUNTING HARDWARE |

| DRIGINATOR JOHN HUGHES                   | PAGEL OF                              |

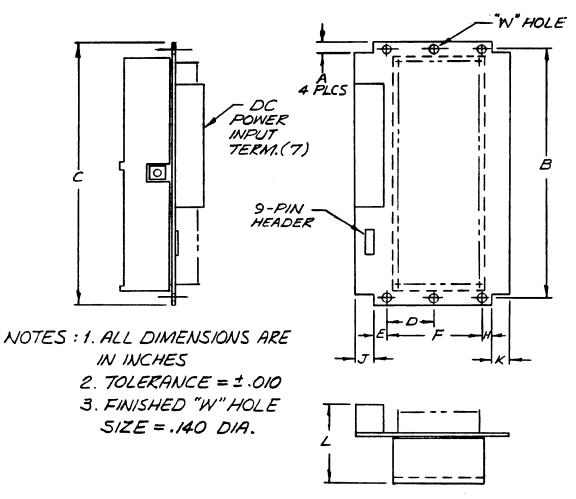

Here is a product that will help in applications that require a mechanically rigid system with double-sized modules in a 4x4 backplane or any time the 9x6 backplane is used. The hold-down bar that is described in the following clipping from the 1977-78 Logic Handbook (page 369) describes the same hold-down bracket that is used on quad-sized modules, like the LSI-11 processor and the MSV11-CD memory board.

To use this bracket, customers can drill out the existing handles on double or quad-sized board and attach the bracket by means of either rivets or screws.

In addition to offering increased rigidity and resistance to vibration, this bracket makes insertion and removal of modules far easier.

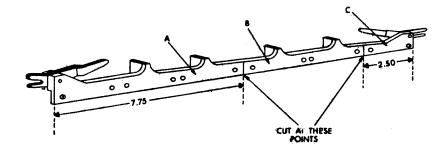

Hold-Down Bracket 12-10711-02

The 12-10711-02 module hold-down bracket serves as a mechanical combination handle and hold-down bracket for Hex-size modules when used with the appropriate cards guides such as an H0341. This bracket can also be used as a hold-down bracket for LSI-11 compatible modules (quad-size) but must be modified as shown in the accompanying drawing.

#### LSI-11 HOLDOWN 12-10711-02

1. CUT BRACKET AT POINTS DESIGNATED ON DRAWING BELOW.

- 2. DISCARD CENTER SECTION "B".

- 3. MOUNT SECTIONS "A" AND "C" ON BOARD AS DESIRED.

COMPONENTS GROUP

| <i>µ</i> note                | NUMBER<br>01 0 A                |  |

|------------------------------|---------------------------------|--|

| TITLE Power Supply For H909C | DATE<br>6 <b>/</b> 7 <b>/</b> 7 |  |

| DISTRIBUTION H909C Customers | PRODUCT<br>H909C                |  |

| ORIGINATOR David Schanin     | PAGE OF2                        |  |

THIS MICRO NOTE REPLACES #010. #010 SHOULD BE DISCARDED AND REPLACED WITH THIS ONE AS IT WAS IN ERROR.

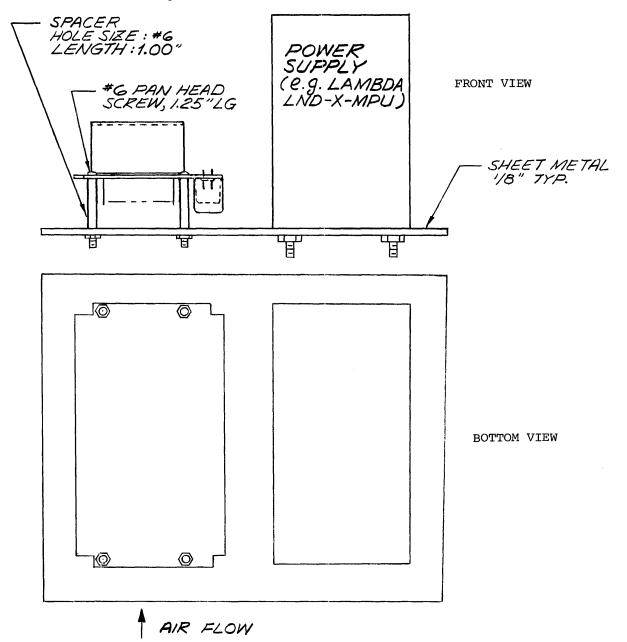

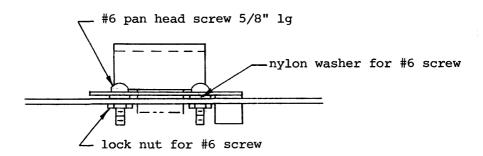

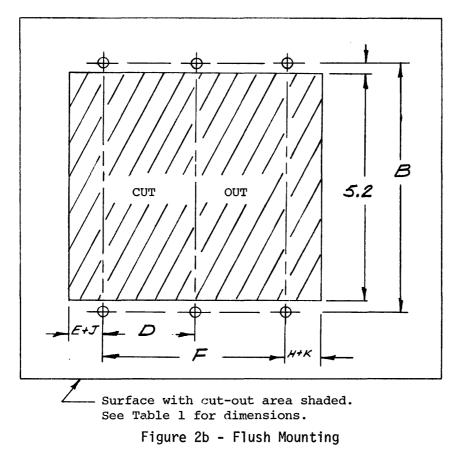

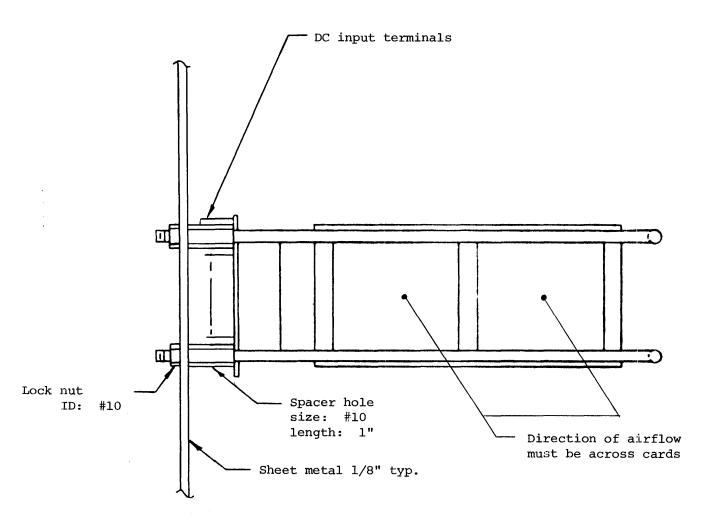

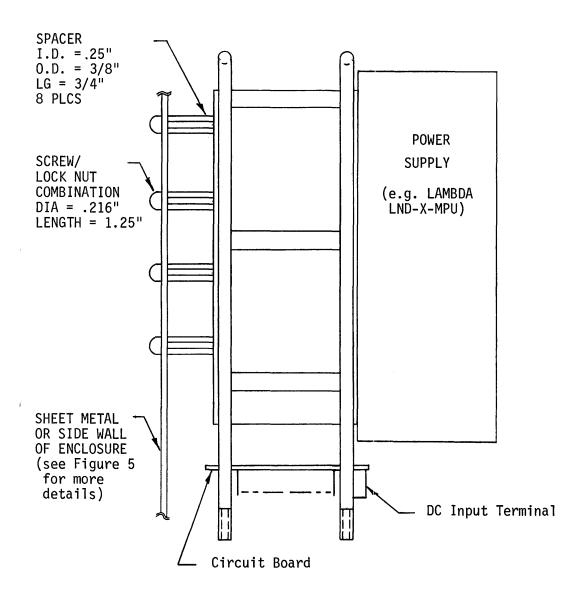

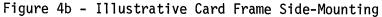

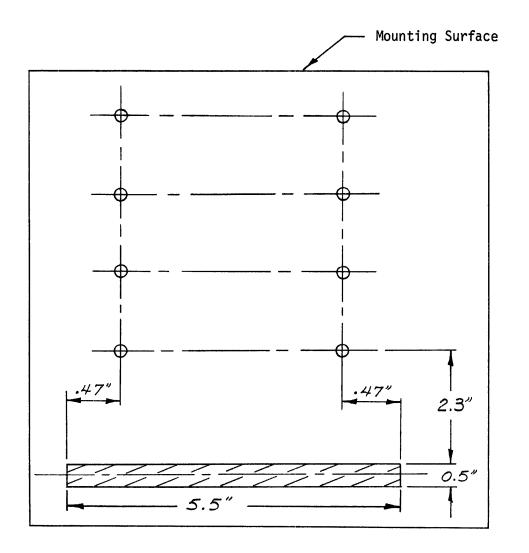

The H909C Expander Box is a convenient way to package the DDV11-B 9x6 backplane with the H0341 card guide. However, the H780 power supply may not be used with the H909C because air flow from the power supply fans will be restricted. Customers must provide their own power supplies and provide for cooling of both the LSI-11 cards and the power supplies.

There are two configurations of Lambda power supplies that have the potential of powering the H909C module systems enclosure. One is a 148-watt configuration that sells for \$400 and the other is a 321-watt configuration that sells for \$760.

The 321-watt configuration requires two +12 volt supplies to be connected in parallel. This is accomplished by connecting a diode in series with each positive output and connecting the sense input on the load side of the diode. One supply will current limit and the other will regulate. The diode is to protect the over-voltage protection circuit.

#### CONFIGURATION ONE

| QTY | MODEL        | VOLTAGE           | CURRENT     | PRICE | POWER     |

|-----|--------------|-------------------|-------------|-------|-----------|

| 1   | LJS-11-5-0V  | 5V                | 20A         | \$220 | 100 Watts |

| 1   | LJS-10-12-0V | 1 2 V             | <b>4</b> A  | \$180 | 48 Watts  |

|     |              |                   |             | \$400 | 148 Watts |

|     |              | <u>CONFI GURA</u> | TION TWO    |       |           |

| QTY | MODEL        | VOLTAGE           | CURRENT     | PRICE | POWER     |

| 1   | LGS-5-5-0V-R | 5V                | <b>4</b> 5A | \$400 | 225 Watts |

| 2   | LJS-10-12-0V | 1 2 V             | 8A          | \$360 | 96 Watts  |

|     |              |                   |             | \$760 | 321 Watts |

•

The KPV11-A can be used to generate the power fail/restore signal sequence and line time clock normally provided by the H780 power supply. An H780 control panel may also be interfaced to the LSI-11 via the KPV11-A.

NOTE: DUE TO PHYSICAL AND COOLING LIMITATIONS, THE H780 POWER SUPPLY CANNOT, UNDER ANY CONDITIONS, BE USED IN THE H909C BOX.

| unote                                       | NUMBER<br>011      |

|---------------------------------------------|--------------------|

| TITLE LSI-11 Halting During Interrupt Cycle | DATE<br>6 / 8 / 77 |

| DISTRIBUTION LSI-11 Customers               | PRODUCT<br>General |

| ORIGINATOR Ted Semple                       | PAGE1 OF2          |

An unusual sequence of events may cause the LSI-11 processor to HALT during an interrupt cycle. The problem occurs when an I/O device requests interrupt service simultaneously with an instruction being executed to reset the interrupt enable bit for the particular interrupt request.

An internal flip flop in the CPU chip set is set by the leading edge of an interrupt request. The processor responds by first completing execution of the current instruction and then asserting BIAK to grant the interrupt. The interrupt grant is then passed in daisy chain fashion down the bus to the board that made the request. However, if the instruction being executed resets the interrupt enable bit, the board will not realize that it was the one that generated the request and will, in turn, continue the daisy chain of the grant down the bus. If no other board has an interrupt request pending, the interrupt grant will pass all the way to the end of the bus and 12 us. later, the processor will time out and enter the HALT mode. This scenario, although unlikely, may be the cause of some previously unexplained CPU HALTs.

These false interrupts can be eliminated by modifying software. Before clearing an interrupt enable bit, all interrupts should be disabled by setting bit 07 of the PSW. To avoid needless interrupt latency, bit 07 of the PSW should be cleared as soon as possible after the interrupt enable bit is cleared.

The same scenario occurs in noisy environments when the BIRQ signal line is glitched by noise. In this case, a BIAK will be issued by the processor when no board has made an interrupt request.

There is a solution for this problem for those customers who are not using system software packages such as RT-11. This solution may be implemented by adding a single strap to the backplane and by a simple software modification.

*µ*note

On the last slot used on the backplane pin AN2, BIAKO, should be connected to pin AF2, BRPLY. During program loading, address location 000000 should be loaded with 000002 and location 000002 should be loaded with 000002.

These modifications will cause the following sequence to occur. When an interrupt acknowledge is not captured by a module, the interrupt acknowledge itself becomes the reply to that interrupt acknowledge. The processor, seeing a reply, will assume that a vector is on the bus. The bus, being in a floating condition, is equivalent to having a 0 vector. The processor then fetches the contents of location 000000 and stores this in the program counter, register 7 of the processor. Next, the processor fetches the contents of memory location 000002 and loads that into the processor status word. As with any interrupt cycle, the processor then begins to execute the program whose starting address is now in register 7. In this case, the processor will begin executing a program starting at memory location 000002. The instruction in this location is an RTI, Return from Interrupt. The RTI instruction causes the processor to return to the original program that was falsely interrupted, and the operation will continue as if the interrupt never occurred.

CAUTION: This solution should only be used with operating systems that do not use memory location 000000. RT-11 and other operating systems use location 000000.

| <i>µ</i> note                        | NUMBER<br>01 2            |

|--------------------------------------|---------------------------|

| TITLE LSI-11 Bus Theory of Operation | DATE<br>7 /11 /77         |

| IISTRIBUTION LSI-11 Customers        | PRODUCT<br>H9270; DDV11-B |

| dRIGINATOR <u>Ted Semple</u>         | PAGE 1 OF 9               |

## 1.0 - PROPAGATION DELAY & REFLECTIONS

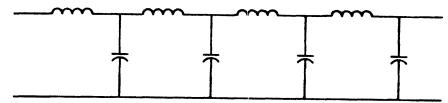

If a voltage is supplied between any two conductors, they may be considered as a transmission line. The ideal transmission line input impedence looks like pure resistance but, in fact, is mainly a combination of capacitance and inductance (see Figure 1).

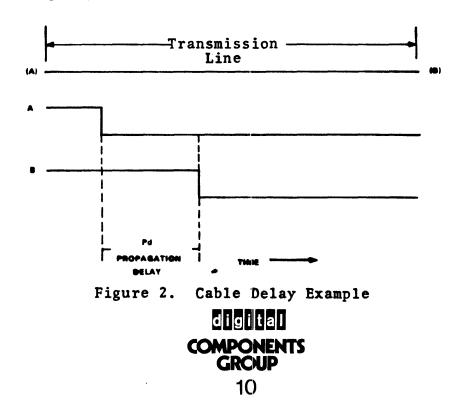

When the voltage at one end of the transmission line is changed, that change does not instantaneously appear at the other end. There is some delay, which is called propagation delay (see Figure 2). The propagation delay of LSI-11 bus cable is approximately 1.4 to 1.9 ns. per foot (or .0348 m).

Figure 1. Transmission Line Circuit Example

Hunote

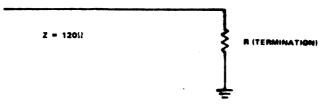

A lossless transmission line of infinite length looks like a pure resistance of value Z = L/C. If such a line is broken and terminated with a resistor of this value (R = Z), the line will behave like an infinitely long line; i.e., appear resistive (see Figure 3). The impedence (Z) of LSI-11 bus cable is approximately 120 ohms.

#### Figure 3. Cable Impedence Example

When a voltage is applied to the line, the instantaneous power consumed will be:

$$P = E^2/Z$$

$P = E^2/120$

Suppose now that the terminating resistor (R) is not equal to the characteristic impedence of the line. The power which is traveling down the line <u>before</u> it reaches the termination (during propagation delay) is equal to  $E^2/Z$ , but the power dissipated in the resistor after propagation delay is approximately equal to  $E^2/R$ .

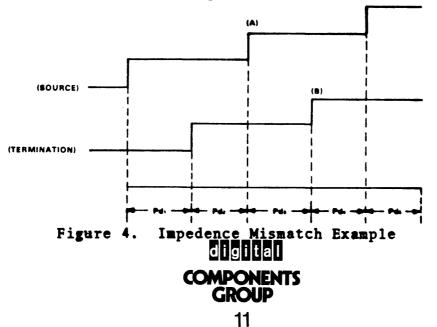

If resistance (R) is greater than the impedence (Z), there will be extra energy available at the termination and since energy cannot simply disappear, it will be reflected back into the line. After one more propagation delay (for the return journey), this reflection will be seen back at the source (see Figure 4A).

*µ*note

NUMBER 012 PAGE 3 OF 9

Some of this reflection will be dissipated by the source impedence and some will be re-reflected back into the line. When this rereflection is seen at the termination (Figure 4B), (after still another propagation delay), the energy difference will be reflected back to the source. Eventually both source and termination will arrive at the same level. The important point to note here is that what was intended to be a level change with a clean transition did not turn out that way on the line due to a termination mismatch between R and Z.

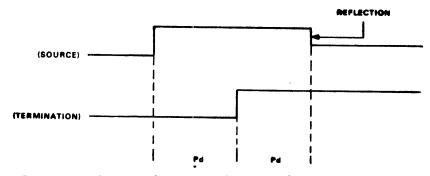

Essentially the same situation occurs when the termination resistor is smaller than the characteristic impedence of the line. If resistance (R) is less than impedence (Z), there will be a mismatch and this will also be reflected back to the source (see Figure 5).

Figure 5. Impedence (Low Resistance) Mismatch Example

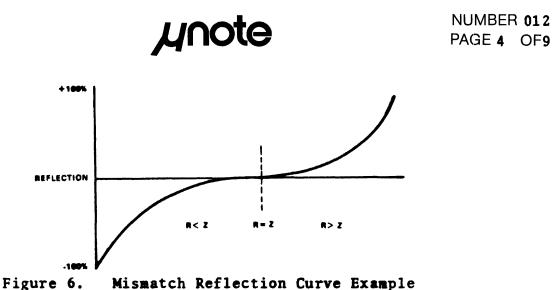

Note that: (a) transmission line which is not terminated in its characteristic impedence will have reflections and (b) the voltage seen at any point on the line or at any instant in time will be a combination of the incident and reflected voltage.

The amount of reflection depends on the mismatch, and approaches 100 percent for either a shorted or an open line (see Figure 6).

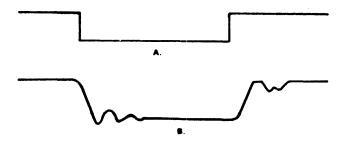

Essentially the same thing happens on the negative going edge of a level change so that what seemed to be a clean transition as in Figure 7A may look more like Figure 7B.

Figure 7. Cable Mismatch (Waveform Example)

To further compound the problem, each device on the bus contributes its own unique impedence and mismatch in complex time relationships (Figure 8).

Figure 8. System Device Impedence Example

All of this impedence and resistance mismatch is normal and to be expected in LSI-11 bus systems. The objective here is to point out the possible impedence mismatch and how to use the appropriate tools to minimize the effects of reflections and "noise".

#### **1.1** - LINE TERMINATION TECHNIQUE

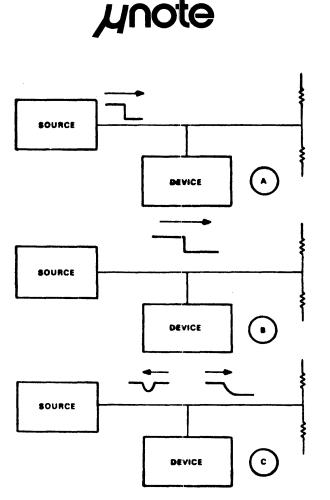

The question may be asked, how can a 178 and 383 ohm resistor properly terminate a line which has an impedence of 120 ohms?

*µ*note

A perfect power supply has an AC resistance (impedence) of zero ohms, so for AC considerations the termination diagram changes somewhat to that shown in Figure 9B and simplified in Figure 9C.

Figure 9. Line Termination Technique Example

The choise of these two values satisfies both the quiescent condition and the required termination impedence.

#### 2.0 - AC LOAD

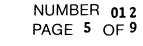

An AC load is defined as a number related to the impedence that a bus element presents to an LSI-11 bus signal line (due to backplane wiring, PC etch runs, receiver input loading, and driver output loading). This impedence load on a transmission line causes a "reflection" to occur when a step is sent down the line. This reflection shows up on an oscilloscope as a spike occurring shortly after an asserting or unasserting edge. An AC load is nominally 9.35 pf. of capacitance. Nine lumped AC loads reflect 20 percent and 20 lumped AC loads reflect 40 percent of a 25 ns. risetime step. AC loads must be distributed

*µ*∩ote

on the bus in the manner described in the LSI-11 Configuration Guidelines in order to provide bus operation with reflections guaranteed to be at or less than a tolerable level. The AC load rating of LSI-11 bus elements is usually based on the greatest of the capacitances that the element presents to the BDOUT, BDIN, BRPLY, BSYNC, BREF and BSACK signal lines. If the element is customer-designed, its AC loading must be determined from a reasonable estimate of the equivalent capacitance presented to the LSI-11 bus.

#### 3.0 - DC LOAD

A DC load is defined as a number related to the amount of DC leakage current that a bus element presents to an LSI-11 bus signal line which is high (undriven). A DC load is nominally 105 uA (80 uA - receiver plus 25 uA - driver). However, the DC load rating of a bus element is not strictly based on the element's signal line that has the greatest leakage, (e.g., DC leakage is less important on BDAL lines than it is on BSYNC). The DC loading of an element should always be obtained from the specification for that element. It should not be obtained from a calculation of the receiver and driver leakage current, unless the element is custom-designed and is not listed in the applicable documentation.

#### 4.0 - LOADING RULES

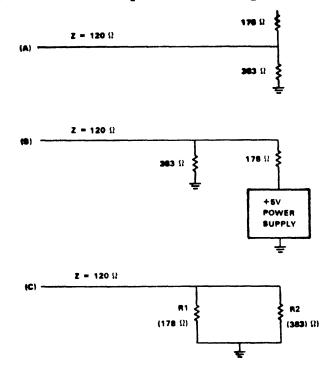

4.1 In multiple backplane systems, each backplane can have up to 20 AC loads. If a load is too large, it may generate a reflection on the LSI-11 bus large enough to create a false logic signal and cause a failure. Figure 10 illustrates such a failure. The reflection may cause the threshold of the 8640 receiver to be crossed a second time.

*µ*note

To avoid this problem, some of the modules should be moved to another backplane. Best results will be obtained when the AC loading of all backplanes is equal.

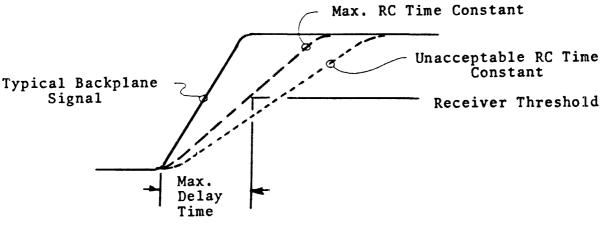

4.2 In single backplane systems, the number of AC loads is limited by the bus termination impedence. The RC time constant of the loaded backplane determines the rise time of a signal line when a driver unasserts that line. If the maximum RC time constant is exceeded, the signal may not rise within 25 ns. (see Figure 11). 25 ns. is the maximum delay permissible and still meet bus timing requirements.

Figure 11. Single Backplane Signal Waveform

To slow a rise time may also cause the output of some bus receivers to oscillate as the input signal rises through the receivers threshold.

#### 5.0 - DC LOADING RULE

The maximum number of DC loads in either a single or multiple backplane system is 20. If too many DC loads are put on the bus, the quiescent undriven voltage may be lowered to a level where bus receivers become susceptible to reflections from lumped loads and the overall noise margin on the high end (bus undriven) may become too small.

> **COMPONENTS GROUP** 17

Hunote

## 6.0 - CABLING RULES

In multiple backplane systems, the cables must be at least 2 feet long. If a cable is less than 2 feet long, the system will behave like a single backplane system.

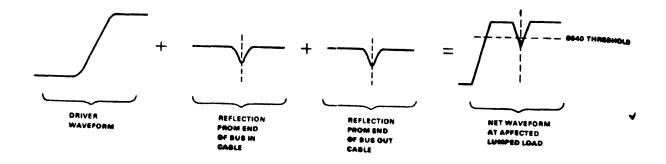

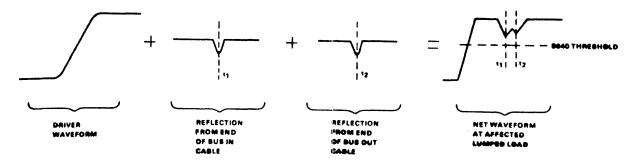

In multiple backplane systems, the cables must be at least 4 feet different in length. When this rule is violated and a driver in the middle backplane unasserts the bus, reflections from the other backplanes will arrive back at the middle backplane simultaneously and superimpose. The net reflection may cross the 8640 threshold and cause a failure (see Figure 12). When the cables are different lengths, the reflections will arrive at slightly different times (see Figure 13).

Figure 12. Violation Of Cable Length Rule Waveform

Figure 13. Proper Cable Length Rule Waveform

**COMPONENTS GROUP** 18

| unote                                   | NUMBER<br>013     |  |

|-----------------------------------------|-------------------|--|

| TITLEInstalling APL-11 on 11V03 & 11T03 | DATE<br>8 / 2 /17 |  |

| DISTRIBUTION All APL-11 Customers       | PRODUCT<br>APL-11 |  |

| ORIGINATOR <u>Rich Billig</u>           | PAGE OF           |  |

When installing RT-11 APL on an 11V03 or 11T03 system, you must consider two options:

• Choice of:

SINGLE PRECISION variables (7 decimal digits of precision), OR DOUBLE PRECISION variables (17 decimal digits of precision), AND

KEV11 optional hardware

Unless the application requires high precision, we recommend choosing SINGLE PRECISION for speed reasons.

To choose the correct APL interpreter file for your configuration, refer to the following table:

| KEV11<br>PRESENT? | SINGLE PRECISION | DOUBLE PRECISION |

|-------------------|------------------|------------------|

| YES               | APL04.SAV        | APL03.SAV        |

| NO                | APL00.SAV        | APL01.SAV        |

| <i>µ</i> note                                                           | NUMBER<br>014      |

|-------------------------------------------------------------------------|--------------------|

| Correct Input Parameters for the<br>TITLE QJV11 PROM Formatting Program | DATE<br>9 / 28 / 7 |

| DISTRIBUTION All QJV11 Users                                            | PRODUCT            |

| ORIGINATOR Dave Schanin                                                 |                    |

|                                                                         | PAGE 1 OF 2        |

The document that is shipped with the QJV11 PROM Formatting Program has a serious error in it. The document is in the process of being corrected, but until such time, Chapter 7 of the Microcomputer Handbook should be used as a guide to using the QJV11.

The error is in the description of the answers the user is supposed to give to questions printed by QJV11. A sample typeout is listed below:

| PROM VO1-00                                                                                                                                                                                                                                                                                                                                                                                                    |                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| ENTER AN OCTAL VALUE IN RESPONSE TO QUESTIONS<br>WHICH REQUIRE A NUMERIC RESPONSE. TYPE 'Y' FOR<br>YES AND 'N' OR NOTHING FOR NO. TERMINATE ALL<br>RESPONSES WITH A <cr> (CARRIAGE RETURN).<br/>RUBOUT MAY BE USED TO DELETE ONE CHARACTER AT<br/>A TIME BEFORE <cr> IS TYPED. CTRL/U MAY BE<br/>USED TO DELETE THE ENTIRE RESPONSE. CTRL/O<br/>MAY BE TYPED TO TURN OFF OUTPUT TO THE<br/>TERMINAL.</cr></cr> | Initial<br>Message  |

| HOW MANY WORDS ARE IN A PROM?<br>HOW MANY BITS ARE IN A PROM WORD?<br>HOW MANY PROMS ARE USED IN PARALLEL?<br>ARE THE DATA BITS INVERTED?<br>ARE THE ADDRESS LINES INVERTED?<br>HOW MANY BYTES ARE IN THE AREA TO BE<br>OUTPUT?<br>WHAT IS THE STARTING ADDRESS OF THE AREA TO<br>BE OUTPUT?<br>IS YOUR INPUT/OUTPUT DEVICE ON THE HIGH SPEED<br>READER/PUNCH?<br>READY INPUT, TYPE < CR> WHEN READY. < CR>    | Input<br>Parameters |

| DO'YOU WISH TO PUNCH TAPES? $\underline{Y}$<br>DO YOU WANT TO VERIFY A TAPE? $\underline{Y}$<br>READY INPUT, TYPE <cr> WHEN READY. <cr><br/>DO YOU WANT A LIST OF THE PROM CONTENTS? <math>\underline{Y}</math><br/>DO YOU WANT IT ON A LINE PRINTER? <math>\underline{N}</math></cr></cr>                                                                                                                     | QJV11<br>Operation  |

**COMPONENTS COMPONENTS CROUP** 20 *µ*note

The proper responses, based on the type of PROMs used, are listed below. Note that all of this information is copied from the Microcomputer Handbook.

| 9                                                            | MRV11-AA                                   | Applications                              | MRV11-BA Application                       |

|--------------------------------------------------------------|--------------------------------------------|-------------------------------------------|--------------------------------------------|

| Parameter                                                    | $512 \times 4$ PROMs                       | $256 \times 4$ PROMs                      | 1K × 8 PROMs                               |

| No. words in a PROM (Na)                                     | 1000                                       | 400                                       | <b>20</b> 00                               |

| No. bits in a PROM<br>word (N <sub>8</sub> )                 | 4                                          | 4                                         | 10                                         |

| No. PROMs used in parallel                                   | 4                                          | 4                                         | 2                                          |

| Are data bits inverted                                       | N                                          | N                                         | N                                          |

| Are addr, lines inverted                                     | Y                                          | Y                                         | N                                          |

| How many bytes in the area<br>to be output (N <sub>8</sub> ) | 20000                                      | 10000                                     | 20000                                      |

| Starting Address                                             | 0, 20000, 40000,<br>60000, 100000,<br>etc. | 0, 10000, 20000,<br>30000, 40000,<br>etc. | 0, 20000, 40000,<br>60000, 100000,<br>etc. |

| I/O device on the H.S.<br>reader/punch                       | Y or N                                     | Y or N                                    | Y or N                                     |

Table 7-5 QJV11 Input Parameters

# COMPONENTS GROUP 21

| ynote                                                | NUMBER<br>015        |

|------------------------------------------------------|----------------------|

| TITLE <u>Power Sequencing for the KD11-HA Module</u> | DATE<br>11 / 21 / 77 |

| DISTRIBUTION Unrestricted ORIGINATOR Dave Schanin    | PRODUCT<br>KD11-HA   |

|                                                      | PAGE 1 OF 3          |

The KD11-HA power-up and power-down sequencing functions are exactly the same as on the KD11-F. The user may select any one of four power-up modes:

| Mode | Start-up Function  |  |  |

|------|--------------------|--|--|

| 0    | PC at 24, PS at 26 |  |  |

| 1    | ODT microcode      |  |  |

| 2    | PC at 173000       |  |  |

| 3    | Reserved microcode |  |  |

Power-Up

On all KD11's, there are two <u>methods</u> (not <u>modes</u>) to start the LSI-11 and cause it to power-up through the selected <u>mode</u>:

- <u>Method 1</u>: Use an H780 power supply or KPV11 power sequence module. They function as follows:

- a) DC power is applied to the backplane, while BPOK and BDCOK are asserted.

- b) 3-10 ms. following DC power application, BDCOK is released. At this time, the CPU comes up, does a fast DIN on location 4 (a DIN which ignores the actual contents of location 4), and in doing so reads the power-up jumpers and the state of BPOK. The CPU senses BPOK is asserted and continues looping.

- c) 70 ms. (min.) following the release of BDCOK, BPOK is released. The CPU, which had been looping on reading the BPOK line, now senses that BPOK has been released and jumps to the location specified by the power-up jumpers.

*µ*note

- <u>Method 2</u>: Use a pushbutton. Connect a pushbutton, preferably debounced, to the BDCOK line. This pushbutton should allow BDCOK to float when the button is released, and should assert (ground) BDCOK when the button is depressed. This method functions as follows:

- a) DC power is applied. BDCOK and BPOK are released. The CPU is in an undefined state and will not run.

- b) The pushbutton is depressed following DC power application and, therefore, BDCOK is asserted. As long as BDCOK is asserted, the CPU is in a reset condition and non-functional.

- c) The button is released so BDCOK is released. The CPU comes up, does a fast DIN on location 4, reads the power-up jumpers, and the state of BPOK.

- d) Since BPOK is not asserted, the CPU jumps to the location specified by the power-up jumpers.

#### Power-Down

On all KD11's, two power-down methods exist:

- <u>Method 1</u>: Power-fail detection. This requires a KPV11 or an H780 power supply. This method allows for detection of AC loss by causing a trap through location 24. The CPU then has 4 ms. to complete its transaction and halt. This method works as follows:

- a) Upon AC loss, BPOK is asserted. This causes a trap through location 24. The power supply ride-through will maintain DC power for 4.05 ms. (min.) beyond AC power loss. The user software must complete all housekeeping functions in less than 4 ms. and halt.

- b) 4 ms. following BPOK assertion, BDCOK is asserted suspending CPU operations, locking out core memory access, and initializing peripherals.

- c) 5 us. following BDCOK assertion, DC power is lost.

- <u>Method 2</u>: Non power-fail detection. Loss of DC power, while BDCOK and BPOK are released. Under this method, DC power is simply shut off to the backplane. The CPU may lose power anywhere in a bus or execution cycle and may cause any random event to occur on the bus or at a peripheral due to the unknown state of all devices on the bus as they

randomly lose power. This is unacceptable in a core-based system since the core contents may get "scrambled". However, in a MOS RAM system where the peripherals cannot cause damage or harm to anything should they execute a random operation, this power-down method is perfectly acceptable.

How do these power-up and power-down methods affect the new KD11-HA? For most applications, the only requirement is automatic power-up and -down, as outlined in Method 2. Full sequenced power-up and -down, Method 1, is usually only required for core based systems. Therefore, the KD11-HA incorporates a "wake-up" circuit which automatically powers up and down the CPU according to Method 2 (i.e., no power-fail detection) with no external hardware requirements. Essentially, the "wake-up" circuit consists of a single shot tied to the BDCOK line which is asserted following the application of +5 volts backplane power. Since this single shot only is tied to +5, +5 and +12 must come up within 50 ms. of each other to insure reliable power-up. See Micro Note #016 for recommended power supplies.

<u>CAUTION</u>: MSV11-B memories should not be used as bank 0 memory on the KD11-HA unless it is ECO REV E or higher. Failure to use at least a REV E board will result in inability of the KD11-HA to power-up (note that external refresh is required from the REV11). The reason for this is that on REV D or lower MSV11-B's, the negative voltage charge pump will not attain operating voltage before the KD11-HA does a fast DIN on location 4 to read the power-up jumpers. If location 4 does not reply, the CPU will hang, and never power-up.

| unote                         | NUMBER<br>017                      |

|-------------------------------|------------------------------------|

| TITLELSI-11/2 Processor Clock | DATE<br>11 <b>/</b> 28 <b>/</b> 77 |

| DISTRIBUTION Unrestricted     | PRODUCT                            |

| ORIGINATOR Ron Young          | KD11-HA                            |

|                               | PAGE 1 OF1                         |

The CPU clock is a crystal controlled (non-adjustable) clock that will set the machine cycle time to 380 ns.  $\pm$  .01%. This should, at last, lay to rest any competitor's claim that we have to "tune" the clock to make the CPU work.

The tight tolerance on the clock will serve to tighten system performance between systems.

In addition, the 380 ns. figure was selected to optimize CPU--memory performance for our new memory offering without impairing performance with our older memories. This marriage of CPU and memory will serve to further enhance system performance.

<u>NOTE</u>: It has been brought to my attention that customers have been using "instruction loops" for timing purposes. This is not a good method for marking time. One must consider that the memory has "refresh cycles" to perform which can add time to the instruction execution time. This makes exact execution time impossible to calculate.

digital COMPONENTS GROUP 25

| µ∩ote                       | NUMBER<br>018        |  |

|-----------------------------|----------------------|--|

| TITLE DR11-C vs. DRV11      | DATE<br>11 / 28 / 77 |  |

| DISTRIBUTION Unrestricted   | PRODUCT<br>DRV11     |  |

| ORIGINATOR <u>Ron Young</u> | PAGE 1 OF 4          |  |

The following tables and figures list the differences between the DR11-C and the DRV11.

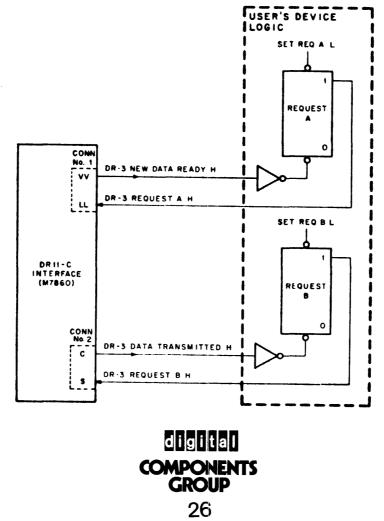

Some concern has been expresses on the manipulation of the REQUEST A and REQUEST B lines. Let me remind you of the "handshaking" necessary between the interface and the user's device. The user's manuals (DR11-C General Device Interface Manual--chapter 6, and ADV11-A, KWV11-A, AAV11-A, DRV11 User's Manual--chapter 5) state the need for the user to hold the REQUEST lines until the NEW DATA READY or the DATA TRANSMITTED signals are generated. The recommended method is illustrated in Figure 1 below.

# *µ*note

# TABLE I

# OUTPUT SIGNAL LOADING

| SIGNAL                    | DRV11                  | <u>DR11-C</u>                 |

|---------------------------|------------------------|-------------------------------|

| New Data Ready            | 10 Loads **            | 30 Loads                      |

| Data Transmitted          | 30 Loads               | 30 Loads                      |

| Init.                     | 10 Loads Per Connector | 30 Loads Over Both Connectors |

| New Data Ready LO* (byte) | N/A                    | 30 Loads                      |

| New Data Ready HI* (byte) | N/A                    | 30 Loads                      |

| All Other Outputs         | 5 Loads                | 7 Loads                       |

\* Byte-oriented control signals available on DR11-C only. ETCH REV E or later.

\*\* One load is defined as (-1.6 mA) one TTL load

# Hunote

# TABLE II

## VARIABLE LENGTHS OF OUTPUT CONTROL SIGNALS

| EXTERNAL CAPACITOR | NEW DATA READY | DATA TRANSMITTED |

|--------------------|----------------|------------------|

|                    | DR11-C         | <u>DR11-C</u>    |

| None               | 350 ns.        | 450 ns.          |

| 470 pF.            | 500 ns.        | 600 ns.          |

| 820 pF.            | 600 ns.        | 750 ns.          |

|                    |                |                  |

|                    | DRV11          | DRV11            |

| None               | 350 ns.        | 350 ns.          |

| .0047 uF.          | 750 ns.        | 750 ns.          |

| .01 uF.            | 1550 ns.       | 1550 ns.         |

| .02 uF.            | 2330 ns.       | 2330 ns.         |

| .03 uF.            | 3150 ns.       | 3150 ns.         |

|                    |                |                  |

Hunote

# TABLE III

# BERG CONNECTOR PIN DIFFERENCES

| SIGNAL                   | <u>DRV11</u> | <u>DR11-C</u> |

|--------------------------|--------------|---------------|

| In 02                    | J2 H,E       | J2 H          |

| Out 02                   | J1 RR,NN     | J2 NN         |

| New Data Ready HI (Byte) | N/A          | J1 E          |

| New Data Ready LO (Byte) | N/A          | J1 H          |

| unote                       | NUMBER<br>019        |

|-----------------------------|----------------------|

| TITLE EIA RS-422 and RS-423 | DATE<br>11 / 29 / 77 |

| DISTRIBUTION Unrestricted   | PRODUCT<br>DLV11-J   |

| ORIGINATOR Ted Semple       | PAGE1 OF 4           |

Electronic Industries Association (EIA) standards RS-422 and RS-423 have been accepted as new international standards for transmission lines between electronic equipment. These new standards offer a considerable performance improvement over traditional EIA RS-232C and current loops. Unlike RS-422 and RS-423 which were developed so that newly designed equipment could have higher performance, RS-232C and current loops grew out of existing applications and were accepted after the fact as standards. RS-232C was originally developed by the Bell System as a standard for interconnecting terminal equipment to communications equipment (modems). Current loops were the method employed to interconnect teletypewriter devices.

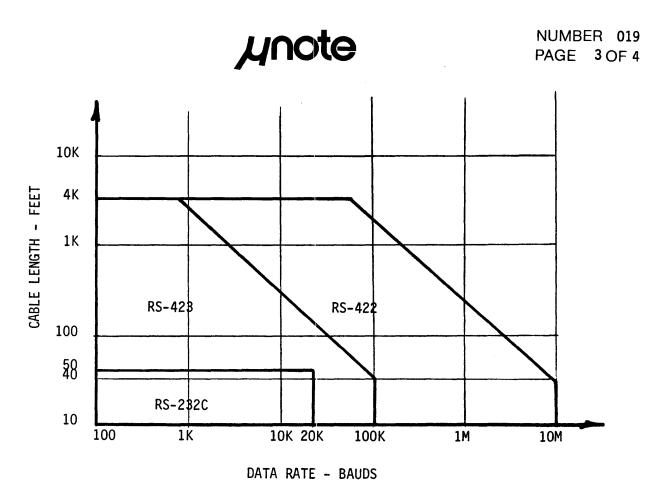

Figure I graphically shows the performance differences between RS-232C, RS-422 and RS-423. With RS-232C, the maximum reliable cable length is 50 feet and the maximum frequency is 20K baud. Comparing that with RS-422, you will see that RS-422 has the capability of going all the way up to 4000 feet and a maximum baud rate of 10 megabaud (although not simultaneously). Table I is a more detailed comparison of the specifications.

The new RS-422 and RS-423 specifications define the characteristics of the transmitters and receivers used to drive the transmission line as well as the characteristics of the transmission line itself. The receivers and cables used for both standards are identical, but the transmitters are different. RS-422 is a differential (balanced) line system which is capable of transmitting data at high baud rates over long distances with the high noise immunity associated with balanced line systems. RS-423 is a single-ended line system which inherently does not have the capability of a differential line.

EIA RS-423 is actually a stepping stone between EIA standards RS-232C and RS-422. RS-423 transmitters and receivers are actually backward compatible with RS-232C transmitters and receivers. This means that an RS-232C transmitter can send data to an RS-423 receiver and vice versa. Since the receivers used for RS-423 are identical to the receivers used for RS-422, it is possible to design systems which will work with existing RS-232C equipment and can then be upgraded (usually via a strapping change) to RS-422. This provides for a smooth transition between current equipment utilizing RS-232C and newly designed equipment utilizing

RS-422 without instantaneously obsoleting existing equipment. Remember that when RS-232C and RS-423 transmitters and receivers are interconnected, the system performance is that of RS-232C rather than the improved performance of complete RS-423 systems.

The DLV11-J 4-line serial line unit has been designed with the new hardware for RS-422 and RS-423. Straps have been provided which permit use of the RS-423 transmitters initially and then by restrapping, the board can be upgraded to RS-422 transmitters. The DLV11-J can, therefore, be used with RS-232C peripheral devices. In the future, new peripheral devices designed by Digital and other manufacturers will most likely utilize the new RS-422 specifications. The maximum baud rate with the DLV11-J is 38.4K baud, not the limit of either RS-422 or RS-423.

The product line has additional technical details on RS-422 and RS-423 for those who need it.

FIGURE 1 - DATA RATE vs. CABLE LENGTH

µ∩ote

### Table 1. Comparison of the old and new interface standards

| Parameter                                                                             | RS232                                                              | RS422                                                                                 | RS423                                                                                                                                                   |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line length (recom-<br>mended max—may be<br>exceeded with proper<br>design).          | 50 ft                                                              | 1200 m (4000 ft)<br>See Fig. 3                                                        | 1200m (4000 ft)<br>See Fig. 5                                                                                                                           |

| Input Z                                                                               | 3 to 7 kΩ<br>2500 pF                                               | > 4 kΩ                                                                                | > 4 kΩ                                                                                                                                                  |

| Max frequency (baud)                                                                  | 20 kbaud                                                           | 10 Mbaud                                                                              | 100 kbaud                                                                                                                                               |

| Transition time*<br>(time in undefined area<br>between "1" and "0")<br>tr = 10 to 90% | 4% of <i>τ</i><br>or<br>1 ms                                       | $tr \leq 0.1 \ r:$<br>$\tau \geq 200 \ ns$<br>$tr \leq 20 \ ns:$<br>$\tau < 200 \ ns$ | $\begin{array}{l} \mathrm{tr} \leq .3 \ \tau: \\ \tau < 1 \ \mathrm{ms} \\ \mathrm{tr} \leq 300 \ \mu\mathrm{s}: \\ \tau > 1 \ \mathrm{ms} \end{array}$ |

| dV/dt (wave shaping)                                                                  | 30 V/µs                                                            | See transition time                                                                   | See Fig. 4                                                                                                                                              |

| Mark (Data ''1'')<br>Space (Data ''0'')                                               | -3 V<br>+3 V                                                       | A < B<br>A > B                                                                        | A = Negative<br>B = Positive                                                                                                                            |

| Common mode voltage<br>(for balanced receiver)                                        | -                                                                  | -7 V < V <sub>CM</sub> < +7 V                                                         | -                                                                                                                                                       |

| Output Z                                                                              | -                                                                  | < 100 $\Omega$ Balanced                                                               | < 50 Ω                                                                                                                                                  |

| Open-circuit<br>output voltage (V <sub>o</sub> )                                      | $3 V <  V_0  < 25 V$                                               | V <sub>0</sub>  ≤ 6 V **                                                              | $4 V \le  V_0  \le 6 V$                                                                                                                                 |

| V <sub>t</sub> = loaded V <sub>o</sub>                                                | $5 <  V_o  < 15 V$<br>3 to 7k $\Omega$ load                        | 2 V or .5 V <sub>o</sub> < $ V_t $ †<br>100 $\Omega$ balanced load                    | V <sub>t</sub>  ≥ .9  V <sub>o</sub>  <br>450 Ω load                                                                                                    |

| Short circuit current                                                                 | 500 mA                                                             | 150 mA                                                                                | 150 mA                                                                                                                                                  |

| <b>Power</b> -off leakage<br>(V <sub>o</sub> applied to unpowered<br>device)          | > 300 $\Omega$<br>2 V < $ V_{0}  < 25 V$<br>V <sub>0</sub> applied | < 100 $\mu$ A<br>0 V < $\epsilon$ V <sub>o</sub> < 6 V<br>V <sub>o</sub> applied      | < 100 $\mu$ A<br>$ V_o  < 6 V$<br>$V_o$ applied                                                                                                         |

| Min receiver input<br>for proper V <sub>o</sub>                                       | > ±3 V                                                             | 200 mV differential                                                                   | 200 mV differential                                                                                                                                     |

r is bit period

across output, or output to ground t whichever is greater

ELECTRONIC DESIGN 18, September 1, 1977

digital COMPONENTS GROUP 33

| <i>µ</i> note                                | NUMBER<br>020      |

|----------------------------------------------|--------------------|

| TITLE 9x6 Slot Backplane Documentation Error | DATE<br>11 / 30 /7 |

| DISTRIBUTION DDV11-B Users                   | PRODUCT<br>DDV11-B |

| ORIGINATOR Joe Austin                        | PAGE 1 OF1         |

There is an error in the two documents which define the backplane pin assignments for the DDV11-B 9x6 slot backplane. Pins ET1 and FT1 in all slots are actually bussed to ground as shown in the table below.

These pins are <u>not</u> blank as indicated in the Components Group, Logic Products Option Bulletin (ED 06703 76, dated September, 1976) entitled "DDV11-B 9x6 Slot LSI-11 Backplane".

(Corrected)

DDV11-B Backplane Pin Assignments

|      |                |                 |           |                 | -       |       |       |       |

|------|----------------|-----------------|-----------|-----------------|---------|-------|-------|-------|

| SIDE | 2              | 1               | 2         | 1               | 2       | 1     | 2     | 1     |

| ROW  | A&C            | A&C             | B&D       | B&D             | E       | E     | F     | F     |

| A    | +5V            | BSPARE 1        | +5V       | BDCOK H         | +5V     | BLANK | +5V   | BLANK |

| в    | -12V           | <b>BSPARE 2</b> | -12V      | BPOK H          | -12V    | BLANK | -12V  | BLANK |

| С    | GND            | BAD 16          | GND       | SSPARE 4        | GND     | BLANK | GND   | BLANK |

| D    | +12V           | BAD 17          | +12V      | SSPARE 5        | BLANK   | BLANK | BLANK | BLANK |

| Е    | <b>BDOUT L</b> | SSPARE 1        | BDAL 2 L  | SSPARE 6        | BLANK   | BLANK | BLANK | BLANK |

| F    | BRPLY L        | SSPARE 2        | BDAL 3 L  | SSPARE 7        | BLANK   | BLANK | BLANK | BLANK |

| н    | BDIN L         | SSPARE 3        | BDAL 4 L  | SSPARE 8        | BLANK   | BLANK | BLANK | BLANK |

| J    | BSYNCL         | GND             | BDAL 5 L  | GND             | BLANK   | BLANK | BLANK | BLANK |

| к    | BWTBT L        | MSPARE A        | BDAL 6 L  | MSPARE B        | BLANK   | BLANK | BLANK | BLANK |

| L    | BIRQ L         | MSPARE A        | BDAL 7 L  | MSPARE B        | BLANK   | BLANK | BLANK | BLANK |

| М    | BIAKIL         | GND             | BDAL 8 L  | GND             | BLANK   | BLANK | BLANK | BLANK |

| Ν    | BIAKOL         | BDMR L          | BDAL 9 L  | BSACK L         | BLANK   | BLANK | BLANK | BLANK |

| Р    | BBS7L          | BHALT L         | BDAL 10 L | <b>BSPARE 6</b> | BLANK   | BLANK | BLANK | BLANK |

| R    | BDMGIL         | BREF L          | BDAL 11 L | <b>BEVNT L</b>  | BLANK   | BLANK | BLANK | BLANK |

| S    | BDMGOL         | PSPARE 3        | BDAL 12 L | PSPARE 4        | BLANK 🖌 | BLANK | BLANK | BLANK |

| т    | BINITL         | GND             | BDAL 13 L | GND             | BLANK   | gnd   | BLANK | gnd   |

| U    | BDALOL         | PSPARE 1        | BDAL 14 L | PSPARE 2        | BLANK   | BIANK | BLANK | BLANK |

| v    | BDAL 1 L       | +5B             | BDAL 15 L | +5B             | BLANK   | BLANK | BLANK | BLANK |

| <i>µ</i> note                                    | NUMBER<br>021      |

|--------------------------------------------------|--------------------|

| TITLE Comparison of Data Transmission Techniques | DATE<br>12 / 05 /7 |

| DISTRIBUTION Unrestricted                        | PRODUCT            |

| ORIGINATOR Ted Semple                            |                    |

|                                                  | PAGE1 OF5          |

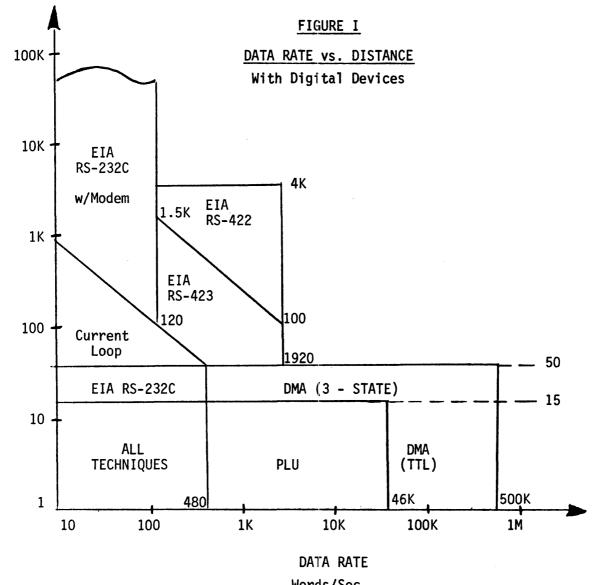

Frequently, the application arises where a data transmission path has to be established between two devices. Usually the distance between the devices is known, and also the rate of data transmission is known. The problem comes with deciding which is the best communication technique to use to interconnect the devices. Figure I should help you with this decision.

Figure I is a graph of data rate vs. distance for the various standard transmission techniques. Parallel data transmission techniques (PLU's and DMA) give the highest data rate; however, they are only good for relatively short distances. The serial techniques (RS-232C, RS-422 and current loops) are good for longer distances but at limited data rates.

While analyzing Figure I, remember that the axes are logrithmic and that the data rate is in words per second rather than baud rate. The limits established for both distance and data rate are a function of both the inherent limitations of the transmission technique and of the Digital Equipment Corporation device used to do the interconnection. As an example, look at the 422 section of the graph. Maximum distance is 4000 feet as established by the EIA standard RS-422, but the maximum data rate of 1920 words per second is based on the maximum baud rate of the DLV11-J which is 38.4K baud.

Table I is a summary of the LSI-11 devices which can be used with each communication technique. The Unibus equivalent for each device is also shown. Currently, there is no Unibus device for EIA RS-422.

The material for this Micro Note was extracted from the "CPU Interconnection Techniques" session given at the DCG International Sales Meeting. The entire presentation is available in 35 mm. slides, together with backup material, from the LSI-11 Presentation Library. Contact the product line if you would like further information.

digital

## Hunote

NUMBER 021 PAGE 2 OF F

Words/Sec.

DISTANCE--FT.

i

# *µ*note

#### NOTES AND ASSUMPTIONS FOR FIGURE 1

- 1. Data Rate Definition

- a. One word equals 16 bits

- b. For serial techniques, one word equals two characters formatted with one start bit, eight data bits and one stop bit. Asynchronous serial transmission is assumed.

- 2. Serial Line Maximum Data Rate

- a. Modems were limited to 120 words/sec. (2400 baud) because modems with higher rates cost more than LSI-11 systems usually warrant. Higher data rate modems are generally synchronous rather than asynchronous.

- b. 480 words/sec. is equal to 9600 baud, the limit of the DLV11 SLU.

- c. 1920 words/sec. is equal to 38.4K baud, the limit of the DLV11-J SLU.

- 3. PLU (Parallel Line Unit) Limits

- a. The TTL inputs/outputs of the DRV11 limit the distance to 15 feet.

- b. 46K words/sec. assumes non-interrupt driven program servicing with bit testing (TSTB, BMI, MOV and SOB). 97K words/sec. is maximum rate with program servicing without bit testing (MOV and BR). With interrupt driven servicing, the maximum limit is 20K words/sec. assuming 50 us. for interrupt latency and software servicing of interrupt. (380 ns. CPU microcycle time)

- 4. DMA (Direct Memory Access) Limits

- a. The DRV11-B can be used up to 50 feet because it has tri-state drivers and receivers. The distance is limited to 15 feet with TTL devices like the DR11-B.

µ∩ote

NUMBER 021 PAGE 4 OF5

b. DMA transfers with the DRV11-B and the DR11-B are limited to 500K words/sec. in burst mode operation. 250K words/sec. is the limit for single cycle mode operation with either device. These limits are device dependent; they are not LSI-11 bus limits (which is 833K words/sec.). Remember that burst mode can disrupt memory refreshing if bus refreshing (DMA or microcode) is used. Self-refreshing memories, MSV11-CD or MSV11-D, eliminate this problem.

# Hunote

TABLE I

### NUMBER 021 PAGE 5 OF 5

| DEVICES       |                                               |

|---------------|-----------------------------------------------|

| <u>LSI-11</u> | <u>PDP-11</u>                                 |

| DLV11         | DL11-C                                        |

| DLV11         | DL11-D                                        |

| DLV11-E       | DL11-E                                        |

| DLV11-J       |                                               |

| DRV11         | DR11-C                                        |

| DRV11-B       | DR11-B                                        |

|               | DLV11<br>DLV11<br>DLV11-E<br>DLV11-J<br>DRV11 |

| unote                              | NUMBER<br>023      |

|------------------------------------|--------------------|

| TITLE Using the MSV11-D 30K Option | DATE<br>12 /16 /77 |

| DISTRIBUTION Unrestricted          | PRODUCT<br>MSV11-D |

| ORIGINATOR <u>Rich Billig</u>      | PAGE 1 OF 1        |

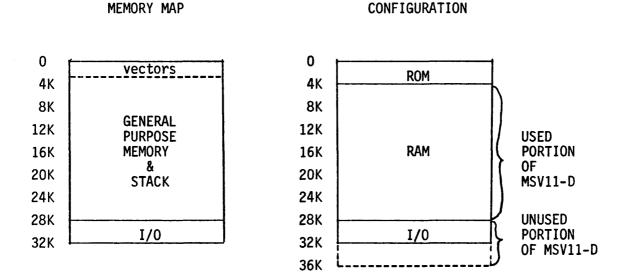

The MSV11-D memory, when configured with the full complement of 16K RAM chips, provides 32K words of storage. In the LSI-11 memory map, however, the top 4K words (addresses 160000 to 177777) are normally reserved for I/O device registers (the so-called "I/O Page").

The 32K MSV11-D, as delivered, operates as a 28K word memory for the LSI-11. In this configuration, it is totally compatible with all DEC-supplied software. The 4K word region which is located at address 160000 is present but inaccessible to the program.

To allow more of the memory to be used (for large applications), a jumper-selectable option on the MSV11-D makes 30K words (rather than 28K) addressable by the program. This is done by "removing" the low 2K word area of the I/O page (addresses 160000 to 167777). When the 30K option is enabled, the memory map is:

000000 to 167777 - RAM Memory 170000 to 177777 - I/O Page

Because current system software expects a 4K word I/O page, RT-11 and RSX-11S cannot make use of the extra 2K words of RAM. (A userwritten program operating under either system may, however, access locations 160000 to 167777 directly if desired.)

Engineering is presently evaluating the feasibility of supporting the full 30K RAM in the next release of RT-11 (V3B). Similar modifications to RSX-11S would be more extensive and are not currently planned.

When the 30K option is used, all I/O devices <u>must</u> be configured to place their I/O page addresses in the range 170000 to 177777. (This would not be the default assignment for such devices as the DUV11 and DZV11.) Also, it is <u>not</u> possible to use the REV11 bootstrap with this option, as a portion of the bootstrap PROM code resides at addresses 165000 to 165777. The new quad bootstrap module (BDV11) may be used in the 30K environment.

| <i>µ</i> note                              | NUMBER 024A<br>SUPERSEDES µNOTE #024 |

|--------------------------------------------|--------------------------------------|

| TITLE Async., Serial Line Unit Comparisons | DATE<br>10 / 13 / 78                 |

| DISTRIBUTION LSI-11 Users                  | PRODUCT<br>Async. SLU's              |

| ORIGINATORJoe Austin                       | PAGE 1 OF 5                          |

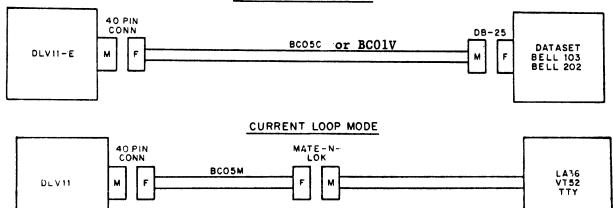

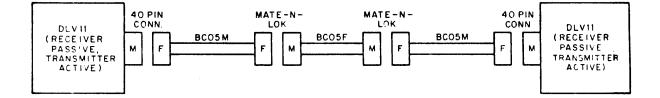

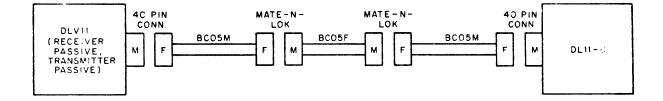

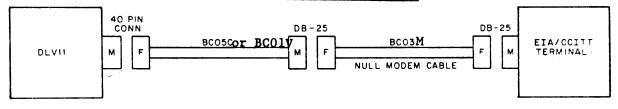

Attached are charts comparing the different members of the families of asynchronous serial line products. All modules of the DLV11 series are dual height modules. The DLV11-E, -F, and -J modules detect overrun conditions which are reported in the receiver CSR. These modules will not generate phantom interrupts on overrun.

#### DLV11-J

Each of the 4 serial ports on this module are separate and independent from the others. This is <u>not</u> a multiplexed module. Each port has its own CSR's, data buffers, interrupt vectors, baud rates, UARTs, etc. The net effect of this module is to achieve a 4:1 compression ratio over the DLV11-F and the DLV11. The main functional difference between the ports of the DLV11-J and the DLV11 is that the DLV11-J provides the higher performance EIA RS-422 and RS-423 interfaces (RS-423 on the DLV11-J also meets the EIA RS-232C specification) and requires the DLV11-KA option (one per port) to add the 20 mA current loop interface, to add 110 baud, and to add reader run functions.

#### DLV11-E

This module is functionally equivalent to the DL11-E except that it has programmable transmit baud rates. This module provides one serial port that has full modem control.

#### DLV11-F

This module is functionally equivalent to the DLV11 and will eventually replace it. In addition, it can be configured to provide programmable transmit baud rates.

#### DLV11-KA

This option allows an EIA port to be connected to a terminal with a 20 mA interface, such as an ASR33. It consists of a small PC card containing the interface conversion logic within a box that is externally mounted. Mating cables are included. This module is not restricted to 110 baud.

# *µ*note

#### TABLE 1

#### COMPARISON OF HARDWARE FEATURES

|                                                                                                                                                                                                                                                                                                                                                             | UNIBUS      |                                                                                |           |                                                                     |                              |              |                                                                     |  | LSI-11 BUS    |          |                                                                                                                                                            |                             |             |                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------|------------------------------|--------------|---------------------------------------------------------------------|--|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------|------------------------------|

|                                                                                                                                                                                                                                                                                                                                                             | DZ11-A      | DL11-A                                                                         | DL11-B    | DL11-C                                                              | DL11-D                       | DL11-E       | DL11-W                                                              |  | DLV11         | DLV11-E  | DLV11-F                                                                                                                                                    | DLV11-J                     | DLV11-KA    | DZV11-A,B                    |

| Number of Ports Per Module<br>EIA RS-232C<br>Full Modem Control                                                                                                                                                                                                                                                                                             | 8<br>√      | 1                                                                              | 1         | 1                                                                   | 1                            | 1<br>√       | 1                                                                   |  | 1             | 1        | 1                                                                                                                                                          | 4                           | 1           | 4<br>√                       |

| Limited Modem Interface<br>EIA RS-422, RS-423<br>Data Leads Only<br>20 mA Current Loop<br>RCVR Active or Passive<br>XMIT Active or Passive<br>XMIT Active Only<br>CCITT<br>HALT on Framing Error (4)<br>BOOT on Framing Error (4)                                                                                                                           | 1           | √                                                                              | √         | V                                                                   | ✓<br>✓                       | √            | V                                                                   |  | $\bigvee$     | V        |                                                                                                                                                            | √<br>√<br>(2)<br>(2)<br>(6) | ✓<br>✓<br>✓ | V                            |

| Baud Rates (see Table 3)<br>Programmable<br>Split Speed Clocks Included<br>Reader Run Control<br>Error Flags<br>Transmit Break Generation Bit<br>Receiver Active Bit<br>Maintenance Bit<br>Internal Real Time Clock<br>UART Cleared by INIT<br>UART Cleared by DCOK<br>No Trap on Write to Input<br>Buffer<br>Easy Configuration Using<br>Wire-Wrap Jumpers | √<br>√<br>√ | $\checkmark \checkmark \checkmark \checkmark \checkmark \checkmark \checkmark$ | $\bigvee$ | $\checkmark \checkmark \checkmark \checkmark \checkmark \checkmark$ | $\checkmark$                 | $\checkmark$ | $\checkmark \checkmark \checkmark \checkmark \checkmark \checkmark$ |  | √<br>√<br>(3) |          | $\bigvee \bigvee $ | (2)<br>√<br>√<br>(3)<br>√   | ✓           |                              |

| Stop Bits<br>1<br>1.5<br>2                                                                                                                                                                                                                                                                                                                                  | √<br>√<br>√ | √                                                                              | V         | $\checkmark$                                                        | $\checkmark$<br>$\checkmark$ |              |                                                                     |  | √<br>√        | √<br>(5) | √<br>(5)                                                                                                                                                   | √<br>√                      |             | $\checkmark$<br>$\checkmark$ |

**COMPONENTS COMPONENTS CROUP** 42 Hunote

#### TABLE 2

#### COMPARISON OF SOFTWARE FEATURES

|          |                                                                              |                                                                                                                                                                                               | <b></b>                                     | r                                         | UNI                                                                            | BUS                                                                                | ·                                                                                                                                                          |                                                                                    | LS                          | <u>I-1</u>                                                                                                                                                 | 1 B                                                                                                                                                                                                                 | US                                                                                                                                                           |

|----------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REGISTER | BIT                                                                          | NAME                                                                                                                                                                                          | DL11-A                                      | DL11-B                                    | DL11-C                                                                         | DL11-D                                                                             | DL11-E                                                                                                                                                     | DL11-W                                                                             | DLV11                       | DLV11-E                                                                                                                                                    | DLV11-F                                                                                                                                                                                                             | DLV11-J                                                                                                                                                      |