# Semiconductor Databook

Volume 1

ERRATA

**Confidential and Proprietary**

1987

# Introduction

This publication contains additions and revisions to the information contained in the 1987 Semiconductor Databook Volume 1.

In order to properly reference the information in this publication, it is recommended that the following pages in the 1987 Semiconductor Databook Volume 1 be marked to note that changes exist.

| CAISt.             |                                                                     |

|--------------------|---------------------------------------------------------------------|

| Page               | Change Description                                                  |

| Inside front cover | Confidential and copyright disclosure                               |

| vi,vii             | Product cross-referencing                                           |

| 1-48               | Recommended Operating Conditions and Part Number Variations         |

| 1-51,1-52          | Table 19 and Notes                                                  |

| 1-54               | Table 20 and Notes                                                  |

| 1-55               | Figure 42                                                           |

| 1-56               | Table 21                                                            |

| 1-57               | Table 22                                                            |

| 1-82               | Table 1 and MicroVAX bus Interface Signals                          |

| 1-83               | External vector enable (XVEC)                                       |

| 1-85               | Registers                                                           |

| 1-86               | Polarity register and Level/Edge Register                           |

| 1-87               | Level/Edge register, Pending Summary register, and Interrupt Enable |

|                    | register                                                            |

| 1-88               | IRQ Map register                                                    |

| 1-89               | Round Robin register and Interrupt Vector register                  |

| 1-90               | Table 6                                                             |

| 1-99,1-100         | Table 7                                                             |

| 1-101              | Table 8, notes, and text                                            |

| 1-102              | Figure 18                                                           |

| 1-103              | Figure 19                                                           |

| 1-106,1-107        | Table 9 and notes                                                   |

| 1-153,1-154        | Table 21                                                            |

| 1-157,1-158        | Table 23                                                            |

| 1-169              | Table 28                                                            |

| 1-170              | Figure 40                                                           |

| 1-171              | Table 29                                                            |

| 1-250              | Figure 2                                                            |

| 1-251              | Table 1                                                             |

| 1-253              | Figure 3                                                            |

| 1-271              | Table 14                                                            |

| 1-274,1-275        | Interrupts, Table 17 and notes                                      |

| 1-277              | Bus Read Transactions                                               |

| 1-282              | Interrupt Acknowledge                                               |

| 1-309              | Table 31                                                            |

| 1-310              | Table 32                                                            |

| 1-313              | Figure 33, Table 33 and notes                                       |

| 1-315              | Table 34                                                            |

| 1-317              | Table 35                                                            |

| 1-319              | Table 36                                                            |

| 1-320              | Figure 40                                                           |

|                    |                                                                     |

| Page                | Change Description                               |

|---------------------|--------------------------------------------------|

| 1-321,1-322         | Table 37                                         |

| 1-397               | Figure 27                                        |

| 3-27                | Features                                         |

| Page preceeding 4-1 | Chipkit Descriptions                             |

| 4-139               | Table 1                                          |

| 4-140               | Table 2                                          |

| 4-141               | II Parity Select (II PSEL)                       |

| 4-142               | Table 4                                          |

| 4-143               | BCI Parity (BCI PO) and BCI Data Strobe (BCI DS) |

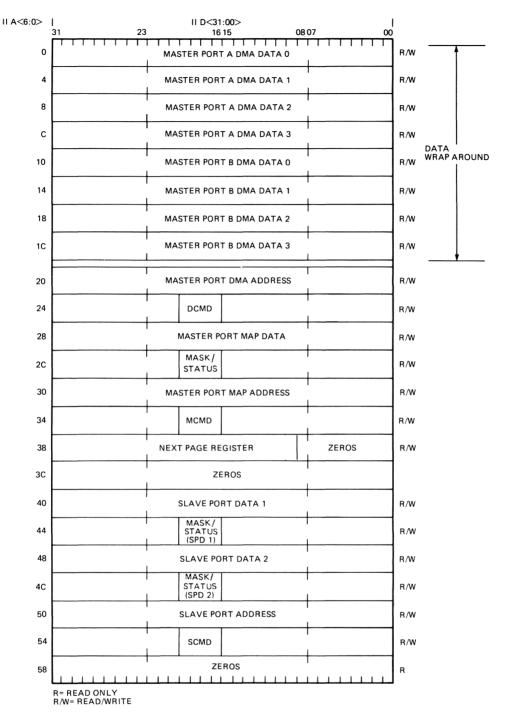

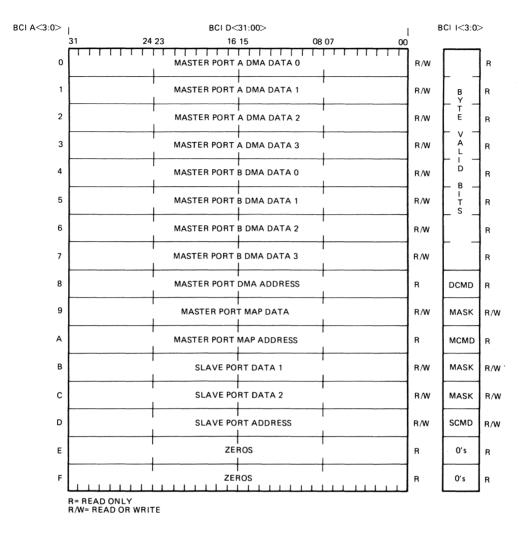

| 4-144               | General Register Addressing                      |

| 4-145,1-146         | Figure 4 and Figure 4 caption                    |

| 4-151               | Table 5                                          |

| 4-152               | ac Electrical Characteristics                    |

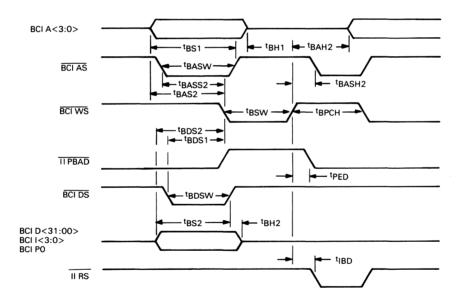

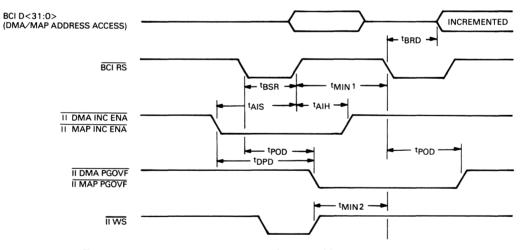

| 4-153               | Figure 7                                         |

| 4-155               | Figure 9                                         |

| 4-156               | Figure 10                                        |

| 4-182               | Table 10                                         |

| 4-224               | Figure 2                                         |

| 4-233               | Figure 1                                         |

|                     |                                                  |

# Part Identification Codes

The following identification codes are used with the devices in this databook.

# 780 Series

| 78xyz - xx                |                            | - XX                |

|---------------------------|----------------------------|---------------------|

| $\uparrow 0 = Processors$ | 5 = Controllers            | GA = Gullwing       |

| 1 = Coprocessor           | 6 = Graphic devices        | FA = Straight       |

| 2 = Memories              | 7 = Bus interfaces         | PA = Pin grid array |

| 3 = I/O devices           | 8 = Communications devices |                     |

| 4 = Reserved              | 9 = Reserved               |                     |

| DC Sarias                 |                            |                     |

# **DC** Series

DCxyz

| ↑ 0 =    | Custom bipolar devices | 3 = MOS devices |

|----------|------------------------|-----------------|

| <u> </u> | Custom bipolar devices | 5 = MOS devices |

# Cross-referencing of Semiconductor Products

| Part  | Part           | Purchase      | Description                                             |

|-------|----------------|---------------|---------------------------------------------------------|

| Name  | Number         | Number        | Description                                             |

| DC003 | DC003          | 19-12730-00   | Dual-interrupt Circuit                                  |

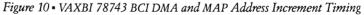

|       | DC003<br>DC004 | 19-12729-00   | -                                                       |

| DC004 |                |               | Register Selector (Protocol) Logic<br>4-bit Transceiver |

| DC005 | DC005          | 19-13040-00   |                                                         |

| DC006 | DC006          | 19-14035-00   | Word Count/Bus Address Logic                            |

| DC010 | DC010          | 19-14038-00   | Direct Memory Access                                    |

| DC013 | DC013          | 19-14438-00   | UNIBUS Request Logic                                    |

| DC018 |                | 19-17043-00/1 | Serializer/Deserializer                                 |

| DC021 | DC021          | 19-19015-00   | Octal Bus Transceiver                                   |

| DC022 |                | 19-17871-00   | 16-Word by 4-bit Register File                          |

| DC024 |                | 19-20116-01   | Encoder/Decoder Logic                                   |

| DC028 | 78701          | 19-22110-01   | VAXBI Clock Driver                                      |

| DC029 | 78702          | 19-22111-01   | VAXBI Clock Receiver                                    |

| DC102 |                | 19-13888-00   | Equals Checker                                          |

| DC301 |                | 21-12623-00   | Dual Baud Rate Generator                                |

| DC309 |                | 21-15102-00   | Reed Solomon Generator                                  |

| DC310 | DCT11          | 21-17311-01   | DCT11 16-bit Microprocessor                             |

| DC319 | DC319          | 21-17312-00   | DLART                                                   |

| DC321 | FPJ11          | 21-21858-00   | FPJ11 Floating-point Accelerator                        |

| DC502 | 78680-GA       | 21-25011-01   | Video Processor (VIPER)                                 |

| DC323 | 78690-GA       | 21-21553-01   | Video Control (ADDER)                                   |

| DC324 | 78732-PA       | 21-21689-00   | VAXBI BIIC                                              |

| DC327 |                | 21-20852-AA   | V-11 ROM/RAM                                            |

| DC328 |                | 21-20851-AA   | V-11 Instruction/Execution Logic                        |

| DC329 |                | 21-20850-AA   | V-11 Memory Management Logic                            |

| DC330 |                | 21-20849-AA   | V-11 Floating-point Accelerator Logic                   |

| DC333 | 78032-GA       | 21-20887-01,  | MicroVAX 32-bit CPU                                     |

|       |                | -04, -05, -06 |                                                         |

|       | DCJ11-AC       | 57-19400-08   | DCJ11 16-bit Microprocessor (15 MHz)                    |

|       | DCJ11-AA       | 57-19400-09   | DCJ11 16-bit Microprocessor (18 MHz)                    |

Confidential and Proprietary

vi

| Part<br>Name | Part<br>Number | Purchase<br>Number | Description                                  |

|--------------|----------------|--------------------|----------------------------------------------|

| DC335        | DCJ11          | 21-17679-00        | DCJ11 16-bit Microprocessor                  |

| DC337        | 78132-GA       | 21-22797-01        | MicroVAX Floating-point Unit                 |

| DC343        | 78743-PA       | 21-23838-01        | VAXBI BCAI                                   |

| DC344        | 78733-PA       | 21-23839-01        | VAXBI BCI3                                   |

| DC349        | 78808-GA       | 21-23458-01        | Octal ART                                    |

| DC5003       | 78584-GA       | 21-23864-01        | Dynamic RAM Controller (DYRC)                |

| DC358        | 78532-GA       | 21-24329-01        | MicroVAX Direct Memory Access (DMA)          |

| DC503        | 78610-GA       | 21-24941-01        | Programmable Sprite Cursor                   |

| DC506        | 78516-GA       | 21-24330-01        | MicroVAX Vectored Interrupt Controller (VIC) |

| ADVICE       | ADVICE         |                    | MicroVAX Incircuit Evaluation/Emulation Unit |

# **Recommended Operating Conditions**

• Supply voltage ( $V_{DD}$ ): 4.75 V to 5.25 V

- Active supply current: (I<sub>DD</sub>): 700 mA (maximum)

- Temperature  $(T_A)$ : 0°C to 70°C

- Relative humidity: 10% to 95% (noncondensing)

- Minimum airflow over chip: 250 linear feet/minute

#### Part Number Variations

Four variations of the MicroVAX 78032 are available. All variations operate at a maximum clock (CLKI) rate of 40 MHz. The Digital part numbers assigned to these are

| Part Number | Package Leads |

|-------------|---------------|

| 21-20887-01 | formed        |

| 21-20887-04 | unformed      |

| 21-20887-05 | formed        |

| 21-20887-06 | unformed      |

The functional restrictions of the 21-20887-01, and -04 versions are

- -DMA requests that coincide with memory management activity or floating-point completion polling, may cause the MicroVAX CPU to missequence. To prevent this, the assertion of  $\overline{\text{DMR}}$  signal should be synchronized with the deassertion of the  $\overline{\text{AS}}$  signal to the chip.

- —Interrupt requests that are asserted and then deasserted before being serviced (passive release) by the MicroVAX CPU, may cause the CPU to missequence. To prevent this, the  $\overline{IRQ} < 3:0$  line should remain asserted until the chip acknowledges the request with the interrupt acknowledge cycle.

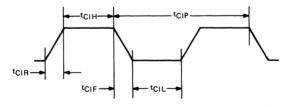

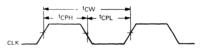

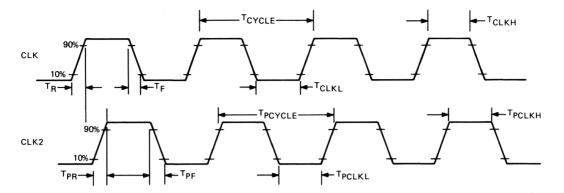

#### **Clock Input Timing**

Figure 38 shows the timing specifications for the CLKI input clock signal and Table 18 lists the timing parameters indicated on the diagram.

Figure 38 • MicroVAX 78032 CLK1 Timing Waveform

| Timing Symbol      | Signal Definition  | Requirements (ns) |      |

|--------------------|--------------------|-------------------|------|

|                    |                    | Min.              | Max. |

| t <sub>CIF</sub>   | Clock in fall time |                   | 4.5  |

| t <sub>cih</sub>   | Clock in high      | 8                 |      |

| t <sub>CIL</sub>   | Clock in low       | 8                 | -    |

| t <sub>CIP</sub> * | Clock period       | 25                | 50   |

| t <sub>CIR</sub>   | Clock in rise time |                   | 4.5  |

#### . . . . . - -

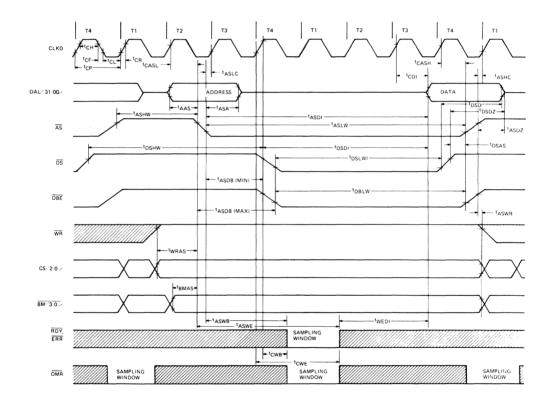

#### **CPU Read and Write Cycle Timing**

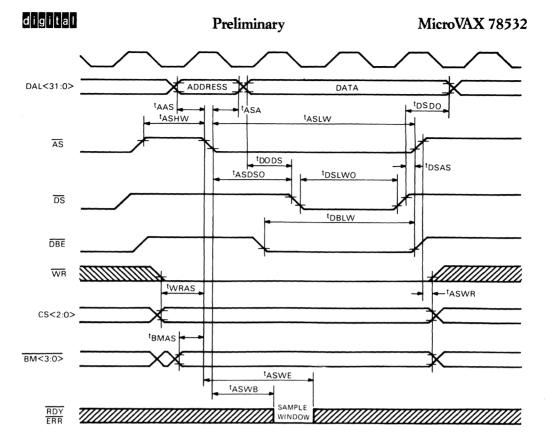

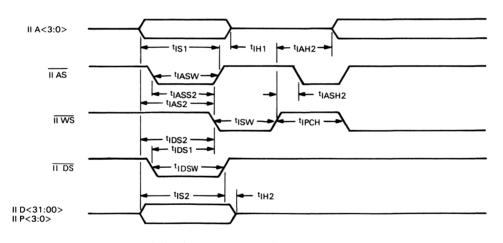

Figure 39 shows the timing sequence for the CPU read cycle and Figure 40 shows the timing sequence for the CPU write cycle. The parameters for the CPU read and write cycles are listed in Table 19.

Figure 39 • MicroVAX 78032 CPU Read Cycle Timing Sequence

Confidential and Proprietary

| Table 19 • MicroVAX 78032 CPU Read and Write Cycle Parameters |                                                                                                                                                               |                                        |               |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------|

| Timing<br>Symbol                                              | Signal Definition                                                                                                                                             | Requirements (<br>Min.                 | ns)<br>Max.   |

| t <sub>AAS</sub>                                              | Address set up time to $\overline{\text{AS}}$ assertion                                                                                                       | 2P-28                                  |               |

| t <sub>ASA</sub>                                              | Address hold time after $\overline{AS}$ assertion                                                                                                             | 2P-15                                  |               |

| t <sub>ASHC</sub>                                             | $\overline{\text{AS}}$ rising through 2.0 V to CLKO rising through 0.8 V                                                                                      | P-23                                   |               |

| t <sub>ASLC</sub>                                             | AS falling through 0.8 V to<br>CLKO rising through 0.8 V                                                                                                      | P-20                                   |               |

| t <sub>asdb</sub>                                             | $\overline{\text{AS}}$ assertion to $\overline{\text{DBE}}$ and $\overline{\text{DS}}$ (read) assertion                                                       | 3P-15                                  | 3P+20         |

| t <sub>asdi</sub>                                             | AS assertion to read data valid <sup>1</sup>                                                                                                                  | •••••••••••••••••••••••••••••••••••••• | 11P-30+8PS    |

| t <sub>ASDSO</sub>                                            | $\overline{\text{AS}}$ assertion to $\overline{\text{DS}}$ assertion (write)                                                                                  | 5P-15                                  | 5P+20         |

| t <sub>ASDZ</sub>                                             | AS and DBE deassertion to data three-state                                                                                                                    |                                        | 2P-20         |

| t <sub>ASHW</sub>                                             | AS deassertion width                                                                                                                                          | 3P                                     |               |

| t <sub>ASLW</sub>                                             | AS assertion width                                                                                                                                            | 12P-15+8PS                             |               |

| t <sub>ASWB</sub>                                             | $\overline{\text{AS}}$ assertion to beginning of $\overline{\text{RDY}}$ , $\overline{\text{ERR}}$ , and $\overline{\text{DMR}}$ sampling window <sup>2</sup> |                                        | (6P-45) + 8PS |

| t <sub>ASWE</sub>                                             | $\overline{\text{AS}}$ assertion to end of $\overline{\text{RDY}}$ ,<br>ERR, and $\overline{\text{DMR}}$ sampling window <sup>3</sup>                         | 6P+10+8PS                              |               |

| t <sub>ASWR</sub>                                             | $\overline{WR}$ , $\overline{BM < 3:0}$ , CS < 2:0 > hold<br>time from $\overline{AS}$ deassertion                                                            | P-20                                   | ·             |

| t <sub>BMAS</sub>                                             | $\overline{BM < 3:0>}$ set up time before $\overline{AS}$ assertion                                                                                           | 2P-25                                  |               |

| t <sub>CASH</sub>                                             | CLKO rising through 2.0 V to $\overline{\text{AS}}$ rising through 0.8 V                                                                                      | P-7                                    | P+15          |

| t <sub>CASL</sub>                                             | CLKO rising through 2.0 V to $\overline{\text{AS}}$ falling through 2.0 V                                                                                     | P-9                                    | P+16          |

| t <sub>cdi</sub>                                              | CLKO rising through 2.0 V to read data valid                                                                                                                  |                                        | P-5           |

| t <sub>cdo</sub>                                              | Write data hold time from CLKO rising through 2.0 V                                                                                                           | P-15                                   |               |

| t <sub>CF</sub>                                               | CLKO fall time                                                                                                                                                |                                        | 12.5          |

| t <sub>CH</sub>                                               | CLKO high                                                                                                                                                     | (2P-25) x .5                           |               |

| t <sub>CL</sub>                                               | CLKO low                                                                                                                                                      | (2P-25) x .5                           |               |

| t <sub>CP</sub>                                               | CLKO period                                                                                                                                                   | 50                                     | 100           |

| t <sub>cr</sub>                                               | CLKO rise time                                                                                                                                                |                                        | 12.5⁴         |

| t <sub>CWB</sub>                                              | T4 CLKO rising through 2.0 V to beginning of $\overline{\text{RDY}}$ , $\overline{\text{ERR}}$ , and $\overline{\text{DMR}}$ sampling window <sup>2</sup>     |                                        | 3P-45         |

| t <sub>cwe</sub>                                              | T4 CLKO rising through 0.8 V to end of $\overline{\text{RDY}}$ , $\overline{\text{ERR}}$ , and $\overline{\text{DMR}}$ sampling window <sup>3</sup>           | 3P+15                                  |               |

|                    | Table 19 • MicroVAX 78032 CPU Read and Write Cy                                                      | cle Parameters (C    | Cont.)       |  |

|--------------------|------------------------------------------------------------------------------------------------------|----------------------|--------------|--|

| Timing<br>Symbol   | Signal Definition                                                                                    | Requirements<br>Min. | (ns)<br>Max. |  |

| t <sub>dblw</sub>  | DBE assertion width                                                                                  | 9P-20+8PS            |              |  |

| t <sub>DOC</sub>   | Write data set-up time to CLKO rising through 0.8 V                                                  | 3P-42                |              |  |

| t <sub>DODS</sub>  | Write data set-up time to $\overline{\text{DS}}$ assertion                                           | 3P-30                |              |  |

| t <sub>dsas</sub>  | $\overline{\text{DS}}$ deassertion to $\overline{\text{AS}}$ and $\overline{\text{DBE}}$ deassertion | P-15                 |              |  |

| t <sub>DSD</sub>   | Read data hold time after $\overline{\text{DS}}$ deassertion                                         | 0                    |              |  |

| t <sub>dsdi</sub>  | DS assertion to read data valid <sup>1</sup>                                                         |                      | 8P-35+8PS    |  |

| t <sub>dsdo</sub>  | Write data hold time from $\overline{\text{DS}}$ deassertion                                         | 3P-20                |              |  |

| t <sub>DSDZ</sub>  | DS deassertion to read data high impedence                                                           |                      | 31-20        |  |

| t <sub>DSHW</sub>  | DS deassertion width                                                                                 | 6P                   |              |  |

| t <sub>DSLWI</sub> | DS assertion width (read)                                                                            | 8P-20+8PS            |              |  |

| t <sub>DSLWO</sub> | DS assertion width (write)                                                                           | 6P-20+8PS            |              |  |

| twedi              | Sampling window end to read data valid                                                               |                      | 5P-25        |  |

| t <sub>WRAS</sub>  | $\overline{WR}$ , CS < 2:0 > set up time before<br>AS assertion                                      | 3P-35                |              |  |

Notes:

<sup>1</sup> Read data is valid early enough if  $t_{ASDI}$  or  $t_{DSDI}$  or  $t_{CDI}$  is satisfied.

<sup>2</sup> Requirements for the beginning of the sampling window are satisfied if either  $t_{ASWB}$  or  $t_{CWB}$  is satisfied.

<sup>3</sup> Requirements for the end of the sampling window are satisfied if either  $t_{ASWE}$  or  $t_{CWE}$  is satisfied.

$^{4}$  t<sub>CH</sub>, t<sub>CL</sub>, and t<sub>CP</sub> parameters are minimum for this value.

۹.,

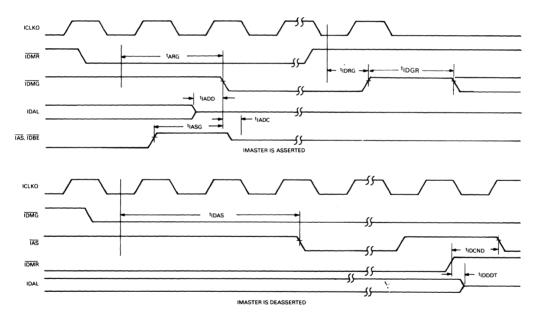

| Table 20 • MicroVAX 78032 DMA Cycle Timing Parameters |                                                                                                                                                                                                                                                          |                                    |                                 |  |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|--|

| Timing<br>Symbol                                      | Signal Definition                                                                                                                                                                                                                                        | Requirements<br>Min.               | (ns)<br>Max.                    |  |

| t <sub>ASG</sub>                                      | $\overline{\text{AS}}$ and $\overline{\text{DBE}}$ deassertion to $\overline{\text{DMG}}$ assertion                                                                                                                                                      | 4P-25                              |                                 |  |

| t <sub>cgh</sub>                                      | CLKO rising through 2.0 V to DMG rising through 0.8 V                                                                                                                                                                                                    | P-7                                | P + 16                          |  |

| t <sub>CGL</sub>                                      | CLKO rising through 2.0 V to<br>DMG falling through 2.0v                                                                                                                                                                                                 | P-7                                | P + 18                          |  |

| t <sub>dmrg</sub>                                     | $\overline{\text{DMR}}$ to $\overline{\text{DMG}}$ latency                                                                                                                                                                                               | 10P-25                             | 60P+20+16PS                     |  |

| t <sub>dmrgu</sub>                                    | DMR to DMG latency with bus unlocked                                                                                                                                                                                                                     | 10P-25                             | 28P+20+8PS                      |  |

| t <sub>dmrh</sub> <sup>3</sup>                        | DMR hold with respect to<br>DMG assertion                                                                                                                                                                                                                | 0                                  | _                               |  |

| t <sub>gdalz</sub>                                    | DMG deassertion to external device three-state of DALS.                                                                                                                                                                                                  | _                                  | 4P-20                           |  |

| t <sub>gdmr</sub>                                     | DMG assertion to DMR deassertion<br>such that no more DMA cycles are<br>requested                                                                                                                                                                        | _                                  | $6P-45 + ((N-2) \times 8P)^{1}$ |  |

| t <sub>GHC</sub>                                      | DMG rising through 2.0 V to<br>CLKO rising through 0.8 V                                                                                                                                                                                                 | P-25                               |                                 |  |

| t <sub>GLC</sub>                                      | DMG falling through 0.8 V to<br>CLKO rising through 0.8 V                                                                                                                                                                                                | P-23                               | _                               |  |

| t <sub>glw</sub>                                      | DMG minimum assertion width                                                                                                                                                                                                                              | 10P-25+<br>((N-2)×8P) <sup>1</sup> | _                               |  |

| t <sub>GSZ</sub>                                      | $\overline{\text{DMG}}$ assertion to three-state<br>of $\overline{\text{AS}}$ , $\overline{\text{DS}}$ , $\overline{\text{DBE}}$ , $\overline{\text{WR}}$ . $\text{CS} < 2:0 >$<br>and $\overline{\text{BM}} < 3:0 >$                                    | -10                                | 0                               |  |

| t <sub>GZ</sub>                                       | $\overline{\text{DMG}}$ deassertion to external<br>device of three-state of $\overline{\text{AS}}$ , $\overline{\text{DS}}$ ,<br>$\overline{\text{DBE}}$ , $\overline{\text{WR}}$ , $\text{CS} < 2:0 > < 3:0 > \text{and } \overline{\text{BM} < 3:0 >}$ |                                    | 3P-20 <sup>2</sup>              |  |

Notes:

<sup>1</sup> The number of microcyles that occur during a DMA grant. A DMA grant is issued for a minimum of two microcycles.

<sup>2</sup> At the conclusion of a  $\overline{\text{DMA}}$  grant the external logic must deassert the  $\overline{\text{AS}}$ ,  $\overline{\text{DS}}$ , and  $\overline{\text{DBE}}$  signals before the external bus drivers become a high impedance.

' If  $t_{DMRH}$  parameter is not met (DMR is deasserted before  $\overline{DMG}$  is asserted), then  $\overline{DMR}$  must not be reasserted for 2.5 microcycles (500 ns at maximum frequency).

# **External Processor Cycle Timing**

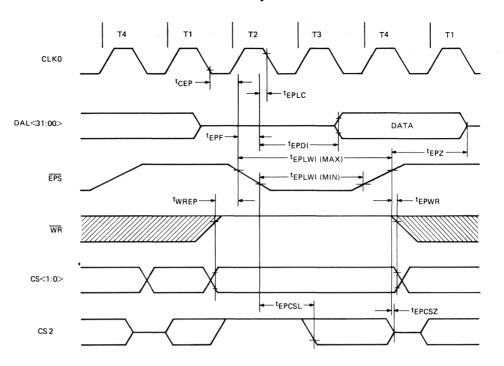

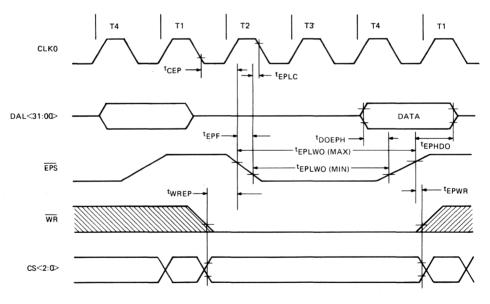

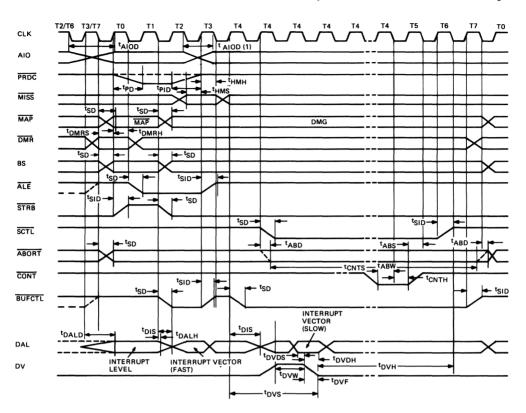

Figure 42 shows the timing sequence for the external processor read and response timing and for the external processor write command timing. Table 21 lists the timing parameters for the symbols referenced on the diagrams.

Confidential and Proprietary

Preliminary

External Processor Read/Response Timing

External Processor Write/Command Timing

Figure 42 • MicroVAX 78032 External Processor Cycle Timing Sequence

Confidential and Proprietary

|                    | Table 21 • MicroVAX 78032 External Processor Cycle Timing P                     | arameters       |               |

|--------------------|---------------------------------------------------------------------------------|-----------------|---------------|

| Timing<br>Symbol   | Signal Definition                                                               | Require<br>Min. | ments<br>Max. |

| t <sub>cep</sub>   | CLKO falling through 0.8 V to $\overline{\text{EPS}}$ falling through 2.2 V     | P-5             | P+19          |

| t <sub>doeph</sub> | Write data valid set up time to $\overline{EPS}$ deassertion                    | 2P-35           |               |

| t <sub>EPCSL</sub> | EPS assertion to external processor assertion of CS2                            | 0               | 3P-40         |

| t <sub>EPCSZ</sub> | EPS deassertion to CS2 high impedance by external processor                     | 0               | 2P-20         |

| t <sub>epdi</sub>  | EPS assertion to read data valid                                                |                 | 4P-40         |

| t <sub>EPF</sub>   | EPS fall time from 2.2 V to 0.6 V                                               | 0               | 10            |

| t <sub>ephdo</sub> | Write data hold time from EPS deassertion                                       | 2P-25           |               |

| t <sub>EPLC</sub>  | EPS falling through 0.6 V to CLKO falling through 2.0 V                         | P-25            |               |

| t <sub>eplwi</sub> | EPS assertion width (read)                                                      | 4P-20           | 4P+20         |

| t <sub>eplwo</sub> | EPS assertion width (write)                                                     | 5P-20           | 5P+20         |

| t <sub>EPWR</sub>  | $\overline{WR}$ and CS < 1:0 > hold time from $\overline{EPS}$ deassertion      | P-20            |               |

| t <sub>epz</sub>   | EPS deassertion to read data high impedance                                     |                 | 3P-20         |

| t <sub>wrep</sub>  | $\overline{WR}$ and $CS < 1:0 >$ set up time before $\overline{EPS}$ assertion. | 2P-35           |               |

|                    |                                                                                 |                 |               |

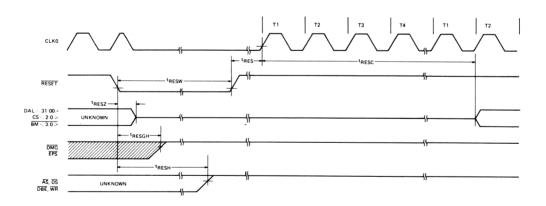

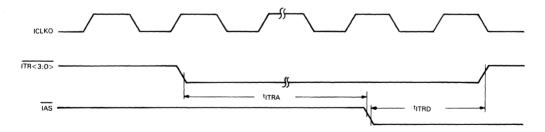

# **Reset Timing**

Figure 43 shows the timing sequence for the reset function of the processor and Table 22 lists the timing parameters for the symbols referenced on the diagram.

Figure 43 • MicroVAX 78032 Reset Timing Sequence

Confidential and Proprietary

| Timing             | Signal Definition                                                                                                                                                  | Requiremen | nte (ne) |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|

| Symbol             |                                                                                                                                                                    | Min.       | Max.     |

| t <sub>res</sub>   | <b>RESET</b> deassertion to first CLKO pulse if <b>RESET</b> is deasserted synchronously                                                                           | 3P+10      | 3P+85    |

| t <sub>resc</sub>  | Number of CLKO periods from RESET deassertion until first DAL activity                                                                                             | 32 periods |          |

| t <sub>resgh</sub> | $\overline{\text{RESET}}$ assertion to $\overline{\text{DMG}}, \overline{\text{EPS}}$ deassertion <sup>1</sup>                                                     |            | 150      |

| t <sub>resh</sub>  | $\overline{\text{RESET}}$ assertion to $\overline{\text{AS}}$ , $\overline{\text{DS}}$ , $\overline{\text{DBE}}$ , $\overline{\text{WR}}$ deassertion <sup>2</sup> |            | 1.0 µs   |

| t <sub>RESW</sub>  | $\overline{\text{RESET}}$ assertion width after $V_{\text{DD}}$ = 4.75 V                                                                                           | 3.0 ms     |          |

| t <sub>reswb</sub> | $\overline{\text{RESET}}$ assertion width if $V_{\text{DD}}$ has already been at 4.75 V for 3 ms when $\overline{\text{RESET}}$ is asserted                        | 3.0 µs     |          |

| t <sub>resz</sub>  | $\overline{\text{RESET}} \text{ assertion to DAL < 31:00>, } \overline{\text{BM} < 3:0>},$<br>CS < 2:0 > high impedence'                                           | _          | 100      |

#### T 11 00 3.51 WAX TOOTO D · · · n

Notes:

<sup>1</sup> When the RESET level is asserted, the DMG and EPS signals become high and remain high.

<sup>2</sup> When RESET is asserted, AS, DS, DBE and WR outputs become a high impedance state and the levels become high by low current internal pull-ups.

'When the  $\overline{\text{RESET}}$  level is asserted the  $\overline{\text{BM} < 3:0>}$  lines and CS<2:0> lines become highimpedance.

# Mechanical Specifications

The dimensions of the MicroVAX 78032 68-pin cerquad surface and socket mount packages are shown Appendix E.

Preliminary

| Pin               | Signal          | Input/Output | Definition/Function                                                                                                                                                                                                         |

|-------------------|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 57                | IAKEON          | output       | Interrupt acknowledge enable out N—An active<br>low pulldown output that connects together with<br>the IAKEOP output to the IAKEI input of the<br>next device in the daisychain or connects to the<br>ERR input of the CPU. |

| 39                | CSEL            | input        | Chip select—Enables read/write operations to the internal registers.                                                                                                                                                        |

| 31                | RESET           | input        | Reset—Sets the VIC to a known initial state.                                                                                                                                                                                |

| 30                | CLK             | input        | Clock—Used to generate the internal time states of the VIC.                                                                                                                                                                 |

| 10,11,29,44,49,60 | V <sub>dd</sub> | input        | Voltage—5 V Power supply voltage.                                                                                                                                                                                           |

| 12,32,48,58,59    | V <sub>ss</sub> | input        | Ground—Ground reference                                                                                                                                                                                                     |

| 33-38             | NC              |              | No Connection                                                                                                                                                                                                               |

#### MicroVAX Bus Interface Signals

**Data/Address lines (DAL < 15:00 > )**—These lines are bidirectional and are used to transfer address and data between the VIC and the CPU. During internal VIC register access cycles, when the  $\overline{\text{CSEL}}$  line is asserted, the DAL < 15:00 > lines transfer data to and from the internal registers. During the first part of an IACK cycle, the level of the pending interrupt being acknowledged is decoded from the low-order information on the DAL. During the response part of the IACK cycle when the pending interrupts on the IPL level being acknowledged are recognised and priority was passed by asserting IAKEI, the VIC transfers information from an Interrupt Vector (IVEC) register to DAL < 15:00 > if bit 01 of the Interrupt Vector register is clear. When bit 01 is set, an external vector must be made available from the interrupting device. Refer to the IVEC registers (0-15) for additional information. The DALs are driven by the VIC only when IAKEI is asserted, IAKEON is not asserted, and IVEC bit 0 is cleared. During all other conditions, the DALs are high-impedance during the IACK cycles.

Address strobe ( $\overline{AS}$ )—When asserted, this signal latches the information on the DAL<06:00>, CS<2:0>, and the  $\overline{WR}$  lines into the VIC. This information is used internally to latch the PIRQ<15:00> line information for the duration of a read or interrupt acknowledge bus cycle that addresses the VIC.

**Data strobe** ( $\overline{DS}$ )—This signal is used by the VIC for data timing during internal register access cycles and interrupt acknowledge cycles. When writing to one of the internal registers, the assertion of this signal strobes the DAL < 15:00 > line data into the selected register. When reading an internal register, the assertion of this signal is used to transfer the contents of the selected register onto the DAL < 15:00 > lines. When responding to an interrupt acknowledge cycle, the assertion of this signal is used to transfer the contents of the selected register onto the DAL < 15:00 > lines. When responding to an interrupt vestor register onto the DAL < 15:00 > lines.

**Write** ( $\overline{WR}$ )—This signal is used with the CS < 2:0> information by the VIC during CPU read, write, and interrupt acknowledge cycles to specify if the access to a VIC register is a read or write operation. A CPU-to-VIC write cycle is indicated if  $\overline{CSEL}$  is asserted when  $\overline{WR}$  is asserted and a write transaction is decoded from the CS lines.

**Control status (CS < 2:0 > )**—These lines and the  $\overline{WR}$  input are decoded to determine the presence of a read, write, or interrupt acknowledge bus cycle. The bus cycle selections are listed in Table 2.

Confidential and Proprietary

|                           | Table 2 • MicroVAX 78516 Bus Cycle Decoding* |   |   |   |                       |  |  |  |  |  |

|---------------------------|----------------------------------------------|---|---|---|-----------------------|--|--|--|--|--|

| CS Line WR CSEL Bus Cycle |                                              |   |   |   |                       |  |  |  |  |  |

| 2                         | 1                                            | 0 |   |   |                       |  |  |  |  |  |

| H                         | X                                            | Х | Н | L | Read                  |  |  |  |  |  |

| Н                         | Х                                            | Н | L | L | Write                 |  |  |  |  |  |

| L                         | Н                                            | Н | Н | Х | Interrupt acknowledge |  |  |  |  |  |

\*H = high level, L = low level, X = either high or low level.

**Ready (RDY)**—This signal is asserted by the VIC when its internal registers are accessed during a read or write cycle or during an interrupt acknowledge (IACK) cycle when the VIC is providing an interrupt vector. During IACK cycles, at least one ready slip will be generated to allow an interrupt acknowledge enable signal (IAKEI, IAKEOP, or IAKEON) to propagate through the daisychain. The total number of ready slips that occur depends on the length of the daisychain. This is an open drain (pulldown) output capable of sinking 16 mA.

#### **Interrupt Interface Signals**

**Peripheral interrupt request (PIRQ** < 15:00 >)—These input lines are used by peripheral circuits to request an interrupt. When one or more of these lines are asserted and the interrupts are enabled, the VIC will assert the appropriate IRQ line(s). Mapping between each PIRQ line and the IRQ line is programmable by software though the IRQ Map registers. The interrupt request can be sensed by a signal level or edge or by the signal polarity. The sensing is programmable by the user. Unused PIRQ lines must be connected to a valid logic level.

**Interrupt request** ( $\overline{IRQ} < 3:0 >$ )—One or more of these lines will be asserted by the VIC when a PIRQ line is asserted and the interrupts are enabled. The IRQ Map registers determine which IRQ line is asserted for a particular PIRQ line. An IRQ line will be deasserted when all pending interrupts mapped to that IRQ line have been serviced. These are open drain (pulldown) outputs that require external pullup resistors.

**Interrupt acknowledge** ( $\overline{IACK}$ )—This signal is a result of decoding the CS < 2:0> and the  $\overline{WR}$  lines and will be asserted for all interrupt acknowledge cycles. The signal is not affected by the interrupt acknowledge daisychain signals. It allows the external logic to disable the memory transceivers during an interrupt acknowledge cycle.

**External vector enable** ( $\overline{XVEC}$ )—This signal is used by external logic when the VIC is requesting that the interrupting device transfer its vector to the CPU. During an interrupt acknowledge cycle when the vector is being supplied by an external device, the hardware supplying the vector must assert the  $\overline{RDY}$  signal at the appropriate time. The assertion of the  $\overline{XVEC}$  signal also indicates that the VIC has placed the DALs in the high-impedance state.

#### Daisychain Interface Signals

**Interrupt acknowledge enable in** (**IAKEI**)—This input allows more than one VIC and other peripheral chips to be connected together in a daisychain. When this input is asserted, the VIC can respond to the current interrupt acknowledge bus cycle. This signal should be connected to a ground reference if the VIC is the highest priority device in the daisychain.

#### Preliminary

level. The CPU will respond with an interrupt acknowledge cycle that contains the priority level of the interrupt being acknowledged. The VIC then decodes the IACK cycle and IPL line information and if the VIC generated the interrupt and the IAKEI (daisychain input) signal is asserted, it selects the vector of the next PIRQ to be serviced for that IPL level. It then places that vector on the DAL < 15:00 > lines. If the VIC did not request the interrupt, it asserts the IAKEON (daisychain output) signal to allow the next devices in the daisy chain to be serviced. When the VIC is responding to an interrupt, it holds the IAKEON line from being asserted to prevent devices in the daisychain that have a lower priority from responding.

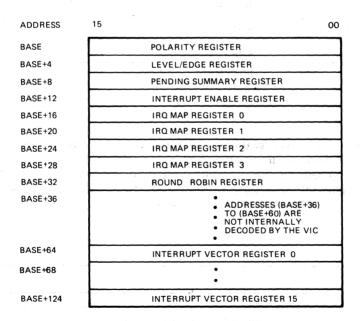

#### Registers

The VIC contains 16 interrupt vector registers and 9 interrupt control registers that allow each request to be individually configured by software. The internal VIC registers, shown in Figure 3, are accessible by the CPU and are used by software to configure the operation of the VIC. Each register consists of 16-bits and is located on a longword boundary. The base address is determined by external address decode logic. Direct access to the VIC registers is enabled when the  $\overline{\text{CSEL}}$  signal is asserted and the VIC decodes the address on the DAL < 06:00 > lines to select the register to be accessed.

The Polarity, Level/Edge Interrupt Enable and Pending Summary registers are cleared by the assertion of the  $\overline{\text{RESET}}$  input. Therefore, the VIC is programmed for the falling edge of PIRQ assertion and all interrupts are disabled. The IRQ Map and Interrupt Vector registers must be programmed before the interrupts are enabled.

**NOTE:** Only word access to the lower 16-bits of the longword are allowed to transfer data between the CPU and the VIC. Byte accesses and longword accesses are not allowed. Longword access may result in the CPU reading the incorrect data or lost data during a write cycle.

Figure 3 • MicroVAX 78516 Register Address and Descriptions

Confidential and Proprietary

# Preliminary

**Polarity register**—The polarity (POL) is a read/write register that selects the polarity of the input used to assert a PIRQ < 15:00 > line. When a bit is set, the corresponding line is asserted by a low-to-high transition or by a high level. When a bit is clear, the corresponding line is asserted by a high-to-low transition or by a low level. The register format is shown in Figure 4.

PIRQ<15:00>LEVEL/EDGE POLARITY

The POL register is used with the level/edge (LE) register to configure each PIRQ input. A PIRQ input may be configured to respond to a rising edge, a falling edge, a high level, or a low level signal. Table 3 shows the bit selections of the POL and LE registers and the resulting state of a PIRQ line. When the **RESET** line is asserted, the POL register is cleared.

| Table 3 - MicroVAX 78516 PIRQ Input Line Configurations |        |                     |  |  |  |

|---------------------------------------------------------|--------|---------------------|--|--|--|

| POL Bit                                                 | LE Bit | PIRQ Asserted State |  |  |  |

| 0                                                       | 0      | Falling edge        |  |  |  |

| 1                                                       | 0      | Rising edge         |  |  |  |

| 0                                                       | 1      | Low level           |  |  |  |

| 1                                                       | 1      | High level          |  |  |  |

**Level/Edge register**—The level/edge (LE) is a read/write register used to select the way in which a PIRQ < 15:00 > line detects an interrupt request. It allows the user to select either level or edge sensitive triggering. When a bit is set, the corresponding PIRQ line is level sensitive. When a bit is clear, the corresponding PIRQ line is edge sensitive. The polarity of the PIRQ line input is selected by the polarity register (POL). Figure 5 shows the LE register format.

PIRQ<15:00>LEVEL/EDGE TRIGGER

Figure 5 • MicroVAX 78516 Level/Edge Register Format

1-86

#### Preliminary

Level-sensitive inputs allow more than one device to be connected to a single PIRQ line by using a wired AND/OR structure. Once the correct polarity level is detected by the VIC, the corresponding interrupt pending bit is set in the pending summary register (PSR). The interrupt pending bit will remain set until the PIRQ line is cleared. Therefore, an interrupt acknowledge cycle from the CPU will not clear the interrupt pending bit in the PSR register until the PIRQ line is deasserted. If a wired AND/OR structure is used, an external pullup/pulldown resistor is required on the PIRQ line.

Edge sensitive inputs detect either a high-to-low (falling edge) or low-to-high (rising edge) transition. When the correct transition is detected, the corresponding bit in the PSR register will be set. When the **RESET** line is asserted, the LE register is cleared.

**Pending Summary register**—The pending summary register (PSR) is a read/clear register that provides a summary of the internal interrupt pending flags. When a bit is set, an interrupt request is pending for the corresponding PIRQ line. When a bit is clear, no interrupt is pending for the corresponding PIRQ line. When the VIC performs the IACK cycle, the corresponding PSR bit will be cleared if the corresponding bit in the LE register is cleared. If the corresponding bit in the LE register is set, the interrupting device must deassert its PIRQ line when serviced. The contents of the PSR register are latched during a read and IACK cycle. The register format is shown in Figure 6.

PIRQ<15:00>INTERRUPT PENDING

Figure 6 • MicroVAX 78518 Pending Summary Register Format

The VIC manages the setting and clearing the PSR register bits for level and edge sensitive PIRQ inputs as follows. When the  $\overrightarrow{\text{RESET}}$  input is asserted, the PSR register is cleared.

- For level sensitive PIRQ inputs, the corresponding PSR bit will be set when the PIRQ line is asserted and cleared when line is deasserted.

- For edge sensitive PIRQ inputs, the corresponding PSR bit is set on the asserting edge of the PIRQ input. The PSR bit for a PIRQ input will be cleared by an interrupt acknowledge cycle that acknowledges the interrupt request of the corresponding PIRQ line, when the software clears the PSR bit by writing a zero into the appropriate bit, or when information is written into the LE register.

**Interrupt Enable register**— The interrupt enable (IEN) is a read/write register that is used to enable or disable the reporting of interrupts to the CPU by each PIRQ line. When a bit is set, it allows an interrupt request from the associated PIRQ line to generate an interrupt to the CPU. When a bit is clear, the associated PIRQ line is prevented from generating an interrupt to the CPU. The register format is shown in Figure 7.

Confidential and Proprietary

| d | i | g | i | ł | а | ٥ | te. |  |  |  |  |  |

|---|---|---|---|---|---|---|-----|--|--|--|--|--|

|---|---|---|---|---|---|---|-----|--|--|--|--|--|

Preliminary

|     |       |   |         |     |     |      |       |     |                         |     |         |                                  |      |   |    | 1 00 |          |

|-----|-------|---|---------|-----|-----|------|-------|-----|-------------------------|-----|---------|----------------------------------|------|---|----|------|----------|

| 1.1 | 1     | 1 | ्ष      | 1   | ÷   | 1    |       | 1 i | $\mathbf{L}^{O,\alpha}$ | 1   | 1. 1 A. |                                  | 1    | 1 | 1  |      | 1        |

|     | 1. 19 | 1 | and the | 1.1 | 100 | í .  | 4 192 | 1   | 1.151                   | 110 | 10.0    | nd a                             | 1212 | 1 | 1. | 122  |          |

|     | F.    |   |         |     |     | 14.1 | 1     |     |                         |     | 6 - N   | - 19 - 19 - 19<br>- 19 - 19 - 19 |      |   |    |      | <u>.</u> |

PIRQ<15:00>INTERRUPT ENABLE/DISABLE

Figure 7 • MicroVAX 78516 Interrupt Enable Register Format

The IEN register enables or disables the generating of an interrupt to the CPU and does not affect the detection of interrupts by the VIC. When a PIRQ line is asserted, the corresponding bit in the PSR register is set regardless of the state of the IEN bit for the PIRQ line. The IEN register provides the support for a software interrupt polling scheme. The register is cleared when the RESET input is asserted.

**IRQ Map registers (0-3)**—The interrupt request map (IMAP0 through IMAP3) are read/write registers that are used to select the IRQ line to be asserted by the VIC when a PIRQ line is asserted. When a bit in one of the IMAP registers is set, the corresponding PIRQ line is mapped to the associated IRQ line. The register format is shown in Figure 8. Each register corresponds to one of the IRQ outputs as defined in Table 4.

PIRQ<15:00>TO MicroVAX IRQ LINE

Figure 8 • MicroVAX 78516 IRQ Map Registers (0-3) Format

| Table 4 • MicroVAX 78516 IMAP Register to IRQ Mapping |             |                                                                                                                 |   |           |              |                         |                |                              |

|-------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------|---|-----------|--------------|-------------------------|----------------|------------------------------|

| Register                                              | Line        |                                                                                                                 |   | 19. 1 F   |              |                         | 1.             | ta da ya e                   |

| IMAP3                                                 | IRQ3        |                                                                                                                 | 1 | 21 - 14 A | 1943 - A. A. | a generate              | t i fan de ser | and a state of the           |

| IMAP2                                                 | IRQ2        |                                                                                                                 |   |           |              | 1. 14 <sup>1</sup> . 14 | y digening     | nor a girlin<br>Angi an angi |

| IMAP1                                                 | <b>IRQ1</b> | The second se |   | a di kat  |              |                         |                | and a second                 |

| IMAP0                                                 | <b>IRQ0</b> |                                                                                                                 |   |           |              |                         |                | : *                          |

Example: If bit 3 of the IMAP1 register is set when the PIRQ3 line is asserted and the IEN register bit is set for this line, line IRQ1 will be asserted.

The IMAP registers are not initialized when the **RESET** line is asserted and the contents will be undefined until programmed by software.

Confidential and Proprietary

# Preliminary

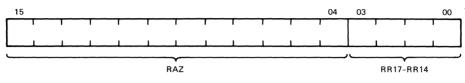

**Round Robin register**— The round robin (ROBIN is a read/write register that is used to select either fixed or round robin priority mode of operation for each IRQ level. More than one bit may be set in this register at a time and the register controls only the PIRQ lines for the associated VIC. The register is cleared when the RESET input is asserted. The register format is shown in Figure 9. Table 5 describes the function of each bit.

Figure 9 • MicroVAX 78516 Round Robin Register Format

|       | Table 5 • MicroVAX 78516 Round Robin Register Description                                                                                                                                                                                         |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit   | Description                                                                                                                                                                                                                                       |  |  |  |  |  |

| 15:04 | RAZ (Read as zeros)—Not used                                                                                                                                                                                                                      |  |  |  |  |  |

| 03:00 | RR17-RR14 (ROUND ROBIN IPL17-IPL14)—These bits select the priority mode for all interrupts mapped to lines $\overline{IRQ < 3:0>}$ . RR17 selects IRQ3 etc. When set, the round robin mode is selected. When cleared, the fixed mode is selected. |  |  |  |  |  |

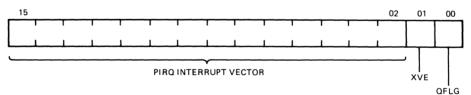

**Interrupt Vector registers (0-15)**—Each of the 16 interrupt vector (IVEC0 through IVEC15) registers is a read/write register that contains a fully programmable 16-bit vector. There is one IVEC register for each PIRQ line. Each register can select any location in the CPU System Control Block during the interrupt acknowledge cycle. The VIC automatically transfers the highest priority register information onto the DALs during the second half of the CPU IACK cycle. These registers can be read by software using a CPU read cycle. The register format is shown in Figure 10 and Table 6 describes the function of each bit.

Figure 10 • MicroVAX 78516 Interrupt Vector Registers (0-15) Format

T11 / M

. 17

•

(0.15) D

174 17 TOF1 / T

. .

|       | Iable 6 • MicroVAX 78516 Interrupt Vector Registers (0-15) Description                                                                                                                                                                                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Description                                                                                                                                                                                                                                                                                                                   |

| 15:02 | VECTOR (PIRQ interrupt vector)—This vector is the offset into the system control block (SCB) for the location of the interrupt routine.                                                                                                                                                                                       |

| 01    | XVE (External vector enable)—When set, the DAL < $15:00$ line drivers are disabled and the $\overline{XVEC}$ line is asserted during an IACK cycle, indicating that an external vector is to be supplied. When clear, the VIC will drive the contents of the IVEC register onto the DAL < $15:00$ lines during an IACK cycle. |

| 00    | QFLG (Normal/Q-bus processing flag)—Setting this bit causes the CPU to<br>respond by setting its internal IPL to 17 (hexadecimal). This feature is useful for<br>programming Q-bus systems. The status of bits 15:10 and the XVE bit 01 are<br>ignored by the CPU. When clear, the CPU will service the interrupt normally.   |

These registers are not initialized when the  $\overline{\text{RESET}}$  input is asserted and the contents of the register is undefined until programmed by software.

#### Interrupt Level Triggering and Edge Triggering

The sensing of an interrupt condition by the VIC may be programmed for each PIRQ input by the LE register. Each PIRQ line can be set to respond to either a signal level or to a signal transition (edge). The polarity of the sensed condition is also programmable.

In the edge-triggered mode, either a high-to-low or low-to-high transition on the PIRQ line will cause the VIC to latch the PIRQ line information. Further transitions on this PIRQ line will have no effect. After the acknowledgment of the latched assertion by the CPU, the VIC resets the latching mechanism allowing the user to again assert the interrupt with a proper transition on the PIRQ line. A latched PIRQ assertion may be cleared by writing to the LE register or by writing a zero to the corresponding bit of the pending status register.

In the level mode, the interrupting device must deassert the PIRQ input before the interrupt service routine ends to prevent the VIC from sensing the previous level and posting the same interrupt twice. During edge- or level-triggering, a bit in the pending summary register corresponding to that PIRQ line indicates the pending interrupt and if the interrupt is enabled, the VIC will assert the appropriate IRQ line as programmed in the IMAP register.

If the CPU responds to an interrupt caused by a edge-triggered signal, the completion of the IACK cycle will cause the VIC to clear the corresponding PSR register bit. If level-triggered mode was selected, the PSR bit would continue to reflect the PIRQ status.

Confidential and Proprietary

# Preliminary

#### **Absolute Maximum Ratings**

Stresses greater than the absolute maximum ratings may cause permanent damage to the device. Exposure to the absolute maximum ratings for extended periods may adversely affect the reliability of the device.

- Storage temperature range: -55°C to 125°C

- Active temperature range: 0°C to 70°C

- Power supply voltage (V<sub>DD</sub> to V<sub>SS</sub>): 0 V to 6 V

• Input or output voltage applied: -0.3 V to (V<sub>DD</sub> + 0.3 V)

#### **Recommended Operating Conditions**

• Temperature: 0°C to 70°C

- Power supply voltage: 4.75 V to 5.25 V

- Power dissipation: 1.0 W (maximum)

# dc Electrical Characteristics

The dc input and output parameters for the VIC are listed in Table 7.

|                                | Table 7 • Micro                                       | oVAX 78516 dc Input and Output  | Parameter      | rs             |       |

|--------------------------------|-------------------------------------------------------|---------------------------------|----------------|----------------|-------|

| Symbol                         | Parameter                                             | Test Conditions                 | Requin<br>Min. | ements<br>Max. | Units |

| V <sub>IH</sub>                | High-level<br>input voltage                           |                                 | 2.0            |                | V     |

| V <sub>IL</sub>                | Low-level<br>input voltage                            |                                 |                | 0.8            | V     |

| V <sub>0H</sub> <sup>1,2</sup> | High-level<br>output voltage                          | $I_{\rm OH} = -400 \ \mu A$     | 2.4            |                | V     |

| V <sub>ol</sub> <sup>1</sup>   | Low-level<br>output voltage                           | $I_{ol} = 2.0 \text{ mA}$       |                | 0.4            | V     |

| I <sub>ilc</sub>               | Input leakage<br>current                              | $0 < V_{in} < (V_{DD} - 0.6 V)$ |                | 30             | А     |

| I <sub>olc</sub>               | Output leakage<br>current                             | $0 < V_{in} < (V_{DD} - 0.6 V)$ |                | 30             | μA    |

| I <sub>ccac</sub> '            | Active supply current                                 |                                 |                | 100            | mA    |

| V <sub>olod1</sub> 4           | Open drain<br>pulldown<br>low-level output<br>voltage | $I_{0L} = 6.0 \text{ mA}$       |                | 0.4            | V     |

Confidential and Proprietary

Preliminary

| Symbol                          | Parameter                                             | Test Conditions          | Requir<br>Min. | ements<br>Max. | Units |

|---------------------------------|-------------------------------------------------------|--------------------------|----------------|----------------|-------|

| V <sub>OLOD2</sub> <sup>5</sup> | Open drain<br>pulldown<br>low-level output<br>voltage | $I_{ol} = 25 \text{ mA}$ |                | 0.4            | V     |

| C <sub>in</sub>                 | Input capacitance                                     |                          |                | 15             | pF    |

| C <sub>out</sub>                | Output capacitance                                    |                          |                | 20             | pF    |

<sup>1</sup>Only one output may be shorted to either supply rail at one time and the duration of the short must be less than 2 seconds.

<sup>2</sup>This specification also applies to the open drain output on IAKEOP

'All outputs floating, all inputs connected to either supply rail. The CLK input is fully swinging between both supply rails at 20 MHz.

<sup>4</sup>Applies only to the  $\overline{IRQ < 3:0 >}$  outputs.

$^{5}$ Applies only to the  $\overline{\text{RDY}}$  and  $\overline{\text{IAKEON}}$  outputs.

#### ac Electrical Characteristics

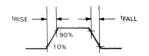

Figure 16 shows the input signal and clock signal waveforms and the parameters are listed in Table 8.

CLOCK INPUT

INPUT SIGNAL

Figure 16 • MicroVAX 78516 Input and Clock Signal Timing

| Symbol                        | Definition         | Require | ments              |

|-------------------------------|--------------------|---------|--------------------|

|                               |                    | Min.    | Max.               |

| t <sub>CPH</sub> <sup>1</sup> | Input clock high   | 15 ns   |                    |

| t <sub>cpl</sub>              | Input clock low    | 15 ns   |                    |

| t <sub>cw</sub>               | Input clock period | 50 ns   |                    |

| t <sub>rise</sub>             | Input signal rise  |         | 15 ns <sup>2</sup> |

| t <sub>FALL</sub>             | Input signal fall  |         | 15 ns <sup>2</sup> |

#### Table 8 • MicroVAX 78516 Input and Clock Signal Timing Parameters

$^1\mathrm{V}_{DD}$  must be greater than or equal to 4.75 V during this period.

<sup>2</sup>Measured between 10% and 90% levels.

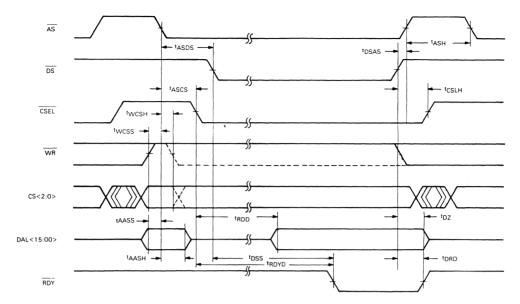

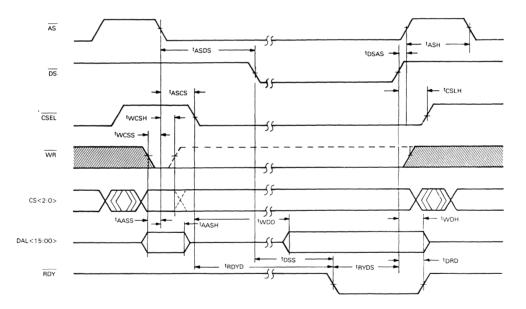

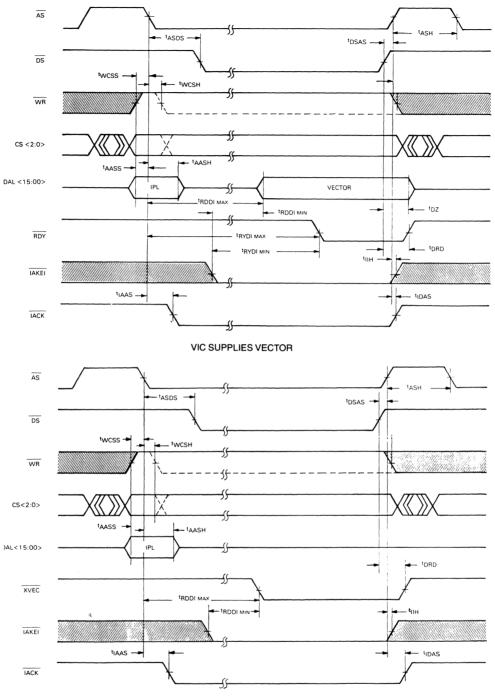

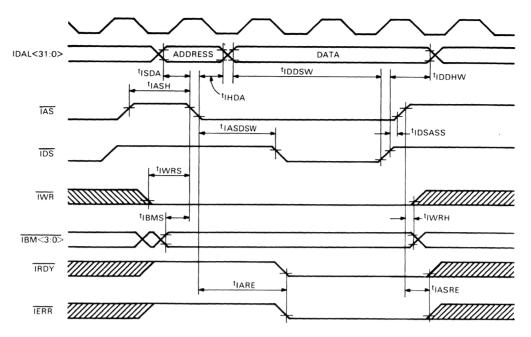

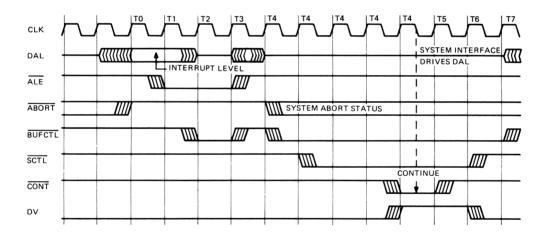

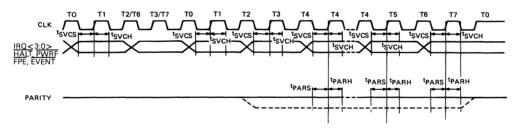

Figure 17 and 18 show the signal timing and symbols for a register read cycle and register write cycle, respectively, between the CPU and VIC. Figure 19 shows the signal timing and symbols for an interrupt acknowledge cycle when the VIC responds with a vector and when the external device supplies the vector. Figure 20 shows the timing and symbols for a daisychain configuration when the interrupt priority is not passed to the VIC and when it is passed to the VIC. Figure 21 shows the signal timing and symbols for the PIRQ input to IRQ output signal generation. It also includes the RESET input signal timing. Table 9 lists and defines the symbols and parameters used on the figures. The following notes apply to the table information.

• (T) = input clock period  $(t_{cw})$

• All units are nanoseconds (ns) except where indicated.

• All times are specified with a 100-pF capacitive load on the outputs.

• All times are measured at the 50 percent levels of the waveforms except where indicated.

## Confidential and Proprietary

# Preliminary

Figure 17 • MicroVAX 78516 Register Read Cycle Timing

Figure 18 • MicroVAX 78516 Register Write Cycle Timing

# Preliminary

EXTERNAL DEVICE SUPPLIES VECTOR

Figure 19 • MicroVAX 78516 Interrupt Acknowledge Cycle Timing

| Table 9 • | MicroVAX | 78516 | Signal | Timing | Parameters |

|-----------|----------|-------|--------|--------|------------|

|           |          |       |        |        |            |

| Symbol                         | Definition                                                                                                                                                           | Requireme<br>Min. | nts<br>Max.                           |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------|

| t <sub>AASH</sub>              | DAL < 06:00 > hold after $\overline{\text{AS}}$ assertion                                                                                                            | 10                |                                       |

| t <sub>AASS</sub>              | DAL < 06:00 > setup to $\overline{\text{AS}}$ assertion                                                                                                              | 15                |                                       |

| t <sub>ASCS</sub>              | $\overline{\text{CSEL}}$ assertion after $\overline{\text{AS}}$ assertion                                                                                            | _                 | 1 μs                                  |

| t <sub>ASDS</sub>              | $\overline{\text{DS}}$ assertion after $\overline{\text{AS}}$ assertion                                                                                              | 0                 |                                       |

| t <sub>ASH</sub>               | AS high after deassertion                                                                                                                                            | 1.5T              |                                       |

| t <sub>cslh</sub>              | $\overline{\text{CSEL}}$ hold after $\overline{\text{AS}}$ deassertion                                                                                               | 10                |                                       |

| t <sub>DRD</sub>               | $\overline{\text{RDY}}$ deassertion from $\overline{\text{DS}}$ deassertion                                                                                          |                   | 45                                    |

| t <sub>drdx</sub>              | XVEC deassertion from AS deassertion                                                                                                                                 |                   | 45                                    |

| t <sub>DSAS</sub>              | AS deassertion after DS deassertion                                                                                                                                  | 0                 |                                       |

| t <sub>DSS</sub>               | DS setup before RDY assertion                                                                                                                                        | 30                |                                       |

| t <sub>DZ</sub>                | Read data high-impedance delay from $\overline{\text{DS}}$ deassertion                                                                                               |                   | 30                                    |

| t <sub>ENA</sub> 1             | RESET deassertion to VIC enabled internally                                                                                                                          | 5T+250            |                                       |

| t <sub>IAAS</sub>              | $\overline{\text{IACK}}$ assertion after $\overline{\text{AS}}$ assertion                                                                                            | 1.5T              | 2T+30                                 |

| t <sub>idas</sub>              | IACK deassertion after AS deassertion                                                                                                                                | 0                 | 50                                    |

| t <sub>idrd</sub>              | IAKEO/IAKEOP deassertion from AS deassertion                                                                                                                         |                   | 60                                    |

| t <sub>IIDmin</sub>            | $\overline{IAKEON}/IAKEOP$ delay from $\overline{IAKEI}$ assertion ( $\overline{IAKEI}$ asserted 7.5T or more after $\overline{AS}$ )                                | 25                |                                       |

| t <sub>IIDmax</sub>            | $\overline{IAKEO}/IAKEOP$ delay from $\overline{AS}$ assertion ( $\overline{IAKEI}$ asserted less than 7.5T more after $\overline{AS}$ )                             |                   | 8.5T+25                               |

| t <sub>IIH</sub>               | IAKEI hold after AS deassertion                                                                                                                                      | 0                 |                                       |

| t <sub>PIAD</sub> <sup>2</sup> | PIRQ assertion to IRQ assertion delay                                                                                                                                | 0                 | 100                                   |

| t <sub>pidd</sub>              | PIRQ deassertion to IRQ deassertion delay<br>(applicable to level triggering only)                                                                                   |                   | 150                                   |