## **Important Notice**

As of May 17, 1998, Digital Equipment Corporation's StrongARM, PCI Bridge, and Networking component businesses, along with the chip fabrication facility in Hudson, Massachusetts, were acquired by Intel Corporation and transferred to Intel Massachusetts, Inc. As a result of this transaction, certain references to web sites, telephone numbers, and fax numbers have changed in the documentation. This information will be updated in the next version of this manual. Copies of documents that have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling **1-800-332-2717** or by visiting Intel's website for developers at:

#### http://developer.intel.com

The Intel Massachusetts Customer Technology Center continues to service your StrongARM Product, Bridge Product, and Network Product technical inquiries. Please use the following information lines for support:

| For documentation and general informa   | tion:             |  |

|-----------------------------------------|-------------------|--|

| Intel Massachusetts Information Line    |                   |  |

| United States:                          | 1-800-332-2717    |  |

| Outside United States:                  | 1-303-675-2148    |  |

| Electronic mail address:                | techdoc@intel.com |  |

|                                         |                   |  |

| For technical support:                  |                   |  |

| Intel Massachusetts Customer Technologi | ogy Center        |  |

| Phone (U.S. and international):         | 1-978-568-7474    |  |

| Fax:                                    | 1–978–568–6698    |  |

| Electronic mail address:                | techsup@intel.com |  |

# Upgrading to the Digital Semiconductor 21140–AE and 21140–AF

#### Overview

The purpose of this document is to provide customers of Digital Semiconductor's 21140 family with information to upgrade to its newest and most powerful members, the 21140–AE and the 21140–AF. The 21140–AE has already achieved product qualification, and the 21140–AF is scheduled to achieve product qualification in May 1997, providing customers with timely upgrades to more robust products.

This document describes how to upgrade your designs from current Digital Semiconductor 21140 and 21140A devices (order numbers 21140–AB and 21140–AC, respectively) to the latest Digital Semiconductor 21140A devices (order numbers 21140–AE and 21140–AF). It also describes register-level differences, and serves as a convenient reference for upgrading customer-developed 21140 drivers. For detailed programming information and for register descriptions, consult the *Digital Semiconductor 21140A PCI Fast Ethernet LAN Controller Hardware Reference Manual* (order number EC–QN7NF–TE).

#### Advantages of Upgrading to the 21140-AE and the 21140-AF

The 21140–AE and the 21140–AF are pin compatible and are the functional equivalent of the 21140–AB and 21140–AC, yet offer the following additional features and performance enhancements:

- Supports early receive and transmit interrupt for improved data throughput<sup>1</sup>

- Provides an upgradable boot ROM interface of up to 256KB that can support remote boot applications<sup>1</sup>

- Implements low-power management with two power-saving modes (sleep or snooze) to minimize power consumption<sup>1</sup>

- Supports automatic loading of subsystem vendor ID and subsystem ID from the serial ROM to the configuration register that can uniquely identify a customer's 21140 product<sup>1</sup>

- Supports PCI read line, read multiple, and write and invalidate commands to maximize PCI bus performance and to minimize CPU utilization

- Supports both PCI 5.0-V and 3.3-V signaling environments for a variety of hardware applications<sup>1</sup>

- Contains a variety of flexible address filtering modes, including pass all incoming packets with a status report for monitoring purposes<sup>1</sup>

#### Physical Features of the 21140–AE and the 21140–AF

The 21140–AE and the 21140–AF are packaged in the same 144-pin PQFP package as other 21140 devices, with the same pinouts as the 21140–AB and 21140–AC, making them drop-in replacements. Compared to the 21140–AB, each 21140–AE and 21140–AF has an internal 2-K $\Omega$  pull-down resistor added to pin **sr\_cs**, and internal 5-K $\Omega$  pull-up resistors<sup>2</sup> added to pins **sr\_do**, tdi, and tms.

<sup>&</sup>lt;sup>1</sup>This feature is also available on the 21140–AC device.

<sup>&</sup>lt;sup>2</sup>The value of this resistor was 12 K $\Omega$  for the 21140–AC.

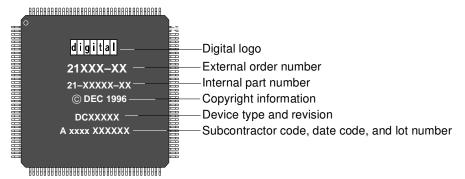

### **Package Marking Conventions**

All Digital Semiconductor 21140 devices use the following conventions for package markings.

#### **Cross-Referencing Package Markings**

Use the following table to cross-reference the 21140 and 21140A package markings with related documentation.

| External Order<br>Number | Device | Internal Part<br>Number | Device Type<br>and Revision | Hardware Reference<br>Manual Number | Data Sheet<br>Number |

|--------------------------|--------|-------------------------|-----------------------------|-------------------------------------|----------------------|

| 21140-AB                 | 21140  | 21-40673-02             | DC1010 CA                   | EC-QC0CA-TE                         | EC-QC0BB-TE          |

| 21140-AC                 | 21140A | 21-43864-01             | DC1036 DA                   | EC-QN7NC-TE                         | EC-QN7PC-TE          |

| 21140-AE                 | 21140A | 21-43864-03             | DC1064 B                    | EC-QN7NE-TE                         | EC-QN7PE-TE          |

| 21140–AF                 | 21140A | 21-43864-04             | DC1064 C                    | EC-QN7NF-TE                         | EC-QN7PF-TE          |

#### **Migrating Drivers**

Software compatibility is retained for those customers utilizing Digital Semiconductor's drivers, allowing the same drivers and SROM format to be used with the 21140–AE and the 21140–AF that were used for the 21140–AB and the 21140–AC. For those customers who have developed their own drivers and require register information, see the section titled Comparing Registers in the 21140 Family.

The following table lists the network and communications software available from Digital Semiconductor for the 21140 and 21140A devices. For the latest driver and software information, see the Networks and Communications page available on the Digital Semiconductor World Wide Web at: http://www.digital.com:80/.i/info/semiconductor

| Drivers                               | Supports                                                                                                                             |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| NDIS3 Unified DC21x4 driver           | NDIS3 MAC drivers for Windows NT 3.5, Windows NT 3.51, Windows NT 4.0, Windows for Workgroups 3.11, Windows 95, and Windows 95 OSR 2 |

| NDIS4 Unified DC21x4 driver           | NDIS4 MAC drivers for Windows NT 4.0 and Windows 95 OSR 2                                                                            |

| Novell Server Unified DC21x4 driver   | 32-bit ODI drivers for Versions 3.1 <i>x</i> and 4 <i>.x</i> Novell Servers, Client32 drivers for DOS and Windows 95                 |

| Novell Client Unified DC21x4 driver   | 16-bit ODI drivers for DOS                                                                                                           |

| NDIS2 Unified DC21x4 driver           | NDIS2 MAC drivers for DOS, OS/2, Windows 3.1, Windows for Workgroups 3.11, and Windows 95                                            |

| SCO UNIX Unified DC21x4 driver        | SCO UNIX LLI and MDI drivers                                                                                                         |

| Support Files                         | Description                                                                                                                          |

| SROM Specification for DC21x4 devices | SROM data and format requirements for interoperability with DC21x4 drivers                                                           |

| SROM programming tool kit             | SROM programming utilities                                                                                                           |

| BSDL                                  | Boundary Scan Description Language files for Digital Semiconductor network chips                                                     |

#### **Comparing Registers in the 21140 Family**

Many enhancements have been added to the 21140–AE and the 21140–AF, resulting in a device that consumes less power with a higher throughput, and is compliant with revisions 2.0 and 2.1 of the *PCI Local Bus Specification*. Some changes have also been made to the register fields of the 21140–AE and the 21140–AF; these items are identified with asterisks in the following table and may require some support for customer-developed drivers.

| New or<br>Different Items | 21140–AB                                    | 21140-AC                                                                                                                                                                              | 21140–AE and 21140–AF                                                                                                                                                                 |

|---------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration R           | egisters                                    |                                                                                                                                                                                       |                                                                                                                                                                                       |

| CBER                      | Reserved                                    | Boot ROM                                                                                                                                                                              | Boot ROM                                                                                                                                                                              |

| CFRV<7:0>                 | 12H                                         | 20H                                                                                                                                                                                   | 22H                                                                                                                                                                                   |

| CFCS<4>                   | Reserved                                    | Reserved                                                                                                                                                                              | Memory write and invalidate enable                                                                                                                                                    |

| CFDD<31>                  | Reserved                                    | Sleep mode                                                                                                                                                                            | Sleep mode                                                                                                                                                                            |

| CFDD<30>                  | Reserved                                    | Snooze mode                                                                                                                                                                           | Snooze mode                                                                                                                                                                           |

| CFLT<7:0>                 | Reserved                                    | Reserved                                                                                                                                                                              | Cache-line size in longwords                                                                                                                                                          |

| Control and Sta           | tus Registers                               |                                                                                                                                                                                       |                                                                                                                                                                                       |

| CSR0<24>                  | Reserved                                    | Reserved                                                                                                                                                                              | Write and invalidate enable                                                                                                                                                           |

| CSR0<23>                  | Reserved                                    | Reserved                                                                                                                                                                              | Read line enable                                                                                                                                                                      |

| CSR0<21>                  | Reserved                                    | Read multiple enable (for bursts greater than two longwords)                                                                                                                          | Read multiple enable (for bursts greater than two longwords)                                                                                                                          |

| CSR0<20>                  | Reserved                                    | Big endian descriptor                                                                                                                                                                 | Big endian descriptor                                                                                                                                                                 |

| CSR0<19>                  | Reserved                                    | Automatic polling interval                                                                                                                                                            | Automatic polling interval                                                                                                                                                            |

| CSR0 value after reset    | FFF80000H                                   | FF800000H                                                                                                                                                                             | FE000000H                                                                                                                                                                             |

| CSR5<16>*                 | Normal interrupt<br>summary                 | Normal interrupt summary<br>Added (compared to 21140–AB):<br>• CSR5<11> – General-purpose timer expired<br>• CSR5<14> – Early receive interrupt                                       | Normal interrupt summary<br>Added (compared to 21140–AB):<br>• CSR5<11> – General-purpose timer expired<br>• CSR5<11> – Early receive interrupt                                       |

| CSR5<15>*                 | Abnormal interrupt<br>summary               | Abnormal interrupt summary<br>Added (compared to 21140–AB):<br>• CSR5<10> – Early transmit interrupt<br>Removed (compared to 21140–AB): •<br>CSR5<11> – General-purpose timer expired | Abnormal interrupt summary<br>Added (compared to 21140–AB):<br>• CSR5<10> – Early transmit interrupt<br>Removed (compared to 21140–AB):<br>• CSR5<14> – General-purpose timer expired |

| CSR5<14>                  | Reserved                                    | Early receive interrupt                                                                                                                                                               | Early receive interrupt                                                                                                                                                               |

| CSR5<10>                  | Reserved                                    | Early transmit interrupt                                                                                                                                                              | Early transmit interrupt                                                                                                                                                              |

| CSR6<31>                  | Reserved                                    | Special capture effect enable                                                                                                                                                         | Special capture effect enable                                                                                                                                                         |

| CSR6<30>                  | Reserved                                    | Receive all enable                                                                                                                                                                    | Receive all enable                                                                                                                                                                    |

| CSR6<25>                  | Must be one <sup><math>\dagger</math></sup> | Must be one                                                                                                                                                                           | Must be one                                                                                                                                                                           |

| CSR6 value after reset    | E2000040H <sup>‡</sup>                      | 32000040Н                                                                                                                                                                             | 32000040Н                                                                                                                                                                             |

reset

\*Customer-developed 21140 drivers that use these registers may require modification. For detailed programming information and for register descriptions, consult the *Digital Semiconductor 21140A PCI Fast Ethernet LAN Controller Hardware Reference Manual* (order number EC–QN7NF–TE).

<sup>†</sup>CSR6<25> is documented in the original *Digital Semiconductor 21140 PCI Fast Ethernet LAN Controller Hardware Reference Manual* (order number EC–QC0CA–TE) as Must Be Zero. For all versions of the 21140, this bit should be documented as Must Be One. When operating the 21140 in Symbol mode, CSR6<25>=0 causes the 21140 to clear an internal link failure flag after the establishment of a new link earlier than defined by the IEEE 802.3 standard. When CSR6<25>=1, the link failure is cleared according to the standard. Digital Semiconductor suggests that this software update be made for all versions of the 21140.

<sup>‡</sup>The values after reset were incorrectly documented for CSR6 as E0000040H and for CSR9 as FFF097F0H in the *Digital Semiconductor 21140 PCI Fast Ethernet LAN Controller Hardware Reference Manual* (order number EC–QC0CA–TE).

| New or<br>Different Items                        | 21140–AB                                                              | 21140–AC                                                                                                                                                                                                   | 21140–AE and 21140–AF                                                                                                                                                                                      |

|--------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSR7<14>                                         | Reserved                                                              | Early receive interrupt enable                                                                                                                                                                             | Early receive interrupt enable                                                                                                                                                                             |

| CSR7<10>                                         | Reserved                                                              | Early transmit interrupt enable                                                                                                                                                                            | Early transmit interrupt enable                                                                                                                                                                            |

| CSR8<28>                                         | Reserved                                                              | Overflow counter overflow                                                                                                                                                                                  | Overflow counter overflow                                                                                                                                                                                  |

| CSR8<27:17>                                      | Reserved                                                              | Overflow counter                                                                                                                                                                                           | Overflow counter                                                                                                                                                                                           |

| CSR8 value after reset                           | FFFE0000H                                                             | Е0000000Н                                                                                                                                                                                                  | Е0000000Н                                                                                                                                                                                                  |

| CSR9<14>                                         | Serial ROM read enable                                                | Serial and boot ROM read enable                                                                                                                                                                            | Serial and boot ROM read enable                                                                                                                                                                            |

| CSR9<13>                                         | Serial ROM write enable                                               | Serial and boot ROM write enable                                                                                                                                                                           | Serial and boot ROM write enable                                                                                                                                                                           |

| CSR9<7:4>                                        | Reserved                                                              | Boot ROM data                                                                                                                                                                                              | Boot ROM data                                                                                                                                                                                              |

| CSR9<3:0>                                        | Serial ROM control                                                    | Boot ROM data or serial ROM control                                                                                                                                                                        | Boot ROM data or serial ROM control                                                                                                                                                                        |

| CSR9 value after reset                           | FFF497FFH <sup>‡</sup>                                                | FFF483FFH                                                                                                                                                                                                  | FFF483FFH                                                                                                                                                                                                  |

| CSR10                                            | Reserved                                                              | Boot ROM programming address                                                                                                                                                                               | Boot ROM programming address                                                                                                                                                                               |

| SSID                                             | Reserved                                                              | Subsystem vendor ID                                                                                                                                                                                        | Subsystem vendor ID                                                                                                                                                                                        |

| Receive and Tra                                  | ansmit Descriptor                                                     | ſS                                                                                                                                                                                                         |                                                                                                                                                                                                            |

| RDES0<30>*                                       | Most-significant<br>bit of frame length<br>indicator,<br>RDES0<30:16> | Filtering fail is always 0 unless receive all addressing mode is enabled, (CSR6<30>=1)                                                                                                                     | Filtering fail is always 0 unless receive all addressing mode is enabled, (CSR6<30>=1)                                                                                                                     |

| RDES0<15>*                                       | Error Summary                                                         | Error summary<br>Removed (compared to 21140–AB):<br>• RDES0<0> – Overflow                                                                                                                                  | Error summary<br>Removed (compared to 21140–AB):<br>• RDES0<0> – Overflow                                                                                                                                  |

| RDES0<3>                                         | Always a one                                                          | Receive error reported from physical layer                                                                                                                                                                 | Receive error reported from physical layer                                                                                                                                                                 |

| RDES0<0>*                                        | Reports FIFO<br>overflow                                              | Reports that FIFO overflow occurred during a reception only if FIFO had been partially unloaded to the host. Otherwise, the overflowed frame is discarded and counted in CSR8<27:17>, the overflow counter | Reports that FIFO overflow occurred during a reception only if FIFO had been partially unloaded to the host. Otherwise, the overflowed frame is discarded and counted in CSR8<27:17>, the overflow counter |

| TDES0<2>                                         | Reserved                                                              | Link fail report                                                                                                                                                                                           | Link fail report                                                                                                                                                                                           |

| Bus Commands                                     | 5                                                                     |                                                                                                                                                                                                            |                                                                                                                                                                                                            |

| Memory read line                                 | Unsupported                                                           | Unsupported                                                                                                                                                                                                | Supported as initiator and target                                                                                                                                                                          |

| Memory write and invalidate                      | Unsupported                                                           | Unsupported                                                                                                                                                                                                | Supported as initiator and target                                                                                                                                                                          |

| Expanded Featu                                   | ures                                                                  |                                                                                                                                                                                                            |                                                                                                                                                                                                            |

| Support for big<br>endian descriptors            | Unsupported                                                           | Supported                                                                                                                                                                                                  | Supported                                                                                                                                                                                                  |

| Automatic polling intervals                      | 4                                                                     | 8                                                                                                                                                                                                          | 8                                                                                                                                                                                                          |

| JTAG boundary-<br>scan includes boot<br>ROM pins | Unsupported                                                           | Supported                                                                                                                                                                                                  | Supported                                                                                                                                                                                                  |

\*Customer-developed 21140 drivers that use these registers may require modification. For detailed programming information and for register descriptions, consult the *Digital Semiconductor 21140A PCI Fast Ethernet LAN Controller Hardware Reference Manual* (order number EC–QN7NF–TE).

## **Comparing Characteristics of the 21140 Family**

The following table compares the programming characteristics of the 21140–AB and the 21140–AC to the 21140–AE and the 21140–AF.

| Characteristic                                                                                                                             | 21140-AB               | 21140–AC                                                                                             | 21140–AE and 21140–AF                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Receive overflow errata                                                                                                                    | Did not exist          | Exists                                                                                               | Resolved                                                                                             |

| Minimum PCI clock frequency                                                                                                                | 25 MHz                 | 24.9 MHz <sup>1</sup>                                                                                | 20 MHz                                                                                               |

| Boot ROM                                                                                                                                   | Unsupported            | CBER – Base address and size<br>CSR9 – Management<br>CSR10 –Address                                  | CBER – Base address and size<br>CSR9 – Management<br>CSR10 – Address                                 |

| Subsystem Vendor ID and Subsystem ID                                                                                                       | Unsupported            | SSID                                                                                                 | SSID                                                                                                 |

| Sleep and snooze low-power modes                                                                                                           | Unsupported            | CFDD<31:30>                                                                                          | CFDD<31:30>                                                                                          |

| Receive all address filtering mode                                                                                                         | Unsupported            | CSR6<30> – Receive all <sup>2</sup><br>RDES0<30> – Filtering fail                                    | CSR6<30> – Receive all<br>RDES0<30> – Filtering fail                                                 |

| Early receive interrupt to indicate that the first data buffer of the packet is filled                                                     | Unsupported            | CSR5<14> – Early receive interrupt<br>CSR7<14> – Early receive enable                                | CSR5<14> – Early receive interrupt<br>CSR7<14> – Early receive enable                                |

| Early transmit interrupt to indicate that the<br>packet to be transmitted was fully transferred<br>into the chip's internal transmit FIFOs | Unsupported            | CSR5<10> – Early transmit interrupt<br>CSR7<10> – Early transmit enable                              | CSR5<10> – Early transmit interrupt<br>CSR7<10> – Early transmit enable                              |

| Enhanced resolution of capture effect on network                                                                                           | Unsupported            | CSR6<31>                                                                                             | CSR6<31>                                                                                             |

| Indicator that link test failed before the frame was transmitted through the symbol port                                                   | Unsupported            | TDES0<2>                                                                                             | TDES0<2>                                                                                             |

| Indicator that a receive error in the physical<br>layer was reported during the frame<br>reception                                         | Unsupported            | RDES0<3>                                                                                             | RDES0<3>                                                                                             |

| Promiscuous mode setting after reset                                                                                                       | CSR6<6>=1<br>(Enabled) | $CSR6<6>=x^{1}$ (Undefined)                                                                          | CSR6<6>=1<br>(Enabled)                                                                               |

| Memory-read-multiple command on the PCI bus                                                                                                | Unsupported            | CSR0<21>                                                                                             | CSR0<21>                                                                                             |

| Specifies, in units of 32-bit words, the system cache line size                                                                            | Unsupported            | Unsupported                                                                                          | CFLT<7:0>                                                                                            |

| Supports the memory-write-and-invalidate (MWI) command on the PCI bus                                                                      | Unsupported            | Unsupported                                                                                          | CFCS<4><br>CSR0<24>                                                                                  |

| Supports the memory-read-line (MRL) command on the PCI bus                                                                                 | Unsupported            | Unsupported                                                                                          | CSR0<23>                                                                                             |

| Cache alignment limit value (CSR0<15:14>)                                                                                                  | Cannot be zero         | No limitations                                                                                       | No limitations unless PCI commands<br>MWI or MRL are enabled                                         |

| Programmable burst length value<br>(CSR0<13:8>)                                                                                            | No limitations         | No limitations                                                                                       | No limitations unless PCI commands<br>MWI or MRL are enabled                                         |

| Bits for transmit automatic polling                                                                                                        | CSR0<18><br>CSR0<17>   | CSR0<19><br>CSR0<18><br>CSR0<17>                                                                     | CSR0<19><br>CSR0<18><br>CSR0<17>                                                                     |

| Receive overflow counter                                                                                                                   | Unsupported            | CSR8<27:17> – Overflow counter<br>overflow indicator<br>RDES0<0> – Zero<br>RDES0<15> – Error summary | CSR8<27:17> – Overflow counter<br>overflow indicator<br>RDES0<0> – Zero<br>RDES0<15> – Error summary |

<sup>1</sup>This behavior is described in an errata.

<sup>2</sup>An errata affects this characteristic.

#### **Hardware Characteristics**

The following table describes the temperature and power characteristics of the 21140 family of devices.

| 21140 Family                                        |

|-----------------------------------------------------|

| 0°C to 70°C (32°F to 158°F)                         |

| 144-pin PQFP                                        |

| 413 mW maximum                                      |

| 198 mW maximum                                      |

| 248 mW maximum                                      |

| <b>Vdd</b> = 3.3 V, <b>Vdd_clamp</b> = 5 V or 3.3 V |

| -55°C to +125°C (~67°F to 257°F)                    |

|                                                     |

#### **Ordering Digital Semiconductor Products**

To order the Digital Semiconductor 21140A PCI Fast Ethernet LAN Controller and Evaluation Boards, contact your local distributor. To obtain a *Digital Semiconductor Product Catalog*, contact the Digital Semiconductor Information Line.

The following table lists some of the products available from Digital Semiconductor:

| Product                                                            | Order Number          |

|--------------------------------------------------------------------|-----------------------|

| Digital Semiconductor 21140A PCI Fast Ethernet LAN Controller      | 21140-AE              |

| Digital Semiconductor 21140A PCI Fast Ethernet LAN Controller      | 21140–AF <sup>1</sup> |

| Digital Semiconductor 21140A 10/100BASE–TX Evaluation<br>Board Kit | 21A40-TX              |

<sup>1</sup>Available only as a prototype until the product qualifies.

#### **Ordering Digital Semiconductor Documentation**

For a complete list of available documentation, contact the Digital Semiconductor Information Line or visit Digital Semiconductor's World Wide Web Internet site.

To determine which documents apply to a particular device part number, visit the Digital Semiconductor Documentation Library on Digital Semiconductor's World Wide Web Internet site at:

http://ftp.digital.com/pub/Digital/info/semiconductor/literature/dsc-library.html

#### For More Information

To learn more about the 21140A, visit the Digital Semiconductor World Wide Web Internet site:

http://www.digital.com/semiconductor

or contact the Digital Semiconductor Information Line:

United States and Canada 1–800–332–2717 Outside North America 1–510–490–4753 Electronic mail address semiconductor@digital.com

While DIGITAL believes the information in this publication is correct as of the date of publication, it is subject to change without notice.

© Digital Equipment Corporation 1997.

All rights reserved.

Printed in U.S.A.

EC-R2S0B-TE

DIGITAL, Digital Semiconductor, and the DIGITAL logo are trademarks of Digital Equipment Corporation.

Digital Semiconductor is a Digital Equipment Corporation business.

Novell is a registered trademark of Novell, Inc.; OS/2 is a registered trademark of International Business Machines Corporation; SCO is a trademark of Santa Cruz Operations, Inc.; UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Ltd.; Windows 95 is a registered trademark, and Windows NT and Windows for Workgroups are trademarks of Microsoft Corporation. All other trademarks and registered trademarks are the property of their respective owners.