# OMNIBUS

## **Specification**

TITLE: OMNIBUS Specification

ABSTRACT: This document describes in detail the mechanical and electrical characteriatics of a bus scheme used to interconnect circuit modules that form the various PDP-8 series of mini-computers. This specification should be followed carefully when designing a device that is going to connect to the UMNBUS.

| 19 -Aug-76 - | L.Narhi | C.Noelche | A | - |

|--------------|---------|-----------|---|---|

|--------------|---------|-----------|---|---|

| Size | Code | Number     | Rev. |

|------|------|------------|------|

|      |      |            |      |

| А    | DS   | EL00157-00 | ) A  |

|       |                                         | ******* |                                |

|-------|-----------------------------------------|---------|--------------------------------|

|       | PAGE REVISIO                            |         | DL                             |

| PAGE  |                                         | PAGE    |                                |

| NO.   |                                         | NO.     | PAGE REVISIONS                 |

|       | TRGE REVISIONS                          |         |                                |

| 1     | A                                       | 31      | A                              |

| 2     | A                                       | 32      | A                              |

| 3     | A                                       | 33      | A                              |

| 4     | A                                       | 34      | A                              |

| 5     | A                                       | 35      | A                              |

| 6     | A                                       | 36      | A                              |

| 7     | A                                       | 37      | A                              |

| 8     | A                                       | 38      | A                              |

| 10    | A                                       | 39      | A                              |

| 10    | A                                       | 40      | A .<br>A                       |

| 11    | A<br>A                                  | 41      | A                              |

| 13    | A                                       | 43      | A                              |

| 14    | Å                                       | 44      | Ä                              |

| 15    | 4                                       | 45      | Ä                              |

| 16    | Å                                       | 46      | Ä                              |

| 17    | A                                       | 1 47    | A .                            |

| 18    | A                                       | 48      | A                              |

| 19    | A                                       | : 49    | A                              |

| 20    | A                                       | ! 50    | A                              |

| 21    | λ                                       | ! 51    | A                              |

| 22    | A                                       | 1 52    | A                              |

| 23    | A                                       | 1 53    | A                              |

| 24    | A                                       | 54      | A                              |

| 25    | A<br>A                                  |         |                                |

| 27    | A                                       | :       |                                |

| 28    | A                                       | :       |                                |

| 29    | Å                                       | -       |                                |

| 30    | ñ.                                      | ī       |                                |

|       |                                         |         |                                |

| SEC.  |                                         | I SEC.  |                                |

| REV   |                                         | ! REV   |                                |

|       | *************************************** |         | ****************************** |

| STD   |                                         | I STD   |                                |

| REV   | A                                       | I REV   | A                              |

| ***** |                                         |         |                                |

CUSUITED EN-010474-14-16 R177(327)

Page 3

TABLE OF CONTENTS

1.0 GENERAL. 2.0 MAJOR GROUPS OF SIGNALS 2.1 Memory Address 2.2 Memory Data and Direction Control 2.3 Data Bus 2.4 I/O Control Signals 2.5 DMA Control Signals 2.6 Timing Signals 2.7 **CPU** State 2.8 Memory Timing Signals Miscellaneous Signals 2.9 2.10 Interconnection Diagram 3.0 DETAILED LOGIC DESCRIPTION 3.1 Memory Address 3.2 Memory Data and Direction Control 3.3 Data Bus 3.4 I/O Control Signals 3.5 DMA Control Signals (also includes a description of DMA sequence) 3.6 Timing Signals 3.7 CPU State 3.8 Memory Timing Signals 3.9 Miscellaneous Signals 4.0 TIMING 4.1 Time Pulses and Time States 4.2 Memory Timing 4.3 Relationship Between CPU and Memory Timing 4.4 Basic I/O Timing 4.5 Expanded I/O Timing 4.6 Data Break Timing 4.7 CPU States, INT IN PROG H 4.8 Timing Start and Stop 4.9 Asynchronous Signals 4.10 Special Signals 5.0 ELECTRICAL CHARACTERISTICS AND INTERFACING 5.1 Logic Levels 5.2 Bus Loads 5.3 Driving the OMNIBUS 5.4 Drive Available for Peripherals 5.5 Receivers and Load Relief Techniques

digital

-

- -5.6 Sample I/O Interface

- Sample DMA (Data Break) Interface 5.7

- General Cautions Regarding Interfaces Transmission Line Effects 5.8

- 5.9

- 6.0 POWER SUPPLY REQUIREMENTS

- 7.0 INDEX OF OMNIBUS SIGNAL NAMES

- GLOSSARY OF REFERENCE DOCUMENTS 8.0

1.0 G"NERAL

1.1

This specification describes the OMNIBUS used on the PDP-8E, PDP-8M, PDP-8P and PDP-8A computers. The OMNIBUS is an internal, parallel bus used to connect central processor, memories, peripherals, etc.

#### 1.2

Physically, the OMNIBUS consists of DEC standard H863 connector blocks (DEC part number 12-10258) arranged to accept quad modules.

#### 1.3

Certain pins are preassigned as follows:

Ground: Pins C, F, N, T of all connectors (ACl, AC2, AFl, AF2, AN1, AN2, AT1, AT2, BCl, BC2, BF1, BF2, BN1, BN2, BT1, BT2, CC1, CC2, CF1, CF2, CN1, CN2, CT1, CT2, DC1, DC2, DF1, DF2, DN1, DN2, DT1, DT2)

+5 volts: Pins AA2, BA2, CA2

+15 volts: Pin DA2

-15 volts: Pins AB2, BB2, CB2, DB2

Test points or special signals: Pins AAl, ABl, BAl, BBl, CAl, CBl, DAl, DBl.

#### 1.4

All other pins are parallel-wired (pin CM2 of slot 1 is wired to pin CM2 of slot 2, etc.) to form the 96 signals of the OMNIBUS.

#### 1.5

A note on nomenclature:

Many places in this document, symbology of the general form MD<3:8>L is used. This symbology should be read "MD3 L through MD8 L", and interpreted as meaning MD3 L, MD4 L, MD5 L, MD6 L, MD7 L, and MD8 L.

didital

#### 1.6

Occasionally this specification will separately refer to PDP-8E and PDP-8A. Unless specifically stated to the contrary, statements recarding the PDP-8E apply equally to the PDP-8M and PDP-8F.

#### 1.7

When this specification describes the operation of signal names it is done in a positive manner. I.e., unless the specification says otherwise, don't do it.

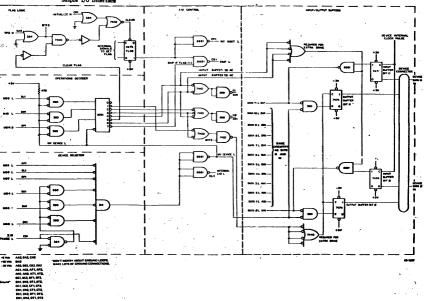

#### 2.0 MAJOR GROUPS OF SIGNALS

The 96 signals of the OMNIBUS can be divided into 9 major classes, dependent on their use within the computer. See section 3 for detailed logic description.

#### 2.1 Memory Address -- 15 Lines

The 15 lines EMA(012)L; MA(011)Li form a bus which defines the currently active memory address. The source of MA(011L)L is the CPU during instruction processing, and the currently active data break dovice during DMA operations. The source of EMA(012L)L is the memory extension control during instruction processing, and the currently active data break device during DMA operations. Load resistors within the CPU define EMA(012)L as zeros (highs) if there is no memory extension control in the system.

2.2 Memory Data And Direction Control -- 13 Lines

#### 2.2.1

The 12 signals MDC0:11>L from a bidirectional data path between memory and CPU. In addition, these lines are monitored by Programmed I/O devices to determine device code and sub-device operation; and by data break devices to obtain output (memory-to-DMA device) words.

### 2.2.2

The source of information on MD-0:11)L is controlled by MD DIR L. If MD DIR is low, the data of the currently active memory is gated onto MD.0:11>L. If MD DIR L is high, the contents of the CPU's memory buffer register areguted onto MD.0:11>L.

0 9 1 3 1 EN 010474-14-16 R172(327)

2.3 Data Bus -- 12 Lines

The 12 signals DATA(0:11): form a mult-purpose 12-bit bus. This bus is used for data exchange between peripheral and CPU, for data input from DNA device, for front-panel monitoring of selected registers, and for the determination of data break priority.

2.4 I/O Control Signals -- 10 Lines

This group of signals controls the I/O dialogue between CPU and Programmed peripherals. This group also includes INITIALIZE H, which is used for clearing peripheral flags.

#### 2.5 DMA Control Signals -- 8 Lines

This group of signals controls the operation of data break (DNA). Several of these signals are also activated for certain front-panel operations. Also included in this group is RUN L, which is used for clearing data break requests when the computer is halted.

#### 2.6 Timing Signals -- 9 Lines

Pive time pulses serve as system clocks. Similarly, four time state levels serve as system enabling levels. All of these signals originate within the main timing generator of the CPU.

2.7 CPU State -- 6 Lines

The major state of the CPU appears on the major st  $\pm$  lines (P L, D L, E L); the op code of the instruction currently being processed appears on IR(0:22L.

2.8 Memory Timing Signals -- 5 Lines

Five signals originate in the main timing generator of the CPU and are bussed to all memories. These signals (SOURCE H, RETURN H, WRITE H, INNIBIT H, and STROBE H) control all memory operations.

#### 2.9 Miscellaneous Signals -- 18 Lines

These signals do not fit into any of the above categories. A large percentage of them are used by the operator's console (front panel). Two signals (ROM ADDRESS L and MTS STALL) are driven by some types of memories under special conditions, and are sonitored by the CFU and siscellaneous. Included in this group is a signal (FOWER OK H) which reports the validity of the power supely voltages.

#### 2.10

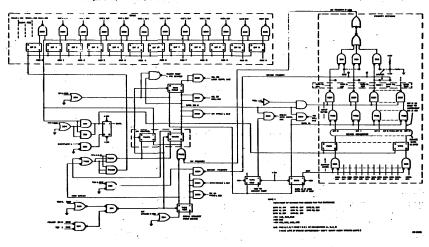

The interconnection of various system parts via the OMNIBUS is shown below:

| !!         | 11        | !!       | 11      | !! !!           |

|------------|-----------|----------|---------|-----------------|

| i ang i    |           |          | 1       | I DMA I IPANELI |

| i CPU i    | I EXT I I | i mism i | : 1/0 : | 1 * 1 1 1       |

| 1 .1       |           | : .:     | ÷ .:    |                 |

| 1 b!       |           |          | 1 b1    |                 |

| ! 0 0!     |           |          |         | 1 0 01 1 0 01   |

| li u tl    |           |          | li u t! |                 |

| in t hi    |           |          | in t hi |                 |

| [!         | 11        | 11       | 11      | !! !!           |

|            |           |          |         |                 |

|            |           |          |         |                 |

| MEM ADD x  | x         | -x       |         | xx              |

|            |           |          |         |                 |

| MEM DATx-  | x         | x        |         | -xxx            |

|            |           |          |         |                 |

| DATA BUSx  | x         |          | x       | xx-             |

|            |           |          |         |                 |

| I/O CTRLx  | x         |          | x       | xx              |

|            |           |          |         |                 |

| DMA CTRL-x | x         |          |         | xx              |

|            |           |          |         |                 |

| TIMING     | x         |          | -x      | xx              |

|            |           |          |         |                 |

| CPU ST     | x         |          |         | x               |

|            |           |          |         |                 |

| MEM TIM    |           | -x       |         |                 |

|            |           |          |         |                 |

| MISC       | x         | x        |         | x-              |

3.0 DETAILED LOGIC DESCRIPTION OF THE 96 OMNIBUS SIGNALS

This section describes the logical operation of each of the OMNIBUS signal lines. The paragraphs are arranged similarly to section 2 for easier correlation between the two sections. Unless otherwise stated; a logic H=2ero. See paragraph 4 for a description of the timing signals referenced.

3.1 Memory Address -- 15 Lines

These signals are changed starting at the leading edge of PULSE LOAD ADDRESS H or TP4 H and remain static through the entire memory cycle.

3.1.1 EMA<0:2>L L=one - Must be settled 50 ns prior to leading edge of SOURCE H and RETURN H.

signal pin

EMAOL AD2 Most significant EMALL AE2 EMA2L AH2

3.1.2 MA<0:11>L L=one - Must be settled 50 ns prior to leading edge of SOURCE H and RETURN H.

signal pin

| MAOL  | AD1 | Most | significant |

|-------|-----|------|-------------|

| MAIL  | AEL |      |             |

| MA2L  | AHI |      |             |

| MA3L  | AJ1 |      |             |

| NA4L  | BD1 |      |             |

| MA5L  | BEL |      |             |

| MAGL  | BH1 |      |             |

| MA7L  | BJ1 |      |             |

| MASL  | DD1 |      |             |

| MA9L  | DE1 |      |             |

| NA10L | DH1 |      |             |

| MAIIL | DJ1 |      |             |

\*This is just the DWA portion of what is usually a complex peripheral. Such a peripheral usually uses the Programmed I/O signals as well.

diditat

Page 10

3.2 Memory Data And Direction Control -- 13 Lines

3.2.1 MOC011126 LP1 - These lines form the data path to and from emp y. If MD DIR L will remain low for the entire memory cycle, information from memory may be placed on the MD lines as late as 150 ns prior to TP2; otherwise, the information must be present 250 ns before TP2. If MD DIR L is allowed to go high, the new MD information from the CPU's Memory Buffer register must be on the OWNIBDS 150 ns prior to the leading edge of INHIBIT H, and must remain statle for the duration of INHIBIT in for proper memory operation. It is desirable cycle to facilitate displaying the contents of memory when sincle-stepping orograms.

| MDOL<br>MD1L<br>MD2L<br>MD3L   | AK1<br>AL1<br>AM1<br>AP1 | Most | significant |

|--------------------------------|--------------------------|------|-------------|

| MD4L<br>MD5L<br>MD6L<br>MD7L   | BK1<br>BL1<br>BM1<br>BP1 |      |             |

| MD8L<br>MD9L<br>MD10L<br>MD11L | DK1<br>DL1<br>DM1<br>DP1 |      |             |

3.2.2 MD DIR L. L-Memory Driving MD Lines - B-CPU's MB register driving MD lins. MD DIR L is always low from 100 ms after the leading edge of TPJ B to the leading edge of TPJ M, when it may be bus in static, hence case should be taken to guarantee that this line does not "glitch". If MD DIR L remains low for the entire memory cycle, the information on the MD lines is valid from the time met is in the static of the state of the state of the state is to the state of the state of the state of the state of the does not "glitch". If MD DIR L remains low for the entire memory cycle, the information on the MD lines is valid from the time it is time need be allotted for comput 'g and storing information in the does propagation after TPZ. The PDP-BR, M and F make use of this cycles.

signal pin

MD DIR L AK2

#### 3.3 Data Bus -- 12 Lines L=one

The data bus is a multi-purpose 12-bit bus whose use is a function of the machine state. During TSI of every memory cycle, the data bus carries indicator information, as defined by the IND lines (see paragraph 3.91).

During TS2 of fetch cycles, the data bus carries the contents of the AC. During TS2 of DMA cycles, the data bus carries information to be placed in memory, or information to be added to the contents of memory (see paragraph 3.5.5).

During TSJ of 10T instructions, the information on the data bus is a function of the 1/0 control lines (see paragraph 3.4.5). During TSJ of OP2 instructions, the contents of the CPU's AC are placed on the data bus if the CJA bit (bit 4 of the instruction word) is zero, and the contents of the control panel's switch register are placed on the data bus if bit 3 of the instruction word is a superments data bus is reserved for determining data beak (DMA) priority. See paragraph 3.5 for more details.

A good general rule is for all logic to stay off the data bus unless the conditions are met in the preceding paragraph. The data bus must be left free for use by the CPU.

signal pin

DATADL ARI Most significant bit DATALL ASI DATALL AUI DATAJL AVI DATAJL VI DATAJL SEI DATAJL SEI DATAGL BUI DATAGL BUI DATAGL BUI DATAGL DEI DATAGL DEI DATAJL DEI DATAJL DEI DATAJL DUI

#### 3.4 I/O Control Signals -- 10 Lines

Basic 1/0 devices may perform data exchange between the AC of the CPU and the device's segisters. The state of the device is tested using skip instructions. These devices need not make connection to C2 L, BOS STROBE L, anl NOT LAST XFER L.

More complicated I/O devices may use BUS STROBE L and NOT LAST XFER L to stall the CPU, perform multiple transfers in a single IOT, and/or

modify the PC (and/or the Link).

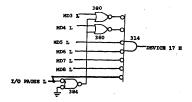

3.4.1 I/O PAUSE L -- Pin CDI - I/O PAUSE L is low if F L, MDO L and RDI L are low and USER MODE L and RDL L are high. Also included is a gating term from the timing chain. It is the command to all contents of MOG18bL if a peripheral finds equality with MOG18bL it decodes MDG3bL1 to determine the sub-device operation to be performed. The peripheral has 100 nanoseconds in which to decode its subdevice operation and essert information onto the C lines and deal L is negated. It is not an information of the subdevice operation of the subdevice operation.

I/O PAUSE L remains asserted during extended I/O cycles until the CPU has been restarted. (see paragraph 3.4.7)

Although not mandatory, it is strongly urged that the peripheral logic design incorporate load-relief logic to minimize loading  $\circ$  the Data and MD busses when I/O PAUSE is negated. Loading rules require load relief if there is more than one Programmed - I/O peripheral.

3.4.2 INTERNAL I/O L -- Pin CLI - INTERNAL I/O L alerts the KA8E Positive I/O Bus Adapter that an I/O device on the OMNIBUS has recognized the 107 being processed. If the KA8E finds this line not grounded, it processes the IOT by stopping the CPU and entering an expanded I/O evcle.

All internal (OMNIBUS) I/O devices ground this line if they find equality between MD<3:8>L and their device code when I/O PAUSE L is low.

3.4.3 SKIP L — Pin CS1 – SKIP L is sampled by the CPU at TP2 to determine if an I/O skip should occur. The skip occurs if SKIP L is low. Caution: This line may be sampled every TP3 (not just during IOT instructions), depending on the CPU.

3.4.4 INT ROST L -- Pin CPL - INT ROST L is sampled by the CPU at the leading edge of INT STROOM H if all other interrupt conditions are met to determine if an interrupt request is pending. This line is grounded by a peripheral device when a condition which causes an interrupt is encountered. Since the CPU contains a synchronizing filp-flop, this line may be grounded at any time. In addition, if this line is grounded 100 ns or more before TP3, the SRQ instruction will skip.

3.4.5 C<0:2)L -- Pins CEl (C0 L) - CHl (C1 L); CJl (C2 L) C<0:2>L control the type of transfer during an IOT as shown below:

C<0:2>L transfer 0 1 2

- H x H AC->DATA<0:11>L->AC (peripheral may "or" information onto DATA<0:11>L)

- L H H AC->DATA<0:11>L; 0->AC

- L L H DATA<0:11>L->AC

- x H L DATA<0:11>L+PC->PC

- x L L DATA<0:11>L=>PC

In general, peripherals use only SKIP L to modify the pc, and so do not make connection to C2 L. See paragraph 4.4 for the impact on timing.

Historically, the HHH combination was reserved for output transfer, and the HLH combination for input or transfer. Many designs violated this convention; hence the HXH definition above.

3.4.6 BUS STROBE L -- Pin CK1 - BUS STROBE L is a negative - going pulse which causes the AC or PC to be loaded during an IOT. BUS STROBE L is also used in conjunction with NOT LAST XFER L during long 1/O cycles (see parataph 3.4.7).

During an IOT, gating within the CPU generates a single BUS STROBE L pulse at TP3 time if MOT LAST XFER L is high (i.e., if the IOT is not an extended IOT). If an extended I/O cycle is in process (i.e., if MOT LAST XFER L is low at TP3 H), the peripheral must generate all BUS STROBE L pulses. The AC or PC (depending on C2 L) is loaded at the leading (falling) edge of BUS STROBE L.

3.4.7 NOT LAST XFER L -- Pin CLI - MOST peripheral controllers require only one transfer per IOF; hence the single transfer at TP3 time is adeguate. Such peripherals do not ground NOT LAST XFER L and do not drive SUS STROBEL 0. Other, more complex peripherals (the KABE Positive I/O Adapter, for example) require extended timing and use NOT LAST XFER L to "stall" the CPU in an I/O exple.

To stop the CPU in TS3 of an I/O cycle, ground NOT LAST XPER L prior to TP3 H of the IOT.

The CPU will remain in time state 3, and will not generate INT STROBE

H or BUS STROBE L. Timing is now controlled by the peripheral.

The peripheral may make any number of transfers by controlling C<0:2>L, generating BUS STROBE L and keeping NOT LAST XFER L at ground.

The CPU is restarted by allowing NOT LAST XPER L to go high before the leading (falir). edge of BUS STORE L. In addition to making a final data transfer, the CPU restarts by generating INT STROBE H, entering T54 and by negating 1/O PAUSE L.

Caution: extended I/O cycles increase DMA latency times.

3.4.8 INITIALIZE H -- Pin CRl - INITIALIZE H is asserted (high) by:

- the operator's console (control panel) clear key being operated

- the CAF instruction (octal 6007)

- the negation of POWER OK H.

INITIALIZE 8 statically clears the AC, Link, interrupt system and peripheral flags. It also sets the interrupt enable filp-flops of peripherals which must remain program - compatible with older versions which did not have an interrupt enable filp-flop. (Two important devices in this category are the TTY and paper tape reader/punch interrupt enables.)

#### 3.5 DMA Control Signals -- 8 Lines

Data breaks (DMA) allow a peripheral to communicate directly with memory, bypassing the CVU. The only CPU register available to the DMA by the communication of the communication of the communication of the breaks may occur between any CPU cycles, but a data break cannot be performed while the CPU is in the midst of an extended I/O or EAE cycle because the currently active memory is then supplying informed in to the bus. Data breaks take place in the following informed.

- At INT STROBE H leading edge, the decision to request a data break is made at the peripheral by strobing its break request flip-flop.

- A device starting a data break unconditionally grounds CPMA DISABLE L and BREAK IN PROG L until its break request flip-flop is cleared.

GILO IL DRA 1184

- 3. Data break priority is determined on DATA(0:11)L when TS4 L is asserted. Each data break device is assigned a unique line on DATA(0:11)L, with DATA(0:L being the highest-priority DATA(0:11)L, and examines the state of all higher-priority lines to determine if they are all high. For example, a device grounding DATA(0:15)L examines DATA(0:4)L to make sure these lines are all high. Higher-priority devices remain in etc.)

- 4. The device winning the priority test sets its MA Control flip-flops at the leading edge of TP4 H. (The path from TP4 H to the memory address lines must have as little delay as possible; hence two flip-flops are recommended to provide adequate drive without introducing the delay of a buffer. See paragraph 5.7.1 The MA Control flip-flops gate the break plishes to the set of the set of the set of the break DISABLE L and (if this cycle is a data exchange cycle) BK CYCLE L.

- 5. At TPl H, the active device grounds MA, MS LOAD CONT L.

- 5. For input to memory, the active device merely places is data on DATA(011)L during TS2. For output from memory, the device grounds BREAK DATA CONT L during TS2 L, and loads its register with the contents of MitO(11)L at the leading edge places the data to be added on DATA(011)L during TS2, and grounds BREAK DATA CONT L during TS2. The modified information is loaded into the CRU's MB and overflow flip-flop at TP2 H, and may be read by the device at TP3 H or TP4 H. Tria is generally used, since OVERPLOW L is valid read at the leading edge of TP2 H.

- ?. At the completion of a data break, all lines are released in the same order and at the same times in which they were asserted.

- Three-cycle data breaks are merely three one-cycle data breaks with a special control to handle word count and current address cycles. BREAK CYCLE L is not grounded during these two cycles; it is grounded only for the final, data exchange cycle.

DMA latency is the longest machine cycle, plus the time of TS4.

3.5.1 BRK IN PROG L -- Pin BE2 - This signal provides indicator information to the console. It is grounded at INF STROBE Heading edge, if a break is to take place; and causes the console "BRK IN PROG" light to turn on.

3.5.2 CPMA DISABLE L -- Pin CUI - CPMA DISABLE L is asserted (grounded) by break devices if data breaks are to occur. It is sampled by the CPU and memory extension control at the leading edge of TP4 8. If CPMA DISABLE L is low at that time, the memory extension control's field bits and the CPU's memory address bits are removed from EMA(0.5)L and Med/11)L. If CPMA DISABLE Lis megated (high) at CPU's memory address register are gated to EMA(0:2)L and MA(0:11)L respectively.

3,5,3 MS, IR DISABLE L -- Pin CV1 when MS, IR DISABLE L is high, the vajor state and IR flip-flops drive the major state and IR flip-flops drive the major state and IR flip-flops drive the major state and IR bins are not driven by the CPU. Unless some external device asserts a major state, the CPU is then in the DMA state.

3.5.4 MA, MS LOAD COWT L -- Pin BHZ -- MA, MS LOAD COWT L is negated (nigh), the CPU and memory antension control function normally. Asserting this line inhibits the loading of new information into the CPU's major state and and memory address registers; and into certain control flip-flops of the memory extension control. This signal must not change while TP4 H is high, it is normally changed at TP1 time.

3.5.5 BREAK DATA COWT L -- Pin BK 2 - This signal is ignored unless BK, IR DISABLE L: us grounded (PDP-BK) or unless F L, D L, and E L are all high (PDP-BA). BREAK DATA COWT L should be stable as early in TS2 as possible, and defines the information loaded into the MB at TP2 H. 17 BREAK DATA COWT L is high during TS2 of a DMA, DATAGOILLL Indeed into MBG(01L). If BREAK DATA COWTL L is blowder into the MB at TP2 H. DATA COWT L is high during TS2 of a DMA, DATAGOILLL DATAGOT L low and placing no information (seros) on DATAGOILLL causes a DMA which does not modify memory.

CI GI L 2 CN -01047A-1A-16 R177(327)

3.5.6 OVERFLOW L -- Pin BJ2 - This line is asserted (low) during TS3 if a carry occurs at TP2. Hence this line is asserted if any of the following occur:

> auto index or JMS wrap-around ISZ overflow data break overflow or carry

3.5.7 BK CYCLE L -- Pin BL2 - Panel information from the data break device. Low indicates a break data transfer cycle is in process.

3.5.8 RUN L -- Pin 502 - This signal is really a CPU state, since it indicates the CPU's timing generator is running (when low). It is included in this group of signals because its most important function is as a gating term used to clear ail break requests when negated (high).

#### 3.6 Timing Signals -- 9 Lines

Five pulses and four levels originate in the timing generator of the CFU and are used as system clocks and enabling levels respectively. Time pulses are nominally 100 ns wide (INT STROPE H is more loosely defined-use paragraph 4.1). Time states change nominally 50 ns after machine is at the beginning of TS1. Applying a single MEK START L course the timing chain to start and continue to run until.

- 1. The STOP L line on the OMNIBUS is asserted at TP3, or

- 2. The CPU encounters a HLT instruction at TP3, or

- POWER OK H is negated at TP3

and the current memory cycle has completed. A time state precedes the time pulse of the same number; INT STROBE H is coincident with TP3 H except when in an extended IOT or EAE operation; TS1 L is automatically entered at the end of TS4.

| signal | pin |

|--------|-----|

| TS1 L  | CK2 |

| TS2 L  | CL2 |

| TS3 L  | CM2 |

| TS4 L  | CP2 |

| TP1 H  | CD2 |

| TP2 H  | CE2 |

| TP3 H  | CH2 |

TP4 H CJ2 INT STROBE H BD2

3.7 CPU STATE -- 6 Lines

3.7.1 Major State Lines - The CPU major state appears on these lines unless MS, IR DISABLE Line same state as seen by the CPU's instruction decoder is taken from these lines (except for the enabling of BRAK DATA CONT. Louring DWA in the instructions to the CPU. Normally the major state lines charge at TP4.

| major      | state | pin               |

|------------|-------|-------------------|

| F L<br>D L |       | DJ2<br>DK2<br>DL2 |

| D L<br>E L |       |                   |

3.7.2 IRO:225 Bellect The State Of The CPU's - instruction register provided MS, IR DISABLE is high. A low on IRO:221 represents a one in the corresponding bit of the instruction register. As in the case of the sajor state lines, the IR lines are disconnected from the by the CPU during D and E major states is obtained from these lines. (During instruction fectoding is done directly from the MD lines. See individual CPU spects for this information.) As with the major state lines, it is possible to force instructions during the for the set of the sajor state lines, it is not force instructions during the force the could be colleged at T2 of an interrupt is being homored (IRT IN PROF B is high).

| signal     |   | pin        |

|------------|---|------------|

| IRU<br>IR1 |   | DD2<br>DE2 |

| IR2        | L | DH2        |

00001101 EN-01047A-1A-16-8177(327)

3.8 Memory Timing Signals -- 5 Lines

These signals are defined in terms of the PDP-8E's original core memory, the MM8E. See paragraph 4.1 for waveforms.

3.8.1 SOURCE H -- Fin AL2, And RETURN H -- Pin AR2 - These signals become asserted (high) at the same time, and direct the core memory to turn on its read/write currents. RETURN H becomes negated 50 ns later than SOURCE H, thereby defining the voltage to which the memory stack is charged.

3.8.2 WRITE H -- Pin AS2 - WRITE H controls the direction of current flow in the memory stack. It is high during write and low during read. If WRITE H is low, the positive-going transition of SOURCE H is usually used to clear all memory data registers.

3.8.3 INHIBIT H -- Pin AP2 - INHIBIT H is a gating level to the inhibit drivers of core memory. When high, it causes the selected memory inhibit drivers to turn on.

3.8.4 STROBE H -- Pin AW2 - The leading edge of STROBE H provides a time reference from which the stobe in each individual core memory is derived. Each memory delays this edge by an optimum amount for that memory, and then strobes its sense amplifiers. The selected memory must have its data on MDC0:11)L at or before strobe leading edge plus 150 nanoseconds (this time does not include bus charging time).

#### 3.9 Miscellaneous Signals -- 18 Lines

3.9.1 INDI L -- Pin CO2, And IND2 L -- Pin CO2 - These signals control the information gated to DATA(011)L during TSI. Since DATA(011)L is defined as low for a 1, ones in register bits place lows on DATA(011)L.

IND1 L IND2 L info on DATA<0:11>L

| н | в | status word*      |

|---|---|-------------------|

| H | L | MQ<0:11>          |

| L | н | all zeros (highs) |

| L | L | AC<0:11>          |

|   |   |                   |

\*status word:

bit information

| DEC | STD | 157 |

|-----|-----|-----|

|     |     |     |

Link GT Flip-Flop (PDF-8E EAE only) 2 INT ROST L (low on DATA2 L if INT ROST L [Pin CP1] is low) Int Inh Flip-Flop\*\* (PDP-8E only) ۵ Interrupt Delay Flip-Flop (denotes interrupt on) USER MODE L\*\* 6-8 TF<0:2>\*\* DF<0+2>\*\* 9-11 \*\*from memory extension control if present. Otherwise these remain high (zeros). Gating circuitry in any logic driving IND1 L and IND2 L should ground IND1 L and allow IND2 L to go high if LA ENABLE L is asserted (low). See paragraph 3.9.9. 3.9.2 MEM START L -- Pin AJ2 - Grounding MEM START L causes the timing chain of the CPU to start. MEM START L may be a 100 ns negative -- going pulse or it may be a level which is ground if TS1 L is asserted and the logical decision to start the machine has been made. MEM START L must not be at ground beyond TP2 H, since it may then interfere with possible HLT instructions. A single MEM START L pulse causes the CPU to start and continue to run until halted by the program or by the STOP L line (see paragraph 3.9.31. 3.9.3 STOP L -- Pin DS2 - STOP L is sampled by the CPU at the leading edge of TP3 H of every machine cycle. If STOP L is asserted (low), the CPU completes its current memory cycle and stops in TS1 (just after TP4 H goes to ground). At that point in its cycle, the CPU can display: new memory address (on EMA<0:2>L and MA<0:11>L new major state (on F L, D L, and E L) memory data of last-referenced location (on MD<0:11>L) status or AC or MQ (on DATA<0:11>L, depending on IND1 L and IND2 L) any other lines on the OMNIBUS for which display

provision has been made

digilal En-01047A-TA 16 B177(327)

STOP L is asserted by control panel keys (halt and single step), and is also asserted when: process examine operation is in process a HLT instruction process a HLT instruction rectal 7402; POWER OK H is low REY CONTROL L is low (PDP-8E) prel examine or panel deposit condition (FDP-8A) (see 1.9.9)

3.9.4 LINK L -- Pin AV2 - Link L is low if the Link bit of the CPU is a one, and high if the link is a zero.

3.9.5 LINK LOAD L -- Pin CS2, And LINN DATA L - Pin CR2 - These two signals allow loading of the Link From the OMNIBUS. Loading occurs on the leading (falling) edge of LINK LOAD L, and the data loaded into the Link is a one if LINK DATA L is low. PDP-BC: these two signals these two signals should be used only in extended I/O cycles while NOT LAST YRFER L is low.

3.9.6 FSET L -- Pin DP2 - This line is asserted (low) if the major state gating of the CPU indicates the next major state will be a fetch. The conditions causing this line to be asserted are:

- A major state of execute, no interrupt being honored (see paragraph 3.9.8) and a final execute cycle if the machine is a PDP-8E with EAE and doing a multi-state EAE operation.

- 2. A major state of defer and an IR of 5 (JMP instruction).

- A major state of fetch, a JMP instruction and MD3 L high (direct jump)

- 4. A major state of fetch and an IOT instruction

- A major state of fetch and an operate instruction (unless the machine is a PDP-8E with EAE and the instruction is MUY, DVI, ASR, SEL, SEL, DAD, OR DST)

- 6. DMA (F L, D L and E L all high)

dicital

3.9.7 USER MODE L -- Pin DM2 - This line is normally driven by the timeshare portion of the memory extension control, and is tied high by a load resistor in the CPU if no memory extension control is in the system. USER MODE L is changed only at TP4 time.

If USER MODE L is high, the CPU and control panel function normally. If USER MODE L is asserted (low), the following operations are inhibited:

- 1. The halt instruction (inhibited in the CPU)

- 2. The OSR and LAS instructions (inhibited in the panel logic)

- I/O PAUSE L remains high even though an. IOT instruction is fetched from memory (inhibited in the CPU)

Interruption of the program upon detection of any of these conditions is handled by the memory extension control.

3.9.8 INT IN PROG H -- Pin BP2 - INT IN PROG H is allowed to go high if:

- The interrupt system has been turned on by an ION or RTF instruction ar3 at least one subsequent instruction fetch has occurred, and

- An interrupt request has been recognized by the Int Sync flip-flop of the CPU (which sets at the leading edge of INT STROBE H if INT ROST L and PSET L are both low), and

- There is no interrupt inhibiting condition. This condition is preserved in the Int Inhibit flip-flop in the memory extension control, and is generated if a CIP, CUP, SWP or RTF instruction has been processed and a JWP or JMS has not yet occurred to complete the field change.

INT IN PROG H is used by the CPU to load 0 into the CPU's NA, force the major state to Execute and IR to JAKS, and to turn off the interrupt system. INT IN PROG H is also used by the memory extension control to load the save field, and to else the Hs.IF and DP. INT IN PROC H goes high at INT STRONG H time, that in PROC H, THY STRONG H that not DRA for DPD-SA, INT IN PROG H, TPI H and not DRA for PDP-SA.

digital (N-01047A 1A-16 R1771327)

3.9.9 LA EMABLE L -- Pin BM2, And KEY CONTROL - L -- Pin DU2 These lines must not be asserted (grounded) unless the CPU is in the DMA state. (MS IR DISABLE L at ground and F L, D L, and E Lall high). If LA EMABLE L is low, any logic driving IND1 L and IMD2 L must ground IND1 L and turn off any drivers driving IND2 L.

PDP-BS: LA ENABLE L, when asserted, establishes a data path from DATA(0:11)L to the CPU's MA. This data path is a straight transfer, and is used for loading the contents of the control panel's switch register into the CPU's MA upon a load address command at the control panel.

PDP-88: KEY CONTOL L, when asserted, grounds STOP L and INT IN PROG H; sets up gating in the CPU to cause MA+L->PC at TPI H and PC->HA at TP4 H; and establishes a data path in the memory extension which loads the field bits from DATA<6:1L>L if a PULSE LA H is asserted.

PDP-8A: The function of LA ENABLE L, KEY CONTROL L and BREAK DATA CONT L are defined as follows:

| LA EN       | KC | BDC | Function         |

|-------------|----|-----|------------------|

| L           | L  | L   | XLA 7            |

| L           | L  | н   | XLA 0            |

| L<br>L<br>L | н  | L   | Non-stop deposit |

| L           | н  | н   | Load address     |

| в           | L  | L   | Panel examine    |

| н           | L  | н   | Panel deposit    |

| н           | н  | L   | Add to memory*   |

| н           | н  | н   | Break deposit*   |

\*See Paragraph 3.5.5

Panel examine grounds STOP L, performs one memory cycle at the address in the CPU's MA register; does a break add to memory, and increments the MA.

Panel deposit grounds STOP L, performs one memory cycle at the address in the CPU's MA register; does a break deposit with the SR of the panel providing input data, and increments the MA.

Load address -- there are two possible functions. If PUGSE LA H is asserted, the PM is loaded from DATAGOILD. If MEM STAFTL is asserted, the CPU starts performing an examine at whatever location is in the CPU's MA. At TP3 H, the contents of DATAGOILD. Are loaded into the PC and transferred to the CPU's MA at TP4 H. The CPU is not stopped. (STOP L is not grounded.)

Non-stop deposit -- same as panel deposit except STOP L is not grounded, so the CPU continues to run. Useful for loading bootstrap programs into memory.

XLAO--there are two modes of operation. If PULSE LA B is asserted,

memory extension control is loaded with whatever is on the DATA<6:11>L. If MEM START L is asserted, the CPU starts and does an examine at whatever location is in the CPU's MA. The memory extension control is loaded at TP3 H, but 0 is on DATA<6:11>L so the memory extension control's IF, IB and DF registers are cleared. STOP L is not grounded, so the CPU continues to run.

XLA7--like XLA0 with MEM START L, except that the CPU places 7777 on DATA<0:11>L, loading 7 into the IB, IF, and DF. Note: The AC must be 0 for this function to work properly.

3.9.10 PULSE LA H -- Pin DR2 - PULSE LA H causes the CPU's MA register to be loaded if KEY CONTROL L is high; or the memory extension control's IB, IF, and DF registers to be loaded if KEY CONTROL L is low. PULSE LA H is a nominal 100 nsec. positive-going pulse.

3.9.11 ROM ADDRESS L -- Pin AU2 - ROM ADDRESS L is examined by core and other read-write memories. If ROM ADDRESS L is high, the read-write memory functions normally. If ROM ADDRESS L is low, the read-write memory is disabled. ROM ADDRESS L is grounded by small ROMs which overlay read-write memories, thus providing a small number of read-only locations in a large read-write memory. Note: the gating must be fast.

There is only 25 ns from the time the address lines have been established to the time this signal must be asserted.

ROM ADDRESS L also modifies the JMS instruction by inhibiting the incrementing of the new PC contents. This action causes the JMS instruction to act like a JMP instruction (except for timing) if a JMS to ROM is attempted.

3.9.12 NTS STALL L -- Pin BR2 - On PDP-8E, this line should not be used for any purpose.

On PDP-8A, NTS STALL L (next time state stall 1) provides a means of stalling machine operation to accomodate memories slower than the one for which the timing chain was designed.

When NTS STALL L is high, the timing chain of the CPU functions normally. If NTS STALL L is asserted (low), the timing chain functions normally to the middle of the next time pulse. The time state changes and the time pulse completes in the normal 106 nsec, but the timing chain stalls at the beginning of the new time state. The stalling of the time state continues until NTS STALL L goes high, restarting the timing chain. Note that NTS STALL L has no effect on the duration of the five memory timing signals. It merely stretches the time before read, the time between read and write, and the time

after write before new address. NTS STALL L must be low 100 ns before the leading edge of a time pulse to guatantee stalling in the next time state. The timing generator will not stall in the next time state if NTS STALL L is high for the 100 ns prior to the leading edge of the time pulse.

| NTS<br>STALL<br>low<br>at: | TS<br>becomes<br>longer | And there is                                                                                                             |

|----------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------|

| TPl H                      | т52                     | Longer time from end<br>of read to TP2,<br>allowing the CPU<br>to accommodate<br>memories with long<br>read access time. |

| TP2 H                      | 783                     | Longer time from when<br>MB is loaded to the<br>start of write                                                           |

| тРЗ Н                      | TS4                     | Longer time from start<br>of write to time address<br>is changed, accomodating<br>memories with long<br>write times.     |

| TP4 H                      | TS2                     | Longer time from address<br>change to start of read                                                                      |

NOTE: watch break latency!!

3.9.13 SW -- Pin DV2 - This line reflects the state of the "SW" switch on the PDP-8E or PDP-8M panel, or the state of the "bootstrag" flip-flop controlled by the button on the PDP-8A panel. The signal is high if the switch is up on the PDP-8E, M or P; but low if the switch is up on the PDP-8A Limited Function Panel.

On machines equipped with bootstrap options, the low-to-high transition of this line initiates bootstrap operation if the CPG is halted. If there is no bootstrap option in the machine, this line is available for any use the user any devise. This line has wwitch bounce, so logic which requires a clean transition should ore-condition this signal.

digital

3.9.14 POWER OK H -- PIN BV2 - POWER OK H originates in the power supply, and reports the state of the dc voltages to the CPU, memory extension control and core memories. The dc supplies are in regulation if this signal is high (see paragraph 6.4).

Caution: as the dc supplies fall toward ground, POWER OK H will be negated but may go somewhat ositive again as the 45 v. supply nears ground. ROWER OK H must remain at less than 0.4 volts until all supply voltages are less than 30% of their nominal. Otherwise, modification of core memory contents may occur.

POWER OK H being low grounds STOP L. POWER OK H going low is also applied to an integrator in the CPU, the output of which generates INTIALIZE H and is used as a master clear for the timing chain. Similar integrators in each of the core memories enable and disable the memory current supplies.

Negating POWER OK H does the following:

- STOP L is asserted immediately.

- 2. At the next TP3 H, RUN L is negated by the CPU.

- 3. At the following TS1, all break devices clear their break requests, and the memory extension control initializes its EMA Enable filp-flop. The gating to accomplish this is usually the "and" of POWER OK H being low, TS1 L being low, and RUN L being high.

- 4. After a delay (15-500 microsec) long enough to allow the longest possible memory cycle to complete, the timing chain is preset to the beginning of TS1 with TP4 low. All memory timing signals are made low. The CPU's control flip-flop being the signal state of the signal state of the signal state of the signal state signal state. INITIALIZE is a generated, clearing the KC, Link and interrupt system.

- After a similar delay, each core memory disables its current sources so that memory cannot be altered if memory timing signals should become asserted as the dc voltages go away.

Upon application of power:

- The CPU, extension control and peripherals are all initialized.

- Hemory current sources are enabled 1 to 70 milliseconds after POWER OK H is asserted. This enabling is accomplished by an integrating capacitor, so that "spikes" on POWER OK H are filtered out.

- The internal clear signal and the OMNIBUS INITIALIZE H signal are negated 200 to 1000 millisec after POWER OK H is asserted.

All portions of the computer should be ready to run 0.1 sec after POWER OK H is asserted.

PDP-SE: MEM START L must not be asserted until INITIALIZE H is negated.

PDP-8A: MEM START L will not be recognized until after INITIALIZE H is negated.

3.9.15 RES -- Pin BS2 - RES is an unused line. Digital Equipment Corporation reserves the right to define this line at a later date, and disclaims any responsibility to make this definition agree with any prior illicit useage.

#### 4.0 TIMING

Many signals on the OMMIBUS are wire-ored. For these signals, the high level is determined by a load resistor, and the low level is determined by one or more open-collector gates which ground the signal. Bus capacitance is moderately high; hence fall times in such situations are fast and rise times are slow (about 100 nanoseconds). This 100 nanoseconds is or the following timing diagrams by adding the 100 nanoseconds to the set-up times where necessary, requires (C102) to be defined from 450 nanoseconds before the leading edge of BUS STROBE L; 100 nanoseconds of this time is allotted to charging C4025L.

#### 4.1 Time Pulses And Time States

The time pulses (TP1 H, TP2 H, TP3 H, INT STROBE H and TP4 H) plus their associated time states (TS1 L, TS1 L, TS3 L and TS4 L) serve as the timing reference from which all other timing is derived. Timing pulses and time states are derived from a master crystal Clock (20 mbz) in the timing generator of the CP0. This clock has a stability of 0.11; hence the time between positive edges of time pulses accurate to 0.18. Time pulses widths are shold wrime(). states change nominally at 50 nsc cafter the leading edge of the time pulses, but logic delays and loading introduce an uncertainty in this time. See closer

digital

i<--a-->i<--b-->i<--c-->i<--d-->i . 1 1 1 1 TP4H---! !---------TP1H------! |------TP2H-----! !---------TP3H, INT STROBE H-----! !-----! TS]L----! !----------! \_\_\_\_\_ ------TS2L |----! ----------TS3L |----1 \_\_\_\_\_ TS4L 1-----1 time in nanoseconds: time PDP-8E PDP-8E PDP-8A interval fast slow all cvcle **c**<sub>i</sub>cle cycles 300 300 350 nsec a 250 450 400 b с 350 350 400 à 300 300 350 total 1200 1400 1500

The PDP-8E fast cycle-alow cycle choice is determined by major state and the contents of  $M_{c}(011)L$ . Past cycle is taken if the major state is fetch (FL is low), or if the major state is defer (DL is low) and he MA lines are not 10-17 (one or more of  $M_{c}(07)TL$  is low or MA 8 Lis high). Otherwise, slow cycle is taken. A jumper on the 8E timing board (M8300) forces all slow cycles when in place.

Detail of time pulse and timestate change:

(this applies to TPl H, TP2 H and TP 4 H.)

1<--90 to 110 ns-->1 10 ns min-->!!<--1 time state ! . Old Uncertain New Details of TP3 H timing if NOT LAST XFER L is high and if I/O PAUSE L is high. (See paragraph 4.5 for other condition.) !<--90 to 110 ns-->! ------1-----TP 3H-----! . !<--->! 10 ns min--->11<---1

time pulse-----! !-----

## 4.2 Memory Timing

Normal memory timing is based on the PDP-8E's core memory, and is shown below:

write read ---------------INBIBIT H-----! !--150 ns->! !<---->1 1<--90 to 150 ns STROBE H-----1 !---------------- i i i 1 WRITE H --------------

> Unless otherwise noted, all times above are + or - 10 nsec.

DEC JTD 157

read TP4 H-----! 1------1<-a->1 ROM ADDRESS L, ! ! USER MODE L <u>0</u>14 ? Settled (incl bus charge time) -->11<--25 nsec min SOURCE H-----! 1----->1 1<--100 ns min EMA<0:2>L, 1.1 MA<0:11>L Old ? Settled (incl bus charge) STROBE H------->1 I<--120 ns max MD<0:11>L 1 1 1 -------New 01d 0 ? ı Clear all memories ->! 1 at leading edge of SOURCE H New memory data on bus----->! 1 New memory data settled----->1 write EMA, MA, ROM ADDRESS L ----stable from previous read

4.3 Relationship Between CPU And Memory Timing

## digital

MD<0:11>L changes at TP2 H only if MD DIR L is allowed to go high. If MD DIR L remains low, MD<0:11>L is settled on bus at STROBE H leading edge + 250 ns.

time in nanoseconds

a b PDP-8E 150 250 PDP-8A 200 300

#### NOTE

The times given for PDP-88 and PDP-8A take into consideration the type of load on MD(0:115), EMA(0:2)L and MA(0:11)L and its position, plus maximum bus capacitance. A special bus-charging circuit in PDP-8E allows a charging time of less than the usual 100 nanoseconds.

4.4 Basic I/O Timing

4.4.1 This Timing Assumes: -

- Single transfer during IOT

- No modification of PC (no connection to C2 L).

- C<0:1>L do not go to ground and then positive between the falling edge of I/O PAUSE L and the rising edge of TP3 H.

----STROBE H--! !-----MD<0:11>L-----!-----! 2 IOT T/O PAUSE I. !<---->!b!<--TP2 H------TP3 H-----! !----Indicator ? AC ? Depends on ? Bk info C<0:1>1 Prior Dimension a PDP-8E 350 to 450 nsec PDP-8A: 450 to 550 nsec Dimension b 50 nsec min, 100 ns max

Peripheral must place its data on DATA(0:11)L and assert any C lines at least 250 nsec prior to TP3H. Skip L must be asserted at least 100 nsec before TP3H if a skip is to occur. Peripheral registers are loaded at the leading edge of TP3H. Peripheral registers must be edge-triggered, since DATA(0:11)L may start to change before TP3H ocea low acain.

diqita

4.4.2 CAF Timing: -----TP 3 H---! !------>!!<---20 ns min -----INITIALIZE H ----! !-----1<-300 to 900 ns->! (never extends to next TP3 H) 4.5 Expanded I/O Timing The restrictions of 4.4 regarding single transfer and limited use of C<0:2>L do not apply. 4.5.1 To stop the CPU (this operation is not confined to IOTs) TP3 H------ 1 !------->! !<--100 ns min</pre> ->11<--20 ns min ----NOT LAST XFER L !----!---4.5.2 To make transfers to or from the AC, or to the PC: -----!-----!----DATA<0:11>L ? periph data\* ->1 350 ns mi 350 ns min 1<-C<0:1>L. ---!-----!----C2 L (8A only) 2 Defined 2 1<---- 450 ns min--->11<20 ns Min C2 L (8E only) ---!-----!-\_\_\_\_\_ --peripheral-generated BUS STROBE L I---! 90-150 ns--->! !<--

Peripheral data registers should be edge-triggered, and loaded at the leading edge of BUS STROBE I. (since the contents of the Data bus may change as a result of sending BUB STROBE L to the CPU).

4.5.3 External Loading Of Link - PDP-8A restriction: Must take place only in an expanded I/O cycle, and than not at restart time.

| DIGK | VA 1A | 5 | ? info on bus ?<br>->! 150 ns min !< |

|------|-------|---|--------------------------------------|

|      |       |   | 20 ns min>!!<                        |

| LINK | LOAD  | L | 90 ns min>! !<                       |

|      |       |   | 20 to 150 ns>! I<                    |

| LINK | L     |   | old new                              |

4.5.4 To Restart CPU: - Loading of Link not allowed because of timing restrictions as the CPU leaves TS3. (PDP-8A only)

NOT LAST XFER L ----! ? hiqh !<-200 ns min->! (incl bus charge time) BUS STROBE L \* 1---1 90 to 150 nsec--->1 1<--20 to 100 ns====>!!<= INT STROBE H ------1-----90 to 200 nsec---->1 1<--0 to 50 ns---->!!<--------I/O PAUSE L (if IOT) ----- [ 1 20 to 100 ns---->1 1<-------

digital

Time state of CPU------TS3 TS4 NOTE \* This BUS STROBE L is generated by the controlling peripheral, and causes a data transfer. The set-up time requirements for C<0:2>L and DATA<0:11>L must be met. 4.6 Data Break Timing 4.6.1 Initial Operations -----INT STROBE H----! !----->!!<--20 nsec min ------BRK IN PROG L, !----!---! CPMA DIS L ->! !<--50 nsec min ----------Priority on data bus :-----! -1 !<--150 ns min \_\_\_\_ old ma break EMA and MA 50 ns max---->! !<- on bus MS, IR DISABLE 1\* |-----20 ns min---->!!<--100 ns min-->! !<-1-----MA, MS LOAD CONT L н 7 Must be low 20 nsec before next TP4 H leading edqe

0 9 1 1 3 EN-01047A-1A 16 R177(327) DRA 118A 4.6.2 Data Exchange - Data to be placed in memory or used to modify memory must be in a register which has been loaded prior to TP1 H. ---тр2 н ----- ! !-----250 ns min->1 1<--break device-->! data settled on bus OVERFLOW L I a serve a ----BREAK DATA CONT L must be settled on bus at same time as input data. 4.6.3 Final Operations -INT STROBE H---! !-----TP4 H-----! |------TP1 H-----! -----BRK IN PROG L, ---!-----! CPMA DIS L ->!!<-20 ns min>!\*!<-20 ns min->11<-MS, IR DISABLE L-----i 100 ns min\*-->1 1<-------20 ns min->11<- Must be high 20 nsec prior to

TP4 H

\*Including bus charge time

digital

4.7 CPU States, INT IN PROG H 4.7.1 Major States -TP4 H-----! |------>1 !<--20 to 150 nsec</pre> -----F L, D L, E L-----!----old new ->1 1<---40 to 200 nsec ------FSET L ----olà new (or not /alid if fetch) 4.7.2 IR--Fetch Cycle -TP2 H------ ! !------>! !<--20 to 150 nsec ------, IR<0:2>L ------->! 1<--40 to 200 ns ------FSET ----not valid new 4.7.3 Interrupt Recognition -----INT STROBE H ----! !----->1 1<--50 ns min to be recognized INT ROST L -- L----...... INT IN PROG H ----!-----! 1.\* ->!!<---20 to 150 nsec -->1 1<---40 to 200 ns 1-----FSET L -----! EN-01047A-1A-16-R177(327)

Page 39

40 to 200 ns-->1 1<--

TP4 H \_\_\_\_\_\_\_\_ 20 to 150 nsec>! 1<---\_\_\_\_\_\_ Maj states, IR \_\_\_\_\_\_\_ previous state \_\_\_\_\_\_ JMS and E \*Goes low at JNS\*E\*TP1 (PDP-8E) or

\_\_\_\_\_

"Goes low at JMS"E"TPI (PDP"8E) 0

JMS\*E\*INT STROBE (PDP-8A)

4.8 Timing Start And Stop

4.8.1 Start -

4.8.2 Stop -

4.9 Asynchronous Signals

The following signals are allowed to change asynchronously with respect to the CPU's timing chain:

POWER OK H (when negated also causes INITIALIZE H to change)

SW IND1 L IND2 L INT RQST L STOP L

4.10 Special Signals

The following signals should be asserted only when the CPU is not running:

MT4 START L (see 4.8.1) PULSE LA H (90 ns min width positive pulse)

# 5.0 ELECTRICAL CHARACTERISTICS AND INTERPACING

5.1 Logic Levels

Low = -0.5 volts to +0.4 volts High = +2.7 volts to +4.5 volts.

#### 5.2 Bus Loads

The characteristics and placement of bus terminating resistors has great influence on rise-time and reflection on the OWNIBUS. Refer to individual CPU specifications for the value and placement of these loads and their impact on bus length.

#### 5.3 Driving The OMNIBUS

Drivers not on the CPU are open-collector, and should sink 25 microamperes or less at +5 volts (unless the number of drivers per line is limited to  $10^{--1}$ eakage may then be increased to 250 microamperes.)

Signal Driver must sick (ma) # 0.4 v. BREAK CYCLE L 16 BREAK DATA CONT L 16 BRK IN PROG L 16 BUS STROBE L 60 (that's right, sixty) C0 L 16 CI L 16 C2 L 16 CPMA DISABLE L 16 DL 30 \* DATA<0:11>L 16 each line 30\* E L EMA<0:2>L 30 each line FL 30\* FSET L Do not drive -- may be TTL output IND1 L 16 IND2 L 16 INSIBIT B Do not drive--TTL output INITIALIZE H Special--See 5.3.1 16 INT IN PROG H INT ROST L 16 INT STROBE H Do not drive--TTL output INTERNAL I/O L 16 T/O PAUSE L Do not drive--TTL output IR<0:2>L 16\* each line KEY CONTROL L 16 LA ENABLE L 16 LINK DATA L , 16 LINK L Do not drive LINK LOAD L 60 (SIXTY!) 30\* each line MA<0:11>L MA, MS LOAD CONT L 16 16\* each line MD<0:11>L (Memories only) 30 MD DIR L MEN START L 16

MS, IR DISABLE L 16 NOT LAST XFER L 16 NTS STALL L 15 OVERFLOW L Do not drive POWER OK H Special--See 5.3.2 PULSE LA H Special--See 5.3.2 RES 16 RETURN H Do not drive--TTL output ROM ADDRESS L 30 RUN L Do not drive--May be TTL SKIP L 16 SOURCE H Do not drive--TTL output STOP L 16 STROBE H Do not drive--TTL output TP1, 2, 3, 4 H Do not drive--TTL output TS1, 2, 3, 4 L Do not drive--TTL output USER MODE L 16 WDTTR H Do not drive--TTL output

Signals marked \* are driven by Tri-state gates on PDP-8A. Users should not drive these lines unless the CPU is not driving them.

| Signal                     | CPU not driving if                                |  |  |

|----------------------------|---------------------------------------------------|--|--|

| D L, E L, F L,<br>IR<0:2>L | MS, IR DISABLE is low                             |  |  |

| MD<0:11 L                  | MD DIR L is high                                  |  |  |

| E! .<0:2>L; MA<0:11>L      | CPMA DISABLE L was low at<br>leading edge of last |  |  |

The DEC 8891 (P/N 19-09705) will meet the 16 and 30 ma requirement. Two 8881's in parallel will meet the 60 ma requirement.

5.3.1 INITIALIZE H And PULSE LA H - Driver must supply 30 ma at +3 volts, and source less than 1 ma at ground. An emitter follower is recommended. Typical circuit is shown below: 45 w.

| berow:    |         |     | - +5 V.  |

|-----------|---------|-----|----------|

| 7401 or   | \$470   | , ₹ | 27       |

| equivalen | د ∶ [ ] | 1   | 213009   |

|           | نتسلسم  | wh  | )        |

|           | 1. I    | 9   |          |

| 4         |         |     | - output |

00001100 EN--01047A 1A 16 R177(327)

5.3.2 POMER OK H - Tais line is driven high by circuitry within the power supply, but can be grounded by options (such as the bootstrap loaders) which need to initialize the CPU and memory extension NA control flip-flops. The power supply driver must supply an arisium of 10 ma at +3 wolts, and muct not supply more than 100 ma when the 0.4 wolts, and sink less than 1 mm leakage at +5 volts.

#### 5.4 Drive Available For Peripherals

The following currents are available for driving options, memories, etc, from the CPU and memory extension. Signals marked \* are generally not used as output from CPU or memory extension.

|                               | Source     | Sink        |  |

|-------------------------------|------------|-------------|--|

| Signal                        | ma<br>@ +3 | ma<br>êgnđ  |  |

| BREAK CYCLE L                 | 3          | 5           |  |

| BREAK DATA CONT               | L 3<br>3   | 5           |  |

| BRK IN PROG L<br>BUS STROBE L | 3          | 5<br>5<br>* |  |

| C<0:2>L                       | • 1        | *           |  |

| CPMA DISABLE L                | •          | *           |  |

| DL                            | 3          | 3           |  |

| DATA<0:11>L                   | 2          | 2           |  |

| E L                           | 3          | 3<br>3      |  |

| EMA<0:2>L                     | 3          | 3           |  |

| FL                            | 3          | 3           |  |

| FSET L                        | 5          | 5           |  |

| IND1 L                        | •          | . <u>*</u>  |  |

| IND2 L                        | ÷          | *.          |  |

| INHIBIT H                     | 10         | 10<br>3     |  |

| INITIALIZE H                  | 10         | 3           |  |

| INT IN PROG H                 | 2          | 2           |  |

| INT ROST L<br>INT STROBE H    | 10         | 10          |  |

| INT STROBE H                  | 5          | 5           |  |

|                               |            | -           |  |

| I/O PAUSE L                   | 10         | 10          |  |

| IR<0:2>L                      | 3          | 3           |  |

| KEY CONTROL L                 | 3          | 3           |  |

| LA ENABLE L                   | 3          | 3           |  |

| digital                       |            |             |  |

| LINK DATA L<br>LINK L<br>LINK LOAD L                    | *<br>5<br>*      | *<br>5<br>*          |

|---------------------------------------------------------|------------------|----------------------|

| MA<0:11>L<br>MA,MS LOAD CONT L<br>MD<0:11>L<br>MD DIR L | 5<br>*<br>2<br>3 | 5<br>*<br>2<br>3     |

| MEM START L<br>MS, IR DISABLE L                         | :                | :                    |

| NOT LAST XPER L<br>NTS STALL L                          | *                | :                    |

| OVERFLOW L                                              | 5                | 5                    |

| RES                                                     | 5                | Depends on<br>driver |

| RETURN H<br>ROM ADDRESS L<br>RUN L                      | 10<br>3<br>5     | 10<br>3<br>5         |

| SKIP L<br>SOURCE H<br>STOP L<br>STROBE H                | *<br>10<br>10    | *<br>10<br>*         |

| TP<1:4>H<br>TS<1:4>L                                    | 10<br>10         | 10 each<br>10 each   |

| USER MODE L                                             | 3                | 3                    |

| USER HODE D                                             | 3                | 3                    |

#### 5.5 Receivers And Load Relief Techniques

The use of Utilogic gates (Signetics SP314, SP380, etc) or other high-imgedance circuits as bus receivers is strongly recommendar. These gates have high threshold and low input drive, and thus present saminum noise immunity while introducing minimum our relactions. Since the main available only on CPU thing and manory thing signals, on the Own1805.

A typical I/O decoder is shown below. Note the use of buffered I/O PAUSE L. This signal keeps the MD receivers from loading the MD lines, since buffered I/O PAUSE L supplies all needed base current to the three gates on the MD lines unless I/O PAUSE L is low.

# similar techinques should be employed for signals from DATA<0:11>L to peripherals.

# PAGE 46

Sample I/O interface

.

PAGE 47

Sample DNA (data break) interface

#### 5.6 General Cautions Regarding Interfaces

- Minimize capacitance on the OMNIBUS lines. The OMNIBUS will work properly only if the 100 ns allowed for bus charge time is met. Limit wire lengths on interface modules to 6 inches per signal. In general, this requirement means you should place bus receivers and drivers near the pins (which you will do anyway to minimize the crossovers if making a pc board).

- Good ground grids on interface boards are maidatory.

- Observe normal TTL rules for +5 volt bypassing. (Normal DEC bypassing is .01 mfd per IC, plus a 6.8 mfd tantalum capacitor where power supply voltade enters board.)

- Except for gating EMA<0:2>L and MD<0:11> to bus (50 ns max), a peripheral has 100 ns to react.

#### 5.7 Transmission Line Effects

Rise-times on the OWNIBUS are generally long compared to propagation velocities. Hence most OWNIBUS signals should be treated as capacitively-loaded lines. This trait is most pronounced on long busses.

Some signals driven by TTL drivers are a different matter entirely. These signals must either be kept (hort (less than 1 hort) and critical rise times controlled, or terminated at the far end of the bus from the CPU. The PDP-BA does the forcer; the PDP-B4, the latter. The signals which must be so treated are the nine CPU timing signals, the five memory timing signals and I/O PMSE L. In addition, BUS ETMOBE L and LINK LOAD L must be terminated at both ends of the machines. For short busies (less than 1 foot), a single resistor of 150 ohms to +5 volts in the CPU is sufficient. These terminating resistors are built into the CPU and/or bus loads modules.

It must be remembered that the characteristic impedance of the OMNIBUS tiself (about 120 ohns) is a very small part of the overall picture. Of far more importance is the value and position of the capacitive load presented by boards connected to the OMNIBUS.

#### **J.O FOWER SUPPLY REQUIREMENTS**

The modules designed for use on the OWNIBUS have varying current regurmements; hence it is not possible to present a coaprehensive chart in this general specification. For the most part, however, voltage requirements are standard. The design of the power supply

should include good high-frequency bypassing at the Output to keep noise on the power lines from affecting the system, and also to prevent the power supply from tending to oscillate under some dynamic load conditions. Also, the use of large wire diameters in the dc distribution lines from power supply to ONNISUS is c mended.

# 6.1 +5 Volts

+5 volts dc is required for Vcc for the TTL logic, plus other needs. The TTL logic requires met is most stringent, and requires the +5 volt supply to deliver an absolute minimum of 5.0 v and an absolute maximum of 5.25 v, under all conditions of line, load, temperature and ripple. This requirement allows the power distribution system (cables and the OMRIBUS listelf, plus board etch) a maximum of 250 mv. drop.

The +5 volt supply must be equipped with an over-voltage crowbar which is designed to prevent by , from ever exceeding 7.0 volts, to protect the integrated circuits from damage in the event of a power supply failure.

### 6.2 -15 Volts

-15 volts dc is used for some load resistors, as a memory supply voltage, and as a dc supply for E16 converters and other miscellaneous gear. It should be within + or - 5% of its nominal value for all conditions of load, line, temperature and ripple. The regulation may be relaxed to + or - 7.5% if core memory is not attached to the supply.

#### 6.3

+15 volts +15 volt dc requirements are similar to those for -15 volts dc.

#### 6.4 POLER OK H

POWER OF I is a logic signal, generated at the power supply, which reports to the OWNIBUS (Pin BY2) that the dc voltages are satisfactory. This signal should be regated on power application be negated as soon as the regulation circuitry is in demoger of saturation when the primary power is removed. It is desirable that this circuitry have hysteresis to prevent the "motorbating" oscillation that could result if there is an appreciable increase the **HEMPENDE**. voltages--which may cause the POWER OK H signal to be negated again, etc. The hysteresis should be greater than the change of voltage from no load to full load.

# 6.5

The computer should not be started until at least 0.5 seconds after POWER OK H has been asserted, but all devices should be ready to run 0.1 sec after POWER OK H is asserted.

#### 7.0 INDEX OF OWNIBUS SIGNAL NAMES

Also see 5.2, 5.3 and 5.4

| Signal name                                                         | Pin                      | Paragraphs where described                                                                                                                              |

|---------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| +5 Volts                                                            | AA2<br>BA2<br>CA2        | 1.03, 6.1                                                                                                                                               |

| +15 Volts                                                           | DA2                      | 1.03, 6.3                                                                                                                                               |

| -15 Volts                                                           | AB2<br>BB2<br>CB2<br>DB2 | 1.03, 6.2                                                                                                                                               |

| BREAK CYCLE L<br>BREAK DATA CONT L<br>BRK IN PROG L<br>BUS STROBE L |                          | 2.5, 3.5.7, 4.6.1, 4.6.3<br>2.5, 3.5.5, 3.9.9, 4.6.2<br>2.5, 3.5.1, 4.6.1, 4.6.3<br>2.4, 3.4.6, 4.5                                                     |

| CO L<br>Cl L<br>C2 L<br>CPMA DISABLE L                              | CE1<br>CH1<br>CJ1<br>CU1 | 2.4, 3.4.5, 4.4, 4.5<br>2.4, 3.4.5, 4.4, 4.5<br>2.4, 3.4.5, 4.5<br>2.5, 3.5.2, 4.6.1, 4.6.3                                                             |

| DL                                                                  | DK2                      | 2.7, 3.7.1, 4.7                                                                                                                                         |

| DATAO L<br>Datal L<br>Data2 L<br>Data3 L                            | AS1                      | 2.3, 3.3, 4.4, 4.5.2, 4.6.2<br>2.3, 3.3, 4.4, 4.5.2, 4.6.2<br>2.3, 3.3, 4.4, 4.5.2, 4.6.2<br>2.3, 3.3, 4.4, 4.5.2, 4.6.2<br>2.3, 3.3, 4.4, 4.5.2, 4.6.2 |

| DATA4 L<br>DATA5 L<br>DATA6 L<br>DATA7 L                            | BR1<br>BS1<br>BU1<br>BV1 | 2.3, 3.3, 4.4, 4.5.2, 4.6.2<br>2.3, 3.3, 4.4, 4.5.2, 4.6.2<br>2.3, 3.3, 4.4, 4.5.2, 4.6.2<br>2.3, 3.3, 4.4, 4.5.2, 4.6.2<br>2.3, 3.3, 4.4, 4.5.2, 4.6.2 |

| DATAS L                                                             | DR1                      | 2.3, 3.3, 4.4, 4.5.2, 4.6.2                                                                                                                             |

| GIGILI 31 EN-01047A-1A-16 H1                                        |                          |                                                                                                                                                         |

CICLUCE DRA 118A

| DEC STD 157                              | REV. A                                                                                                                                                                            | Page 51 |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| DATA9 L<br>DATA10 L<br>DATA11 L<br>E L   | DS1         2.3, 3.3, 4.4, 4.5.2, 4.6.2           DU1         2.3, 3.3, 4.4, 4.5.2, 4.6.2           DV1         2.3, 3.3, 4.4, 4.5.2, 4.6.2           DL2         2.7, 3.7.1, 4.7 |         |

| EMAO L<br>Emai L<br>Emai L               | AD2 2.1, 3.1, 4.3<br>AE2 2.1, 3.1, 4.3<br>AH2 2.1, 3.1, 4.3<br>AH2 2.1, 3.1, 4.3                                                                                                  |         |

| F L<br>PSET L                            | DJ2 2.7, 3.7.1, 4.7<br>DP2 2.9, 3.9.6, 4.7.1                                                                                                                                      |         |

| Ground                                   | AC1 1.03<br>AF1<br>AN1<br>AT1                                                                                                                                                     |         |

| Ground (cont)                            | AC2 1.03<br>AF2<br>AN2<br>AT2                                                                                                                                                     |         |

| Ground (cont)                            | BC1 1.03<br>BF1<br>BN1<br>BT1                                                                                                                                                     |         |

| Ground (cont)                            | BC2 1.03<br>BF2<br>BN2<br>BT2                                                                                                                                                     |         |

| Ground (cont)                            | CC1 1.03<br>CF1<br>CN1<br>CT1                                                                                                                                                     |         |

| Ground (cont)                            | CC2 1.03<br>CF2<br>CN2<br>CT2                                                                                                                                                     |         |

| Ground (cont)                            | DC1 1.03<br>DF1<br>DN1<br>DT1                                                                                                                                                     |         |

| Ground (cont)                            | DC2 1.03<br>DF2<br>DN2<br>DT2                                                                                                                                                     |         |

| INDI L<br>INDI L<br>INHIBIT H<br>JIGJIJI | CU2 2.9, 3.9.1, 4.9<br>CV2 2.9, 3.9.1, 4.9<br>AP2 2.8, 3.8.3, 4.2                                                                                                                 |         |

•

| INITIALIZE H               | CR1                      | 2.4, 3.4.8                                                                        |

|----------------------------|--------------------------|-----------------------------------------------------------------------------------|

| INT IN PROG H              | BP2                      | 2.9. 3.9.8. 4.7.3                                                                 |

| INT ROST L                 | CPI                      | 2.9, 3.9.8, 4.7.3<br>2.4, 3.4.4, 4.7.3                                            |

| INT ROST L<br>INT STROBE H | 802                      | 2.6, 3.6, 4.1                                                                     |

| INTERNAL I/O L             | BP2<br>CP1<br>BD2<br>CL1 | 2.4. 3.4.2                                                                        |

| INIBALLE I/O B             | CDI                      |                                                                                   |

| I/O PAUSE L                | CD1                      | 2.4, 3.4.1, 4.4, 4.5<br>2.7, 3.7.2, 4.7<br>2.7, 3.7.2, 4.7                        |

| IRO L                      | DD2                      | 2.7. 3.7.2. 4.7                                                                   |

| IR1 L                      | DE2                      | 2.7. 3.7.2. 4.7                                                                   |

| IR2 L                      | DH2                      | 2.7, 3.7.2, 4.7                                                                   |

|                            |                          |                                                                                   |

| KEY CONTROL L              | DU2                      | 2.9, 3.9.9                                                                        |

|                            |                          |                                                                                   |

| LA ENABLE L                | BM2                      | 2.9, 3.9.9                                                                        |

| LINK DATA L                | CR2                      | 2.9, 3.9.5, 4.5.3                                                                 |

| LINK L                     | AV2                      | 2.9, 3.9.4, 4.5.3                                                                 |