DQS11-A/B PDP-11 COMMUNICATIONS CONTROLLER

> OPTION DESCRIPTION CSS-MO-F-3.2-03

digital Computer Special Systems

# NOTEBOOK SECTION

3.2-03

# **OPTION NUMBER**

----

DRAWING SET NUMBER

DQS11-A DQS11-B

# **PROGRAM NUMBER**

DECSPEC-11-ARIAD DECSPEC-11-ARIBD DECSPEC-11-ATKAD DECSPEC-11-ATKBD

# DOCUMENT NUMBER REVISION

CSS-MO-F-3.2-03

С

# DATE

JANUARY 1979

DQS11-A/B PDP-11 COMMUNICATIONS CONTROLLER

> OPTION DESCRIPTION CSS-MO-F-3.2-03

# digital Computer Special Systems

NASHUA

1st Printing October 1972 2nd Printing (Rev) June 1973 3rd Printing (Rev) April 1974 4th Printing (Rev) April 1975 5th Printing April 1978 6th Printing January 1979

# Copyright © 1972, 1973, 1974, 1975, 1978, 1979 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECtape | PDP              |

|--------------|---------|------------------|

| DECCOMM      | DECUS   | RSTS             |

| DECsystem-10 | DIGITAL | <b>TYPESET-8</b> |

| DECSYSTEM-20 | MASSBUS | TYPESET-11       |

|              |         | UNIBUS           |

# CONTENTS

|           |                                          | Page |

|-----------|------------------------------------------|------|

| SECTION 1 | INTRODUCTION                             |      |

| 1.1       | General Description                      | 1-1  |

| 1.2       | Operation                                | 1-1  |

| 1.3       | Configuration                            | 1-2  |

| 1.4       | Specifications                           | 1-2  |

| 1.5       | Availability                             | 1-2  |

| SECTION 2 | INSTALLATION                             |      |

| 2.1       | Site Considerations                      | 2-1  |

| 2.2       | Cables                                   | 2-1  |

| 2.2.1     | PDP-11 Unibus                            | 2-2  |

| 2.2.2     | Modem Control                            | 2-2  |

| 2.3       | Initial Operation                        | 2-3  |

| 2.3.1     | Checkout And Acceptance Procedure        | 2-3  |

| 2.4       | Related Documents                        | 2-3  |

| SECTION 3 | OPERATION AND PROGRAMMING                |      |

| 3.1       | DQS11 Registers                          | 3-1  |

| 3.1.1     | Controller Status Register 16XXX0        | 3-1  |

| 3.1.2     | Byte Count Register 16XXX2               | 3-5  |

| 3.1.3     | Bus Address Register 16XXX4              | 3-6  |

| 3.1.4     | Data Buffer Register 16XXX6              | 3-6  |

| 3.2       | Message Formats                          | 3-6  |

| 3.2.1     | Character Mode                           | 3-7  |

| 3.2.1.1   | SYN – Synchronous Idle                   | 3-8  |

| 3.2.1.2   | SOH – Start of Heading                   | 3-8  |

| 3.2.1.3   | STX – Start of Text                      | 3-8  |

| 3.2.1.4   | ETX – End of Text                        | 3-8  |

| 3.2.1.5   | ETB – End of Transmission Block          | 3-8  |

| 3.2.1.6   | EOT – End of Transmission                | 3-8  |

| 3.2.1.7   | ENQ – Enquiry                            | 3-8  |

| 3.2.1.8   | ACK – Acknowledge                        | 3-9  |

| 3.2.1.9   | NAK – Negative Acknowledge               | 3-9  |

| 3.2.1.10  | DLE – Data Link Escape                   | 3-9  |

| 3.2.1.11  | Stick Characters                         | 3-9  |

| 3.2.2     | Transparent Mode                         | 3-9  |

| 3.2.2.1   | DLE STX – Start of Transparent Text      | 3-10 |

| 3.2.2.2   | DLE ETX – End of Transparent Test        | 3-10 |

| 3.2.2.3   | DLE ETB – End of Transparent Block       | 3-10 |

| 3.2.2.4   | DLE ENQ – End of Faulty Transparent Text | 3-10 |

# CONTENTS (Cont)

|                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| SECTION 3 (Cont)                                                                                                        | OPERATION AND PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                 |

| 3.2.2.5<br>3.2.3<br>3.3<br>3.4<br>3.5<br>3.5.1<br>3.5.2                                                                 | DLE SYN – Transparent Synchronous Idle<br>Cyclic Redundancy Check<br>Transmit<br>Receive<br>Interrupts<br>Interrupt Level And Vector Address<br>Service Routine Timing Restrictions                                                                                                                                                                                                                                                                                         | 3-10<br>3-10<br>3-11<br>3-12<br>3-13<br>3-13<br>3-13                                            |

| SECTION 4                                                                                                               | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.3<br>4.4.4<br>4.5<br>4.6<br>4.6.1<br>4.6.2<br>4.6.3<br>4.6.4 | The DQS11 And The Unibus<br>The DQS11 And The Modem<br>Data Flow During Transmission<br>Transmit Mode Control Logic<br>The Register And The Counter<br>State Flip–Flops Strobed By TOGCND<br>State Flip–Flops Strobed By CNTR1<br>Control Of Parallel Data Flow<br>Receive Mode Data Flow<br>Receive Mode Control Logic<br>The Registers And The Counter<br>State Flip–Flops Strobed After Every Bit<br>State Flip–Flops Strobed By TOGCND<br>Control Of Parallel Data Flow | 4-1<br>4-3<br>4-3<br>4-4<br>4-4<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-8<br>4-8<br>4-9<br>4-10 |

| SECTION 5                                                                                                               | MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |

| 5.1<br>5.2<br>SECTION 6                                                                                                 | Special Test Equipment<br>Maintenance Techniques<br>MODULES                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-1<br>5-1                                                                                      |

| 6.1                                                                                                                     | Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-1                                                                                             |

| APPENDIX A                                                                                                              | DQS11 DIAGNOSTIC PROGRAM DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                 |

| A.1<br>A.2<br>A.3<br>A.4<br>A.4.1                                                                                       | Abstract<br>Requirements<br>Loading Procedure<br>Operating Procedure<br>Starting Addresses                                                                                                                                                                                                                                                                                                                                                                                  | A-1<br>A-1<br>A-2<br>A-2<br>A-2                                                                 |

# CONTENTS (Cont)

Page

| APPENDIX A (Cont) | DQS11 DIAGNOSTIC PROGRAM DESCRIPTION                           |              |

|-------------------|----------------------------------------------------------------|--------------|

| A.4.2             | Option Switches                                                | A-3          |

| A.4.2.1           | The Test Monitor                                               | A <b>-</b> 3 |

| A.4.2.2           | Printout Suppression                                           | A-3          |

| A.4.2.3           | Transmit And Receive Clock Simulation                          | A-4          |

| A.5               | Errors                                                         | A <b>-</b> 4 |

| A.5.1             | BITCHK (Bit Check)                                             | A <b>-</b> 4 |

| A.5.2             | CHBAWC (Check Bus Address And Word Count)                      | A <b>-</b> 4 |

| A.5.3             | CHKCHR (Check Characters)                                      | A <b>-</b> 5 |

| A.5.4             | CHKRCV (Check Receive)                                         | A <b>-</b> 5 |

| A.5.5             | STATUS And STAMSK (Status Masked)                              | A <b>-</b> 5 |

| A.5.6             | TRPNO (No Trap)                                                | A <b></b> 5  |

| A.5.7             | TRPYES (Trap Expected)                                         | A-6          |

| A.5.8             | TRPSUB (Trap Subroutine)                                       | A <b>-</b> 6 |

| APPENDIX B        | DQS11 MODEM EXERCISER PROGRAM DESCRIPTION                      |              |

| B.1               | Abstract                                                       | B-1          |

| B.2               | Requirements                                                   | B-1          |

| B.3               | Loading Procedure                                              | B-1          |

| B.4               | Operating Procedure                                            | B-1          |

| B.4.1             | Starting Addresses                                             | B-2          |

| B.4.2             | Option Switches                                                | <b>B-2</b>   |

| B.5               | Errors                                                         | <b>B-</b> 2  |

| B.5.1             | CHKCHR (Check Characters)                                      | B-2          |

| B.5.2             | CHKST1 (Check Status Of Device One)                            | B-3          |

| B.5.3             | CHKST2 (Check Status Of Device Two)                            | <b>B-</b> 3  |

| B.5.4             | TOERR (Time Out Error)                                         | B-3          |

| B.5.5             | TRPSUB (Trap Subroutine)                                       | B-3          |

| APPENDIX C        | SHIPPING LIST                                                  |              |

| C.1<br>C.2        | Equipment Furnished (DQS11–A)<br>Equipment Furnished (DQS11–B) | C-1<br>C-1   |

|                   | ILLUSTRATIONS                                                  |              |

| Figure No         | Title                                                          | D            |

| Figure No.        | Ime                                                            | Page         |

|                   |                                                                |              |

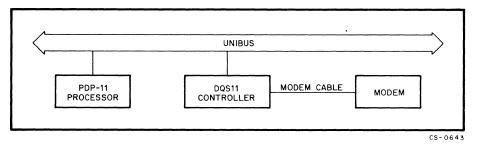

| 1-1 | System Block Diagram | 1-1 |

|-----|----------------------|-----|

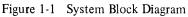

| 2-1 | System Unit Mounting | 2-1 |

# CONTENTS (Cont)

# Page

# ILLUSTRATIONS (Cont)

#### Figure No. Title Page Cable Slot Assignments 2-2 2-2 Controller Status Register Word Format 3-1 3-1 General Block Diagram 4-1 4-2 TABLES Table No. Title Page

| 3-1 | Characters Decoded By DQS11–A and DQS11–B | 3-7 |

|-----|-------------------------------------------|-----|

| 6-1 | DQS11 Module Complement                   | 6-1 |

| A-1 | Program Switch Options                    | A-2 |

5/75

Section 3.2-3B

# DQS11-A/B

# **BI-SYNC CONTROLLERS FOR PDP-11**

# 1.1 GENERAL DESCRIPTION

DQS11-A/B are half-duplex synchronous communications controllers for the PDP-11 Family, capable of operating as speeds to 230.4K baud depending on the characteristics of the modem employed. Data transfers occur directly to memory by means of the PDP-11 NPR facility.

The DQS11-A/B follows the IBM Binary Synchronous Communication (BSC) line-control procedures for the transmission of data. The two available options provide automatic recognition of standard ASCII (DQS11-A) or EBCDIC (DQS11-B) control characters. Additional features include automatic sync acquisition, automatic control of DLE sequences for "transparent" operation, and automatic generation and checking of a two character (16-bit) cyclic redundancy check message. The DQS11-A also performs odd parity generation and checking for "non-transparent" text.

# 1.2 OPERATION

The DQS11-A/B is initialized (Power ON or System RESET) to the Transmit Idle state. No transmission occurs until the software has prepared a message, loaded the Bus Address and Byte Count registers and issued a GO command to the device. The DQS11-A/B precedes the message with four SYN (ASCII or EBCDIC Synchronous Idle) characters and appends two CRC characters if the message ends with ETX or ETB. One pad character  $(377_8)$  is sent at the end of transmission. During transparent mode transmission, the DQS11-A/B generates an additional DLE character for each DLE character encountered in the data string. The Control DLE in the terminating sequence (DLE ETX or DLE ETB) is not padded. Upon completion of transmission, the device sets its RDY bit and, if Interrupt Enable is set, generates an interrupt request to the program interrupt facility.

When "primed" by the operating program to receive a message , i.e., set to the Receive mode, the DQS11-A/B monitors the receive data for two consecutive SYN characters. Once synchronization has been achieved, the first non-SYN character is handled as data. If a GO Command has been received, specifying that a buffer area has been reserved for data storage, memory transfers commence. Normal mode SYN characters, Transparent mode DLE SYN sequences, and the first DLE of DLE DLE sequences are not transferred to memory. At the end of the message, the two character CRC word is checked (when present), and the device's RDY bit is set. The DQS11-A/B remains in Receive mode, searching for Synchronous Idle, until software places it in Transmit mode.

ł

#### 1.3 CONFIGURATIONS

The DQS11-A/B is available in four configurations. Model numbers and configurations are:

DQS11-AA ASCII characters, EIA interface levels

DQS11-AB ASCII characters, Current Mode

- DQS11-BA EBCDIC characters, EIA interface levels

- DQS11-BB EBCDIC characters, Current Mode.

#### 1.4 SPECIFICATIONS\*

a.

Mechanical: Logic Panels Dimensions Weight Interconnections Unibus Modem Cable

Mounting Prerequisite

- Electrical: Prerequisite Power Source Input Voltages Logic Module Type

- c. Operational: Transfer Mode Data Transfer Control Characters

Modem Signal Drive

Operating Speed

# 1.5 AVAILABILITY

The DQS11-A/B are products of Digital's Computer Special Systems group and are available, with new installations or for add-on to existing compatible systems, from facilities in:

Digital Equipment Corporation Main Street Maynard, Massachusetts 01754 U.S.A. Telephone: (617) -897-5111

Digital Equipment Corporation Ltd. 4 Arkwright Road Reading, Berkshire, England Telephone: 0734–583555 Digital Equipment Corporation 310 Soquel Way, Sunnyvale, California 94086 U.S.A Telephone: (408) -735-9200

Digital Equipment GmbH 8 Muenchen 13 Wallensteinplatz 2 West Germany Telephone: 0811-35031

Digital Equipment Australia Pty., Ltd. 75 Alexander Street Crows Nest N.S.W., Australia 2065 Telephone: 439-2566

Digital Equipment Corporation 2110 South Anne Street Santa Ana, California 92704 U.S.A. Telephone: (714) -979-2460

One, Type H933-C (System Unit)

19 in. w, 10-1/2 in. h, 2-1/2 in. d

BC11A or M920 (as required)

H720 mounted in BA11 box +5 Vdc, +8 Vdc, -15 Vdc

BC01R25 (25 feet) for EIA drive.

BC01W25 (25 feet) for current drive Space in BA11 mounting box

DMA via Non-Processor Request (NPR) Block, Half-duplex, Bi-directional

Optional: any speed up to 230.4K baud

10 lb (approx.) Supplied

TTL

**M**-Series

ASCII (DQS11-A)

EIA (standard) Current (optional) Standard: 2000 baud

EBCDIC (DQS11-B)

Digital Equipment France 18 rue Saarinen Zone Silic 94533 Rungis, France Telephone: 687–2333

> Digital Equipment of Canada, Ltd. 100 Herzberg Drive Kanata, Ontario, Canada Telephone: (613) -592-5111

Main offices are at 146 Main Street, Maynard, Massachusetts, 01754.

\*Specifications are subject to change without notice.

Copyright © 1972, 1973, 1974, 1975 by Digital Equipment Corporation.

**Digital Equipment Corporation International**

Englundavagen 7, 171 41 Solna, Sweden

Kowa Building No. 25 (3rd Floor)

Chiyoda-ku, Tokyo 102, JAPAN Telephone: 264-7101

8-7, Sanban-cho,

Digital Equipment AB

Telephone: 98 13 90

Stockholm

SECTION 2 INSTALLATION

Each DQS11 occupies one PDP-11 system unit which is usually housed in a BA11 Mounting Box as shown in Figure 2-1 but can be mounted in a vertical rack when required.

Figure 2-1 System Unit Mounting

# 2.1 SITE CONSIDERATIONS

Environmental requirements for this device are identical to those specified for the PDP-11 computer system in the PDP-11 maintenance literature.

# 2.2 CABLES

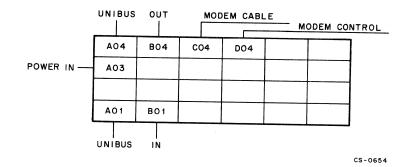

The DQS11 requires Unibus and Modem Control Cables. Figure 2-2 shows the cable slot assignments. These cables assemblies are described in the following paragraphs.

Figure 2-2 Cable Slot Assignments

# 2.2.1 PDP-11 Unibus

All communications with the PDP-11 system take place over the Unibus. BC11A Unibus cables or M920 Unibus Jumper Modules are supplied as required. The input slots for the Unibus are A01 and B01. The output slots, A04 and B04, connect to another system device or, if the DQS11 is the last unit on the bus, they accept the M930 Bus Terminator Module.

# 2.2.2 Modem Control

Data and modem control signals are carried on either a BC01R or a BC01W cable, depending on the modem employed. The BC01R cable is used with the M594 EIA Voltage Converter. The BC01W cable is used with the M595 Current Mode Converter. The BC01R has a DEC "paddle board" connected at the DQS11 end and an RS232 compatible connector at the modem end. The BC01W has a DEC "paddle board" connector at one end and a Burndy MD 12MXP-17TC connector at the other. Both cables connect to DQS11 slot C04. The following are names with respective pin locations.

| Signal Names                          | Modem Connector Pin |

|---------------------------------------|---------------------|

| · · · · · · · · · · · · · · · · · · · |                     |

| ba transmit data                      | E2                  |

| BB RECEIVE DATA                       | F2                  |

| CA REQUEST TO SEND                    | L2                  |

| CB CLEAR TO SEND                      | K2                  |

| CC DATA SET RDY                       | N2                  |

| CD TERM RDY                           | R2                  |

| CF CARRIER                            | P2                  |

| DB TRANSMIT CLOCK                     | H2                  |

| DD RECEIVE CLOCK                      | J2                  |

# 2.3 INITIAL OPERATION

The following Checkout and Acceptance procedures are performed in-house prior to shipment of the DQS11. These, if performed again at the time of installation, serve an initial turn-on procedure which validates proper operation.

# 2.3.1 Checkout And Acceptance Procedure

Perform the Checkout And Acceptance Procedure in the following sequence:

- a. Remove the converter module from slot D04 of the device system unit. Run either DECSPEC-11-ARIAD or DECSPEC-11-ATKAD (the DQs11-A and DQs11-B diagnostic programs discussed in Appendix A). The diagnostic exercises and checks the entire device except for the nine logic paths leading to and from the modem. If no failure is detected, the DQS11 satisfies this portion of the Checkout and Acceptance Procedure.

- b. Run either DECSPEC-11-ARIBD or DECSPEC-11-ATKBD (the DQS11-A and DQS11-B Modem Exerciser Programs discussed in Appendix B). These programs require that two similar DQS11 devices be located on a common Unibus and that the two devices be attached to two modems through which communications can take place. If no failure is detected, the DQS11 satisfies this portion of the Checkout and Acceptance Procedure.

# NOTE

Omit Section b. if the required equipment is not available.

# 2.4 RELATED DOCUMENTS

The following DEC publications contain material which supplements the information in this option description:

PDP-11 Processor Handbook PDP-11 Peripheral Handbook Logic Handbook ×

# SECTION 3 OPERATION AND PROGRAMMING

This device provides the means by which bidirectional block data transfers occur between the PDP-11 core memory and certain half-duplex synchronous communication equipments (modems).

All data transfers occur directly with the PDP-11 core memory utilizing the PDP-11 Non-Processor Request (NPR) facility. Non-data transfers for establishing and examining control conditions occur over the PDP-11 Unibus under program control.

# 3.1 DQS11 REGISTERS

Four registers employed by the DQS11 reside on the PDP-11 Unibus. The absolute bus addresses of these registers are determined by jumpers on the M105 Device Selector Module. Within any DQS11 the relative register addresses are fixed and only the address of the Controller Status Register need be specified.

# 3.1.1 Controller Status Register 16XXX0

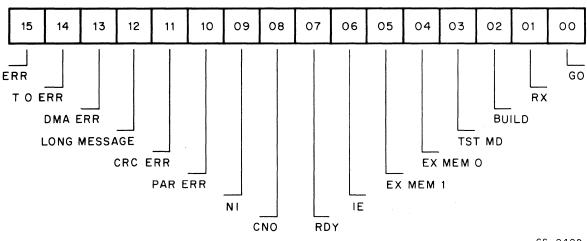

The Controller Status Register (CSR) provides the means by which the PDP-11 commands and monitors the DQS11. The CSR is organized as shown in Figure 3-1.

CS-0409

# Figure 3-1 Controller Status Register Word Format

The following lists each CSR bit and the significance of each when set.

| Bit      | Mnemonic             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00       | GO                   | This write-only bit (always read as zero) in Transmit Mode causes<br>the DQS11 to transmit the message specified by the Bus Address<br>and Word Count Registers. In the Receive Mode, the DQS11 is<br>notified that an input buffer has been established for the received<br>message.                                                                                                                                                                                                                                                                                                              |

| 01       | RX                   | RECEIVE. This read-write bit places the DQS11 in the Receive mode. This bit is cleared by system RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 02       | BUILD                | This read-write bit alters the significance of Byte Count Overflow.<br>When this bit is clear, Byte Count Overflow signals end of message<br>when transmitting and data buffer overflow when receiving. When<br>this bit is set, Byte Count Overflow asserts the RDY bit, notifying<br>the software that a new data buffer must be assigned. This feature<br>conserves core memory by allowing the software to process a mes-<br>sage in segments. While the software handles one data buffer,<br>the DQS11 transfers data to or from another data buffer. This bit<br>is cleared by system RESET. |

| 03       | TST MD               | TEST MODE: This read-write bit is set for maintenance purposes<br>only. Bits 08 and 09 become the read-write bits; TEST CLOCK,<br>and TEST DATA respectively. This bit is cleared by system RESET.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 04<br>05 | EX MEM 0<br>EX MEM 1 | These read-write bits specify the 32K memory field which is to be<br>the target of NPR data transfers should the PDP-11 system contain<br>more than 28K of core memory. These bits are cleared by system<br>RESET.                                                                                                                                                                                                                                                                                                                                                                                 |

| 06       | IE                   | INTERRUPT ENABLE: This read-write bit causes the DQS11 to<br>interrupt the PDP-11 whenever the Ready bit is set. Interrupts<br>are inhibited when the IE bit is cleared. This bit is cleared by<br>system RESET.                                                                                                                                                                                                                                                                                                                                                                                   |

...

| Bit | Mnemonic | Function                                                            |

|-----|----------|---------------------------------------------------------------------|

| 07  | RDY      | READY. This read-only bit is set whenever the DQS11 is available    |

|     |          | to receive a transfer to the CSR with the GO bit set. This GO       |

|     |          | Command clears the RDY bit. RDY is set at the completion of the     |

|     |          | transmit or receive operation or by Time Out Error. RDY is set by   |

|     |          | a transfer to the CSR with the GO bit clear. System RESET also      |

|     |          | sets RDY.                                                           |

| 08  | CNO      | CARRIER NOT ON: During normal operation, this read-only bit         |

|     |          | reflects the Data Carrier Detector (Connection CF) signal from the  |

|     |          | Modem. A true condition indicates that the data carrier is lost,    |

|     |          | either because the transmitting signal converter is turned OFF or   |

|     |          | because of a fault condition.                                       |

|     |          | When bit-3 (TEST MODE) is SET, bit-8 becomes the read/write         |

|     |          | bit TEST CLOCK used by maintenance software to simulate transmit    |

|     |          | or receive clock pulses.                                            |

| 09  | NI       | NO INTERLOCK: During normal operation, this read–only bit           |

|     |          | reflects the Data Set Ready (Connection CC) signal from the Modem.  |

|     |          | When this bit is true, the modem is not in the data mode.           |

|     |          | When bit-3 (TEST MODE) is SET, bit-9 becomes the TEST DATA          |

|     |          | bit. If bit-1 (RX) is also set, TEST DATA is a read/write bit which |

|     |          | simulates the serial receive data. If bit-1 is clear, TEST DATA is  |

|     |          | a read-only bit which reflects the serial transmitted data.         |

| 10  | PAR ERR  | PARITY ERROR: This read-only bit is set whenever the DQS11-A        |

|     |          | is not in transparent mode and an ASCII character is received       |

|     |          | consisting of an even number of ones (even parity). This bit is     |

|     |          | cleared by system RESET and by any GO Command which initiates       |

|     |          | a new operation. This bit is not cleared by a GO Command that       |

|     |          | continues a build mode operation. The DQS11-B does not check        |

|     |          | vertical parity and never causes this bit to be set.                |

|     |          |                                                                     |

3-3

Bit Mnemonic

CRC ERR

LM

# Function

Cyclic Redundancy Check Error. This read only bit is set when the DQS11 receives a character CRC message which does not equal the CRC message generated by the receiver. This bit is cleared by system RESET and by any GO Command which initiates a new operation. This bit is not cleared by a GO Command that continues a build mode operation.

LONG MESSAGE: This read-only bit specifies that the message is longer than the available memory buffer area. When transmitting, the final character (as indicated by CSR Bit-2 clear and Byte Count Overflow set) must be a terminator character. If it is not, the Interface transmits the ENQ Character to specify faulty transmission. When receiving, Byte Count Overflow inhibits the transfer of data to memory. Bit-12 sets when a data word is lost. The RDY bit is not set until the end of the message and the entire message is checked for parity errors. When receiving in Build Mode (CSR bit-2 set), Byte Count Overflow must be cleared by a GO Command before data is lost. Otherwise Bit-12 is set. This bit is cleared by system RESET, and any GO Command which initiates a new operation. This bit is not cleared by a GO Command which continues a build mode operation.

DMA ERR DMA ERROR: This read only bit specifies that the transfer of data between the interface and the computer is failing to keep up with the communications channel. When receiving, a GO Command must be received from the computer before the detection of the first non-SYN character following synchronization. Also, the DMA transfer of each two character word must occur within the

12

11

3-4

13

| Bit | Mnemonic          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 13  | DMA ERR<br>(Cont) | transmission time of one character. When transmitting, the inter-<br>face responds to a DMA Error by terminating transmission with an<br>ENQ character. This bit is cleared by system RESET, and by any<br>GO Command which initiates a new operation. This bit is not<br>cleared by a GO Command that continues a build mode operation.                                                                                                                                                                                                   |  |  |  |

| 14  | TO ERR            | TIME OUT ERROR: This bit sets between 5.0 and 6.0 seconds<br>after the beginning of transmission or, when in Receive mode, after<br>synchronization. In Transmit mode, the Time Out Clock begins<br>with the initial GO Command. In Receive mode, the Time Out<br>Clock begins when the first two consecutive SYN characters are<br>received. In both cases, the Time Out Clock is stopped if the<br>message ends before the time out period. This error, which should<br>only occur in the event of a hardware failure, sets the RDY bit. |  |  |  |

| 15  | ERR               | Bit-14 is cleared by system RESET and any GO Command.<br>ERROR: This read-only bit is the "OR" condition of PAR ERR, CRC<br>ERR, LONG MESSAGE, DMA ERR, and TO ERR.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

# 3.1.2 Byte Count Register 16XXX2

The Byte Count Register is a 16-bit read-write register which specifies the maximum (or total) number of bytes to be transferred to or from memory. When transmitting, the program loads this register with the 2's complement of the exact number of bytes to be transferred to the DQS11. Although each transfer contains two bytes, the interface handles byte count incrementation in a manner which allows an odd number to be specified. When receiving, this register specifies the number of memory bytes available for character storage. Because each transfer contains two bytes, this number must be even.

# 3.1.3 Bus Address Register 16XXX4

The Bus Address Register is a 16-bit read-write register which specifies the Bus Address which is the target of the next NPR transfer. Since data is transferred on a word basis, this register must contain a word address. The contents of the Bus Address Register are increased by two with each NPR transfer.

# 3.1.4 Data Buffer Register 16XXX6

The 16-bit Data Buffer Register may be written into and read from for maintenance purposes.

# NOTE

During message handling, this register forms part of the data path to memory. Any attempt to write into the Buffer Register during message handling will cause loss of data.

# 3.2 MESSAGE FORMATS

The DQS11 is capable of sending or receiving 8-bit bytes of data in either character or transparent mode. In character mode, each byte represents a seven bit ASCII (DQS11-A) or an eight bit EBCDIC (DQS11-B) character. The DQS11-A generates and detects odd parity. In transparent mode, 8-bit bytes are sent as retrieved from memory. Lateral parity is neither generated nor detected. Text Control characters for both modes conform to Binary Synchronous Communications (BSC) conventions.\* As described in this section, most control characters must be supplied as part of the message block stored in computer memory for transmission. The leading SYN characters and the DLE characters used to pad the appearance of DLE in transparent text are the two main exceptions. These are generated by the transmitting interface and stripped (not transferred to memory) by the receiving interface. The interface also generates and detects a two byte Cyclic Redundancy Check (CRC) word following each properly delimitted block of data.

\*Conventions of Digital Data Communications Link Designed by J.L. Eisenbies, IBM Systems Journal Vol. 6 No. 4 1967.

# 3.2.1 Character Mode

The DQS11 detects and responds to ten Control characters which compose five groups. SYN establishes character synchronization. SOH and STX indicate the beginning of data blocks and initiate CRC generation and detection. ETX and ETB terminate data blocks and are followed by the two byte CRC word. EOT, ENQ, ACK, and NAK abruptly terminate transmission and are not followed by a CRC word. DLE is used primarily for transparent mode control.

The DQS11 also detects a group of "Stick" characters which, when preceeded by DLE, abruptly terminate transmission. This feature allows the DQS11 to handle the two character affirmative acknowledge sequences.

Table 3-1 lists the ASCII and EBCDIC characters which are decoded by the DQS11-A and DQS11-B respectively. Bits represented by "X" may be either a "0" or a "1".

| Character | DQS11-A<br>ASCII P, 7-1 |          | 1     | S11-B<br>DIC 0-8 |

|-----------|-------------------------|----------|-------|------------------|

|           | Octal                   | Binary   | Octal | Binary           |

| SYN       | 026                     | X0010110 | 062   | 00110010         |

| SOH       | 001                     | ×0000001 | 001   | 00000001         |

| STX       | 002                     | X0000010 | 002   | 00000010         |

| ETX       | 003                     | X0000011 | 003   | 00000011         |

| ETB       | 027                     | X0010111 | 046   | 00100110         |

| EOT       | 004                     | X0000100 | 067   | 00110111         |

| ENQ       | 005                     | X0000101 | 055   | 00101101         |

| ACK       | 006                     | X0000110 | 056   | 00101110         |

| NAK       | 025                     | X0010101 | 075   | 00111101         |

| DLE       | 020                     | 00010000 | 020   | 00010000         |

| Stick     | -                       | XXIXXXXX | -     | 01XXXXXX         |

| Stick     | -                       | -        | -     | 10XXXXXX         |

| Stick     | -                       | -        | -     | 11XXXXXX         |

Table 3–1 Characters Decoded by DQS11–A and DQS11–B

3.2.1.1 <u>SYN - Synchronous Idle</u> - The interface preceeds each transmission with four SYN characters. When receiving, the interface synchronizes on the first pair of consecutive SYN characters and treats the next non-SYN character as data. SYN control characters are not sent to computer memory.

3.2.1.2 <u>SOH - Start of Heading</u> - SOH preceeds a block of characters (the heading) which contains address or routing information. Whether transmitting or receiving, the interface begins CRC accumulation with the character following SOH. The appearance of STX indicates the end of the "heading", but the CRC accumulation is not terminated until the detection of either ETX or ETB.

3.2.1.3 <u>STX - Start of Text</u> - STX preceeds a block of characters (text) which is transmitted as an entity. If an SOH character has been detected, the interface includes STX in the CRC accumulations. Otherwise, CRC accumulation begins with the character following STX. The text and CRC accumulation are both terminated by either ETX or ETB.

3.2.1.4 <u>ETX - End of Text</u> - ETX terminates a block of characters started with SOH or STX and transmitted as an entity. When transmitting, the interface sends the two CRC bytes immediately following ETX. When receiving, the interface shifts ETX and the two following bytes into the CRC accumulator and sets an ERROR Flag if the result is not zero.

3.2.1.5 <u>ETB – End of Transmission Block</u> – ETB terminates a block of characters started with SOH or STX, where block structure is not necessarily related to processing format. The interface treats ETX and ETB identically.

3.2.1.6 <u>EOT - End of Transmission</u> - EOT indicates conclusion of a transmission (including text and associated headings) of one or more messages. When transmitting, the interface recognizes EOT as a legitimate message terminator. When an interface in Receive Mode detects EOT, it transfers the character to memory and then sets the RDY bit (CSR bit-07). EOT will usually be sent as a single character.

3.2.1.7 <u>ENQ - Enquiry</u> - As a single character, ENQ requests a response indicating identification, station status, repeat, or reply. When ENQ terminates a message string, it specifies that the message was in error and should be ignored. When transmitting, if the last character does not correctly terminate the message, the interface sets Long Message Error and terminates transmission by generating an ENQ character. In Receive Mode, the interface treats ENQ as EOT. 3.2.1.8 <u>ACK - Acknowledge</u> - ACK specifies that the previous block in the transmission was received without error and that the receiver is ready for the next block. The interface responds to ACK and EOT identically.

3.2.1.9 <u>NAK - Negative Acknowledge</u> - NAK indicates that the previous block in the transmission was not accepted and that the receiver is ready for retransmission. The interface responds to NAK and EOT identically.

3.2.1.10 <u>DLE - Data Link Escape</u> - DLE provides additional BSC control signals by changing the meaning of the character that follows it. Section 3.2.2 discusses the use of DLE for control-ling transparent mode. Section 3.2.1.11 discusses the use of DLE in two character affirmative acknowledge sequences.

3.2.1.11 <u>Stick Characters</u> – Any stick character preceeded by DLE forms part of a two character control sequence. When transmitting, the interface recognizes DLE "Stick" as a legitimate message terminator. When an interface in Receive Mode detects DLE "Stick", it transfers both characters to memory and then sets the RDY bit (CSR bit-07). This feature is intended primarily for the detection of the BSC affirmative acknowledge sequences which are DLE0 and DLE1 for ASCII and DLE " $160_8$ " and DLE / for EBCDIC.

3.2.2 Transparent Mode

Transparent mode control is provided automatically by the DQS11. The DQS11 remains in the character mode until the data link escape (DLE,  $020_8$ ), start of text (STX,  $002_8$ ) sequence is recognized in the message. All subsequent data is in the transparent mode. Because line control is provided in the transparent mode by DLE, whenever the DLE bit pattern ( $020_8$ ) is encountered during transparent text, it must be paired with a second DLE if it is not intended as a control character. When transmitting in transparent mode, the interface generates an additional DLE following every DLE in the message except when Byte Count Overflow is set indicating the end of the message. This exception specifies that the control DLE in the terminating DLE ETX (or DLE ETB) sequence is not padded. When receiving in transparent mode, the interface strips (does not transfer to memory) the first DLE in every DLE DLE sequence received. All control characters not preceeded by an unpaired DLE are treated as data.

3-9

3.2.2.1 <u>DLE STX - Start of Transparent Text</u> - All characters following DLE STX are treated as transparent text. If an SOH character has been detected, the interface includes both DLE and STX in the CRC accumulation. Otherwise, CRC accumulation begins with the character following STX. The text and CRC accumulation are both terminated by either DLE ETX or DLE ETB.

3.2.2.2 <u>DLE ETX - End of Transparent Test</u> - DLE ETX terminates a block of transparent text started with DLE STX and transmitted as an entiry. When transmitting, the interface sends the two CRC bytes immediately following ETX. When receiving, the interface shifts ETX and two following bytes into the CRC accumulator and sets an ERROR Flag if the result is not zero. In neither case is the DLE control character included in the CRC accumulation.

3.2.2.3 <u>DLE ETB – End of Transparent Block</u> – The interface treats DLE ETB and DLE ETX identically.

3.2.2.4 <u>DLE ENQ - End of Faulty Transparent Text</u> - When transmitting in transparent mode, and if the message is not properly terminated, the interface sets Long Message error and terminates the message by generating the DLE ENQ sequence. When receiving in transparent mode, the interface recognizes the DLE ENQ sequence as a message terminator.

3.2.2.5 <u>DLE SYN - Transparent Synchronous Idle</u> - DLE SYN is used as a time fill to retain character synchronization in a transparent text message. Because the DMA facilities provide data must faster than the transmission rate, the interface is never required to generate the DLE SYN sequence. If the data is not provided, the DMA ERROR Flag is set and the message is terminated. However, when receiving in transparent mode, the interface detects and strips all DLE SYN sequences. Both characters are omitted from CRC accumulation.

# 3.2.3 Cyclic Redundancy Check

The DQS11 hardware provides a cyclic redundancy checking (CRC) feature to facilitate error detection in messages in both the character and transparent modes. Two 8-bit CRC bytes are derived from the circuit-implemented cyclic redundancy checking polynominal  $X^{16} + X^{15} + X^2$  +1 (IBM CRC - 16 compatible). Whether transmitting or receiving, CRC accumulation starts with the character following the first SOH or STX control character in the data block. In character mode, all characters except SYN are included in the CRC accumulation. In transparent mode all characters except DLE SYN sequences, one DLE of DLE DLE sequences, and the DLE of

3-10

the terminating sequence (DLE ETX, or DLE ETB) are included in the CRC accumulation. When transmitting, the interface sends the two CRC bytes immediately following the terminating ETX (or ETB). When receiving, the interface shifts the ETX (or ETB) and the two following bytes into the CRC accumulator and sets an ERROR Flag if the result is not zero.

The Hardware which implements the CRC function can be modified as required to provide compatibility with remote terminal equipment. Consult DEC Special Systems personnel for information.

# 3.3 TRANSMIT

The DQS11 is initialized to the transmit idle state (RX bit clear, RDY bit set). The software initiates transmission by clearing the RDY bit with a GO Command to the CSR (bit-0 set). Immediately upon entering the transmit active state (RX bit clear, RDY bit clear), the DQS11 raises Request to Send (Connection CA) to the modem. When the modem responds with Clear To Send (Connection CB) and Transmitter Signal Element Timing (Transmit Clock, Connection DB), the DQS11 transmits four SYN characters followed by the message data retrieved from memory.

Before issuing the GO Command, the software loads the Bus Address Register with a pointer to the even byte which contains the first character and loads the Byte Count Register with the negative of the number of characters to be transmitted. When transmitting normal text, the last character must be either a terminating control character (ETX, ETB, ENQ, ACK, or NAK) or part of a two character terminating sequence (DLE "Stick"). When terminating transparent text, the last two characters must be one of the terminating control characters preceeded by DLE (e.g. DLE ETX, DLE ETB, or DLE ENQ). Otherwise, a Long Message error will occur. After sending the entire message, including the two CRC bytes (if applicable) and one pad character (a 377<sub>8</sub>), the DQS11 sets the RDY bit and, if Interrupt Enable is asserted, causes the processor to trap to the interface's vector address. The Build mode feature of the DQS11 reduces the core memory required for message storage by allowing the software to build messages during transmission and store the message segments in two or more memory buffers. For example, the software stores the first segment in buffer one, initializes the Bus Address and Byte Count Registers, and asserts Build mode (CSR bit–02) when issuing the GO Command. The software stores the second segment in buffer two and then waits for the DQS11 to assert the RDY bit, indicating that the first segment has been sent. Because Build mode is asserted, the interface does not look for a terminating character, but asserts RDY when byte count overflow sets. The software reinitializes the Bus

Address and Byte Count Registers for the new buffer, issues a new GO Command and then stores the next segment in the buffer area which is now available. This process continues through the last segment except that, when the final GO Command is issued, Build Mode must be cleared, causing the interface to search for and recognize the terminating character.

# 3.4 RECEIVE

The DQS11 is placed in the Receive mode by setting Bit-1 in the CSR. Immediately upon entering the Receive Mode, the DQS11 monitors the Receiver Signal Element Timing (Receive Clock, Connection DD) from the modem. When the Receive Clock becomes active, the Received Data (Connection BB) is monitored for SYN. When two consecutive SYN characters are detected, the DQS11 becomes synchronized. If the software has initialized the Bus Address and Byte Count Registers and issued a GO Command to the CSR, data transfer begins with the first Non-SYN character and continues until either Byte Count Overflow occurs or a terminating control character is received. If Byte Count Overflow occurs before a terminating character is detected, Long Message Error and DMA Error are set. Although data transfer ceases, RDY is not set until the terminating character (and CRC bytes, if applicable) has been received. If a GO Command has not been issued, the detection of the first Non-SYN character causes DMA Error to be set. No data is transferred to memory.

The Build Mode feature of the DQS11 reduces the core memory required for message storage by allowing the interface to store segments of the message in two or more independent memory buffers as directed by software. Once received, each segment must be processed or transferred to secondary storage before the software reassigns that buffer to the interface. For example, the software initializes the Bus Address and Byte Count Registers and issues a GO Command while asserting BUILD and RX. At each instance that the interface. If Build Mode is still set, the BUILD bit to determine if it has been cleared by the interface. If Build Mode is still set, the software reinitializes the Bus Address Byte Count Register and issues another GO Command, leaving BUILD and RX asserted. The clear condition of Build Mode specifies that the entire message has been received. The software checks the error bits and sends the relevant positive or negative acknowledge character.

3-12

# 3.5 INTERRUPTS

Conditions required for trapping to the DQS11 Vector Address and service routine timing restrictions are discussed in this section.

3.5.1 Interrupt Level And Vector Address

The interrupt level and the vector address for each DQS11 is determined at system configuration time. The DQS11 will cause the processor to trap to its vector address if the following conditions are true.

- a. The unit's interrupt enable is asserted and

- b. The units RDY bit is asserted and

- c. The units interrupt level is greater than the current processor priority and

- d. No higher priority devices are requesting attention.

#### **3.5.2** Service Routine Timing Restrictions

The DQS11 imposes no timing restrictions on service routines which respond to the end of a Transmit or Receive Mode operation; however, when using Build Mode, the service routine must set up a new buffer and issue a GO Command during the interval between two NPR transfers. When transmitting in Build Mode, all memory blocks except the last must contain an even number of characters. A time interval, defined as 15/BAUD RATE (368 microseconds for 40.8K Baud), is allowed between setting the interrupt request and completion of the NPR data transfer, initiated by the GO Command. In Receive Mode, a similar interval is allowed between the beginning of the NPR transfer which sets Byte Count Overflow and the time when the service routine issues the GO Command. SECTION 4 THEORY OF OPERATION

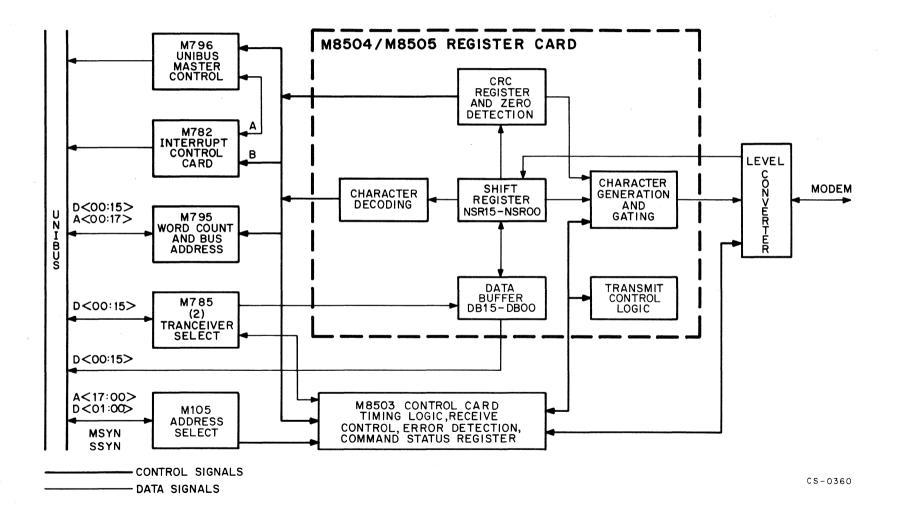

#### 4.1 THE DQS11 AND THE UNIBUS

All logic described in this section appears on Drawing DQS11-0-0-2. All transfers of information between the central processor and the DQS11 or between the DQS11 and memory occur via the Unibus on a master/slave basis. During a program controlled transfer, the processor, as Bus Master, loads or reads one of the four device registers. The register addresses are decoded from the Bus Address Lines by the M105 Address Selector card which also provides the necessary slave response. The M105 output signals are combined on the M8506 Control card to produce the signals which load the registers or gate their contents onto the Data Bus.

The DQS11, as Bus Master, can transfer data directly to or from memory. The logic for requesting and acknowledging control of the bus is contained on the M7821 Interrupt Control card and the M796 Unibus Master Control card. When the DQS11 becomes Bus Master, the M796 card generates the Master control signals to the Unibus and the internal signals which gate the slave address onto the Bus Address lines. These internal signals enable the Data Buffer or gate its contents onto the Bus Data lines, depending on the direction of data transfer. The slave address, contained on the M795 Word Count and Bus Address card, is incremented by two at the completion of each transfer.

The M7821 card also contains logic for generating a program interrupt request. An interrupt request occurs if both the RDY and the Interrupt Enable bits (Controller Status Register Bits 7 and 6) are set. The level of the interrupt is determined by a jumper plug located on the M8504 (M8505 for DQS11-B) register card, IC slot E1. Figure 4-1 is a general block diagram of the device.

The two M785 Transceiver cards contain Bus Data line receivers for the Controller Status Register and the Data Buffer and Bus Data Line drives for the Controller Status Register. The Bus Data line drivers for the Data Buffer are located on the M8504 (M8505) Register Card.

Part 2 of the PDP-11 Peripherals and Interfacing Handbook contains a detailed description of Unibus Operation and of the standard Unibus interfacing modules used in this device (M105, M7821, M785, M795 and M796 modules).

Figure 4-1 General Block Diagram

4-2

#### 4.2 THE DQS11 AND THE MODEM

All logic described in this section appears on Drawing DQS11-0-02 (Sheet 2 of 3). The DQS11 asserts Circuit CD-Data Terminal Ready whenever power is supplied to the system unit. When The DQS11 has a message to be transmitted, it asserts Circuit CA-Request to Send. When the modem responds by asserting Circuit CB-Clear to Send, the DQS11 Monitors Circuit DB-Transmitter Signal Element Timing for internal clocking and output serial data on Circuit BA-Transmitted Data. When in Receive Mode, the DQS11 monitors Circuit DD-Receiver Signal Element Timing for internal clocking and monitors Circuit DD-Receiver Signal Element Timing for internal clocking BB-Received Data for Serial Data In.

Controller Status Register bits 8 and 9 reflect the status of Circuit CF-Data Carrier Detector and Circuit CC-Data Set Ready respectively. The status bits are asserted whenever respective signals are off.

EIA Standard RS-232-B, Interface Between Data Processing Terminal Equipment and Data Communication Equipment, contains a more complete description of these signals.

# 4.3 DATA FLOW DURING TRANSMISSION

The logic described in this section appears on drawing M8504–0–01 (DQS11–A) and on drawing M8505–0–01 (DQS11–B). The CRC and NSR Registers appear on sheet 4 of 6. The Data Buffer Register and character generation logic appear on sheets 3 and 6 respectively.

The serial data sent to the modem has three possible sources: the 16-bit shift register (data originating in core memory), the 16-bit CRC register (the two Cyclic Redundancy Check Characters which follow a terminating ETX or ETB) and a multiplexer controlled by the transmit logic (for interface generated characters SYN, DLE and ENQ). Serial Data Out is asserted during the transmission of the required final pad character. Serial Data Out also serves as the input to the CRC register, which is initialized by the first STX or SOH character in a message. The CRC register is inhibited (not strobed) during the transmission of characters which should not be included in the accumulation.

The portion of the message originating in core memory is transferred from memory to the 16-bit Data Buffer (DB15-DB00) in two character blocks. The even byte (DB07-DB00) contains the first character (of the two) to be transmitted. DB00 contains the least significant bit, which is the first bit to be transmitted. The complements of data buffer bits DB15-DB00 are transferred in parallel to shift register bits NSR15-NSR00 respectively.

# 4.4 TRANSMIT MODE CONTROL LOGIC

This section contains a description of events which occur within the Transmit Mode Control logic during a data transfer operation. Control logic pertaining to Transmit mode only appears on drawing M8504-0-01 (M8505-0-01 for the DQS11-B), Sheet 2 of 6. Control logic used by both Transmit and Receive mode appears on Drawing M8506-0-01, Sheet 2 of 5. Timing logic appears on Drawing M8506-0-01, Sheet 4 of 5.

# 4.4.1 The Register And the Counter

During transmission, the DQS11 bases its internal clocking on Circuit DB-Transmitter Signal Element Timing from the Modem. Changes in the serial data sent to the modem occur at the time of Circuit DB transitions from the OFF to the ON condition. The following operations occur on this clock edge:

- a. The shift register is loaded if the state flip-flops SHFT SR and SRINH are both in the clear condition.

- b. The contents of the shift register are shifted one bit to the right if state flip-flop SHFTSR is set and state flip-flop SRINH is clear.

- c. The previous data out bit is shifted into the CRC register if state flip-flop CRC ON is set and state flip-flop CRCINH is clear.

- d. The divide by eight counter is incremented. When the output data is the first or least significant bit of a character, this counter equals one, and the signal CNTR1 is asserted. When the output data is the eighth or most significant bit of a character, this counter equals zero (0) and the signal CNTR0 is asserted. Signals C1, C2 and C4 represent the binary coded value of the counter and serve as input to the multiplexer which generates the SYN, DLE and ENQ characters.

# 4.4.2 State Flip-Flops Strobed By TOGCND

The serial data sent to the modem remains constant during Circuit DB transitions from the ON to OFF condition. This transition, gated by CNTR1, is the leading edge of the signal TOGCND, which strobes those state flip-flops whose state depend on the identity of the character being

transmitted. The control characters are decoded from the shift register byte NSR 07-NSR 00, which contains the entire character when CNTR1 is asserted. The following state flip-flops are strobed by the leading edge of TOG CND:

- a. If DLESTR is in the clear condition and if the present character is a DLE, then DLESTR is set by TOG CND; otherwise, it is cleared.

- b. If the present character is either SOH or STX, then STX SOH is set and remains set until the end of transmission.

- c. If STX SOH is already set, then CRCON is set, causing CRC accumulation to begin with the first character following the initial SOH or STX.

- d. If DLESTR is set and the present character is STX (indicating the DLESTX sequence), then TRNSP is set and remains set until the DLE ETX or DLE ETB sequence terminates transparent mode.

- e. If TRNSP is set, DLESTR is clear, and the present character is DLE, then CRC INH is set. Thus, in transparent mode, the first DLE of all two character control sequences is omitted from CRC accumulation.

- f. If SNDDLE is set (indicating that the interface is generating a DLE character), SRINH is set to inhibit the shift register, preventing the loss of one character.

- g. If LSTCHR is set (indicating that the present character is the last character coming from core memory), if RFC (Ready For Command) is asserted (indicating that either transmission is in non-transparent mode or that the present character was preceeded by a single DLE), and if ENDCHR is asserted (indicating that a correct non-CRC termination is present), then STREC is set.

- h. If LSTCHR is set, if RFC is asserted, and if the present character is either ETX or ETB, then STP1 is set, beginning the CRC termination sequence. The state of STP1 is strobed into STP2 and the state of STP2 is strobed into STP3.

- i. If LSTCHR is set and if a correct termination character is not present, then NOEND is set.

# 4.4.3 State Flip-Flops Strobed By CNTR1

The leading edge of CNTR1 signals that the first bit of the next character is set up for transmission. This leading edge strobes the state flip-flops, including those which determine the origin and composition of the serial data, in the following manner:

- a. SNDSYN is held clear when RX is set and is held set during the transmission of the four leading SYN characters. Once TRENB4 is asserted, SNDSYN is strobed clear by the next CNTR1 pulse and remains clear until the end of transmission.

- b. SND DLE is set by CNTR1 causing the interface to generate a DLE character if either one of two condition is met: If TRNSP and DLESTR are both set and the conditions for setting LSTCHR are not met, then a data DLE character has been detected and must be padded with an additional DLE; if TERMT (Terminate Transmission) is asserted (indicating a fault condition) and RFC (Ready for Command) is not asserted, then a DLE must be generated to preceed the terminating ENQ.

- c. If TERMT and RFC are both asserted, then SND ENQ is set by CNTR1 to generate a terminating ENQ character which indicates faulty transmission.

- d. If STP1 or STP2 was set during the transmission of the previous character, then SNDCRC is strobed set and the CRC register is the origin of the serial data out.

- e. If SNDENQ was previously set or if TRNEND is asserted (indicating that the entire message, including CRC characters if necessary, has been sent), then PAD CHR is set, causing the interface to generate a final pad character (377<sub>g</sub>).

- f. If PAD CHR was previously set, CNTR1 sets DONET which sets the RDY flip-flop.

- g. If OVF has been set by the Byte Count Register, if BUILD is not set, and if the contents of the Data Buffer have been transferred to the shift register, then LST CHR is set, indicating that the character being transmitted is the last character coming for core memory.

- h. If, because of system failure, no data is ready for transmission, DMA FLT (DMA Failure during Transmission) is set by CNTR1.

# 4.4.4 Control Of Parallel Data Flow

During transmission, the control of parallel data flow depends on the following four state flipflops on the M8504 (M8505) Register Card:

- a. DBFULL is set at the end of an NPR transfer of data from memory to the data buffer. DBFULL is cleared when SHFTSR is cleared.

- b. SHFT SR is always set except when the contents of the data buffer are loaded into the shift register. SHFTSR is cleared by the trailing edge of STRBSR only if four

conditions are met: CNTRO must be asserted, indicating that the next STRBSR will set up the first bit of a new character; SREMP must be set, indicating that both characters previously loaded into the shift register have been transmitted; DBFULL must be set; and SRINH (Shift Register Inhibit) must be clear.

- c. SREMP (Shift Register Empty) is held clear when SHFTST is in a clear condition. Otherwise, SREMP is strobed set by CNTR1 if either SREMP was previously set or if SRINH is clear.

- d. DMAENBT (Transmit Mode DMA Enable) is set by the trailing edge of STRBSR if SHFTSR was previously cleared. Assuming OVF and DBFULL are not set, DMAENBT allows the trailing edge of the next STRBSR to initiate a DMA request.

# 4.5 RECEIVE MODE DATA FLOW

All logic described in this section appears on Drawing M8504–0–01 (M8505–0–01 for DQS11–B), Sheets 3 and 4 of 6.

The serial data from the modem is loaded first into shift register byte NSR07-00 where most of the character decoding takes place. The data shifted from NSR00 provides input both to shift register byte NSR15-08 and to the 16-bit CRC register. When the shift register contains two complete characters, one or both of them may be transferred in parallel to the data buffer. Because the character in NSR15-08 preceeded the character in NSR07-00, this character is transferred into the low data buffer byte, DB07-00. The character in NSR07-00 is loaded into DB15-08. Normal mode SYN characters, transparent mode DLE SYN sequences and the first DLE of transparent mode DLE DLE sequences are not part of the message and, therefore, are not sent to the computer memory.

Whenever the shift register contains two complete characters, one of the following conditions results:

- a. If the data buffer is empty and the character contained in NSR15-08 is not part of the message, no data transfer occurs.

- b. If the data buffer is empty and the character contained in NSR15-08 is part of the message, both shift register bytes are loaded into the Data Buffer. The Data Buffer is now considered half full.

- c. If the Data Buffer is half full and the character contained in NSR15-08 is not part

of the message, the character in NSR07-00 is loaded into DB15-08 where it replaces the character in NSR15-08. The Data Buffer is still considered half full.

d. If the Data Buffer is half full and the character contained in NSR15-08 is part of the message, the contents of the Data Buffer are transferred to core memory. After completion of the transfer, the data Buffer is again considered empty.

# 4.6 RECEIVE MODE CONTROL LOGIC

This section contains a description of events which occur within the Receive Mode control logic during a data transfer operation. Most of the logic described in this section appears on Drawing M8506-0-01 (Sheet 2 of 5).

# 4.6.1 The Registers And The Counter

When in Receive Mode, the DQS11 bases its internal timing on Circuit DD-Receiver Signal Element Timing from the modem. The transition of Circuit DD from ON to OFF indicates the center of each signal element on Circuit BB-Received Data. The following operations occur on this clock edge:

- a. The contents of the shift register are shifted one bit to the right. Received data provides the input to NSR07. NSR00 provides the input to NSR15.

- b. The content of NSR00 is shifted into the CRC register if state flip-flop CRC ON is set and state flip-flop CRC INH is clear.

- c. The divide by eight counter is held equal to zero until two consecutive SYN characters are received. When the first, or least significant bit of the next character is received, the counter is incremented to one and CNTR1 is asserted. After the eighth or most significant bit has been received the counter equals zero and CNTR 0 is asserted.

# 4.6.2 State Flip-Flops Strobed After Every Bit

The transition of Circuit DD from OFF to ON is used by the DQS11 to strobe the following state flip-flops:

a. INSYNC is strobed set when both shift register bytes contain SYN characters. It is forced clear either by SET RDY or by RX bit clear.

- b. When LDDB is set, both shift register bytes are transferred into the Data Buffer.

LDDB is strobed set when the following conditions are met:

CNTRO is asserted, indicating that the shift register contains two complete characters; DBEMP (Data Buffer Empty) is set; DBTAK is set; DATDIS is not asserted indicating that the character destined for the data buffers low byte (DB07-00) is part of the message.

- c. When LDHB is set, shift register byte NSR07-00 is transferred to the high data buffer byte (DB15-08). LDHB is strobed set when the following conditions are met: CNTRO is asserted; DBEMP (Data Buffer Empty) is clear; DBTAK is clear, indicating that the Data Buffer is only half full; DATDIS is asserted, indicating that the character which was sent to DB15-08 during the last transfer is not part of the message and should be replaced by the next character which is now in NSR07-00.

- d. DMAFLR (Receive Mode DMA Failure) is strobed set when the following conditions are met: CNTRO is asserted; DBEMP (Data Buffer Empty) is clear; DBTAK is set, indicating (with DBEMP Clear) that the Data Buffer is completely full and should have been transferred to memory, setting DBEMP; DATDIS is not asserted, indicating that data is available for transfer to the data buffer.

# 4.6.3 State Flip-Flops Strobed By TOGCND

When the transition of Circuit DD from OFF to ON is gated by CNTR 0, it becomes the leading edge of TOGCND which strobes the state flip-flops whose states depend on the identity of the last character received. The control characters are decoded from shift register byte NSR07-00, which contains the entire character when CNTR 0 is asserted. The following state flip-flops are strobed by TOG CND:

- a. DLESTR, STXSOH, CRCON, TRNSP, and CRCINH state flip-flops function as described in Section 4.4.2.

- b. If RFC (Ready For Control Character) is asserted and if END CHR is asserted (indicating that a correct non-CRC termination is present), then STREC is strobed set.

- c. If RFC is asserted and if the present character is either ETX or ETB, then STP1 is strobed set, beginning the CRC termination sequence. With each successive TOG

CND, the state of STP1 is strobed into STP2 and the state of STP2 is strobed into STP3.

- d. DATENB is strobed set if INSYNC has been set, if a message terminator has not yet been recognized, and if the character is NSR07-00 is not a control SYN character. The character is then shifted into NSR 15-08 and is accepted as part of the message if DATENB is set and if it is not a transparent mode control DLE character followed by either a data DLE or a control SYN character.

- e. FINRCV (Finish Receive) is strobed set if STP1 is set, if STREC is set, or if FINRCV has already been set.

- f. DONER is strobed set by the trailing edge of TOGCND if FINRCV was set by the leading edge. If DONER and DBEMP are both set and if CRCIP (CRC in process) is not asserted, RDY is set.

# 4.6.4 Control Of Parallel Data Flow

The Control of parallel data flow depends on the following four state flip-flops on the M8506 Control Card.

- a. LDDB and LDHB are described in Section 4.6.2.

- b. DBEMP is set either by a software initiated GO Command or by the completion of an NPR data transfer from the Data Buffer to core memory. It is cleared when DBTAK is cleared, indicating that the data buffer is half full.

- c. DBTAK is set at the start of Receive Mode operation and remains set until data is transferred to the Data Buffer. DBTAK is strobed clear by TOG CND whenever LDDB or LDHB are being set. DBTAK clear indicates that the Data Buffer is half full. When the Data Buffer contains two valid message characters, DBTAK is strobed set, initiating an NPR data transfer from the Data Buffer to core memory.

# SECTION 5 MAINTENANCE

## 5.1 SPECIAL TEST EQUIPMENT

No special test equipment is required for maintaining the DQS11.

#### **5.2 MAINTENANCE TECHNIQUES**

Maintenance procedures are based primarily on the DQS11-A and DQS11-B diagnostics described in Appendix A. These diagnostics not only isolate and describe individual failures, but can be caused to loop on any particular test for use with an oscilloscope. An additional feature allows the technician to step through the simulated transmission or reception of data on a bit-by-bit basis.

The DQS11-A and DQS11-B Modem Exercisers are described in Appendix B. Assuming the diagnostic runs correctly, problems uncovered by the Modem Exerciser will probably be traced to the level converter card (M594 or M595), the logic and signal paths leading directly to or from that card, or the modem and modem connections.

## SECTION 6 MODULE LIST

# 6.1 MODULES

Table 6-1 lists the DQS11 modules by type number, function, and system unit slot location.

| DEC Type No. | Function                   | Slot Location |

|--------------|----------------------------|---------------|

| G8000        | +8V Filter                 | A02           |

| M105         | Address Selector           | B02           |

| M594*        | EIA Voltage Converter      | D04           |

| M595*        | Current Level Converter    | D04           |

| M7821        | Interrupt Control          | B03           |

| M785         | Unibus Transceiver         | C03           |

| M785         | Unibus Transceiver         | D03           |

| M795         | Word Count And Bus Address | EF03          |

| M796         | Unibus Master Control      | E04           |

| M8504†       | DQS11-A Register Card      | CDEF01        |

| M8505†       | DQS11–B Register Card      | DCEF01        |

| M8506        | DQS11 Control Card         | CDEF02        |

Table 6–1 DQS11 Module Complement

\*DQS11 system unit slot D04 contains an M594 for interfacing modems which feature EIA voltage signals or an M595 for interfacing modems which feature current signals. †DQS11-A system unit slots CDEF01 receive the M8504 Register Card. DQS11-B system unit slots CDEF01 receive the M8505 Register Card.