EK-M8207-TM-002

# M8207 Microprocessor Technical Manual

EK-M8207-TM-002

# M8207 Microprocessor Technical Manual

Prepared by Educational Services of Digital Equipment Corporation

#### 1st Edition, May 1979 2nd Edition (Rev), November, 1982

Copyright <sup>©</sup> 1979, 1982 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

#### Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS |

|---------|--------------|---------|

| DEC     | DECSYSTEM-20 | OMNIBUS |

| PDP     | DIBOL        | OS/8    |

| DECUS   | EDUSYSTEM    | RSTS    |

| UNIBUS  | VAX          | RSX     |

|         | VMS          | IAS     |

## **CONTENTS**

## PREFACE

| CHAPTER 1  | INTRODUCTION                              |

|------------|-------------------------------------------|

| 1.1        | PURPOSE1-1                                |

| 1.2        | DESCRIPTION 1-1                           |

| 1.3        | M8207 BASIC CONTROLLING ELEMENTS          |

| 1.4        | MAJOR FUNCTIONAL AREAS                    |

| 1.5        | MICROPROCESSOR FEATURES                   |

|            |                                           |

| CHAPTER 2  | TECHNICAL DESCRIPTION                     |

| 2.1        | SCOPE                                     |

| 2.2        | TIMING                                    |

| 2.3        | CONTROL ROM AND INSTRUCTION REGISTER      |

| 2.4        | SOURCE ROM AND DATA MULTIPLEXER           |

| 2.5        | ARITHMETIC LOGIC UNIT SCRATCHPAD AND      |

|            | FUNCTION ROM                              |

| 2.6        | MULTIPORT RAM                             |

| 2.7        | DATA MEMORY                               |

| 2.8        | PROGRAM COUNTER                           |

| 2.9        | NPR AND MISCELLANEOUS REGISTERS           |

| 2.9.1      | Microprocessor NPR Control Register       |

| 2.9.2      | Microprocessor Miscellaneous Register     |

| 2.10       | BERG PORT                                 |

| 2.11       | BRANCH CONTROL                            |

| 2.12       | BRANCH REGISTER                           |

| 2.12       | DESTINATION ROM                           |

| 2.13       | CONTROL AND STATUS REGISTERS              |

| 2.17       |                                           |

| CHAPTER 3  | SERVICE                                   |

| 3.1        | SCOPE                                     |

| 3.2        | MAINTENANCE PHILOSOPHY                    |

| 3.2.1      | Preventive Maintenance                    |

| 3.2.2      | Corrective Maintenance                    |

| 3.3        | MICROPROCESSOR USE WITH LINE UNIT         |

| 3.4        | LINE UNIT PORT CABLE CONSIDERATION        |

| 3.5        | M8207 LINE UNIT PORT                      |

| 3.6        | MICRODIAGNOSTICS                          |

| 3.7        | ROM REPLACEMENT                           |

| APPENDIX A | MICRODIAGNOSTIC TESTS                     |

| APPENDIX B | INTEGRATED CIRCUIT DESCRIPTIONS           |

|            | INTEGRATED CIRCOTT DESCRIPTIONS           |

| APPENDIX C | M8207 MICROPROCESSOR JUMPER CONFIGURATION |

## **CONTENTS** (Cont)

### GLOSSARY

## INDEX

## **FIGURES**

## Figure No.

## Title

## Page

| 1-1  | Microprocessor Simplified Block Diagram            | . 1-3 |

|------|----------------------------------------------------|-------|

| 2-1  | Microprocessor                                     | .2-2  |

| 2-2  | System Clock                                       | .2-5  |

| 2-3  | Main Timing Chain                                  | .2-7  |

| 2-4  | Control ROM, Maintenance and Instruction Registers | .2-8  |

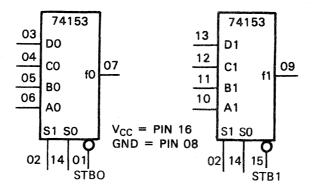

| 2-5  | Source ROM and DMUX                                | 2-10  |

| 2-6  | ALU, Scratchpad, and Function ROM                  | 2-11  |

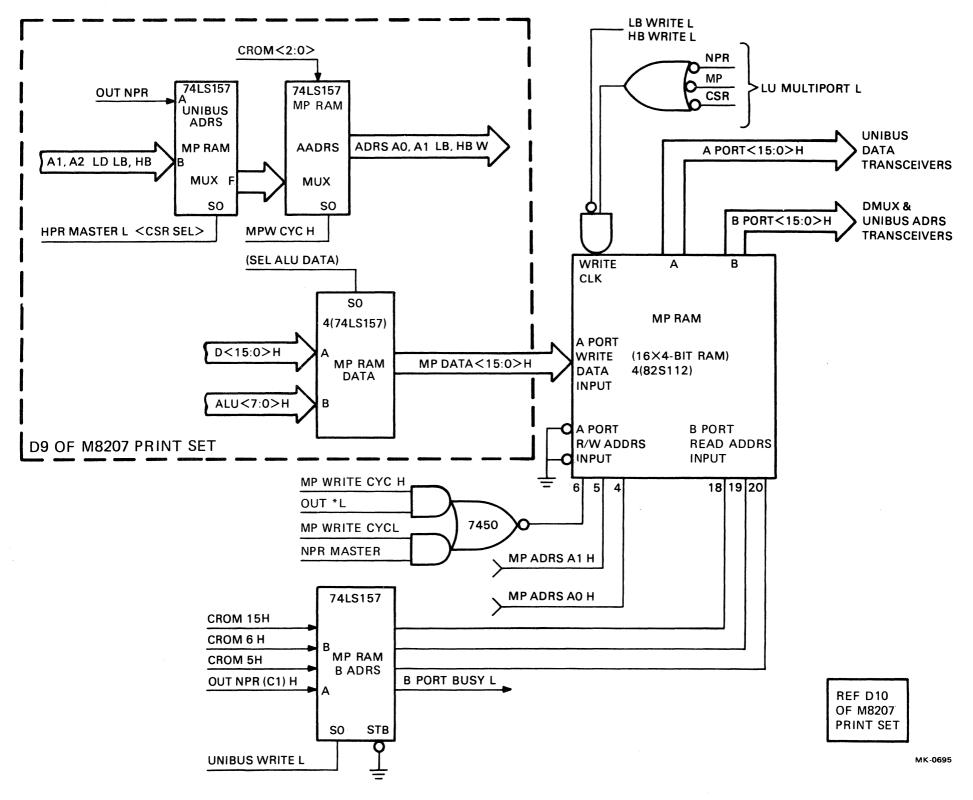

| 2-7  | Multiport RAM                                      | 2-13  |

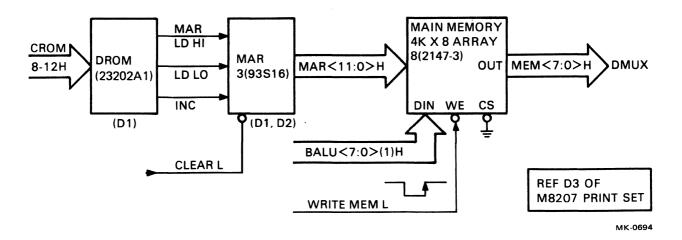

| 2-8  | Data Memory                                        |       |

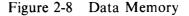

| 2-9  | Program Counter                                    | 2-15  |

| 2-10 | Interrupt and NPR Control                          |       |

| 2-11 | Miscellaneous Registers                            | 2-18  |

| 2-12 | Timing Through BERG Port                           | 2-21  |

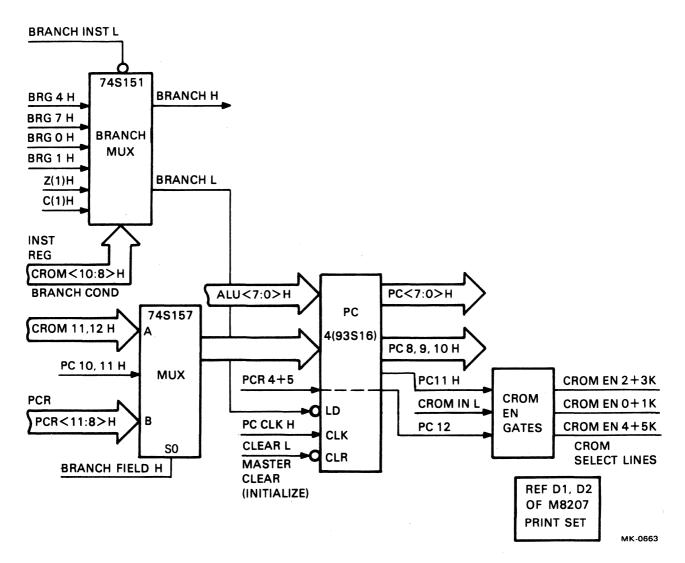

| 2-13 | Branch Control Logic                               |       |

| 2-14 | Branch Register                                    | 2-24  |

| 2-15 | Destination ROM                                    |       |

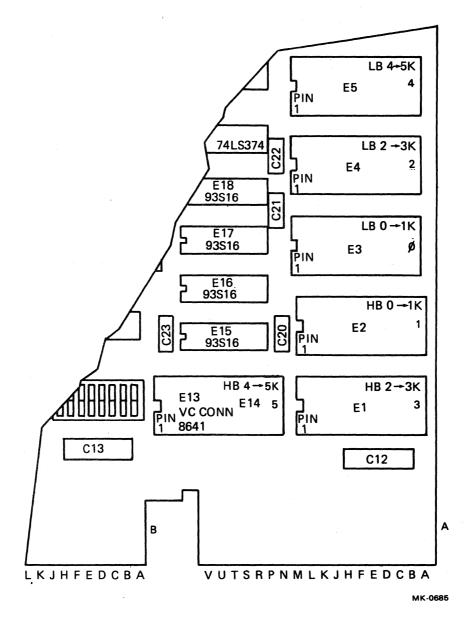

| 3-1  | Extract of M8207 Module Component Layout           |       |

| C-1  | M8207 Microprocessor Jumper Locations              | C-1   |

## **TABLES**

## Table No.

## Title

## Page

| 1-1 | Microprocessor Features | 1-6 |

|-----|-------------------------|-----|

| 2-1 | DMUX Select Input       |     |

| 3-1 | Chip Address Range      |     |

| C-1 | M8207 Jumper Chart      | C-1 |

## PREFACE

The *M8207 Technical Manual* describes the hardware portion of the processor operation. The information presented consists of a brief discussion of the purpose and features of the M8207, a technical description of circuit operation which includes key timing functions, and module level diagnostics. Appendix A contains Microdiagnostic Tests, Appendix B contains Integrated Circuit Descriptions, and Appendix C contains the M8207 microprocessor jumper configurations. A Glossary and an Index are also provided.

The following documents provide supplementary information.

- *M8207 Print Set* (D-CS-M8207-0-0)

- M8203 Technical Manual (EK-M8203-TM-001)

## CHAPTER 1 INTRODUCTION

#### **1.1 PURPOSE**

The M8207, a Direct Memory Access (DMA) device, is a UNIBUS compatible, general purpose microprocessor with Read Only Memory (ROM) control storage. Working as a parallel Input/Output (I/O) processor, the M8207 is used primarily to reduce I/O load on the Central Processing Unit (CPU), and therefore, functions more like a data handler than a data processor.

#### **1.2 DESCRIPTION**

The M8207 microprocessor is implemented on a single hex multilayer board and will operate in most hex SPC slots of a UNIBUS (DD11-B backplane cannot be used). The only power requirement is +5 Vdc.

The functions performed by the M8207 are determined by the microprogram contained in its instruction memory as specified by the microcode stored in the ROMs.

The architecture is based on a 16-bit instruction set. The M8207 cannot modify its own instruction area.

All communications between the microprocessor and external UNIBUS devices are accomplished through a Multiport Random Access Memory (MP RAM). An 8-bit port (BERG Port) allows the microprocessor to communicate with a line unit or other device without use of the UNIBUS.

M8207 features are outlined below.

- Instructions Located in 2-K by 16-bit ROM

- (increase to 6K in 2K increments) Length = 16-bits Time = 180 ns minimum except Branch True = 240 ns MP RAM Access ≥ 210 ns

- Programming ROMs perform an appropriate task

- Data Memory 4K- by 8-bits

- Scratchpad 16- by 8-bits

- Data Paths 8-bits wide

- Non-Processor Request Address 18-bits

- Interrupt Vector 2 (XX0 and XX4).

- Control and Status Register defined by the hardware 1 byte

- Control and Status Registers defined by microcode 7 bytes

- Arithmetic Logic Unit Functions 16

- Multiple Transfer per Non-Processor Request

- Program Timer 1 millisecond

- UNIBUS Transfer byte or word

- Read Program Counter and Memory Address Register

- Assert AC LO is jumper selectable

- BERG Port is compatible with M8200 and M8204

#### **1.3 M8207 BASIC CONTROLLING ELEMENTS**

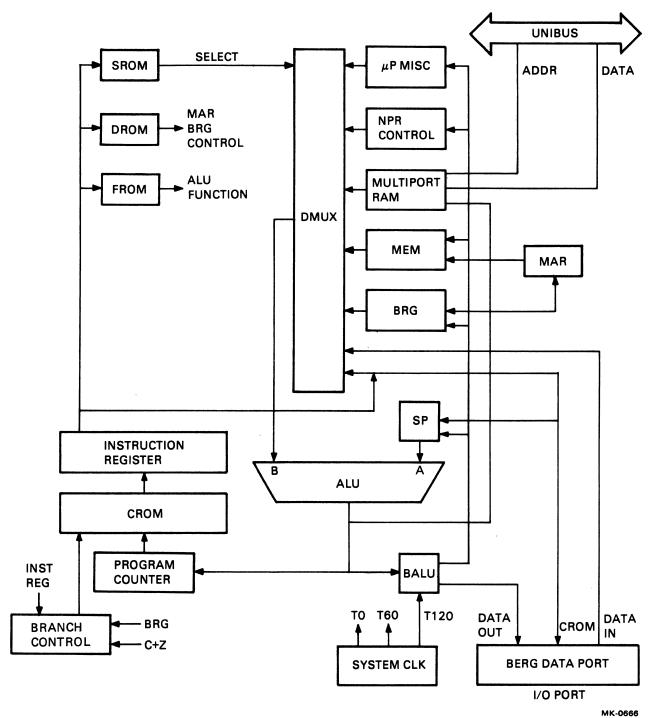

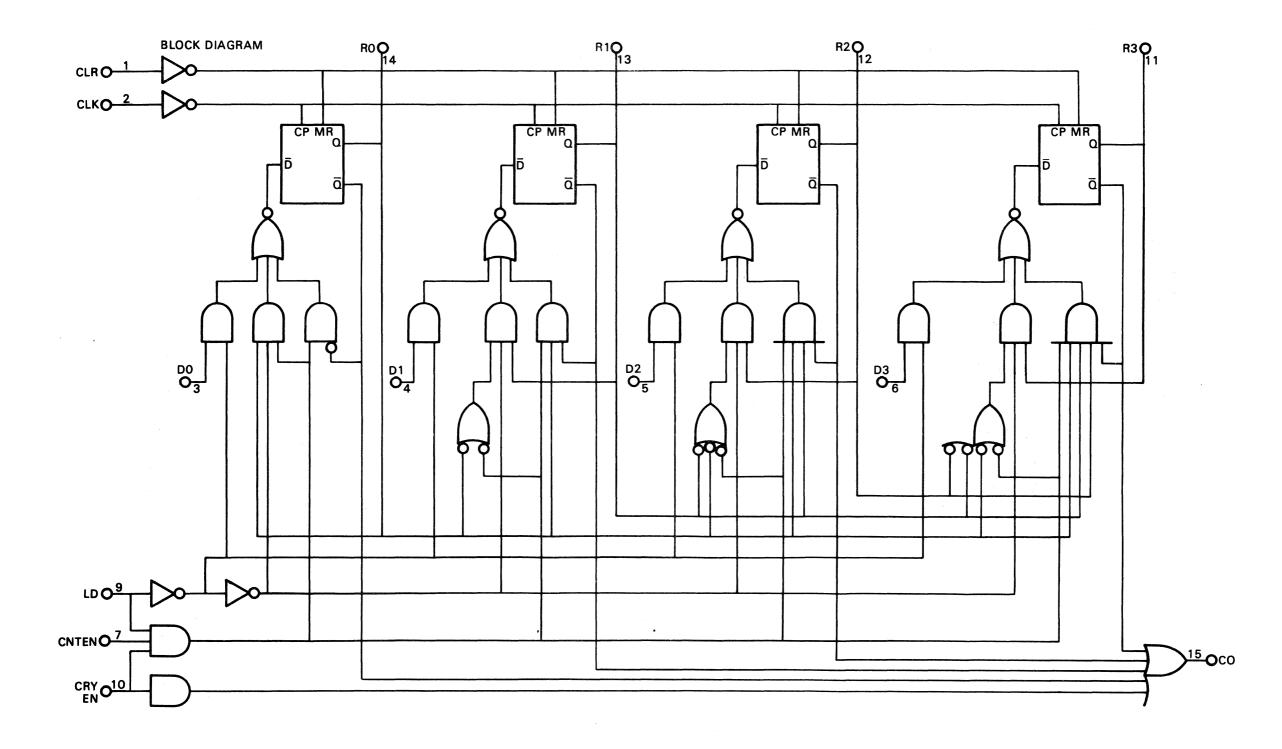

A simplified block diagram of the M8207 is shown in Figure 1-1. The block diagram identifies the basic controlling elements of the M8207 and shows the functional location of the microprocessor between the UNIBUS and its I/O Port. The M8207 I/O BERG Port interfaces with a line unit through a one foot cable.

The M8207 interfaces with the UNIBUS and performs DMA operations using Non-Processor Requests (NPRs) and interrupts (Bus Requests – BRs). Communication between CPU and the micro-processor's UNIBUS Control and Status Registers (CSRs) is done through Data In (DATI) transactions for reading and Data Out (DATO) or Data Out Byte (DATOB) transactions for writing.

#### **1.4 MAJOR FUNCTIONAL AREAS**

The major functional areas of the M8207 Microprocessor are:

#### Main Memory (MEM) and Memory Address Register (MAR)

The MEM is the M8207 data storage area consisting of a 4096 by 8-bit RAM. This area cannot be used for instruction storage nor can the stored data be executed as an instruction. The MEM cannot be accessed directly by the CPU.

The MAR is set up by the microprocessor to address the MEM.

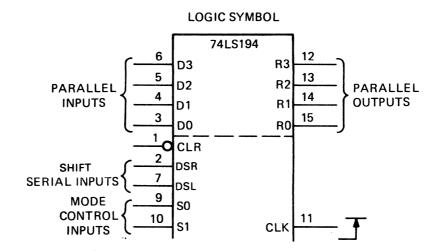

#### **Branch Register (BRG)**

The BRG is an 8-bit register used as a temporary data register for branch determination and for a rotate right operation. It has three modes of operation: load, shift right, and hold. Input data comes from the Buffered Arithmetic Logic Unit (BALU). During a right shift, only the BRGs most significant bit (bit 7) is sourced from BALU bit 0. Output data goes to the B input of the ALU via the Data Multiplexer (DMUX).

#### **Program Counter (PC)**

The PC is a 14-bit counter that can be parallel loaded from the ALU for the lower eight bits during a branch instruction, when the branch is true. The upper six bits are loaded from two sources: from the Program Counter Register (PCR – OUTBUS\* 13) on branch condition 0, or, on branch conditions 1 through 7, from bits 11 and 12 of the branch instruction for the page bits. The field bits are simply rewritten from the PC. The branch not true and the move instruction increment the PC. The output of the PC controls the address of the Control ROM directly.

Figure 1-1 Microprocessor Simplified Block Diagram

#### Control ROM (CROM), Instruction Register (IR), and Maintenance Instruction Register (MIR)

The M8207 uses up to a 6K- by 16-bit array of ROMs for the instruction memory. The CROM can be configured for 2K, 4K, or 6K with the 23XXXF4 PROM. The CROMs are addressed by the PC during execution of the previous instruction. At time state zero, the output of the ROMs are clocked into the IR. The outputs of the ROMs are wire-ORed with the outputs of the MIR. The MIR is used for loading a single microinstruction from the CPU (typically for maintenance purposes). Selection between the MIR and the ROMs is done by CSR 0, bit 9 (ROMI). When bit 9 is set, the MIR is selected. The MIR is loaded every time CSR 6 is loaded.

#### Data Multiplexer (DMUX) and Source ROM (SROM)

The DMUX is an 8-bit wide, 8-to-1 line multiplexer. Its 8-bit output goes to the B input of the ALU. Input selection for the DMUX is controlled by the SROM which is a 32- by 8-bit ROM. The SROM also determines if a move instruction is to be executed.

#### Scratchpad Memory (SP) and Addressing Multiplexer

The SP is a 16- by 8-bit read/write memory that is used for temporary storage of data. An operand can be presented to the A input of the ALU only through the SP. Scratchpad addressing is done through a multiplexer. During normal operation, the addressing is controlled by the lower four bits of the CROM. During an output transfer to the destination field OUT or OUT\* registers, SP address 0000 is automatically presented to the A input of the ALU.

#### Arithmetic Logic Unit (ALU) and Function ROM (FROM)

The ALU allows the microprocessor to perform arithmetic and logic operations on its A and B inputs. The FROM, which is a 32- by 8-bit ROM, controls up to 16 functions to be performed by the ALU. The carry output (C bit) of the ALU is connected to a flip-flop to store the carry indication if it occurs during a move, or if it is forced by the FROM.

The AB output (Z bit) of the ALU is connected to a flip-flop to store the indication of equality of the A and B inputs of the ALU if it occurs during a move instruction.

#### Multiport RAM (MP RAM) and Associated Logic

The Multiport RAM is a RAM that contains all the M8207 status registers except four: NPR Control, Miscellaneous, PC, and MAR registers. The Multiport RAM has two ports (A and B) that can be accessed simultaneously for a read operation; however, only the A port can be written into. The associated logic consists of read/write control and addressing multiplexers which allow access to the Multiport RAM by the microprocessor and the CPU. The Multiport RAM contains the CSRs that are accessible by both the M8207 and the CPU program. It also contains the NPR buffer pointers and NPR data that are accessible only by the M8207.

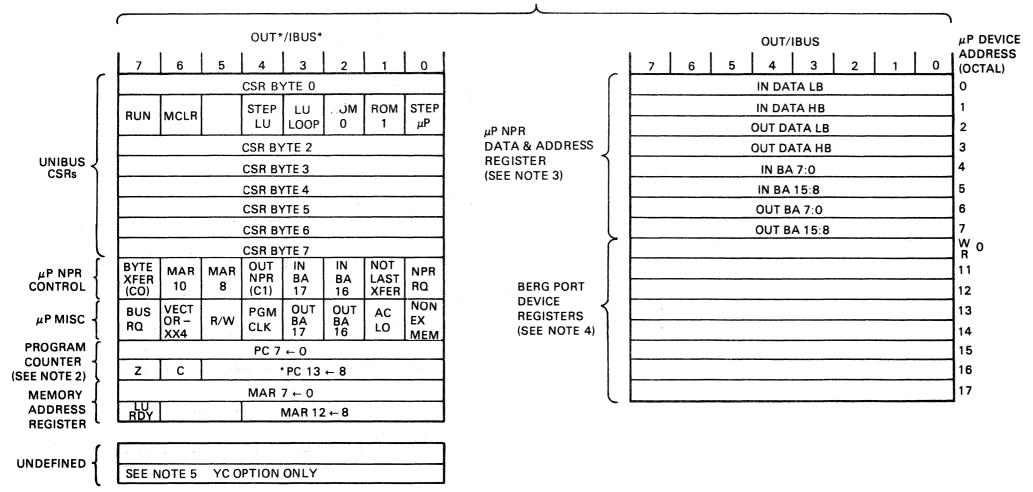

Microprocessor registers 0 through 7 of OUT/IBUS and OUT\*/IBUS\*, and CSR bytes 0 through 7 are implemented in the MP RAM.

#### NOTE

A write to CSR byte 1 sets and clears bits in internal controlling logic and MP RAM. A read from CSR 1 reads the RAM only.

#### System Clock

The clock provides clock pulses for the microprocessor. It generates a series of three nonoverlapping 60 ns time pulses for a time interval of 180 ns for branch instructions, condition not true, and move instructions that do not access the Multiport RAM. The branch true instruction delays T60 by 60 ns for an instruction time of 240 ns. The move instruction that accesses the Multiport RAM adds a minimum of 30 ns to the instruction time if the Multiport RAM is not being accessed by the processor. The 30 ns is extended for a processor write or an NPR in progress; the system clock is held up until the transfer is complete.

#### Non-Processor Request (NPR) and Control Logic

The control logic allows the microprocessor to initiate an NPR under microprogram control and assume UNIBUS mastership so that it can transfer data to or from the CPU memory. The not last transfer bit can be used to retain bus mastership for multiple DMA transfers.

#### **Interrupt Control Logic**

This logic allows the microprocessor to interrupt the CPU and cause vectoring to either of two locations in the floating vector address space. The vector address is switch selectable and occupies two consecutive vector locations: XX0 and XX4. The M8207 interrupt priority is plug selectable for level 4, 5, 6, or 7; however, it is normally shipped as a level 5 device.

#### **Address Selection Logic**

This logic consists of switches to specify the microprocessor device address plus logic to decode this address. Address selection logic also decodes the selected register and the type of UNIBUS transaction requested. Using these factors, the logic generates the appropriate control signals to implement a read or write operation as directed by the UNIBUS control lines.

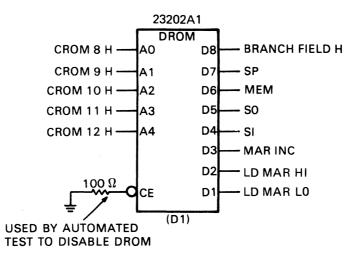

#### **Destination ROM (DROM) and D Decode**

DROM and D Decode are driven by the destination field of the microinstruction, and control the destination location of data in a move instruction.

#### NPR Control Register (Register 10) and Microprocessor Miscellaneous Register (Register 11)

These registers are used for M8207 general control and status. The bit functions are described in Chapter 2.

#### **Branch Control**

The branch control multiplexer is driven directly by the instruction register output bits CROM <10:8>. It is used for determining branch conditions.

#### **1.5 MICROPROCESSOR FEATURES**

Features of the M8207 provided in Paragraph 1.2 are compared with features of other microprocessors in Table 1-1.

| Function                                     | M8200                                    | M8207                                                               | (M8204)<br>KMC11-A                       | (M8206)*                                                            |

|----------------------------------------------|------------------------------------------|---------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------------|

| Instruction<br>Time                          | 300 ns min<br>except<br>MP RAM<br>330 ns | 180 ns min<br>except<br>Branch true<br>240 ns &<br>MP RAM<br>210 ns | 300 ns min<br>except<br>MP RAM<br>330 ns | 180 ns min<br>except<br>Branch true<br>240 ns &<br>MP RAM<br>210 ns |

| Instruction<br>Memory                        | $1 \mathrm{K} \times 16$                 | 6K × 16                                                             | $1 \mathrm{K} \times 16$                 | $4K \times 16$                                                      |

| Data Memory                                  | 256 	imes 8                              | $4K \times 8$                                                       | $1 \mathrm{K} \times 8$                  | $4K \times 8$                                                       |

| Instructions<br>in ROM                       | yes                                      | yes                                                                 | no                                       | no                                                                  |

| Instructions<br>in RAM                       | no                                       | no                                                                  | yes                                      | yes                                                                 |

| Multiple<br>Transfer per<br>NPR              | no                                       | yes                                                                 | yes                                      | yes                                                                 |

| Program<br>Timer                             | 1 ms                                     | 1 ms                                                                | 50 µs                                    | 50 µs                                                               |

| Load PC                                      | no                                       | no                                                                  | no                                       | yes                                                                 |

| Read PC<br>(Host)                            | no                                       | yes                                                                 | no                                       | yes                                                                 |

| Read MAR                                     | no                                       | yes                                                                 | no                                       | yes                                                                 |

| Assert AC LO                                 | yes                                      | selectable                                                          | yes                                      | selectable                                                          |

| Load MAR HI                                  | no                                       | yes                                                                 | yes                                      | yes                                                                 |

| Latch of no<br>IBUS* 12-15<br>in Maintenance |                                          | no                                                                  | no                                       | yes                                                                 |

| IBUS* 12-15                                  | no                                       | yes                                                                 | no                                       | yes                                                                 |

| LU Stop CLK                                  | no                                       | yes                                                                 | no                                       | yes                                                                 |

| Power                                        | +5 V @7 A                                | +5 V @7 A                                                           | +5 V @7 A                                | +5 V @7 A                                                           |

## Table 1-1 Microprocessor Features

\*M8206 is a CSS special programming module for the M8207.

## CHAPTER 2 TECHNICAL DESCRIPTION

#### 2.1 SCOPE

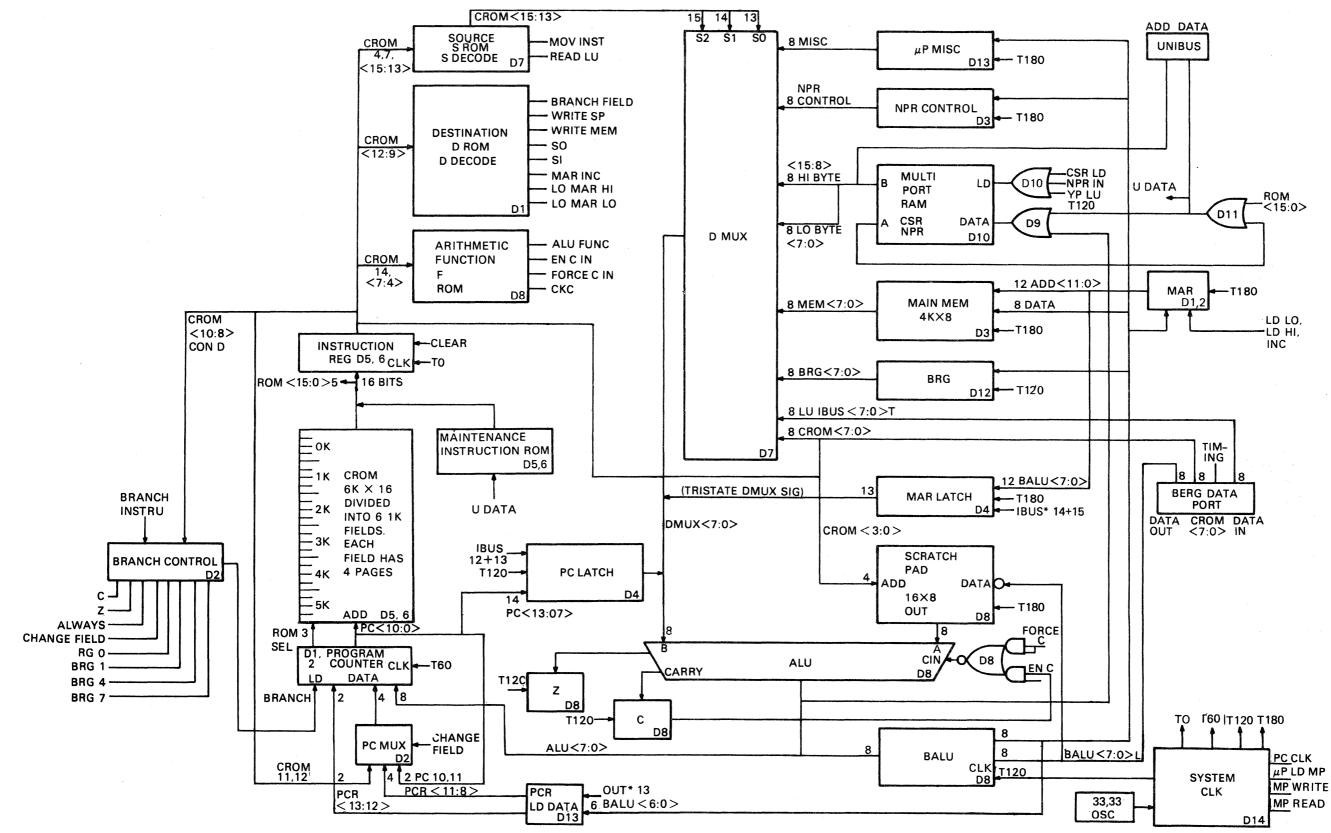

The technical description is addressed to circuit operation on a functional level. Logic block diagrams are included to supplement the text, and reference to the *M8207 Print Set* is made throughout the chapter. The block diagram of Figure 2-1 (Sheet 1) shows the major interconnections between the basic controlling elements of the microprocessor. A map of the Control and Status Registers (CSRs), is provided in Figure 2-1 (Sheets 2 and 3). Detailed descriptions of the area represented in Figure 2-1 constitute the following sections of this chapter.

#### NOTE

#### Dx references in the text are based on the signal map rather than the actual sheet numbers of the Print Set.

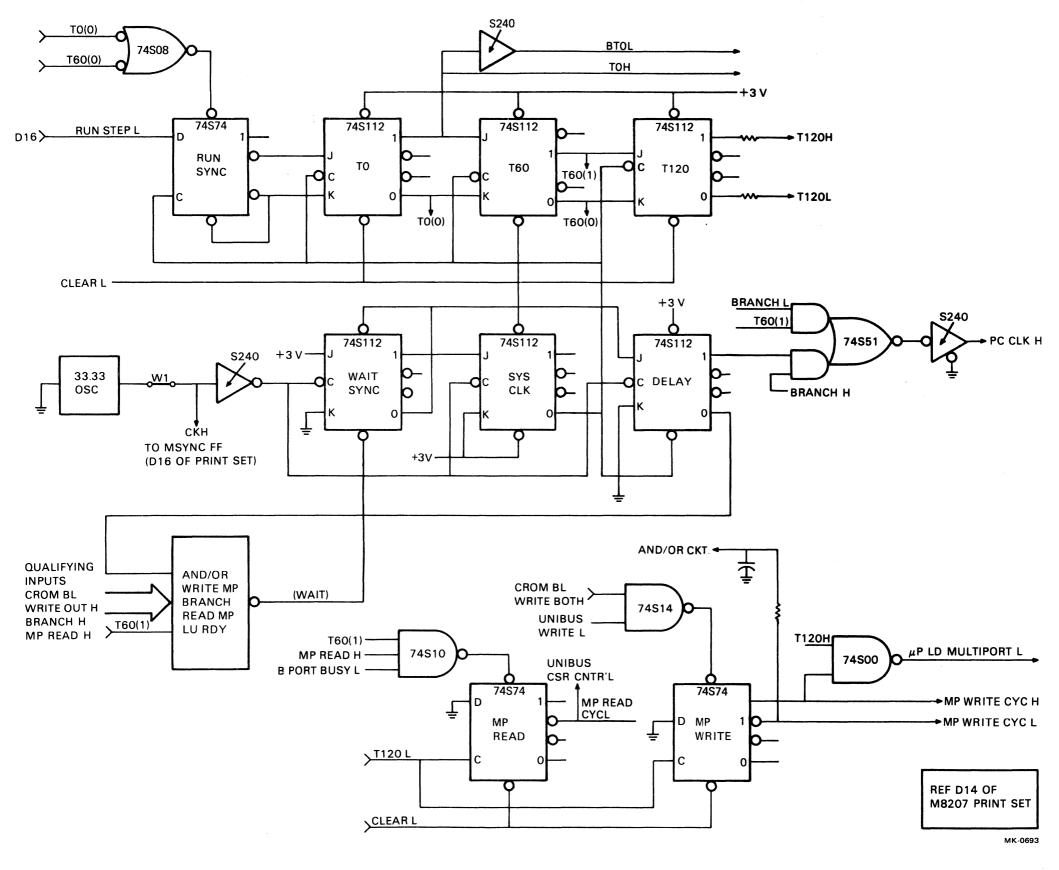

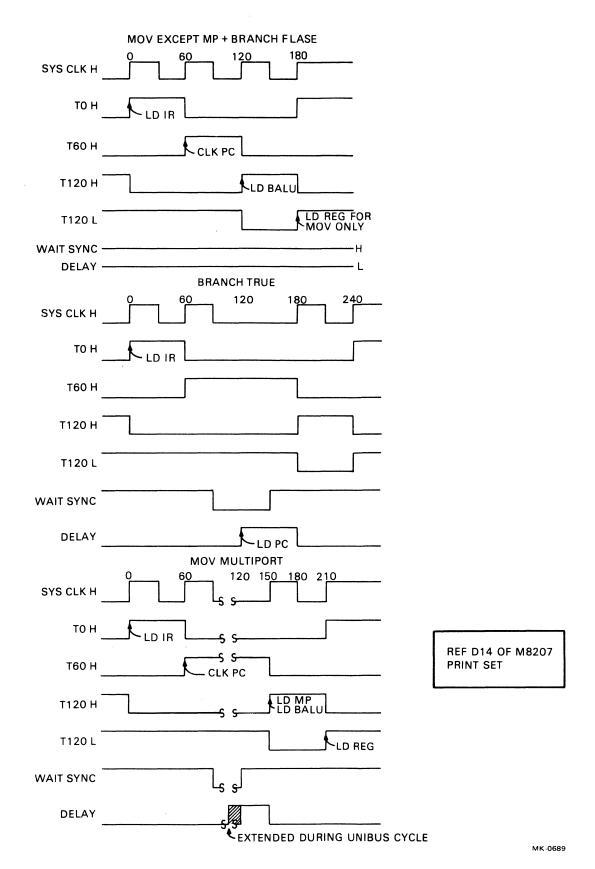

#### 2.2 TIMING (Figure 2-2)

The basic timing is generated by a 33.33 MHz crystal that can be disabled by removing jumper W1 to accommodate automated circuit board testers. The crystal output provides the clock input to the MSYNC flip-flop (D16 of Print Set) and buffered clock inputs, via a 74S240 inverter, to the WAIT SYNC, SYSTEM CLOCK (SYS CLK), and DELAY flip-flops.

The SYS CLK flip-flop:

- is used to generate the 60 ns timing pulses for the timing chain.

- is only held clear when the WAIT SYNC flip-flop is clear or in a wait state.

- is held set during a master clear.

- clear and K inputs are tied to +3 volts.

- J input comes from the output of the WAIT SYNC flip-flop.

- output is used to drive the clocks of the RUN SYNC, T0, T60, and T120 flip-flops.

The WAIT SYNC flip-flop:

• is used to eliminate timing problems when the wait signal goes away too close to the clocking edge of the system clock.

Figure 2-1 Microprocessor (Sheet 1 of 3) a. Interconnection Between Controlling Elements

2-2

MK-0692

| RESS |

|------|

|      |

|      |

|      |

|      |

| -    |

#### UNIBUS CONTROL AND STATUS REGISTERS

ROM

MK-0691

6

Figure 2-1 Microprocessor (Sheet 2 of 3) b. UNIBUS Control and Status Registers

#### μP & LU CONTROL & STATUS REGISTERS

NOTES

- 1. UNIBUS CSRs ARE IN THE MULTIPORT RAM. BYTE 1 HAS A HARDWARE STATUS REGISTER THAT IS ADDRESSABLE ONLY FROM THE WNIBUS. IF THE µP ADDRESSES BYTE 1, IT WILL ONLY WRITE INTO THE RAM. ALL THE OTHER CSR BYTES ARE DEFINED BY THE MICROCODE EXCEPT IN MAINTENANCE MODE.

- 2. IBUS\* 12-15 REFLECT THE PROGRAM COUNTER FOR THE INSTRUCTION BEING EX-ECUTED AND THE MEMORY ADDRESS REGISTER FOR THE PREVIOUS INSTRUCTION. OUT\*13 IS THE PCR WHICH IS A SHADOW REGISTER. THE CONTENTS OF THE PCR WILL BE TRANSFERRED TO THE PC ONLY ON A BRANCH (CHANGE FIELD).

- 3. NPR DATA AND BA REGISTERS ARE RAMs; HOWEVER, ADDRESS ASSIGNMENTS ARE HARDWIRED AND CANNOT BE REDEFINED.

- 4. OPTIONAL THESE REGISTERS ARE ONLY VALID IF EXTERNAL DEVICES ARE AT-TACHED TO THE BERG PORT

- 5. OPTIONAL YC ONLY FOR 22 BIT NPR ADDRESS

MK-0664

Figure 2-1 Microprocessor (Sheet 3 of 3) c. Microprocessor and Line Unit Control

Figure 2-2 System Clock

The RUN SYNC flip-flop:

- is used to sync the transition of run or step to the system clock to eliminate race conditions.

- is a 74S74 flip-flop whose data input is low true when either the run or step function is true.

- is clocked clear to enable the start of the main timing chain.

#### Main Timing Chain (Figures 2-2 and 2-3)

Both high and low outputs of the RUN SYNC flip-flop go to T0s inputs. Once clocked clear, RUN SYNC is latched clear until it is set by a negative OR on its preset side during time states T0 and T60. Data input to the RUN SYNC flip-flop must then be true low during T120 in order to reset RUN SYNC for the next instruction.

The preset side of the time state flip-flops are tied to +3 volts. This ensures that all time states are not true at the same time. The clear side of all time states are common to the CLEAR L signal from the UNIBUS. The timing chain is cleared and restarted on a master clear or power up.

- <u>T0</u> T0 is used to start an instruction. The high output from T0 clocks the Instruction Register (IR) and the line unit, or option, connected to the BERG Connector. Both outputs from T0 are input to T60 so that the next clock will generate the next time state.

- <u>T60</u> T60 is clocked on the trailing edge of T0. T0 is always 60 ns long. However, T60 is delayed by a wait during a branch true or move instruction using the Multiport RAM (line unit WAIT L when the line unit is addressed and is not ready). The high output from T60 is used to increment the Program Counter (PC) when branch is not true, and to generate the wait pulse. During this time period, the instruction has been decoded, the arithmetic function has been executed, and execution of the instruction has started. Both outputs from T60 are input to T120.

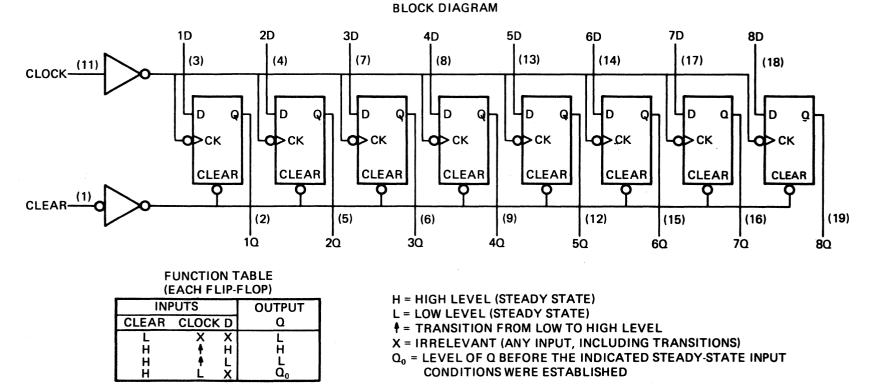

- <u>T120</u> The next clock sT120. The leading edge of T120 is used to clock data out of the Arithmetic Logic Unit (ALU). The source and arithmetic functions are complete at this time; normally 120 ns from the beginning of the instruction. The trailing edge of T120 loads all the registers and memories with data from the Buffered ALU (BALU). The exception is the Multiport RAM which is loaded on the leading edge from the ALU.

During T120, the RUN SYNC flip-flop is allowed to reset for the next instruction. Both the leading and trailing edges of T120 are actually used to load all registers and memories on the board, except the PC. The PC is loaded by the DELAY flip-flop during a branch true, or incremented by the leading edge of T60. Gating for the PC clock is done with a 74S51 (D14 of Print Set).

The wait for the timing chain is defined through a 74S64, which is a 4-2-3-2 input AND-OR gate. The qualifying inputs are defined by the instruction and are qualified at the leading edge of T60. The four qualifying conditions are:

- Line unit not ready to be read

- Branch true

- Read to the Multiport RAM

- Write to the Multiport RAM

The wait output is sync'd with the system clock through the WAIT SYNC flip-flop.

Figure 2-3 Main Timing Chain

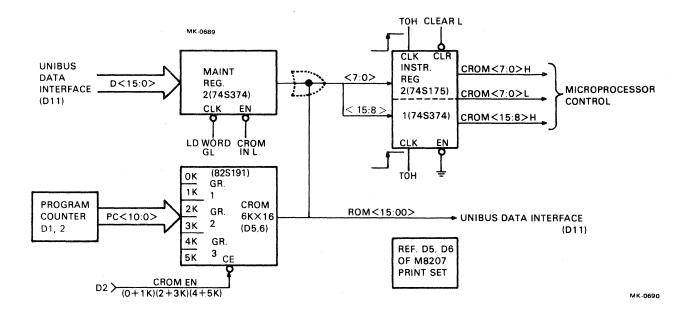

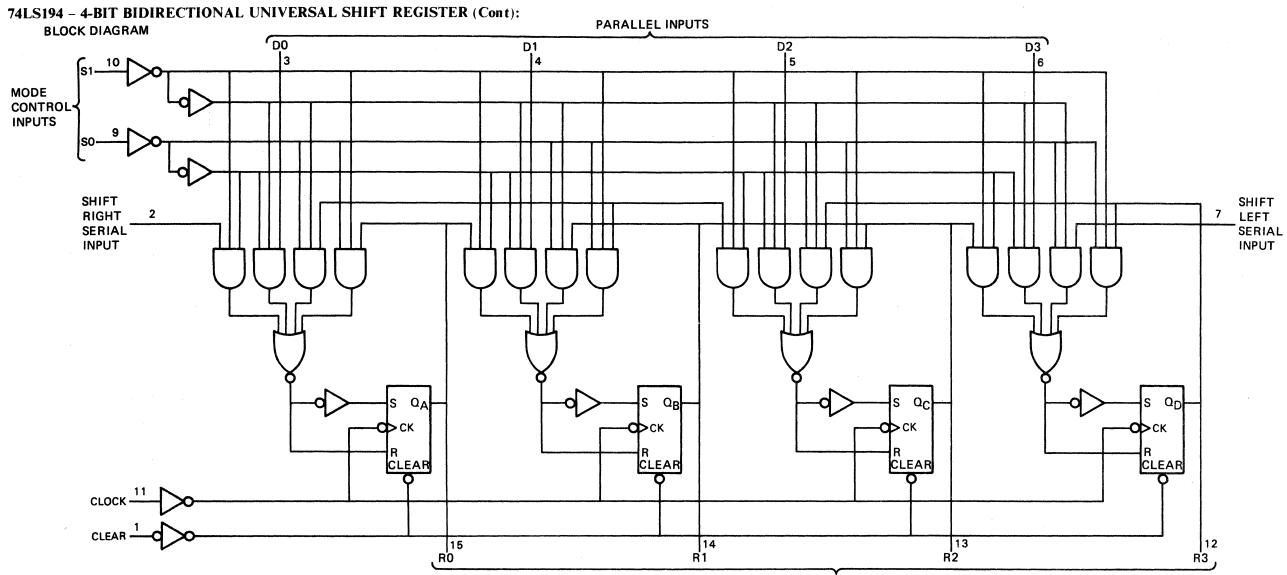

#### 2.3 CONTROL ROM (CROM) AND INSTRUCTION REGISTER (IR) (Figure 2-4)

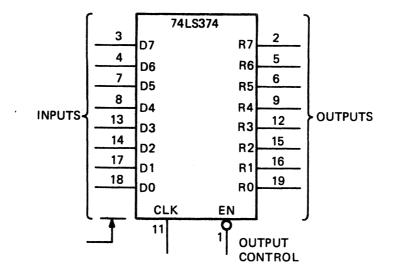

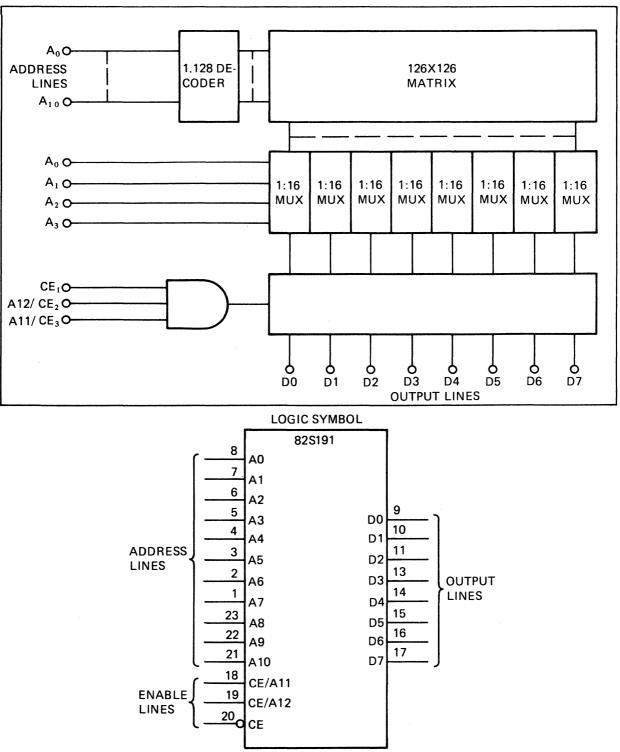

CROM consists of up to six 2K- by 8-bit (82S191) high speed ROMs. The ROMs are broken up into two groups of 2K each, whose address is controlled by the PC. The groups are selected and deselected via three 74S00 gates (D2 of Print Set). These gates are driven by the high order bits of the PC and the maintenance selection bit, CROMIN L, which is CSR 0 bit 9. When bit 9 is set, both sets of ROMs are disabled and the Maintenance Instruction Register (MIR) is selected, allowing an instruction to be loaded in CSR 6.

When loaded, CSR 6 loads bytes 6 and 7 of the Multiport RAM (D9 of Print Set) with data for the microprocessor and loads the 16-bit MIR consisting of two 74S374 octal tristate D flip-flops (D5 and D6 of Print Set). These flip-flops are selected during a maintenance instruction.

CROM and MIR outputs are wire-ORed to the IR; two 74S175s are input by the lower eight bits <7:0>, and a 74S374 octal D flip-flop is input by the upper eight bits <15:8>. The low outputs of the 74S175 are used by the BERG Port for address selection of LU IBUS and OUT registers.

The IR is clocked at the leading edge of T0; at the beginning of an instruction. The outputs of the IR are used to control the microprocessor. They are decoded for the following via respective ROMs.

- Type of instruction (Source ROM SROM)

- Function (Function ROM FROM)

- Destination (Destination ROM DROM)

CROM outputs directed to the Data Multiplexer (DMUX) are used during maintenance to verify the contents of the ROMs.

#### Figure 2-4 Control ROM, Maintenance and Instruction Registers

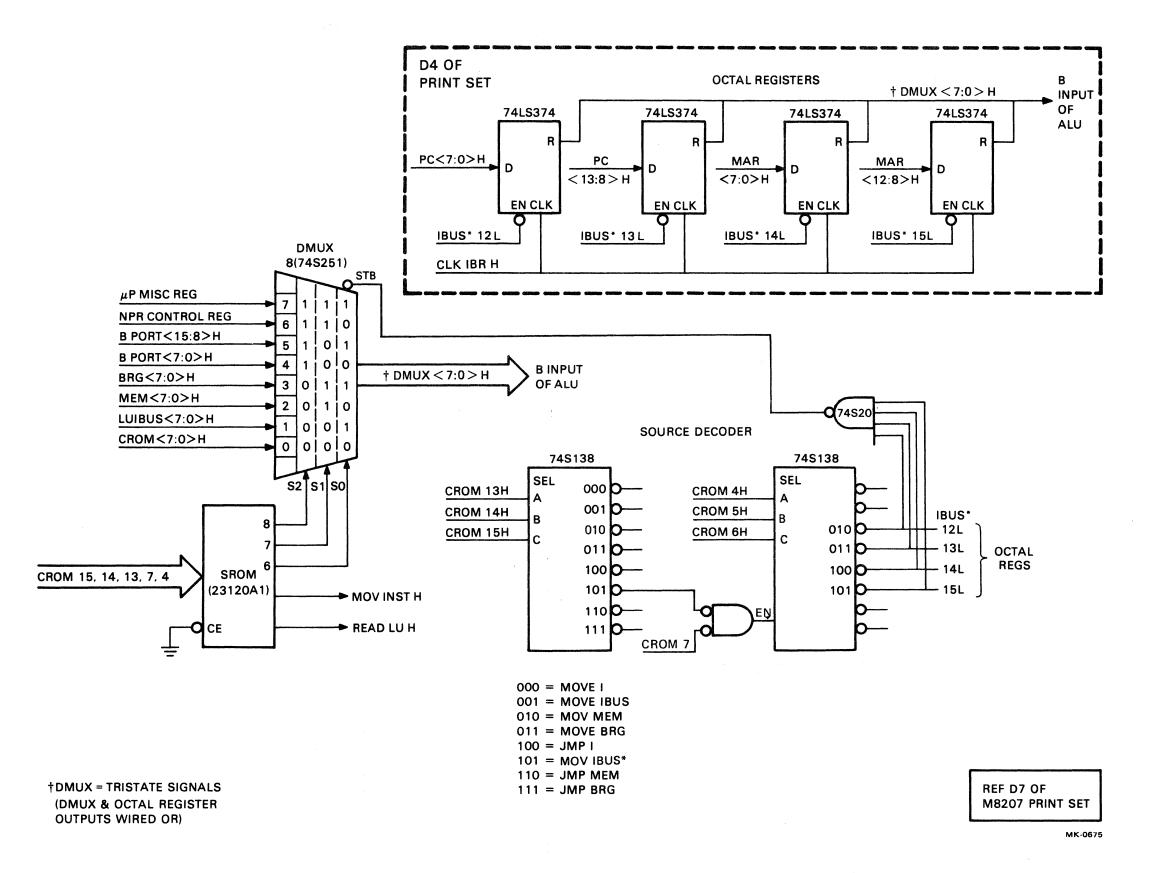

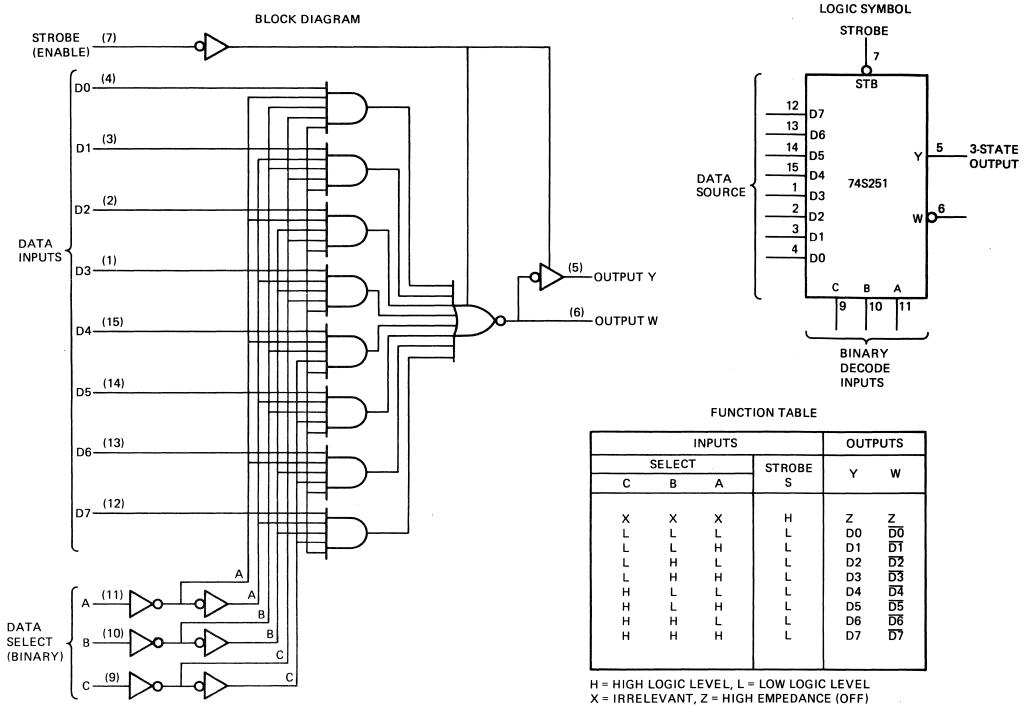

#### 2.4 SOURCE ROM (SROM) AND DATA MULTIPLEXER (DMUX) (Figure 2-5)

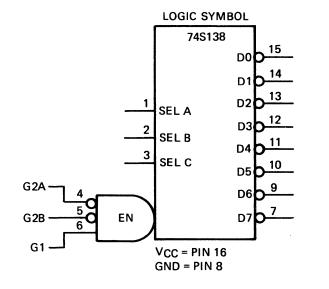

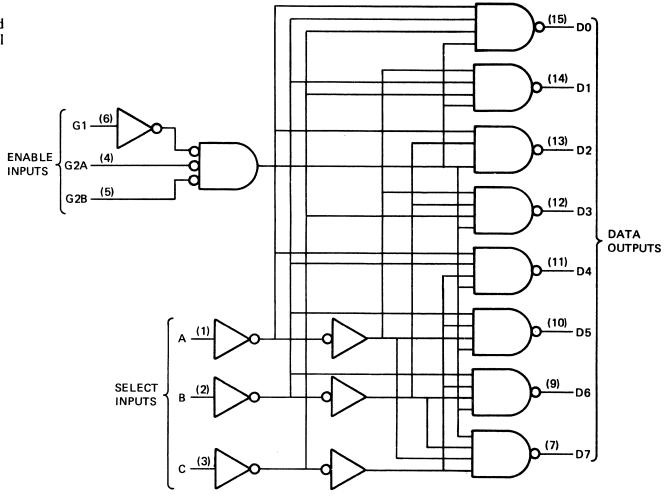

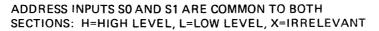

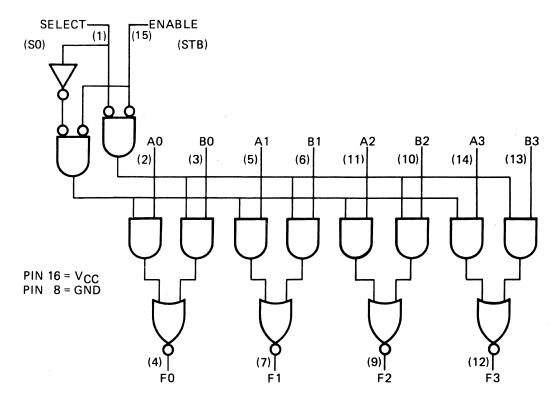

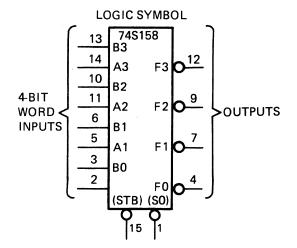

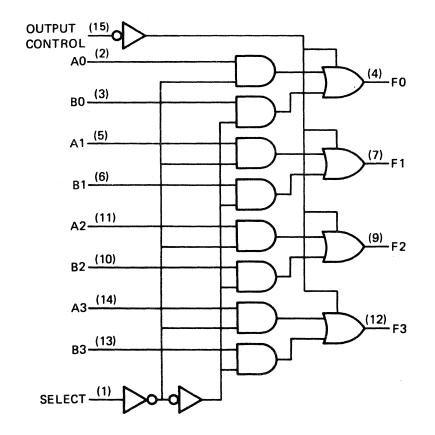

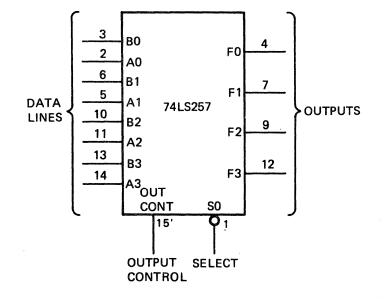

The DMUX consists of a tristate 8-to-1 multiplexer, and four octal tristate registers controlled by the SROM and the Source Decoder. SROM is a 32- by 8-bit (23120A1) ROM driven from instruction register CROM bits 4, 7, 13, 14, and 15, which define the instruction and its source. SROM is always enabled. Output bits 6, 7, and 8 are DMUX select inputs S0, S1, and S2 respectively.

| DMUX Select |    |    |     |                                             |                                                                                                                                        |

|-------------|----|----|-----|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| <b>S2</b>   | S1 | S0 |     | Data Selected                               | Definition                                                                                                                             |

| L           | L  | L  | (0) | CROM<7:0>H                                  | Immediate branch and move instructions                                                                                                 |

| L           | L  | н  | (1) | LU IBUS<7:0>H                               | Reads all ones if nothing is connected to the BERG Connector. There are $10_8$ addresses provided, usually from a MUX on the line unit |

| L           | н  | L  | (2) | MEM<7:0>H                                   | Location addressed by Memory Address Register                                                                                          |

| L<br>、      | н  | н  | (3) | BRG<7:0>H                                   | Single, 8-bit register used for shifting branch condi-<br>tions                                                                        |

| Н           | L  | L  | (4) | B PORT<7:0>H                                | From Multiport RAM                                                                                                                     |

| Η           | L  | н  | (5) | BPORT<15:8>H                                | IBUS and IBUS* registers for CSR and Non-Proces-<br>sor Request registers                                                              |

| Н           | н  | L  | (6) | NPR Control<br>Register                     | (See Paragraph 2.9)                                                                                                                    |

| Н           | Н  | Н  | (7) | Microprocessor<br>Miscellaneous<br>Register | Can only be accessed by the microprocessor (See Par-<br>agraph 2.9)                                                                    |

Table 2-1DMUX Select Input

Disabling the DMUX and selecting individual octal registers is accomplished through a 74S138 decoder. The decoder monitors the source and instruction register lines. The 74LS374 octal registers are clocked at the leading edge of T120. At this time the data in the registers are read from the PC and Memory Address Register (MAR).

The outputs of the octal registers are wire-ORed with the outputs of the DMUX and provide the B input to the ALU. Additional outputs from the SROM and Source Decoder are used by the timing and branch logic for control of the microprocessor.

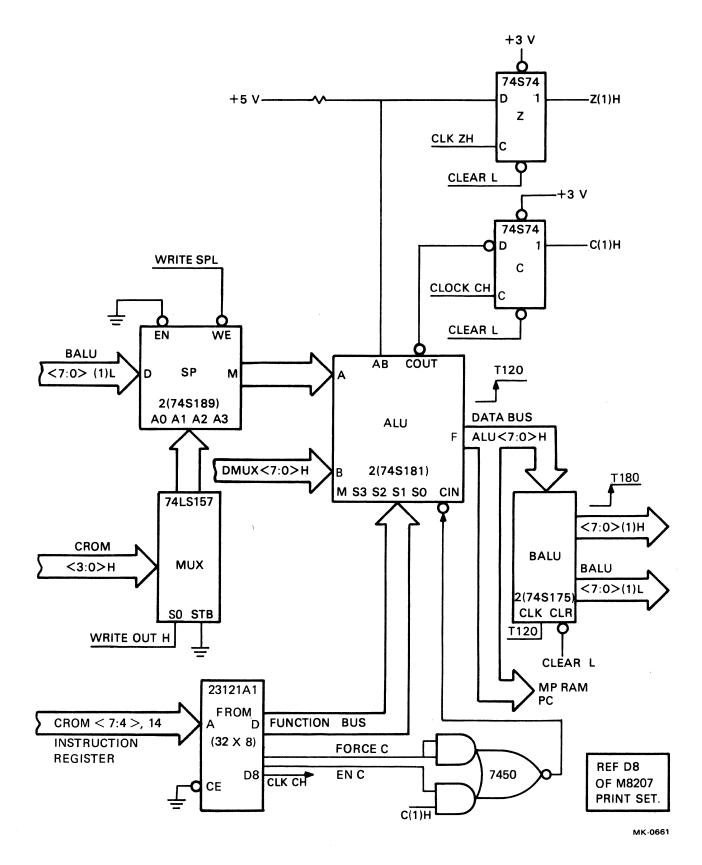

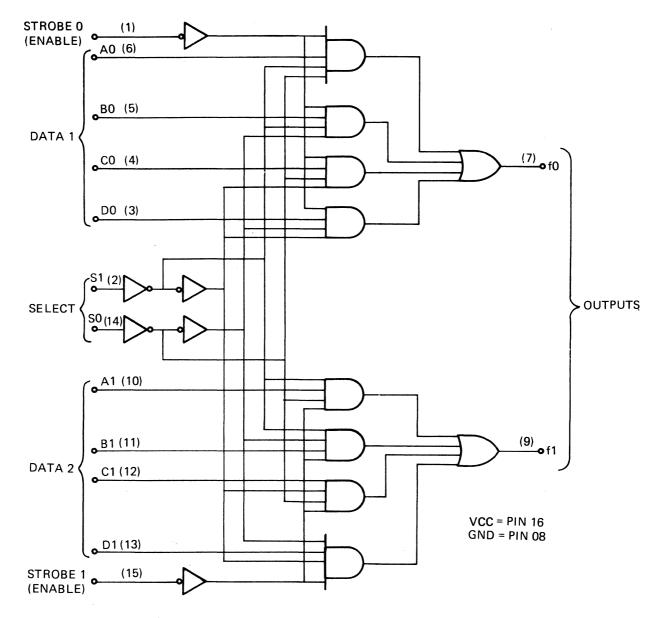

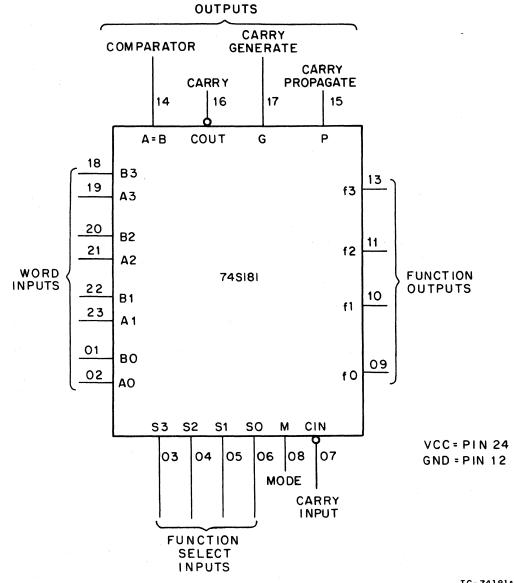

## **2.5** ARITHMETIC LOGIC UNIT (ALU), SCRATCHPAD (SP), AND FUNCTION ROM (FROM) (Figure 2-6)

The ALU consists of two 74S181 chips and performs arithmetic and logical operations on two designated operands; input A is the SP operand (scratchpad has 17 octal locations), and input B from the DMUX is the Main Memory (MEM) or Branch Register (BRG) source operand for move and branch instructions. A 5-bit function bus defines the type of operation to perform on the A and B operands and is gated into the ALU from the FROM. The FROM is a 32- by 8-bit ROM whose address lines, CROM 14, and <7:4> are from the IR.

#### Figure 2-5 Source ROM and DMUX

Figure 2-6 ALU, Scratchpad, and Function ROM

ALU functions are not allowed when bits 4 through 7 are used for address or data. The ALU then selects the B inputs only. The results of the operations performed by the ALU are sent to: (1) the BALU, (2) the DMUX for the Multiport RAM, and (3) the lower eight bits of the PC for branch instructions.

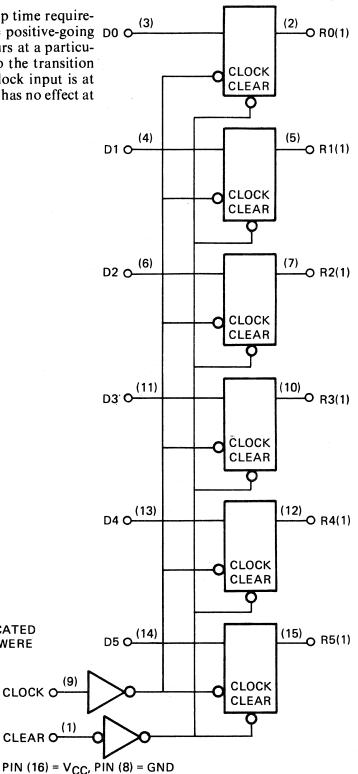

The BALU (two 74S175 quad D flip-flops with both high and low outputs) clocks data out of the ALU at T120. The output data from the BALU is clocked at T180 and provides input to the data memory, SP, BRG, Non-Processor Request (NPR) control, miscellaneous register, Program Counter Register (PCR), and the BERG Port. The BALU is clocked directly from the T120 flip-flop, and its clear input is generated by master clear or initialize.

The ALU chips are configured for a ripple carry that is clocked into flip-flop C, which is used in branch operations. The C flipflop is clocked by a 74S157 MUX, which provides the clock only on a move instruction and when the FROM output CK C H is true. This occurs at T120.

The AB output from the ALU is asserted when the ALU output data bus contains all ones. The AB outputs from each chip are wire-ORed and input to the Z flip-flop. The Z flip-flop is clocked at T120 on every move instruction. Both C and Z flip-flops are clocked from the same 74S157 MUX and cleared by master clear or initialize.

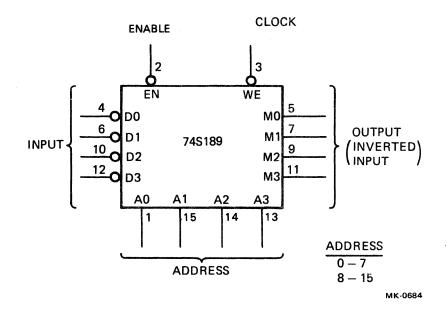

The ALU A operand is always generated at the SP (two 74S189 RAMs). The SP is addressed by CROM bits 0 to 3 via a 74LS157 MUX during all instructions except OUT and OUT\*, when the SP address is zero.

WRITE OUT H is asserted during an OUT or OUT\* operation. The SP is inverted so the low side of the BALU is used for data inputs (the RAM chips are always enabled). The SP is clocked from a 74S158 decoder MUX (D1 of Print Set), which selects the output of the DROM on a move instruction by loading the SP at T180.

#### 2.6 MULTIPORT RAM (Figure 2-7)

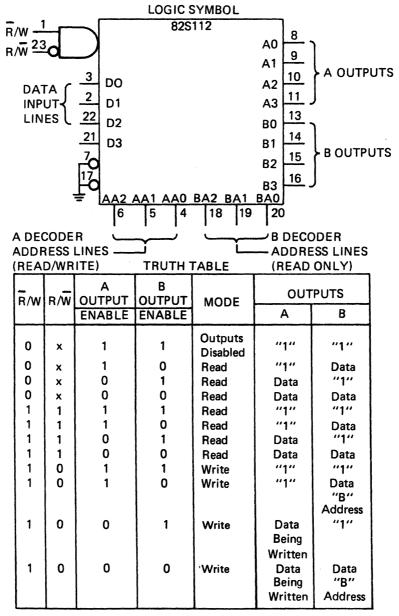

The Multiport RAM (82S112 chips) is a 16- by 4-bit random access memory that is the main interface between the processor and microprocessor. All data transferred from NPRs or through CSRs go through the Multiport RAM. Data can only be written through Port A, but can be read from ports A and B simultaneously. The read from ports A and B is disabled during the write time to avoid reading invalid data.

Addressing and data transfer is accomplished through 74LS157 Multiplexers. The microprocessor is able to read and write the registers. The NPR logic reads and writes half of the Multiport RAM and the Central Processing Unit (CPU) reads the other half.

Port A addressing goes through two levels of multiplexing. The first level is for control by the microprocessor or second multiplexer. The second level is for control by the CSR or NPR logic. This is acomplished by two 74LS157 MUXs. Selection control for the first MUX (MP RAM A ADDRS) is via the microprocessor MP WRITE CYCLE H signal (D14 of Print Set). The signal switches the address to the lower three bits of the instruction (CROM <2:0>), and selects the data address to be written from the ALU via the Multiport DMUX.

Figure 2-7 Multiport RAM

Control of the A Port address by the second MUX (UNIBUS ADRS MP RAM) occurs when the microprocessor is not attempting to write to the Multiport RAM. The UNIBUS ADRS MP RAM MUX is controlled by the NPR MASTER L signal. When the M8207 is bus master, bytes 0 + 1 or bytes 2 + 3 are always addressed (A input is selected). RAM location is a function of direction. Bytes 0 + 1 are selected for a data transfer in; bytes 2 + 3 are selected for a data transfer out. CSR selection comes directly from the UNIBUS address transceivers. When NPR MASTER L is high, the B input is selected, allowing the UNIBUS address bits to control Multiport RAM address selection. Port A data input is selected by four 74LS157 MUXs. Data is gated from the UNIBUS transceivers except when the microprocessor MP WRITE CYCLE H signal is true, in which case the data comes from the ALU.

Port B address is selected by one 74LS157 MUX. CROM bits 5, 6 and 15 from the IR determine the B address. The exception is when the UNIBUS WRITE L select input to the MUX selects OUT NPR (Cl)H which is used for the NPR address, Multiport RAM address bytes 4 + 5 are selected for an NPR read, and address bytes 6 + 7 are selected for an NPR write.

Port A output goes to the UNIBUS data transceivers (D11 of Print Set). Port B output goes to the DMUX (D7 of Print Set) and to the UNIBUS address transceivers (D12 of Print Set). The write signal to the Multiport RAM comes from a three input OR gate under three conditions:

- NPR Load Multiport

- Microprocessor Load Multiport

- CSR Load Multiport

Its output is ANDed with the byte select for the byte to be written; LB WRITE L for bits 7-0; HB WRITE L for bits 15-8.

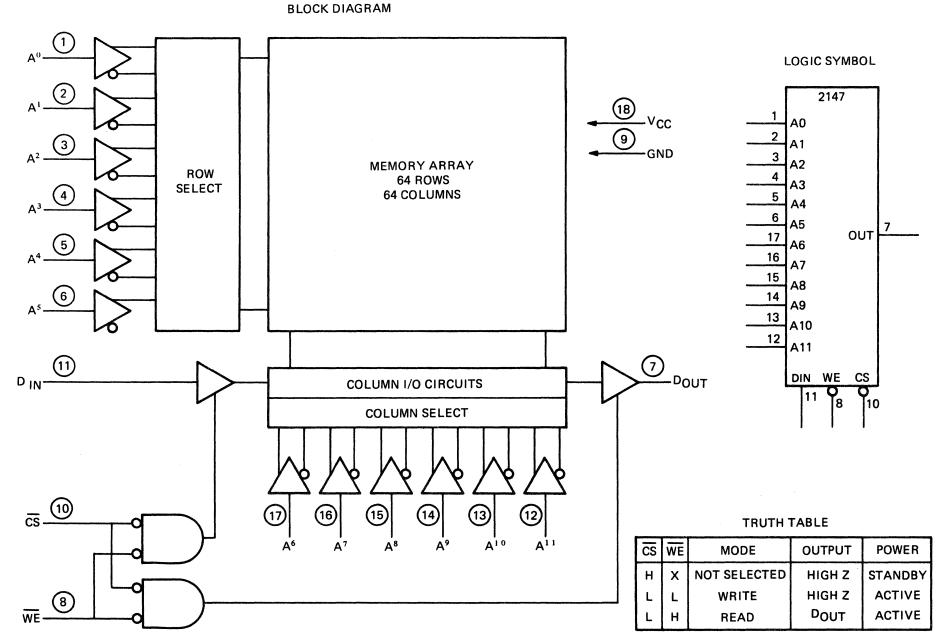

#### 2.7 DATA MEMORY (Figure 2-8)

The data memory, a 4K- by 8-bit array of 2147-3 chips, can only be accessed by the microprocessor for data storage. The data memory is completely separate from the instruction memory. The memory is addressed from the 12-bit MAR. A move instruction loads the MAR, high or low bytes, and also increments the MAR via CROM bits 11 and 12 of the move instruction, which are input to the Destination ROM. DROM controls both loading and incrementing of the MAR and data memory. The MAR is clocked on every move instruction and cleared low on master clear and initialize. The contents of the MAR can be read through IBUS\* registers 14 and 15, with page and field overflow on bits 5 and 6 of IBUS\* register 10. IBUS\* registers 14 and 15, represent the MAR for the previous instruction (see Figure 2-1, Sheet 3 of 3). Data memory is loaded from the BALU at time 180. The write pulse comes from a 74S158 (D1 of Print Set) on a move instruction when the DROM output is true. Data memory output is sent to the DMUX (D7 of Print Set).

#### 2.8 **PROGRAM COUNTER (PC) (Figure 2-9)**

The PC is a 14-bit counter that is incremented at time 60 unless the instruction is a true branch. In this case, the PC is parallel loaded 120 ns from the beginning of the instruction. The lower eight bits of the PC are loaded from the ALU; the next four bits are loaded through a 74LS157 MUX, and the upper two bits are loaded from the Program Counter Register (PCR), bits 4 and 5.

- If branch condition zero exists the MUX selects PCR outputs <13:8>H

- <u>If branch conditions 1 through 7 exist</u> CROM bits 11 and 12 of the IR are used for the paging bits, and the field bits are reloaded from the PC.

The PCR is OUT\* register 13. It contains the upper six bits to be loaded (PCR <13:8>H) into the PC on branch condition 0. This provides extra field addressing with future expansion capability.

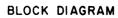

Figure 2-9 Program Counter

The contents of the PC can be read by the program through INBUS\* registers 12 and 13 for the instruction that is being executed. The PC is cleared with CLEAR L during a master clear and bus initialization. Branch control is accomplished through an 8-to-1 (74S151) multiplexer driven by CROM bits 8 through 10 from the IR. The branch MUX is only enabled during branch instructions.

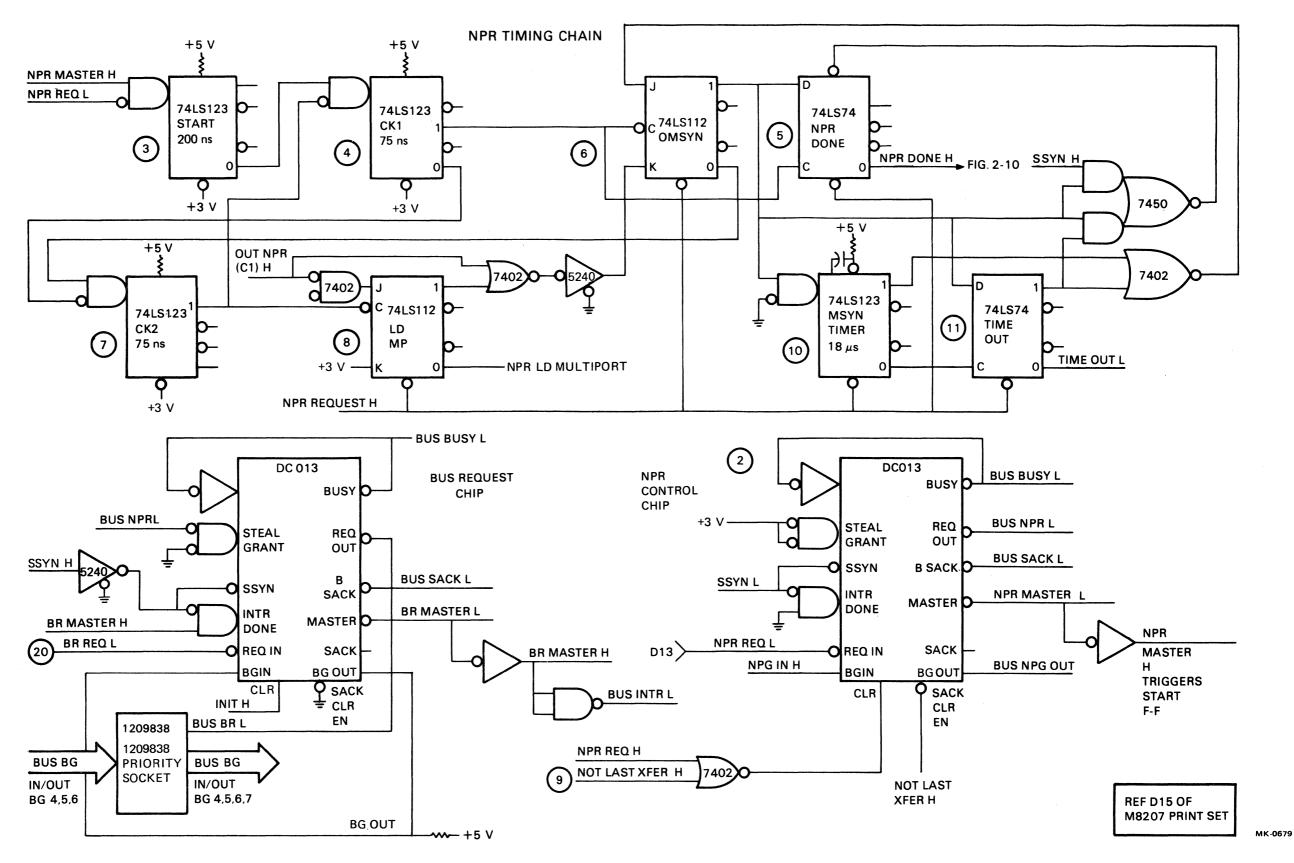

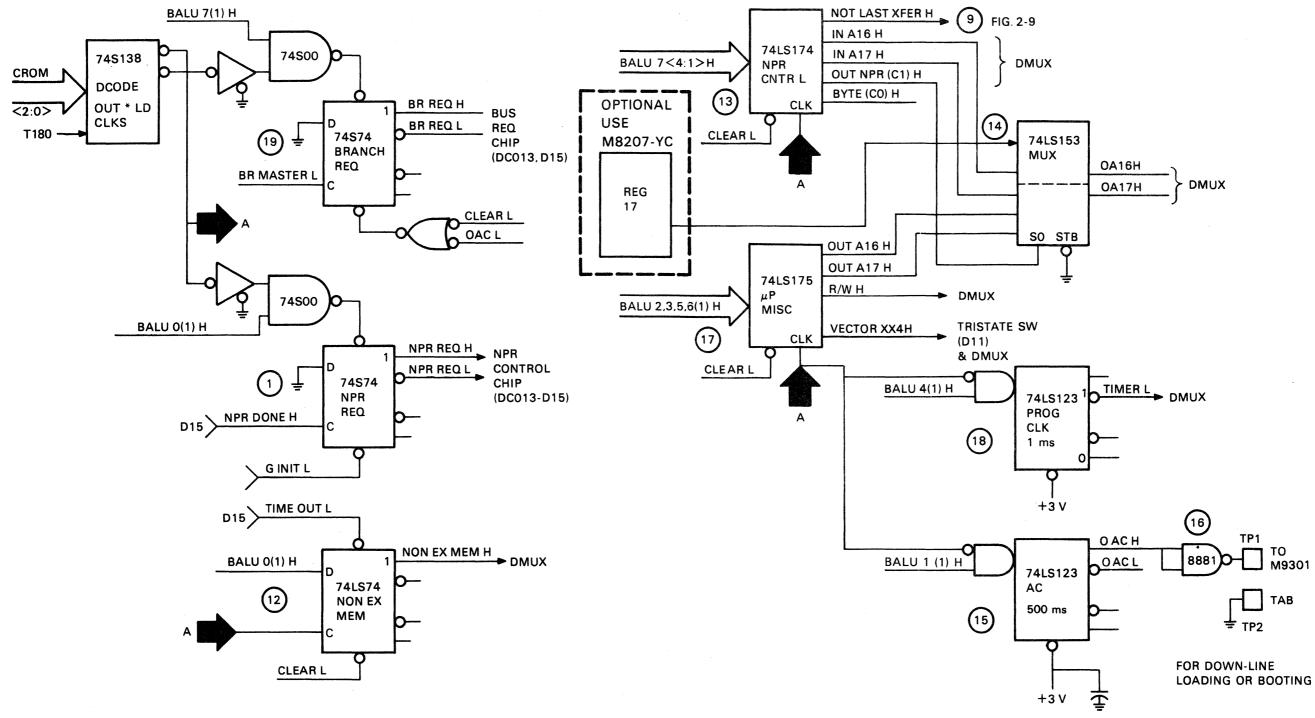

#### 2.9 NPR AND MISCELLANEOUS REGISTERS (Figures 2-10 and 2-11)

The microprocessor has two registers that are used for microprocessor hardware control and status, INBUS\*/OUT\* 10 and 11. Register 10 controls the NPR circuitry and starts the NPR timing. Register 11 is a status register. The following discussion describes the bits and functions of both registers.

#### NOTE

Circled numerics are used in the following discussion to associate those areas of text with corresponding areas in Figures 2-10 and 2-11.

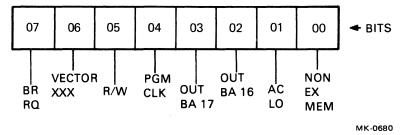

#### 2.9.1 Microprocessor NPR Control Register (Register 10)

| 7                    | 6         | 5        | 4                  | 3          | . 2        | 1                   | 0 •        | BITS         |

|----------------------|-----------|----------|--------------------|------------|------------|---------------------|------------|--------------|

| BYTE<br>XFER<br>(CO) | MAR<br>10 | MAR<br>8 | OUT<br>NPR<br>(C1) | IN<br>BA17 | IN<br>BA16 | NOT<br>LAST<br>XFER | NPR<br>REQ |              |

|                      |           |          | 1                  |            |            |                     |            | -<br>MK-0662 |

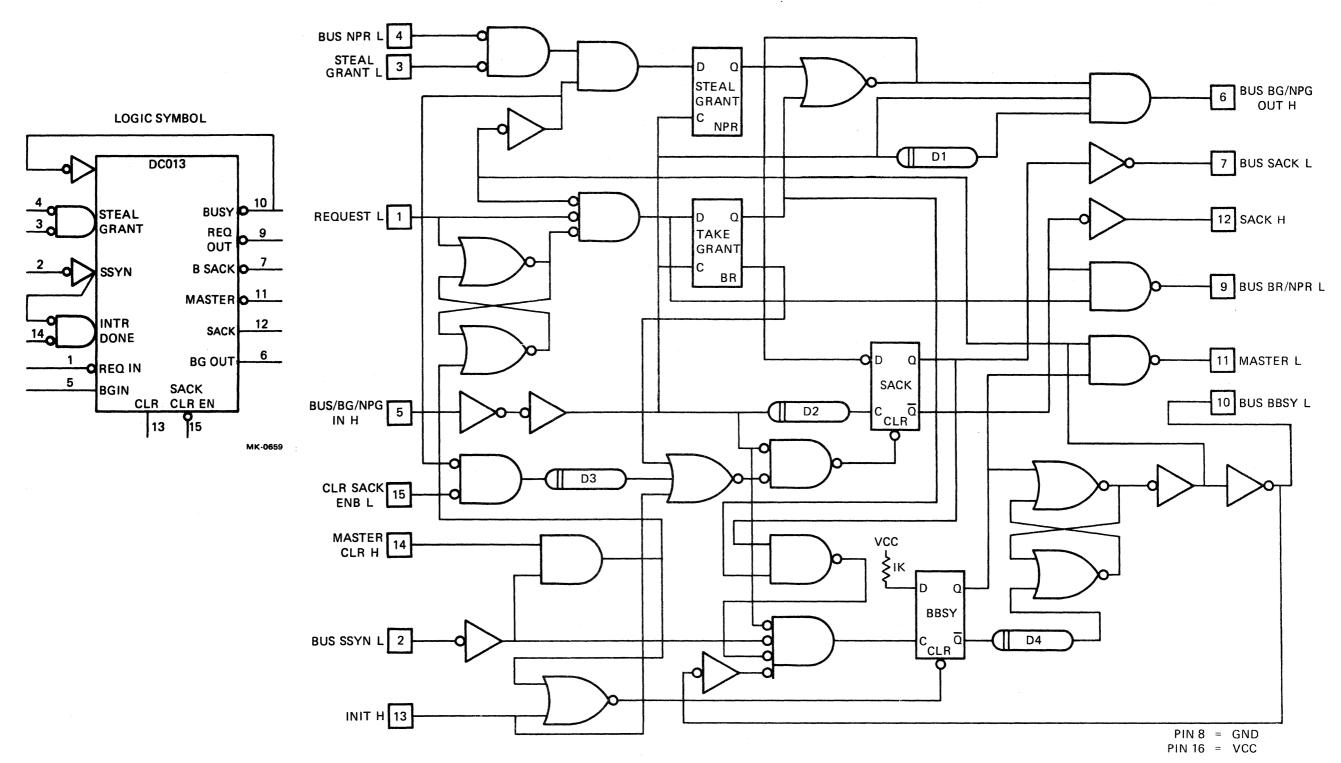

• <u>Bit 0</u> is the NPR bit and can only be written to a 1 by the microprocessor; clearing is done by the hardware. The NPR flip-flop (Fig. 2-11 (1)) is set through a NAND gate, via the flip-flop's preset input when the program writes a 1 to bit 0. This starts the NPR cycle through NPR control chip (Fig. 2-10 (2)), which generates BUS NPR, then waits for the request to be granted via NPG IN. The microprocessor then becomes bus master and the NPR MAS-TER H signal triggers the START one-shot (Fig. 2-10 (3)), a 200 ns timer. The 200 ns time period allows: (1) the multiplexers to select the address and data from the Multiport RAM, (2) propagation through the Multiport RAM, the bus transceivers, and bus delays, and (3) a 75 ns deskew time for the signals on the bus.

The trailing edge of the 200 ns pulse from the start timer triggers the second timer CK1 - a75 ns timer (Fig. 2-10 4). The leading edge of CK1 clocks the NPR DONE flip-flop (Fig. 2-10 5). The data input is clear at this time. The trailing edge of CK1 clocks the OM-SYNC flip-flop (Fig. 2-10 6)), which generates master sync on the bus and enables CK2 - a75 ns timer (Fig. 2-10 7). CK2 is triggered after slave sync is returned and presets the NPR DONE flip-flop.

The leading edge of CK2 does nothing; the trailing edge clocks the NPR LOAD MULTI-PORT flip-flop (Fig. 2-10 (8)) during a transfer in and retriggers CK1. The leading edge of CK1 now clocks NPR DONE which is set and the data input is true, keeping NPR DONE in a set state. The trailing edge of CK1 clears OMSYN and retriggers CK2 which clears NPR LOAD MULTIPORT and retriggers CK1. CK1 clears NPR DONE which clocks the NPR RQ flip-flop whose input is grounded.

Clearing the NPR RQ flip-flop clears the NPR control unless this is not the last transfer, in which case NOT LAST TRANSFER signal is set (Figures 2-10, 2-11 (9)). When OMSYN is set, an 18 microsecond timer is started (Fig. 2-10 (10)). If this timer times out before slave sync is returned, the TIME OUT flip-flop is set (Fig.2-10 (11)). This clears the NPR control circuitry as if slave sync had been returned, and presets a flip-flop (Fig. 2-11 (12)) that generates a signal line called NON EX MEM H gated to the DMUX.

Figure 2-10 Interrupt and NPR Control

REF D13 OF M8207 PRINT SET

v

MK0696

Figure 2-11 Miscellaneous Registers

2-18

- <u>Bit 1</u> is the not last transfer bit which is part of a hex D flip-flop used for register 10. The output of the flip-flip goes to the NPR circuit and keeps the NPR control chip (DC013) from clearing at the end of an NPR cycle. This maintains BUS BUSY for multiple Direct Memory Access (DMA) transfers. The NOT LAST XFER H signal line is also sent to the DMUX (D7 of Print Set) and should be cleared when the last NPR RQ is set.

- <u>Bits 2 and 3</u> are NPR address bits 16 and 17 respectively. These bits are loaded into the hex D flip-flop used for register 10 via the BALU (Fig.2-11 (13)). Outputs of the hex D flipflop (IN16 H, IN17 H) are gated into a MUX (Fig. 2-11 (14)) which is controlled by OUT NPR (C1) H. If this control signal is not set, bits 2 and 3 of register 10 are used as the upper two bits of the NPR address. The MUX upper two bit outputs OA16 H and OA17 H are also gated into the DMUX to be read by the microprocessor.

- <u>Bit 4</u> is the OUT NPR (C1) H bit of register 10 used to control the direction of an NPR transfer. Bit 4 is used by the multiplexers to select: (1) the registers to be used for the address of an NPR transfer, and (2) the register to be loaded for an IN (read) transfer, or the register to be loaded onto the bus for an OUT (write) transfer. Bit 4 is also loaded into the hex D flip-flop (Fig. 2-11 (13)) and the output, OUT NPR (C1) H controls bits 2 and 3 as described in the previous paragraph. The control line is also gated into the DMUX to be read by the microprocessor.

- <u>Bits 5 and 6</u> are read only bits showing MAR bits 8 and 10, which are page and field overflow bits. These bits are duplicated in register 15 and kept in register 10 for compatibility with previous versions of the microprocessor family.

- <u>Bit 7</u> is used for byte transfers. This bit uses the hex D flip-flop and can be read through the  $\overline{DMUX}$  by the microprocessor.

## 2.9.2 Microprocessor Miscellaneous Register 11 (Register 11)

- <u>Bit 0</u> is a nonexistent memory error. It uses a 74LS74 flip-flop that can be set and cleared by the microprocessor. When a time out occurs during an NPR transfer, the flip-flop is preset, indicating that slave sync was not returned within 18 microseconds. Bit 0 can be read through the DMUX.

- <u>Bit 1</u> is AC LO which controls a one-shot (Fig. 2-11 (15)) that can be used to generate an ac low on the UNIBUS, and a control signal to TP1 (spade lug located near BERG Connector). This control bit should not be used for non-DEC programming unless the AC LO function to the UNIBUS is disabled by removing jumper W3. Field Service representatives should check this function if unusual problems are occurring with AC LO.

The AC LO feature is used for initializing the CPU and causes a one-half second AC LO pulse on the UNIBUS (if W3 is installed). During this time, the microprocessor protects itself from initialization by the UNIBUS INIT signal.

The output of the one-shot is also gated into an 8881 driver (Fig. 2-11 (16)) connected to TP1. The output of the 8881 is GND when the AC LO bit is asserted and requires a pull-up resistor (typically 1K ohms at 5 volts). The intention is to drive a boot module directly without using AC LO on the bus. The OAC H output is also input to the DMUX as a status bit.

- <u>Bits 2 and 3</u> are OUT NPR address bits 16 and 17 respectively. These bits are loaded into a quad D flip-flop (Fig. 2-11 ()) used for register 11 via the BALU. Outputs OUT A16 H and OUT A17 H are gated into the same MUX as IN A16 H and IN A17 H (see bits 2 and 3 of the NPR Control Register 10). The MUX is used to select the extended IN or OUT address bits for NPR transfer (see bit 4 of register 10). These bits can also be read through the DMUX by the microprocessor.

- <u>Bit 4</u> is the program clock which is a 1 ms one-shot (normally the function can change with the "Y" version) (Fig. 2-11 (18)) used by the microprogram for timing. The output of the one-shot, TIMER L, can be read through the DMUX by the microprocessor and does not affect the operation of the microprocessor hardware.

- <u>Bit 5</u> has no hardware function, but should be reserved for future versions of the microprocessor. The bit is generated via register 11s quad D flip-flop and the output can be read through the DMUX by the microprocessor.

- <u>Bits 6 and 7</u> are used for interrupts. Bit 6 selects the vector to be used for the interrupt. If bit 6 is set, the interrupt vector is XX4. If bit 6 is clear, the interrupt vector is XX0. Bit 7 initiates the interrupt.

The actual bit is written into register 11s quad D flip-flop (Fig. 2-11 (17)). The flip-flop output (XX4/XX0) goes to the tristate switch (D11 of Print Set) for the interrupt vector address, and to the DMUX to be read by the microprocessor. Bit 7 is BR RQ (Fig. 2-11 (19)) which can only be written to a one by the microprocessor. The flip-flop must be cleared by the hardware. A NAND gate is used to clock the data to the preset input of a 74S74 flip-flop. The data input to the flip-flop is tied to ground and used only to clear the flip-flop on the completion of an interrupt. The BR RQ flip-flop is cleared by the CLEAR L or OAC L signals. The output of the BR RQ flip-flop is used to initiate the interrupt through the DC013 chip (Fig. 2-10 (20)). The DC013 uses the priority plug to ensure the proper level, normally level 5. When the DC013 gives up bus mastership, the BR RQ flip-flop is cleared.

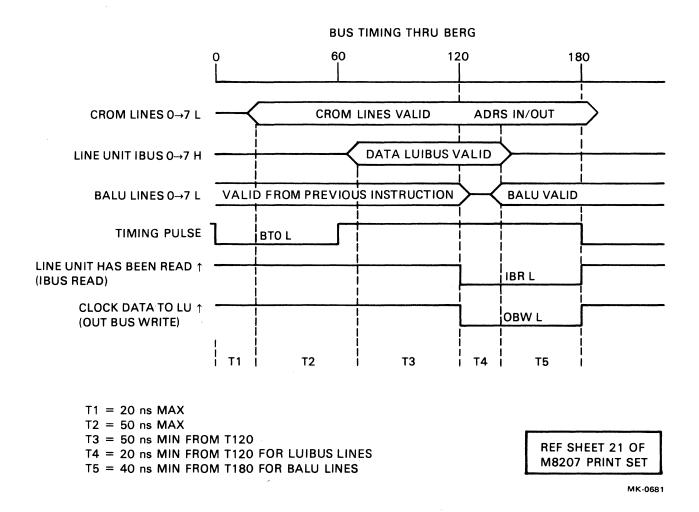

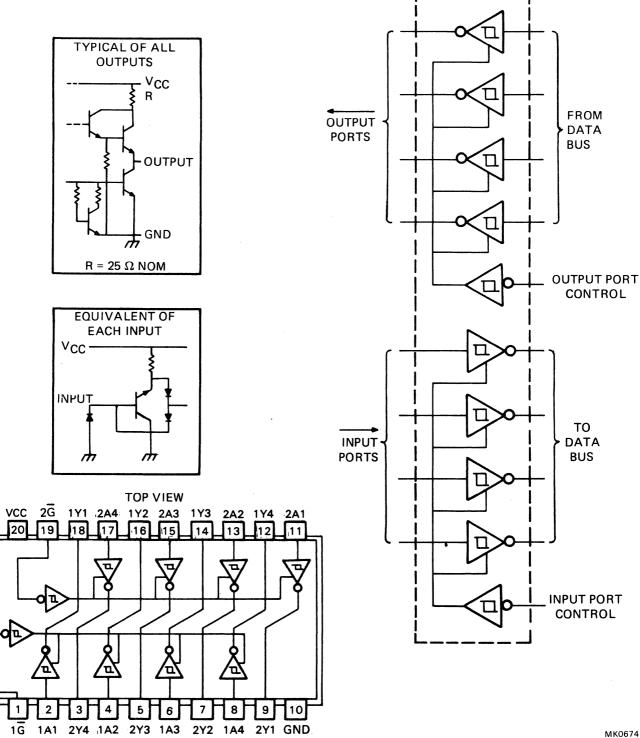

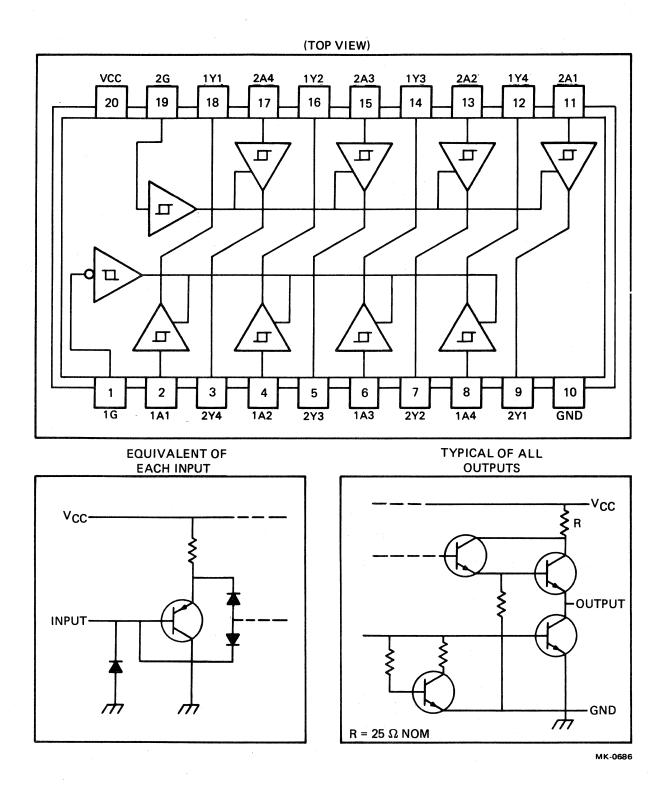

#### 2.10 BERG PORT (Figure 2-12)

The BERG Port is an 8-bit parallel port which allows the microprocessor to communicate with a line unit without using the UNIBUS. The port runs at an instruction speed of 180 ns. Eight addresses are used both for read and for write transactions (using the microprocessor as reference).

- <u>Read Transactions</u>: The address is output 20 ns after the beginning of the instruction at time zero (T0). Buffered T0 goes to the port for syncing the line unit to the microprocessor. Data must be valid for a read, 50 ns after the address is set up, and must remain valid until 20 ns after the leading edge of IBR low. IN BUS has been read (IBR low) starting at T120 and ending at T180.

- <u>Write Transactions</u>: The address is valid 20 ns from T0. The data is valid on the BALU lines 140 ns after T0. The data should be clocked on the trailing edge of OUT BUS WRITE (OBW). Recommended interface chips are shown on the last sheet of the *M8207 Print Set*.

Figure 2-12 Timing Through BERG Port

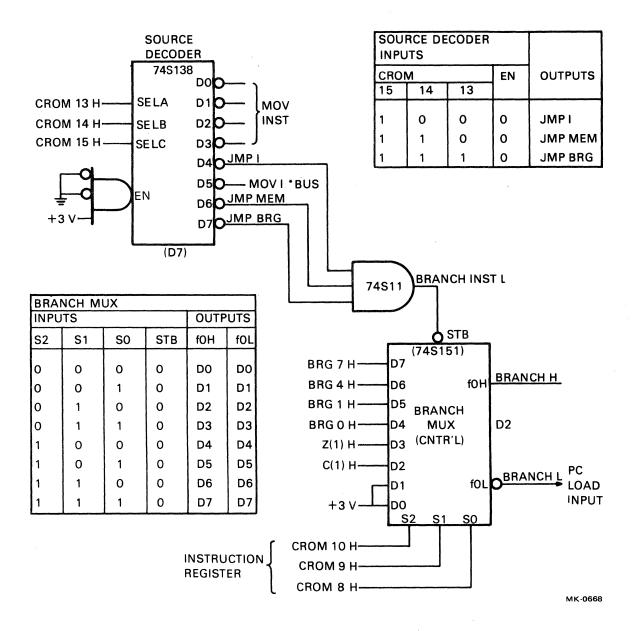

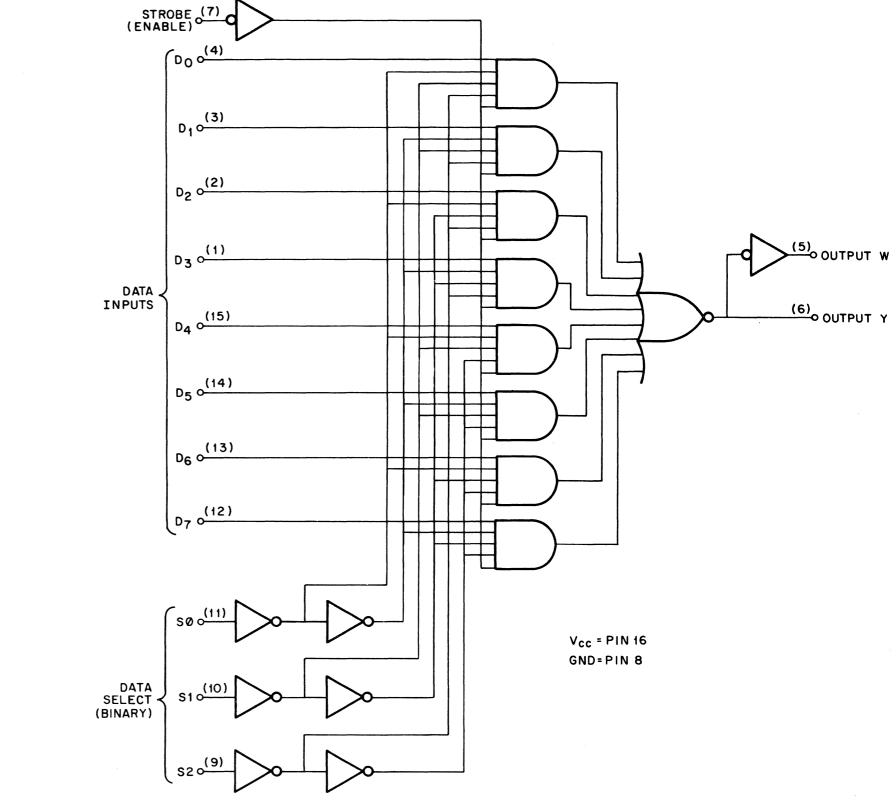

#### **2.11 BRANCH CONTROL** (Figure 2-13) Three branch instructions are defined by Source Decoder input bits CROM <15:13>:

- Branch Immediate (JMP I)

- Branch Memory (JMP MEM)

- Branch Register (JMP BRG)

When a branch condition is established, BRANCH INST L is asserted. This provides the strobe input to the 8-to-1 branch control multiplexer, which is driven directly by instruction register CROM <10.8> condition bits. The control MUX is disabled during a move instruction as defined by the Source Decoder. In this case BRANCH INST L is unasserted, thereby removing the required strobe input to enable the control MUX.

Branch MUX control inputs are:

- +3 Volts (inputs D0, D1) branch always instructions

- C(1) H bit (input D2) branch on carry

- Z(1) H bit (input D3) branch on Z (ALU all ones)

- BRG 0, 1, 4, 7 (H) bits (inputs D4 D7)

<u>BRG 0</u> (Branch Field) – During this branch, the upper six bits of the PC are always loaded from the PCR (OUT\*13); the page and field bits are changed to the contents of register 13.

<u>BRG 1, 4, 7</u> – These branches use bits 11 and 12 of the IR for paging bits, but cannot change the field bits. The only way to change the field bits is with Branch 0, unless the field is incremented into.

Figure 2-13 Branch Control Logic

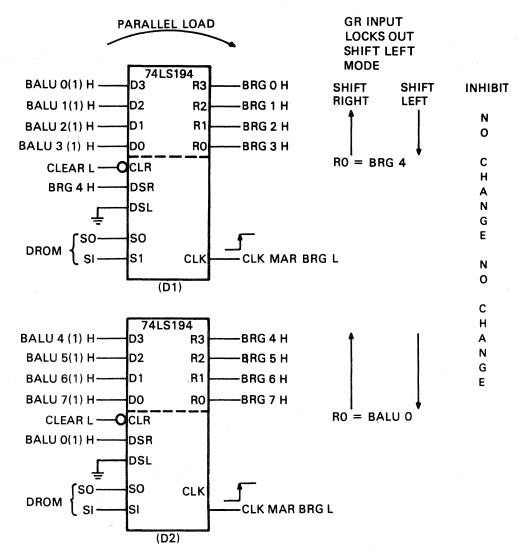

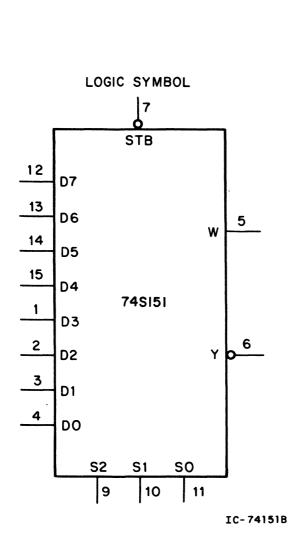

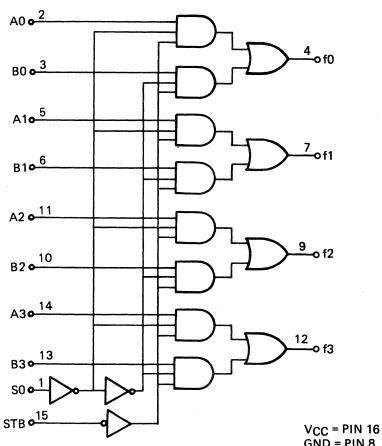

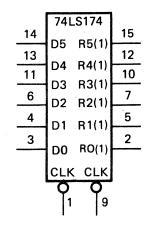

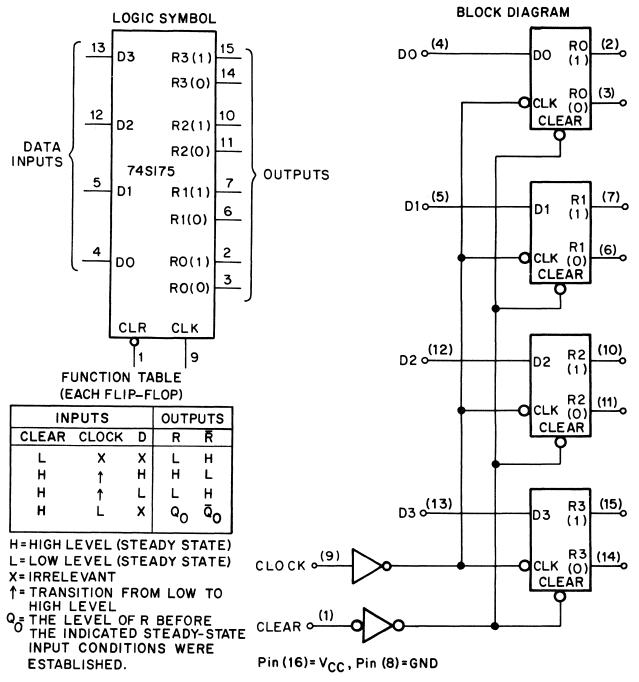

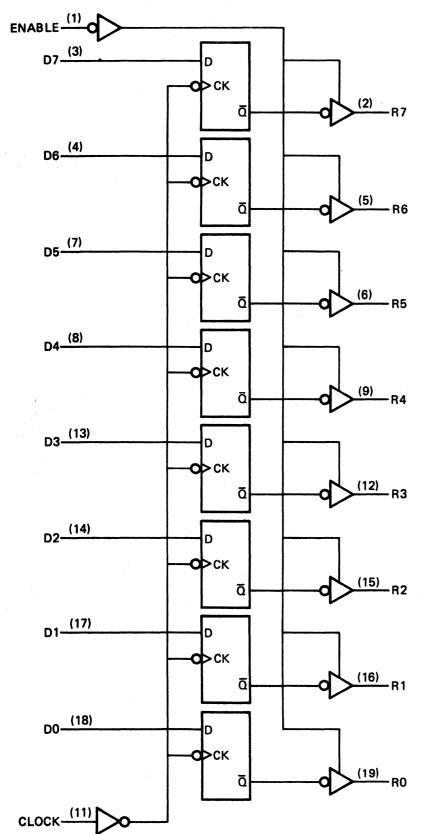

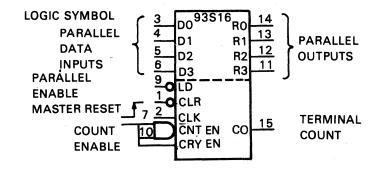

#### **2.12 BRANCH REGISTER** (**BRG**) (Figure 2-14)

The BRG is an 8-bit register which is used as a temporary storage register. It provides four distinct modes of operation used under branch conditions:

- Parallel Loading

- Shift Right

- Shift Left (ground input locks out shift left mode)

- Inhibit Clock

These modes of operation are determined by the states of SO and SI inputs from the Desination ROM. Refer to Figure 2-13 and note that the operations occur on the positive-going edge of CLK MAR BRG L.

#### 2.13 **DESTINATION ROM (DROM)** (Figure 2-15)

The DROM provides control lines SO and SI to the BRG and increment inputs to the MAR. DROM also provides three additional control outputs determined by CROM input bits <12:8>:

- <u>BRANCH FIELD H</u> output is used as the select input to a 74S157 MUX in the PC circuitry.

- <u>SP and MEM</u> outputs are gated into a 74S158 MUX to generate: (1) the write enable input, WRITE MEM L, for the memory, and (2) the write enable input, WRITE SP L, for the SP.

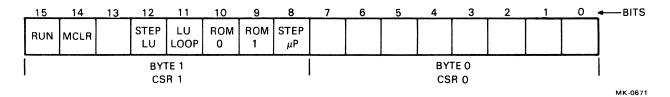

#### 2.14 CONTROL AND STATUS REGISTERS (CSR0 and CSR6)

The control and status registers are primarily defined by the microcode. Byte 1 of CSR0 is defined by the hardware. When written to by the CPU, the microprocessor can write into the Multiport RAM without affecting the hardware register. CSR6 is only defined when used with byte 1, bit 9, and bit 10 of CSR0.

#### CSR0 – Address 76XXX0

The M8207 uses the floating address area. Actual setting of the address depends on the microcode variation option, of which the M8207 is a part. The space requires eight bytes or four words for CSR0 through CSR6 locations. The XXX in the address is switch selectable and should be set up when the module is installed in the system. Bits and associated CSR1 (high byte of CSR0) are controlled in the following manner. Note that RUN bit 15 can be disabled via the RUN INHIBIT switch (see D16 of Print Set).

#### NOTE Switch 8 of the Interrupt Switch Pack is used to disable ALL CSRs.

| INPUTS |                |    |          |       |          |    |    |    |    | OUTPUTS |           |    |    |   |

|--------|----------------|----|----------|-------|----------|----|----|----|----|---------|-----------|----|----|---|

|        | мо             | DE |          | SERIA | PARALLEL |    |    |    |    |         |           |    |    |   |

| CLR    | SI             | SO | CLK      | LEFT  | RIGHT    | DO | D1 | D2 | D3 | RO      | <b>R1</b> | R2 | R3 |   |

| н      | н              | н  | Î        | х     | х        | DO | D1 | D2 | D3 | DO      | D1        | D2 | D3 | 0 |

| н      | L              | н  | <b>↑</b> | х     | H/L      | х  | х  | х  | x  | H/L     | RO        | R1 | R2 | 0 |

| н      | н              | L  | <b>↑</b> | L     | x        | х  | х  | х  | X  | R1      | R2        | R3 | L  | 3 |

| Н      | L <sub>.</sub> | L  | х        | х     | x        | х  | х  | х  | х  | R0      | R1        | R2 | R3 | 4 |

1 PARALLEL LOADING - OUT = THE LEVEL OF STEADY STATE INPUTS (BALU BITS)

2 SHIFT RIGHT - OUT = RO IS AT LEVEL OF DSR INPUT RO-R3 SHIFTED RIGHT

3 SHIFT LEFT – OUT = RO-R3 SHIFTED LEFT, DSL AT LOW LEVEL (GND IN) AT VACATED R3 BIT POSITION

4 INHIBIT CLOCK - OUT = NO CHANGE

MK-0670

Figure 2-14 Branch Register

|           | MICROINS         | MICROINSTRUCTIONS |  |

|-----------|------------------|-------------------|--|

| CROM BITS | BRANCH           | MOVE              |  |

| 12,11     | BRANCH ADDR BITS | MAR FUNCTION      |  |

| 10,9,8    | CONDITION CODE   | DESTINATION FIELD |  |

MK-0669

Figure 2-15 Destination ROM

- BIT 8 (STEP  $\mu P$ ) steps the microprocessor through one instruction cycle.

- <u>BITS 9, 10, 11, 12 and 15</u> functions are asserted on the positive-going edge of CSR0 clock input signal.

- <u>BIT 9 (ROM I)</u> when cleared generates CROM enable 0 + 1K, 2 + 3K, and 4 + 5K inputs to the control ROM circuitry. Bit 9 when set enables CSR6 to be used as the maintenance register.

- <u>BIT 10 (ROM 0)</u> is ANDed with A1 and A2 to provide the select input to the data select multiplexers at the UNIBUS data interface. When select input is unasserted, A PORT data is directed to the UNIBUS interface. When select input is asserted, ROM data is selected to verify the contents of the ROMs.

- <u>BIT 11 (LU LOOP)</u> connects line unit serial line back to its serial line in (optional with the line unit).

- BIT 12 (STEP LU) shifts transmitters/receivers (optional with the line unit).

- BIT 13 reads/writes in the Multiport RAM; does not perform any hardware functions.

- BIT 14 (MASTER CLEAR) clears both the microprocessor and line unit.

- <u>BIT 15 (RUN)</u> controls the microprocessor clock via the RUN STEP L signal input to the system clock circuitry (set on Master Clear).

- <u>BITS 11, 12, 14, and 15</u> are directly connected to the line unit via the J1 connector. (See D16 of Print Set.)

#### CSR6 – Address 76XXX6

In maintenance mode, an instruction can be loaded with bit 9 of CSR0. In CROM display, the contents of the ROM can be verified with bit 10 of CSR0 in a set state.

# CHAPTER 3 SERVICE

# 3.1 SCOPE

Maintenance procedures used in servicing an M8207 module are discussed in this chapter.

#### NOTE

The M8207 performs no useful function without application firmware supplied only by DIGITAL.

# There are no built-in maintenance features such as error checking or self-diagnosis.

#### **3.2 MAINTENANCE PHILOSOPHY**

The M8207 module is the Field Service Field Replaceable Unit (FRU). Isolation to the module must be done through the use of DEC Diagnostics and/or any microdiagnostics that may have been incorporated in the Control Read Only Memory (CROM). In some applications, ROMs are provided for replacement by a Field Change Order when an error is detected in CROM.

#### 3.2.1 Preventive Maintenance

There is no specific Preventive Maintenance (PM) schedule for the M8207 module. Voltages and connections should be checked during system PM or when problems exist. While special tools are required for PM, standard test equipment may be used. The diagnostics include:

- Microprocessor basic diagnostics (not requiring CROMs) are provided

- Functional diagnostics based on ROM code application

#### **3.2.2** Corrective Maintenance

Standalone diagnostics are provided for checkout of the basic M8207 Microprocessor. These diagnostics check out the M8207 logic and determine whether the microprocessor is capable of running a microprogram from CROM.

Microinstructions are clocked into the Maintenance Instruction Register (MIR) from the UNIBUS, allowing one microinstruction to be executed at a time. Although individual microinstructions are executed at full microprocessor speed, the time between instructions depends upon Central Processing Unit (CPU) execution time.

Basic M8207 diagnostics are designed to run on the basic microprocessor logic with or without CROMs installed.

Functional diagnostics are provided for specific DIGITAL supplied applications implemented in the CROMs. These diagnostics are application oriented, implementing and testing features provided in

microcode as well as in the M8207 hardware. They should be run whenever possible to ensure total option functionality. The functional diagnostics perform a Cyclic Redundancy Check (CRC) on the CROM contents, before starting the microprocessor. CROMs can be diagnosed in 2K segments and may be replaced if required.

# NOTE

#### A 2K segment consists of 2 chips, each 2K- by 8-bits.

When problems occur, the voltage levels should be checked on the backplane,\* and all connections should be checked for proper installation and seating. In systems where the M8207 is newly installed or add-ons have been implemented, proper bus configuration must be ensured. Diagnostics should then be run starting with the basic tests and continuing on to the functional diagnostics.

If a customer's application does not work, but all diagnostics run successfully, and the system checks out, the M8207 should be replaced. Diagnostics should then be run on the new M8207. Upon successful completion of the diagnostic, the customer's application can be retried. The possibility that faulty microcode or software drivers exist should be considered.

#### NOTE The M8207 will only be supported when used in a DIGITAL supplied subsystem, including DIGITAL supplied microcode.

#### 3.3 MICROPROCESSOR USE WITH LINE UNITS

M8207 diagnostics should be run before any line unit diagnostics. This is necessary because the M8207 provides all access and control for the line unit and could erroneously cause a line unit to appear faulty.

As with M8207 basic tests, microinstructions are loaded and clocked at the CPU execution speed. Execution of individual microinstructions occurs at the microprocessor cycle rate.

#### **3.4 LINE UNIT PORT CABLE CONSIDERATION**

The line unit cable (BC08S-1 or BC08R-1) is susceptible to damage from frequent bending and chafing. This cable may be responsible for apparent line unit failures and should be replaced if in doubt.

#### 3.5 M8207 LINE UNIT PORT

Only DEC supplied line units are supported on the line unit port.

#### **3.6 MICRODIAGNOSTICS**

Microdiagnostics are not part of the M8207 module. They must be incorporated as part of the application microcode. Recommended microdiagnostic tests are provided in Appendix A. A microdiagnostic failure, in general, is reason to run CPU based diagnostics or replace the indicated module. It should be noted that the microdiagnostic cannot be relied upon for 100% logic failure detection.

The microdiagnostic relies upon a basically operational microprocessor. Some faults in a microprocessor could cause the microdiagnostic to report incorrect error information or, in extreme cases, not to report at all.

<sup>\*</sup>The M8207 microprocessor draws 7 amps at +5 volts. This should be considered, especially when adding a load to a regulator. Nine slot SPC backplanes, such as the DD11-D, permit configurations with power supply overload capability.

Refer to Appendix A for error codes and a description of the internal and interface diagnostics. The intent of the microdiagnostic is to:

- Identify a faulty unit

- Provide error information indicative of the fault

The first intent can help the customer isolate a faulty option under system operation. This could allow reasonable system operation to continue while placing a call for service. And, if the customer can identify the failing subsystem, the Field Service time needed to diagnose the problem would be reduced.

The second intent may indicate which module is defective, effectively reducing diagnostic and repair time.

#### **3.7 ROM REPLACEMENT**

The Programmable ROMs (PROMs) on the M8207 are 2K- by 8-bits. The last four bytes on the PROM contain information about the PROM. The first of the last four bytes contains the ASCII Version number. The second byte contains the ROM number (0, 1, 2, 3, 4, or 5). The third and fourth bytes contain a negative CRC-CCITT word for that PROM. The two static diagnostics written for the M8207 do not check the PROMs. The functional diagnostics written for a specific option associated with the M8207 should be used for verification of ROM contents and ROM placement checking.

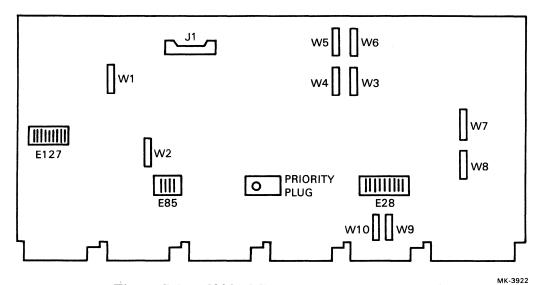

Figure 3-1 is an extract of the M8207 module component layout; component side view of upper connector pins and ROM portion. Pin 1 is identified on each chip to ensure proper orientation and installation of a good chip should it become necessary. A ROM Kit including ROM replacement procedures is supplied with the shipment.

Table 3-1 shows the relationship of the E numbers and address range of chips 0 through 5.

| Chip<br>Location | Chip<br>No. | Byte | Address<br>Range         |

|------------------|-------------|------|--------------------------|

| E03              | 0           | LOW  | 0000- 3777 <sub>8</sub>  |

| E02              | 1           | HIGH | 0000- 3777 <sub>8</sub>  |

| E04              | 2           | LOW  | 4000- 7777 <sub>8</sub>  |

| E01              | 3           | HIGH | 4000- 7777 <sub>8</sub>  |

| E05              | 4           | LOW  | 10000-13777 <sub>8</sub> |

| E14              | 5           | HIGH | 10000-137778             |

| Table 3-1 | Chin | Address | Range |

|-----------|------|---------|-------|

|-----------|------|---------|-------|

# CAUTION

Care should be exercised when replacing ROMs.

- Avoid touching chip surface

- Handle ROMs by placing fingers on either ends of the chip

- Do not bend pins during insertion

Figure 3-1 Extract of M8207 Module Component Layout

Refer to Figure 3-1 and check for:

- Proper chip orientation

- Proper chip location

Following is a sample test to check out ROM 0 for CRC/CCITT (ROM contents) and ROM position.

|      | MOV<br>MOV                  | #0,ROMN<br>#0,CADDR                               | ;ROM NUMBER<br>;GET STARTING ADDR.                                            |

|------|-----------------------------|---------------------------------------------------|-------------------------------------------------------------------------------|

|      | MOV                         | #-1,CWORD                                         | ;INIT CRC WORD.                                                               |

| 10\$ | JSR                         | PC,GWORD                                          | ;GET FIRST BYTE.                                                              |

|      | MOVB<br>INC<br>JSR<br>Movb  | @SEL6,WORDT<br>CADDR<br>PC,GWORD<br>@SEL6,WORDT+1 | ;STORE FIRST BYTE.<br>;UPDATE ADDR.<br>;GET A BYTE.<br>;STORE IN HIGH BYTE OR |

|      | INC<br>CMP<br>BEQ           | CADDR<br>CADDR,#3777+1<br>20\$                    | WORDT<br>;UPDATE ADDR.<br>;AT END?<br>;YES,EXIT LOOP.                         |

|      | JSR                         | PC,CRCR                                           | ;NO-CALCULATE CRC ON THIS WORD.                                               |

|      | BR                          | 10\$                                              | ;LOOP                                                                         |

| 20\$ | СОМ                         | CWORD                                             | ;STORED CRC WORD IS<br>COMPLEMENT.                                            |

|      | CMP<br>BEQ<br>Error         | CWORD,WORDT<br>30\$                               | ;EQUAL?<br>;ROM CRC WORD BAD.                                                 |

| 30\$ | MOV                         | #3775,CADDR                                       | ;SET ADDRESS FOR ROM<br>NUMBER.                                               |

|      | JSR<br>CMPB<br>BEQ<br>Error | PC,GWORD<br>ROMN,WORDT<br>40\$                    | ;READ ROM<br>;IS ROM NUMBER CORRECT?                                          |

#### 40\$

END TST

| GWORD:   | CLR                         | @SEL0                                   | ;INIT                               |

|----------|-----------------------------|-----------------------------------------|-------------------------------------|

|          | MOVB                        | CADDR+1,@SEL2                           | SET HIGH BYTE OF ADDRESS            |

|          | JSR                         | R5,ROMCLK                               |                                     |

|          | .WORD                       | 121053                                  | ;MOV IBUS* 2 TO OBUS*13             |

|          | BIC                         | #377,1\$                                | STRIP ADDR FIELD.                   |

|          | BISB                        | CADDR,1\$                               | ADD IN IMM ADDR.                    |

|          | JSR                         | R5,ROMCLK                               | GO DO BRANCH                        |

|          |                             |                                         |                                     |

| 1\$      | .WORD                       | 100000                                  | ;BRANCH EXT PUTS ADDR. IN<br>PCREG. |

|          | BIS                         | #2000,@SEL0                             |                                     |

|          |                             |                                         |                                     |

|          | <b>RTS PC</b>               |                                         | ;EXIT                               |

|          |                             |                                         |                                     |

| **       | . * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |                                     |

| ,*       |                             |                                         |                                     |

| ,<br>·*R | OMCLK                       | ROUTINE TO SINGLE                       | STEP AN INSTRUCTION IN THE          |

| .*       | OMEEN                       | M8207                                   |                                     |

| ,<br>.*  |                             | CALL=JSR R5, ROMCI                      | ĴK.                                 |

| .*       |                             | .WORD INSTR                             |                                     |

| ·*       |                             | <b>RETURNS HERE</b>                     |                                     |

| .***     | *********                   | *********                               | ***********                         |

#### **ROMCLK:**

| BISB | #2,@SEL1      | ;SET ROMI       |

|------|---------------|-----------------|

| MOV  | (R5)+,@BSEL 6 | SET INSTRUCTION |

| BISB | #3,@BSEL1     | ;CLOCK INSTR.   |

| BICB | #7,@BSEL1     | ;CLEAR          |

| RTS  | R5            |                 |

\*\*\*\*\*\* \*\*\*\*\*\*\*\*\*\*\*\* .\*: ;\*CRCR ROUTINE TO TAKE 16 BITS OF DATA AND CONVERT THEM \* INTO PART OF A SERIAL STREAM THAT WE'RE CALCULATING A CRC-CCITT WORD FROM. CALL=JSR PC,CRC ENTER WITH 16 BITS IN WORDT EXIT WITH 16 BIT WORD IN CWORD NOTE:: CWORD MUST HAVE BEEN INITED TO -1 PRIOR TO ;\* FIRST CALLING THIS ROUTINE .\*\* \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

| CRCR: | MOV | R1,-(SP)         | ;SAVE GEN REGS R1,R2 |

|-------|-----|------------------|----------------------|

|       | MOV | R2,-(SP)         |                      |

|       | MOV | #16., <b>R</b> 2 |                      |

10\$

20\$

| CLC |                     |

|-----|---------------------|

| ROR | CWORD               |

| ROR | WORDT               |

| BVC | 20\$                |

| MOV | #102010, <b>R</b> 1 |

| BIC | CWORD,R1            |

| BIC | #102010,CWORD       |

| BIS | R1,CWORD            |

| DEC | R2                  |

| BGT | 10\$                |

| MOV | (SP)+,R2            |

| MOV | (SP)+,R1            |

# ;CRC/CCITT POLYNOMIAL

;RESTORE GEN REGS

RTS PC

;EXIT

# APPENDIX A MICRODIAGNOSTIC TESTS

# A.1 INTRODUCTION

The microdiagnostics contained in this Appendix were written for the M8207 Microprocessor. The following tests are recommended for all M8207 applications.

#### NOTE

#### The microdiagnostics provided in this section are EXAMPLES and are not to be construed as the ONLY IMPLEMENTATION.

### A.2 HARDWARE REQUIREMENTS

The following hardware is required to run the microdiagnostics.

- Central Processing Unit (CPU)

- M8207

- 16K Memory

#### A.3 RELATED SOFTWARE

Internal microdiagnostics need no external supporting software. Interface microdiagnostics for PDP-11s require "CZDMTC0 DMP11 FCTNL TST#1.

# A.4 INTERNAL MICRODIAGNOSTICS

- Internal microdiagnostics are written in KDA assembler format that run on initialization within the DMP11 subsystem. These diagnostics are go/nogo type.

- Errors are isolated to the module level. When an error is detected, the microdiagnostic attempts to insert an error number in BSEL4 and enter an infinite loop. The CPU software may test the run bit and error number at the end of the test, or a visual inspection can be performed by evaluation of the Control and Status Registers (CSRs).

- Good and bad data are entered in BSEL 3 and 5 when applicable.

- The current test number is entered in BSEL 6.

- Test numbers are not in sequential order.

#### NOTE

If a hardware failure prevents the microdiagnostics from reporting an error indication, some or all of the above will not occur.

# A.5 INTERNAL MICRODIAGNOSTIC TEST PROCEDURES

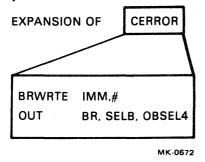

In the following microdiagnostic tests, CERROR is a macro that, when expanded, generates a current error number, outputs this number to BSEL 4, and increments the error number to identify the next error.

Example:

# A.5.1 Branch Test #1 – Branch False and Branch Always

Errors in this test may be caused by the failure of a BRWRTE instruction and/or the Arithmetic Logic Unit (ALU), as well as the branch not operating properly.

START:

|         | BRWRTE<br>OUT                                                                   | IMM,0<br>BR,SELB,OBSEL1                          | ;<br>;ZERO MASTER CLEAR BIT<br>;                                                                                                                                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBRANC: | BRWRTE<br>OUT<br>CERROR                                                         | IMM,143<br>BR,SELB,OBSEL6                        | ;SHOW BRANCH TEST<br>;<br>;ERROR #1 TO BSEL 4 IN CASE OF FAILURE                                                                                                                                                                                                                                        |

| DBR.F:  | BRWRTE<br>Z<br>BRWRTE<br>BR0<br>BRWRTE<br>BR1<br>BRWRTE<br>BR4<br>BRWRTE<br>BR7 | DBRERR<br>IMM,375<br>DBRERR<br>IMM,357<br>DBRERR | ;LOAD 0 IN BREG<br>;SHOULD NOT BRANCH, Z BIT CLEAR.<br>;SET ALL BUT BIT 0.<br>;NOW BRANCH ON BIT 0, IF ERROR.<br>;SET ALL BUT BIT 1.<br>;ONLY AN ERROR WILL CAUSE A BRANCH.<br>;SET ALL BUT BIT 4.<br>;ONLY AN ERROR WILL CAUSE A BRANCH.<br>;SET ALL BUT BIT 7.<br>;ONLY AN ERROR WILL CAUSE A BRANCH. |

|         | ALWAYS I                                                                        | DBRFE                                            | ,<br>;NOW BRANCH TO END OF TEST.<br>;IF BRANCH ALWAYS FAILS, END UP IN<br>;ERROR ROUTINE                                                                                                                                                                                                                |

| DBRERR: | ALWAYSI                                                                         | DBRERR                                           | ;<br>;LOOP HERE ALWAYS                                                                                                                                                                                                                                                                                  |

| DBRFE:  |                                                                                 |                                                  | ;END OF TEST<br>;                                                                                                                                                                                                                                                                                       |

**A.5.2** Branch Test #2 – Branch True Errors in this test may be caused by the same failures defined in Test #1.

| DBR.T:     | BRWRTE | IMM,200               | ;SET BIT 7                                 |

|------------|--------|-----------------------|--------------------------------------------|

|            | BR7    | DBR.T2                | BR IF KNOWN SET                            |

|            | ALWAYS | DBRTER                | ELSE GOTO ERROR.                           |

| DBR.T2:    | BRWRTE | IMM,20                | ;SET BIT 4.                                |

|            | BR4    | DBR.T3                | ;BR IF KNOWN SET.                          |

|            | ALWAYS | DBRTER                | ;ELSE GOTO ERROR.                          |

| DBR.T3:    | BRWRTE | IMM,2                 | ;SET BIT 1                                 |

|            | BR 1   | DBR.T4                | ;BR IF KNOWN SET.                          |

|            | ALWAYS | DBRTER                | ;ELSE GOTO ERROR.                          |

| DBR.T4:    | BRWRTE | IMM,1                 | ;SET BIT 0                                 |

|            | BR0    | DBR.T5                | ;BR IF KNOWN SET.                          |

|            | ALWAYS | DBRTER                | ;ELSE GOTO ERROR.                          |

| DBR.T5:    | SP     | IMM,377, <b>SP</b> 17 | ;SET ALL BITS, CAUSE Z BIT SET.            |

|            | Z      | DBR.T6                | ;BR IF Z BIT SET.                          |

|            | ALWAYS | DBRTER                | ;                                          |

| DBR.T6:    | SP     | BR,INCA,SP17          | ;SET "C" (CARRY BIT).                      |

|            | С      | DBR.T7                | ;BR IF C BIT SET.                          |

|            | ALWAYS | DBRTER                | ;ELSE GOTO ERROR.                          |

| DBR.T7:    | ALWAYS | DBR.T8                | ;DOUBLE CHECK THAT BR ALWAYS WORKS         |

| DBRTER:    |        |                       |                                            |

| D DICI LIC | CERROR |                       | ,<br>;ERROR #2 IF BRANCH TEST (TRUE) FAILS |