# Preliminary Engineering Specification for the KA650-AA PROCESSOR MODULE

specification V1.00 18 April 1986

Gary Lidington Digital Equipment Corporation MLO5-5/E71 DTN 223-3771

# RESTRICTED DISTRIBUTION

# COMPANY CONFIDENTIAL RESTRICTED DISTRIBUTION COPYRIGHT (c) 1986 by DIGITAL EQUIPMENT CORPORATION

This information shall not be disclosed to non-Digital personnel or generally distributed within Digital. Distribution is restricted to persons authorized and designated by the responsible engineer or manager. This document shall not be left unattended, and when not in use shall be stored in a locked storage container.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may occur in this document.

The information in this document does not describe any program or product currently available from Digital Equipment Corporation. Nor does Digital Equipment Corporation commit to implement this specification in any program or product. Digital Equipment Corporation makes no commitment that this document accurately describes any product which it might ever make.

# CONTENTS

| 1       | INTRODUCTION                             | 8  |

|---------|------------------------------------------|----|

| 1.1     | Scope Of Document                        | 8  |

|         |                                          | 0  |

| 1.2     | Applicable Documents                     | 0  |

| 2       | GENERAL DESCRIPTION                      | 9  |

| 2.1     | KA650-AA Module Summary                  | 9  |

| 2.2     | MS650 Module Summary                     | 10 |

| 3       | KA650-AA CENTRAL PROCESSOR               | 12 |

| 3.1     | Processor State                          | 12 |

|         |                                          | 12 |

| 3.1.1   | General Purpose Registers                |    |

| 3.1.2   |                                          | 13 |

| 3.1.3   |                                          | 14 |

| 3.1.3.1 | KA650-AA VAX Standard Internal Processor |    |

|         |                                          | 16 |

| 3.1.3.2 | Registers                                | 16 |

|         | Discos characterist ricessor registers   |    |

| 3.2     | Process Structure                        | 17 |

| 3.3     | Data Types                               | 17 |

| 3.4     | Instruction Set                          | 17 |

| 3.5     | Memory Management                        | 18 |

| 3.5.1   | Translation Buffer                       | 19 |

| 3.5.2   | Memory Management Control Registers      | 19 |

|         |                                          |    |

| 3.6     | Exceptions And Interrupts                | 20 |

| 3.6.1   | Interrupts                               | 20 |

| 3.6.2   |                                          | 23 |

| 3.6.3   | Machine Check Parameters                 | 24 |

| 3.6.4   |                                          | 25 |

| 3.6.5   |                                          | 28 |

|         |                                          |    |

| 3.7     |                                          | 28 |

| 3.8     |                                          | 29 |

| 3.9     | System Identification                    | 29 |

| 3.10    | CPU References                           | 30 |

| 3.10.1  |                                          | 30 |

| 3.10.2  |                                          | 30 |

| 3.10.3  |                                          | 31 |

| -       |                                          |    |

| 4       |                                          | 32 |

| 4.0.1   |                                          | 32 |

| 4.0.2   | Floating Point Accelerator Data Types    | 32 |

| 5       | KA650-AA CACHE MEMORY                    | 33 |

| 5.1     | Cacheable References                     | 33 |

| 5.2     |                                          | 33 |

| 5.2.1   |                                          | 34 |

| 5.2.2   |                                          |    |

|         |                                          | 35 |

| 5.2.3   |                                          | 38 |

| 5.2.4   |                                          | 38 |

| 5.2.5   | Cache Disable Register (IPR 37)          | 38 |

| 5.2.6   | Cache Disable Register (IPR 37)          | 40 |

| 5.2.7   |                                          | 41 |

| 5.3     |                                          | 42 |

|         |                                          |    |

| 5.3.1   |                                          | 42 |

| 5.3.2   |                                          | 44 |

| 5.3.3   | Second-Level Cache Data Block Allocation | 47 |

| 5.3.4   | Second-Level Cache Behavior On Writes    | 47 |

| 5.3.5   |                                          | 47 |

| 5.3.6   |                                          | 48 |

|         |                                          |    |

| 5.3.7   | 4                                        | 49 |

| 5.3.8   |                                          | 50 |

| 6       | KA650-AA PROCESSOR MAIN MEMORY SYSTEM    | 52 |

| 6.1                | Main Memory Organization                                                              |          |

|--------------------|---------------------------------------------------------------------------------------|----------|

| 6.2                | Main Memory Addressing                                                                | 52       |

| 6.3<br>6.4         | Main Memory Behavior On Writes                                                        | 53       |

| 6.5                | Configuring Main Memory                                                               | 53       |

| 0.5                | MAIN MEMORY CONFIGURATION REGISTERS (MEMOSRO -                                        | 54       |

| 6.6                | MEMCSR15)                                                                             | 56       |

| 6.7                | Main Moment Control And Discretic Ctatus                                              |          |

|                    | Register (MEMCSR17)                                                                   | 57       |

| 6.8                |                                                                                       | 00       |

| 7                  | KA650-AA CONSOLE SERIAL LINE                                                          | 62       |

| 7.1                | Console Registers                                                                     | 62       |

| 7.1.1              | Console Receiver Control/Status Register (IPR                                         | 62       |

| 7.1.2              | 32)                                                                                   | 63       |

| 7.1.3              | Console Transmitter Control/Status Register                                           | 0.5      |

|                    | (IPR 34)                                                                              | 64       |

| 7.1.4              |                                                                                       |          |

|                    | Break Response                                                                        |          |

| 7.3                | Baud Rate                                                                             |          |

| 7.4                |                                                                                       | 65       |

| 8<br>8.1           | KA650-AA TOY CLOCK AND TIMERS                                                         |          |

| 8.2                | Interval Timer                                                                        |          |

| 8.3                | Programmable Timers                                                                   |          |

| 8.3.1              | Timer Control Registers (TCR0-TCR1)                                                   |          |

| 832                | Timor Interval Pogisters (TTPO-TTP1)                                                  | 68       |

| 8.3.3              | Timer Next Interval Registers (TNIR0-TNIR1) .                                         | 68       |

| 8.3.4              | Timer Next Interval Registers (TIRO-TIRI)                                             | 69       |

| 9                  | KA650-AA PROCESSOR BOOT AND DIAGNOSTIC FACILITY .                                     | 70       |

| 9.1                | Boot And Diagnostic Register (BDR)                                                    | 70       |

| 9.3                | Diagnostic LED Register                                                               | 72       |

| 9.3.1              | ROM Socket                                                                            | 72       |

| 9.3.2              | ROM Address Space                                                                     | 72       |

| 9.3.3              | KA650-AA Console Program Operation                                                    | 73       |

| 9.3.3.1            | Power Up Modes                                                                        | 74       |

|                    | Battery Backed-up RAM                                                                 | 74       |

| 9.5                | KA650-AA Initialization                                                               | 75       |

| 9.5.1<br>9.5.2     | Power-Up Initialization                                                               | 75<br>75 |

| 9.5.3              |                                                                                       | 75       |

| 9.5.3.1            | I/O Bus Reset Register (IPR 55)                                                       | 75       |

| 9.5.4              |                                                                                       | 75       |

| 9.5.4.1            |                                                                                       | 76       |

| 9.5.5              | SSC Base Address Register (SSCBR)                                                     | 76       |

| 9.5.6              |                                                                                       | 76       |

| 9.5.7<br>9.5.8     |                                                                                       | 77<br>77 |

| 9.5.9              | BDR Address Decode Match Register (BDMTR)<br>BDR Address Decode Mask Register (BDMKR) | 77       |

| 9.5.10             | SSC Configuration Register (SSCCR)                                                    | 78       |

| 9.6                | CDAL Bus Timeout Control Register (CBTCR)                                             |          |

| 10                 | KA650-AA Q22-BUS INTERFACE                                                            | 81       |

| 10.1               | Q-22 Bus To Main Memory Address Translation                                           | 82       |

| 10.1.1             | Q-22 Bus Map Registers (QMR's)                                                        | 83       |

| $10.1.2 \\ 10.1.3$ | Accessing The Q-22 Bus Map Registers                                                  | 04<br>85 |

| 10.1.3             | CDAL Bus To Q-22 Bus Address Translation                                              | 86       |

|                    |                                                                                       |          |

| 10.3<br>10.3.1<br>10.3.2<br>10.4<br>10.5<br>10.5.1<br>10.6<br>10.7<br>10.8<br>10.9<br>10.10<br>11<br>11.1<br>11.2<br>11.3<br>11.4 | KA650-AA Based Multi-Processor Systems 98<br>PDP-11 Based Multi-Processor Systems 99                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPENDIX A                                                                                                                        | KA650-AA PHYSICAL SPECIFICATIONS (PINOUTS/CONNECTORS)                                                                                                                            |

| A.2.5<br>A.3                                                                                                                      | DIMENSIONS                                                                                                                                                                       |

| APPENDIX B                                                                                                                        | KA650-AA ELECTRICAL SPECIFICATIONS                                                                                                                                               |

|                                                                                                                                   | DC POWER CONSUMPTION                                                                                                                                                             |

| APPENDIX C                                                                                                                        | KA650-AA ENVIRONMENTAL AND RELIABILITY SPECIFICATIONS                                                                                                                            |

| C.1<br>C.2<br>C.3                                                                                                                 | STORAGE CONDITIONS                                                                                                                                                               |

| APPENDIX D                                                                                                                        | KA650-AA ADDRESS ASSIGNMENTS                                                                                                                                                     |

| D.2<br>D.3                                                                                                                        | KA650-AA GENERAL LOCAL ADDRESS SPACE MAP D-1<br>KA650-AA DETAILED LOCAL ADDRESS SPACE MAP D-3<br>EXTERNAL, INTERNAL PROCESSOR REGISTERS D-7<br>GLOBAL Q-22 BUS ADDRESS SPACE MAP |

APPENDIX E KA650-AA INSTRUCTION SET

APPENDIX F KA650-AA ERROR MATRICES

KA650-AA Processor Module Engineering Specification V1.00 Page 7 18 April 1986

# REVISION HISTORY

| REV  | DATE        | AUTHOR         | REASON                                        |

|------|-------------|----------------|-----------------------------------------------|

| 0.00 | 20-DEC-1985 | Charlie Devane | First draft document for review               |

| 0.01 | 11-MAR-1986 | Gary Lidington | Preliminary draft for<br>first design review. |

| 1.00 | 18-APR-1986 | Gary Lidington | First draft for general review.               |

KA650-AA Processor Module Engineering Specification V1.00 Page 8 INTRODUCTION 18 April 1986

#### 1 INTRODUCTION

#### 1.1 Scope Of Document

This specification documents the functional, physical and environmental characteristics of the KA650-AA Processor Module. It should be used along with the VAX Architecture Standard (DEC STD 032) to provide a complete programmer's reference to the module.

Some information on the MS650 memory expansion modules is also provided. These modules are documented more completely in the MS650 Memory Module Specification.

# 1.2 Applicable Documents

The following reference material contains detailed information regarding the VAX-11 family, the KA650-AA module, and the required environment.

- o KA650-AA Console Program Specification

- o MS650 Memory Module Specification

- o CVAX CPU Chip Engineering Specification

- o CVAX Clock Chip Engineering Specification

- o CVAX FPU Chip Engineering Specification

- o CVAX Memory Controller Chip Engineering Specification

- o CVAX Q22-Bus Interface Chip Engineering Specification

- o MicroVAX System Support Chip Functional Specification

- o VAX Architecture Handbook

- o VAX Software Handbook

- o VAX Hardware Handbook

- o DEC STD 032 VAX Architecture Standard

- o DEC STD 102 Environmental Specification

- o DEC STD 160 Q-Bus Specification

KA650-AA Processor Module Engineering Specification V1.00 Page 9 GENERAL DESCRIPTION 18 April 1986

### 2 GENERAL DESCRIPTION

The KA650 CPU module and MS650 memory modules combine to form a VAX CPU/Memory subsystem which uses the Q22-Bus to communicate with mass storage and I/O devices. The KA650 and MS650 modules mount in standard Q22-Bus backplane slots which implement the Q22-Bus in the AB rows and the CD interconnect in the CD rows. These modules communicate via the MS650 Memory Interconnect, which utilizes the CD interconnect and a 50-pin ribbon cable. A single KA650 module can support up to four MS650 modules, provided that sufficient Q22/CD slots are available.

The KA650 may be configured as either an arbiter or auxilliary CPU. Every system must contain an arbiter, which always resides in the first backplane slot. This arbiter CPU arbitrates Q22-Bus mastership and fields Q22-Bus interrupt requests plus any on-board interrupt requests. Systems with a sufficient number of Q22/CD slots can also support up to three auxiliary KA650 modules. An auxilliary CPU module can only field its own on-board interrupts. To access the Q22-Bus, an auxilliary CPU must request bus mastership from the arbiter.

The KA650 communicates with the console device via the CPU rear I/O distribution insert, which also contains configuration switches and a LED display.

Estimated compute performance for the CPU/Memory subsystem is 2.5 times a VAX 11/780.

# 2.1 KA650-AA Module Summary

The KA650-AA consists of a single, quad height, Q22-Bus module (M7620-AA) that uses six new in-house VLSI chips implement the following functionality:

- o A VAX central processor that supports the MicroVAX chip subset of the VAX instruction set and data types, as well as full VAX memory management with demand paging and 4GB of virtual memory.

- A floating point accelerator with the MicroVAX chip subset of the VAX floating point instruction set and data types.

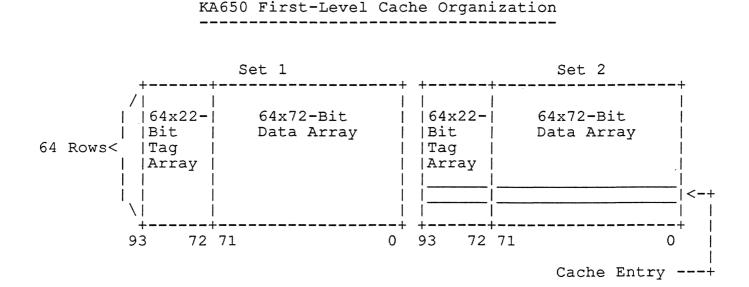

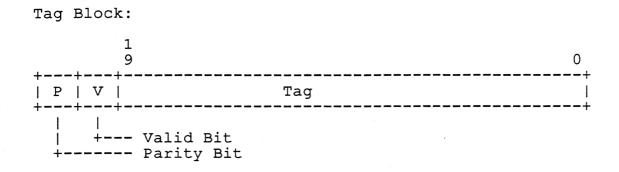

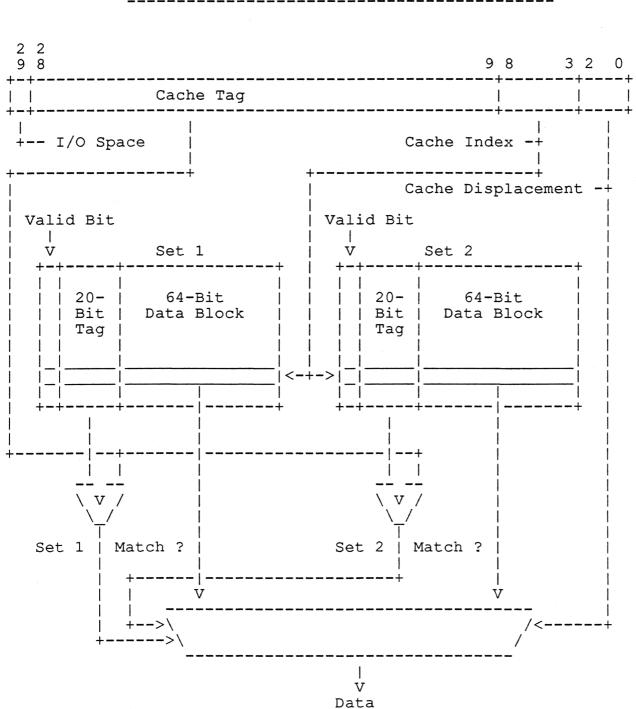

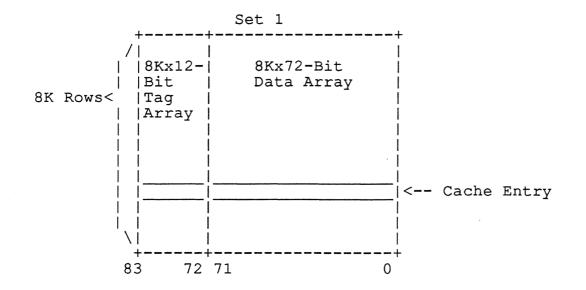

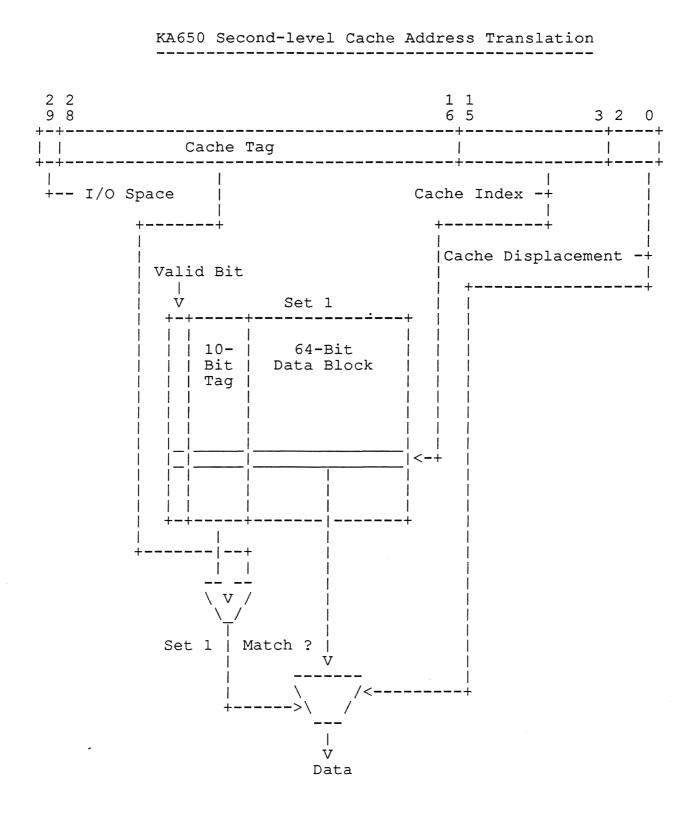

- o A two-level cache consisting of a 1KB, 100ns, first-level cache and a 64KB, 200ns, second-level cache. Both caches provide parity protection on the tag and data stores.

- o A main memory controller that supports up to 64MB of 400ns, ECC memory, that resides on one to four MS650 memory modules, depending on the system configuration.

- A VAX compatible console port whose baud rate can be set via an external switch located on the CPU rear I/O distribution insert.

KA650-AA Processor Module Engineering Specification V1.00 Page 10 GENERAL DESCRIPTION 18 April 1986

- o A set of processor clock registers that support:

- A VAX standard Time Of Year (TOY) clock with support for battery back-up (Batteries are located on the CPU rear I/O distribution insert.)

- An interval timer with 10Ms interrupts.

- Two programmable timers, similar in function to the VAX standard interval timer.

- o A boot and diagnostic facility with four on-board LED's and support for an external 4-bit display and configuration switches located on the CPU rear I/O distribution insert, and 64KB of byte-wide ROM containing programs for:

- Board initialization.

- Emulation of a subset of the VAX standard console.

- Power-up self-testing of the KA650 and MS650 modules.

- Booting from supported Q22-Bus devices.

- o A Q22-Bus interface that supports up to 16-word, block mode transfers between a Q22-Bus DMA device and main memory, and up to 2-word, block mode transfers between the CPU and Q22-Bus devices. This interface contains:

- A 16-entry map cache for the 8,192 entry, main memory resident, "scatter-gather" map, which is used for translating 22-bit, Q22-Bus addresses into 26-bit, main memory addresses.

- Interrupt arbitration logic that recognizes Q22-Bus interrupt requests BR7-BR4.

- An interprocessor communication facility that supports communication between the Q22-Bus arbiter and up to three auxiliary processors via "doorbell" interrupts.

- 240 ohm termination

### 2.2 MS650 Module Summary

MS650 memory options come in two variations. Each option consists of a single, quad height, Q22-Bus module. The difference between options is the array size, which is dependent on the number, density, and packaging style of the RAM chips used. The two variations are listed below: KA650-AA Processor Module Engineering Specification V1.00 Page 11 GENERAL DESCRIPTION 18 April 1986

- o MS650-AA (M7621-A) An 8MB, 400ns, 39-bit wide array (32-bit data and 7-bit ECC) implemented with 256Kb dynamic RAMS in zig-zag in-line packages (ZIPS).

- o MS650-BA (M7622-A) A 16MB, 400ns, 39-bit wide array (32-bit data and 7-bit ECC) implemented with 1Mb dynamic RAMS in dual in-line packages (DIPS).

KA650-AA Processor Module Engineering Specification V1.00 Page 12 KA650-AA CENTRAL PROCESSOR 18 April 1986

#### 3 KA650-AA CENTRAL PROCESSOR

The central processor of the KA650-AA supports the MicroVAX Chip subset of the VAX instruction set and data types and full VAX memory management. It is implemented via a single VLSI chip called the CVAX.

### 3.1 Processor State

The processor state consists of that portion of a process's state which is stored in processor registers rather than in memory. The processor state is composed of sixteen General Purpose Registers (GPR's), the Processor Status Longword (PSL), and the Internal Processor Registers (IPR's).

Non-privileged software can access the GPR's and the Processor Status Word (bits 15:00 of the PSL). The IPR's and bits 31:16 of the PSL can only be accessed by privileged software. The IPR's are explicitly accessible only by the the Move To Processor Register (MTPR) and Move From Processor Register (MFPR) instructions which require kernal mode privileges.

#### 3.1.1 General Purpose Registers

The KA650-AA implements 16 General Purpose Registers per DEC STD 032. These registers are used for temporary storage, accumulators, and base and index registers for addressing. These registers are denoted R0 - R15. The bits of a register are numbered from the right <0> through <31>.

| 3 |       |

|---|-------|

| 1 | 0     |

| + | <br>+ |

| 1 | 1     |

| + | <br>+ |

Certain of these registers have been assigned special meaning by the VAX-11 architecture:

- o R15 is the program counter (PC). The PC contains the address of the next instruction byte of the program.

- o R14 is the stack pointer (SP). The SP contains the address of the top of the processor defined stack.

- o R13 is the current frame pointer (FP). The VAX-11 procedure call convention builds a data structure on the stack called a stack frame. The FP contains the address of the base of this data structure.

- o R12 is the argument pointer (AP). The VAX-11 procedure call convention uses a data structure termed an argument list. The AP contains the address of the base of this data structure.

KA650-AA Processor Module Engineering Specification V1.00 Page 13 KA650-AA CENTRAL PROCESSOR 18 April 1986

DEC STD 032 should be consulted for more information on the operation and use of these registers.

### 3.1.2 Processor Status Longword

The KA650-AA Processor Status Longword (PSL) is implemented per the DEC STD 032, which should be consulted for a detailed description of the operation of this register. The PSL is saved on the stack when an exception or interrupt occurs and is saved in the Process Control Block (PCB) on a process context switch. Bits 15:00 may be accessed by non-privileged software, while bits 31:16 may only be accessed by privileged software. Processor initialization sets the PSL to 041F 0000 (hex).

| 33<br>10<br>+-+- | ) 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | r<br>Mariana<br>Jacob |   | - | 1<br>5 |     |       |   |      |       | 1  |    |  |

|------------------|-----|---|---|---|---|---|---|---|---|---|-----------------------|---|---|--------|-----|-------|---|------|-------|----|----|--|

| 11               | 1   | 1 | F | 1 |   |   | 2 |   | M |   |                       |   |   |        |     | 1     |   |      | 1     | ++ | 1  |  |

| C 1<br> M F      |     |   |   |   |   |   |   |   |   |   | IP                    | ۲ |   |        | MBZ | •     | • |      | <br>• | vI | •  |  |

| +-+-             | -+  |   | + | + |   |   |   |   | + |   |                       |   |   | +      |     | <br>+ |   | <br> | <br>+ | +  | -+ |  |

PSL<31> (CM) Compatibility Mode. This bit always reads as zero, loading a "1" into this bit is a NOP.

#### NOTE

VAX Compatibility Mode Instructions can be emulated by macrocode, but the emulation software runs in native mode, so the CM bit is never set.

PSL<30> (TP) Trace Pending.

PSL<29:28> Unused, must be written as zero.

PSL<27> (FPD) First Part Done.

PSL<26> (IS) Interrupt Stack.

PSL<25:24> (CUR) Current Mode.

PSL<23:22> (PRV) Previous Mode.

PSL<21> Unused, must be written as zero.

PSL<20:16> (IPL) Interrupt Priority Level.

PSL<15:8> Unused, must be written as zero.

PSL<7> (DV) Decimal Overflow Trap Enable. This read/write bit has no effect on KA650-AA hardware; it can be used by macrocode which emulates VAX decimal instructions.

KA650-AA Processor Module Engineering Specification V1.00 Page 14 KA650-AA CENTRAL PROCESSOR 18 April 1986

- PSL<6> (FU) Floating Underflow Fault Enable.

- PSL<5> (IV) Integer Overflow Trap Enable.

- PSL<4> (T) Trace Trap Enable.

- PSL<3> (N) Negative Condition Code.

- PSL<2> (Z) Zero Condition Code.

- PSL<1> (V) Overflow Condition Code.

- PSL<0> (C) Carry Condition Code.

- 3.1.3 Internal Processor Registers

The KA650-AA Internal Processor Registers (IPR's) can be accessed by using the MFPR and MTPR privileged instructions. Each IPR falls into one of the following five categories:

- 1= Implemented by KA650-AA as specified in the VAX Architecture Standard (DEC STD 032)

- 2= Implemented by KA650-AA uniquely.

- 3= Not implemented, read as zero, nop on write.

- 4= Access not allowed; accesses result in a reserved operand fault.

- 5= Accessible, but not fully implemented, accesses yield UNPREDICTABLE results.

A table listing each of the KA650-AA IPR's with it's Mnemonic, its access type (read or write) and it's category number appears below. A list of Category One IPR's and the section where they are referenced is given in section 3.1.3.1. A list of Category Two registers and the section where they are described in full is given in section 3.1.3.2.

An "I" following the category number in the table below indicates that the register is initialized on power-up and by the negation of DCOK. KA650-AA Processor Module Engineering Specification V1.00Page 15KA650-AA CENTRAL PROCESSOR18 April 1986

| Number                                                                                                  | Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mnemonic                                      | Туре                                                                   | Category                                                                               |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br><7:5>                                                                          | Kernel Stack Pointer<br>Executive Stack Pointer<br>Supervisor Stack Pointer<br>User Stack Pointer<br>Interrupt Stack Pointer<br>reserved                                                                                                                                                                                                                                                                                                                              | KSP<br>ESP<br>SSP<br>USP<br>ISP               | r/w<br>r/w<br>r/w<br>r/w<br>r/w                                        | 1<br>1<br>1<br>1<br>3                                                                  |

| 8<br>9<br>10<br>11<br>12<br>13<br><14:15>                                                               | PO Base Register<br>PO Length Register<br>P1 Base Register<br>P1 Length Register<br>System Base Register<br>System Length Register<br>reserved                                                                                                                                                                                                                                                                                                                        | POBR<br>POLR<br>P1BR<br>P1LR<br>SBR<br>SLR    | r/w<br>r/w<br>r/w<br>r/w<br>r/w                                        | 1                                                                                      |

| 16<br>17<br>18<br>19<br>20<br>21<br><23:22>                                                             | Process Control Block Base<br>System Control Block Base<br>Interrupt Priority Level<br>AST Level<br>Software Interrupt Request<br>Software Interrupt Summary<br>reserved                                                                                                                                                                                                                                                                                              | PCBB<br>SCBB<br>IPL<br>ASTLVL<br>SIRR<br>SISR | r/w<br>r/w<br>r/w<br>w<br>r/w                                          | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>3                                                   |

| 24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br><41:40> | Interval Clock Control/Status<br>Next Interval Count<br>Interval Count<br>Time Of Year<br>Console Storage Receiver Statu<br>Console Storage Receiver Data<br>Console Storage Transmit Statu<br>Console Storage Transmit Data<br>Console Receiver Control/Statu<br>Console Receiver Data Buffer<br>Console Transmit Control/Statu<br>Console Transmit Data Buffer<br>Translation Buffer Disable<br>Cache Disable<br>Machine Check Error Summary<br>Memory System Error | CSRD<br>S CSTS<br>CSTD<br>S RXCS<br>RXDB      | r/w<br>w<br>r/w<br>r/w<br>r/w<br>r/w<br>r/w<br>r/w<br>r/w<br>r/w<br>r/ | 2I<br>3<br>3<br>1<br>5I<br>5I<br>5I<br>2I<br>2I<br>2I<br>2I<br>3<br>2I<br>3<br>2I<br>3 |

| 42<br>43<br><47:44>                                                                                     | Console Saved PC<br>Console Saved PSL<br>reserved                                                                                                                                                                                                                                                                                                                                                                                                                     | SAVPC<br>SAVPSL                               | r<br>r                                                                 | 2<br>2<br>3                                                                            |

| 48<br>39<br>50<br>51<br>52                                                                              | SBI Fault/Status<br>SBI Silo<br>SBI Silo Comparator<br>SBI Maintenance<br>SBI Error Register                                                                                                                                                                                                                                                                                                                                                                          | SBIFS<br>SBIS<br>SBISC<br>SBIMT<br>SBIER      | r/w<br>r<br>r/w<br>r/w<br>r/w                                          | 3<br>3<br>3<br>3<br>3                                                                  |

KA650-AA Processor Module Engineering Specification V1.00 Page 16 KA650-AA CENTRAL PROCESSOR 18 April 1986

| 53<br>54<br>55                               | SBI Timeout Address Register<br>SBI Quadword Clear<br>IO Bus Reset                                                                                                                        | SBITA<br>SBIQC<br>IORESET                                      |                                         | 3<br>3<br>2                |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------|----------------------------|

| 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63 | Memory Management Enable<br>TB Invalidate All<br>TB Invalidate Single<br>TB Data<br>Microprogram Break<br>Performance Monitor Enable<br>System Identification<br>Translation Buffer Check | MAPEN<br>TBIA<br>TBIS<br>TBDATA<br>MBRK<br>PMR<br>SID<br>TBCHK | r/w<br>w<br>r/w<br>r/w<br>r/w<br>r<br>w | 1<br>1<br>3<br>3<br>1<br>1 |

| 64 <b>:</b> 127                              | and all those not listed - reser                                                                                                                                                          | rved                                                           |                                         | 4                          |

### 3.1.3.1 KA650-AA VAX Standard Internal Processor Registers

Internal Processor Registers (IPR's) which are implemented per DEC STD 032 are classified as Category One IPR's. DEC STD 032 should be consulted for details on the operation and use of these registers.

The following category one registers are also referenced in other sections of this specification:

| Number | Register Name                 | Mnemonic | Section |

|--------|-------------------------------|----------|---------|

|        |                               |          |         |

| 12     | System Base Register          | SBR      | 3.5.2   |

| 13     | System Length Register        | SLR      | 3.5.2   |

| 16     | Process Control Block Base    | PCBB     | 3.2     |

| 17     | System Control Block Base     | SCBB     | 3.6.4   |

| 18     | Interrupt Priority Level      | IPL      | 3.6.1   |

| 20     | Software Interrupt Request    | SIRR     | 3.6.1   |

| 21     | Software Interrupt Summary    | SISR     | 3.6.1   |

| 27     | Time Of Year Clock            | TODR     | 8.1     |

| 56     | Memory Management Enable      | MAPEN    | 3.5.2   |

| 57     | Trans. Buffer Invalidate All  | TBIA     | 3.5.2   |

| 58     | Trans. Buffer Invalidate Sing | . TBIS   | 3.5.2   |

| 62     | System Identification         | SID      | 3.9     |

| 63     | Translation Buffer Check      | TBCHK    | 3.5.2   |

# 3.1.3.2 KA650-AA Unique Internal Processor Registers

Internal Processor Registers (IPR's) which are implemented uniquely on the KA650-AA (i.e. they are not contained in, or do not fully conform to DEC STD 032) are classified as Category Two IPR's and are described in detail in this specification. Refer to the following sections for a description of these registers: KA650-AA Processor Module Engineering Specification V1.00Page 17KA650-AA CENTRAL PROCESSOR18 April 1986

| Number                                                   | Register Name                                                                                                                                                                                                                                                        | Mnemonic | Section                                                                                                |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------|

| 24<br>32<br>33<br>34<br>35<br>37<br>39<br>42<br>43<br>55 | Interval Clock Control/Status<br>Console Receiver Control/Status<br>Console Receiver Data Buffer<br>Console Transmit Control/Status<br>Console Transmit Data Buffer<br>Cache Disable<br>Memory System Error<br>Console Saved PC<br>Console Saved PSL<br>IO Bus Reset | RXDB     | $\begin{array}{c} 8.2\\ 7.1.1\\ 7.1.2\\ 7.1.3\\ 7.1.4\\ 5.1.5\\ 5.1.6\\ 3.7\\ 3.7\\ 9.5.1 \end{array}$ |

3.2 Process Structure

A process is a single thread of execution. The context of the current process is contained in the Process Control Block (PCB) which is pointed to by the Process Control Block Base Register (PCBB). The KA650-AA implements these structures as defined in DEC STD 032, which should be referenced for a description of the PCB and the PCBB.

3.3 Data Types

The KA650-AA CPU supports the following subset of the VAX data types:

1. byte

2. word

3. longword

4. quadword

5. character string

6. variable length bit field

Support for the remaining VAX data types can be provided via macrocode emulation.

3.4 Instruction Set

The KA650-AA CPU implements the following subset of the VAX instruction set types in microcode.

1. Integer arithmetic and logical

KA650-AA Processor Module Engineering Specification V1.00 Page 18 KA650-AA CENTRAL PROCESSOR 18 April 1986

- 2. Address

- 3. Variable length bit field

- 4. Control

- 5. Procedure call

- 6. Miscellaneous

- 7. Queue

- 8. Character string moves (MOVC3 and MOVC5)

- 9. Operating system support,

- 10. F floating

11. G floating

12. D floating

The KA650-AA CVAX chip provides special microcode assistance to aid the macrocode emulation of the following instruction groups:

- 1. Character string (except MOVC3 and MOVC5)

- 2. Decimal string

- 3. CRC

- 4. EDITPC

The following instruction groups are not implemented, but may be emulated by macrocode:

- 1. Octaword

- 2. Compatibility Mode Instructions

Appendix E lists the entire KA650-AA instruction set, indicating which instructions are implemented in the Floating Point Accelerator FPA, and which instructions have microcode assists to speed up macrocode emulation.

#### 3.5 Memory Management

The KA650-AA implements full VAX Memory Management as defined in DEC STD 032. System Space addresses are virtually mapped through single-level page tables, and process space addresses are virtually mapped through two-level page tables. See DEC STD 032 for descriptions of the virtual to physical address translation process, and the format for VAX Page Table Entries (PTE's).

KA650-AA Processor Module Engineering Specification V1.00 Page 19 KA650-AA CENTRAL PROCESSOR 18 April 1986

# 3.5.1 Translation Buffer

To reduce the overhead associated with translating virtual addresses to physical addresses, the KA650-AA employs a 32-entry, fully associative, translation buffer for caching modified VAX PTE's. Each entry can store a modified PTE for translating virtual addresses in either the VAX Process Space, or VAX System Space.

Each entry is divided into two parts: a 23-bit Tag Register and a 31-bit PTE Register. The Tag Register is used to store the Virtual Page Number (VPN) of the virtual page that the corresponding PTE Register maps. The PTE register stores the 21-bit PFN field, the PTE.V bit, the PTE.M bit and an 8-bit partially decoded representation of the 4-bit VAX PTE PROT field, from the corresponding VAX PTE, as well as a Translation Buffer Valid (TB.V) bit. The CVAX CPU Design Spec can be referenced for details of the 8-bit PROT field.

During virtual to physical address translation, the contents of the 32 Tag Registers are compared with the Virtual Page Number Field (bits <31:9>) of the virtual address of the reference. If there is a match with one of the Tag Registers, then a translation buffer "hit" has occured, and the contents of the corresponding PTE register is used for the translation.

If there is no match, the translation buffer does not contain the necessary VAX PTE information to translate the address of the reference, and the PTE must be fetched from memory. Upon fetching the PTE, the translation buffer is updated by replacing the entry that is selected by the replacement pointer. Since this pointer is moved to the next sequential translation buffer entry whenever it is pointing to an entry that is accessed, the replacement algorithm is Not Last Used (NLU).

#### 3.5.2 Memory Management Control Registers

There are four IPR's that control the Memory Management Unit (MMU): IPR 56 (MAPEN), IPR 57 (TBIA), IPR 58 (TBIS) and IPR 63 (TBCHK).

Memory management can be enabled/disabled via IPR 56 (MAPEN). Writing "0" to this register with a MTPR instruction disables memory management and writing a "1" to this register with a MTPR instruction enables memory management. To determine whether or not memory management is enabled, IPR 56 is read using the MFPR instruction.

### NOTE

Whenever memory management is disabled, the contents of translation buffer are UNPREDICTABLE. Therefore, before enabling memory management during processor initialization, or any other time, the entire translation buffer must be cleared by software.

Translation buffer entries that map a particular virtual address can

KA650-AA Processor Module Engineering Specification V1.00 Page 20 KA650-AA CENTRAL PROCESSOR 18 April 1986

be invalidated by writing the virtual address to IPR 58 (TBIS) using the MTPR instruction.

#### NOTE

Whenever software changes a valid Page Table Entry for the system or current process region, or a System Page Table Entry that maps any part of the current process page table, all process pages so mapped must be invalidated in the translation buffer.

The entire translation buffer can be invalidated by writing a "0" to IPR 57 (TBIA) using the MTPR instruction.

#### NOTE

Whenever the location or size of the system map is changed by changing the SBR or SLR, the entire translation buffer must be cleared.

The translation buffer can be checked to see if it contains a valid translation for a particular virtual page by writing a virtual address within that page to IPR 63 (TBCHK) using the MTPR instruction. If the translation buffer contains a valid translation for the page, the condition code V bit (bit<1> of the PSL) is set.

NOTE

The TBIS, TBIA, and TBCHK IPR's are write only. The operation of a MFPR from any of these register is UNDEFINED.

# 3.6 Exceptions And Interrupts

Both exceptions and interrupts divert execution from the normal flow of control. An exception is caused by the execution of the current instruction and is typically handled by the current process (e.g. an arithmetic overflow), while an interrupt is caused by some activity outside the current process and typically transfers control outside the process (e.g. an interrupt from an external hardware device).

### 3.6.1 Interrupts

The VAX architecture specifies 31 interrupt levels which are used by the KA650-AA as follows:

KA650-AA Processor Module Engineering Specification V1.00 Page 21 KA650-AA CENTRAL PROCESSOR 18 April 1986

| Interrupt<br>Levels | Interrupt<br>Condition                                                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| non-maskable        | BHALT asserted on Q-22 Bus,<br>BREAK generated by console                                                                                           |

| 1F                  | unused                                                                                                                                              |

| 1E<br>1D            | BPOK negated on Q-22 Bus,<br>CDAL Bus parity error,<br>Q-22 Bus NXM on a write,<br>CDAL Bus timeout during DMA,<br>uncorrectable main memory errors |

| 1B - 1C             | unused                                                                                                                                              |

| 1A                  | 2nd-level cache tag parity errors, correctable main memory errors                                                                                   |

| 18 - 19             | unused                                                                                                                                              |

| 17                  | BR7 L asserted                                                                                                                                      |

| 16                  | Interval Timer Interrupt, BR6 L asserted                                                                                                            |

| 15                  | BR5 asserted                                                                                                                                        |

| 14                  | Console Terminal Interrupts, Programmable Timer<br>Interrupts, Interprocessor Doorbell Interrupts,<br>BR4 L asserted                                |

| 10 - 13             | unused                                                                                                                                              |

| 01 - OF             | software interrupt request                                                                                                                          |

|                     |                                                                                                                                                     |

#### NOTE

Because the Q22-Bus does not allow differentiation between the four bus grant levels (i.e a BR7 device could grab a level 4 bus grant), the KA650-AA CPU must set the IPL to 17 after responding to any interrupt request BR7-4. The IPL is set to 14 after a console terminal, programmable timer interrupt or interprocessor doorbell, and it is set to 16 after an interval timer interrupt.

#### NOTE

When the KA650-AA is configured as an auxiliary CPU it ignores Q22-Bus BR7-4 interrupt requests, but does

KA650-AA Processor Module Engineering Specification V1.00Page 22KA650-AA CENTRAL PROCESSOR18 April 1986

respond to IPL 14 requests from its own console serial line unit, programmable timers, and interprocessor doorbell (in that order of priority). It also responds to interrupt requests from its own interval timer at IPL 16.

The interrupt system is controlled by three IPR's: IPR 18, the Interrupt Priority Level Register (IPL), IPR 20, the Software Interrupt Request Register (SIRR), and IPR 21, the Software Interrupt Summary Register (SISR). The IPL is used for loading the processor priority field in the PSL (bits<20:16>. The SIRR is used for creating software interrupt requests. The SISR records pending software interrupt requests at levels 1 through 15. The format of these regiters is presented below, refer to DEC STD 032 for more information on these registers.

| 3<br>1      |            |                 |             | 5 4         | 0      |       |

|-------------|------------|-----------------|-------------|-------------|--------|-------|

| +           | ignored, i | returns 0       |             | +<br> PSL<2 | 20:16> | :IPL  |

| 3<br>1      |            |                 |             | 4 3         | 0      |       |

| +           | ignoi      | red             | ·           |             | equest | :SIRR |

|             |            |                 |             |             |        |       |

| 3<br>1<br>+ |            | 1 1<br>6 5<br>+ |             |             | 0      |       |

|             |            | Pendir          | ig Software | Interrup    | ts  M  |       |

|F E D C B A 9 8 7 6 5 4 3 2 1 | Z |

|B| :SISR

KA650-AA Processor Module Engineering Specification V1.00Page 23KA650-AA CENTRAL PROCESSOR18 April 1986

3.6.2 Exceptions

The VAX architecture recognizes six classes of exceptions.

Exception Class arithmetic traps/faults Instances

integer overflow trap integer divide by zero trap subscript range trap floating overflow fault floating divide by zero fault floating underflow fault

memory management exceptions

operand reference exceptions

instruction execution exceptions

tracing exception

system failure exceptions

access control violation fault translation not valid fault

reserved addressing mode fault reserved operand fault or abort

reserved/privileged instr. fault emulated instruction faults extended function fault breakpoint fault

trace fault

machine check abort (including CDAL Bus parity errors, cache parity errors, Q-22 Bus timeout errors, Q-22 Bus device parity errors, CDAL Bus timeout errors and main memory uncorrectable errors) kernel stack not valid abort interrupt stack not valid abort KA650-AA Processor Module Engineering Specification V1.00 Page 24 KA650-AA CENTRAL PROCESSOR 18 April 1986

3.6.3 Machine Check Parameters

In response to a machine check, the following parameters are pushed on the stack:

|   |                              | - おおおす際には合いそのもから                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | byte count (00000010 hex)    | :SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| - | machine check code           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| - | most recent virtual address  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| - | internal state information 1 | +<br>!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| - | internal state information 2 | Conservation and a service of the se |

| - | PC                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | PSL is .                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| - |                              | +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

The parameters are:

machine check code (hex):

| 1 |     | undefined MMGT.STATUS                        |

|---|-----|----------------------------------------------|

|   | =   | floating point protocol error                |

| 3 | -   | floating point reserved instruction          |

| 4 | =   | undefined MOVCx state                        |

| 5 |     | process PTE in PO space during TB miss flows |

| 6 | -   | process PTE in P1 space during TB miss flows |

|   | -   | process PTE in PO space during $M = 0$ flows |

| 8 | ==  | process PTE in P1 space during $M = 0$ flows |

| 9 | =   | undefined INT.ID value                       |

| 8 | 0 = | memory read error                            |

| 8 | 1 = | SCB, PCB, or SPTE read error                 |

| 8 | 2 = | memory write error                           |

| 8 | 3 = | SCB, PCB, or SPTE write error                |

most recent virtual address:

<31:0> = current contents of VAP register

internal state information 1:

| <31:24> | = | opcode                                    |

|---------|---|-------------------------------------------|

| <23:16> | = | 1111, highest priority software interrupt |

|         |   | <3:0>                                     |

| <15:8>  |   | CADR<7:0>                                 |

| <7:0>   |   | MSER<7:0>                                 |

internal state information 2:

<31:24> = most recent contents of SC register <7:0>

KA650-AA Processor Module Engineering Specification V1.00 Page 25 KA650-AA CENTRAL PROCESSOR 18 April 1986

| <pre>&lt;23:16&gt; = &lt;15:8&gt; = &lt;7:0&gt; =</pre> | <pre>11, state flags &lt;5:0&gt; restart flag, 111, ALU CC flags &lt;3:0&gt; offset from saved PC to PC at time of machine check</pre> |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| PC: <31:0> =                                            | PC at the start of the current instruction                                                                                             |

| PSL: <31:0> =                                           | current contents of PSL                                                                                                                |

3.6.4 System Control Block (SCB)

The System Control Block (SCB) is a page containing the vectors for servicing interrupts and exceptions. The SCB is pointed to by IPR 17, the System Control Block Base Register (SCBB).

| 332<br>109 |          |          |               | 9 8 | 0           |

|------------|----------|----------|---------------|-----|-------------|

| MBZ        | physical | longword | address of PC | Bİİ | MBZ   :SCBB |

| ++         |          |          |               |     | +           |

KA650-AA Processor Module Engineering Specification V1.00Page 26KA650-AA CENTRAL PROCESSOR18 April 1986

The System Control Block format:

| vector | name                               | type pa                        | aram | notes                                          |

|--------|------------------------------------|--------------------------------|------|------------------------------------------------|

| 00     | unused                             | <br>Alexande in the state date |      | IRQ passive release on other VAXes             |

| 04     | machine check                      | abort                          | 3    | parameters depend on<br>error type             |

| 08     | kernel stack not valid             | abort                          | 0    | must be serviced on interrupt stack            |

| 0C     | power fail                         | interrupt                      | 0    | IPL is raised to 1E                            |

| 10     | reserved/privileged<br>instruction | fault                          | 0    |                                                |

| 14     | customer reserved instruction      | fault                          | 0    | XFC instruction                                |

| 18     | reserved operand                   | fault/<br>abort                | 0    | not always recoverable                         |

| 10     | reserved addressing<br>mode        | fault                          | 0    |                                                |

| 20     | access control<br>violation        | fault                          | 2    | parameters are virtual<br>address, status code |

| 24     | translation not valid              | fault                          | 2    | parameters are virtual<br>address, status code |

| 28     | trace pending (TP)                 | fault                          | 0    |                                                |

| 2C     | breakpoint instruction             | fault                          | 0    |                                                |

| 30     | unused                             | -                              | -    | compatibility mode<br>in other VAXes           |

| 34     | arithmetic                         | trap/<br>fault                 | 1    | parameter is type code                         |

| 38-30  | C unused                           | _                              | -    | -                                              |

| 40     | СНМК                               | trap                           | 1 .  | parameter is sign-<br>extended operand word    |

| 44     | CHME                               | trap                           | 1    | parameter is sign-<br>extended operand word    |

| 48     | CHMS                               | trap                           | 1    | parameter is sign-<br>extended operand word    |

KA650-AA Processor Module Engineering Specification V1.00Page 27KA650-AA CENTRAL PROCESSOR18 April 1986

| 4C     | CHMU                 | trap                                                                                                                                          |                               | parameter is sign-<br>extended operand word                                                                                                                                                                                                                         |

|--------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

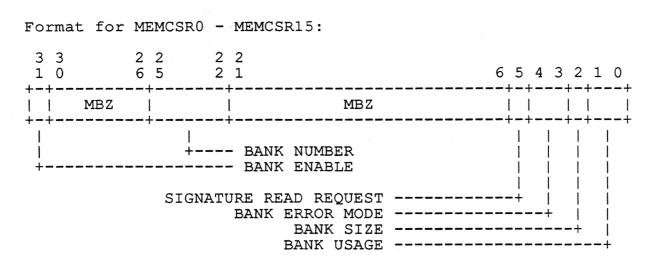

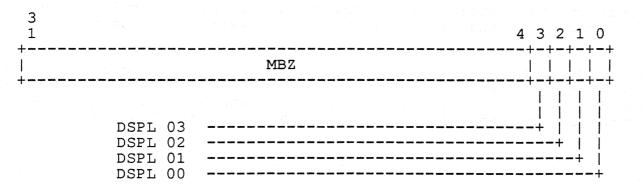

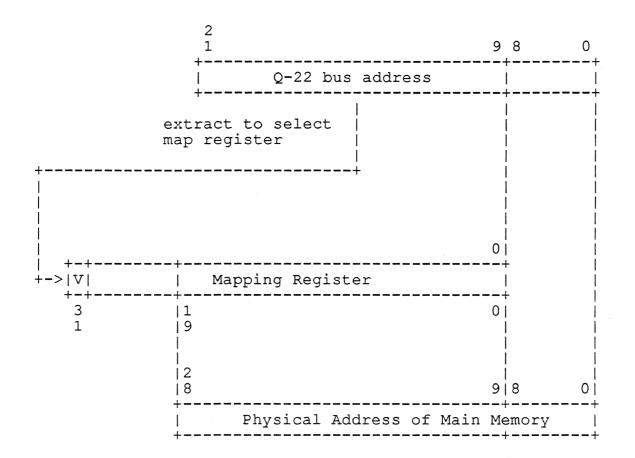

| 50     | unused               |                                                                                                                                               |                               |                                                                                                                                                                                                                                                                     |