EK-FP730-TD-001

# VAX-11/730 FP730 Floating-Point Accelerator Technical Description

Prepared by Educational Services of Digital Equipment Corporation

#### Copyright © 1982 by Digital Equipment Corporation

#### All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

## This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS      |

|---------|--------------|--------------|

| DEC     | DECSYSTEM-20 | OMNIBUS      |

| PDP     | DIBOL        | <b>OS</b> /8 |

| DECUS   | EDUSYSTEM    | RSTS         |

| UNIBUS  | VAX          | RSX          |

|         | VMS          | IAS          |

## CONTENTS

#### CHAPTER 1 INTRODUCTION

| 1.1   | GENERAL                                    | 1-1 |

|-------|--------------------------------------------|-----|

| 1.2   | RELATED DOCUMENTATION                      | 1-1 |

| 1.3   | PHYSICAL DESCRIPTION                       | 1-2 |

| 1.4   | FUNCTIONAL DESCRIPTION                     | 1-2 |

| 1.5   | DIAGNOSTIC FEATURES                        | 1-3 |

| 1.6   | FLOATING-POINT NUMBERS AND ARITHMETIC      | 1-3 |

| 1.6.1 | Integers                                   | 1-3 |

| 1.6.2 | Floating-Point Numbers                     |     |

| 1.6.3 | Normalization                              | 1-4 |

| 1.6.4 | Floating-Point Notation                    | 1-6 |

| 1.6.5 | Floating-Point Addition and Subtraction    |     |

| 1.6.6 | Floating-Point Multiplication and Division |     |

|       |                                            |     |

#### CHAPTER 2 DATA FORMATS

| 2.1   | GENERAL                   | 2-1 |

|-------|---------------------------|-----|

| 2.2   | FLOATING-POINT FORMATS    | 2-1 |

| 2.2.1 | Fraction                  | 2-2 |

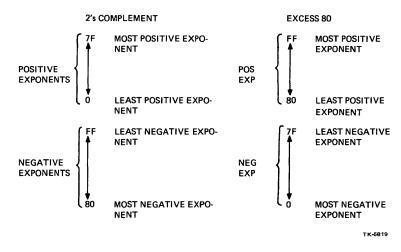

| 2.2.2 | Exponent                  | 2-4 |

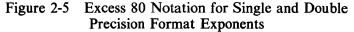

| 2.3   | INTEGER FORMAT            | 2-7 |

| 2.4   | FLOATING-POINT EXCEPTIONS | 2-7 |

| 2.4.1 | Overflow                  | 2-7 |

| 2.4.2 | Underflow                 | 2-7 |

| 2.4.3 | Divide-by-Zero            | 2-7 |

| 2.4.4 | Reserved Operand Fault    | 2-7 |

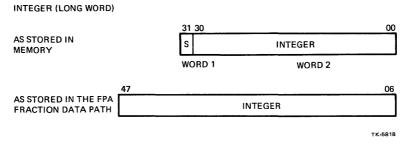

### CHAPTER 3 INTERFACING

| 3.1   | GENERAL                             | 3-1 |

|-------|-------------------------------------|-----|

| 3.2   | INTERFACE SIGNALS                   | 3-1 |

| 3.3   | INTERFACE OPERATION                 | 3-3 |

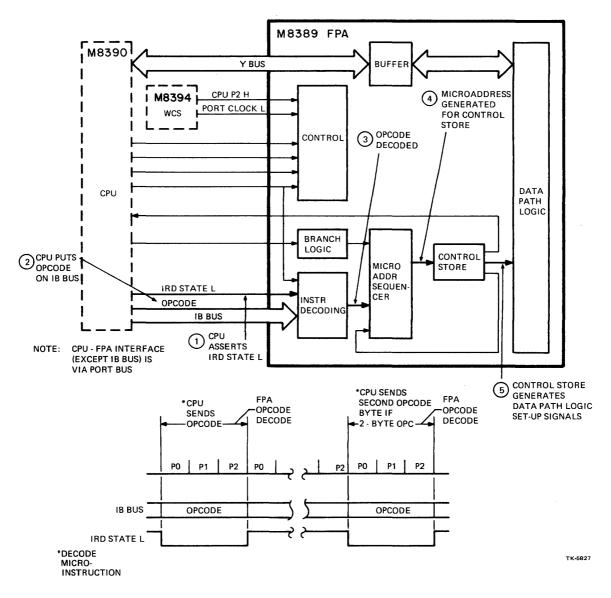

| 3.3.1 | Op Code Decoding                    | 3-3 |

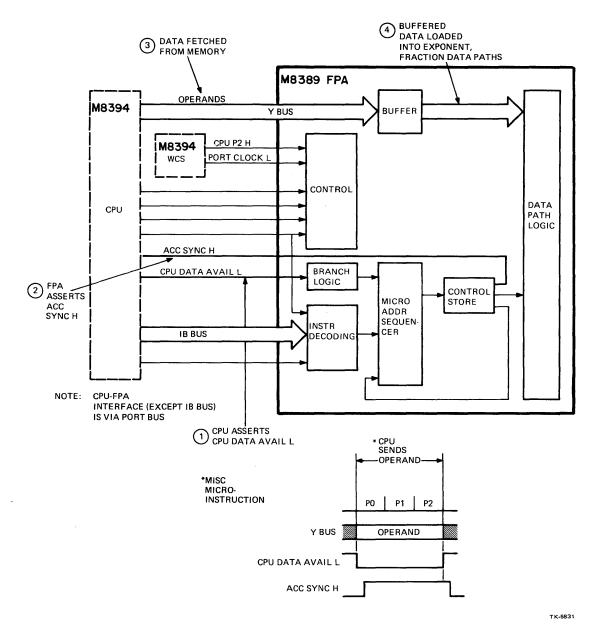

| 3.3.2 | Operand Loading                     |     |

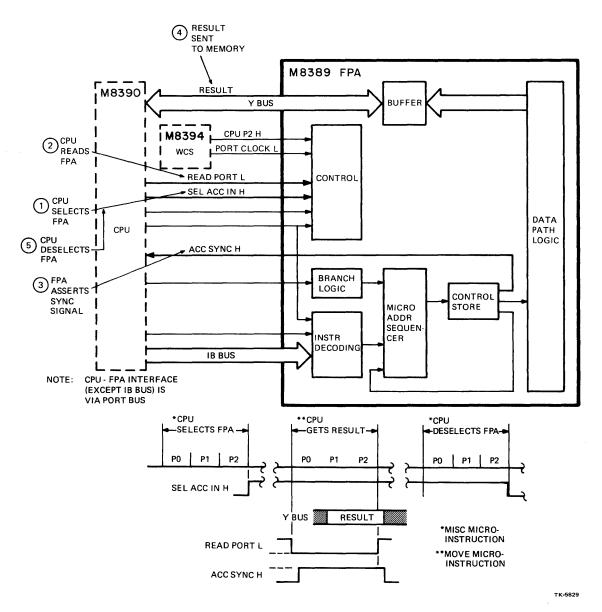

| 3.3.3 | Result Storing                      | 3-5 |

| 3.4   | CPU FORCE/READ MICROADDRESS CONTROL | 3-6 |

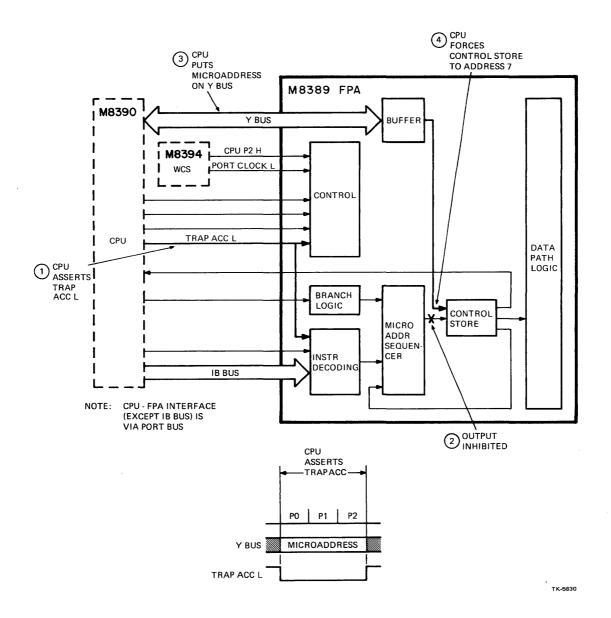

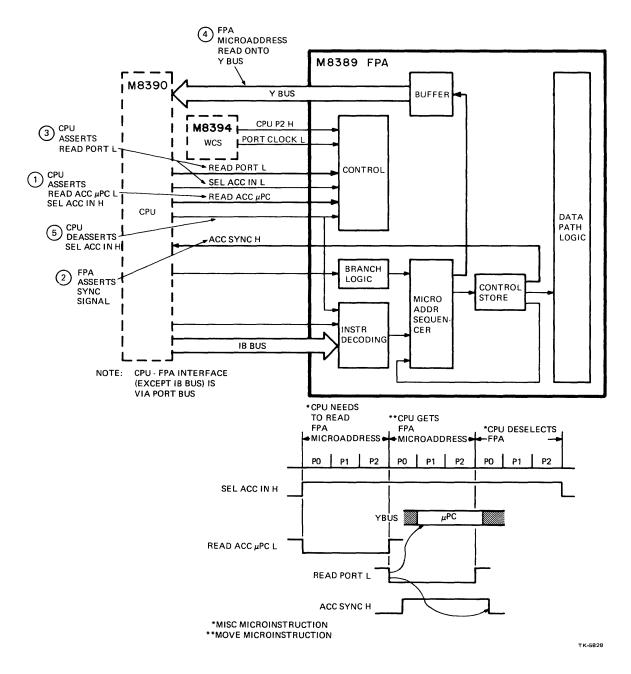

| 3.4.1 | Force Microaddress Control          | 3-6 |

| 3.4.2 | Read Microaddress Control           | 3-7 |

| 3.5   | ERROR REPORTING                     | 3-8 |

| 3.5.1 | Parity                              | 3-8 |

| 3.5.2 | Condition Codes                     | 3-8 |

|       |                                     |     |

## CHAPTER 4 INSTRUCTIONS AND ALGORITHMS

| 4.1     | GENERAL                                    | 4-1  |

|---------|--------------------------------------------|------|

| 4.2     | ARITHMETIC INSTRUCTIONS                    | 4-2  |

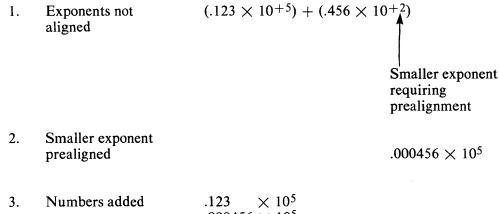

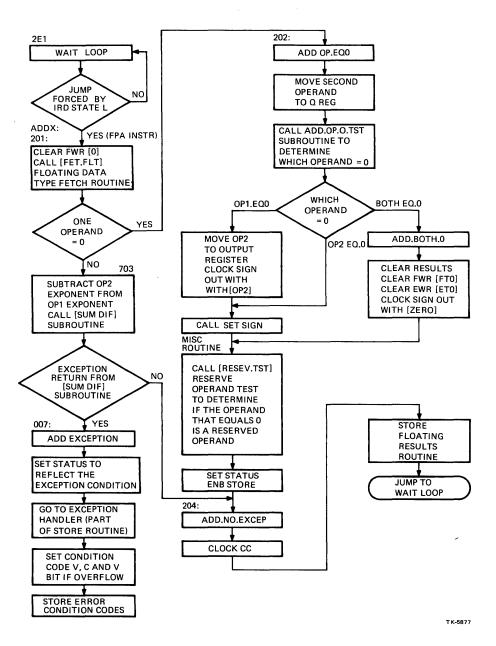

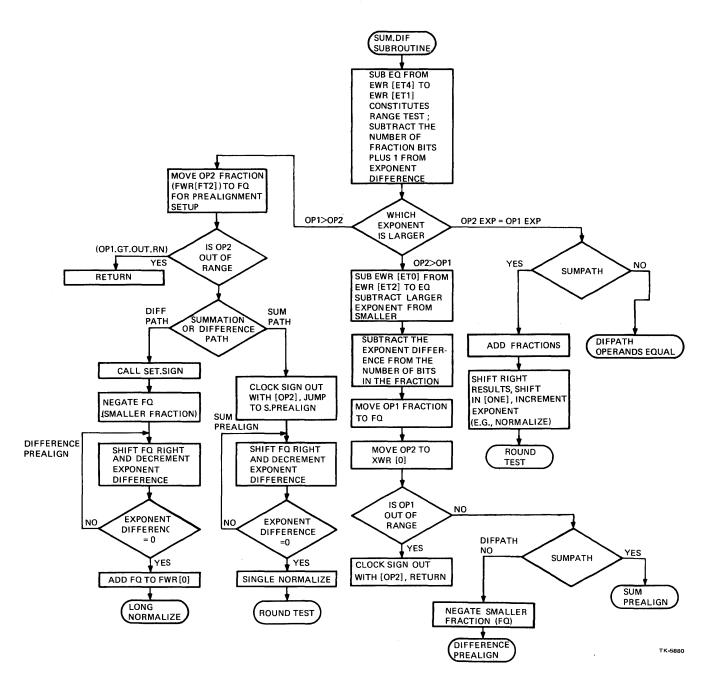

| 4.2.1   | Add/Subtract                               | 4-2  |

| 4.2.2   | Compare (CMP) Instructions                 | 4-10 |

| 4.2.3   | Polynomial (POLY) Instruction              |      |

| 4.2.4   | Divide (DIV) Instruction                   |      |

| 4.2.4.1 | DIV                                        | 4-12 |

| 4.2.4.2 | DIVL Instruction                           | 4-12 |

| 4.2.5   | Multiply (MUL) Instruction                 | 4-13 |

| 4.2.5.1 | MUL Algorithm                              |      |

| 4.2.5.2 | MULL Instruction                           |      |

| 4.2.6   | Extended Precision Multiply and Integerize |      |

|         | (EMOD)                                     | 4-14 |

| 4.3     | CONVERSION INSTRUCTIONS                    | 4-15 |

| 4.3.1   | Floating-Type-to-Integer Conversion        | 4-15 |

| 4.3.2   | Integer-to-Floating-Type Conversion        |      |

| 4.3.3   | Precision Conversion                       | 4-18 |

## CHAPTER 5 THEORY OF OPERATION

| 5.1   | GENERAL                      | 5-1  |

|-------|------------------------------|------|

| 5.2   | DATA FLOW                    | 5-3  |

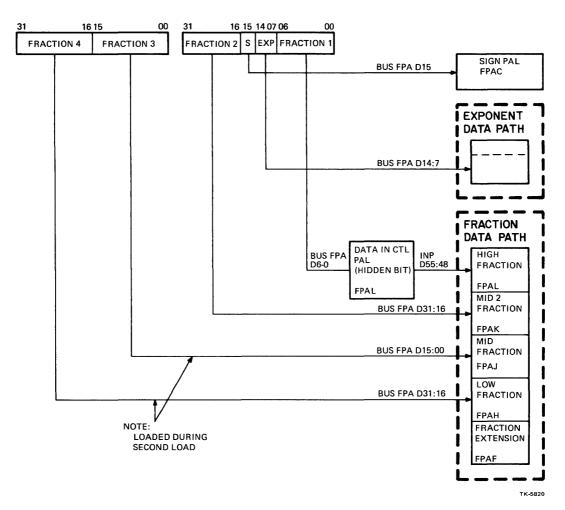

| 5.2.1 | Operand Fetching             | 5-3  |

| 5.2.2 | Result Storing               |      |

| 5.2.3 | Aborts                       | 5-6  |

| 5.2.4 | Exceptions or FPA Errors     | 5-6  |

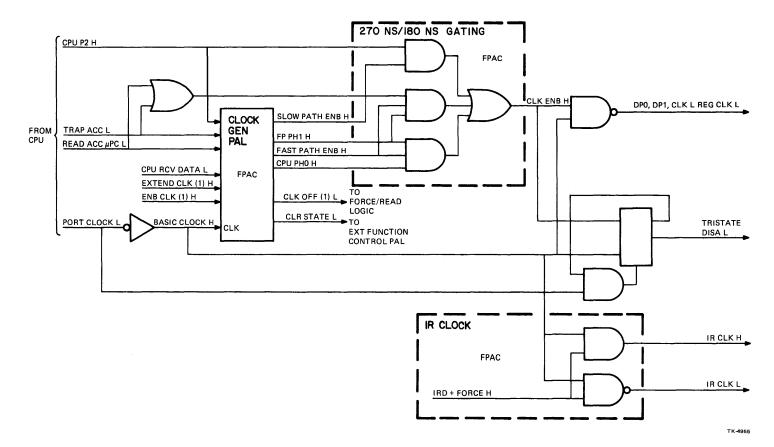

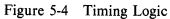

| 5.3   | TIMING                       |      |

| 5.4   | INSTRUCTION DECODING         | 5-16 |

| 5.5   | NEXT MICROADDRESS GENERATION | 5-18 |

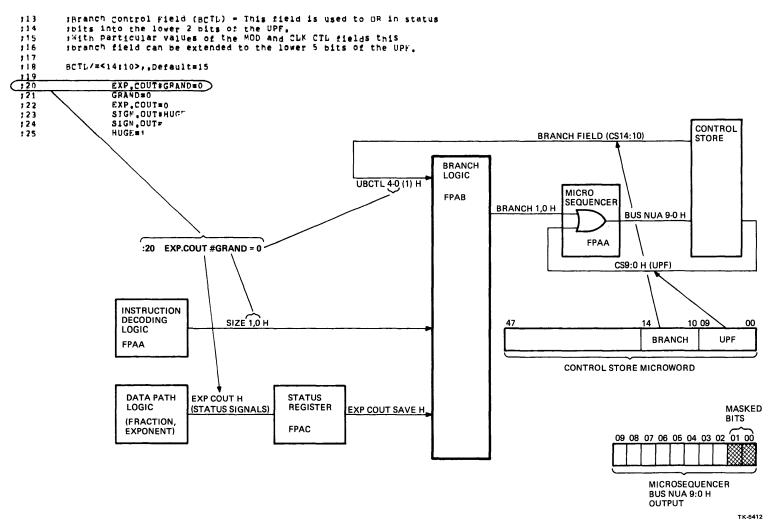

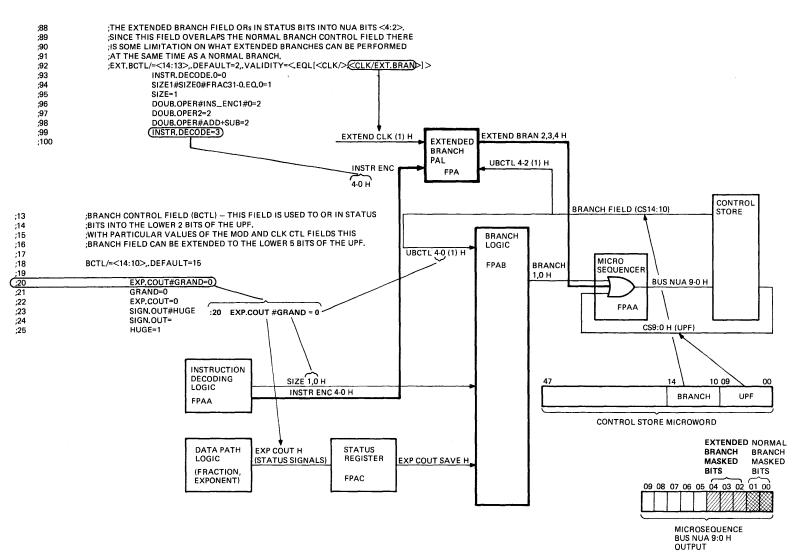

| 5.6   | NEXT MICROADDRESS BRANCHING  | 5-20 |

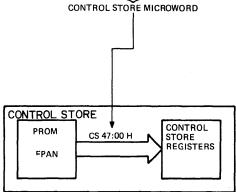

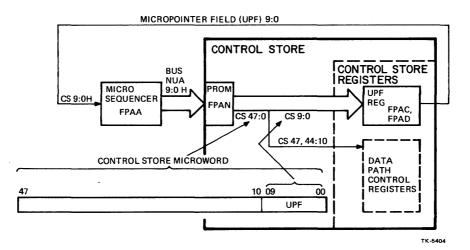

| 5.7   | CONTROL STORE                | 5-22 |

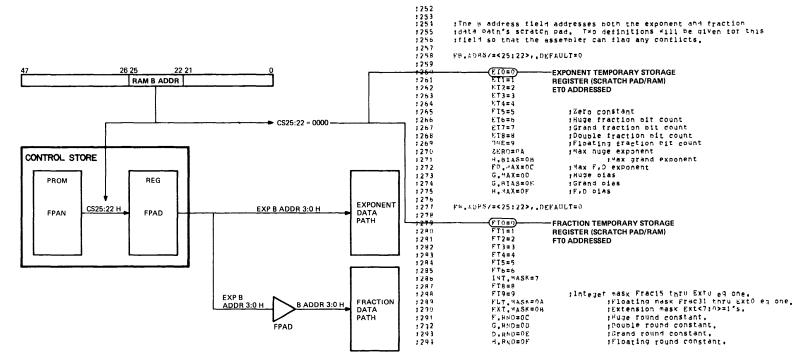

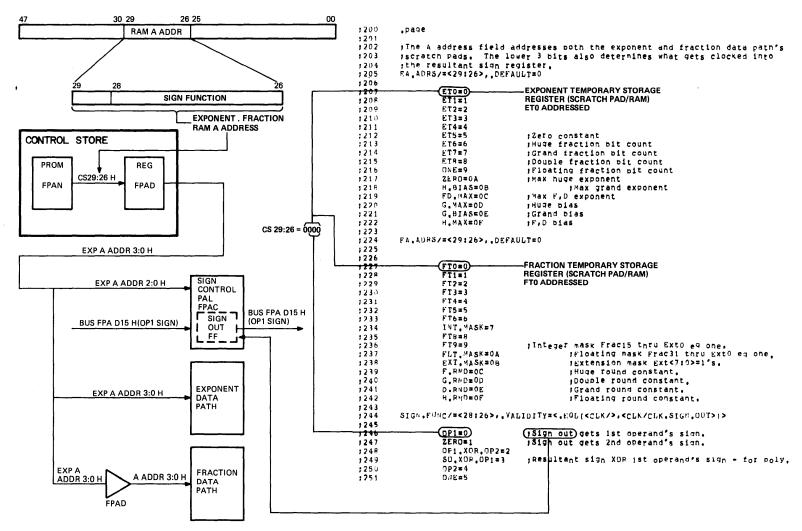

| 5.8   | DATA MANIPULATION            | 5-31 |

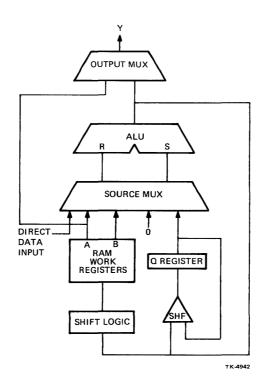

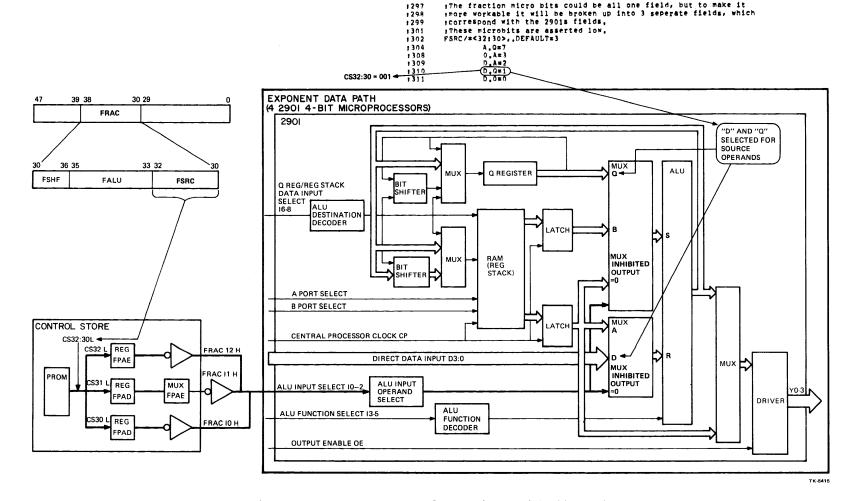

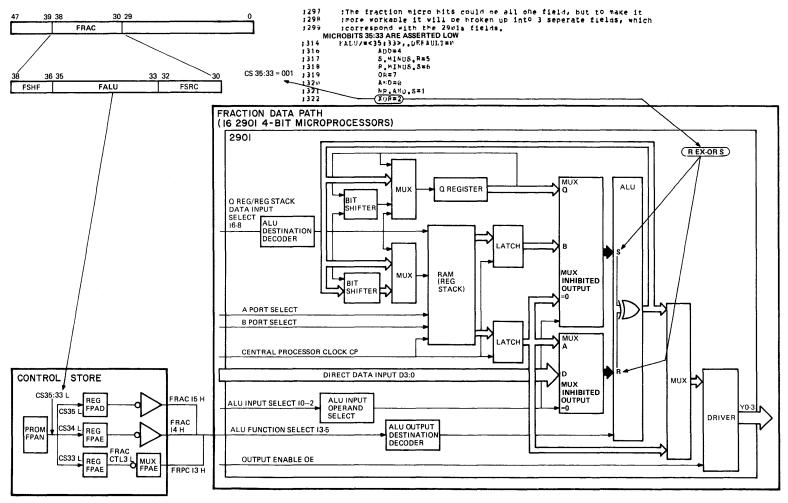

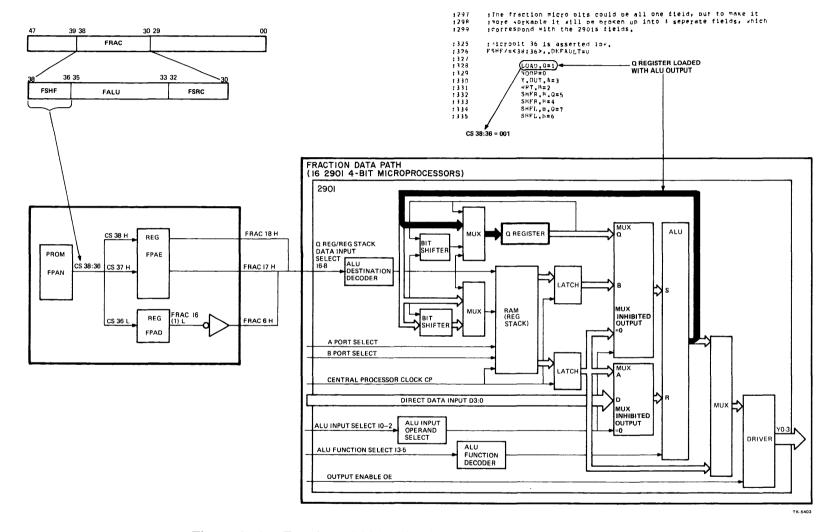

| 5.8.1 | 2901 Four-Bit Slice          | 5-34 |

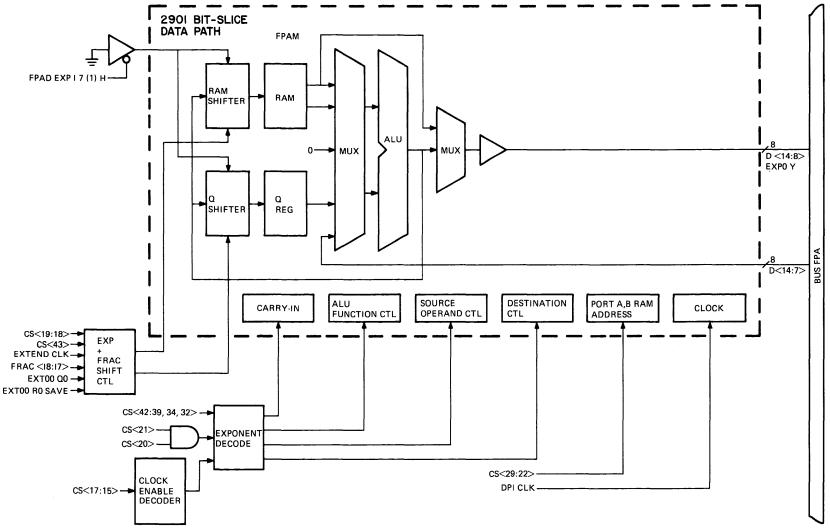

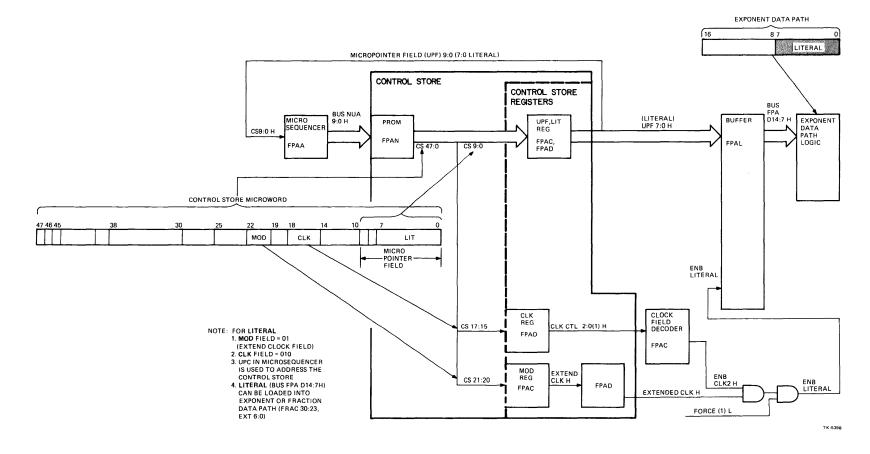

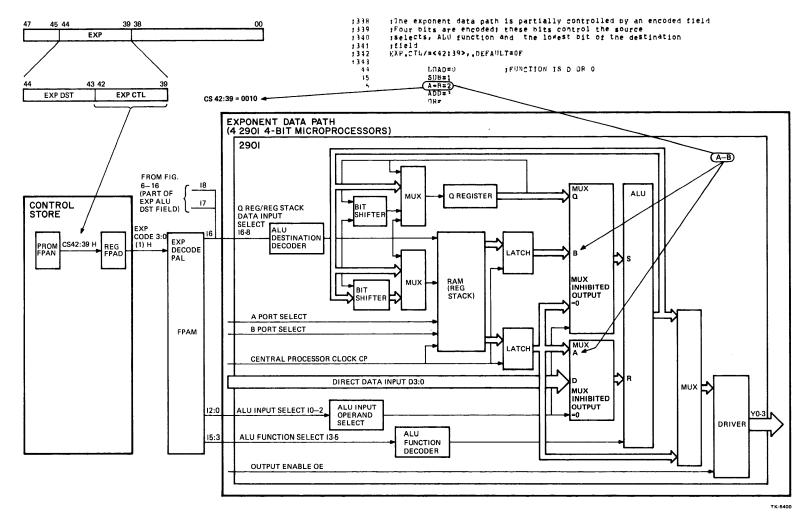

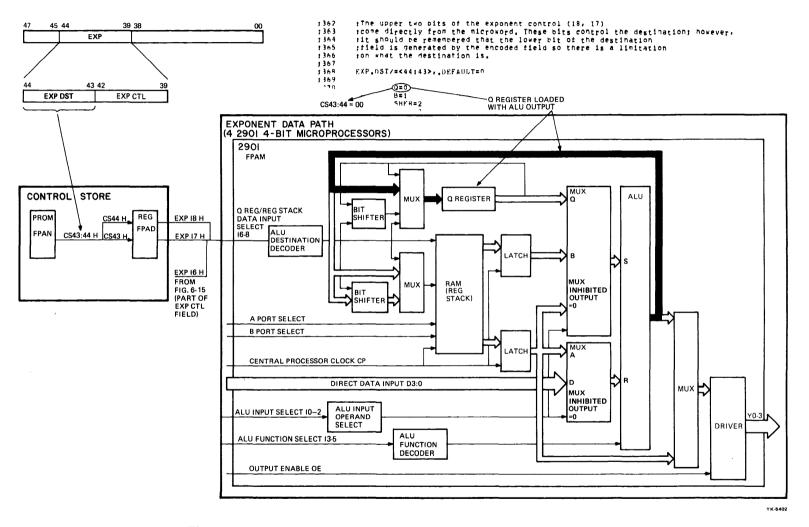

| 5.8.2 | Exponent Data Path           | 5-34 |

| 5.8.3 | Fraction Data Path           |      |

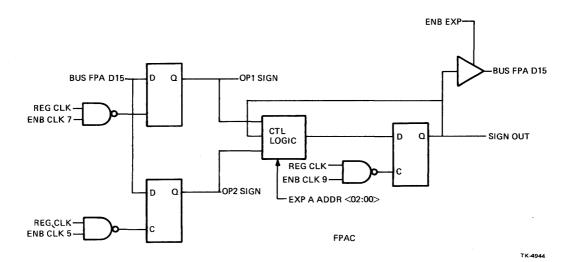

| 5.8.4 | Sign Logic                   | 5-37 |

| 5.9   | MAINTAINABILITY FUNCTIONS    |      |

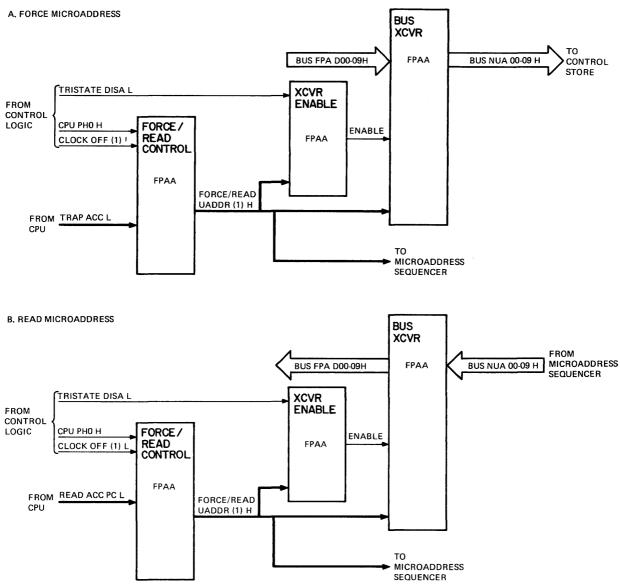

| 5.9.1 | Force Microaddress           | 5-39 |

| 5.9.2 | Read Microaddress            | 5-39 |

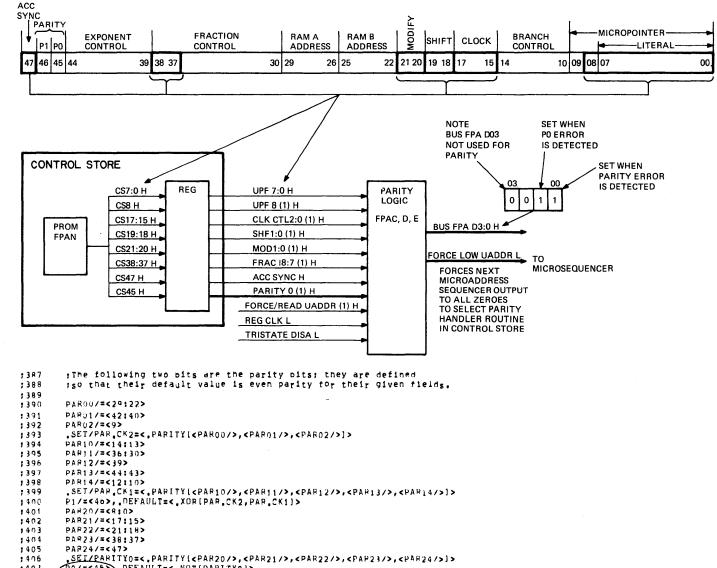

| 5.10  | PARITY LOGIC                 | 5-39 |

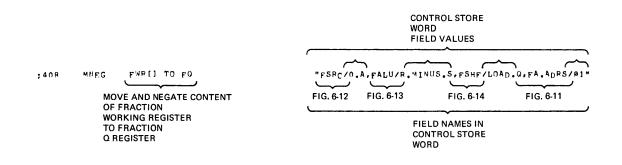

## CHAPTER 6 MICROCODE DESCRIPTIONS

| 6.1 | GENERAL           | 6-1  |

|-----|-------------------|------|

| 6.2 | FIELD DEFINITIONS | 6-1  |

| 6.3 | MACRODEFINITIONS  | 6-1  |

| 6.4 | MICROROUTINE      | 6-22 |

|     |                   |      |

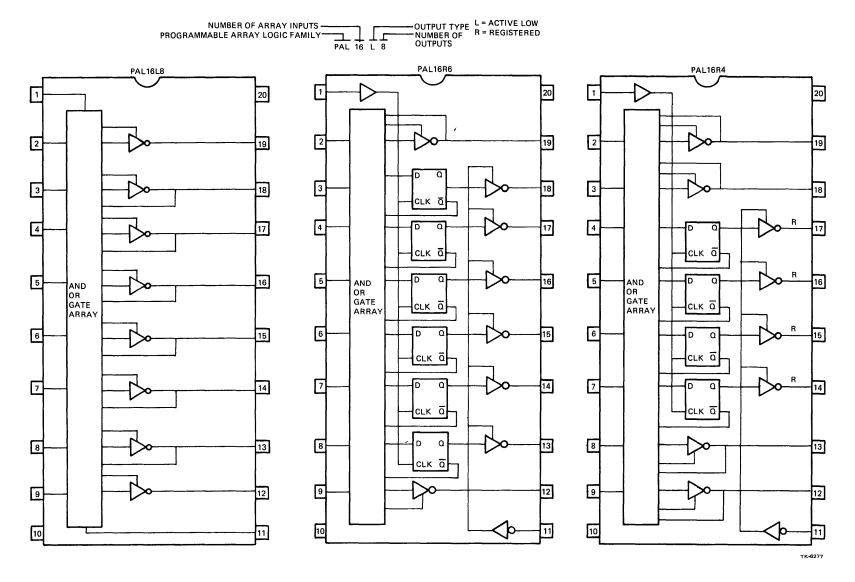

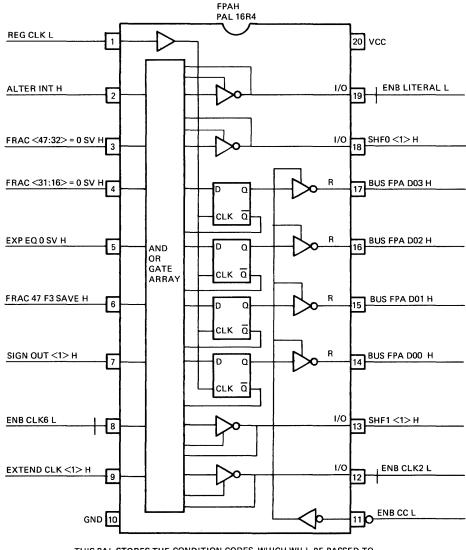

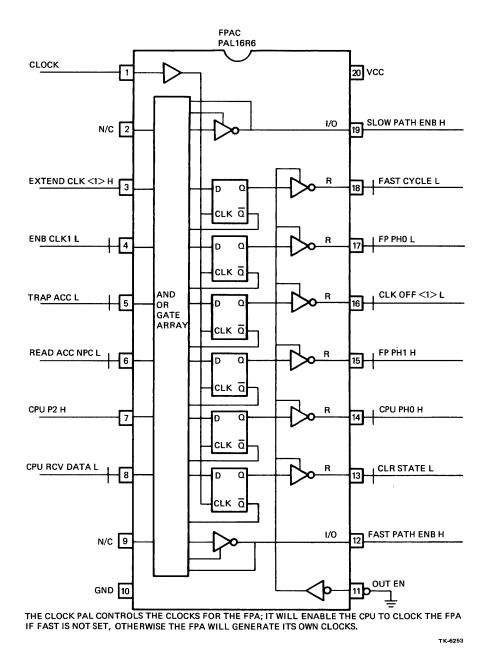

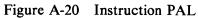

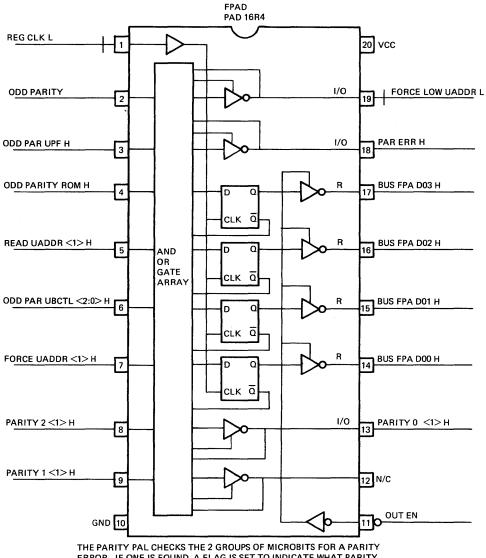

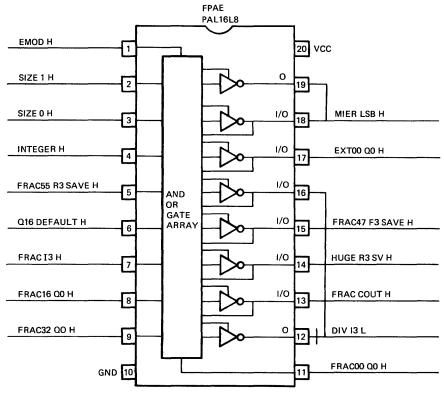

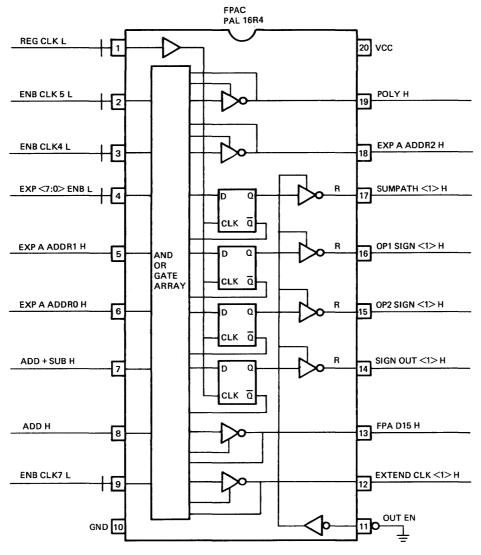

## APPENDIX A PROGRAMMED ARRAY LOGIC DEVICES (PALs)

| A.1 | INTRODUCTION     | A-1 |

|-----|------------------|-----|

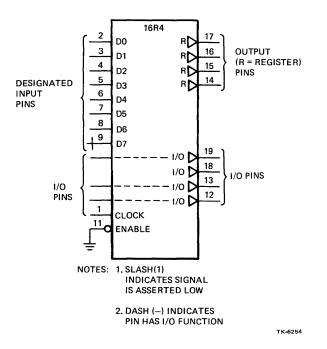

| A.2 | PIN DESIGNATIONS | A-1 |

| A.3 | PAL FUNCTIONS    | A-1 |

APPENDIX B GLOSSARY

## **FIGURES**

| Figure No. | Title                                              | Page |

|------------|----------------------------------------------------|------|

| 1-1        | FPA-11/730                                         |      |

| 2-1        | Single Precision Data Format                       |      |

| 2-2        | Double Precision Data Format                       |      |

| 2-3        | Grand Data Format                                  |      |

| 2-4        | Huge Data Format                                   |      |

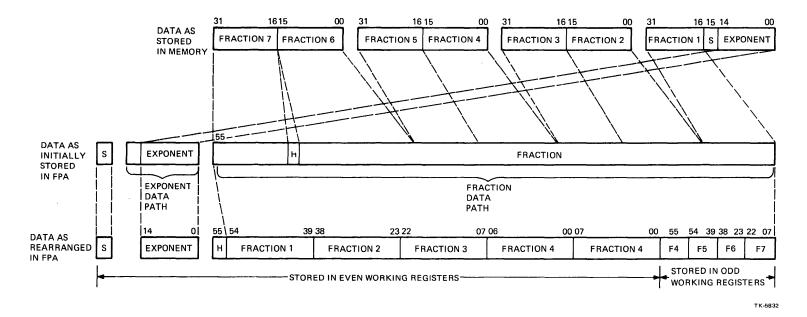

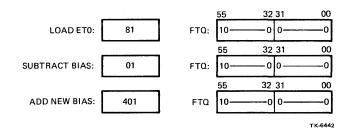

| 2-5        | Excess 80 Notation for Single and Double Precision |      |

|            | Format Exponents                                   |      |

| 2-6        | Integer Format                                     |      |

| 3-1        | FPA-CPU Interface                                  |      |

| 3-2        | Op Code Decoding                                   |      |

| 3-3        | Operand Loading                                    |      |

| 3-4        | Result Storing                                     |      |

| 3-5        | Force Microaddress Control                         |      |

| 3-6        | Read Microaddress Control                          |      |

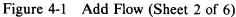

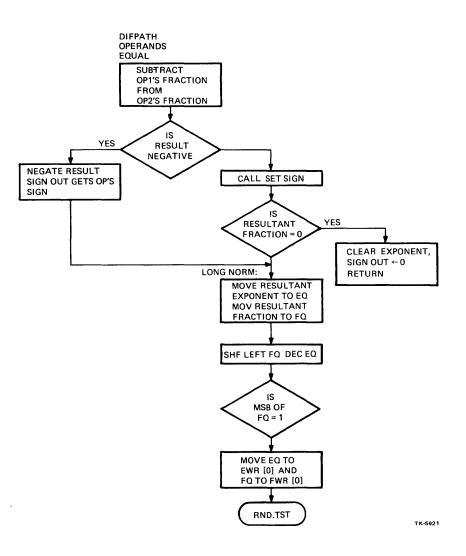

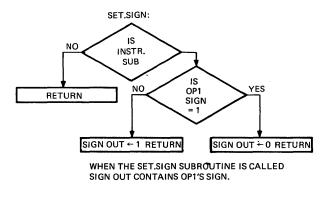

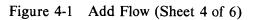

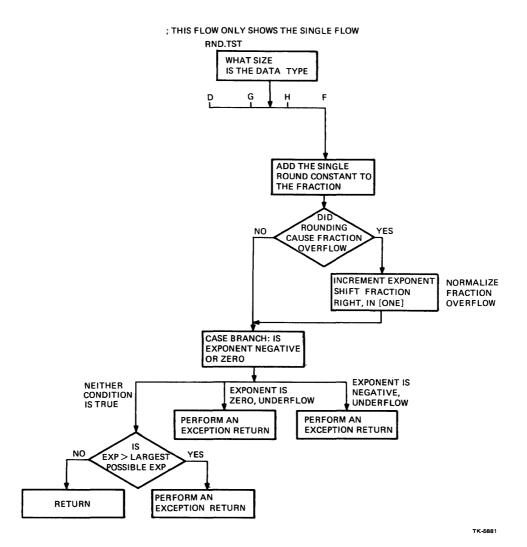

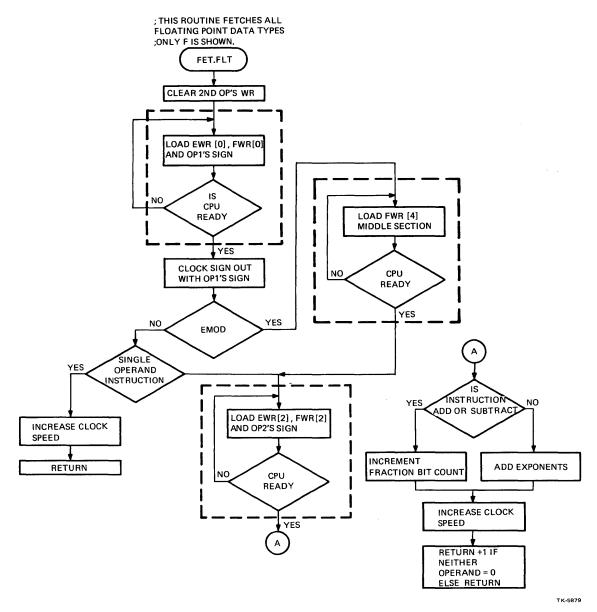

| 4-1        | Add Flow                                           |      |

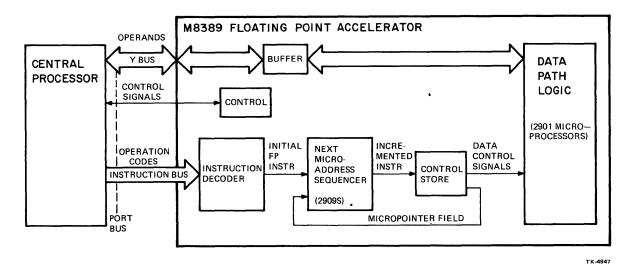

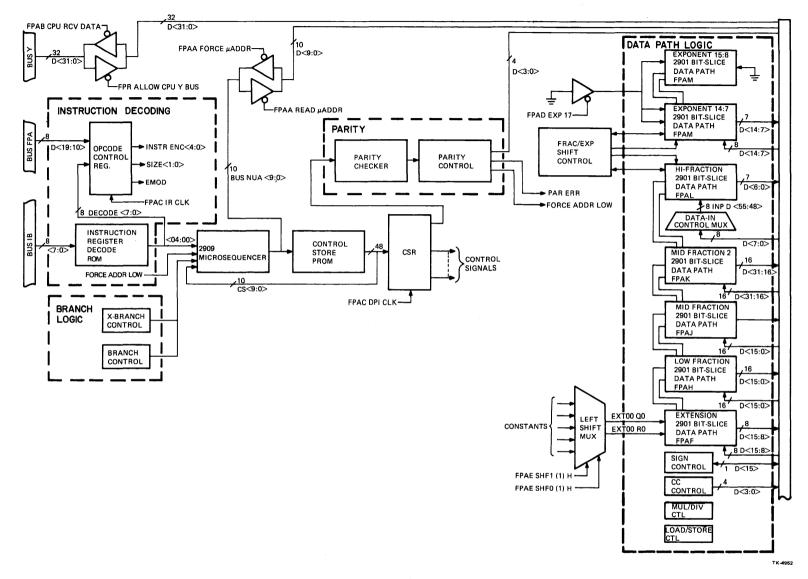

| 5-1        | FPA-11/730 Block Diagram                           |      |

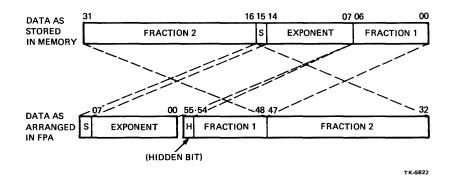

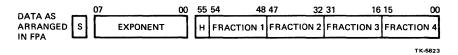

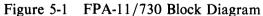

| 5-2        | Single Format Loading                              |      |

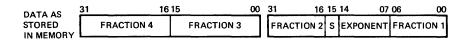

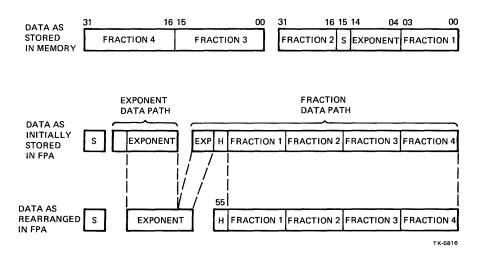

| 5-3        | Double Format Loading                              |      |

| 5-4        | Timing Logic                                       |      |

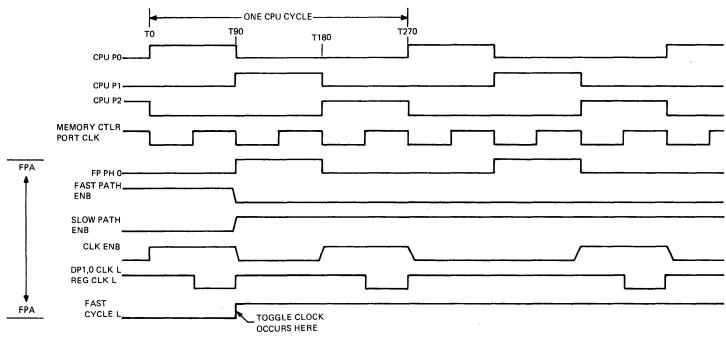

| 5-5        | FPA Synchronization via Toggle Clock During CPU    |      |

|            | РНО                                                |      |

| 5-6        | PFA Synchronization via Toggle Clock During CPU    |      |

| - •        | PH1                                                |      |

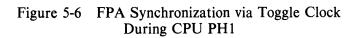

| 5-7        | FPA Synchronization via Toggle Clock During CPU    |      |

|            | PH2                                                |      |

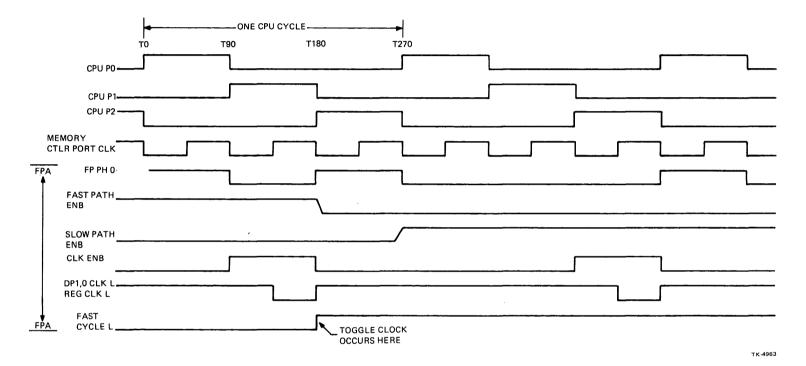

| 5-8        | Fast/Slow Cycle Gating                             |      |

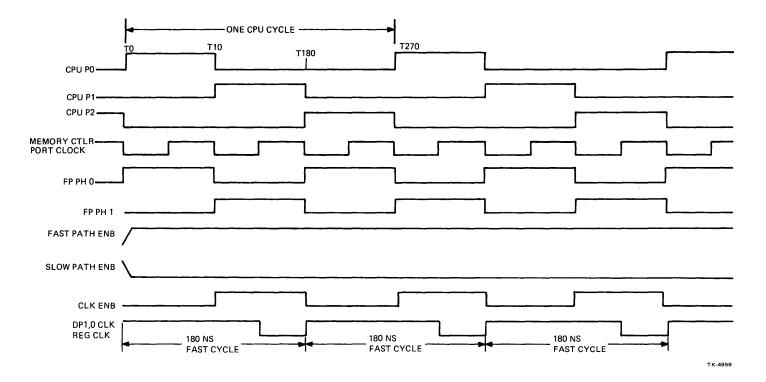

| 5-9        | Fast Cycle Timing                                  |      |

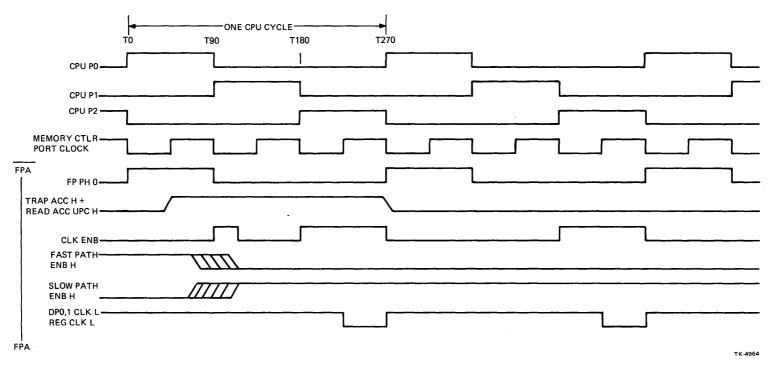

| 5-10       | FPA Synchronization via CPU Force Trap or Read     |      |

|            | During FPA PH0                                     | 5-14 |

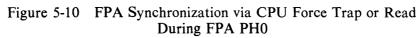

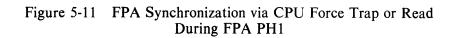

| 5-11       | FPA Synchronization via CPU Force Trap or Read     |      |

|            | During FPA PH1                                     |      |

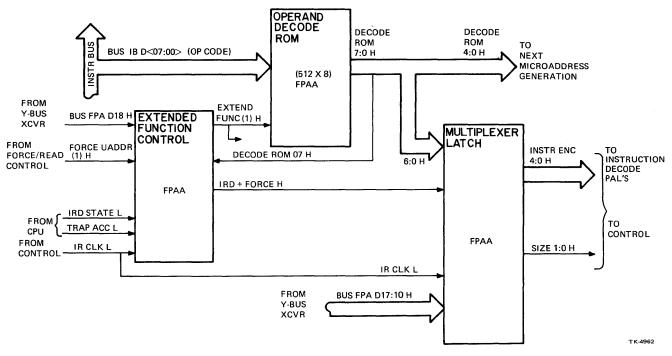

| 5-12       | Instruction Decoding                               |      |

| 5-13       | Op Code Instruction Decoding                       |      |

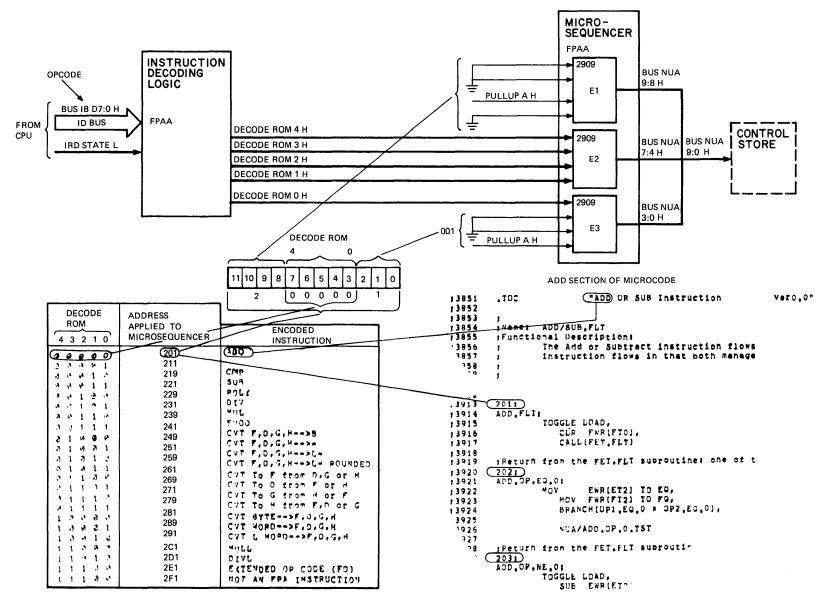

| 5-14       | Instruction Decoding MUX Signal Inputs             |      |

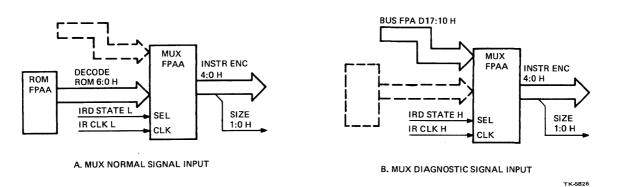

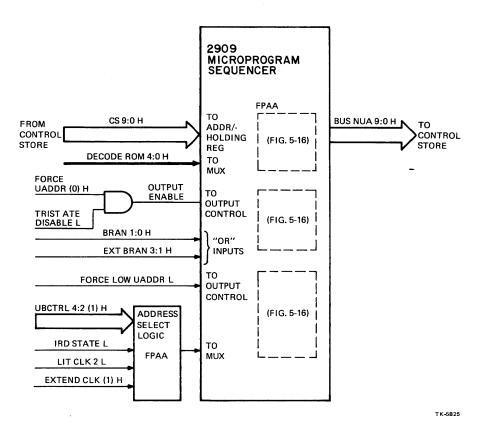

| 5-15       | Microsequencer Logic                               |      |

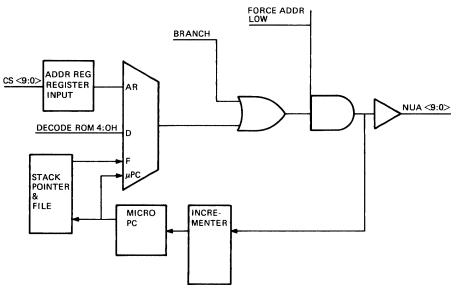

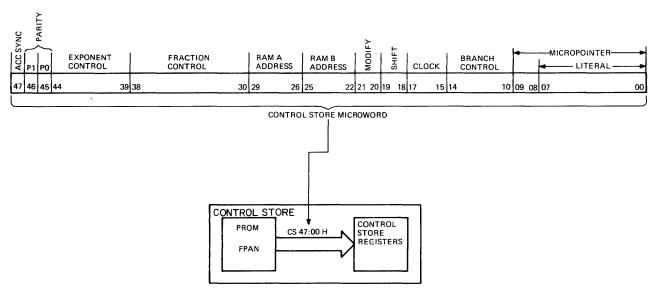

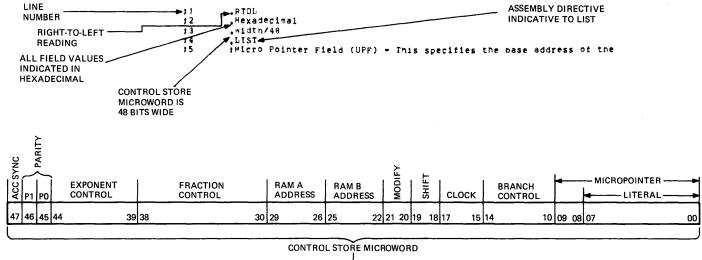

| 5-17         Control Store Logic         5-22           5:18         Control Store Microword         5-33           5:19         Data Path Logic         5-31           5:20         2901 Block Diagram         5-31           5:21         Exponent Data Path Logic         5-35           5:22         Sign Control PAL Logic         5-35           5:23         Force/Read Microaddress Control         5-40           5:24         Control Store Fields Checked by Parity Bit P0         5-41           5:25         Control Store Fields Checked by Parity Bit P1         5-42           6-1         Field Definitions         6-2           6-2         Literal Field         6-3           6-3         Micropointer Field         6-4           6-4         Branch Field         6-5           6-5         Extended Branch Field         6-6           6-6         Clock Field (Used to Clock Fast Cycle)         6-7           6-7         Shift Field (Used to Eatble Division)         6-9           6-8         Modify Field (Used to Enable Division)         6-9           6-9         Modify Field (Used to Enable Division)         6-10           6-11         RAM A Address Field         6-11           6-12 <th>5-16</th> <th>2909 Microprogram Sequencer</th> <th>5-19</th>     | 5-16 | 2909 Microprogram Sequencer                    | 5-19        |

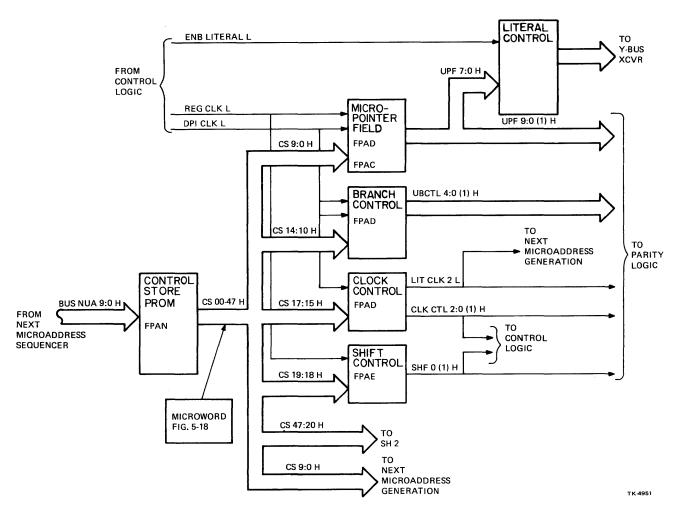

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------|-------------|

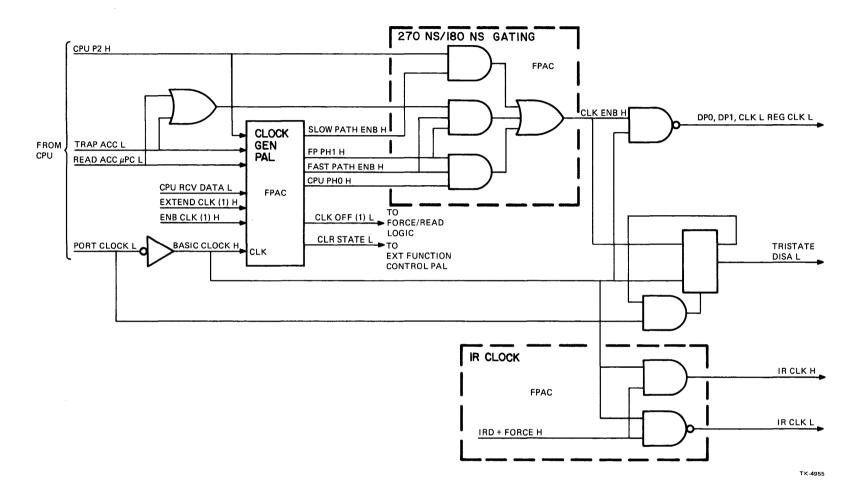

| 5-18         Control Store Microword.         5-23           5-19         Data Path Logic.         5-31           5-20         2901 Block Diagram         5-31           5-21         Exponent Data Path Logic         5-35           5-22         Sign Control PAL Logic         5-38           5-23         Force/Read Microaddress Control         5-40           5-24         Control Store Fields Checked by Parity Bit P0.         5-41           5-25         Control Store Fields Checked by Parity Bit P1.         5-42           6-1         Field Definitions         6-2           6-2         Litteral Field         6-3           6-3         Micropointer Field         6-4           6-4         Branch Field         6-5           6-5         Extended Branch Field         6-6           6-6         Clock Field (Used to Clock Fast Cycle)         6-7           6-7         Shift Field (Used to Set V and C Bits)         6-8           6-8         Modify Field (Used to Set V and C Bits)         6-8           6-9         Modify Field (Used to Enable Multiplication)         6-10           6-10         RAM B Address Field.         6-11           6-11         RAM A Address Field.         6-12                                                                      | 5-17 |                                                |             |

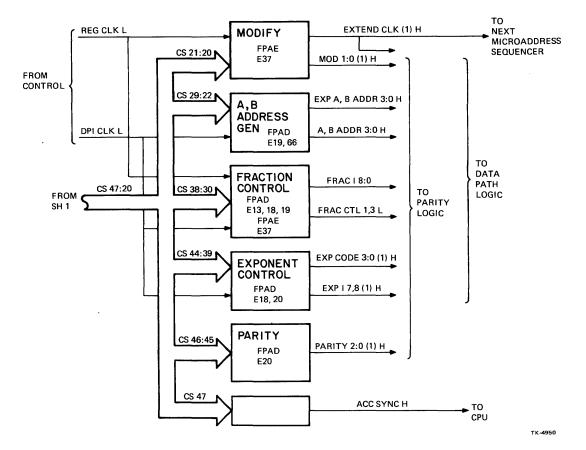

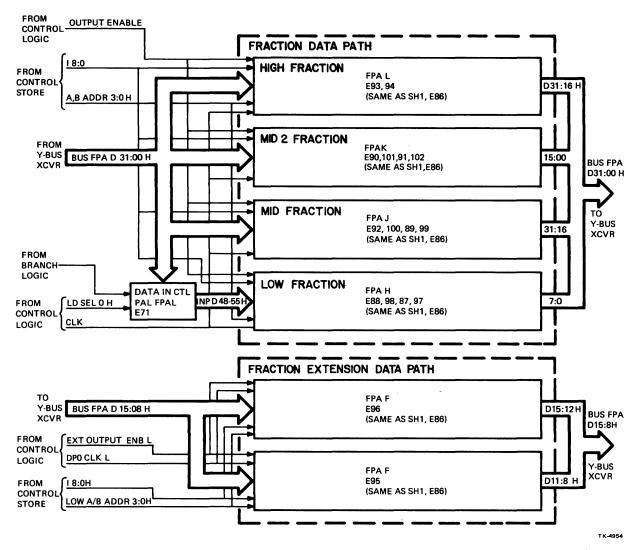

| 5-19       Data Path Logic       5-11         5-20       2901 Block Diagram       5-34         5-21       Exponent Data Path Logic       5-35         5-22       Sign Control PAL Logic       5-35         5-23       Force/Read Microaddress Control       5-40         5-24       Control Store Fields Checked by Parity Bit P0       5-41         5-25       Control Store Fields Checked by Parity Bit P1       5-42         6-1       Field Definitions       6-2         6-2       Literal Field       6-3         6-3       Micropointer Field       6-6         6-6       Clock Field (Used to Clock Fast Cycle)       6-6         6-6       Clock Field (Used to Clock Fast Cycle)       6-7         6-7       Shift Field (Used to Clock Fast Cycle)       6-8         6-8       Modify Field (Used to Enable Division)       6-9         6-9       Modify Field (Used to Enable Multiplication)       6-10         6-10       RAM B Address Field       6-14         6-11       Ration ALU Source Operand (DQ) Field       6-13         6-12       Fraction ALU Destination (Q-Register) Control       6-16         6-15       Exponent ALU Destination (Q-Register) Control       6-16         6-16                                                                                      | 5-18 |                                                |             |

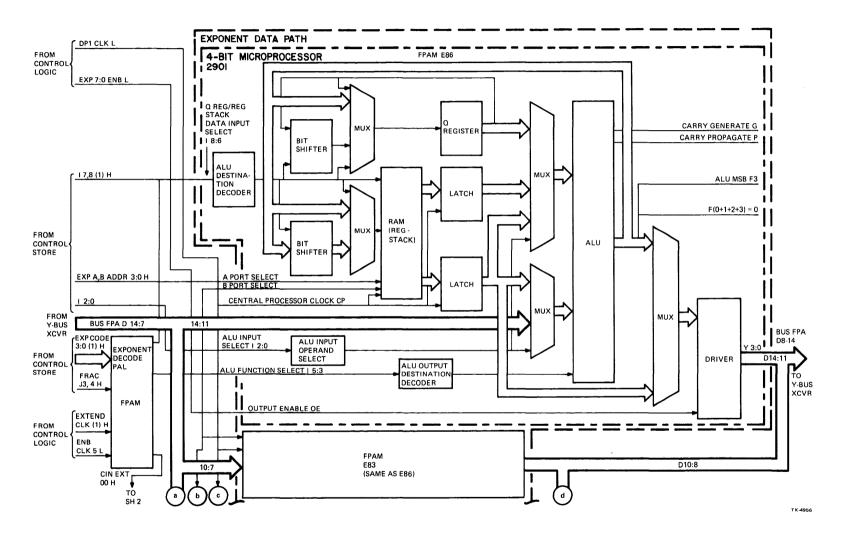

| 5-202901 Block Diagram5-345-21Exponent Data Path Logic5-355-22Sign Control PAL Logic5-355-23Force/Read Microaddress Control5-405-24Control Store Fields Checked by Parity Bit P05-415-25Control Store Fields Checked by Parity Bit P15-426-1Field Definitions6-26-2Literal Field6-36-3Micropointer Field6-46-4Branch Field6-66-5Extended Branch Field6-66-6Clock Field (Used to Set V and C Bits)6-86-7Shift Field (Used to Set V and C Bits)6-86-8Modify Field (Used to Enable Division)6-99Modify Field (Used to Enable Division)6-106-10RAM A Address Field6-126-12Fraction ALU Function (R XOR S) Field6-136-13Fraction ALU Destination (Q-Register) Control6-166-16Exponent Catrol (A-B) Field6-166-17Parity Field P06-226-20MACRO Definitions6-216-21Microcode Overview6-236-22Microcode Overview6-236-23Parity Field P16-196-24A-1FPA PAL Types6-25SP in Designations6-216-16Exponent ALU Destination (Q-Register) Control6-166-17Parity Field P06-246-18Parity Field P16-196-20MACRO Definitions <td< td=""><td>5-19</td><td></td><td></td></td<>                                                                                                                                                                                                                                            | 5-19 |                                                |             |

| 5-21         Exponent Data Path Logic         5-15           5-22         Sign Control PAL Logic         5-38           5-23         Force/Read Microaddress Control         5-40           5-24         Control Store Fields Checked by Parity Bit P0         5-41           5-25         Control Store Fields Checked by Parity Bit P1         5-42           6-1         Field Definitions         6-2           6-2         Literal Field         6-3           6-3         Micropointer Field         6-4           6-4         Branch Field         6-5           6-5         Extended Branch Field         6-6           6-6         Clock Field (Used to Clock Fast Cycle)         6-7           6-7         Shift Field (Used to Set V and C Bits)         6-8           6-8         Modify Field (Used to Enable Division)         6-9           6-9         Modify Field (Used to Enable Division)         6-10           6-10         RAM B Address Field         6-11           6-11         RAM A Address Field         6-12           6-12         Fraction ALU Destination (Q-Register) Control         6-13           6-13         Fraction ALU Destination (Q-Register) Control         6-16           6-15         Exponent Control (A-B) Field <td>5-20</td> <td></td> <td></td> | 5-20 |                                                |             |

| 5-22         Sign Control PAL Logic.         5-38           5-23         Force/Read Microaddress Control.         5-40           5-24         Control Store Fields Checked by Parity Bit P0         5-41           5-25         Control Store Fields Checked by Parity Bit P1         5-42           6-1         Field Definitions         6-2           6-2         Literal Field         6-3           6-3         Micropointer Field         6-4           6-4         Branch Field         6-5           6-5         Extended Branch Field         6-6           6-6         Clock Field (Used to Clock Fast Cycle)         6-7           6-7         Shift Field (Used to Enable Multiplication)         6-9           6-9         Modify Field (Used to Enable Multiplication)         6-10           6-10         RAM B Address Field         6-12           6-12         Fraction ALU Source Operand (DQ) Field         6-13           6-13         Fraction ALU Source Operand (DQ) Field         6-16           6-14         Fraction ALU Destination (Q-Register) Control         6-16           6-15         Exponent Control (A-B) Field         6-16           6-16         Exponent Control (A-B) Field         6-16           6-17         Parity Fiel                               | 5-21 |                                                |             |

| 5-23       Force/Read Microaddress Control       5-40         5-24       Control Store Fields Checked by Parity Bit P0       5-41         5-25       Control Store Fields Checked by Parity Bit P1       5-42         6-1       Field Definitions       6-2         6-2       Literal Field       6-3         6-3       Micropointer Field       6-4         6-4       Branch Field       6-5         6-5       Extended Branch Field       6-6         6-6       Clock Field (Used to Clock Fast Cycle)       6-7         6-7       Shift Field (Used to Clock Fast Cycle)       6-8         6-8       Modify Field (Used to Enable Division)       6-9         6-9       Modify Field (Used to Enable Multiplication)       6-10         6-10       RAM B Address Field       6-11         6-11       RAM A Address Field       6-12         6-12       Fraction ALU Source Operand (DQ) Field       6-13         6-13       Fraction ALU Destination (Q-Register) Control       6-16         6-15       Exponent Control (A-B) Field       6-16         6-16       Exponent ALU Destination (Q-Register) Control       6-17         6-17       Parity Field P1       6-18         6-18       Parity Field P1 <td></td> <td></td> <td></td>                                                        |      |                                                |             |

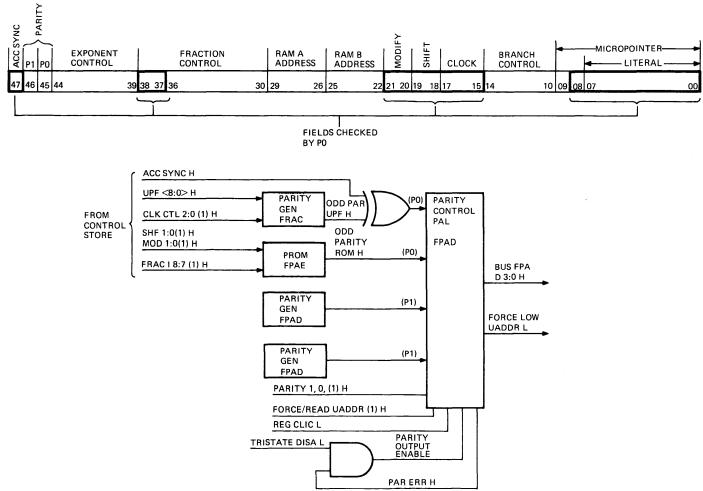

| 5-24       Control Store Fields Checked by Parity Bit P0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                |             |

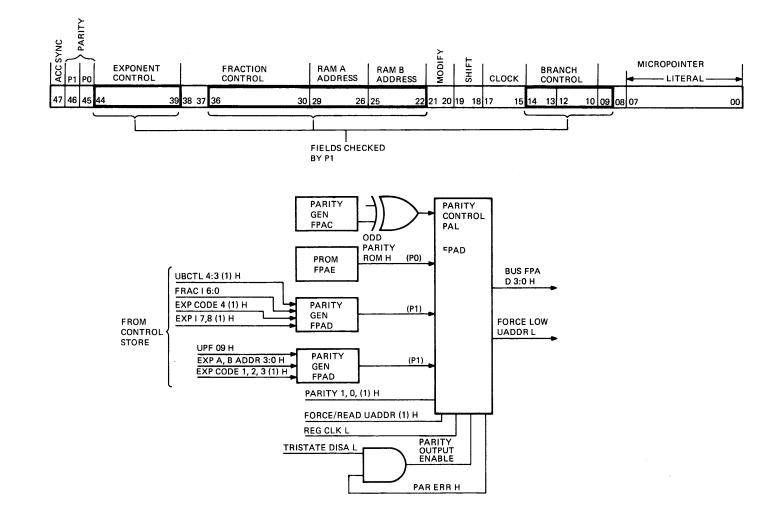

| 5-25       Control Store Fields Checked by Parity Bit P1       5-42         6-1       Field Definitions       6-2         6-2       Literal Field       6-3         6-3       Micropointer Field       6-4         6-4       Branch Field       6-5         6-5       Extended Branch Field       6-6         6-6       Clock Field (Used to Clock Fast Cycle)       6-7         6-7       Shift Field (Used to Enable Division)       6-9         6-8       Modify Field (Used to Enable Multiplication)       6-10         6-10       RAM B Address Field       6-11         6-11       RAM A Address Field       6-14         6-12       Fraction ALU Function (R XOR S) Field       6-14         6-14       Fraction ALU Function (R XOR S) Field       6-15         6-15       Exponent Control (A-B) Field       6-16         6-16       Exponent ALU Punction (Q-Register) Control       6-17         6-17       Parity Field P1       6-20       6-20         6-20       MACRO Definitions       6-21         6-21       Microcode ADD Flow       6-23         6-22       Microcode ADD Flow       6-24         6-14       FPA PAL Types       A-2         A-2                                                                                                                               |      |                                                |             |

| 6-1       Field Definitions       6-2         6-2       Literal Field       6-3         6-3       Micropointer Field       6-4         6-4       Branch Field       6-5         6-5       Extended Branch Field       6-6         6-6       Clock Field (Used to Clock Fast Cycle)       6-7         6-7       Shift Field (Used to Clock Fast Cycle)       6-7         6-8       Modify Field (Used to Enable Division)       6-9         6-9       Modify Field (Used to Enable Multiplication)       6-10         6-10       RAM A Address Field       6-11         6-11       RAM A Address Field       6-13         6-12       Fraction ALU Source Operand (DQ) Field       6-13         6-13       Fraction ALU Destination (Q-Register) Control       6-16         6-16       Exponent Control (A-B) Field       6-16         6-17       Parity Field P0       6-18         6-18       Parity Field P1       6-19         6-20       MACRO Definitions       6-20         6-21       Microcode Overview       6-23         6-22       Microcode Overview       6-24         6-22       Microcode Overview       6-24         6-21       Microcode ADD Flow                                                                                                                                    |      |                                                |             |

| 6-2       Literal Field       6-3         6-3       Micropointer Field       6-4         6-4       Branch Field       6-5         6-5       Extended Branch Field       6-6         6-6       Clock Field (Used to Clock Fast Cycle)       6-7         6-7       Shift Field (Used to Clock Fast Cycle)       6-7         6-8       Modify Field (Used to Enable Division)       6-9         6-9       Modify Field (Used to Enable Multiplication)       6-10         6-10       RAM B Address Field       6-11         6-11       RAM A Address Field       6-13         6-12       Fraction ALU Source Operand (DQ) Field       6-14         6-13       Fraction ALU Source Operand (DQ) Field       6-15         6-14       Fraction ALU Destination (Q-Register) Control       6-16         6-15       Exponent Control (A-B) Field       6-16         6-16       Exponent ALU Destination (Q-Register) Control       6-18         6-18       Parity Field PI       6-18         6-19       Accelerator Sync Field       6-20         6-20       MACRO Definitions       6-21         6-21       Microcode ADD Flow       6-24         A-1       FPA PAL Types       A-2                                                                                                                        | 6-1  |                                                |             |

| 6-3       Micropointer Field.       6-4         6-4       Branch Field       6-5         6-5       Extended Branch Field.       6-6         6-6       Clock Field (Used to Clock Fast Cycle)       6-7         6-7       Shift Field (Used to Enable Division)       6-9         6-8       Modify Field (Used to Enable Multiplication)       6-10         6-10       RAM B Address Field       6-11         6-11       RAM Address Field       6-12         6-12       Fraction ALU Source Operand (DQ) Field       6-13         6-13       Fraction ALU Destination (Q-Register) Control       6-15         6-15       Exponent Control (A-B) Field       6-16         6-16       Exponent ALU Destination (Q-Register) Control       6-17         6-17       Parity Field PO       6-18         6-18       Parity Field PO       6-19         6-19       Accelerator Sync Field       6-21         6-19       Accelerator Sync Field       6-23         6-20       MACRO Definitions       6-24         6-21       Microcode ADD Flow       6-24         6-22       Microcode ADD Flow       6-24         6-23       Microcode ADD Flow       6-24         A-3 <t< td=""><td>6-2</td><td></td><td></td></t<>                                                                                      | 6-2  |                                                |             |

| 6-4       Branch Field       6-5         6-5       Extended Branch Field       6-6         6-6       Clock Field (Used to Clock Fast Cycle)       6-7         6-7       Shift Field (Used to Clock Fast Cycle)       6-8         6-8       Modify Field (Used to Clock Fast Cycle)       6-9         6-9       Modify Field (Used to Enable Division)       6-9         6-10       RAM B Address Field       6-11         6-11       RAM A Address Field       6-12         6-12       Fraction ALU Source Operand (DQ) Field       6-13         6-13       Fraction ALU Destination (Q-Register) Control       6-15         6-15       Exponent Control (A-B) Field       6-16         6-16       Exponent ALU Destination (Q-Register) Control       6-17         6-17       Parity Field P0       6-18         6-18       Parity Field P1       6-19         6-19       Accelerator Syne Field       6-20         6-20       MACRO Definitions       6-23         6-22       Microcode Overview       6-23         6-22       Microcode Overview       6-24         A-1       FPA PAL Types       A-3         A-3       Fusable Link Programming       A-4         A-4                                                                                                                            | 6-3  |                                                |             |

| 6-5       Extended Branch Field       6-6         6-6       Clock Field (Used to Clock Fast Cycle)       6-7         6-7       Shift Field (Used to Set V and C Bits)       6-8         6-8       Modify Field (Used to Enable Division)       6-9         6-9       Modify Field (Used to Enable Multiplication)       6-10         6-10       RAM B Address Field       6-11         6-11       RAM A Address Field       6-12         6-12       Fraction ALU Source Operand (DQ) Field       6-13         6-13       Fraction ALU Usetination (Q-Register) Control       6-14         6-14       Fraction ALU Destination (Q-Register) Control       6-16         6-16       Exponent Control (A-B) Field       6-16         6-17       Parity Field P0       6-16         6-18       Parity Field P1       6-18         6-19       Accelerator Sync Field       6-20         6-20       MACRO Definitions       6-21         6-21       Microcode Overview       6-23         6-22       Microcode ADD Flow       6-24         A-1       FPA PAL Types       A-2         A-2       AND OR GATE ARRAY Details       A-3         A-3       Fusable Link Programming       A-4                                                                                                                     | 6-4  |                                                |             |

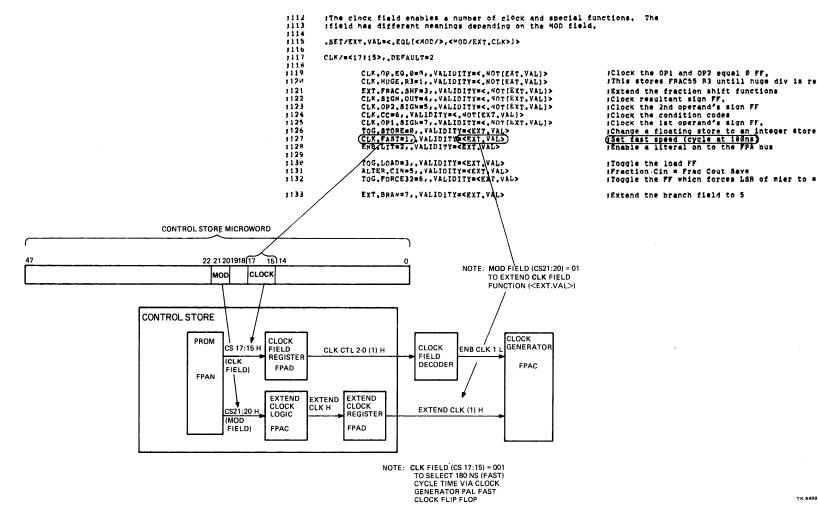

| 6-6       Clock Field (Used to Clock Fast Cycle)       6-7         6-7       Shift Field (Used to Set V and C Bits)       6-8         6-8       Modify Field (Used to Enable Division)       6-9         6-9       Modify Field (Used to Enable Multiplication)       6-10         6-10       RAM B Address Field       6-11         6-11       RAM A Address Field       6-12         6-12       Fraction ALU Source Operand (DQ) Field       6-13         6-13       Fraction ALU Destination (Q-Register) Control       6-16         6-16       Exponent Control (A-B) Field       6-16         6-16       Exponent Control (A-B) Field       6-17         6-17       Parity Field P0       6-18         6-18       Parity Field P1       6-19         6-19       Accelerator Sync Field       6-20         6-20       MACRO Definitions       6-21         6-21       Microcode ADD Flow       6-23         6-22       Microcode ADD Flow       6-24         6-23       Accelerator Sync Field       6-23         6-24       A-1       FPA PAL Types       A-2         A-2       AND OR GATE ARRAY Details       A-3         A-3       Fusable Link Programming       A-4                                                                                                                        | 6-5  |                                                |             |

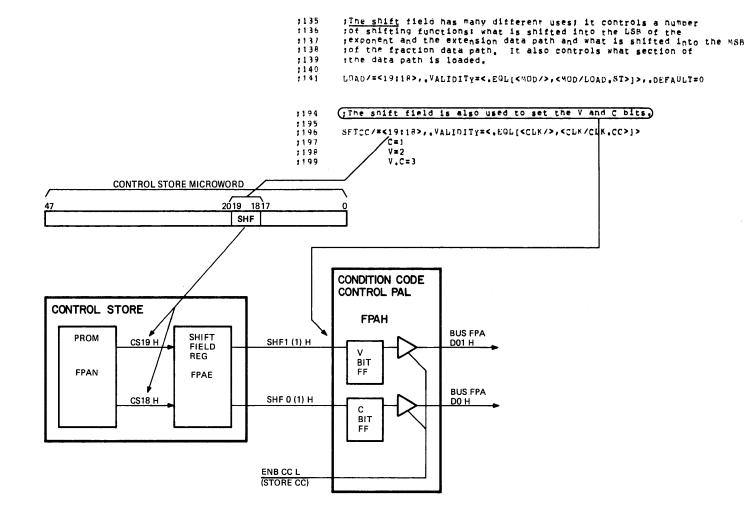

| 6-7       Shift Field (Used to Set V and C Bits)       6-8         6-8       Modify Field (Used to Enable Division)       6-9         6-9       Modify Field (Used to Enable Multiplication)       6-10         6-10       RAM B Address Field       6-11         6-11       RAM A Address Field       6-12         6-12       Fraction ALU Source Operand (DQ) Field       6-13         6-13       Fraction ALU Source Operand (DQ) Field       6-14         6-14       Fraction ALU Destination (Q-Register) Control       6-16         6-15       Exponent Control (A-B) Field       6-16         6-16       Exponent ALU Destination (Q-Register) Control       6-17         6-17       Parity Field P0       6-18         6-18       Parity Field P1       6-19         6-20       MACRO Definitions       6-23         6-21       Microcode ADD Flow       6-24         A-1       FPA PAL Types       A-2         A-2       AND OR GATE ARRAY Details       A-3         A-3       Fusable Link Programming       A-4         A-4       Integer Division Enabled for Data Shift in PAL       A-7         A-5       Pin Designations       A-7         A-5       Pin Designations       A-7                                                                                                      | 6-6  |                                                |             |

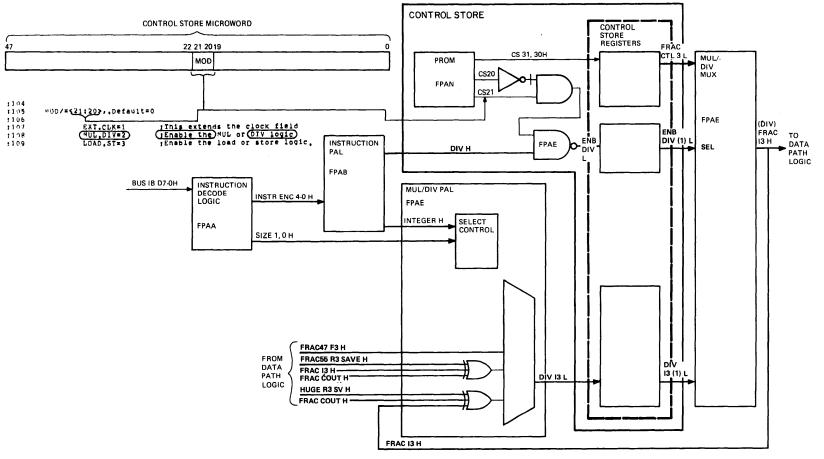

| 6-8       Modify Field (Used to Enable Division)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                                |             |

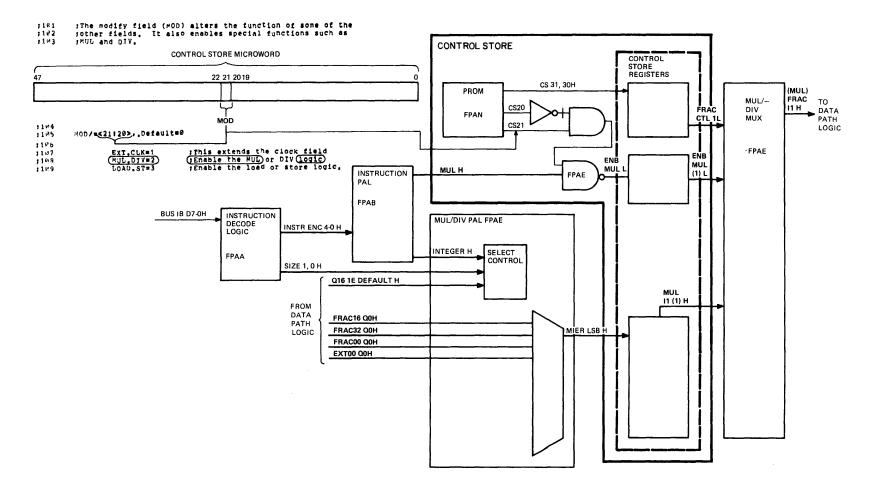

| 6-9       Modify Field (Used to Enable Multiplication)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-8  |                                                |             |

| 6-10       RAM B Address Field       6-11         6-11       RAM A Address Field       6-12         6-12       Fraction ALU Source Operand (DQ) Field       6-13         6-13       Fraction ALU Destination (Q-Register) Control       6-14         6-14       Fraction ALU Destination (Q-Register) Control       6-15         6-15       Exponent Control (A-B) Field       6-16         6-16       Exponent Control (A-B) Field       6-17         6-17       Parity Field P0       6-18         6-18       Parity Field P1       6-19         6-19       Accelerator Sync Field       6-21         6-20       MACRO Definitions       6-23         6-21       Microcode Overview       6-23         6-22       Microcode ADD Flow       6-24         A-1       FPA PAL Types       A-3         A-3       Fusable Link Programming       A-4         A-4       Integer Division Enabled for Data Shift in PAL       A-5         A-5       Pin Designations       A-7         A-7       Input Enable PAL       A-9         A-8       Data Shift in PAL       A-4         A-10       Branch 3 PAL       A-10         A-11       Branch 3 PAL       A-10 <td></td> <td></td> <td></td>                                                                                                              |      |                                                |             |

| 6-11       RAM A Address Field       6-12         6-12       Fraction ALU Source Operand (DQ) Field       6-13         6-13       Fraction ALU Function (R XOR S) Field       6-14         6-14       Fraction ALU Destination (Q-Register) Control       6-15         6-15       Exponent Control (A-B) Field       6-16         6-16       Exponent Control (A-B) Field       6-17         6-17       Parity Field P0       6-18         6-18       Parity Field P1       6-19         6-20       MACRO Definitions       6-21         6-21       Microcode ADD Flow       6-23         6-22       Microcode ADD Flow       6-23         6-22       Microcode ADD Flow       6-23         6-22       Microcode ADD Flow       6-24         A-2       AND OR GATE ARRAY Details       A-3         A-3       Fusable Link Programming       A-4         A-4       Integer Division Enabled for Data Shift in PAL       A-5         A-5       Pin Designations       A-7         A-6       Hidden Bit PAL       A-9         A-7       Input Enable PAL       A-9         A-8       Data Shift in PAL       A-10         A-10       Branch 2 PAL       A-10 <td></td> <td></td> <td></td>                                                                                                              |      |                                                |             |

| 6-12Fraction ALU Source Operand (DQ) Field6-136-13Fraction ALU Function (R XOR S) Field6-146-14Fraction ALU Destination (Q-Register) Control6-156-15Exponent Control (A-B) Field6-166-16Exponent ALU Destination (Q-Register) Control6-176-17Parity Field P06-186-18Parity Field P16-196-20MACRO Definitions6-216-21Microcode Overview6-236-22Microcode ADD Flow6-24A-1FPA PAL TypesA-3A-2AND OR GATE ARRAY DetailsA-3A-3Fusable Link ProgrammingA-4A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-7A-7Input Enable PALA-8A-8Data Shift in PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-14A-14Extended Function PALA-16A-15Fraction Shift Control PALA-16A-16Exponent Ontrol PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                                |             |

| 6-13Fraction ALU Function (R XOR S) Field6-146-14Fraction ALU Destination (Q-Register) ControlField6-156-15Exponent Control (A-B) Field6-16Exponent ALU Destination (Q-Register) ControlField6-166-17Parity Field P06-186-196-19Accelerator Sync Field6-20MACRO Definitions6-21Microcode Overview6-22Microcode ADD Flow6-236-24A-16-17FPA PAL TypesA-2AND OR GATE ARRAY DetailsA-3Fusable Link ProgrammingA-4A-5Pin DesignationsA-6Hidden Bit PALA-7A-6Hidden Bit PALA-70A-70A-71A-71A-72A-73A-74A-74A-75A-75A-76A-77A-74A-74A-75A-75A-74A-74A-75A-74A-74A-75A-75A-74A-74A-75A-74A-74A-75A-75A-74A-74A-75A-74A-74A-75A-75A-74A-74A-75A-75A-74A-74A-75A-75A-74 </td <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                                |             |

| 6-14       Fraction ALU Destination (Q-Register) Control         Field       6-15         6-15       Exponent Control (A-B) Field         6-16       Exponent ALU Destination (Q-Register) Control         Field       6-17         6-17       Parity Field P0         6-18       Parity Field P1         6-19       Accelerator Sync Field         6-20       MACRO Definitions         6-21       Microcode Overview         6-22       Microcode ADD Flow         6-23       6-24         A-1       FPA PAL Types         A-2       AND OR GATE ARRAY Details         A-3       Fusable Link Programming         A-4       Integer Division Enabled for Data Shift in PAL         A-5       Pin Designations         A-6       Hidden Bit PAL         A-7       Aput Enable PAL         A-8       Data Shift in PAL         A-9       Extended Branch PAL         A-10       Branch 3 PAL         A-11       Branch 3 PAL                                                                                                                                                                                                                                                                                                                                                                         |      | Fraction ALU Function (R XOR S) Field          | 6-14        |

| Field6-156-15Exponent Control (A-B) Field6-166-16Exponent ALU Destination (Q-Register) ControlField6-17Parity Field P06-186-18Parity Field P16-19Accelerator Sync Field6-20MACRO Definitions6-21Microcode Overview6-22Microcode Overview6-236-24A-1FPA PAL TypesA-2AND OR GATE ARRAY DetailsA-3Fusable Link ProgrammingA-4Integer Division Enabled for Data Shift in PALA-5Pin DesignationsA-6Hidden Bit PALA-7Input Enable PALA-8Data Shift in PALA-9Extended Branch PALA-10Branch 3 PALA-11A-12Branch 1 PALA-13A-14A-14A-15A-15A-15A-16A-16A-17A-17A-16A-17A-17A-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                                | • • •       |

| 6-15Exponent Control (A-B) Field6-166-16Exponent ALU Destination (Q-Register) ControlField6-176-17Parity Field P06-18Parity Field P16-19Accelerator Sync Field6-20MACRO Definitions6-21Microcode Overview6-22Microcode ADD Flow6-236-24A-1FPA PAL TypesA-2AND OR GATE ARRAY DetailsA-3Fusable Link ProgrammingA-4Integer Division Enabled for Data Shift in PALA-5Pin DesignationsA-7Input Enable PALA-7Anput Enable PALA-8Aata Shift in PALA-9Extended Branch PALA-10Branch 3 PALA-12Branch 3 PALA-13Branch 0 PALA-14Extended Function PALA-15Fraction Shift Control PALA-16Extended Function PALA-17Store Control PALA-18A-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.1. |                                                | 6-15        |

| 6-16Exponent ALU Destination (Q-Register) Control<br>Field.6-17Parity Field P0.6-176-18Parity Field P1.6-196-19Accelerator Sync Field.6-206-20MACRO Definitions6-216-21Microcode Overview.6-236-22Microcode ADD Flow6-24A-1FPA PAL TypesA-2A-2AND OR GATE ARRAY DetailsA-3A-3Fusable Link ProgrammingA-4A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-9A-7Input Enable PALA-9A-8Data Shift in PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-11A-12Branch 1 PALA-12A-13Branch 0 PALA-14A-14Extended Function PALA-16A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-16A-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-15 |                                                |             |

| Field6-176-17Parity Field P06-18Parity Field P16-19Accelerator Sync Field6-20MACRO Definitions6-21Microcode Overview6-22Microcode ADD Flow6-236-24A-1FPA PAL TypesA-2AND OR GATE ARRAY DetailsA-3Fusable Link ProgrammingA-4Integer Division Enabled for Data Shift in PALA-5Pin DesignationsA-6Hidden Bit PALA-7Anput Enable PALA-8Data Shift in PALA-9Extended Branch PALA-10Branch 3 PALA-11Branch 2 PALA-12Aranch 1 PALA-13Branch 0 PALA-14Artended Function PALA-15Fraction Shift Control PALA-16Exponent Control PALA-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                                | • • •       |

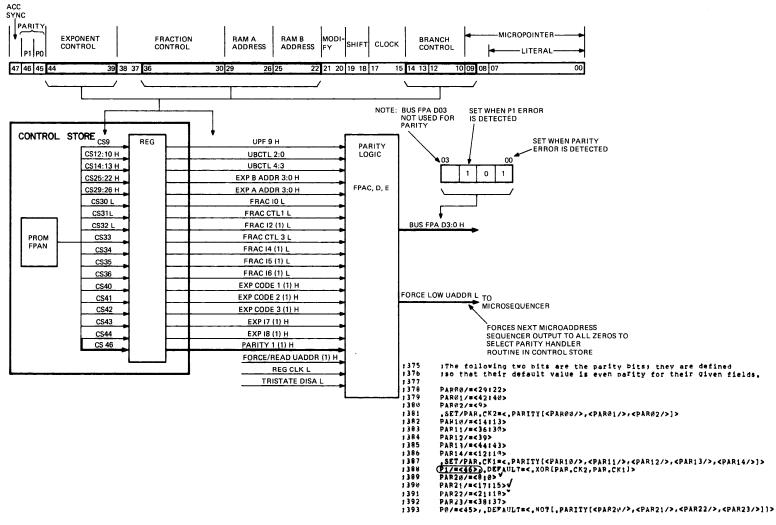

| 6-17Parity Field P0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.10 |                                                | 6-17        |

| 6-18Parity Field P16-196-19Accelerator Sync Field6-206-20MACRO Definitions6-216-21Microcode Overview6-236-22Microcode ADD Flow6-24A-1FPA PAL TypesA-2A-2AND OR GATE ARRAY DetailsA-3A-3Fusable Link ProgrammingA-4A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-8A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-17 |                                                |             |

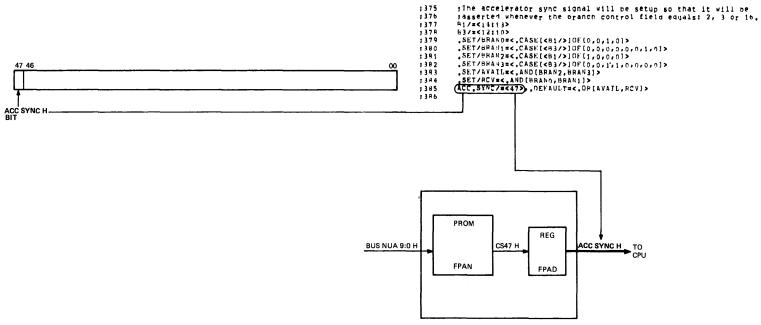

| 6-19Accelerator Sync Field6-206-20MACRO Definitions6-216-21Microcode Overview6-236-22Microcode ADD Flow6-24A-1FPA PAL TypesA-2A-2AND OR GATE ARRAY DetailsA-3A-3Fusable Link ProgrammingA-4A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-8A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-13A-12Branch 1 PALA-14A-13Branch 0 PALA-15A-14Extended Function PALA-16A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                                |             |

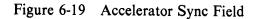

| 6-20MACRO Definitions6-216-21Microcode Overview6-236-22Microcode ADD Flow6-24A-1FPA PAL TypesA-2A-2AND OR GATE ARRAY DetailsA-3A-3Fusable Link ProgrammingA-4A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-7A-7Input Enable PALA-8A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-12A-12Branch 1 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                                |             |

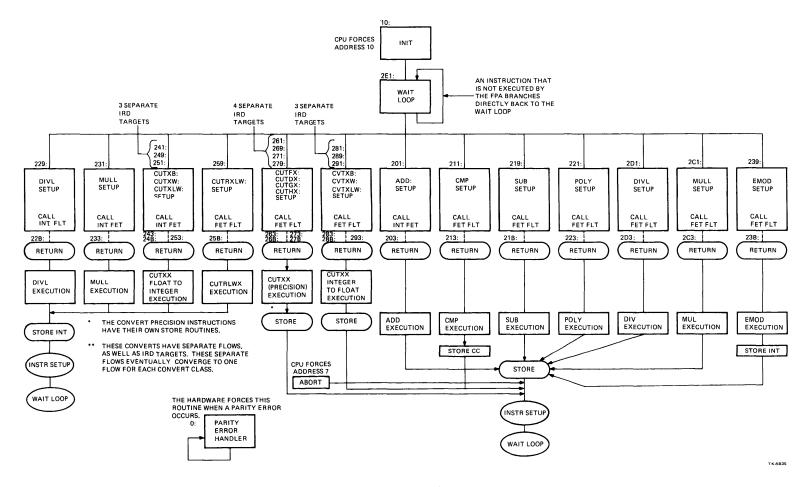

| 6-21Microcode Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-20 |                                                |             |

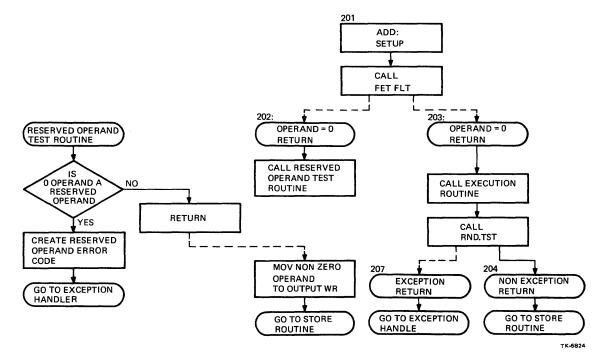

| 6-22Microcode ADD Flow6-24A-1FPA PAL TypesA-2A-2AND OR GATE ARRAY DetailsA-3A-3Fusable Link ProgrammingA-4A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-7A-7Input Enable PALA-8A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-14A-14Extended Function PALA-16A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                                                |             |

| A-1FPA PAL TypesA-2A-2AND OR GATE ARRAY DetailsA-3A-3Fusable Link ProgrammingA-4A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-7A-7Input Enable PALA-8A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-14A-14Extended Function PALA-16A-15Fraction Shift Control PALA-17A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                                |             |

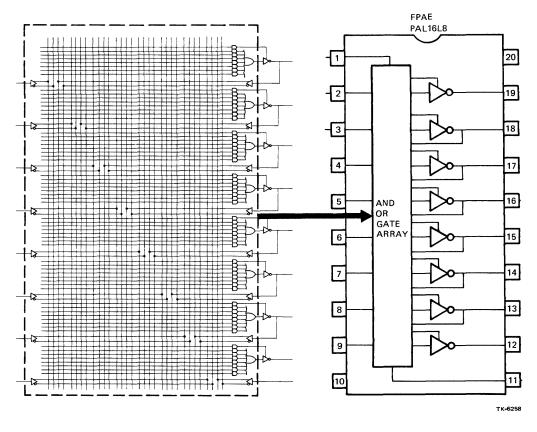

| A-2AND OR GATE ARRAY DetailsA-3A-3Fusable Link ProgrammingA-4A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-7A-7Input Enable PALA-7A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A-1  |                                                |             |

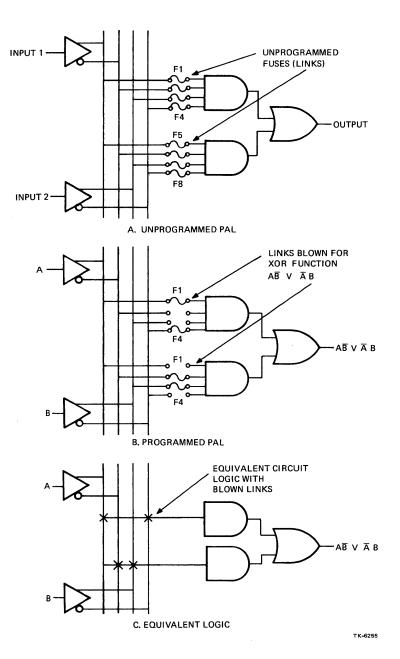

| A-3Fusable Link ProgrammingA-4A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-7A-7Input Enable PALA-8A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-15A-14Extended Function PALA-16A-15Fraction Shift Control PALA-17A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A-2  |                                                |             |

| A-4Integer Division Enabled for Data Shift in PALA-5A-5Pin DesignationsA-7A-6Hidden Bit PALA-7A-7Input Enable PALA-8A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-17A-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A-3  | Fusable Link Programming                       | A-4         |

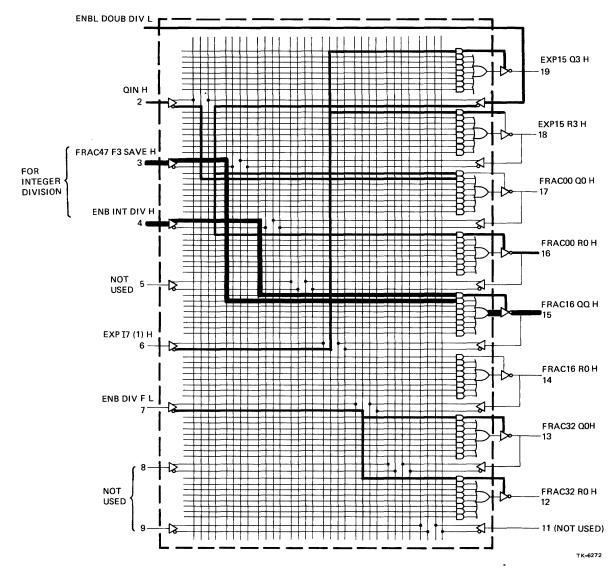

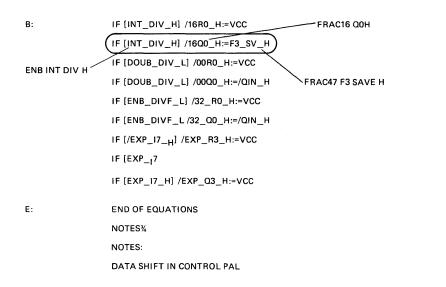

| A-5Pin DesignationsA-7A-6Hidden Bit PALA-7A-7Input Enable PALA-8A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A-4  | Integer Division Enabled for Data Shift in PAL | A-5         |

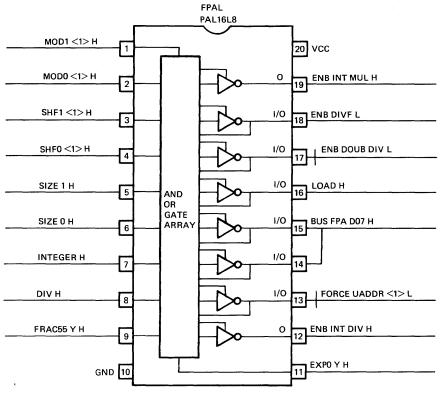

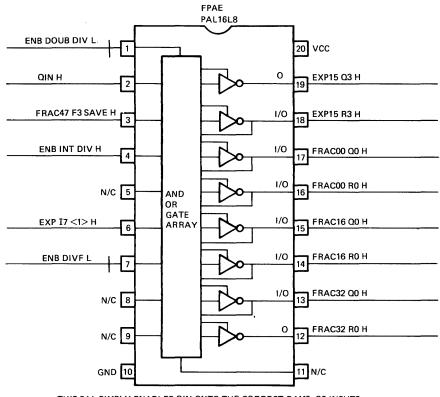

| A-7Input Enable PALA-8A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                                                |             |

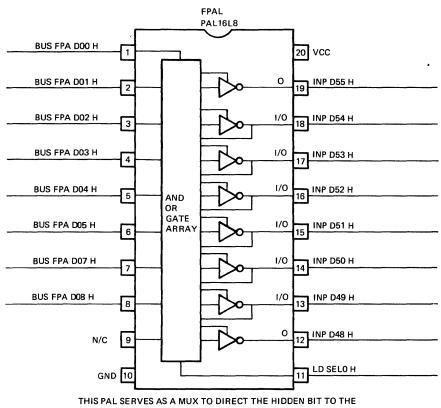

| A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A-6  | Hidden Bit PAL                                 | <b>A-</b> 7 |

| A-8Data Shift in PALA-9A-9Extended Branch PALA-10A-10Branch 3 PALA-11A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                                |             |

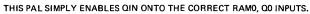

| A-9Extended Branch PALA-10A-10Branch 3 PAL·A-11A-11Branch 2 PAL·A-12A-12Branch 1 PAL·A-13A-13Branch 0 PAL·A-14A-14Extended Function PAL·A-15A-15Fraction Shift Control PAL·A-16A-16Exponent Control PAL·A-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A-8  |                                                |             |

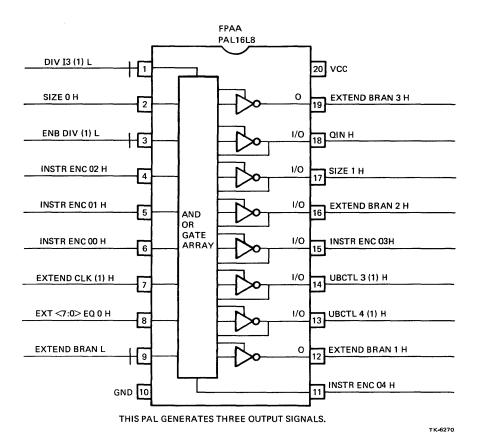

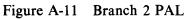

| A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-17A-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A-9  |                                                |             |

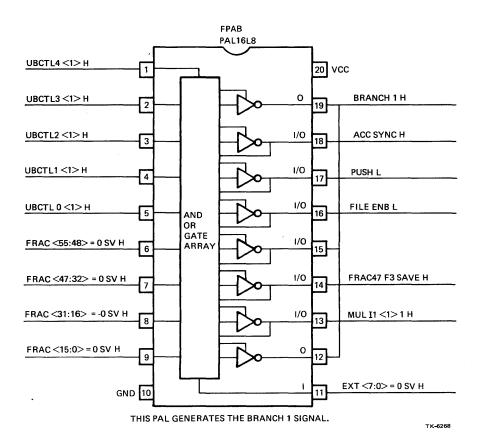

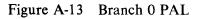

| A-11Branch 2 PALA-12A-12Branch 1 PALA-13A-13Branch 0 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-17A-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A-10 | Branch 3 PAL                                   | A-11        |

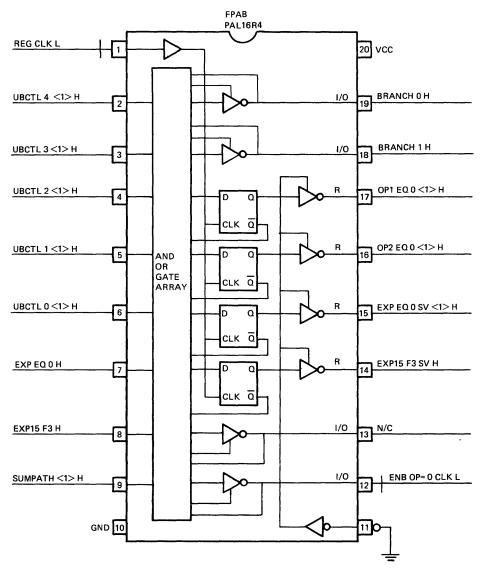

| A-13Branch 0 PALA-14A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-17A-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                |             |

| A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-17A-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A-12 | Branch 1 PAL                                   | A-13        |

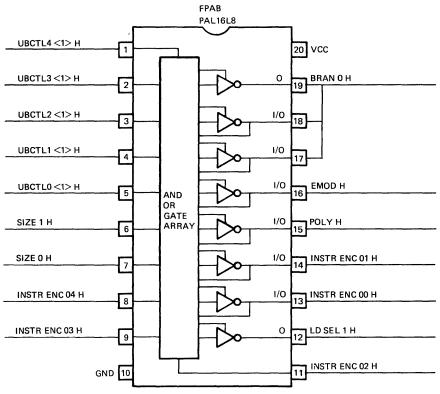

| A-14Extended Function PALA-15A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-17A-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A-13 |                                                |             |

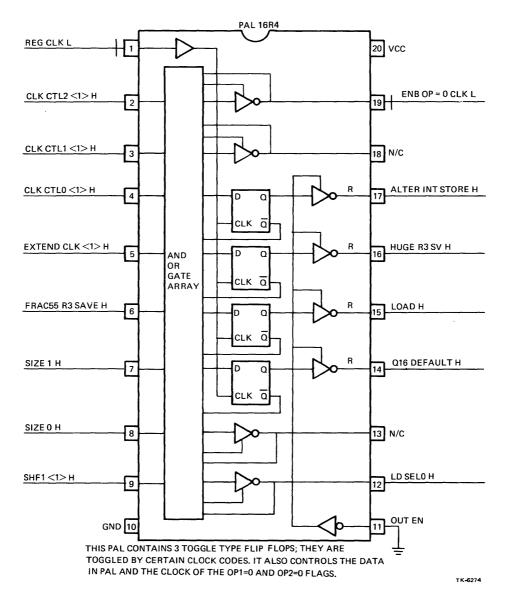

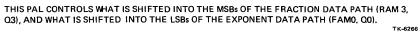

| A-15Fraction Shift Control PALA-16A-16Exponent Control PALA-17A-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                                |             |

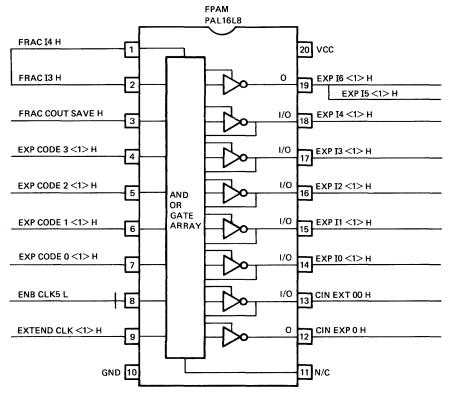

| A-16Exponent Control PALA-17A-17Store Control PALA-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                                |             |

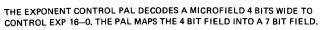

| A-17 Store Control PAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                                                |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                                |             |