# VAX-11/730 IDC Technical Description

Prepared by Educational Services of Digital Equipment Corporation

#### Copyright © 1982 by Digital Equipment Corporation

#### All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| digital | DECsystem-10 | MASSBUS      |

|---------|--------------|--------------|

| DEC     | DECSYSTEM-20 | OMNIBUS      |

| PDP     | DIBOL        | <b>OS</b> /8 |

| DECUS   | EDUSYSTEM    | RSTS         |

| UNIBUS  | VAX          | RSX          |

|         | VMS          | IAS          |

\_\_\_\_\_

# CONTENTS

## CHAPTER 1 INTRODUCTION

| 1.1   | GENERAL DESCRIPTION                        |     |

|-------|--------------------------------------------|-----|

| 1.2   | PHYSICAL DESCRIPTION                       | 1-1 |

| 1.3   | POWER REQUIREMENTS                         | 1-3 |

| 1.4   | FUNCTIONAL DESCRIPTION                     |     |

| 1.4.1 | Disk Drive Select and Drive Status Monitor | 1-4 |

| 1.4.2 | Asserting Disk Drive Commands              | 1-4 |

| 1.4.3 | Synchronization of IDC Operation           | 1-4 |

| 1.4.4 | Address Location                           | 1-4 |

| 1.4.5 | Data Transfers                             | 1-5 |

| 1.4.6 | Verifying Data Integrity                   |     |

| 1.4.7 | Status Word Generation                     | 1-5 |

|       |                                            |     |

# CHAPTER 2 INTERFACES

| 2.1     | IDC INTERFACES                             | 2-1  |

|---------|--------------------------------------------|------|

| 2.2     | IDC/PORT BUS AND UNIBUS INTERFACES         | 2-1  |

| 2.2.1   | Control Words                              |      |

| 2.2.1.1 | IDC Control Word                           | 2-3  |

| 2.2.1.2 | Disk Drive Control Words                   |      |

| 2.2.1.3 | RL02 Get Status Command                    |      |

| 2.2.1.4 | RL02 Seek Command                          |      |

| 2.2.1.5 | R80 Seek Command                           |      |

| 2.2.1.6 | R80 Head Select Command                    | 2-8  |

| 2.2.1.7 | R80 Recalibrate Command                    |      |

| 2.2.2   | Address Information                        |      |

| 2.2.3   | Status Information                         | 2-8  |

| 2.2.3.1 | IDC Status Word                            |      |

| 2.2.3.2 | RL02 Status                                | 2-8  |

| 2.2.3.3 | R80 Status                                 | 2-8  |

| 2.2.4   | Error Detection Information                |      |

| 2.2.5   | Port Microinstruction Inputs               |      |

| 2.2.6   | PORT INSTR Input                           |      |

| 2.2.7   | READ PORT and SEL ACC IN Inputs            |      |

| 2.2.8   | CPU P2 and PORT CLOCK Inputs               |      |

| 2.3     | IDC/R80 INTERFACE                          |      |

| 2.3.1   | R80 TAG 3:1 and R80 TAG BUS 9:0            |      |

| 2.3.2   | ACLO, GND, and R80 INITIALIZE              | 2-21 |

| 2.3.3   | R80 WRITE DATA and R80 WRITE CLOCK         |      |

| 2.3.4   | R80 SECTOR COUNT 1, 2, 4, 8, and 16        |      |

| 2.3.5   | R80 FAULT, R80 PLUG VALID, R80 SEEK ERROR, |      |

|         | R80 ON CYLINDER, R80 DRIVE READY, and R80  |      |

|         | WRITE PROTECT                              |      |

| 2.3.6   | R80 SELECT ADDRESS 1 and 2                 |      |

| 2.3.7   | R80 INDEX PULSE and R80 SECTOR PULSE       |      |

| 2.3.8   | R80 READ DATA and R80 READ CLOCK           |      |

| 2.4   | IDC/RL02 INTERFACE                   | 2-23 |

|-------|--------------------------------------|------|

| 2.4.1 | RL DRIVE COMMAND and RL SYSTEM CLOCK |      |

| 2.4.2 | RL DRIVE SELECT 0 and 1              | 2-25 |

| 2.4.3 | POWER FAIL (ACLO)                    | 2-25 |

| 2.4.4 | RL WRITE GATE and RL WRITE DATA      |      |

| 2.4.5 | RL DRIVE READY                       | 2-26 |

| 2.4.6 | RL DRIVE ERROR                       |      |

| 2.4.7 | RL STATUS and RL STATUS CLOCK        |      |

| 2.4.8 | RL SECTOR PULSE                      | 2-26 |

| 2.4.9 | RL READ DATA                         | 2-26 |

## CHAPTER 3 THEORY OF OPERATION

| 3.1     | IDC FUNCTIONS                                       | -1 |

|---------|-----------------------------------------------------|----|

| 3.2     | OVERALL IDC OPERATION                               | .3 |

| 3.2.1   | Initiating IDC Functions                            |    |

| 3.2.1.1 | Loading Required Inputs                             | .3 |

| 3.2.1.2 | Loading the IDC Control Word                        |    |

| 3.2.2   | IDC Operation                                       |    |

| 3.2.3   |                                                     |    |

|         | Transfer of Information and Data<br>from IDC to CPU | .4 |

| 3.2.3.1 | IDC Status Information Transfer                     |    |

|         | (IDC to CPU)                                        | -4 |

| 3.2.3.2 | Disk Drive Status Information Transfer              |    |

|         | (IDC to CPU)                                        | -4 |

| 3.2.3.3 | ECC/CRC Error Detection Information Transfer        |    |

|         | (IDC to CPU)                                        | .5 |

| 3.2.3.4 | Current Address Information Transfer                |    |

|         | (IDC to CPU)                                        | -5 |

| 3.2.3.5 | Data Transfer (IDC to CPU)                          | .5 |

| 3.3     | OVERALL IDC LOGIC FAMILIARIZATION                   | -5 |

| 3.3.1   | IDC Port Control Logic                              | .5 |

| 3.3.2   | Microcontroller                                     |    |

| 3.3.3   | Y-Bus Transceivers                                  | •6 |

| 3.3.4   | Disk Address Register                               |    |

| 3.3.5   | Data Input Register, Data Buffer, and Data          |    |

|         | Register Control Logic, Data Output Register,       |    |

|         | Read Data Tristate Drivers, and R80 Multiplexer     | •6 |

| 3.3.6   | Control Status Register                             | 6  |

| 3.3.7   | Clock Control                                       | .9 |

| 3.3.8   | TAG Bus Control                                     | 9  |

| 3.3.9   | Serializer                                          | .9 |

| 3.3.10  | Header/Data Comparator3-                            | 9  |

| 3.3.11  | Data Shift Register                                 | 9  |

| 3.3.12  | NRZ Data Formatter                                  | 0  |

| 3.3.13  | MFM Encoder                                         | 0  |

| 3.3.14  | ECC/CRC Logic                                       | 0  |

| 3.3.15  | Read Data Separator                                 |    |

| 3.3.16  | Status/Data Gate                                    | 0  |

| 3.3.17  | Disk Data Multiplexer                               |    |

| 3.3.18  | Data Synchronizer                                   | 0  |

| 3.3.19  | Sector and Index Pulse Multiplexer and Synchronizer | 0  |

| 3.4      | IDC FUNCTIONAL THEORY OF OPERATION          |      |

|----------|---------------------------------------------|------|

| 3.4.1    | Seek Functions                              |      |

| 3.4.1.1  | RL02 Seek                                   |      |

| 3.4.1.2  | R 80 Seek                                   |      |

| 3.4.2    | RL02 Get Status                             |      |

| 3.4.3    | R80 Get Status                              |      |

| 3.4.4    | Read Header                                 |      |

| 3.4.4.1  | RL02 Read Header                            |      |

| 3.4.4.2  | R80 Read Header                             |      |

| 3.4.5    | Write Data, Read Data, and Write Check Data |      |

| 3.4.5.1  |                                             |      |

| 5.4.5.1  | RL02 Write Data, Read Data, and Write       | 2 17 |

| 2 4 5 2  | Check                                       |      |

| 3.4.5.2  | R80 Write Data, Read Data, and Write        | 2.24 |

| 2.4.4    | Check.                                      |      |

| 3.4.6    | Read Data Without Header Check              |      |

| 3.4.6.1  | RL02 Read Data Without Header Check         |      |

| 3.4.6.2  | R80 Read Data Without Header Check          |      |

| 3.4.7    | Write Format                                |      |

| 3.4.8    | Idle Mode                                   |      |

| 3.5      | DETAILED FUNCTIONAL DESCRIPTIONS            | 3-38 |

| 3.5.1    | Disk Drive Selection and Drive              |      |

|          | Status Monitor                              |      |

| 3.5.1.1  | Generation of DRIVE SEL 0 and 1             |      |

| 3.5.1.2  | Generation of RL02 and R80                  |      |

| 3.5.1.3  | Gating DRIVE RDY                            |      |

| 3.5.1.4  | Gating DRIVE ERR                            |      |

| 3.5.2    | TAG Bus Control Logic                       |      |

| 3.5.2.1  | Asserting R80 Seek, Head Select,            |      |

| 5.5.2.1  | and Recalibrate Commands                    | 3-41 |

| 3.5.2.2  | Asserting Read Gate                         |      |

| 3.5.2.3  | Asserting Write Gate                        |      |

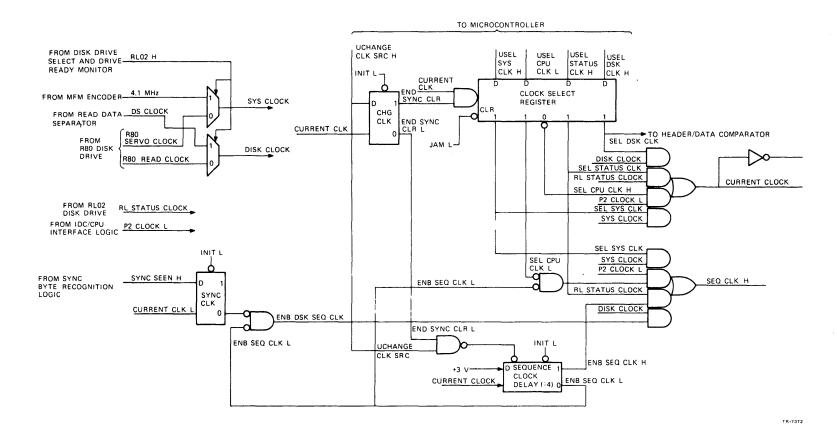

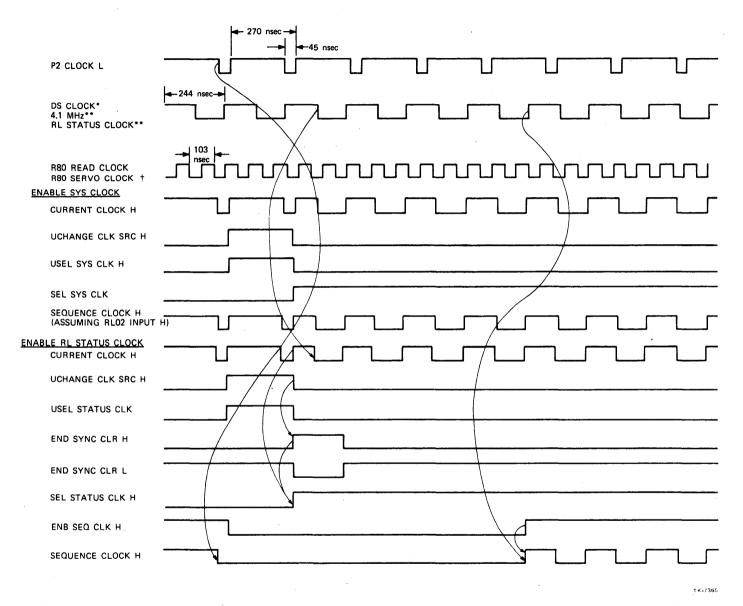

| 3.5.3    | Clock Control Logic                         |      |

| 3.5.3.1  | Enable SYS CLOCK                            |      |

| 3.5.3.2  | Enable RL STATUS CLOCK or CPU CLOCK         |      |

|          | Enable DISK CLOCK                           |      |

| 3.5.3.3  |                                             |      |

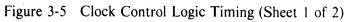

| 3.5.4    | Sync Byte Recognition Logic                 |      |

| 3.5.5    | RL02 Header Comparison Logic                |      |

| 3.5.6    | R80 Header Comparison and Skip Sector       |      |

|          | Monitor Logic                               |      |

| 3.5.6.1  | R80 Header Comparison Logic                 |      |

| 3.5.6.2  | Skip Sector Monitor Logic                   |      |

| 3.5.7    | SKIP SECTOR CONTROL LOGIC                   |      |

| 3.5.8    | Write Check Data Comparison Logic           |      |

| 3.5.9    | Interrupt Control Logic                     |      |

| 3.5.9.1  | UBUS BR5                                    |      |

| 3.5.9.2  | PORT XFER REQ                               |      |

| 3.5.10   | IDC Control Register, Timeout Logic,        |      |

|          | and Status Logic                            |      |

| 3.5.10.1 | IDC Control Register                        |      |

| 3.5.10.2 | Timeout and Status Logic                    |      |

| 3.5.11   | Serializing Data from Data Buffer           |      |

|          | and Sync Byte Tristate Drivers              | 3_60 |

| 3.5.12   | Formatting and Loading Disk Drive Read Data |      |

| 5.5.12   | in Data Buffers                             |      |

| 3.5.13   | IDC/CPU Interface Logic                |  |

|----------|----------------------------------------|--|

| 3.5.13.1 | Loading CSR                            |  |

| 3.5.13.2 | Reading CSR                            |  |

| 3.5.13.3 | Loading Disk Address Register          |  |

| 3.5.13.4 | Read Disk Address Register             |  |

| 3.5.13.5 | Reading ECC/CRC Logic                  |  |

| 3.5.13.6 | Loading IDC Data Buffers               |  |

| 3.5.13.7 | Reading IDC Data Buffers               |  |

| 3.5.13.8 | Initializing/Clearing IDC and R80      |  |

|          | Disk Drive                             |  |

| 3.5.14   | Microcontroller Branching, Loops,      |  |

|          | and Stalls                             |  |

| 3.5.14.1 | Microcontroller Branching              |  |

| 3.5.14.2 | Microcontroller Loops                  |  |

| 3.5.14.3 | Microcontroller Stalls                 |  |

| 3.5.15   | Read Data Separator Operation          |  |

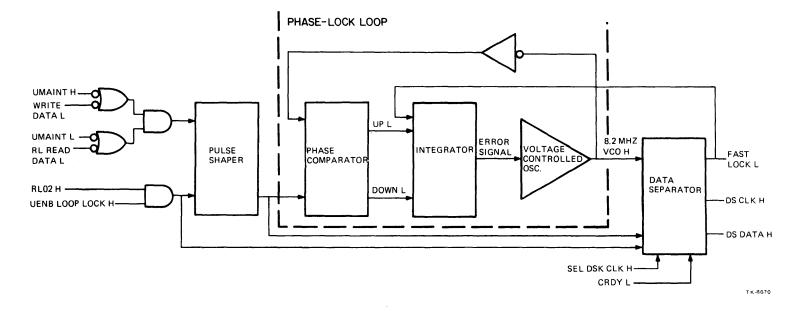

| 3.5.15.1 | Phase Lock Loop (PLL)                  |  |

| 3.5.15.2 | Data Separator                         |  |

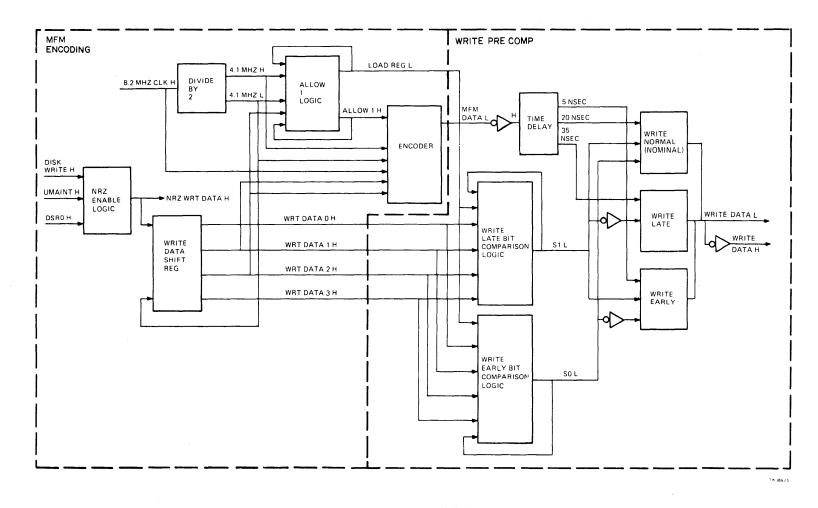

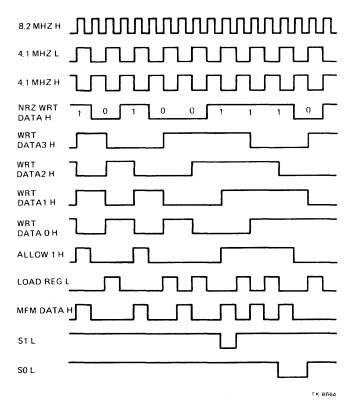

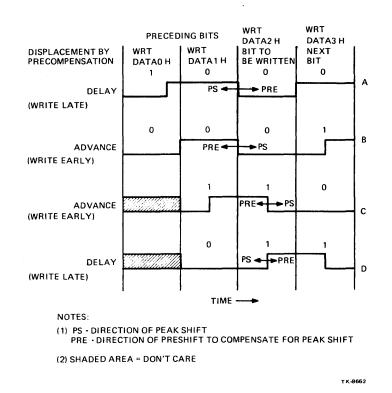

| 3.5.16   | MFM Encoding and Write Precompensation |  |

| 3.5.16.1 | MFM Encoding                           |  |

| 3.5.16.2 | Write Precompensation                  |  |

# CHAPTER 4 MAINTAINABILITY FEATURES

| 4.1   | MAINTAINABILITY FEATURES          | 4-1 |

|-------|-----------------------------------|-----|

| 4.1.1 | Maintenance Mode                  | 4-1 |

| 4.1.2 | Data Loopback                     | 4-1 |

| 4.1.3 | Write Inhibit and Timeout Inhibit |     |

| 4.1.4 | Defeatable Enables                | 4-1 |

# CHAPTER 5 PROGRAM INTERFACE

| 5.1     | BASIC SYSTEM OPERATION                  | 5-1 |

|---------|-----------------------------------------|-----|

| 5.2     | PROGRAMMING OVERVIEW                    | 5-1 |

| 5.2.1   | IDC Registers                           | 5-1 |

| 5.2.1.1 | Control Status Register (CSR)           | 5-1 |

| 5.2.1.2 | Bus Address Register (BAR)              |     |

| 5.2.1.3 | Byte Count Register (BCR)               |     |

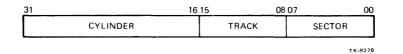

| 5.2.1.4 | Disk Address Register (DAR)             |     |

| 5.2.1.5 | Multipurpose Register (MPR)             | 5-7 |

| 5.2.1.6 | ECC Position Register                   | 5-8 |

| 5.2.1.7 | ECC Pattern Register                    | 5-8 |

| 5.2.1.8 | IDC Initialization Register             | 5-8 |

| 5.3     | COMMANDS                                | 5-8 |

| 5.3.1   | Positioning Commands                    | 5-8 |

| 5.3.1.1 | Seek Function                           | 5-8 |

| 5.3.2   | Data Transfer Commands                  | 5-9 |

| 5.3.2.1 | Read Header Function                    | 5-9 |

| 5.3.2.2 | Write Data Function                     | 5-9 |

| 5.3.2.3 | Read Data Function                      | 5-9 |

| 5.3.2.4 | Read Data Without Header Check Function | 5-9 |

| 5.3.2.5  | Write Check Function                       | 5-9  |

|----------|--------------------------------------------|------|

| 5.3.2.6  | Get Status Function                        | 5-9  |

| 5.3.3    | Housekeeping Commands                      | 5-12 |

| 5.3.3.1  | NOP Function                               | 5-12 |

| 5.4      | R80 ECC HANDLING                           | 5-12 |

| 5.5      | HARDWARE ERROR RECOVERY                    | 5-12 |

| 5.6      | SOFTWARE ERROR CORRECTION                  | 5-12 |

| 5.7      | R80 SKIP SECTOR OPERATION                  |      |

| 5.7.1    | R80 Bad Spot Problem                       | 5-13 |

| 5.7.2    | The Concept of Skip Sectoring              | 5-13 |

| 5.7.2.1  | The Concept of Skip Sectoring              | 5-13 |

| 5.7.3    | Skip Sectoring (with the Automatic Inhibit |      |

|          | Bit Set)                                   | 5-13 |

| 5.8      | R80 FORMATTING                             | 5-13 |

| 5.9      | EXAMPLES OF SYSTEM OPERATION               | 5-14 |

| 5.9.1    | Seek Operation                             | 5-14 |

| 5.9.2    | Data Transfer Operation (Read/Write)       | 5-15 |

| APPENDIX | PROGRAMMED ARRAY LOGIC DEVICES (PALS)      | A-1  |

# **FIGURES**

| Figure No. | Title                                        | Page |

|------------|----------------------------------------------|------|

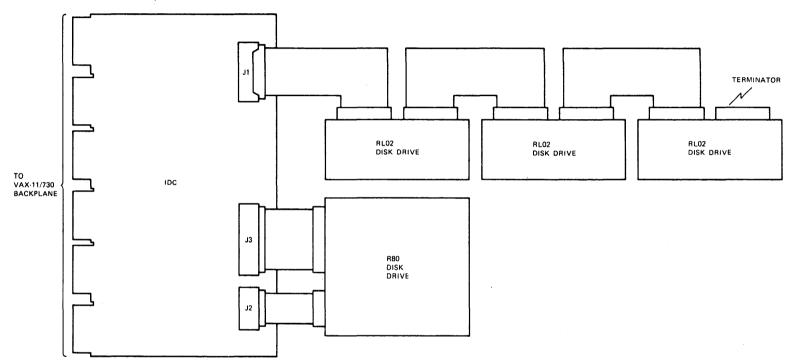

| 1-1        | Interconnections for Possible Configuration  |      |

|            | of RB730 Disk Subsystem                      | 1-2  |

| 2-1        | IDC Signal Interfaces                        |      |

| 2-2        | IDC Control Word Data Format and             |      |

|            | Bit Significance                             |      |

| 2-3        | RL02 Get Status Command Data Format and      |      |

|            | Bit Significance                             | 2-5  |

| 2-4        | RL02 Seek Command Data Format and            |      |

|            | Bit Significance                             | 2-6  |

| 2-5        | R80 Seek Command Data Format and             |      |

|            | Bit Significance                             | 2-7  |

| 2-6        | R80 Head Select Command Data Format and      |      |

|            | Bit Significance                             | 2-9  |

| 2-7        | R80 Recalibrate Command Data Format and      |      |

|            | Bit Significance                             | 2-10 |

| 2-8        | RL02 Read/Write Data Address Data Format and |      |

|            | Bit Significance                             | 2-11 |

| 2-9        | R80 Read/Write Data Address Data Format and  |      |

|            | Bit Significance                             | 2-12 |

| 2-10       | IDC Status Word Data Format and              |      |

|            | Bit Significance                             | 2-13 |

| 2-11       | RL02 Status Information Data Format and      |      |

|            | Bit Significance                             | 2-14 |

| 2-12       | R80 Status Information Data Format and       |      |

|            | Bit Significance                             |      |

| 2-13       | Port Microinstructions Format and<br>Bit Significance                                 | 2-17          |

|------------|---------------------------------------------------------------------------------------|---------------|

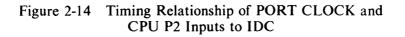

| 2-14       | Timing Relationship of PORT CLOCK and CPU P2<br>Inputs to IDC                         |               |

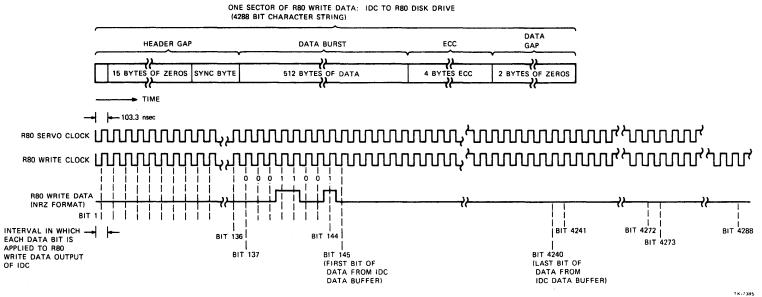

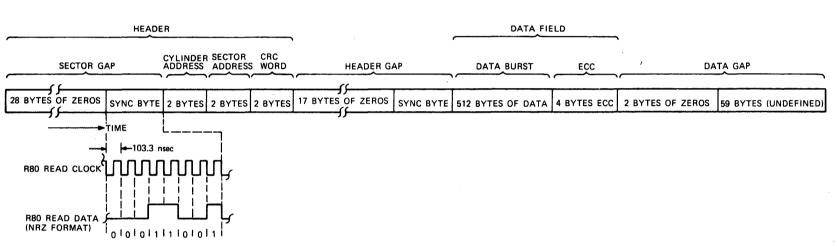

| 2-15       | R80 Write Data Format and Data Transfer Timing:                                       | 2 <b>-</b> 20 |

| 2-15       | IDC to R80                                                                            | 2-22          |

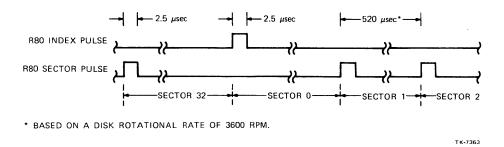

| 2-16       | R80 Sector Pulse and Index Pulse Timing                                               |               |

| 2-17       | R80 Read Data Format and Data Transfer Timing:                                        | 225           |

| 21.        | R80 to IDC                                                                            | 2-24          |

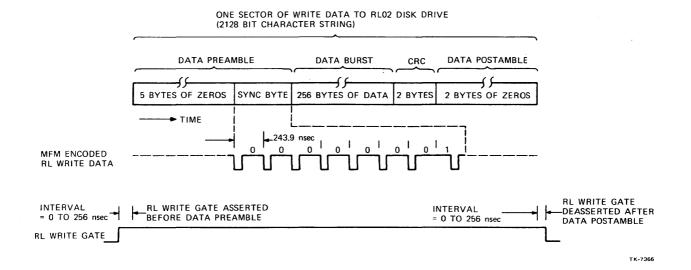

| 2-18       | RL Write Data Format and Data Transfer Timing:<br>IDC to RL02                         |               |

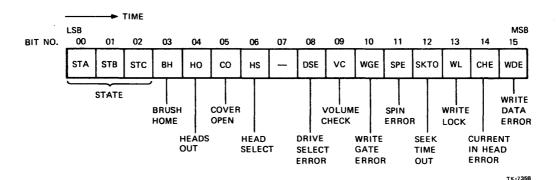

| 2-19       | Format and Bit Significance of RL02 Status                                            |               |

|            | Information Transfer: RL02 to IDC                                                     | 2-26          |

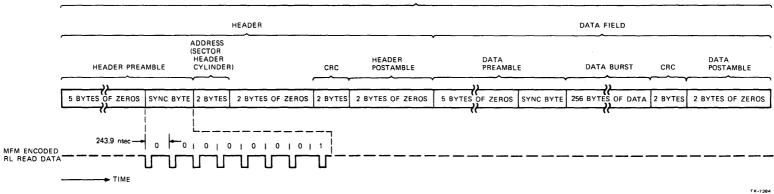

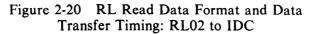

| 2-20       | RL Read Data Format and Data Transfer Timing:                                         |               |

|            | RL02 to IDC                                                                           | 2-27          |

| 2.1        |                                                                                       | 2.7           |

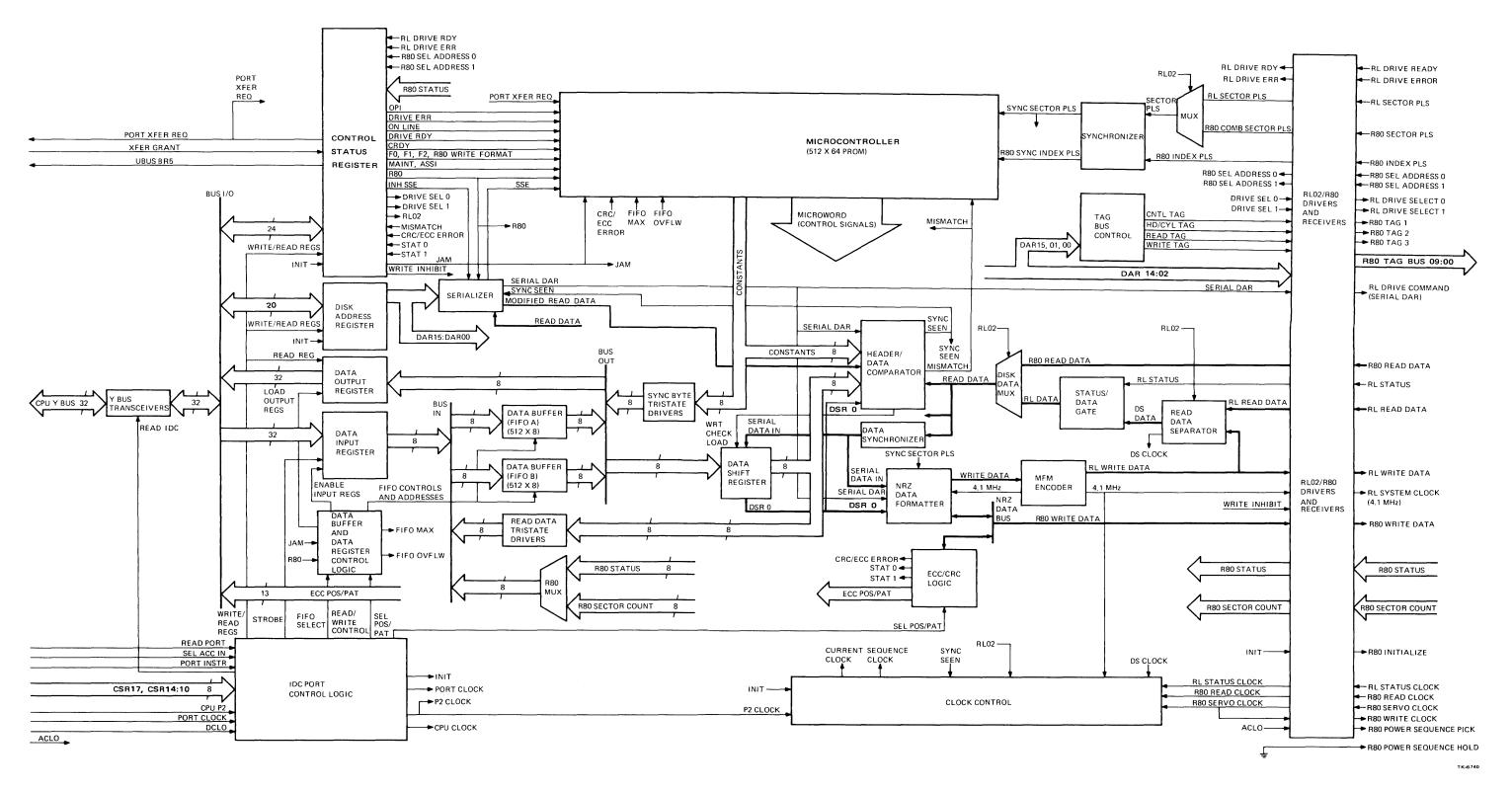

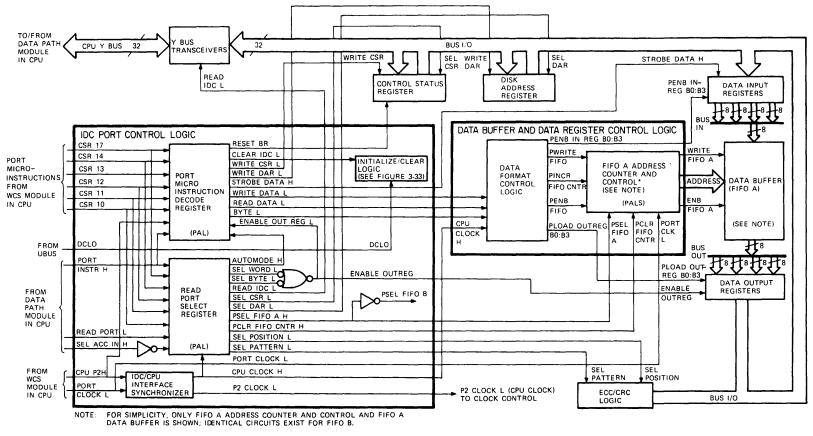

| 3-1        | IDC Functional Block Diagram                                                          |               |

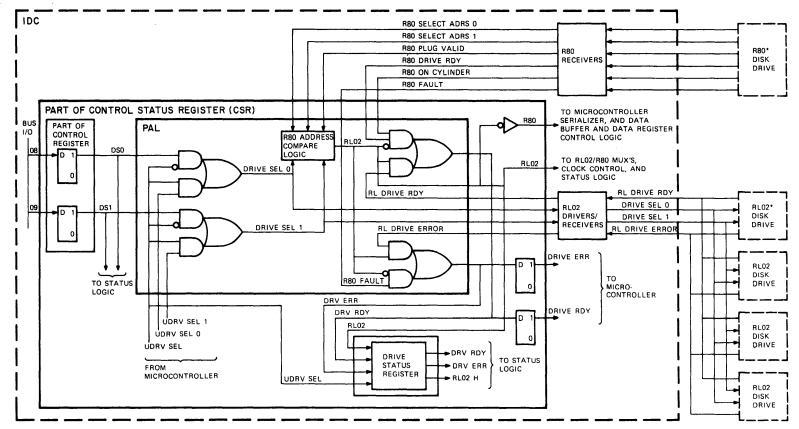

| 3-2        | Disk Drive Selection and Drive Status Monitor                                         |               |

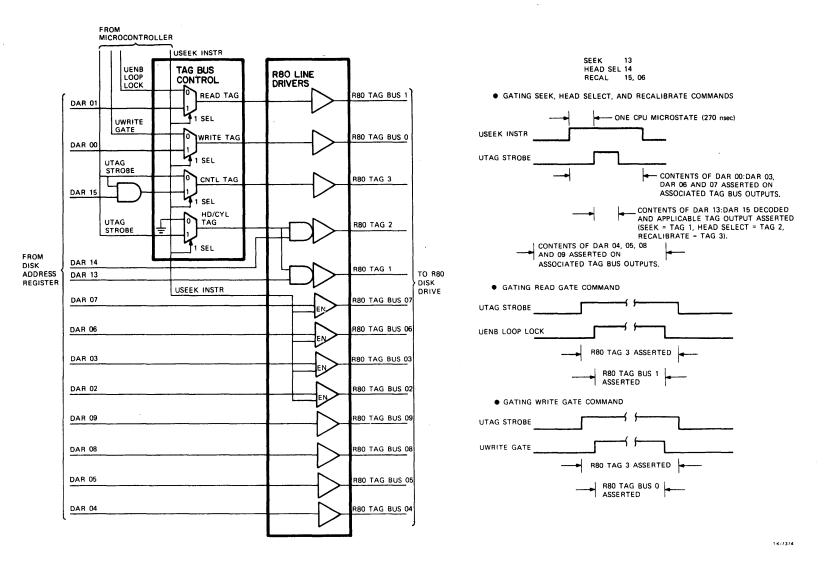

| 3-3        | TAG Bus Control Logic Functional Diagram                                              |               |

| 3-4        | Clock Control Logic Functional Block Diagram                                          |               |

| 3-5        | Clock Control Logic Timing Diagram                                                    | 3-42          |

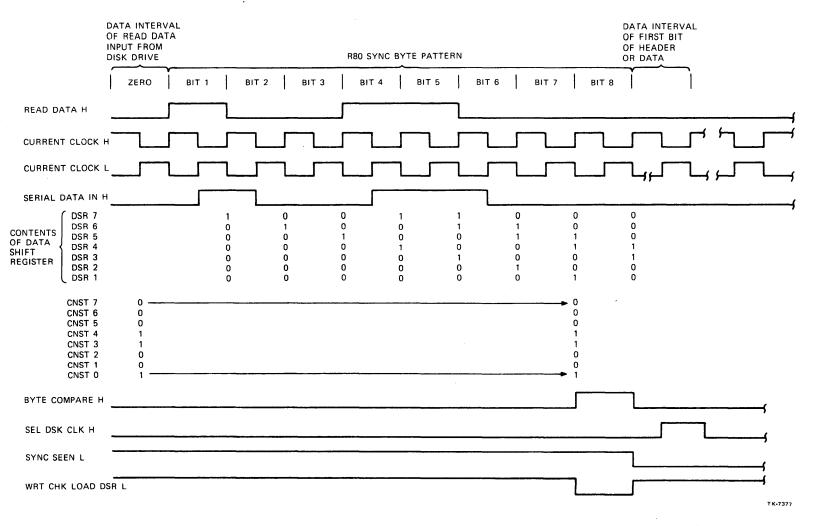

| 3-6        | Sync Byte Recognition Logic Functional<br>Block Diagram                               | 2 16          |

| 3-7        |                                                                                       |               |

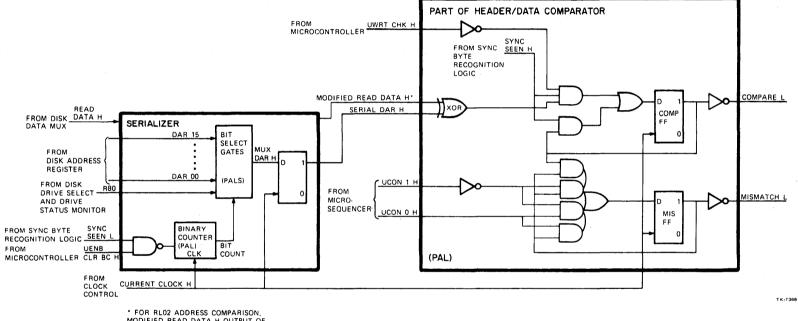

| 3-7<br>3-8 | Sync Byte Recognition Logic Timing Diagram<br>RL02 Header Comparison Logic Functional | 3-47          |

| 3-0        | Block Diagram                                                                         | 2 40          |

| 3-9        | RL02 Header Comparison Logic Timing Diagram                                           |               |

| 3-10       | R80 Header Comparison and Skip Sector Monitor                                         | 5-51          |

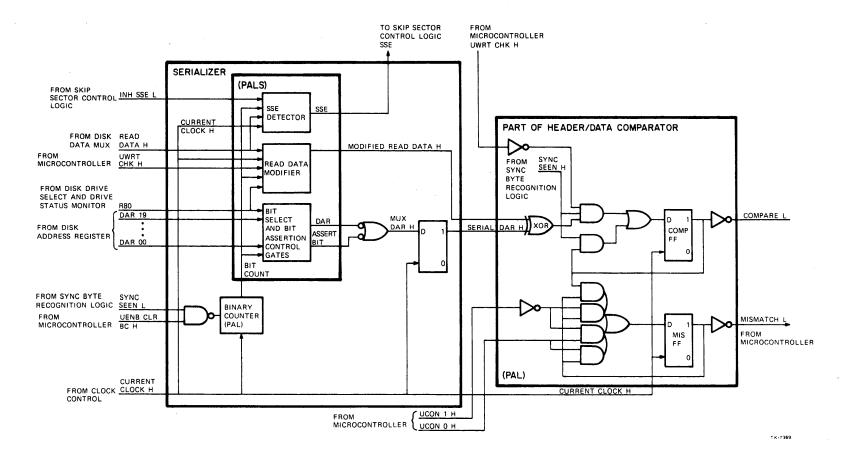

| J-10       | Logic Functional Block Diagram                                                        | 3-52          |

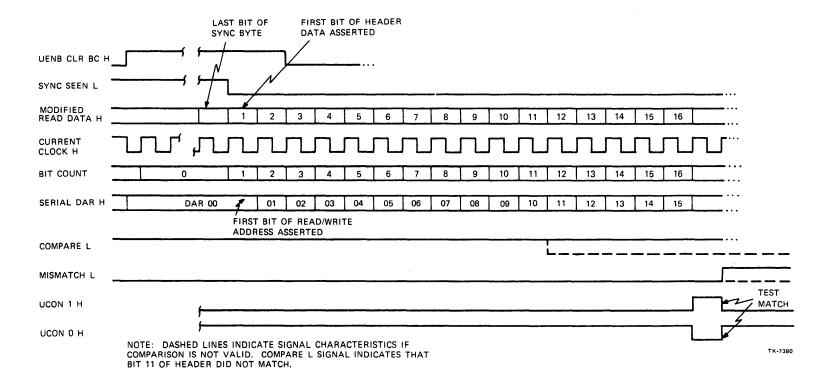

| 3-11       | R80 Header Data Modification and Comparison                                           | 5-52          |

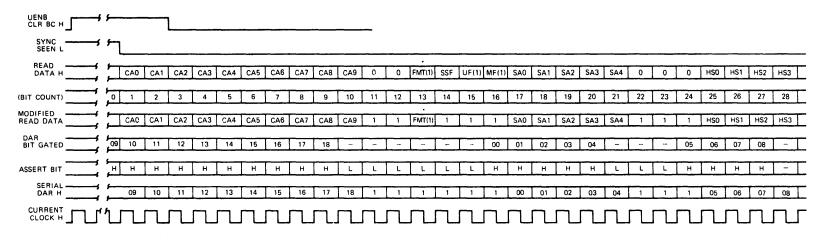

| 511        | Data Control Timing                                                                   | 3-54          |

| 3-12       | Skip Sector Control Logic Functional Block                                            | 5 54          |

| 512        | Diagram                                                                               | 3-55          |

| 3-13       | Skip Sector Example                                                                   |               |

| 3-14       | Write Check Data Comparison Logic Functional                                          | 5 50          |

|            | Block Diagram                                                                         | 3-57          |

| 3-15       | Write Check Data Comparison Logic Timing                                              |               |

|            | Diagram                                                                               | 3-59          |

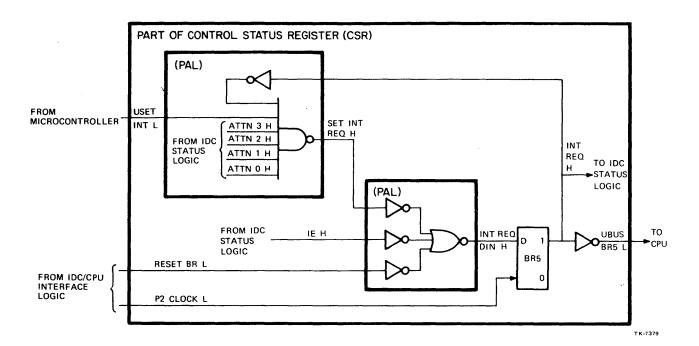

| 3-16       | UBUS BR5 Interrupt Control Logic Functional                                           |               |

|            | Block Diagram                                                                         | 3-60          |

| 3-17       | PORT XFER REQ Logic Functional Block Diagram                                          |               |

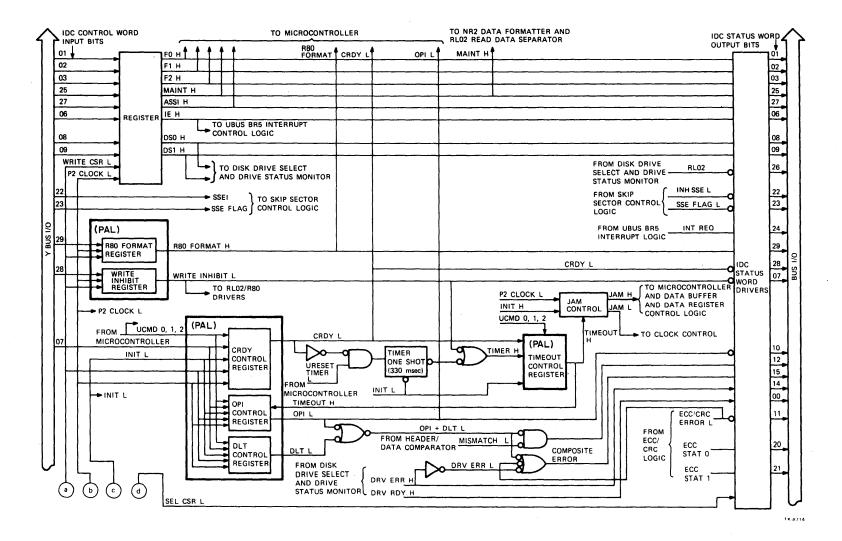

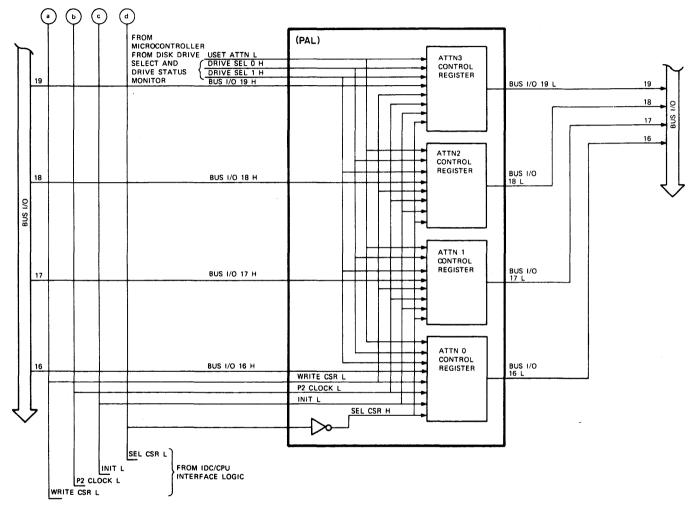

| 3-18       | IDC Control Register Timeout Logic and Status                                         |               |

|            | Logic Functional Block Diagram                                                        | 3-62          |

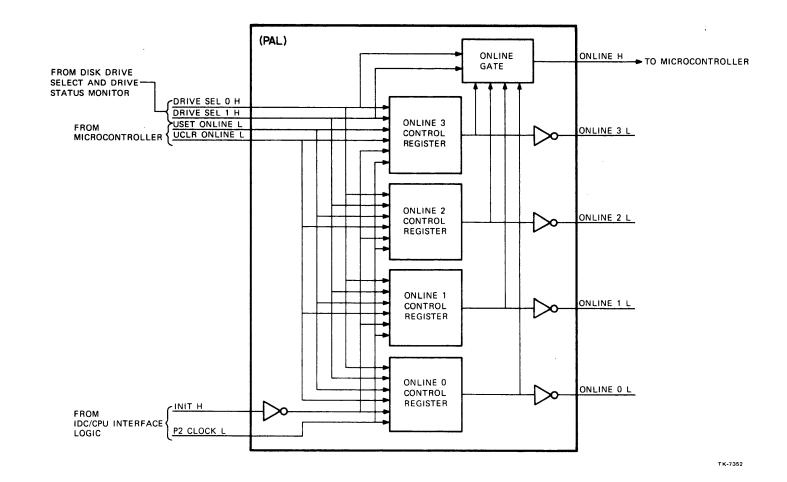

| 3-19       | Data and Sync Byte Serialization Control Logic                                        |               |

|            | Functional Block Diagram                                                              | 3-68          |

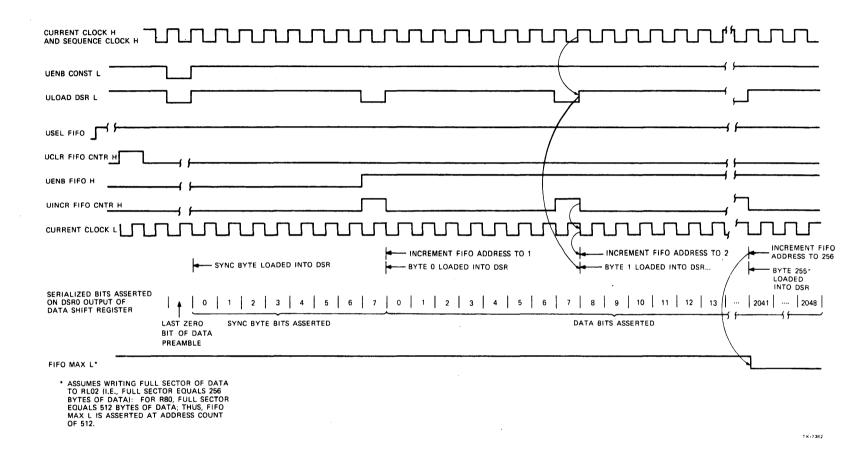

| 3-20       | Data and Sync Byte Serialization Control Logic                                        |               |

|            | Timing Diagram                                                                        | 3-70          |

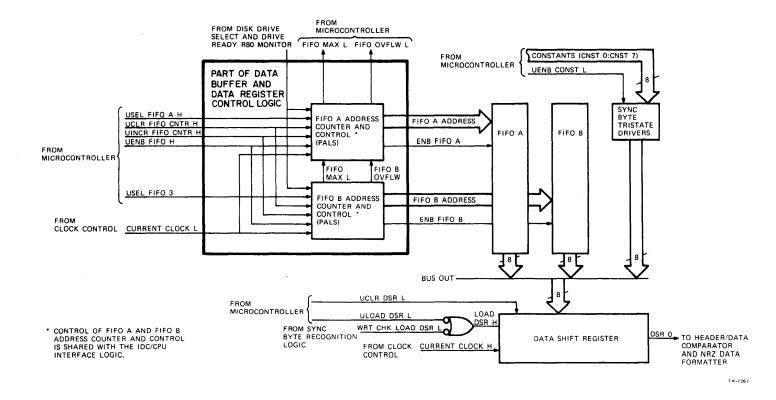

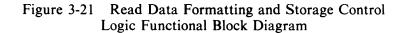

| 3-21       | Read Data Formatting and Storage Control Logic                                        |               |

|            | Functional Block Diagram                                                              | 3-72          |

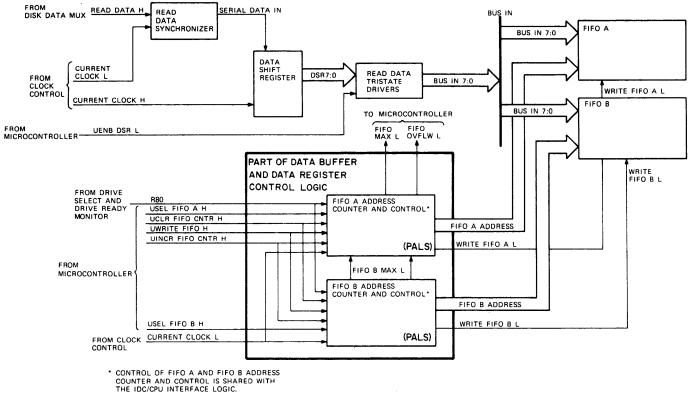

| 3-22       | Formatting and Loading Read Data Input to FIFO:                                       |               |

|            | Timing Diagram                                                                        | 3-73          |

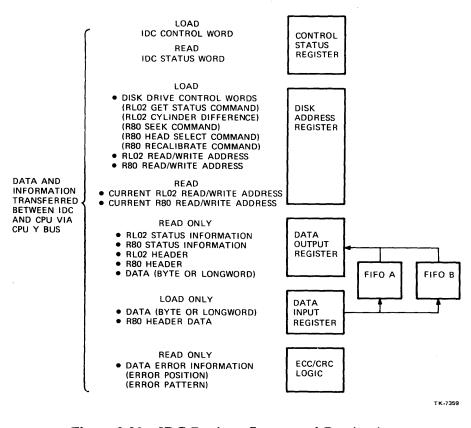

| 3-23  | IDC Register Source and Destination for        |    |

|-------|------------------------------------------------|----|

|       | Data and Information Transferred between IDC   |    |

|       | and CPU via CPU Y-Bus 3-7                      | /4 |

| 3-24  | IDC/CPU Interface Logic Functional             |    |

|       | Block Diagram 3-7                              | 15 |

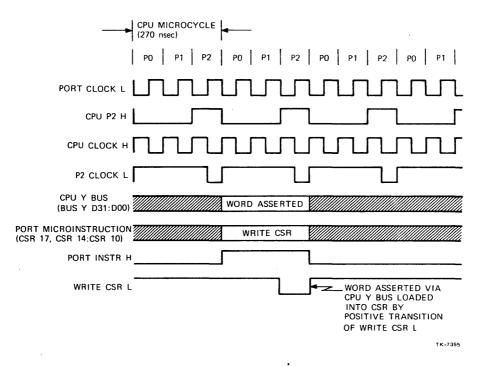

| 3-25  | IDC Control Word Transfer Timing (CPU to IDC)  | 16 |

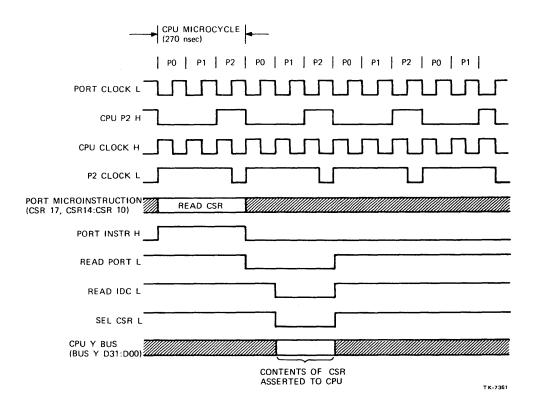

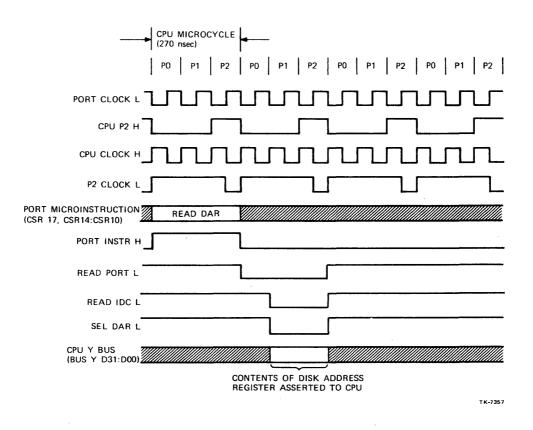

| 3-26  | IDC Status Word Transfer Timing (IDC to CPU)   | 17 |

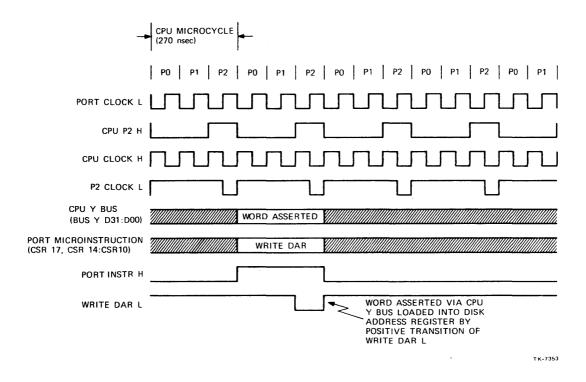

| 3-27  | Disk Drive Control Word and Read/Write Address |    |

|       | Transfer Timing (CPU to IDC) 3-7               | 18 |

| 3-28  | Current Read/Write Address Transfer Timing     |    |

|       | (IDC to CPU) 3-7                               | 19 |

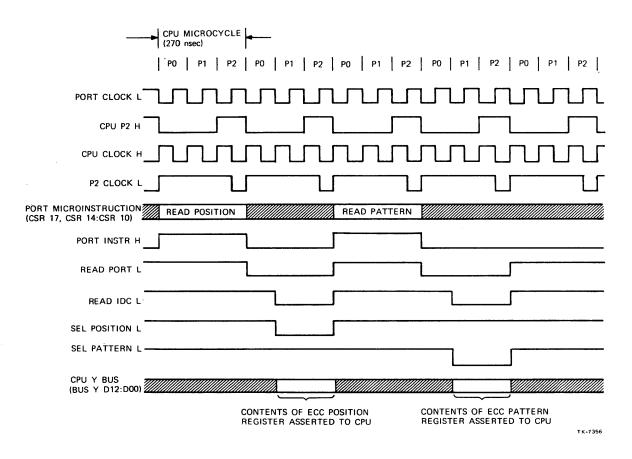

| 3-29  | Data Error Information Transfer Timing         |    |

|       | (IDC to CPU) 3-8                               |    |

| 3-30  | Data Byte Transfer Timing (CPU to IDC) 3-8     |    |

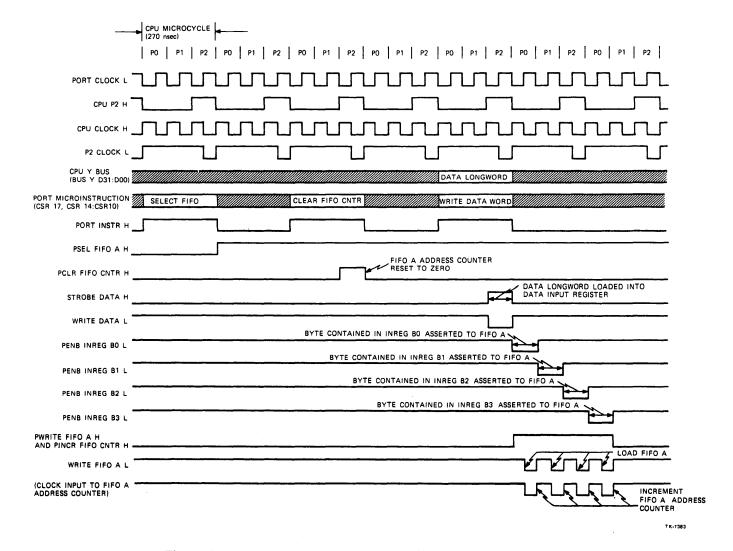

| 3-31  | Data Longword Transfer Timing (CPU to IDC)     |    |

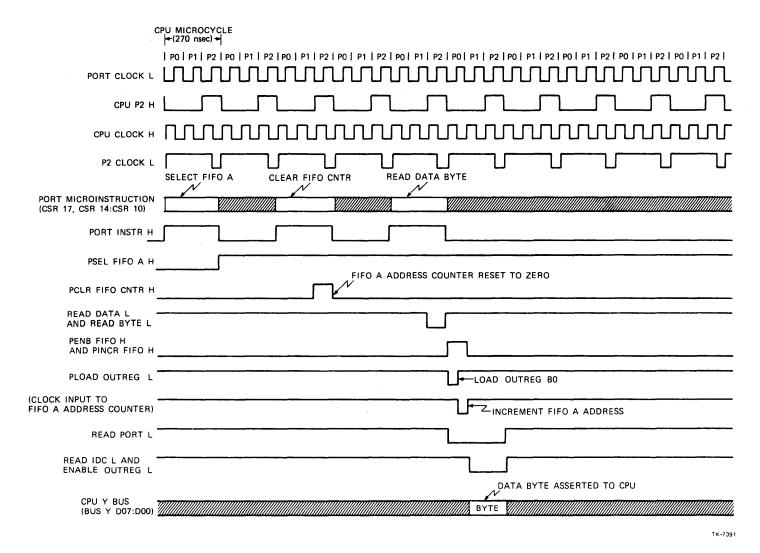

| 3-32  | Data Byte Transfer Timing (IDC to CPU)         | 56 |

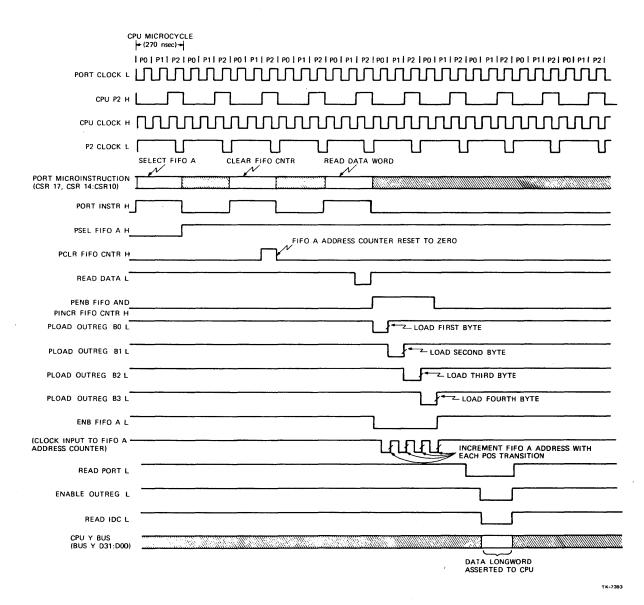

| 3-33  | Single Data Longword Transfer Timing           |    |

|       | (IDC to CPU)                                   | 57 |

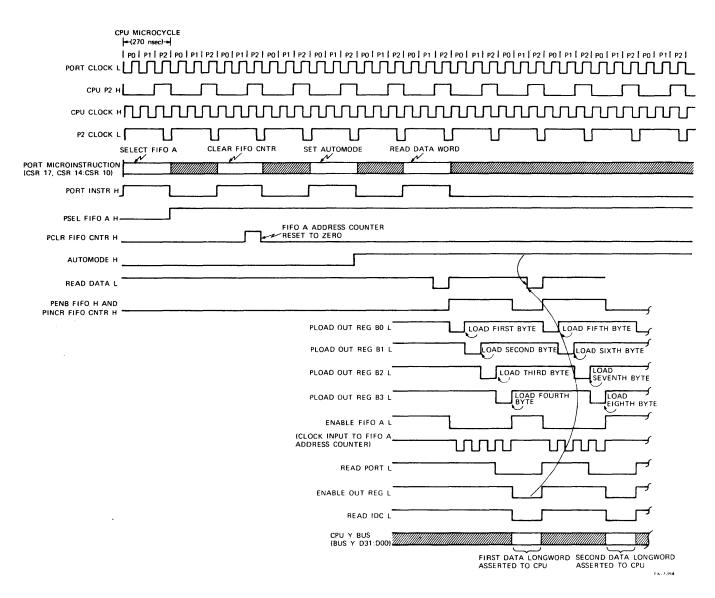

| 3-34  | Automode Data Longword Transfer Timing         |    |

|       | (IDC to CPU)                                   | 38 |

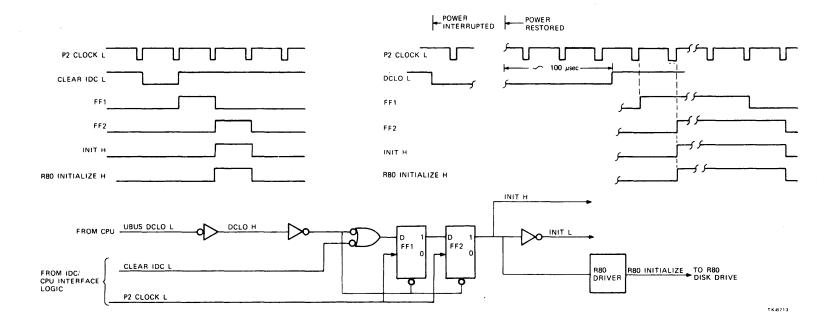

| 3-35  | Initialize/Clear Logic Diagram 3-8             | 59 |

| 3-36  | Microcontroller Functional Block Diagram       | 0  |

| 3-37  | Read Data Separator Block Diagram              | 12 |

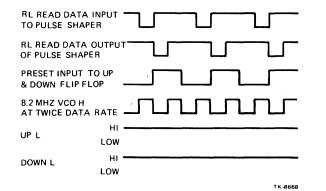

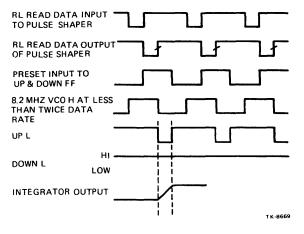

| 3-38a | VCO Output at Twice Data Rate (Frequency Lock) |    |

|       | Timing Diagram                                 | 13 |

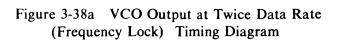

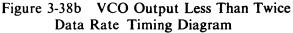

| 3-38b | VCO Output Less Than Twice Data Rate           |    |

|       | Timing Diagram                                 | 13 |

| 3-38c | VCO Output More Than Twice Data Rate           |    |

|       | Timing Diagram                                 | 14 |

| 3-39  | Loop Lock Settling Time                        | 14 |

| 3-40  | Data Separator Detailed Diagram                | 15 |

| 3-41  | Data Separator Timing Diagram 3-9              |    |

| 3-42  | MFM Encoding and Write Precompensation         |    |

|       | Logic Functional Block Diagram                 | 17 |

| 3-43  | MFM Encoding and Write Precompensation         |    |

|       | Timing Diagram                                 | 18 |

| 3-44  | Write Precompensation Early/Late Bit           |    |

|       | Combinations                                   | 19 |

| 5-1   | Disk Address Register                          | -7 |

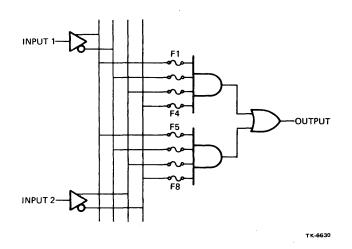

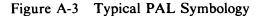

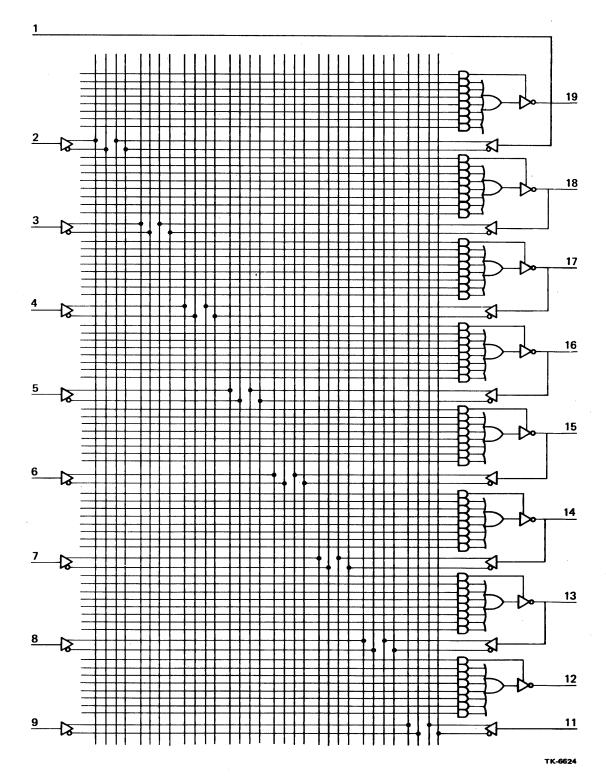

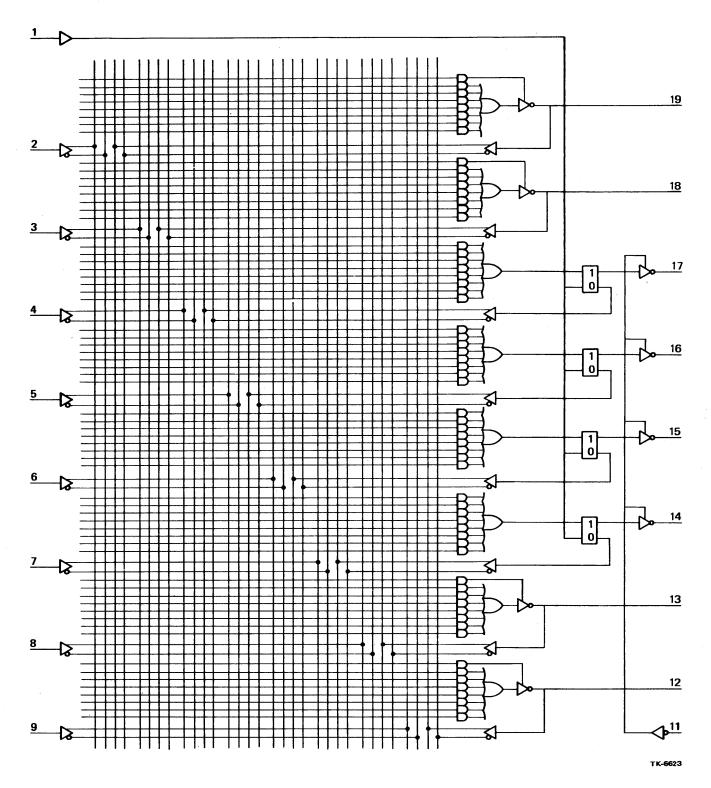

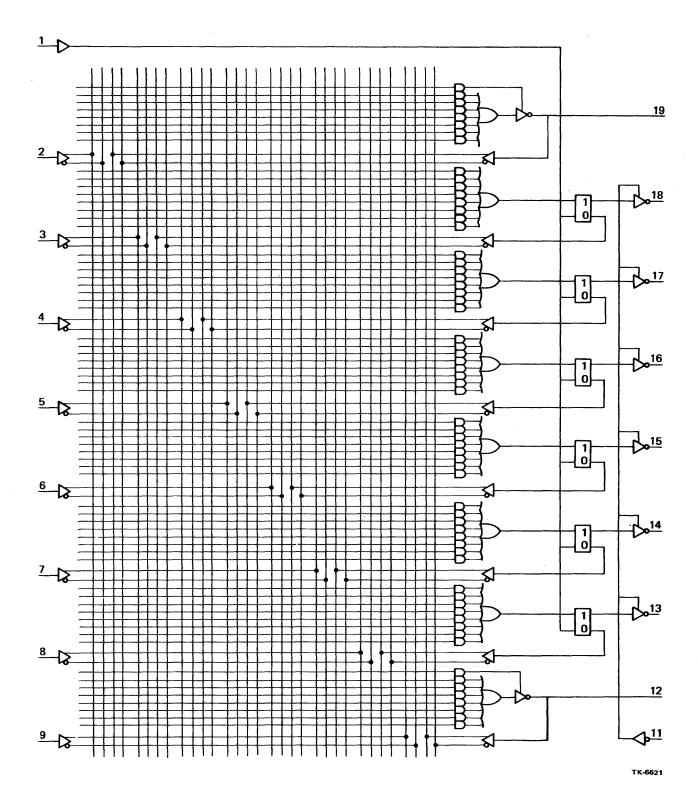

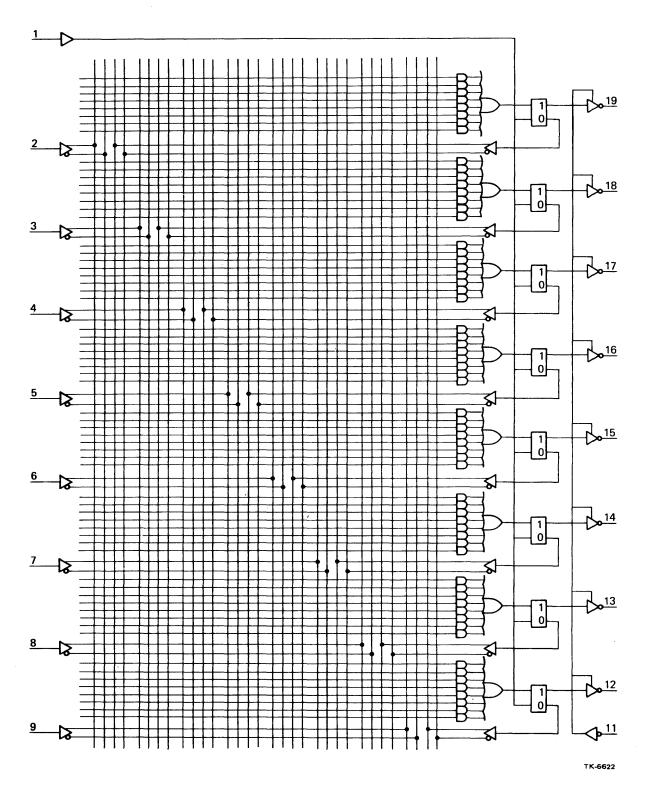

| A-1   | Basic PAL Logic Configuration A-               | -1 |

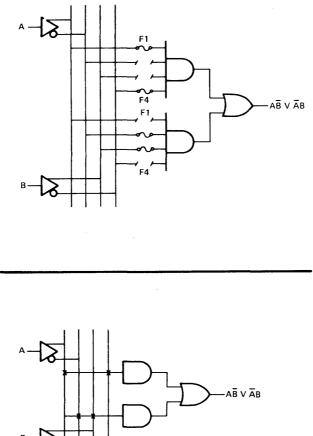

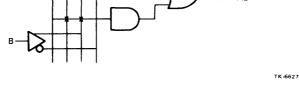

| A-2   | XOR Logic Function Using PAL Logic A-          |    |

| A-3   | Typical PAL Symbology                          |    |

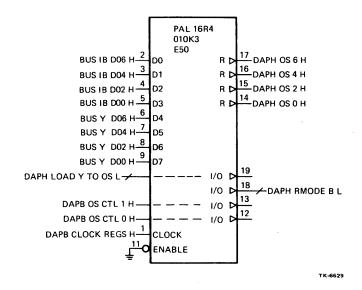

| Δ-4   | PAL Plot Listing                               |    |

| A-5   | Logic Diagram: PAL16L8                         |    |

| A-6   | Logic Diagram: PALI6R4                         |    |

| A-9   | Logic Diagram: PAL16R6                         |    |

| A-10  | Logic Diagram: PAL16R8                         |    |

|       |                                                |    |

# TABLES

| Table No.  | Title                                                | Page |

|------------|------------------------------------------------------|------|

| 1-1<br>1-2 | Related Documentation<br>CPU-Initiated IDC Functions |      |

| 2-1        | Port Microinstruction Functions                      | 2-18 |

| 3-1        | IDC Functions                                        |      |

| 5-1        | IDC Registers                                        |      |

| 5-2        | Control Status Register Bit Assignments              |      |

| 5-3        | MPR Bit Assignments                                  |      |

| 5-4        | RL02 Get Status                                      |      |

| 5-5        | R80 Get Status                                       | 5-11 |

| A-1        | PAL Device Types Used in the VAX-11/730              | A-3  |

# CHAPTER 1 INTRODUCTION

#### **1.1 GENERAL DESCRIPTION**

The Integrated Disk Controller (IDC) is part of the RB730 disk subsystem, a hardware option of the VAX-11/730. The RB730 disk subsystem includes the IDC and up to four RL02 disk drives or the IDC, one R80 disk drive, and up to three RL02 disk drives. The IDC provides the interface between the VAX-11/730 CPU and the associated disk drives of the RB730 disk subsystem for the purpose of data storage and retrieval. This manual presents the IDC technical description. Other documents related to the RB730 disk subsystem of the VAX-11/730 are listed in Table 1-1.

#### **1.2 PHYSICAL DESCRIPTION**

The IDC is a single hex-size module (M8388) that plugs into the VAX-11/730 backplane. All electrical connections for interfacing the IDC with the CPU are provided via the VAX-11/730 backplane. The electrical connections for interfacing the IDC with an R80 disk drive are provided via connectors J2 and J3. Connector J1 provides the electrical connections for interfacing the IDC with the RL02 disk drive(s) in a daisy chain fashion. Figure 1-1 shows the electrical connections for one possible configuration of the RB730 disk subsystem.

| Document                                                                                                                                                                                                      | Document Number                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| IDC Field Maintenance Print Set<br>R80 Disk Drive Field Maintenance Print Set<br>RL02 Disk Drive Field Maintenance Print Set<br>RL01/RL02 Disk Drive Technical Manual<br>R80 Disk Drive Technical Description | MP-01278<br>MP-01419<br>MP-01332<br>EK-RL012-TM<br>EK-00R80-TD |

| VAX-11/730 Central Processing Unit<br>Technical Description                                                                                                                                                   | EK-KA730-TD                                                    |

#### Table 1-1 Related Documentation

1K-7478

#### **1.3 POWER REQUIREMENTS**

The IDC requires approximately 55 watts of dc power. The dc power requirements are as follows:

#### **1.4 FUNCTIONAL DESCRIPTION**

The IDC controls the operation of the associated disk drives of the RB730 disk subsystem to store and retrieve data. IDC operation is initiated by the CPU. The CPU loads the IDC with the information required to initiate and perform each of the functions necessary in storing and retrieving data from a specific address location of the selected disk drive. Once a function is specified by the CPU, the IDC controls the operation of the disk drive to perform the function. After the function has been completed, the IDC, if enabled, generates and asserts an interrupt to the CPU. Table 1-2 lists the functions that can be specified by the CPU and describes the purpose of each one.

| Function Specified by CPU                          | Purpose                                                                                                                                               |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Seek                                               | Position the specified disk drive read/write head over the specified cylinder and enable it.                                                          |

| Get status                                         | Retrieve the status information from the specified disk drive and store it in the IDC data buffer.                                                    |

| Read header                                        | Read from the specified disk drive the header information from the first sector encountered and store it in the IDC data buffer.                      |

| Write data                                         | Write the data contained in the IDC data buffer at the specified read/write data address of the specified disk drive.                                 |

| Read data                                          | Read from the specified disk drive the data from the specified read/write data address and store the data in the IDC data buffer.                     |

| Read data without<br>header check                  | Read from the specified disk drive the data from the first sector en-<br>countered and store the data in the IDC data buffer.                         |

| Write check                                        | Read from the specified disk drive the data from the specified read/write data address and compare this data with data contained in the data buffers. |

| Write format<br>(Used only with R80<br>disk drive) | Write new header data to each of the 32 sectors of the applicable R80 cylinder.                                                                       |

| Maintenance                                        | Place the IDC in the maintenance mode so that the IDC logic may be exercised by microdiagnostic routines.                                             |

Table 1-2 CPU-Initiated IDC Functions

When the IDC is not performing a CPU-specified function, it operates in the idle mode. In this mode, the IDC selects and monitors the status of each associated disk drive. If an operational status change is detected, the IDC alerts the CPU.

The IDC contains the control and monitoring circuitry for:

- Selecting the CPU-specified disk drive, monitoring disk drive operational status, and enabling the appropriate IDC data paths for interfacing to the selected disk drive

- Asserting the CPU-specified disk drive commands to control selection and positioning of the disk drive read/write heads

- Synchronizing IDC operation with the selected disk drive or the CPU

- Locating the address (sector) to or from which data is to be stored or retrieved

- Performing single or successive block data transfers between the CPU and the disk drives

- Verifying the integrity of the data through the storage and retrieval cycle

- Generating a status word that can be used by the CPU to identify data error detection, the reason the IDC could not complete a CPU-specified function, or disk drive status changes

#### 1.4.1 Disk Drive Select and Drive Status Monitor

The IDC uses the disk drive select information specified by the CPU to select the desired disk drive. The IDC also monitors the operational status of the selected disk drive to make certain that the drive is operational and not busy before issuing further commands. The disk drive select information is also used within the IDC to select the proper data paths, specify the data buffer storage capacity, and gate the proper clocks for synchronization.

During the idle mode of operation, the IDC selects and monitors the operational status of the associated disk drives and records any detected operational status change. If a change is detected, the IDC alerts the CPU.

#### 1.4.2 Asserting Disk Drive Commands

The IDC controls assertion of the CPU-specified disk drive commands in the format that is compatible with the selected disk drive. The RL02 disk drive commands are converted to a serial format and asserted to the RL02 disk drives; the R80 disk drive commands are gated to the R80 disk drive in a parallel format.

#### **1.4.3** Synchronization of IDC Operation

Any one of six clocks may be selected by the IDC as the basic timing clock to ensure synchronous operation between the selected disk drive or CPU and the IDC.

#### **1.4.4 Address Location**

The IDC compares the read/write address specified by the CPU with the address information read from the selected disk drive to locate the address (sector) to or from which data is to be stored or re-trieved.

#### 1.4.5 Data Transfers

The IDC provides for single or successive block data transfers between the CPU and the disk drives. A block of data is defined as the data storage capacity of the disk for each addressable storage location (sector). Each sector of an RL02 disk drive provides the storage capacity for 256 bytes of data (one block). Each sector of the R80 disk drive provides the storage capacity for 512 bytes of data (one block).

The IDC provides buffering for all data to be written to or read from the disk. The IDC contains two data buffers: each data buffer provides storage for up to 512 bytes of data. Control of each of the data buffers is shared by the IDC and the CPU.

The CPU controls the data buffers to load the IDC with data to be written to the disk drives. The CPU also controls the data buffers to transfer the data contained in the data buffers from the IDC to the CPU.

The IDC controls the data buffers to store the data read from the disk drives until it is transferred to the CPU under CPU control. This dual IDC data buffer arrangement provides the capability for reading or writing successive sectors of data. While the IDC is reading or writing one sector of data using one of the IDC data buffers, the CPU can be using the other data buffer to transfer the data read from the previous sector or to load the data to be written in the next sector.

#### 1.4.6 Verifying Data Integrity

The IDC verifies the integrity of the data throughout the storage and retrieval cycle. When data are being written to the disk, the IDC generates a coded word based on the configuration of data written to the disk. This coded word is also written on the disk during the write data cycle. When data are being read from the disk, the IDC generates a coded word based on the configuration of data read from the disk. After the data have been read, the coded word stored on the disk is compared with the coded word generated from the configuration of the data read from the disk. If the coded words are identical, data integrity has been maintained throughout the storage and retrieval cycle (the data read are identical to the data written).

#### 1.4.7 Status Word Generation

During the performance of each CPU-specified function, the IDC tests the results of conditions and operations required to execute the function. The results of these tests are recorded and formatted to produce an IDC status word. During the idle mode, the IDC records any detected drive status change. Any recorded drive status change is provided as part of the IDC status word. The IDC status word can be read by the CPU.

# CHAPTER 2 INTERFACES

#### 2.1 IDC INTERFACES

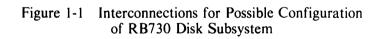

The electrical connections between the IDC and the VAX-11/730 CPU (port bus and UNIBUS interfaces), the IDC and the R80 disk drive (R80 interface), and the IDC and the RL02 disk drive (RL02 interface) are shown in Figure 2-1.

All connections for the port bus and UNIBUS interfaces are provided via the VAX-11/730 backplane. The R80 interface is provided via two ribbon cables. A 60-wire ribbon cable connects J3 of the IDC with J201 of the R80 disk drive. A 26-wire ribbon cable connects J2 of the IDC with J202 of the R80 disk drive. The RL02 interface is provided via a 40-wire ribbon cable that connects J1 of the IDC with J12 of the RL02 disk drive.

All of the signal lines (except ACLO) at the R80 and RL02 interfaces are dual signal lines (indicated in Figure 2-1 by the dual listing of pin numbers at the interface connectors). The first pin number listed refers to the low level signal line; the second number refers to the high level signal line. These signal lines are driven or detected by differential line drivers or receivers.

The port bus interface BUS Y D31:D00 signal lines form a common bidirectional bus that interconnects the IDC and floating-point accelerator (FPA) with the Y-bus of the CPU data path module. These signal lines are driven/detected by octal transceivers on the IDC and the FPA. The rest of the signal lines at the port bus and UNIBUS interfaces are dedicated signal lines.

All of the input/output signals at the IDC/port bus, UNIBUS, R80, and RL02 interfaces are also shown in Figure 2-1. The following paragraphs discuss the characteristics and significance of the input/output signals at each of the interfaces.

#### 2.2 IDC/PORT BUS AND UNIBUS INTERFACES

The input/output signals at the IDC/port bus and UNIBUS interfaces include BUS Y D31:D00, CSR17 and CSR14:10, PORT INSTR, READ PORT, SEL ACC IN, CPU P2, PORT CLOCK, PORT XFER REQ, XFER GRANT, BR5, ACLO, and DCLO.

The BUS Y D31:D00 signal lines are used to transfer control words, address information, and data from the CPU to the IDC, and to transfer IDC and disk drive status information, current address information, error detection information, and data from the IDC to the CPU. The CPU initiates and controls the transfer of all control words, information, and data between the IDC and the CPU via port microinstruction inputs to the IDC. The port microinstruction inputs are asserted via the CSR17 and CSR14:CSR10 signal lines.

The port microinstruction inputs to the IDC, together with the PORT INSTR input, are used to preset the IDC and to cause the transfer of control words, address information, and data from the CPU to the IDC. The port microinstruction inputs to the IDC together with the PORT INSTR, READ PORT, and SEL ACC IN inputs are used to cause the transfer of the IDC and disk drive status information, current address information, error detection information, and data from the IDC to the CPU. (The state of the SEL ACC IN input identifies the READ PORT signal as being applicable to the FPA or the IDC: a low SEL ACC IN signal indicates READ PORT is IDC specific.)

|               |                         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                            | <i></i>           |                        |          |            |                        |           |

|---------------|-------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------|-------------------|------------------------|----------|------------|------------------------|-----------|

|               | VAX-11/730              |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                            | T .               |                        | <b>-</b> |            | _                      |           |

| (             | BACKPLANE               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1,2            |                            | $\mathbf{H}$      | 1.2 E                  | 8L       | ۵ <u>۱</u> |                        |           |

|               | BUS Y DOO CP2           | INTEGRATED      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3,4            | R80 TAG 2                  |                   | 1,2 <b>€</b><br>3,4 €  |          | R80        |                        |           |

|               | BUS Y DO1 CM1           | DISK CONTROLLER |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5,6            | R80 TAG 3                  | $\square$         | 5,6                    |          | DISK       |                        |           |

|               | BUS Y DO2 CK2           | (M8388)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7,8            | R80 TAG BUS 0              |                   | 7,8                    |          | DRIVE      | 1.                     |           |

|               | BUS Y D03               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9,10           | KR80 TAG BUS 1             | $\square$         | 9,10 2                 |          |            |                        |           |

|               | BUS Y D04 CE1           |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11,12          | R80 TAG BUS 2              | ∔                 | 11,12 €                | _        |            |                        |           |

|               | BUS Y D05 CD2           |                 | $ \longrightarrow $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13,14          | R80 TAG BUS 3              | $\mathbf{H}$      | 13,14                  |          |            |                        |           |

|               | BUS Y D06<br>BUS Y D07  |                 | <b>├</b> →→                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15,16          | R80 TAG BUS 4              | ⊷                 | 15,16 🔾                | -        |            |                        |           |

|               | BUC V DOB               |                 | $ \rightarrow $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17,18          | R80 TAG BUS 6              | ╉                 | 17,18                  |          |            |                        |           |

|               |                         |                 | $ \rightarrow $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19,20          | R80 TAG BUS 7              | H                 | 19,20 🗲                | -        |            |                        |           |

|               | BUC V DIO               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21,22          | R80 TAG BUS 8              | +-,               | 21,22                  |          |            |                        |           |

|               | BUS Y DI1<br>CL1<br>CK1 |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23,24          | R80 TAG BUS 9              | $\mathbf{T}$      | 23,24                  |          |            | 1 1                    |           |

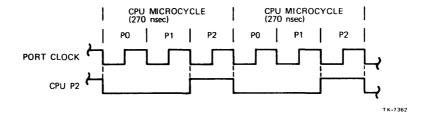

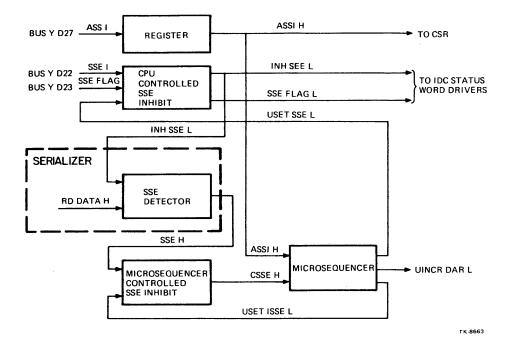

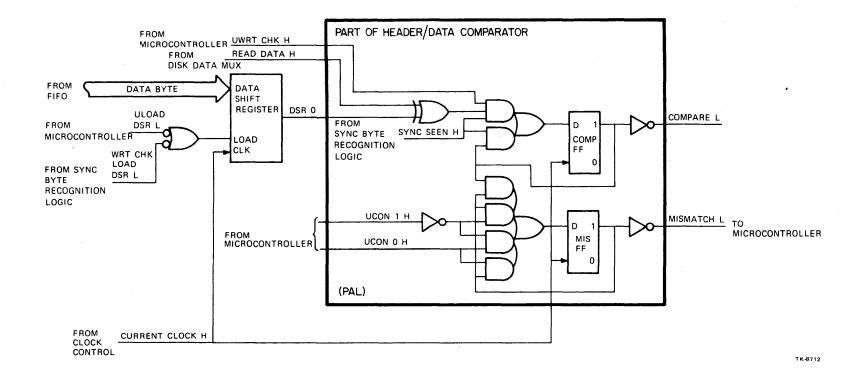

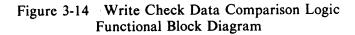

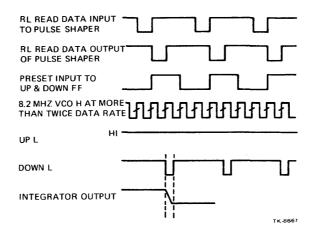

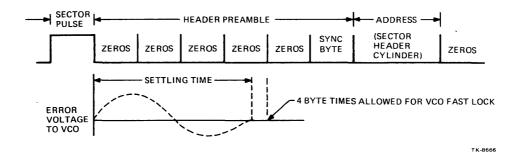

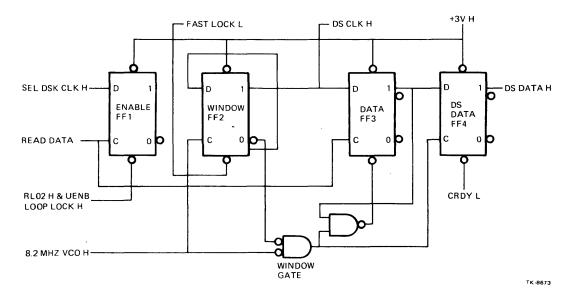

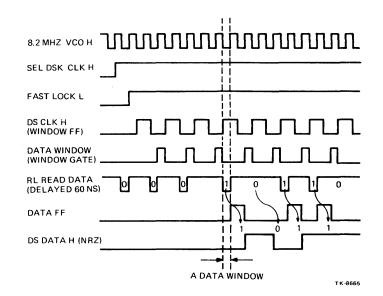

|               | BUS Y D12 CE1           |                 | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25,26<br>53,54 | R80 SECTOR COUNT 1         | $\mathbf{D}$      | 25,26                  |          |            |                        |           |