## VAX-11/750 LEVEL II

For Internal Use Only

.

Student Workbook

### Copyright © 1980, Digital Equipment Corporation. All Rights Reserved.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Bedford, Massachusetts 01730.

# Printed in U.S.A.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may not be used or copied except in accordance with the terms of such license.

Digital Equipment Corporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by Digital.

The following are trademarks of Digital Equipment Corporation. Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS     |

|---------|--------------|-------------|

| DEC     | DECSYSTEM-20 | OMNIBUS     |

| PDP     | DIBOL        | <b>OS/8</b> |

| DECUS   | EDUSYSTEM    | RSTS        |

| UNIBUS  | VAX          | RSX         |

|         | VMS          | IAS         |

## SYSTEM INTRODUCTION

#### INTRODUCTION

The 11/750 system is an extension of the VAX Family System with many of the same characteristics of the VAX 11/780.

The 11/750 system allows users up to 4.3 billion virtual address while only using 2 MEG of physical memory. To do this the 11/750 has mass storage devices on a Mass bus or Unibus for quick and easy access by the CPU.

The 11/750 may run in two modes of operation:

- 1. NATIVE (VAX VMS)

- 2. COMPATABILITY (PDP-11)

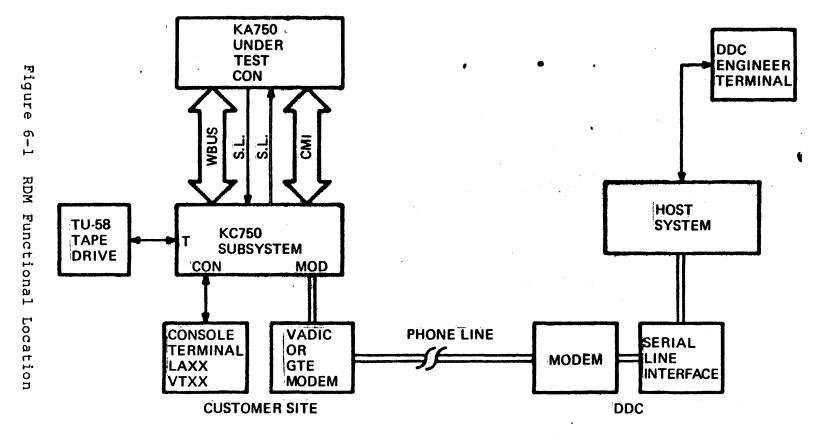

There is also the capability of Remote diagnostics to help both the user and the field service technician. With this Introduction Module we will attempt to give you the basic facts and concepts of the 11/750 System including:

1. Basic Architecture

2. Analysis of Block Diagram

3. Physical Characteristics

4. Diagnostic Overview

#### 11/750 SUPPORT COURSE

### MODULE I: SYSTEM INTRODUCTION

#### SYNOPSIS

The system introduction module consists of 11/750 system characteristics and block diagram analysis.

### OBJECTIVES

Provided with a blank 11/750 system block diagram and a list of 11/750 component names, correctly label the 11/750 system block diagram.

Given a list of 11/750 characteristics, correctly indicate as True/False the characteristics that make 11/750 a unique system.

### SAMPLE TEST ITEM

Identify the following 11/750 unique characteristics as True or False.

- 1. The 11/750 Processor Microword is 99 bits.

- 2. The 11/750 has a Virtual Memory System.

- 3. The 11/750 data path is 16 bits.

- There is no Remote Diagnosis capability with the 11/750 system.

#### RESOURCES

11/75Ø Specification New Product Data Sheet 11/75Ø Block Diagram 11/75Ø 11/75Ø Pocket Reference Guide

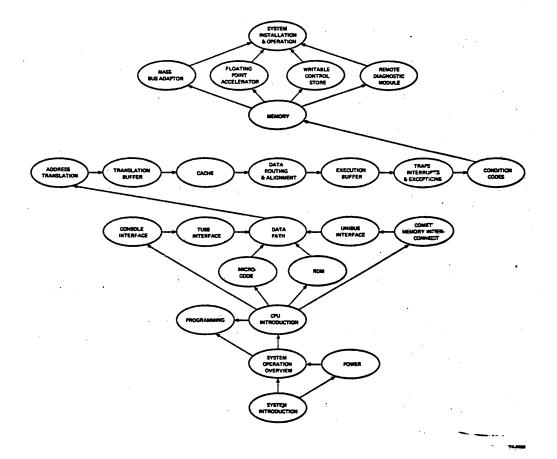

## MODULE OUTLINE

- I. SYSTEM INTRODUCTION

- A. Course Overview

- B. Basic Architecture

- 1. 11/750 Specifications

- 2. 11/750 Physical Characteristics

- C. Block Diagram Analysis

- 1. CPU

- a. Data Path Module

- b. Memory Interconnect Module

- c. 11/750 Control Store

- d. Unibus Interface

- e. Major Buses

- 2. Memory

- a. Controller (1)

- b. Array Boards (up to 8)

- 3. Options

- a. CPU Options

- 1. Writable Control Store

- 2. Floating-Point Accelerator

- b. Mass Bus Options

- c. Unibus Options

- d. Remote Diagnostic Module

1-3

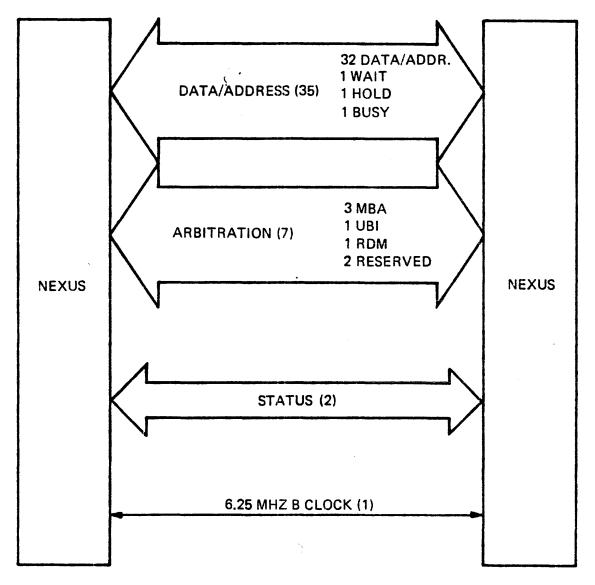

- D. 11/750 Physical Inspection

- 1. Front Panel

- 2. Card Locations

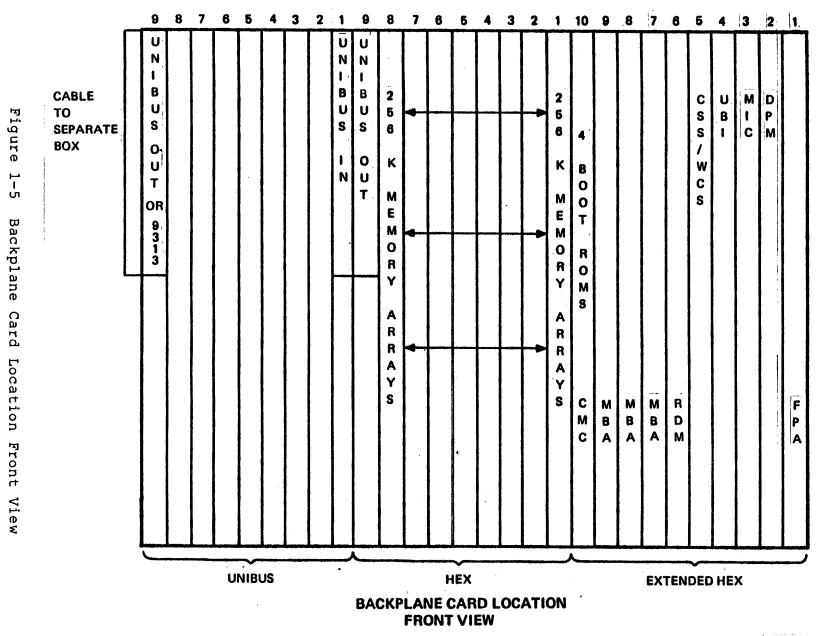

- 3. Backplanes

- 4. Power

.

E. Diagnostic Overview

Basic Architecture

- 1. Comet Specifications

- a. Micro-controlled machine

- b. Similar 32-bit architecture except:

- (1) Use of LSI curcuits (gate arrays)

- (2) Increases reliability

- (3) Decreases size

- c. Virtual 32-bit addressing (hexidecimal)

- (1) 4.3 billion virtual processes

- (2) 2 meg max physical (moss batt. backup 10 min.)

- Two modes of operatiton d.

- (1) Native (VAX VMS)

- (2) Compatibility (PDP-11)

- Remote Diagnostic Capability e.

- (1) Company owner module

- (a) Increase level of service

- (b) Improves field service efficiency

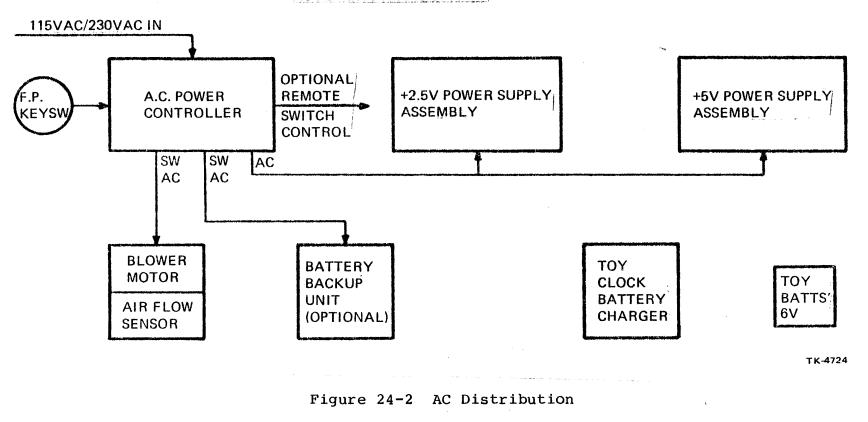

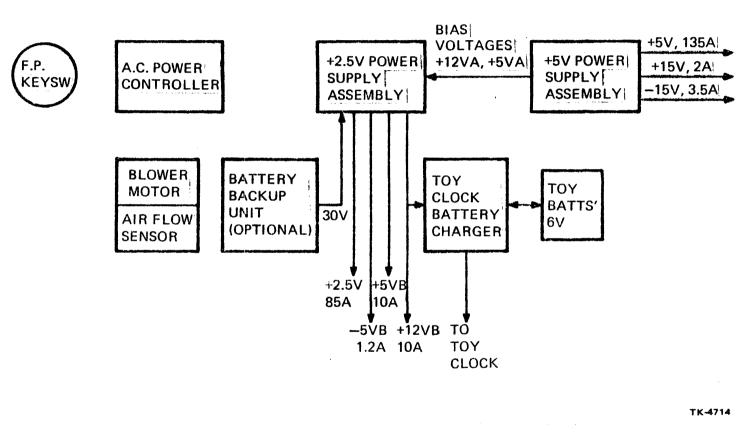

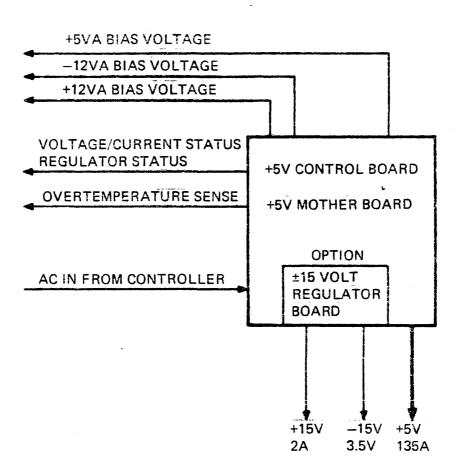

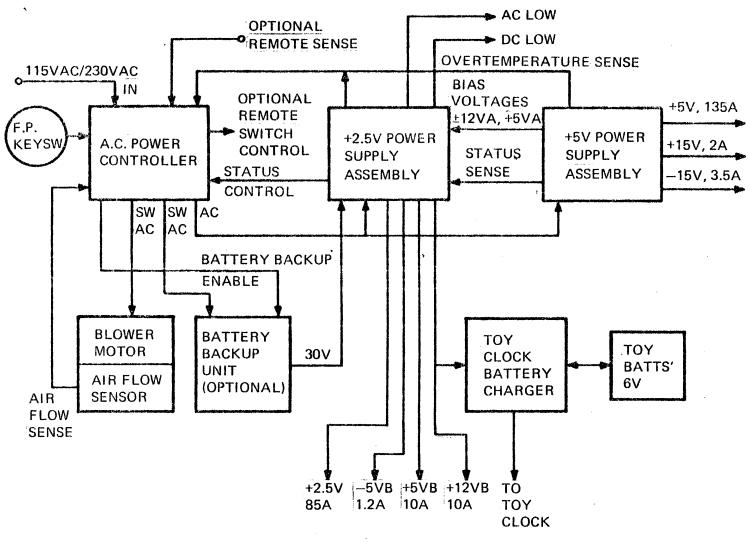

- f. Power

- (1) 115 or 230 volts

- Physical Characteristics 2.

- a. 40 inches high, 30 inches deep, 29 inches wide

- Five basic sections b.

- (1) CPU 4 boards 3 major buses

- (2) Options CPU and I/O

- (3) Front Panel(4) Backplanes Comet and Unibus

- (5) Power

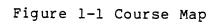

#### What Is an 11/750 Gate Array?

400 identical two transistor cells which can:

- 1. Be connected to form 4 input NAND

- 2. Together with a neighboring cell be connected to form 4 input NAND or AND.

44 identical transceiver cells which can:

- By disconnecting the receiver, be a TTL, Tri-state or open collector drives (Internal array to outside world)

- 2. By disconnecting the driver, be a TTL receiver (high impedance)

- 3. Both

Implementation Technique - Gate Arrays Circuit Technology - Low Power Dipolar Schottky Circuit Density - Large Scale Integration (LSI)

Die Size - .215 inches X .244 inches Power Utilized per Die - 2 watts max

Package Size - 1.44 sq. in. (2.4 inches X Ø.6 inches) Number of Pins/Package - 48

I/O Circuits/die - 44 I/O transceiver gates

Logic Gates - 400 identical 4 input NAND gates

Voltage Used - +2.5 volts, +5 volts Speed per Gate - 5-10 nanoseconds

Unique Gate Array Types

CPU and Memory Controller - 27 Floating-Point Accelerator - 7 Mass Bus Adaptor - 5

Total Number of Gate Arrays Used:

CPU and Memory Controller - 55 Floating-Point Accelerator - 28 Mass Bus Adaptor - 12

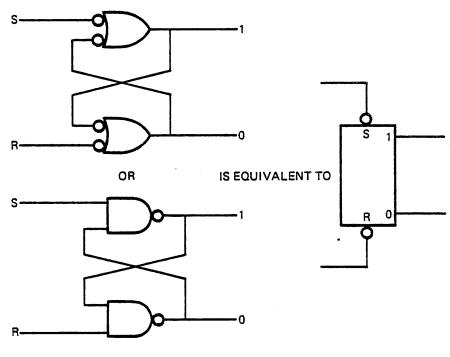

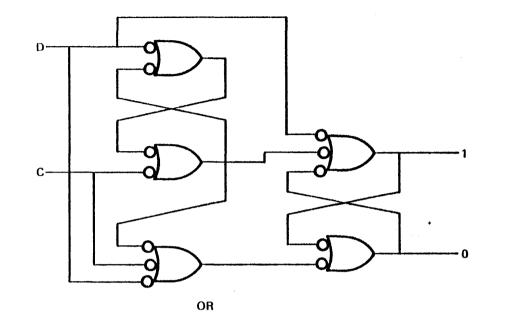

LOGIC CIRCUIT EQUIVALENCES

System Introduction

1-8

TK-2098

1-9

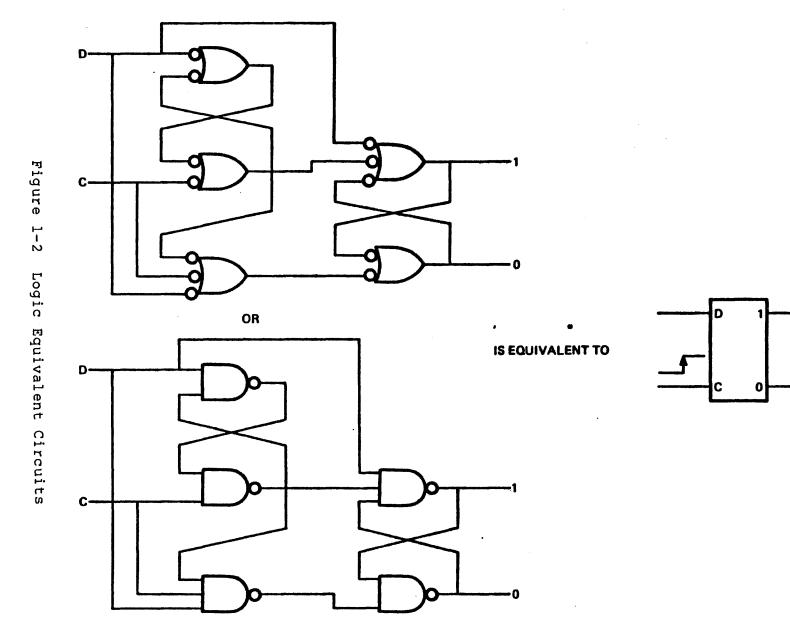

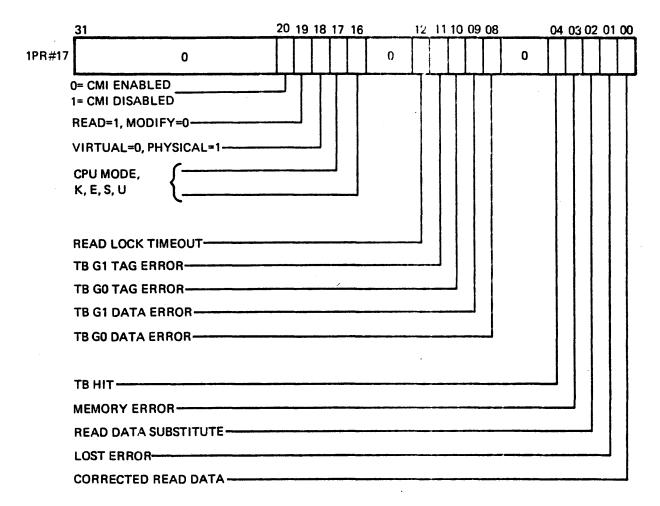

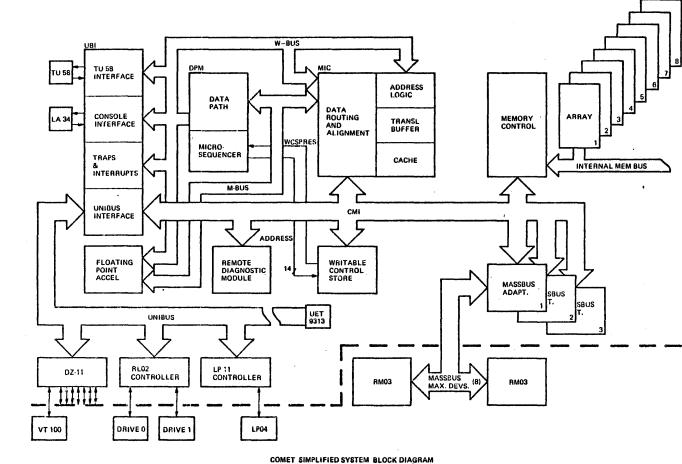

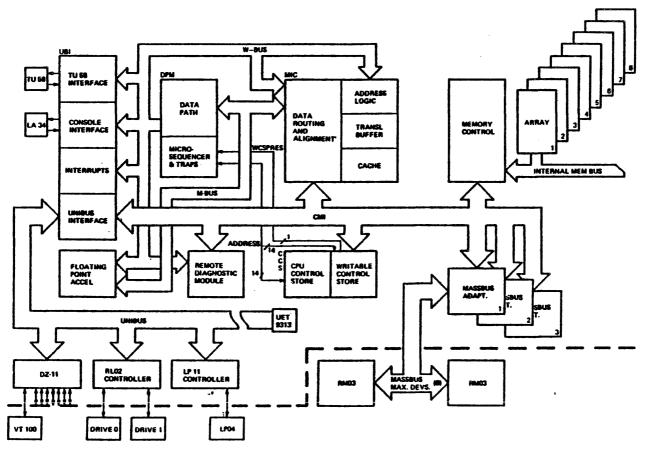

COMET SIMPLIFIED SYSTEM BLOCK DIAGRAM

TK 2079

Introduction

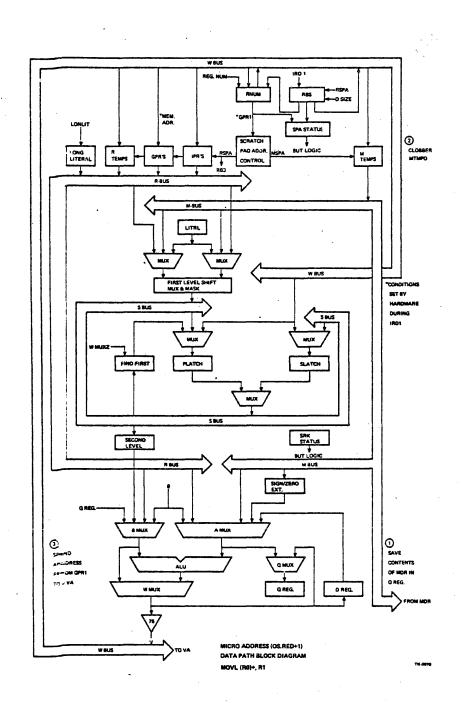

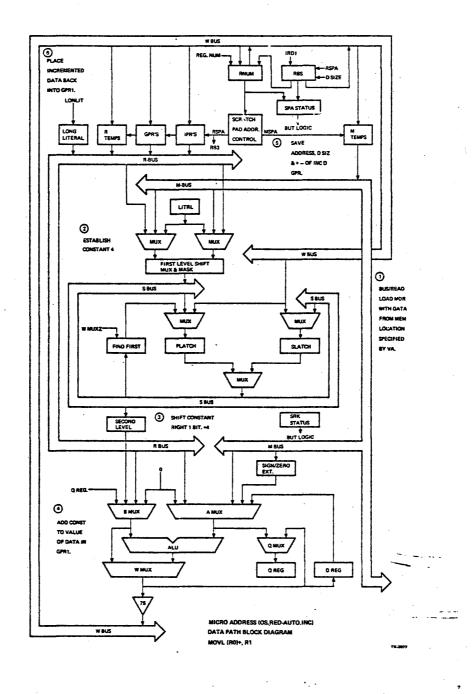

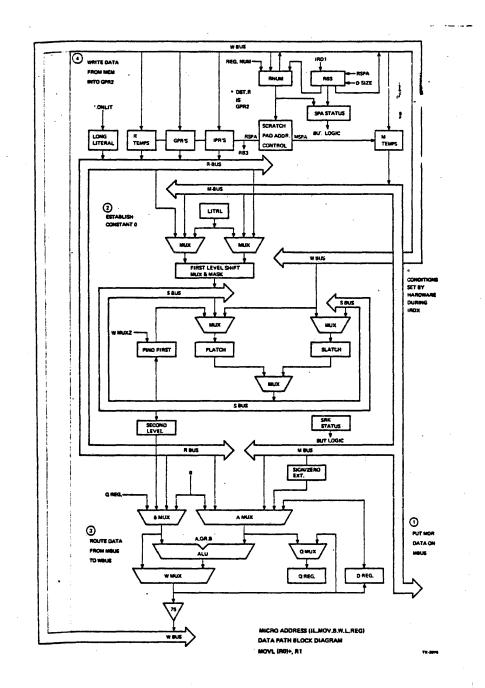

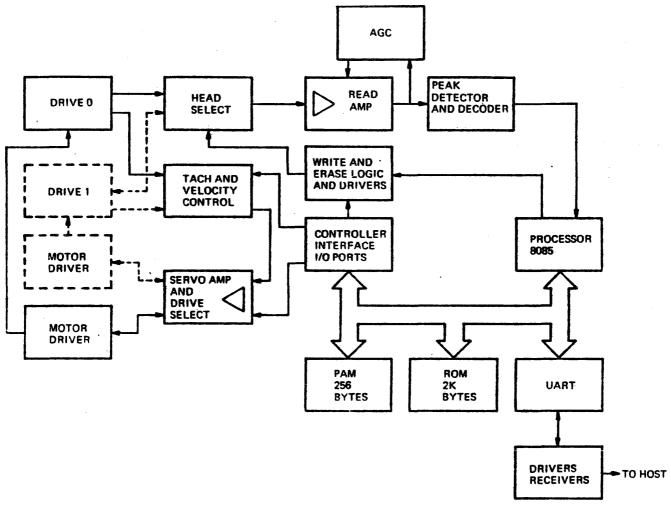

Block Diagram Analysis

- 1. CPU Four Boards

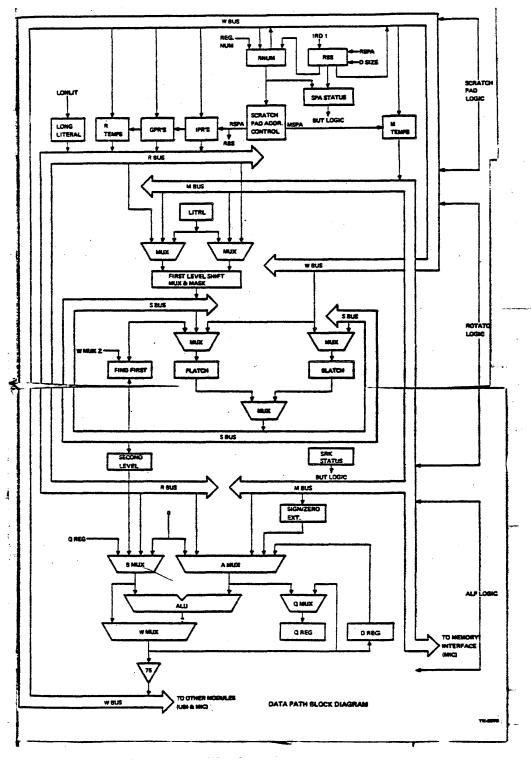

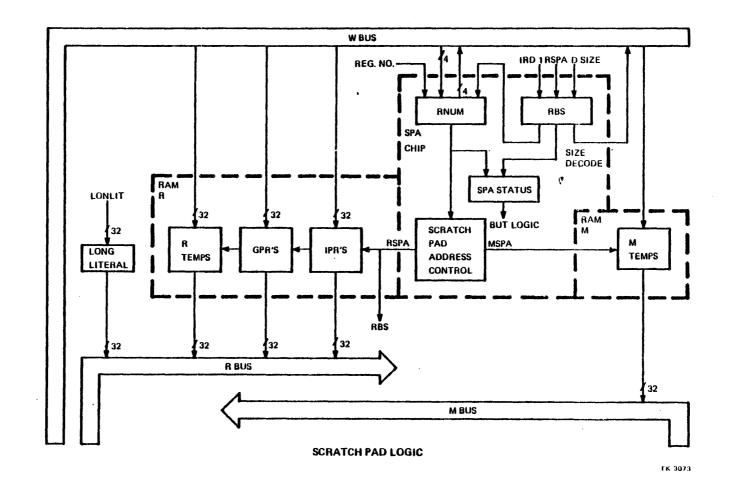

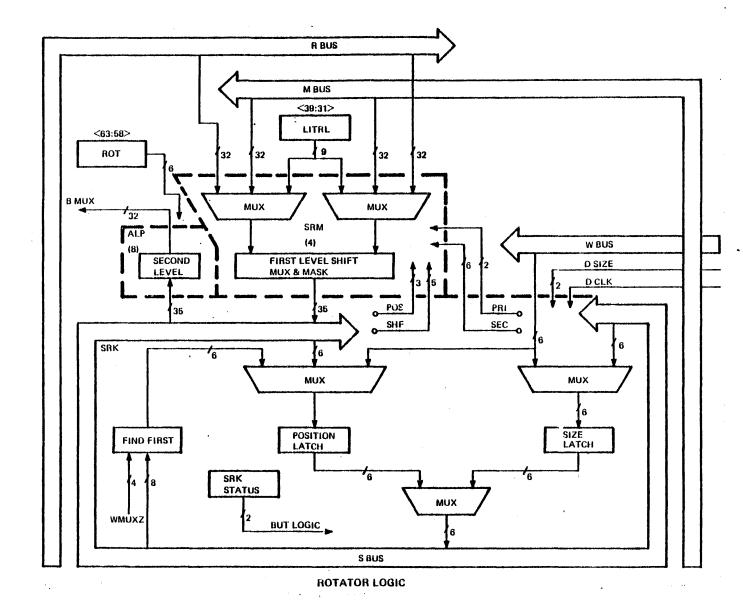

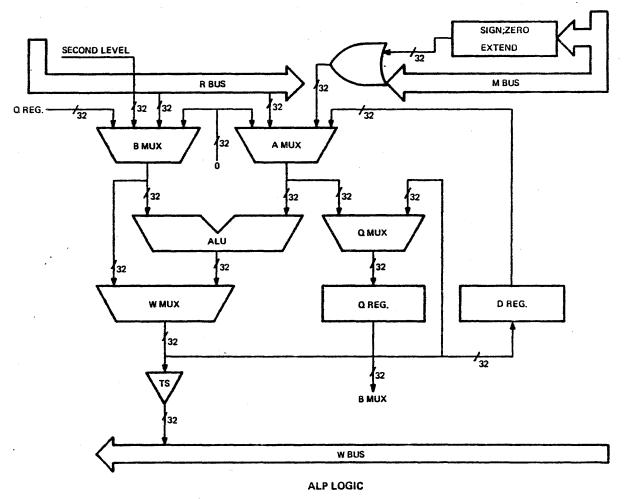

- a. Data path module (slot 2) DPM

- (1) Functions

- (a) Control Microsequencing

- (b) Arithmetic actions

- (c) Generate basic CLK from OSC on CCS

- (2) Contents

- (a) Super Rotator

- (b) ALU

- (c) 64 GPRs

- (d) Interval timer and basic CLK

- (e) Microsequencer

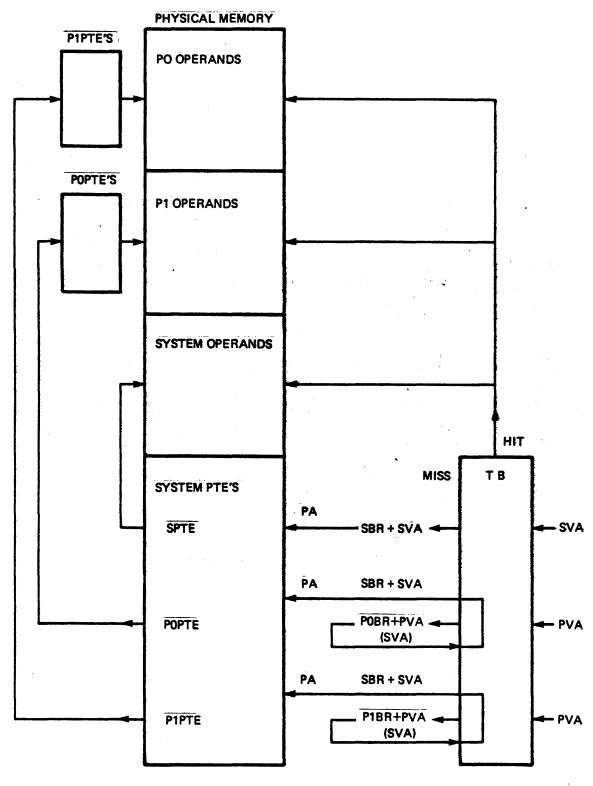

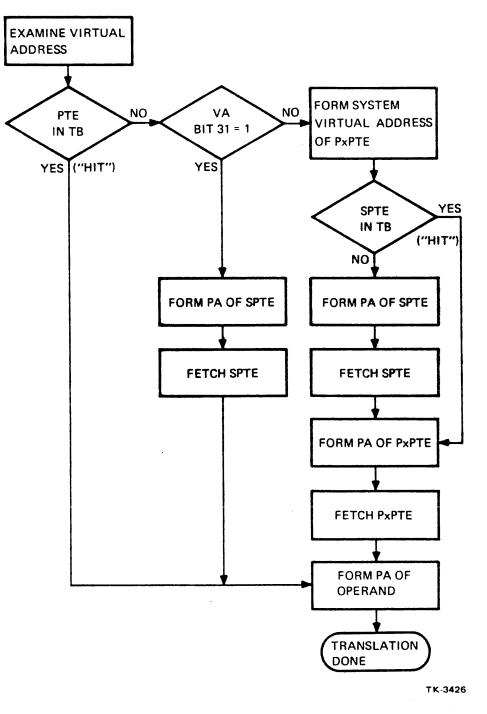

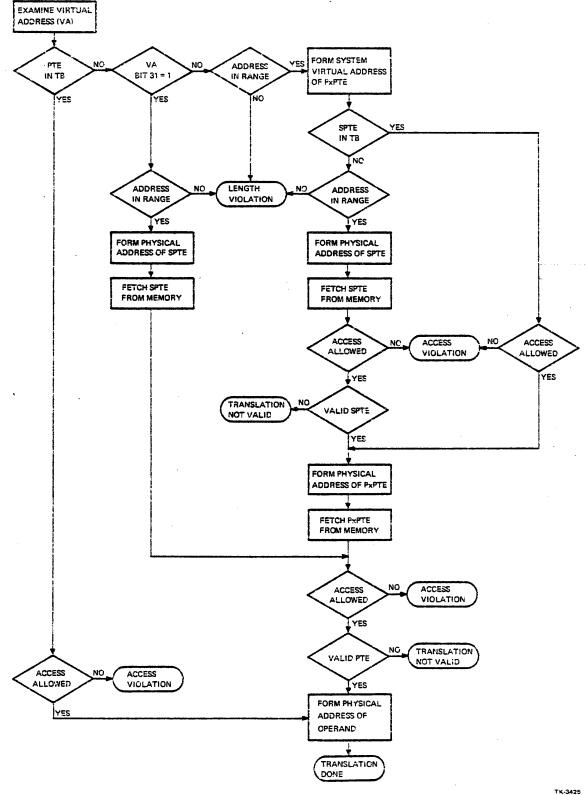

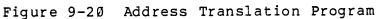

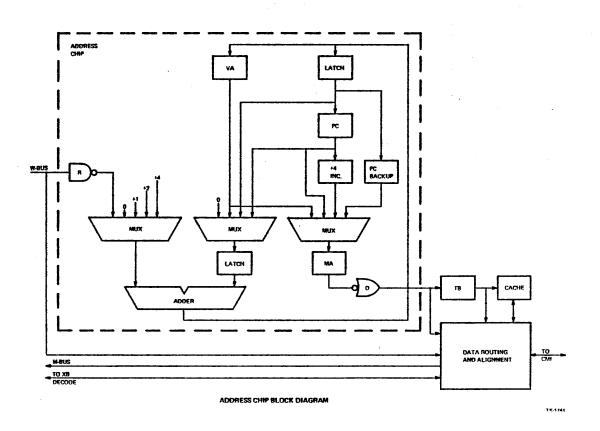

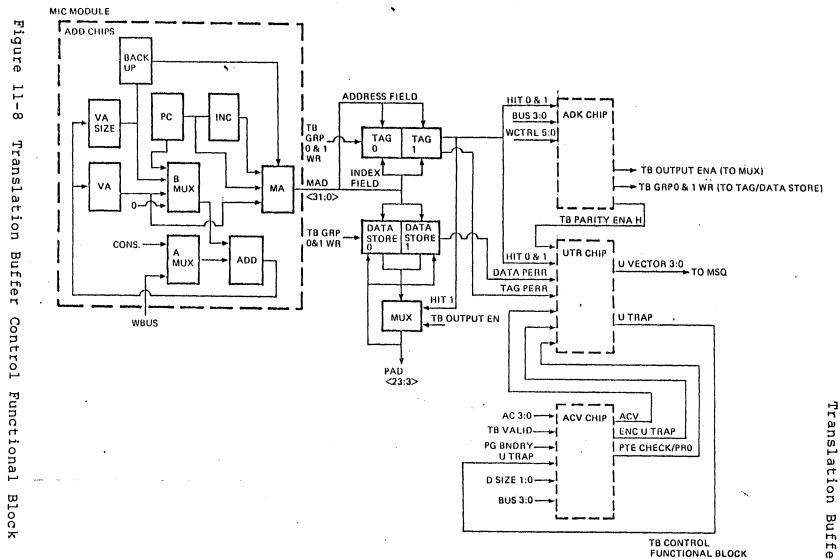

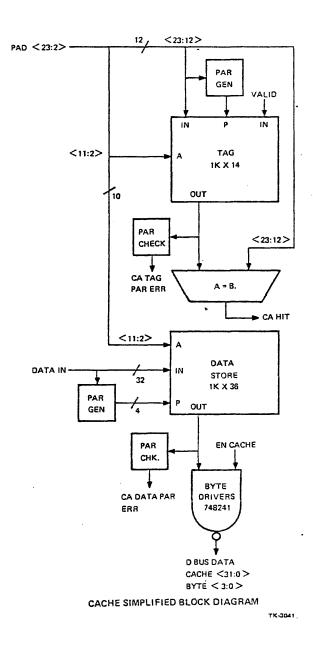

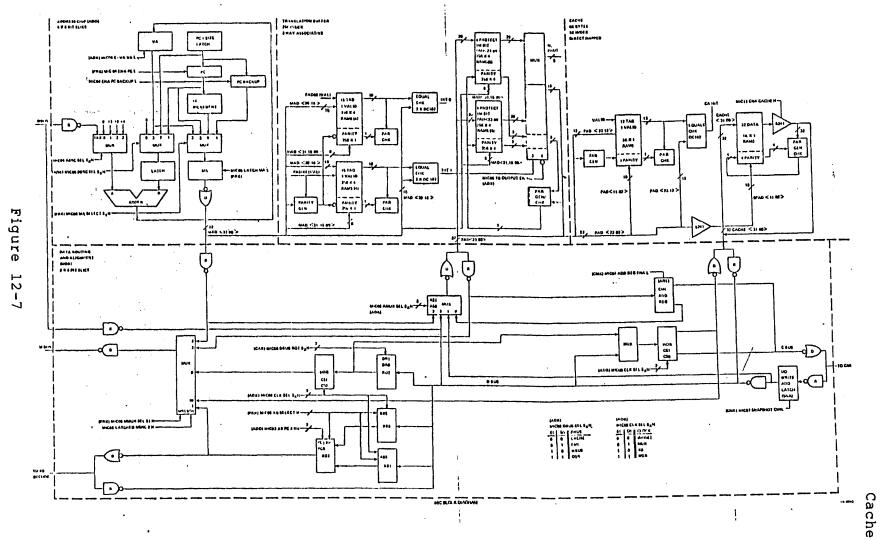

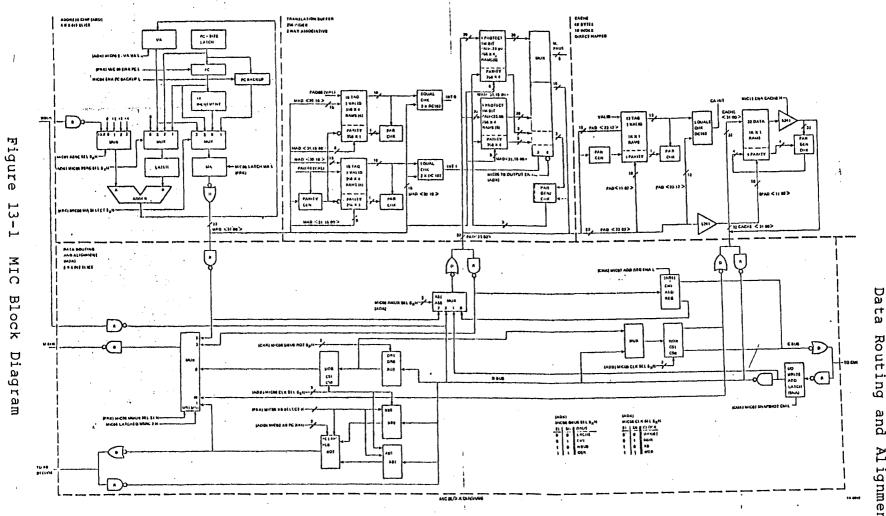

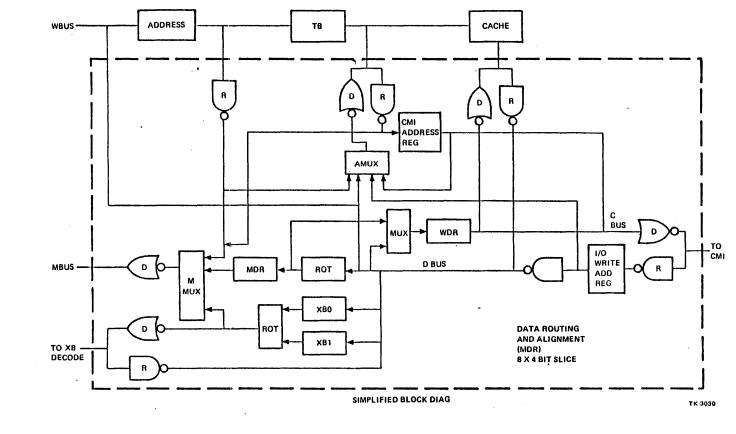

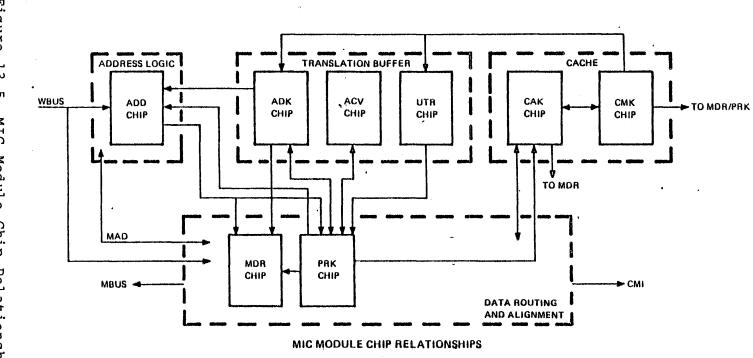

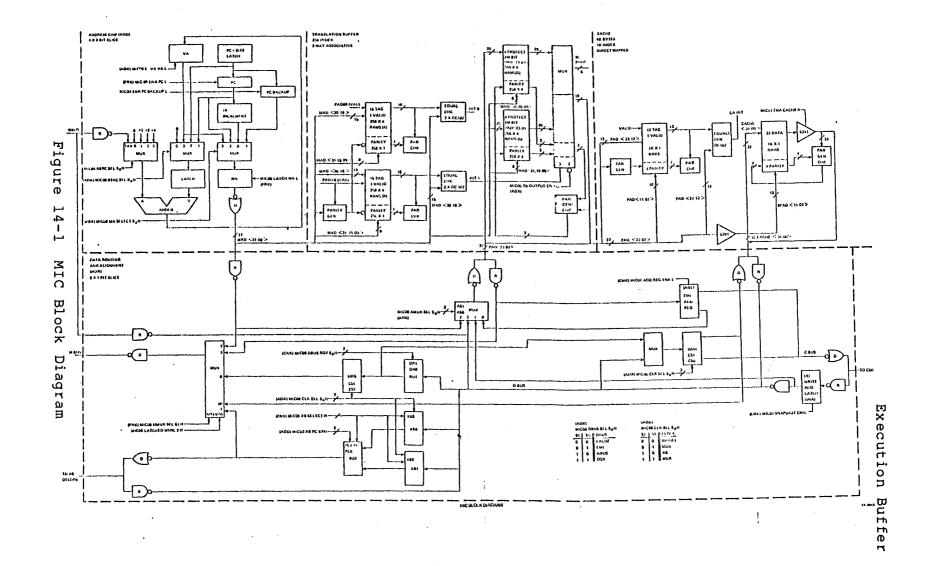

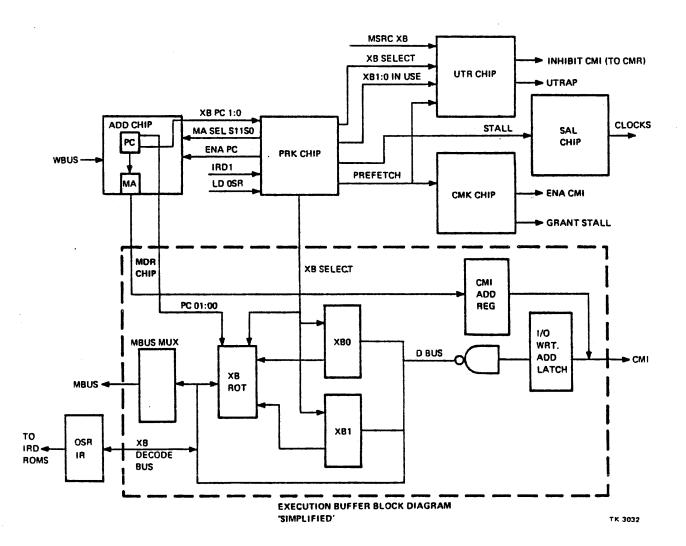

- b. Memory Interconnect Module (Slot 3) MIC

- (1) Functions

- (a) Acts as memory management by making physical address from virtual address

- (b) Checks for that physical address to find if it is located in memory

- (c) Stores data in a LK cache for quick use by the CPU

- (d) Holds "PC" (program counter) to allow CPU greater efficiency. (Updates the PC without CPU microintervention.)

- (e) Due to VAX data and instruction storage it aligns data or instructions to useable positions for DPM.

- (f) Generates microtraps for needed interrupts and exceptions

- (2) Contents

- (a) Address Logic

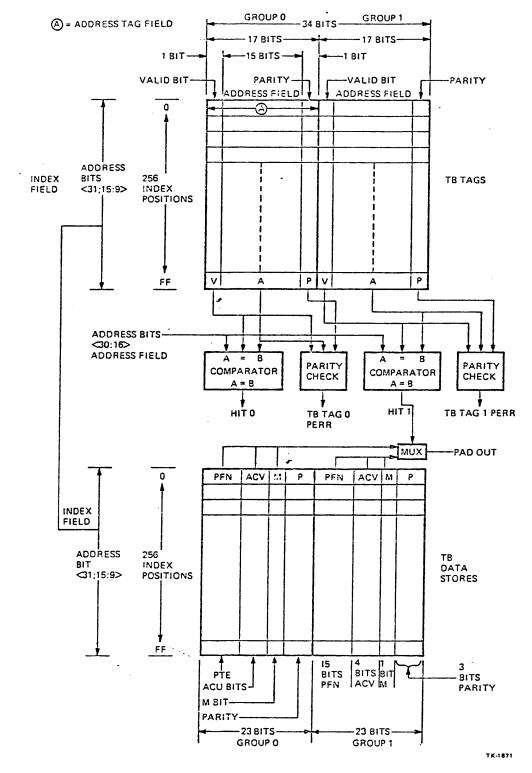

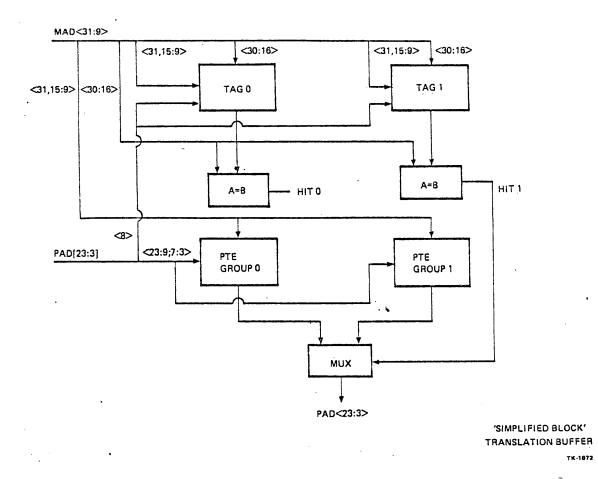

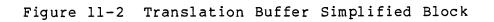

- (b) Translation Buffer 2-way set associative cache

1-10

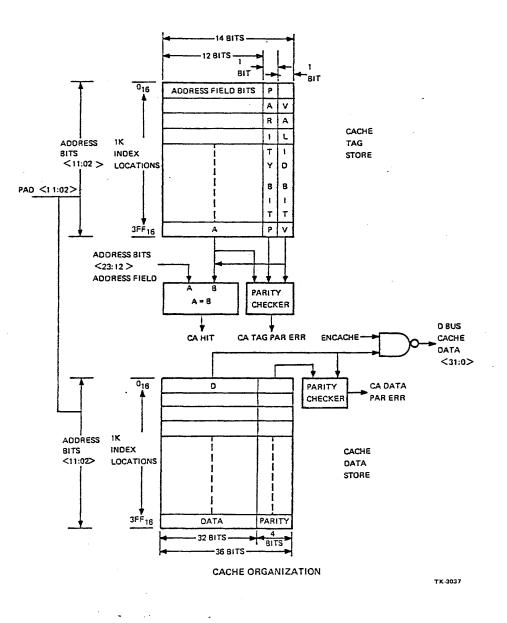

- (c) Cache 1K direct for data

- (d) Data routing and alignment holds PC and execution buffer.

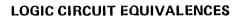

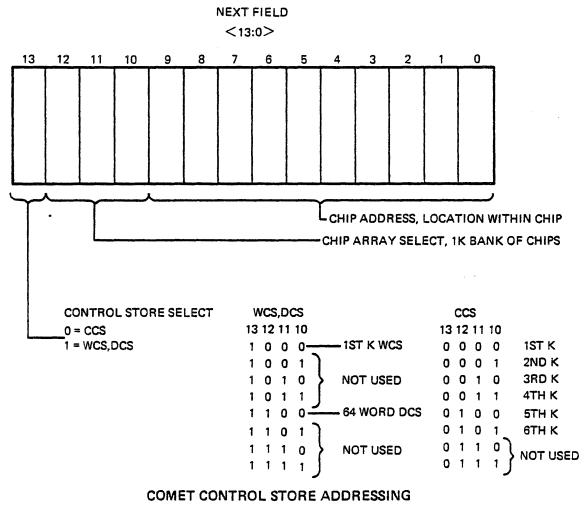

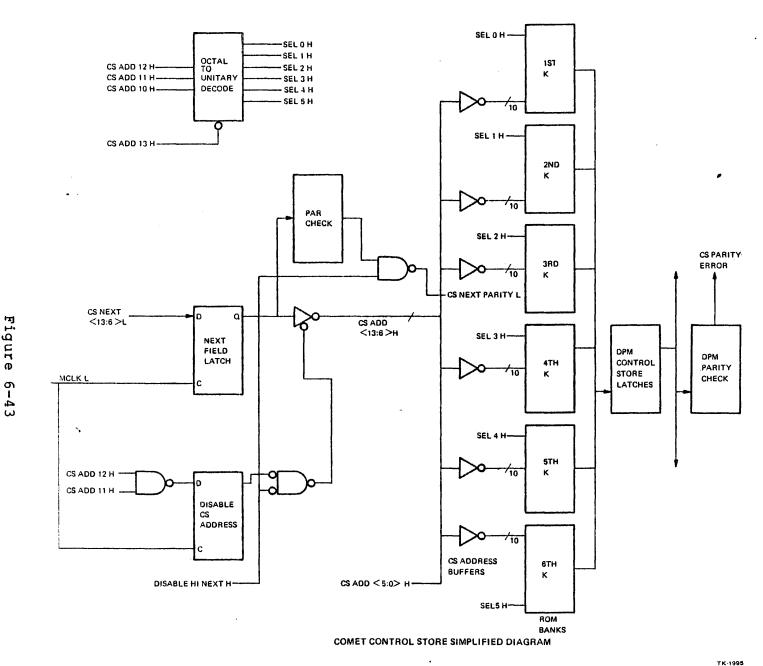

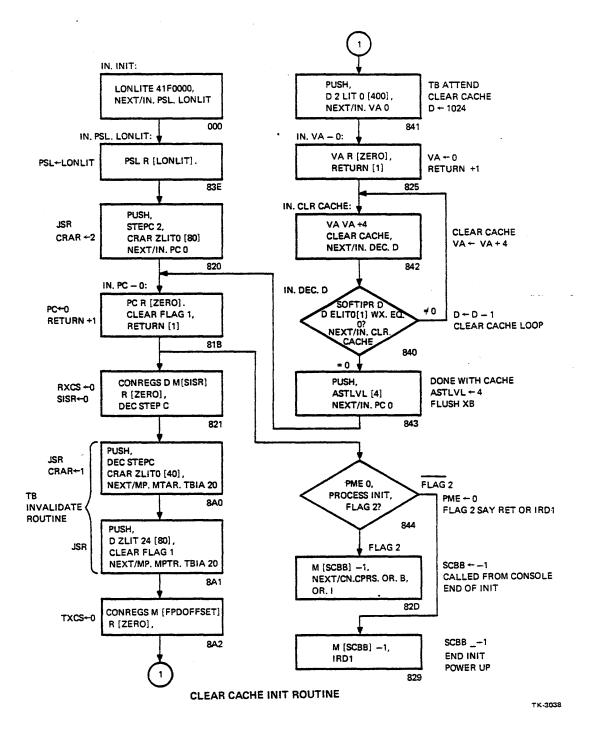

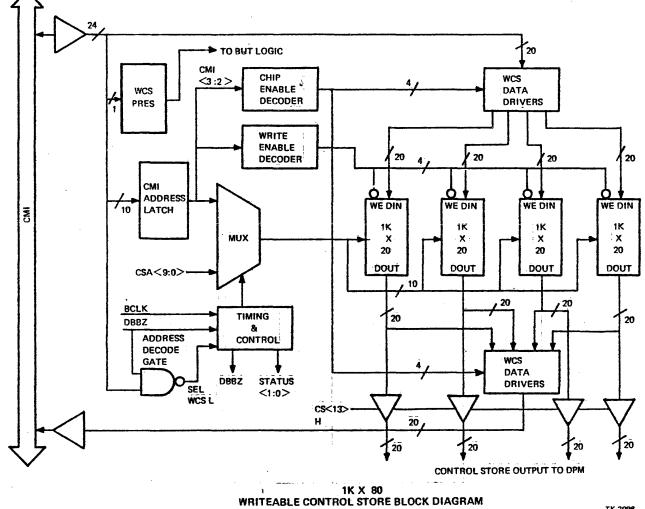

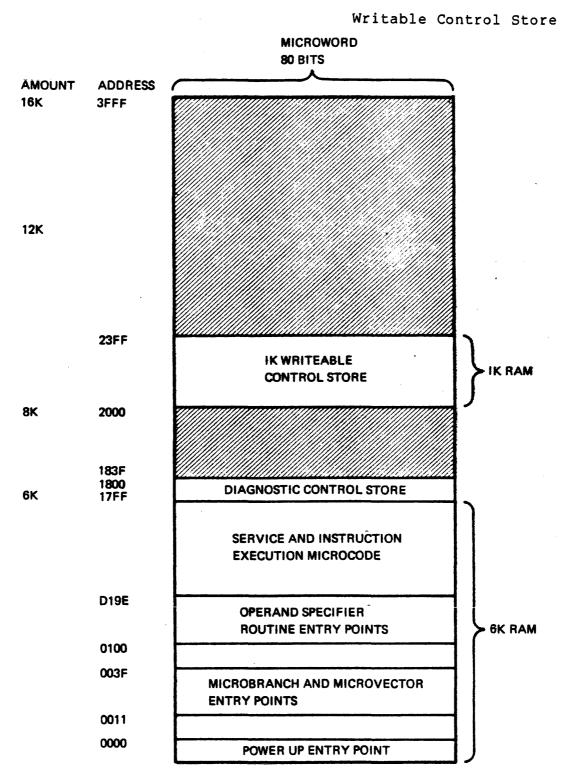

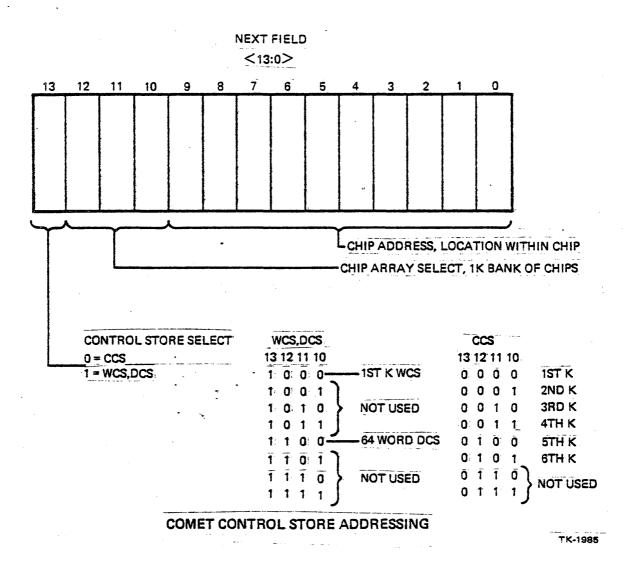

- c. CPU Control Store (Slot 5) CSS

- (1) Functions

- (a) Hold proms (microprogram)

- (b) Mother board for WCS option

- (c) Works in conjunction with microsequencer

- (2) Contents

- (a) Proms for <u>80 bit</u> microword (1K)

- (b) Snap on for WCS

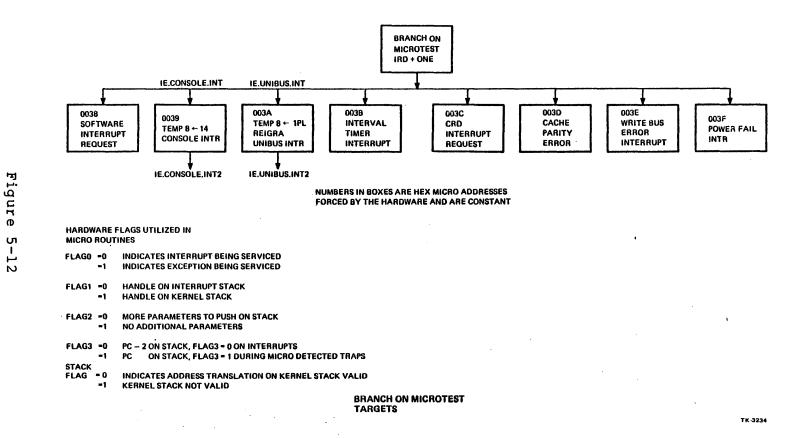

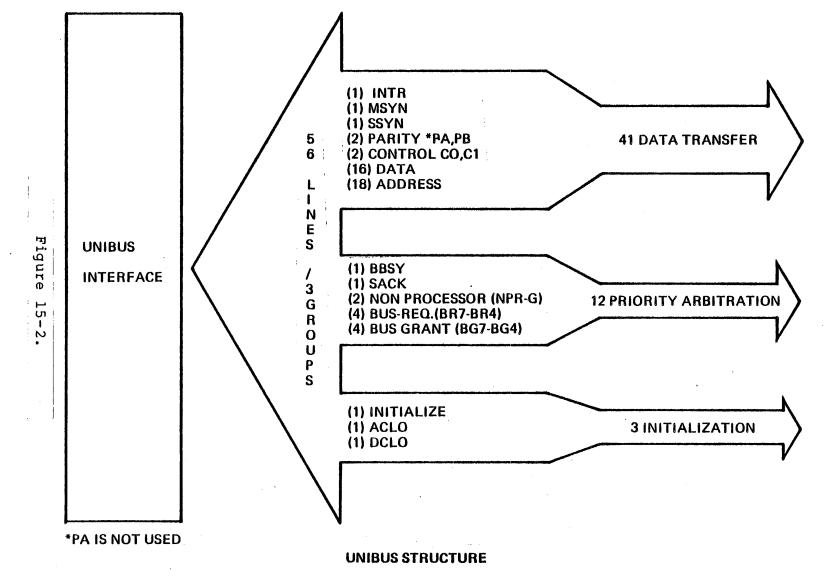

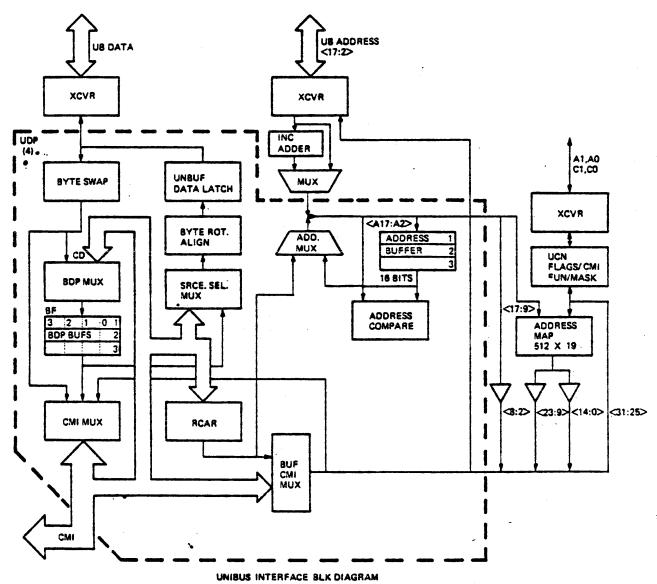

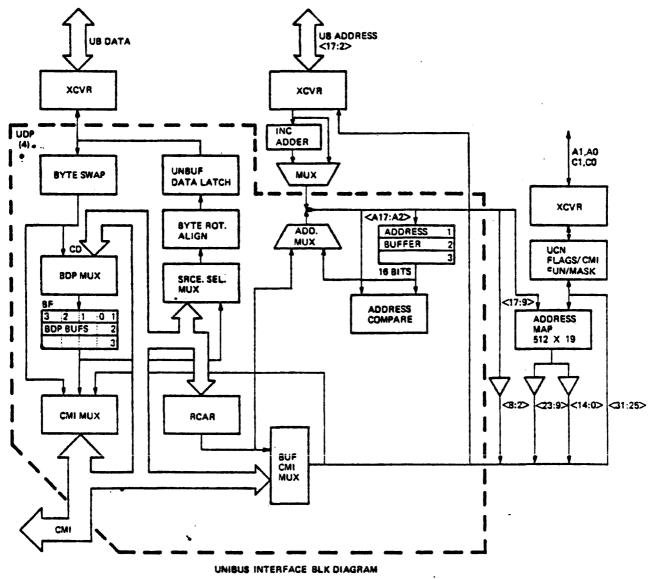

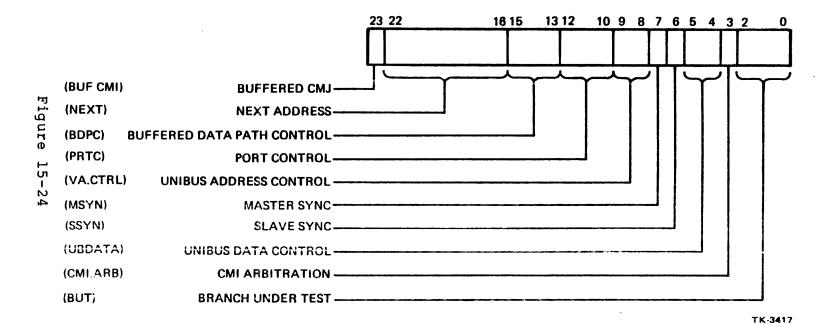

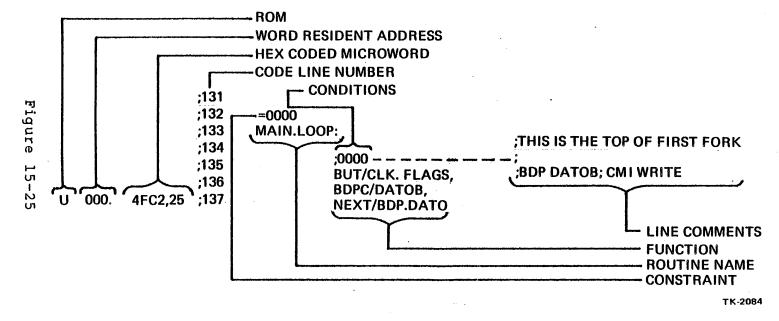

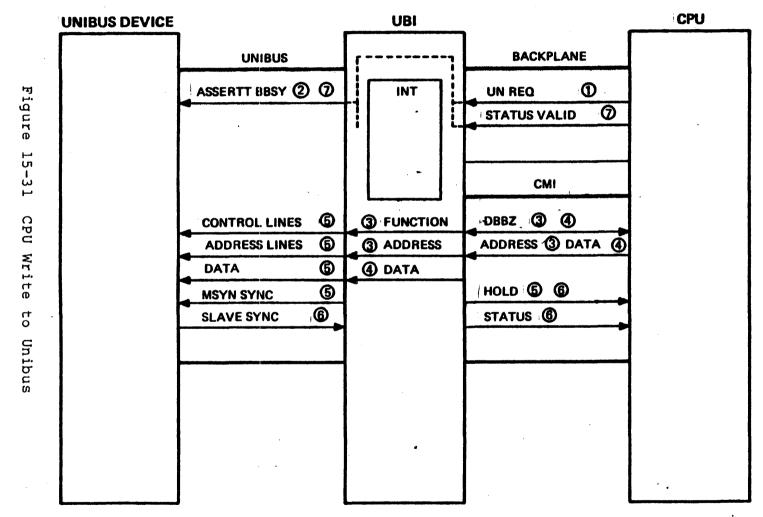

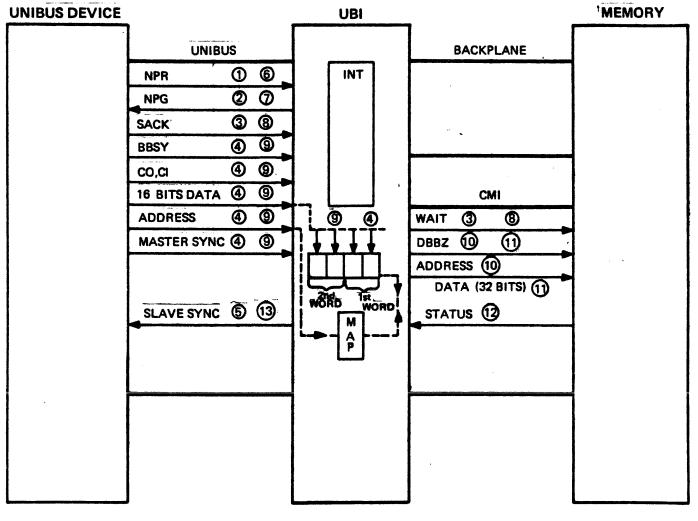

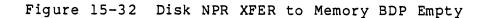

- d. CPU Unibus Interface Module (Slot 4) UGI

- (1) Functions

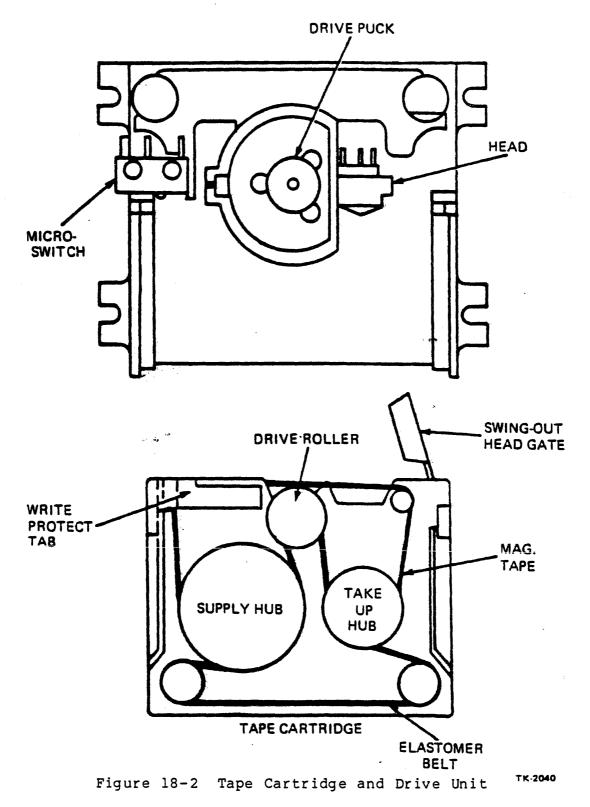

- (a) Interface the TU58 cartridge tape to operating system. TU58 used possibly for booting the system or loading of diagnostics. One chip, serial data between TU58 and interface. Parallel between interface and CPU.

- (b) Interface the console terminal so operator may talk to system. May be used as user input. Once chip serial data between console and interface. Parallel between interface and CPU.

- (c) Interface for all data to be passed between CPU and unibus.

- (d) Generates all interrupts from unibus, massbus devices, TU58 and console terminal.

- (e) Acts as generator for time of year (TOY) clock. To keep system informed as to correct time. Battery run. (Batteries included)

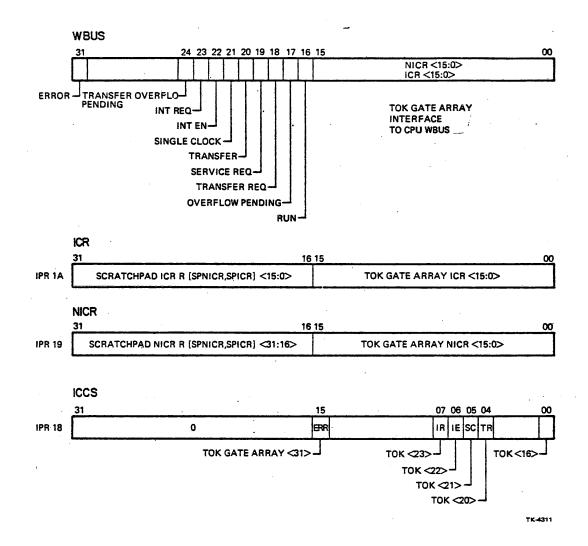

- e. Buses: M, W, CMI

- Functions to interconnect via etching on backplane all sections of CPU to allow them to communicate.

- (a) M Bus used to transmit data to and from scratch pad registers, memory data registers, PC, virtual address registers, PC, virtual address registers and data path module. Also included is data to and from FPA.

- (b) W Bus originates at ALU in DPM and xmits data to data routing and alignment, address logic, unibus interface and FPA.

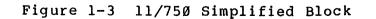

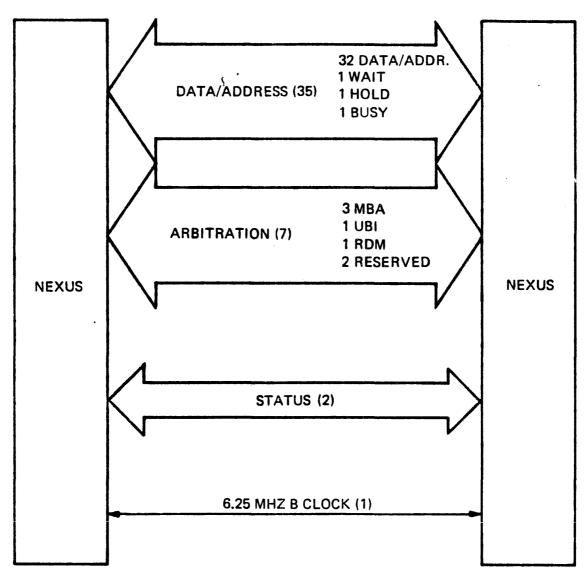

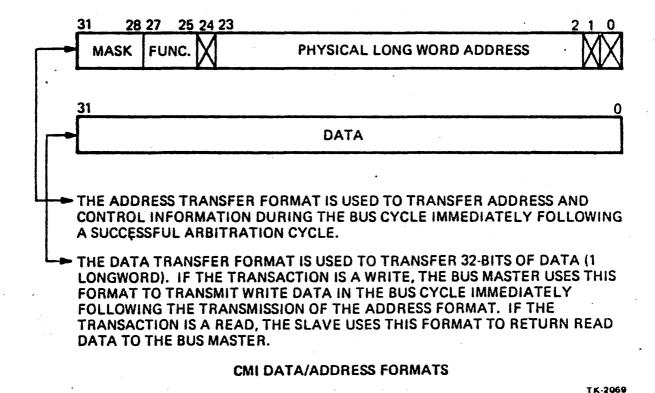

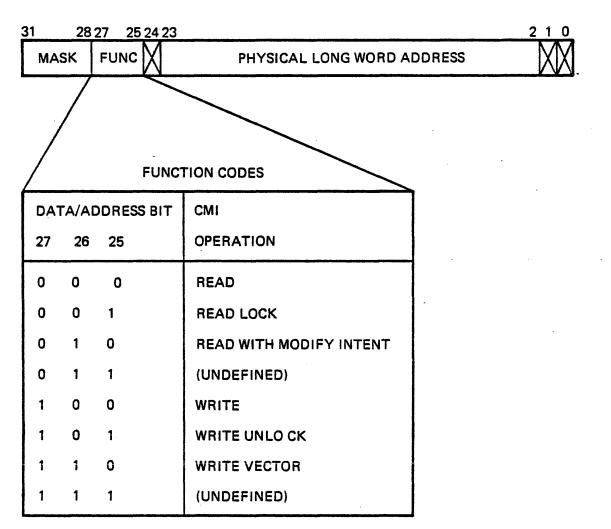

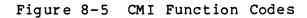

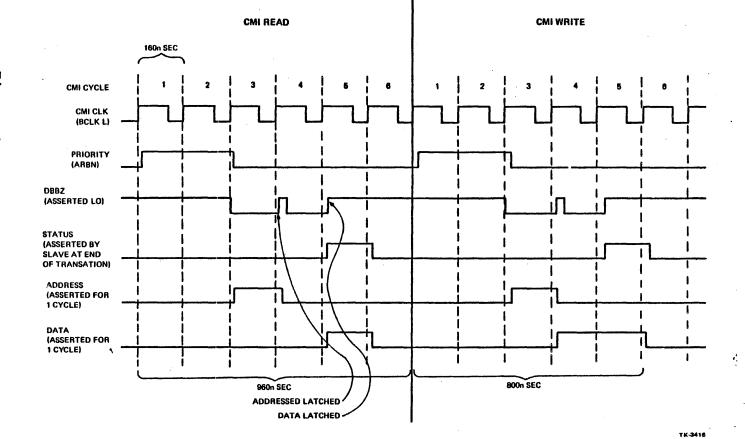

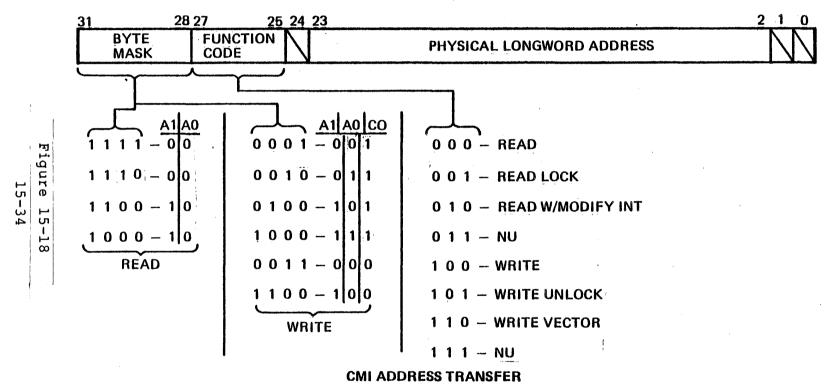

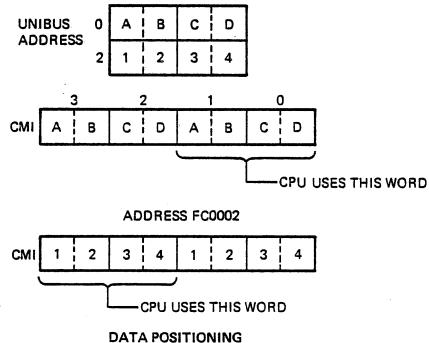

- (c) CMI Bus (CPU Memory Interconnect) etch on backplane that connects CPU to all I/O buses and memory for data exchange. Synchronous interlocked 160 nanosec cycle.

- (2) Contents

- (a) M Bus data lines <31:0>

- (b) W Bus data lines <31:0>

- (c) CMI Bus 45 lines

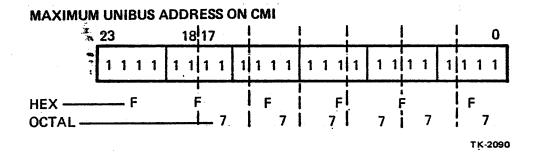

i. 32 data/address ii. 1 wait iii. 1 hold iv. 1 busy v. 7 arbitration lines vi. 2 status vii. 1 8MHZ clock

1-12

THE CMI STRUCTURE

TK-2064

## Figure 1-4 CMI Structure

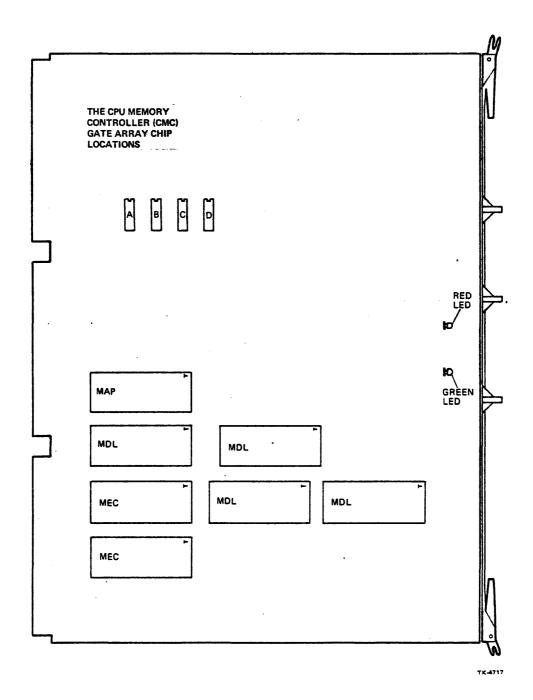

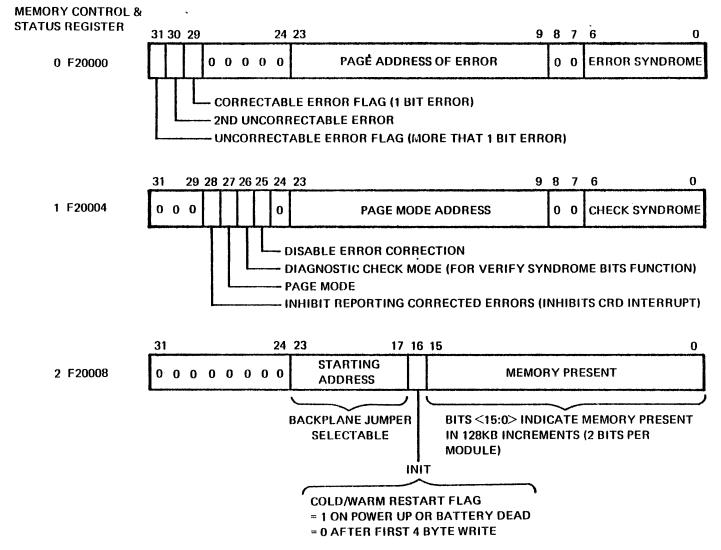

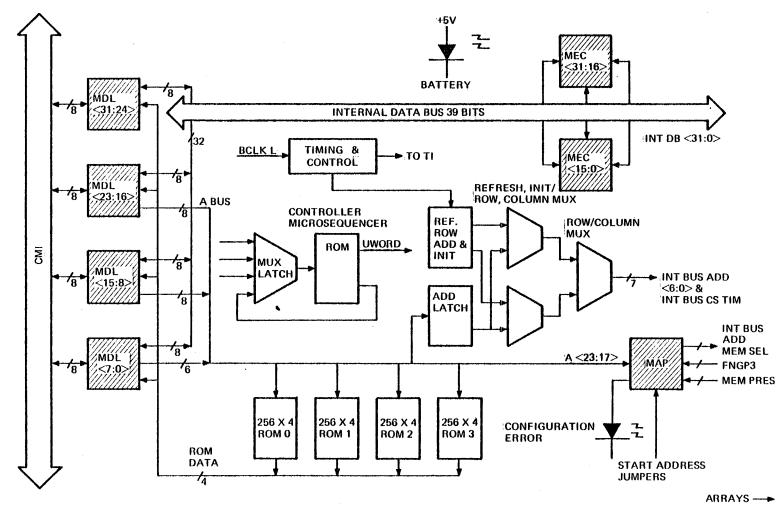

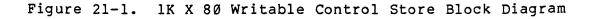

- 2. Memory two to nine modules

- a. Controller module (Slot 10)

- (1) Functions

- (a) Controls data moving to and from CMI and memory

- (b) Controls refresh circuitry for moss memory

- (c) Performs error correction for 1 bit

- (d) Has boot ROMs (up to 4)

- (2) Contents

- (a) Two clocks

- i. fast used between CMI and controller

- ii. slow used between controller and memory

- (b) Error correcting circuitry

- (c) Up to 4 boot ROMs

- (d) refresh circuitry

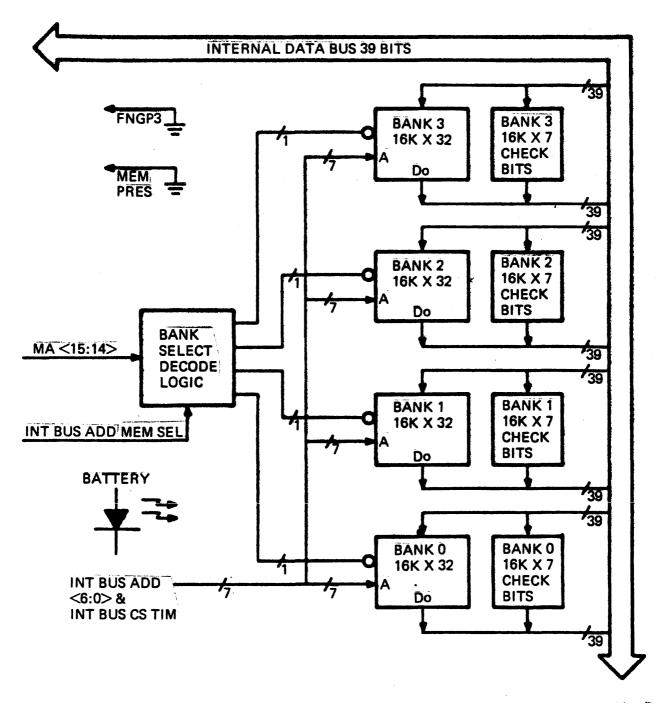

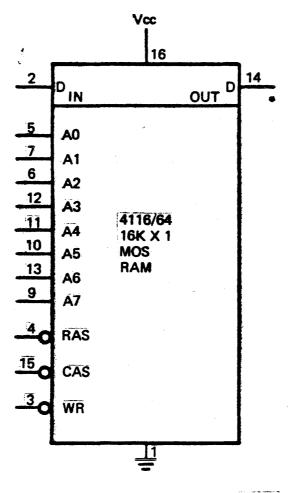

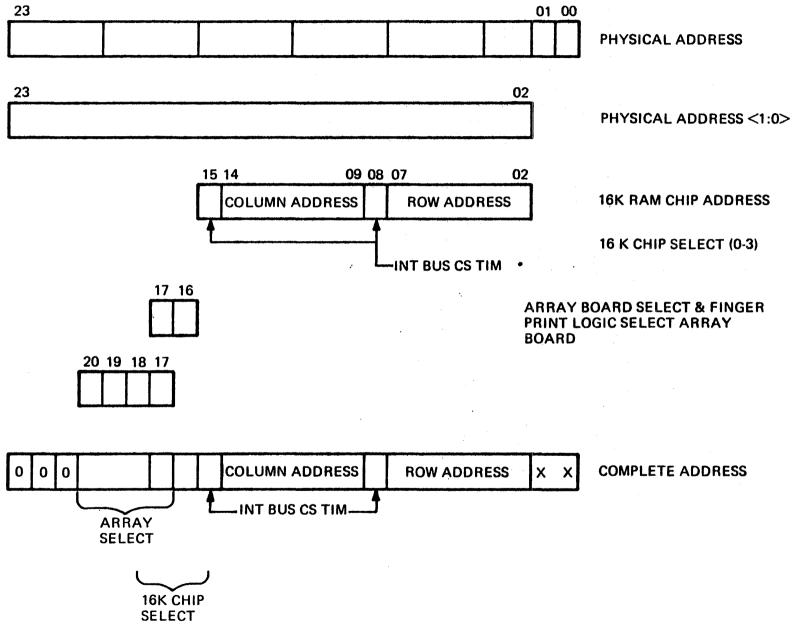

- b. Array Boards up to 8 (slots  $1 \rightarrow 8$  in hex)

- (1) Function hold data for storage up to 2

meg

- (2) Content

- (a) 256K of mos¥ each board

- (b) max 8 boards

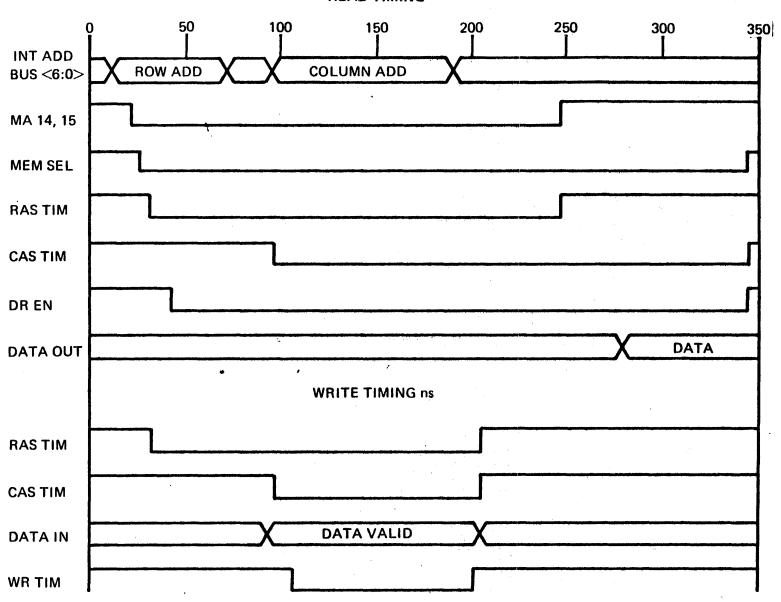

- c. Memory Internal Bus

- Function carry data addresses and control signals between controller and memory

. .....

- (2) Contents

- (a) 39 data lines

1-14

- (b) 7 multiplexed chip address lines

- (c) Two address lines for 16K 39 grp select

- (d) One ROM address strobe or column address strobe

- (e) One read/write control

- 3. Options

- a. CPU options 2 boards

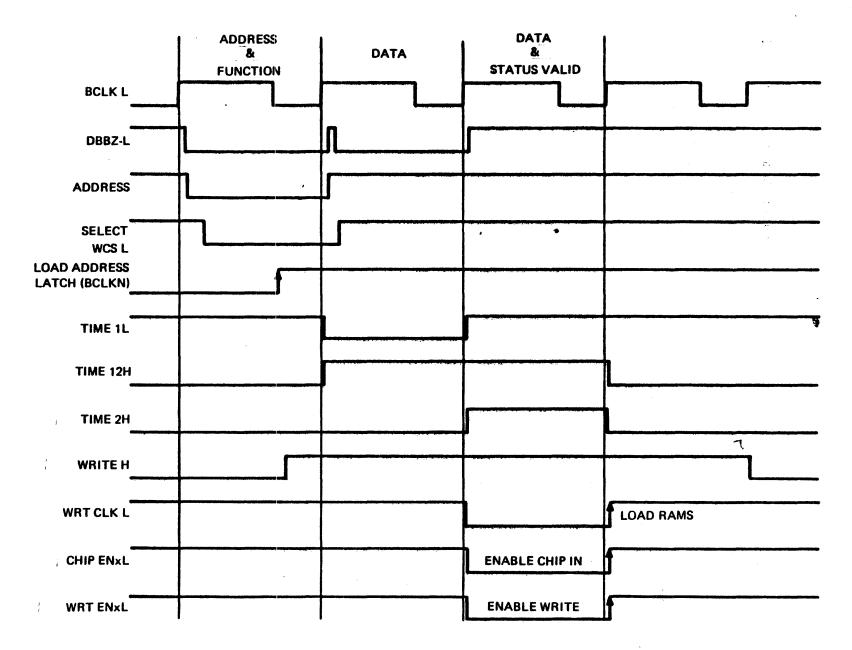

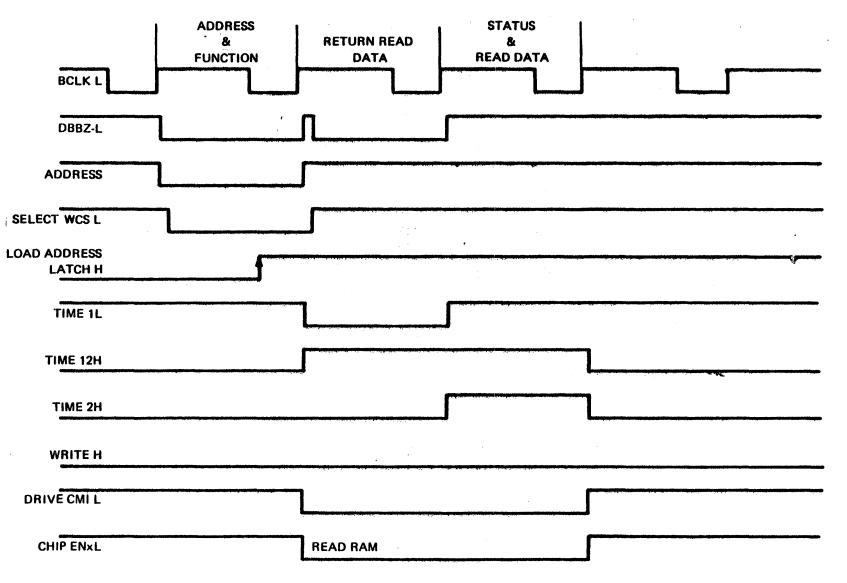

- (1) Writeable control store (slot 5 in ex-hex)

- (a) Function allow programmer to write his own microcode. Ex: subroutine

- (b) Contents-RAMs, board is plugged to CCS

- (2) Floating-point accelerator (slot 1 in ex-hex)

- (a) Function used for working arithmetic functions which have large numbers of many decimal places

- b. Massbus Options maximum of 3 adaptors (slots 7 -> 9 in ex-hex)

- Function to interface data between one of 8 devices possible on each adaptor to the CMI bus. Devices could be used for storage of operating system, space for user programs or overall virtual memory space.

- (2) Contents made up of LSI arrays and standard logic

#### Note

Interrupts from massbus devices are given a BR4 level and passed to CPU via unibus interface board. To receive BG back it must have the BG jumper removed if adaptor is present in a slot.

- c. Unibus Options (slots 1 -> 9 unibus backplane)

- Function many and varied according to what devices are purchased. DZ11 is normally bought to interface up to 8 user terminals.

- (2) Contents relative to what is purchased, but will always have M9313 for end of the bus termination and diagnostics.

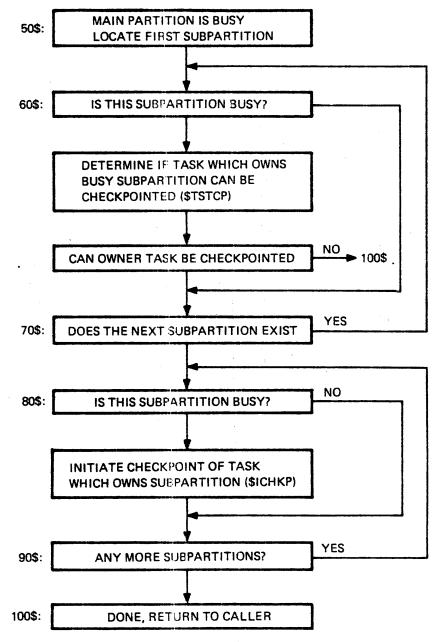

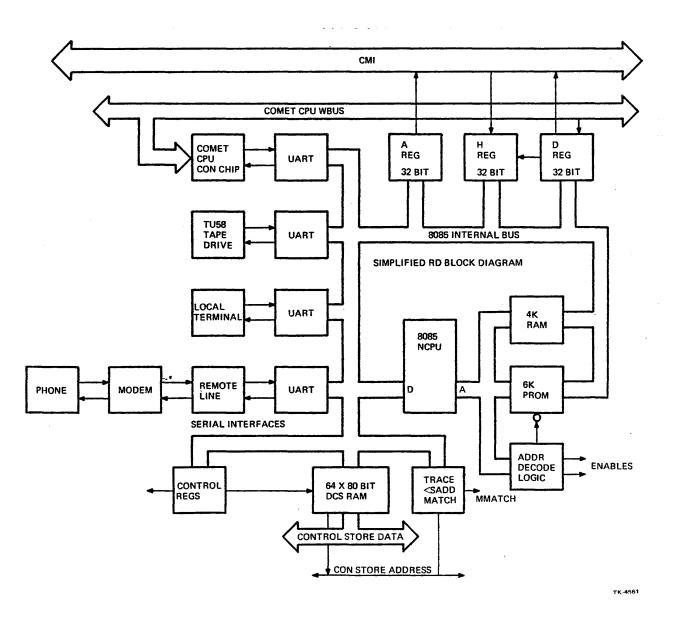

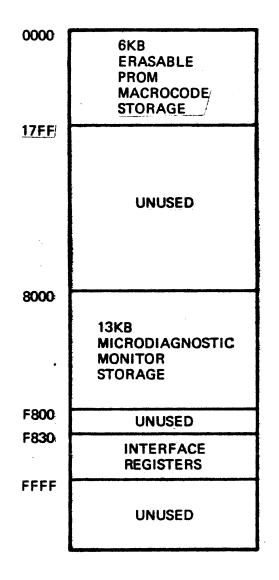

- d. Remote Diagnostic Module (slot 6 ex-hex) RDM

- (1) Functions

- (a) Needed to run microdiagnostics

- (b) Run macrodiagnostics from remote site

- (c) If macros won't run, differentiate between CPU and memory

- (d) Utilize TU58 as backup source for hardcore, cache/TB diagnostic supervisor in case mass medium is down

- (e) Down line load of micros is not a goal

- (2) Contents

- (a) RAMs to hold microdiagnostic monitor

- (b) DCS (Data Control Store) to hold microsequencers loaded by monitor

1-16

TK-3210

TK-3211

Figure 1-6 Backplane Rear View

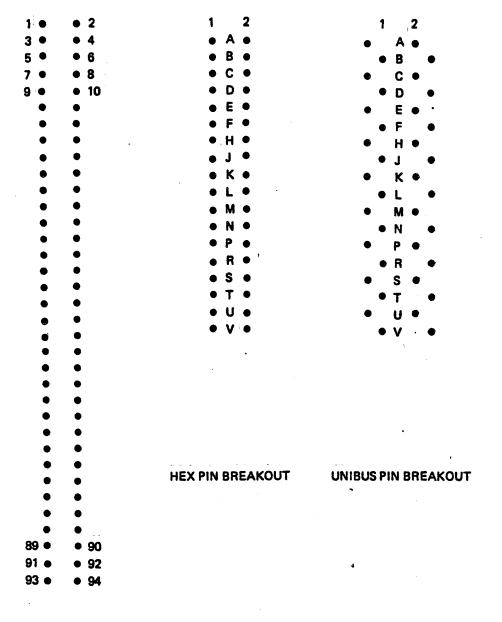

EXTENDED HEX PIN BREAKOUT COMET BACKPLANE PIN BREAKOUTS

TK-3213

Figure 1-7 11/750 Backplane Pin Breakouts

.

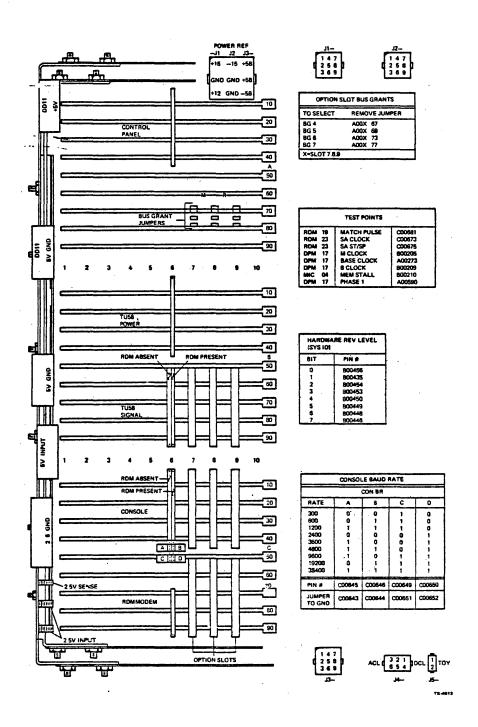

Figure 1-8 Jumper and Cable Connections

TK-3209

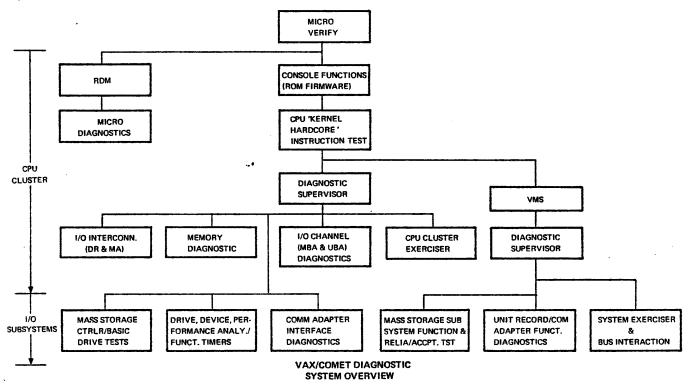

Figure 1-9 VAX Diagnostic Overview

The next section describes the diagnostics available on the 11/750 their different levels of usage. The names and locations of all diagnostics be found on micro fiche under ZZ-EVNDX. There is an other tape [TU58] lable to the field that is not concerned with diagnostics; that being CONSOLE tape which has the BOOT 58 program and BOOT command files locates it. That tape is not listed here and will be discussed later.

This is the beginning of diagnostic overview.

Diagnostics are broken down into five levels, four of which are numbered 1-4. The remaining level is microdiagnostics.

- LEVEL 1. These are diagnostics that run under the VMS operating system and not using the diagnostic supervisor. EX. UETP (not a diagnostic, an excersiser).

- LEVEL 2. These are diagnostics that run under the diagnostic supervisor while the VMS system is still operating. EX. Reliability and acceptance tests, line printer.

- LEVEL 3. These are diagnostics that run under the diagnostic supervisor while the VMS system is not running. The diagnostic supervisor must be running stand alone. EX. UBI DIAGNOSTIC.

- LEVEL 4. These are diagnostics that are run stand alone without the diagnostic supervisor or VMS operating. EX. Hardcore instruction.

- MICROS These are diagnostics that are loaded from the TU58 and run from the RDM RAM memory. There will be a total of four;

- 1. DPM micro [data path]

- 2. MIC micro [memory interconnect]

- 3. CMC micro [memory controller]

- 4. FPA micro [floating point]

Of these four only the first two are available as of August 1, 1980.

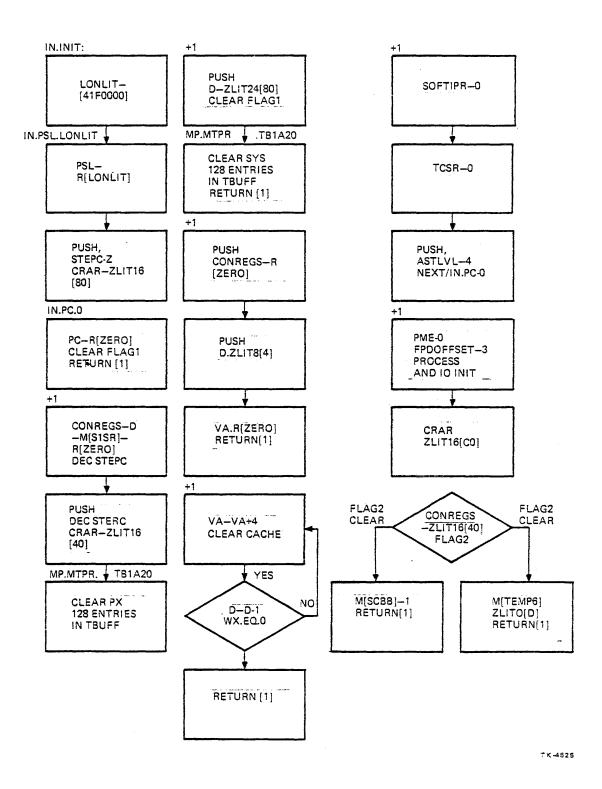

There is another diagnostic that is run every time the machine is powered up or the Initialize button is pushed. This is called micro verify. This is resident in the machine inside the microcoded CSC module and checks the basic sanity of the data path and mic module before any other operations are performed. This is discussed in its entirety in a later section.

There are some diagnostics that may be run under level 2 or 3 and should not be thought of as just level 2 or 3. These will be discussed as we reach them.

The following is a list of the diagnostics that are available and which TU58 tape they are distributed on.

The following four tapes are run at the micro level to check the CPU. They are not to be run in their numerical order for troubleshooting purposes. Order for troubleshooting will be discussed later.

- TU58 TAPE #1: VAX 11/750 MICRO DATA PATH [DPM] ECKAA.EXE MICRODIAGNOSTIC MONITOR [MM FROM NOW ON] ECKAB.EXE MICRODIAGNOSTIC DPM

- TU58 TAPE #2: VAX 11/750 MICRO MEMORY INTERCONNECT [MIC] ECKAA.EXE MM ECKAC.EXE MICRODIAGNOSTIC MIC

- TU58 TAPE #3: VAX 11/750 MICRO COMET MEMORY CONTROLLER [CMC] ECKAA.EXE MM ECKAD.EXE MICRODIAGNOSTIC CMC

- TU58 TAPE #4: VAX 11/750 MICRO FLOATING POINT [FPA] ECKAA.EXE MM ECKAE.EXE MICRODIAGNOSTIC FPA [TAPE 3 AND 4 NOT RELEASED AS OF AUG. 1ST 1980]

The following four tapes are used to test the CPU levels other than MICRO.

- TU58 TAPE #5: VAX 11/750 CACHE/TB;MEMORY;CLUSTER EXCERSISOR ECKAL.EXE CACHE/TB [BOOTABLE;LEVEL 4] ECKAM.EXE MEMORY DIAGNOSTIC [LEVEL 3] ECKAX.EXE CLUSTER EXCERSISOR [LEVEL 3]

- TU58 TAPE #6: VAX 11/750 DW 750 [UBI];DIAGNOSTIC SUPERVISOR ESSAA.EXE DIAGNOSTIC SUPERVISOR [ONLY TAPE TO CONTAIN THIS BOOTABLE] ECCBA.EXE UBI DIAGNOSTIC [LEVEL 3]

- TU58 TAPE #7: VAX 11/750 HARDCORE INSTRUCTION EVKAA.EXE HARDCORE INSTRUCTION [BOOTABLE;LEVEL 4]

- TU58 TAPE #8: VAX 11 INSTRUCTION TESTS EVKAB.EXE VAX ARCHITECTURAL INST. [LEVEL 2 AND 3] EVKAC.EXE VAX FLOATING POINT INST. [LEVEL 3] EVKAD.EXE VAX COMPATIBILITY MODE INST. [LEVEL 3] EVKAE.EXE VAX PRIVILEGED ARCHITECTURAL INST. [LEVEL 3]

Remaining tapes that follow are to be used to test options available on the 11/750. These will be [as the previous tapes #7 and 8] the same diagnostics that are run on the 11/780. To determine which level the diagnostics will be run at you will need to read the associated manual.

| TU58 | TAPE | <b>#9:</b> | VAX | CR/DISK | USER | MODE |  |

|------|------|------------|-----|---------|------|------|--|

|      |      |            |     | •       |      |      |  |

| AX LOADABLE | DRIVER FOR                                                  | RMOX/RM 8Ø                                                                                                                                                |

|-------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| AX LOADABLE | DRIVER FOR                                                  | RK611-RKØ6/Ø7                                                                                                                                             |

| AX LOADABLE | DRIVER FOR                                                  | RL11-RLØ1/Ø2                                                                                                                                              |

| AX CR11 CR  | DIAGNOSTIC                                                  |                                                                                                                                                           |

| AX RP/RK/RM | I/RX/TU58 REI                                               | LIABILITY                                                                                                                                                 |

| AX DISK FOR | MATTER                                                      |                                                                                                                                                           |

|             | VAX LOADABLE<br>VAX LOADABLE<br>VAX CR11 CR<br>VAX RP/RK/RM | VAX LOADABLE DRIVER FOR<br>VAX LOADABLE DRIVER FOR<br>VAX LOADABLE DRIVER FOR<br>VAX CR11 CR DIAGNOSTIC<br>VAX RP/RK/RM/RX/TU58 REI<br>VAX DISK FORMATTER |

| TU 58 | TAPE #10: | KMC11/DMC11/DZ11          |

|-------|-----------|---------------------------|

|       | EVDMA     | VAX M8203 REPAIR LEVEL    |

|       | EVDXA     | VAX COMM IOP REPAIR LEVEL |

|       | EVDAA     | VAX DZ11 8 LINE ASYNC MUX |

- TU58 TAPE #11: RK611 DIAGNOSTICS #1EVREAVAX RK611 DIAGNOSTIC PART AEVREBVAX RK611 DIAGNOSTIC PART B

- TU58 TAPE #12: RK611 DIAGNOSTICS #2EVRECVAX RK611 DIAGNOSTIC PART CEVREDVAX RK611 DIAGNOSTIC PART DEVREEVAX RK611 DIAGNOSTIC PART E

- TU58 TAPE #13: RK611 DIAGNOSTICS #3EVREFVAX RKØ6/Ø7 DRIVE FUNCTION TEST PART 1EVREGVAX RKØ6/Ø7 DRIVE FUNCTION TEST PART 2

- TU58TAPE #14:RMØ3/RMØ5EVRDAVAXRMØ3/RMØ5/RM8ØDISKLESSEVRDBVAXRMØ3/RMØ5FUNCTIONAL

- TU58 TAPE #15: TS11 DIAGNOSTICSEVQTSVAX LOADABLE DRIVER FOR TS11/TSØ4EVMAAVAX TMØ3/TE16/TU45EVMADVAX TS11 SUBSYSTEM REPAIR

TU58 TAPE #16: RLØ2 SUBSYSTEM FUNCTIONAL DIAGNOSTICSEVRFAVAX RLØ2 SUBSYSTEM FUNCTIONAL DIAGNOSTICSEVRGAVAX RM8Ø FORMATTEREVRGBVAX RM8Ø FUNCTIONAL DIAGNOSTICS

As of August 1, 1980 the above were the only diagnostics proven compatible with both the 11/780 and 11/750. The following are the remaining diagnostics that are planned.

| POSSIBLE ON | E TAPE: |     |       |         |       |

|-------------|---------|-----|-------|---------|-------|

| ESDRB       |         | VAX | DR11W | DIAGNOS | TIC   |

| ESDRE       |         | VAX | DR11W | REPAIR  | LEVEL |

| POSSIBLE | 2ND | TAPE: |     |        |    |         |        |            |

|----------|-----|-------|-----|--------|----|---------|--------|------------|

| ESDE     | 3A  |       | VAX | M82Ø1/ | /2 | REPAIR  | LEVEL  | DIAGNOSTIC |

| ESDE     | BB  |       | VAX | DMC11  | ΕŻ | CERSISC | DR PRO | GRAM       |

| POSSIBLE | 3RD | TAPE: |     |       |        |       |      |   |  |

|----------|-----|-------|-----|-------|--------|-------|------|---|--|

| ESDU     | JP  |       | VAX | DUP11 | REPAIR | LEVEL | PART | 1 |  |

| ESDU     | JÕ  |       | VAX | DUP11 | REPAIR | LEVEL | PART | 2 |  |

Please note that all diagnostic (not including the micro diag. or EVKAA and ECKAL) that relate to your system will be sent with the system pack as part of the system on whatever medium your VMS is incorporated in.

## VAX 11-/750 LEVEL II

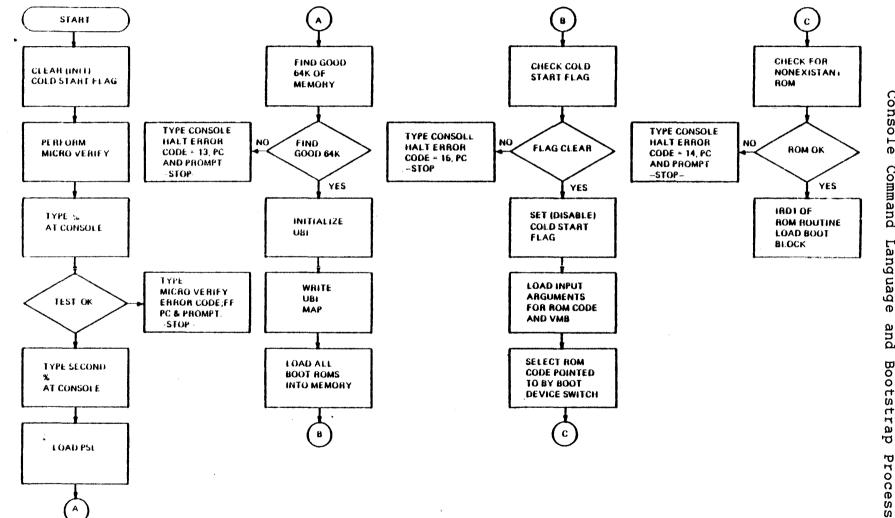

Console Command Language and Bootstrap Process

Student Guide

Course produced by Educational Services Department of Digital Equipment Corporation Console Command Language and Bootstrap Process

## OUTLINE

## II. A. Console Command Language

•

- 1. Control Characters

- 2. Console Command Symbols

- 3. Console Commands

- 4. Errors and Illegal Characters

## B. Bootstrap Process

- 1. Definition

- 2. Different Boot Methods

- 3. How Boot is Accomplished

- 4. Boot 58

- 5. Automatic Boot

- 6. System Shutdown

- 7. Copy Console Device Files

### INTRODUCTION

This lesson introduces the student to the VAX console commands needed to communicate with the VAX-11/750. After becoming familiar with the commands and their functions in the classroom, a lab session will be provided to utilize each command. The lab session will allow the student to initialize the system and perform deposits and examinations to various registers and memory locations.

This lesson also covers the VAX-11/750 bootstrap process. By using flowcharts, the process will be covered from device selection to error indications. Once the process has been covered by lecture, a lab session will be utilized to reinforce the concepts and to demonstrate error conditions. Console Command Language and Bootstrap Process

#### OBJECTIVES

- 1. Using console commands, initialize the system.

- 2. Using console commands, deposit data to a register.

- 3. Using console commands, examine data in a register.

- 4. Boot the system.

- 5. Given the console printout indicating a boot failure, clear the fault by locating the problem.

#### SAMPLE TEST ITEM

This console printout occurred while booting the system with FPS1 set to boot.

% %

XXXXXXX 13

>>>

What is indicated to the operator?

a. A 64K bytes of good memory not foundb. A nonexistent boot ROMc. A HALT was executedd. Wrong Rev. level

#### RESOURCES

VAX 11/750 RDM Maintenance Card

VAX 11/750 Diagnostic System Overview Manual

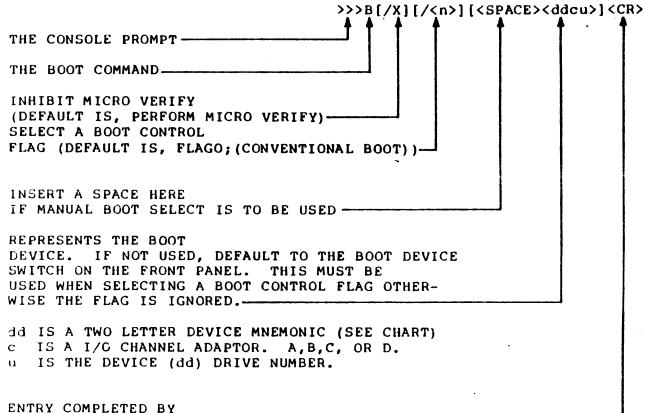

THE BOOT COMMAND

| d        | ld          |

|----------|-------------|

| MNEMONIC | DEVICE      |

| DL       | RLØ2        |

| DM       | RKØ6/7      |

| DB       | RPØ4/5/6    |

| DR       | RMØ3        |

| DD       | <b>TU58</b> |

2-4

CARRIAGE RETURN ----

Console Command Language and Bootstrap Process

| BOOT CONTROL<br>FLAG | FUNCTION                 | / <n></n> |

|----------------------|--------------------------|-----------|

| Ø                    | CONVERSATIONAL BOOT.     | 1         |

| 1                    | DEBUG                    | 2         |

| 2                    | INITIAL BREAKPOINT       | 4         |

| 3                    | NOT USED WITH VAX 11/750 | 8         |

| 4                    | DIAGNOSTIC BOOT          | 10        |

| 5                    | BOOTSTRAP BREAKPOINT     | 2Ø        |

| 6                    | IMAGE HEADER             | 4Ø        |

| 7                    | MEMORY TEST INHIBIT      | 8Ø        |

| 8                    | FILE NAME                | 100       |

| 9                    | HALT BEFORE TRANSFER     | 200       |

.

## BOOT CONTROL FLAG FUNCTIONS

## THE DEPOSIT COMMAND

## >>>D[<qualifier-list>][<space><address>]<space><data><cr>

CONSOLE PROMPT

DEPOSIT COMMAND

SIZE & SPACE /B /V /W /P /L /I /G

TO SELECT A DEPOSIT ADDRESS OTHER THAN Ø

<nnnnnnn> -- HEX ADDRESS

<\*> -- LAST LOCATION

<P> -- PSL

<+> -- NEXT LOCATION

YOU MUST SELECT A HEX VALUE (1-8 DIGITS)

OPERATION COMPLETED

#### THE BOOT/BOOTSTRAP AS DEFINED BY THE DEC DICTIONARY - PG 28

- boot (boots, booting, booted)\* v. (See also bootstrap.) To bring a device or system to a defined state where it can operate on its own. EXAMPLE(S): The operator boots the system before starting operation.

- boot (boots)\* n. A protective housing, usually made from a resilient

material, used to protect connectors or other terminals from moisture.

EXAMPLE(S) : Pull the boot up over the plug to make the connection

waterproof.

N

- bootstrap (bootstraps, bootstrapping, bootstrapped)\* v. (See also boot.)

To bring a device or system to a defined state where it can operate on

its own. EXAMPLE(S): You must bootstrap the system before logging on.

- bootstrap (bootstraps) \* n. A technique or device designed to bring a system or device into a desired state by means of its own action, e.g., a machine routine whose first few instructions are sufficient to bring the rest of itself into the computer from an input device. EXAMPLE(S): Using the bootstrap saves time.

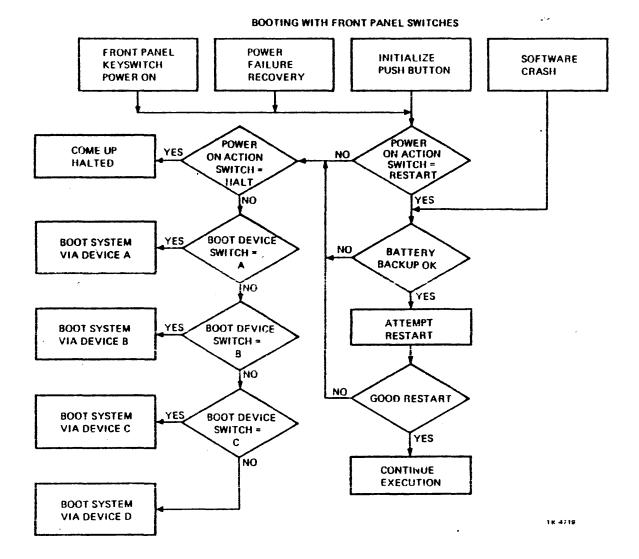

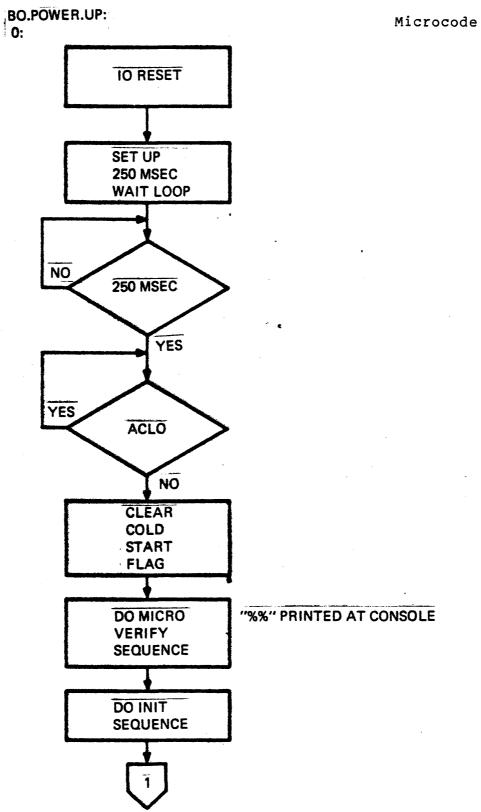

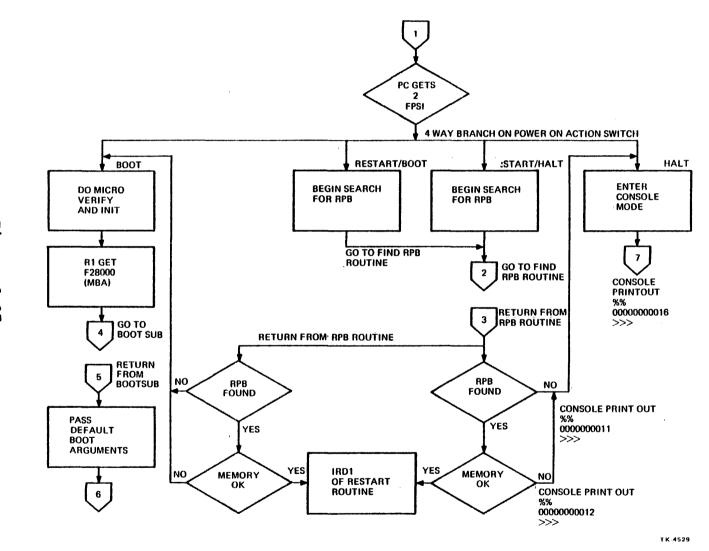

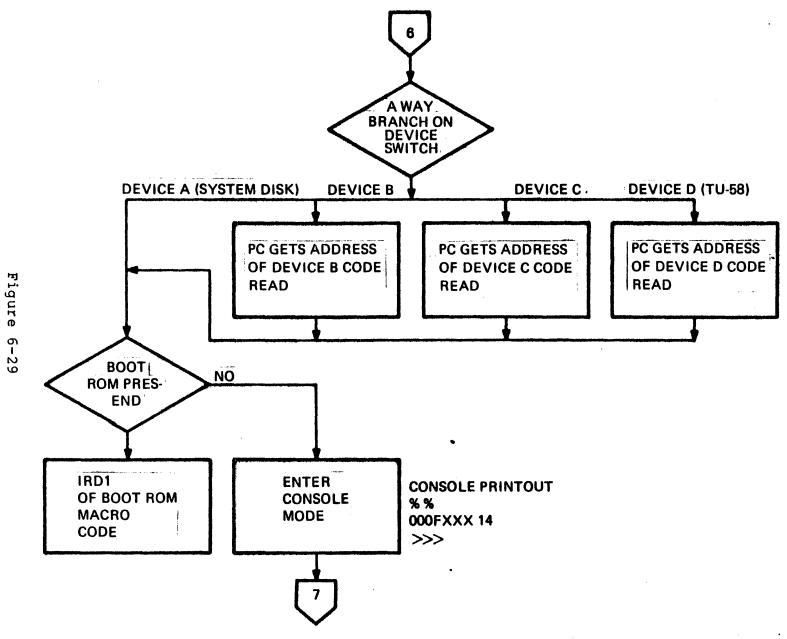

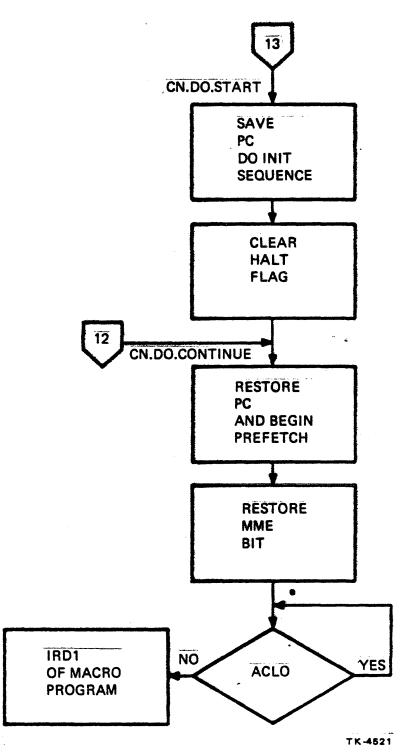

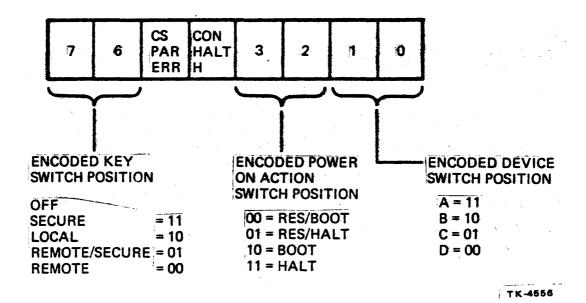

## CONSOLE MICROCODE EXAMINES THE BOOT DEVICE AND POWER ON ACTION SWITCHES ON THE FRONT PANEL;

When you initially apply power by turning the front panel keyswitchWhen recovering from a power failure

o When the operator pushes the front panel initialize switch.

o After a software "CRASH"

÷

.

.

Figure 2-1

.

Console Command Language and Bootstrap Process

# SOFTWARE BOOT CONTROL FLAGS

.

# (1 of 2)

| Flag | Hex<br>Value | Function                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Ø    | 1            | Conversational boot. At various points<br>in the system boot procedure, parameters<br>and other inputs will be solicited from<br>the console.                                           |  |  |  |  |  |  |  |  |

| 1    | 2            | Debug. This flag is passed through to<br>VMS and causes the code for the executive<br>debugger to be included in the running<br>system.                                                 |  |  |  |  |  |  |  |  |

| 2    | 4            | Initial breakpoint. If this flag is set,<br>and the executive debugger code is<br>included (flag bit 1), then a breakpoint<br>will occur immediately after the exec<br>enables mapping. |  |  |  |  |  |  |  |  |

| 3    | 8            | Not used on the VAX-11/750.                                                                                                                                                             |  |  |  |  |  |  |  |  |

| 4    | 10           | Diagnostic boot. This flag causes a boot<br>by file name for the diagnostic<br>supervisor.                                                                                              |  |  |  |  |  |  |  |  |

Console Command Language and Bootstrap Process

# SOFTWARE BOOT CONTROL FLAGS

# (2 of 2)

| Flag | Hex<br>Value | Function                                                                                                                                                                                     |  |  |  |  |  |  |  |

|------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 5    | 2Ø           | Bootstrap breakpoint. This flag causes<br>the bootstrap to stop at a breakpoint<br>after performing necessary<br>initialization.                                                             |  |  |  |  |  |  |  |

| 6    | 40           | Image Header. If this flag is set, the<br>transfer address from the image header of<br>the boot file will be used. Otherwise<br>control will transfer to the first byte<br>of the boot file. |  |  |  |  |  |  |  |

| 7    | 8Ø           | Memory test inhibit. This flag inhibits<br>the testing of memory during<br>bootstrapping.                                                                                                    |  |  |  |  |  |  |  |

| 8    | 100          | File name. Causes the bootstrap to solicit the name of the boot file.                                                                                                                        |  |  |  |  |  |  |  |

| 9    | 200          | Halt before transfer. Causes a HALT<br>instruction to be executed prior to the<br>transfer to the secondary boot file.<br>This option is useful for debugging<br>purposes.                   |  |  |  |  |  |  |  |

# BOOT DEVICE CODES (ddcu)

DEVICE CODE (dd) \* DEVICE TYPE DL RLØ2 DM RKØ6/Ø7 DB RPØ4/Ø5/Ø6 RMØ3/RPØ7 DR DD TU58 Identifies the device that is storing the boot block. CHANNELS ADAPTER (C) Α B , To which port is the Device (dd) channeled to. C D

DRIVE NUMBER (u)

\*

Ø ) on which drive of our device (dd) is 1 ) our boot block located.

2-12

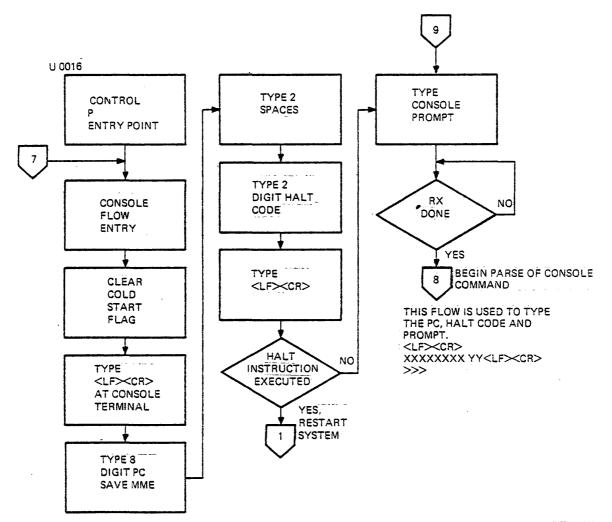

#### CONSOLE COMMAND ERROR CODES

If an illegal console command is attempted or command is aborted because of a microtrap or some other condition a two digit error code is typed out and the console waits for new input. For example...

| >>>E P <cr></cr> | !Examine PSL                                      |

|------------------|---------------------------------------------------|

| >>>E <cr></cr>   | Implies Examine Next Location, this is illegal.   |

| ?11              | !Question Mark and error code is typed by console |

| >>>              | At this point ready for new command               |

Error Codes

20= Deposit or Examine of Memory Failed (Access Violation, Translation not valid, Bus Error, TB Parity Error, or Control Store Parity E ll= Illegal access of an ipr

$3\emptyset = Apt$  Loading Checksum error

33= Attempt to Boot from unknown Device type (DM,DL,DO) 34= Boot Device Controller not "A", "B", "C", OR "D"

# ROM STARTING ADDRESSES

.

e

| DEVICE | ROM | STARTING | ADDRESS |

|--------|-----|----------|---------|

| А      |     | FAØ      | 2       |

| В      |     | FBØ      | 2       |

| с      |     | FCØ      | 2       |

| D      |     | FDØ      | 2       |

۱

CONSOLE SUBSYSTEM ACTION ON BOOT

Console Command Lang uag e and Bootstrap Proces

2-15

18 4727

### INPUT ARGUMENTS

The general registers receive the input arguments from the console subsystem.

- Rl system bus address of a Massbus adapter (MBAØ unless otherwise specified in the Boot command).

- R2 physical address of the Unibus I/O page associated with a Unibus adapter (UBIØ unless otherwise specified in the Boot command).

- R3 device unit number (Ø unless otherwise specified in the Boot command).

- R5 software boot control flags (Ø unless otherwise specified in the Boot command).

- SP <base address + ^X200> of the 64K bytes of good

memory.

C(SP) - transfer address of the boot block code.

# FUNCTIONS AVAILABLE UNDER BOOT 58

.

.

| 0 | Load and start level 4 diagnostic programs.                                                                                                 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | Bootstrap from the Massbus adapter                                                                                                          |

| 0 | Bootstrap from a disk whose boot block is bad.                                                                                              |

| 0 | Bootstrap from a disk whose error rate prohibits ROM and boot block loading of a primary bootstrap.                                         |

| 0 | Boot the diagnostic supervisor instead of VMS.                                                                                              |

| 0 | Deposit and examine data in physical memory, general registers, and internal processor registers.                                           |

| 0 | Load and start a program from a magtape drive on a Massbus.                                                                                 |

| 0 | Store and invoke indirect command files on the TU58 cartridge to perform any of the above functions automatically as well as interactively. |

### POWER UP AND BOOT ERROR REPORTS

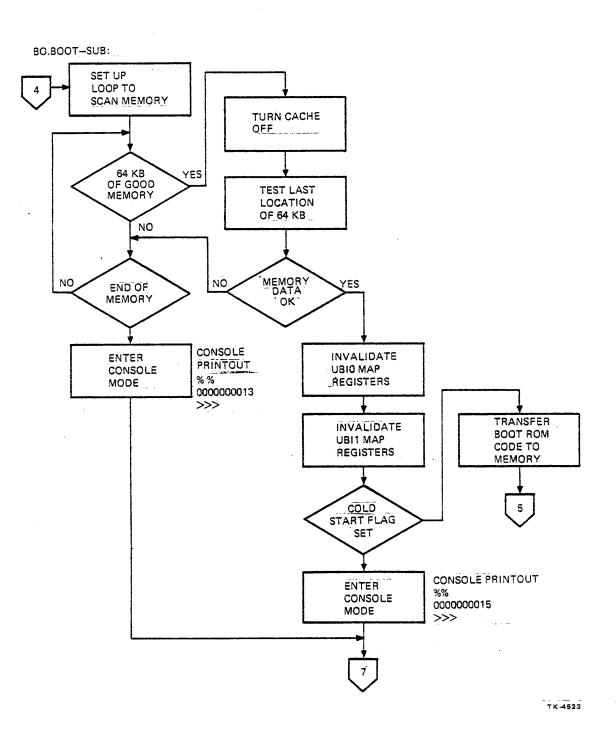

- xxxxxxx 13 This indicates that a good 64KB section of

memory was not found and return to console

mode

- xxxxxxx 14 This indicates a failure or nonexistance of

the boot ROM

- xxxxxxx Ø6 If a halt instruction is executed after typing a console boot command, this indicates a failure of the read of logical block Ø from the selected boot device, the PC should be equal to the base address of the first good 64KB of memory plus FX16 for TU58 or FX2Ø for RKØ6. This failure occurs in the Boot ROM routine.

Console Command Language and Bootstrap Process

### VMB PRIMARY BOOT FAILURES

BOOT is the program name for VMB.EXE The "F" indicates a fatal error and the type of error is reported. **%BOOT-F-Unknown** processor This indicates that CPU is not a Comet or 11/780, check SID register for proper jumpering in the CPU type field on the Backplane. **%BOOT-F-Unexpected Exception** This indicates that one of the following exceptions occurred. 1. Access Violation 2. Breakpoint Opcode 3. Reserved Operand 4. TBit Trap 5. Page Fault (TNV) **%BOOT-F-Unexpected Machine Check** This indicates some sort of machine Check occurred. Check all adaptors using console examine and deposit commands. Probably a timeout. **%BOOT-F-Nonexistant** Drive Self explanatory, Check DEFBOO.CMD on 11/780 and insure system disk is drive being booted. find **%BOOT-F-Unable** to locate BOOT can't VMB file [SYSEXE]SYSBOOT.EXE or if bit 4 in R5 is set, VMB can't find [SYSMAINT]DIAGBOOT.EXE **%BOOT-F-Bootfile** not contiguous Indicates that [SYSEXE]SYSBOOT.EXE or [SYSMAINT]DIAGBOOT.EXE is not contiguous on system disk. Recopy or rebuild %BOOT-F-I/O error reading boot Indicates problem reading file boot file from disk by \$QIO service (VMS System Service).

# VAX-11/750 LEVEL II

System Overview

Student Guide

Course produced by Educational Services Department of Digital Equipment Corporation

# INTRODUCTION

.

This lesson is developed to give you a basic understanding of location of Gate Arrays in 11/750 prints and overall understanding of how each board (DPM, MIC, UBI, and CCS) is laid out. All of the data given out in this section will be reiterated when each board is gone over in detail. You should start to form concepts of how the machine works functionally and how the prints are set up. There will be very little in the Student Guide so listen, take notes in your prints or Functional Block.

### OBJECTIVES

The student will be able to locate all gate arrays in the prints relating to the four basic LPU boards, DFM, MIC, UBI and CCS.

The student will be able to take a MOVL LONG instruction and follow the path of the data from beginning to end.

## SAMPLE TEST ITEM

The access control violation chip is located on which board?

1. DPM 2. MIC 3. UBI 4. CCS

### RESOURCES

11/750 Print Set 11/750 Functional Block

- A. The CPU Overview

- 1. Board common to all CPUs four (4) each

- a. Unibus Interface (UBI Module Slot 4 of extended hex section)

- 1) TU58 Data in and out

- 2) Console Data in and out

- 3) Handles interrupts

- 4) Interfaces Unibus data and CPU data with each other

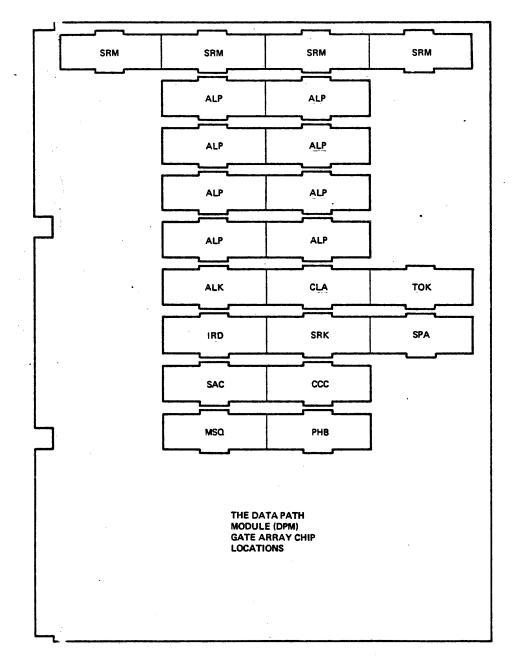

- b. Data Path Module (DPM Slot 2 of extended hex section)

- 1) Contains the arithmetic logic

- 2) Contains the rotator logic

- 3) Houses the Scratch Pad logic (Registers)

- 4) Also houses the Microsequencer logic

- c. Memory Interconnect (MIC Module Slot 3 of the extended hex section)

- 1) Contains the address logic (PC)

- 2) Houses the Translation Buffer which translates virtual addresses to physical addresses

- 3) Cache

- 4) Contains the Data Routing and alignment which handles the routing of data in and out of or to and from memory and the data path.

- d. CPU Control Store (CCS Module Slot 5 of extended hex section)

- 1) Contains the Control Store ROMs for the Microcode

- 2) Houses the optional snap on WCS Module

#### B. Component Analysis

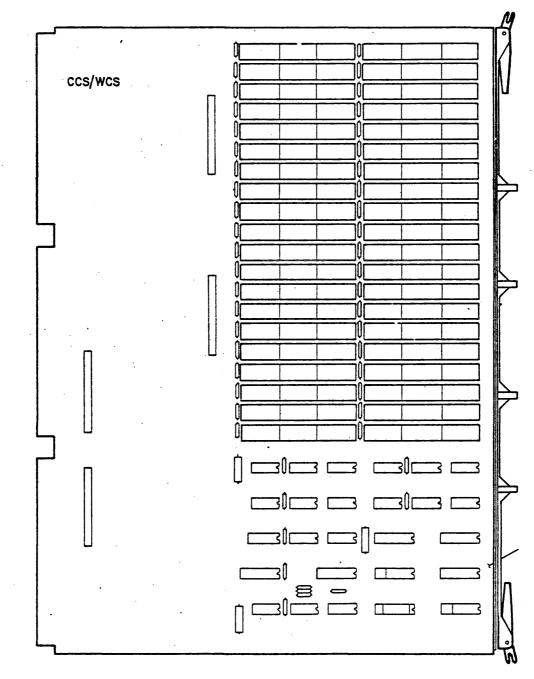

- 1. CPU Control Store (CCS)

- a. 6K x 8Ø Bits, no gate arrays

- 2. Data Path (DDPM) 22 gate arrays

- a. Gate Array Chips

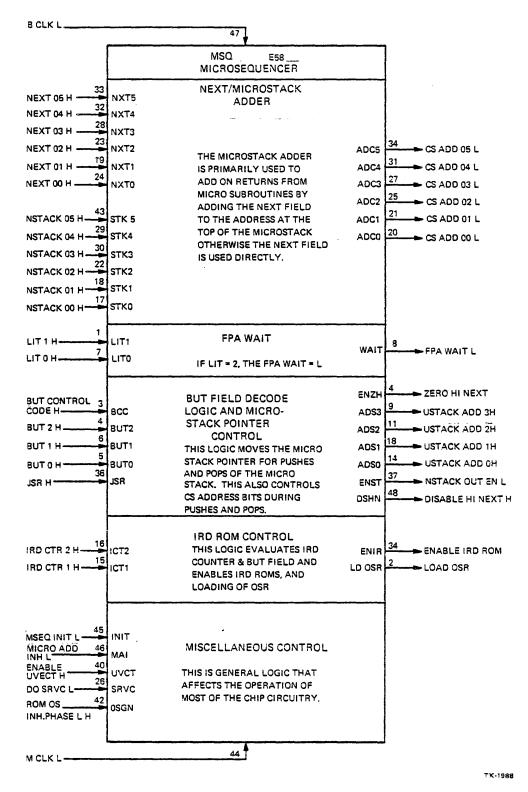

- The microsequencer (MSQ) Sequences the CPU microcode that controls most operations (NOT SHOWN AS ONE CHIP ON BLOCK SHOW IN PRINTS)

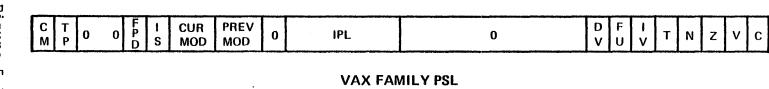

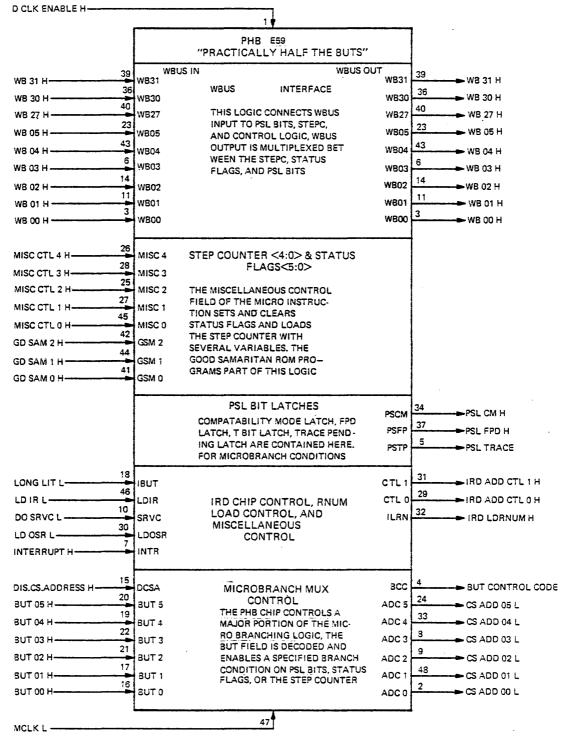

- Practically Half the Buts (PHB) Contains some of the bits of the PSL, the status flags and the step counter. It also contains the logic to generate half of the but micro orders.

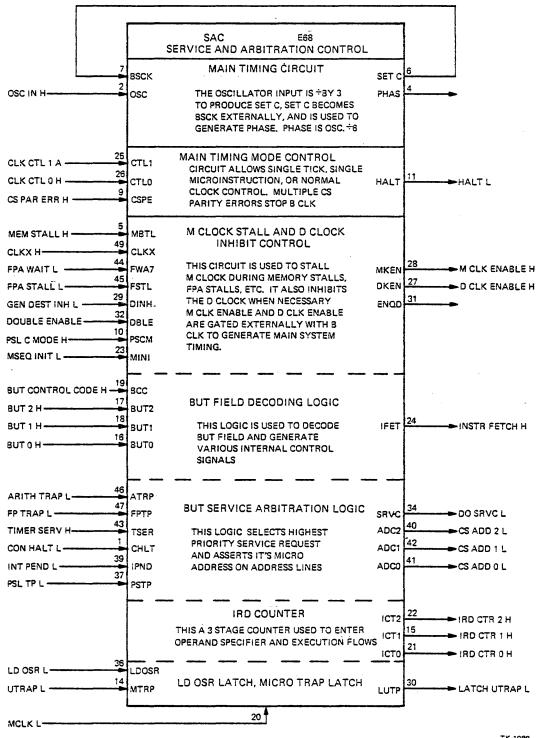

- Service Arbitration and Clock (SAC) Deals with the IRD counter, service arbitration, and the system clock.

- 4) Condition Code Chip (CCC) Deals with condition codes. It determines the condition codes for both VAX and compatability mode instructions, stores the PSL bits <FU,IV,DV,N,Z,V,C>, reads the bits out at Ucode request.

- 5) Instruction Register Decode (IRD) Handles the IR Decode. It receives an opcode and operand specifier from the execution buffer (XB), decodes it and creates the signals needed by the microsequencer to process the appropriate routine.

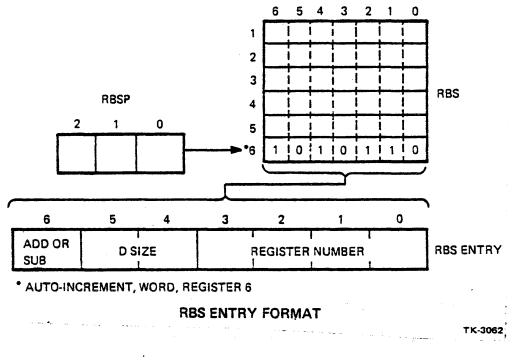

- 6) Super Rotator Control (SRK) It controls the functions of the Super Rotator (SR). The info it needs to control the SR comes from the 6 bit ROT field of the microcode. (NOT ON BLOCK IN TOTAL, PRINTS.)

- a. SPK chip contains the S and P latches and their associated mux in and out. Controls the super rotator via the ROT field of the microword and certain Wbus inputs.

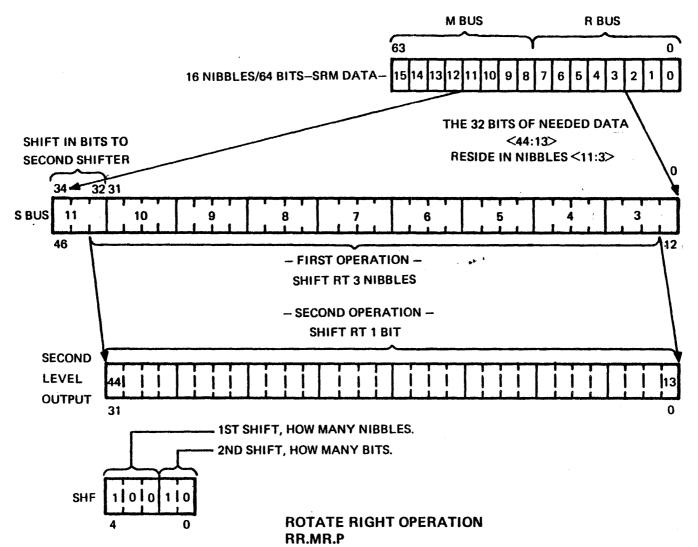

- Super Rotator Multiplex (SRM) 4 ea Perform 64 different operations via control of the SRK chip.

- 8) Scratch Pad Addressing (SPA) Controls the operating of the 64 scratch pad registers, and it provides a mechanism to undo the auto decrementing and auto incrementing of the general purpose registers.

#### SYSTEM OVERVIEW

- 9) Timed Operation Control (TOK) Implements the architecturally defined programmable interval time clock.

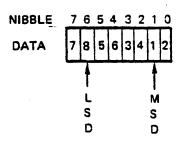

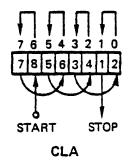

- 10) Carry Look Ahead (CLA) An array of combinational logic used to propagate and generate carries for up to 8 ALU slices. (NOT ON BLOCK, SHOW IN PRINTS.)

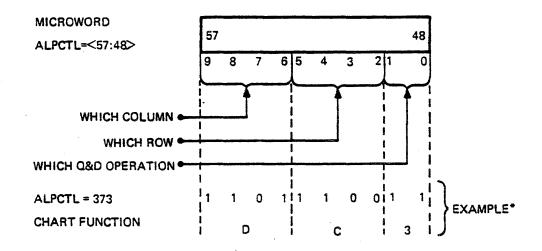

- 11) Arithmetic and Logic Control (ALK) (NOT ON BLOCK, SHOW IN PRINTS.)

- a) Reencodes the ALP control field of the microword for special functions.

- b) Controls the carry input and shift inputs for the ALP chips.

- c) Decodes the scratch pad write enable.

- d) Decodes miscellaneous signals.

- 12) Arithmetic Logic Processors (ALP) 8 ea -Each chip is 4 bits wide. They form the circuit that performs the majority of the data manipulating when executing macro instructions.

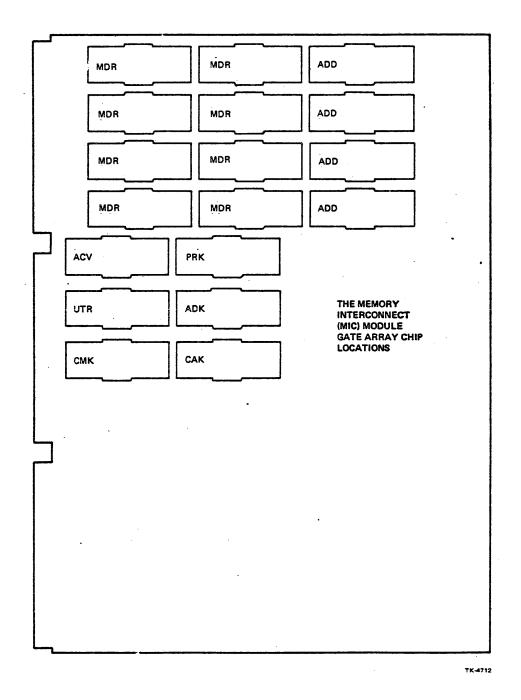

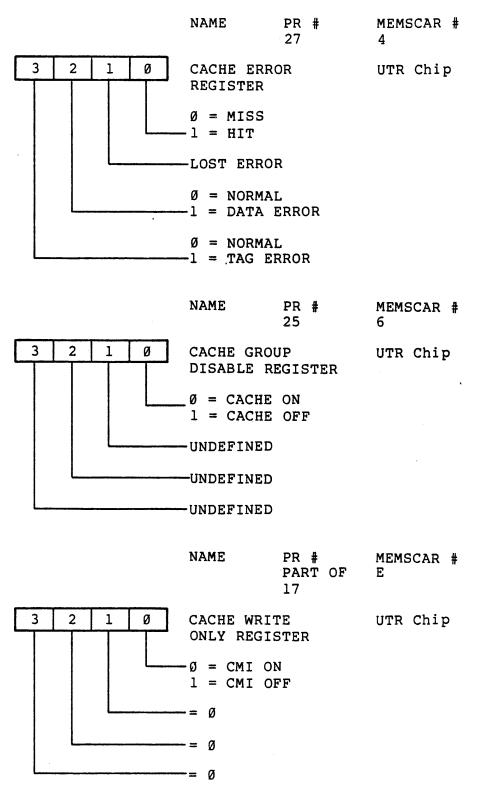

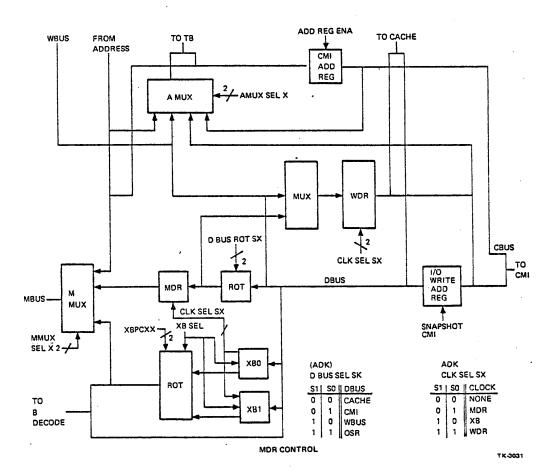

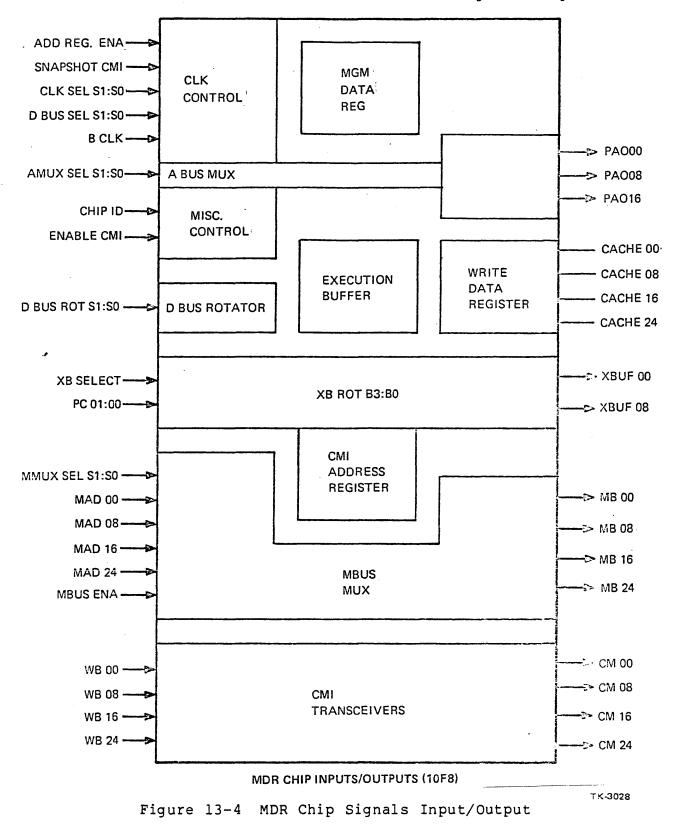

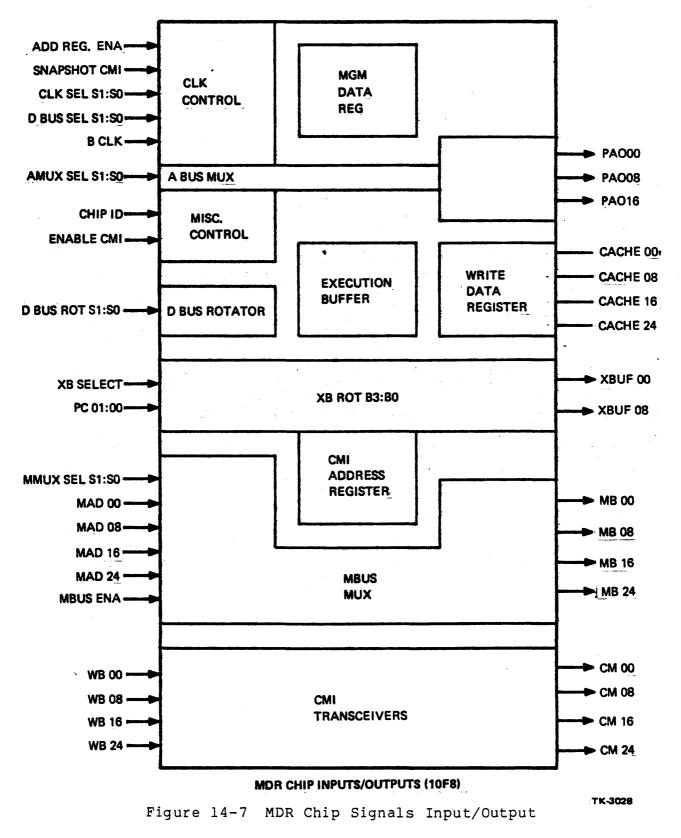

- 3. Memory Interconnect Module (MIC) 18 Gate Arrays

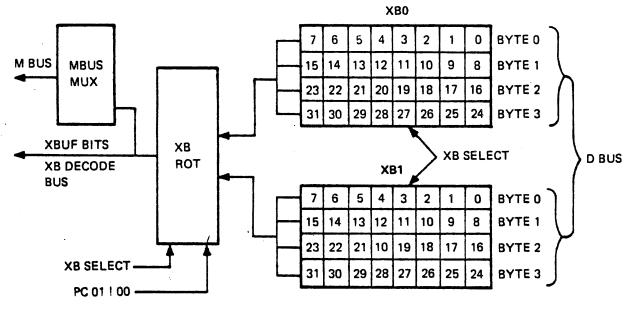

- a. 1) Memory Data Registers (MDRs) 8 ea Major portion of the data routing and alignment circuit. They receive and hold data in/out to/from the Mbus.

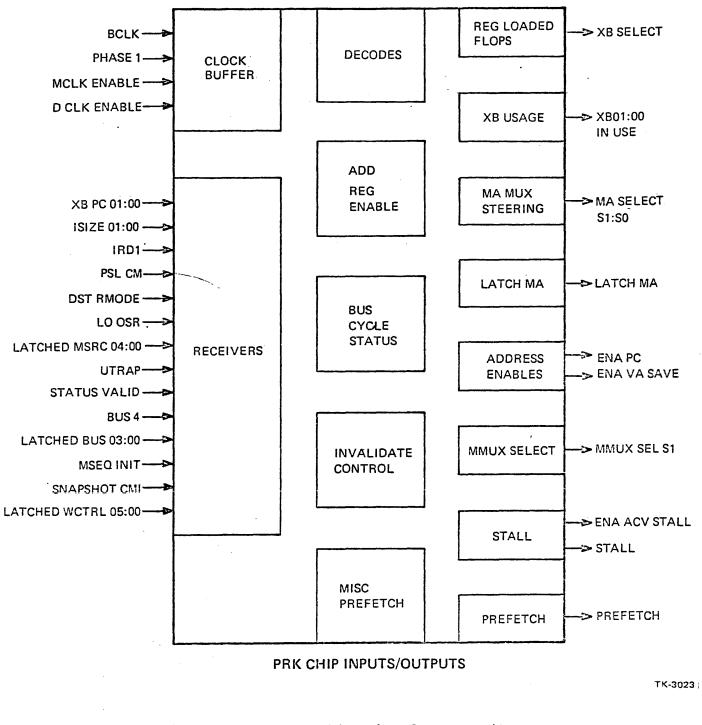

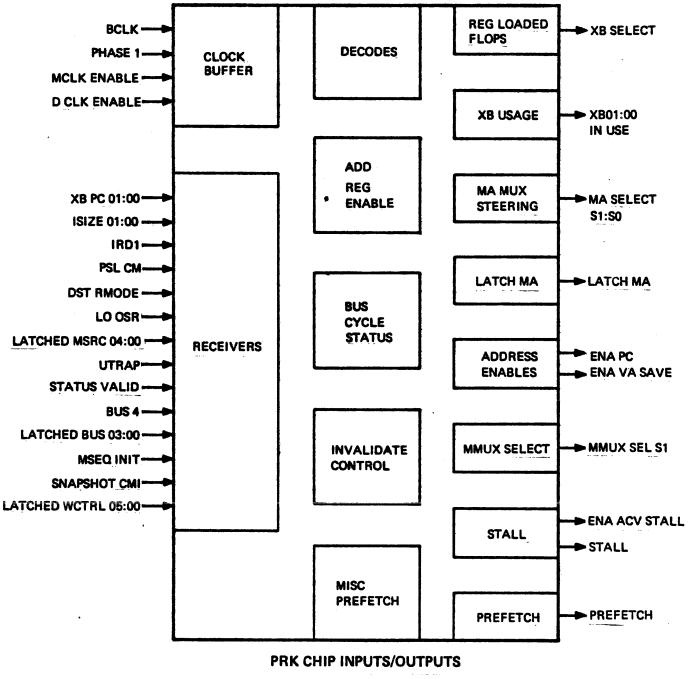

- Prefetch Control (PRK) chip Prefetch 8 bytes of instruction data starting with the PC address and replace used bytes as execution progresses.

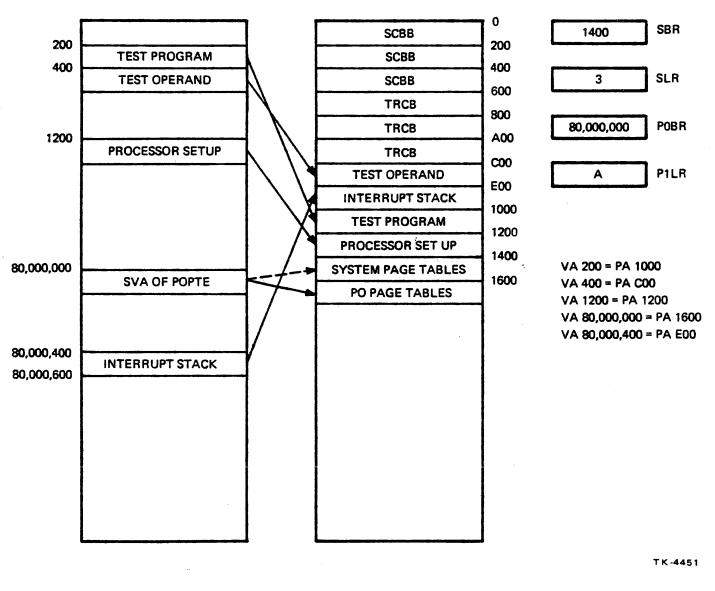

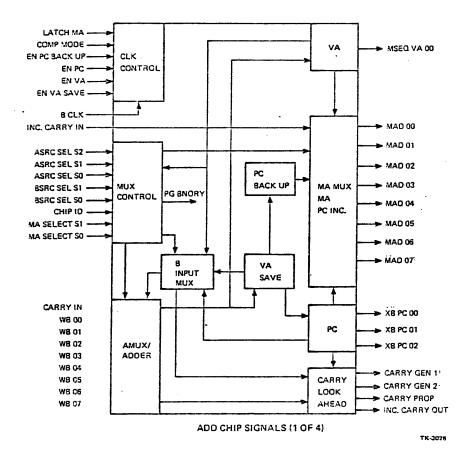

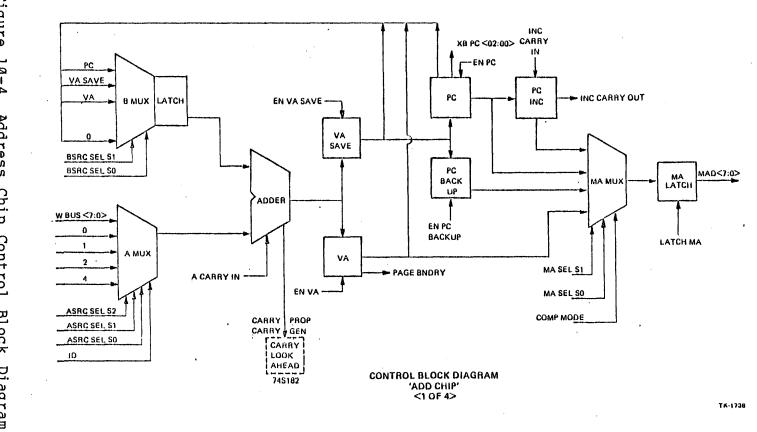

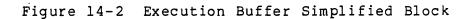

- 3) Address (ADD) chips Contain the VA, PC, PC backup and VA save circuits.

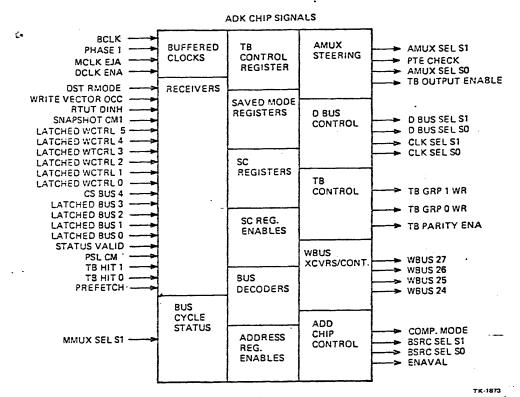

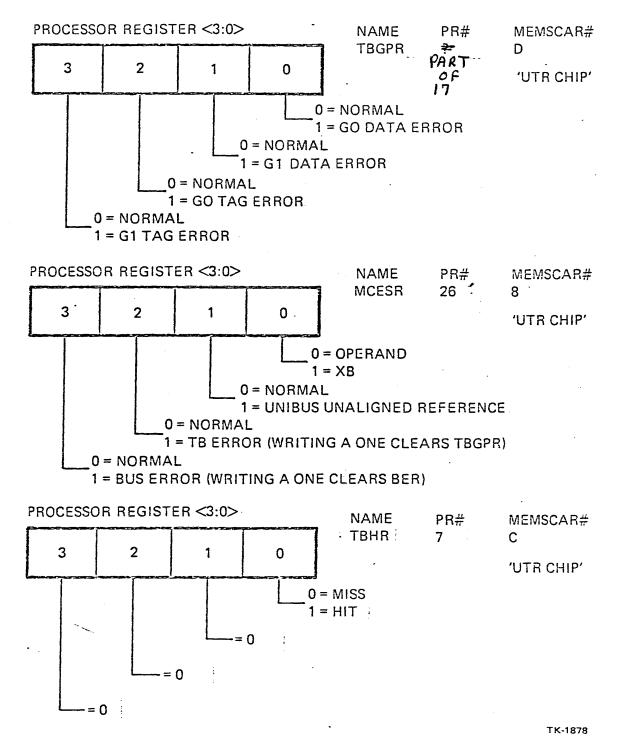

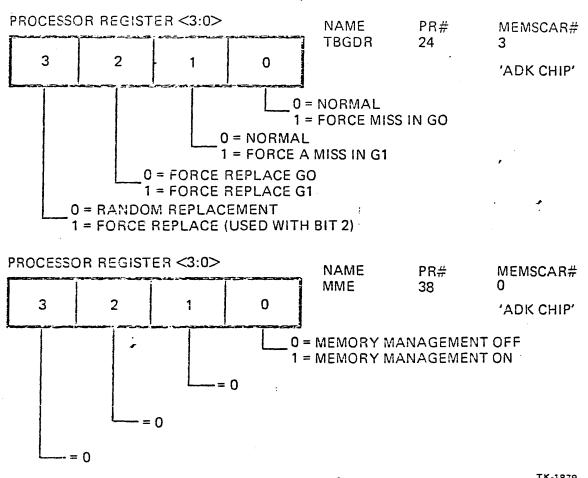

- 4) Address Control (ADK) chip Is the control for the address logic and also works in conjunction with the prefetch control and memory data regs.

4-7

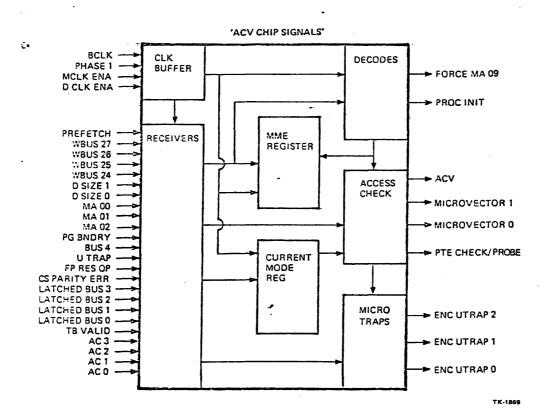

- Access Violation (ACV) chip Besides detecting access violations it monitors and detects.

- a. Control store parity errors

- b. FPA reserved operands

- c. Unaligned data, including unibus data.

- d. Crossing of page boundaries.

It then generates the appropriate Utrap signals to the Microtrap chip (UTR).

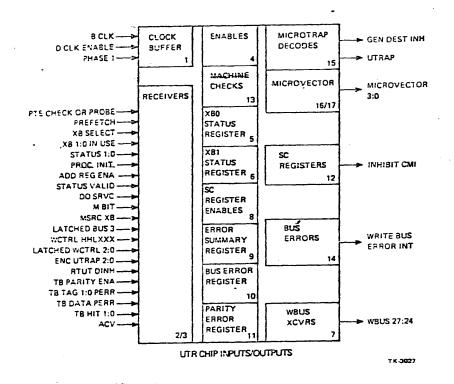

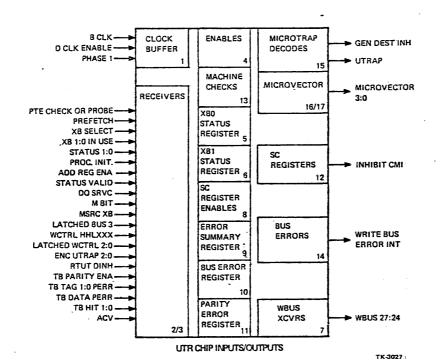

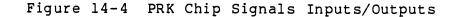

- 6) Microtrap (UTR) chip Monitors machine conditions that can cause a microtrap.

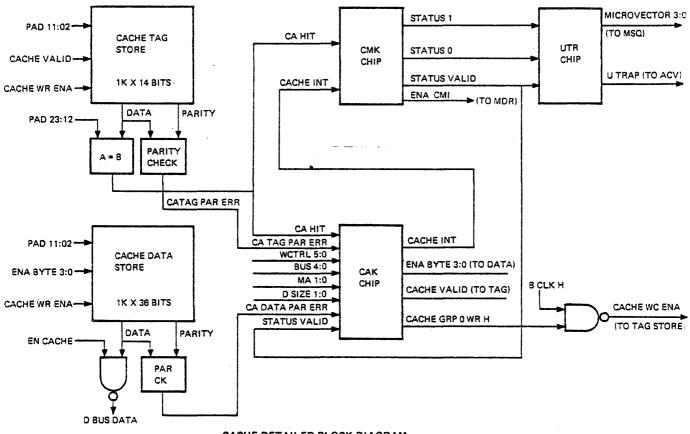

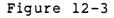

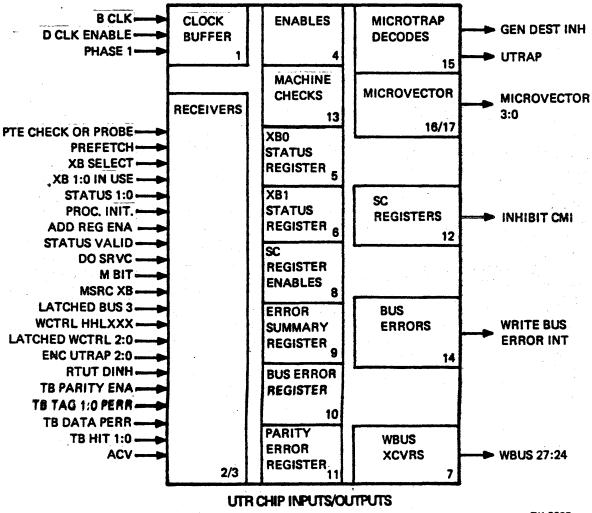

- 7) The Cache control (CAK) chip Controls the enabling and disabling of cache, controls the transfer of data to/from the MDR chips. Works in conjunction with the CMK chip to invalidate cache on CMI writes.

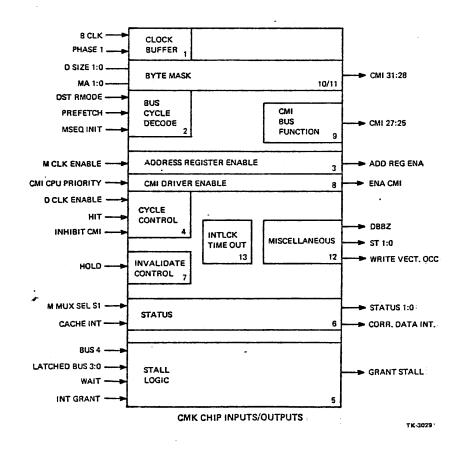

- 8) CPU Memory Interconnect Control (CMK) -Monitors and transmits control signals to/from the CMI bus. (Busy and HOLD.) Stalls the microcode for certain conditions.

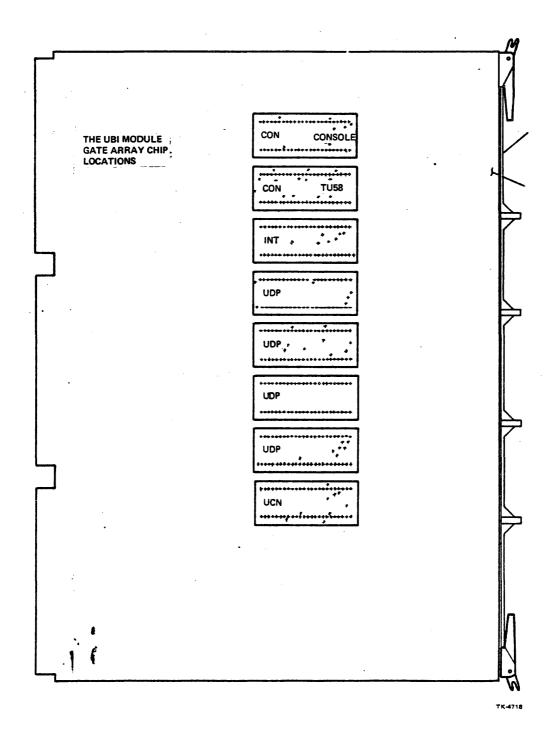

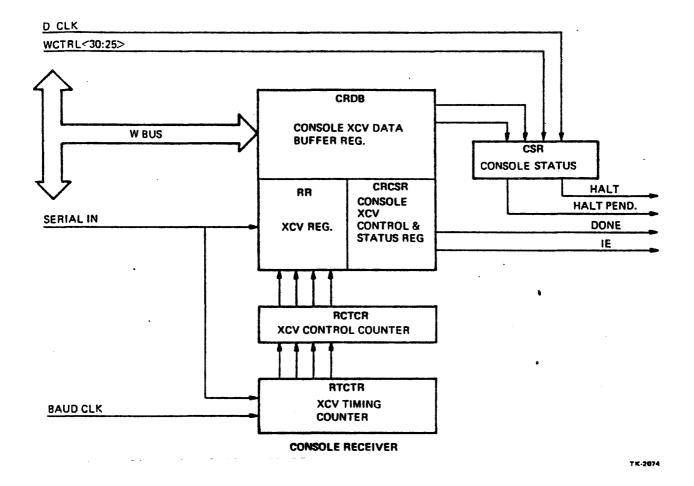

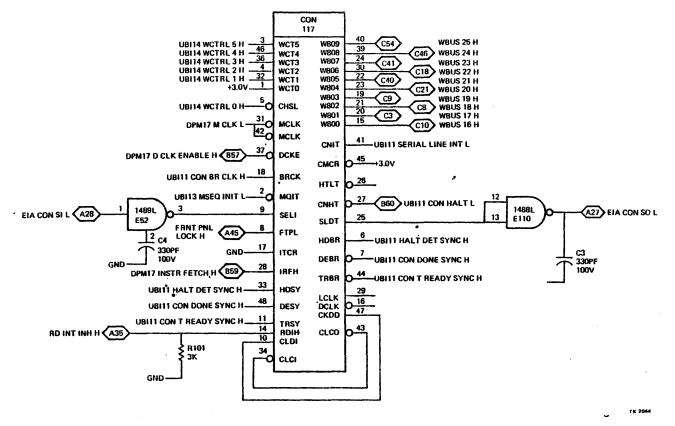

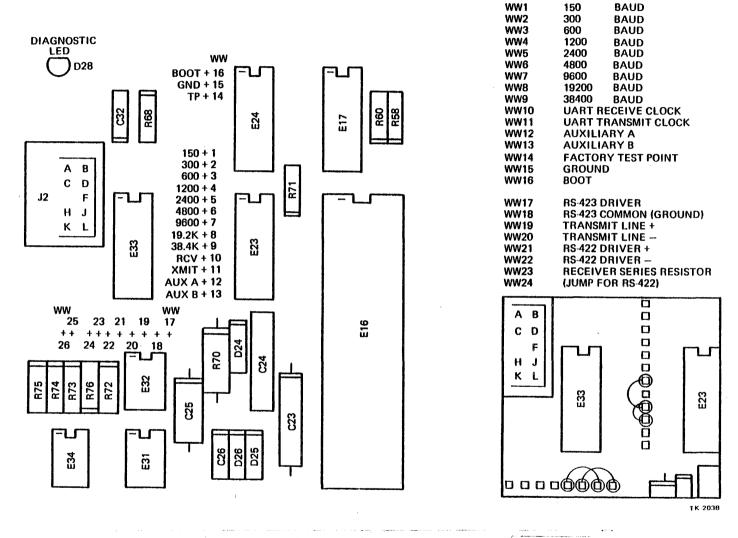

- 4. Unibus Interface Module (UBI) 8 Gate Arrays

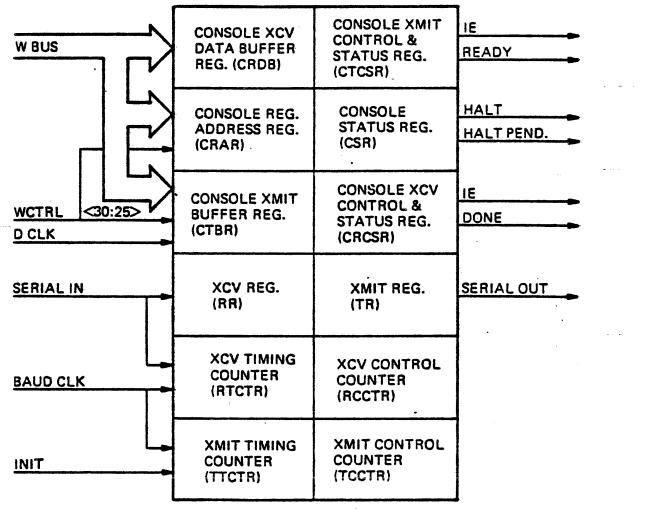

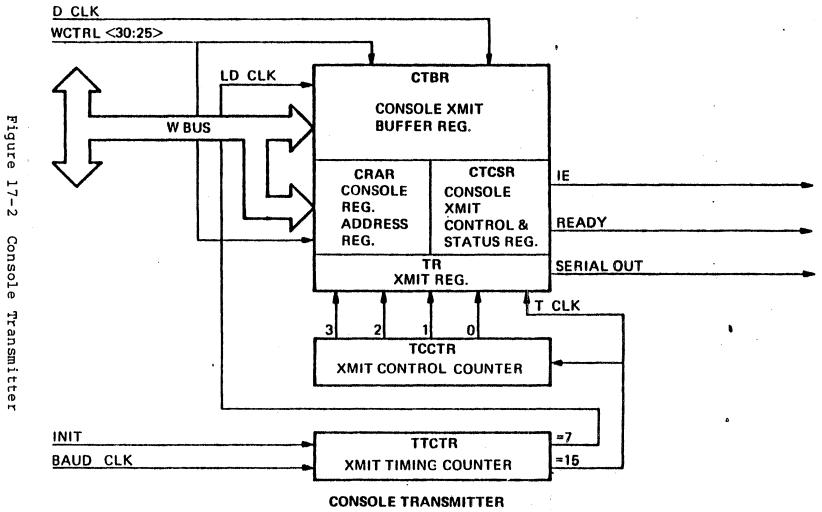

- a. 1. The TU58 Interface consists of a Gate Array Chip (CON) and some associated logic that allows communication between the CPU.

- 2. The console Interface consists of a Gate Array chip (CON) and some associated logic that enables communication between the CPU and its console.

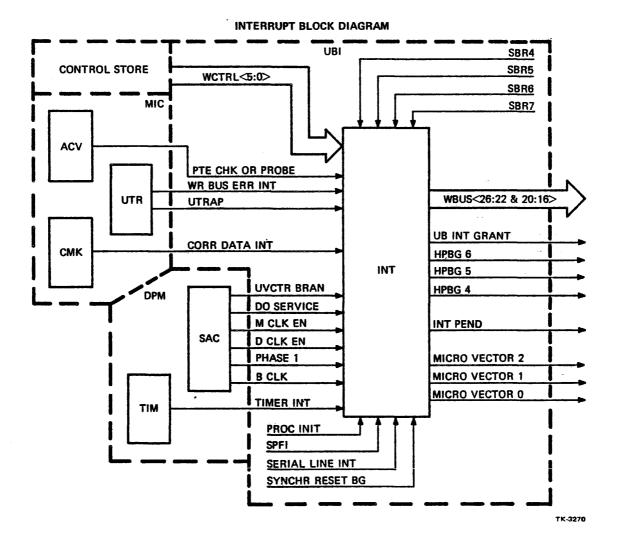

- 3. The interrupts circuit consists of a Gate Array chip (INT) and some associated logic that enable the handling of interrupts.

- 4. The Unibus interface consists of five (5) Gate Array chips, a ROM and Unibus Map.

- a. The Unibus Data Path (UDP) chips make up the data path for the unibus interface, four (4) ea.

- 1) Areas that represent UDP Chips.

- a. 3 buffered data paths for data and addresses

- b. l direct data path for data and addresses

- c. Byte swapping and rotating circuits to align data

- b. The Unibus Data Path Control Controls UDC chips and Microcode (UCN) chip.

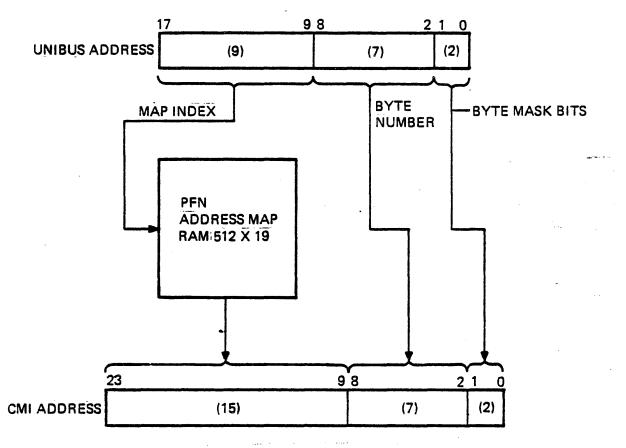

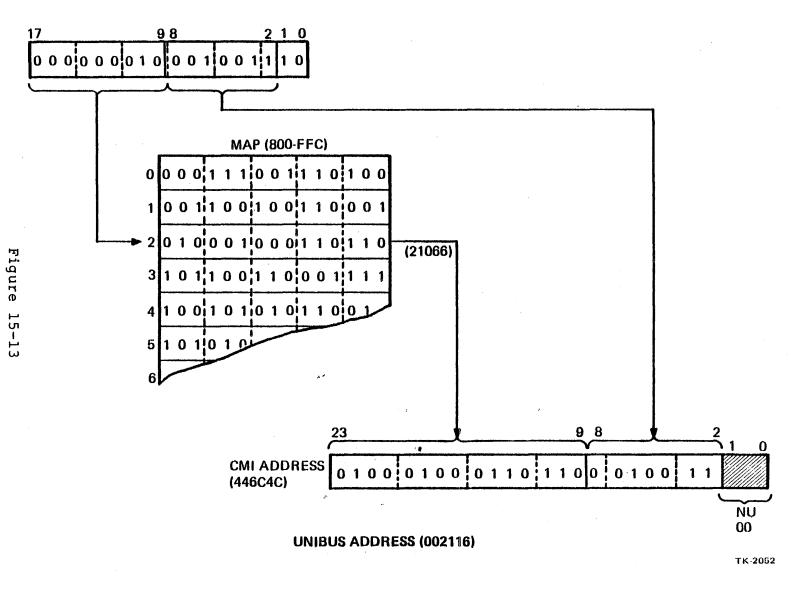

- c. Unibus map for translating Unibus addresses to CMI addresses.

- d. ROM for controlling UBI functions independent of CPU. (Note circles controlling UDP Chips are fields from ROM.)

TK-4711

Figure 4-1 DPM Gate Array Locations

Figure 4-2 MIC Gate Array Locations

Figure 4-3 UBI Gate Array Locations

TK-4710

Figure 4-4 CCS Module

Figure 4-5 Memory Controller

# VAX-11/750 LEVEL II

Programming

ς.

Student Guide

Course produced by Educational Services Department of Digital Equipment Corporation

### OUTLINE

### V. PROGRAMMING

- A. VAX Instruction Set

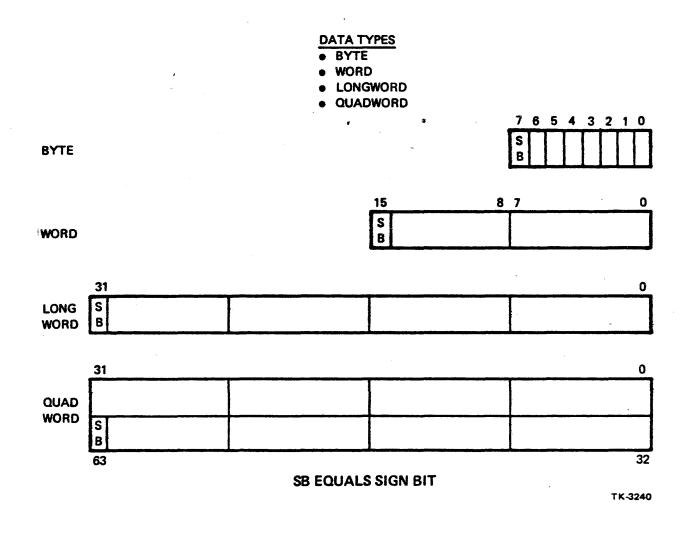

- 1. Operand and Instruction Formats

- 2. VAX Addressing Modes

- 3. VAX Integer and Logical Instructions

- 4. VAX Branching Instructions

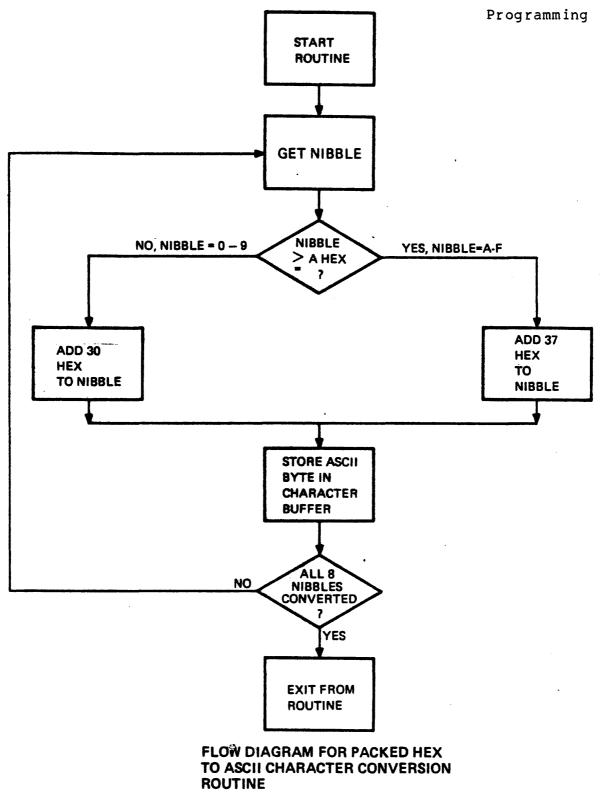

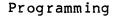

### B. Laboratory Exercise 3

Write a routine to convert packed hex data to an ASCII string utilizing VAX 11 Programming Tools

- C. VAX Instruction Set

- 1. VAX Floating-Point Instructions

- 2. VAX Subroutine and Procedure Calling Instructions

- D. Laboratory Exercise 4

Modify routine written in previous lab to be called as a procedure utilizing a CALLS or CALLG instruction

- E. VAX Instruction Set

- 1. VAX Character String, Packed Decimal and Field Instructions

- 2. VAX Privileged Instructions

- 3. Programming Examples

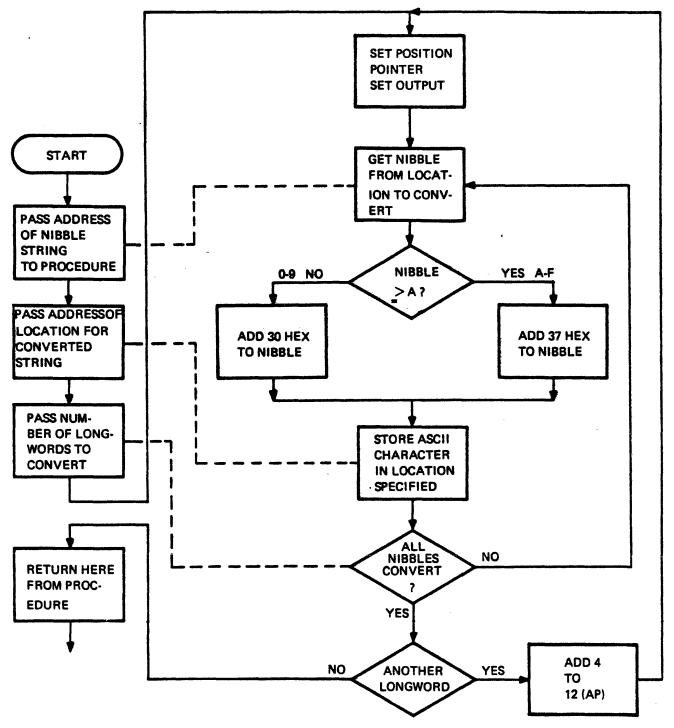

- F. Laboratory Exercise 5 Write a standalone program for the Comet CPU to communicate between the local console and a terminal on the Unibus

G. Summary

#### OBJECTIVES

Utilizing the VAX-11/780 Programming card, Architecture handbook and any class notes, write two (2) programs that perform the following:

- a) Packed hex to ASCII conversion

- b) 2 way communication between CPU Console and a terminal on the Unibus.

Load and execute the previously written programs and the instructor will verify operation.

#### SAMPLE TEST ITEM

Using the Comet system, load and execute the two (2) programs previously written in class. The instructor will verify proper operation by witnessing program execution.

#### LAB EXERCISE

- a) Utilizing the VAX program development tools, write a packed hex to ASCII conversion routine in VAX-11 Macrocode.

- b) Again, utilizing the same VAX programming tools, write a standalone program to communicate between the console terminal and a Unibus terminal and copy it on to a TU58 tape cartridge for console loading.

#### RESOURCES

VAX-11/780 Architecture Handbook VAX-11/780 Software Handbook Terminals and Communications Handbook Program Development Listing

Figure 5-1

#### DATA TYPES . • FLOATING DOUBLE FLOATING FLOATING 31 16 15 14 76 0 S B FRACTION EXPONENT 3 FRACTION DOUBLE FLOATING 31 16 15 14 76 0 S FRACTION EXPONENT FRACTION B FRACTION FRACTION

63

.

48 47

TK-3241

32

|                                      |         |   |   |   |   |   |   |   |    | _   |

|--------------------------------------|---------|---|---|---|---|---|---|---|----|-----|

| ARRAY::                              | 31      | Ö | 0 | 1 | 1 | 2 | 2 | 3 | 3  | 0   |

| +4                                   | 63      | 4 | 4 | 5 | 5 | 6 | 6 | 7 | 7  | 32  |

| +8                                   | 95      | 8 | 8 | 9 | 9 | А | A | в | В  | 64  |

| +c                                   | 127     | С | С | D | D | E | E | F | F  | 96  |

| AFTER EXECUTION                      |         |   |   |   |   |   |   |   | •  |     |

| EXTZV#48,#8, ARF                     | RAY, RO | 0 | 0 | 0 | 0 | 0 | 0 | 5 | 5  | RO  |

|                                      |         |   |   |   |   |   |   |   |    | -   |

| EXTV#64,#8, ARR                      | F       | F | F | F | F | F | в | В | R1 |     |

|                                      | ·       |   |   |   |   |   |   |   |    | •   |

|                                      |         |   | _ |   |   | N | Z | V | С  | _   |

| CMPV#48,#, ARRA<br>BEQL 1\$          | Y, R0   | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0  | PSW |

|                                      |         |   |   |   |   |   |   |   |    | -   |

| FFC, #0, #8, ARRA                    | Y, R2   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 2  | R2  |

| FIELD INSTRUCTION EXECUTION EXAMPLES |         |   |   |   |   |   |   |   |    |     |

TK-3238

Figure 5-3

٠

.

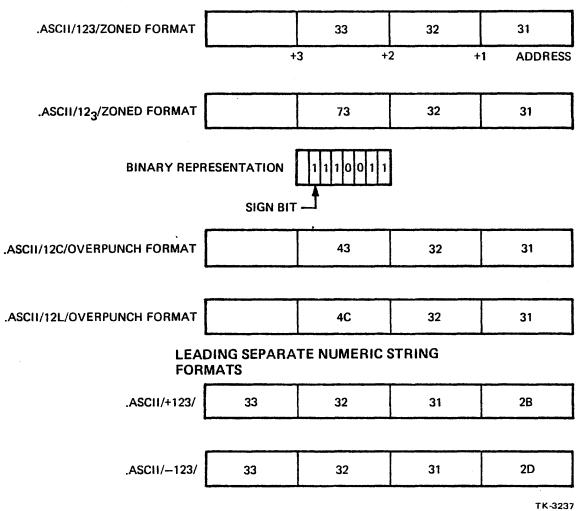

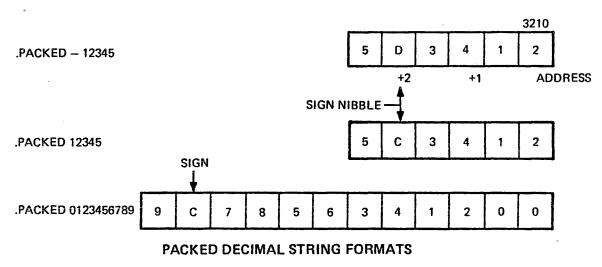

# **REPRESENTATIONS OF + AND – 123 CHARACTER STRINGS TRAILING NUMERIC**

Figure 5-4

TK-3239

Figure 5-5

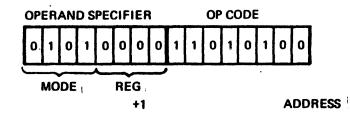

SINGLE OPERAND

Programming

Figure

5-6

ASSEMBLER

CLRL RO

D

.

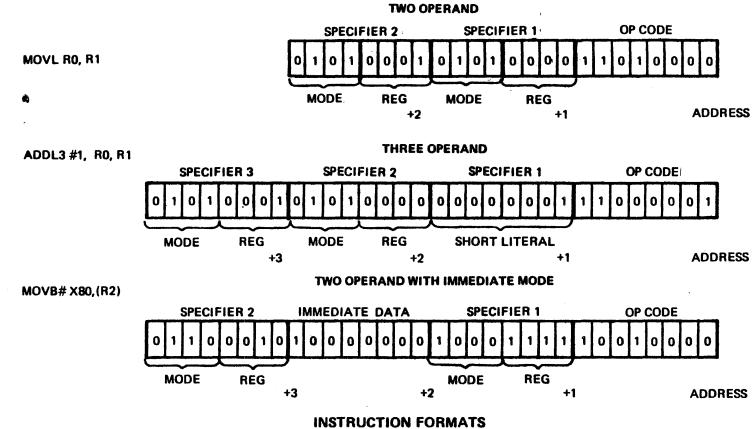

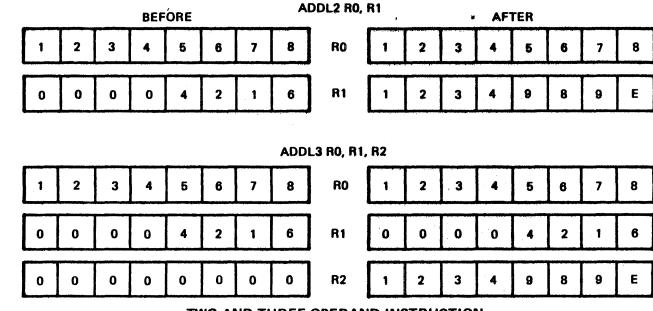

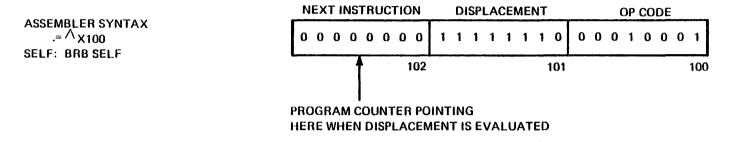

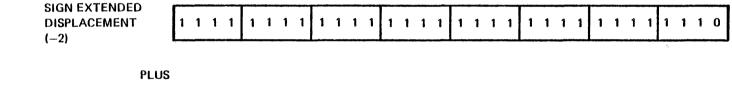

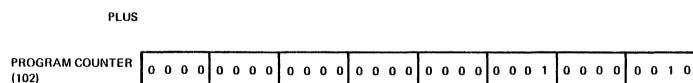

TWO AND THREE OPERAND INSTRUCTION EXECUTION IN REGISTER MODE

.

TK-3242

Figure

5-7

Programming

TK-3225

Programming

Figure

J

00

TK-4458

Figure 5-10

.

тк-3224

5-1

4

Figure 5-13

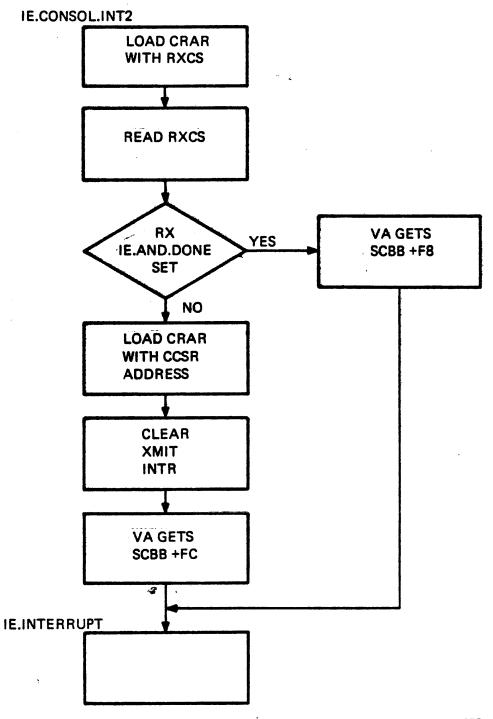

TK-4456

5-16

Figure 5-15

Programming

Programming

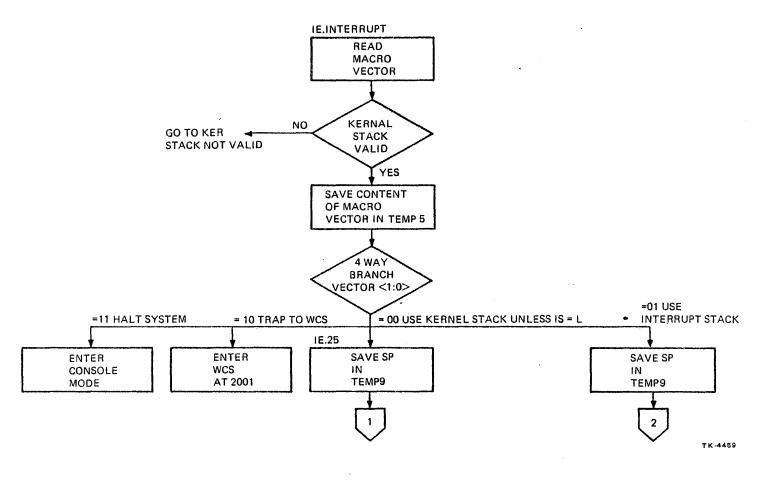

5-1 7A

.

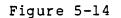

Figure 5-16

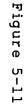

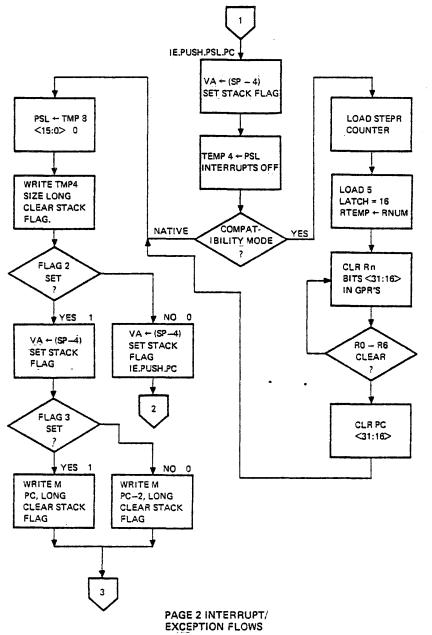

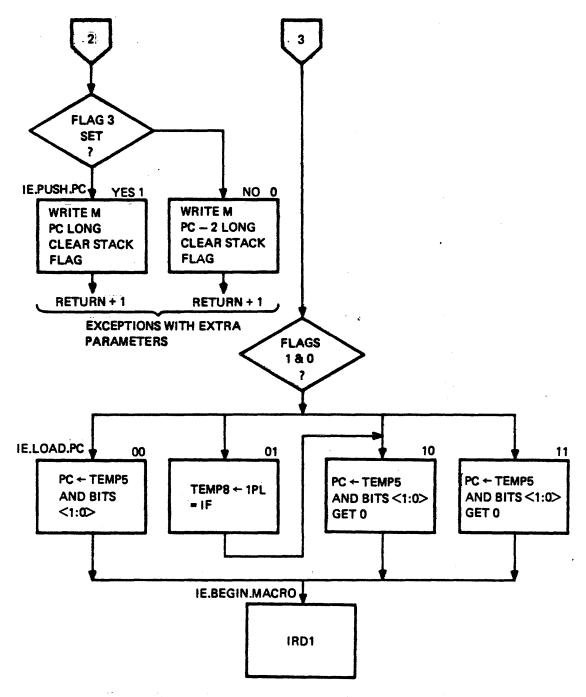

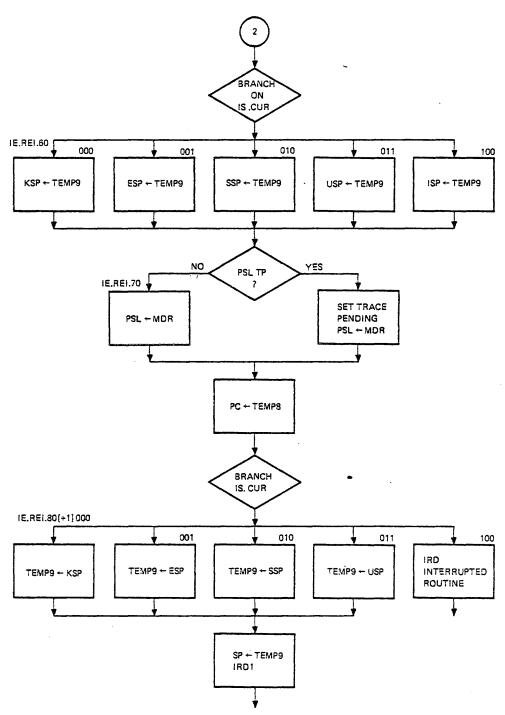

# PAGE 3 GENERALIZED INTERRUPT/ EXCEPTION FLOWS

.

.

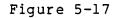

Figure 5-18

Figure 5-19

## FLOW DIAGRAM FOR PACKED HEX TO ASCII CHARACTER CONVERSION PROCEDURE

Figure 5-20

Figure 5-21

TK-3226

5-24

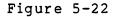

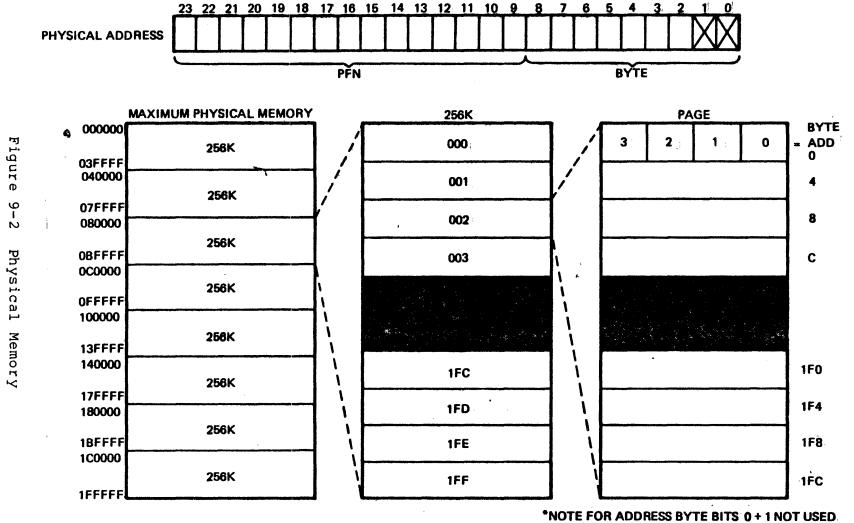

COMET PHYSICAL MEMORY ORGANIZATION

TK-1735

## Figure 5-23

5-25

|       |                                | MSB<br>15           | 14                | 13                | 12                     | 11              | 10                        | 09                      | BYT<br>High<br>08       |                                | 06                      | 05                      | 04                      | 03                               | 02                       | 01                       | L\$B<br>00               |

|-------|--------------------------------|---------------------|-------------------|-------------------|------------------------|-----------------|---------------------------|-------------------------|-------------------------|--------------------------------|-------------------------|-------------------------|-------------------------|----------------------------------|--------------------------|--------------------------|--------------------------|

| DR0   | CONTROL<br>& STATUS<br>(CSR)   | RO                  | RW                | <u>RO</u><br>SA   | <u>RW</u>              | 101 Cost        | RO<br>TLINE<br>C          | <u>RO</u><br>TLINE<br>B | <u>RO</u><br>TLINE<br>A | RO<br>RDONE                    | FINE STATES             | rw.<br>Mise             | <u>RW</u><br>CLR        | <u>RW</u><br>MAINT               | 1.02-50                  | 102 NOT                  | Lon Cost                 |

| DR2-  | RECEIVER<br>BUFFER<br>(RBUF)   | RO<br>DATA<br>VALID | RO<br>OVRN        | RO<br>FRAM<br>ERR | RO<br>PAR<br>ERR       | 102 NOV         | RO<br>RX<br>LINE<br>C     | RO<br>RX<br>LINE<br>B   | RO<br>RX<br>LINE<br>A   | RO<br>RBUF<br>D7               | RO<br>RBUF<br>D6        | RO.<br>RBUF<br>D5       | RO<br>RBUF<br>D4        | RO<br>RBUF<br>D3                 | RO<br>RBUF<br>D2         | RO<br>RBUF<br>D1         | RO<br>RBUF<br>D0         |

|       | LINE<br>PARAMETER<br>(LPR)     | LOT UCT             | 102<br>102<br>102 |                   | NC X<br>RX<br>RX<br>RX | WO<br>Fred<br>G | WQ<br>T T T<br>FAEQ<br>IS | WO<br>FRED<br>Ø         | WO<br>FREQ<br>A         | WO<br>ODD<br>PAR               | WO<br>PAR<br>ENAB       | WO<br>STOP<br>CODE      | NO<br>CHAR<br>LGTH      | WO<br>SCHAR<br>LOTH              | WO<br>LINE<br>C          | WO<br>LINE<br>B          | WO<br>LINE<br>A          |

| DR4 { | TRANSMIT *<br>CONTROL<br>(TCR) | RW<br>DTR<br>7      | RW<br>DTR<br>6    | RW<br>DTR<br>5    | RW<br>DTR<br>4         | RW<br>DTR<br>3  | RW<br>DTR<br>2            | RW<br>DTR<br>1          | <u>RW</u><br>DTR<br>0   | <u>RW</u><br>LINE<br>ENAB<br>7 | RW<br>LINE<br>ENAB<br>6 | RW<br>LINE<br>ENAB<br>5 | RW<br>LINE<br>ENAB<br>4 | _ <u>RW</u><br>LINE<br>ENAB<br>3 | _RW<br>LINE<br>ENAB<br>2 | _RW<br>LINE<br>ENAB<br>1 | RW.<br>LINE<br>ENAB<br>O |

| DR6   | MODEM *<br>STATUS<br>(MSR)     | RO<br>CO<br>7       | RO<br>CO<br>6     | RO<br>CO<br>5     | RO<br>CO<br>4          | RO<br>CO<br>3   | <u>RO</u><br>CO<br>2      | RO<br>CO<br>1           | RO<br>CO<br>0           | RO<br>RI 7                     | RO<br>RI 6              | RO<br>RI 5              | RO<br>RI 4              | RO<br>RI 3                       | RO<br>RI 2               | RO<br>Ri 1               | RO<br>RI 0               |

|       | TRANSMIT<br>DATA<br>(TDR)      | WO<br>BRK<br>7      | WO<br>BRK<br>6    | WO<br>BתK<br>5    | WO<br>BRK<br>4         | WO<br>BRK<br>3  | WO<br>BRK<br>2            | WO<br>BRK<br>1          | WO<br>BRK<br>O          | WO<br>TBUF<br>7                | WO<br>TBUF<br>6         | WO<br>TBUF<br>5         | WO<br>TBUF<br>4         | WO<br>TBUF<br>3                  | WO<br>TBUF<br>2          | WO<br>TBUF<br>1          | WO<br>TBUF<br>0          |

"The high byte of the TCR (Data Terminal Ready) and the MSR are not used with the 20 mA options.

.

.

Figure 5-24

5-26

Programming

# Programming

Figure 5-26

Programming

٠

٠

Figure 5-27

| 00 | KSP | KERNEL STACK POINTER     |

|----|-----|--------------------------|

| 01 | ESP | EXECUTIVE STACK POINTER  |

| 02 | SSP | SUPERVISOR STACK POINTER |

| 03 | USP | USER STACK POINTER       |

| 04 | ISP | INTERRUPT STACK POINTER  |

| 31 |                                 | 00 |

|----|---------------------------------|----|

|    | VIRTUAL ADDRESS OF TOP OF STACK |    |

08 POBR PO BASE REGISTER

RESERVED OPERAND FAULT IF VLA < 2\*\*31

0A P1BR PI BASE REGISTER RESERVED OPERAND FAULT IF VLA < 2\*\*31 - 2\*\*21

| 31                       | 02 01 00 |

|--------------------------|----------|

| VIRTUAL LONGWORD ADDRESS | MBZ      |

- 09 POLR PO LENGTH REGISTER LENGTH OF POPT IN LONGWORDS

- OB P1LR PI LENGTH REGISTER 2\*\*21 - LENGTH OF P1PT IN LONGWORDS

- OD SLP SYSTEM LENGTH REGISTER LENGTH OF SPT IN LONGWORDS RESERVED OPERAND FAULT IF MBZ =0

| <u>31 22</u> | 21 00               |

|--------------|---------------------|

| MBZ          | LENGTH IN LONGWORDS |

TK-1750

#### HEX NAME

10 PCBB

| PROCESS CONTROL BLOCK BASE              |

|-----------------------------------------|

| RESERVED OPERAND FAULT IF MBZ $\neq$ 0. |

| 31 30 29                                |

| 31 30 29 |                                  | 02 01 00 |

|----------|----------------------------------|----------|

| MBZ      | PHYSICAL LONGWORD ADDRESS OF PCB | MBZ      |

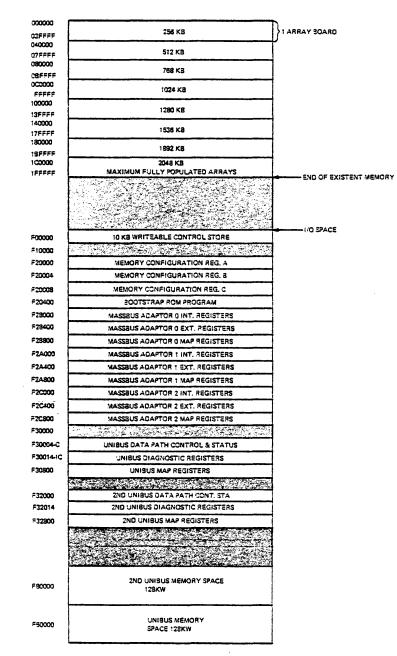

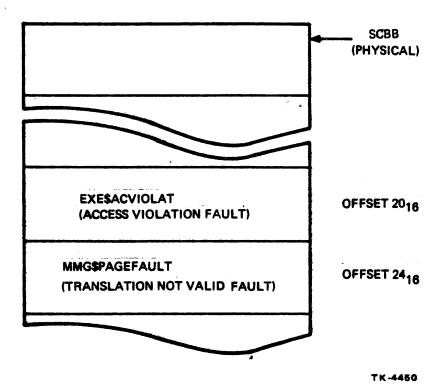

#### 11 SCBB

# SYSTEM CONTROL BLOCK BASE

RESERVED OPERAND FAULT IF MBZ  $\neq$  0.

| 31 30 29 |                              | 02 01 00 |

|----------|------------------------------|----------|

| MBZ      | PHYSICAL PAGE ADDRESS OF SCB | MBZ      |

## 12 IPLR INTERRUPT PRIORITY LEVEL REGISTER

| 31  | 05 04 | 00       |

|-----|-------|----------|

| MBZ | PS    | L<20:16> |

13 ASTR

#### AST LEVEL REGISTER

RESERVED OPERAND FAULT IF NOT VALID I.E., MBZ  $\neq$  0.

| 31  | 03 02 | 00  |

|-----|-------|-----|

| MBZ | AST   | LVL |

OC SBR

#### SYSTEM BASE REGISTER

RESERVED OPERAND FAULT IF MBZ  $\neq$  0.

| 31 30 | 29 02                     | 01 00 |  |

|-------|---------------------------|-------|--|

| MBZ   | PHYSICAL LONGWORD ADDRESS | MBZ   |  |

TK-1753

Programming

•.

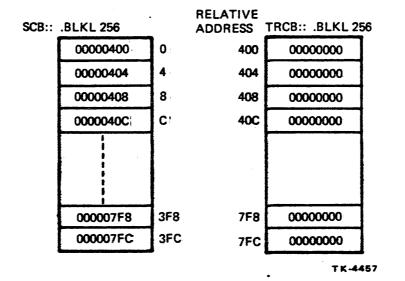

INTERVAL TIMER PROCESSOR REGISTERS

Figure 5-30

| 1B | TODR | TIME OF DAY REGISTER                                                        |       | 00   |

|----|------|-----------------------------------------------------------------------------|-------|------|

|    |      | TIME OF DAY (10 MILLISECOND INCREMENTS)                                     |       |      |

| 14 | SIRR | SOFTWARE INTERRUPT REQUEST REGISTER<br>RESERVED OPERAND FAULT IF READ<br>31 | 04 03 | 00   |

|    |      | MBZ                                                                         | SI    | RL   |

|    | ~    | WRITE ONLY                                                                  |       |      |

| 15 | SISR | SOFTWARE INTERRUPT SUMMARY REGISTER                                         |       | 0100 |

,

.

| MBZ   | SOFTWARE INTERRUPT REQUEST    |

|-------|-------------------------------|

| IVIBZ | F E D C B A 9 8 7 6 5 4 3 2 1 |

MBZ

TK-1752

## CONSOLE STORAGE RECEIVER STATUS

#### **CONSOLE STORAGE RECEIVER DATA**

## **RECEIVE FROM TU-58**

CONSOLE STORAGE TRANSMIT STATUS

CONSOLE STORAGE TRANSMIT DATA

31

7 6 5 4 3 2 1 0

0

TRANSMIT

0

TRANSMIT

DATA

IF

**TRANSMIT TO TU-58**

1K-1733

Programming

5-34

Figure

5-32

тк-1734

| HEX | NAME |                                 |    |       |        |       |

|-----|------|---------------------------------|----|-------|--------|-------|

| 20  | RXCS | CONSOLE RECEIVE CONTROL/STATUS  |    |       |        |       |

|     |      | 31                              | 08 | 07060 | 5      | 00    |

|     |      | MBZ                             |    | IE    | MBZ    |       |

|     |      |                                 | D  | ONE   | 5      |       |

| 21  | RXDB | CONSOLE RECEIVE DATA BUFFER     |    |       |        |       |

|     |      | 31                              | 08 | 07    |        | 00    |

|     |      |                                 |    |       | BYTE 0 |       |

|     |      | READ ONLY                       |    |       |        |       |

| 22  | тхсѕ | CONSOLE TRANSMIT CONTROL/STATUS |    |       |        |       |

|     |      | 31                              | 08 | 07060 | 5      | 00    |

|     |      | MBZ                             |    | IE    | MBZ    |       |

|     |      |                                 | RE | ADY   |        |       |

| 23  | TXDB | CONSOLE TRANSMIT DATA BUFFER    |    |       |        |       |

|     |      | 31                              | 08 | 07    |        | 00    |

|     |      |                                 |    |       | BYTE O |       |

|     |      | WRITE ONLY                      |    |       |        |       |

|     |      |                                 |    |       | тк     | -1749 |

.

.

| HEX NAME ID# |                                                                                   |       |

|--------------|-----------------------------------------------------------------------------------|-------|

| 38 MME       | MEMORY MANAGEMENT ENABLE<br>WRITE 1 ALSO CAUSES MICROCODE TO INVALIDATE TB.<br>31 | 01 00 |

| 39 TBIA      | TRANSLATION BUFFER INVALIDATE ALL<br>RESERVED OPERAND FAULT IF READ<br>31         | 0     |

|              | MBZ                                                                               |       |

|              | WRITE ONLY                                                                        |       |

| 3A TBIS      | TRANSLATION BUFFER INVALIDATE SINGLE<br>RESERVED OPERAND FAULT IF READ            | 00    |

|              | VIRTUAL ADDRESS                                                                   |       |

|              | WRITE ONLY                                                                        |       |

| 3D PMR       | PERFORMANCE MONITOR REGISTER<br>RESERVED OPERAND FAULT IF >1<br>31                | 01.00 |

|              | MBZ                                                                               |       |

|              |                                                                                   | PME   |

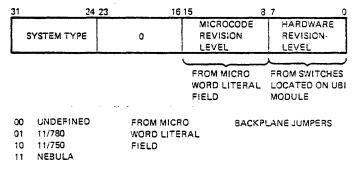

3E SID SYSTEM IDENTIFICATION (READ ONLY)

RESERVED OPERAND FAULT IF WRITE

| 31 | 24          | 23 | 16 15    |                       | 8 7                  | 0  |

|----|-------------|----|----------|-----------------------|----------------------|----|

|    | SYSTEM TYPE | 0  | 1        | MICROCODE<br>REVISION | HARDWARE<br>REVISION |    |

|    |             |    |          | LEVEL                 | LEVEL                |    |

|    |             |    | <u> </u> |                       | J                    | )  |

|    |             |    | FF       | ROM MICRO             | FROM SWITCHE         | S  |

|    |             |    | W        | ORD LITERAL           | LOCATED ON U         | BI |

|    |             |    | FI       | ELD                   | MODULE               |    |

|    |             |    |          |                       |                      |    |

тк-2099

Programming

Figure

σ L ω

თ

ω

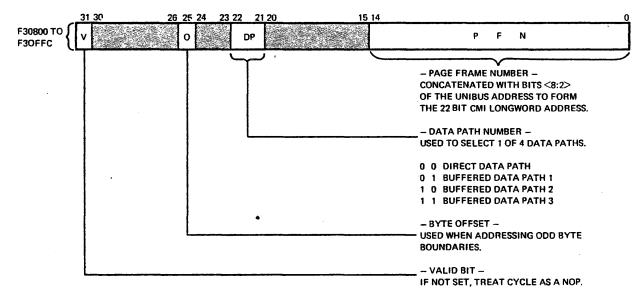

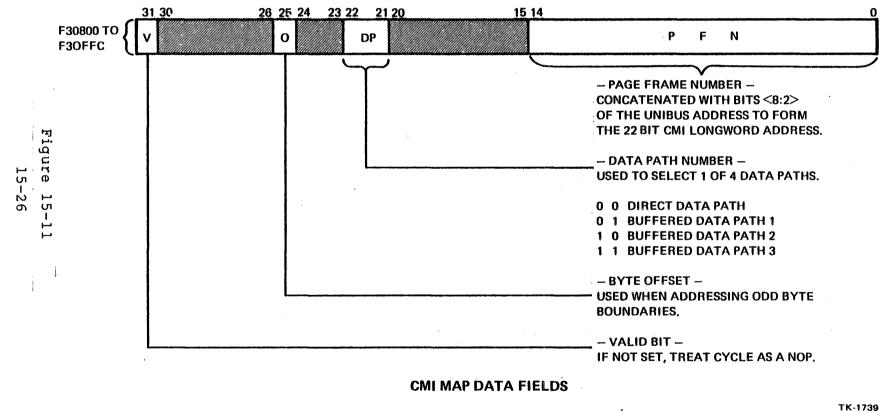

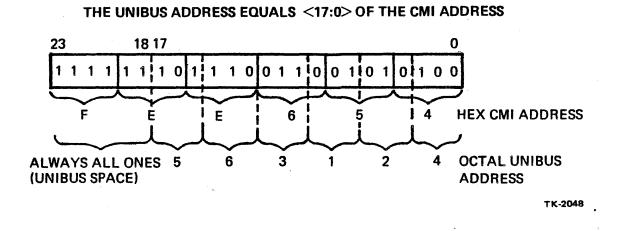

UNIBUS TO CMI MAP DATA FIELDS ADDRESS

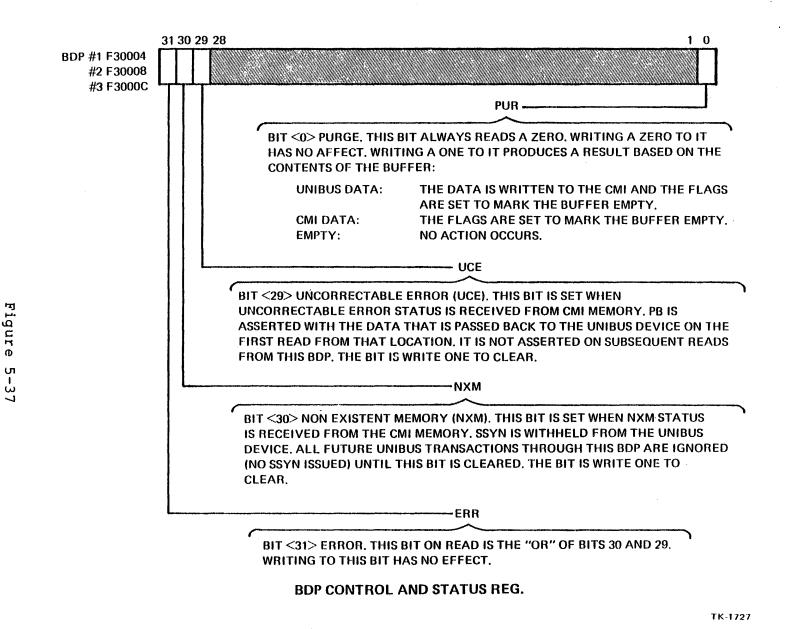

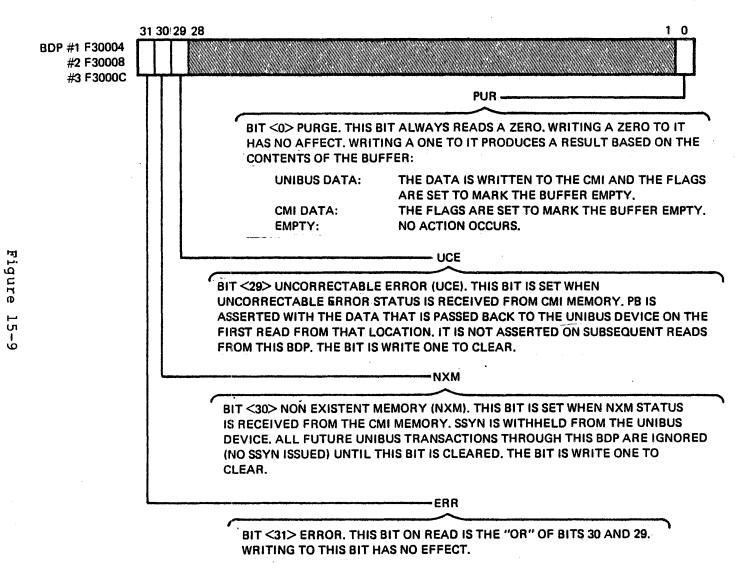

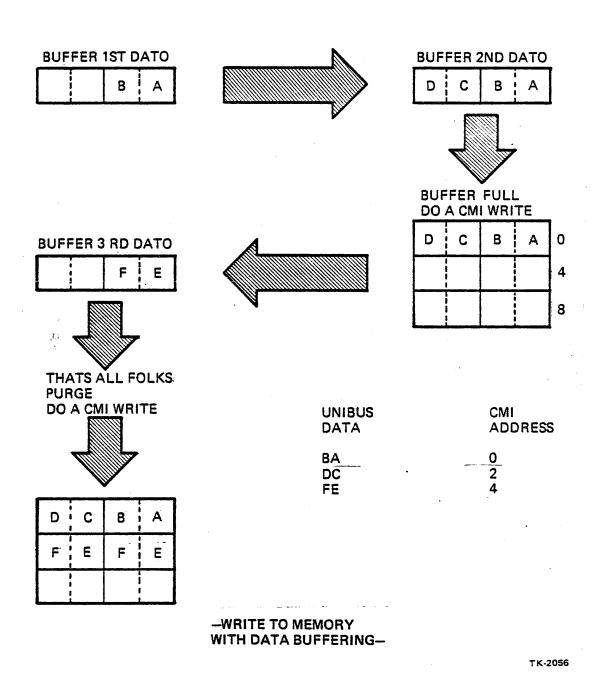

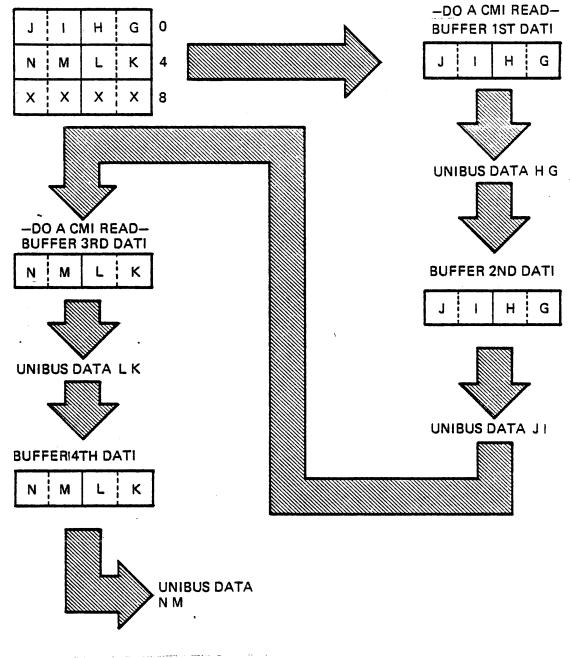

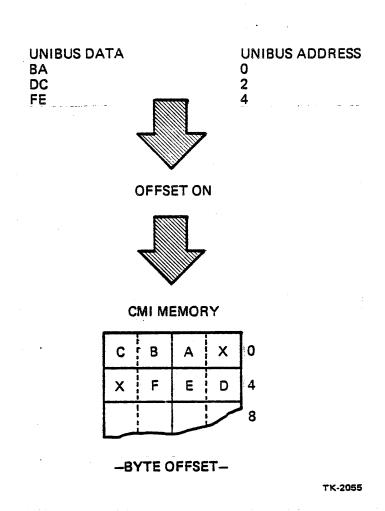

NOTE 1: THERE ARE FIVE FLAGS THAT KEEP TRACK OF THE DATA IN THE DATA BUFFER, NAMED CD AND BF3 THROUGH BF0. IF CD = 1, THEN THE BUFFER HAS FOUR BYTES OF DATA FROM THE CMI AND BF3 THROUGH BF0 ARE ALWAYS 0. IF CD = 0, THEN BF3 THROUGH BF0 INDICATE WHICH BYTES IN THE DATA BUFFER HAVE VALID UNIBUS DATA. IF THEY ARE ALL 0, THEN THE BUFFER IS CONSIDERED EMPTY.

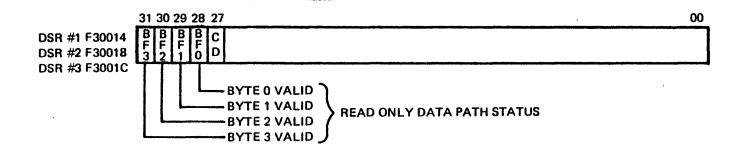

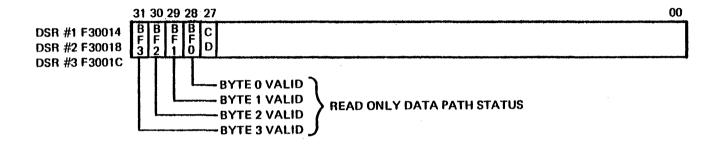

NOTE 2: THIS IS A READ ONLY REGISTER THAT ALLOWS ONE TO CHECK THE FLAG BITS ASSOCIATED WITH EACH BDP. IT IS INTENDED ONLY FOR POSSIBLE DIAGNOSTIC USE AND NO REFERENCE TO IT IS REQUIRED FOR NORMAL USE OF THE BDP'S.

**CUI DIAGNOSTIC STATUS REGISTER**

## CMI ERROR PROCESSOR REGISTER

TK-3266

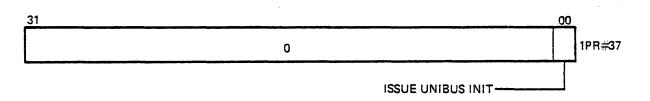

# IO RESET PROCESSOR REGISTER

| нех | NAME | ID≑ |                                                                             |       |

|-----|------|-----|-----------------------------------------------------------------------------|-------|

| 38  | MME  |     | MEMORY MANAGEMENT ENABLE<br>WRITE 1 ALSO CAUSES MICROCODE TO INVALIDATE TB. |       |

|     |      |     | 31                                                                          | 01 00 |

|     |      |     |                                                                             |       |

|     |      |     | · · ·                                                                       | MME   |

| 39  | TBIA |     | TRANSLATION BUFFER INVALIDATE ALL                                           | a.    |

|     |      |     | RESERVED OPERAND FAULT IF READ                                              |       |

|     |      |     | 31                                                                          | 00    |

|     |      |     | MBZ                                                                         |       |

WRITE ONLY

3A TBIS

TRANSLATION BUFFER INVALIDATE SINGLE RESERVED OPERAND FAULT IF READ

| 31 | 00              |   |

|----|-----------------|---|

|    | VIRTUAL ADDRESS | , |

|    | WRITE ONLY      |   |

WRITE ONL'

3D PMR

3E

PERFORMANCE MONITOR REGISTER RESERVED OPERAND FAULT IF >1

| 1 |     | 01.00 |

|---|-----|-------|

|   | MBZ |       |

|   |     |       |

|   |     | P     |

SYSTEM IDENTIFICATION (READ ONLY) SID RESERVED OPERAND FAULT IF WRITE

TK-2099

00

# VAX-11/750 LEVEL II

# Microcode

Student Guide

Course produced by Educational Services Department of Digital Equipment Corporation

Microcode

#### OBJECTIVES

Utilizing the Comet microcode listing, correctly trace a microroutine for a specific machine function, listing only the microaddresses.

Provided with a Comet microcode macro expansion and a Comet microcode listing, write each of the field values for that microinstruction.

Provided with a schematic diagram, trace the origin and destination of a specific signal within the microsequencer logic.

Given a series of true/false questions, correctly indicate as true or false statements regarding the comet microsequencer operation.

Provided with a laboratory exercise procedure, the student will

- a) load Microdiagnostics

- b) operate the remote diagnosis module

- c) trace microroutines

- d) set up and trace selected signals

#### SAMPLE TEST ITEM

Referring to the CUI module schematic, drawing number 1 of 14, locate the signal called "RCS Ø1 CS AD 13 L". Trace the origin of this signal and all of the destinations in the space below.

#### LAB EXERCISE

- a) load microdiagnostics

- b) operate the RDM Module

- c) trace microroutines

- d) set up and trace selected signals

#### RESOURCES

- 1. COMET CPU Microcode listing

- 2. DPM module schematic

- 3. LSI Chip Schematic

SAC MSQ PHB IRB

.

- 4. Wall charts

- 5. COMDEC, Microword decoding program

-

#### Microcode

#### OUTLINE

- I. INTRODUCTION TO MICROCODE

- A. Why Microcode?

- 1. Concepts

- 2. Advantages

- B. Comet CPU Microinstruction

- 1. 80 bits

- 2. Vertical functionality

- 3. Microcode/hardware relationship

- 4. Fields and functionality

- 5. How is microcode created?

- C. Summary

### II. MICROCODE LISTINGS

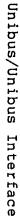

- A. Microprogrammers Code

- B. Microcode Listing/Macrocode Listing Similarities

- C. File Structure

- D. Reading the Listing

- 1. Assembler directives

- 2. Addressing constraints

- 3. Machine definitions

- 4. Macro expansions

- 5. Next address field

- 6. CREF

- E. Summary

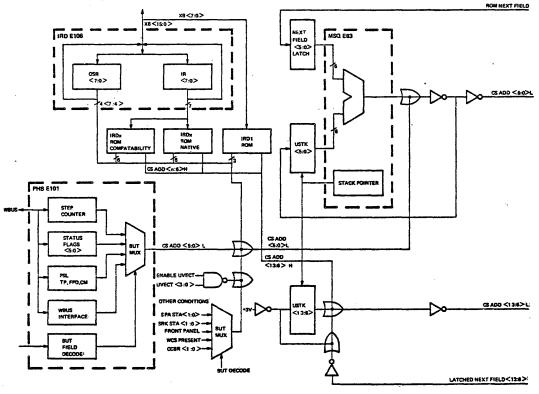

III. MICROSEQUENCER AND CONTROL STORE SUBSYSTEM

- A. Purpose

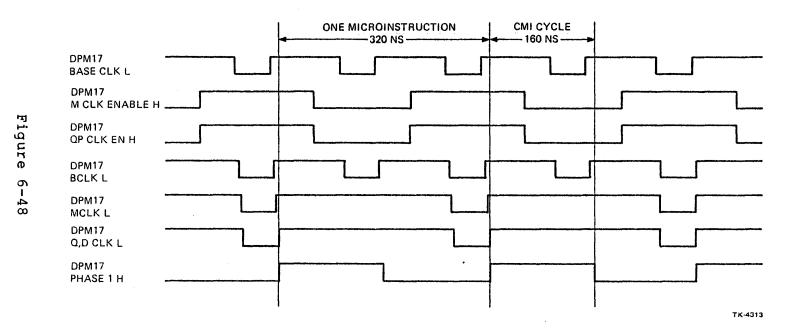

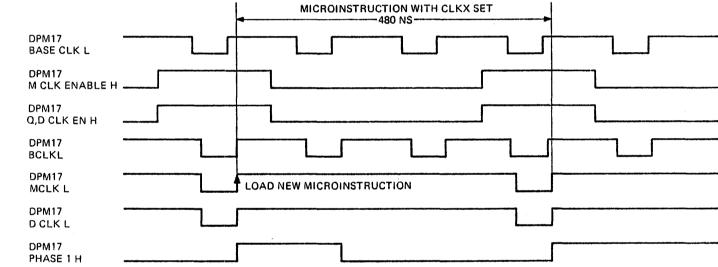

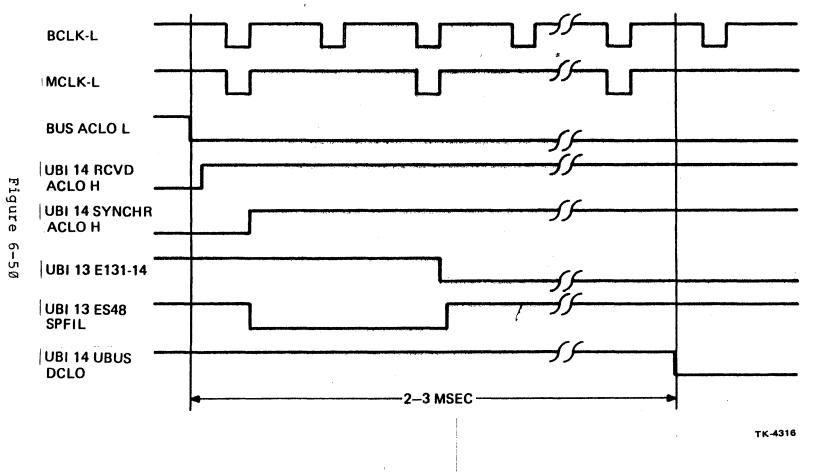

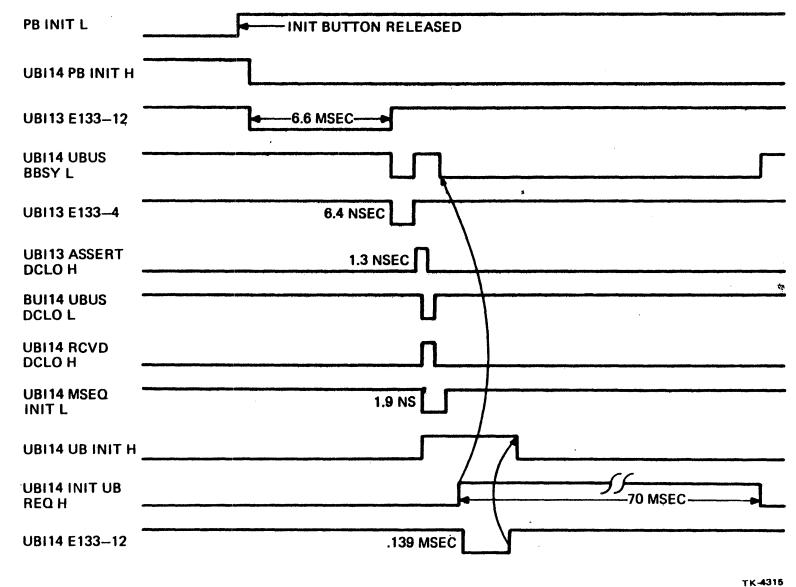

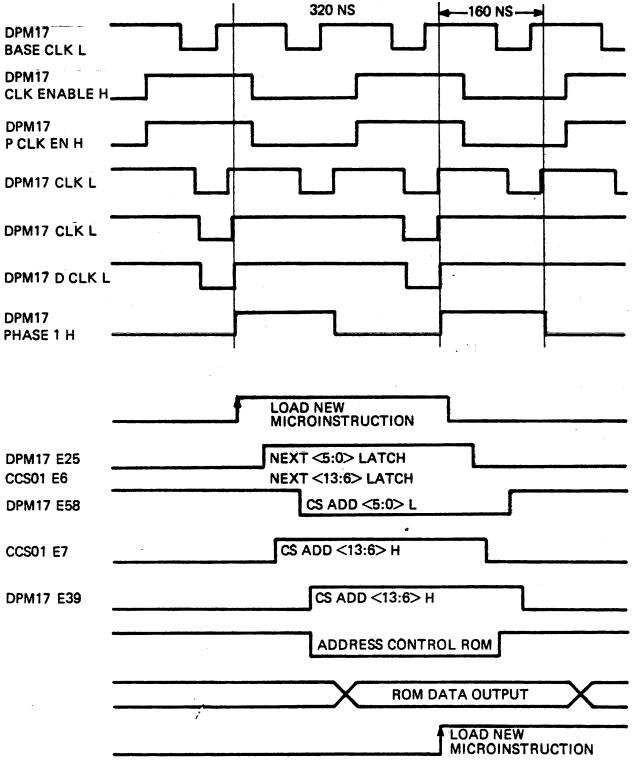

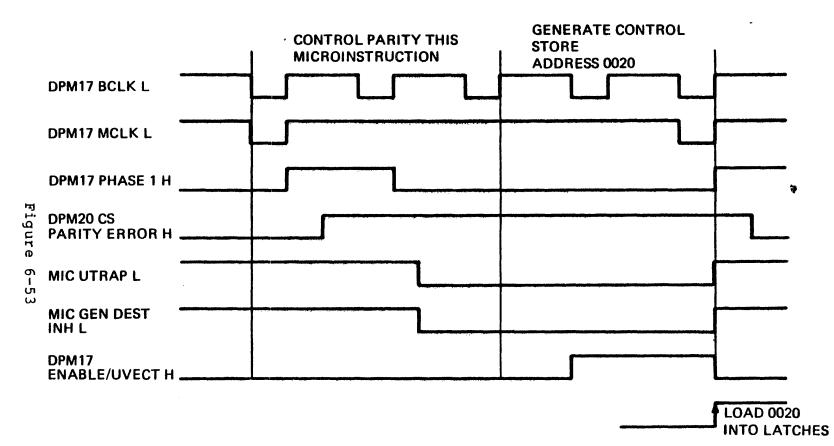

- B. Cycle Time

- C. LSI Chips

- 1. SAC

- 2. MSQ

- 3. PHB

- 4. IRD

- E. CCS Interface

- F. Block Diagram Analysis

- G. CCS Module Block Diagram Analysis

- H. Schematic Analysis

- 1. Major addressing modes

- 2. LSI chip functionality

- 3. Timing

- IV. CLASSROOM EXERCISE LOCATE AND TRACE INIT MICROROUTINE

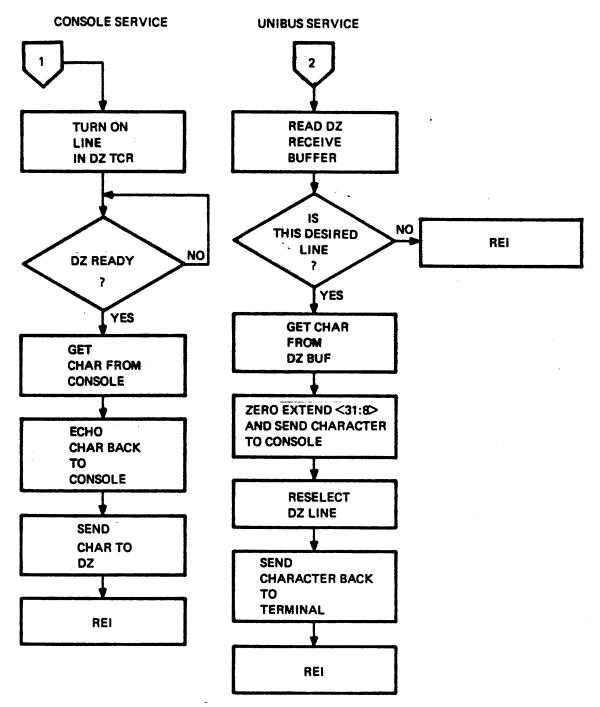

- V. CPU CONSOLE MICROCODE

- A. Console Emulator

- B. Console Interface

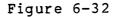

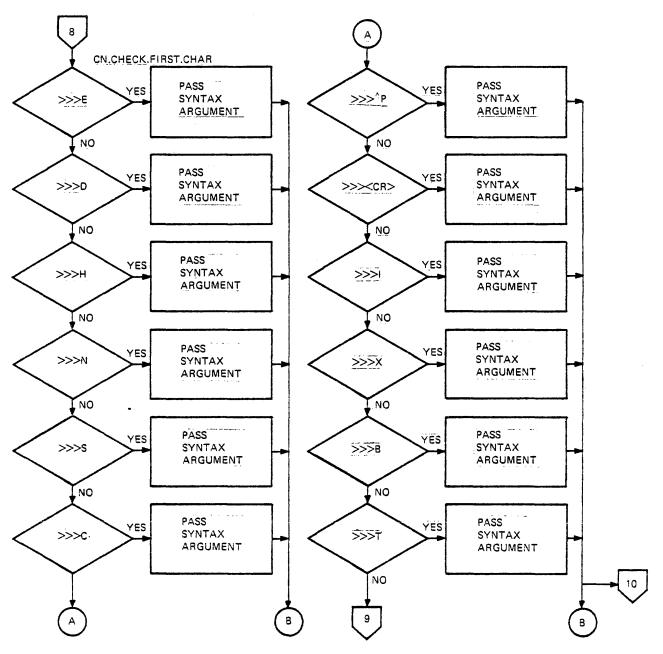

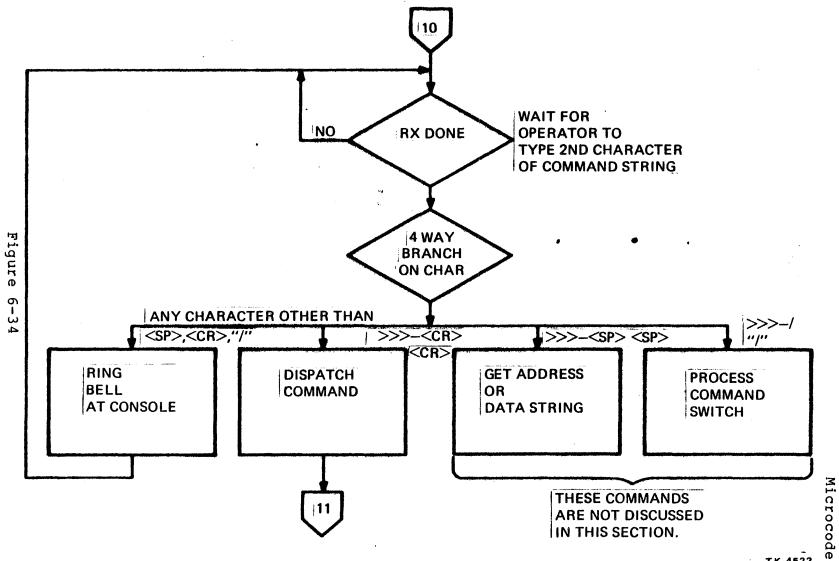

- C. Microroutines Character by Character Parse

- D. Console Functions

- E. Console Functions Flow Diagram Analysis

- VI. LABORATORY EXERCISE 6 TBS

- VII. LESSON SUMMARY

÷

- I. INTRODUCTION TO MICROCODE

- A. Why Microcode?

- 1. Basic computer designs

- a. direct hardware decode of macro instruction requires elaborate timing and hardware design

- b. microprogrammed machine architecture allows general purpose design to be customized with ROM microcode.

- Microcoding has created a demand for an individual that understands hardware and software to write microroutines

- 3. Microcode can repair design problems without changing hardware.

- Microcode updates require changing only control store ROMS.

- B. The advantages or microprogramming are clearly apparent to other hardware designs

- C. COMET CPU Microinstruction

- 1. 80 bits wide

- 2. Vertical functionality

- 3. Microcode/hardware relationship

- a. DPM module green

b. UBI module blue

c. MIC module yellow

d. WCS module red

TK-2079

.

Figure

6-1

•

## Microcode

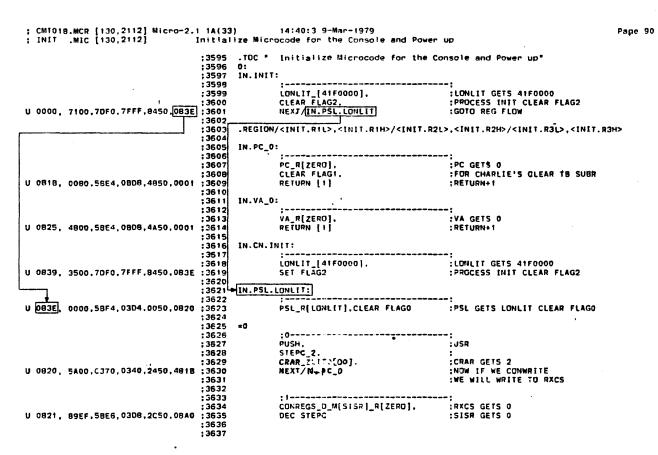

|               |          | 30,2112] Micro-2.1 14(3)                           | 3) 14:4                               | 0:3 9-Mar-1979                        | ENTIRE LISTING NAME                   | Page   | 30 |

|---------------|----------|----------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|--------|----|

| ; DEFIN       | I MIC I  | 30,2112] DEFIN.MIC                                 |                                       |                                       | SUBFILE NAME                          |        |    |

| <b></b>       | LINE 1   | IUMBER                                             | :969 .10C<br>:970 .10C<br>:971 :      |                                       |                                       |        |    |

| ŧ             |          |                                                    | ;972                                  |                                       |                                       |        |    |

| :973          | .NOBIN   | •                                                  |                                       |                                       | DO NOT LIST BINARY OUTPUT             |        |    |

| ;974          | RTOL     |                                                    |                                       |                                       | NUMBERS ARE FROM RIGHT TO LEFT FOR I  | BINARY |    |

| ;975          | .HEXADE  |                                                    |                                       |                                       | RADIX IS HEX                          |        |    |

| :976<br>:977  | .SET/NA  |                                                    |                                       |                                       |                                       |        |    |

| ;978          | .NOCREF  |                                                    | FOR CREE CNI                          | Y WHEN FULL ASSEMBL                   | VAX NATIVE INSTRUCTION MICROCODE      |        |    |

| :979          | LINDERET |                                                    |                                       |                                       | DO NOT CROSS REFERENCE FOLLOWING CO   | )DE    |    |

| 960           | . TOC -  | Revision Histor                                    | • • •                                 |                                       |                                       |        |    |

| :931          | ليتشيبنا |                                                    | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | INSERT TEXT IN TABLE OF CONTENTS      |        |    |

| :982          | ; 53     | CORRECT WIDTH OF CODE                              | Compatibility                         | ) ROM                                 |                                       |        |    |

| ;993          | :        | ACD NEW MOR_O CONFLICT                             |                                       |                                       |                                       |        |    |

| ;984          | :        | ADD NEW MSRC, VA CONFLIC                           |                                       |                                       |                                       |        |    |

| ;985          | ; 52     | CHANGE INDI ROM DEFINIT                            |                                       |                                       |                                       |        |    |

| ;986          |          | ADD MICRO ORDERS FOR OF                            |                                       |                                       |                                       |        |    |

| ;987<br>;263  |          | CHANGE IRDX ROM DEFINIT<br>DELETE 'BUT/MBUS19T018' |                                       |                                       |                                       |        |    |

| ;989          | :        | CHANGE CHODE ROM PER SN                            |                                       | .75                                   |                                       |        |    |

| :990          | : 51     | UPDATE VO23 & VO25 AND                             |                                       | TR PER BINDER 25-JA                   | N-79                                  |        |    |

| :991          | : 50     | ADD VALIDITY CHECKS FOR                            |                                       |                                       |                                       |        |    |

| :992          | ; 49     | CHANGE 'MSRC/MTEMPIT' 1                            |                                       | D' TO REFLECT ITS P                   | ROPER USE                             |        |    |

| :993          | ;        | CHANGE VALIDITY CHECKS                             | TO ALLOW 'CLR                         | TB.VA_WB' WITH 'PRB                   | .RD.PTE' WHEN NOT 'BUT/UVCTR'         |        |    |

| ;994          | ;        | CHANGE NOTATION FOR MUL                            |                                       |                                       |                                       |        |    |

| ;995          | ; 48     | DELETE 'WCTRL/VA_VAS+WE                            |                                       |                                       |                                       |        |    |

| ;996          | ;        | DELETE 'WXTRL/RDM' & 'W                            |                                       |                                       |                                       |        |    |

| :997          | •        | ADD 'WCTRL/FPA.ENABLE_W                            |                                       |                                       |                                       |        |    |

| ;998          | 1        | CORRECT DESCRIPTION OF                             |                                       |                                       |                                       |        |    |

| ;999<br>:1000 |          | ADD INFORMATION ABOUT C<br>ADD VALIDITY CHECKS TO  |                                       |                                       |                                       |        |    |

| :1001         |          | REVISION HISTORY FR                                |                                       | EIE VALID.MIC                         |                                       |        |    |

| :1002         | •        |                                                    |                                       | CKS AND REMOVE COME                   | NT STATUS OF CASE CHECKS              |        |    |

| : 1003        |          |                                                    |                                       | USE IT IS IDENTICAL                   |                                       |        |    |

| ;1004         | -        |                                                    | RELEASE                               |                                       |                                       |        |    |

| :1005         | ;        | ADD 'WCTRL/MDR_0' AS CO                            |                                       |                                       |                                       |        |    |

| ;1006         | :        | ADD NEW CONFLICT FOR SC                            |                                       |                                       |                                       |        |    |

| ;1007         | :        | ADD NOTE TO BUT'S ON IF                            |                                       |                                       | LITY MODE                             |        |    |

| :1008         | ;        | CHANGE 'BUS VS MSRC' VA                            |                                       |                                       |                                       |        |    |

| ;1009         |          |                                                    |                                       |                                       | T/ASL.R.P', & 'ROT/ASL.M.P'           |        |    |

| ;1010         | :        | ADD VALIDITY CHECKS FOR                            |                                       |                                       | CRO ORDER ASSIGNMENTS PER SMITH 12-JA | N=79   |    |

| ;1012         | 47       | CHANGE 'WCTRL/STEPC' TO                            |                                       |                                       | CITUNS                                |        |    |

| :1013         | . 4/     | CHANGE 'WCTRL/FLAGS' TO                            |                                       |                                       |                                       |        |    |

| ;1014         | :        | RENAME IND ROM FIELDS T                            |                                       |                                       | M MACROS                              |        |    |

| ,1015         |          | INCOPORATE CHANGES PER                             |                                       |                                       |                                       |        |    |

| ;1016         | ;        | 1.) CHANGE 'WX_S.Q                                 |                                       | _0'                                   |                                       |        |    |

| ;1017         | ;        | 2.) CHANGE WX_D_S.                                 |                                       |                                       |                                       |        |    |

| ;1018         | ;        | 3.) DELETE 'MUXDZ'                                 |                                       |                                       |                                       |        |    |

| ;1019         | ;        | 4.) DELETE 'DQ4' FI                                |                                       |                                       |                                       |        |    |

| ;1020         | :        | 5.) ADD NEW SPECIAL                                |                                       |                                       |                                       |        |    |

| :1021         | ; 46     | CHANGE ALL VOD3 TO VOOT                            |                                       |                                       |                                       |        |    |

| :1022         |          | CORRECT VALIDITY CHECK                             |                                       |                                       |                                       |        |    |

| ;1023         | ; 45     | CORRECT COMPATABILITY N                            | UDE IND KUM DI                        | CF \$1911 1UN                         |                                       |        |    |

|               |          |                                                    |                                       |                                       |                                       |        |    |

•

MICRO2 ASSEMBLER DIRECTIVES 1

Figure 6-3

Microcode

|                                                             | 8.MCR [130,2112] Micro-2.1 1A(33) 14:40:3 9-Mar-1979<br>.MIC [130,2112] Machine Definition : IRD1 ROM                                     |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| :1961<br>:1962<br>:1963<br>:1964<br>:1965<br>:1965          | .TOC " Machine Definition : IRD1 ROM"<br>.ICODE<br>.WIDTH/32<br>.WIDTH/32                                                                 |

| ;1967<br>;1968<br>;1969<br>;1970<br>;1971<br>;1972<br>;1973 | IVIVII     II     F     F       IFFF     IRD1.FPA     O     IRD1     F       RFPO     P     O     P       DDDP     P     P       11     I |