VAXSTATION 100 ENGINEERING SPEC

REV 0.1

15 MARCH 1983 15 JUNE 1983

#### 1. OVERVIEW

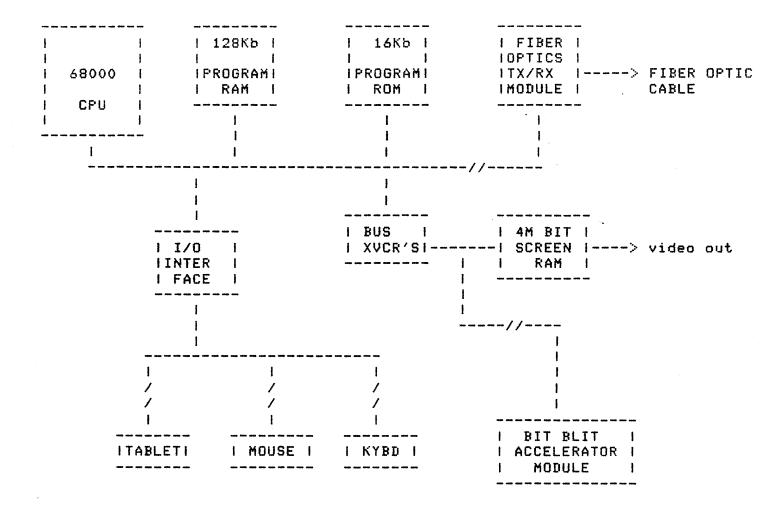

The VS100 workstation is a 19° monochrome workstation designed for the professional user. The VS100 consists of a corporate standard multibox containing an H7865 power supply, display processor module, a fiber optics transmitter/receiver module and a bitblit accelerator module. The VS100 uses a 19 in monitor (VR100) in a landscape format. The monitor has a screen resoultion of 1088 pixel horizontally by 864 pixels vertically. The VS100 interfaces to a VAX 11/7XX CPU through a 10MHz fiber optic cable and a VAX installed Unibus window module. The VS100 is supplied with a LK201Cx keyboard and a VS10X-EA mouse as input devices. An optional digitizing tablet VS10X-BA is available.

2. PRODUCT DESCRIPTION AND FUNCTION

#### **3. PRODUCT REQUIREMENTS**

#### 4. STANDARDS, REGULATIONS AND CERTIFICATION

The VS100 complies with the standards and resulations listed in the following subsections.

4.1 PRODUCT SAFETY

DEC.STD. 119 - disital product safets (covers UL 478, UL 114, CSA 22.2 NO. 154, VDE 0804, and IEC 435)

IEC 435 Safety requirements for data processing equiptment

4.2 AC POWER

DEC.STD. 002 - AC power wiring, grounding, receptacles and nameplates

DEC.STD. 122 - AC power line standard ( operating frequency 47-63 Hz, operating voltages 87-128VAC or 174-256VAC ).

4.3 ELECTROMAGNETIC COMPATABILITY

DEC. STD. 103 - electromagnetic compability (EMC) hardware design requirements.

FCC rules and regulations, part 15 - Radio frequency devices, subpart J (level A )

DIRECTIVE EEC - 76/889-EMI/RFI requirements for the British Isles

VDE 0871 level N-12 - Limits of radio interference from radio frequency apparatus and installations.

#### 4.4 ACOUSTIC NOISE

DIN 45635 PT1 and PT16 - Measurement of airborne noise emmited by machines

VDE 2058 Part 2

DEC.std. 102, section 4 will supercede the above suidelines when available

#### 4.5 ERGONOMICS

ZN1/535 - Ersonomics requirements for display workstations in the office enviroment.

#### 4.6 ENVIRONMENT

DEC.std. 102 - Environment standard for computers and peripherals ( class B, with operating temperature range of 10 to 40 degrees C and 10 to 90 percent relative humidity).

4.7 LANGUAGE

DEC.std. 107 - Digital standard for terminals keyboards

DEC. std. 168 - Multinational character set

#### 4.8 MISCELLANEOUS

DEC.std. 060 - Design and certification of hardware products to national and international regulations and standards.

DEC.std. 092 - Color and finish standard

DEC.std. 105 - Display workstation ergonomics

VDE 0730 - office machine equiptment

VDE 0860 - video display equiptment

### 4.9 CERTIFICATION AND APPROVAL

The VS100 is designed such that it will obtain the following listings, certifications, and approvals:

(safety) listing against UL 478 and CSA 22.2, No 154

(safety) certification of compliance to IEC 435

(EMI/RFI) international certification of compliance to FCC level A and VDE N-12 level

#### 5. HARDWARE

### 5.1 DISPLAY PROCESSOR BOARD

### 5.1.1 DESCRIPTION

The display processor module (DPM) in the VS100 contains the MC68000 cpupprogram rampprogram rom, screen rampand I/O ports. Connected to the display processor module as daughter boards are the fiber optic transmitter/reciever (FOT/R) module and the Bit Blit Accelerator (BBA) module.

The timing for the DPM is derived from a 79.96Mhz ECL oscillator and divided down to 40Mhz, 20Mhz, 10Mhz and other lower frequencies for use in the system. The 80Mhz clock allows for a screen display of 1088 pixels horizontally by 864 pixels vertically.

Communication with the host cpu (VAX11/7xx) is thru a fiber optic cable of up to 300 meters in length, which connects to the Unibus Window Module (UBW) located in the VAX unibus backplane. The fiber optic interface operates at a 10Mhz rate. All transmissions across the fiber optic cable are initiated by the DFM's 68000 cpu or by the BBA module. Transmissions to the VAX cpu are 54 bits in length (16 data bits, 16 crc bits, 18 address bits, 1 control bit, 3 spare bits). Recieved data from the VAX cpu is 24 bits in length.(16 data bits, 1 control bit and 7 spare bits). Data is transfered across the fiber link in a BI-PHASE L encoding scheme. All data transmissions are sent with a 16 bit CRC checksum.

The DPM also contains:

a programmable CRTC controller for generating the necessary timing signals for the VR100 monitor

two programmable USART's for communication with the optional disitizing tablet and the LK201Cx keyboard.

A discrete interface for the VS10X-EA hand held mouse

A set of 5 LED's for fault indication. 4 led's are red, and 1 led is sreen. The led's are located on the rear of the DPM, and are viewable from the rear of the multibox.

A power-up self test diagnostic used for testing of all major portions of the BPM module, the BBA module, the FOT/R module, and the LK201Cx keyboard. An extended set of tests are provided for user tests of the VS10X-EA hand held mouse, the VS10X-BA digitizing tablet, and alignment of the VR100 monitor.

Ilde loop self test that will run continuosly after power-up self test is run, but before the user loss onto the VAX cpu. Idle self-test provide a continuous check of the functionality of the VS100.

The Micro-diagnostics also has a MAINTANCE MODE which will enable the user to run specific tests and to test the I/O devices.

5.1.3. MEMORY MAP

The VS100 has a total of 656kb on board memory, allocated as follows:

| PROGRAM RAM   | 128Kb                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------|

| PROGRAM ROM   | 16Kb                                                                                                                     |

| SCREEN RAM    | 512Kb (4.2M bits)                                                                                                        |

| ADDRESS SPACE | 000000-07FFFF = PROGRAM RAM<br>080000-0FFFFF = UNIBUS<br>100000-17FFFF = FRAME BUFFER RAM<br>180000-1FFFFF = PROGRAM ROM |

The VS100 can address 256Kb of unibus address space

### 5.1.4. I/O REGISTERS

The following devices are mapped into the I/O space (addr 23 = 1) of the MC68000 cpu:

Tablet USART Keyboard USART Mouse position register Crt controller register System status register test led register BBA 'go' f/f

### 5.1.4.1 CRT controller resister

The CRT controller provides the necessary timing signals to the VR100 monitor, and the address for the start of the visible screen memory that will be read out sequentially during refresh of the screen. The CRT controller has two memory addresses assigned in the I/O space. The first is a pointer register that is loaded with the value of the register that data will be deposited in. Their are 14 registers available for use in the CRT controller. The second register is the data register. Any data deposited in the data register will be transfered to the register pointed to by the address register.

|     | CTRC AI           | DDRESS           | REGI  | STER  |    |      |       |        |

|-----|-------------------|------------------|-------|-------|----|------|-------|--------|

|     | addres            | s = 80           | 00000 | (HEX) |    |      | write | e only |

|     | CRTC I<br>address | 0ATA R<br>5 = 80 |       |       |    |      | read  | /write |

| BIT | 7                 | 6                | 5     | 4     | 3  | 2    | 1     | 0      |

|     | 1 D7 I            | D6 I             | D5    | D4 I  | D3 | D2 I | D1    | DO I   |

REFER TO DEC. SPEC. A-PS-16963-00 FOR MORE DETAILED INFORMATION

The required parameters for proper operation of the VR100 monitor at a screen resolution of 1088 Horz x 960Vert pixels are:

| RO = 45  | R1 = 34  |

|----------|----------|

| R2 = 37  | R3 = 06  |

| R4 = 74  | R5 = 05  |

| R6 = 72  | R7 = 72  |

| R8 = 00  | R9 = 11  |

| R10 = 00 | R11 = 00 |

| R12 = 00 | R13 = 00 |

| R14 = 00 | R15 = 00 |

5.1.4.2 DISPLAY PROCESSOR STATUS REGISTER

\_

The DISPLAY PROCESSOR STATUS resister is used by the MC68000 cpu to obtain the status of events the have an effect on the operation of the VS100 system. This resister is a "read only" resister.

| address = 8000C0 (HEX)           | read only                                                                                                                                                                                                               |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7 6 5 4 3                    | 2 1 0                                                                                                                                                                                                                   |

| I D7 I D6 I D5 I D4 I D3         | D2   D1   XX                                                                                                                                                                                                            |

| bit 7 = mouse pushbutton,right.  |                                                                                                                                                                                                                         |

| bit 6 = mouse pushbutton;middle. | logic 0 (0v) = ON<br>logic 1 (3v) = OFF<br>logic 0 (0v) = ON                                                                                                                                                            |

| bit 5 = mouse pushbutton,left    |                                                                                                                                                                                                                         |

|                                  | logic 1 (3v) = link is present<br>logic 0 (0v) = link not available                                                                                                                                                     |

| bit 3 = link error               | losic 1 (3v) = link error detected<br>losic 0 (0v) = no link error detected                                                                                                                                             |

| bit 2 = non-existant memory      | logic 1 (3v) = the UBW attempted to<br>access non-existant VAX memory.<br>Illegable address from the BBA<br>or the DPM. Used as a status<br>bit to indicate the reason<br>for failure to gain access to<br>the UNI-BUS. |

|                                  | <pre>logic 0 (0v) = address placed on the<br/>the uni-bus was a valid address,<br/>logic 0 (0v) =</pre>                                                                                                                 |

| bit 1 = BBA present              | logic 1 (3v) = BBA not present<br>logic 0 (0v) = BBA present                                                                                                                                                            |

| bit 0 = manufacturins mode       | logic 1 (3v) = not in manufacturing<br>mode<br>logic 0 (0v) = the module is in a                                                                                                                                        |

|                                  | manufacturing enviroment.                                                                                                                                                                                               |

### 5.1.4.3 MOUSE POSITION REGISTER

The MOUSE POSITION register is used as a count/direction register by the 68000 cpu. This register will contain the value of increments that the mouse was moved since the last "MOUSE POSITION REG" read by the 68000 cpu.

|         | address = 800060 (HEX)         | read only                                                                                            |   |

|---------|--------------------------------|------------------------------------------------------------------------------------------------------|---|

| bit     | 15                             | 8 7                                                                                                  | 0 |

|         |                                | Y0   X7                                                                                              |   |

| bit 15  |                                | ition register. Used to indica<br>ment in the vertical axis (Y a<br>logic 1 (3v) =<br>logic 0 (0v) = |   |

| bit 14- | -8 = the value of the mouse mo |                                                                                                      |   |

| bit 7 = |                                | tion register. Used to indicat<br>in the horizontal axis (X axi<br>logic 1 (3v) =                    |   |

| bit 6-0 | ) = the value of the mouse mo  | logic 0 (0v) =<br>evement in the "X" direction.                                                      |   |

### 5.1.4.4 TEST LEDS REGISTER

The TEST LED's register is used to turn on/off the 4 red led's and 1 green led located on the rear of the DPM board. These LED's are used by the microdisgnostics to indicate failure of any of the major sections of hardware in the VS100 system.

|         | address = 80008 | 0 (HEX)                                                                                                         | WRITE ONLY             |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------|------------------------|

| BIT     | 765             | 4 3 2 1 0                                                                                                       |                        |

|         | I XX I XX I OK  | I G5 I R3 I R2 I R1 I R0                                                                                        |                        |

| bit 7 = | RESERVED        |                                                                                                                 |                        |

| bit 6 = | RESERVED        |                                                                                                                 |                        |

| bit 5 = | TEST OK         |                                                                                                                 | ssfully passed burn-in |

| bit 4 = | sreen led       | <pre>losic 0 (0v) = test fail<br/>losic 1 (3v) = led off<br/>losic 0 (0v) = led on in<br/>passed power-up</pre> | dicates the VS100 has  |

| bit 3 = | red led 3       | losic 1 (3v) = led off<br>losic 0 (0v) = led on                                                                 |                        |

| bit 2 = | red led 2       | losic 1 (3v) = led off<br>losic 0 (0v) = led on                                                                 |                        |

| bit 1 = | red led 1       | losic 1 (3v) = led off<br>losic 0 (0v) = led on                                                                 |                        |

| bit 0 = | red led O       | logic 1 (3v) = led off<br>logic 0 (0v) = led on <sup>.</sup>                                                    |                        |

REFER TO SECTION 7.5 FOR A COMPLETE DESCRIPTION OF THE TEST LEDS ERROR CODES

### 5.1.4.5 TABLET USART

The TABLET USART register is 4 I/O mapped locations used to set-up the 2661 USART for proper communications with the optional VS10X-BA digitizing tablet. The clock to the USART is 5.000Mhz. The normal communications baud rate to the tablet is 9600 baud

|     | 30 | dre | 259 | 5 = | 8 | 0002 | 20 | (HI | ΞX  | )  |   |    |  | RE  | AD. | /WR] | ITE   |

|-----|----|-----|-----|-----|---|------|----|-----|-----|----|---|----|--|-----|-----|------|-------|

|     |    |     |     |     | 8 | 0002 | 22 | (HI | ΞX  | )  |   |    |  | RE  | AD. | /WR] | I T E |

|     |    |     |     |     | 8 | 0002 | 24 | (HE | EX. | )  |   |    |  | REA | ۹D. | /WR] | [TE   |

|     |    |     |     |     | 8 | 0002 | 26 | (HI | ΞX  | )  |   |    |  | RE  | AD. | /WR] | ITE   |

| BIT |    | 7   |     | 6   |   | 5    |    | 4   |     | 3  |   | 2  |  | 1   |     | 0    |       |

|     | 1  | D7  | 1   | D6  | 1 | D5   |    | D4  |     | D3 | 1 | D2 |  | D1  |     | DO   |       |

|     |    |     |     |     |   |      |    |     |     |    |   |    |  |     |     |      |       |

REFER TO DEC.SPEC. A-PS-18623-00 FOR MORE DETAILED INFORMATION

NOTE: The clock input to the USART is 5.000Mhz

#### 5.1.4.6 KEYBOARD USART

The KEYBOARD USART resister is 4 I/O mapped locations used to set-up the 2661 USART for communications with the LK201Cx keyboard. The clock to the USART is 5.000Mhz. The baud rate for the LK201Cx keyboard is 4800 baud.

|     | 3 | ddre | 259 | 5 = | 8( | 000 | )0 |    |   | F  | RE / | AD/V | IR:  | ITE |   |    |  |

|-----|---|------|-----|-----|----|-----|----|----|---|----|------|------|------|-----|---|----|--|

|     |   |      |     |     | 80 | 000 | )2 |    |   | F  | REA  | AD/V | IR:  | ITE |   |    |  |

|     |   |      |     |     | 8( | 000 | )4 |    |   | F  | RE   | AD/V | IR : | [TE |   |    |  |

|     |   |      |     |     | 8( | 000 | )6 |    |   | F  | RE ( | AD/1 | IR : | ITE |   |    |  |

| BIT |   | 7    |     | 6   |    | 5   |    | 4  |   | 3  |      | 2    |      | 1   |   | 0  |  |

|     |   | D7   | 1   | D6  | 1  | D5  | 1  | D4 | 1 | D3 |      | D2   | 1    | D1  | 1 | DO |  |

|     |   |      |     |     |    |     |    |    |   |    |      |      |      |     |   |    |  |

REFER TO DEC.SPEC. A-PS-18623-00 FOR MORE DETAILED INFORMATION NOTE: The clock input to the USART is 5.000 Mhz

#### 5.1.5 I/O CONNECTOR DESCRIPTIONS

•

The following I/O connectors are located on the rear panel of the VS100 DISPLAY PROCESSOR MODULE.

5.1.5.1 MONITOR OUTPUT CONNECTORS

The VR100 monitor uses 3 seperate outputs. These outputs are provided through isolated BNC type 50 ohm connectors. The levels of the outputs are:

| video     |      |           | 0.0v-800 mv. |  |  |  |

|-----------|------|-----------|--------------|--|--|--|

| ٤         | lack | =         | 0.00         |  |  |  |

| te        | hite | =         | 0.7000       |  |  |  |

| horz.sync | :    | 0.4v-2.4v |              |  |  |  |

| vert.sync | :    |           | 0.4v-2.4v    |  |  |  |

5.1.5.2 TABLET POWER AND SIGNAL CONNECTORS

pin 13

all other pins = n.c.

The tablet uses 2 connectors. one for power and one for signals. The connectors are industry standard D-SUB miniature type connectors, located on the backpanel of the DPM module.

reserved (test OK )

9 pin power connector (female, D-sub miniature)

| pin 1                   | +5v                       |

|-------------------------|---------------------------|

| pin 2                   | +5v                       |

| pin 3                   | N+C+                      |

| pin 4                   | +12v                      |

| pin 5                   | N.C.                      |

| pin 6                   | -12v                      |

| pin 7                   | sround                    |

| pin 8                   | sround                    |

| pin 9                   | chassis ground            |

|                         |                           |

| 25 pin signal connector | (female, D-sub miniature) |

|                         |                           |

| pin 1                   | safety ground             |

| pin 2                   | transmit                  |

| pin 3                   | receive                   |

| pin 7                   | signal ground             |

| pin 12                  | reserved (test INIT)      |

### 5.1.5.3 MOUSE POWER/SIGNAL CONNECTOR

15 pin power/signal connector (female, D-sub miniature)

\*\*\*\*

| pin 3 | 1  | YA            |

|-------|----|---------------|

| pin 2 | 2  | YB            |

| pin 3 | 3  | XB            |

| pin 4 | 4  | XA            |

| pin : | 5  | N+C+          |

| pin ( | 6  | +5V D.C.      |

| pin 3 | 7  | N+C.          |

| pin ( | В  | N+C+          |

| pin ' | 9  | GROUND        |

| pin 3 | 10 | GROUND        |

| pin 3 | 11 | N+C.          |

| pin 3 | 12 | RIGHT BUTTON  |

| pin 3 | 13 | MIDDLE BUTTON |

| pin 3 | 14 | LEFT BUTTON   |

| pin 3 | 15 | N + C +       |

# 5.1.5.4 KEYBOARD POWER/SIGNAL CONNECTOR

4 pin female telco connectorRS-423 COMPATIBLEpin 1RECEIVEpin 2GROUNDpin 3+12v dcpin 4TRANSMIT

#### 5.1.6 INTERRUPTS

The MC68000 uP on the DPM has 7 levels of interrupt. Level 7, the highest level is non-maskable. Interrupt vector addresses are fixed. The 7 levels of interrupt are:

| level 7 = | BBA non-existent memory. Set when the BBA tries to address   |

|-----------|--------------------------------------------------------------|

|           | non-existent memory in the VAX cpu, Cleared by clearing the  |

|           | BBA 'so' bit.( the BBA will then clear its memory request,   |

|           | which will clear the LEVEL 7 interrupt.                      |

| level 6 = | VERTICAL SYNC, used as a watchdos timer, Set by VERT, SYNC,  |

|           | from the CRT controller. Cleared by RESET SIX. (read from    |

|           | address 8000E0 (HEX)                                         |

| level 5 = | LINK TRANSITION. indicates that the Fiber Optic link has had |

|           | either LINK ERROR asserted, or that LINK AVAILABLE has       |

|           | chansed states. Cleared by either a power-up reset           |

|           | (hardware) or a read from address 800040 (HEX)               |

| level 4 = | BBA DONE. Used to indicate that the BBA has completed an     |

|           | operation. Cleared by the BBA when the 68000 uP clears the   |

|           | BBA 'so' bit                                                 |

| level 3 = | Tablet USART interrupt, Receiver buffer full,or transmitter  |

|           | buffer emety.                                                |

| level 2 = | Keyboard USART interrupt, Receiver buffer full,or            |

|           | transmitter buffer empty.                                    |

| level 1 = |                                                              |

|           |                                                              |

## 5.1.7 MANUFACTURING MODE

A jumper has been provided on the DPM module that will allow for a dynamic functional burn-in of the zebra/bba/fotr in a manufacturing environment. This jumper requires the use of loopback connectors on the tablet i/o port (DEC. PT# 12-15536-00), and a loopback connector on the keyboard port (DEC.PT# 12-XXXX-XX). when in this mode, the micro-diagnostics will loop continuously on the power-up self test. The unit will halt at the first occurance of a detected error, and display the test number in the led indicators.

#### 5.2 UNIBUS WINDOW MODULE

#### 5.2.1 FUNCTIONAL DESCRIPTION

The M7452 module is a standard height hex size module used as an interface between the VS100 and the VAX11/7XX cpu. The module connects to the VAX unibus backplane and recieves its power from the VAX. The M7852 is connected to the VS100 by a 2 channel fiber optic cable. The M7452 has 8-16 bit resisters used for the transfer of data between the VS100 and the VAX cpu. The VAX is allowed to address the control/status resisters only. The VS100 can address either the control/status resisters or the VAX memory.

The M7452 is an NPR device and is also capable of interrupts to the VAX. The address range of the module is selected by switches. The interrupt vector addresses are programmable. The Interrupt level is selected by a standard BR chip; set at level BR5.

The unibus module is capable of supporting one (1) VS100 communications link The maximum length of Fiber optic cable that can used with the VS100 is 300 meters.

#### 5.2.2 MAINTANCE MODE LOOPBACK

The M7452 module is provided with the capability to perform loopback of data while under program control. This is accomplished on two levels. The first is an electrical loopback of data that has been encoded into bi-phase L data at an ECL voltage level.While in this mode, the XMIT ON bit should be dis-asserted. this will prevent data from being transmitted to the VS100 display processor board. Also, while in this mode, the CRC generator may be disabled.

The second level of loopback is the OPTICAL loopback. this mode requires that an optical loopback connector (DEC PT. # 12-yyyyy-zz) be installed on the fiber optic connectors. While in this mode, the XMIT ON bit must be asserted, and the CRC generator may be either asserted or de-asserted.

The loopback process is started by first setting the appropriate bits in CSR 0,then loading the data to be looped back into CSR5. Loading of data into CSR5 will initiate the loopback sequence. Data will be loaded into CSR6. If interrupts are enabled,the unibus module will interrupt the host,with the vector address that was previously loaded onto CSR7.

#### 5.2.3 SWITCH SELECTABLE BUS ADDRESSES

The base address of the M7852 is selectable through a set of switches located on the module. The range of addresses is 760000-777760 (BASE 8) The numbering and location of the switches is as follows:

| address bit     | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4      | UNIBUS<br>ADDRESS |

|-----------------|------|------|------|------|------|------|------|------|--------|-------------------|

| NO              | אס ו | I ON | אס ו | I ON | 1    | 1 ON | אס ו | 1    | I ON I | 760440(8)         |

| OFF             | 1    | 1    | 1    | 1    | IOFF | 1    | 1    | IOFF |        | FFE120(16)        |

| switch position | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9      |                   |

## 5.2.4 SOFT VECTOR ADDRESSES

The VECTOR addresses that the VS100 uses to interrupt the host cpu are loaded by the DEVICE DRIVER prior to ucode load. The vector address must be loaded into CSR 7. The allowable range of addresses is 000000-001776(BASE 8)

5.2.4 BLOCK DIAGRAM

| IUNIBUS I |                | I  | FIBER    | IXMIT S.F | 8.1> | FIBER |

|-----------|----------------|----|----------|-----------|------|-------|

| I. I<     |                | >1 | OPTIC I< | ->        |      | OPTIC |

| IXCVR'S I | 1              | I  | XVCR'SI  | IREC S.R. | <    | CABLE |

|           | 1              |    |          |           |      |       |

|           | V              |    |          |           |      |       |

|           |                | -  |          |           |      |       |

| 1         | CONTROL/STATUS | 1  |          |           |      |       |

| 1         | REGISTERS      | 1  |          |           |      |       |

|           |                |    |          |           |      |       |

# 5.2.6 CONTROL/STATUS REGISTER BIT ASSINGMENTS

|        | 15  | 5 5  | 14 13 12 11 10 9 8 7 6 5 4 1 0                                                                                                                                                                                                     |

|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSR 0  | 1 1 | _T I | LA I LE I XO I MM I CD I MD IRES.I OWN IRES.I IE I FUNCT I GO I                                                                                                                                                                    |

|        | BIT | 15   | Link Transtition<br>set when:<br>1. a link error occurs<br>2. there is a change in the state of the link<br>available bit<br>cleared by: The host CPU                                                                              |

|        | BIT | 14   | Link Available indicates the status of the fiber cable squelch                                                                                                                                                                     |

| circui | try |      | set when: a sufficient level of light is detected by the fiber<br>optic receiver<br>cleared by: The host CPU                                                                                                                       |

|        | BIT | 13   | Link Error<br>set when: a CRC error is detected by the fiber optic receiver<br>during data reception                                                                                                                               |

|        |     |      | cleared by: cleared when the host cpu clears bit 15                                                                                                                                                                                |

|        | BIT | 12   | Xmitter On used to control the state of the Fiber Optic PIN<br>transmitter diode<br>set to 1 = light on<br>cleared to 0 = light off                                                                                                |

|        | BIT | 11   | Maintance Mode controls the state of the U.B.W. module. Allows<br>data to be loored back internally to the module<br>for testing purposes.<br>set to a 1 = maintance mode enabled<br>cleared to 0 = normal operation of the module |

|        | BIT | 10   | Crc Disable used by diagnostics to disable the generation of<br>CRC checksums.                                                                                                                                                     |

|        |     |      | set to 1 = disable CRC generation<br>cleared to 0 = enable CRC generation                                                                                                                                                          |

|        | BIT | 9    | Maintance Done used to signal the end of a maintance mode                                                                                                                                                                          |

|        |     |      | set to 1 = maintance mode cycle done<br>cleared to 0 =                                                                                                                                                                             |

|        | BIT | 8    | RESERVED                                                                                                                                                                                                                           |

|        | BIT | 7    | OWN                                                                                                                                                                                                                                |

|        | BIT | 6    | Interrupt Enable                                                                                                                                                                                                                   |

|        | BIT | 5    | RESERVED .                                                                                                                                                                                                                         |

|        | BIT | 4-1  | FUNCTION CODE specifies an operation to be performed by the display processor.                                                                                                                                                     |

|        | BIT | 0    | GO bit                                                                                                                                                                                                                             |

The VS100 micro-code will support the following 3 functions in ROM based firmware, and the 2 commands associated with the SEND PACKET function.

|          | BIT POSITION                                                                                                                                 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| CODE     | 5 4 3 2 1 I FUNCTION                                                                                                                         |

| 0        | I O I O I O I O I INITIALIZE                                                                                                                 |

| 1        | I O I O I O I 1 I SEND PACKET                                                                                                                |

| 2        | I O I O I O I 1 I O I START DISPLAY                                                                                                          |

| are supp | PACKET" function has two seperate commands that<br>rted in the VS100, They are:                                                              |

| :        | <ul> <li>REPORT STATUS this command returns information about the<br/>display's status and addressing enviroment to<br/>the host.</li> </ul> |

2. MOVE OBJECT ---- this command allows down-line loading of the display micro-code into display local memory.

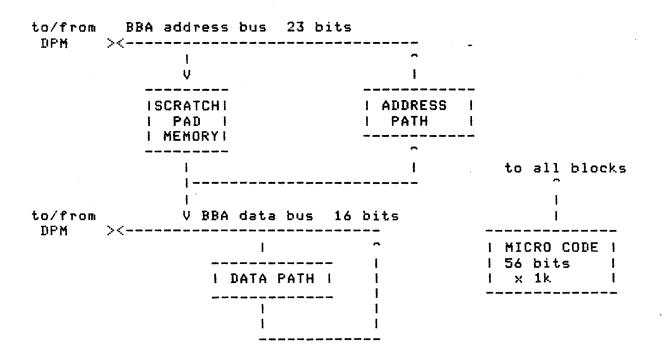

### 5.3 BIT BLIT ACCELERATOR

#### 5.3.1 FUNCTIONAL DESCRIPTION

The Blit Bit Accelerator (BBA) is used to move data to and from the Display Processor Screen memory at high speed independant of the Display Processor CPU. The BBA recieves command packets from the Display processor, and can modify,manipulate and move data for the purpose of quickly changing visually displayed information.

From a functional viewpoint, the BBA is divided into two sections. One secton interpets commands, computes addresses, and provides control and execution of algorithms. The second section is used to process bit data.

The following instructions are supported by the BBA firmware

- A. COPY AREA

- B. PRINT TEXT

- C. VECTOR

- D. HALFTONE

For a complete description of these instructions, refer to the WORKSTATION GRAPHIC ARCHITECTURE V1.0 , HANK LEVY MARCH 1, 1983

#### 5.3.2 BLOCK DIAGRAM

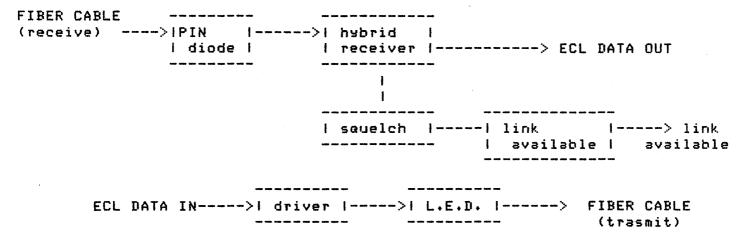

#### FIBER OPTIC TRANSMITTER/RECEIVER MODULE (DEC. # 54-16010) 5.4

#### 5.4.1 FUNCTIONAL DESCRIPTION

The fiber optic transmitter/receiver module is used to drive the fiber optic cable. The data inputs to the module are ECL level signals. the data outputs from the module are ECL level signals. Also output from the module is the link available signal, used to indicate that the light received is above a minimum value as determined by the squelch circuitry.

NOTE: the link available signal assereted indicates that light is being received. It does not mean that the fiber optic link is functional.

### 5.4.2 BLOCK DIAGRAM

the FOT/R has four sections. These are: 1. the hybrid receiver, 2. the squelch circuit, 3. the link available circuit and 4. the transmit L.E.D. driver.

#### 5.4.3 SIGNAL DESCRIPTION

| 40 pi | in connector, Fema           | 3le            |

|-------|------------------------------|----------------|

| Pins  | 1,2,3,4                      | +5v            |

| pins  | 5,6,11,12,                   | GND.           |

|       | 29,30,32,33,<br>34,36,37,38, |                |

|       | 40                           |                |

| pins  | 7,8,9,10                     | +12v           |

| pins  | 13,14,15,16                  | -12v           |

| pins  | 17,18,22, N.C.               |                |

|       | 23,24,25,26,                 |                |

|       | 27,28                        |                |

| pin   | 19                           | link avail H   |

| pin   | 20                           | link avail L   |

| pin   | 21                           | xmit on H      |

| pin   | 31                           | ecl tx data L  |

| pin   |                              | ecl tx data H  |

| pin   | 39                           | ecl bip data L |

5.5 FIBER OPTIC CABLE

DEC.PT# 17-00333-01 unterminated DEC.PT# 17-00343-xx terminated (BC25B-xx)

The fiber optic cable used in the VS100 is a two channel cable, that operates in a graded-index mode of operation, the optical fiber is 100nm in diameter, clad with glass that is 140nm in diameter.

5.5.1 WEIGHT

The weisht of the fiber optic cable is 100 lbs/km nominal, 45ks/km nominial

5.5.2 COLOR

The color of the outer jacket of the cable is TAN (per DEC. 216, BEIGE)

5.5.3 CABLE LENGHTS

The terminated cable is available in standard lengths of:

| DIGITAL PART NO. | DIGITAL OPTION NO. | LENGTH (-0%+2%,+30cm.) |

|------------------|--------------------|------------------------|

| 17-00343-02      | BN25B15            | 15M (49 ft.)           |

| 17-00343-03      | BN25B30            | 30M (98 ft.)           |

| 17-00343-04      | BN25B60            | 60M (197 ft.)          |

| 17-00343-05      | BN25B90            | 90M (295 ft)           |

| 17-00343-01      | BN25B150           | 150M (492 ft.)         |

| 17-00343-06      | BN25B300           | 300M (984 FT.)         |

The cable is available in the unterminated version only on special order. The DEC pt# for unterminated cable is 17-00333-01. All disital cable that meets these purchase specs will have the transmit cable clearly identified. The recieve cable will also be identified. The cable has the following charactersites:

minimum bend radius, fiber cable with outer sheathins > 3.0 inches, > 7.6cm

minimum bend radius fiber cable without outher sheathins > 1.0 inch, > 2.54cm

the cable will withstand a crush force of 400LBS./linear inch

#### 5.6 VR100 monitor

#### 5.6.1 DECSRIPTION

The monitor used with the VS100 is a 19in (diagonal) landscape mode monochrome cathode ray tube(CRT) containing all of the necessary electronics for displaying high resolution alphanumeric/graphic video information. It is AC powered, self contained in a compact plastic enclosure and receives video and synchronizing signals thru a 3 conductor cable from the VS100 multibox.

The monitor is equiped with fault indicating LEDs (normally on) and is intended for mounting on a tilt/swivel base. Other key features of the monitor are:

rear panel mounted controls for brightness and contrast self contained power supply OCLI anti-glare screen coating noise free operation without a fan meets class A FCC radiation levels UL approved

#### 5.6.2 VIEWABLE AREA

FORMAT:

The viewable presentation is a rectanglular format of square pixels with 1088 pixels across the horizontal dimension and 864 pixels across the vertical dimension.

#### 5.6.3 ACTIVE DISPLAY AREA:

With a solid white screen applied and at a maximum signal level of 40 foot-lamberts, the active display size shall be:

| Horizontal    | 354.3mm | +- 1.5mm | 13.95in |

|---------------|---------|----------|---------|

| Vertical      | 281.4mm | +- 1.5mm | 11.08in |

| screen aspect | ratio   | 1.26:1   |         |

#### 5.6.4 PIXEL SIZE:

| Horizóntal   | .325m  |     | 0.0128 | in |

|--------------|--------|-----|--------|----|

| Vertical     | .325mm |     | 0.0128 | in |

| pixel aspect | ratio  | 1:1 |        |    |

### 5.6.5 FAULT INDICATING L.E.D.S

The VR100 monitor is equiped with 4 fault indicating LEDs. These LEDs are normally illuminated to indicate the presence of the necessary signals/voltages for the proper operation of the monitor.

The LEDs indicate the following conditions:

| VIDEO      | minimum threshold of 300MV required           |

|------------|-----------------------------------------------|

| HORZ SYNC  | TTL level required                            |

| VERT SYNC  | TTL level required                            |

| B+ Volta⊴e | 80% of required B+ level for normal operation |

|            | of the monitor is available                   |

figure of back panel

T.B.S.

### 5.6.6 POWER REQUIREMENTS

115v @ lamp. 240v @ .5amp fuse type = 3AG (U.S.) 5mm X 20mm (EUROPEAN)

#### 5.6.7 CONTROLS, EXTERNAL

brightness contrast

### 5.6.8 INPUTS

The inputs to the VR100 monitor are BNC type connectors, located on the rear panel of the monitor.

5.6.8.1 VERTICAL

| ۷. | sync width =      | 0.1 to 0.5 Msec |

|----|-------------------|-----------------|

| V. | sync period =     | 16.667 Msec     |

| ٧. | sync. Tr = <3ns.  | Tf = <3ns₊      |

| ٧. | blanking interval | 0.775 Msec      |

| ٧. | unblank interval  | 15.912 Msec     |

| ٧. | frequency =       | 60Hz.           |

### 5.6.8.2 HORIZONTAL

| Η. | sync width =      | 2-8 uSEC          |

|----|-------------------|-------------------|

| Η. | sync, period =    | 18,416 USEC       |

| Η. | sync. Tr = <3ns.  | <b>Tf</b> = <3ns∙ |

| Η. | blankins interval | 4.804 uSEC        |

| Η. | unblank interval  | 13.612 uSEC       |

| н. | frequency =       | 54.3KHz.          |

5.6.8.3 VIDEO

| Voh = | (white | level) |

|-------|--------|--------|

| Vol = | (black | level) |

| Tr =  | < 3ns. |        |

| Tf =  | < 3ns. |        |

### 5.6.9 POWER REQUIREMENTS

120v ac @ 1amp 240 v ac @ .5 amp

### 5.6.10 PHYSICAL DIMENSIONS

heisht(w/o tilt/swivel) = 14.75 in. (37.5cm)

width = 18.0 in. (45.7cm)

depth = 16.0 in. (40.6cm)

weisht(w/o tilt/swivel) = <45 lb. (20.5 ks)</pre>

### 5.6.11 TILT/SWIVEL BASE

supplied with each unit. customer installed

swivel range = 360 degrees (limited by the cables)

tilt range = -5 to +15 degrees

#### 5.7 MOUSE VS10x-EA

#### 5.7.1 DESCRIPTION

The MOUSE is a hand held pointing device used to select objects on the display screen. It is attached to the display processor module through a 12ft. cable with a male 15 pin D-sub miniture connector. Power for the MOUSE is derived from the display processor module. The MOUSE provides relative position data to the display processor by means of quadurature encode signals for each axis (X and Y). The MOUSE also has 3 buttons used to signal events to the display processor. The mouse buttons are numbered 1 thru 3 from left to right.

#### 5.7.2 PHYSICAL DIMENSIONS

Heisht = 1.3 in (3.3cm) Lensth = 3.75in (9.5cm) Width = 2.75in (7.0cm) Weisht = <10oz. (280sr.) cable lensth = 12 FT. cable color = DEC 068 GREY

#### 5.7.3 SIGNAL DESCRIPTION

15 pin D-SUB miniature connector type,male pin 1 thru 15

NOTE: cable shield is tied to the metal housing of the connector.

### 5.7.4 ACCURACY

The VS10x-EA is capable of providing 200 pulses/inch. The rate of movement of the MOUSE is limited to 10 in/sec.

5.7.5 POWER REQUIREMENTS +5Vdc +/-10% @ <150ma. protected by a circuit board mounted "pico"fuse.

Note: the "pico" fuse is not customer serviceable.

5.7.6 OPERATION

TABLET, W/5 BUTTON PUCK DEC. PT. # 30-20037-01 5.8

5.8.1 DESCRIPTION

The VS10X-BA disitizing tablet is highly accurate absolute positioning device used to input coordinate data to the display processor board. The disitizing tablet is connected to the display processor by two cables. One is a 9 pin cable used to supply power to the tablet, and the second cable supplies data to and from the tablet. The tablet itself is a micro-processor controlled device, with a hand held puck which has 5 buttons for controlling the operation of the tablet.

The VS10X-BA is a disitizing system consisting of the following components

| TABLET             | VS10X-CA    |

|--------------------|-------------|

| 5 BUTTON CURSOR    | VS10X-DA    |

| 12 FT POWER CABLE  | 17-00341-01 |

| 12 FT SIGNAL CABLE | 17-00322-06 |

The disitizing tablet is a computerized input device which sends X-Y coordinate date to the VS100 to indicate the position of the cursor on the surface of the tablet to a high level of accuracy

5.8.2 ACCURACY

The accuracy of the tablet is 1000 Lines/inch at 22 des.C +/- 4 des. C at the specified humidity and altitude

REPEATABILITY +/ - 0,001 inch (with cursor)

COORDINATE ORIGIN: absolute

5.8.3 OPERATION OF THE TABLET

The tablet may be operated in any of the following modes of operation

POINT: stylus switch or cursor indicates a single X-Y output

- CONTINUOUS: Multiple X-Y pairs are output as long as the stylus or cursor is in the proximity of the tablet. No switch activation is required.

- LINE: Multiple X-Y pairs are output as long as the stylus or cursor switch is held down.

INCREMENTAL: Movement of the stylus or cursor of more than 0.01 inch in line mode initiates output.

5.8.4 PHYSICAL DIMENSIONS

5.8.4.1 DIGITIZING TABLET VS10X-CA

height 2.171 in (55mm) in level position 4.203 in (122mm) in tilt position

tilt angle 14 deg +/- 2 deg.

width 16.75 in (425 mm)

depth 16.75 in (425 mm)

weisht

5.8.4.2 USEABLE SURFACE SIZE

The surface is seamless, opaque acrylic plastic

width 11.0 in (273.4 mm) depth 11.0 in (273.4 mm)

5.8.5 POWER REQUIREMENTS

5V DC < 2.0 amp +12V DC < 120ma -12V DC < 120ma

5.8.6 SIGNAL DESCRIPTION

I/O cable, 25 pin male, 12ft. (3.7m),DEC 068 srey

| pin        | function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | dimensional statements of the statement of the stat |

| 2          | transmit data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3          | recieve data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4          | request to send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5          | clear to send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6          | data set ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7          | sround                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8          | carrier detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 20         | data terminal ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| other pins | reserved for other functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

POWER CABLE, 9 pin female, 12ft. (3.7m), DEC 068 srey

| PIN    | PIN FUNCTION   |  |  |

|--------|----------------|--|--|

| 1      | +5v            |  |  |

| 2      | +5v            |  |  |

| 2<br>3 | N.C.           |  |  |

| 4      | +12v DC        |  |  |

| 5      | N+C+           |  |  |

| 5      | -12v DC        |  |  |

| 7      | sround         |  |  |

| 8      | sround         |  |  |

| 9      | n.c.           |  |  |

| shell  | chassis ground |  |  |

# 5.8.7 RELIABILITY

The M.T.B.F. shall be > 10,000 hrs.

5.8.8 DATA FORMAT

•

figure to be supplied

5.8.9 SWITCH POSITION SETTINGS

figure to be supplied

### 5.9 LK201-CA KEYBOARD

#### 5.9.1 DESCRIPTION

The keyboard used with the VS100 workstation is the LK201Cx. This keyboard is a product specific variation of the D.E.C. standard LK201 family of keyboards. For a more detailed description of the LK201 keyboard, refer to the documents listed in the appendix.

5.9.2 MODEL DESIGNATIONS

All LK200 family keyboards are designated by a model number which describes the keyswitch groups implemented, keycap placement, and labeling. The keyboards described here are designated LK201Cx

LK201 C ×

\_ \_

1

I ---- alphabetic describing keycap labels.

----- alphabetic designating a VS100 specific keyboard.

| мо | DEL NO.  | KE | YBOARD   | LEGEND            | _ |

|----|----------|----|----------|-------------------|---|

| 1  | VS10X-AA | 1  | LK201-CA | I USA/CANADA I    |   |

| 1  | VS10X-AB | 1  | LK201-CB | IBELGUIM FLEMISHI | _ |

| 1  | VS10X-AC | 1  | LK201-CC | ICANADA (FRENCH)I |   |

| 1  | VS10X-AD | 1  | LK201-CD | I DENMÄRK I       | _ |

| 1  | VS10X-AE | 1  | LK201-CE | IUNITED KINGDOM I |   |

| 1  | VS10X-AF | 1  | LK201-CF | I FINLAND I       | - |

| 1  | VS10X-AG | 1  | LK201-CG | I GERMANY I       | • |

| 1  | VS10X-AH | 1  | LK201-CH | I HOLLAND I       | - |

| 1  | VS10X-AI | 1  | LK201-CI | I ITALY I         | _ |

| 1  | VS10X-AJ |    | LK201-CJ | IJAPAN KATAKANA I |   |

| 1  | VS10X-AK | 1  | LK201-CK | ISWISS (FRENCH) I | _ |

| 1  | VS10X-AL | 1  | LK201-CL | ISWISS (GERMAN) I | - |

| 1  | VS10X-AM |    | LK201-CM | I SWEDEN I        |   |

| 1  | VS10X-AN | 1  | LK201-CN | I NORWAY I        |   |

| 1  | VS10X-AP | 1  | LK201-CP | I FRANCE I        |   |

| 1  | VS10X-AS |    | LK201-CS | I SPAIN Í         |   |

| 1  | VS10X-AZ | 1  | LK201-CZ | I AUSTRALIA I     | • |

|    |          |    |          |                   |   |

#### 5.9.3 DIMENSION

The height from the desktop to the finger contact surface of the home row of keys shall be 30 mm. +/-1.0 mm.

The overall dimensions for the keyboard are :

width 21 inches 53.3cm derth 6.75 inches 17.2cm height (including keycars) 2.0 inches 5.1cm

The unsculptured keys are mounted on a curved base which will produce a sculptured keyboard profile with unsculptured keys.

The weight of the keyboard with the interconnecting cable is less than 5.0 lbs 2.3kg

### 5.9.3.1 COLOR

The function keys located on the top row of keys, the cursor keys and the six keys located directly above the cursors will be a neutral color (DEC 217).The color of the remainder of the keys and the keyboard are grey (DEC 068).

### 5.9.3.2 REFLECTANCE

The keycaps reflect less than 45% of the incident light.

5.9.3.3 LEGEND

figure to be supplied

### 5.9.3.4 KEYBOARD INTERCONNECT

The keyboard interconnect cable is 16 ft in lenght. In an uncoiled condition, the cable is 19 ft. The keyboard cable uses a 4 pin male telephone connector at each end.

### 5.9.3.5 KEYBOARD OPERATION

The operator uses the keyboard to transmit encoded keying events to a buffer in the workstation. A keying event is transmitted when:

any key is newly pressed

any of a certain set of keys is depressed

certain keys are held down and are generating auto repeatkeying events.

except as allowed above, the release of a key is not an event.

data is transmitted from and recieved by the keyboard at a rate of 4800 baud.

transmitted data is in single byte format for a given key. upon receiving a reset command from the VS100, the keyboard will perform a power-up self test and then transmit a 4 byte code to the VS100. The 4 bytes transmitted at power-up are defined as follows:

| fourth byte | indicates specific key down if any                                                               |

|-------------|--------------------------------------------------------------------------------------------------|

| third byte  | error code or 0 error code can<br>indicate RAM error;ROM checksum<br>error or key down condition |

| second byte | hardware I.D.                                                                                    |

| first byte  | firmware I.D.                                                                                    |

The user must identify the keyboard to the VS100 ie. what natural language, german, french etc., either in the set-up mode or through escape sequences when switching keycaps or keyboards.

### 5.9.3.6 N KEY ROLLOVER

The keyboard will transmit the last key down even though other keys are not released. This will enable the workstation to exibit the N key rollover feature when:

1. "phantom key" possibilities do not exists.

2. The bell of the keyboard can be programmed for various volume levels

3. The keyclick indicator can be programmed to an ON or OFF condition.

#### 5.10 POWER SUPPLY - H7865

### 5.10.1 OPERATION

The H7865 power supply is a single ended, switch type, resulated AC-DC converter circuit. It utilizes a uni-directional transformer in a half wave transformer coupled mode. The unit operates at a constant frequency and resulation is achieved by pulse width modulation of the inverter primary current conduction time. Primary energy storage is in the input filter capacitors at approximately 300V DC. Discrete pulses of known current are provided to the UDT primary winding with each triggered period of operation. This current is transformed by the UDT and is available at lower voltage and higher current at the secondary windings of the UDT. By increasing or decreasing the pulse width , the available output voltage is affected correspondingly. Hence, a constant output DC voltage is maintained with varying lines and loads by increasing or decreasing the converter pulse width.

#### 5.10.2 ELECTRICAL SPECIFICATIONS

### 5.10.2.1 AC INPUT SPECIFICATIONS

#### 5.10.2.2 LINE VOLTAGE

Line voltage input range is selected by an operator accessible switch located near the AC inlet connector. This switch requires a small tool, such as a screwdriver to operate.

- 5.10.2.2.1 120V AC nominal, single phase, 3 wire. 87V AC to 128V AC.

- 5.10.2.2.2 220V AC nominal, single phase, 3 wire. 174V AC to 256V AC.

5.10.3 FREQUENCY

5.10.4 CURRENT

5.10.4.1 6A RMS Maximum (87V AC input for full rated output)

5.10.4.2 4A RMS Maximum (174V AC input for full rated output)

### 5.10.5 POWER FACTOR

The power factor \_\_\_\_RMS WATTS\_\_\_\_\_ of the input shall be greater RMS volts x RMS amps

than 0.60 at full output power and 120V AC, 60 Hz line.

#### 5.10.6 INRUSH CURRENT

At the first application of input voltage to the power supply, the stated surge current may be reached for 1/2 cycle of the input line. Following that surge, there will be repetitive peaks of exponentially decaying amplitude for up to 10 or more cycles of the line until steady state operation is reached.

> 128V AC: 70Amps (peak) 256V AC: 70Amps (peak)

#### 5.10.7 OVERLOAD PROTECTION

- 5.10.7.1 An externally accessible circuit breaker is provided to protect the output wiring. The is rated at 6 Amps,250V AC and covers both input voltage ranges.

- 5.10.72 The start-up transformer is protected against overheating during a fault by a 1/2 Amp,250V fast blow fuse. This fuse is mounted on the circuit board and is serviceable only by qualified personnel.

- 5.10.8 REAL INPUT POWER

320 watts input maximum at full rated DC output load.

5.10.9 EFFICIENCY

The ratio of DC output power to real input power at full rated load shall be 0.7 minimum over either input voltage range.

- 5.10.10 LINE VOLTAGE DISTURBANCE

- 5.10.10.1 UNDERVOLTAGE

- 5.10.10.1.1 UNDERVOLTAGE WITHSTAND

The power supply is capable of withstanding any undervoltage condition for any duration without physical damage or degradation.

5.10.10.1.2 RIDE THROUGH

The POK signal(reset to the VS100 mother board) shall remain asserted during one half cycle of less than the minimum line voltage.

5.10.10.1.3 HIGH VOLTAGE TRANSIENTS

NOTE: A spike is defined as a voltage transient, of either polarity and of either common or differential mode, with a rise time (10% to 90 %) of 0.1 microseconds or less and a fall time (to 10%) of 10 microseconds or more.

The average power of spikes shall not exceed 0.5 watts.

5.10.10.1.4 LOW ENERGY TRANSIENTS