# ELTEC-58K-595TEM

Documentation PIG1/68K

Revision A dated 5/86

Documentation PIG1/68k Revision A 5/86 Page -2-

#### (C) 1986 ELTEC Elektronik GmbH, Mainz

This document contains copyrighted information. All rights including those of translation, reprint, broadcasting, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part, are reserved. If single copies are made for professional purposes with written approval of ELTEC, an allowance will have to be paid in accordance with para. 54.2 of Urh.G. For details please contact ELTEC.

ELTEC reserves the right to modify without notice the product described herein in keeping with state-of-the-art technology at any time. Although this document has been reviewed carefully ELTEC refuses any liability due to misprints and detriments caused thereby.

This document is edited and printed by:

ELTEC Elektronik GmbH, D-6500 Mainz

Documentation PIG1/68k Revision A 5/86 Page -3-

#### CONTENTS

Contents How to use this manual?

| 1<br>1 • 1<br>1 • 2                                                                      | Specifications Scope of delivery Hardware Software support Technical features VME Eurocard Specification Nomenclature used in this manual                                                                                                                                                                      |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>3.1<br>3.2<br>3.3<br>3.4<br>4<br>4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.3<br>5 | Adaption to your system Introduction Default setting as board is shipped VMEbus-Interface Base address Address modifier Device addresses Interrupter Adaption to your monitor Monitor synchronisation Video signals Separate lines Composite video signal Blinking Numbers of bitplanes Master/slave operation |

| 7                                                                                        | External access to local bus                                                                                                                                                                                                                                                                                   |

Documentation PIG1/68k Revision A 5/86 Page -4-

| Programmer's information            |

|-------------------------------------|

| Registers of the ACRTC              |

| Hardware accessible registers       |

| Directly accessible registers       |

| FIFO accessible registers           |

| Frame-buffer interface of the ACRT( |

| Introduction                        |

| Colors and bitplanes                |

| Examples to set up the ACRTC        |

| The horizontal display width        |

| Crawl                               |

| Zoom                                |

| Blinking                            |

| Hardware status register            |

|                                     |

Documentation PIG1/68k Revision A 5/86 Page -5-

| Part D  | Hardware                               |

|---------|----------------------------------------|

| 1       | VMEbus interface                       |

| 2       | Control logic for VMEbus and local Bus |

| 2<br>3  | Local hardware status-register         |

| 4<br>5  | Advanced cathode ray tube controller   |

| 5       | Frame-buffer interface                 |

|         | Central timing logic                   |

| 6<br>7  | Two-port-RAM timing generator          |

| 8       | Video shift-register                   |

| 9       | Frame-buffer                           |

| 10      | Monitor interface                      |

| Appendi | ×                                      |

| Α       | Addressmodifier VMEbus                 |

| В       | Jumpers, switches                      |

| С       | Connectors                             |

| D       | Sample program                         |

| Ε       | Layout diagram                         |

| F       | Parts list                             |

| G       | Circuit diagrams                       |

| Н       | Data sheet HD63484                     |

Documentation PIG1/68k Revision A 5/86 Page -6-

# How to use this documentation?

This documentation is divided into four parts to give only as much information as needed for a certain purpose.

Part A contains all general specifications of the product and its documentation like scope of delivery and technical specs and the general nomenclature used in this manual.

Part B decribes the procedure you should follow to adapt the product to your specific system and peripherals.

Part C gives detailed information to the user who wants to program the board himself.

Part D gives detailed information about the hardware-aspects of the board for service etc.

If you only use the board with a software package, that means as a user, not as a programmer, you should find complete information while reading only part B.

#### ELTEC Elektronik GmbH

## ELTEC 68K-SYSTEM

DOCUMENTATION

PIG1/68k

PART A

DO.68 01749

ELTEC-68K-SYSTEM

Documentation PIG1/68k Revision A 5/86 Part A Page -2-

# 1 Scope of delivery

## 1.1 Hardware

PIG1/68k.....Order No FE .68 01748

Consisting of

PIG1/68k with 1MByte frame buffer

Dot clock generator of 55MHz

Factory configured as described

in part B, chapter 2

Documentation PIG1/68k

5 cables FE KAB 1888

PIG2/68k......Order No FE .68 01750

Board set consisting of

PIG1/68k with 1MByte frame buffer

and local extension of another

1MByte frame buffer

Dot clock generator of 55MHz

Factory configured as documented

Documentation-package

consisting of documentations

PIG1/68k and PIG2/68k

2 cables FE KAB 1888

8 cables (4 sets) FE KAB 1726

Cable (SMB-Coax to BNC, 3 mtr)...Order No FE KAB 01888

Cable-set (2 \* SMB-Coax 20 cm)...Order No FE KAB 01726

Documentation PIG1/68k.....Order No DO .68 01749

Documentation PIG2/68k.....Order No DO .68 01751

Documentation PIG1/68k Revision A 5/86 Part A Page -3-

## 1.2 Software support

PIGpac for OS-9/68000 8"/77T....Order No AS OS9 01753

PIGpac for OS-9/68000 5"/40T....Order No AS OS9 01762

PIGpac for OS-9/68000 5"/80T....Order No AS OS9 01763

PIGpac is a complete, modern grafics package, which is completely window-oriented. It consists of an OS-9/68000 de/ice driver with a terminal emulation and an interface to assembler and C language. Some samples and several monitor tables are included.

GKS-0A for OS-9/68000 8"/77T....Order No AS OS9 01770 GKS-0A for OS-9/68000 5"/40T....Order No AS OS9 01773 GKS-0A for OS-9/68000 5"/80T....Order No AS OS9 01771

GKS-0A is an implementation of the Grafical Kernel System in accordance to ISO 7942 and DIN-Standard. A C-binding is provided.

Documentation PIG1/68k Revision A 5/86 Part A Page -4-

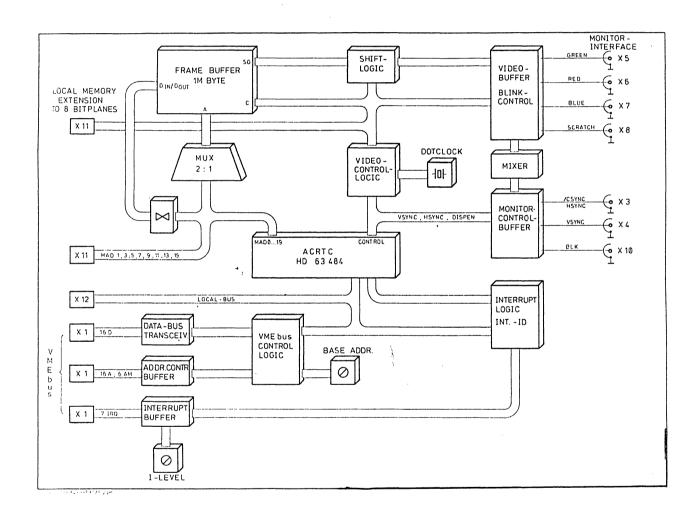

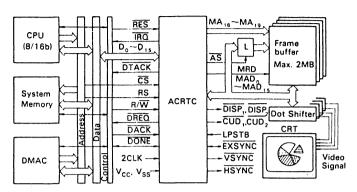

Dia A.2.1: Block diagram PIG1/68k

Documentation PIG1/68k Revision A 5/86 Part A Page -5-

# 2 Technical specifications

- -VMEbus interface in accordance to revision C with interrupter option on all levels

- -Grafics controller ACRTC HD63484

- -Black and white, greyscale and color operation

- -Maximum dotclock 64MHz in a 1 l bitplane configurations

- -Programmable sync format and flexible hardware interface to control nearly every raster scan monitor on the market

- -Modern dual-port video RAM architecture to provide highest drawing speed; useful especially with the ACRTC's powerful bit-block operations

- -Three bitplane configurations:

One bitplane with 8 MegaPixel capacity

Two bitplanes, each with 4 MegaPixel capacity

Four bitplanes, each with 2 MegaPixel capacity

- -Option PIG2/68k to get 8 bitplanes with no restriction in dotclock

- -Video-Zooming with factors of 1, 2 or 4 for both directions; separate vertical zooming with factors of 1 to 16

- -Pixel-by-pixel panning facility in both directions

- -Exact pixel-based blinking attribute

- -Access of local CPU-module prepared

- -Software support PIGpac

- -Software support GKS

Documentation PIG1/68k Revision A 5/86 Part A Page -6-

3 VME Eurocard Specification PIG1/68k

Slave Data Transfer Options A16: D16

Interrupter Options

Any one of

I(1),I(2),I(3),I(4),I(5),I(6) or I(7) (STAT)

Environmental Options

Storage temperature: -55...+85 degree Celsius

Operating temperature: 0...+70 degree Celsius

Maximum operating humidity: 85 Percent relative

Power options max 4.2 A (3.8 A typ) at +5 Volt

Physical configuration options NEXP

Documentation PIG1/68k Revision A 5/86 Part A Page -7-

# 4 Nomenclature of this manual

A hexadecimal notation is identified by a leading dollar sign ("\$").

A binary notation is identified by a leading "B".

A logic low (high) level is identified by "L" ("H") or "0" ("1") independent of the assertion-type of the signal.

Names of level-controlled signals preceded by a slash ("/") indicate that this signal is active low. Names of edge-controlled signals preceded by a slash ("/") indicate that this signal becomes active with the trailing edge.

Positions of jumpers refer to those shown in diagram dia B.1.1, which are identical to pin numbers. If not mentioned otherwise, "J401:1-2" for instance means, that jumper J401 must be set to connect pins 1 and 2.

## ELTEC Elektronik GmbH

# ELTEC 68K-SYSTEM

DOCUMENTATION

PIG1/68k

PART B

DO.68 01749

Documentation PIG1/68k Revision A 5/86 Part B Page -2-

# 1 Introduction

This part of the manual gives you all information necessary to adapt the board to your system, ie to your VMEbus-computer and monitor. If you use ELTEC's PIGpac there should be no need to read other parts of this manual to get started.

Please follow this procedure for adaption:

```

Adaption of the base address - refer to chapter 3

Adaption of the address modifiers - refer to chapter 3

Adaption of desired interrupt level - refer to chapter 3

Adaption to your monitor - refer to chapter 4

Blinking - refer to chapter 4

Adaption of numbers of bitplanes - refer to chapter 5

Master/slave operation - refer to chapter 6

External access to local bus - refer to chapter 7

```

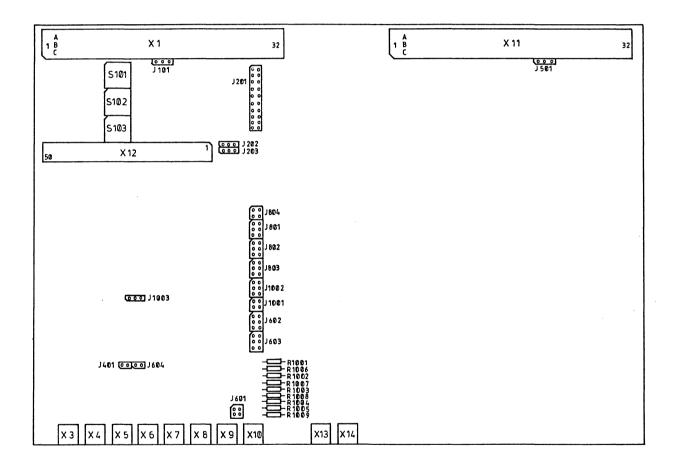

Block diagram Dia A.2.1 gives an overview over the whole board. Diagram Dia B.1.1 shows the position of all jumpers, connectors and switches.

In appendix B you will find a complete list of all jumpers and switches.

In appendix C you will find a complete list of all connectors.

In chapter B.2 you find the default setting as board is shipped.

Documentation PIG1/68k Revision A 5/86 Part B Page -3-

Dia B.1.1: Switches, jumpers, connectors PIG1/68k

Documentation PIG1/68k Revision A 5/86 Part B Page -4-

# 2 Default setting as board is shipped

#### Base address

\$FF8D00

S101:8 S102:D

S103:0 (Non-privileged; i.e. User-Mode I/O)

- Refer to chapter 3.1!

# Address modifier

short supervisory I/O

S103:0

J101:1-2 (AM2 decoded)

- Refer to chapter 3.2!

#### Interrupter

I(7)

J201:1-2

- Refer to chapter 3.4!

#### ELTEC Elektronik GmbH Mainz

ELTEC-68K-SYSTEM

Documentation PIG1/68k Revision A 5/86 Part B Page -5-

## Monitor interface

- Sync signals

separate syncs positive polarity TTL-level

J1001:3-4 J1002:5-6

- Video outputs

R1001 == 0 Ohm

R1002 == 0 Ohm

R1003 == 0 Ohm R1004 == 0 Ohm

R1005 == no resistor

R1006 == no resistor

R1007 == no resistor R1008 == no resistor

R1009 == no resistor

- Dot clock

- Refer to chapter 4!

U601 == 55 MHz

#### Blinking

J1003:1-2

- refer to chapter 4!

disabled

TTL-level

#### ELTEC Elektronik GmbH Mainz

ELTEC-68K-SYSTEM

Documentation PIG1/68k Revision A 5/86 Part B Page -6-

| Number of bitplanes                                                                                                   | 4 bitplanes |

|-----------------------------------------------------------------------------------------------------------------------|-------------|

| J602:1-2<br>J603:1-2<br>J801:1-2<br>J802:1-2<br>J803:1-2<br>J804:1-2<br>J804:3-4<br>J501:1-2<br>- refer to chapter 5! |             |

| Master/slave-mode                                                                                                     | stand-alone |

| J401:1-2<br>J601:1-2<br>J604:1-2<br>- refer to chapter 6!                                                             | •           |

| External access to local bus                                                                                          | disabled    |

| J202:1-2<br>J203:1-2<br>- refer to chapter 7!                                                                         | •           |

Documentation PIG1/68k Revision A 5/86 Part B Page -7-

# 3 VMEbus-Interface

The slave PIG1/68k occupies 64 Byte in short I/O addressing range.

All on-board devices are byte- or word-oriented. While trying to access the board with longword bus transfer cycle or with single-byte transfer on even addresses, a bus-error is generated.

The interrupter module can generate interrupts on all VMEbus interrupt levels, selectable by a jumper. Several interrupt sources can be chosen by software.

The complete VMEbus interface logic is realized via PAL's. So it is possible to make changes in addressing the on-board devices, decoding of address modifiers etc very easy. ELTEC's firmware, however, expects the features documented herein.

The bus grant daisy chain is closed in the printed circuit, so there is no need for modifications on the backplane.

You always have to remove the jumper for the corresponding interrupt acknowledge daisy chain on the backplane.

Documentation PIG1/68k Revision A 5/86 Part B Page -8-

## 3.1 Base address

The base address can be switched via hex-switches S101, S102 and S103 in steps of 64 Bytes (address-lines A15 thru A06 - short I/O).

For adaption to the desired base address its highest nibble must be switched with S101. S102 is for the next nibble (A11 thru A08). S103 determines with its lower bits A07 and A06 of the base address. The upper bits of S103 are used to decode adressmodifier AM2 and AM1. Please refer to chapter B.3.2!

Documentation PIG1/68k Revision A 5/86 Part B Page -9-

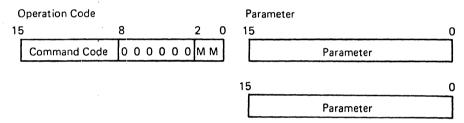

#### 3.2 Address modifier

The address modifiers AM2 and AM1 can be switched via hex-switch S103. Please refer to table Tab B.3.1!

AMO is decoded in a PAL to assert only with AMO=H.

AM5 and AM3 are wired to H, AM4 is wired to L (16-Bit addressing).

With jumper J101 set to position 2-3 it is possible to decode Adressmodifier AM2 as "don't care" to decode the board in the non-proivileged and in the supervisory addressing range.

Please refer to appendix A (Address modifier in the VMEbus-specification) for further details.

Tab B.3.1: Switching the desired address modifier

| AM-Code<br>Hex | AM5 | AM4 | AM3 | AM2 | AM1 | AMØ | S103 | Note           |

|----------------|-----|-----|-----|-----|-----|-----|------|----------------|

| 29             | 1   | 0   | 1   | 0   | 0   | 1   | 0-3  | non-privileged |

| 2B             | 1   | 0   | 1   | 0   | 1   | 1   | 4-7  | reserved .     |

| 2D             | 1   | 0   | 1   | 1   | 0   | 1   | 8-B  | supervisory    |

| 2F             | 1   | 0   | 1   | 1   | 1   | 1   | C-F  | reserved       |

#### Note:

- -The lower two bits of S103 define Address lines A07 and A06 of base address.

- -Decoding of AM2 is only done if jumper J101 is in position 1-2

Documentation PIG1/68k Revision A 5/86 Part B Page -10-

# 3.3 Device addresses

Table Tab B.3.2 shows the relative addresses of all on-board devices.

Tab B.3.2: Relative addresses of all devices

| rel addr |     |                      | Transfer-type |        |  |

|----------|-----|----------------------|---------------|--------|--|

|          | hex | Device               | R/W           | Length |  |

|          | 0   | HD63484 status reg   | Read          | Word   |  |

|          | Ø   | HD63484 address reg  | Write         | Word   |  |

|          | 2   | HD63484 control regs | Both          | Word   |  |

|          | 5   | Hardware status reg  | Both          | Byte   |  |

Documentation PIG1/68k Revision A 5/86 Part B Page -11-

# 3.4 Interrupter

The interrupter module on PIG1/68k is able to generate interrupts on one of any VMEbus interrupt-level. The selection is done by jumper J201. For details please refer to table Tab B.3.3! Please be sure to set the levels of request and acknowledge identically.

If you use the on-board interrupter, you must remove the jumper for the interrupt acknowledge daisy chain on the backplane.

For programming the internal interrupt sources and the interrupt-ID-Byte (vector) please refer to part C!

Tab B.3.3: Selecting the interrupt level

| Jumpering J201  |            |                       |  |  |  |  |

|-----------------|------------|-----------------------|--|--|--|--|

| Desired         | VMEbus     | Interrupt-acknowledge |  |  |  |  |

| interrupt level | IRQ-Level  | level decoding        |  |  |  |  |

| I(7) = /IRQ7    | J201:1-2   | Level 7 = not set     |  |  |  |  |

| I(6) = /IRQ6    | J201:3-4   | Level 6 = J201:19-20  |  |  |  |  |

| I(5) = /IRQ5    | J201:5-6   | Level 5 = J201:17-18  |  |  |  |  |

| I(4) = /IRQ4    | J201:7-8   | Level 4 = J201:17-18  |  |  |  |  |

|                 | •          | J201:19-20            |  |  |  |  |

| I(3) = /IRQ3    | J201:9-10  | Level 3 = J201:15-16  |  |  |  |  |

| I(2) = /IRQ2    | J201:11-12 | Level 2 = J201:15-16  |  |  |  |  |

|                 |            | J201:19-20            |  |  |  |  |

| I(1) = /IRQ1    | J201:13-14 | Level 1 = J201:15-16  |  |  |  |  |

|                 |            | J201:17-18            |  |  |  |  |

|                 |            | J201:19-20            |  |  |  |  |

Documentation PIG1/68k Revision A 5/86 Part B Page -12-

- 4 Adaption to your monitor

- 4.1 Monitor synchronisation

PIG1/68k is able to drive monitors with different logic-levels on the sync line(s). The voltage level is always TTL-level.

Refer to table B.4.1 to see what to do to adapt PIG1/68k to the sync line(s) of your monitor. Please be sure to program the grafic display controller with a suitable parameter set. You have to use the corresponding dotclock generator U601, too.

Refer to Part C for further information about parameter sets for synchronisation and dotclock.

Refer to documentation of PIGpac to choose the correct parameter set for your monitor under control of this package.

To connect your monitor to PIG1/68k you should use the added coaxial cables.

Documentation PIG1/68k Revision A 5/86 Part B Page -13-

Tab B.4.1: Monitor synchronisation PIG1/68k

| HSY | VSY | CSY | Jumper                 | Connection         |

|-----|-----|-----|------------------------|--------------------|

| Р   | Р   | _   | J1002:5-6<br>J1001:3-4 | HSY: X3            |

| Р   | · N |     | J1002:5-6              | HSY: X3            |

| N   | Р   | _   | J1001:1-2<br>J1002:3-4 | VSY: X4<br>HSY: X3 |

| N   | N   |     | J1001:3-4<br>J1002:3-4 | VSY: X4<br>HSY: X3 |

| _   | _   | N . | J1001:1-2<br>J1002:1-2 | VSY: X4<br>CSY: X3 |

#### Notes:

HSY.....Horizontal synchronisation VSY.....Vertical synchronisation

CSY.....Composite synchronisation

P......Positive logic-level (active high)

N.....Negative logic-level (active low)

Documentation PIG1/68k Revision A 5/86 Part B Page -14-

# 4.2 Video signals

## 4.2.1 Separate lines

PIG1/68k is able to generate up to four bitplanes per pixel. Normally the voltage-level is TTL. Please notice, that it is possible to adapt the hardware to reduce the number of planes in order to get higher pixel capacity per plane. Please refer to chapter B.5!

There is a possibility to reduce the output voltage by changing resistors R1001 to R1004. In combination with the input-impedance (mostly 750hm) of the monitor the result is an "analogue" signal. A good approach for 750hm-input and 1Vpp is to use 1000hm resistors instead of 00hm.

Table B.4.2 shows you the connectors for the bitplanes. In case of using a standard RGB-color monitor, one bitplane is not used. If you want to apply a color monitor with a separate white- or intensity-input you can drive it by this scratch-plane. In other cases you can use the plane to control the generate shapes to control the blink attribute (see chapter 4.3!).

Documentation PIG1/68k Revision A 5/86 Part B Page -15-

Tab B.4.2: Bit planes and connectors

| Monitor    | No of planes | X5       | Х6 | Х7       | X8   |

|------------|--------------|----------|----|----------|------|

| B/W<br>B/W | 4 2          | P3<br>P3 | P2 | P1<br>P2 | P0/S |

| B/W        | 1            | Р3       | _  | _        | _    |

| Color      | 4            | G        | R  | В        | S    |

| Color      | 2            | G        |    | R/S      |      |

| Color      | 1            | G        |    |          |      |

#### Notes:

P3-P0...Weight of greyscale modulation to be connected to a monitor with integrated D/A-Conversion

R.....Red-channel

G.....Green-channel

B.....Blue-channel

S.....Scratch-plane

Documentation PIG1/68k Revision A 5/86 Part B Page -16-

# 4.2.2 Composite signal

Via resistors R1001 to R1008 it can be build a simple d/a-converter (R-2\*R-ladder-network) generating an analogue signal at connector X5. Please notice, that this conversion is not always free of glitches. Respectively with dotclocks of more than 40MHz you should use this simple converter only as a first approach.

To get a 1Vp-p video-signal (at 750hm video input) with 16 greyscales R1001 to R1005 must be 1000hm and R1006 to R1008 must be 500hm. If you want to generate a composite video signal, you have to add the composite synchronsignal via R1009 (=ca 150 0hm). Please refer to chapter B.4.1, too!

Tab B.4.3: Components of video mixer

|         | Resistor |          |  |  |  |

|---------|----------|----------|--|--|--|

| Plane   | Serial   | Parallel |  |  |  |

|         |          |          |  |  |  |

| Р3      | R1001    |          |  |  |  |

| P2      | R1002    | R1006    |  |  |  |

| P1      | R1003    | R1007    |  |  |  |

| PØ      | R1004    | R1008    |  |  |  |

| Termina | tor R10  | 105      |  |  |  |

#### Note:

- P() denotes significance of bitplane

ELTEC-68K-SYSTEM

Documentation PIG1/68k Revision A 5/86 Part B Page -17-

## 4.3 Blinking

The blinking attribute can be statically enabled with jumper J1003 set in position 2-3. If blinking is enabled, all shapes generated in the scratch plane blink against background (video-"black"). The blinking rate can be programmed in the ACRTC. Please refer to part C of this manual or to manual of PIGpac.

Documentation PIG1/68k Revision A 5/86 Part B Page -18-

# 5 Number of bitplanes

In most cases PIG1/68k is used in the four bitplane mode, where you get four planes with a capacity of 2Mega-pixels each. Some hardware modifications can be done to define the attributes controlled by the several planes. Please refer to chapter 4!

In some cases it can be necessary to have a higher bitplane capacity. As documented in table Tab B.5.1 you have to make some adaptions.

The X-Y memory configuration depends on programming the ACRTC. Please refer to part C of this manual.

Jumper J501 is reserved for special purposes in combination with the display memory upgrade. It should be set to position 1-2 or left open.

Tab B.5.1: Adapting the bitplane number

| Capacity per<br>plane (pixel) | J602 | Se<br>J603 | t jump<br>J801 |     | J803 | J804       |

|-------------------------------|------|------------|----------------|-----|------|------------|

| 2Mega/4 planes                | 1-2  | 1-2        | 1-2            | 1-2 | 1-2  | 1-2        |

| 4Mega/2 planes                | 3-4  | 3-4        | 3-4            | 3-4 | 3-4  | 1-3<br>2-4 |

| 8Mega/1 plane                 | 5-6  | 5-6        | 5-6            | 5-6 | 5-6  | 1-2<br>3-4 |

Documentation PIG1/68k Revision A 5/86 Part B Page -19-

#### 6 Master/slave operation \_\_\_\_\_\_

If you want to use several PIG1/68k in parallel to work on the same monitor, you must define one board as master, the other(s) as slave(s).

Please be sure to make the following adaptions:

Master - Set jumper J601:1-2 and J601:3-4

- Set jumpers J401 and J604 (default) - Set jumper J601:1-3

Slave

- Remove jumpers J401 and J604

- Remove U601

Connect master and slave via X9, X13, X14 (use cable-set FE KAB 1726!)

The stand-alone mode is nearly the same as the master mode with no connection to other PIG1/68k's and with jumper J601:1-2 only.

Of course it is possible to have several PIG1/68k in stand-alone-mode in one system, having each of them work to a separate monitor.

Please refer to PIGpac manual for software support!

Documentation PIG1/68k Revision A 5/86 Part B Page -20-

# 7 External access to local bus

The complete local address— and databus and most of the lines of local controlbus are wired to connector X12. So it is possible to access to all local devices of PIG1/68k by a separate CPU and/or a DMA-controller, situated on a piggy-back-board, having full advantage of a separate bus. In low-cost applications a local CPU-module can access without the need of a separate VMEbus-backplane.

To make external access possible it is necessary to disable the VMEbus-buffers and -latches. Jumpers J202 and J203 are intended for this purpose.

Because all lines on X12 are decoupled VMEbus-lines, the buslogic and timing on the local bus is the same as on the VMEbus.

To enable the external access, please do the following modifications:

- Set J202:2-3, instead of J202:1-2

- Set J203:2-3, instead of J202:1-2

#### ELTEC Elektronik GmbH

#### ELTEC 68K-SYSTEM

DOCUMENTATION

PIG1/68k

PART C

Documentation PIG1/68k Revision A 5/86 Part C Page -2-

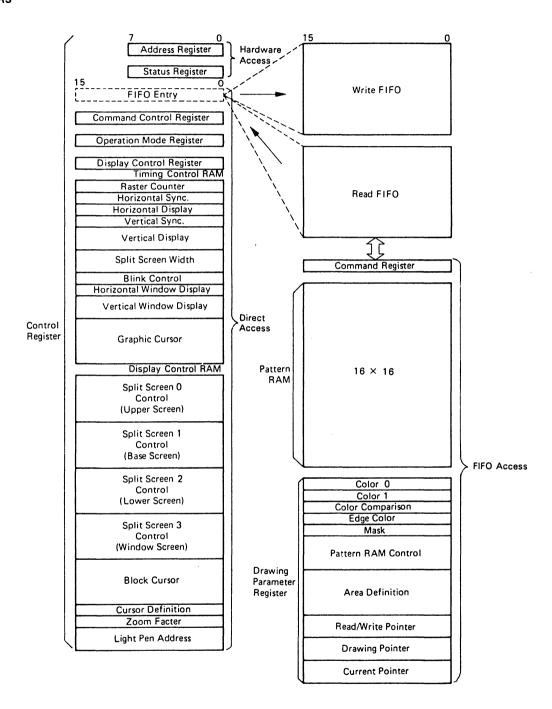

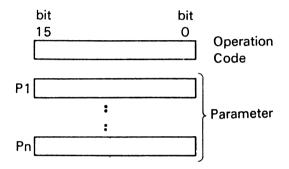

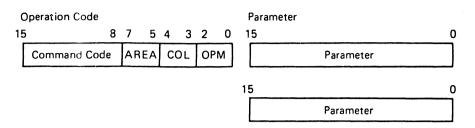

### 1 Registers of the ACRTC

The ACRTC occupies two wordwide VMEbus address locations, which are documented in chapter B.3.3 of this manual. The ACRTC must be accessed as a wordwide device. In some cases only the lowest 8 bits are significant, however.

In this chapter a short introduction is given to the ACRTC's programming model. For more details you should read the data sheet of the controller and other literature, which is published by Hitachi Ltd.

The ACRTC has over two hundred bytes of accessible registers. These are organized as Hardware, Directly and FIFO accessible.

ELTEC-68K-SYSTEM

Documentation PIG1/68k Revision A 5/86 Part C Page -3-

#### 1.1 Hardware accessible registers

The lower address location of the ACRTC provides the status register, when a read-cycle is performed. The status register summarizes the ACRTC state and is used by the CPU to monitor the overall operation of the ACRTC. When a write-cycle is performed to the lower address-location, the address register is activated, in order to program the ACRTC with the address of the desired directly accessible internal register.

Only the lower 8 bits of both registers are significant.

Documentation PIG1/68k Revision A 5/86 Part C Page -4-

#### 1.2 Directly accessible registers

These registers are accessed by prior loading of the address register with the chosen register address. When the CPU accesses the higher VMEbus-address location, the chosen register is activated.

The FIFO entry enables access to FIFO accessible registers using the ACRTC's read and write FIFO's.

The Command Control Register CCR is used to control overall ACRTC operation such as aborting or pausing commands, defining DMA protocols, enabling/disabling interrupt sources etc.

The Operation Mode Register OMR defines basic parameters of ACRTC operation such as frame buffer access mode, display or drawing priority, cursor and display timing skew factors, raster scan mode etc.

The Display Control Register DCR allows the independent enabling and diabling of each of the four ACRTC logical display screens (Base, Upper, Lower and Window). Also this register contains 8 bits of user defineable video attributes, the Attribute Register ATR.

The Timing Control RAM TCR contains registers which define ACRTC video timing. This includes timing specification registers for CRT control signals, logical display screen size and display period, blink timing and so on. The names of some important registers are:

- Horizontal Sync Register HSR

- Horizontal Display Register HDR

- Vertical Sync Register VSR

- Vertical Display Register VDR

- Split Screen Width Register SSW

Documentation PIG1/68k Revision A 5/86 Part C Page -5-

The Display Control RAM DCR contains registers which define logical screen display parameters such as start addresses, raster addresses and memory width. Also included are the cursor(s) definition, zoom factor and light pen registers. The names of some important registers are:

- Memory Width Registers MWR0...MWR3

- Start AddressRegisters SAR0...SAR3

- Zoom Factor Register ZFR

Documentation PIG1/68k Revision A 5/86 Part C Page -6-

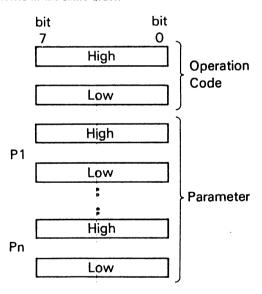

### 1.3 FIFO accessible registers

For high performance drawing, key drawing processor registers are coupled to the CPU via the ACRTC's separate 16-byte read and write FIFO's.

ACRTC commands are sent from the CPU via the write-FIFO to the command register. As the ACRTC completes command execution, the next command is automatically fetched from the FIFO into the command register.

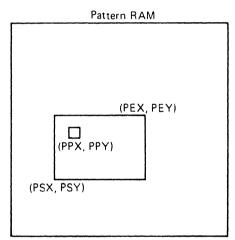

The pattern RAM is used to define drawing and painting patterns. The pattern RAM is accessed using the ACRTC's Read Pattern RAM (RPTN) and Write Pattern RAM (WPTN) register access commands.

The Drawing Parameter Registers DPR define detailed parameters of the drawing process, such as color control, area control and pattern RAM pointers. The DPR's are acessed using the ACRTC's Read Parameter Register (RPR) and Write Parameter Register (WPR) register access commands.

Documentation PIG1/68k Revision A 5/86 Part C Page -7-

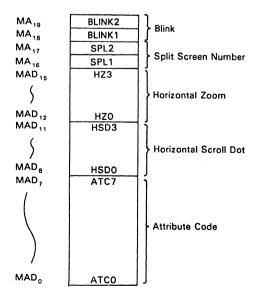

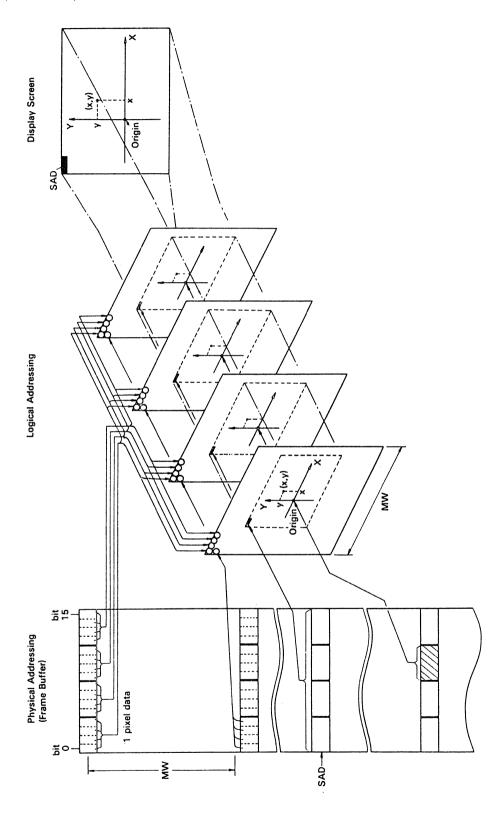

### 2 Frame-buffer interface of the ACRTC

#### 2.1 Introduction

The ACRTC has a 16-bit wide data interface to the frame buffer lines (MADO...MAD15). These 16 bits can be defined to be from 16 pixel in one plane to 16 planes of one pixel. On PIG1/68k all even MAD-lines are connected to the data-port of the frame buffer. All odd lines are used for the frame-buffer extension in the PIG2/68k-upgrade.

On PIG1/68k the frame buffer size is one MegaByte, which can be configured as one bitplane with eight MegaPixel, as two planes with four MegaPixels each or as four planes with two MegaPixels each. Please refer to part B of this manual for correct adaption, concerning the hardware-video-port.

According to the video-read-out configuration the ACRTC must be programmed with the correct Graphic Bit Mode GBM. It is important to have in mind, that the complete hardware is designed for generating 8 bitplanes with one ACRTC. If you use PIG1/68k alone, the effective GBM must be twice the desired number of bitplanes.

One of the design goals of PIG1/68k was to support the high drawing speed of the ACRTC by a suitable frame buffer architecture. Modern video RAM-chips have been used to reduce the need of time for display refresh to an absolute minimum: Only one cycle per raster scan line is necessary for that task. It is sufficient to program the ACRTC with a horizontal display width of one, to load 4096 bits (physical pixels) in the RAM's on-chip shift registers. In the four-bitplane-mode 1024 logical pixels are provided for one raster scan line, which is the maximum in that mode. In the two-bitplane-mode 2048 logical pixels are provided and in the one-bitplane-mode 4096 pixels per raster scan line are possible.

Documentation PIG1/68k Revision A 5/86 Part C Page -8-

The dual-port-RAM architecture brings a very high throughput (factor 4 to 6 in comparison to conventional frame-buffer-concepts). but there are some restrictions. which should be mentioned here:

- The window (fourth screen) has always the same width as the other screens

- The horizontal pan feature (crawl) works always within one module of logical pixels - The horizontal memory width must always

- be defined modulo the number of logical pixels The horizontal memory width has to be a power of two (512, 1024, 2048..)

Some of these restrictions can be compensated by using the powerful instruction set of the ACRTC efficiently. bit-block-operations should be mentioned in this context. Because of the modern frame-buffer architecture they are working and thus can be used extensively without additional host-interaction.

Documentation PIG1/68k Revision A 5/86 Part C Page -9-

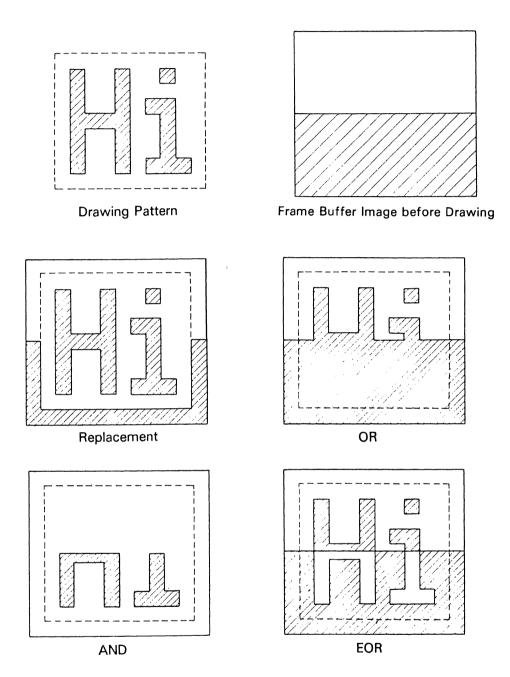

#### 2.2 Colors and Bitplanes

Controlling of the color mode is done with the Drawing Parameter Registers and within that set especially with the color registers COLO and COL1. Please notice, that always all bits must be set according to the desired color. Please refer to table C.2.1 for details!

Tab C.2.1: Color control for PIG1/68k

| Color   | Control      | Register-value |        |        |

|---------|--------------|----------------|--------|--------|

|         | Byte         | GBM=3          | GBM=2  | GBM=1  |

| BLACK   | \$00         | \$0000         | \$0000 | \$0000 |

| GREEN   | <b>\$</b> 01 | \$0101         | \$1111 | \$5555 |

| RED     | \$04         | \$0404         | \$4444 |        |

| BLUE    | \$10         | \$1010         |        |        |

| SCRATCH | \$40         | \$4040         |        |        |

| YELLOW  | <b>\$0</b> 5 | \$0505         | \$5555 |        |

| CYAN    | \$11         | \$1111         |        |        |

| MAGENTA | \$14         | \$1414         |        |        |

| WHITE   | \$15         | \$1515         |        |        |

#### Note:

Color.... means the effect on the monitor when connected as described in chapter B!

Register-value...means the effective value to be written into the appropriate registers with different Grafic Bit Modes GBM

---....denotes impossible configurations

Documentation PIG1/68k Revision A 5/86 Part C Page -10-

### 3 Examples to set up the ACRTC

In table C.3.1 you will find some set-up's for different monitors. It is important to have in mind, that the horizontal CRT sync timing is given in units of memory cycles. The length of one cycle is the dotrate, divided by 32. The length of the vertical parameters are given in units of raster scan lines. Please notice, like mentioned in the ACRTC data sheet, that some of the parameters must be subtracted by one before written into the ACRTC' registers. Table C.3.1 shows adjusted parameters.

#### Please note some general hints:

- The Grafic Address Increment parameter GAI should always be set to 2.

- The board should always be initialized as slave, even in standalone mode.

- The grafic bit mode GBM must always be twice the effective number of bitplanes, if no frame-buffer extension is used.

- The display start addresses must be adjusted by several so-called kluge-factors, which must be subtracted from the desired display start addresses. These factors depend on the ACRTC's mask-version and therefore can change. The given examples are evaluated with a S-mask.

- The horizontal display width HDW should always be set to one. The true parameter must be set in the ATR (Attribute Control) register.

Documentation PIG1/68k Revision A 5/86 Part C Page -11-

Tab C.3.1: Set-up-examples for PIG1/68k (4 bitplane-mode)

| Parameter                | Me   | onitor- | Гуре | Name | ACRTC |

|--------------------------|------|---------|------|------|-------|

| Nates in ()              | 0    | 1       | 2    |      | Reg   |

| Hor Sync Width (1;2)     | 2    | 2       | 3    | HSW  | HSR   |

| Hor Cycle (1;2)          | 27   | 45      | 41   | HC   | HSR   |

| Hor Disp Width (1;2;4)   | 1    | 1       | 1    | HDW  | HDR   |

| Eff Hor Disp Width (1;5) |      | 31      | 31   | -    | ATR   |

| Hor Disp Start (1;2)     | 2    | 6       | 3    | HDS  | HDR   |

| Ver Sync Width (1;2)     | 3    | 3       | 10   | VSW  | VDR   |

| Ver Cycle (1;2)          | 625  |         | 850  | VC   | VSR   |

| Ver Disp Width (1;2)     | 512  | 512     | 785  | SPx  | SSW   |

| Ver Disp Start (1;2)     | 67   | 67      | 40   | VDS  | VDR   |

| Hor Plane Width (1;2)    |      | 1024    | 1024 | MW   | MWR   |

| Graphic Bit Mode (1;2)   | 3    | 3       | 3    | GBM  | CCR   |

| GAI Mode (1;2)           | 2    | 2       | 2    | GAI  | OMR   |

| Operation Mode (1;3)     | 410B | 4108    | 4108 | -    | OMR   |

| Kluge Factor: (2;6)      |      |         |      |      |       |

| Screen Ø (Upper)         | 4    | 4       | 4    |      | SAR0  |

| Screen 1 (Base)          | 0    | 4       | 4    |      | SAR1  |

| Screen 2 (Lower)         | 4    | 4       | 4    |      | SAR2  |

| Screen 3 (Window)        | 0    | 0       | 0    |      | SAR3  |

| Dotclock (7)             | 14   | 48      | 55   |      |       |

| Horiz· frequency in kH:  |      |         |      | •0   |       |

| Field frequency (8)      | 50   | 50      | 50   |      |       |

#### Notes:

- 1...Parameter given not register-value

- 2...Decimal notation

- 3...Hexadecimal notation

- 4...Only one cycle because of Dual-port-RAM

- 5...Please refer to chapter C.4

- 6...To be subtracted from desired display start address

- 7...The dotclock is given in MHz with U601

- 8...In Hz; monitor-type 0 with interlaced fields

Documentation PIG1/68k Revision A 5/86 Part C Page -12-

# 4 The Horizontal Display Width

As mentioned earlier, the effective horizontal display width (HDW) is programmed with register ATR. To be compatible with the ACRTC's normal nomenclature, it is recommended to calculate this parameter like to be written into register HDR.

#### Example:

If you want to have a horizontal display width of 1024 pixels on the screen with the four-bitplane-mode (GBM=3) the equivalent parameter HDW is 31 (32 minus 1).

The lower byte of register HDR should be set to one and the effective horizontal display width must be transformed in the following way:

First step: Complement HDW

Second step: Apply AND-mask of hex 3E

Third step: Write this value into register ATR

Documentation PIG1/68k Revision A 5/86 Part C Page -13-

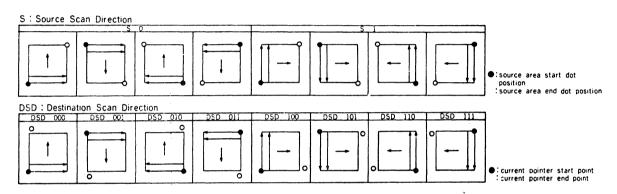

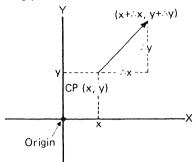

### 5 Crawl

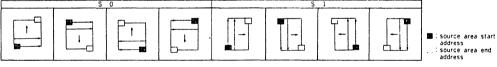

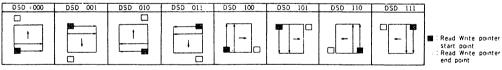

Crawling is defined as repositioning the screen on the display memory in horizontal direction. In general always ACRTC's registers SARx are used for panning. If you want to use the horizontal pixel-by-pixel pan-feature the parameter Start Dot Address SDA within the SAR-registers are used. Those four bits define the offset of the screen position within that module which can be reached with the used grafic bit mode GBM. Please refer to table C.5.1!

Tab C.5.1: Significance of SAR-bits

| GBM | SAR-bits |     |     |     |

|-----|----------|-----|-----|-----|

|     | D11      | D10 | D09 | DØ8 |

|     |          |     |     |     |

| 3   | ×        | ×   | ×   | 1   |

| 2   | ×        | ×   | 2   | 1   |

| 1   | ×        | 4   | 2   | 1   |

#### Note:

GBM....means grafic bit mode, which corresponds to the hardware-adapted number of bitplanes

x.....not used - should be set to zero

1,2,4...binary significance of Start Dot Address

Documentation PIG1/68k Revision A 5/86 Part C Page -14-

### 6 Zoom

Programming the zoom-factor is very easy. The ACRTC has a special Zoom Factor Register ZFR. Four bits are used for the horizontal and another four bits are used for the vertical zoom factor VZF. The vertical zoom factor is used only within the ACRTC to modify vertical display refresh addressing. All 16 factors can be used. The horizontal zoom factor HZF is used by the ACRTC and external hardware, which supports only factors of 1,2 and 4. That is why only these factors should be used for horizontal zooming. Please refer to table C.6.1!

Tab C.6.1: Allowed horizontal zoom factors

| Zoom<br>factor | ZFR<br>D15 | -Bits<br>D14 | for<br>D13 | HZF<br>D12 |

|----------------|------------|--------------|------------|------------|

| 1              | 0          | 0            | 0          | 0          |

| 4              | 0<br>0     | 0<br>0       | 1          | 1          |

#### Note:

ZFR....means Zoom Factor Register HZF....means Horizontal Zoom Factor

Zoom-factor 1 stands for unzoomed display

ELTEC-68K-SYSTEM

Documentation PIG1/68k Revision A 5/86 Part C Page -15-

# 7 Blinking

Blinking is controlled via shapes generated in the scratch bitplane. Blinking must be hardware-enabled with Jumper J1003 as described in part B of this manual. With ACRTC's register BCR (Blink Control Register) the blinking rate can be modified and software-enabled/disabled. Only the BLINK2-feature is supported by the PIG-hardware.

Documentation PIG1/68k Revision A 5/86 Part C Page -16-

# 8 Hardware status register

The hardware status register is an extra byte-wide register. It can be read and written. For address and bus-cycle please refer to chapter B.3!

It is intended to be used normally as ID/vector-register for the VMEbus interrupt-acknowledge cycle. But it can also be used for establishing semaphores and so on.

Please refer to PigPac manual for used and/or reserved bits.

#### ELTEC Elektronik GmbH

#### ELTEC 68K-SYSTEM

DOCUMENTATION

PIG1/68k

PART D

DO.68 01749

Documentation PIG1/68k Revision A 5/86 Part D Page -2-

#### Preface ======

This part of the documentation is dedicated to all users, who want to deal with the hardware in detail, as in field service, for instance. The hardware is designed modular. The several blocks are:

- VMEbus interface

- --> wiring diagram 1

- Control logic for VMEbus and local bus

- --> wiring diagram 2

- Status/vector register

- --> wiring diagram 3

- Advanced Cathode Ray Tube Controller ACRTC

- --> wiring diagram 4

- Frame-buffer interface

- --> wiring diagram 5

- Central timing logic

- --> wiring diagram 6

Two-port-RAM timing generator

- --> wiring diagram 7

- Video shift-register

- --> wiring diagram 8

- Frame-buffer

- --> wiring diagram 9

- Monitor interface

- --> wiring diagram 10

Documentation PIG1/68k Revision A 5/86 Part D Page -3-

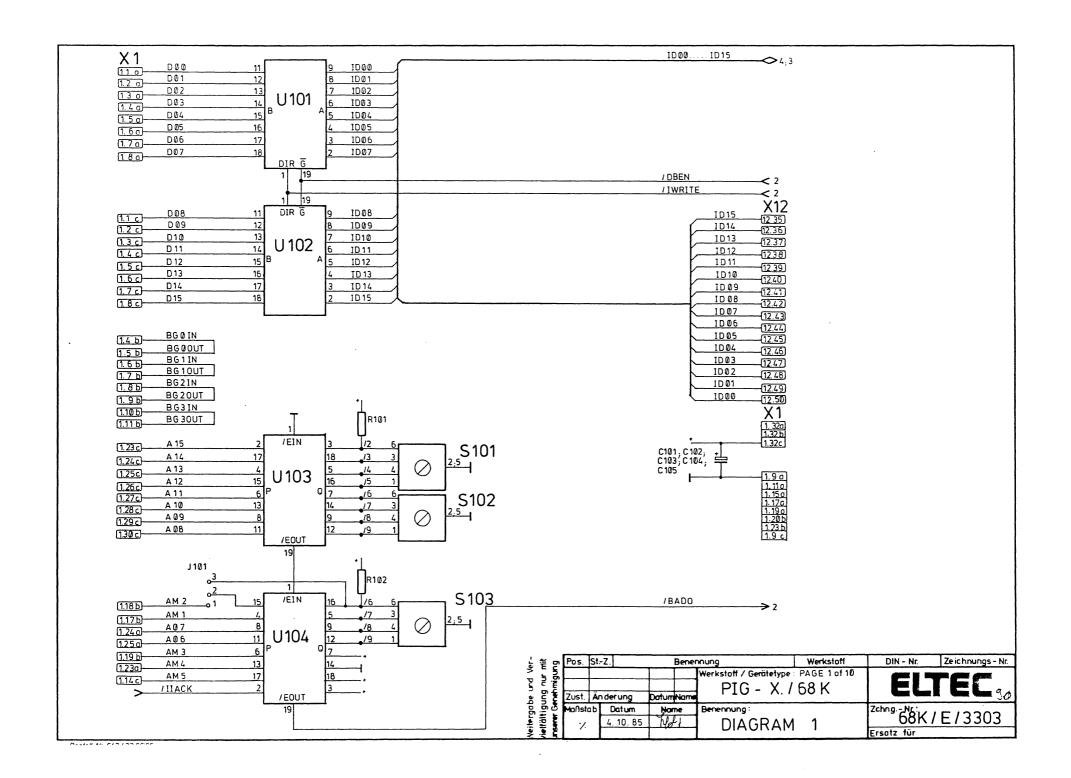

# 1 VMEbus interface

Circuit diagram 1 shows the VMEbus interface.

The data bus is coupled via transceivers U101 and U102. The internal data bus is called ID00 to ID15. U103 and U104 generate the line /BADO (base address decoder out), if the base address and the appropriate address modifiers are decoded.

All internal VMEbus lines have the prefix "I" to show that they are of the same function, but internal.

Hex switches S101, S102 and S103 control the base address. Additionally S103 controls the address modifier AM2 and AM1. J101 can be used to disable decoding of AM2.

Documentation PIG1/68k Revision A 5/86 Part D Page -4-

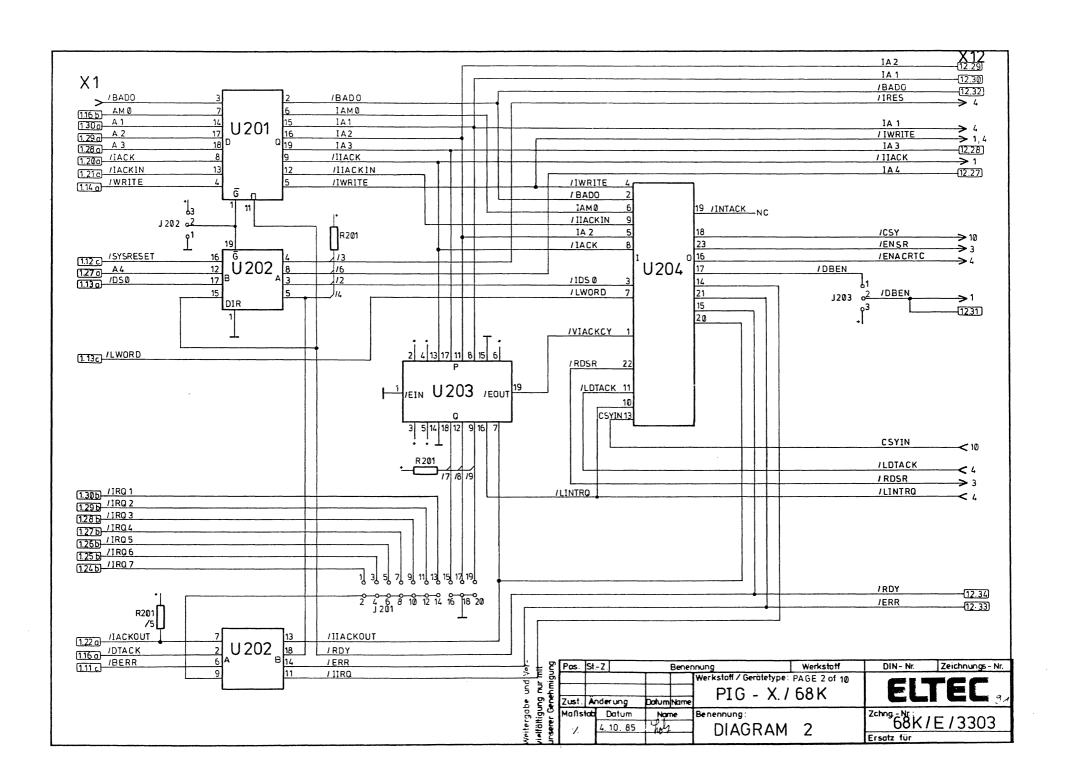

# 2 Control logic for VMEbus and local bus

U201 latches all control lines, which are necessary for internal use. U202 buffers control lines /DS0 and /SYSRESET. Circuit diagram 2 shows details of this module. PAL U204 decodes the devices and handles the VMEbus logic, including the VMEbus interrupt control logic. U203 decodes a valid interrupt acknowledge cycle (line /VIACKCY). U202 buffers the internal IRQ-line. With jumper J201 the desired interrupt level and the appropriate acknowledge level are selected.

All bus grant lines are connected in the printed circuit layout, so there is no need to jumper them on the backplane.

With J202 and J203 the VMEbus transceivers and buffers can be disabled for external access to the local bus.

Documentation PIG1/68k Revision A 5/86 Part D Page -5-

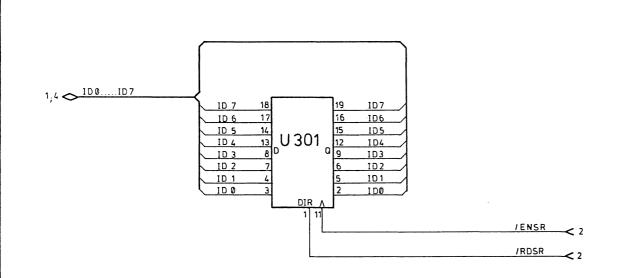

# 3 Status/vector register

Circuit diagram 3 shows the status/vector register.

U301 is a 8 bit wide register, called PIG.STAT. The register can be programmed to contain the interrupt vector. Otherwise it can be used as a general purpose register to store semaphores etc.

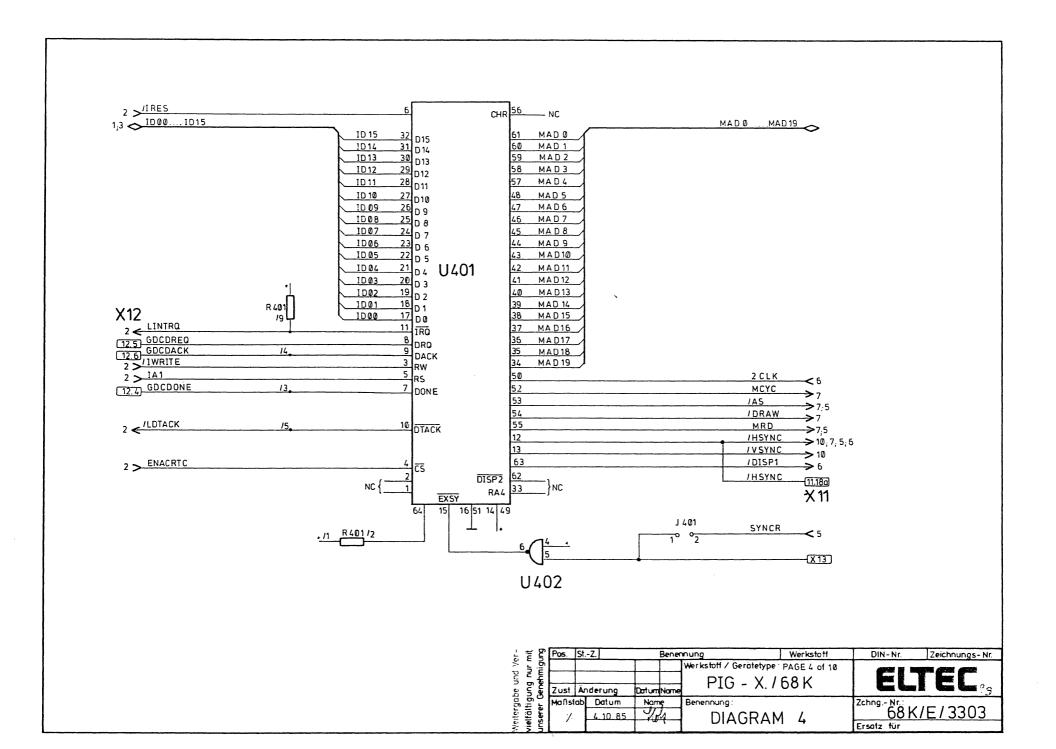

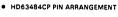

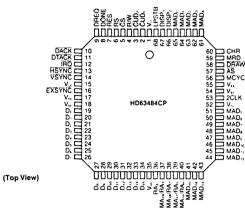

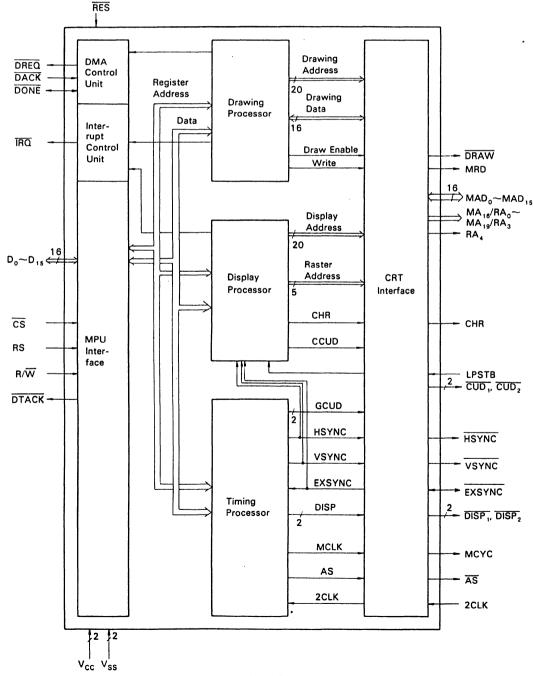

4 Advanced Cathode Ray Tube Controller (ACRTC)

Circuit diagram 4 shows the ACRTC-module.

U401 is the central device of the board. It is decoded by the line /ENACRTC. NAND-gate U402 is used for external synchronisation of the board.

J401 is used for master/slave operation.

Documentation PIG1/68k Revision A 5/86 Part D Page -6-

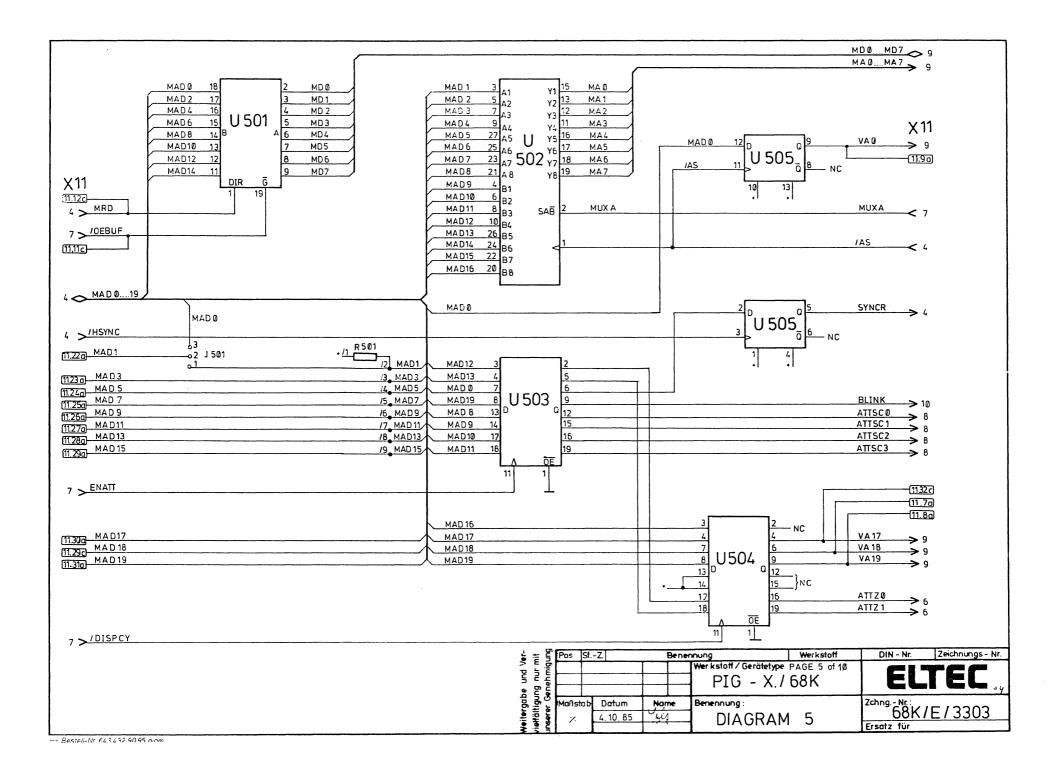

### 5 Frame-buffer interface

Circuit diagram 5 shows details of this module.

U501 is a buffer, which connects the multiplexed data/address-bus of the ACRTC with the databus of the frame-buffer. U502 is a registered multiplexer to address the frame-buffer. U503 and U504 are used to store some of the ACRTC's attribute-bits and the video-address-lines VA17-VA19. These lines are used to select the different RAM-banks. U505 stores the least significant video-address-line VA0, which must be done, because of the ACRTC's multiplexed memory bus.

Line SYNCR is used to synchronize other PIG-board(s).

Documentation PIG1/68k Revision A 5/86 Part D Page -7-

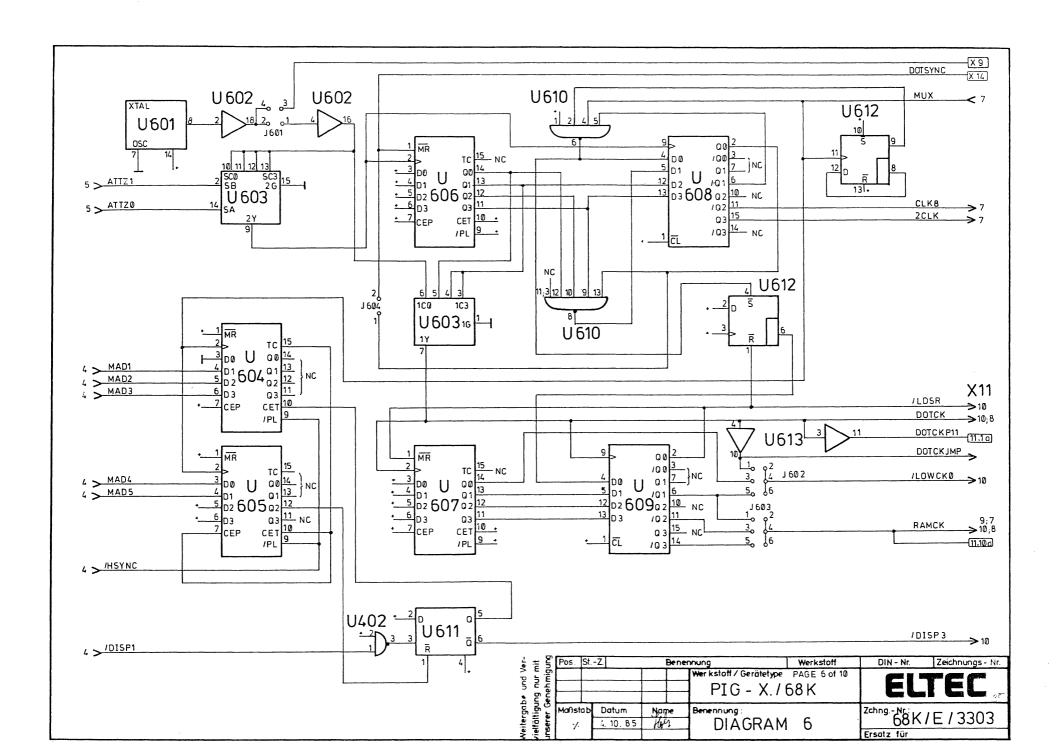

### 6 Central timing logic

Circuit diagram 6 shows details of this module.

U601 is the central dot clock oscillator, which can/must be adapted to the desired monitor parameter set. Jumper J601 defines whether the dotclock comes from the on-board oscillator or from another PIG-board. U606 is clocked by the dotclock to generate other timing control lines. U608 buffers these lines to get a defined and stable timing relationship. The line 2CLK clocks the ACRTC and line CLK8 is used to control the RAM-timing. J602 and J603 must be set properly according to the desired bitplane mode.

U607 and U609 have nearly the same function as U606 and U608, but are clocked via a selectable frequency to control the horizontal video zoom capability.

U604 and U605 form a display-enable-signal, which is independent of the ACRTC. This must be done, because the ACRTC does not support the modern two-port-video-RAM's properly. The desired horizontal display width must be programmed with attribute lines MAD1 to MAD5. The ACRTC's horizontal width parameter determines only, how often a video refresh cycle will be done per raster scan line. Normally one video refresh cycle is necessary.

Jumpers J601 and J604 are used in master/slave-configurations.

Documentation PIG1/68k Revision A 5/86 Part D Page -8-

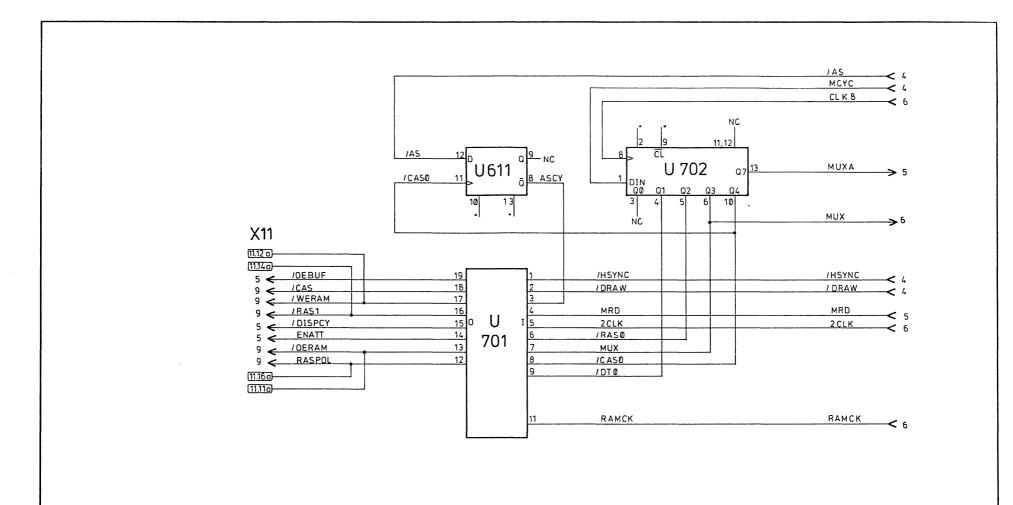

# 7 Two-port-RAM timing generator

Circuit diagram 7 shows details of this module.

Shift register U702 generates basic timing signals, which are used in PAL U701 to form the RAM-control-lines.

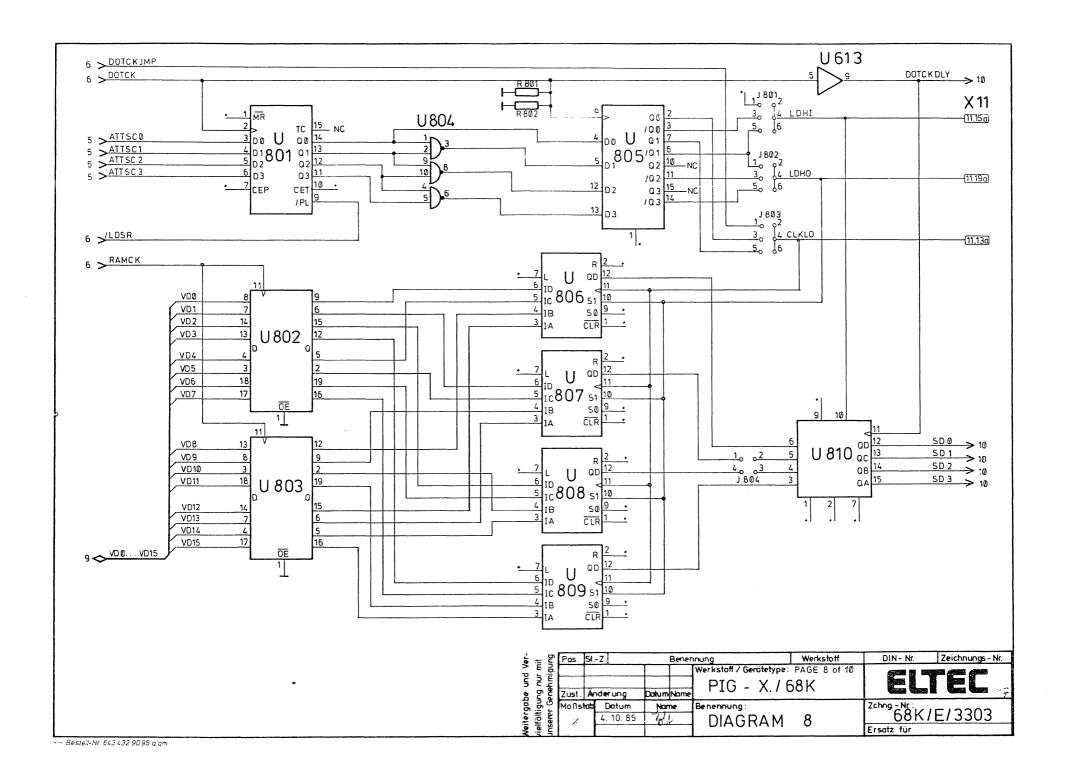

# 8 Video shift-registers

For details see circuit diagram 8!

U802 and U803 store a group of 16 pixels, which are read out of the frame buffer at a time. Counter U801 generates several load-pulses for the shift registers. The chip is programmed with lines ATTSCx, which are the ACRTC's start dot address. With this circuitry it is possible to program the phase relationship between the line RAMCK, which serve as a clock to buffer the video data and the lines LDHI and LDLO, which load two shift register modules.

The first set of shift registers U806 to U809 is clocked by line CLKLO. The pixel-rate is multiplied by four in this stage. The next stage is built by shift register U810, which has different functions: In the four-bitplane-mode it serves only as a register; in other modes it increases the pixel-rate once more. It is important to notice, that jumpers J602, J603, J801, J802, J803 and J804 must be set properly according to the desired numer of bitplanes.

Documentation PIG1/68k Revision A 5/86 Part D Page -9-

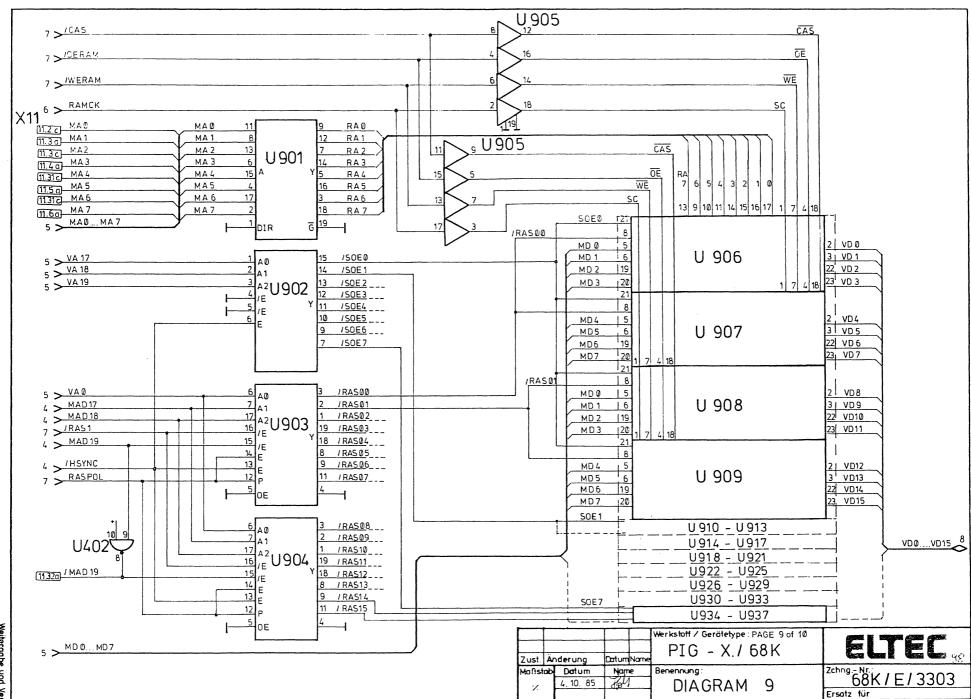

### 9 Frame-buffer

For details see circuit diagram 9!

U906 to U937 are dual-port-video-RAM's, containing the bitmap, generated by the ACRTC. U901 buffers the multiplexed RAM-address-lines. The RAM-chips are organized to 8 banks of 4 chips each. U902 controls the serial port of the several banks. U903 and U904 activate two out of 16 different /RASxx-lines to select two RAM-chips at a time for the ACRTC's random access to the frame-buffer. On PIG1/68k all odd lines of the ACRTC's memory port are connected to the frame-buffer, having all even lines reserved for the eight bit version of the board PIG2/68k.

In case of a RAM-refresh-cycle during the horizontal sync period, all chips will be activated at the same time. Refresh-control is achieved by line RASPOL.

Documentation PIG1/68k Revision A 5/86 Part D Page -10-

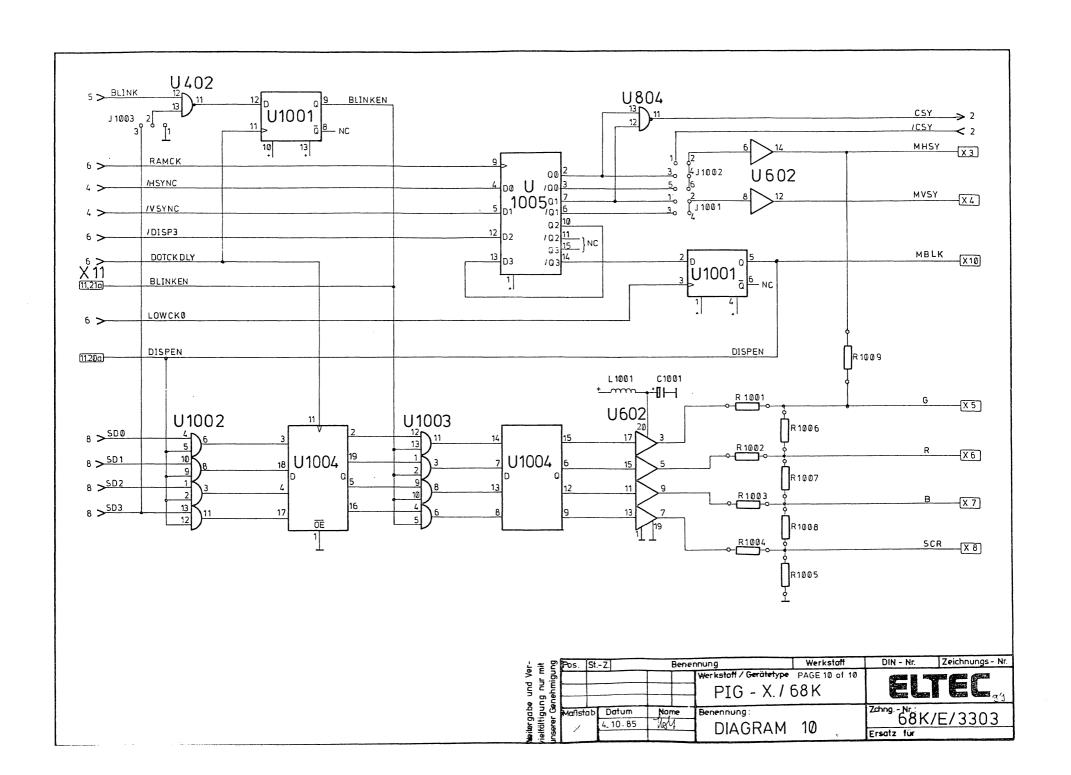

# 10 Monitor interface

For details see circuit diagram 10!

Video-lines SDx are 'ANDed' with the synchronized display enable signal DISPEN, which is available at connector X10 as MBLK and at connector X11 for the local display memory extension. The video-lines are clocked the first time and then ANDed with the blink-enable line BLINKEN. After the second register stage they are driven with buffer U602 and connected to the resistor-network for optional greyscale operation.

The monitor sync signals are synchronized with U1005. With jumpers J1101 and J1102 the polarity can be selected. Another two buffers of U602 are used to drive both lines, which are available at connectors X3 (HSY) and X4 (VSY).

#### ELTEC Elektronik GmbH

#### ELTEC 68K-SYSTEM

DOCUMENTATION

PIG1/68k

APPENDIX

Documentation PIG1/68k Revision A 5/86 Appendix Page -2-

Appendix A: Address modifier VMEbus

| hex Address<br>Code 5 4 3                                                      | modifier<br>2 1 0       | Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Note                                                                                             |

|--------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 3F H H H H 3E H H H H 3C H H H H 3C H H H H 3S H H H H H 3S H H H H 3S H H H H |                         | Standard Supervisory Ascending Standard Supervisory Program Standard Supervisory Data Undefined Standard Non-Privileged Ascend Standard Non-Privileged Program Standard Non-Privileged Data Undefined Undefined Undefined Undefined Short Supervisory I/O Undefined Undefined Short Non-Privileged I/O Undefined Undefined Extended Supervisory Ascending Extended Supervisory Program Extended Supervisory Data Undefined Extended Non-Privileged Ascend Extended Non-Privileged Program | 1<br>2<br>2<br>2<br>2<br>1<br>2<br>2<br>2<br>1<br>1<br>2<br>2<br>3<br>1<br>1<br>1<br>1<br>1<br>1 |

| 09 L L H<br>08 L L H<br>00-07 L L L                                            | L L H<br>L L L<br>x x x | Extended Non-Privileged Data<br>Undefined<br>Undefined                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1<br>2<br>2                                                                                      |

- 1....Defined by VMEbus Specification 2....Definition reserved

- 3....Defined by user

Documentation PIG1/68k Revision A 5/86 Appendix Page -3-

Appendix B: Jumpers, switches

| Id No                                                                                                                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Refer to chapter                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$102<br>\$103<br>J101<br>J201<br>J202<br>J203<br>J401<br>J501<br>J602<br>J603<br>J604<br>J801<br>J802<br>J803<br>J804<br>J1001 | VMEbus base address VMEbus base address VMEbus address modifier Decoding of AM2 VMEbus interrupt level External access External access Master/slave-operation Operation of PIG2-config Master/slave-operation Selects no of bitplanes Selects no of bitplanes Master/slave-operation Selects no of bitplanes | B.3.1; D.1<br>B.3.2; D.1<br>B.3.2; D.1<br>B.3.4; D.2<br>B.7; D.2<br>B.7; D.2<br>B.6; D.4<br>B.5; D.5<br>B.6; D.6<br>B.5; D.6<br>B.5; D.6<br>B.5; D.6<br>B.5; D.8<br>B.5; D.8<br>B.5; D.8<br>B.5; D.8<br>B.5; D.8<br>B.5; D.8<br>B.5; D.8<br>B.5; D.8<br>B.5; D.8<br>B.5; D.8 |

| J1002<br>J1003                                                                                                                  | Jumper for H-sync<br>Enables blinking                                                                                                                                                                                                                                                                                                                                                                                                                        | B.4.3; D.10                                                                                                                                                                                                                                                                  |

Documentation PIG1/68k Revision A 5/86 Appendix Page -4-

# Appendix C: Connectors

| Id No Function Type                                                                         |        |

|---------------------------------------------------------------------------------------------|--------|

| X1 VMEbus-connector P1 96-pin DIN<br>X2 not used                                            | N41612 |

| X3 H-sync autput Mini BNC X4 V-sync autput Mini BNC                                         |        |

| X5 Green output Mini BNC X6 Red output Mini BNC                                             |        |

| X7 Blue output Mini BNC X8 Scratch output Mini BNC                                          | ,      |

| X9 Dotclock output/input Mini BNC                                                           |        |

| X10 Blanking output Mini BNC X11 Local frame buffer bus 64-pin DIN                          |        |

| X12 Local bus 2*25 pin f X13 External synchronisation Mini BNC X14 Prescaler reset Mini BNC | remale |

Documentation PIG1/68k Revision A 5/86 Appendix Page -5-

Connector X1 (VMEbus)

Signals in brackets have no connection to the board.

| Pin No               | Row A    | Row B      | Row C      |

|----------------------|----------|------------|------------|

| 1                    | D00      | (/BBSY)    | DØ8        |

| 2                    | D01      | (/BCLR)    | DØ9        |

| 3                    | D02      | (/ACFAIL)  | D10        |

| 1<br>2<br>3<br>4     | DØ3      | /BG0IN     | D11        |

| 5                    | DØ4      | /BG00UT    | D12        |

| 6                    | D05      | /BG1IN     | D13        |

| 6<br>7               | D06      | /BG10UT    | D14        |

| 8                    | D07      | /BG2IN     | D15        |

| 9                    | GND      | /BG20UT    | GND        |

| 10                   | (SYSCLK) | /BG3IN     | (/SYSFAIL) |

| 11                   | GND      | /BG30UT    | /BERR      |

| 12                   | (/DS1)   | (/BRØ)     | /SYSRESET  |

| 13                   | /DS0     | (/BR1)     | /LWORD     |

| 14                   | /WRITE   | (/BR2)     | AM5        |

| 15                   | GND      | (/BR3)     | (A23)      |

| 16                   | /DTACK   | AMØ        | (A22)      |

| 17                   | GND      | AM1        | (A21)      |

| 18                   | (/AS)    | AM2        | (A20)      |

| 19                   | GND      | AM3        | (A19)      |

| 20                   | /IACK    | GND        | (A18)      |

| 21                   | /IACKIN  | (SERCLK)   | (A17)      |

| 22                   | /IACKOUT | (SERDAT)   | (A16)      |

| 23                   | AM4      | GND        | A15        |

| 23<br>24             | A07      | /IRQ7      | A14        |

| 2 <del>4</del><br>25 | A06      | /IRQ6      | A13        |

| 25<br>26             | A05      | /IRQ5      | A12        |

| 26<br>27             | A04      | /IRQ4      | A11        |

| 2 <i>1</i><br>28     | A03      | /IRQ3      | A10        |

|                      |          |            |            |

| 29                   | A02      | /IRQ2      | A09        |

| 30                   | A01      | /IRQ1      | A08        |

| 31                   | (-12V)   | (+5VSTDBY) | (+12V)     |

| 32                   | +5V      | +5V        | +5V        |

Documentation PIG1/68k Revision A 5/86 Appendix Page -6-

Connector X11

This connector is used for PIG2/68k-configuration.

| Pin No                                                         | Row A                                                                                                | Row B             | Row C                                                         |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                      | DOTCLKP11 GND MA1 MA3 MA5 MA7 VA18 VA19 VA0 RAMCK                                                    | +5V<br>GND        | GND<br>MA0<br>MA2<br>MA4<br>GND<br>GND<br>-12V<br>+5V<br>+12V |

| 11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21 | /OERAM /WERAM CLKLO /RAS1 LDHI RASPOL /CAS /HSYNC LDLO DISPEN BLINKEN                                | GND<br>+5V        | /OEBUF<br>MRD                                                 |

| 22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32 | MAD1<br>MAD3<br>MAD5<br>MAD7<br>MAD9<br>MAD11<br>MAD13<br>MAD15<br>MAD15<br>MAD17<br>MAD19<br>/MAD19 | GND<br>GND<br>+5V | MAD18<br>+5V<br>MA6<br>VA17                                   |

Documentation PIG1/68k Revision A 5/86 Appendix Page -7-

Connector X12

This connector is dedicated for external access to local bus. Lines in () are not used.

| 1 reserved 2 reserved 3 RCTRLØ 4 /GDCDONE 5 /GDCDREQ 6 /GDCDACK 7 /IDSØ 8 /IWRITE 9 /IRES 10 (/IDS1) 11 (SYSCLK) 12 (A19) 13 (A18) 14 (A17) 15 (A16) 16 (A15)                                                                                                                                         | Pin No<br>odd                                                                                                      | Signal                                                                                                                                                                                                                | Pin No<br>even                                                                                                                      | Signal                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 17 (IA14) 18 (IA13) 19 (IA12) 20 (IA11) 21 (IA10) 22 (IA09) 23 (IA08) 24 (IA07) 25 (IA06) 26 (IA05) 27 IA04 28 IA03 29 IA02 30 IA01 31 /DBEN 32 /BADO 33 /ERR 34 /RDY 35 ID15 36 ID14 37 ID13 38 ID12 39 ID11 40 ID10 41 ID09 42 ID08 43 ID07 44 ID06 45 ID05 46 ID04 47 ID03 48 ID02 49 ID01 50 ID00 | 3<br>57<br>9<br>11<br>13<br>15<br>17<br>19<br>21<br>22<br>27<br>29<br>31<br>33<br>33<br>37<br>34<br>43<br>45<br>47 | RCTRLØ<br>/GDCDREQ<br>/IDSØ<br>/IRES<br>(SYSCLK)<br>(A18)<br>(A16)<br>(IA14)<br>(IA12)<br>(IA10)<br>(IA08)<br>(IA06)<br>IA04<br>IA02<br>/DBEN<br>/ERR<br>ID15<br>ID13<br>ID11<br>ID09<br>ID07<br>ID07<br>ID05<br>ID03 | 4<br>6<br>8<br>10<br>12<br>14<br>16<br>18<br>20<br>22<br>24<br>26<br>28<br>30<br>32<br>34<br>36<br>38<br>40<br>42<br>44<br>46<br>48 | /GDCDONE /GDCDACK /IWRITE (/IDS1) (A19) (A17) (A15) (IA13) (IA11) (IA07) (IA05) IA03 IA01 /BADO /RDY ID14 ID12 ID10 ID08 ID04 ID04 ID02 |

Documentation PIG1/68k Revision A 5/86 Appendix Page -8-

## Appendix D: Sample program

```

********************

* Demonstration for PIG1 / HD 63484

* This program shows the initialization of the ACTRC and draws

on the screen one rectangle and some lines

* (C) Eltec Elektronik GmbH Mainz

* rb 220586

************************

OS9-specific declarations

use <oskdefs.d>

* some default stack size

Stk

100

HDA

pigdemo,(Prgrm<<8)!Objct,(ReEnt<<8)!1,0,Stk,pigdemo

psect

end of OS9-specific declarations

$ff8d00

* Hardware Adress of Master Status

acrtc

equ

$100000

* Total memory is 1 megawords

memtot

egu

đ

* log (2) of Bit/pixel for PIG2;

GRM

equ

3

this can be 1, 2 or 3.

* Base screen is specified

* Pixel/line

DN

1<<30

equ

linpix equ

1024

memwid equ

linpix>>(4-GBM)

* 512 Words/line (16 bit;

8 bit with PIG1)

memtot/memwid

linnum equ

* total number of lines

memtot-(785*memwid)-4 * Start Address (upper left)

4 is 'Kluge factor'

startad equ

DN+((memtot-memwid)<<4) * Drawing Pointer for (0,0)

drawpoi equ

on Base Screen

GAI

equ

Operation Mode Register OMR

* Start, Slave, GAI=2, Dual Access

OMR

$4108+(GAI<<4)

equ

Display Control Register DCR

* Enable Base Screen;

DCR

$4020

equ

ATR=$20 i.e. HDW=31

```

Documentation PIG1/68k Revision A 5/86 Appendix Page -9-

```

********************

*

Table for Display Control Ram ($c0 .. $de)

dispoon dc.w

0,memwid,startad>>16,(startad&$ffff) * upper

0,memwid,startad>>16,(startad&$ffff) * base

dc.w

0,memwid,startad>>16,(startad&$ffff) * lower

dc.u

dc.w

0,memwid,startad>>16,(startad&$ffff) * window

dc.w

0.0.0.0.0.0

* Cursor, zoom

************************

Drawing Parameter register contents

*

parreq: dc.w

$0000,$ffff,$ffff,$ffff * Color Registers

$0000,$0000,$00f0 * Pattern Ram Control Registers

dc.w

dc.w

0,0,1023,2047

* Area boundaries

*********************

pigdemo: movem.1 d0-d7/a0-a6,-(a7)

* Pointer to status reg. of ACRTC

move.1 #acrtc,a0

lea.l

2(a0),a1

* Pointer to data register

move

#$2,(a0)

#$8000,(a1)

* Abort (Reset ACRTC)

move

move

#$4,(a0)

* slave mode, display stop

* Init Timing Control Ram

move

#$0,(a1)

intimct

bsr

bsr

clrscrn

#300,d2

* draw rectangle at <d2>,<d3>

move

#200,d3

move

bsr

rect

* draw some lines

her

drautst

movem.1 (a7)+,d0-d7/a0-a6

059

F$Exit

* OS9-specific finish

```

Documentation PIG1/68k Revision A 5/86 Appendix Page -10-

```

*

set RW POINTER to lower left

setrwp: move

#$080c,d1

* Write Pattern Ram

wrfifo

bsr

move.1

#drawpoi,d1

* write lower half register

swap

d 1

bsr

wrfifo

#$080d,d1

move

bsr

wrfifo

swap

d 1

* upper half

wrfifo

bsr

rts

*

Move graphics cursor to x=\langle d2\rangle; y=\langle d3\rangle

*

#$8000,d1

* AMOVE command

move

amove:

wrfifo

bsr

* X

move

d2,d1

wrfifo

bsr

* Y

move

d3,d1

bsr

wrfifo

rts

*

write one byte into the fifo

wrfifo: move

#0,(a0)

* status register is addressed

wrfif1: move

(a0),d6

* read status register

* Write fifo ready?

#2,d6

and

* Wait for it

beq.s

wrfif1

* write data to fifo

d1,(a1)

move

rts

```

Documentation PIG1/68k Revision A 5/86 Appendix Page -11-

```

Initialize Timing Control Ram;

This is for monitor type 2 (see PIG documentation, part C)

* Timing Control RAM init.

#$82,(a0)

intimct: move

* HorCycle, HorSyncWid 82* HorDspStrt, HorDispWid 84

move

\#(41((8)+3.(a1)

#(3<<8)+1,(a1)

mnve

move

#850,(a1)

* VertCycle

86

\#(40<(8)+10,(a1)

* VerDspStrt, VerSyncWid 88

move

#785,(a1)

* Base Screen Width

move

move

#($9c-$8c).d0

* Clear Regs 8c..9c

clr9c

#0,(a1)

move

sub

#2,d0

bpl.s

clr9c

move

#$c0,(a0)

* Display Control RAM

move

#22.d0

* 22 regs total

dispcon(pc),a2

lea

displop move

(a2)+,(a1)

#1,d0

sub

bne.s

displop

move

#$2,(a0)

* Init control regs

#GBM<<8,(a1)

* CCR: remove Abort, set bit/pixel

move

move

#$4,(a0)

* OMR

#OMR, (a1)

move

* Start, Slave, GAI=2, Dual Access

move

#$6,(a0)

* DCR

move

#DCR,(a1)

Initialize Origin to lower left

#$0400.d1

move

* ORG command

wrfifo

bsr

move.1

#drawpoi,d1

* (0,0) is lower left corner

swap

d1

wrfifo

* transfer longword in 2 parts

bsr

d1

swap

wrfifo

bsr

rts

```

Documentation PIG1/68k Revision A 5/86 Appendix Page -12-

```

Initialize parameter registers

clr

* Init par registers

parreg(pc),a2

lea

inpalop: move

#$0800,d1

* WPR Command

or

d2,d1

* Mask in Reg No.

wrfifo

bsr

(a2)+,d1

* Load item from table

move

bsr

wrfifo

add

#1,d2

#12,d2

CMP

bne

inpalop

#$1800,d1

move

* WPTN Write Pattern Ram

bsr

wrfifo

move

#16,d1

bsr

wrfifo

* fill all 16 words with $ffff

#16,d2

* d2 is counter

move

#$ffff,d1

patlop: move

wrfifo

bsr

#1,d2

sub

bne.s

patlop

rts

clrscrn: bsr

setrwp

move

#$5800,d1

* Clear Screen to dark

wrfifo

bsr

* Data is 'dark'

clr

d 1

bsr

wrfifo

#memwid,d1

* X extension of area to clear

move

wrfifo

bsr

* Y

move

#linnum,d1

bsr

wrfifo

rts

```

## ELTEC Elektronik GmbH Mainz

Documentation PIG1/68k Revision A 5/86 Appendix Page -13-

```

* draw rectangle at <d2>,<d3>

rect:

bsr

amove

#$9400,d1

* RRCT command

move

rect1: bsr

wrfifo

#100,d1

* X extension

move

bsr

wrfifo

move

#150,d1

* Y extension

wrfifo

bsr

rts

Draw lines from lower left to the upper edge

drawtst: move

#1800.d4

* x-coordinate on upper edge

linlop: clr

d2

* start at 0,0

clr

dЗ

* set starting point

bsr

amove

#$8800,d1

* ALINE command

move

bsr

wrfifo

d4,d1

wrfifo

move

* X at endpoint

bsr

move

#1800,d1

* Y is always at maximum

bsr

wrfifo

#100,d4

sub

* decrement X

bne.s

linlop

rts

ends

* this is specific for OS9

```

Documentation PIG1/68k Revision A 5/86 Appendix Page -14-

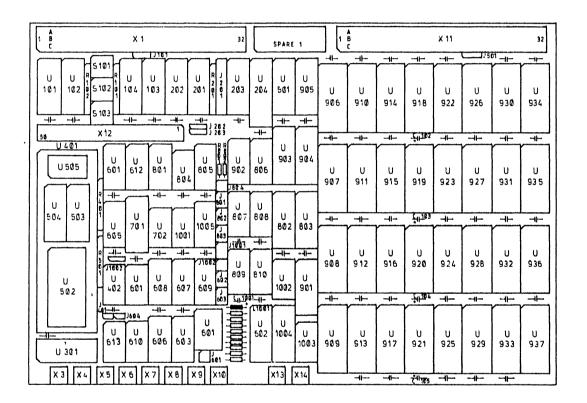

Appendix E: Layout diagram PIG1/68k

Documentation PIG1/68k Revision A 5/86 Appendix Page -15-

### Appendix F: Parts list

The character in the part number identifies the type:

```

B.....Battery

C.....Condensator

D.....Diode, single LED, rectifier

F....Fuse

J.....Jumper

K.....Relais

L....Inductivity, transformer

Q.....Transistor, triac, thyristor

R....Resistor (fixed/variable), Network

S....Switch

T.....Test point

U.....Integrated circuit, display, quartz

```

#### Other abreviations:

X.....Connector

Ta.....Tantalum capacitor Cer....Ceramic capacitor MF.....Metal film

Documentation PIG1/68k Revision A 5/86 Appendix Page -16-

| Part no  | Description                                 |

|----------|---------------------------------------------|

| X1       | 96-pin male connector DIN 41612, rows a,b,c |

| X2<br>X3 | Mini-BNC                                    |

| X4       | Mini-BNC                                    |

| X5       | Mini-BNC                                    |

| Х6       | Mini-BNC                                    |

| X7       | Mini-BNC                                    |

| X8       | Mini-BNC                                    |

| X 9      | Mini-BNC                                    |

| X10      | Mini-BNC                                    |

| X 1 1    | 96-pin female connector DIN 41612, rows a,b |

| X12      | 2*25 pins female                            |

| X13      | Mini-BNC-Buchse abgewinkelt                 |

| С        | Block cap. 47nF/50V; AVX                    |

Documentation PIG1/68k Revision A 5/86 Appendix Page -17-

| Part no              | Description                                                             |

|----------------------|-------------------------------------------------------------------------|

| U102<br>U103         | 74LS645-1 on socket<br>74LS645-1 on socket<br>AM25LS2521<br>AM25LS2521  |

| R101<br>R102         | Resistornetwork 8*3k3<br>Resistornetwork 8*3k3                          |

| C102<br>C103         | Ta 10uF/16V<br>Ta 10uF/16V<br>Ta 10uF/16V<br>Ta 10uF/16V<br>Ta 10uF/16V |

| S101<br>S102<br>S103 | Hex switch<br>Hex switch<br>Hex switch                                  |

| J101                 | Jumper 1*3 pin                                                          |

Documentation PIG1/68k Revision A 5/86 Appendix Page -18-

| Part no | Description                   |

|---------|-------------------------------|

| U201    | 74LS373                       |

| U202    | 74LS641-1 on socket           |

| U203    | AM25LS2521                    |

| U204    | PAL20L10 on socket (PIG1*2.x) |

| R201    | Resistornetwork 8*3k3         |

| J201    | Jumper 2*10 pin               |

| J202    | Jumper 1*3 pin                |

| J203    | Jumper 1*3 pin                |

ELTEC Elektronik GmbH Mainz

ELTEC-68K-SYSTEM

Documentation PIG1/68k Revision A 5/86 Appendix Page -19-

Part no Description

U301 74LS374

Documentation PIG1/68k Revision A 5/86 Appendix Page -20-

| Par | t no | Description                                    |

|-----|------|------------------------------------------------|

| _   |      | HD63484-8 (S-mask or newer) on socket<br>74F00 |

| R   | 401  | Resistornetwork 8*330                          |

| J   | 401  | Jumper 1*2 pin                                 |

Documentation PIG1/68k Revision A 5/86 Appendix Page -21-

| Part no                              | Description                                         |

|--------------------------------------|-----------------------------------------------------|

| U501<br>U502<br>U503<br>U504<br>U505 | 74LS245<br>74LS604<br>74LS374<br>74LS374<br>74LS374 |

| R501                                 | Resistornetwork 8*3k3                               |

| J501                                 | Jumper 1*3 pin                                      |

Documentation PIG1/68k Revision A 5/86 Appendix Page -22-

| Part no                                                                                              | Description                                                                                      |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| U601<br>U602<br>U603<br>U604<br>U605<br>U606<br>U607<br>U608<br>U609<br>U610<br>U611<br>U612<br>U613 | QG 55MHz on socket 74F244 74F352 74LS163 74LS163 74F163 74F175 74F175 74F175 74F20 74LS74 74F243 |

| J601<br>J602<br>J603<br>J604                                                                         | Jumper 2*2 pin<br>Jumper 2*3 pin<br>Jumper 2*3 pin<br>Jumper 1*2 pin                             |

Documentation PIG1/68k Revision A 5/86 Appendix Page -23-

| Part no | Description                 |            |

|---------|-----------------------------|------------|

|         | PAL16L8 on socket<br>74F164 | (PIG1*1.x) |

Documentation PIG1/68k Revision A 5/86 Appendix Page -24-

| Part no                                                              | Description                                                                 |